# VME-QIC2/X Cartridge Tape Controller Hardware Reference Manual

INTEGRATED SOLUTIONS 1140 Ringwood Court San Jose, California 95131 (408) 943-1902

UNIX is a trademark of AT&T Bell Laboratories. DEC and TS11 are trademarks of Digital Equipment Corporation.

490055 Rev. B

November 1986

Copyright 1985, 1986 by Integrated Solutions. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means (e.g., electronic, mechanical, photocopying, recording) without the prior written permission of Integrated Solutions.

The information in this publication is subject to change without notice.

#### PREFACE

This manual describes the Integrated Solutions VME-QIC2/X Cartridge Tape Controller board. The text provided in this manual includes a product overview, specifications, configuration information, and programming information. The manual is divided into five sections:

- SECTION 1: This section describes the general features and architecture of the VME-QIC2/X tape controller board.

- SECTION 2: This section lists the VME-QIC2/X specifications.

- SECTION 3: This section provides information regarding the VME-QIC2/X switch and jumper configuration options.

- SECTION 4: This section describes the VME-QIC2/X tape controller software interface.

- SECTION 5: This section describes the VME-QIC2/X real time clock software interface.

APPENDIX A: This appendix describes the VME-QIC2/X variable length record header block format.

iv

# TABLE OF CONTENTS

| SECTION : | 1: IN7 | TRODUCTION         .         .         .         .         1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |        | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           |        | 1.1.1 Data Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |        | 1.1.2 Variable Size Records                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |        | 1.1.3 Programming Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |        | 1.1.4 Real Time Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 1.2    | Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | 1.2    | 1.2.1 Control Microprocessor         1.2.1 Control Microprocessor         1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |        | 1.2.2 Data Buffer         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1         1.1.2.1 |

|           |        | 1.2.3 EPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |        | 1.2.5 EFROM         1.1.5         1.1.5         1.1.5         1.1.5           1.2.4 VMEbus Interface         1.1.5         1.1.5         1.1.5         1.1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | 12     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 1.3    | Slave Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SECTION 2 | 2: SPE | ECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |        | Form Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |        | Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | 2.3    | Tape Controller Software Interface   2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 2.4    | Transfer Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |        | Real Time Clock         2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |        | Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |        | <b>6</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           |        | Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |        | Address Modifiers         2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |        | Electrical Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |        | Environmental Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           | 2.12   | VMEbus Specified Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SECTION   | 3: CO  | NFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 3.1    | VMEbus Request Level (J2–J9 and J11–J14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 3.2    | VMEbus Cycle Timeout (J15–J18)         3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           | 3.3    | VMEbus Interrupt Level (SW1-3 and SW1-4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 3.4    | VMEbus Interrupt Vector (SW1-1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 3.5    | DTB Master Cycle Address Modifiers (SW1-2 and J10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 3.6    | VMEbus Slave Address Configurations (J19, J20, and SW2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SECTION 4 | 4: TA  | PE CONTROL SOFTWARE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | 4.1    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           |        | Register Definitions         .         .         .         .         .         .         4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |        | 4.2.1 Command Pointer Register (TCPR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |        | 4.2.2 Extended Command Pointer Register (TXCPR) 4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           |        | 4.2.3 Alternate Extended Command Pointer Register (ATXCPR) 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |        | 4.2.4 Status Register (TSSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |        | 4.2.5 Extended Status Register 0 (XST0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |        | 4.2.6 Extended Status Register 1 (XST1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |        | 4.2.7 Extended Status Register 2 (XST2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |        | 4.2.7 Extended Status Register 2 (XS12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | 4.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 4.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |        | <b>4.3.2</b> Message Packet Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 4.3.3 General Status Handling Information . |     | • |     | • | • | • | • | • | 4-14         |

|---------------|---------------------------------------------|-----|---|-----|---|---|---|---|---|--------------|

| 4.4           | Commands                                    | • • | • |     | • | • | • | • | • | 4-16         |

|               | 4.4.1 Command Packet Definitions            |     | • |     | • | • | • | • | • | 4-16         |

|               | 4.4.2 Get Status Command                    |     | • |     | • | • | • | • | • | 4-19         |

|               | 4.4.3 Read Command                          |     | • |     | • | • | • | • | • | <b>4-2</b> 0 |

|               | 4.4.4 Write Characteristics Command         |     | • |     | • | • | • | • | • | 4-21         |

|               | 4.4.5 Write Command                         | • • | • |     | • | • | • | • | ٠ | 4-23         |

|               | 4.4.6 Position Command                      |     | • |     | • | • | • | • | • | 4-24         |

|               | 4.4.7 Format Command                        |     | • |     | • | • | • | • | • | 4-25         |

|               | 4.4.8 Initialize Command                    | ••• | • | • • | • | • | • | • | • | 4-26         |

| SECTION 5: RT | IC SOFTWARE INTERFACE                       | • • | • | ••• | • | • | • | • | • | 5-1          |

| APPENDIX A: V | VARIABLE RECORD FORMAT                      |     |   |     | • |   | • | • | • | A-1          |

# LIST OF FIGURES

| Figure 2-1.  | VME-QIC2/X Control Register Map                            | 2-6  |

|--------------|------------------------------------------------------------|------|

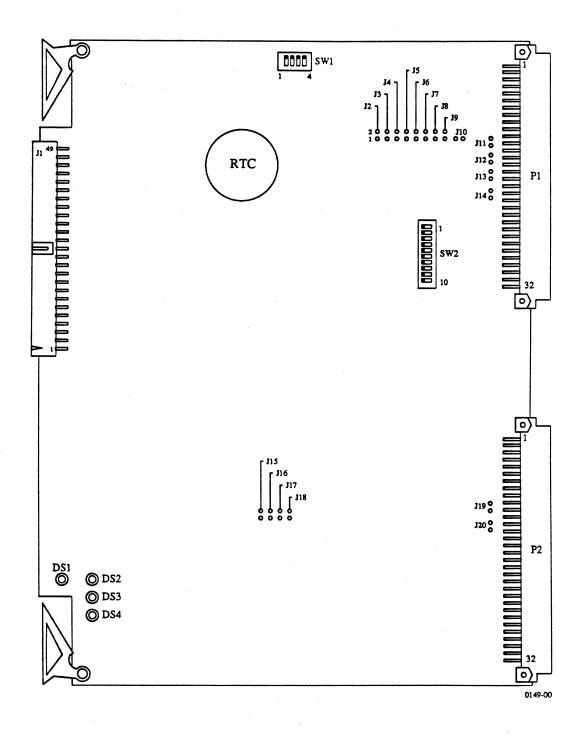

| Figure 3-1.  | VME-QIC2/X Board Layout                                    | 3-2  |

| Figure 4-1.  | TCPR Register Format                                       | 4-3  |

| Figure 4-2.  | TXCPR Register Format                                      | 4-4  |

| Figure 4-3.  | ATXCPR Register Format                                     | 4-5  |

| Figure 4-4.  | TSSR Register Format                                       | 4-5  |

| Figure 4-5.  | XSTO Register Format                                       | 4-7  |

| Figure 4-6.  | XST1 Register Format                                       | 4-9  |

| Figure 4-7.  | XST2 Register Format                                       | 4-9  |

| Figure 4-8.  | XST3 Register Format                                       | 4-9  |

| Figure 4-9.  | Command Packet Format                                      | 4-10 |

| Figure 4-10. | Message Packet Format                                      | 4-12 |

| Figure 4-11. | Command Packet Header Word Format                          | 4-16 |

| Figure 4-12. | Memory/Tape Data Byte Positioning (Case 1)                 | 4-18 |

| Figure 4-13. | Memory/Tape Data Byte Positioning (Case 2)                 | 4-19 |

| Figure 4-14. | Get Status Command Packet                                  | 4-19 |

| Figure 4-15. | Read Command Packet                                        | 4-20 |

| Figure 4-16. | Write Characteristics Command Format — Command Packet      | 4-21 |

| Figure 4-17. | Write Characteristics Command Format — Characteristic Data | 4-21 |

| Figure 4-18. | Write Command Packet                                       | 4-23 |

| Figure 4-19. | Position Command Packet                                    | 4-24 |

| Figure 4-20. | Format Command Packet                                      | 4-25 |

| Figure 4-21. | Initialize Command Packet                                  | 4-26 |

| Figure 5-1.  | Clock Register Format                                      | 5-1  |

Figure A-1. Variable Length Record Header Block Format . . .

A-1

. .

.

# LIST OF TABLES

| Table 2-1.         VMEbus Connector P1 Pin Assignments         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <th>•</th> <th>2-2</th>       | •                                                                                                                                                 | • | • | • | • | •   | • | • | • | • | • | • | 2-2  |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|-----|---|---|---|---|---|---|------|------|

| Table 2-2.         VMEbus Connector P2 Pin Assignments         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td>•</td> <td>2-3</td>       | •                                                                                                                                                 | • | • | • | • | •   | • | • | • | • | • | • | 2-3  |      |

| Table 2-3. I/O Port Connector J1 Pin Assignments       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                 | • | • | • | • | •   | • | • | • | • | • | • | 2-4  |      |