**XT-4000E** Product Specification and OEM Manual

# **XT-4000E**

Product Specification and OEM Manual

Document 1011004 Revision B September 1988

| REVISION RECORD |                |                   |

|-----------------|----------------|-------------------|

| Revision        | Date Published | Revised Contents  |

| 01              | February 1987  | Preliminary Issue |

| Α               | July 1987      | General Changes   |

| В               | September 1988 | General Changes   |

Document No: 1011004

#### WARRANTY

**Maxtor** warrants the XT-4000E Family of disk drives against defects in materials and workmanship for a period of twelve months, for the original purchaser. Direct any questions regarding the warranty to your **Maxtor** Sales Representative. **Maxtor** maintains Customer Service Centers for the repair/reconditioning of all **Maxtor** products. Direct all requests for repair to the **Maxtor** Service Center in San Jose. This assures you of the fastest possible service.

#### **REGULATORY APPROVALS**

| UL Recognition obtained:    | File Number E87276         |

|-----------------------------|----------------------------|

| CSA Certification obtained: | File Number LR54048        |

| VDE Recognition obtained:   | Registration Number 37230G |

Address comments concerning this manual to:

#### **Maxtor Corporation**

Technical Publications 211 River Oaks Parkway San Jose, California 95134-1913 Telephone: (408) 432-1700 Telex: 171074 FAX: (408) 433-0457 The contents of this manual may be revised without prior notice.

© Copyright 1987 by Maxtor Corporation, San Jose, California, USA. All rights reserved

#### PREFACE

**Maxtor** reserves the right to make changes and/or improvements to its products without incurring any obligation to incorporate such changes or improvements in units previously sold or shipped.

**Maxtor** publishes descriptive Brochures and Data Sheets, an OEM Manual, and a Quick Reference Guide for each product line. In addition, important changes to a product are conveyed in the form of a Technical Bulletin sent to all product customers of record. Changes that affect the content of any manual are covered by publishing addendum or revisions to the affected manual.

# TABLE OF CONTENTS

| 1.0 IN     | TRODUCTION                                           | 1 |

|------------|------------------------------------------------------|---|

|            | Concret Description                                  | 4 |

| 1.1<br>1.2 | General Description                                  |   |

| 1.2        | Drive Features                                       | 2 |

| 2.0 PR     | RODUCT SPECIFICATIONS                                | 3 |

| 2.0 11     |                                                      |   |

| 2.1        | Performance Specifications                           | 3 |

| 2.2        | Functional Specifications                            | 3 |

| 2.3        | Physical Dimensions                                  | 4 |

| 2.4        | Environmental Limits                                 | 4 |

| 2.5        | DC Power Requirements                                |   |

| 2.6        | Reliability Specifications                           |   |

| 2.7        | Error Rates                                          |   |

| 2.6        | Standards and Regulations                            | 7 |

|            |                                                      |   |

| 3.0 FU     | JNCTIONAL CHARACTERISTICS                            | 9 |

| 3.1        | Read/Write and Control Electronics                   | ^ |

| 3.1        | Drive Mechanism                                      | - |

| 3.2        |                                                      | - |

| 3.3<br>3.4 | Air Filtration System                                |   |

| 3.4<br>3.5 | Read/Write Heads and Disks                           |   |

| 0.0        |                                                      | 2 |

| 4.0 TH     | IEORY OF OPERATION                                   | 4 |

|            |                                                      | - |

| 4.1        | Spindle Motor Control1                               | 5 |

| 4          | 1.1.1 Hardware Configuration                         | 6 |

| 4          | 1.1.2 Spindle Modes of Operation                     | 7 |

| 4.2        | Actuator Control1                                    | 9 |

| 4          | 2.1 Servo Pattern                                    | 0 |

| 4          | 2.2.2 Block Description                              | 1 |

|            | A Read Amplifier/Pulse Detector                      | 3 |

|            | B Phase-Locked Oscillator 2                          | 4 |

|            | C Synchronization Detector and Servo Data Separator2 | 4 |

|            | D Data and Index Decoder2                            | 4 |

|            | E Hard Sector Control 2                              | 5 |

|            | F Position Demodulator Control 2                     | 5 |

|            | G Main Servo Control Loop 2                          |   |

|            | H Microprocessor Controller2                         | 6 |

|            | I Jumpers2                                           |   |

| 4.3        | Read/Write Channel 2                                 |   |

| 4          | I.3.1 HDA Flex Circuit Interface2                    | 7 |

#### TABLE OF CONTENTS

| Α              | Preamplifier Integrated Circuit                                                                       | 27  |

|----------------|-------------------------------------------------------------------------------------------------------|-----|

| В              | Power                                                                                                 | 27  |

| С              | Head Selection                                                                                        | 27  |

| D              | Read Signal                                                                                           | 31  |

| E              | WRITE Mode and Write Unsafe                                                                           | 31  |

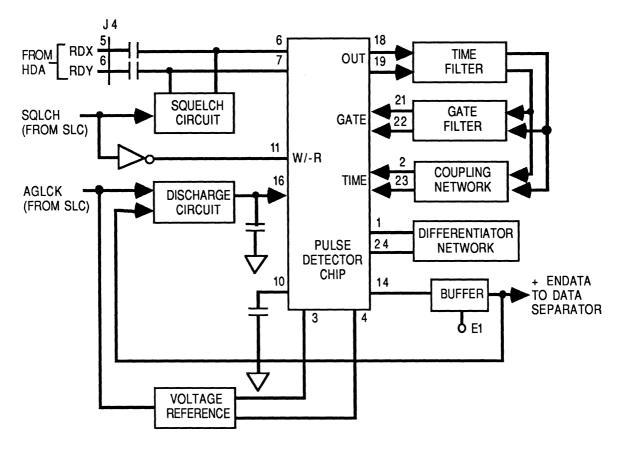

| 4.3.2          | Pulse Detector                                                                                        | 31  |

| А              | Signal Amplification Using AGC                                                                        | 32  |

| В              | Signal Filtering                                                                                      | 32  |

| С              | Pulse Qualification/Peak Detection                                                                    | 32  |

| D              | Write-to-Read and Head Switch Recovery                                                                | 34  |

| 4.3.3          | Clock Recovery and Decoding                                                                           | 35  |

| А              | Data Separator                                                                                        | 36  |

| В              | ENDEC, READ Mode                                                                                      | 37  |

| 4.3.4          | Write Path and Encoding                                                                               | 37  |

| А              | Soft Sector WRITE                                                                                     | 38  |

| В              | Hard Sector WRITE                                                                                     | 38  |

| С              | Encoding Data                                                                                         | 39  |

| D              | Encoding Rules                                                                                        | 39  |

| 4.3.5          | Address Mark Detection                                                                                | 39  |

|                |                                                                                                       |     |

| 5.0 FUNCT      | IONAL OPERATION                                                                                       | 41  |

|                |                                                                                                       |     |

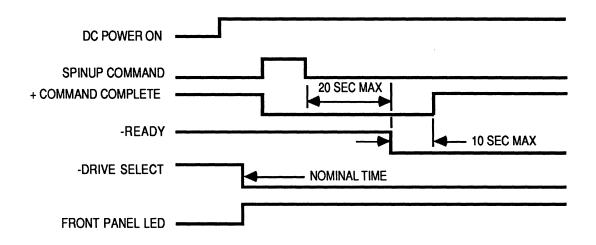

|                | ver Up Sequence                                                                                       |     |

|                | e Selection                                                                                           |     |

| 5.3 Driv       | e Termination                                                                                         | 43  |

|                |                                                                                                       |     |

| 6.0 ELECT      | RICAL INTERFACE                                                                                       | 44  |

| 6.1 Con        | tral Innut Linco                                                                                      | E 4 |

| 6.1.1          | trol Input Lines<br>HEAD SELECT 2 <sup>0</sup> , 2 <sup>1</sup> , 2 <sup>2</sup> , and 2 <sup>3</sup> |     |

| 6.1.1          | HEAD SELECT 2°, 2°, 2°, 2°, and 2°           WRITE GATE                                               |     |

| 6.1.2          | READ GATE                                                                                             |     |

|                |                                                                                                       |     |

| 0              |                                                                                                       | ••  |

| 6.1.5<br>6.1.6 | TRANSFER REQ ADDRESS MARK ENABLE                                                                      |     |

| ••••••         |                                                                                                       |     |

| A              | Soft Sector Mode Only                                                                                 |     |

| B              | Hard and Soft Sector Modes                                                                            |     |

|                | Itrol Output Lines                                                                                    |     |

| 6.2.1          | DRIVE SELECTED                                                                                        |     |

| 6.2.2          |                                                                                                       |     |

| 6.2.3          | CONFIG-STATUS DATA                                                                                    |     |

| 6.2.4          | TRANSFER ACK                                                                                          |     |

| 6.2.5          | ATTENTION                                                                                             | 70  |

11

# TABLE OF CONTENTS

| 6.2.6 INDEX7                                                | 1  |

|-------------------------------------------------------------|----|

| 6.2.7 ADDRESS MARK FOUND (Soft Sector)7                     | 1  |

| 6.2.8 SECTOR MARK (Hard Sector)7                            | 2  |

| 6.2.9 COMMAND COMPLETE7                                     | 3  |

| 6.3 Spindle Synchronization Control Option7                 | 3  |

| 6.4 Data Transfer Lines7                                    | 4  |

| 6.4.1 NRZ READ DATA7                                        | 5  |

| 6.4.2 NRZ WRITE DATA7                                       | 5  |

| 6.4.3 READ/REFERENCE CLOCK                                  | 6  |

| 6.4.4 WRITE CLOCK7                                          | 7  |

| 7.0 PHYSICAL INTERFACE                                      | 8  |

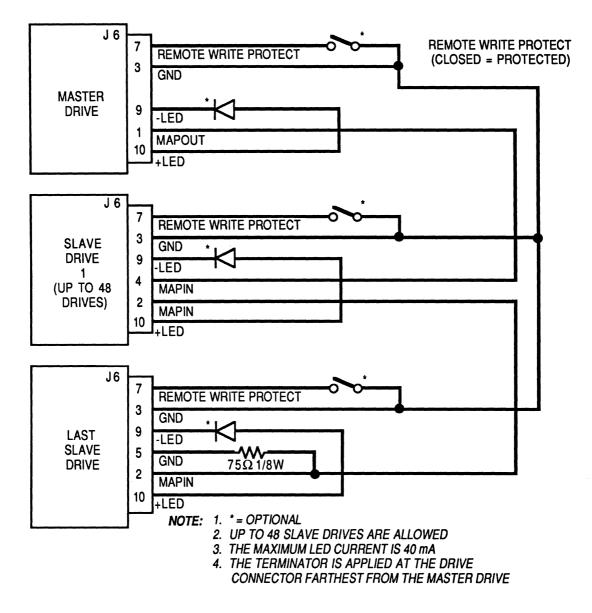

| 7.1 J1/P1 Connector7                                        | '9 |

| 7.2 J2/P2 Connector                                         |    |

| 7.3 J3/P3 Connector                                         |    |

| 7.4 J4/P4 Frame Ground Connector                            |    |

| 7.5 J6/P6 Auxiliary Connector                               |    |

|                                                             |    |

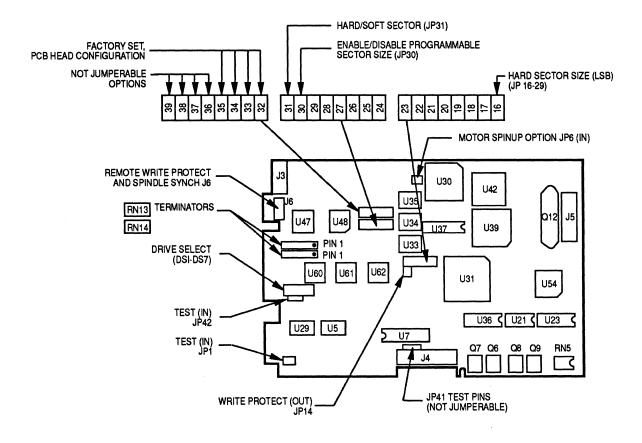

| 8.0 PHYSICAL SPECIFICATIONS                                 | 4  |

|                                                             |    |

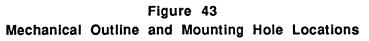

| 8.1 Mounting Orientation                                    |    |

| 8.2 Mounting Holes                                          |    |

| 8.3 Physical Dimensions                                     |    |

| 8.4 Shipping Requirements                                   |    |

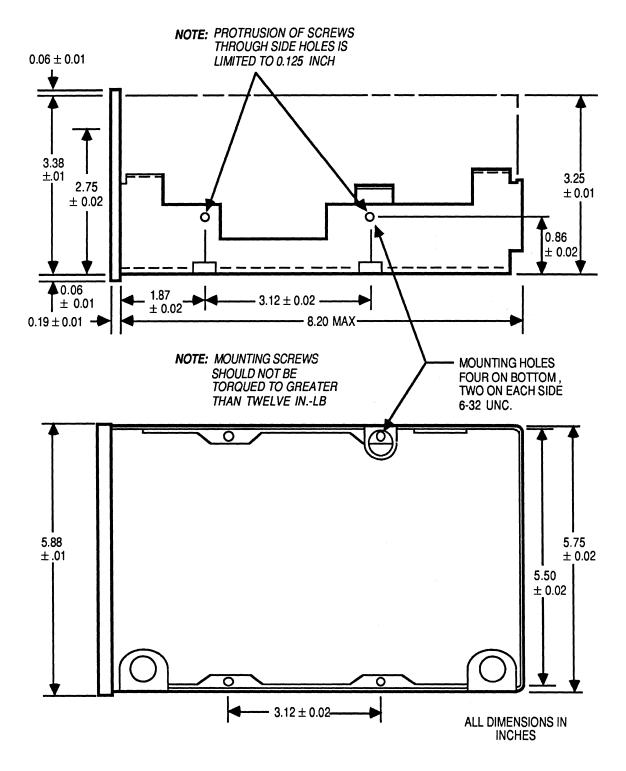

| 8.5 Removable Faceplate                                     | 57 |

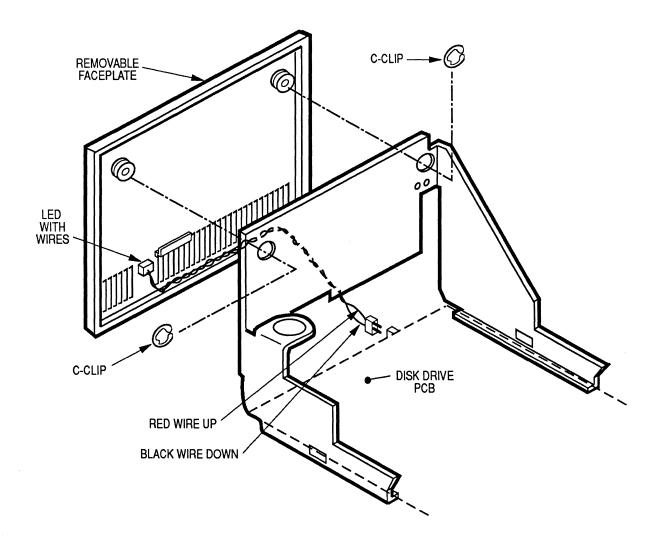

| 9.0 PCB JUMPER OPTIONS                                      | 8  |

| 9.1 Drive Address Selection Jumper8                         | 8  |

| 9.2 Data Head Selection Jumpers (JP32-JP36)9                | 0  |

| 9.3 Write Protect Selection Jumper (JP14)9                  | )1 |

| 9.4 Option for Sequential Spindle Motor Spinup Jumper (JP6) | 1( |

| 9.5 Test Jumpers (JP1, JP41, JP42)9                         |    |

| 9.6 Hard Sector Configuration Jumpers (JP16-29)9            | 1  |

| 10.0 MEDIUM DEFECTS AND ERRORS                              | 3  |

| APPENDIX: UNITS OF MEASURE9                                 | 5  |

| GLOSSARY                                                    | 7  |

#### FIGURES

| Figure 1  | Typical 12 Volt Current Power Up Cycle                                  | 6  |

|-----------|-------------------------------------------------------------------------|----|

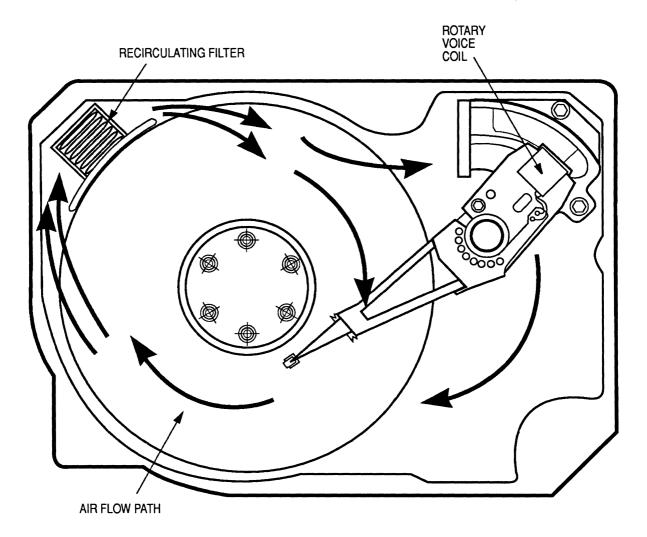

| Figure 2  | Air Filtration System                                                   | 11 |

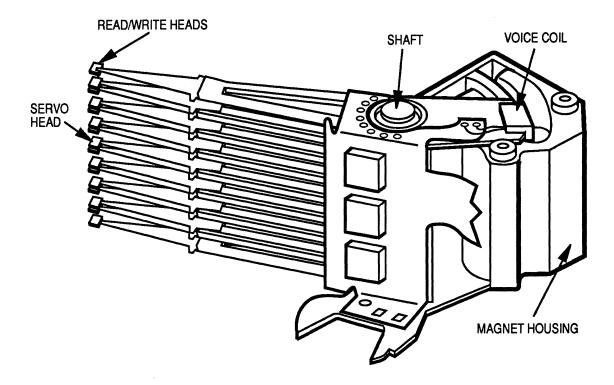

| Figure 3  | Head Positioning System                                                 | 12 |

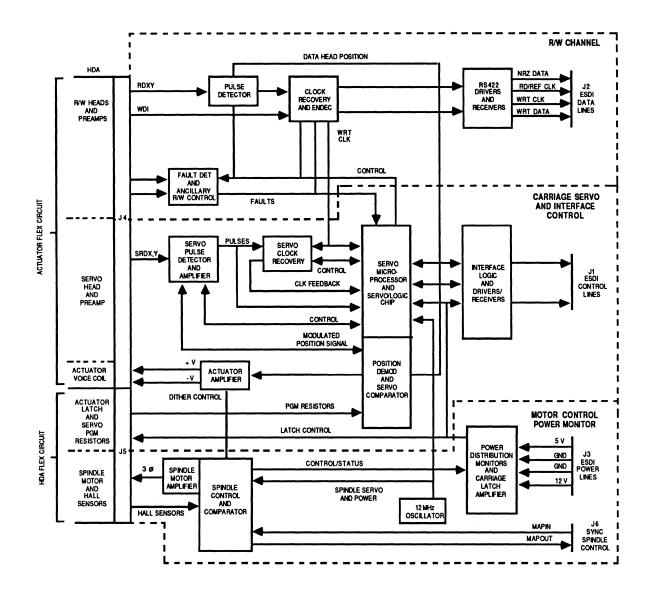

| Figure 4  | General Block Diagram                                                   | 15 |

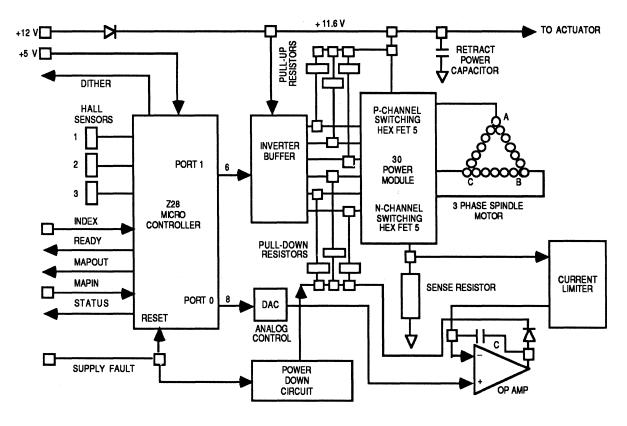

| Figure 5  | Spindle Control Hardware                                                |    |

| Figure 6  | Spindle Control Flow Chart                                              | 17 |

| Figure 7  | Servo Pattern and Read-Back Signal I                                    | 21 |

| Figure 8  | Servo System                                                            | 22 |

| Figure 9  | Main Servo Control Loop                                                 | 23 |

| Figure 10 | Head and Drive Selection                                                | 28 |

| Figure 11 | Preamplifier Head Selection and Read-Back Signal                        | 29 |

| Figure 12 | Head Selection Map                                                      | 30 |

| Figure 13 | Peak Detection                                                          | 33 |

| Figure 14 | Pulse Detector                                                          | 35 |

| Figure 15 | ENDEC/Data Separator READ Mode                                          | 36 |

| Figure 16 | Write Path                                                              |    |

| Figure 17 | Power Up Sequence (Jumper JP6 Open)                                     | 41 |

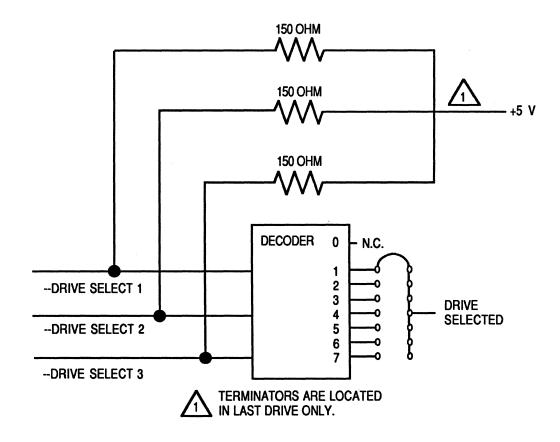

| Figure 18 | Drive Select Circuit                                                    | 42 |

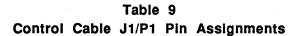

| Figure 19 | Control Cable J1/P1 Signals                                             | 45 |

| Figure 20 | Data Cable J2/P2 Signals                                                |    |

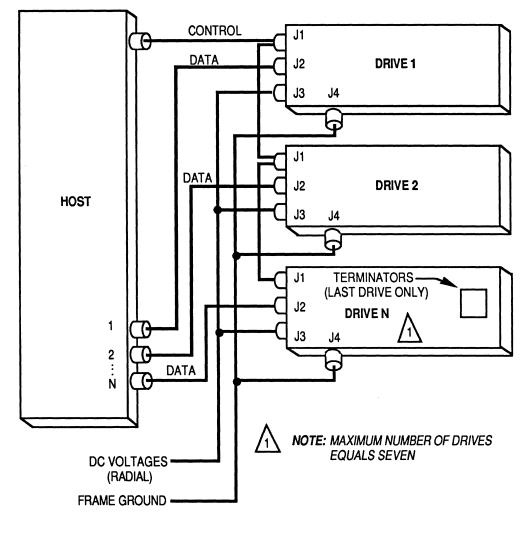

| Figure 21 | Typical Auxiliary Cable and Spindle Synchronization Connection          | 49 |

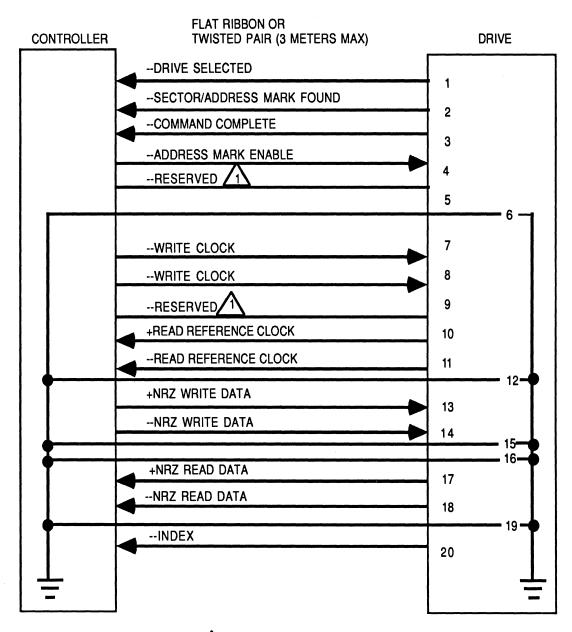

| Figure 22 | Typical Multidrive Connection                                           | 51 |

| Figure 23 | Control Signals, Driver/Receiver Combination                            | 52 |

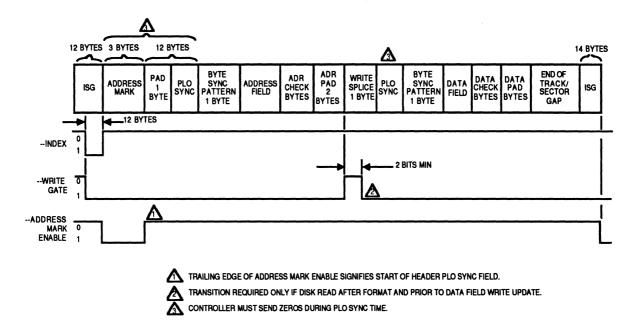

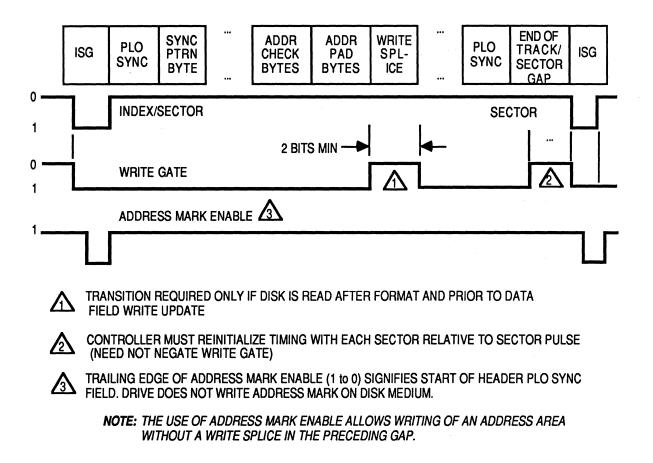

| Figure 24 | Soft Sector Address Mark, WRITE GATE, PLO Synchronous Format Timing     | 53 |

| Figure 25 | Hard Sector WRITE GATE, PLO Synchronous Format Timing, Using ADDRESS MA | RK |

|           | ENABLE                                                                  | 54 |

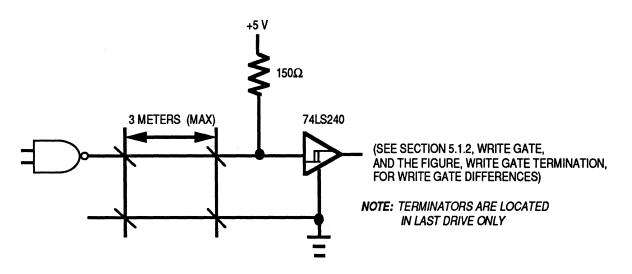

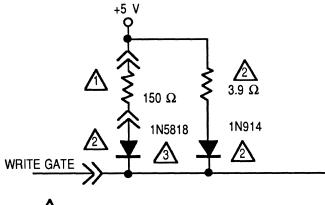

| Figure 26 | WRITE GATE Termination                                                  | 55 |

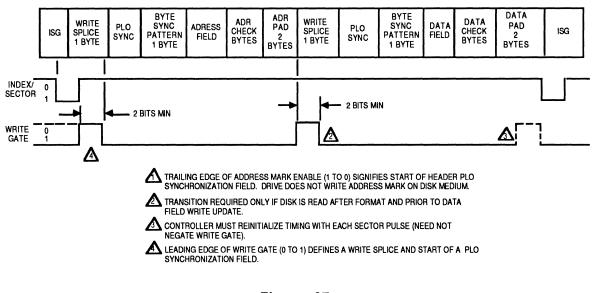

| Figure 27 | Hard Sector WRITE GATE, PLO Synchronous Format Timing                   | 55 |

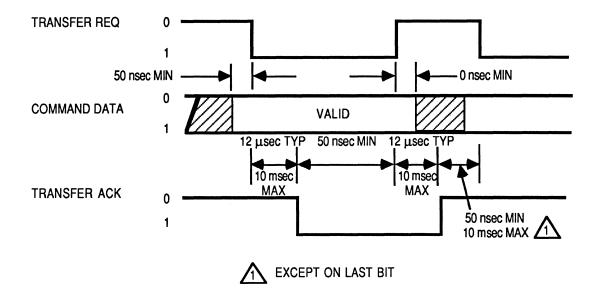

| Figure 28 | One Bit Transfer Timing—To Drive                                        | 58 |

| Figure 29 | COMMAND DATA Word Structure                                             | 58 |

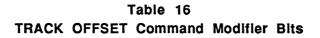

| Figure 30 | One Bit Transfer Timing—From Drive                                      | 62 |

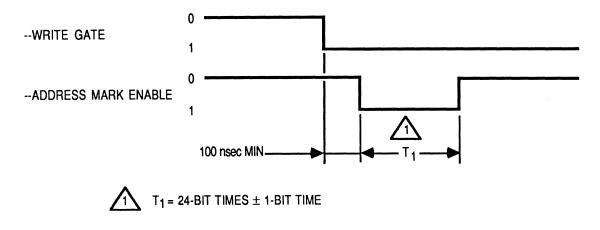

| Figure 31 | Write Address Mark Timing                                               |    |

| Figure 32 | CONFIG-STATUS DATA Word Structure                                       | 64 |

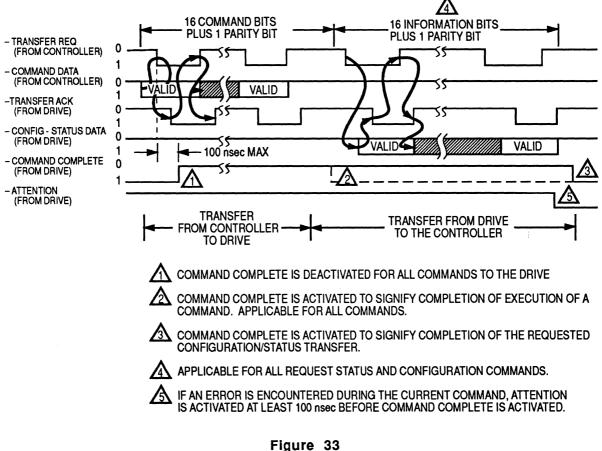

| Figure 33 | Typical Serial Operation(s)                                             | 65 |

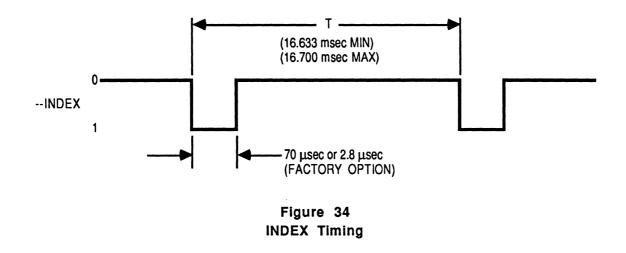

| Figure 34 | INDEX Timing                                                            | 71 |

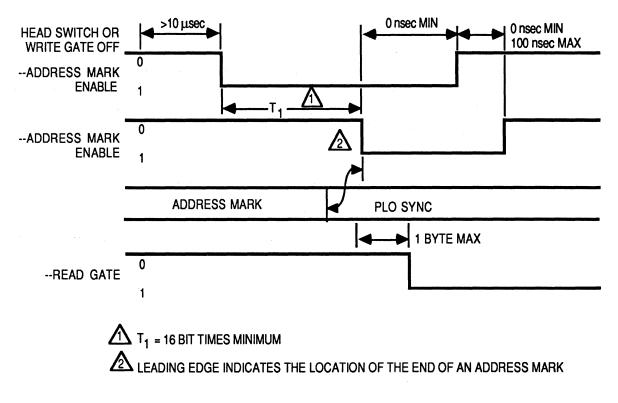

| Figure 35 | Read Address Mark Timing (Hard Sector)                                  | 72 |

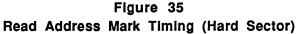

| Figure 36 | Sector Pulse Timing (Hard Sector)                                       | 73 |

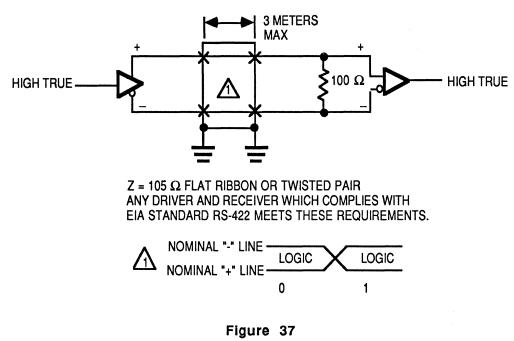

| Figure 37 | Data Line Driver/Receiver Combination                                   | 74 |

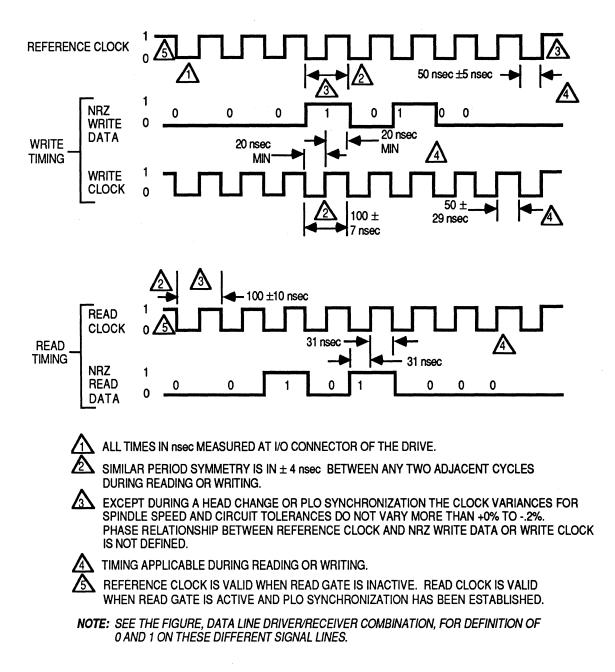

| Figure 38 | NRZ READ/WRITE DATA Timings                                             | 76 |

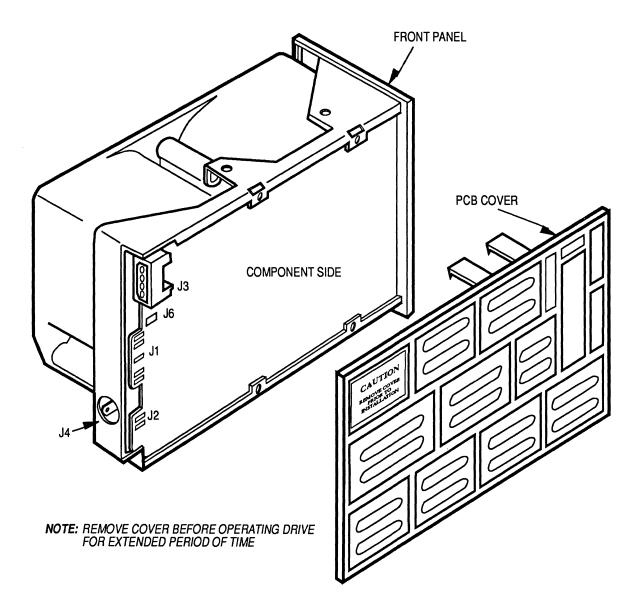

| Figure 39 | Interface Connector Physical Location                                   | 79 |

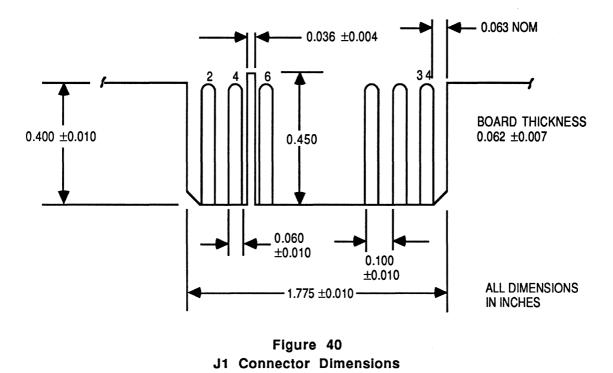

| Figure 40 | J1 Connector Dimensions                                                 | 80 |

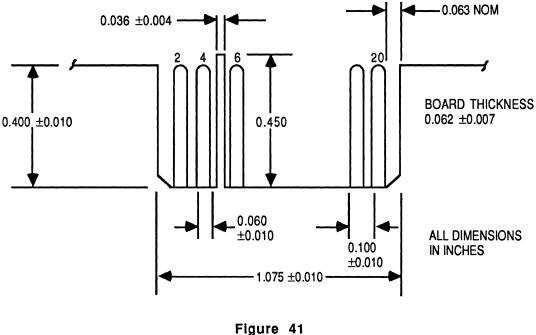

| Figure 41 | J2 Connector Dimensions                                                 | 81 |

| Figure 42 | J3 Connector (Drive PCB Solder Side)                                    | 81 |

#### FIGURES

| Figure 43 | Mechanical Outline and Mounting Hole Locations | .85  |

|-----------|------------------------------------------------|------|

| Figure 44 | Mechanical Outline, Bottom and Side Views      | .86  |

| Figure 45 | Removable Faceplate                            | . 87 |

| Figure 46 | Drive Jumper Options                           | .89  |

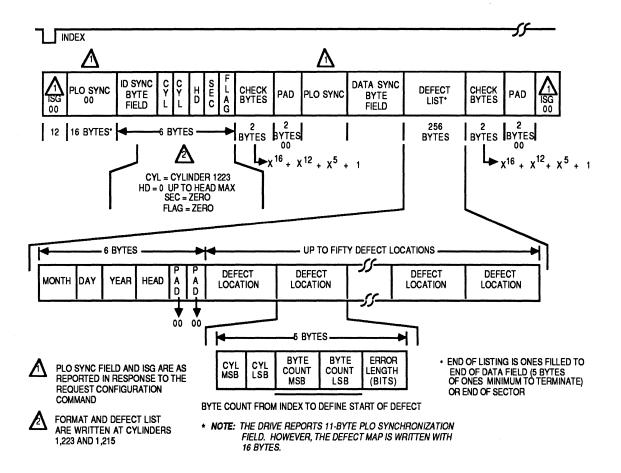

| Figure 47 | Defect List Format                             | .94  |

#### TABLES

| Table 1  | Performance Specifications                |

|----------|-------------------------------------------|

| Table 2  | Functional Specifications                 |

| Table 3  | Physical Dimensions                       |

| Table 4  | Environmental Limits                      |

| Table 5  | DC Power Requirements                     |

| Table 6  | Reliability Specifications                |

| Table 7  | Error Rates                               |

| Table 8  | Drive Selection Matrix                    |

| Table 9  | Control Cable J1/P1 Pin Assignments       |

| Table 10 | Data Cable J2/P2 Pin Assignments          |

| Table 11 | Auxiliary Cable (J6) Pin Assignments      |

| Table 12 | COMMAND DATA Definition57                 |

| Table 13 | REQUEST STATUS Modifier Bits              |

| Table 14 | REQUEST CONFIGURATION Modifier Bits       |

| Table 15 | CONTROL Command Modifier Bits             |

| Table 16 | TRACK OFFSET Command Modifier Bits61      |

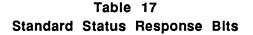

| Table 17 | Standard Status Response Bits             |

| Table 18 | Vendor Unique Status Response Bits        |

| Table 19 | Motor Status                              |

| Table 20 | SEEK Calibration Error Code               |

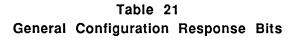

| Table 21 | General Configuration Response Bits       |

| Table 22 | Specific Configuration Response Bits      |

| Table 23 | Power Connector (J3) Requirements         |

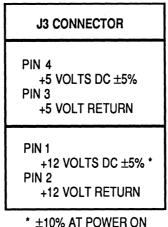

| Table 24 | J6 Auxiliary Signal Cable Pin Assignments |

| Table 25 | Drive Select Jumpers                      |

| Table 26 | Jumper Selections                         |

| Table 27 | Data Head Number Selection Jumpers90      |

| Table 28 | Test Pin Jumpers91                        |

| Table 29 | Customer Selectable Jumpers               |

| Table 30 | Maximum Number of Defects93               |

# **1.0 INTRODUCTION**

## 1.1 GENERAL DESCRIPTION

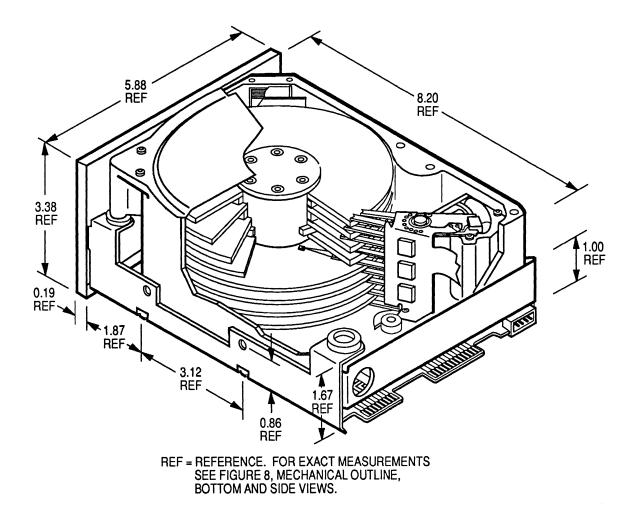

The XT-4000E<sup>™</sup> Family disk drives are high capacity, high performance random access storage devices using from five to eight nonremovable 5<sup>1</sup>/<sub>4</sub>-inch disks as storage media. Each disk surface employs one moveable head to access 1,224 data tracks. The total unformatted capacity of the drive ranges from 179 to 385 megabytes.

The drive incorporates the Enhanced Small Device Interface (ESDI) high performance  $5^{1/4}$ -inch standard. Among the resultant benefits are a 10 megabit per second transfer rate, status and configuration reporting across the interface, and nonreturn to zero (NRZ) data transfer.

Low cost and high performance are achieved through the use of a rotary voice coil actuator and a closed loop servo system using a dedicated servo surface. The innovative MAXTORQ<sup>TM</sup> rotary voice coil actuator provides an average access time of 16 milliseconds, typical, for the eight-disk model (14 milliseconds, typical, for the five-disk model). Track-to-track access time is 2.5 milliseconds for all models. This level of performance is usually achieved only with larger, higher powered, linear actuators. The closed loop servo system and dedicated servo surface combine to allow state of the art recording densities (1,070 tracks per inch, and 14,043 flux changes per inch) in a  $5^{1/4}$ -inch package.

High capacity is achieved through a balanced combination of high areal recording density, run-length limited (RLL) data encoding techniques, and high density packaging techniques. **Maxtor's** advanced MAXPAK<sup>™</sup> electronic packaging techniques use surface mount devices to allow all electronic circuitry to fit on one printed circuit board (PCB). Advanced 3380 Whitney-type flexures allow closer spacing of disks, and therefore allow a higher number of disks in a 5<sup>1</sup>/<sub>4</sub>-inch package. **Maxtor's** unique integrated drive motor/spindle design allows a deeper head/disk assembly (HDA) casting than conventional designs, thus permitting more disks to be used.

The electrical interface is compatible with the industry standards established by the ESDI committee. The same basic drive/HDA is also available with a Small Computer System Interface (SCSI). The drive size and mounting conform to the industry standard 5<sup>1</sup>/<sub>4</sub>-inch floppy and Winchester disk drives, and the drive uses the same direct current (DC) voltages and connectors. No AC power is required.

## **1.2 DRIVE FEATURES**

The key features of the drive are as follows:

- storage capacity of 179 to 385 megabytes unformatted

- same physical size and mounting as standard floppy disk drives

- same control and data cabling as ST506/412 interface drives

- same DC voltages as standard floppy disk drives

- no AC voltage required

- rotary voice coil actuator and closed loop servo system for fast, accurate head positioning

- microprocessor-controlled servo for fast access time, high reliability, and high density functional packaging

- 10.0 megabit per second transfer rate

- ESDI interface

- track capacity of 20,940 bytes, unformatted

- thin film metallic media for higher bit density and resolution plus improved durability

- single PCB for improved reliability

- automatic actuator lock

- brushless DC spindle motor inside disk hub

- microprocessor-controlled spindle motor for precision speed control (±0.1%) under all load conditions

- dynamic braking during power down cycle

- user selectable hard or soft sectors

- synchronization of spindle motors for parallel data transfer of multiple drives

# 2.0 PRODUCT SPECIFICATIONS

This section lists all specifications for the XT-4000E Family disk drives.

### 2.1 **PERFORMANCE SPECIFICATIONS**

Table 1, Performance Specifications, lists the performance specifications for the drive.

|                                                                                                                            | XT-4170E                        | XT-4380E                       |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------|

| Capacity, Unformatted<br>Per Drive (Mbytes)<br>Per Surface (Mbytes)<br>Per Track (bytes) (minimum)                         | 179.45<br>25.64<br>20,940       | 384.53<br>25.64<br>20,940      |

| Capacity, Formatted (512 bytes/sector)<br>Per Drive (Mbytes)<br>Per Surface (Mbytes)<br>Per Track (Mbytes)<br>Sector/Track | 157.93<br>22.56<br>18,432<br>36 | 338.4<br>22.56<br>18,432<br>36 |

| Transfer Rate, Mbits/Sec                                                                                                   | 10.0                            | 10.0                           |

| Typical Seek Time, msec*<br>Average<br>Track-to-Track<br>Full Stroke                                                       | 14<br>2.5<br>27                 | 16<br>2.5<br>29                |

| Max Seek Time, msec*<br>Average<br>Track-to-Track<br>Full Stroke                                                           | 16<br>3<br>3 4                  | 18<br>3<br>3 4                 |

\* Includes Settling

# Table 1Performance Specifications

# 2.2 FUNCTIONAL SPECIFICATIONS

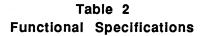

Table 2, Functional Specifications, lists the functional specifications for the drive.

## XT-4000E Product Specification & OEM Manual

| Rotational Speed (rpm) *         3,600         3,600           Average Latency         8.33         8.33           Recording Density (bpi)         21,064         21,064           Flux Density (fci)         14,043         14,04           Track Density (tpi)         1,070         1,070           Cylinders         1,224         1,224           Tracks         8568         18,36           Sectors (36 sectors/track)         308,448         660,9 | 380E |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Average Latency         8.33         8.33           Recording Density (bpi)         21,064         21,064           Flux Density (fci)         14,043         14,043           Track Density (tpi)         1,070         1,070           Cylinders         1,224         1,224           Tracks         8568         18,36                                                                                                                                  |      |

| Recording Density (bpi)         21,064         21,06           Flux Density (fci)         14,043         14,04           Track Density (tpi)         1,070         1,070           Cylinders         1,224         1,224           Tracks         8568         18,36                                                                                                                                                                                        |      |

| Flux Density (fci)         14,043         14,04           Track Density (tpi)         1,070         1,070           Cylinders         1,224         1,224           Tracks         8568         18,36                                                                                                                                                                                                                                                       | 4    |

| Track Density (tpl)         1,070         1,070           Cylinders         1,224         1,224           Tracks         8568         18,36                                                                                                                                                                                                                                                                                                                 |      |

| Cylinders         1,224         1,224           Tracks         8568         18,36                                                                                                                                                                                                                                                                                                                                                                           |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| Sectors (36 sectors/track) 308.448 660.9                                                                                                                                                                                                                                                                                                                                                                                                                    | 0    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60   |

| Data Heads 7 15                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| Servo Heads 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| <b>Disks</b> 5 8                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

\*Accurate to  $\pm 0.1\%$

#### 2.3 PHYSICAL DIMENSIONS

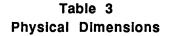

Table 3, Physical Dimensions, lists the physical dimensions of the drive.

| HEIGHT<br>WIDTH<br>DEPTH<br>WEIGHT<br>SHIPPING WEIGHT | = 3.25 in. (82.55 mm)<br>= 5.75 in. (146.05 mm)<br>= 8.20 in. (208.28 mm)<br>= 7.1 lb (3.2 kg)<br>= 9.3 lb (4.2 kg) |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| WEIGHT                                                | = 7.1 lb (3.2 kg)                                                                                                   |

| HEAT DISSIPATION                                      | = 27 W Typical,                                                                                                     |

|                                                       | 35 W Max.                                                                                                           |

#### 2.4 ENVIRONMENTAL LIMITS

Table 4, Environmental Limits, lists the environmental limits of the drive.

|                                         | OPERATING                                                               | NONOPERATING                                                             |

|-----------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|

| AMBIENT TEMPERATURE                     | 50° F to 122° F (10° C to 50° C)                                        | -40° F to 140° F (-40° C to 60° C)                                       |

| MAXIMUM TEMPERATURE<br>GRADIENT         | 18° F/hr (10° C/hr),<br>Below Condensation                              | 18° F/hr (10° C/hr),<br>Below Condensation                               |

| RELATIVE HUMIDITY                       | 8 to 80% Noncondensing with<br>Max Gradient of<br>10% /hr               | 8 to 80% Noncondensing with<br>Max Gradient of<br>10% /hr                |

| MAXIMUM ELEVATION                       | 10,000 ft                                                               | -1,000 ft to 40,000 ft                                                   |

| VIBRATION (INPUTS TO<br>FRAME OF DRIVE) | All axes, 5-25 Hz, 0.006 in. P-P<br>25-500 Hz, 0.20 G Peak Acceleration | All axes, 5-31 hz, 0.02 inches P-P<br>31-500 Hz, 1.0 G Peak Acceleration |

| SHOCK (INPUTS TO<br>FRAME OF DRIVE)     | 2 G with 11 msec Pulse Width, Half<br>Sine Wave, (all axes)             | 20 G With 11 msec Pulse Width, Half<br>Sine Wave, (all axes)             |

# Table 4Environmental Limits

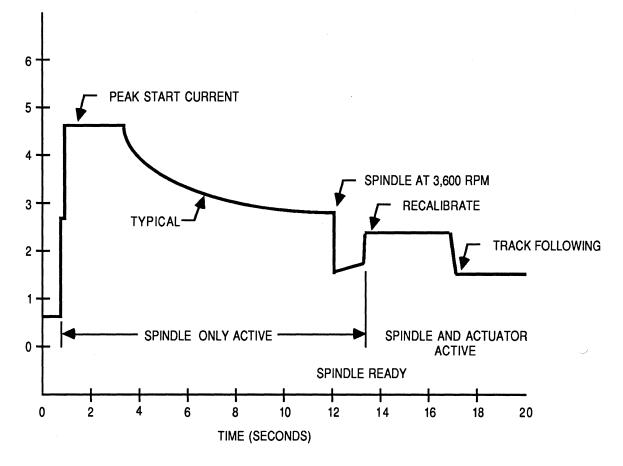

## 2.5 DC POWER REQUIREMENTS

Table 5, DC Power Requirements, lists the DC power requirements of the drive.

| VOLTAGE (NOMINAL)     | +12 V DC | +5 V DC |

|-----------------------|----------|---------|

| Regulation            | ±5%      | ±5%     |

| Current (Typical)     | 1.5 A    | 1.7 A   |

| Current (Maximum)     | 4.5 A *  | 1.9 A   |

| Ripple (Maximum, P-P) | 120 mV   | 50 mV   |

$^{\ast}$  Potential Current Surge for 1st 100 to 200  $\mu sec$  to Charge Capacitors Dependent on Power Supply at Power On

# Table 5DC Power Requirements

NOTE: WHEN A FULL-LENGTH SEEK IS DONE, ONE ADDITIONAL AMP IS REQUIRED FOR A DURATION OF 15 MILLISECONDS

Figure 1 Typical 12 Volt Current Power Up Cycle

# 2.6 RELIABILITY SPECIFICATIONS

Table 6, Reliability Specifications, lists the reliability specifications for the drive.

#### **XT-4000E Product Specification & OEM Manual**

MTBF PM Not Required 30 Minutes MTTR COMPONENT DESIGN LIFE 5 Years

30,000 POH, Typical Usage

#### Table 6 **Reliability Specifications**

#### 2.7 ERROR RATES

Table 7, Error Rates, lists the error rate specifications for the drive.

SOFT READ ERRORS HARD READ ERRORS\* SEEK ERRORS

10 per 10<sup>11</sup> Bits Read 10 per 10 <sup>13</sup> Bits Read 10 per 10 <sup>7</sup> Seeks

\*Not Recoverable Within 16 Retries

Table 7 **Error** Rates

#### 2.6 STANDARDS AND REGULATIONS

The Maxtor XT-4000E Family disk drives satisfy the following standards and regulations:

UNDERWRITERS LABORATORIES (UL) = United States safety; UL 478, Standard for Safety, Electronic Processing Units and Systems.

CANADIAN STANDARDS ASSOCIATION (CSA) = Canadian safety; CSA C22.2 No. 220, 1986, Information Processing and Business Equipment (Consumer and Commercial Products).

VERBAND DEUTSCHER ELECTROTECHNIKER (VDE) = German safety; VDE 0806/8.81, Safety of Office Appliances and Business Equipment.

INTERNATIONAL ELECTROTECHNICAL COMMISSION (IEC) = International safety commission; IEC 950 (formerly 380), Safety of Information Technology Equipment.

#### **XT-4000E Product Specification & OEM Manual**

FEDERAL COMMUNICATIONS COMMISSION (FCC) = United States radiation emissions; Part 15, Subpart J, Class B Consumer Computing Devices.

**CAUTION**: Connections between equipment must be made with shielded cables, and a shielded power cord must me used to connect AC power to the unit.

**CAUTION**: This equipment generates and uses radio frequency energy, and may cause interference to radio and television reception if not installed and used in strict accordance with the instructions in this manual and in <u>XT-4000S Service Manual</u>.

The drive has been tested and found to comply with the limits for a Class B computing device, in accordance with the specifications in Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against radio and television reception interference in a residential installation. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference using one or more of the following measures:

- reorient the receiving antenna

- · reorient the computer with respect to the receiver

- move the computer away from the receiver

- plug the computer into a different outlet, so that the computer and receiver are on different branch circuits

If necessary, consult the dealer, or an experience radio/television technician, for additional suggestions. You may find the FCC booklet *How to Identify and Resolve Radio TV Interference Problems* helpful. This booklet is available from the United States Government Printing Office, Washington, D.C., 20402, stock number 004-000-00345-4.

**Maxtor** is not responsible for any radio or television interference caused by unauthorized modifications to the drive. It is the responsibility of the user to correct such interference.

Doc 1011004, Rev B

# 3.0 FUNCTIONAL CHARACTERISTICS

The XT-4000E Family disk drive consists of read/write and control electronics, read/write heads, a servo head, a head positioning actuator, media, and an air filtration system. The components perform the following functions:

- interpret and generate control signals

- position the heads over the desired track

- read and write data

- provide a contamination-free environment

#### 3.1 READ/WRITE AND CONTROL ELECTRONICS

Drive electronics are packaged on a single PCB. This board, which includes two microprocessors, performs the following functions:

- reading/writing of data

- index detection

- head positioning

- head selection

- drive selection

- fault detection

- voice coil actuator drive circuitry

- track zero detection

- recalibration to track zero on power up

- track position counter

- · power and speed control for spindle drive motor

- braking for spindle drive motor

- drive up-to-speed indication circuit

- monitoring for write fault conditions

- control of all internal timing

- generation of seek complete signals

- RLL encoding/decoding

- data separation

- address mark detection (soft sector)

- sector detection (hard sector)

- spindle synchronization

#### 3.2 DRIVE MECHANISM

A brushless DC drive motor, contained within the spindle hub, rotates the spindle at 3,600 revolutions per minute. The spindle is direct driven, with no belt or pulleys being used. Dynamic braking is used to quickly stop the spindle motor when power is removed. The HDA is shock mounted to minimize transmission of vibration through the chassis or frame.

#### 3.3 AIR FILTRATION SYSTEM

The disks and read/write heads are assembled in an ultra clean-air environment and then sealed within the module. The module contains an internal absolute filter, mounted inside the casting, to provide constant internal air filtration (see Figure 2, Air Filtration System). A second filter, located on top of the base casting, permits pressure equalization between internal and ambient air.

Figure 2 Air Filtration System

## 3.4 **POSITIONING MECHANISM**

The read/write heads are mounted on a head arm assembly, which is then mounted to a ball bearing supported shaft. The voice coil, an integral part of the head/arm assembly, lies inside the magnet housing when installed in the drive. Current from the power amplifier, controlled by the servo system, causes a magnetic field in the voice coil which either aids or opposes the field around the permanent magnets. This reaction causes the voice coil to move within the magnetic field. Since the head arm assemblies are mounted on the voice coil, the voice coil movement is translated through the pivot point directly to the heads, and positions the head over the desired cylinder. See Figure 3, Head Positioning System.

Figure 3 Head Positioning System

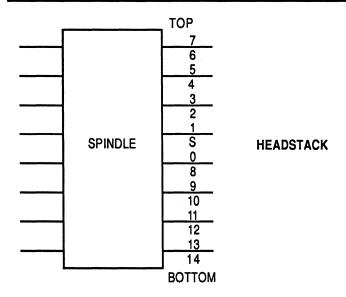

Actuator movement is controlled by the servo feedback signal from the servo head. The servo head is located on the lower surface of the fourth disk from the top, where servo information is prewritten at the factory. This servo information is used as a control signal for the actuator to provide track-crossing signals during a seek operation, track-following signals during on cylinder operation, and timing information, such as index, sector pulses (hard sector), and servo clock.

#### 3.5 READ/WRITE HEADS AND DISKS

The drive employs thin film heads and Whitney-type flexures. This configuration of sliders and flexures provides improved aerodynamic stability, superior head/disk compliance, and a higher frequency response than conventional ferrite heads.

The medium uses thin metallic film deposited on 130 millimeter diameter aluminum substrates. The metallic surface, together with the low load force/low mass Whitney-type heads, permit highly reliable contact start/stop operation. The metallic recording film yields high amplitude signals, and very high resolution performance compared to conventional oxide coated media. The metallic medium also provides a highly abrasion-

#### **XT-4000E Product Specification & OEM Manual**

resistant surface, decreasing the potential for damage caused by shipping shock and vibration.

Data on each of the data surfaces is read by one of fifteen read/write heads, each of which accesses 1,224 tracks. There is one surface dedicated to servo information in each drive.

# 4.0 THEORY OF OPERATION

The drive PCB assembly provides four major functions, 1) spindle motor control; 2) actuator control for head/positioning; 3) the read and write data channel; and 4) ESDI hardware and protocol implementation. In addition, power conditioning and monitoring is provided. Figure 4, General Block Diagram, shows the organization of these functions and the major subsections of each. The following paragraphs describe each of these in more detail.

Figure 4 General Block Diagram

## 4.1 SPINDLE MOTOR CONTROL

The spindle motor in the drive uses a three-phase delta-wound brushless DC motor located inside the hub. Commutation is determined by three hall effect sensors which are mounted on a flex circuit at the bottom of the casting. These hall effect sensors sense magnets under the spindle motor.

#### 4.1.1 Hardware Configuration

Figure 5, Spindle Control Hardware, presents a component block diagram of the spindle system. The hardware provides the functions described below. The Z8 microcontroller is the central element in this diagram, serving to coordinate, direct, and control all of the activity of the spindle.

Figure 5 Spindle Control Hardware

The output of the hall sensors is mapped by the Z8 microcontroller into a three phase commutation sequence. This sequence continuously commutates the in-the-hub four-pole three phase spindle drive motor through the three phase H-bridge power module (six power transistors). The current through the motor is monitored by the voltage across the 0.1 ohm sense resistor. Current control is obtained by comparing the sense voltage with the digital analog converter (DAC) output at a high gain op-amp, and then closing the analog control loop through the (lower) power transistors; an integrating capacitor around the op-amp stabilizes the loop. The net effect of this loop is to desensitize the circuit to variations in the power transistor parameters.

Additional analog circuitry shown in Figure 5, Spindle Control Hardware, provides current limiting of the motor current, and provides graceful shutdown (homing of the actuator and dynamic braking of the spindle) in the event of loss of power, or if the spindle motor is turned off by a STOP command in remote mode.

#### 4.1.2 Spindle Modes of Operation

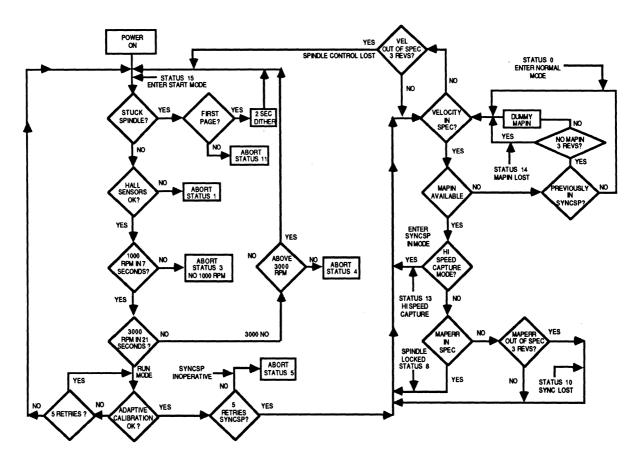

Figure 6, Spindle Control Flow Chart, is a diagrammatic description of the in-line/real-time microcontroller diagnostics for the spindle control system.

Figure 6 Spindle Control Flow Chart

The flowchart describes the sequence of microcontroller activity required during each of the spindle modes of operation; this sequence provides a detailed overview of the diverse control and auxiliary functions of the spindle. The sequence, programmed as algorithms in the microcontroller, provides three basic modes of operation for the drive: START mode, RUN mode, and SYNCSP (synchronous spindle) mode.

<u>START Mode</u>: At power up with the spindle at rest, full current (limited to 4.0 amps) is applied to the spindle motor. Progressive diagnostic and timing checks are performed to detect a spindle drive malfunction and to take corrective action as follows:

Detect a Stalled Spindle Motor

The hall sensors are tested for (commutation) motion. If one second elapses without

motion, either a "stuck" spindle or a power module failure is indicated; actuator dither

is invoked to free up the spindle, and STATUS 2 is posted. At the end of two sec onds of dither, motion is checked again and if not detected, STATUS 2 is posted and

the spindle aborts (powers down).

- Detect a Hall Sensor Failure

The states of the hall sensors are continuously checked at commutation until velocity

lock on. If an illegal state occurs in two consecutive revolutions, STATUS 1 is posted

and the spindle aborts.

- Check 1,000 revolutions per minute at 7 Seconds

The commutation is timed for 1,000 revolutions per minute to occur within 7 seconds.

If 1,000 revolutions per minute do not occur, this indicates excessive drag forces

from the head or bearings, or a motor/driver failure; STATUS 3 is posted and the

spindle aborts.

- Check 3,000 revolutions per minute at 21 Seconds:

The commutation is timed for 3,000 revolutions per minute to occur within 21 seconds. If above 3,000 revolutions per minute, the spindle tries to achieve 3,600 revolutions per minute; in contrast to the stalled spindle motor and 1,000 revolutions per minute in 7 seconds checks, a sufficient back electromotive force from the motor has reduced the voltage overhead across the drivers in the power module such that the reduced power dissipation of the drivers allows multiple retries. (A RETRY is performed beyond this point for any return into the START mode.)

<u>RUN\_Mode</u>: Upon entering RUN mode, the microcontroller sequentially enters a) an adaptive routine to compute the quiescent drag force of the bearing/disks and to compute the dynamic system constant from the DAC input to motor velocity; b) an electronic commutation routine; and c) a velocity lock-on-routine (in thirty revolutions) to insure (monitored) velocity operation of 3,600 revolutions per minute  $\pm 0.1\%$ . The system is then given a STATUS 0 identification of normal mode operation. If a failure occurs at any point between a) and c), the system goes into RETRY mode (into START mode) and is monitored for five successive failures without velocity lock-on before ABORT.

At velocity lock-on, a READY signal is posted to the interface microcontroller to signal that the spindle is at recording velocity (3,600 revolutions per minute).

#### **XT-4000E Product Specification & OEM Manual**

A feature of the drive is the capability of synchronous spindle operation (spindle locked operation) in which INDEX lock is achieved between a master drive and up to forty eight slave drives. This feature allows serial data streams to operate in parallel and thereby multiplies the system data transfer rate (drive-to-host computer) by the number of slave drives.

When the drive is in RUN mode, the code of the microcontroller provides two simultaneous functions: 1) generation of a MAPOUT (master pulse out); and 2) search for a MAPIN (master pulse in). Normal operation implies the lack of a MAPIN pulse, and while in this mode, the drive defaults to a master drive designation.

If a MAPIN pulse is detected, the drive is posted with a slave drive designation (MAPIN available) and the drive goes into SYNCSP mode.

<u>SYNCSP Mode</u>: Upon detection of MAPIN by the microcontroller, the slave drive enters a high-speed CAPTURE mode to bring the MAPIN pulse to the MAP (master pulse) window. Normal velocity control is in effect during this operation (NORMAL mode).

As MAPIN approaches the outer boundaries of the MAP window, a velocity adjustment is made to the slave drive to return the drive to normal velocity prior to entering the MAP window and subsequent phase lock. Within the MAP window, bounds are tested for velocity error and phase error. When the two are within their tolerance zones, the system switches to a phase controlled configuration, wherein the slave drive is locked to the MAPIN pulse, and synchronous spindle operation (spindle locked) STATUS 8 is posted.

In the SYNCSP mode, the velocity and phase error are constantly monitored to assure velocity and INDEX phase tolerances as follows:

velocity: 3,600 revolutions per minute ±0.1% master INDEX/slave INDEX lock ±40 microseconds

If the SYNCSP lock error (MAPERR) is out of tolerance (STATUS 10), the system reverts to CAPTURE mode. If the velocity is out of tolerance (spindle control lost), RETRIES are performed via START mode (recalibration of the adaptive loop) and if SYNCSP is not achieved (with MAPIN available), a SYNCSP inoperative condition error (STATUS 10) is posted and the system attempts operation in NORMAL mode.

# 4.2 ACTUATOR CONTROL

This section describes the servo system used in the XT-4000E Family disk drives. The same servo system is used for both models, with small modifications made to accommodate the different number of heads unique to each model. Two functions are provided, precision track following, and carriage motion to specific tracks in response to in-

#### XT-4000E Product Specification & OEM Manual

terface commands. Typical track-to-track and average access times are 14 milliseconds for the XT-4170E and 16 milliseconds for the XT-4380E.

A dedicated servo surface and quadrature servo pattern is used. This servo incorporates evolutionary and detail improvements over prior generations of **Maxtor** servos.

The level of electronics integration is very high. Three custom analog integrated circuits, an actuator driver integrated circuit, and a standard cell servo logic chip (SLC), are used to implement the servo functions. In addition, the servo uses a microcontroller, which is shared with the drive interfacing function.

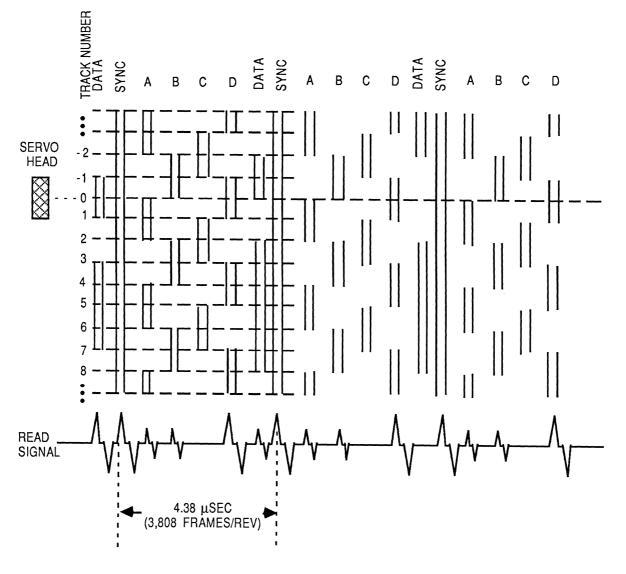

#### 4.2.1 Servo Pattern

The servo pattern consists of 3,808 servo frames per track with twenty-two servo clock intervals per frame. This yields a 228 kilohertz frame rate for the system. Four dibit pulses encode the quadrature position information, and one pulse each is used for synchronization and data (see Figure 7, Servo Pattern and Read-Back Signal I). When the data pulse is present, the frame has a logical "1" value. When the pulse is not present, the frame has a logical "1" value. When the pulse is not present, the frame has a logical "0" value. This serial pulse stream is decoded in 16-bit words, with parity, and is used to encode the absolute track address, index, and configuration data used by the drive and the servo. Thus, the words are repeated 238 times per revolution for a word rate of 14.3 kilowords per second. The synchronization pulse, which follows the data pulse, is present in every frame and is used to synchronize to the servo pattern. The first pair of position pulses, A and B, are used for positioning on even numbered data tracks. The second pair of pulses, C and D, are used for positioning on odd numbered tracks.

Figure 7 Servo Pattern and Read-Back Signal I

#### 4.2.2 Block Description

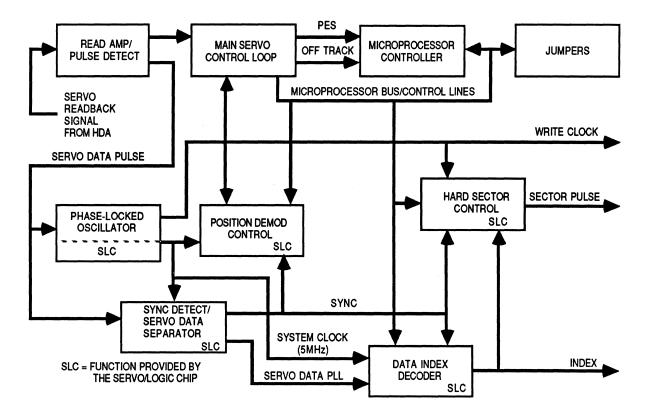

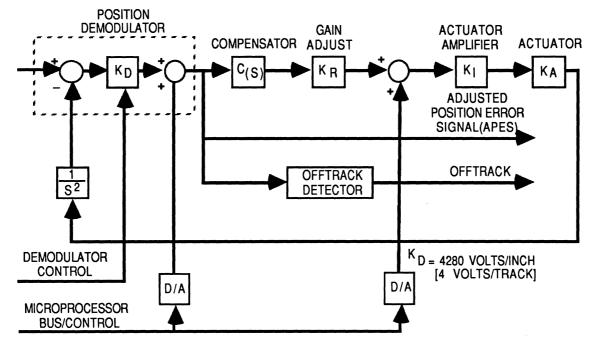

Refer to Figure 8, Servo System, and Figure 9, Main Servo Loop, when reading the following descriptions.

Figure 8 Servo System

Figure 9 Main Servo Control Loop

#### A READ AMPLIFIER/PULSE DETECTOR

The read amplifier and pulse detector provides automatic gain control (AGC) a buffer amplifier for the servo filter and a pulse detector for the dibit pulses. The raw servo signal from the preamplifier enters the read amplifier and is applied to the AGC amplifier. The AGC loop is closed through the position demodulator. The amplified and normalized servo signal then passes through a filter for noise reduction and then on to the pulse detector and peak detector.

The pulse detector detects the zero crossing between the positive and negative going portions of the dibit pulses. The digital output of this detector is used to decode data pulses and issued as the input for the phase-locked oscillator. The peak detector samples the peak values of the position pulses and establishes a reference baseline from which to measure these peak values. The discharge current of the peak detector is switchable to allow the use of a long time constant (peak hold) during servoing, and a shorter time constant which is used to facilitate lock up of the AGC loop at power on.

#### B PHASE-LOCKED OSCILLATOR

The phase-locked oscillator (PLO) harmonically locks to the incoming pulse stream from the pulse detector. During synchronization the oscillator locks in phase and frequency mode to a reference clock generated in the SLC. Also, in the SLC, the oscillator output is divided and used to generate the 5 megahertz master clock from which timing gates are derived. This clock is divided again to provide the 2.5 megahertz feedback clock for the PLO. The fundamental oscillator output frequency is 20 megahertz.

Since the PLO output is synchronized with the physical rotation of the disk stack, it is used as the write clock and as the clock for the sector counter for hard sector mode operation.

#### C SYNCHRONIZATION DETECTOR AND SERVO DATA SEPARATOR

The synchronization detector and servo data separator in the SLC detect the data and synchronization transitions, which are the first two dipulses present in each servo frame. The extracted synchronous transitions are used to create the absolute frame reference for synchronizing the servo frame and for decoding servo position information. Capability is provided for tolerating servo surface defects which may cause missing synchronization pulses. The serial data stream of data pulse transitions is used to verify lock by virtue of its limited run length of zeros when proper lock is in effect. Parity of the data words is also checked. The microprocessor constantly monitors synchronization and data and initiates relocking the PLO and reinitializing the servo if synchronization is lost.

#### D DATA AND INDEX DECODER

The data and index decoder in the SLC is a 16-bit shift register whose contents are read every sixteen frames. If all the frames are valid the word is passed on to other logic in the SLC and then to the microprocessor controller. Index is delineated by a preindex and index word sequence. Absolute track information is also encoded with redundancy. The absolute track information is constantly monitored to verify that the servo is positioned on the correct track. In addition to index and track coding, the guard bands contain configuration data which is used to configure a given PCB for a given HDA. In this way, the same PCB may be used for a family of products. Configuration data includes the number of data tracks and heads, the servowriter version and drive capacity, and the dynamic constants to be used when seeking.

#### E HARD SECTOR CONTROL

The hard sector capability of the drive is provided by a programmable counter in the SLC. This counter is clocked by the PLO and is synchronized with index. User defined jumpers on the PCB are used to set the desired number of bytes per sector. Alternatively, the desired number of bytes per sector may be set via the drive interface. The microprocessor either reads the jumpers or receives the interface command, and in turn sets the decode logic for the proper sector size. The sector pulses are very accurately timed to data since the sector clock is locked to disk rotation.

#### F POSITION DEMODULATOR CONTROL

Timing windows are created in the SLC to gate the synchronization pulses, data pulses, and servo position dipulses. The servo master clock derived from the PLO divides each servo frame into twenty-two equal segments, and is used as the reference for generating these gates. A nominal disk rotation speed of 3,600 and 3,808 frames per revolution results in a 5 megahertz servo master clock.

The synchronization pulse is used to align the gates to the servo frames. The gate generated for synchronization is used to verify lock to synchronization. If lock is lost, synchronization pulses stop appearing in the proper synchronization window and a relock process is initiated by the microprocessor. The gate generated for data pulses is used to decode servo data. When no transition is detected in the window, the frame has a logical "0" value, and when a data transition does occur in the window, the frame has a logical "1" value.

The four gates generated for the four position dipulses (A, B, C, and D) are used to switch the peak detectors in the position demodulator from a tracking mode to a hold mode, providing position information to the control system.

#### G MAIN SERVO CONTROL LOOP

The peak-detected A, B, C, and D dipulses are used to create the locking edges for the position loop. Difference signals corresponding to A-B, B-A, C-D, and D-C are synthesized and used for servoing on the appropriate data tracks.

With the quadrature pattern, track zero uses A-B, track one uses C-D, track two uses B-A, and track three uses D-C. This pattern is repeated every fourth track so that tracks zero, four, eight, twelve, etc., use A-B for generating the position error signal.

Digital to analog converters in the SLC are controlled by the microprocessor. During SEEKs, position and velocity control trajectories are calculated by the microprocessor

and output to the servo control loops via these DAC's. These trajectories are calculated based on the configuration data which is read at power up. The configuration data contains the dynamic constants which are used in calculating the SEEK trajectories.

During track following, the position error is monitored by hardware to obtain fast response to shut down the write current should an off track condition occur during a write operation.

#### H MICROPROCESSOR CONTROLLER

The servo microprocessor exercises supervisory control over the servo during track following mode, and active control while seeking. In addition to the servo function, the microprocessor performs interface control functions per ESDI specifications.

The various peripherals, such as the SLC and configuration jumpers, are memory mapped. The microprocessor makes use of registers inside the SLC for drive status, control, seek current DAC output, position offset current DAC output, track address, servo data words, and peripheral control via output port pins in the SLC.

The microprocessor also controls the recalibration sequence when power is first applied to the drive. When the drive is jumpered to enable starting and stopping the spindle motor via the interface, the microprocessor controls the reset line to the spindle control microprocessor. The status of the spindle control microprocessor is monitored by the servo microprocessor to determine status and detect any error conditions in the system. Such status information is then available to the host through the drive interface.

The servo microprocessor also controls the actuator latch and releases the actuator when the spindle is locked to the proper speed. After power is removed from the drive, or a spindle stop command is received from the interface, the actuator driver pushes the headstack into the landing zone and the latch is enabled. This action takes place while the spindle is still spinning and before dynamic braking begins.

#### JUMPERS

I

Two classes of servo jumpers are used in the drive. The first class includes factory jumpers which configure the PCB to work properly for the particular model of drive on which it is installed. These jumpers program the number of heads, the data transfer rate, and the synchronization field required by the data separator. The microprocessor reads these jumpers and performs accordingly.

The second class of jumpers comprises user selectable jumpers. These jumpers are for setting a hard or soft sectored mode of operation, selecting the sector size in hard sector

mode, enabling or disabling the ability to set the hard sector size through the drive interface, and enabling or disabling automatic spinup.

## 4.3 **READ/WRITE CHANNEL**

The read/write channel is described in the following paragraphs.

## 4.3.1 HDA Flex Circuit Interface

A description of the HDA flex circuit interface, including the preamplifier integrated circuit, power, head selection, the READ signal, and the WRITE mode and write unsafe, follow.

### A PREAMPLIFIER INTEGRATED CIRCUIT

The preamplifier/write driver that is used on the flex circuit is the SSI 521 integrated circuit. This is a thin film head compatible circuit capable of interfacing with up to six heads. There are three SSI 521 chips used on the flex circuit so that a maximum number (fifteen) of heads for a drive can be selected.

#### B POWER

Power is supplied from the main drive PCB through the flex circuit connector, J4. The voltage requirements are Vcc = +5 volts, Vdd = +12 volts.

## C HEAD SELECTION

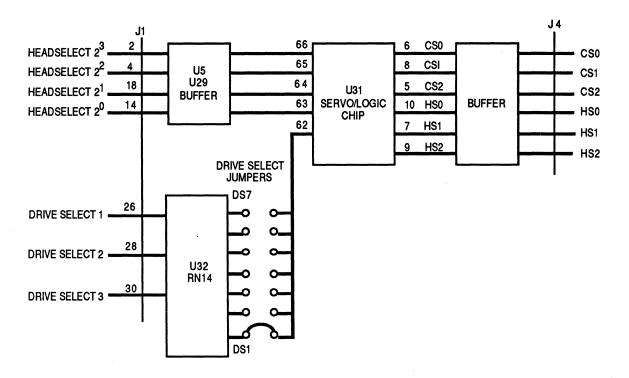

The head selection circuitry starts at the ESDI interface connector, J1. There are four head select lines used at the ESDI interface (Figure 10, Head and Drive Selection).

-Headselect 2<sup>0</sup> -Headselect 2<sup>1</sup> -Headselect 2<sup>2</sup> -Headselect 2<sup>3</sup>

Figure 10 Head and Drive Selection

These are then encoded by the SLC into three chip select lines and three head select lines that are used by the flex circuit. These lines are listed below (also, see Figure 11, Preamplifier Head Selection and Read-Back Signal).

CS0\* CS1\* CS2\* HS0 HS1 HS2

\* Negative true

Doc 1011004, Rev B

Figure 11 Preamplifier Head Selection and Read-Back Signal

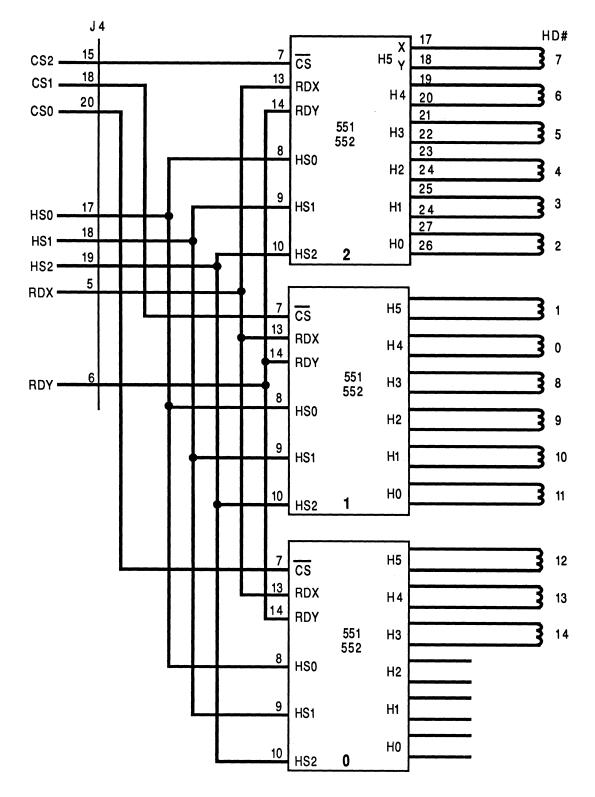

The encoding for the heads is listed in Figure 12, Head Selection Map. Also shown is the mapping of the heads within the HDA.

| HD | CS2 | CS1 | CS0 | HS2 | HS1 | HS0 |

|----|-----|-----|-----|-----|-----|-----|

| 0  | 1   | 0   | 1   | 1   | 0   | 0   |

| 1  | 1   | 0   | 1   | 1   | 0   | 1   |

| 2  | 0   | 1   | 1   | 0   | 0   | 0   |

| 3  | 0   | 1   | 1   | 0   | 0   | 1   |

| 4  | 0   | 1   | 1   | 0   | 1   | 0   |

| 5  | 0   | 1   | 1   | 0   | 1   | 1   |

| 6  | 0   | 1   | 1   | 1   | 0   | 0   |

| 7  | 0   | 1   | 1   | 1   | 0   | 1   |

| 8  | 1   | 0   | 1   | 0   | 1   | 1   |

| 9  | 1   | 0   | 1   | 0   | 1   | 0   |

| 10 | 1   | 0   | 1   | 0   | 0   | 1   |

| 11 | 1   | 0   | 1   | 0   | 0   | 0   |

| 12 | 1   | 1   | 0   | 1   | 0   | 1   |

| 13 | 1   | 1   | 0   | 1   | 0   | 0   |

| 14 | 1   | 1   | 0   | 0   | 1   | 1   |

Figure 12 Head Selection Map

#### D READ SIGNAL

The amplified read-back signal is output from the flex on the RDX (read data x) line. RDY (read data y) lines are shown in Figure 12, Head Selection Map. The nominal gain from the head input, HnX and HnY (where n is the head number), of the preamplifier to the RDX and RDY outputs is 100.

## E WRITE MODE AND WRITE UNSAFE

Write data is sent by the main PCB to the flex circuit via the WDI (write data input) pin on J4. A negative transition on the WDI line changes the direction of the write current in the SSI 521, causing a data transition to be written. (The SSI 521 integrated circuit has a divide-by-two flip-flop internally in the write data path). Write current is selected by three programming resistors on the main PCB, one resistor per SSI 521.

The WUS (write unsafe output) is normally HIGH (unsafe) when in READ or IDLE mode. When a WRITE mode is initiated, WUS goes low after a period of up to 1 microsecond; this indicates a safe condition when in WRITE mode. An unsafe condition exists if any of the following occur:

- the WDI frequency is too low

- there is no write current

- the device is in READ mode

- the chip is disabled

## 4.3.2 Pulse Detector

The primary function of the pulse detector is to detect "legitimate" peaks of the read-back signal from the head, disk, and preamplifier. A legitimate peak corresponds to a written flux transition on the disk. Other undesired peaks can be caused by noise. The pulse detector must detect these legitimate peaks while preserving the timing associated with them. Each peak is represented by the presence of a narrow pulse on the +ENDATA (encoded data) line, with timing information in the leading edge. This pulse stream, representing encoded data, is ultimately time synchronized by the PLL data separator so that it can be decoded by the encoder/decoder (ENDEC).

The pulse (or peak) detection function is implemented with an 8464 pulse detector integrated circuit.

The following functions are used to achieve the primary purpose of this circuitry as stated above.

**NOTE**: Differential signals are denoted by pin pairs.

#### A SIGNAL AMPLIFICATION USING AGC

Figure 14, Pulse Detector, shows the preamplified head signal as the input to a gaincontrolled amplifier in the 8464 pulse detector. AGC is used to maintain a constant, predetermined signal level at the input to the hysteresis comparator in the 8464 (pins twenty-one and twenty-two).

This is important because a DC voltage level on the SET HYSTERESIS line (pin three) programs a comparator hysteresis which is intended to be a fixed percentage of the average zero-to-peak signal amplitude at the comparator input.

This hysteresis comparator provides the means to amplitude-qualify signal peaks as legitimate. This is illustrated below, in Section 4.3.2 C, Pulse Qualification/Peak Detection.

A gain-control signal for the first amplifier stage is derived from the signal at pins twentyone and twenty-two by full-wave rectifying that signal, filtering it by means of the AGC capacitor on pin sixteen, and comparing it to a reference level, VREF (voltage reference), at pin four. The VREF thus determines the signal amplitude at pins twenty-one and twentytwo, while the DC level on pin three, SET HYSTERESIS, determines the amplitude qualification level for peak detection. The discharge circuit connected to pin sixteen allows AGC discharge current to flow only when pulses are present at +ENDATA, thereby allowing the graceful detection of address marks without perturbing the AGC loop.

#### B SIGNAL FILTERING

The amplified read-back signal at pins eighteen and nineteen is processed by a 6.5 megahertz Bessel filter before being input to the differentiator input (pins two and twenty-three). An additional 8 megahertz Bessel filter is placed before the hysteresis comparator (pins twenty-one and twenty-two) to compensate for the additional group delay in the differentiator, as well as some internal delay within the system.

The differentiator network is a two pole Bessel configuration.

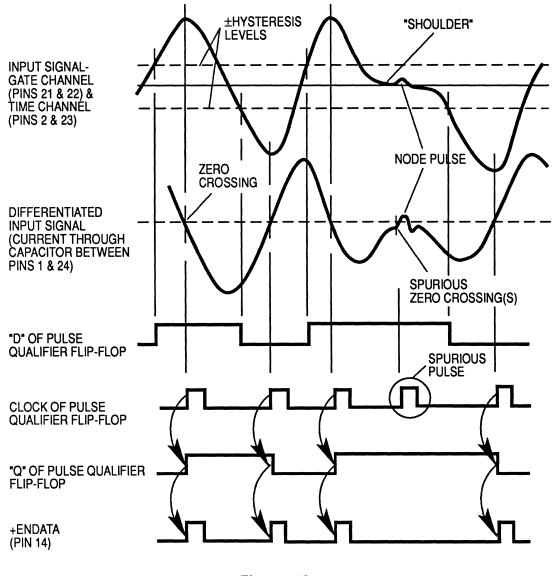

#### C PULSE QUALIFICATION/PEAK DETECTION

Figure 13, Peak Detection, shows pertinent wave forms which are referenced to the pulse detector integrated circuit. The gate channel input signal (to the hysteresis comparator) is shown with the SET HYSTERESIS level on pin three. This is essentially the same wave form that is input to the time channel differentiator stage at pins two and twenty-three. The time differentiated version of this wave form has zero crossings that represent the peaks of the input wave form. These zero crossings are detected by a level comparator which triggers a bidirectional one-shot. The resulting pulses at pins

twelve and thirteen thus have leading edges which carry the timing information of the signal peaks.

Figure 13 Peak Detection

These clocks toggle the pulse-qualifier flip-flop in the 8464 only if the AMPLITUDE QUALIFICATION signal at pin fifteen (D of the flip-flop) has changed state since the last clock was received. Every flip-flop toggle produces a pulse on pin fourteen (+ENDATA) whose leading edge retains the timing of the corresponding signal peak.

Note that the flip-flop D changes state, and thus qualifies the next flip-flop clock only if the gate channel input signal exceeds the preset hysteresis level.

Note that "shoulders" on the differentiator input produce "droop" on the differentiated output which can generate spurious zero crossing. Figure 13, Peak Detection, illustrates the pulse amplitude qualification.

## D WRITE-TO-READ AND HEAD SWITCH RECOVERY

Referring to Figure 14, Pulse Detector, the drive uses a -SQUELCH command, derived in the SLC, which is related to the system WRITE command in the following manner:

- when WRITE is true, -SQUELCH is true (low) and pin eleven is held high, which puts the 8464 in WRITE mode. The 8464 reacts by lowering its internal input impedance at pins eighteen and nineteen, and maintaining the AGC voltage at pin sixteen

- when WRITE is false, -SQUELCH remains true for 5 microseconds and then becomes false. This maintains the reduced input impedance across pins six and seven for the 5 microseconds by virtue of the 8464's internal circuit, as well as an external circuit shown as "squelch net"

Figure 14 Pulse Detector

When a head switch occurs, -SQUELCH becomes true for 5 microseconds with the same result as described above.

The reduced input impedance during squelch permits the input coupling capacitors to pins six and seven to discharge more quickly after any new DC offset voltage which may be the result of write-to-read mode switching or head switching. If these capacitors are not discharged by the time the next read data comes along, the resulting pin six and seven differential input voltage hinders a read operation.

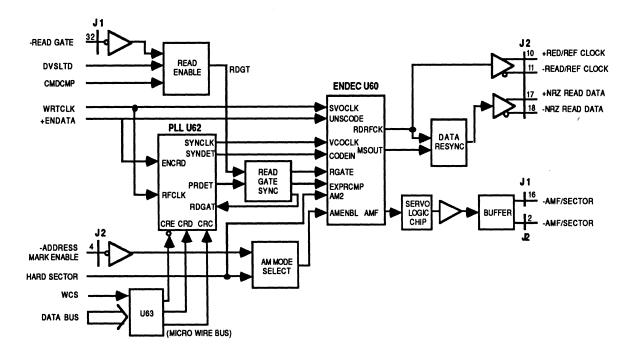

## 4.3.3 Clock Recovery and Decoding

The clock recovery and data standardization functions are provided by the DP8459 integrated circuit which receives +ENDATA from the pulse detector. Decoding is provided by the DP8463B ENDEC integrated circuit according to the rules of (2, 7) 1/2 code. Figure 15, ENDEC/Data Separator, READ Mode, illustrates the system in READ mode. The additional logic in the read gate synchronization block and the data resynchronizer ensures that the data separator/ENDEC combination meets all ESDI specifications.

Figure 15 ENDEC/Data Separator READ Mode

#### A DATA SEPARATOR

The data separator uses a phase-lock loop (PLL) to recover the write clock information from the encoded data stream, +ENDATA. It operates in three modes under control of the read gate synchronization circuits. When not reading or writing (IDLE mode), or when in WRITE mode, the data separator is locked to the write clock from the servo PLL, and operates in a wide band width, phase/frequency mode. This insures proper PLL lock-up, both for phase and frequency. When READ GATE is asserted, RDGAT to the data separator becomes true at the same time, beginning a lock-up sequence; the voltage controlled oscillator (VCO) in the data separator stops and then restarts synchronously with the incoming data stream on +ENDATA, and the phase detector goes into phase only mode. Stopping and restarting the VCO ensures that a relatively low initial phase error occurs so that the lock-up time is well below the time allotted by the 11-byte preamble field. After preamble is detected in the data separator, PRDET becomes true, which reduces the loop gain so that the band width is reduced. Additionally, the PRDET signal is sent to the read gate synchronization logic. The data standardizer in the data separator uses the recovered clock to decide if a +ENDATA pulse has occurred in each window.

The window is nominally 50 nanoseconds wide for 10 megabits per second NRZ data rate. The data standardizer then resynchronizes +ENDATA to the recovered clock, using the window constraint, and sends synchronous data and synchronization clock to the ENDEC.

When -READ GATE becomes false, the RDGAT to the data separator is delayed for about seven write clock periods. This ensures that stopping the VCO does not interfere with the READ/REF clock switch over. The VCO is stopped and then restarted synchronously with write clock to ensure minimal initial phase error. The data separator locks to the write clock in phase/frequency mode and wide band width. After power up, the data separator is initialized through U63 and the microwire bus (National trade mark) on the data separator. This establishes the window centering for the data standardizer in the data separator.

#### B ENDEC, READ MODE

After the read gate synchronization logic receives a preamble-detected signal from the PLL, along with READ GATE true, it issues RGATE to the ENDEC. The ENDEC then switches the READ/REF clock output from the reference clock (servo PLL write clock) to the PLL derived read clock, with no more than two clock periods missing, and no glitches allowed at the switch over point. Additionally, the read gate synchronization logic sends EXPRCMP to the ENDEC after approximately 500 nanoseconds from the leading edge of RGATE. At this point, the ENDEC has acquired code framing and can decode the (2,7) 1/2 encoded data to NRZ data. The NRZ data at the MSOUT output on the ENDEC is then reclocked with the data resynchronizer before going to the line driver. The RDR-FCK output of the ENDEC is also sent to another line driver which then goes to the ESDI interface. When READ GATE becomes false, RGATE and EXPRCMP to the ENDEC both become false at the same time, but RDGAT to the data separator is delayed for about seven write clock periods. This is to ensure that a proper switch over occurs on the READ/REF clock output of the ENDEC. The switch over from the read clock to the reference clock (write clock) occurs at the same time that -READ GATE (or RGATE at the ENDEC) becomes false.

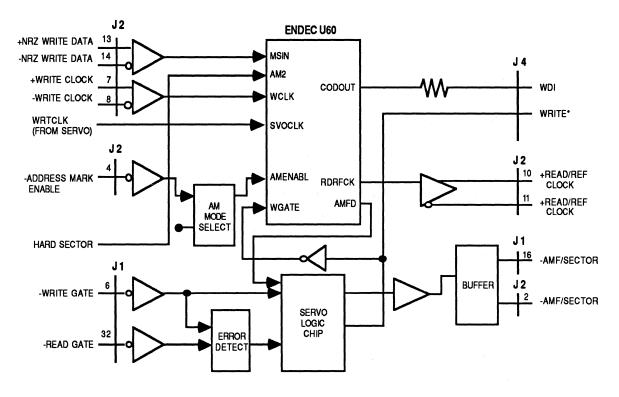

#### 4.3.4 Write Path and Encoding

Figure 16, Write Path, details the write path. The ENDEC receives NRZ data from the line receivers and encodes it to (2,7) 1/2 code according to the encoding rules, using write clock as the master clock.

Figure 16 Write Path

#### A SOFT SECTOR WRITE

When the drive is configured for soft sector operation (JP31 installed), address marks are written on the drive through the -AME (address mark enable) line along with -WRITE GATE. An address mark is a dc erased portion of the track of 3 bytes. When the controller initiates a WRITE in soft sector mode, the -WRITE GATE input becomes true and -AME is enabled at the time an address mark is to be written. The ENDEC does not send pulses out on the WDI lines during this time so that the dc erased mark is written on the disk.

#### B HARD SECTOR WRITE

When the drive is configured for hard sector operation (JP31 removed), address marks are not written on the disk and the start of a sector is indicated by the drive with the sector mark output. The number of sectors per track is selected by jumpers, or can be configured through the interface if the drive is jumpered for this option. -WRITE GATE again initiates a write operation.

#### C ENCODING DATA

The NRZ WRITE DATA and WRITE CLOCK from the controller are received by the line receivers on the drive, and are converted to TTL levels before being sent to the ENDEC. The ENDEC then encodes the NRZ data to (2,7) 1/2 code that is sent out of the COD-OUT output of the ENDEC. This then goes to the WDI input of the flex circuit.

#### D ENCODING RULES

The ENDEC, when in WRITE mode, encodes the NRZ write data using (2, 7) 1/2 encoding rules. The NRZ code is encoded to meet the desired run constraints of no fewer than two, and no more than seven, encoded zeros written between transitions. By doing this, any long runs of NRZ zeros are encoded such that transitions are present for the clock regeneration circuitry (the data separator PLL).