# **Technical Manual**

# **Reflex**<sup>®</sup>**II**

# **Technical Manual**

# **Reflex**<sup>®</sup> II

### PUBLICATION NUMBER 81 1091B

#### PROPRIETARY INFORMATION

The information contained herein is proprietary to and considered a trade secret of Microdata Corporation and shall not be reproduced in whole or part without the written authorization of Microdata Corporation.

© 1981 Microdata Corporation All rights reserved TM-Trademark of Microdata Corporation Specifications Subject to Change Without Notice Printed in U.S.A.

#### FOR INTERNAL USE ONLY

# **Microdata Corporation**

2361 McGaw Avenue, Irvine, California 92714 Telephone: 714/540-6730 Customer Service Training

#### CONTENTS

| Section                                          | Page |

|--------------------------------------------------|------|

| 1 GENERAL DESCRIPTION                            |      |

| Introduction                                     | 1-1  |

| Features, Options, and Accessories               | 1-3  |

| Features                                         | 1-3  |

| Options                                          | 1-3  |

| Accessories                                      | 1-3  |

| General                                          | 1-4  |

| Functional Description                           | 1-4  |

| Input                                            | 1-5  |

| Address Select                                   | 1-6  |

| Bus and Tag Lines                                | 1-6  |

| Configuration Request                            | 1-6  |

| Write Data and Write Clock                       | 1-6  |

| Output                                           | 1-6  |

| Positioning                                      | 1-7  |

| Read/Write • • • • • • • • • • • • • • • • • • • | 1-8  |

| Physical Description                             | 1-10 |

| Safety Features                                  | 1-11 |

| Operator                                         | 1-11 |

| Drive                                            | 1-11 |

| Data                                             | 1-11 |

| Nameplate identification                         | 1-11 |

|                                                  |      |

| Sect | ion <u>P</u>                                        | Page |

|------|-----------------------------------------------------|------|

| 2    | PHYSICAL PLANNING AND INTERFACE REQUIREMENTS        |      |

|      | Introduction                                        | 2-1  |

|      | Environmental Conditions                            | 2-1  |

|      | Stabilization                                       | 2-1  |

|      | Temperature                                         | 2-1  |

|      | Humidity                                            | 2-1  |

|      | Altitude                                            | 2-1  |

|      | Air Flow                                            | 2-2  |

|      | Noise Level                                         | 2-2  |

|      | Storage                                             | 2-2  |

|      | Space Requirements                                  | 2-2  |

|      | Power Requirements                                  | 2-2  |

|      | Input AC Voltage Fluctuations                       | 2-4  |

|      | Power Cable Configurations                          | 2-4  |

|      | AC Power With Optional Internal Power Supply        | 2-5  |

|      | AC Power Without Optional Internal Power Supply     | 2-5  |

|      | DC Voltage Without Optional Internal Power Supply . | 2-6  |

|      | Grounding                                           | 2-7  |

|      | Interface Requirements                              | 2-8  |

|      | Logic Interface                                     | 2-8  |

|      | Cabling                                             | 2-8  |

|      | Data Cable                                          | 2-8  |

|      | Signal Cable • • • • • • • • • • • • • • • • • • •  | 2-8  |

|      | Frame Ground Cable                                  | 2-10 |

| Pa                                          | ige |

|---------------------------------------------|-----|

| Available Cables                            | 10  |

| Connector Jacks                             | ·11 |

| Connector Orientation 2-                    | ·11 |

| Signal Cable Descriptions 2-                | 11  |

| Pin Assignments                             | 11  |

| Signal Cable Definitions 2-                 | ·11 |

| Data Cable                                  | ·22 |

| Pin Assignments                             | ·22 |

| Definitions                                 | ·23 |

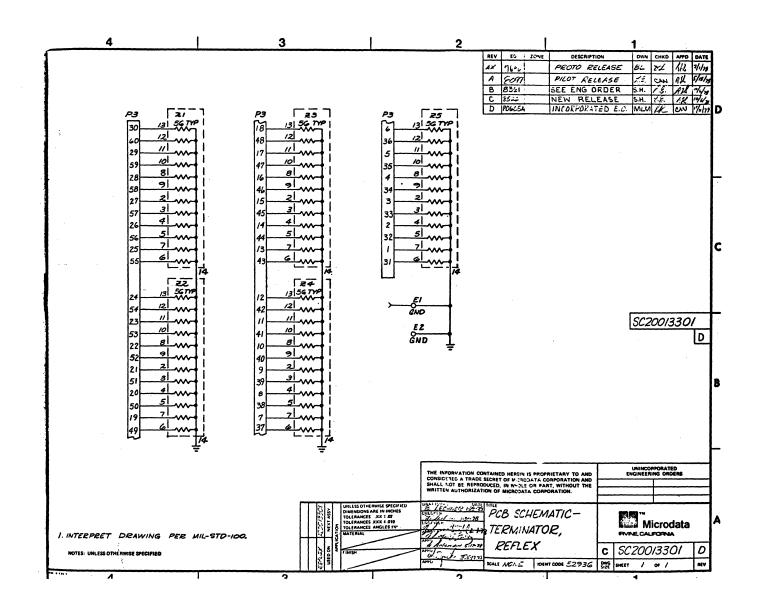

| Transmitters, Receivers, and Terminators 2- | -24 |

| Transmitters and Receivers                  | 24  |

| Terminators                                 | -24 |

| Data Format                                 | -27 |

| Format Considerations                       | -27 |

| Head Select                                 | 27  |

| Write Amplifier                             | -27 |

| Read To Write                               | 27  |

| Read VCO                                    | 27  |

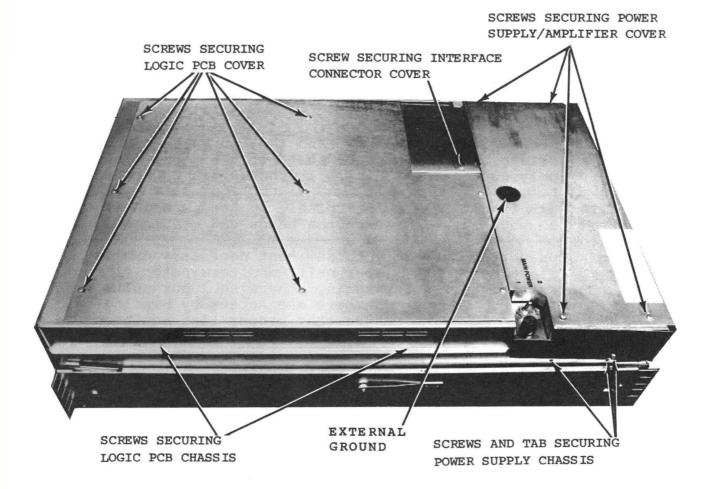

| Splice                                      | ·27 |

| Preamble                                    | -28 |

| Postamble                                   | -28 |

| Synch Pattern                               | -29 |

| Secti | lon                                                      | Page |

|-------|----------------------------------------------------------|------|

|       | Method                                                   | 2-29 |

|       | Write Initialization                                     | 2-29 |

|       | Write Record Data                                        | 2-30 |

|       | Read                                                     | 2-31 |

|       | Format Summary                                           | 2-32 |

|       | Fixed Head Per Track                                     | 2-33 |

|       | Data Security                                            | 2-33 |

| 3     | INSTALLATION AND OPERATION                               |      |

|       | Introduction                                             | 3-1  |

|       | Installation Check List                                  | 3-1  |

|       | Unpacking                                                | 3-3  |

|       | Physical Inspection                                      | 3-4  |

|       | Reflex II Units Without Internal Power Supply            | 3-5  |

|       | Grounding                                                | 3-6  |

|       | AC Power Cable                                           | 3-7  |

|       | Signal, Data, and Exerciser Cables                       | 3-8  |

|       | Initial Checkout Procedure                               | 3-10 |

|       | System Installation                                      | 3-11 |

|       | Power Verification                                       | 3-13 |

|       | 60 Hz Verification • • • • • • • • • • • • • • • • • • • | 3-13 |

|       | 50 Hz Verification • • • • • • • • • • • • • • • • • • • | 3-14 |

|       | Power Conversion                                         | 3-14 |

|       | 60 Hz to 50 Hz • • • • • • • • • • • • • • • • • •       | 3-14 |

|       | 50 Hz to 60 Hz                                           | 3-15 |

| Section                        |      |     |   |   |   |   |   |   |   | Page |

|--------------------------------|------|-----|---|---|---|---|---|---|---|------|

| Operation                      |      |     |   |   |   |   |   |   |   |      |

| Operator Indicator Panel       | • •  | • • | • | • | • | • | • | • | • | 3-15 |

| Maintenance Controls           | ••   |     | • | • | • | • | • | • | • | 3-16 |

| Unit Address Selection         | ••   | • • | • | • | • | • | • | • | • | 3-19 |

| Illegal Head Address Selecti   | on . | ••• | • | • | • | • | • | • | • | 3-19 |

| Sector Selection               | •••  | ••  | • | • | • | • | • | • | • | 3-20 |

| 4 THEORY OF OPERATION          |      |     |   |   |   |   |   |   |   |      |

| Introduction                   | ••   | ••• | • | • | • | • | • | • | • | 4-1  |

| Physical Description           | ••   | • • | • | • | • | • | • | • | • | 4-1  |

| Power Components               | ••   | • • | • | • | • | • | • | • | • | 4-1  |

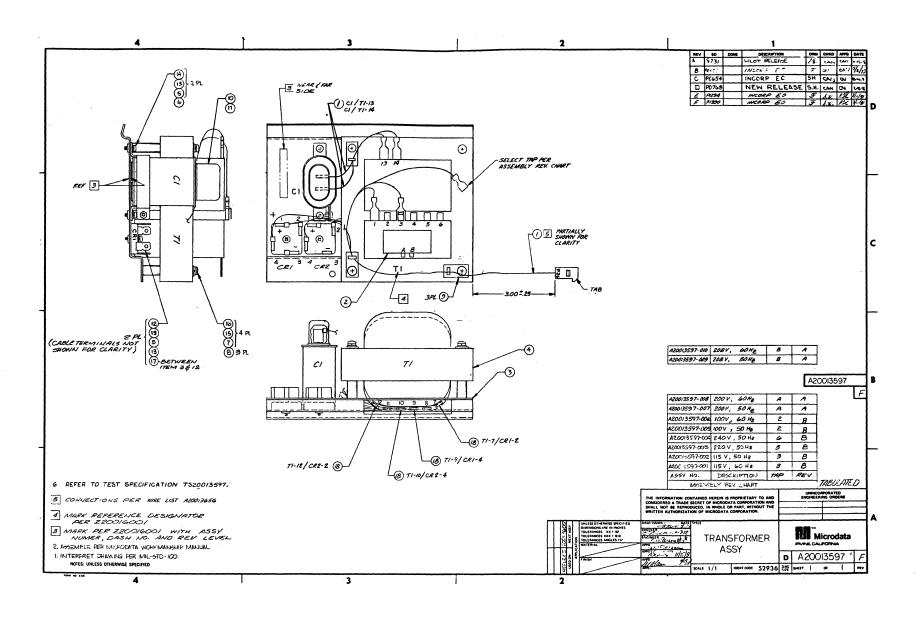

| Transformer Assembly           | ••   | ••• | • | • | • | • | • | • | • | 4-1  |

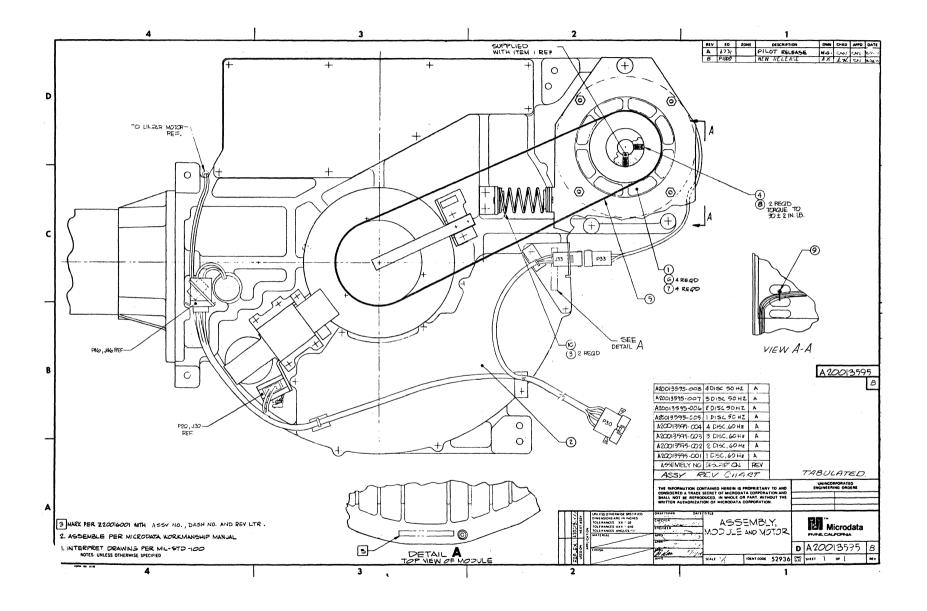

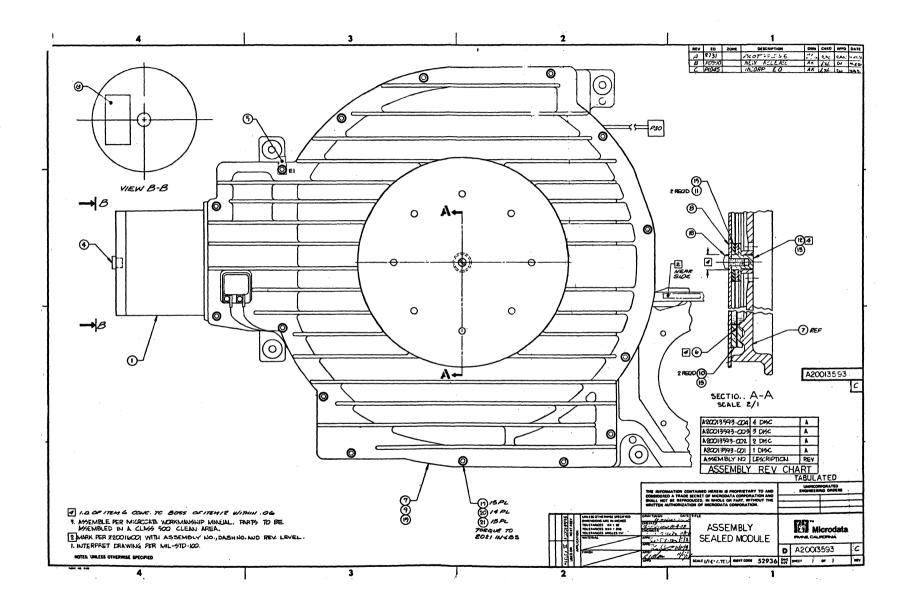

| Sealed Module and Motor Assemb | ly.  | ••• | • | • | • | • | • | • | • | 4-1  |

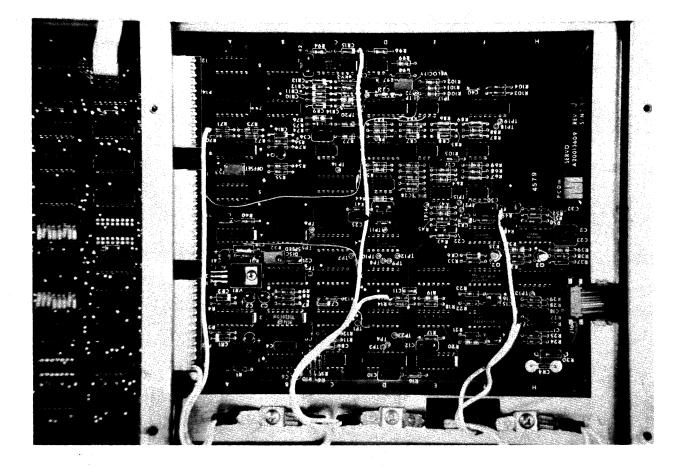

| Printed Circuit Boards         | ••   | ••• | • | • | • | • | • | • | • | 4-2  |

| General                        | ••   | ••• | • | • | • | • | • | • | • | 4-2  |

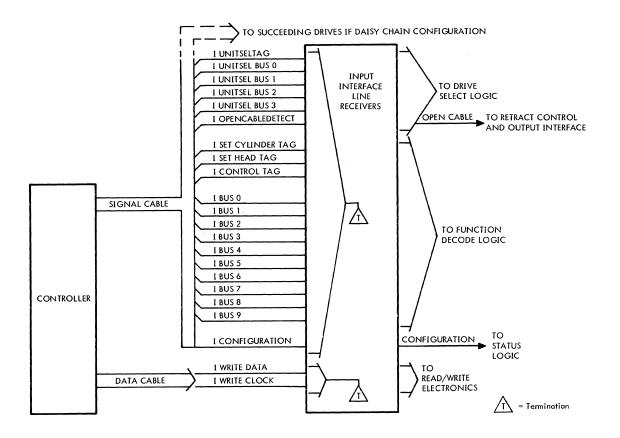

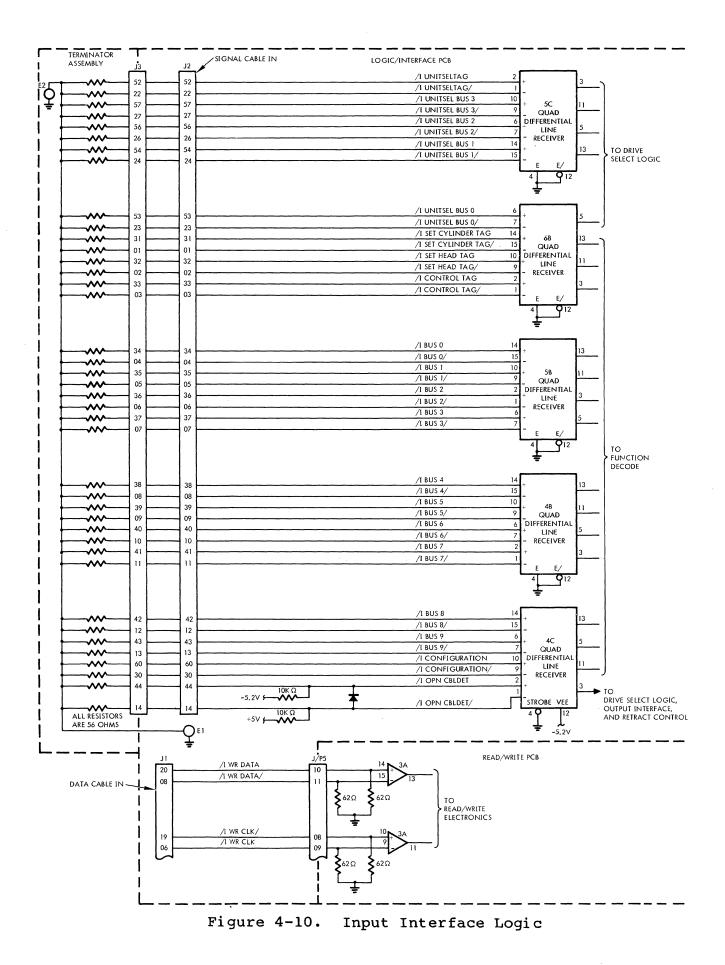

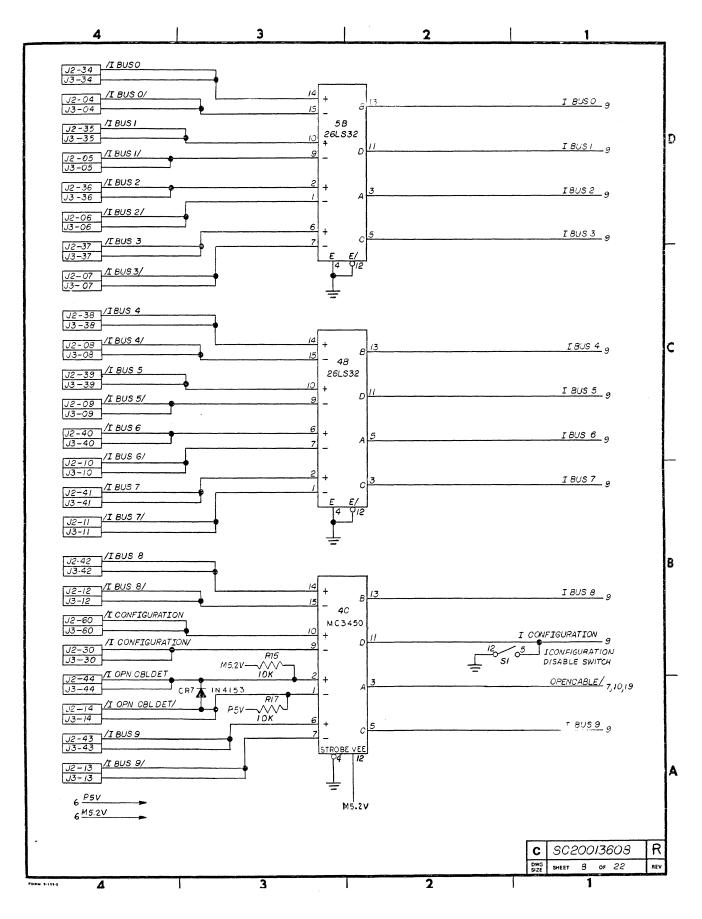

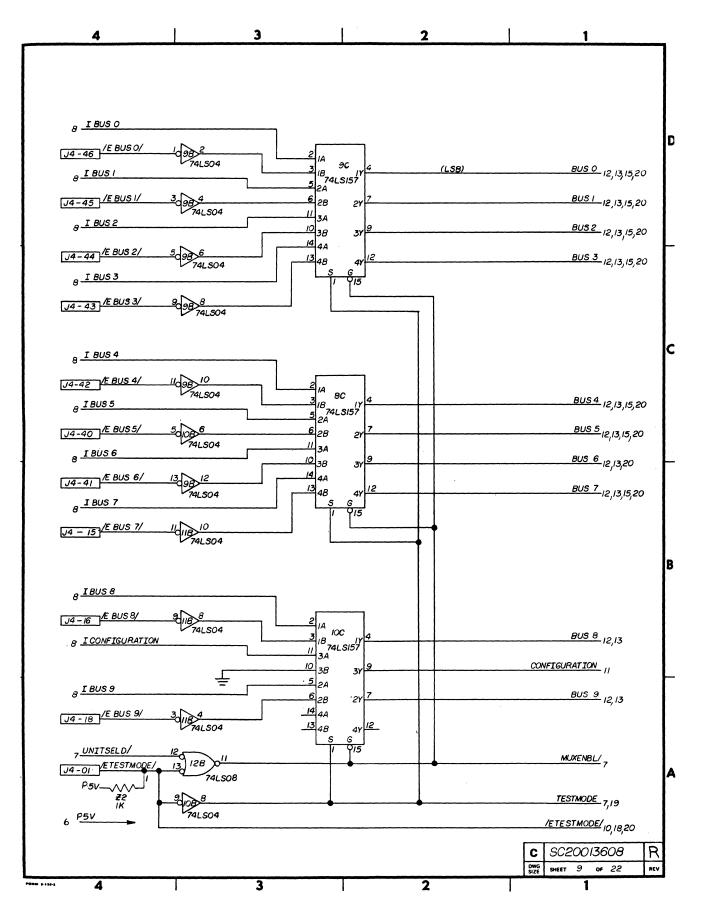

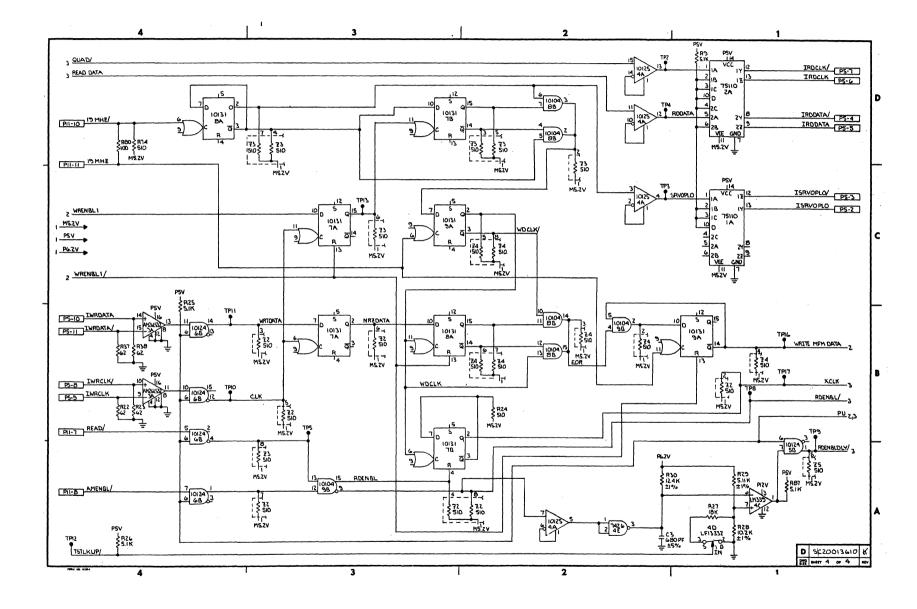

| Input/Output Interface         | ••   | ••• | • | • | • | • | • | • | • | 4-3  |

| Positioning System             | ••   | • • | • | • | • | • | • | • | • | 4-3  |

| Cooling and Clean Air System   | ••   | ••• | • | • | • | • | • | • | • | 4-3  |

| Read/Write System              | • •  | ••• | • | • | • | • | • | • | • | 4-3  |

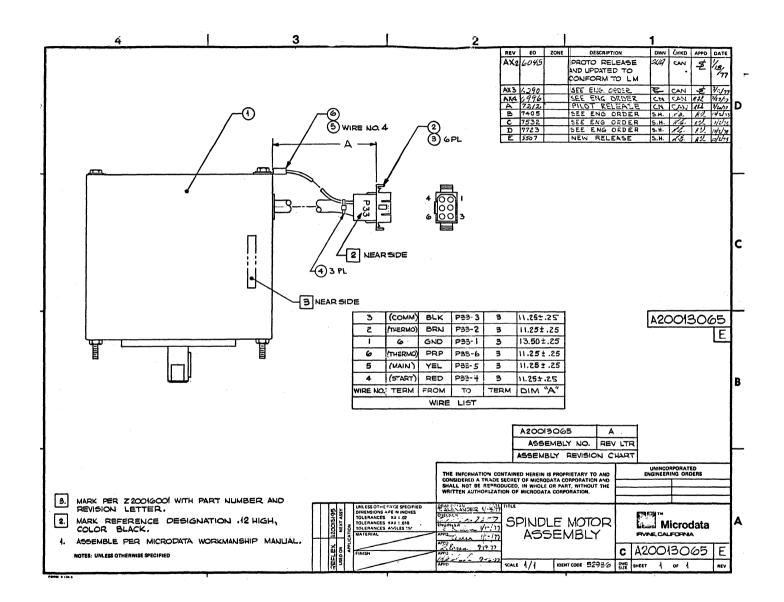

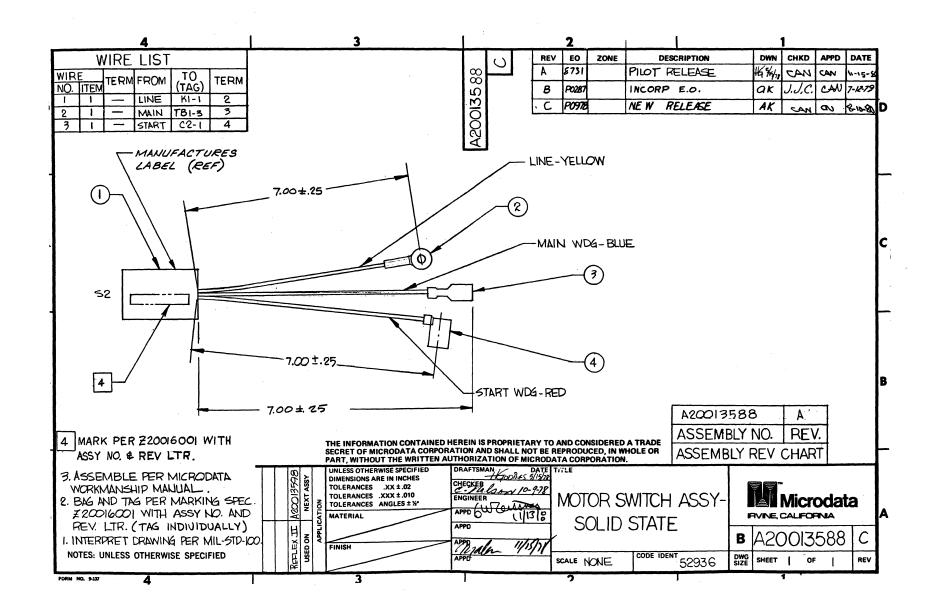

| Spindle Motor System           | ••   | • • | • | • | • | • | • | • | • | 4-4  |

| Functional Description         | • •  | ••• | • | • | • | • | • | • | • | 4-4  |

| General                        | ••   | ••• | • | • | • | • | • | • | • | 4-4  |

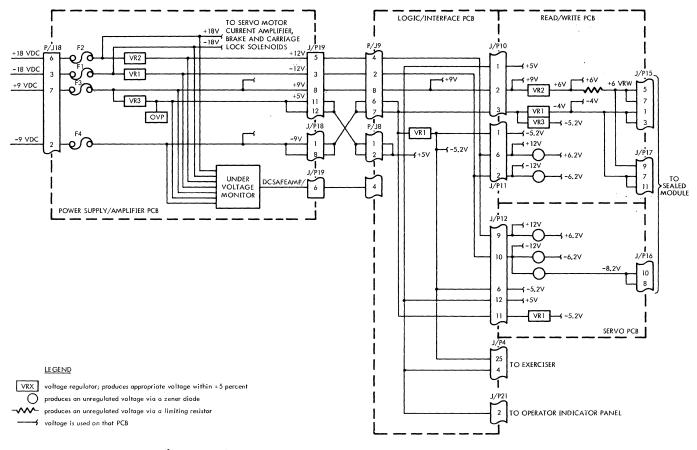

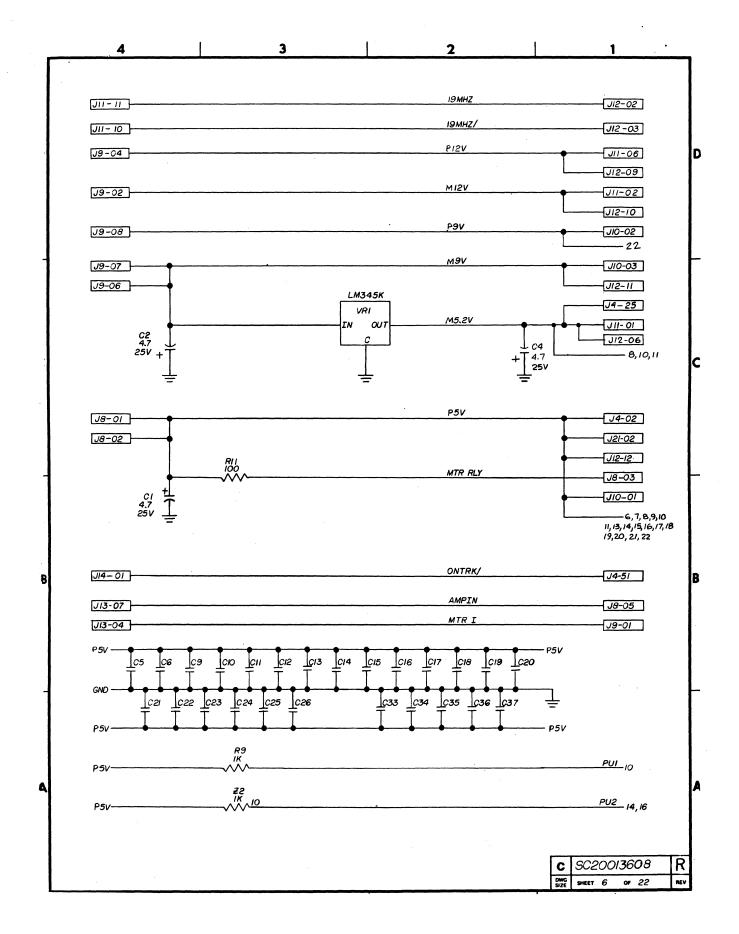

| Power Supplies and Distributio | n    |     |   |   |   |   |   |   |   |      |

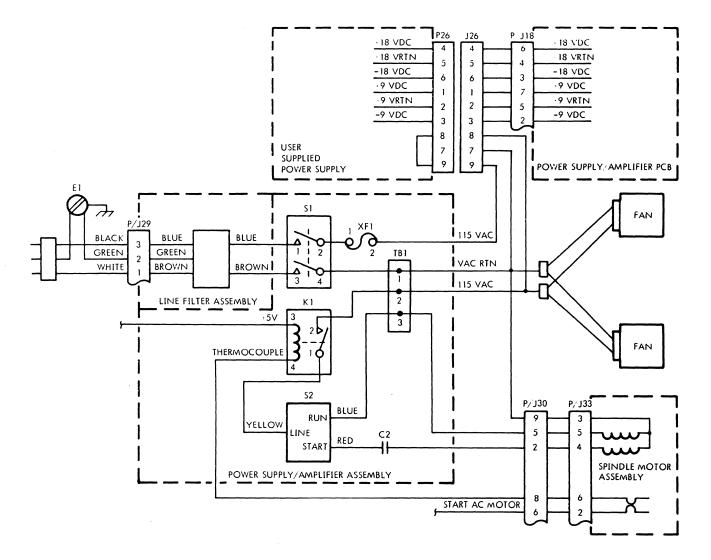

| Standard Power Configuration   | ••   | ••• | • | • | • | • | • | • | • | 4-8  |

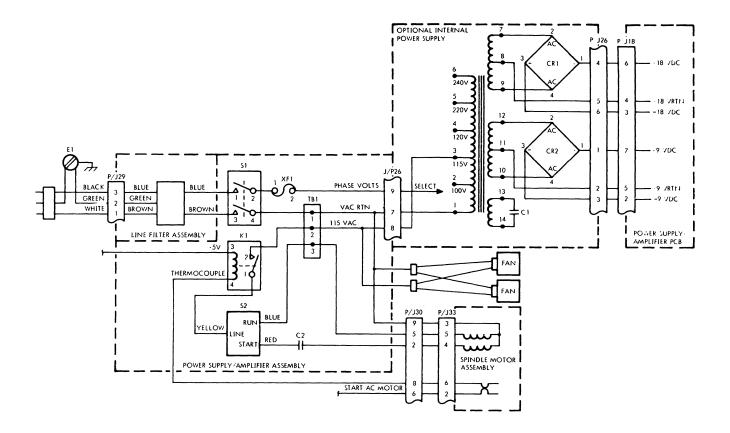

| Optional Power Configuration   |      |     | • | • | • | • | • | • | • | 4-10 |

| Section                              | Page |

|--------------------------------------|------|

| Power Supply/Amplifier PCB           |      |

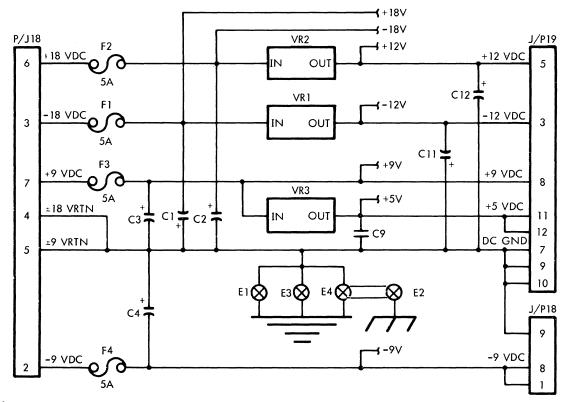

| Voltage Filtration and Generation    | 4-11 |

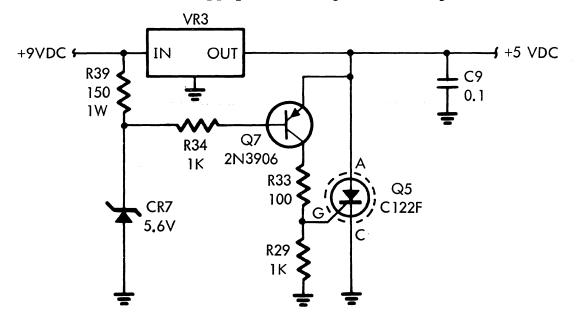

| +5 Volt Overvoltage Protection       | 4-11 |

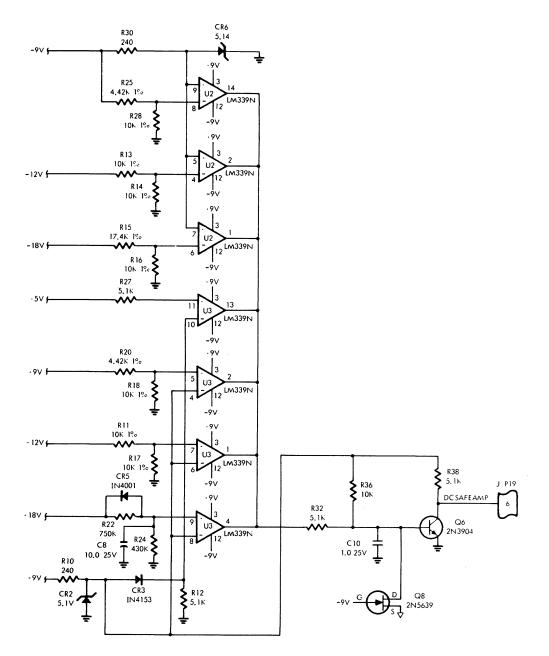

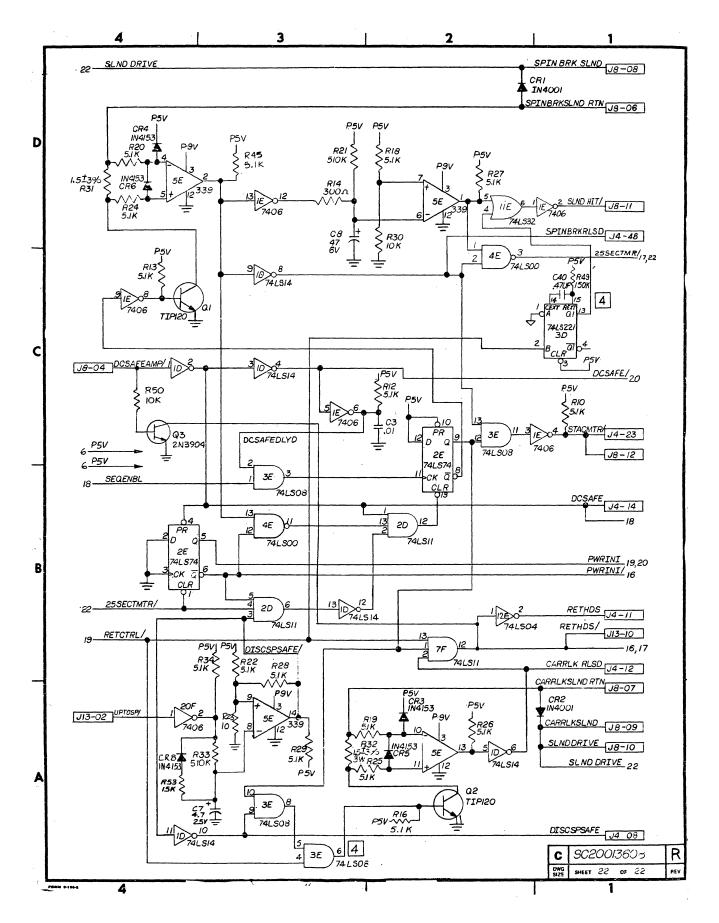

| Under Voltage Monitor (DCSAFE)       | 4-12 |

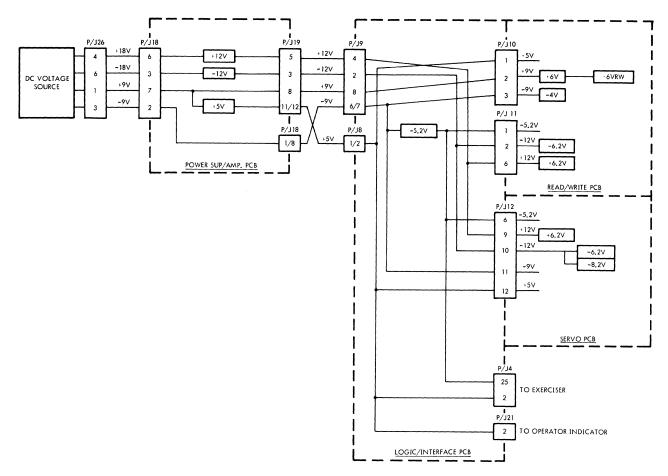

| DC Voltage Distribution              | 4-14 |

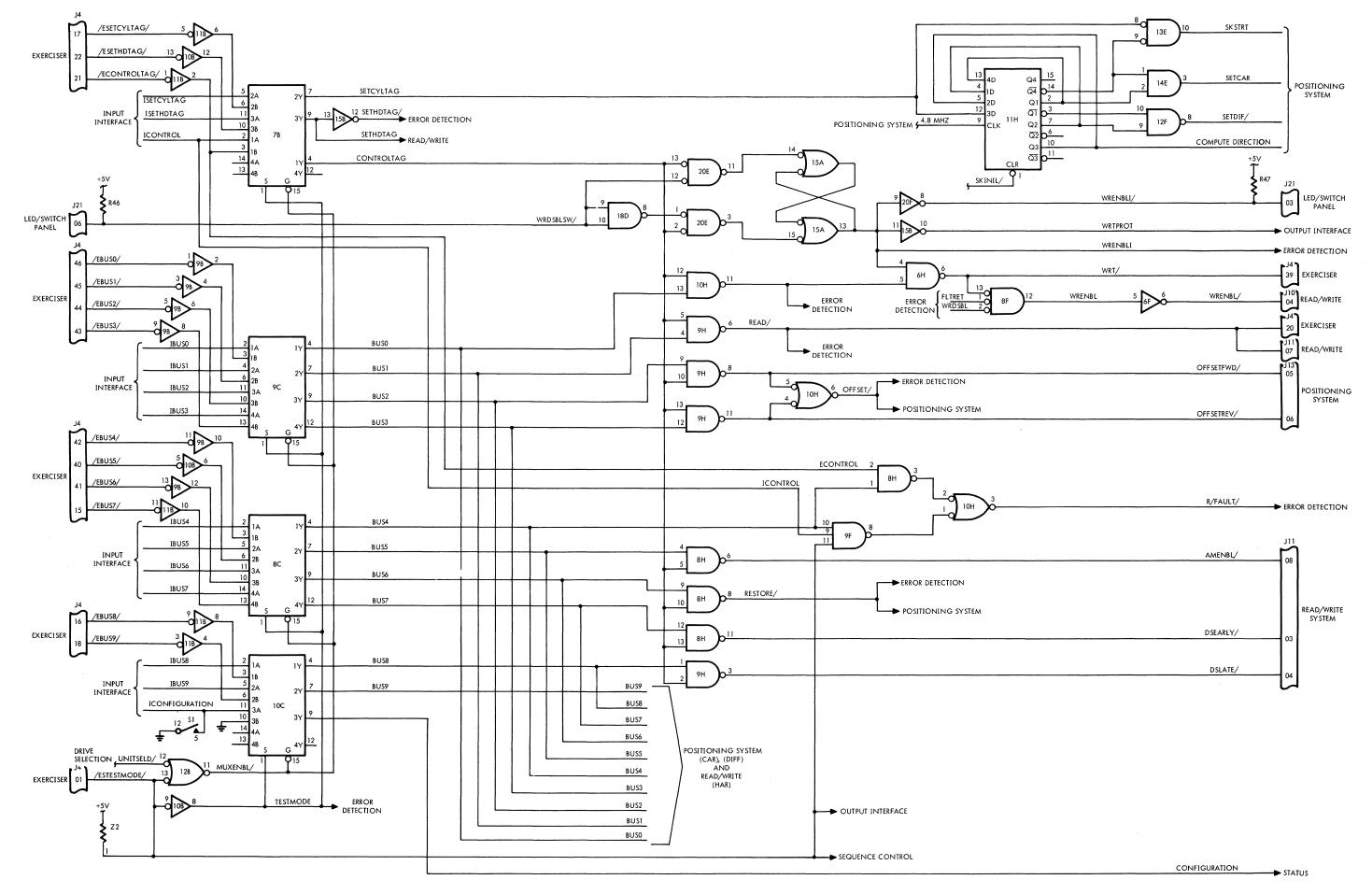

| Input Interface                      | 4-15 |

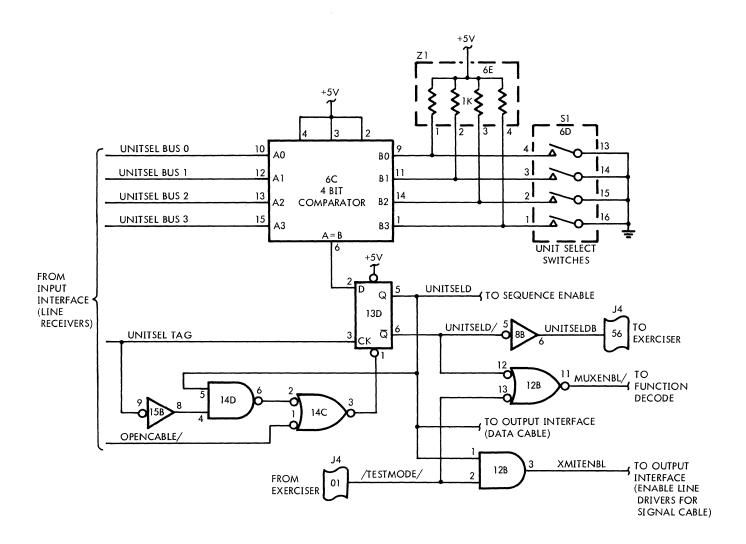

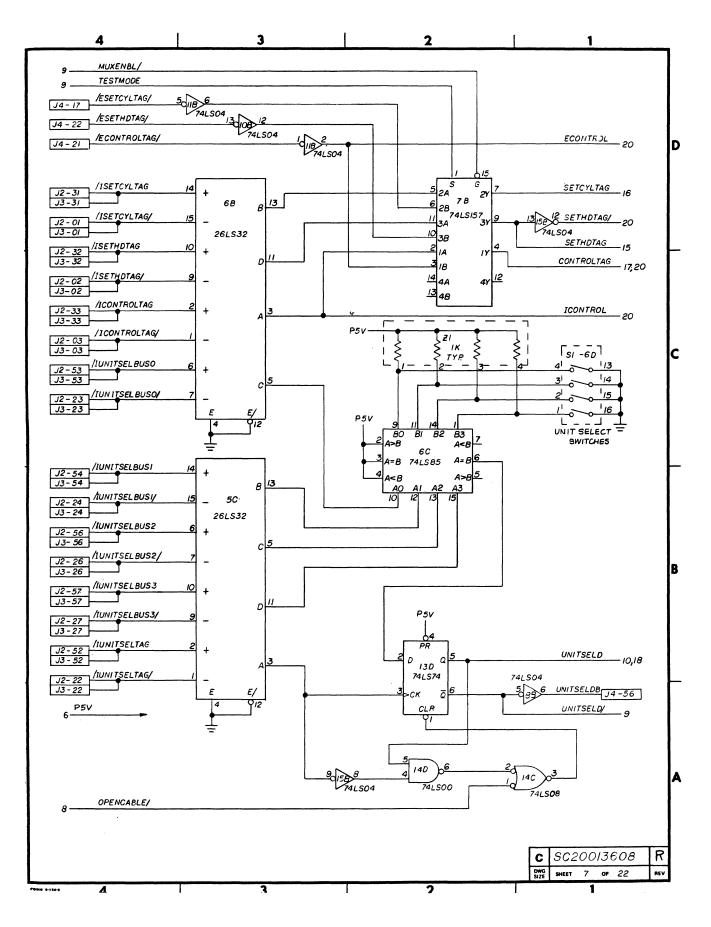

| Drive Selection                      | 4-17 |

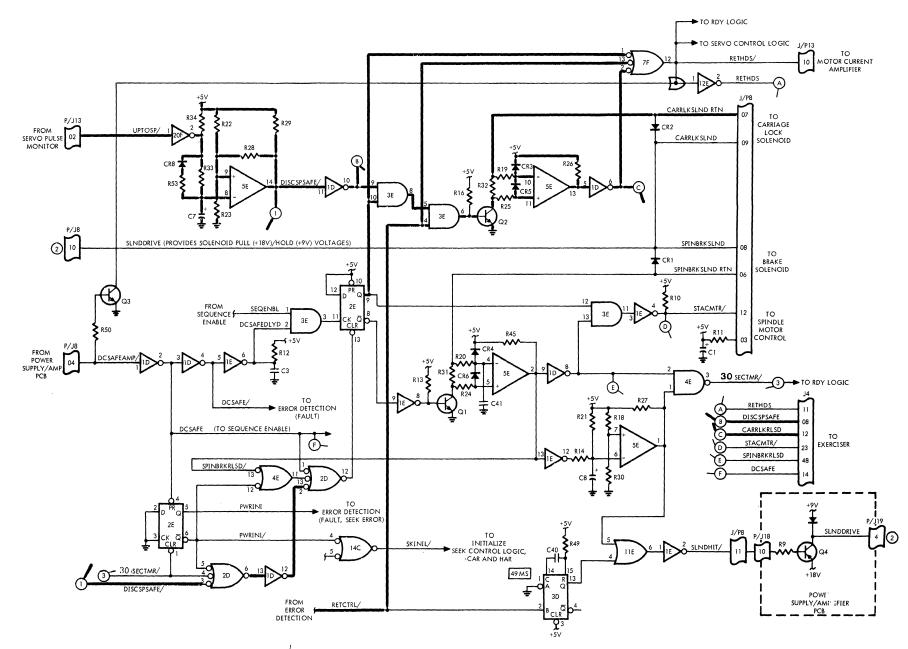

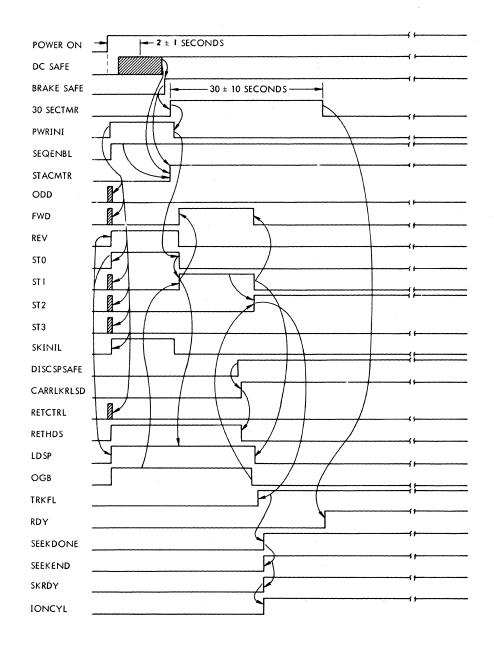

| Sequencing                           | 4-22 |

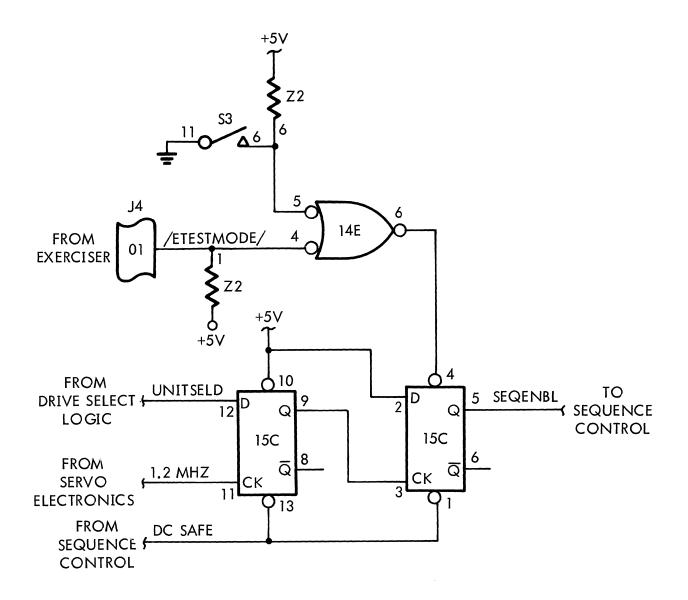

| Sequence Enable                      | 4-22 |

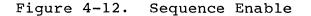

| Sequence Control                     | 4-24 |

| DCSAFE                               | 4-24 |

| PWRINI                               | 4-27 |

| SEQENBL                              | 4-28 |

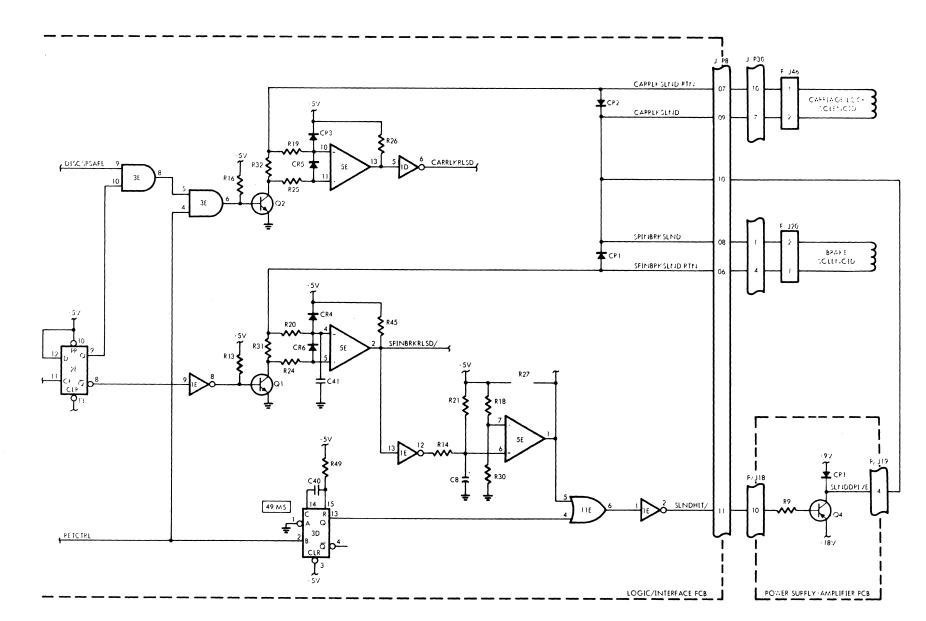

| Energizing the Spindle Motor         | 4-28 |

| Spindle Brake Released (SPINBRKRLSD) | 4-28 |

| Solenoid Activated (Released)        | 4-28 |

| 25-Second Timer                      | 4-32 |

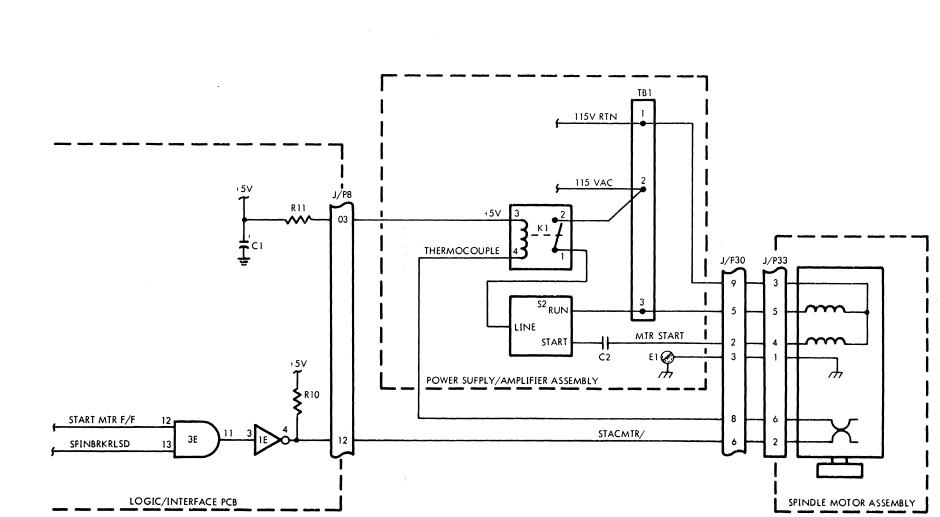

| Start AC Motor (STACMTR/)            | 4-33 |

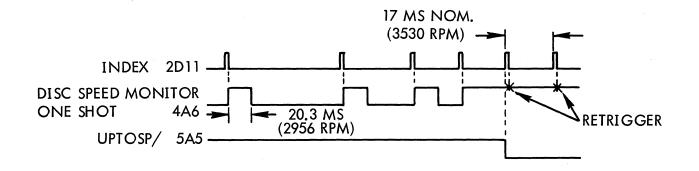

| Up-To-Speed                          | 4-33 |

| Disable Retract Heads (RETHDS/)      | 4-36 |

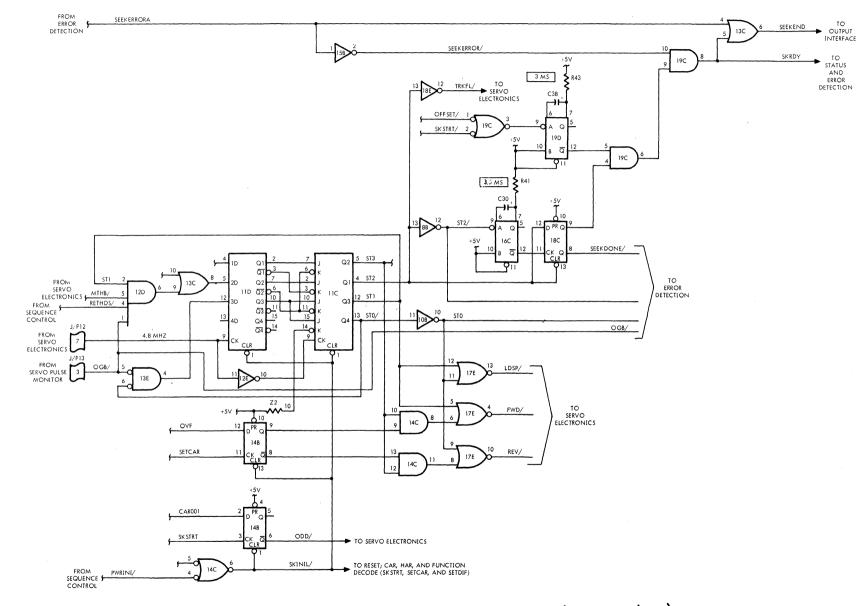

| Servo Control Logic (Sequence Up)    | 4-36 |

| Sequence Summary                     | 4-40 |

| Sequence Down                        | 4-40 |

| Function Decode                      | 4-40 |

| Section                                             | Page |

|-----------------------------------------------------|------|

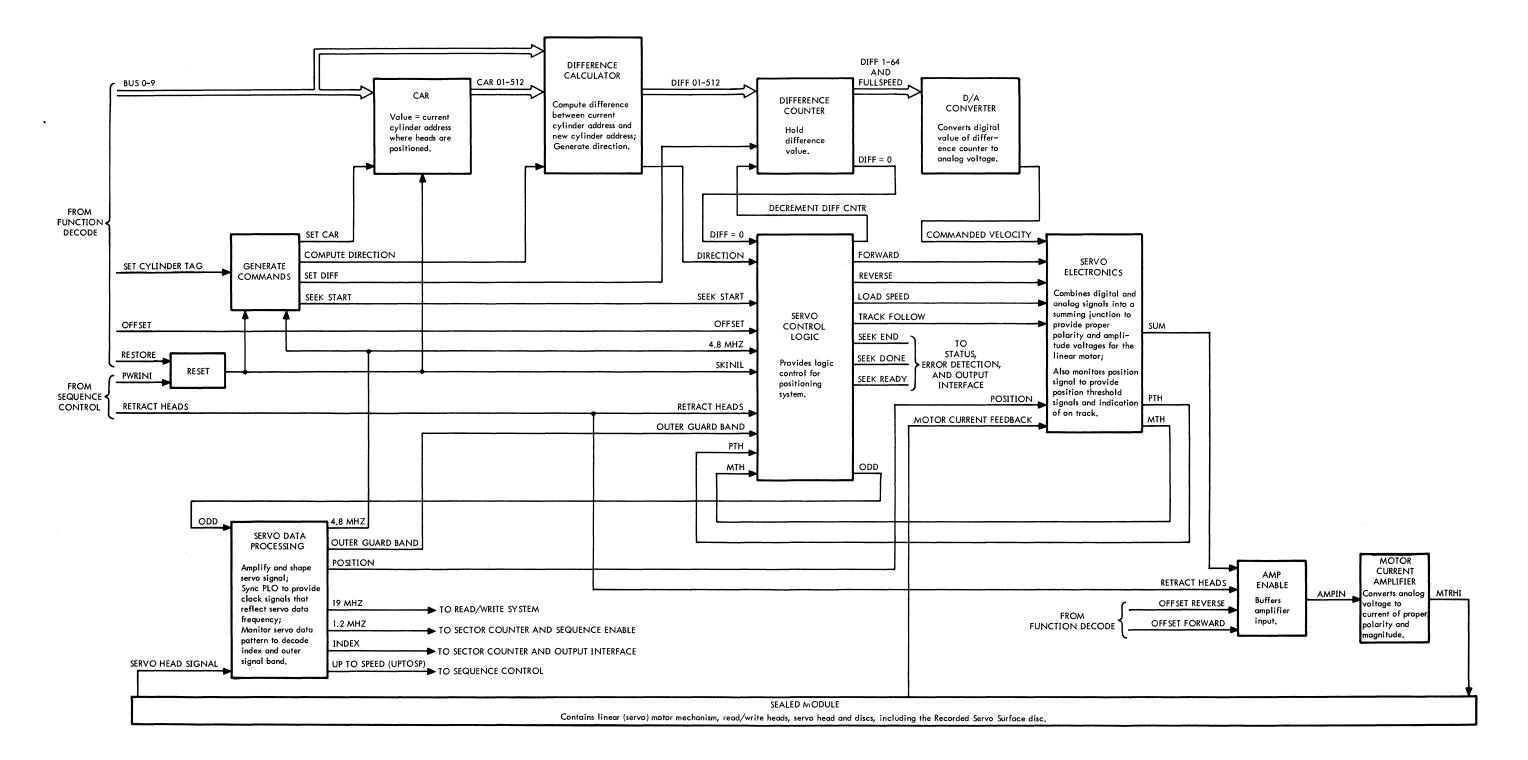

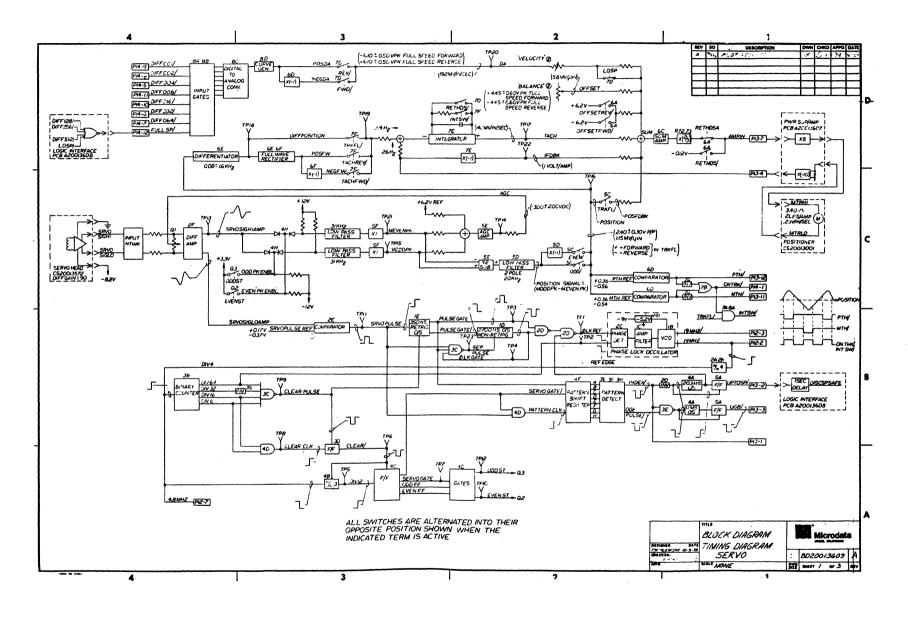

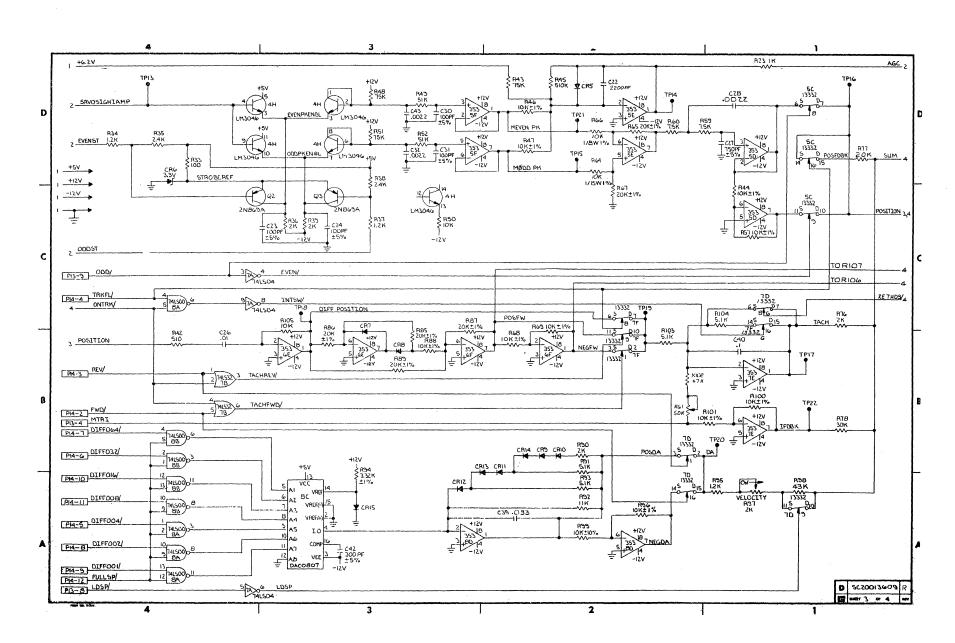

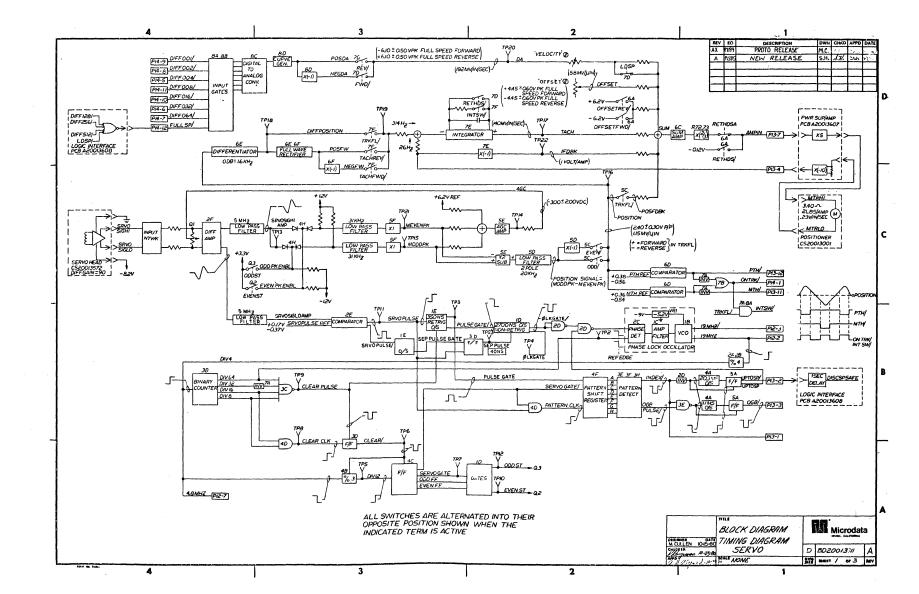

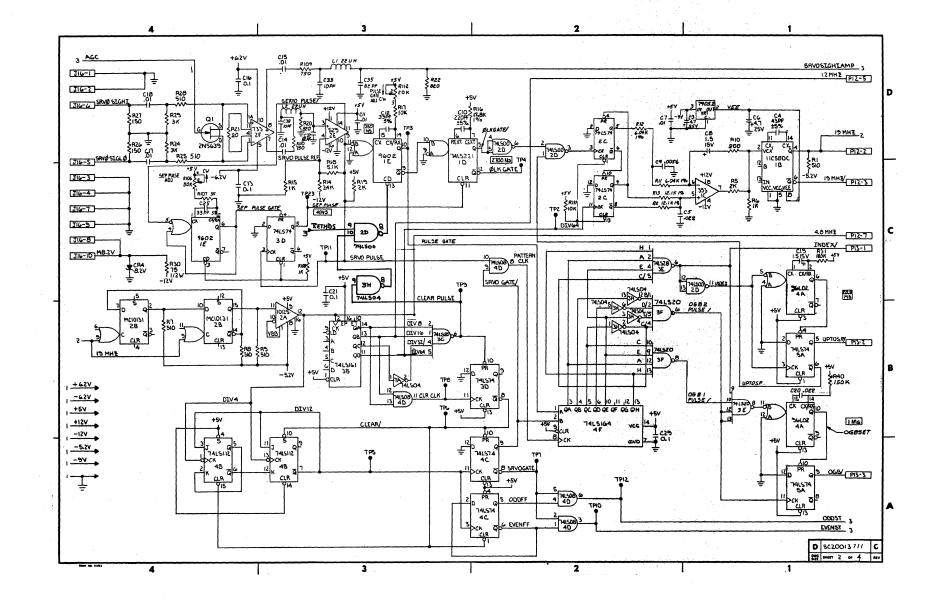

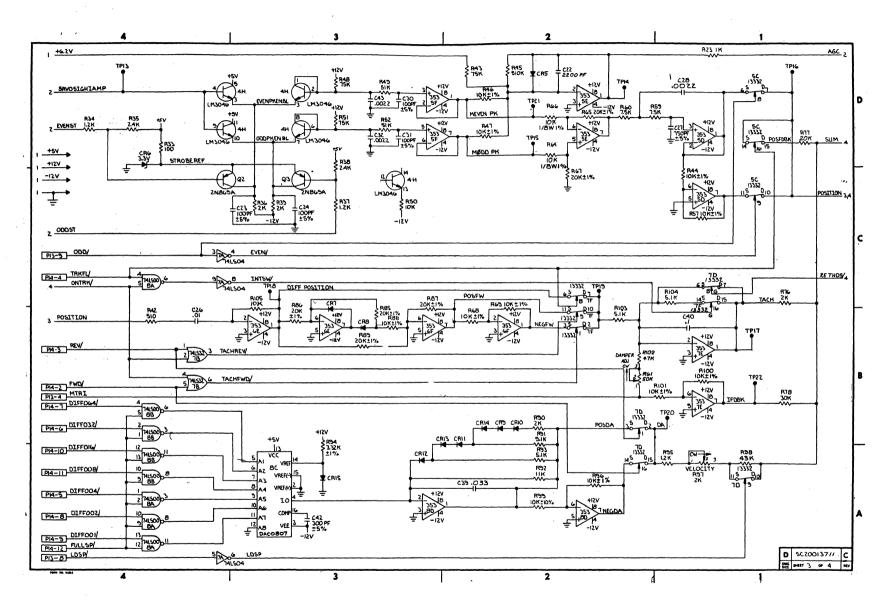

| Positioning System                                  | 4-47 |

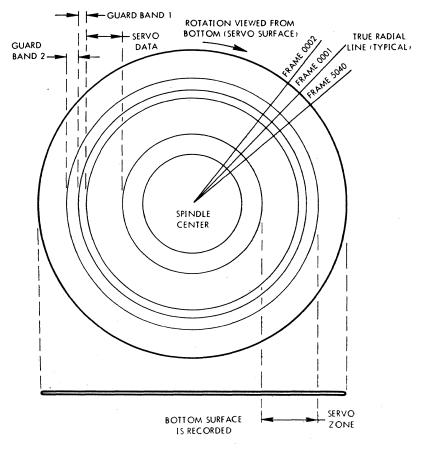

| Recorded Servo Surface                              | 4-47 |

| Servo System Control                                | 4-52 |

| Initial Seek                                        | 4-52 |

| Program Control Seek                                | 4-55 |

| Restore Operation                                   | 4-58 |

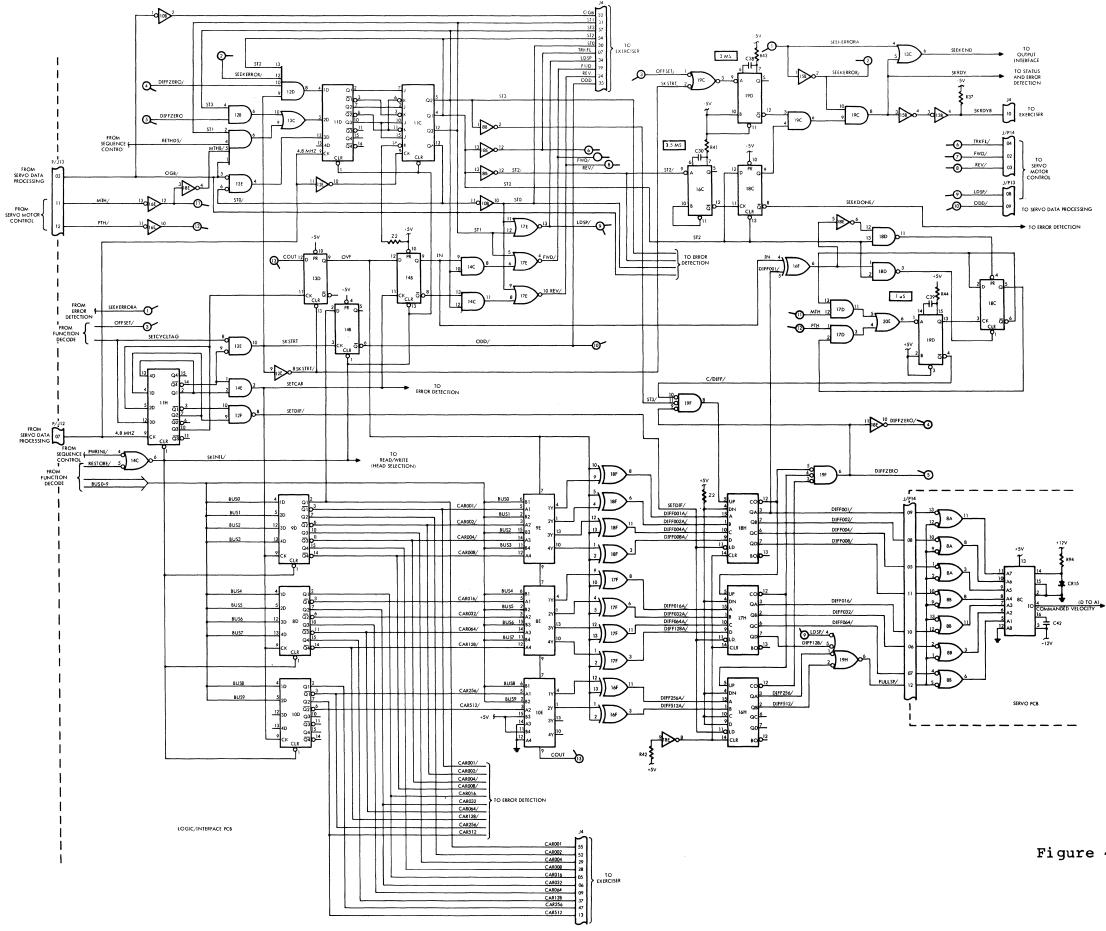

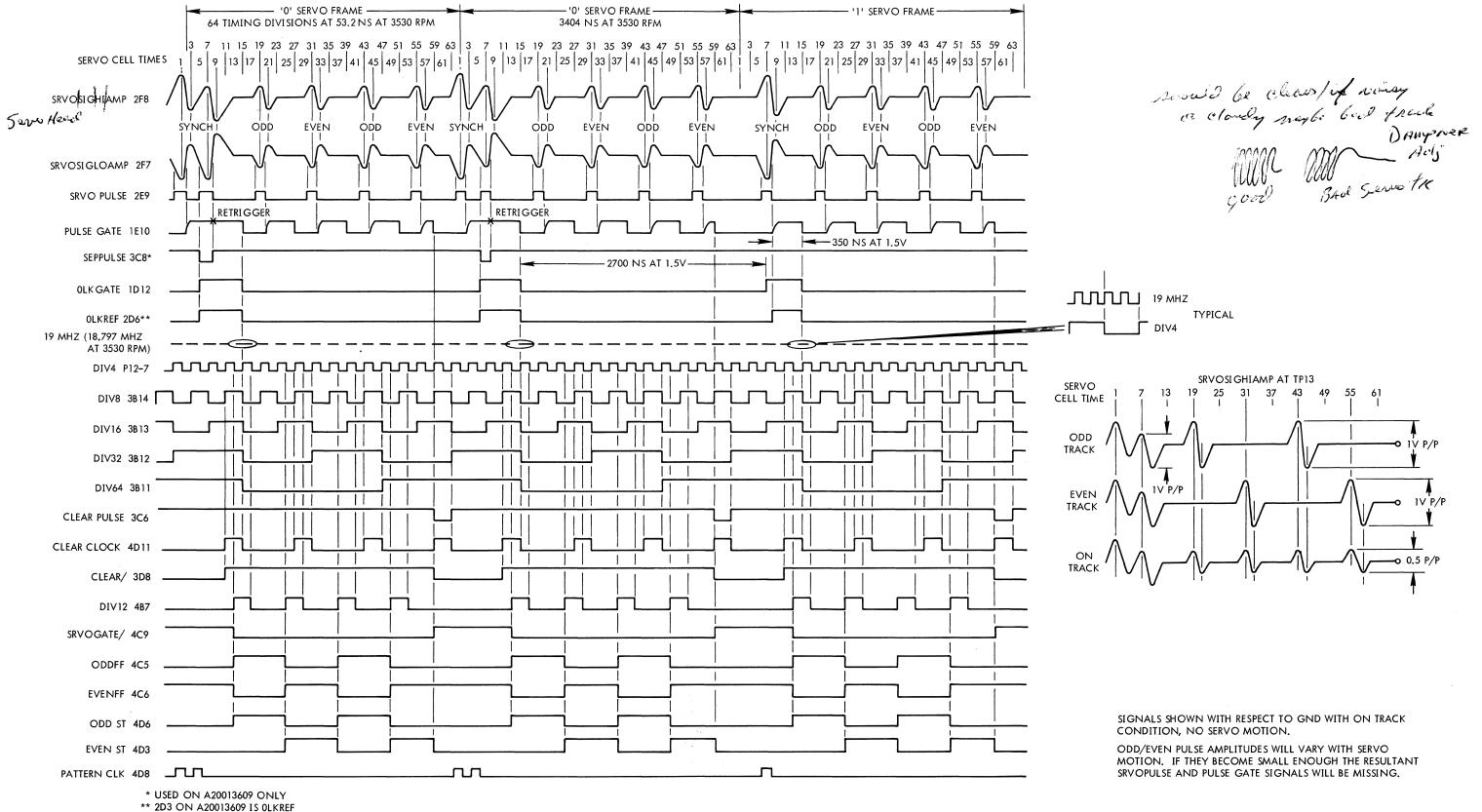

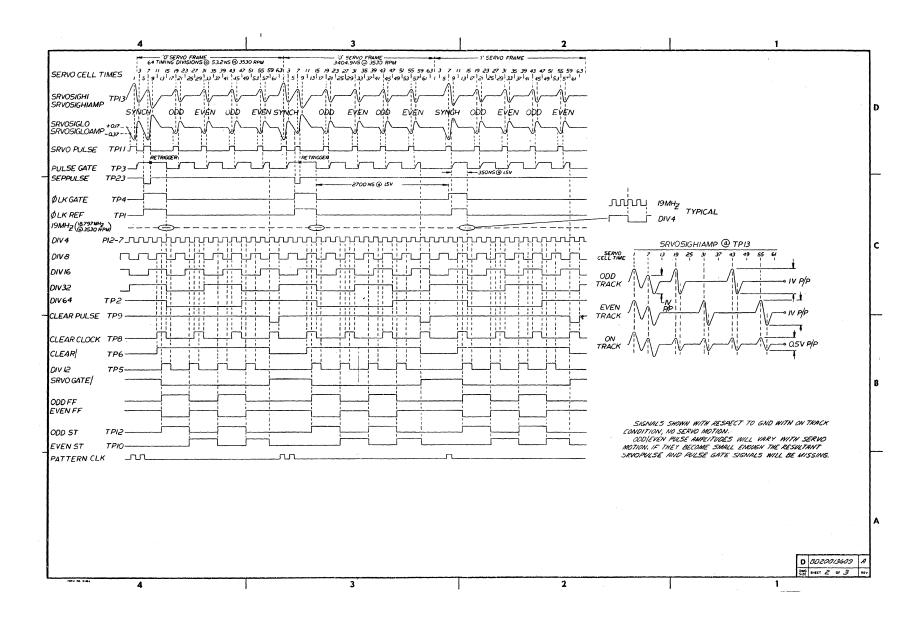

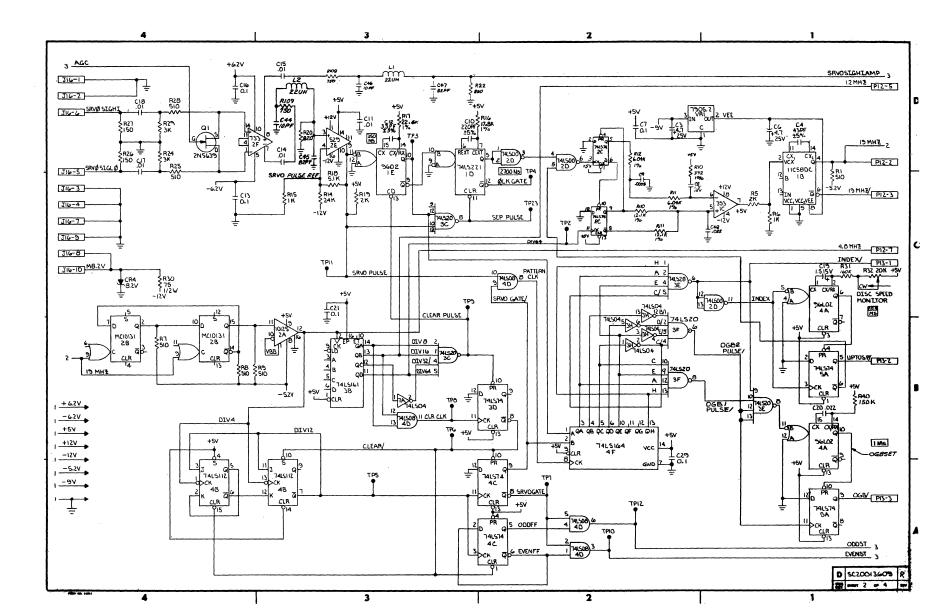

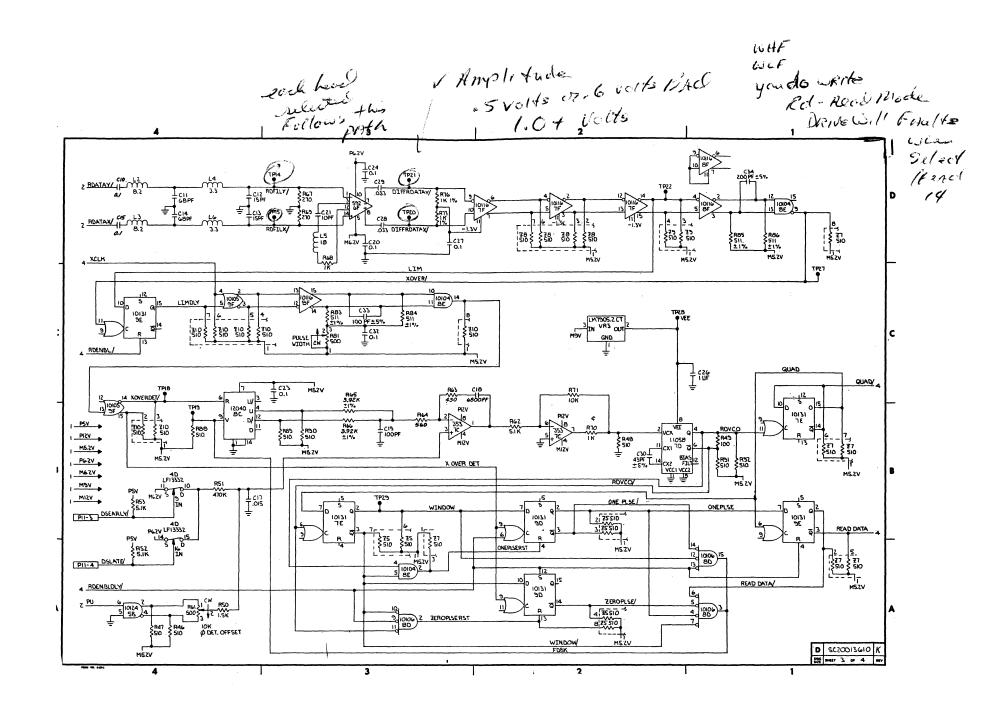

| Servo Data Processing Into Clocks and Position Info | 4-58 |

| Clock Processing                                    | 4-58 |

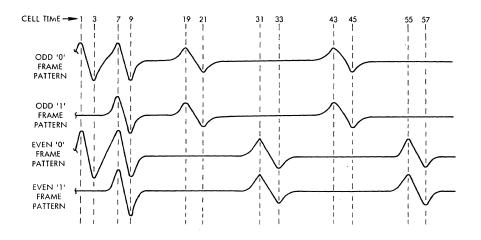

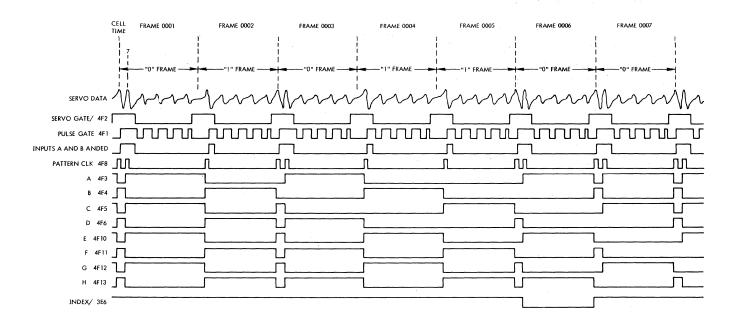

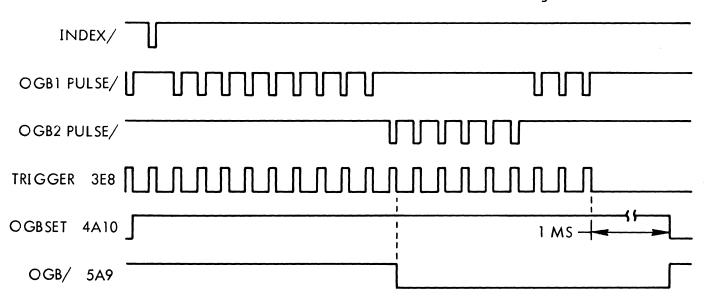

| Pattern Detection                                   | 4-63 |

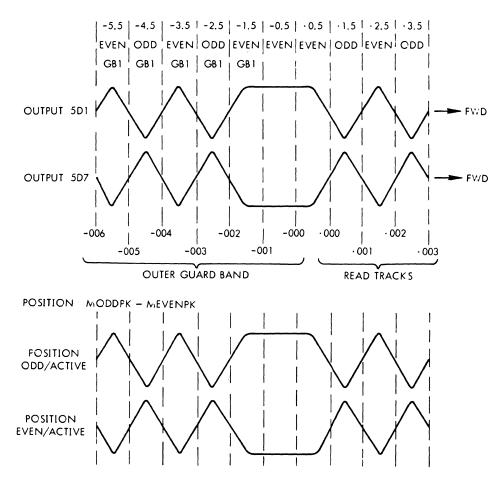

| Position Signal Generation                          | 4-65 |

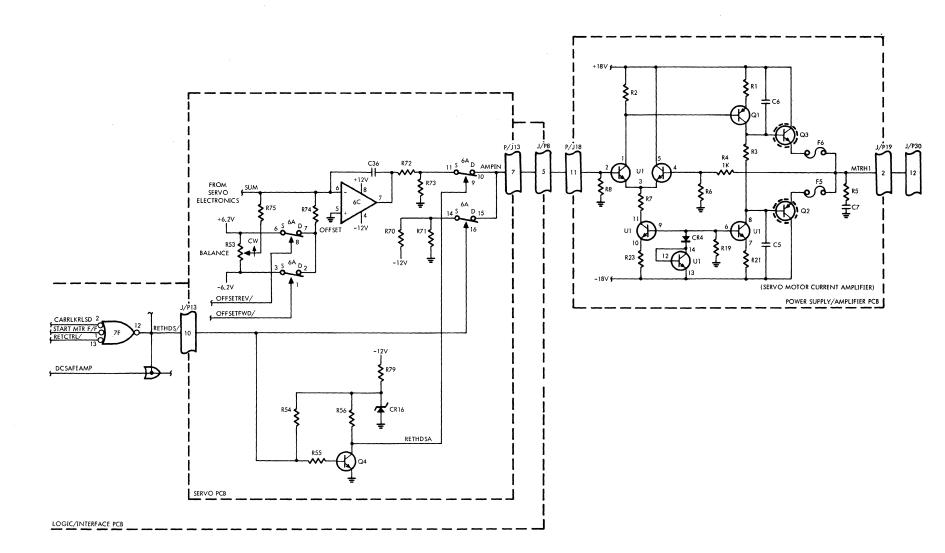

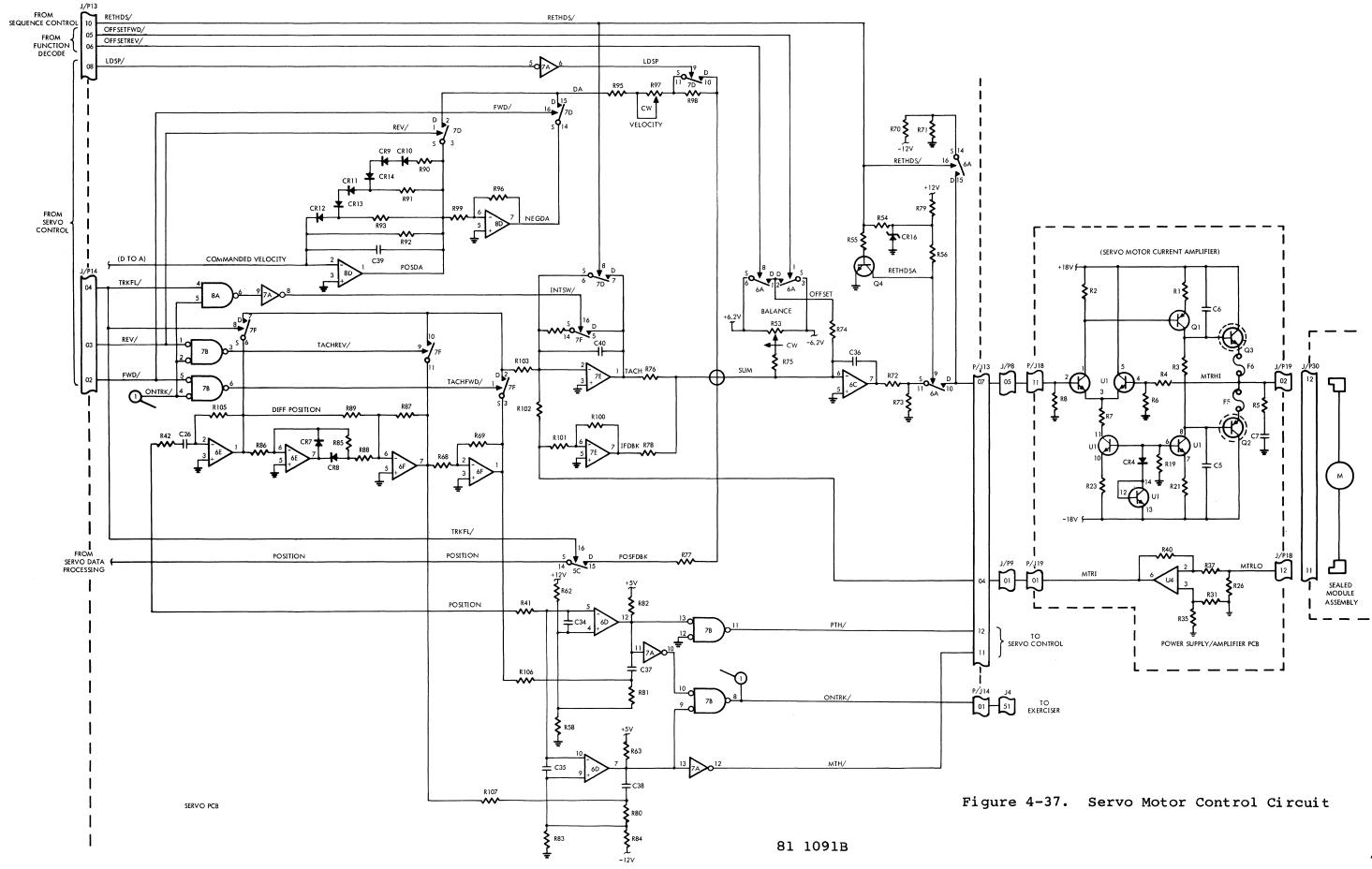

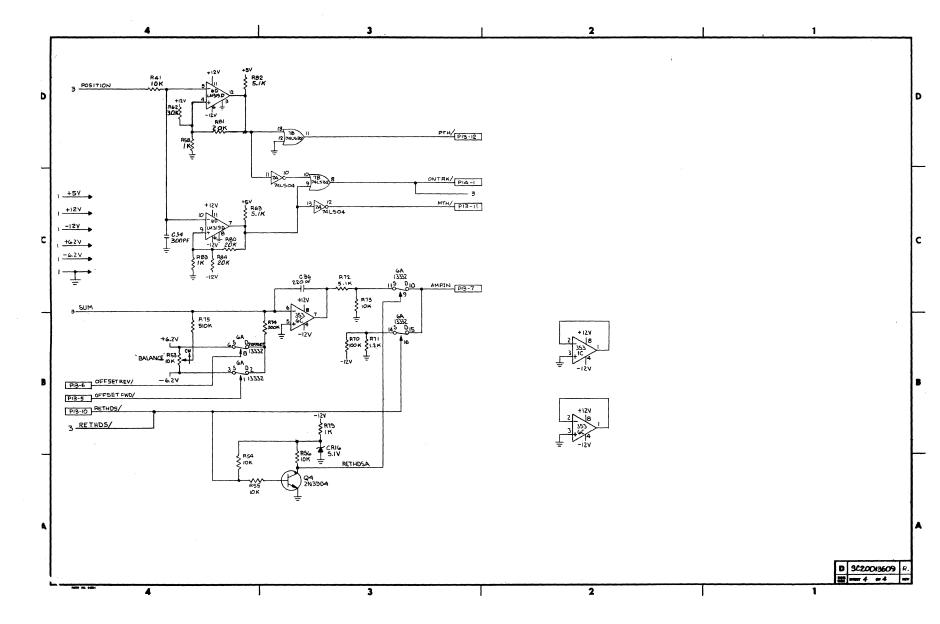

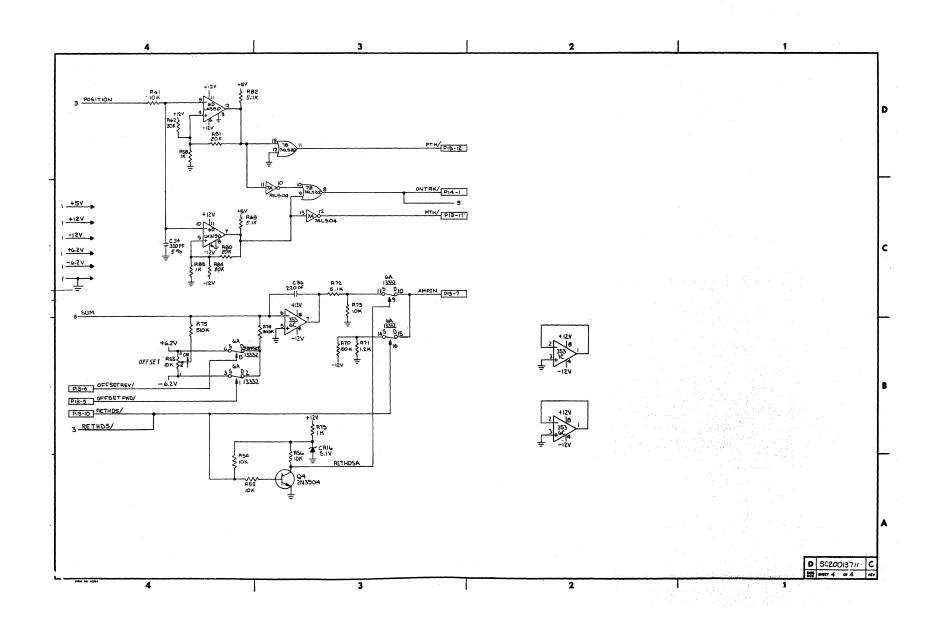

| Servo Motor Control                                 | 4-66 |

| Retract Heads                                       | 4-67 |

| Velocity Mode                                       | 4-68 |

| Track Following Mode                                | 4-72 |

| Servo Motor Current Amplifier                       | 4-73 |

| Positioning System Summary                          | 4-73 |

| Sector Generation                                   | 4-76 |

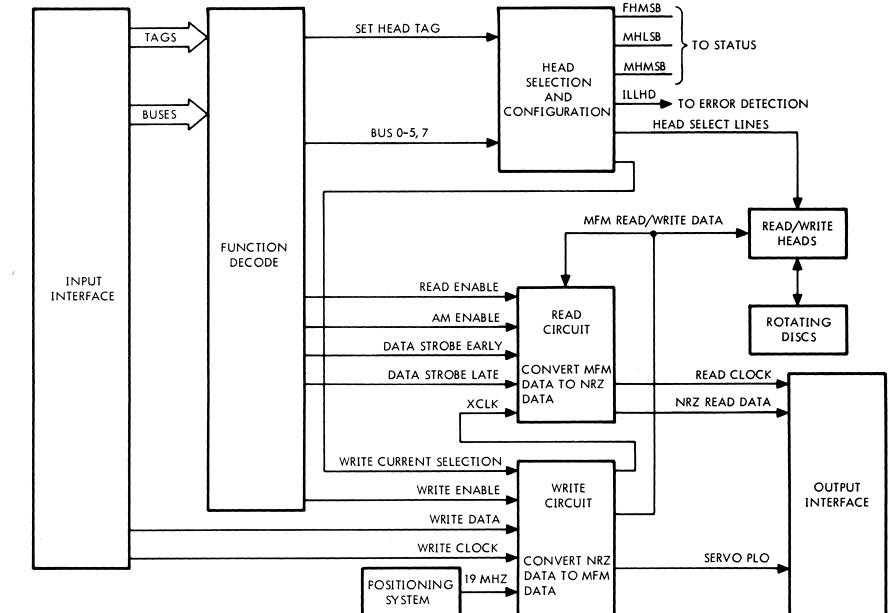

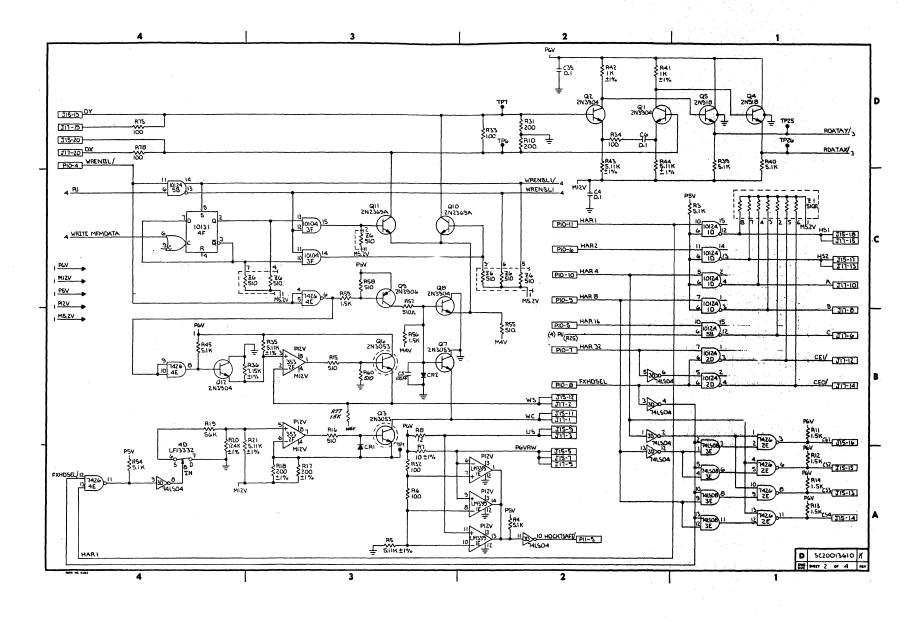

| Read/Write System                                   | 4-78 |

| Recording Format                                    | 4-78 |

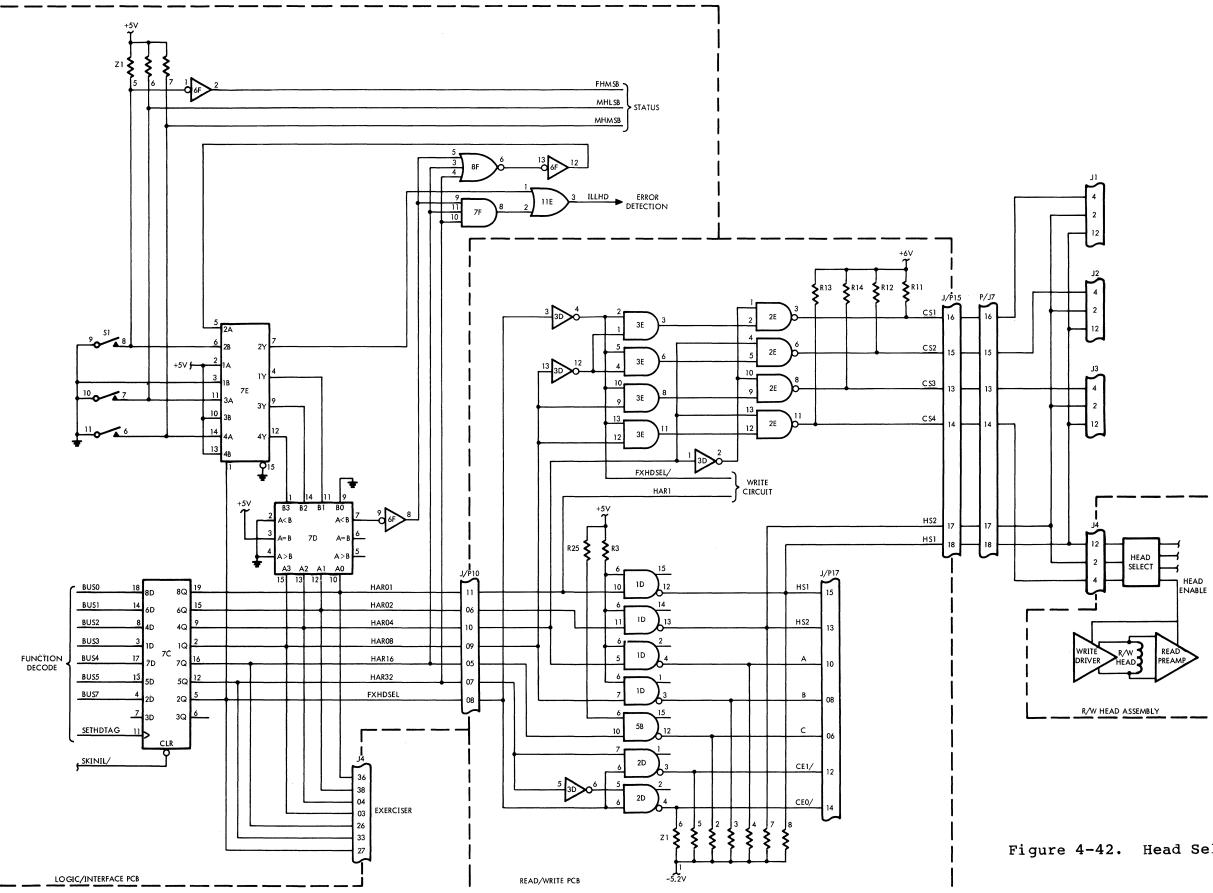

| Head Selection                                      | 4-80 |

| Illegal Head                                        | 4-80 |

| Head Decode                                         | 4-81 |

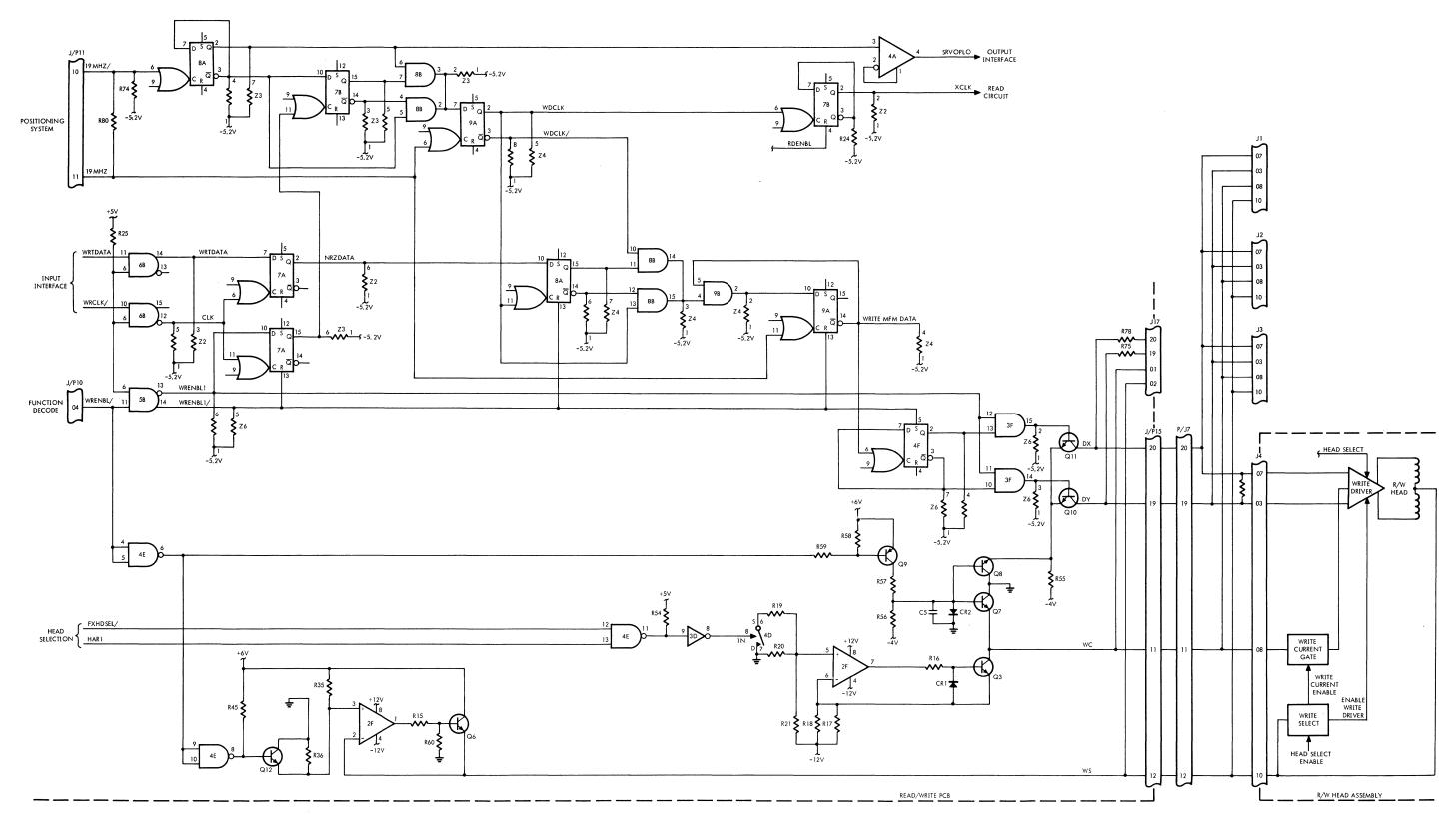

| Write Circuit                                       | 4-82 |

| Enabling R/W Head Write Driver                      | 4-87 |

| Section | <u>-</u>                                   | Page  |

|---------|--------------------------------------------|-------|

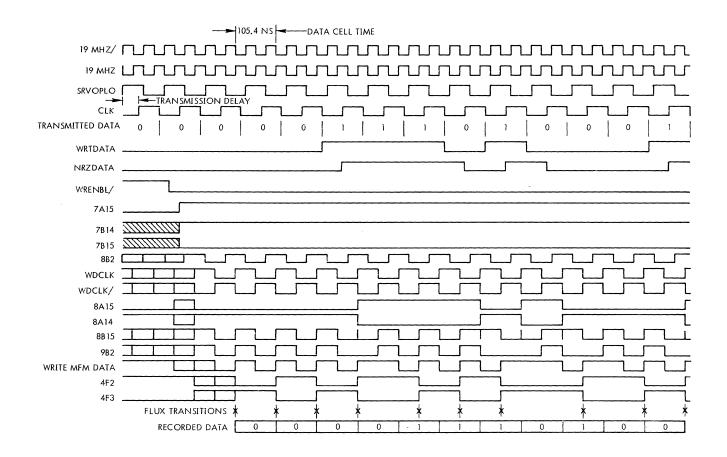

|         | Writing Data                               | 4-89  |

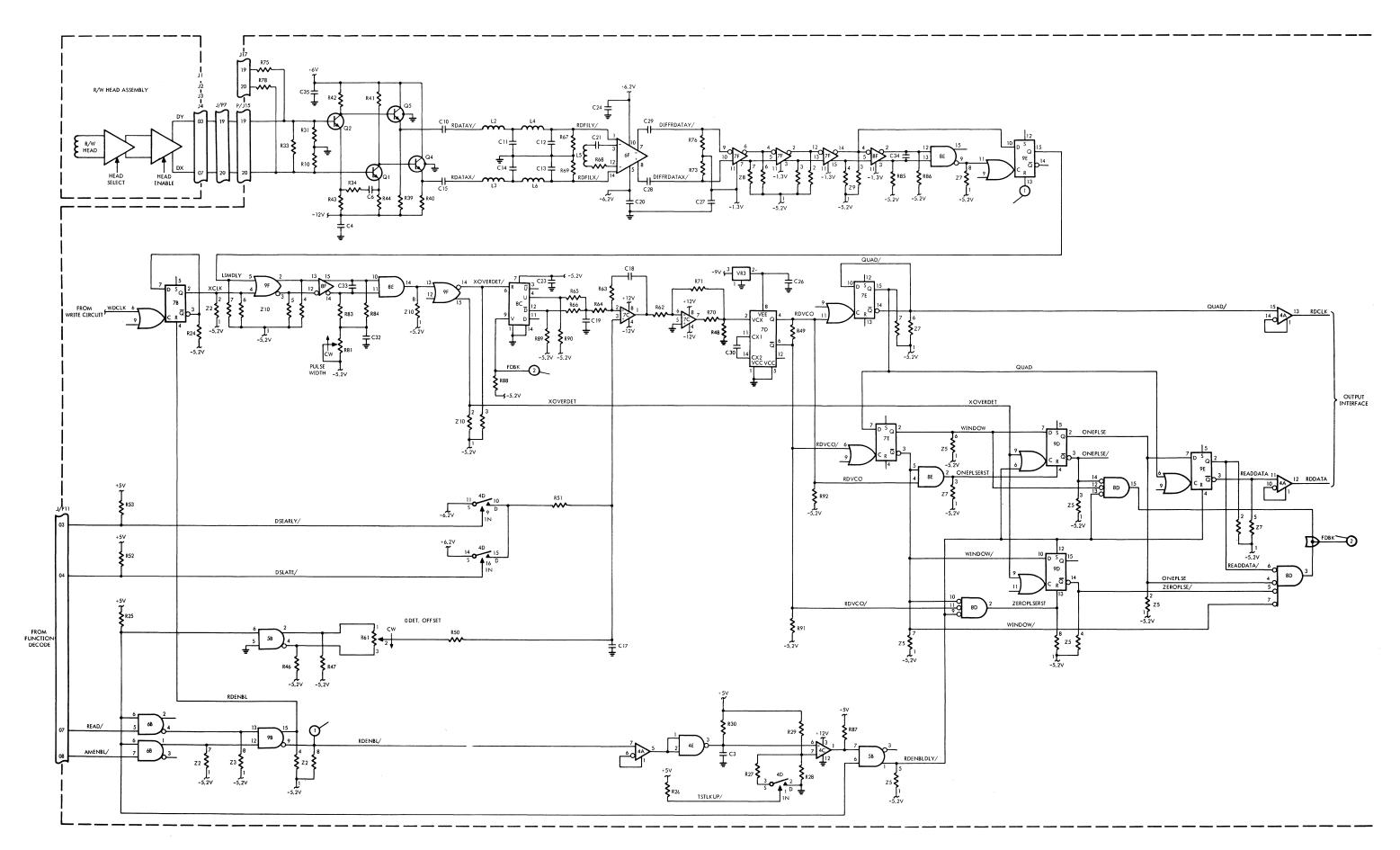

|         | Read Circuit                               | 4-90  |

|         | Read/Write Head Assembly                   | 4-98  |

|         | Error Detection                            | 4-98  |

|         | Fault                                      | 4-98  |

|         | DC Voltage Unsafe                          | 4-99  |

|         | R/W Head Circuit Unsafe                    | 4-99  |

|         | Illegal Head Selected                      | 4-99  |

|         | Invalid Write Operations                   | 4-100 |

|         | Reset Fault                                | 4-100 |

|         | Seek Error                                 | 4-100 |

|         | Attempted Seek While Not Ready             | 4-101 |

|         | Illegal Cylinder Address                   | 4-101 |

|         | Seek Time-Out (1.5 Second Time Out)        | 4-101 |

|         | Open Cable Active While Drive Is On-Line . | 4-102 |

|         | Resetting Seek Error                       | 4-102 |

|         | Retract Control (Emergency Retract)        | 4-102 |

|         | Seek Time-Out Seek Error                   | 4-102 |

|         | Open Cable                                 | 4-102 |

| 5       | Status                                     | 4-105 |

| C       | Dutput Interface                           | 4-105 |

| 5 M#    | AINTENANCE                                 |       |

| Ir      | ntroduction                                | 5-1   |

| Pı      | reventive Maintenance                      | 5-1   |

| Section                             | Page |

|-------------------------------------|------|

| Corrective Maintenance              | 5-1  |

| Troubleshooting                     | 5-1  |

| Fault Isolation                     | 5-2  |

| Maintenance Checks                  | 5-2  |

| Power Supply Check                  | 5-2  |

| DC Voltage Distribution             | 5-5  |

| Sequence Up                         | 5-8  |

| Ground Brush Assembly               | 5-11 |

| Servo Balance (Offset) Verification | 5-12 |

| Velocity Verification               | 5-12 |

| Damper Verification                 | 5-12 |

| Pulse Gate Verification             | 5-12 |

| Separated Pulse Verification        | 5-12 |

| Phase Detector Offset Verification  | 5-13 |

| Read/Write Pulse Width Verification | 5-13 |

| Brake Verification                  | 5-13 |

| Adjustments                         | 5-14 |

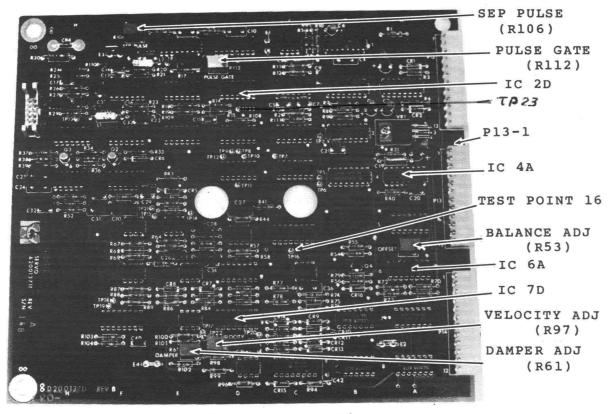

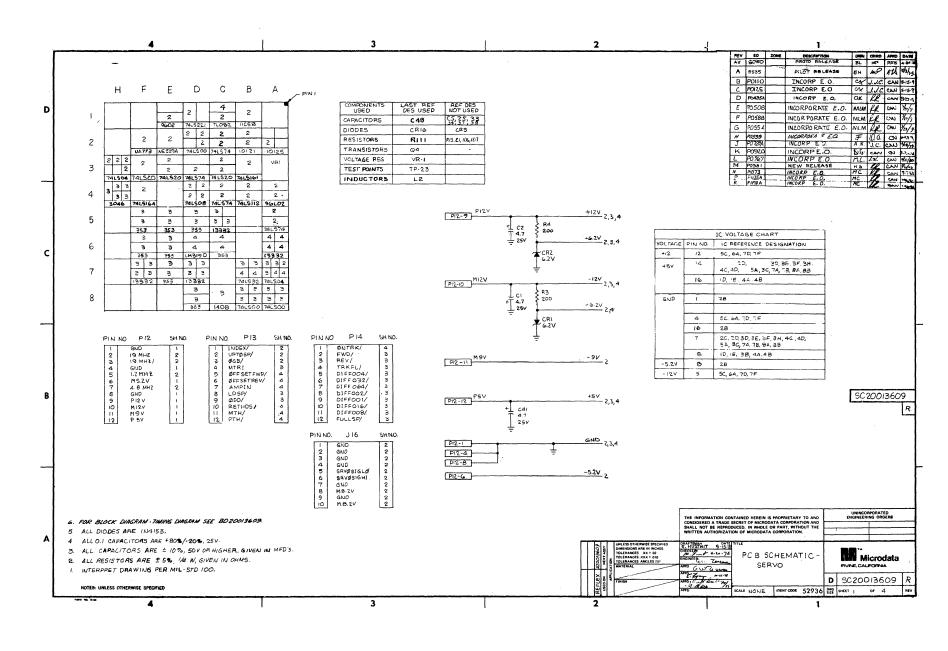

| Servo PCB Adjustments               | 5-14 |

| Speed Adjustment                    | 5-15 |

| Separated Pulse Adjustment          | 5-16 |

| Pulse Gate Adjustment               | 5-16 |

| Balance (offset) Adjustments        | 5-16 |

| Velocity Adjustment                 | 5-17 |

| Damper Adjustment                   | 5-18 |

| Section                                        | Page |

|------------------------------------------------|------|

| Read Write Adjustment                          | 5-18 |

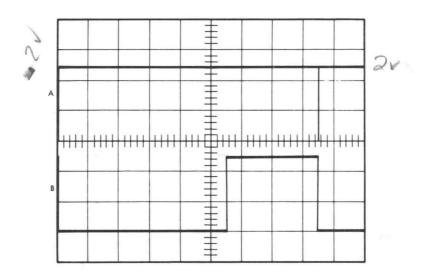

| Phase Detector Offset Adjustment               | 5-18 |

| Pulse Width (Detector Window) Adjustment       | 5-21 |

| Brake Adjustment                               | 5-21 |

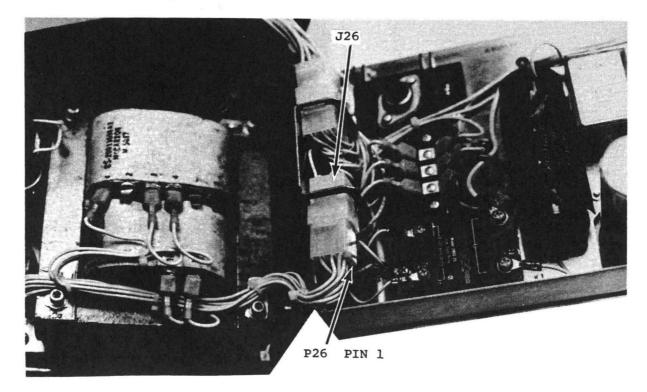

| Removal and Replacement                        | 5-22 |

| Printed Circuit Boards                         | 5-23 |

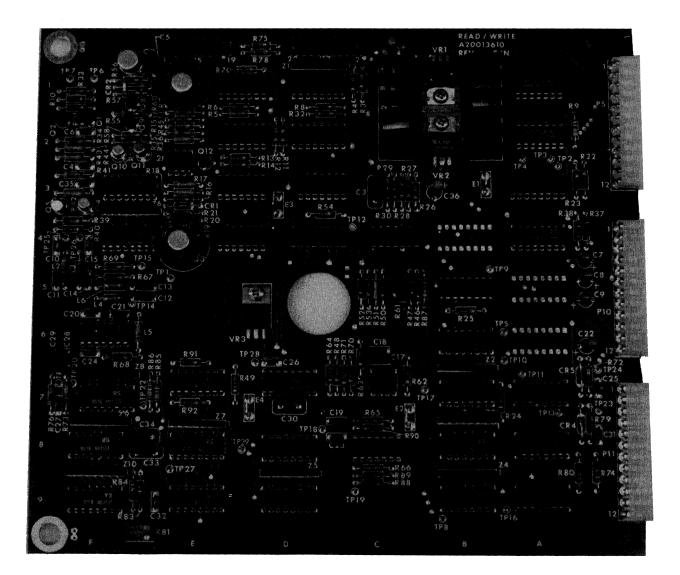

| Read/Write Boards                              | 5-23 |

| Servo PCB                                      | 5-23 |

| Logic/Interface PCB                            | 5-24 |

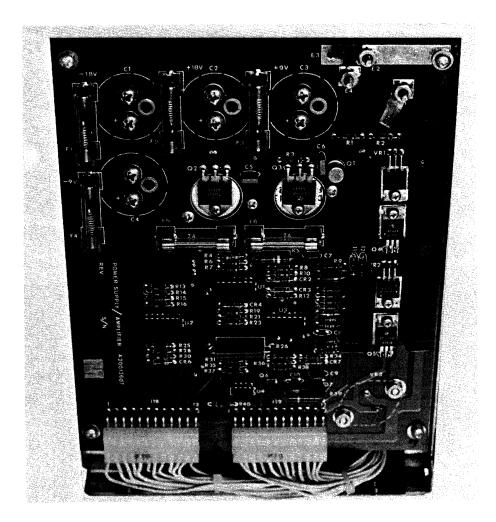

| Power Supply/Amplifier PCB                     | 5-24 |

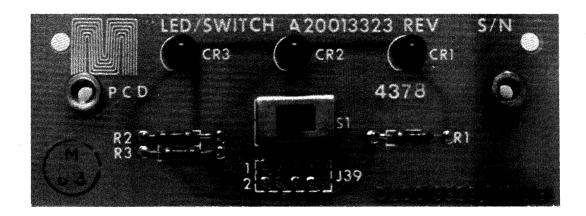

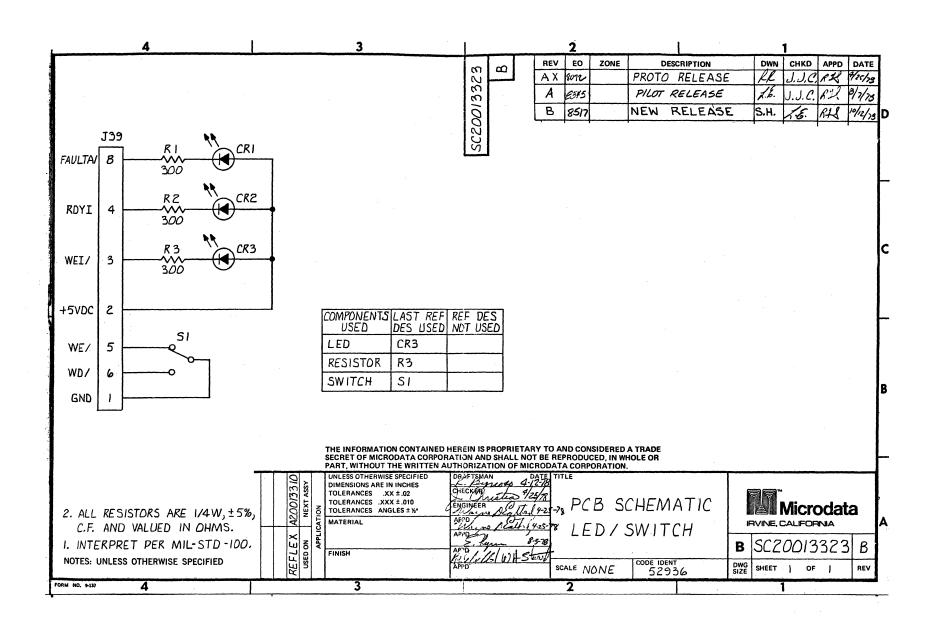

| LED/Switch PCB (Operator Indicator Panel)      | 5-25 |

| Electromechanical Assemblies                   |      |

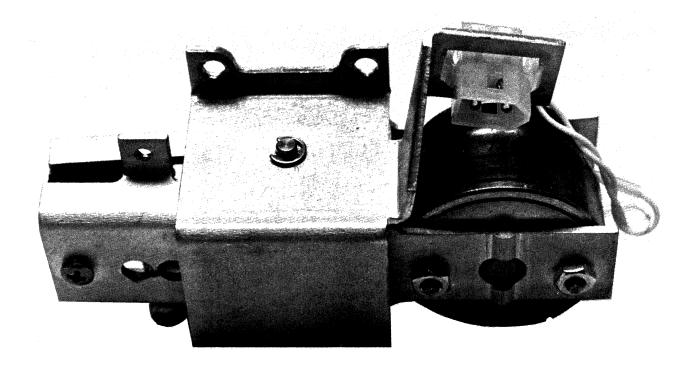

| Sealed Module and Motor Assembly               | 5-26 |

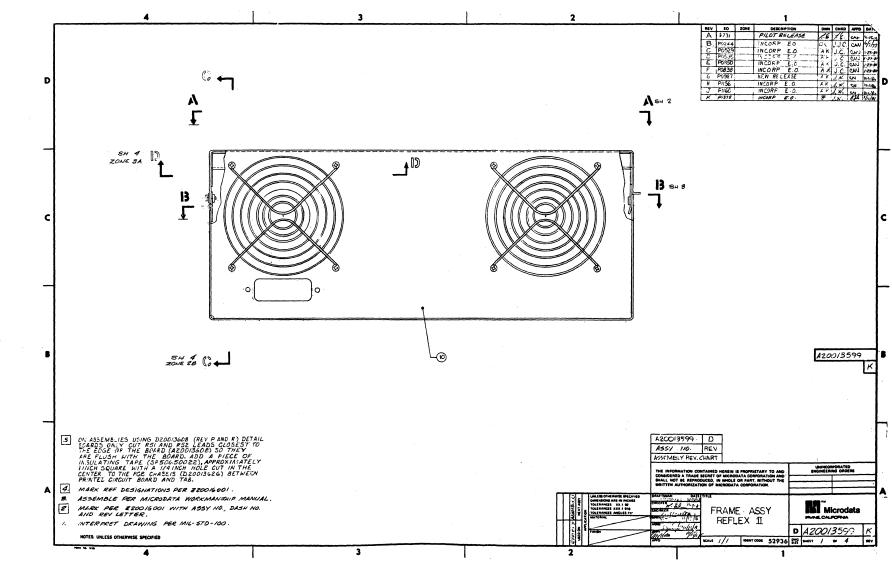

| Cooling Fan(s)                                 | 5-28 |

| Transformer Assembly (DC Voltage Supply)       | 5-28 |

| AC Motor Pulley                                | 5-30 |

| AC Spindle Motor                               | 5-31 |

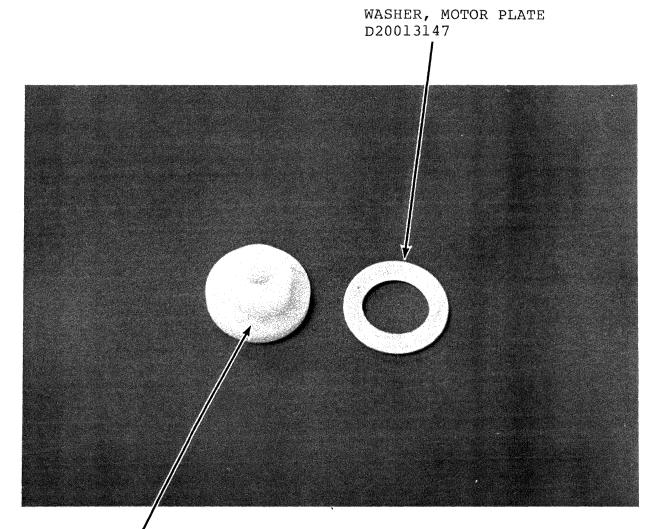

| AC Motor Plate                                 | 5-31 |

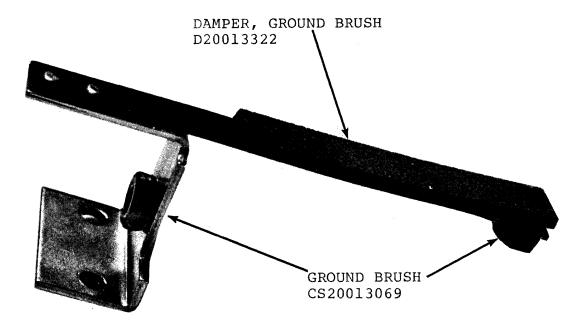

| Ground Brush Assembly                          | 5-32 |

| Brake Assembly                                 | 5-32 |

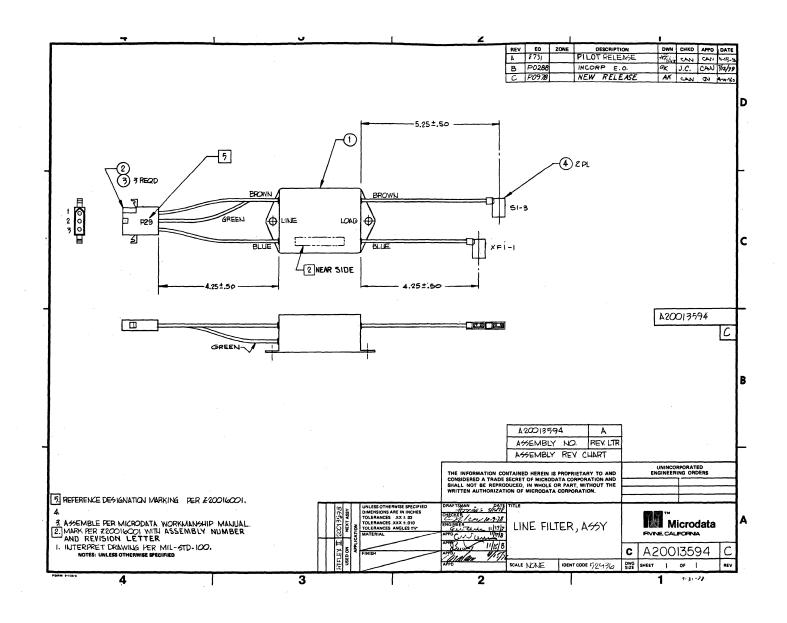

| Line Filter Assembly                           | 5-33 |

| Test Equipment and Tools                       | 5-34 |

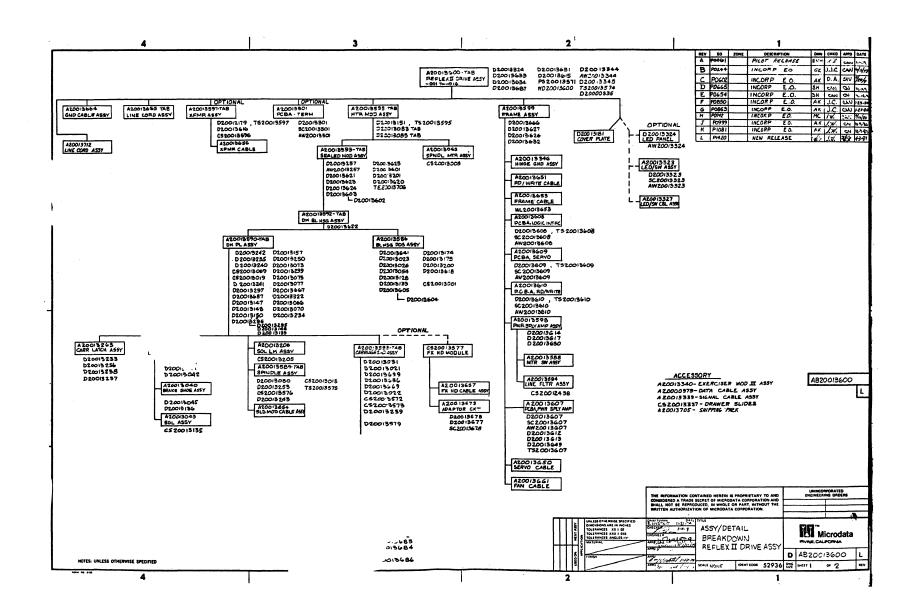

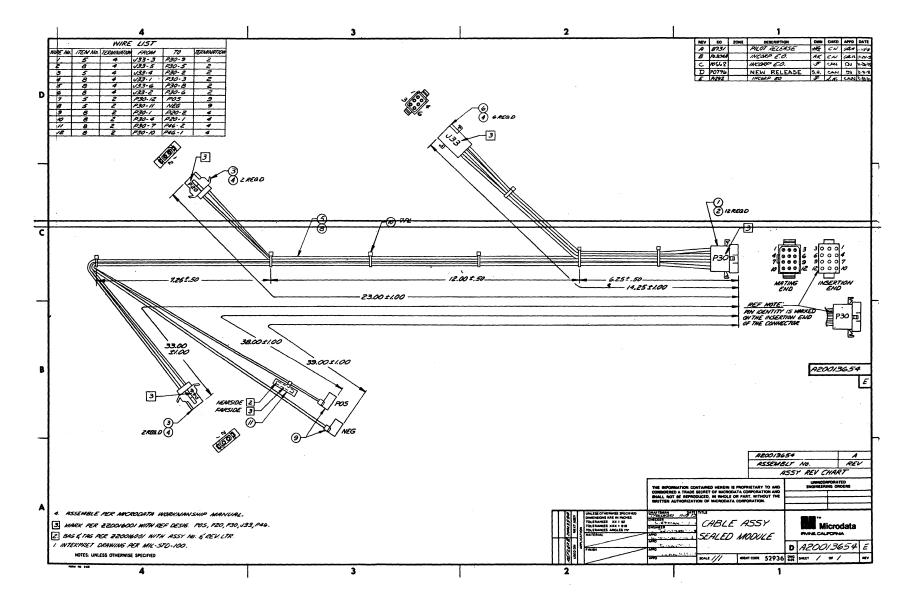

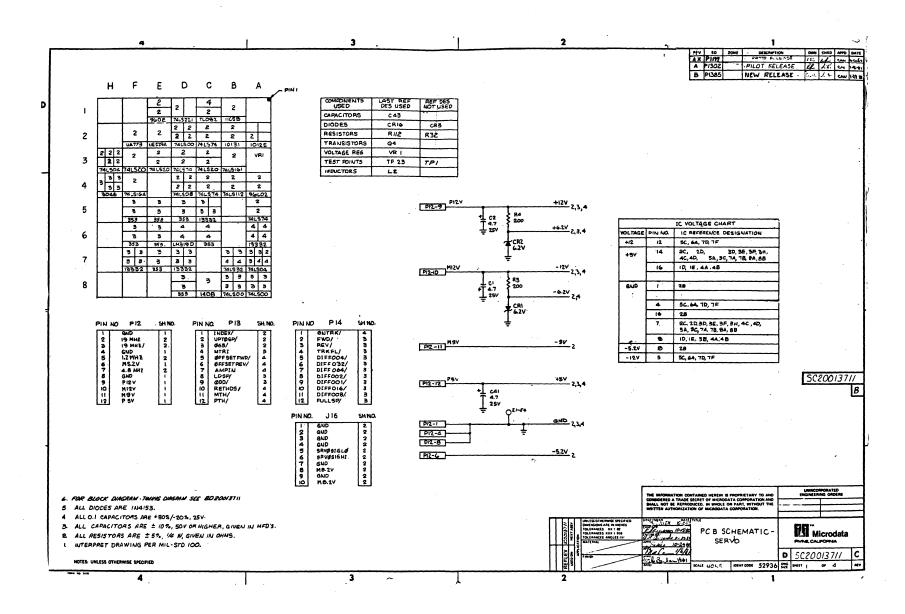

| 6 PARTS LIST, ASSEMBLY DRAWINGS AND SCHEMATICS |      |

| Introduction                                   | 6-1  |

| Section     |                    | Page |

|-------------|--------------------|------|

| Parts List  |                    | 6-1  |

| Appendix A: | Number Conversions | A-1  |

| Appendix B: | Glossary           | B-1  |

#### ILLUSTRATIONS

•

| Figure |                                                                  | Page   |

|--------|------------------------------------------------------------------|--------|

| 1-1    | Reflex <sup>®</sup> II Disc Drive                                | .1-1   |

| 1-2    | Reflex II Without Covers                                         | .1-2   |

| 1-3    | Reflex II Modular Component Accessibility                        | .1-2   |

| 1-4    | Reflex II General Block Diagram                                  | .1-5   |

| 1-5    | Positioner Mechanism • • • • • • • • • • • • • • • • • • •       | .1-7   |

| 1-6    | Reflex II Cylinder Concept                                       | .1-9   |

| 1-7    | Nameplate                                                        | .1-14  |

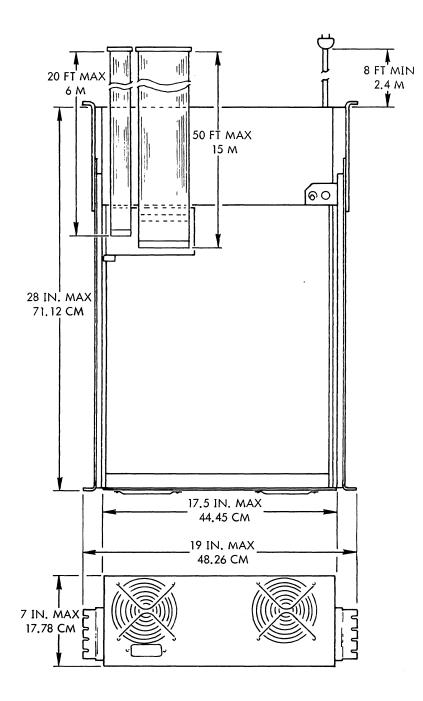

| 2-1    | Physical Dimension Considerations                                | .2-3   |

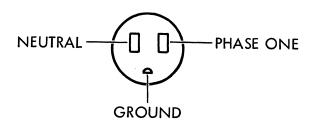

| 2-2    | Standard AC Power Outlet Configuration                           | . 2-4  |

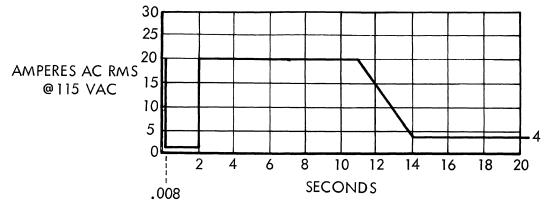

| 2-3    | Typical Current Characteristics With Internal<br>Power Supply    | .2-5   |

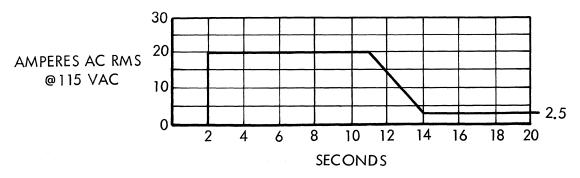

| 2-4    | Typical Current Characteristics Without Internal<br>Power Supply | . 2-5  |

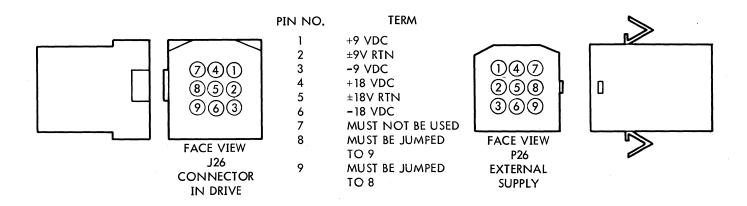

| 2-5    | DC Voltage Supply Cable Pin Assignments                          | .2-6   |

| 2-6    | Cable Connections and Ground Tie Points                          | .2-7   |

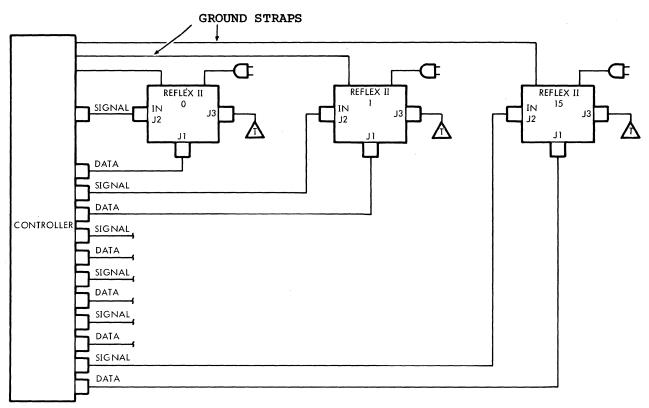

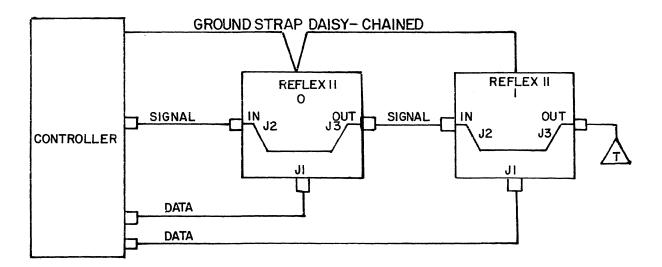

| 2-7    | Daisy Chain and Star Configuration (OEM USE)                     | • 2-9  |

| 2-7A   | Daisy Chain Configuration (REALITY USE) • • • •                  | • 2-10 |

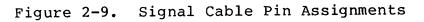

| 2-8    | Connector Pin Orientation                                        | .2-11  |

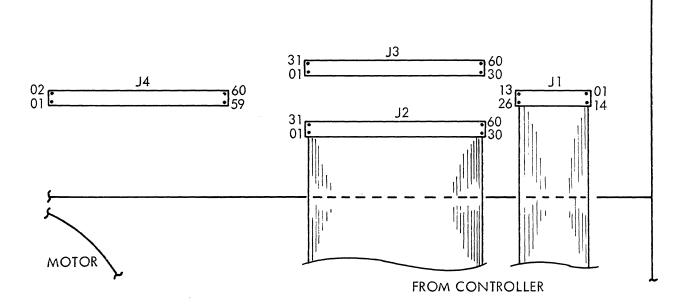

| 2-9    | Signal Cable Pin Assignments                                     | .2-12  |

| 2-10   | Drive Selection                                                  | .2-13  |

| 2-11   | Set Cylinder Timing                                              | .2-14  |

| 2-12   | Set Head Timing • • • • • • • • • • • • • • • • • • •            | .2-15  |

| 2-13   | Set Cylinder and Set Head Timing Relationship .                  | .2-16  |

| 2-14   | Write Command Timing                                             | .2-17  |

| 2-15   | Read Command Timing                                              | .2-17  |

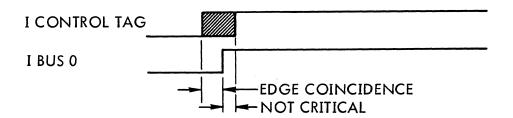

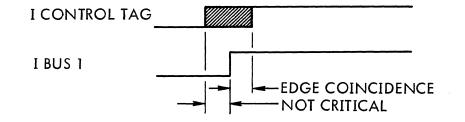

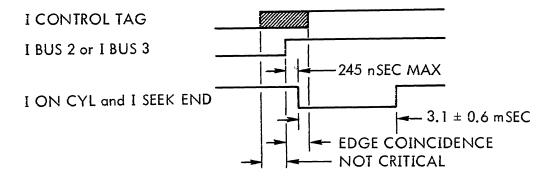

| 2-16   | Offset Command Timing                                            | .2-18  |

| Figure | Page                                                    |

|--------|---------------------------------------------------------|

| 2-17   | Reset Fault Command Timing                              |

| 2-18   | Restore Command Timing                                  |

| 2-19   | Data Cable Pin Assignments                              |

| 2-20   | Read/Write Signal Relationships                         |

| 2-21   | Typical Signal Cable Transmission Line 2-25             |

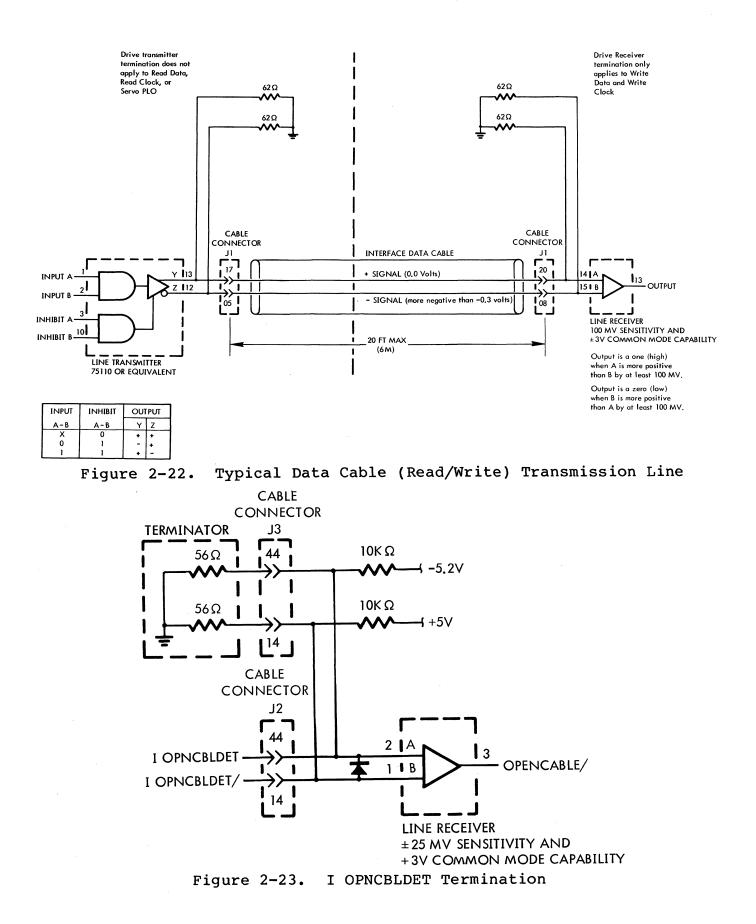

| 2-22   | Typical Data (Read/Write) Transmission Line 2-26        |

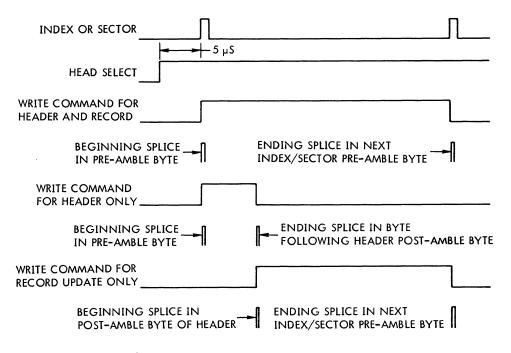

| 2-23   | I OPNCBLDET Termination                                 |

| 2-24   | Splice Location                                         |

| 2-25   | Format Summary                                          |

| 2-26   | Fixed Head Selection                                    |

| 3-1    | Cover Removal                                           |

| 3-2    | DC Voltage Connector                                    |

| 3-3    | DC Voltage Connection                                   |

| 3-4    | Ground Connection                                       |

| 3-5    | AC Power Cable Convention                               |

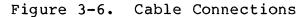

| 3-6    | Cable Connections                                       |

| 3-7    | Operator Indicator Panel                                |

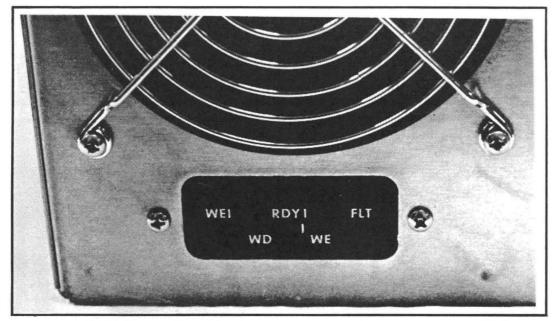

| 3-8    | Power On/Off Switch                                     |

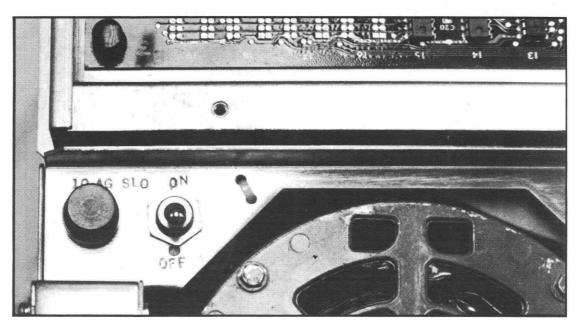

| 3-9    | Logic/Interface Switches                                |

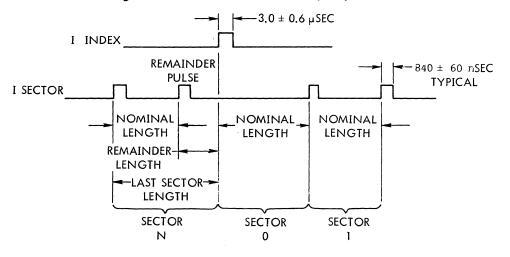

| 3-10   | Sector Length                                           |

| 4-1    | Reflex II System Block Diagram 4-5                      |

| 4-2    | Typical Read/Write Head 4-7                             |

| 4-3    | Standard Power Configuration and AC Distribution .4-9   |

| 4-4    | Optional Power Configuration and AC Distribution . 4-10 |

| Figure | I                                             | Page |

|--------|-----------------------------------------------|------|

| 4-5    | Power Supply Filtering and Voltage Generation | 4-12 |

| 4-6    | +5V Over Voltage Protection                   | 4-12 |

| 4-7    | Under Voltage Monitor                         | 4-13 |

| 4-8    | DC Voltage Distribution                       | 4-15 |

| 4-9    | Input Interface Cable Connection              | 4-16 |

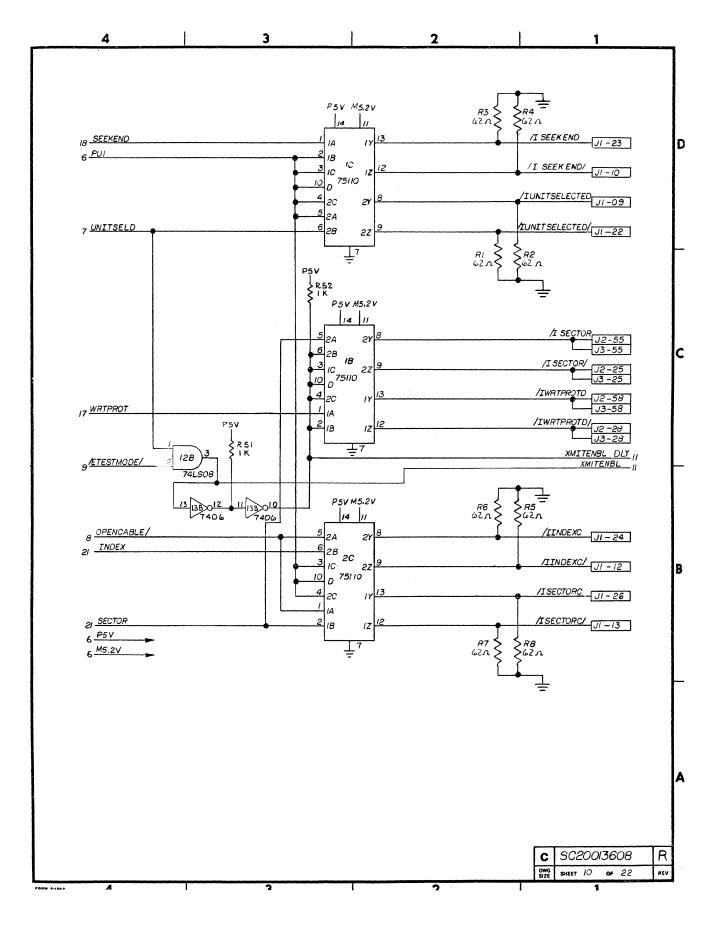

| 4-10   | Input Interface Logic                         | 4-18 |

| 4-11   | Drive Selection Logic                         | 4-21 |

| 4-12   | Sequence Enable                               | 4-23 |

| 4-13   | Sequence Control General Block Diagram        | 4-25 |

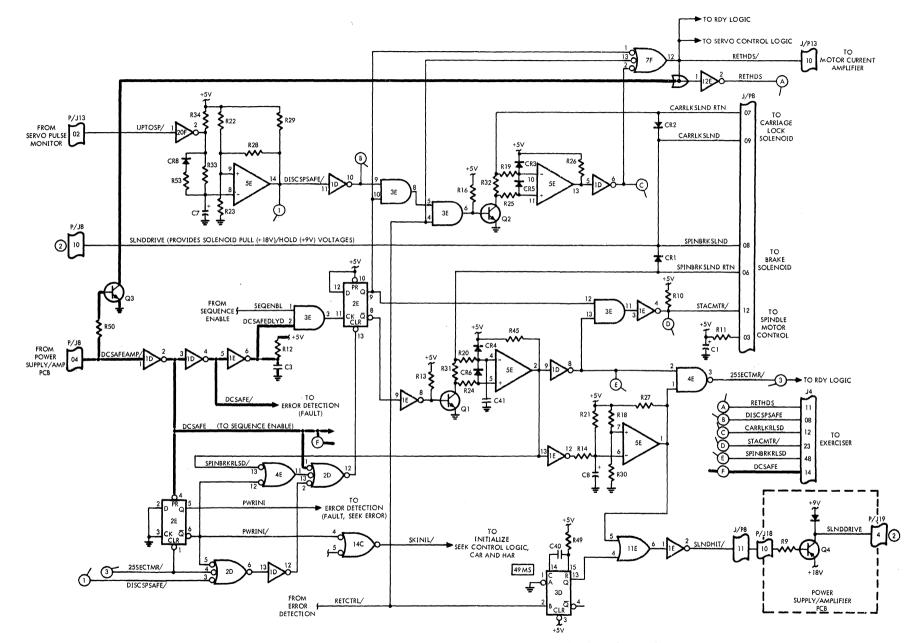

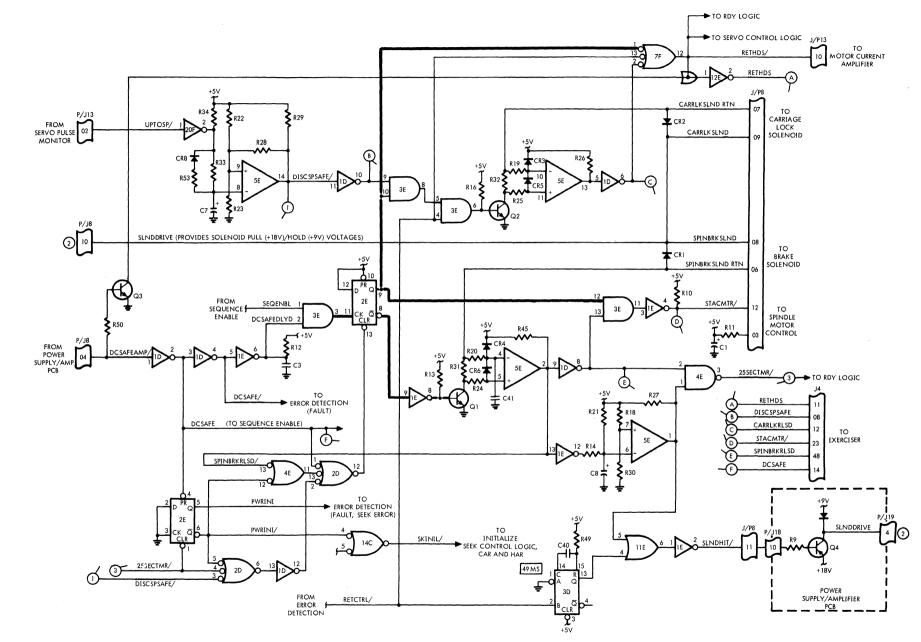

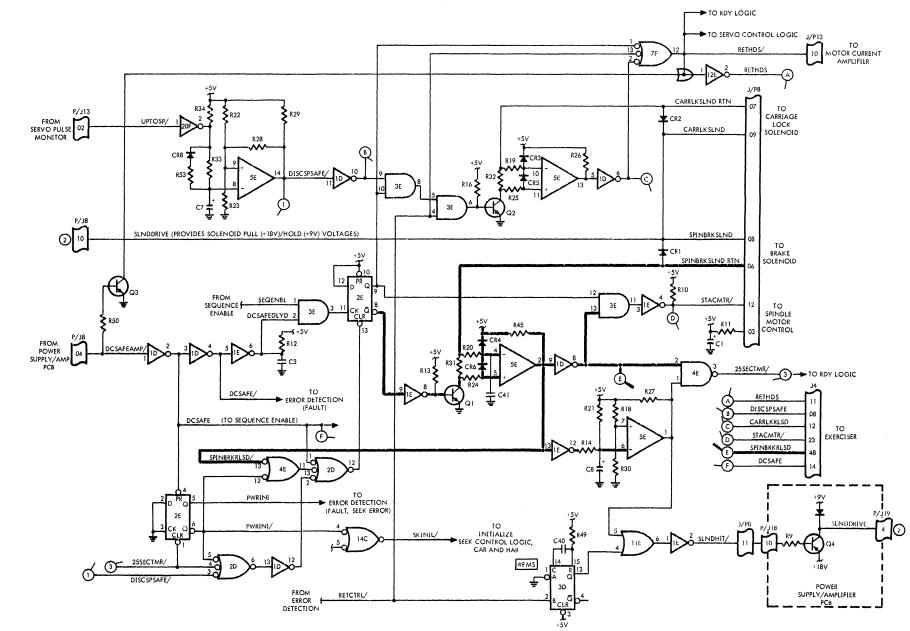

| 4-14   | Sequence Control Initialization               | 4-26 |

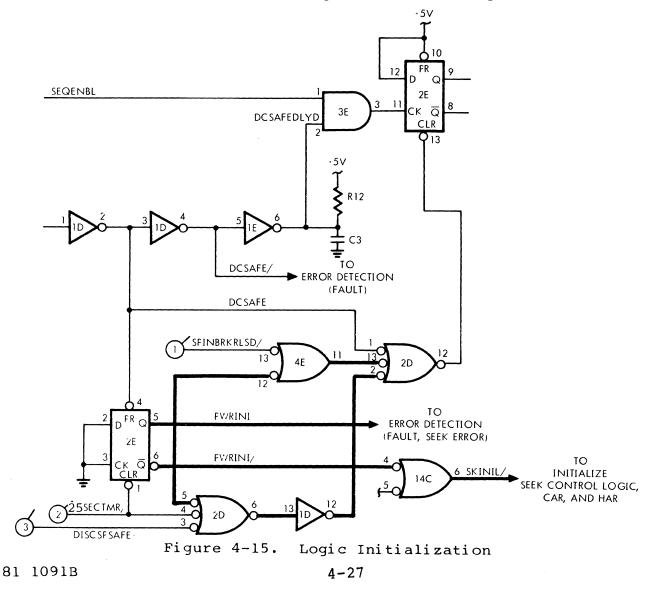

| 4-15   | Logic Initialization                          | 4-27 |

| 4-16   | Spindle Motor Flip-Flop Active                | 4-29 |

| 4-17   | Spindle Brake Released                        | 4-30 |

| 4-18   | Solenoid Drive                                | 4-31 |

| 4-19   | Spindle Motor Control                         | 4-34 |

| 4-20   | Disc Speed Safe/Carriage Unlocked             | 4-35 |

| 4-21   | RETHDS/Control of Servo Motor                 | 4-37 |

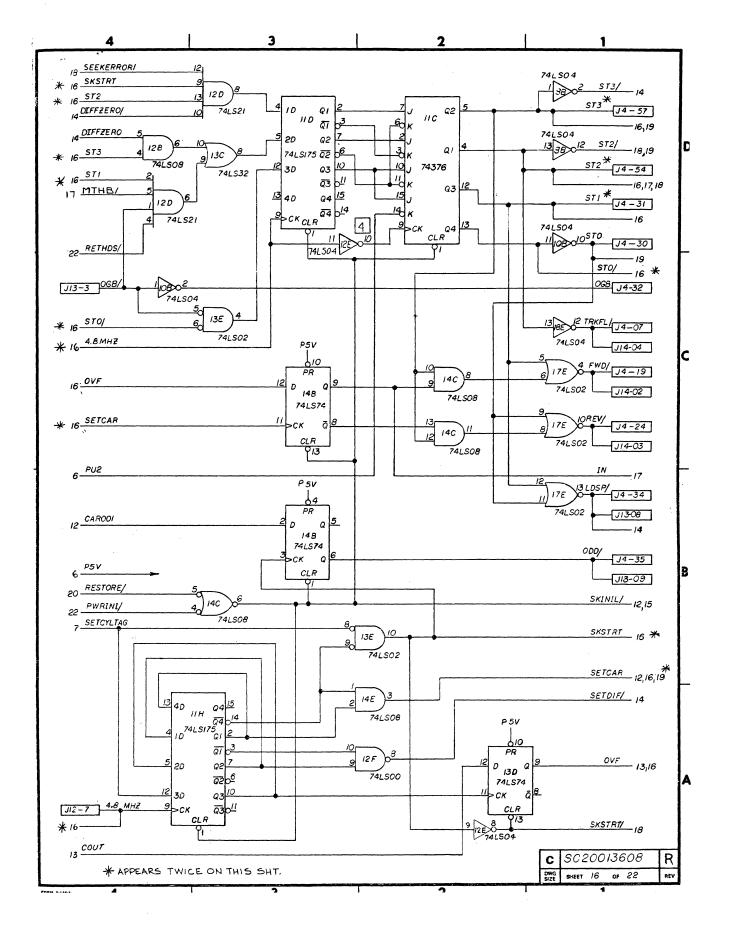

| 4-22   | Servo Control Logic (Sequencing)              | 4-38 |

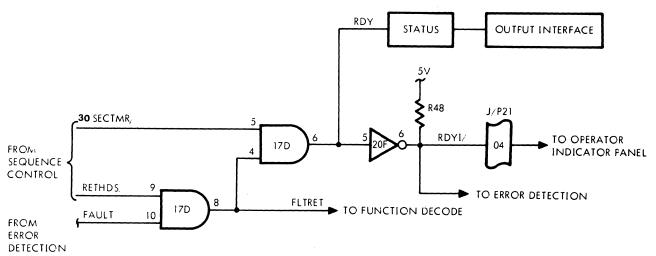

| 4-23   | Ready Logic                                   | 4-39 |

| 4-24   | Function Decode Logic                         | 4-41 |

| 4-25   | Positioning System Block Diagram              | 4-45 |

| 4-26   | Servo Disc Layout                             | 4-48 |

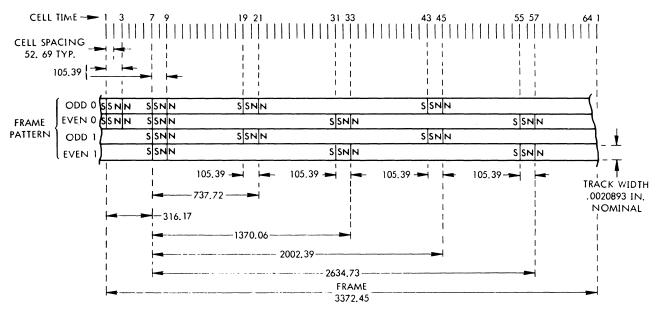

| 4-27   | Servo Track Frame Pattern                     | 4-49 |

| 4-28   | Frame Arrangement                             | 4-50 |

| Figure | Ī                                               | Page  |

|--------|-------------------------------------------------|-------|

| 4-29   | Frame Patterns                                  | 4-51  |

| 4-30   | Servo System Control                            | 1-53  |

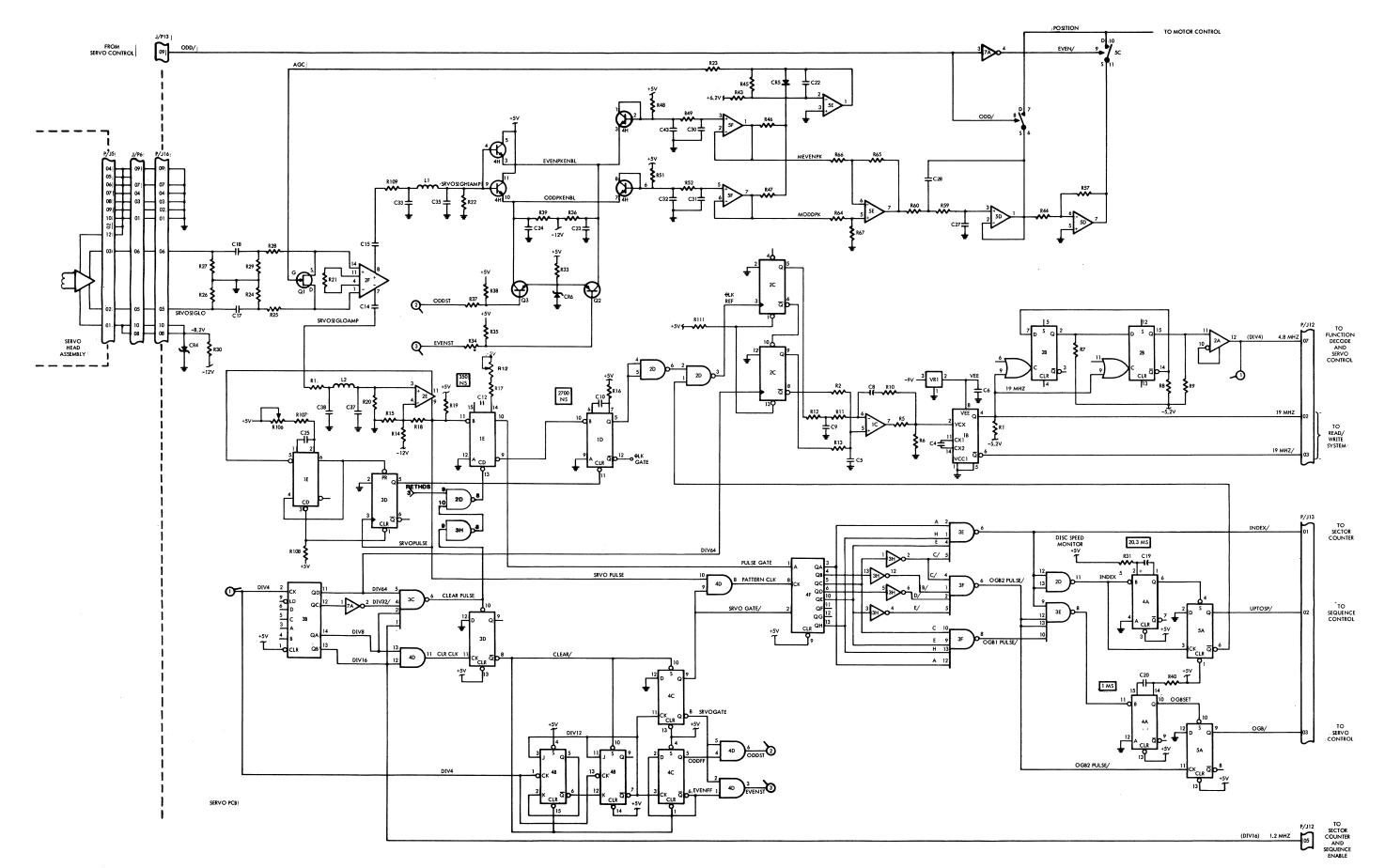

| 4-31   | Servo Data Processing                           | 4-59  |

| 4-32   | Servo Data Timing                               | 4-61  |

| 4-33   | Index Pattern Detection                         | 4-64  |

| 4-34   | Up-To-Speed Detection                           | 4-64  |

| 4-35   | Outer Guard Band Detection                      | 4-65  |

| 4-36   | Position Signal                                 | 4-67  |

| 4-37   | Servo Motor Control Circuit                     | 4-69  |

| 4-38   | Threshold and On Track Generation               | 4-72  |

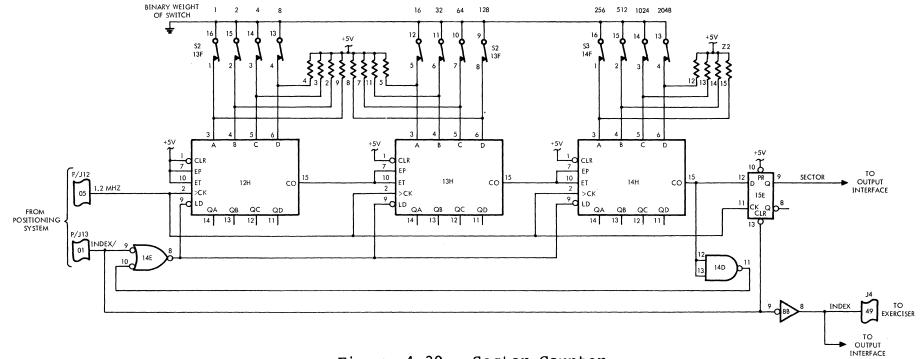

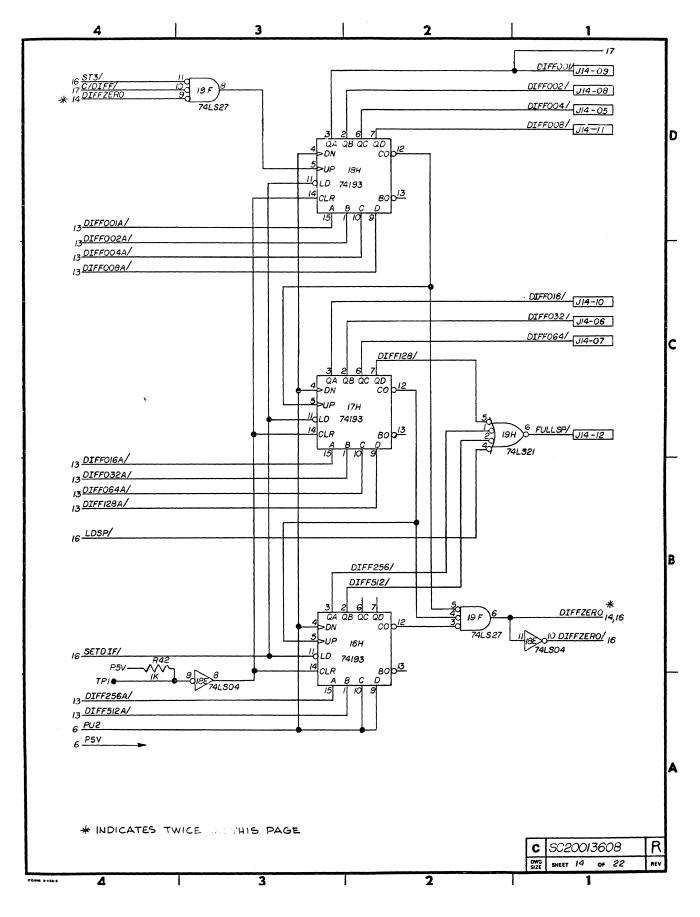

| 4-39   | Sector Counter                                  | 4-77  |

| 4-40   | Simplified Block Diagram, Read/Write System 4   | 4-79  |

| 4-41   | REFLEX II R/W Head Arrangement                  | 4-81  |

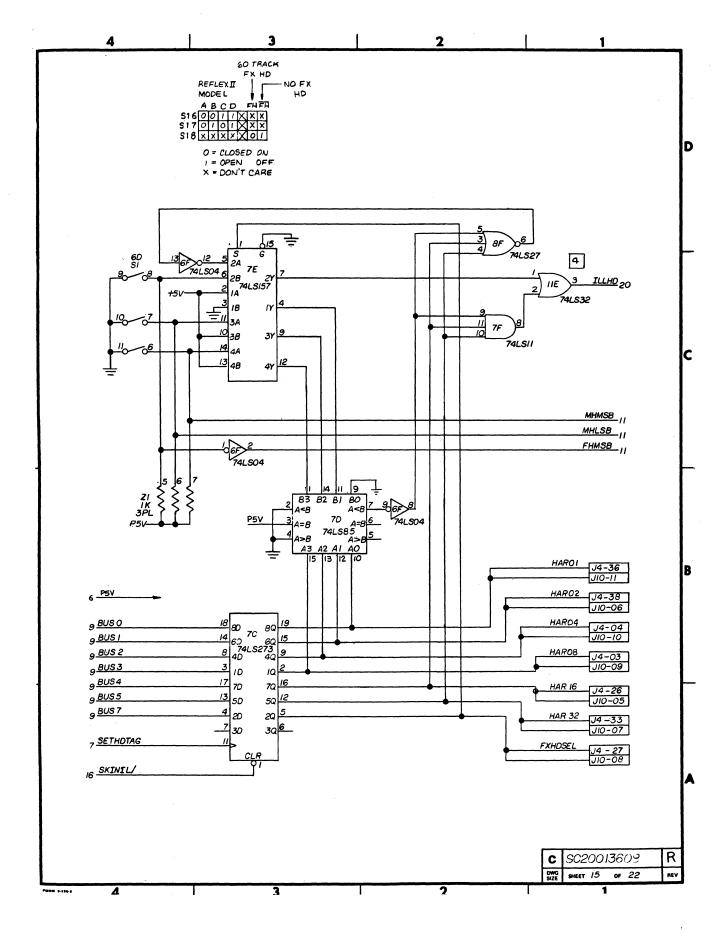

| 4-42   | Head Selection Circuitry                        | 4-83  |

| 4-43   | Write Circuitry                                 | 4-85  |

| 4-44   | Timing Diagram                                  | 4-88  |

| 4-45   | Read Circuit                                    | 4-91  |

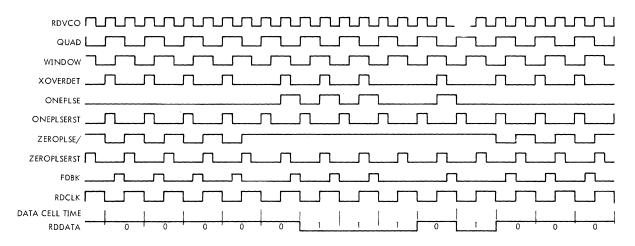

| 4-46   | Data Separator Timing Diagram                   | 4-93  |

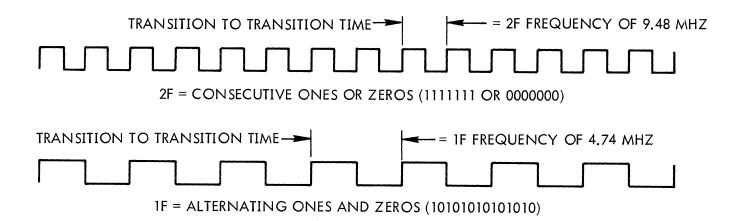

| 4-47   | MFM Low and High Recording Frequencies          | 4-93  |

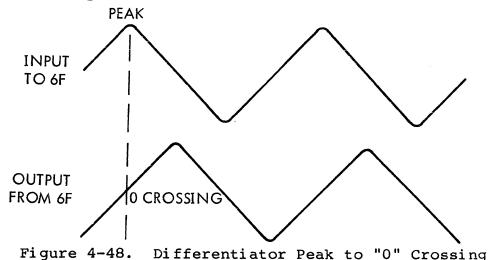

| 4-48   | Differentiator Peak to "0" Crossing             | 4-94  |

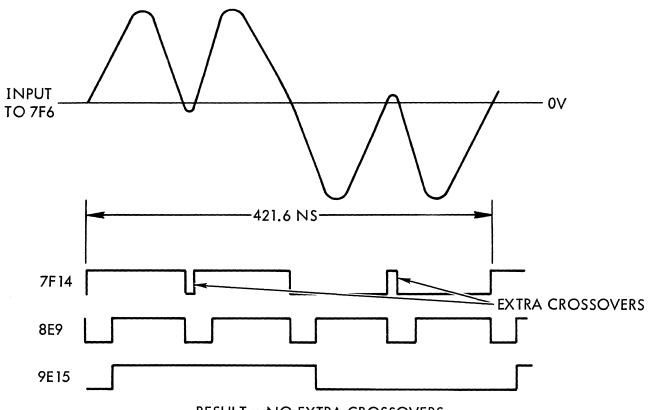

| 4-49   | Eliminate Extra Crossovers From Head Response 4 | 4-95  |

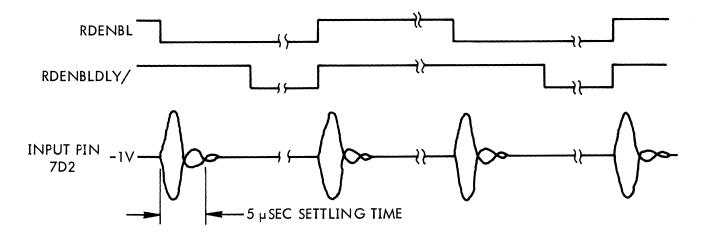

| 4-50   | Read Phase Detection Settling Time              | 4-97  |

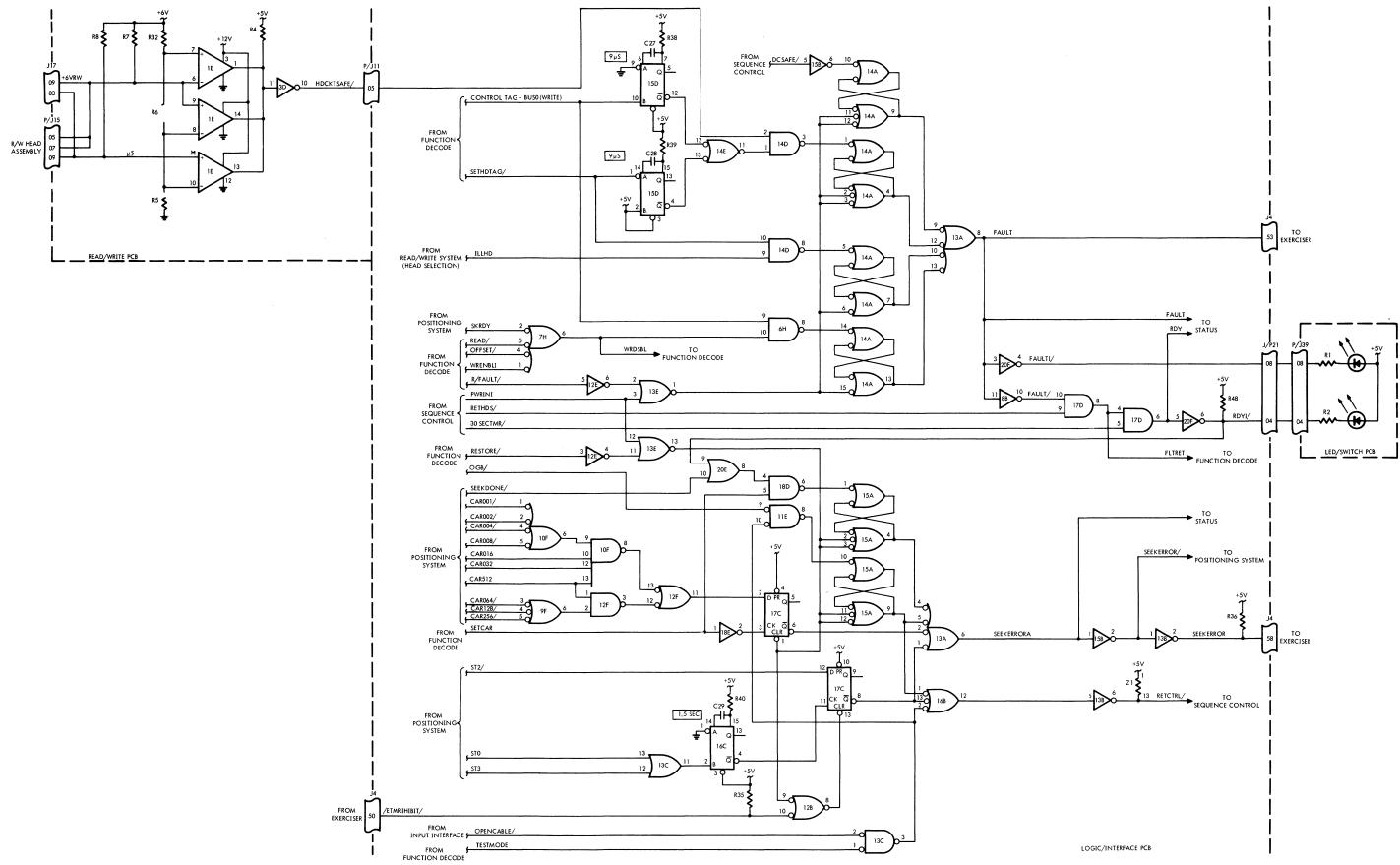

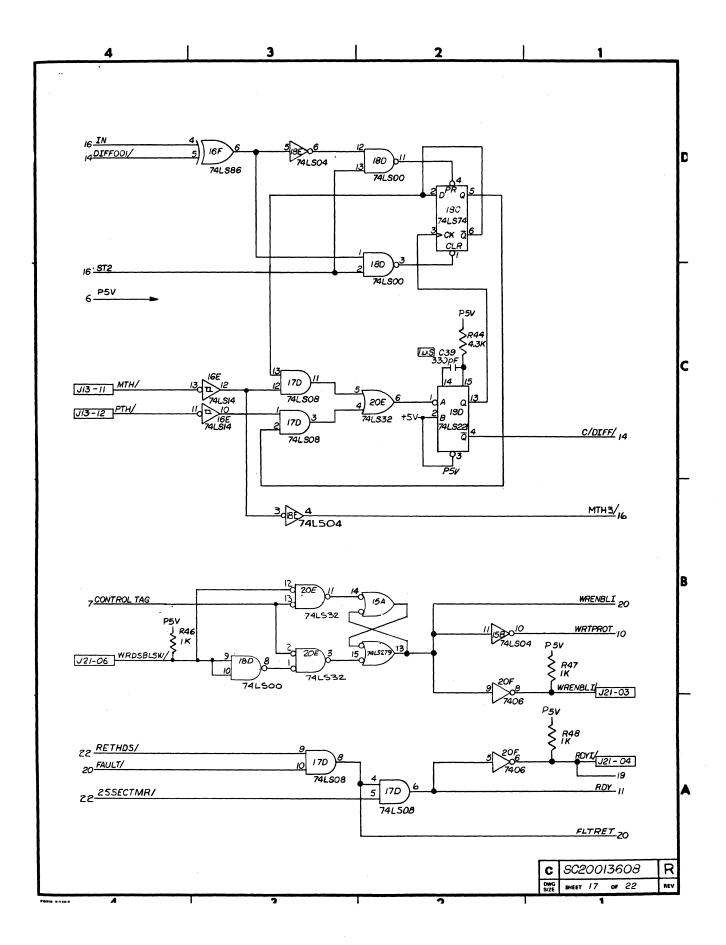

| 4-51   | Fault Logic                                     | 4-103 |

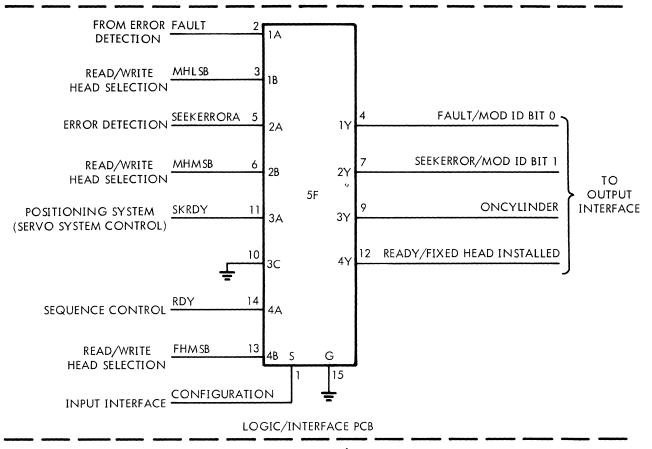

| 4-52   | Primary/Alternate Status                        | 4-105 |

| Figure |                                  | Page  |

|--------|----------------------------------|-------|

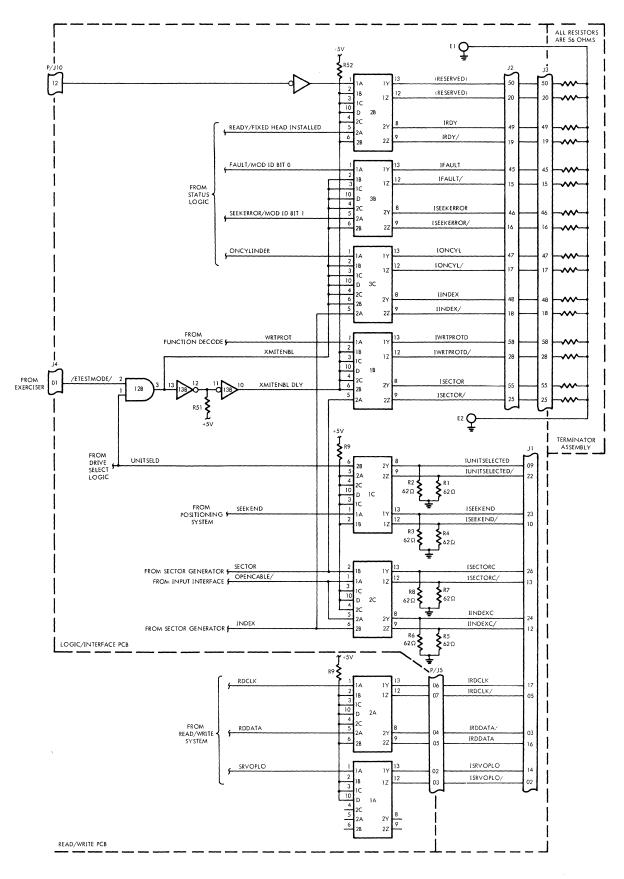

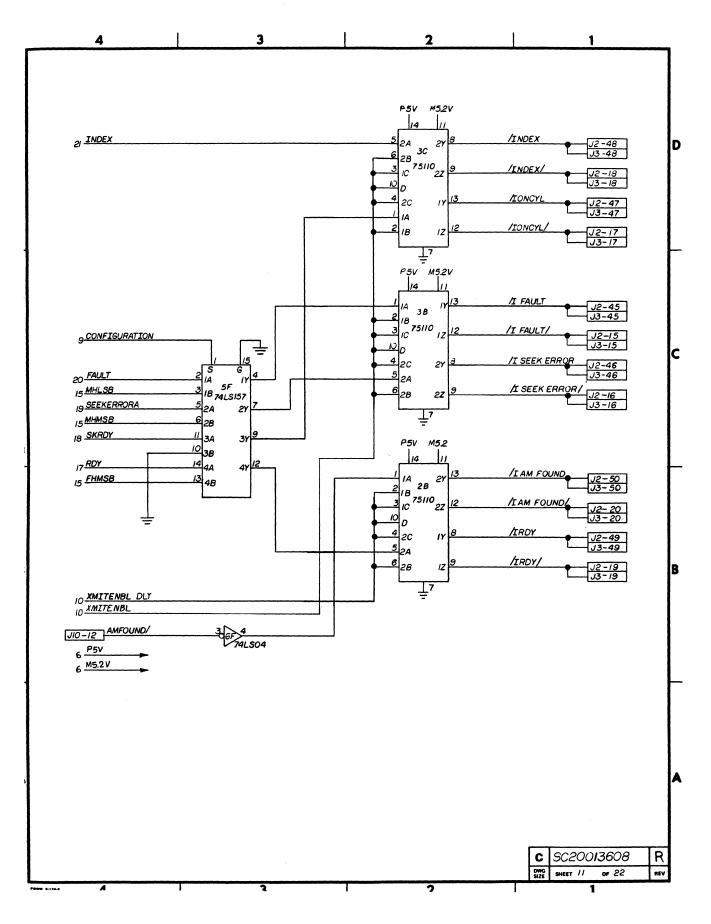

| 4-53   | Output Interface                 | 4-107 |

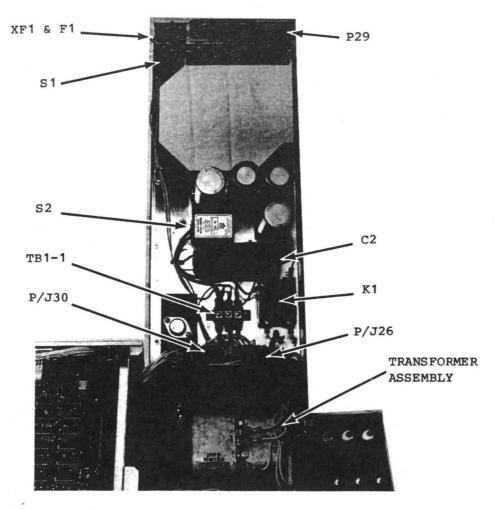

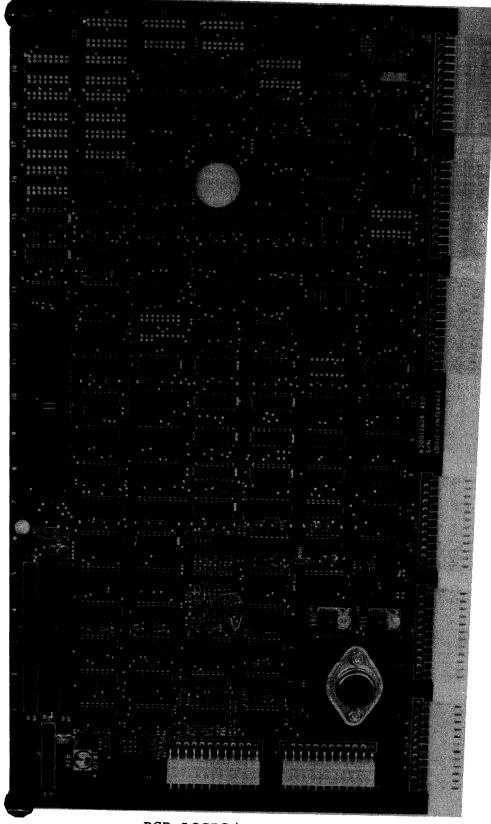

| 5-1    | Power Supply/Amplifier Assembly  | 5-3   |

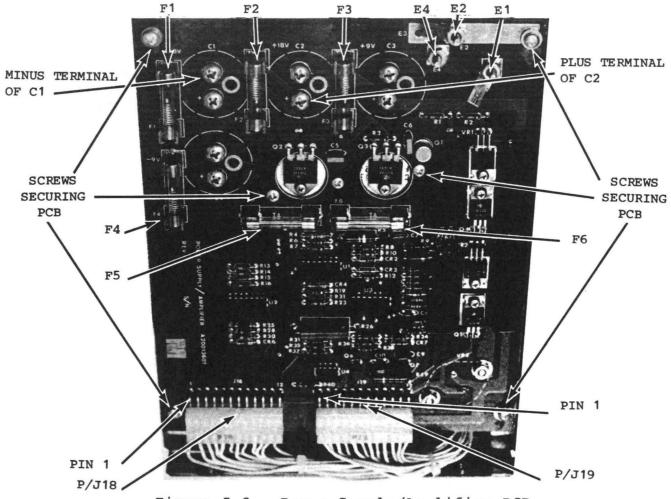

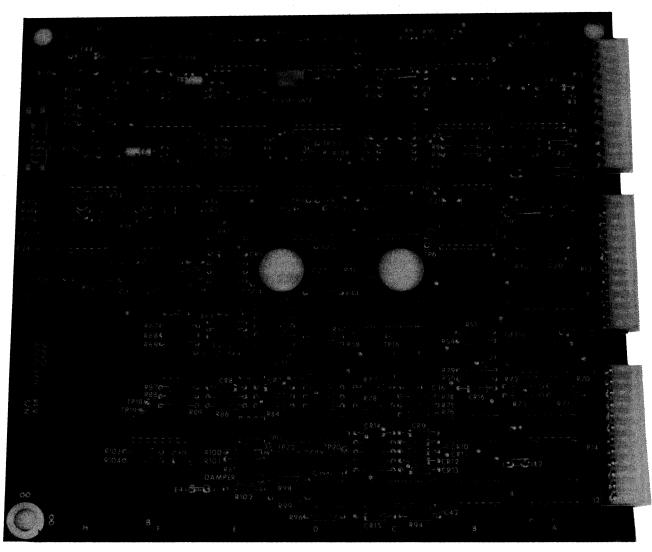

| 5-2    | Power Supply/Amplifier PCB       | 5-5   |

| 5-3    | Servo DC Voltages                | 5-6   |

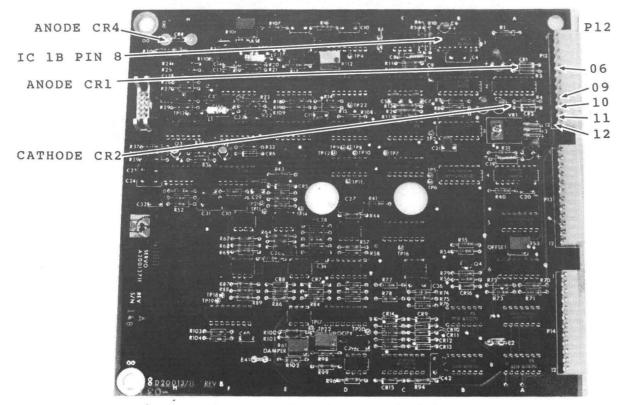

| 5-4    | Read/Write DC Voltages           | 5-8   |

| 5-5    | DC Voltage Distribution          | 5-9   |

| 5-6    | Sequence Up                      | 5-10  |

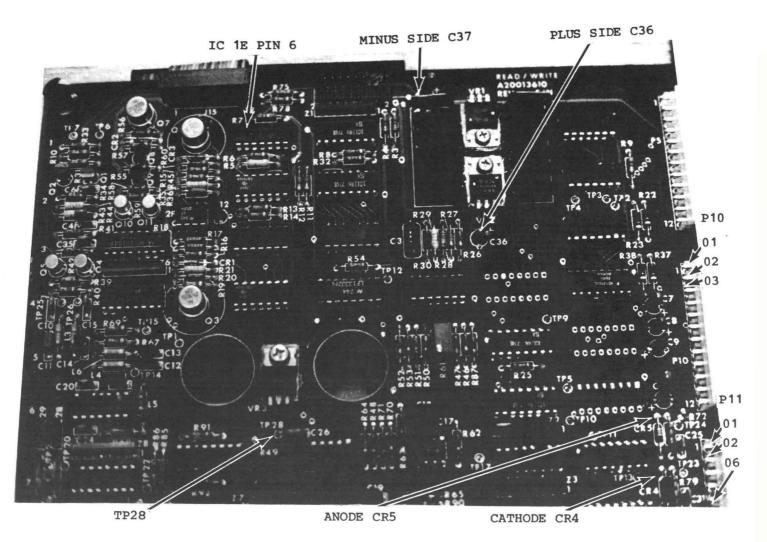

| 5-7    | Servo Adjustments                | 5-14  |

| 5-8    | DELETED                          |       |

| 5-9    | DELETED                          |       |

| 5-10   | Velocity Adjustment              | 5-19  |

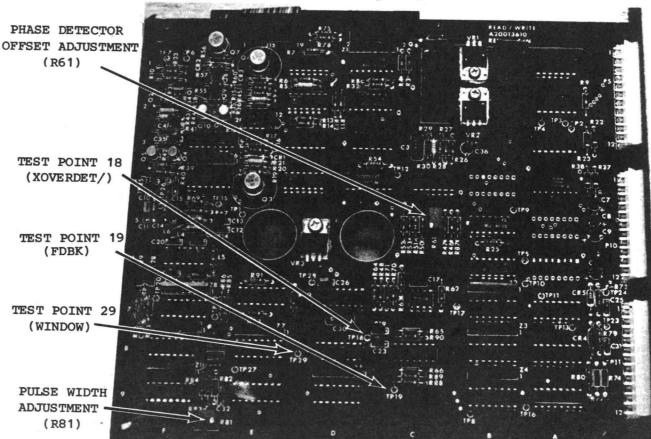

| 5-11   | Read/Write Adjustments           | 5-19  |

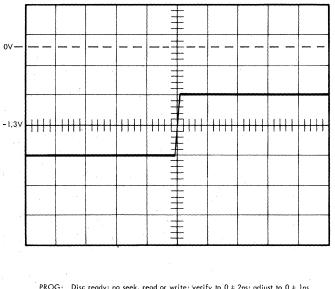

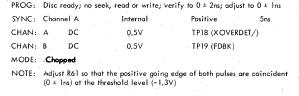

| 5-12   | Phase Detector Offset Adjustment | 5-20  |

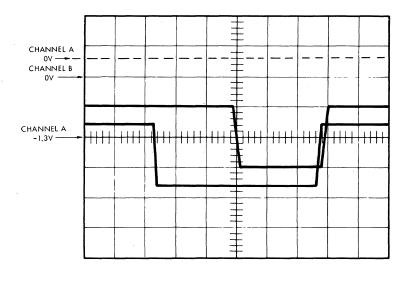

| 5-13   | Pulse Width Adjustment           | 5-22  |

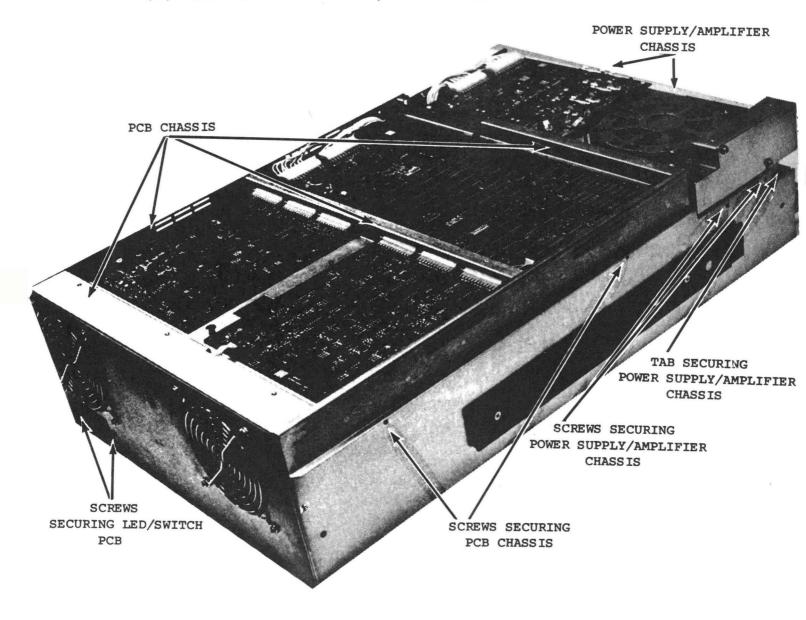

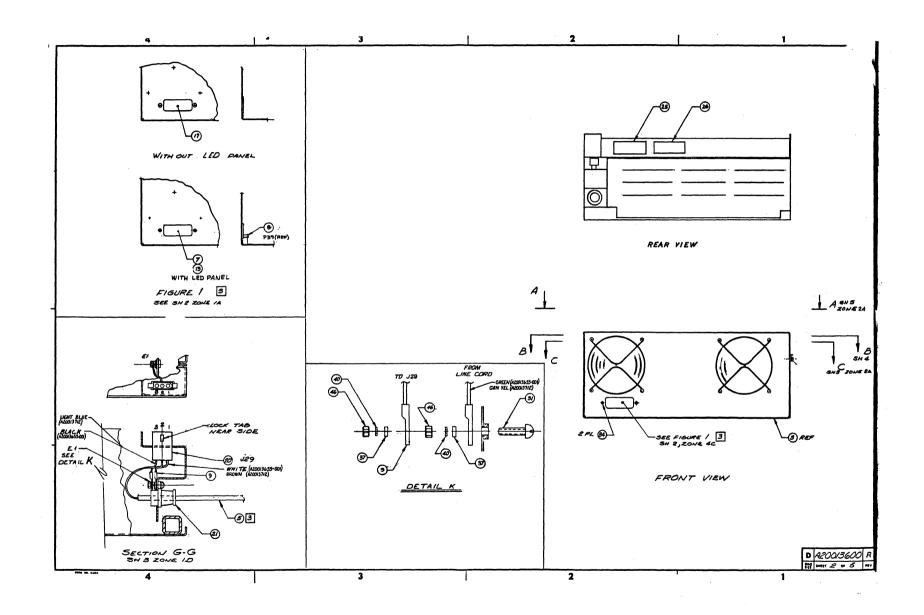

| 5-14   | REFLEX II Front/Side View        | 5-25  |

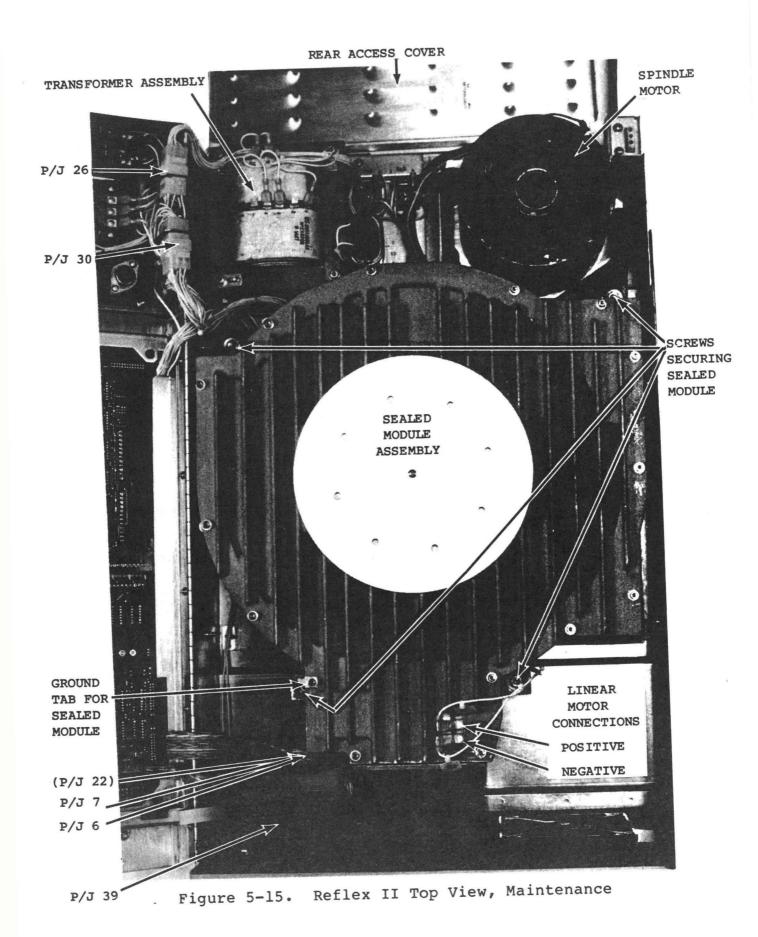

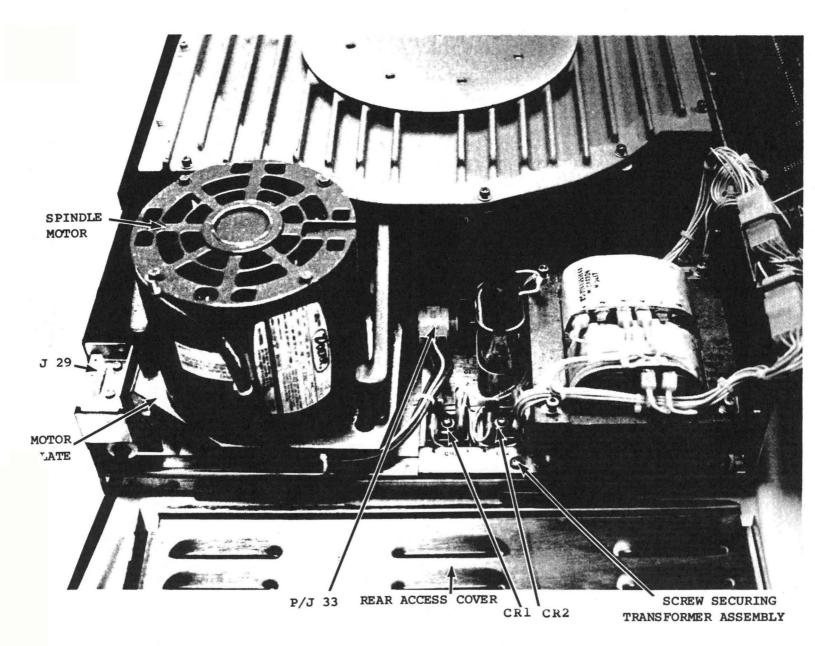

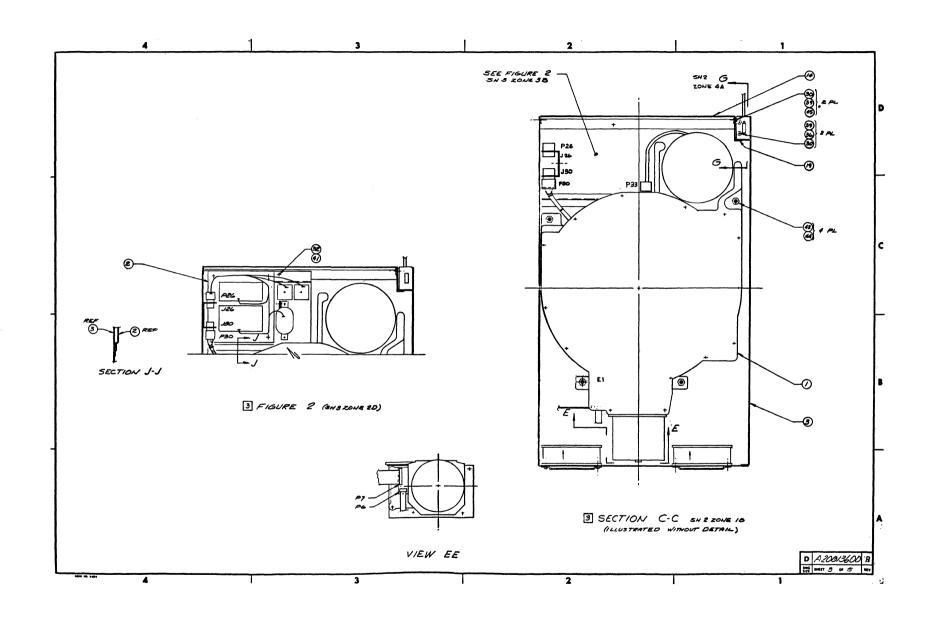

| 5-15   | REFLEX II Top View, Maintenance  | 5-27  |

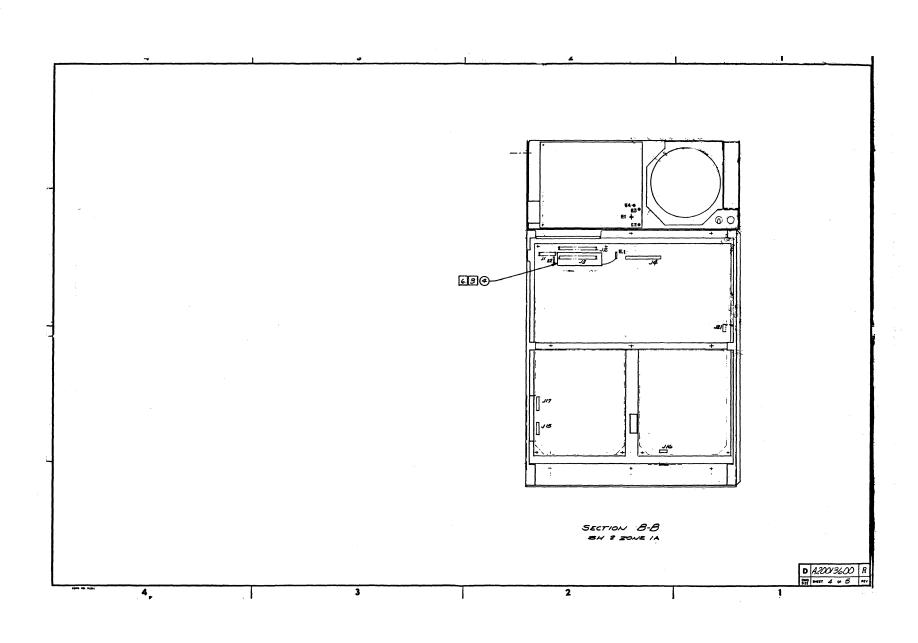

| 5-16   | REFLEX II Rear View              | 5-29  |

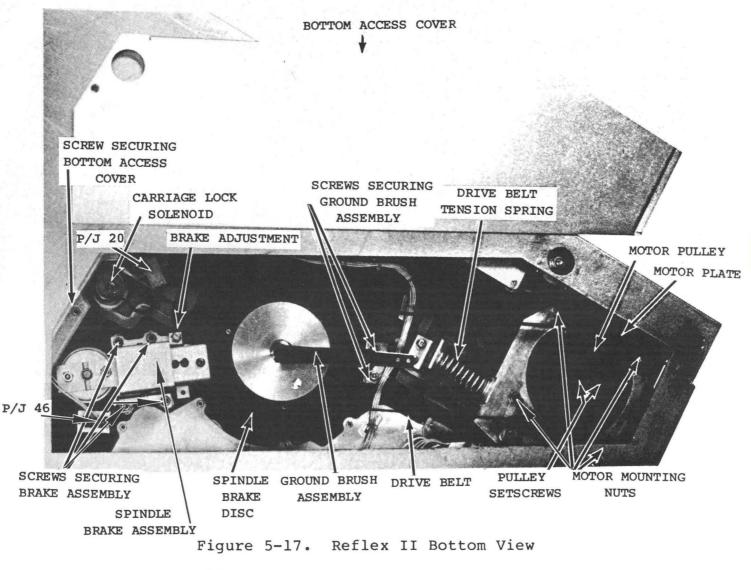

| 5-17   | REFLEX II Bottom View            | 5-30  |

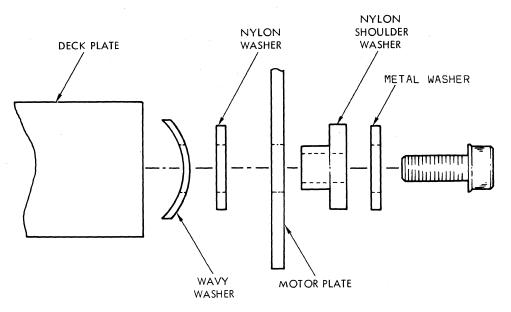

| 5-13   | Motor Plate Hardware             | 5-32  |

| 5-19   | Line Filter Assembly             | 5-34  |

TABLES

| Table |                                                   | Page |

|-------|---------------------------------------------------|------|

| 1-1   | REFLEX II Specifications                          | 1-12 |

| 2-1   | Input AC Voltage Fluctuations                     | 2-4  |

| 2-2   | DC Voltage Requirements                           | 2-6  |

| 2-3   | Operation Signals                                 | 2-14 |

| 2-4   | I Configuration Status                            | 2-20 |

| 3-1   | Installation and Operation                        | 3-1  |

| 3-2   | Cable Connector Assignments                       | 3-8  |

| 3-3   | System Connection Information                     | 3-12 |

| 3-4   | Operator Indicator Panel                          | 3-16 |

| 3-5   | Maintenance Controls                              | 3-17 |

| 3-6   | Unit Address Switch Settings                      | 3-19 |

| 3-7   | Head Selection Switch Settings                    | 3-20 |

| 3-8   | Sector Selection                                  | 3-22 |

| 4-1   | Drive Selection Switch Settings                   | 4-19 |

| 4-2   | Bus and Tag Decode                                | 4-43 |

| 4-3   | Movable Head Selection Decode                     | 4-82 |

| 5-1   | Voltage and Test Points for Power Supply/Amp PCB  | 5-4  |

| 5-2   | Voltage and Test Points for Logic/Interface PCB . | 5-5  |

| 5-3   | Voltage and Test Points for Servo PCB             | 5-6  |

| 5-4   | Voltage and Test Points for Read/Write PCB        | 5-7  |

| 6-1   | REFLEX II Part Numbers and Descriptions           | 6-1  |

| 6-2   | REFLEX II Options                                 | 6-3  |

| 6-3   | REFLEX II Accessories                             | 6-3  |

| 6-4   | REFLEX II Schematics                              | 6-3  |

#### SECTION 1

#### GENERAL DESCRIPTION

#### INTRODUCTION

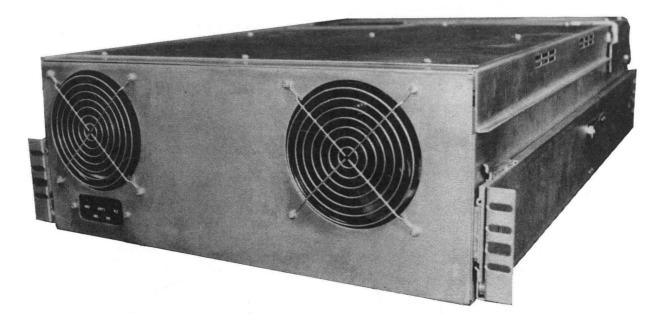

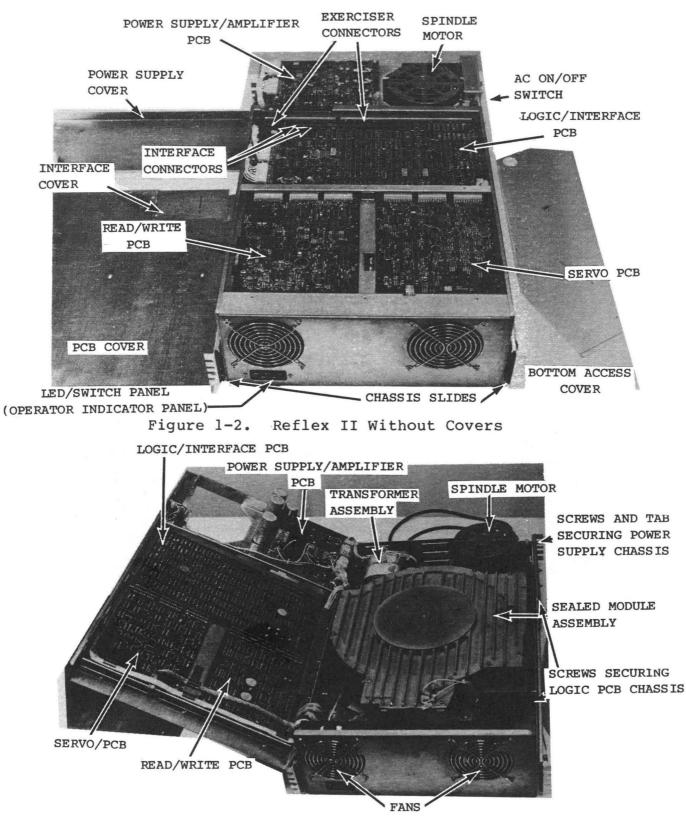

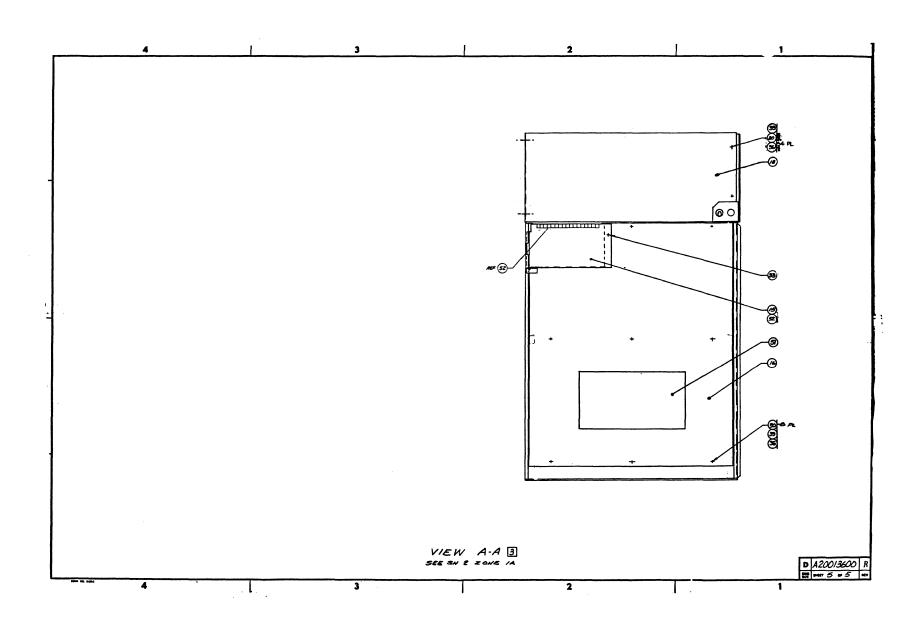

This section includes a general description of the Microdata Reflex® II disc drive. Figure 1-1 presents the Reflex II with all covers intact and all available options. Figure 1-2 shows the Reflex II with all covers removed. The accessibility of the modular components is shown in Figure 1-3.

Figure 1-1. Reflex II Disc Drive

Figure 1-3. Reflex II Modular Component Accessibility

#### REFLEX II FEATURES, OPTIONS, AND ACCESSORIES

#### Features

Reflex II features include the following:

- Winchester technology

- Choice of four models (22.6, 67.8, 113.1, and 158.3 megabyte capacities)

- Fixed disc media

- High transfer rate

- Fast access time

- U.L. recognized component

- Sealed disc and positioning unit

- Modular construction

- Lifetime filters

- Quiet operation

- No scheduled maintenance

- Low temperature rise

- High reliability

- Closed recirculating clean air system

- Daisy chain or star (radial) configuration

- Selectable sector length

- Selectable unit address

- Built-in data separator for modified frequency modulation (MFM) recording

- Non-return to zero (NRZ) data at interface

#### Options

Reflex II optional items include the following:

- Operator indicator panel

- Chassis slides for Radio Electronics Television Manufacturers Association (RETMA) cabinet mounting

- Internal power supply with provision to select voltage combinations and supply all required DC power

- 50 Hz voltage frequency

#### Accessories

Reflex II accessories include the following:

- Data interface cable

- Signal interface cable

- Cable terminator assembly

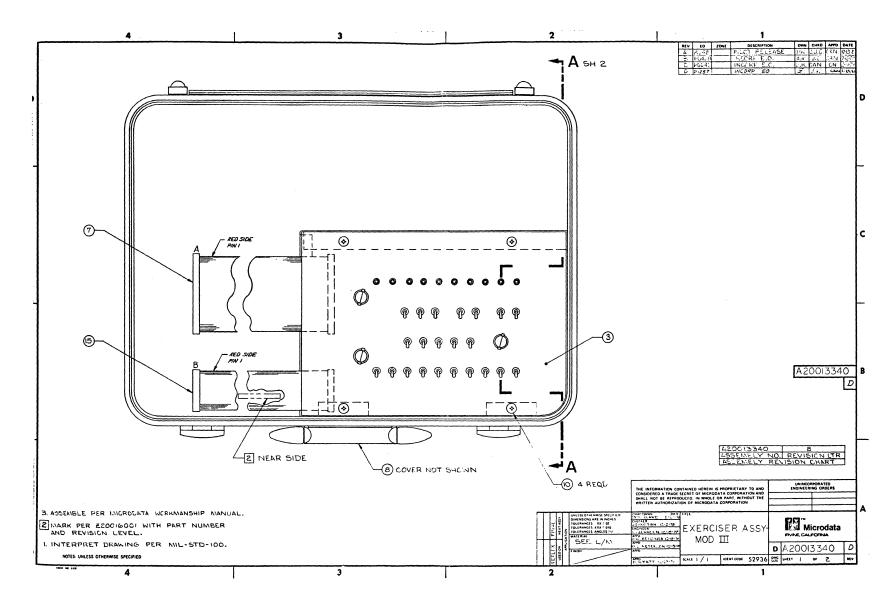

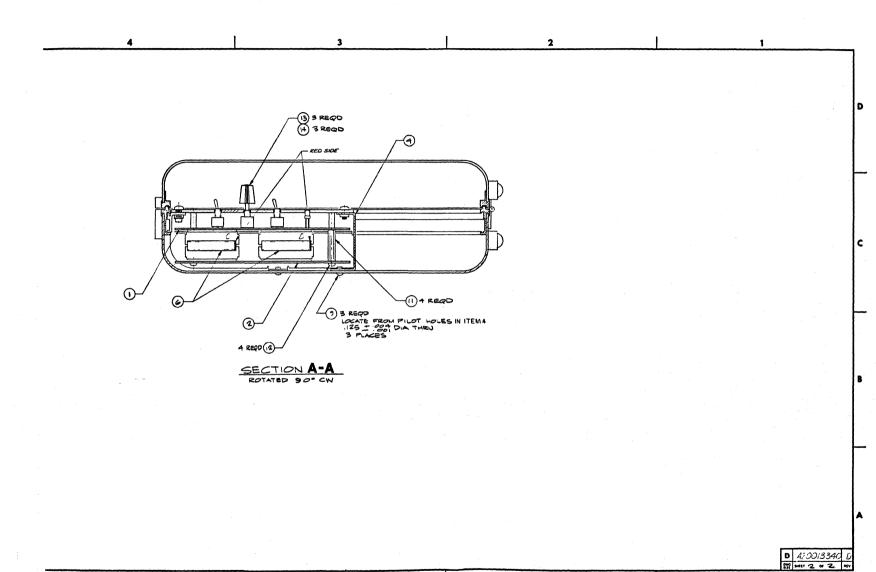

- Exerciser Mod III

#### GENERAL

The Microdata Reflex II series disc drives are high performance, random-access memory devices designed to meet the fixed media storage requirements for minicomputers and small- and medium-sized general purpose computers. Reflex II units are immune to many external environmental conditions, making them exceptionally reliable devices. The unit is designed to be operated in the upright position.

Reflex II is available in four basic versions. Models A, B, C, and D utilize one, two, three or four discs, respectively, on the spindle. Models A, B, C, and D have unformatted storage capacities of 22.6 megabytes, 67.8 megabytes, 113.1 megabytes and 158.3 megabytes of data, respectively. Head positioning time is 6 milliseconds (track to track) and 30 milliseconds (average). Average rotational latency is 8.50 milliseconds. Up to sixteen disc drive units can be daisy-chained from a single controller, providing up to 2532.8 megabytes of unformatted, on-line storage.

Reflex II maintenance requirements are minimal. The need for periodic maintenance, including head alignments, is eliminated due to the integration of the rotating disc, recording heads, and the head positioning mechanism into a single replaceable assembly. A closed loop air circulation and filtration system, combined with positive internal pressure, provides maximum air purity within the assembly.

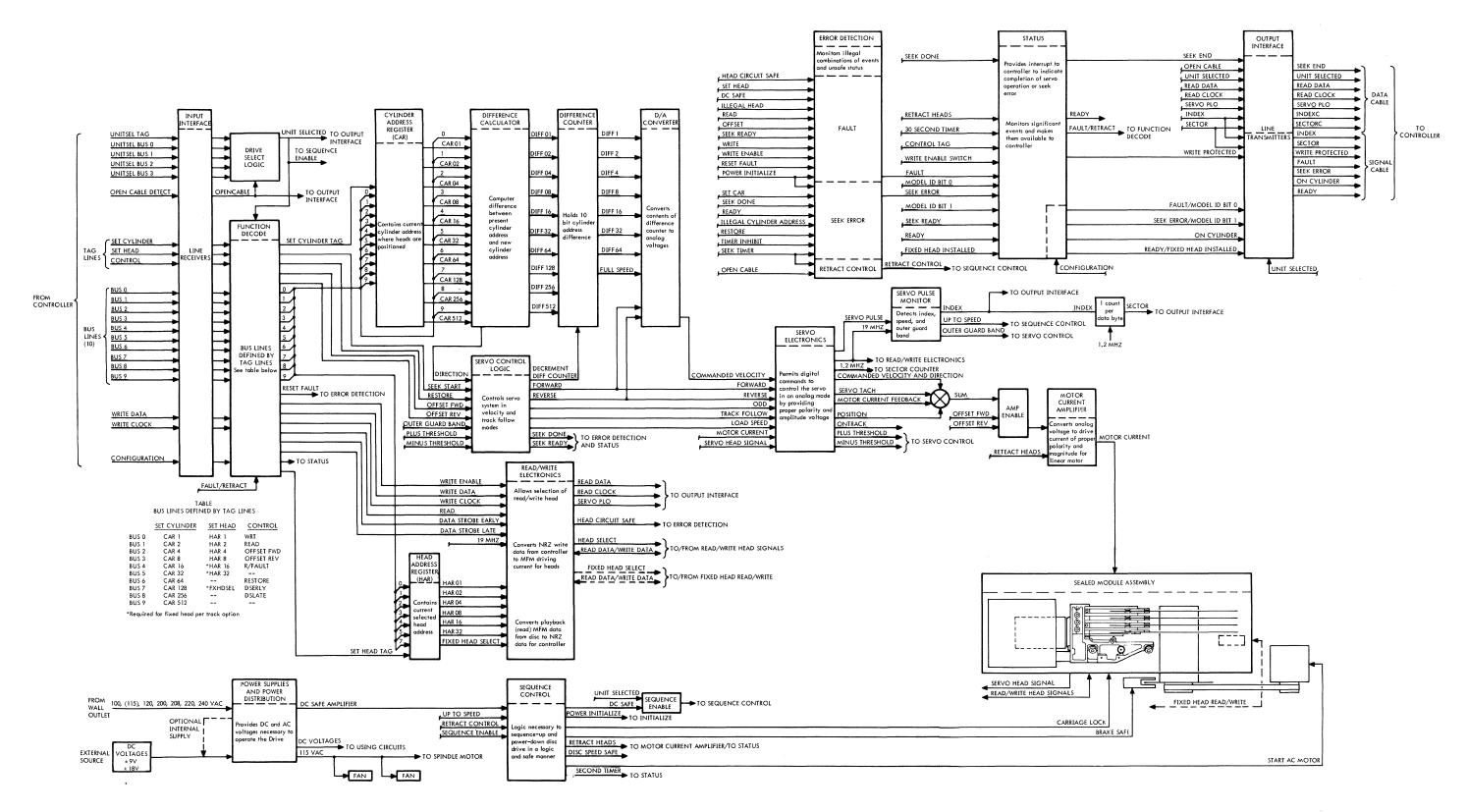

#### FUNCTIONAL DESCRIPTION

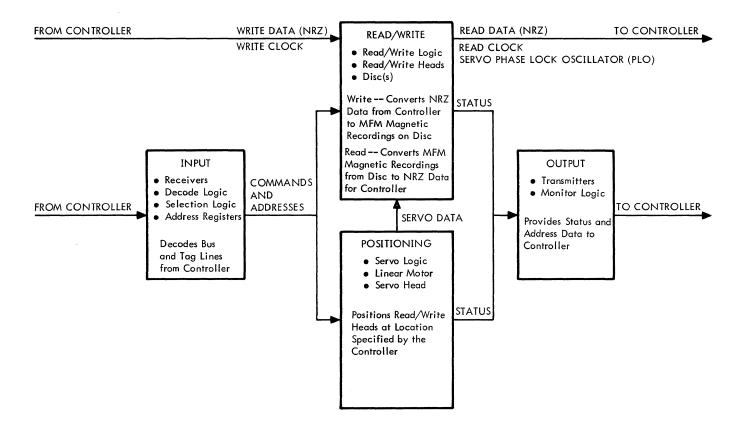

The Reflex II disc drive is a fixed media unit with fast access times, high data transfer rates, and medium capacity storage. The functional areas are shown and described in Figure 1-4. The disc drive can be divided into the following basic functional areas.

- Input/Output

- Positioning

- Read/Write

Figure 1-4. Reflex II General Block Diagram

#### Input

The controller provides the following input interface signals to the drive:

- Address select lines

- Bus and tag lines

- Configuration request

- Write data and write clock lines

#### 1. Address Select

There are four select bus lines and one select tag line. They are connected in parallel to each drive. When the controller activates the select tag line, the drive's address comparison logic looks at the address bus lines and if there is a comparison, the disc drive becomes selected. Selection enables the input and output interface logic of the disc drive.

#### 2. Bus and Tag Lines

There are ten bus lines and three tag lines that are used to provide information to the disc drive. The three tag lines define the information on the bus lines as either addresses or control commands.

#### 3. Configuration Request

The configuration request line is used to differentiate status information from either the moving head disc or the fixed head disc. It is also used to define model type.

#### 4. Write Data and Write Clock

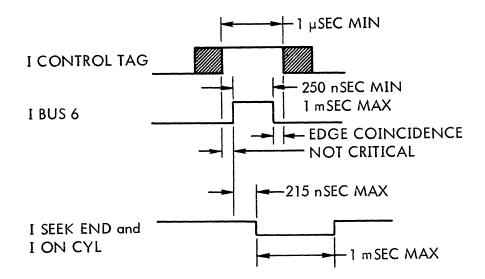

A bidirectional cable is used to present write data and write clock to the drive. It also presents read data, read clock and data from the servo phase lock oscillator (PLO) to the controller. Write data is not directly controlled by the interface logic. The write enable lines are decoded from the bus and tag lines and control the write mode of the drive.

#### Output

Upon selection, the output interface is enabled and the following information is made available to the controller, when queried:

- Selection status

- Operational status

- Error condition status

- Read data and read clock

- Servo PLO (continuously transmitted, regardless of selection)

Seek end (interrupt) is made available to the controller with or without selection.

#### Positioning

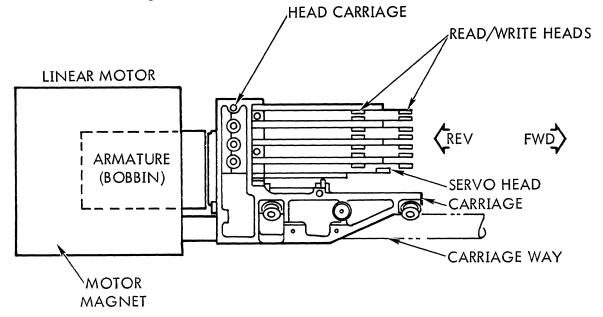

Positioning is accomplished by the servo logic. The servo logic receives its input from the controller via the input interface. The input interface decodes the input from the controller and determines the necessary position of the read/write heads. This information is then passed to the servo logic, which drives and controls the position of the read/write heads. The read/write heads are moved into their proper position by a linear motor. This motor consists of a stationary permanent magnet surrounding a movable, servo-driven voice coil armature (bobbin) (see Figure 1-5).

Power for the linear motor is provided from the servo logic by a direct current, which flows through the bobbin. The magnetic field built up around the bobbin by this current causes a reaction with the permanent magnetic field, and the reaction either forces the bobbin away from the permanent magnet or pulls it into the field of the permanent magnet. The direction of movement depends on the polarity of the current flow. Speed depends on the amplitude of the current.

Fastened to the bobbin is a head carriage which holds the read/write and servo heads. The carriage moves freely on ballbearing rollers. Movement of the bobbin in and out of the permanent magnet moves the carriage backward and forward. This linear travel positions the read/write heads over their respective disc surfaces. The servo has two modes of operation--a velocity mode and a track follow mode. The velocity mode is evoked when the controller commands the read/write heads to move from their current position (cylinder) to another cylinder. The track follow mode is active whenever the velocity mode is not active. The track follow mode works to maintain the present position of the read/write heads.

During either mode of operation, the servo receives information from the servo head. This information is derived from prerecorded data on the servo disc and is monitored by the read only servo head. The information provided during the velocity mode includes velocity information which allows the servo logic to control the speed of movement. It also includes cylinder boundary information to allow the servo logic to position the read/write heads to the commanded cylinder. The information provided during track follow mode allows the servo logic to maintain the position of the read/write heads.

In addition to the servo control information, the servo data provide information that is used to generate index location, sector pulses, and write clock frequency.

#### Read/Write

The read, rite system includes the read/write logic, read/write heads, and discs. The system consists of the elements necessary to convert NRZ data input to MFM data, record the data, retrieve the data and convert it to NRZ data as output data.

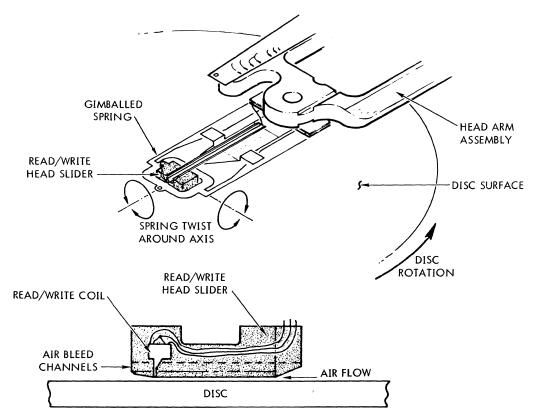

Reflex II employs Winchester technology. This technology uses low mass, high compliance recording heads which fly much closer to the disc surface than permitted by previous technologies. Because of this close proximity to the disc surface, reading and recording may be performed at higher data and track densities, with greater reliability than was possible with the older technologies.

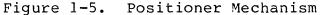

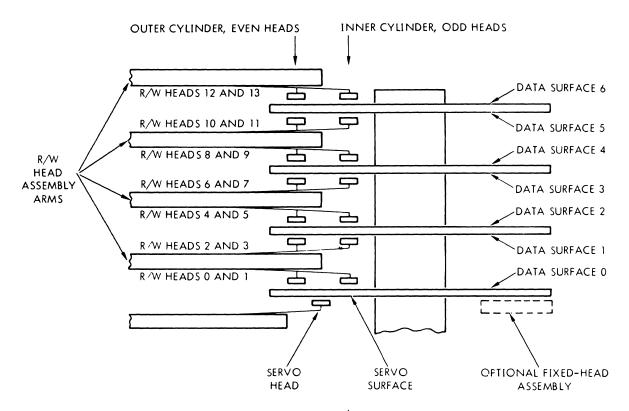

Reflex II uses the cylinder concept with up to four discs providing up to seven read/write data surfaces and one servo data surface. Information is recorded or retrieved from the discs by up to fourteen read/write heads. There are two heads for each recording surface. The read/write heads are mounted in a vertical stack on a single carriage and therefore are positioned together over their respective surfaces.

The discs are evenly spaced and stacked on a central hub. Each disc surface is an aluminum substrate with an oxide coating and a lubricant overcoat. The bottom side of the bottom disc contains the prerecorded servo data.

Figure 1-6. Reflex II Cylinder Concept

Data is recorded by magnetizing digital bit patterns in concentric circles (cylinders) on the recording surfaces. With two heads per surface, there is an inner and outer cylinder. The inner cylinder is comprised of the odd numbered heads while the outer cylinder is comprised of the even number heads. As shown in Figure 1-6, each surface contains 561 cylinders. Since each surface has two heads, there are 1122 tracks per surface. The cylinders are numbered 000 through 560. The cylinder nearest the outer edge of the disc is the beginning of the even numbered heads and the odd numbered heads begin with the cylinder nearest the center of the recording surface.

When the head carriage is moved to a given cylinder position, each read/write head is positioned over a corresponding track on its recording surface. For example, when the head carriage is moved to cylinder 100, head 0 is positioned over track 100 on surface 0 in the outer cylinder boundary. Head 1 will be located over track 100 on surface 0 in the inner cylinder boundary and head 2 will be positioned over track 100 on surface 1 in the outer cylinder boundary.

To select a particular track for recording or retrieval of data, the following is performed:

- (1) The head carriage is moved to the cylinder containing the track to be accessed.

- (2) The appropriate read/write head for the desired track is selected.

Therefore, a complete track address requires both a cylinder address and a read/write head address.

When writing data, the read/write head is essentially an electromagnet that can concentrate a high magnetizing force over a very small area of the adjacent recording surface. The flux field is alternated to magnetize the disc with the desired bit pattern.

When reading data, the read/write head operates as a sensor. A flux reversal on the recorded surface induces a voltage across the electromagnetic coil. This voltage is amplified and conditioned to allow recovery of the recorded data.

#### PHYSICAL DESCRIPTION

Reflex II is a family of fixed disc units, enclosed with removable top covers. Reflex II has a front air intake panel to channel air from the front to the rear and to keep out dust and dirt.

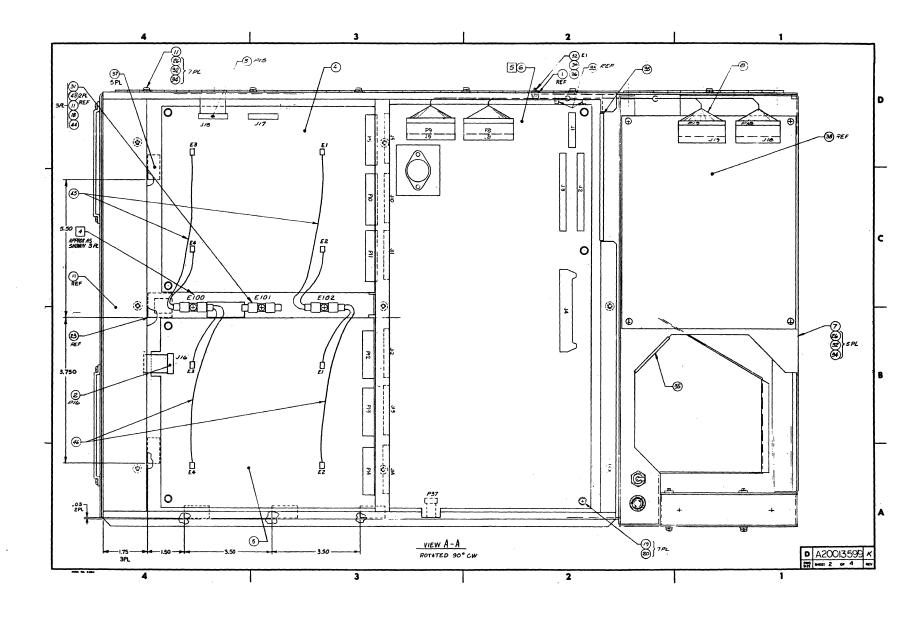

The disc drive consists of a sealed module assembly, cables, panel, frame, power supply, printed circuit boards and covers. The unit will accommodate chassis slides for standard RETMA cabinet mounting, with locks to maintain the drive position in the cabinet.

The sealed module assembly is a field replaceable assembly. It is comprised essentially of the spindle, discs, carriage lock, heads, carriage, way, positioning motor, crash stops, air filters, and metal structure.

Attached to the sealed module are the brake, ground brush, spring-loaded spindle drive motor, and drive belt. These items are field replaceable along with the power supply and printed circuit boards. The discs spin counterclockwise as viewed down from the top of the assembly.

The panel contains a write protect switch and indicators for ready, write protect status, and fault conditions.

The disc spindle is mounted in the sealed module assembly and is driven by a 115 VAC drive motor. The motor and spindle are coupled by a pulley and belt system designed to provide a disc rotational speed of 3530 rpm.

Cooling air is provided by two front mounted fans with 120 CFM flow capability. Air flow is into the front, through the unit and out the rear. Care must be taken not to block the air flow path either at the front or at the rear.

The clean air system is contained within the sealed module assembly and consists of two absolute filters, an air pump and seals. It is implemented to control pressure levels within the module.

#### SAFETY FEATURES

#### Operator

All exposed metal parts are at earth-ground potential. All moving parts and potentially hazardous voltages are covered, except when being serviced.

#### Drive

The linear positioning motor is protected against potential burnout by removing servo power to the motor if a motion command (seek, restore, head load) is not completed within 1-1/2 seconds. Additionally, if the motor is continuously driven against the mechanical stops, protective fuses will blow before either motor or amplifier damage can occur.

The spindle motor is protected against excessive heating by a thermo-cutoff in the motor. (Excessive heating may be caused by repeated start-stop cycles at a rate greater than three consecutive start-stop cycles).

#### Data

There is a write enable/disable switch to disable (prevent) writing when not desired. Extensive safety circuits are present to detect abnormal conditions within the drive and disable write operations if any abnormal condition is detected (see Section 2).

Reflex II specifications are listed in Table 1-1.

# TABLE 1-1

-

| Fannan                                                     | II SPECIFICA                                       |                |                |            |

|------------------------------------------------------------|----------------------------------------------------|----------------|----------------|------------|

| <u>Operational</u>                                         | Model A                                            | <u>Model B</u> | <u>Model C</u> | Model D    |

| Track density (TPI)                                        | 478                                                | 478            | 478            | 478        |

| Number of discs                                            | 1                                                  | 2              | 3              | 4          |

| Number of data surfaces                                    | 1                                                  | 3              | 5              | 7          |

| Number of data cylinders                                   | 561                                                | 561            | 561            | 561        |

| Data heads per cylinder                                    | 2                                                  | 6              | 10             | 14         |

| Data tracks per surface                                    | 1122                                               | 1122           | 1122           | 1122       |

| Data bytes per track                                       | 20160                                              | 20160          | 20160          | 20160      |

| Data bytes per surface (MEGA)                              | 22.62                                              | 22.62          | 22.62          | 22.62      |

| Data byte capacity (MEGA)                                  | 22.62                                              | 67.86          | 113.1          | 158.3      |

| Disc rotation speed (RPM)                                  | 3530 <sup>+3</sup><br>-7                           | 8 3530         | 3530           | 3530       |

| Data byte transfer rate (MHz)                              | 1.186                                              | 1.186          | 1.186          | 1.186      |

| Data bit transfer rate (MHz)                               | 9.489                                              | 9.489          | 9.489          | 9.489      |

| Data bit cell time (nanosecond)                            | 105.4                                              | 105.4          | 105.4          | 105.4      |

| Bit density, inside track (BPI)                            | 6427                                               | 6427           | 6427           | 6427       |

| Optional fixed head per track data<br>byte capacity (MEGA) | 1.2                                                | 1.2            | 1.2            | 1.2        |

|                                                            |                                                    |                |                |            |

| Recording Technology                                       |                                                    |                |                |            |

| Write data input                                           | NRZ at the int                                     | erface, MH     | M at the d     | disc       |

| Read data output                                           | MFM at the dis                                     | c, NRZ at      | the inter:     | Eace       |

| Read/write heads                                           |                                                    |                |                |            |

| Number                                                     | Two (2) per di                                     | sc surface     | 5              |            |

| Туре                                                       | IBM 3350 style                                     |                |                |            |

| Format                                                     | Fixed or varia                                     | ble length     | n, user de     | termined   |

| Accessing                                                  |                                                    |                |                |            |

| Head positioning                                           | High efficienc<br>electronic ve<br>cylinder posi   | locity tra     | ansducer is    | s used for |

| Head positioning time                                      | 6 milliseconds<br>30 millisecond<br>55 millisecond | s average,     | track,         |            |

| 81 1091B                                                   | 1-12                                               |                |                |            |

#### REFLEX II SPECIFICATIONS

50 seconds maximum (drive ready) Start time 10 seconds maximum Stop time Rotational latency 8.50 milliseconds average 17 milliseconds nominal 18.19 milliseconds maximum Error rates Less than one error in  $10^6$  motion commands Head positioning Less than one error in 10<sup>10</sup> bits Recoverable Less than one error in  $10^{13}$  bits Nonrecoverable Mean time between failure Greater than 5000 hours (MTBF) Mean time to repair (MTTR) Less than one hour Dimensions Width 17.5 inches (44.5 cm) Height 7 inches (17.8 cm) Depth 28 inches (71.1 cm) Weight 100 pounds (45 kg) Input Power Requirements AC voltage 100, 115, 120, 200, 208, 220, 240 AC +10 -15 Single phase Amperes Start 20A rms at 115 VAC, first 10 seconds Operating 4A rms at 115 VAC, typical Power consumption 350 watts Line frequency 60 Hz or 50 Hz (+1 Hz) DC voltage +9V @ 3 amperes -9V @ 2 amperes +18V @ 3 amperes NOTE: DC voltage input is not required for drives equipped with optional internal DC power supply.

| · · · · ·         |                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environmental     |                                                                                                                                                        |

| Temperature       |                                                                                                                                                        |

| Operational       | <pre>15°C to 55°C (59°F to 131°F) maximum rate<br/>of change 10°C (18°F) per hour. Inlet<br/>air must be within 15°C to 41°C (59°F to<br/>106°F)</pre> |

| Storage           | -50°C to +80°C (-58°F to +176°F) maximum<br>rate of change 40°C (72°F) per hour.                                                                       |

| Relative humidity |                                                                                                                                                        |

| Operational       | 10 percent to 80 percent noncondensing                                                                                                                 |

| Storage           | 10 percent to 80 percent noncondensing                                                                                                                 |

| Airflow           | 120 CFM minimum, unrestricted                                                                                                                          |

| Altitude          |                                                                                                                                                        |

| Operational       | -100 ft. to +6000 ft. (-30m to +1800m)                                                                                                                 |

| Storage           | 21 inches to 32 inches mercury (53 cm to 81 cm)                                                                                                        |

TABLE 1-1, REFLEX II SPECIFICATIONS (Cont'd)

#### NAMEPLATE IDENTIFICATION

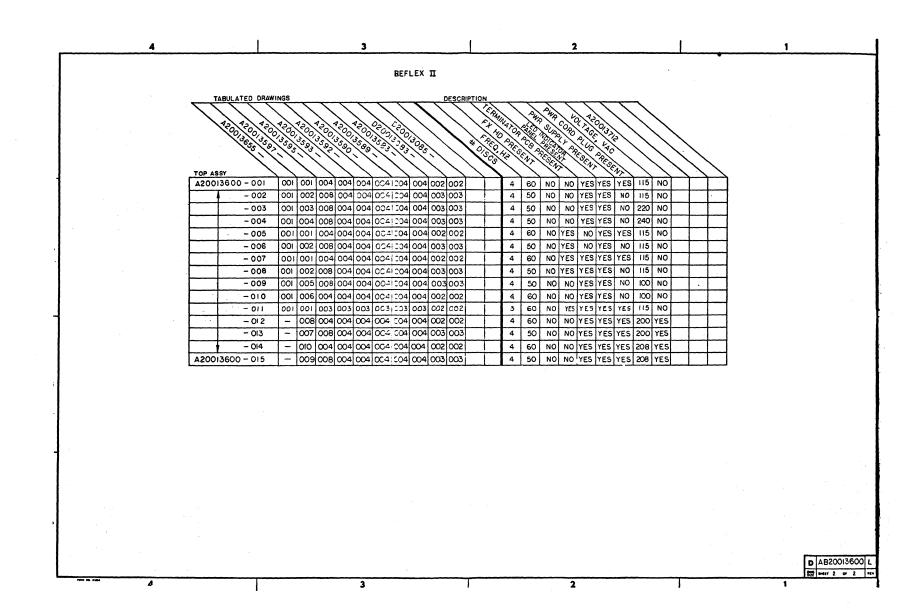

Figure 1-7 shows the nameplate which is affixed to the top left rear of the unit. The information provided includes the model name, top assembly part number, model ID, serial number, and power requirements as to VAC, ampheres, and Hz. A listing of the top assembly part numbers is provided in Appendix A.

| Ľ.   |    | Mi  | Cr( | ) d | a   | ł c |    |   | VI | NE |   | : A | 1 300 | 0 | p; | VI. | A |  |

|------|----|-----|-----|-----|-----|-----|----|---|----|----|---|-----|-------|---|----|-----|---|--|

|      |    |     |     |     |     |     |    |   |    |    |   |     |       |   |    |     |   |  |

| ASSY | A. | IO. |     |     |     |     |    |   |    |    |   |     |       |   |    | ·   |   |  |

| MODI | •  |     |     |     |     |     | SE | R |    |    |   |     |       |   |    |     |   |  |

| POWI | ĒR |     |     |     | /A( |     |    |   | A  | M  | 2 |     |       |   |    |     |   |  |

Figure 1-7. Nameplate

#### SECTION 2

#### PHYSICAL PLANNING AND INTERFACE REQUIREMENTS

#### INTRODUCTION

This section provides information for site considerations, including space, power, configuration and interface requirements.

#### ENVIRONMENTAL CONDITIONS

The typical environment for the Reflex II is an airconditioned office or data processing center. However, this type of environment is not necessary. The Reflex II disc drive should not be directly exposed to outside weather or to unusual chemical or atmospheric gas conditions. The total sum of the environment is the major consideration that will affect the life of the product. While scheduled maintenance is not normally required, conditions of the environment may give rise to periodic maintenance such as vacuuming or removing dust accumulation. Care should be exercised not to exceed the environmental specifications listed in Section 1 and those noted in this section.

#### Stabilization

The Reflex II disc drive is subject to a stabilization period of four hours minimum, only when introduced to an inspecification environment from an out-of-specification environment.

#### Temperature

The drive may be bathed or placed in air with a temperature range of 15°C to 55°C (59°F to 131°F). However, the front panel air inlet temperature must be within 15°C to 41°C (59°F to 106°F). The operating temperature rate of change is limited to 10°C (18°F) per hour.

#### Humidity

The operational humidity range is 10 percent to 80 percent, noncondensing, with a wet-bulb temperature of less than 25.6°C (78°F).

#### Altitude

The altitude range is the sum of the temperature, humidity, and barometric pressure limits. The operational barometric pressure range is -100 to +6000 feet (-30 to +1800 m).

#### Air Flow

Uninhibited air flow must be allowed through the disc drive. The direction of the air flow is from front to back. The openings at the front and rear must be unrestricted to allow for 120 CFM of air flow.

#### Noise Level

The Reflex II disc drive has been designed not to exceed the noise criteria (NC55) standard for noise pollution.

#### Storage

For environmental limits during storage, see the specifications listed in Section 1.

#### SPACE REQUIREMENTS

Reflex II fits within box dimensions of 7 inches (17.78 cm) high, 28 inches (71.12 cm) deep, and 17.5 inches (44.45 cm) wide. The weight of the unit is less than 100 pounds (45 kg). See Figure 2-1 for an outline of physical dimensions.

Optional chassis slides are available for standard RETMA cabinet mounting. The slides allow for the performance of all maintenance activities through frontal access. The slides also allow for the drive to be locked in position when retracted in the cabinet.

#### POWER REQUIREMENTS

Power requirements are different depending on whether the optional internal power supply (transformer assembly) is installed. In either case, Reflex II has been designed to be tolerant of AC line voltage fluctuations. The only requirement is that the AC input power and ground must be consistent to, or common with, the other computer peripheral equipment at the same installation.

Figure 2-1. Physical Dimension Considerations

2-3

### Input AC Voltage Fluctuations

The AC voltage should not vary from its nominal value longer or more frequently than the limits shown in Table 2-1. All occurrences must be noncoincident with each other.

### TABLE 2-1

| Input Voltage<br>(Percent of nominal) | Duration<br>(milliseconds) | Occurrence        |

|---------------------------------------|----------------------------|-------------------|

| 0                                     | 10                         | l per 600 seconds |

| 50                                    | 10                         | l per 10 seconds  |

| 130                                   | 60                         | l per 30 seconds  |

| 200                                   | 10                         | l per 240 seconds |

### INPUT AC VOLTAGE FLUCTUATIONS

### Power Cable Configurations

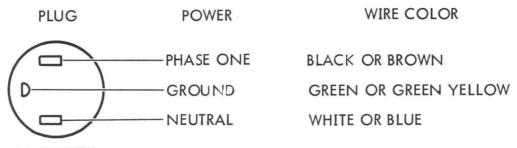

The standard Reflex II configuration is for 115V 60 Hz. For this, a 9 foot (2.7 m) nominal, 8 foot (2.4 m) minimum power cable and connector is furnished to plug into a standard NEMA outlet as shown in Figure 2-2.

Figure 2-2. Standard AC Power Outlet Configuration

For voltage and frequency combinations other than 115V 60Hz, a connector is not provided at the end of the power cable. The user may connect his own connector per the power cable wire assignments listed as follows:

| Power | Wire Color |

|-------|------------|

|       |            |

| Phase one | Black | or | brown |        |

|-----------|-------|----|-------|--------|

| Neutral   | White | or | blue  |        |

| Ground    | Green | or | green | yellow |

2-4

### AC Power With Optional Internal Power Supply

Reflex II has internal taps to accommodate any one of the following single phase voltages: 100, 115, 120, 220, and 240. The voltage tolerances are +10 and -15 percent. The frequency of each voltage may be either 50 +1 or 60 +1Hz.

The run current is 4 amperes AC root mean squared (RMS) typical for 115 VAC, at a 70 percent power factor. However, there is a start current surge of 20 amperes. The typical current characteristics for 115 VAC are shown in Figure 2-3.

Figure 2-3. Typical Current Characteristics With Internal Power Supply

# AC Power Without Optional Internal Power Supply

The input power requirement is 115 VAC +10 -15 percent, single phase with a frequency of either 50  $\pm$ 1 or 60  $\pm$ 1Hz.

The current requirement is 2.5 amperes RMS, nominal, at 115 VAC (considering a 70 percent power factor) with a start current surge of 20 amperes. The typical current characteristics are shown in Figure 2-4.

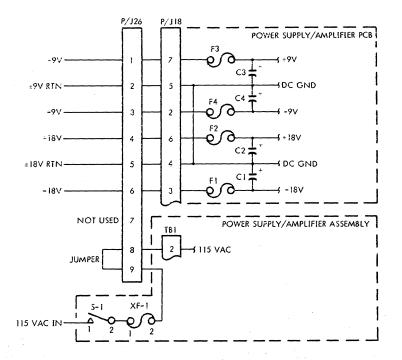

### DC Voltage Without Optional Internal Power Supply

Table 2-2 lists the required DC voltages with their appropriate load current characteristics. Each voltage is independently fused to protect the drive. External fuses may be necessary to protect the source cable or DC sources. Each voltage is filtered in the drive with a 15,000 microfarad (minimum) electrolytic capacitor. The incoming DC voltages must attain specified stable levels within 200 milliseconds of each other.

#### TABLE 2-2

| Min.          | Voltage<br>Nom. | Max.          | RMS Am<br>Min.   | pere<br>Max. | 500 KHz<br>Impedance<br>Max. Ohms | Maximum<br>Transient<br>Current Ampheres |

|---------------|-----------------|---------------|------------------|--------------|-----------------------------------|------------------------------------------|

| <u>P1111.</u> | NOIL •          | <u>Flax</u> . | <u>F1 1 11 •</u> | Max          | Max. Onus                         | current Ampheres                         |

| + 8.0         | + 9.0           | +10.0         | 1                | 3            | 0.05                              | 1                                        |

| -10.0         | - 9.0           | - 8.0         | 0.5              | 2            | 0.05                              | 1                                        |

|               |                 | +19.5         | 1                | 3            | 0.10                              | 5                                        |

| -19.5         | -18.0           | -16.5         | 1                | 3            | 0.10                              | 5                                        |

#### DC VOLTAGE REQUIREMENTS

The voltages are conected to Reflex II connector J26 with pin assignments as shown in Figure 2-5. The mating connector that must be supplied to J26 is a MOLEX connector (part number 19-10-1091), with pins (part number 02-09-1103 or equivalent) for wire gauges of 14 to 20.

Figure 2-5. DC Voltage Supply Cable Pin Assignments

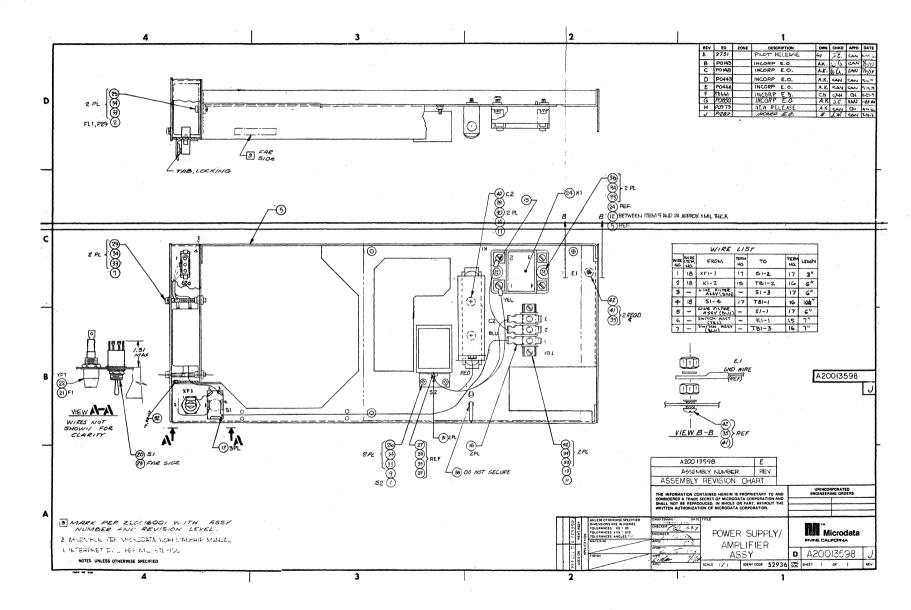

# Grounding

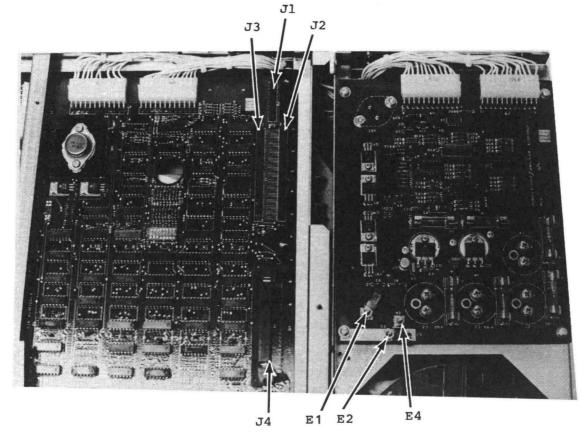

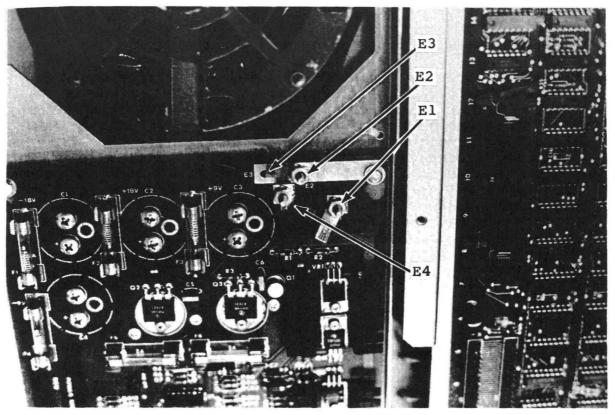

REFLEX II grounding is of the distributed grounding scheme and the terms "frame ground" and "signal ground" become one and the same. A jumper between E2 and E4 on the power supply amplifier PCB is one of the points of commonality of frame and signal ground. An external frame (earth) ground must be connected to the power supply/amplifier PCB at E1 (Figure 2-6). This external GND may be via a system's cabinet frame, but must ultimately connect to earth ground. A 0.25inch male terminal tab is provided for this connection.

Figure 2-6. Cable Connections and Ground Tie Point

2-7

#### INTERFACE REQUIREMENTS

### Logic Interface

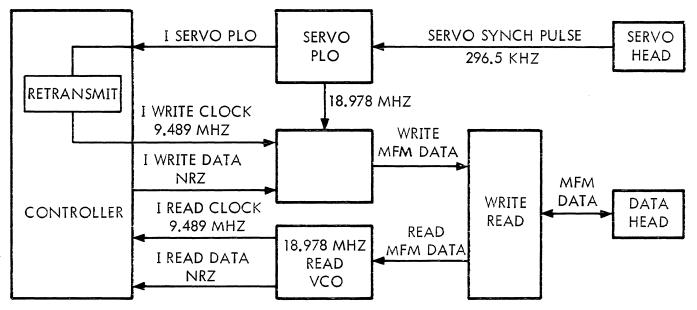

All input and output signals are digital and are received and transmitted differentially through the data and signal cables. Industry standard 75110 transmitters are required. Differential receivers with at least 100MV sensitivity and ±3V common mode capability are to be used (±25MV for I OPNCBLDET signal).

Signal polarity convention for differential signals is defined so that if "SIGNAL" is more positive than "SIGNAL/", the line is considered to be active unless otherwise specified.

#### Cabling

Three cables are required: the AC power cable, the data cable, and the signal cable. The AC power cable is supplied as part of the drive.

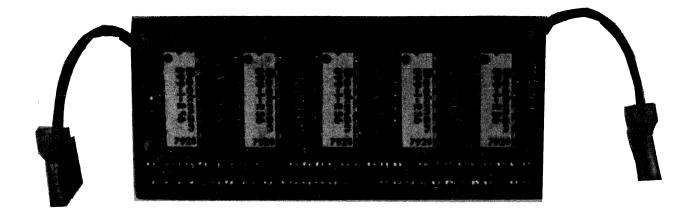

### 1. Data Cable

The data cable is a 26-conductor shielded, flat cable and must be connected directly to the controller. The maximum permissible length for the data cable is 20 feet (6 m). The cable's characteristics are;

| Impedance:   | <pre>130 ± 15 ohm, conductor to<br/>adjacent conductor</pre> |  |  |  |  |

|--------------|--------------------------------------------------------------|--|--|--|--|

|              | 65 ohms nominal, conductor to ground.                        |  |  |  |  |

| Propagation: | <pre>1.7 nanoseconds per foot,<br/>nominal</pre>             |  |  |  |  |

| Capacitance: | 29 pfd per foot, conductor<br>to ground, nominal             |  |  |  |  |

# 2. Signal Cable

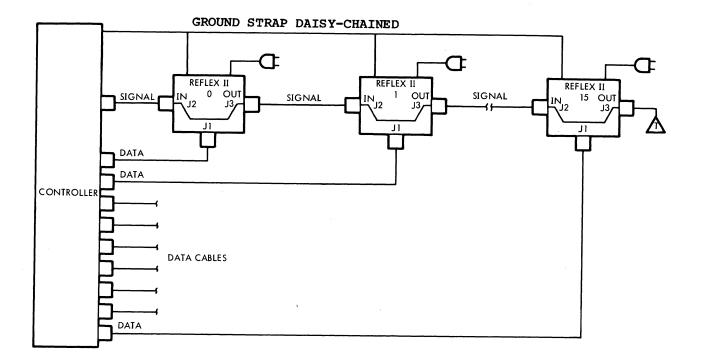

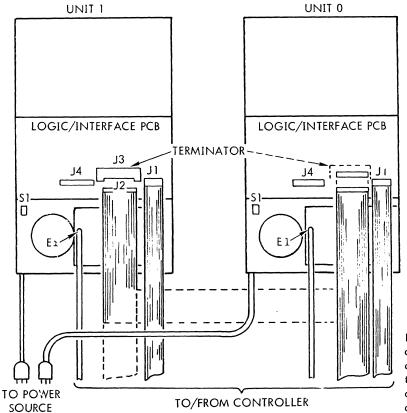

The signal cable is a 60-conductor, 30-twisted pair, flat cable. This cable may connect either directly to the controller or as a daisy-chain configuration to the controller (see Figure 2-7). The configurations shown in Figure 2-7 are for possible OEM use only. Figure 2-7A shows the only acceptable configuration for

TERMINATOR

Figure 2-7. Daisy-Chain (top) and Star Configuration (bottom), For possible OEM use ONLY.

Figure 2-7A. Reality System Daisy-Chain Configuration

use in a Reality System. For a daisy-chain configuration, there is a requirement for the controller to have on driver (transmitter) for each four drives for the I OPNCBLDET line. In either configuration, the signal cable may not exceed 50 feet total aggregated length from controller to terminator. The cable's characteristics are:

| Impedance:   | 100 +10 ohm between conductors<br>of same pair           |

|--------------|----------------------------------------------------------|

| Propagation: | 1.7 nanoseconds per foot,<br>nominal                     |

| Capacitance: | 22 pfd per foot between conductors of same pair, nominal |

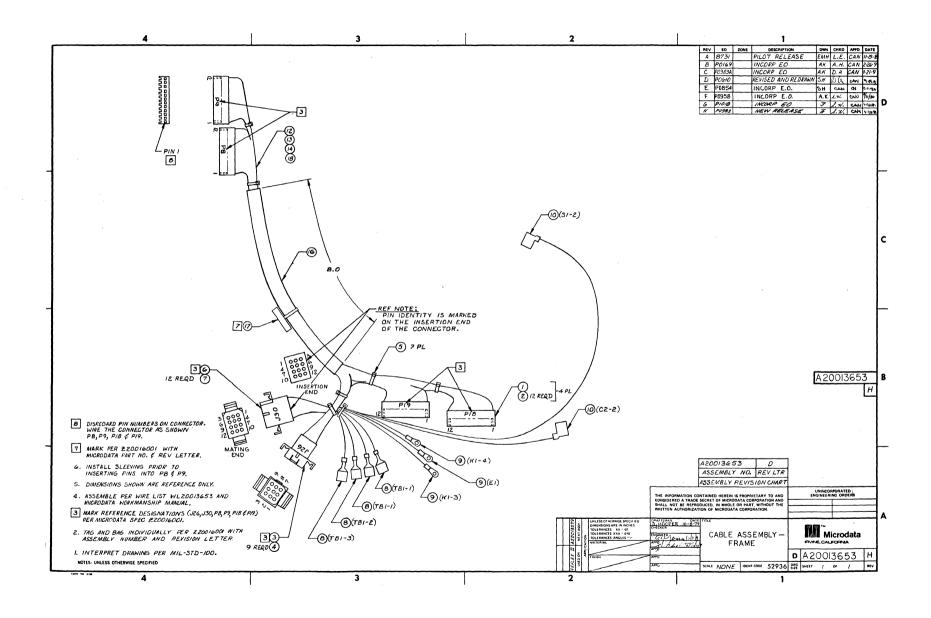

# 3. Frame Ground Cable

A ground cable must be connected to the drive for connecting frame ground to earth ground.

# 4. Available Cables

Cables available for cabling purposes are as follows:

| Signa | al Cable - 60 Conductor |               |   |

|-------|-------------------------|---------------|---|

|       | Controller to Drive     | A20013307-xxx | * |

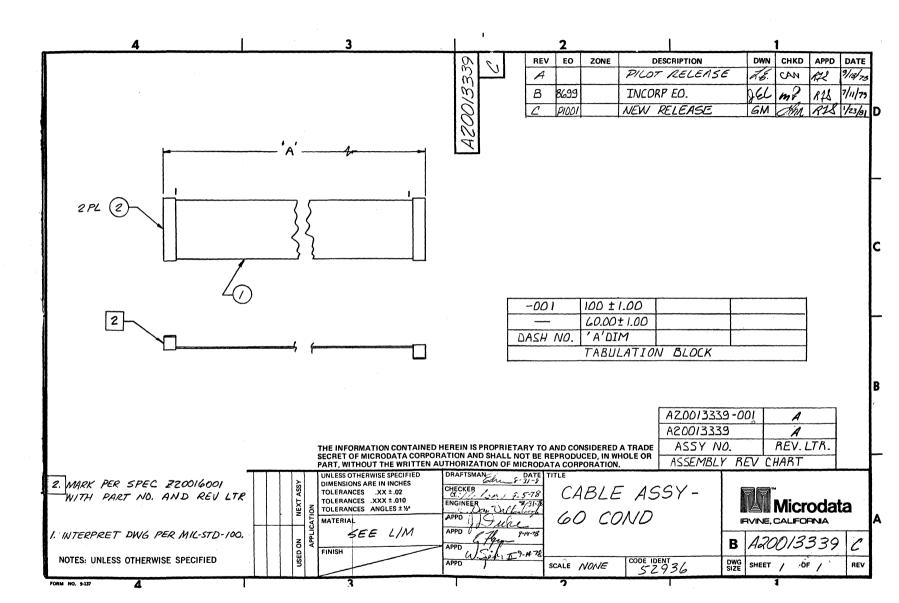

|       | Drive to Drive          | A20013339-xxx | * |

| Data  | Cable - 26 Conductor    | A20000979-xxx | * |

\* The dash number controls cable length, -001 is standard.

#### 5. Connector Jacks

For available lengths, see the drawing for the applicable cable in Section 6. Connector jacks for cabling are as follows:

| Connector     | Reference                   |

|---------------|-----------------------------|

| Signal J2, J3 | AMP 3-87227-0 or equivalent |

| Data Jl       | AMP 1-87227-3 or equivalent |

# 6. Connector Orientation

The connector pin orientation in the drive is shown in Figure 2-8. The connector locations are shown in Figure 2-6.

Figure 2-8. Connector Pin Orientation

# Signal Cable Descriptions

The signal cable consists of 27 signals. Each signal is made up of two wires. For installations using more than one Reflex II drive, the signal cables may be daisy-chained or starcabled (see Figure 2-7).

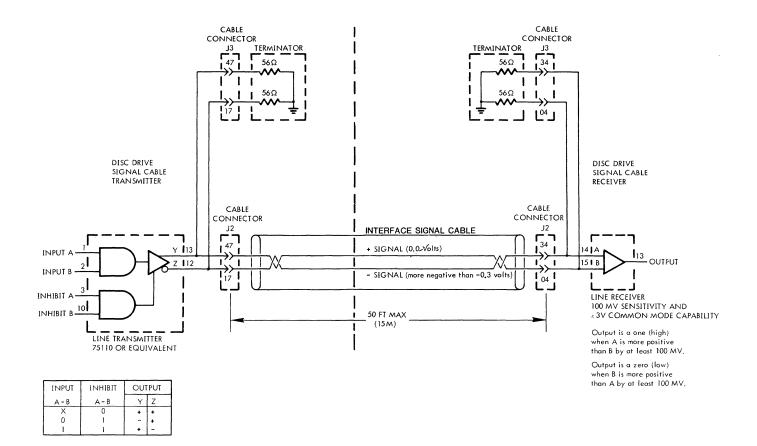

### 1. Pin Assignments

The signal cable signal listing and pin assignments are shown in Figure 2-9. The arrow indicates the transmitted direction. The pin number assignments are shown for the signal pair with the "/" used to describe polarity convention. The prefix "I" is used to indicate that the signal is at the interface.

| CONTROLLER | SIGNAL          | DIRECTION | PIN | /PIN | REFLEX II |

|------------|-----------------|-----------|-----|------|-----------|

|            | I UNITSEL TAG   |           | 52  | 22   |           |

|            | I UNITSEL BUS O |           | 53  | 23   |           |

|            | I UNITSEL BUS 1 |           | 54  | 24   |           |

|            | I UNITSEL BUS 2 |           | 5ó  | 26   |           |

|            | I UNITSEL BUS 3 |           | 57  | 27   |           |

|            | I OPNCBLDET     |           | 44  | 14   |           |

|            | I SET CYL TAG   |           | 31  | 01   |           |

|            | I SET HD TAG    | Ś         | 32  | 02   |           |

|            | I CONTROL TAG   |           | 33  | 03   |           |

|            | I BUS O         |           | 34  | 04   |           |

|            | I BUS 1         |           | 35  | 05   |           |

|            | I BUS 2         |           | 36  | 06   |           |

|            | I BUS 3         |           | 37  | 07   |           |

|            | I BUS 4         |           | 38  | 08   |           |

|            | I BUS 5         |           | 39  | 09   |           |

|            | I BUS 6         |           | 40  | 10   |           |

|            | I BUS 7         |           | 41  | 11   |           |

|            | I BUS 8         |           | 42  | 12   |           |

|            | I BUS 9         |           | 43  | 13   |           |

|            | I FAULT         |           | 45  | 15   |           |

|            | I SEEK ERROR    |           | 46  | 16   |           |

|            | I ON CYL        | 4         | 47  | 17   |           |

|            | I RDY           |           | 49  | 19   |           |

|            | I INDEX         |           | 48  | 18   |           |

|            | I SECTOR        |           | 55  | 25   |           |

|            | I WR PROTD      |           | 58  | 28   |           |

|            | RESERVED        |           | 59  | 29   |           |

|            | RESERVED        |           | 51  | 21   |           |

|            | RESERVED        |           | 50  | 20   |           |

|            | I CONFIGURATION | <b></b>   | 60  | 30   |           |

|            |                 |           |     |      |           |

|            |                 |           |     |      |           |

|            | J               |           |     | L    |           |

# 2. Signal Cable Definitions

The signal cable signals break into three groups. These groups provide selection, operation, and status, with operation breaking into address and control functions.

# a. Open Cable

The first signal necessary is I OPNCBLDET. This signal must be inactive (cable connected) to allow selection, which in turn allows the other functions to work. I OPNCBLDET active indicates the signal cable is not connected or a controller power failure. This signal is active when its "/" term is more positive than its other side. This term active will retract the heads, inhibit writing, and disable all signal cable functions.

### b. Drive Selection

With I OPNCBLDET inactive, selection is allowed. Selection is accomplished by four bus lines (I UNITSEL BUS 0-3) and one tag line (I UNITSEL TAG). Selection occurs when the unit select bus lines are equal to the unit select switches, when the unit select tag line becomes active. The unit select bus lines are weighed so that bus 0 is the least significant bit and bus 3 is the most significant bit. The unit select switches are located on the logic/interface board, in the dip switch package S1.

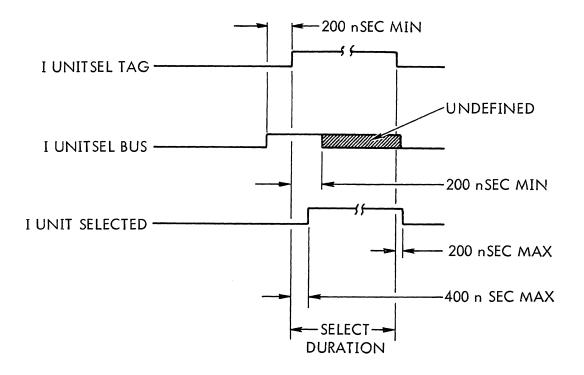

The unit select bus lines must be active at least 200 nanoseconds before the unit select tag line becomes active. If the binary address agrees with the unit select switches, UNIT SELECTED will become active 400 nanoseconds later. It will remain active for 200 nanoseconds beyond the unit select tag remaining active. I UNITSEL TAG must remain active for the duration of selection (see Figure 2-10).

Figure 2-10. Drive Selection

2-13

### c. Operation Commands

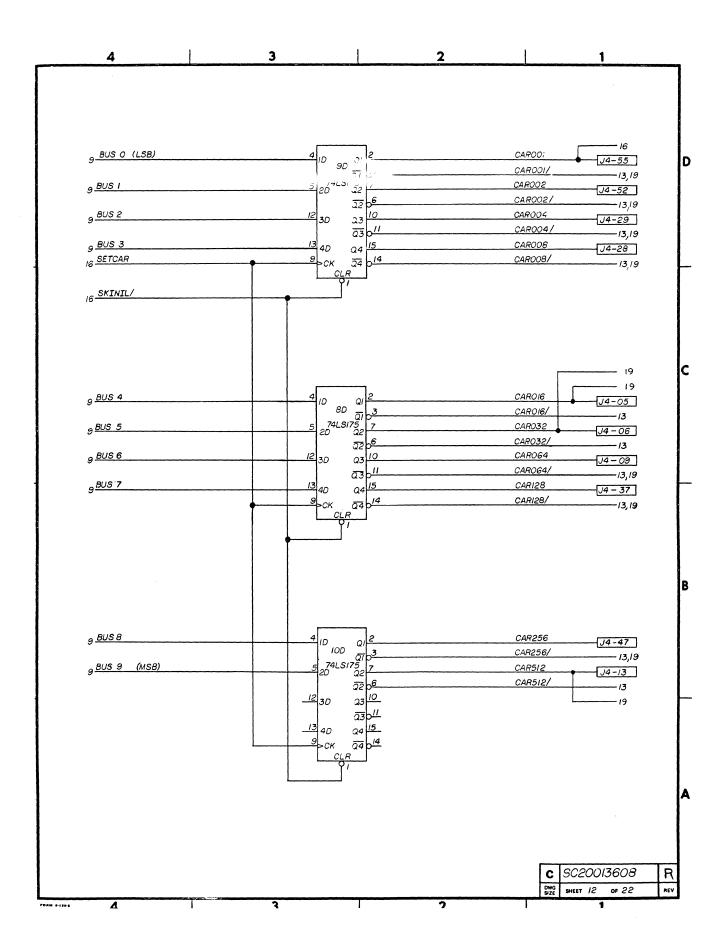

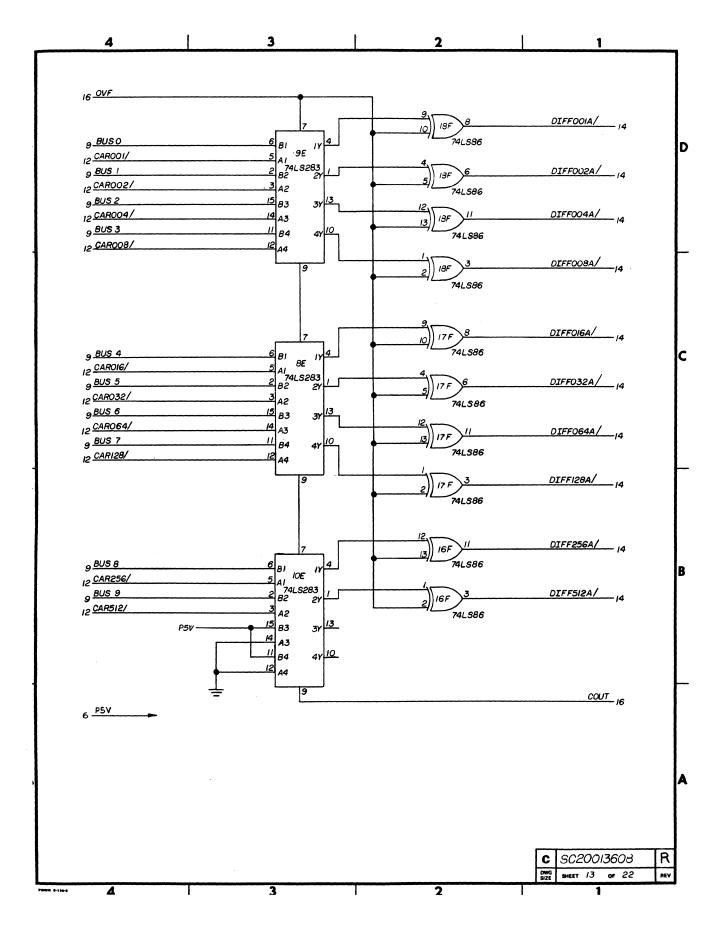

The operation group of signals breaks into address and control functions which are transferred on 10 bus lines and decoded with 3 tag lines as shown in Table 2-3.

#### TABLE 2-3

|                                                                | I SET CYL TAG  | I SET HD TAG    | I CONTROL TAG  |  |  |

|----------------------------------------------------------------|----------------|-----------------|----------------|--|--|

| I BUS O                                                        | CAR 1          | HAR 1           | WRT            |  |  |

| I BUS 1                                                        | CAR 2          | HAR 2           | READ           |  |  |

| I BUS 2                                                        | CAR 4          | HAR 4           | OFFSET FWD     |  |  |

| I BUS 3                                                        | CAR 8          | HAR 8           | OFFSET REV     |  |  |

| I BUS 4                                                        | CAR 16         | *HAR 16         | <b>R/FAULT</b> |  |  |

| I BUS 5                                                        | CAR 32         | *HAR 32         | -              |  |  |

| I BUS 6                                                        | CAR 64         |                 | RESTORE        |  |  |

| I BUS 7                                                        | CAR 128        | *FXHDSEL        | DSERLY         |  |  |

| I BUS 8                                                        | CAR 256        |                 | DSLATE         |  |  |

| I BUS 9                                                        | CAR 512        |                 | ~~             |  |  |

| *Required                                                      | for fixed head | g per track opt | ion            |  |  |

| CAR = Cylinder Address Register<br>HAR = Head Address Register |                |                 |                |  |  |

**OPERATION SIGNALS**

I SET CYL TAG -- When active, the bus lines are decoded as the next cylinder the servo is to seek. The trailing edge of the signal starts the seek. If I SET CYL TAG is issued while ON CYL or RDY are not active, a seek error will occur. The seek error may be cleared by doing a restore command. The timing requirements are shown in Figure 2-11.

Figure 2-11. Set Cylinder Timing

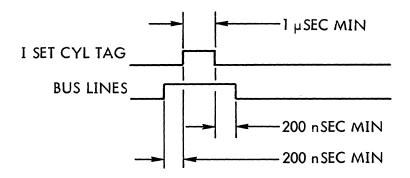

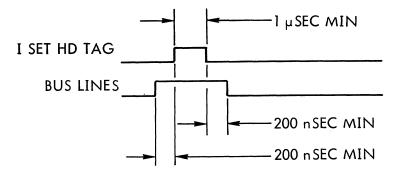

I SET HD TAG -- When active, bus lines 0-3 are decoded as the next moving head to be selected. With the fixed head-per-track option present and with the fixed head select signal active, bus lines 0-5 are decoded as the next fixed head to be selected. The timing requirements are shown in Figure 2-12.

Figure 2-12. Set Head Timing

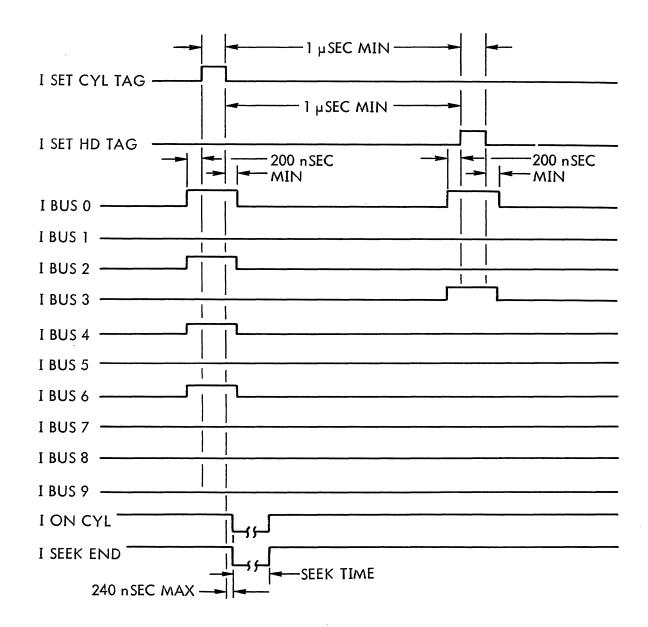

I SET HD TAG must not become active earlier than 1  $\mu$ second after the I SET CYL TAG becomes inactive. The head selection register is reset by issuing a restore command, or cycling power on-off-on, or by issuing I SET HD TAG with the buses not active.

Typical timing for the I SET CYL TAG and I SET HD TAG lines are shown in Figure 2-13, where the next cylinder address is 85 and the next head address is 9.

2-15

Figure 2-13. Set Cylinder and Set Head Timing Relationship I CONTROL TAG -- When active, the bus lines are decoded as commands. The bus lines are decoded by this tag line as follows:

I BUS 0 = Write.

The WRT command enables the writing function for the time that I CONTROL TAG and I BUS 0 are active (see Figure 2-14).

Figure 2-14. Write Command Timing

I BUS 1 = Read.

The READ command enables the read function for the time that I CONTROL TAG and I BUS 1 are each active (see Figure 2-15).

Figure 2-15. Read Command Timing

I BUS 2 = Offset forward I BUS 3 = Offset reverse

The OFFSET FWD and OFFSET REV commands enable track offset for the duration of time that I CONTROL TAG and either I BUS 2 for forward offset or I BUS 3 for reverse offset are active. Forward is toward the spindle with respect to its normal track position. These signals are an aid in recovering marginal data and offset the track position +200 microinches.

The time for the servo to move will not exceed 2.5 milliseconds for:

Normal track location to offset Offset to normal track location Offset forward to offset reverse Offset reverse to offset forward When either OFFSET FWD or OFFSET REV are issued, both I ON CYL and I SEEK END shall become inactive for 3.1 +0.6 milliseconds. The I ON CYL and I SEEK END signals will become inactive within 245 nanoseconds of either the OFFSET FWD or OFFSET REV commands becoming active (see Figure 2-16 for timing).

I BUS 4 = Fault reset.

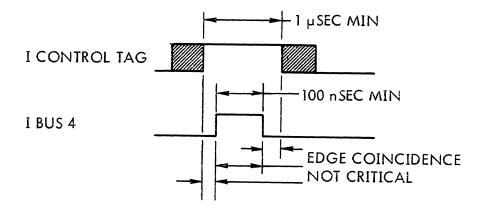

The R/FAULT command clears all fault conditions that do not have active inputs. If there are no existing faults, the I FAULT signal will become inactive. While CONTROL TAG must be active for at least 1  $\mu$ second, BUS 4 only needs to be active for a minimum of 100 nanoseconds (see Figure 2-17).

Figure 2-17. Reset Fault Command Timing

I BUS 6 = Restore

The RESTORE command causes the drive servo to seek to cylinder 000, resets the head address register to 00 and resets any seek error conditions. I BUS 6 shall be active at least 250 nanoseconds, but not more than 1 millisecond (see Figure 2-18).

Figure 2-18. Restore Command Timing

The RESTORE seek time is less than 1 second.

I BUS 7 = Data Strobe Early

I BUS 8 = Data Strobe Late

The DSERLY and DSLATE commands enable the data strobe to shift in time from nominal. Early shifts the strobe 5 nanoseconds earlier than normal and late shifts the strobe 5 nanoseconds later than normal. These functions remain active for the duration of I CONTROL TAG and either I BUS 7 or I BUS 8 being active. The data strobe returns to nominal when neither of these functions are active. These signals are an aid in recovering marginal data that has become marginal due to peak shifting.

d. Status Lines

There are eight status signals; however, four of the status signals (FAULT, SEEK ERROR, ON CYL, and RDY) have alternate definitions, depending on the state of I CONFIGURATION.

I CONFIGURATION = Request Status Alternate Definitions

The I CONFIGURATION command enables the I SEEK ERROR and I FAULT signals to transmit the Reflex II Model configuration. It also enables the IRDY and IONCYCL signals to transmit the Reflex II fixed head configuration to the controller as determined by the indicated Reflex II switch settings on the logic/interface board. Table 2-4 presents the switch settings and definitions.

#### TABLE 2-4

|                           | <u>tch</u><br>51-7 | Reflex Model             | I SEEK ERROR                             | I FAULT                                  |

|---------------------------|--------------------|--------------------------|------------------------------------------|------------------------------------------|

| 0<br>0<br>1<br>1          | 0<br>1<br>0<br>1   | A<br>B<br>C<br>D         | inactive<br>inactive<br>active<br>active | inactive<br>active<br>inactive<br>active |

| <u>Swi</u><br><u>S1-8</u> | tch                | Number of<br>Fixed Heads | I RDY                                    | I ON CYL                                 |

| 1<br>0                    |                    | 0<br>60                  | inactive<br>active                       | inactive<br>inactive                     |

|                           |                    |                          | switch open (off<br>switch closed (o     |                                          |

### I CONFIGURATION STATUS

I CONFIGURATION is disabled when switch S1-5 is closed (on).

I FAULT -- This signal indicates that at least one of the following error conditions in the drive is active:

- (1) Data head circuit unsafe monitor active due to any one or more of the following faults:

- (a) Write command active and head coil open or shortened.

- (b) Write command active and no head selected.

- (c) Write command active and write current level not correct.

- (d) Write command inactive and write current present.

- (e) Write command active and write current transitions missing.

- (f) Multiple heads selected.

- (2) DC voltage unsafe.

- (3) Illegal head selected.

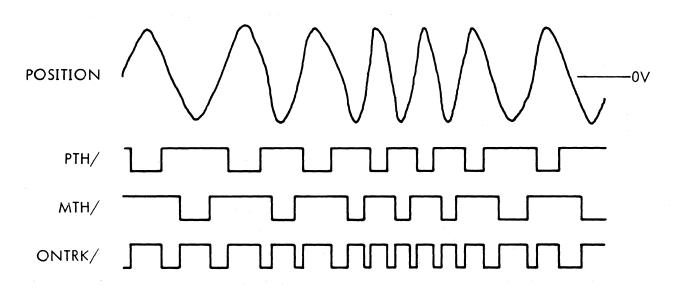

- (4) Write command active and read command active.