# REFERENCE MANUAL FOR THE PHOENIX DIGITAL COMPUTER

**15 NOVEMBER 1963**

| Technic | cal Me | morandum | TM –              | 3870   |

|---------|--------|----------|-------------------|--------|

| Sheet   | 1      | of       | 85                | Sheets |

| Contrac | t No.  | AF 19(   | 628) <del>-</del> | 2390   |

REFERENCE MANUAL FOR THE PHOENIX DIGITAL COMPUTER (Project 508.0)

Distribution List

D-13 Staff

D-13

15 November 1963

This Technical Memorandum is prepared for Corporation use and for controlled external distribution. Reproduction or further dissemination is not authorized. It has not been reviewed by Office of Security Review, Department of Defense, and therefore is not for public release.

#### ABSTRACT

This document describes the structure and operation of PHOENIX (nee FIFI), a digital computer being designed and built by MITRE Department D-13 for SDL.

## TABLE OF CONTENTS

| SECTION     | TITLE                               | PAGE        |

|-------------|-------------------------------------|-------------|

| 0           | Introduction                        | 1           |

| CHAPTER I   | CENTRAL PROCESSOR                   |             |

| 1           | Nomenclature                        | 5           |

| 2           | Live Registers                      | 9           |

| 3           | Timing                              | 21          |

| 4           | The Instruction Cycle               | 33          |

| 5           | Protected Status                    | 37          |

| 6           | Interrupts and Traps                | 38          |

| 7           | Instruction Word Formats            | 41          |

| 8           | Effective Addresses                 | 43          |

| 9           | Description of PHOENIX Instructions | 45          |

| 10          | PHOENIX Initialization              | 107         |

| CHAPTER II  | I/O                                 |             |

| 11          | Definitions                         | 109         |

| 12          | Introduction                        | 109         |

| 13          | I/O Operations                      | 110         |

| 14          | Channel and Device Operation        | 113         |

| 15          | TCU and Tape Units                  | 114         |

| 16          | I/O Interrupts                      | 117         |

| 17          | I/O Control Words and Flowcharts    | 119         |

| CHAPTER III | THE LOW SPEED BUFFER                |             |

| 18          | General Description                 | 137         |

| 19          | Status Indicators                   | 137         |

| 20          | Output Device Control Word          | 142         |

| 21          | Input Device Control Word           | 143         |

| 22          | Interrupts                          | 145         |

| 23          | LSB Operations                      | 147         |

| APPENDICES  |                                     |             |

| Α           | Instruction Summary                 | A-1         |

| В           | Distribution List                   | B <b>-1</b> |

|             |                                     |             |

### LIST OF ILLUSTRATIONS

| Figure or Ta | able No. Dra                                                                 | wing No, | Title                                                                     | Page No. |

|--------------|------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------|----------|

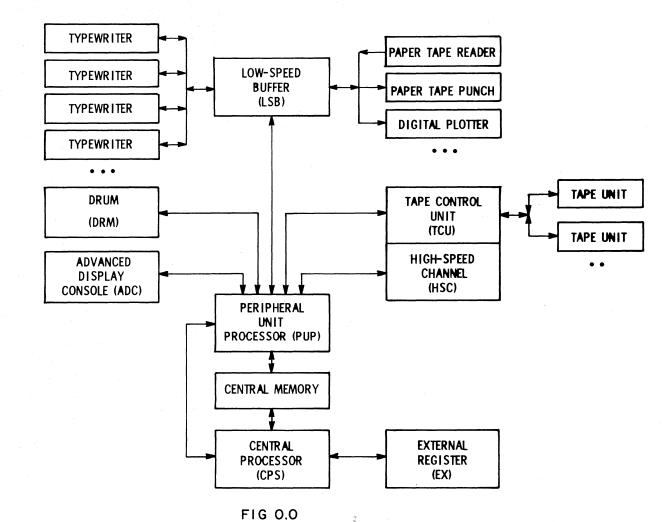

| 0.0          | 18                                                                           | - 12,389 | Organization of the PHOENIX<br>Computer                                   | 0        |

| 3.4          |                                                                              | none     | Instruction Timing                                                        | 29       |

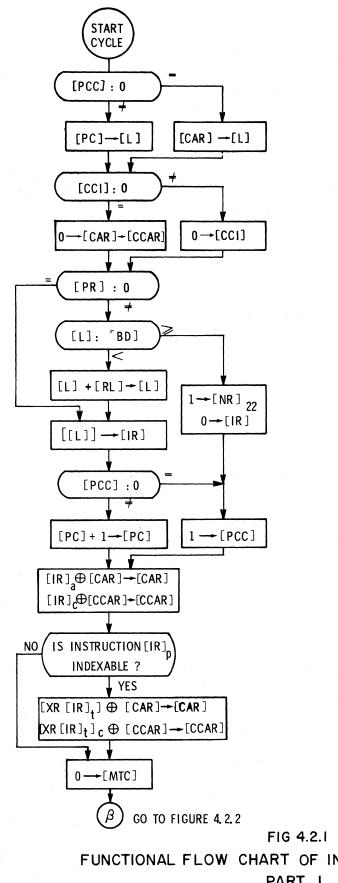

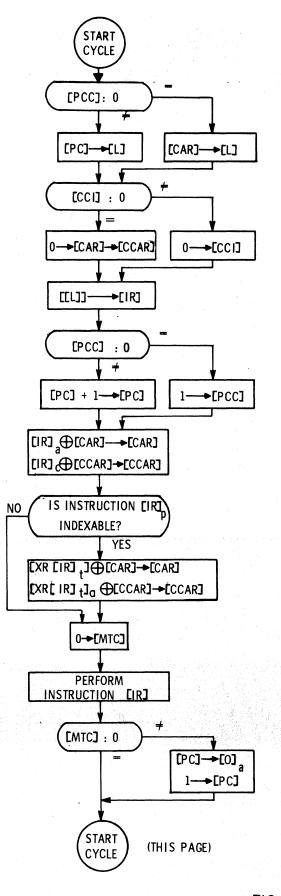

| 4.2.1        | L 1B                                                                         | - 12,380 | Functional Flowchart of<br>Instruction Cycle, Part 1                      | 34       |

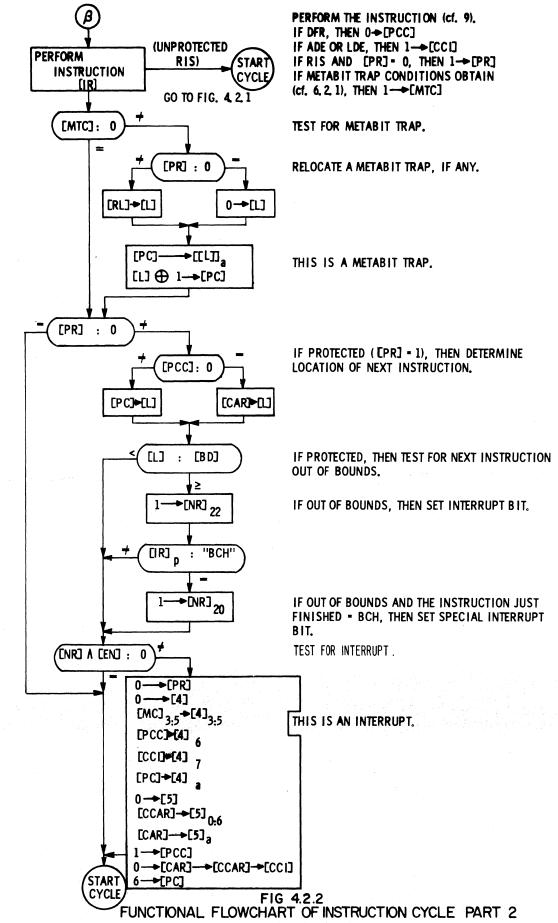

| 4.2.2        | 2 1B                                                                         | - 12,388 | Functional Flowchart of<br>Instruction Cycle, Part 2                      | 35       |

| 4.2.3        | 3 1B                                                                         | - 12,381 | Simplified Functional Instruc-<br>tion Cycle for the "User"<br>Programmer | - 36     |

| 9.46.        | 2                                                                            | none     | I I OBI AMMEI                                                             | 99       |

| 9.46.        |                                                                              | none     |                                                                           | 100      |

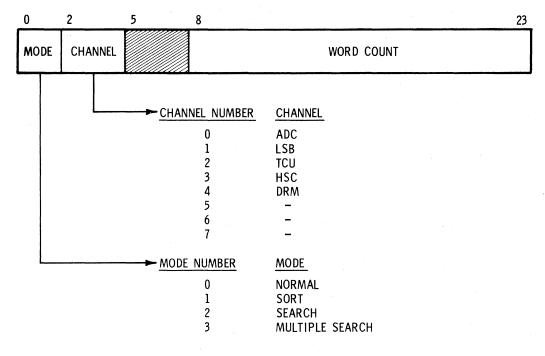

| 17.2         |                                                                              | - 12,377 | CW1 I/O Control Word 1                                                    | 122      |

| 17.3         |                                                                              | - 12,375 | I/O Control Word 2 for ADC                                                | 123      |

| 17.4         |                                                                              | - 12,374 | I/O Control Word 2 for LSB                                                | 124      |

| 17.5         | 18                                                                           | - 12,373 | I/O Control Word 2 for TCU                                                | 125      |

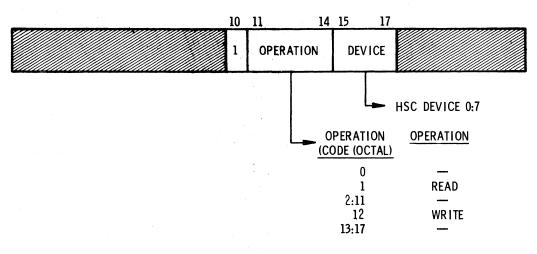

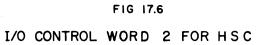

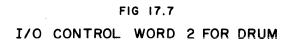

| 17.6         | 18                                                                           | - 12,372 | I/O Control Word 2 for HSC                                                | 126      |

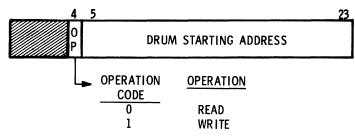

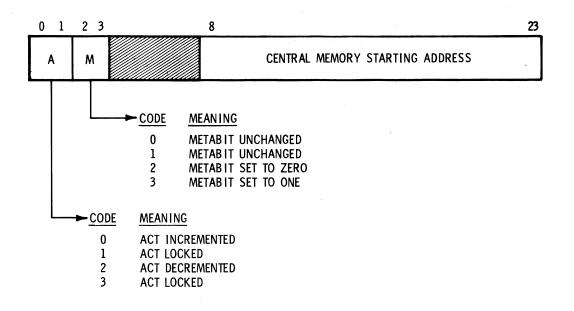

| 17.7         | 1B                                                                           | - 12,371 | I/O Control Word 2 for Drum                                               | 127      |

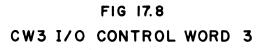

| 17.8         | 1B                                                                           | - 12,376 | CW3 I/O Control Word 3                                                    | 128      |

| 17.9         | 1B                                                                           | - 12,378 | SIO                                                                       | 129      |

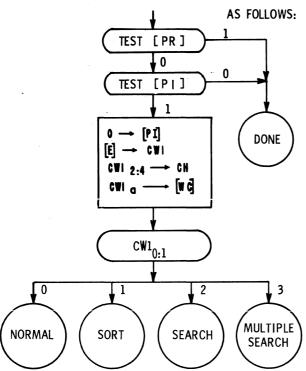

| 17,10        | 18                                                                           | - 12,384 | Normal (Start)                                                            | 130      |

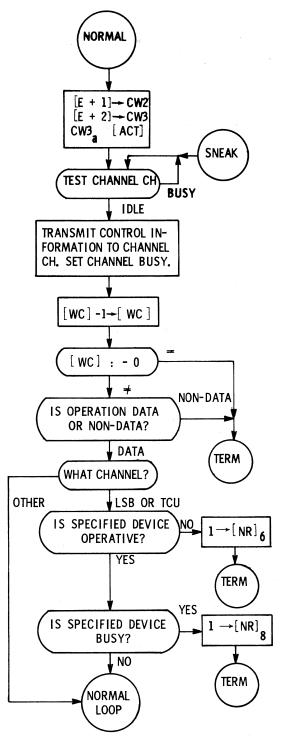

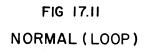

| 17.11        | 18                                                                           | - 12,383 | Normal (Loop)                                                             | 131      |

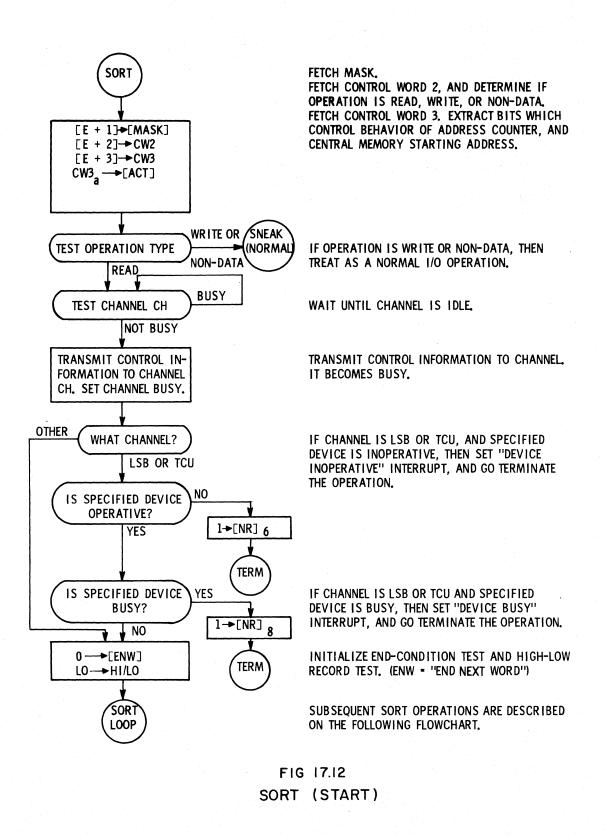

| 17.12        | 1B                                                                           | - 12,385 | Sort (Start)                                                              | 132      |

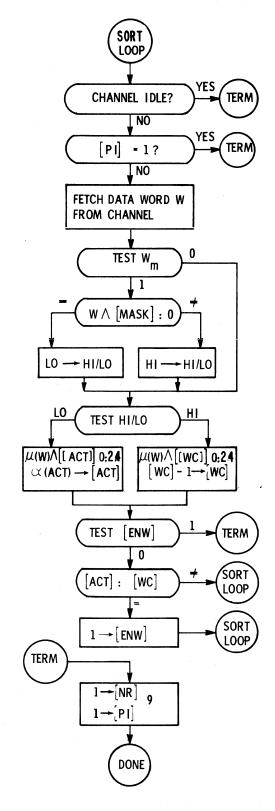

| 17.13        | 1B                                                                           | - 12,387 | Sort (Loop)                                                               | 133      |

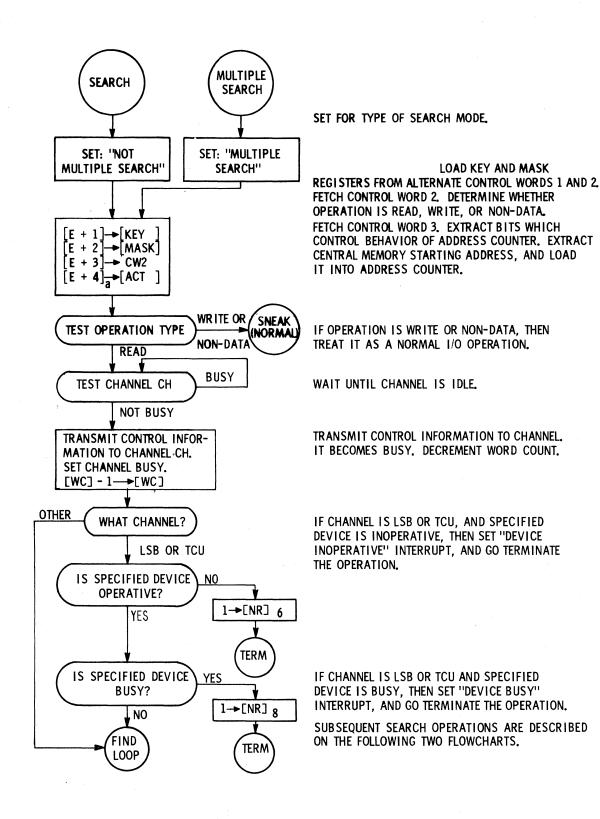

| 17.14        | 18                                                                           | - 12,386 | Search (Start)                                                            | 134      |

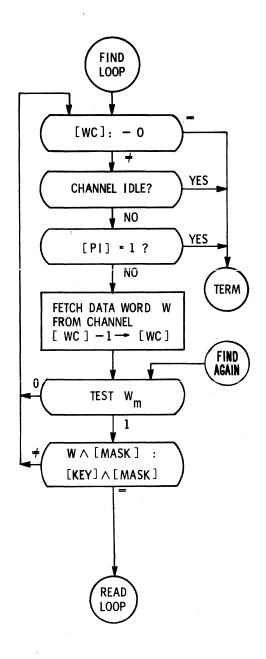

| 17.15        | 18                                                                           | - 12,379 | Search (Find Loop)                                                        | 135      |

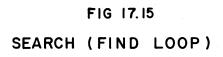

| 17.16        | 18                                                                           | - 12,382 | Search (Read Loop)                                                        | 136      |

| 19.1         |                                                                              | none     | Typewriter Status                                                         | 140      |

| 23.8         |                                                                              | none     | LSB Operations                                                            | 152      |

| A-1 (1       | L)                                                                           | none     |                                                                           | A-2      |

| A-1 (2       |                                                                              | none     |                                                                           | A-3      |

| A-2 (1       |                                                                              | none     |                                                                           | A-4      |

| A-2 (2       |                                                                              | none     |                                                                           | A-5      |

|              | an an an an taon an Arra.<br>Na manganan an |          |                                                                           |          |

#### PREFACE

This manual is intended as a <u>reference</u> manual for the PHOENIX digital computer; it is not a primer, nor a system manual. Logically, the structure of the manual is characterized by the programming terms: "multiple pass" and "recursive."

An attempt has been made to <u>exactly</u> specify the functional characteristics of PHOENIX, and to provide enough information to allow even pathological situations to be analyzed.

The format is chosen to facilitate corrections and additions, which will be issued as needed.

Suggestions for improving this manual will be appreciated.

IB-12,389

ORGANIZATION OF THE PHOENIX COMPUTER

#### 0.0 INTRODUCTION

PHOENIX is a binary single address digital computer which performs instructions at an average rate of 500,000 instructions per second. The overall organization of the machine is shown in Figure 0.0.

#### 0.1 Memory

The main memory consists of 4 memory units (A, B, C, and D) of 16,384 26-bit words each. Each word has, in addition to its normal 24 data bits, an associated metabit which is not affected by normal manipulation, and a parity bit used for internal error checking. These 4 memories are independently accessible, providing for the overlap of instructions, data, and I/O references (cf. 3.0). Memory is assigned to user programs in segments consisting of integral multiples of 4096 words whose base or starting address is effectively 0. The relocation and limiting of the space available to user programs is handled automatically by means of the boundary and relocation registers.

#### 0.2 Central Processor (CPS)

The central processor has a repertoire of 54 basic instructions, several of which sub-divide into whole classes of subsidiary instructions. The entire main memory is addressable by these instructions. Address modification and indexing may be performed. There are 5 index registers <u>per se</u>; in addition, the program counter and the "address" portion of the accumulator are addressable as index registers; also there is an index whose contents are always zero, making a total of 8 "index" registers.

#### TM-3870

The arithmetic unit performs l's complement, fixed-point operations.

A flexible interrupt system provides for interrupting the main stream of instructions to honor a variety of I/O demand and error conditions.

To facilitate time sharing, facilities are built into the machine which automatically relocate the user program, limit the amount of memory available to the user program, and prevent the user program from directly affecting I/O operations.

The external register (EX) provides a convenient and flexible channel for non-overlapped input/output operations between CPS and non-standard external devices.

The basic machine cycle is 1.6 microseconds.

#### 0.3 Input-Output

I/O operations are performed in parallel with program operations by PUP (Peripheral Unit Processor) which mediates data transfers between one of 5 channels and main memory.

PUP operations are available to facilitate searching for records and sorting records, on the basis of key words or portions of a word.

The ADC (Advanced Display Console) is a flexible visual display device with internal storage and response capabilities.

The LSB (Low Speed Buffer) controls the transmission of I/O information between various low-speed devices and an external memory. Thirty-two devices, including 16 typewriters, may be connected to LSB. Initially, there will be 4 typewriters, a paper tape reader, a paper tape punch, and a digital incremental recorder. The TCU (Tape Control Unit) controls I/O transmission to and from a maximum of 8 magnetic tape drives (TU). Four CDC 607 interfaces are provided which will handle data at rates up to 30,000 24-bit words per second. Four IBM 729-IV interfaces are provided which will handle data at rates up to 15,625 24-bit words per second. Initially, there will be two CDC 607 tape drives.

The HSC (High Speed Channel) provides for transmission of information on a character basis between external devices and PHOENIX at variable rates up to 333,000 6-bit characters per second (equivalent to 83,250 24-bit words per second).

The DRM (Drum) has a capacity of 278,528 words (34 sectors of 8,192 words each), which can be transmitted to and from CPS memory at the rate of 491,520 words per second.

## TM-3870

BLANK PAGE

## 4.

#### CHAPTER I -- CENTRAL PROCESSOR

#### 1 NOMENCLATURE

#### 1.1 Quantities, Bits

Let  $\underline{x}$  be an n-bit quantity; that is, an integer in the range 0 to 2<sup>n</sup>-1 inclusive. It is well-known that there exist unique integers  $x_k$  (k = 0,..., n-1), each  $x_k$  = 0 or 1, such that  $x = \sum_{k=0}^{n-1} x_k \times 2^{n-1-k}$ . We call this  $x_k$  the <u>k-th bit of x</u>.

#### 1.2 Bytes

If <u>x</u> is an n-bit quantity, and <u>i</u> and <u>j</u> are integers such that  $0 \le i \le j \le n-1$ , then we define the <u>byte</u>  $x_{i:j} = \sum_{k=i}^{j} x_k \times 2^{j-k}$ .

We also define:

| $\mathbf{x}_{\mathbf{s}} \equiv \mathbf{x}_{0}$ | (sign)    |

|-------------------------------------------------|-----------|

| $x_a \equiv x_{8;23}$                           | (address) |

| $x_t \equiv x_{0:2}$                            | (tag)     |

| $x_p \equiv x_{3:7}$                            | (opcode)  |

| $x_m \equiv x_{24}$                             | (metabit) |

| $x_c \equiv x_{n-7:n-1}$                        | (count)   |

#### 1.3 Registers and their contents

We consider the computer to be a collection of registers, each of which contains a quantity. We describe the operation of the computer in terms of how the contents of these registers change with time. Given a register  $\alpha$ , we use the symbol [ $\alpha$ ] to denote the contents of  $\alpha$ . We speak of  $\alpha$  as an n-bit register if [ $\alpha$ ] is at most an n-bit quantity.

#### TM-3870

1.3.1 <u>Memory registers</u>

A certain set of registers (CPS memory registers) are named by <u>quantities</u>. Given a register  $\alpha$ , where  $\alpha$  is a quantity, then by [ $\alpha$ ] we mean [ $\alpha$ ]<sub>0:23</sub>.

1.3.2 Live registers

Registers which are not CPS memory registers are termed "live registers" and are referred to by symbolic names, rather than by quantities.

1.4 Replacement

" $x \rightarrow [\alpha]_{i:j}$ " means: "The quantity <u>x</u> replaces the contents of register  $\alpha$ , bits <u>i</u> to <u>j</u>, inclusive, the remainder of  $\alpha$  being left unchanged." More precisely, if  $\alpha$  is an n-bit register, then  $[\alpha]$  changes to:

$\sum_{k=0}^{i-1} \left[\alpha\right]_k \times 2^{n-1-k} + \sum_{k=i}^{j} x_{k-1} \times 2^{n-1-k} + \sum_{\substack{k=j+1 \\ k=j+1}}^{n-1} \left[\alpha\right]_k \times 2^{n-1-k}.$

6.

#### 1.5 Operations

Let  $\underline{x}$  and  $\underline{y}$  be quantities of exactly  $\underline{n}$  bits each. We define: 1.5.1 x + y = x + y if  $x + y < 2^{n}$  else  $x + y = x + y - 2^n$ 1.5.2 x  $\bigoplus_{n} y = x + y$  if  $x + y < 2^{n}$  else  $x \oplus_{n} y = x + y - (2^{n} - 1)$ 1.5.3  $x \lor y \equiv \sum_{k=0}^{n-1} \max(x_k, y_k) \times 2^{n-1-k}$ 1.5.4  $x \land y \equiv \sum_{k=0}^{n-1} \min(x_k, y_k) \propto 2^{n-1-k}$ 1.5.5  $x \neq y \equiv \sum_{k=0}^{n-1} (x_k + y_k) \times 2^{n-1-k}$ 1.5.6  $x - y = x + (2^n - y)$ 1.5.7  $x \in y = x \oplus (2^n - y - 1)$  $1.5.8 \overline{x} = 2^{n} - 1 - x$ 1.5.9 abs x = x if  $x < 2^{n-1}$  else abs  $x = \overline{x}$

1.6 Metabits

Words in CPS memory, LSB memory, and drum memory have a 25th bit called the <u>metabit</u> in addition to the normal 24 bits of the word. The metabit is a flag and is not used in normal computations or logical manipulations. The metabit of word W is designated by the notation  $W_m$ . A metabit may be set to 0 or 1 by an I/O operation and the instructions MMZ and MMN. A metabit may be sensed by the user-controlled <u>metabit</u> trap, the instructions SMZ and SMN, or by some I/O operations. TM-3870

#### 1.6.1 Special I/O metabit handling

Data coming from HSC or ADC always has a metabit of 0. When data is sent to a device connected to one of these channels, the metabit is ignored. Data sent to the TCU also has its metabits ignored. However, on an input from the TCU, the first word of every record has a metabit of 1 associated with it.

#### 1.7 Miscellaneous notation conventions

1.7.1 Where there is no possibility of ambiguity, we will elide the subscript specifying the number of bits involved in an arithmetic operation. If this subscript is unspecified, the size of the registers involved will be assumed. For example, we will write " [CAR] + [RL]" for "[CAR]  $+_{16}$  [RL]" since both CAR and RL are 16-bit registers.

1.7.2 Given a register  $\alpha$ , "step  $\alpha$ " means " $[\alpha] + 1 \rightarrow [\alpha]$ ". (Cf. 2.22)

1.7.3 The term "minus zero", also noted "-0", designates the n-bit quantity  $2^{n}$ -1.

8.

#### 2.0 LIVE REGISTERS

The operations of PHOENIX CPS (central processor) can be described in terms of its memory and the registers described in the following sections.

2.1 AC Accumulator (24 bits)

The AC is used in most instructions to hold operands and receive the results of arithmetic and logical operations.  $AC_2 \equiv XR6$

#### 2.2 ACT Address Counter (16 bits)

The ACT is used during I/O operations to determine CPS storage locations for I/O data. [ACT] can be read into [BR] by a PER when [PR]=0. 2.3 <u>BD</u> <u>Boundary Register</u> (16 bits)

This register determines the limits of memory space available to a user program when the computer is in protected status. The BD may be changed only by an LRB instruction.  $[BD]_{4.15} \equiv 0$ .

2.4 BR B-register (24 bits)

The BR is used as an operand register for several arithmetic and logical operations. It also receives the results of several arithmetic and logical operations. The BR is also used to hold a <u>mask</u> for some operations.

2.5 CA Combined Arithmetic Register (47 bits)

The CA has no existence independent of the AC and BR. It is used in some shifts and cycles, divide, multiply, and the double-length arithmetic operations.

$CA_{0:23} \equiv AC_{0:23}$  $CA_{24:46} \equiv BR_{1:23}$

- 10. TM-3870

- 2.6 CAR Central Address Register (16 bits)

The CAR is used in computing effective addresses. It is not directly addressable by the programmer.

2.7 CCAR Cycle and Shift Central Address Register (7 bits)

The CCAR is used for computing the effective address E for shifts and cycles. It is not directly addressable by the programmer.

2.8 CCI Clear CAR Inhibit (1 bit)

If [CCI] = 0, the CAR and CCAR are cleared after the current operation. If [CCI] = 1, the CAR and CCAR are not cleared. CCI is not addressable by the programmer.

2.9 CK Clock (24 bits)

The [CK] may be changed only by an SKM instruction while the CPS is in unprotected status. The [CK] is decremented at intervals of 5  $\mu$ sec,  $\pm$  .005  $\mu$ sec. When its contents are -0, the clock interrupt bit is set. More precisely, every 5  $\mu$ sec, the following sequence of events takes place:

- 1) If [CK] = 1, then  $-0 \rightarrow [CK]$  and  $1 \rightarrow [NR]_{21}$  and go to 4

- 2) If [CK] = 0, then  $2^{24} 2 \rightarrow [CK]$  and go to 4

- 3)  $[CK] 1 \rightarrow [CK]$

- 4) Done.

#### 2.10 EN Enable Register (24 bits)

The enable register acts as a mask for the NR (interrupt register). The [EN] may be changed only by an SKM instruction while the CPS is in unprotected status.  $[EN]_{20} \equiv 1$  and  $[EN]_{22} \equiv 1$ .

## 2.11 EX External Register (24 bits)

EX allows a program to communicate directly with devices external to PHOENIX without the mediation of PUP. The [EX] may be sensed or modified by a SKM instruction if either [PR] = 0, or [EXM] = 1. The sensing of [EX] automatically clears it. An external device suitably connected to EX can set or sense [EX] or any subset of its bits. The external interrupt bit  $[NR]_{13}$  can be set by a pulse generated by an external device. It is intended that this interrupt will be used to request that a program perform an action involving EX.

2.12 EXM EX Mode Control Register (1 bit)

2.13

This register controls the EX with respect to a SKM instruction while the CPS is in protected status. If [EXM] = 0, then [EX] cannot be sensed or changed by a SKM instruction in protected status. If [EXM] = 1, then [EX] can be sensed or changed by a SKM instruction in protected status. [EXM] may be modified only by certain PER instructions which, themselves, are operative only in unprotected status.

| LA | LSB Att | ention | and   | ADC   | <u>Regis</u> | ter | (24 | bits              | 3) |

|----|---------|--------|-------|-------|--------------|-----|-----|-------------------|----|

|    | 0       |        |       |       |              | 16  | 20  | 23                |    |

|    |         | LSB A  | Atter | ntion |              | ADC | XII | $\langle \rangle$ |    |

$[LA]_{0:15}$  are the attention status indicators for the 16 typewriter lines to the LSB.  $[LA]_{16\cdot19}$  are status bits for ADC.

Each bit is set by a pulse from LSB or ADC which also sets one of 3 indicators in NR:

12. TM-3870

| LA bit | Meaning                   | Interrupt bit |

|--------|---------------------------|---------------|

| 0:15   | Typewriter 0:15 attention | 16            |

| 16     | Not Storable              | 8             |

| 17     | Memory overflow           | 8             |

| 18     | Manual Input              | 11            |

| 19     | Display Area Change       | 11            |

[IA] may be changed by SKM in unprotected status

2.14 LB LSB Buffer Status Register (24 bits)

$[LB]_i = 1$  when the LSB memory area assigned to LSB input device  $\underline{i}$  has been filled.  $[LB]_{0:15}$  are for the 16 typewriters;  $[LB]_{16}$  is for the paper tape reader.

2.15 LE LSB Device Error Register (24 bits)

$[LE]_i = 1$  when a device error has occurred during a data transmission between LSB memory and device <u>i</u>, or during other LSB operations involving device <u>i</u>.

| [LE]0:15           | typewriters                  |

|--------------------|------------------------------|

| [LE] <sub>16</sub> | paper tape reader            |

| [LE] <sub>17</sub> | paper tape punch             |

| [le] <sub>18</sub> | digital incremental recorder |

[LE] may be changed through the use of SKM.

## 2.16 LI LSB Input Status Register (24 bits)

$[LI]_i = 1$  when LSB device <u>i</u> is in input status, i.e., when it is entering information into LSB memory.  $[LI]_{0:15}$  are for the 16 typewriters;  $[LI]_{16}$  is for the paper tape reader.

#### 2.17 LO LSB Output Status Register (24 bits)

$[LO]_i = 1$  when LSB device  $\underline{i}$  is in output status, i.e., when it is receiving information from LSB memory.  $[LO]_{0:15}$  are for the 16 type-writers;  $[LO]_{17}$  is for the paper tape punch;  $[LO]_{18}$  is for the digital incremental recorder.

2.18 <u>MC Miscellaneous CPS indicators</u> (24 bits)

$MC_3 \equiv VF$  (overflow indicator)

$MC_{L} \equiv VFP$  (permanent overflow indicator)

$[MC]_5$  is the metabit trap enable bit.

CONTRACTOR STATES AND A STATES

[MC] may be changed through the use of SKM.

| BitUse01PI (PUP idle indicator)2TI (TCU idle indicator)3456IOR parity error7PBR parity error8KEY parity error9MASK parity error10DSA parity error11APR parity error12Unexpected channel demand13Unexpected channel answer14PUP memory request error15ADC noisy16LSB noisy17TCU noisy18DRM noisy192021Step control error23Drum compare error                                                                                                                                                                                      | 2.19 <u>MP</u> | <u>Miscellaneous PUP Indicators</u> (24 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1PI (PUP idle indicator)2TI (TCU idle indicator)3456IOR parity error7PBR parity error8KEY parity error9MASK parity error10DSA parity error11APR parity error12Unexpected channel demand13Unexpected channel answer14PUP memory request error15ADC noisy16LSB noisy17TCU noisy18DRM noisy192021Step control error22Time pulse distribution error                                                                                                                                                                                  | <u>Bit</u>     | n en sente de la construction de la<br>La <mark>Use</mark> de la construction de<br>La construction de la construction de |

| <ul> <li>3</li> <li>4</li> <li>5</li> <li>6 IOR parity error</li> <li>7 PBR parity error</li> <li>8 KEY parity error</li> <li>9 MASK parity error</li> <li>10 DSA parity error</li> <li>11 APR parity error</li> <li>12 Unexpected channel demand</li> <li>13 Unexpected channel answer</li> <li>14 PUP memory request error</li> <li>15 ADC noisy</li> <li>16 LSB noisy</li> <li>17 TCU noisy</li> <li>18 DRM noisy</li> <li>19</li> <li>20</li> <li>21 Step control error</li> <li>22 Time pulse distribution error</li> </ul> | 0<br>1         | <br>PI (PUP idle indicator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>5</li> <li>6 IOR parity error</li> <li>7 PBR parity error</li> <li>8 KEY parity error</li> <li>9 MASK parity error</li> <li>10 DSA parity error</li> <li>11 APR parity error</li> <li>12 Unexpected channel demand</li> <li>13 Unexpected channel answer</li> <li>14 PUP memory request error</li> <li>15 ADC noisy</li> <li>16 LSB noisy</li> <li>17 TCU noisy</li> <li>18 DRM noisy</li> <li>19</li> <li>20</li> <li>21 Step control error</li> <li>22 Time pulse distribution error</li> </ul>                       | 3              | TI (TCU idle indicator)<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7 PBR parity error 8 KEY parity error 9 MASK parity error 10 DSA parity error 11 APR parity error 12 Unexpected channel demand 13 Unexpected channel answer 14 PUP memory request error 15 ADC noisy 16 LSB noisy 17 TCU noisy 18 DRM noisy 19 20 21 Step control error 22 Time pulse distribution error                                                                                                                                                                                                                         | 5              | <br><br>IOR parity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <pre>10 DSA parity error<br/>11 APR parity error<br/>12 Unexpected channel demand<br/>13 Unexpected channel answer<br/>14 PUP memory request error<br/>15 ADC noisy<br/>16 LSB noisy<br/>17 TCU noisy<br/>18 DRM noisy<br/>19<br/>20<br/>21 Step control error<br/>22 Time pulse distribution error</pre>                                                                                                                                                                                                                        | 7<br>8         | PBR parity error<br>KEY parity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>12 Unexpected channel demand</li> <li>13 Unexpected channel answer</li> <li>14 PUP memory request error</li> <li>15 ADC noisy</li> <li>16 LSB noisy</li> <li>17 TCU noisy</li> <li>18 DRM noisy</li> <li>19</li> <li>20</li> <li>21 Step control error</li> <li>22 Time pulse distribution error</li> </ul>                                                                                                                                                                                                             | 10             | DSA parity error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <pre>15 ADC noisy<br/>16 LSB noisy<br/>17 TCU noisy<br/>18 DRM noisy<br/>19<br/>20<br/>21 Step control error<br/>22 Time pulse distribution error</pre>                                                                                                                                                                                                                                                                                                                                                                          | 12<br>13       | Unexpected channel demand<br>Unexpected channel answer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>17 TCU noisy 18 DRM noisy 19 20 21 Step control error 22 Time pulse distribution error</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                | 15             | ADC noisy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2021Step control error22Time pulse distribution error                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17             | TCU noisy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22 Time pulse distribution error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22             | Time pulse distribution error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Note that bits 6:23 represent conditions which may either cause an interrupt or halt the machine entirely. If  $[EN]_1 = 1$  then these conditions cause an interrupt, otherwise the machine halts.  $[MP]_{6:23}$  are set to zero before each I/O operation. These bits do not normally concern the programmer.

$[MP]_{1:2}$  may be set to 1 through the use of SKM in unprotected status.

#### 2.20 MTC Metabit Trap Condition Register (1 bit)

and a second to the second stage for a second stage state of the

a state of the second second

The [MTC] = 1 if the conditions for a metabit trap obtain (cf. 6.2.1), otherwise [MTC] = 0. [MTC] is tested during each normal machine instruction cycle. [MTC] is not directly addressable by the programmer.

15.

#### 16. TM-3870

## 2.21 NR Interrupt Register (24 bits)

Various events cause bits to be set in NR.

```

<u>Bit</u> Event

```

| 0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | I/O faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2  | - <mark></mark> 2011년 - 1월 2012년 - 1월 2012년 1월 2012년 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3  | Magnetic tape read/write error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4  | End-of-file reading tape, or End-of-tape writing tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5  | e 💶 de la companya de la comp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6  | Tape unit or LSB device inoperative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7  | TCU operation complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8  | LSB device busy, tape busy, or ADC I/O exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9  | PUP operation complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10 | Tape unit rewind complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11 | ADC attention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 12 | TCU/HSC special device attention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13 | External device attention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15 | LSB device error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |