-

-

100

1

-

-

-

-

.

-

1

-

-

1

# MVME165 VME/VSB Microcomputer VMEmodule User's Manual

## **BUSINESS REPLY MAIL**

FIRST CLASS MAIL PERMIT NO. 321 TEMPE, ARIZONA

POSTAGE WILL BE PAID BY ADDRESSEE

### **TECHNICAL PUBLICATIONS M/D DW164**

MOTOROLA

Computer Group 2900 S. DIABLO WAY TEMPE, AZ 85282-9602

Links

NO POSTAGE NECESSARY IF MAILED IN THE UNITED STATES

122161

.....

### **READER COMMENTS**

Write if we're not right (or even if we are)...

Motorola welcomes your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Please take the time to complete and mail this reply card.

| Manual Title             |                                        | Presentation    | 1                                                      |

|--------------------------|----------------------------------------|-----------------|--------------------------------------------------------|

| Part Number              | Date                                   |                 | easy to use? 🗆 Yes 🛛 No                                |

|                          |                                        | Please explain  | what is good or poor:                                  |

| Your Title               | Telephone ()                           |                 |                                                        |

| Company                  |                                        |                 |                                                        |

| Address                  |                                        |                 |                                                        |

|                          |                                        |                 | ion easy to understand? 🗆 Yes 🛛 No                     |

|                          |                                        | If you checked  | no, please explain:                                    |

| General Information      | ו:                                     | ·····           |                                                        |

| Do you read this man     |                                        | In the informat | ion easy to find?                                      |

| □ Install the product    |                                        |                 | no, please explain:                                    |

|                          | Reference information                  |                 |                                                        |

| In general, how do you : | locate information within this manual? |                 |                                                        |

| 🗆 Index                  | 🗇 Page Headings                        | Accuracy:       |                                                        |

| Table of Contents        | □ Other                                | If you have fou | nd technical or typographical errors, please list them |

| Completeness:            |                                        | here.           |                                                        |

| •                        | like more information on:              | Page Number     | Description of Error                                   |

|                          |                                        |                 |                                                        |

|                          |                                        |                 |                                                        |

|                          |                                        |                 | <u> </u>                                               |

|                          | $\bigcirc$                             |                 |                                                        |

|                          | ( <b>M</b> ) <b>мот</b> о              | DROLA           |                                                        |

|                          | 、ノ                                     |                 |                                                        |

| ന്തും            |                                 |

|------------------|---------------------------------|

|                  |                                 |

| (1998)           |                                 |

| শ্যেক্ষরিয়      |                                 |

|                  |                                 |

|                  |                                 |

| F                |                                 |

| (~               |                                 |

| F                | MVME165                         |

| (2000 <b>)</b>   | VME/VSB MICROCOMPUTER VMEmodule |

| 100,000          | User's Manual                   |

|                  | (MVME165/D2)                    |

| िल्लाम           |                                 |

| (12300K)         |                                 |

| (500 <b>)</b>    |                                 |

| েইউউ)            |                                 |

| ( <u></u>        |                                 |

| (2)100<br>(2)100 |                                 |

|                  |                                 |

| 1-2210000        |                                 |

|                  |                                 |

| (77888)          |                                 |

|                  |                                 |

|                  |                                 |

#### NOTICE

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Not part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

#### **RESTRICTED RIGHTS LEGEND**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282-9602

### PREFACE

This manual provides general information, hardware preparation and installation instructions, operating instructions, and functional description for the MVME165 VME/ VSB Microcomputer VMEmodule.

This manual is intended for anyone who wants to design OEM systems, supply additional capability to an existing compatible system, or work in a lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

10000

1000

1000

1.5800

Children

<u>- 2000</u>

NO P

To use this manual, you may need to be familiar with the publications listed in the *Related Documentation* section in Chapter 1 of this manual.

The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., first published 1991, and may be used only under license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

### WARNING THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTIONS MANUAL, MAY CAUSE INTERFERENCE TO RADIO COMMUNICATIONS. IT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS A COMPUTING DEVICE PURSUANT TO SUBPART J OF PART 15 OF FCC RULES, WHICH ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST SUCH INTERFERENCE WHEN OPERATED IN A COMMERCIAL ENVIRONMENT. OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE INTERFERENCE IN WHICH CASE THE USER, AT HIS OWN EXPENSE, WILL BE REQUIRED TO TAKE WHATEVER MEASURES NECESSARY TO CORRECT THE INTERFERENCE.

Motorola and the Motorola symbol are registered trademarks of Motorola, Inc. MVME165bug, VMEmodule, and VMEsystem are trademarks of Motorola, Inc.

© Copyright Motorola 1992 Second Edition December 1992 All Rights Reserved Printed in the United States of America First Edition October 1990

### SAFETY SUMMARY SAFETY DEPENDS ON YOU

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola inc. assumes no liability for the customer's failure to comply with these requirements. The safety precautions listed below represent warnings of certain dangers of which we are aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### **GROUND THE INSTRUMENT.**

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet international Electrotechnical Commission (IEC) safety standards.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

#### **KEEP AWAY FROM LIVE CIRCUITS.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

#### DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

#### USE CAUTION WHEN EXPOSING OR HANDLING THE CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

#### DO NOT SUBSTITUTE PARTS OR MODIFY EQUIPMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

#### WARNING

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

(198**6**)

C3000

C73882

12/2000

Granes.

C7/90

12276

CORE

5720U

------

10000

(17)000

## CONTENTS

03150

6.000

1.000

(C)000

(~\%

1.000

17200

1.500

(-0.90)

(T) 888

10.900

(73) (73)

1.000

1.000

1000

|          | ction                           |

|----------|---------------------------------|

| Model I  | Designations                    |

| Features | 5                               |

|          | ations                          |

|          | ng Requirements                 |

|          | Compliance                      |

|          | Description                     |

| Related  | Documentation                   |

| Support  | Information                     |

| Manual   | Terminology                     |

|          | RE PREPARATION AND INSTALLATION |

|          | ction                           |

|          | ing Instructions                |

|          | re Preparation                  |

|          | Timer Input (J3)                |

|          | /Bus Mapping (J4/J5)            |

|          | ort Cabling                     |

|          | hassis Installation             |

| VIVIE C  |                                 |

|          | NG INSTRUCTIONS                 |

|          | ction                           |

|          | anel                            |

|          | Indicators                      |

|          | RT Switch (S1)                  |

|          | T Switch (S2)                   |

| •        | Y Maps                          |

|          | Метогу Мар                      |

| VME      | bus Short I/O Memory Map        |

| VME      | bus Short I/O Memory Map        |

|          | NAL DESCRIPTION                 |

|          | ction                           |

|          | Description                     |

|          | Description                     |

| Address  | s Map                           |

| ROM                                            | 4-7  |

|------------------------------------------------|------|

| Local Memory                                   | 4-7  |

| Time-of-Day Clock/NVRAM                        | 4-7  |

| DRAM Array                                     | 4-8  |

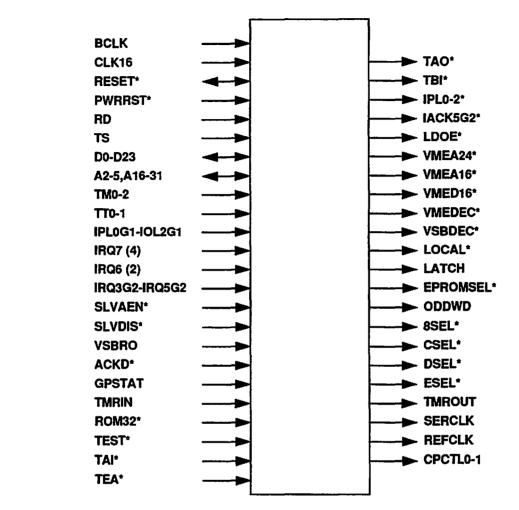

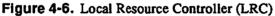

| Local Resource Controller (LRC)                | 4-10 |

| MC68040 Interface                              | 4-10 |

| Interrupt Handler                              | 4-11 |

| Local Device Control                           | 4-13 |

| Clocks                                         | 4-14 |

| LRC Control Status Registers                   | 4-14 |

| Timers                                         | 4-15 |

| General Control Register (GCR)                 | 4-18 |

| Bus Control Register                           | 4-20 |

| Interrupt Control And Status Register          | 4-21 |

| RAM Address Register                           | 4-27 |

| Composite Bus Error Status                     | 4-28 |

| LRC Reset Operation                            | 4-28 |

| MVME165 Control And Status Registers           | 4-28 |

| DUART                                          | 4-32 |

| DUART Port Assignments                         | 4-33 |

| VMEbus                                         | 4-34 |

| VMEbus Control/Status Registers                | 4-34 |

| VMEbus Short I/O                               | 4-36 |

| VME Subsystem Bus (VSB)                        | 4-36 |

| Local Timeout                                  | 4-37 |

| Interrupt Processing                           | 4-37 |

| ACFAIL Interrupt                               | 4-38 |

| ABORT Interrupt                                | 4-38 |

| Parity Error Interrupt (PARERR)                | 4-38 |

| DUART Timer Interrupt (TICKTMR)                | 4-39 |

| VSB Interrupt (VSBIRQ)                         | 4-39 |

| LRC Timer Interrupt (TMR0IRQ,TMR1IRQ,TMR2IRQ), | 4-39 |

| DUART Interrupt (DRTIRQ)                       | 4-40 |

| VMEbus/Utility Interrupts                      | 4-40 |

| RMC Operation                                  | 4-40 |

| Reset Operation                                | 4-41 |

Carrier a

P.....

**\_\_\_\_**

<del>.....</del>

(mar )

(1997)

-----

.....

**(**2007)

......

## **APPENDICES**

(\*\*\*\*\***\***\*\*

(<u>1996</u>)

(1999) (1997)

1000

() ()

[10000]

(internal second

(Ninger)

(\*\*\*\*\*

1

Contra

1000

0.000

েজ্ঞা

(1999) (1999)

10000

1.000

1.199

1000e

S-200

10000

| APPENDIX A - 4Mb Debugger Operation Per Jumpers             | A-1 |

|-------------------------------------------------------------|-----|

| APPENDIX B - 16Mb Debugger Operation Per Jumpers            | B-1 |

| APPENDIX C - VMEchip Local Control And Status Register Set  | C-1 |

| APPENDIX D - VMEchip Global Control And Status Register Set | D-1 |

| APPENDIX E - MVME165 Initialization Scheme                  | E-1 |

| APPENDIX F - Configuring A VME Subsystem Bus                | F-1 |

| APPENDIX G - VSB Control And Status Register                | G-1 |

## INDEX

| INDEX | IN | -1 | İ |

|-------|----|----|---|

|       |    |    |   |

# **FIGURES**

| Figure 2-1. MVME165 Jumper, Switch, and Connector Location Diagram |

|--------------------------------------------------------------------|

| Figure 3-1. MVME165 Front Panel                                    |

| Figure 4-1. MVME165 Block Diagram                                  |

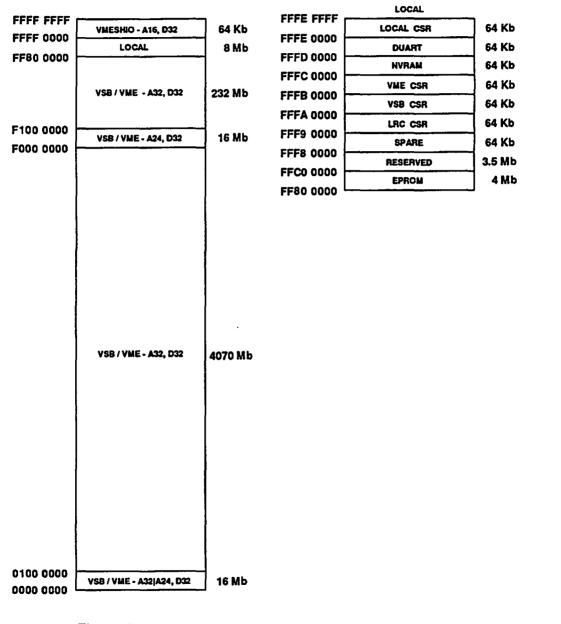

| Figure 4-2. System Address Map (VSBMD = 0, VSBEN = 1)              |

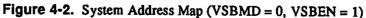

| Figure 4-3. System Address Map (VSBMD = 1, VSBEN = 1)              |

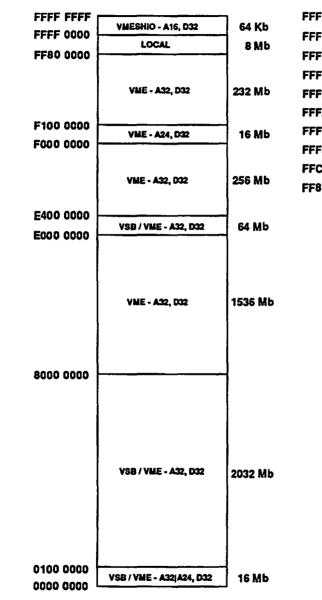

| Figure 4-4. System Address Map (VSBMB = Don't Care, VSBEN = 0)     |

| Figure 4-5. Memory Multiplexer (MEMMUX)                            |

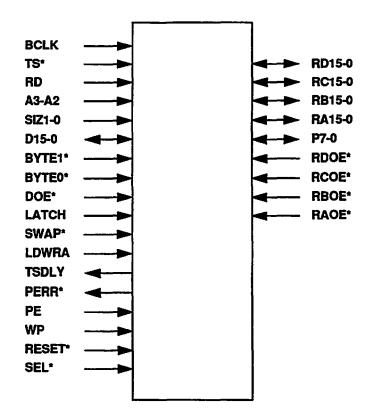

| Figure 4-6. Local Resource Controller (LRC)                        |

| Figure 4-7. LRC Memory Map                                         |

| Figure 4-8. LRC Timer Control Registers                            |

| Figure 4-9. General Control Register                               |

| Figure 4-10. Bus Control Register                                  |

| Figure 4-11. Interrupt Control Register 0                          |

| Figure 4-12. Interrupt Control Register 1                          |

| Figure 4-13. Status Register                                       |

| Figure 4-14. RAM Address Register                                  |

| Figure 4-15. Bus Error Register                                    |

| Figure 4-16. MVME165 Control and Status Register (\$FFFE0000)      |

| Figure 4-17. MVME165 Control and Status Register (\$FFFE0004)      |

## TABLES

e .....

-

Control

-----

-----

Sec.

| Table 2-1. | Jumper Block Placements                        | 2-3  |

|------------|------------------------------------------------|------|

|            | Serial Cabling To A Terminal                   | 2-5  |

| Table 2-3. | Serial Cabling To A Modem                      | 2-5  |

| Table 3-1. | MVME165 Front Panel LED Status                 | 3-3  |

| Table 3-7. | VMEchip Slave Access to GCSR                   | 3-8  |

| Table 4-1. | Time-Of-Day Clock Address Map                  | 4-8  |

| Table 4-2. | Interrupt Vector Data Bits (Least Significant) | 4-12 |

| Table 4-3. | MVME165 LRC Address Map                        | 4-14 |

| Table 4-4. | MVME165 DUART Address Map                      | 4-32 |

| Table 4-5. | MVME165 DUART Port Assignments                 | 4-33 |

| Table 4-6. | VMEchip Local Control and Status Registers     | 4-35 |

| Table 4-7. | VMEchip Global Control and Status Registers    | 4-35 |

| Table 4-8. | VSBchip Address Map                            | 4-36 |

| Table 4-9. | MVME165 Interrupt Assignments                  | 4-38 |

# CHAPTER 1 GENERAL INFORMATION

## Introduction

0.995

ന്ത്ര

29960

(1999) (1999)

0.0000

(P)VPD

0.000

C 19995

11200

(76**0**00)

C.2003

220

. shar

This user's manual provides general information, preparation for use and installation instructions, operating instructions, and a functional description of the MVME165 series of VME/VSB Microcomputers (referred to as the MVME165 throughout this manual).

## **Model Designations**

The MVME165 is available in four models, which are listed in Table 1-1.

| Product Number | Product Description            |

|----------------|--------------------------------|

| MVME165-01     | 25MHz, 4Mb Embedded Processor  |

| MVME165-02     | 25MHz, 16Mb Embedded Processor |

| MVME165-03     | 33MHz, 4Mb Embedded Processor  |

| MVME165-04     | 33MHz, 16Mb Embedded Processor |

| Table 1-1. | MVME165 | Model | Designations |

|------------|---------|-------|--------------|

|------------|---------|-------|--------------|

### Features

These are some of the major features of the MVME165:

- MC68040 microprocessor with 8Kb cache, MMU (Memory Management Unit), and FPU (Floating Point Unit)

- 4/16Mb of DRAM (burst fill completes in 4-1-1-1 processor clock cycles)

- Cache Monitor providing cache coherency for the local DRAM

- Two 32-pin JEDEC standard sockets for the EPROM

- One 28-pin JEDEC standard socket for the TOD/NVRAM (Time-of-Day Clock/8K x 8 Non-Volatile RAM)

- Two front panel RS-232C serial ports (MC68681)

- One 16-bit programmable timer (MC68681)

- Three 24-bit programmable counter/timers implemented as the Local Resource Controller (LRC)

#### **GENERAL INFORMATION**

| • | VSB bus Master/Slave Interface using the MVSB2400 (VSBchip) which has:        | <b></b>        |

|---|-------------------------------------------------------------------------------|----------------|

|   | VSB system controller/bus arbiter                                             | (1-1-1)        |

|   | • VSB requester with programmable timeout module                              |                |

|   | Block transfer module with byte count register                                |                |

|   | Control and Status Register (CSR)                                             | <b></b>        |

| • | VMEbus A32/D32 Master/Slave Interface using the MVME6000 (VMEchip) which has: |                |

|   | VMEbus System Controller with 4-Level Arbiter                                 | للمستع         |

|   | <ul> <li>VMEbus A32/A24/A16;D32/D16/D08 Master Interface</li> </ul>           |                |

|   | VMEbus 7-Level Interrupter                                                    |                |

|   | VMEbus 7-Level Interrupt Handler                                              | ويؤسفها        |

|   | VMEbus 4-Level Requester                                                      | ()             |

|   | Multi-processor Control/Status Registers                                      |                |

| ٠ | Front panel FAIL, HALT, RUN, and SCON LED (Light Emitting Diode) indicators   | ليلمنع         |

| • | Front panel ABORT and RESET push-button switches                              | ·              |

| • | Thirteen general purpose software control jumpers                             |                |

| • | VMEbus double-high, single-wide form factor                                   | <b>(7</b> .77) |

| - |                                                                               |                |

577

**\_\_\_\_**

.....

(With)

1000

.....

Ċ.

<del>.....</del>

# **Specifications**

General specifications for the MVME165 are listed in Table 1-2.

| Characteristics | Specifications                                                                                                                                                                         |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor  | MC68040 32-bit microprocessor                                                                                                                                                          |

| Clock signal    | 25.0-33.0 MHz CPU clock frequency<br>(The specific operating frequency is determined by the<br>oscillator installed.)                                                                  |

| CACHE           | The MC68040 contains an internal 8Kb cache (with 4K instruction and 4K data) which supports one cycle read accesses and external (to the processor) bus snooping of local DRAM memory. |

| DRAM            | 4/16Mb of DRAM (Dynamic RAM) are provided using either one megabit or four megabit RAMs.                                                                                               |

Table 1-2. MVME165 Specifications

| 1 |  |

|---|--|

| Characteristics                                                                       | Specifications                                                                                                             |  |  |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| MMU                                                                                   | The MC68040 contains an internal Memor<br>Management Unit (MMU) which supports 4K or 8I<br>page sizes.                     |  |  |

| FPU                                                                                   | The MC68040 contains a Floating Point Unit (FPU which implements a subset of the MC68881/MC6888 FPU.                       |  |  |

| SRAM                                                                                  | One 28-pin JEDEC socket which provides 8K x 8 o<br>NVRAM (Non-Volatile RAM) and a TOD (Time-Of<br>Day) Clock.              |  |  |

| ROM                                                                                   | Two 32-pin JEDEC sockets which provide support for 128K x 8, or 256K x 8 EPROMs (165Bug supplie with 256K x 8 devices).    |  |  |

| I/O                                                                                   | Two RS-232C asynchronous serial ports are provide<br>through the MC68681 DUART (Dual Asynchronou<br>Receiver/Transmitter). |  |  |

| Timers                                                                                | Three 24-bit counter/timers are in the LRC and on 16-bit timer is in the MC68681 DUART.                                    |  |  |

| VMEbus                                                                                | A VMEbus master/slave interface (A32 A24<br>D32 D16) is implemented with the MVME600<br>(VMEchip).                         |  |  |

| VSB                                                                                   | A VSB (bus) master/slave interface (A32/D32) is implemented using the MVSB2400 (VSBchip).                                  |  |  |

| Power requirements                                                                    | +5Vdc, 5.9 Amps maximum (5.4 A typical)<br>+12Vdc, 250 mA maximum<br>-12Vdc, 250 mA maximum                                |  |  |

| Operating temperature<br>(refer to the <i>Cooling</i><br><i>Requirements</i> section) | 0° to 55° C at point of entry of forced air cooling<br>(approximately 490 LFM)                                             |  |  |

| Storage temperature                                                                   | -40° to 85° C                                                                                                              |  |  |

| Table 1-2. 1 | MVME165 S | Specifications ( | (cont'd) |

|--------------|-----------|------------------|----------|

|--------------|-----------|------------------|----------|

লক্ষ

1998

्रमुख्यु

9999 1997

- 1999 (M

(199**6**)

1.339

5.5890

[\*?**8**%

**NAME**

्राणम्।

0000

(<sup>1</sup>)/98

(1999) (1999)

/ प्राप्तम्

(72<u>995</u>)

146945

(1990) (1990)

10000

1990

7.000

গোজা

িক্ষা

0.000

**য**়বাজ |

#### GENERAL INFORMATION

| Characteristics                                           | Specifications                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Relative humidity                                         | 5% to 95% (non-condensing)                                                                                                                                                                                                                                                                                                                                                                                              |

| Physical characteristics:<br>Height<br>Width<br>Thickness | VME double-high, single-wide form-factor<br>6.30 inches (160.0 mm)<br>9.19 inches (233.4 mm)<br>0.062 inch (1.57 mm)                                                                                                                                                                                                                                                                                                    |

| Part projections:<br>Component side<br>Solder side        | 0.50 inch (12.7 mm) maximum<br>0.067 inch (1.7 mm) maximum                                                                                                                                                                                                                                                                                                                                                              |

| Connectors                                                | <ul> <li>The 96-pin P1 backplane connector provides the interface to the VMEbus signals.</li> <li>The 96-pin P2 backplane connector provides the interface to the extended VMEbus signals and VSB signals.</li> <li>The 9-pin J1 front panel connector provides the interface to the Channel A serial port.</li> <li>The 9-pin J2 front panel connector provides the interface to the Channel B serial port.</li> </ul> |

| Table 1-2. | MVME165 | Specifications | (cont'd) |

|------------|---------|----------------|----------|

|------------|---------|----------------|----------|

### **Cooling Requirements**

The Motorola MVME165 VMEmodule is specified, designed, and tested to operate reliably with an incoming air temperature range from 0° to 55° C (32° to 131° F) with forced air cooling at a velocity typically achievable by using a 100 CFM axial fan. Temperature qualification is performed in a standard Motorola VMEsystem 1000 chassis. Twenty-five watt load boards are inserted in two card slots, one on each side, adjacent to the board under test, to simulate a high power density system configuration. An assembly of three axial fans, rated at 100 CFM per fan, is placed directly under the VME card cage. The incoming air temperature is measured between the fan assembly and the card cage, where the incoming airstream first encounters the module under test. Test software is executed as the module is subjected to ambient temperature variations. Case temperatures of critical, high power density integrated circuits are monitored to ensure component vendors specifications are not exceeded.

While the exact amount of airflow required for cooling depends on the ambient air temperature and the type, number, and location of boards and other heat sources,

1

1-4

adequate cooling can usually be achieved with 10 CFM and 490 LFM flowing over the module. Less airflow is required to cool the module in environments having lower maximum ambients. Under more favorable thermal conditions, it may be possible to operate the module reliably at higher than 55° C with increased airflow. It is important to note that there are several factors, in addition to the rated CFM of the air mover, which determine the actual volume and speed of air flowing over a module.

### FFC Compliance

(S778)

100000

िञ्चार

S:SIMP

1.0000

1.5900

12000

10000

55,000

-1997 -

12288.00

1.500

10000

The MVME165 was tested in an FCC-compliant chassis, and meet the requirements for Class A equipment. FCC compliance was achieved under the following conditions:

- 1. Shielded cables on all external I/O ports.

- 2. Cable shields are connected to earth ground via metal shell connectors bonded to a conductive module front panel.

- 3. Conductive chassis rails connected to earth ground. This provides the path for connecting shields to earth ground.

- 4. All chassis and MVME165 front panel attachment screws are properly tightened.

For minimum RF emissions, it is essential that the conditions above be implemented; failure to do so could compromise the FCC compliance of the equipment containing the module.

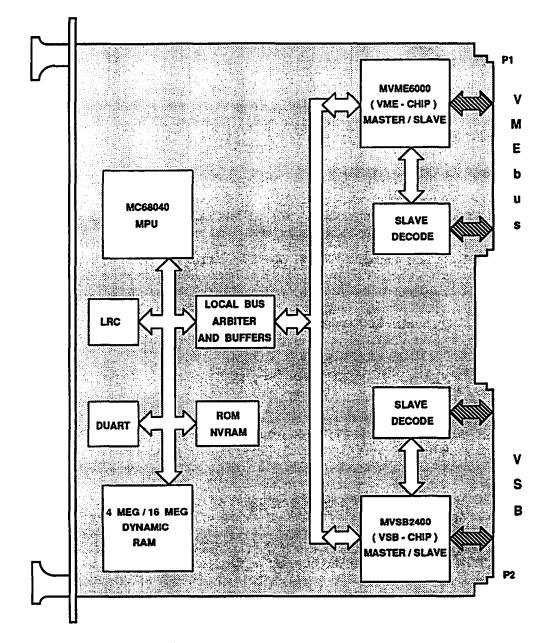

## **General Description**

The MVME165 microcomputer is a VME/VSB-based CPU engine, utilizing the Motorola MC68040 microprocessor. The MC68040 features 8Kb of internal cache, a floating point unit, and a memory management unit.

The MVME165 includes the MC68681 DUART for serial I/O and software timing, the Local Resource Controller (LRC) for local CSR, counter/timers, and local interrupt source; a full VMEbus 32-bit master/slave interface, a VMEbus interrupt handler, interrupter, system controller and a global register set (MVME6000); a full VSB bus master/slave interface (MVSB2400); two 32-pin JEDEC standard sockets for EPROM, one 28-pin JEDEC socket for Time-of-Day Clock/Non-Volatile RAM (TOD/NVRAM), and a 4/16Mb DRAM.

The optional MVME714 transition module with two DB-25 connectors is available to connect two RS-232C devices to the MVME165. A 2400 baud modem is also available with the MVME714M, which provides one console port and one port for terminal/printer/ modem.

## **Related Documentation**

The following publications are applicable to the MVME165 and may provide additional helpful information. If not shipped with this product, they may be purchased from Motorola, Inc, Computer Group, Technical Literature Center, 1919 West Fairmont Drive, Suite 8, Tempe, Arizona 85282; telephone: 1-800-458-6443; FAX: (602) 438-0240.

| Document Title                                                                    | Motorola<br>Publication Number |

|-----------------------------------------------------------------------------------|--------------------------------|

| SIMVME165 VME/VSB Microcomputer VMEmodule<br>Support Information                  | SIMVME165                      |

| MVME165BUG 165Bug Debugging Package User's<br>Manual                              | MVME165BUG                     |

| MVME165 Diagnostic Firmware User's Manual                                         | MVME165DIAG                    |

| MVME714 and MVME714M Two-Channel Serial I/O<br>Distribution Modules User's Manual | MVME714                        |

| MC68040 Enhanced 32-Bit Microprocessor User's<br>Manual                           | MC68040UM                      |

| MC68040 Designer's Handbook                                                       | MC68040DH                      |

| MC68681 Dual Asynchronous Receiver/Transmitter<br>(DUART) Data Book               | MC68681                        |

| MC68881/MC68882 Floating-Point Coprocessor<br>User's Manual                       | MC68881UM                      |

| MVME6000 (VMEchip) VMEbus Interface User's<br>Manual                              | MVME6000UM                     |

| MVSB2400 VSBchip User's Manual                                                    | MVSB2400UM                     |

| VSB (bus) - The Parallel Sub System Bus of the IEC<br>821 Bus                     | MVMESB                         |

**NOTE:** Although not shown in the above list, each Motorola Computer Group manual publication number is suffixed with characters that represent the revision level of the document, such as /D2 (the second revision of a manual); each supplement bears the same number as the manual but has a suffix such as /A1 (the first supplement to the manual).

The following non-Motorola publications may also be of interest and may be obtained from the sources indicated. The VMEbus Specification is contained in ANSI/IEEE Standard 1014-1987.

| ANSI/IEEE Std 1014-1987<br>Versatile Backplane Bus: VMEbus | The Institute of Electrical and Electronics<br>Engineers, Incorporated<br>Publication and Sales Department<br>345 East 47th Street<br>New York, New York 10017-2633<br>Telephone: 1-800-678-4333 |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EIA RS-232C Serial Interface<br>Specification              | Electronic Industries Association<br>2001 Eye Street N.W.<br>Washington, D.C. 20006<br>Telephone (202) 457-4900                                                                                  |

## **Support Information**

Same

[-0086]

1:2000

555 W

1000000

C/Sugar

C. 10000

1000

1

-----

Contract

178sdar

15150

The SIMVME165 contains the connector signal information, parts list, and schematic diagram for the MVME165.

The manual may be obtained free of charge from Motorola, Inc, Computer Group, Technical Literature Center, 1919 West Fairmont Drive, Suite 8, Tempe, Arizona 85282; telephone: 1-800-458-6443; FAX: (602) 438-0240.

## **Manual Terminology**

Throughout this manual, a convention is used which precedes data and address parameters by a character identifying the numeric format as follows:

- \$ dollar specifies a hexadecimal character

- % percent specifies a binary number

- & ampersand specifies a decimal number

For example, "12" is the decimal number twelve, and "\$12" is the decimal number eighteen. Unless otherwise specified, all address references are in hexadecimal.

An asterisk (\*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on a high to low transition.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation

#### GENERAL INFORMATION

and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

**(19**53)

\*\*\*\*

C 7.0

-----

(m)))

كرنيس

ومناهيا

Carse)

1000

<del>(11)</del>

التشير

10,000

(755) (755)

"Words" are 16-bit entities.

When individual bits are discussed in the text, "set" means 1 and "clear" means 0.

#### HARDWARE PREPARATION AND INSTALLATION

### **CHAPTER 2**

### HARDWARE PREPARATION AND INSTALLATION

### Introduction

10088

P-92920

1 mile

1211/000

1120004

17,000

0.000

100970

This chapter provides the unpacking, hardware preparation, and installation instructions for the MVME165 VMEmodule.

### **Unpacking Instructions**

#### NOTE

If shipping carton is damaged upon receipt, request that the carrier's agent be present during unpacking and inspection of equipment.

Carefully unpack the equipment from the shipping carton. Refer to the packing list and verify that all items are present. Save the shipping carton and packing materials for storing or reshipping of the equipment.

CAUTION

Avoid touching areas of integrated circuits. Static discharge can damage these components.

Inspect the equipment for any shipping damage. If no damage exists, then the module can be prepared for operation according to the following sections of this chapter.

### **Hardware Preparation**

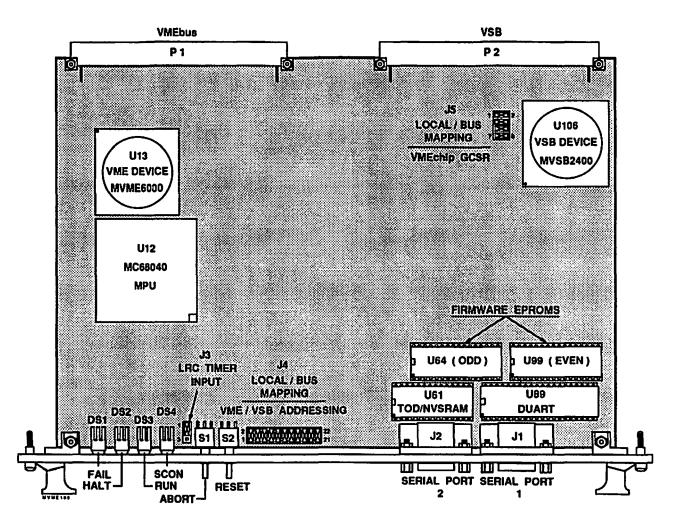

To select the desired configuration and ensure proper operation of the MVME165, certain modifications may be necessary before installation. These modifications are made through jumper block settings as described in the following sections. Therefore, the user should verify the jumper block configurations before installation and alter the jumpers, as required, for the user's particular system operation. The MVME165 has been factory tested and is shipped with factory-installed jumper configurations as illustrated in Figure 2-1.

Figure 2-1. MVME165 Jumper, Switch, and Connector Location Diagram

11111

- total

j

1.60

and the

N

1

]

1

]

3

100

1

1

H

| (T)(M)                                                                                                         |                                     | HARDWAI                                                  | RE PREPARATION AND INSTALLATION                                                         |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|

| (1988)                                                                                                         | Table 2-1 lists t                   | he jumper blocks by d                                    | esignation, function, and factory-installed                                             |

| CERTON                                                                                                         | configuration. A following sections | more detailed description<br>. In addition, four LED i   | n of these jumper blocks is provided in the ndicators (FAIL, HALT, RUN, and SCON)       |

|                                                                                                                |                                     | front panel. Refer to Cha<br>e use of these control indi | pter 3 for detailed information regarding the cators.                                   |

| 2.13000                                                                                                        |                                     | Table 2-1. Jumper                                        | r Block Placements                                                                      |

| (79)N                                                                                                          | Jumper                              | Function                                                 | Factory Configuration                                                                   |

| (PRINC)                                                                                                        | J1                                  | Serial Port 1 Connect                                    | Front Panel Terminal Connector                                                          |

| 110mg                                                                                                          | J2                                  | Serial Port 2 Connect                                    | Front Panel Host Connector                                                              |

| নিউটন                                                                                                          | J3                                  | LRC Timer Input                                          | J3 (1-2)                                                                                |

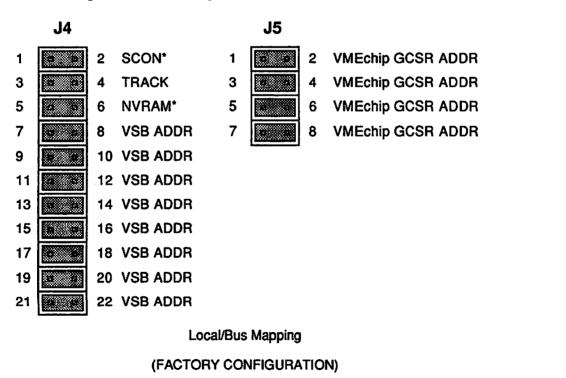

| (*******                                                                                                       | J4                                  | Local/Bus Mapping                                        | J4 (1-2),(3-4),(5-6),(7-8),(9-10),(11-12),<br>(13-14),(15-16),(17-18),(19-20),(21-22)   |

| 1 <u>11/11</u>                                                                                                 | J5                                  | Local/Bus Mapping                                        | J5 (1-2),(3-4),(5-6),(7-8)                                                              |

| (দেশলায়)                                                                                                      | LRC Timer In                        | put (J3)                                                 | ······································                                                  |

|                                                                                                                | Jumper block J3 se                  | elects the source for the t                              | imer input pin (TMRIN) to the LRC's Timer                                               |

| ( The second | connected to the 7                  | <b>FMRIN</b> pin which allows                            | s 1-2, the timer output pin (TMROUT) is<br>s separate timers within the LRC to be tied  |

| (1999)                                                                                                         | jumper cap across                   | pins 3-4, the timer clock                                | the <i>Timers</i> section in Chapter 4). With a $(OP3)$ of the local DUART (MC68681) is |

| Cores                                                                                                          |                                     | to the TMRIN pin of the<br>DUART Port Assignme           | e LRC for similar longer, but different time <i>nts</i> section in Chapter 4).          |

| فيسترا                                                                                                         |                                     | J3                                                       | J3                                                                                      |

| <u>्रिय</u><br>-                                                                                               | 1                                   | TMROUT                                                   | 1 D TMROUT                                                                              |

| (199 <b>0)</b>                                                                                                 | 2                                   |                                                          | 2 TMRIN                                                                                 |

| (Tringers)                                                                                                     | 3                                   |                                                          | з тмпск                                                                                 |

LRC Timer Output to

LRC Timer Input Connect

(FACTORY CONFIGURATION)

(<sup>10</sup>66)

াল্যান্ত

1.000

( Sound

1398

199300

DUART Timer Clock (OP3) to LRC Timer Input Connect

2-3

#### HARDWARE PREPARATION AND INSTALLATION

### Local/Bus Mapping (J4/J5)

Jumper blocks J4 and J5 provide the set-up and decode for the MVME165. These jumpers are readable and the 165Bug reads this set of jumpers at local address \$FFFE0004 and then loads this information, or information from the NVRAM or ROM (depending on the TRACK and NVRAM\* jumpers), into address FFFE0000 (165CSR), which then provides the selected decode range or particular option. Appendix A (MVME165 - 4Mb, versions -01 and -03) and Appendix B (MVME165 - 16Mb, versions -02 and -04) show how these jumpers are configured and the address range mapped for the two busses and the local DRAM.

The 165Bug default from the factory sets the local, VME and VSB address maps starting at \$0. The VMEchip GCSR default 165CSR value is set at \$A (see Figure 4-15), which programs the VME slave address of the VMEchip GCSR at \$FFFFCAFx (x representing the individual register in the VMEchip, refer to Table 3-7).

1.500.00

## **Serial Port Cabling**

Circle 8

1000

100,000

5300w

100000

10000

12:0200

1.5000

Column 1

Silon

1.000

110000

**ENSING**

1.000

(Prints)

The following tables provide the recommended cable connections for connecting the MVME165 serial ports to a terminal or modem interface. 165Bug expects the terminal to be attached to Serial Port 1. Serial Port 2 may be used as another terminal interface, or as a connection to a host system for upload/download using S-Record format.

| MVME165<br>DB-9 Board Connector |      | RS-232C<br>DB-25 Unit Connector |     |        |

|---------------------------------|------|---------------------------------|-----|--------|

| Signal                          | Pin  |                                 | Pin | Signal |

| RXDA                            | J1-2 | to                              | 2   | TXD    |

| TXDA                            | J1-3 | to                              | 3   | RXD    |

| CTSA                            | J1-8 | to                              | 4   | RTS    |

| RTSA                            | J1-7 | to                              | 5   | CTS    |

| DTRA                            | J1-4 | to                              | 8   | DCD    |

| GND                             | J1-5 | to                              | 7   | SGND   |

| DCDA                            | J1-1 | to                              | 20  | DTR    |

| DSRA                            | J1-6 | to                              | 6   | DSR    |

| Table 2-3 | Serial | Cabling 1 | To A | Modem |

|-----------|--------|-----------|------|-------|

|-----------|--------|-----------|------|-------|

| MVME165<br>DB-9 Board Connector |      |    | RS-232C<br>DB-25 Unit Connecto |        |

|---------------------------------|------|----|--------------------------------|--------|

| Signal                          | Pin  |    | Pin                            | Signal |

| TXDB                            | J2-2 | to | 2                              | TXD    |

| RXDB                            | J2-3 | to | 3                              | RXD    |

| RTSB                            | J2-7 | to | 4                              | RTS    |

| CTSB                            | J2-8 | to | 5                              | CTS    |

| DSRB                            | J2-6 | to | 6                              | DSR    |

| GND                             | J2-5 | to | 7                              | SGND   |

| DCDB                            | J2-1 | to | 8                              | DCD    |

| DTRB                            | J2-4 | to | 20                             | DTR    |

| 9 |   |    |   |

|---|---|----|---|

| _ | r |    | 1 |

|   |   | ٢. | 4 |

## **VME Chassis Installation**

The following section discusses installation of the MVME165 into a VME chassis. Ensure that EPROM devices are installed as needed. Factory configuration is with two EPROMs installed for the MVME165Bug debug monitor, in sockets U64 and U99. Ensure that all header jumpers are configured as desired.

a. Turn all equipment power OFF and disconnect power cable from ac power source.

#### CAUTION

Inserting or removing modules while power is applied could result in damage to module components.

### WARNING

DANGEROUS VOLTAGES, CAPABLE OF CAUSING DEATH, ARE PRESENT IN THIS EQUIPMENT. USE EXTREME CAUTION WHEN HANDLING, TESTING, AND ADJUSTING.

- b. The MVME165 may be installed into any double-high slot on a VMEmodule chassis. Make certain that the intended slot does not have I/O cabling on P2, since that could potentially damage the MVME165 VSB (bus) interface.

- c. Using a firm grip on the module, slide the unit into the card slide until the P1 and P2 connectors of the unit align and seat into the backplane sockets. Use a firm, steady pushing motion to install the unit snugly into the backplane.

- d. Install any other required VMEmodules in the system.

- e. Connect power cable to ac power source and turn equipment power ON.

# CHAPTER 3 OPERATING INSTRUCTIONS

## Introduction

COMM

েজাচা

13,836

1

110000

(\*\*\*\*\*

Need

1.000

This chapter provides necessary information to use the MVME165 in a system configuration. This includes operating controls, indicators, and memory map details found on the MVME165 microcomputer.

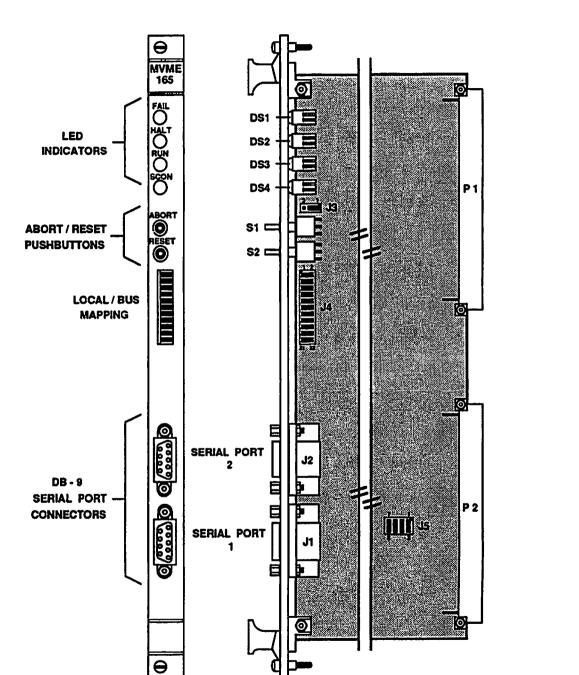

## **Front Panel**

The MVME165's front panel is illustrated in Figure 3-1. As shown, one red, one yellow, and two green LED indicators (FAIL, HALT, RUN, and SCON, respectively) are located on the top of the front panel. Located below the LED indicators are the two push-button switches S1 and S2 (ABORT and RESET, respectively). Below the push-button switches is a cutout for accessing the 22-pin jumper header J4. This is followed by the DB-9 connectors for Serial Ports 1 and 2.

### **LED Indicators**

The MVME165 has four LED indicators: FAIL, HALT, RUN, and SCON. They are described below. Table 3-1 provides the MVME165 status for all possible combinations of these LEDs.

The red FAIL LED indicator (DS1) is illuminated whenever the software detects an error and writes a "1" to the VMEchip's BRDFAIL bit.

The yellow HALT LED indicator (DS2) is illuminated whenever the MC68040 status lines PST3, PST2, PST1, and PST0 indicate a HALT condition (equal 0101).

The green **RUN** LED indicator (DS3) is illuminated whenever there is bus activity on the MC68040 bus, i.e., the TIP\* signal is driven. Note that if all the cycles hit in the cache, the **RUN** LED is not ON, even though the MC68040 is running.

The green **SCON** LED indicator (DS4) is illuminated whenever the MVME165 is configured as the system controller; i.e., jumper cap J4(1-2) is installed.

### **ABORT Switch (S1)**

The **ABORT** switch is a momentary-action switch that causes a local interrupt to the processor when pressed (pressed = 0, not pressed = 1). The button is debounced and fed to an edge-detector. The edge-detector output (the assertion of the ABORT bit in the local CSR register) is used to generate the ABORT interrupt request. The ABORT

O BOT

**DATE:**

- **1**

िरस्त

C2112

10.0

Figure 3-1. MVME165 Front Panel

interrupt is used to gain access to the 165Bug debugger firmware located in the MVME165 EPROMs. Refer to the *Interrupt Processing* section in Chapter 4 for more details.

| FAIL DS1<br>Red | HALT DS2<br>Yellow | RUN DS3<br>Green | SCON DS4<br>Green | MVME165 Status                                                                     |

|-----------------|--------------------|------------------|-------------------|------------------------------------------------------------------------------------|

| OFF             | OFF                | OFF              | OFF               | No power is applied to the module, or the MPU is not the current local bus master. |

| OFF             | OFF                | ON/OFF           | ON/OFF            | Normal operation.                                                                  |

| ON/OFF          | ON                 | OFF              | ON/OFF            | The MC68040 is in a halted state.                                                  |

| ON              | OFF                | ON/OFF           | ON/OFF            | An error is detected by software<br>and the VMEchip's BRDFAIL bit<br>is ON.        |

Table 3-1. MVME165 Front Panel LED Status

### **RESET Switch (S2)**

0.0000

(1990) (1990)

C->2880

C:2500

1000

100,000

The **RESET** switch is a momentary-action switch which, when pressed (pressed = 0, not pressed = 1), generates a local reset (PRESET\*) that is asserted for 200 milliseconds from the time that the switch is released. If the MVME165 is the system controller, then a VMEbus system reset (SYSRESET\*) is also generated; it is asserted for 200 milliseconds from the time that the switch is released.

### **Memory Maps**

The following tables and text discuss the MVME165 memory maps.

### **Main Memory Map**

The physical addresses of the devices that respond to the MC68040 MPU are provided in Table 3-2.

| nort I/O<br>(replicated)<br>'(replicated) | A16,D32                                                                                                                        | 64Kb                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                   |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | <br>D32                                                                                                                        |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

|                                           | D32                                                                                                                            |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

| (replicated)                              |                                                                                                                                | 8Kb                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |

|                                           |                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

|                                           | D8                                                                                                                             | 16b                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                 |

| VRAM (replicated)                         |                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

| -Day Clock                                | D8                                                                                                                             | 8b                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                 |

| ic RAM                                    | D8                                                                                                                             | 8184b                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                 |

| ip (replicated)                           |                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

| ip (CSR)                                  | D8                                                                                                                             | 48b                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |

|                                           |                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

| p CSR (A32)                               | D32                                                                                                                            | 8b                                                                                                                                                                                                                   | ·                                                                                                                                                                                                                                                                                 |

| plicated)                                 |                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

| cal CSR                                   | D32                                                                                                                            | 64b                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |

| l                                         |                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

|                                           | D32                                                                                                                            | 4Mb                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                 |

| AEbus (A32)                               | D32                                                                                                                            | 232Mb                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                   |

| AEbus (A24)                               | D32                                                                                                                            | 16Mb                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                   |

| AEbus (A32)                               | D32                                                                                                                            | 3814Mb                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                   |

| AEbus (A24,A32)                           |                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                   |

|                                           | ic RAM<br>ip (replicated)<br>ip (CSR)<br>p CSR (A32)<br>plicated)<br>cal CSR<br>i<br>MEbus (A32)<br>MEbus (A24)<br>MEbus (A32) | ic RAM     D8       ip (replicated)        ip (CSR)     D8       I        p CSR (A32)     D32       plicated)        ccal CSR     D32       I        D32     D32       MEbus (A32)     D32       MEbus (A24)     D32 | ic RAM       D8       8184b         ip (replicated)           ip (CSR)       D8       48b         i           p CSR (A32)       D32       8b         plicated)           ccal CSR       D32       64b         i           D32       4Mb         MEbus (A32)       D32       232Mb |

| Table 3-2. | <b>MVME165</b> | Physical | Address | Memory | Мар |

|------------|----------------|----------|---------|--------|-----|

|------------|----------------|----------|---------|--------|-----|

**NOTES:** 1. Least significant byte of each longword.

2. LTO (Local Time Out) on writes.

The address range area from 00000000 to FF7FFFFF is for the VSB, VMEbus resources, and local DRAM. This address area can be allocated differently depending on the state of the bus mode select bit (VSBMD) of the CSR within the LRC. This bit is described in the *Bus Control Register* section in Chapter 4. The address map as it exists with each state of this bit is illustrated in Figures 4-2 and 4-3.

The jumpers at J4 and J5 are provided for user configuration of the local and bus mapping of the local DRAM. These jumpers do not directly determine how the memory will be decoded, but they are interpreted by the 165bug in certain conditions to determine where local memory should be mapped locally as well as from the VMEbus and VSB. These jumpers can be read at \$FFFE0004, as illustrated in Figure 4-15.

Mapping is determined by setting bits in the 165CSR register at \$FFFE0000 bits D0 through D14. The mapping possibilities for the Local DRAM as viewed from the MC68040 for both versions is provided in Table 3-3. Table 3-4 (MVME165 - 4Mb) and

**OPERATING INSTRUCTIONS**

Table 3-5 (MVME165 - 16Mb) provide the possible mapping configurations of the DRAM as viewed from the VMEbus. VSB mapping options are provided in Table 3-6.

| 165CSR<br>HEX | 165CRS<br>Data Bits |     |     | Local Access to DRAM from CPU<br>(Starting Address) |                 |  |

|---------------|---------------------|-----|-----|-----------------------------------------------------|-----------------|--|

| Value         | D14                 | D13 | D12 | MVME165 (4Mb)                                       | MVME165 (16Mb)  |  |

| \$0           | 0                   | 0   | 0   | \$0000000                                           | \$0000000       |  |

| \$1           | 0                   | 0   | 1   | \$00400000                                          | \$0100000       |  |

| \$2           | 0                   | 1   | 0   | \$00800000                                          | \$02000000      |  |

| \$3           | 0                   | 1   | 1   | \$00C00000                                          | \$03000000      |  |

| \$4           | 1                   | 0   | 0   | \$0100000                                           | \$04000000      |  |

| \$5           | 1                   | 0   | 1   | \$01400000                                          | \$05000000      |  |

| <b>\$</b> 6   | 1                   | 1   | 0   | Local DRAM Access Disabled                          |                 |  |

| \$7           | 1                   | 1   | 1   | Local DRAM                                          | Access Disabled |  |

Table 3-3. Local DRAM Mapping From The MC68040

**NOTE:** When the VMEbus tracking mode is selected, the debugger ignores the most significant bit of the VME mapping jumper (refer to Appendix A).

Table 3-4. MVME165 (4Mb Version) VME Addressing

| 165CSR VMEbus Bits |        |     |           |          | Slave Access to DRAM from VME |                         |  |

|--------------------|--------|-----|-----------|----------|-------------------------------|-------------------------|--|

| HEX                | Binary |     | (Addressi | ng Mode) |                               |                         |  |

| D11-D08            | D11    | D10 | D09       | D08      | Extended (A32)                | Standard (A24)          |  |

| \$0                | 0      | 0   | 0         | 0        | \$00000000 - \$003FFFFF       | \$xx000000 - \$xx3FFFFF |  |

| <b>\$</b> 1        | 0      | 0   | 0         | 1        | \$00400000 - \$007FFFFF       | \$xx400000 - \$xx7FFFFF |  |

| \$2                | 0      | 0   | 1         | 0        | \$00800000 - \$00BFFFFF       | \$xx800000 - \$xxBFFFFF |  |

| \$3                | 0      | 0   | 1         | 1        | \$00C00000 - \$00FFFFFF       | \$xxC00000 - \$xxFFFFFF |  |