MVME320B VMEbus Disk Controller Module User's Manual

# HARDWARE

MVME320B/D1 JANUARY 1988

### MVME320B

### VMEbus DISK CONTROLLER MODULE

### USER'S MANUAL

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

SYSTEM V/68, VERSAdos, and VMEsystem 1000 are trademarks of Motorola Inc. IBM is a trademark of International Business Machines.

The computer program stored in the Read Only Memory of this device contains material copyrighted by Motorola Inc., first published 1987, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

### WARNING

THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE CAUSE INTERFERENCE INSTRUCTIONS MANUAL. MAY TO RADIO COMMUNICATIONS. IT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS A COMPUTING DEVICE PURSUANT TO SUBPART J OF PART 15 OF FCC RULES, WHICH ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST SUCH INTERFERENCE WHEN OPERATED IN A COMMERCIAL ENVIRONMENT. OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE INTERFERENCE IN WHICH CASE THE USER, AT HIS OWN EXPENSE, WILL BE REQUIRED TO TAKE WHATEVER MEASURES NECESSARY TO CORRECT THE INTERFERENCE.

### First Edition

Copyright 1988 by Motorola Inc.

# SAFETY SUMMARY SAFETY DEPENDS ON YOU

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola Inc. assumes no liability for the customer's failure to comply with these requirements. The safety precautions listed below represent warnings of certain dangers of which we are aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

### **GROUND THE INSTRUMENT.**

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

### **KEEP AWAY FROM LIVE CIRCUITS.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

### DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

### USE CAUTION WHEN EXPOSING OR HANDLING THE CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

### DO NOT SUBSTITUTE PARTS OR MODIFY EQUIPMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact Motorola Field Service Division for service and repair to ensure that safety features are maintained.

### DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

### WARNING

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

### PREFACE

Unless otherwise specified, all address references are in hexadecimal throughout this manual.

An asterisk (\*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on a high to low transition.

Signal names in parentheses denote internal module (onboard) signals.

# TABLE OF CONTENTS

# CHAPTER 1 - GENERAL INFORMATION

| 1.1 INTRODUCTION                            | 1-1 |

|---------------------------------------------|-----|

| 1.2 MVME320 FAMILY DIFFERENCES              |     |

| 1.3 FEATURES                                | 1-2 |

| 1.4 SPECIFICATIONS                          |     |

| 1.4.1 Cooling Requirements                  | 1-3 |

| 1.4.2 FCC Compliance                        | 1-4 |

| 1.5 GENERAL DESCRIPTION                     |     |

| 1.6 DRIVE COMPATIBILITY AND CAUTIONS        | 1-5 |

| 1.7 DUAL DENSITY PERFORMANCE CONSIDERATIONS | 1-6 |

| 1.8 PROGRAMMING CAUTIONS                    |     |

| 1.9 RELATED DOCUMENTATION                   | 1-8 |

## CHAPTER 2 - HARDWARE PREPARATION AND INSTALLATION INSTRUCTIONS

| 2.1 INTRODUCTION                                           | 2 - 1 |

|------------------------------------------------------------|-------|

|                                                            | 2 - 1 |

| 2.3 HARDWARE PREPARATION                                   | 2 - 1 |

|                                                            | 2-3   |

| 2.3.2 Interrupt Level (J7 and J11) 2                       | 2 - 4 |

| 2.3.3 Address Modifier (J8) 2                              | 2 - 5 |

| 2.3.4 Address Decode (J9) 2                                | 2 - 5 |

|                                                            | 2-6   |

| 2.3.6 PROM Enable (J12) 2                                  | 2-6   |

| 2.3.7 Clock Select (J13) 2                                 | ! - 7 |

| 2.3.8 PROM Size (J14) 2                                    | ! - 7 |

|                                                            | - 7   |

|                                                            | -8    |

|                                                            | -8    |

|                                                            | - 9   |

| 2.4 MVME320B SOFTWARE SPEED CONTROL 2-                     |       |

| 2.5 INSTALLATION CONSIDERATIONS 2-                         |       |

| 2.6 CABLING 2-                                             |       |

| 2.6.1 System Configurations 2-                             | _     |

| 2.6.1.1 Examples of Termination of 5-1/4 Inch Hard Disk 2- |       |

| 2.6.2 Floppy Disk Cabling 2-                               | 21    |

# CHAPTER 3 - FUNCTIONAL DESCRIPTION

| 3.1 | INTRODUCTION    | 3-1 |

|-----|-----------------|-----|

| 3.2 | LOGIC OPERATION | 3-1 |

# CHAPTER 4 - REGISTERS

| 4.1 | INTRODUCTION                                         | 4-1   |

|-----|------------------------------------------------------|-------|

| 4.2 | EVENT CONTROL AREA REGISTERS (REGISTERS 1-7)         | 4-2   |

| 4.3 | INTERRUPT VECTOR REGISTER (REGISTER 9)               | 4-3   |

|     | INTERRUPT SOURCE REGISTER (REGISTER B)               | 4-3   |

|     | DRIVE STATUS AND CONFIGURATION REGISTER (REGISTER D) | 4 - 4 |

CHAPTER 5 - EVENT CONTROL AREA

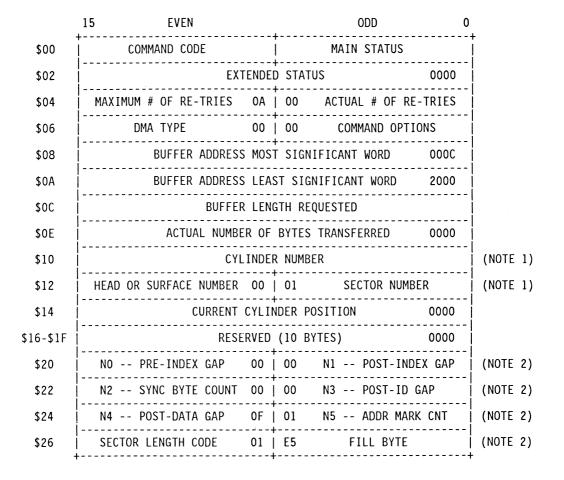

| 5.2.1       Command Code (1 byte; offset = \$00)       5-2         5.2.2       Main Status (1 byte; offset = \$01)       5-3         5.2.3       Extended Status (2 bytes; offset = \$02)       5-3         5.2.4       Maximum Number of Re-tries (1 byte; offset = \$04)       5-5         5.2.5       Actual Number of Re-tries (1 byte; offset = \$05)       5-5         5.2.6       DMA Type (1 byte; offset = \$06)       5-5         5.2.7       Command Options (1 byte; offset = \$07)       5-6         5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$06)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$07)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$10)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8 | 5.1 IN  | TRODUCTION                                              | 5-1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------|-----|

| 5.2.2       Main Status (1 byte; offset = \$01)       5-3         5.2.3       Extended Status (2 bytes; offset = \$02)       5-3         5.2.4       Maximum Number of Re-tries (1 byte; offset = \$04)       5-5         5.2.5       Actual Number of Re-tries (1 byte; offset = \$05)       5-5         5.2.6       DMA Type (1 byte; offset = \$06)       5-5         5.2.7       Command Options (1 byte; offset = \$07)       5-6         5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$06)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$06)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                    | 5.2 EC/ | A FIELDS                                                | 5-2 |

| 5.2.2       Main Status (1 byte; offset = \$01)       5-3         5.2.3       Extended Status (2 bytes; offset = \$02)       5-3         5.2.4       Maximum Number of Re-tries (1 byte; offset = \$04)       5-5         5.2.5       Actual Number of Re-tries (1 byte; offset = \$05)       5-5         5.2.6       DMA Type (1 byte; offset = \$06)       5-5         5.2.7       Command Options (1 byte; offset = \$07)       5-6         5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$06)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$06)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                    | 5.2.1   | Command Code (1 byte; offset = \$00)                    | 5-2 |

| 5.2.3       Extended Status (2 bytes; offset = \$02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.2.2   |                                                         | 5-3 |

| 5.2.4       Maximum Number of Re-tries (1 byte; offset = \$04)       5-5         5.2.5       Actual Number of Re-tries (1 byte; offset = \$05)       5-5         5.2.6       DMA Type (1 byte; offset = \$06)       5-5         5.2.7       Command Options (1 byte; offset = \$07)       5-6         5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$00)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$00)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)                                                                                                                                                                                                                                                                                                        | 5.2.3   |                                                         | 5-3 |

| 5.2.5       Actual Number of Re-tries (1 byte; offset = \$05)       5-5         5.2.6       DMA Type (1 byte; offset = \$06)       5-5         5.2.7       Command Options (1 byte; offset = \$07)       5-6         5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$00)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$00)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                              | 5.2.4   |                                                         | 5-5 |

| 5.2.6       DMA Type (1 byte; offset = \$06)       5-5         5.2.7       Command Options (1 byte; offset = \$07)       5-6         5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$00)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$00)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                                                                                                              | 5.2.5   |                                                         | 5-5 |

| 5.2.7       Command Options (1 byte; offset = \$07)       5-6         5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$0C)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$0C)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.2.6   | DMA Type (1 byte; offset = \$06)                        | 5-5 |

| 5.2.8       Buffer Address (4 bytes; offset = \$08)       5-7         5.2.9       Buffer Length Requested (2 bytes; offset = \$0C)       5-7         5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$0C)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.2.7   | Command Options (1 byte; offset = \$07)                 | 5-6 |

| 5.2.9Buffer Length Requested (2 bytes; offset = \$0C)5-75.2.10Actual Number of Bytes Transferred (2 bytes; offset = \$0E)5-75.2.11Physical Starting Disk Address (4 bytes; offset = \$10)5-75.2.12Current Cylinder Position (2 bytes; offset = \$14)5-75.2.13Reserved (10 bytes; offset = \$16)5-75.2.14Disk Track Format Fields (8 bytes; offset = \$20)5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.8   |                                                         | 5-7 |

| 5.2.10       Actual Number of Bytes Transferred (2 bytes; offset = \$0E)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.2.9   |                                                         | 5-7 |

| \$0E)       5-7         5.2.11       Physical Starting Disk Address (4 bytes; offset = \$10)       5-7         5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.2.10  |                                                         |     |

| 5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                                         | 5-7 |

| 5.2.12       Current Cylinder Position (2 bytes; offset = \$14)       5-7         5.2.13       Reserved (10 bytes; offset = \$16)       5-7         5.2.14       Disk Track Format Fields (8 bytes; offset = \$20)       5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.11  | Physical Starting Disk Address (4 bytes; offset = \$10) | 5-7 |

| 5.2.14 Disk Track Format Fields (8 bytes; offset = \$20) 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.12  |                                                         | 5-7 |

| 5.2.14 Disk Track Format Fields (8 bytes; offset = \$20) 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.13  | Reserved (10 bytes; offset = \$16)                      | 5-7 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.2.14  |                                                         | 5-8 |

| 5.2.15 Reserved (6 bytes; offset = \$28) 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.2.15  | Reserved (6 bytes; offset = \$28)                       | 5-8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.2.16  |                                                         | 5-8 |

| 6.2 CO | TRODUCTION                                  | 6-1<br>6-2 |

|--------|---------------------------------------------|------------|

| 6.2.1  | Recalibrate to Track Zero (0)               | 6-2        |

| 6.2.2  | Write with Deleted Data (1)                 | 6-3        |

| 6.2.3  | Verify (2)                                  | 6-3        |

| 6.2.4  | Transparent Sector Read (3)                 | 6-3        |

| 6.2.5  | Read Identifier (4)                         | 6-3        |

| 6.2.6  | Read Multiple Sector with Implied Seek (5)  | 6-3        |

| 6.2.7  | Write Multiple Sector with Implied Seek (6) | 6-4        |

| 6.2.8  | Format a Track with Implied Seek (7)        | 6-4        |

### CHAPTER 6 - COMMANDS

<u>Page</u>

| CHAPTER | 7 - ERROR CORRECTION                                                                                                                                                                          |                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|         |                                                                                                                                                                                               | '-1<br>'-1                                   |

| CHAPTER | 8 - DISK TRACK FORMAT                                                                                                                                                                         |                                              |

|         | 8.2BAD SECTOR HANDLING88.3ECA TRACK FORMAT FIELDS8                                                                                                                                            | -1<br>-3<br>-3<br>-4                         |

| CHAPTER | 9 - SYSTEM OPERATION                                                                                                                                                                          |                                              |

|         | 9.2MVME320B INITIALIZATION99.3STATUS ON RESET99.4HOST INITIALIZATION99.5ECA FIELD TYPES99.5.1ECA Formats99.5.2Drive Control Parameters99.5.3Command Execution Parameters99.5.4Command Status9 | -1<br>-1<br>-1<br>-2<br>-2<br>-3<br>-3<br>-3 |

CHAPTER 10 - SCHEDULER CONCEPTS

| 10.1 INTRODUCTION                       | 10-1 |

|-----------------------------------------|------|

| 10.2 RESOURCES                          | 10-1 |

| 10.3 LOGICAL OPERATIONS                 | 10-2 |

| 10.4 COMMAND INITIATION                 | 10-2 |

| 10.4.1 New Command Requests             | 10-3 |

| 10.4.2 Validity Checks for New Commands | 10-3 |

| 10.5 MVME320B DISK DRIVE CONTROLS       | 10-4 |

| 10.5.1 Positioning Operations           |      |

| 10.5.2 Read/Write Operations            | 10-5 |

| 10.5.3 DMA Transfers                    | 10-7 |

| 10.6 DISK WRITE I/O FOR FORMAT COMMANDS | 10-7 |

CHAPTER 11 - THEORY OF OPERATION

| 11.1 INTRODUCTION        | 11-1 |

|--------------------------|------|

| 11.2 THEORY OF OPERATION | 11-1 |

|          |                     |                                                                                                                                   | <u>Page</u>                               |

|----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| CHAPTER  | 12 -                | MAINTENANCE                                                                                                                       |                                           |

|          | 12.2<br>12.3        | INTRODUCTION<br>PREVENTIVE MAINTENANCE<br>CORRECTIVE MAINTENANCE<br>VCO TEST PROCEDURE                                            | 12-1<br>12-1<br>12-1<br>12-2              |

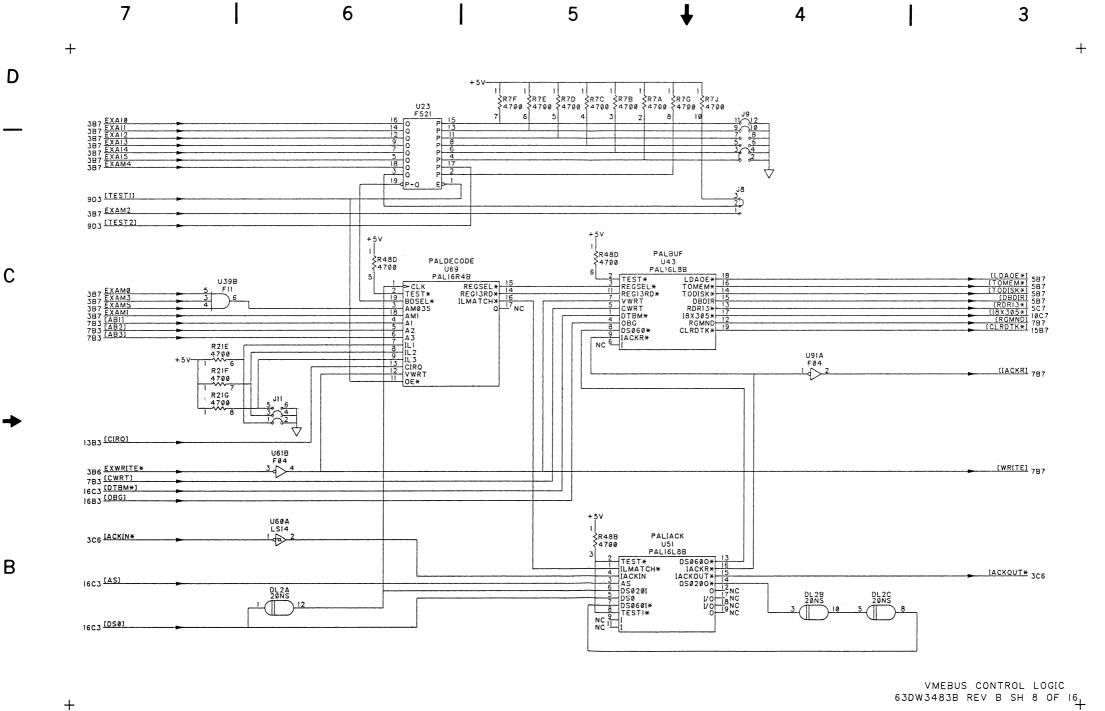

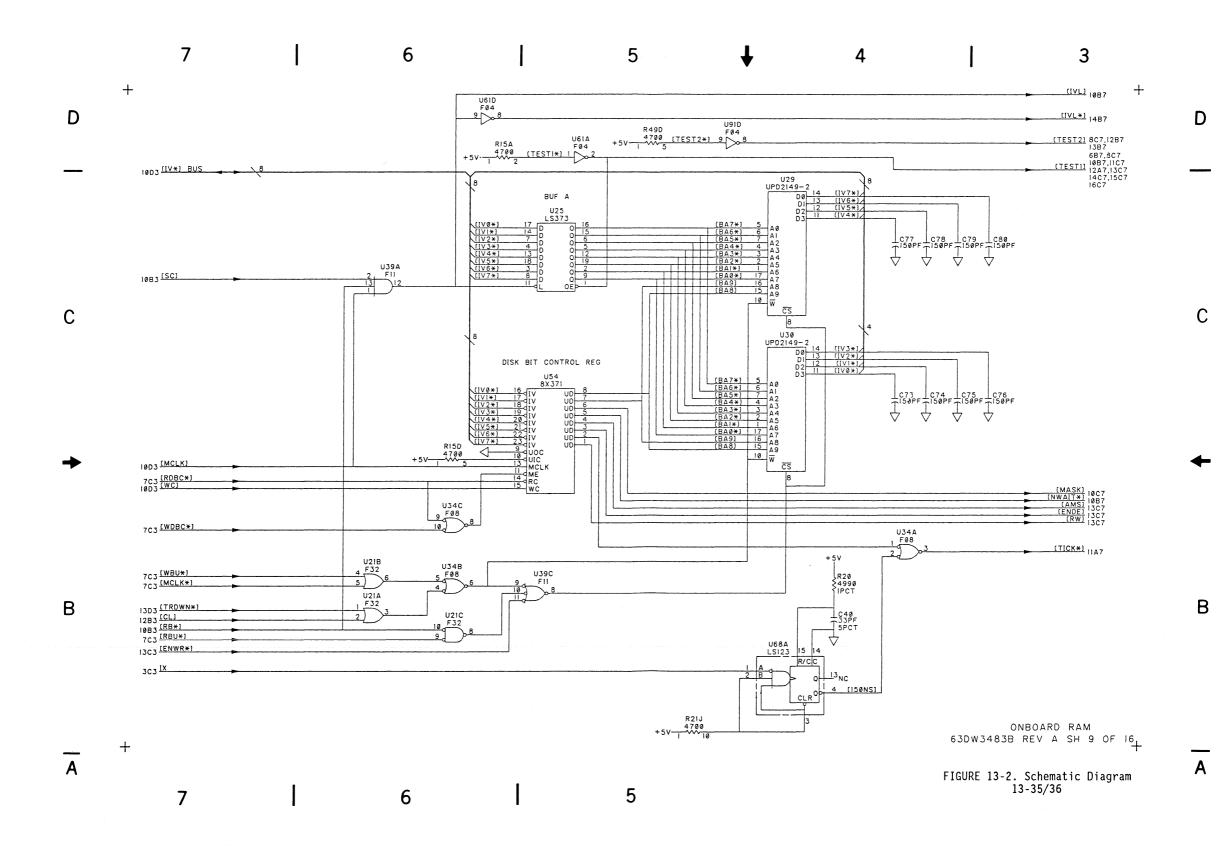

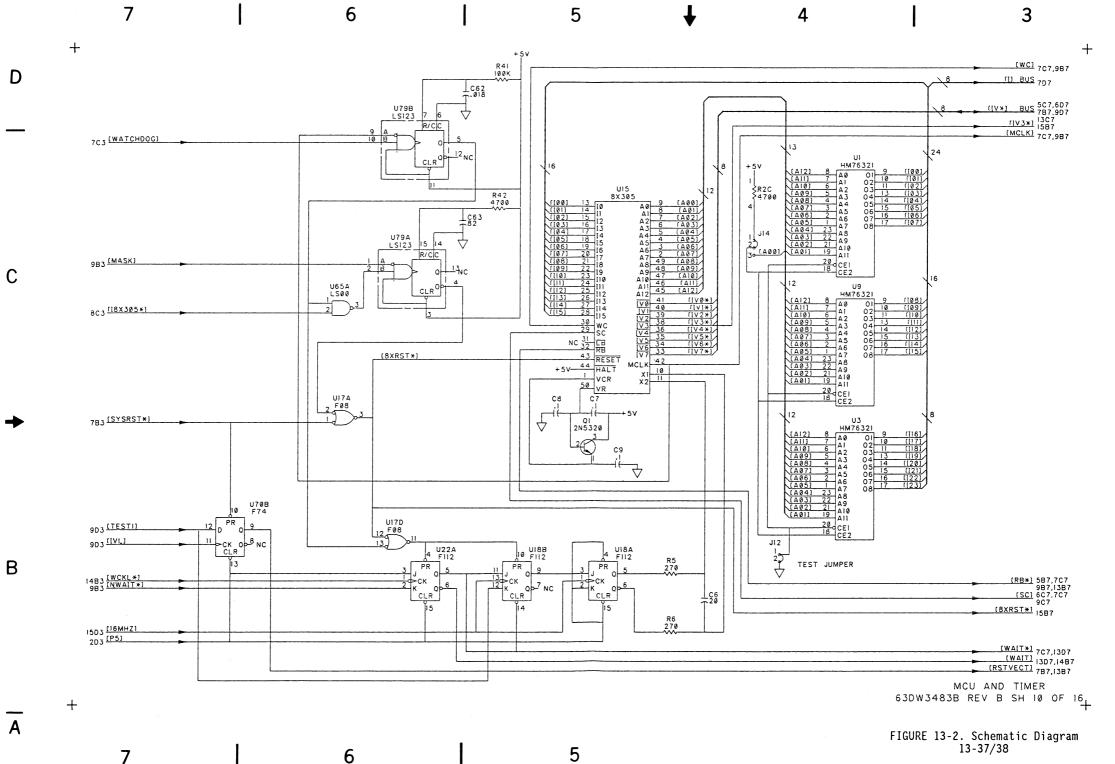

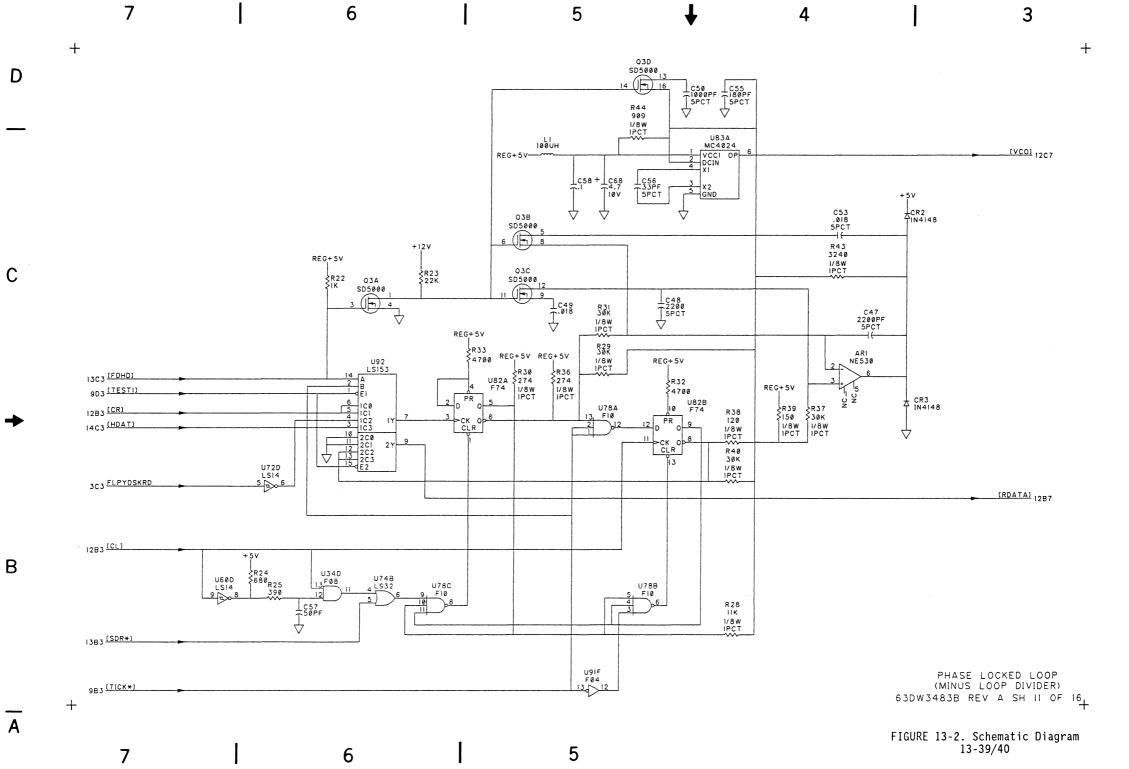

| CHAPTER  | 13 -                | SUPPORT INFORMATION                                                                                                               |                                           |

|          | 13.2<br>13.3        | INTRODUCTION<br>CONNECTOR PIN SIGNALS<br>PARTS LIST<br>SCHEMATIC DIAGRAMS                                                         | 13-1<br>13-1<br>13-1<br>13-1<br>13-18     |

| APPENDI) | (A -                | DISK FORMATS                                                                                                                      |                                           |

|          | A.2<br>A.3<br>A.3.1 | INTRODUCTION<br>5-1/4 INCH HARD DISK FORMATS<br>8-INCH AND 5-1/4 INCH DISKETTE FORMATS<br>3740 IBM Format<br>System 34 IBM Format | A - 1<br>A - 1<br>A - 3<br>A - ∻<br>A - 5 |

| APPENDIX | КВ-                 | ECA BLOCK TABLES                                                                                                                  | B-1                                       |

| APPENDIX | C -                 | PROGRAMMING CONCEPTS AND SEQUENCE                                                                                                 |                                           |

|          | C.2<br>C.3          | INTRODUCTION<br>PROGRAMMING CONCEPTS<br>PROGRAMMING SEQUENCE<br>COMMAND EXECUTION                                                 | C-1<br>C-1<br>C-1<br>C-3                  |

| INDEX    | ••••                |                                                                                                                                   | IN-1                                      |

# LIST OF ILLUSTRATIONS

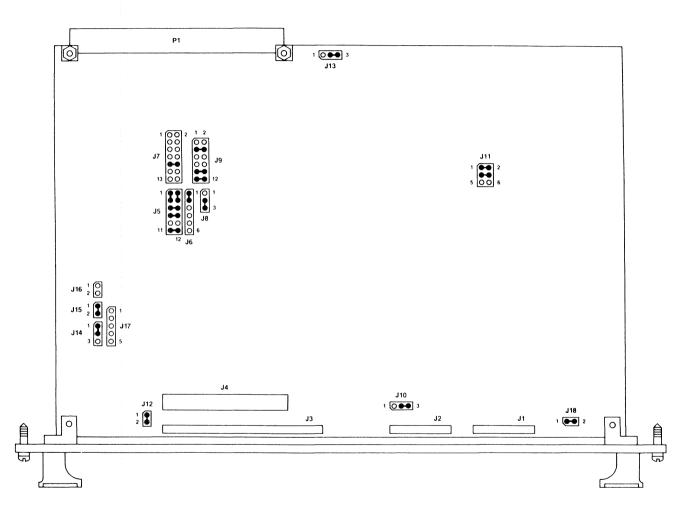

| FIGURE 2-1. | MVME320B Connector and Header Locations                   | 2-2  |

|-------------|-----------------------------------------------------------|------|

| FIGURE 2-2. | TEAC Drive FD-55GFV-17-V (Motorola Number 01-W0316B01)    | 2-11 |

| FIGURE 2-3. | TEAC Drive FD-55GFR-606-U (Motorola Number 01-W0316B02) . | 2-12 |

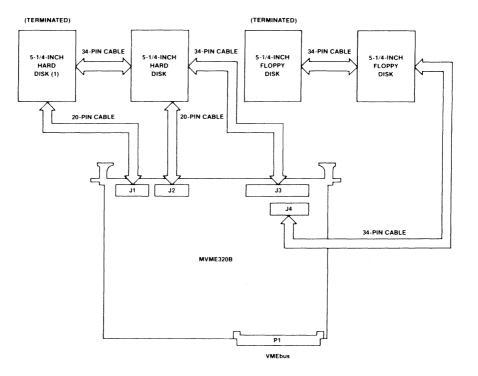

| FIGURE 2-4. | Two 5-1/4 Inch Hard and Two 5-1/4 Inch Floppy Drives      | 2-16 |

| FIGURE 2-5. | Four 5-1/4 Inch Floppy Drives                             | 2-17 |

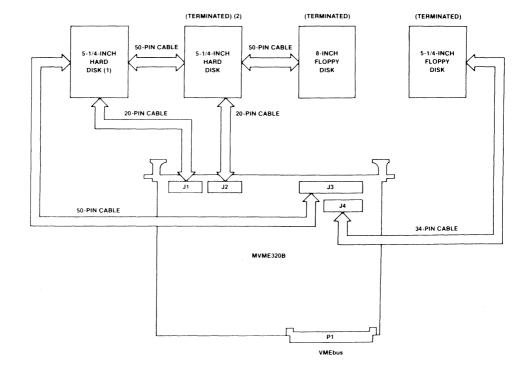

| FIGURE 2-6. | Two 5-1/4 Inch Hard, One 8-Inch and One 5-1/4 Inch Floppy |      |

|             | Drives                                                    | 2-18 |

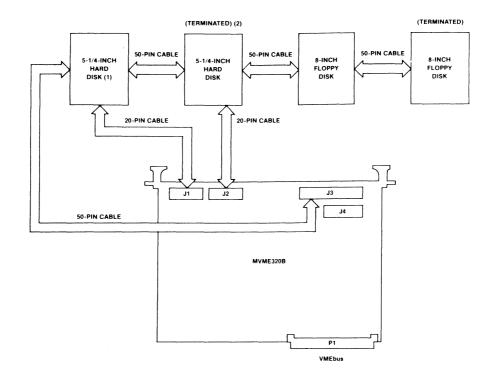

| FIGURE 2-7. | Two 5-1/4 Inch Hard and Two 8-Inch Floppy Drives          | 2-19 |

| FIGURE 2-8. | 5-1/4 Inch Floppy Drives Not Using J4                     | 2-20 |

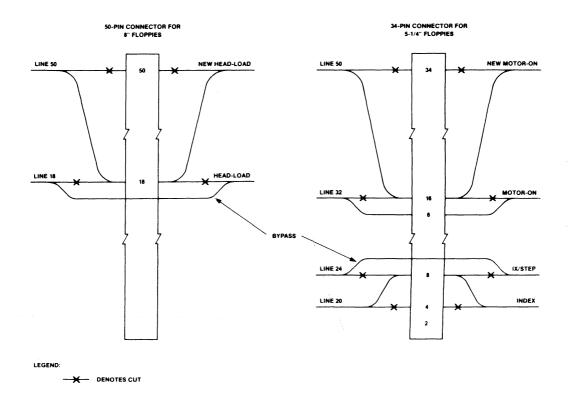

| FIGURE 2-9. | Floppy Disk Cabling                                       | 2-21 |

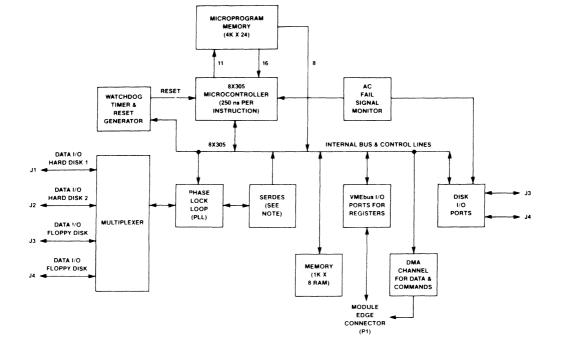

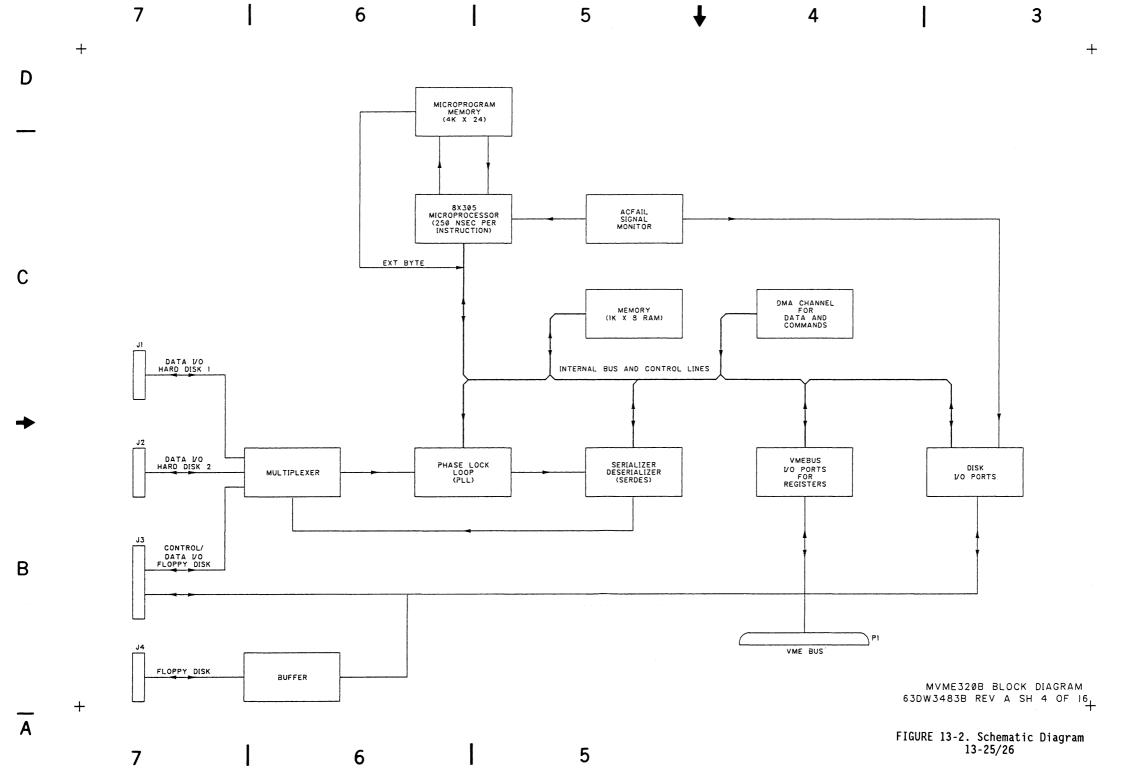

| FIGURE 3-1. | MVME320B Block Diagram                                    | 3-3  |

# <u>Page</u>

| FIGURE | 4-1.  | Internal Registers                                    | 4-1   |

|--------|-------|-------------------------------------------------------|-------|

|        |       | Internal Register Address                             | 4-2   |

| FIGURE | 5-1.  | ECA Block Format                                      | 5-1   |

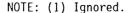

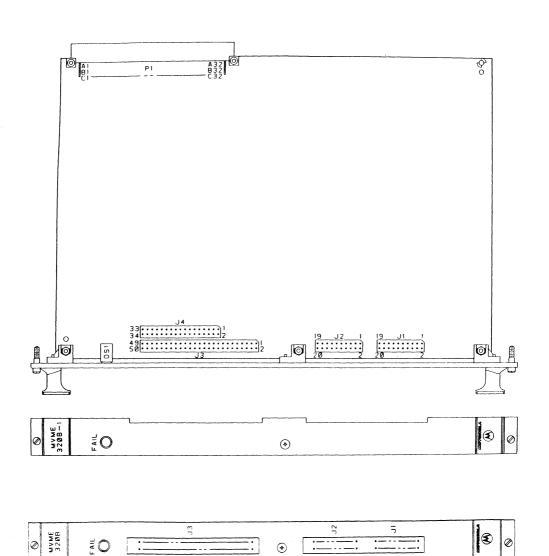

| FIGURE | 13-1. | MVME320B Parts Location Diagram (2 Sheets)            | 13-16 |

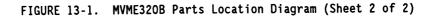

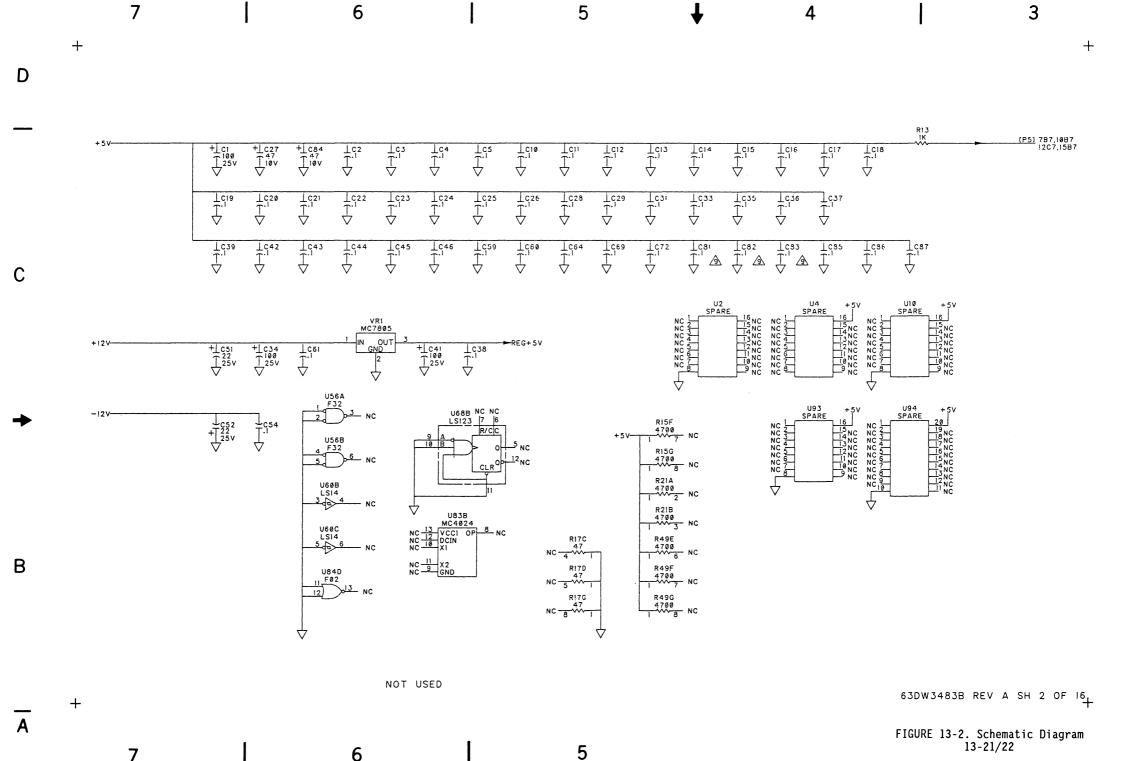

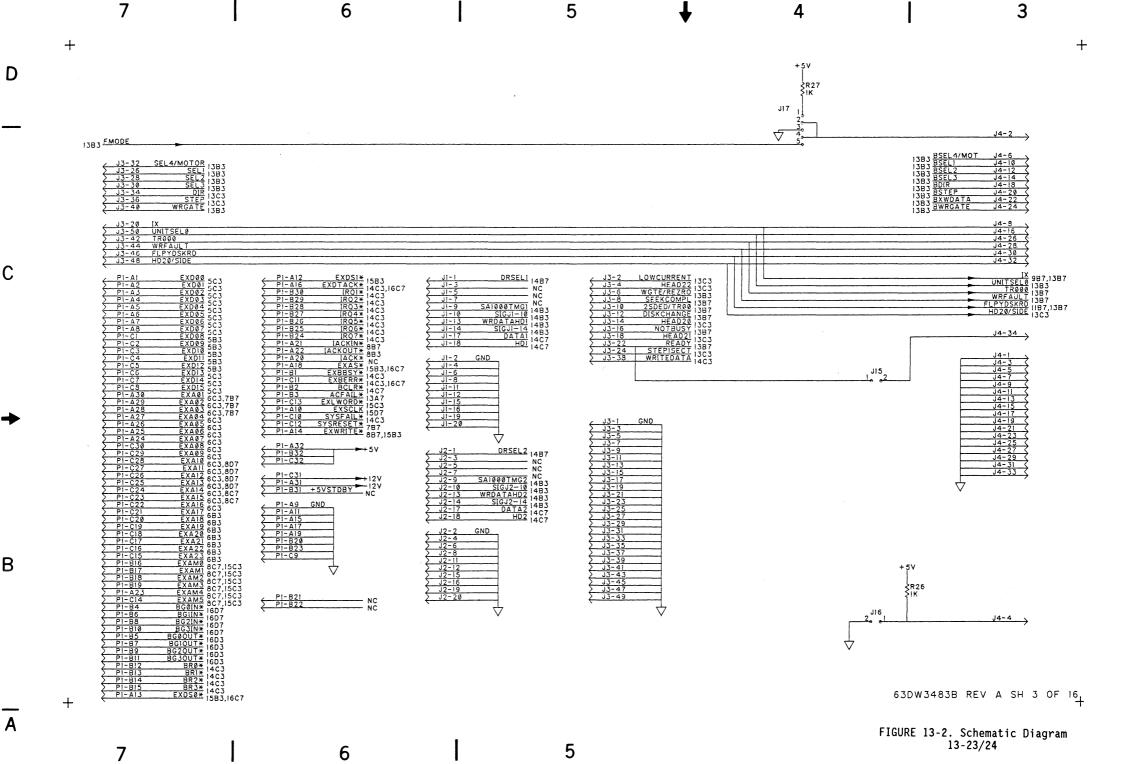

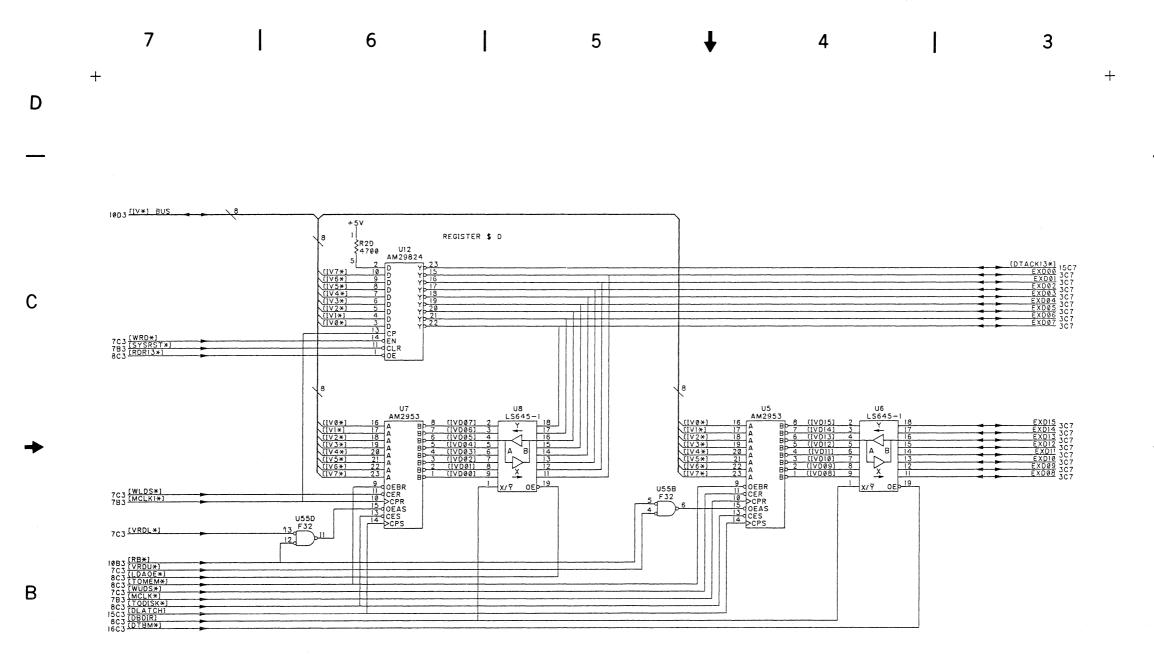

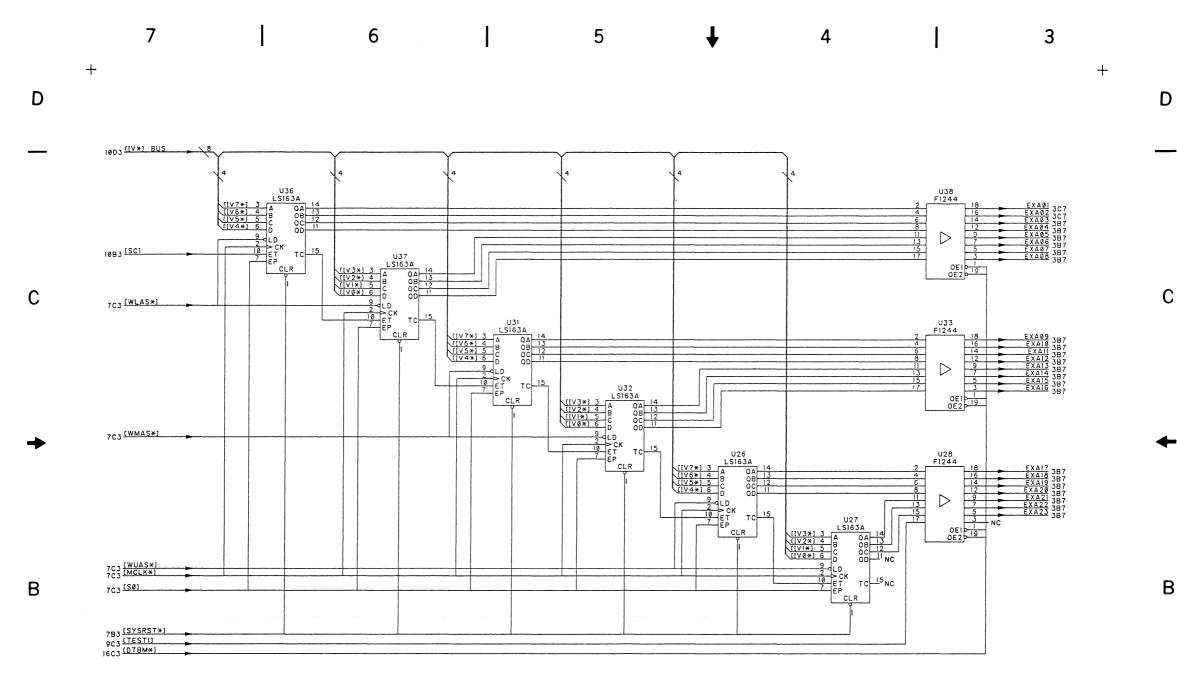

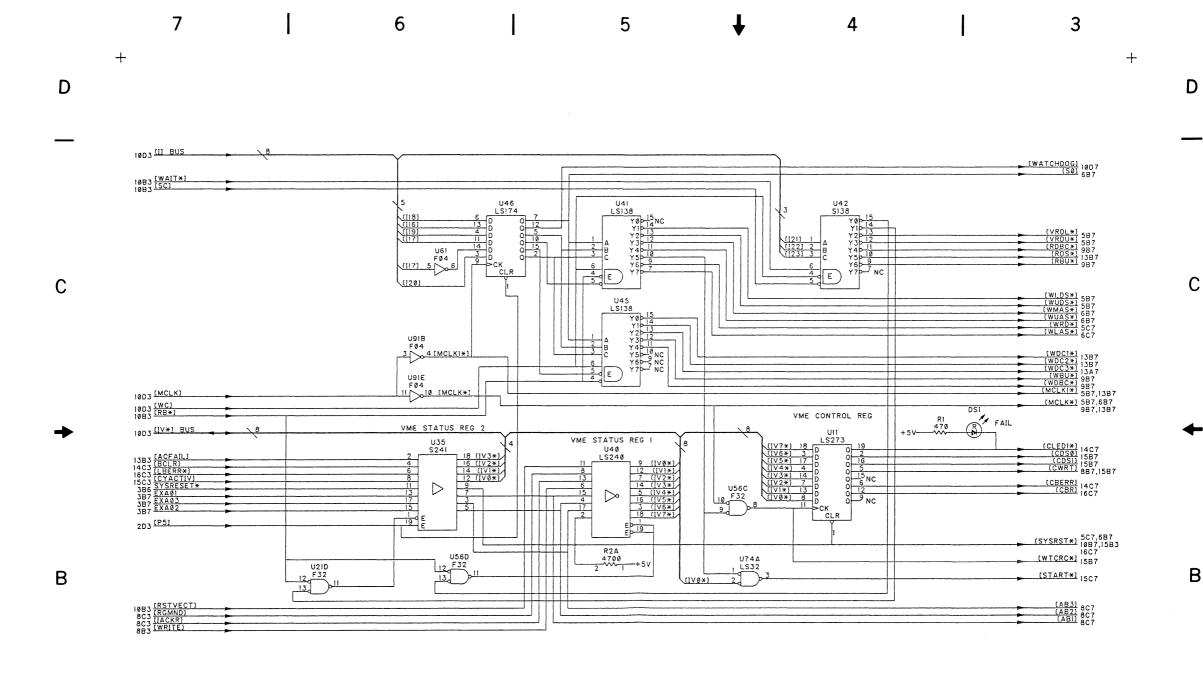

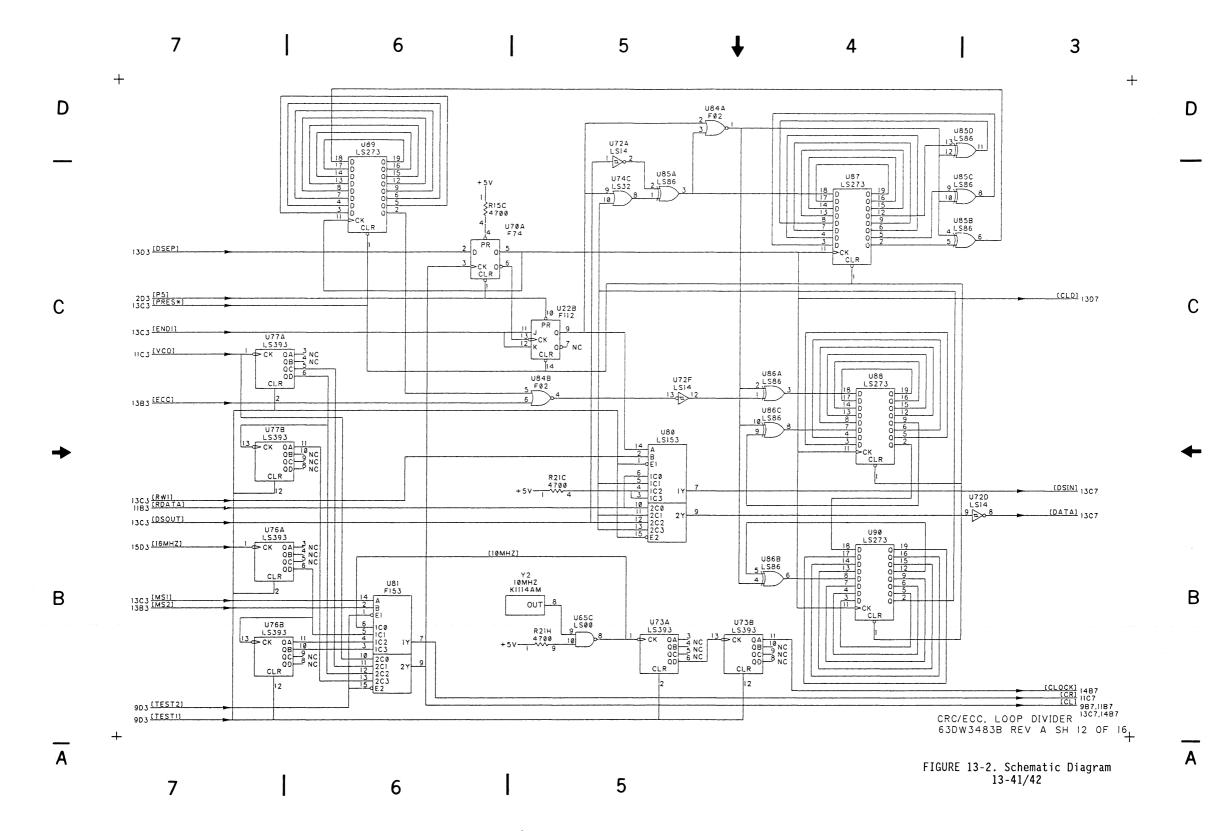

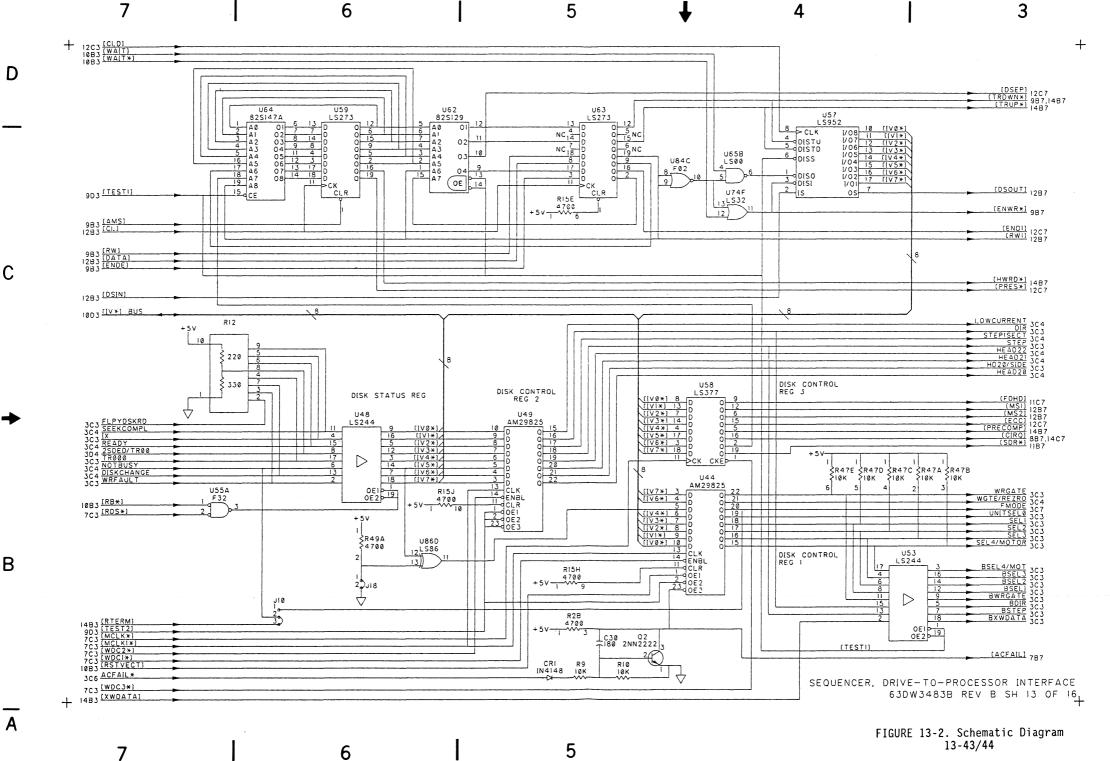

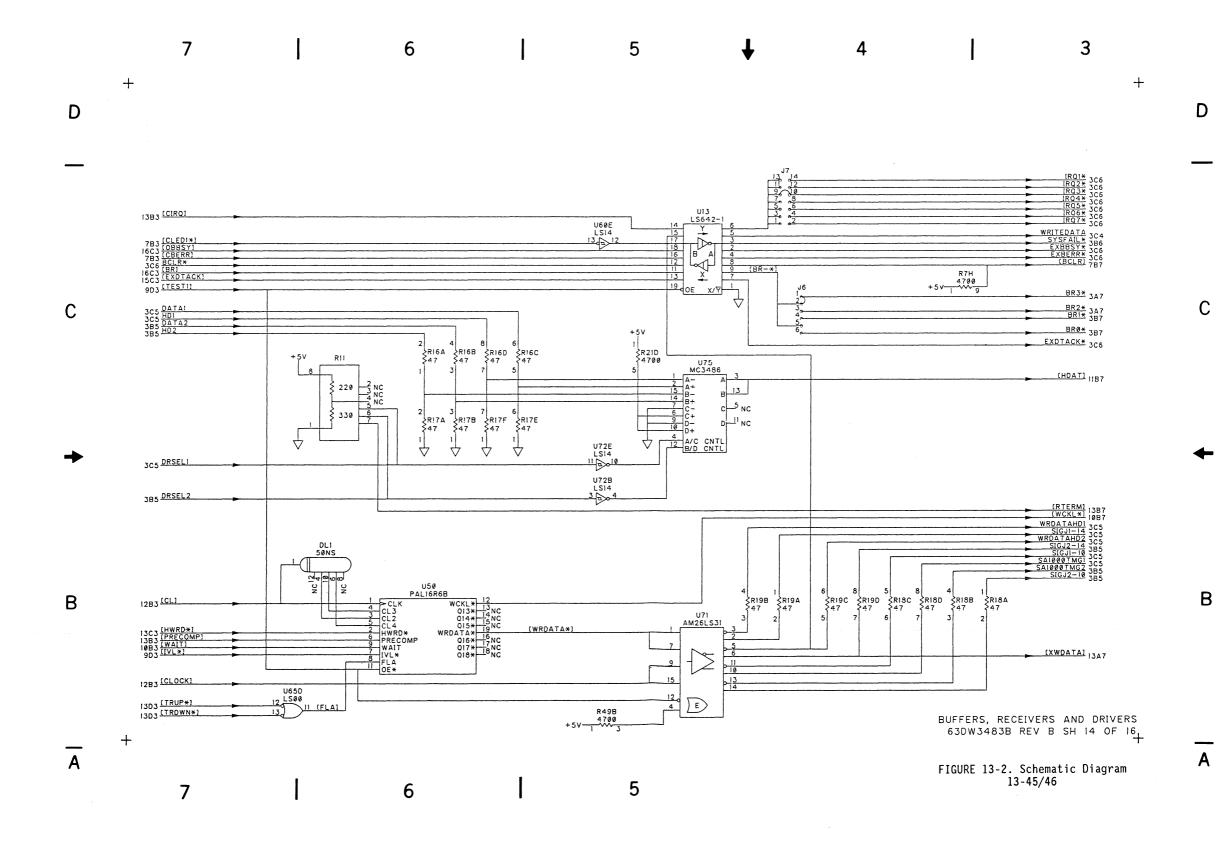

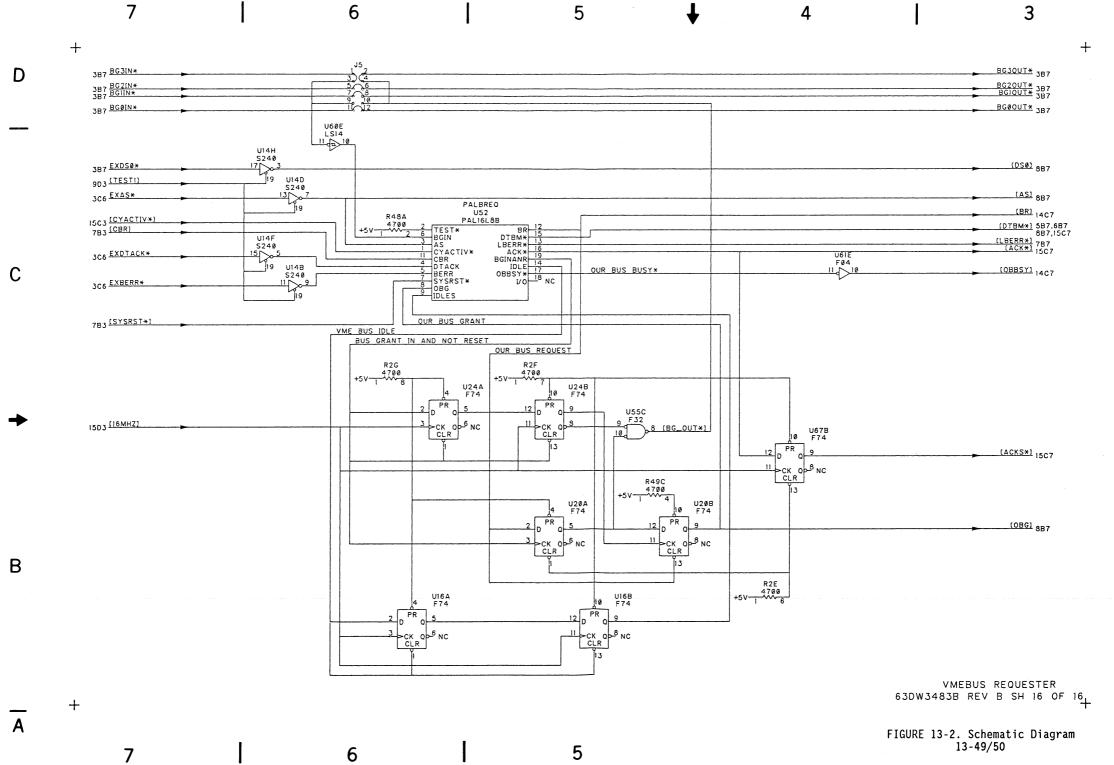

| FIGURE | 13-2. | Schematic Diagram                                     | 13-19 |

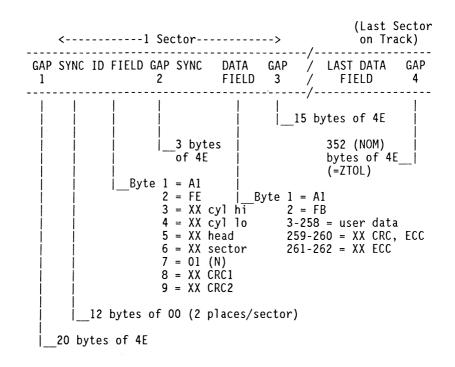

| FIGURE | A-1.  | Recommended Hard Disk Track Format (256 Bytes/Sector) | A-2   |

| FIGURE | A-2.  | IBM FM Track Format (128 Bytes/Sector)                | A-4   |

| FIGURE | A-3.  | IBM MFM Track Format (256 Bytes/Sector)               | A-5   |

| FIGURE | B-1.  | Sample ECA Block Format Shugart 450                   | B-1   |

| FIGURE | B-2.  | Sample ECA Block Format Shugart 450                   | B-3   |

| FIGURE | B-3.  | Sample ECA Block Format Shugart 860                   | B-5   |

| FIGURE | B-4.  | Sample ECA Block Format Shugart 860                   | B-7   |

| FIGURE | B-5.  | Sample ECA Block Format ST412                         | B-9   |

# LIST OF TABLES

| TABLE | 1-1.  | MVME320B Specifications                    | 1-2  |

|-------|-------|--------------------------------------------|------|

| TABLE | 2-1.  | As-Shipped Jumper Configurations           | 2-1  |

| TABLE | 5-1.  | Status Codes                               | 5-3  |

| TABLE |       | Examples of Error Codes                    | 5-4  |

|       |       | Command Option Byte                        | 5-6  |

| TABLE | 8-1.  | Summary of Format Parameters               | 8-2  |

| TABLE | 8-2.  | Track Format Definitions and Abbreviations | 8-5  |

|       |       | Connector P1 Signals                       | 13-1 |

| TABLE | 13-2. | Connectors J1 and J2 Pin Assignments       | 13-5 |

| TABLE | 13-3. | Connector J3 Pin Assignments               | 13-6 |

| TABLE | 13-4. | Connector J4 Pin Assignments               | 13-7 |

| TABLE | 13-5. | MVME320B Parts List                        | 13-9 |

THIS PAGE INTENTIONALLY LEFT BLANK.

1

### CHAPTER 1 - GENERAL INFORMATION

### 1.1 INTRODUCTION

This manual describes the Motorola MVME320B Disk Controller Module (hereafter referred to as MVME320B), which interfaces with industry-standard 5-1/4 inch hard disk drives and floppy disk drives (5-1/4 inch and 8-inch). The manual includes a general description, hardware preparation and installation instructions, a functional description, operations information, and support information for the MVME320B.

### 1.2 MVME320 FAMILY DIFFERENCES

The original MVME320 and MVME320-1 Disk Controller modules were upgraded to the MVME320A and MVME320A-1. These have been upgraded to the MVME320B and MVME320B-1. The MVME320/320A/320B have front mount drive connectors for J1, J2, and J3. The MVME320-1/320A-1/320B-1 have side mount drive connectors, intended for cables to be routed to the rear of the module.

The MVME320 and MVME320-1 were intended for use with the MVME702 and MVME702A Transition boards when connecting to 5-1/4 inch floppy drives. The MVME320A/320A-1/320B/320B-1 have an additional 34-pin drive connector (J4) for direct connection to 5-1/4 inch floppy drives. These disk controller modules are compatible with the MVME702 and MVME702A, but, because of the new J4 connector, do not require an MVME702 or MVME702A Transition board in most applications.

The MVME320A and MVME320A-1 modules, compared to the MVME320/320-1, have revised firmware with additional features, including support for large capacity hard disk drives using up to 16 heads, and speed-enhanced firmware, with interleave factors up to 2:1. The board layout was also revised and provides an onboard clock as a substitute for SYSCLK.

The MVME320A/320A-1 may be substituted for the MVME320/320-1.

Additionally, the MVME320B/320B-1 modules, compared to the MVME320A/320A-1, have revised board layout and VMEbus interface. The firmware has been revised with software selection of speed/density, when using 5-1/4 inch dual density/speed drives connected to J4. These new drives, when operated in the high density/speed mode, operate with 8-inch floppy data rates and formats, but interface with the controller module as a standard 5-1/4 inch floppy disk drive. For these drives, provision has been made to connect the READY line via optional jumpers. Another jumper connects the speed/density control line.

The MVME320B/320B-1 may be substituted for the MVME320A/320A-1 or for the MVME320/320-1. Do not attempt to replace newer boards with the older versions.

### 1.3 FEATURES

The features of the MVME320B include:

- . Combined control for hard and floppy disk drives

- . Supports MFM and FM recording

- . Cylinder number: 8- or 16-bit

- . Standard IBM formats

- . Multiple-sector read/write

- . Implied seek

- . Error correction up to 11 bits

- . 32-bit ECC code

- . Serial data rate of 5 megabits/sec hard disk

- . Serial data rates of 125/250/500 kilobits/sec floppy disk

- . 8-bit register transfer, 16-bit DMA data transfer

- . 24-bit host address and 6-bit address modifier

- . VMEbus-compatible

- . Supports drives with up to 16 heads

- . Software selectable speed/density for 5-1/4 inch floppy disk drives

### 1.4 SPECIFICATIONS

The MVME320B is a VMEbus-compatible module. The specifications are given in Table 1-1.

| TABLE 1-1. | MVME320B | Specifications |

|------------|----------|----------------|

|            |          |                |

| CHARACTERISTIC | SPECIFICATIONS |

|----------------|----------------|

|                |                |

Physical characteristics

| Height<br>Width<br>Thickness                                          | 160 mm (6.299 inches)<br>233.35 mm (9.187 inches)<br>12.7 mm (0.5 inches)           |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Power requirements<br>(at 25 degrees C<br>and no drives<br>connected) | 3.9 A typical at +5 Vdc<br>60 mA typical at +12 Vdc<br><20 mA typical at -12 Vdc    |

| Operating temperature                                                 | O degrees C to 55 degrees C at point of entry of forced air (approximately 150 LFM) |

| Storage temperature                                                   | -40 degrees C to 85 degrees C max.                                                  |

| Relative humidity                                                     | 0% to 90% (noncondensing)                                                           |

| TABLE 1-1.                           | MVME320B Specifications (cont'd)                                                                                                             |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CHARACTERISTIC                       | SPECIFICATIONS                                                                                                                               |

| Serial data rate                     | 5 megabits/second (hard disk)<br>125 kilobits/second (floppy disk)<br>250 kilobits/second (floppy disk)<br>500 kilobits/second (floppy disk) |

| Configuration                        |                                                                                                                                              |

| DTB master<br>DTB slave<br>Requester | A24, D16<br>A16, D8<br>Release when done                                                                                                     |

### 1.4.1 **Cooling Requirements**

The Motorola MVME320B VMEmodule is specified, designed, and tested to operate reliably with an incoming air temperature range 0 degrees C to 55 degrees C (32 degrees to 131 degrees F) with forced air cooling at a velocity typically achievable by using a 71 CFM axial fan. Temperature gualification is performed in a standard Motorola VMEsystem 1000 chassis. Twenty-five watt load boards are inserted in two card slots, one on each side, adjacent to the board under test, to simulate a high power density system configuration. An assembly of three axial fans, rated at 71 CFM per fan, is placed directly under the VME card cage. The incoming air temperature is measured between the fan assembly and the card cage, where the incoming airstream first encounters the module under test. Test software is executed as the module is subjected to ambient temperature variations. Case temperatures of critical, high power density integrated circuits are monitored to ensure component vendors' specifications are not exceeded.

While the exact amount of airflow required for cooling depends on the ambient air temperature and the type, number, and location of boards and other heat sources, adequate cooling can usually be achieved with 10 CFM and 150 LFM flowing over the module. Less airflow is required to cool the module in environments having lower maximum ambients. Under more favorable thermal conditions, it may be possible to operate the module reliably at higher than 55 degrees C with increased airflow. It is important to note that there are several factors, in addition to the rated CFM of the air mover, which determine the actual volume and speed of air flowing over a module.

### 1.4.2 FCC Compliance

This VMEmodule was tested in an FCC-compliant chassis, and meets the requirements for Class A equipment. FCC compliance was achieved under the following conditions:

- a. Shielded cables on all external I/O ports.

- b. Cable shields connected to earth ground via metal shell connectors bonded to a conductive module front panel.

- c. Conductive chassis rails connected to earth ground. This provides the path for connecting shields to earth ground.

- d. Front panel screws properly tightened.

- e. Drives and cables to the MVME320B were internal to the chassis.

For minimum RF emissions, it is essential that the conditions above be implemented; failure to do so could compromise the FCC compliance of the equipment containing the module.

### 1.5 GENERAL DESCRIPTION

The MVME320B is a dual-height module that provides the traditional and advanced features required to control Winchester-type hard disk drives and floppy disk drives. It can control up to four disk drives (up to two hard disk drives or up to four floppy disk drives) in many combinations. The MVME711 Transition board (or equivalent) enables the use of four hard disk drives with the MVME320B.

The MVME320B supports single- and double-density (FM and MFM) recordings on floppy disk drives, and double-density (MFM) recording on hard disk drives.

- . IBM 3740 single-density format (FM)

- . IBM System 34 double-density format (MFM)

- . Hard disk format

The controller is programmable using high-level commands over the VMEbus. The Direct Memory Access (DMA) data transfer on the host bus is 16-bit in parallel at one megabyte/second. The MVME320B is capable of handling serial data rates up to five megabits/second over the disk drive interface.

The disk interface consists of two sections:

- . Input and output ports that sense and generate "slow changing" or static control signals.

- . Serial data Input/Output (I/O) and high-speed disk control.

Because both sections are controlled by a fast internal microprocessor (8X305), the MVME320B is able to control a variety of different disk types and media formats.

1-4

The host system communicates with the MVME320B through Event Control Areas (ECAs) which reside in system memory. An ECA parameter block is set up for each disk drive (up to four) to be controlled. These areas contain information required by the MVME320B to execute disk commands. This information includes data about the requested command and the disk drive. DMA operations are defined by the ECA description of the command.

The MVME320B contains seven internal 8-bit registers. The host system requests an operation using these registers. Registers 1, 3, 5, and 7 are loaded with the 24-bit address (divided by 2) of the pointer to the ECA parameter block to be acted upon. Register 1 is the Least Significant Byte (LSB). After a command is accepted for execution, no further interaction between the host processor and the MVME320B need occur until the command is completed. For the register formats, see Figure 4-1.

The MVME320B microprogram uses the data contained in the ECA block to generate disk interface signals and perform the requested drive I/O. Data transfers to and from floppy disks are executed in real-time (with 2-byte buffering). Data transfers to and from Winchester drives are buffered on a sector basis.

The host is informed of completion of a command by an interrupt request signal from the MVME320B. The MVME320B writes the return status information to the appropriate ECA block memory. On interrupt service, the host reads the interrupt vector number from the internal vector number register on the data bus.

### 1.6 DRIVE COMPATIBILITY AND CAUTIONS

- a. All ST506 and SA400 drives are not the same. Although designed to meet the ST506 and SA400 standard, all such drives are not identical, and the MVME320B may be sensitive to some of these differences. The user will need to independently qualify the drives to be used in an MVME320B system. When using 1.6Mb (unformatted) 5-1/4 inch drives in the high density mode, the user will also have to qualify the media. High density media is not usable in the low density mode.

- b. The user should take care to comply with vendor environmental specifications for drives and media, and must be careful to lock out those sectors corresponding to media defects as identified by the drive vendor and the user's incoming inspection procedures.

- c. The MVME320B supports interleave factors of up to 2:1. It is important to select the interleave factor that matches your system performance. It is suggested that you try several interleave factors to decide which one will give you the best performance from your system.

- d. The MVME320B supports drives with up to four head selects.

- e. Disk drives which have power supplies separate from the MVME320B must not be powered up when the MVME320B is not powered up; power up these drives <u>after</u> the MVME320B is on, and remove the drive power <u>before</u> turning off the MVME320B.

- f. Do not open or close the floppy disk drive door when the drive is selected, or about to be selected.

- g. Do not power down the drive when the drive is selected, or about to be selected.

- h. Remove the "READY" jumper, J15, when using drives which are not truly ready when this signal is asserted.

- i. Floppy disk reads are not buffered; therefore, a heavily loaded VMEbus can cause floppy I/O not to complete. One suggested solution is to raise the priority of the MVME320B.

### 1.7 DUAL DENSITY PERFORMANCE CONSIDERATIONS

Each time that the drive speed is changed, the drive requires that a "speed change" time delay occur. At present, this delay is 1.25 seconds. Whenever the 320B firmware generates a change in floppy speed, such as when selecting another floppy to be run at a density different from the last floppy selected, or when changing density on a single floppy, the "speed change" time delay will be invoked. For multiple accesses to a floppy at the same density, no time delay is necessary, except for floppy drives which do not sense the pin 2 signal when not selected. THESE DRIVES ARE NOT SUPPORTED IN THE DUAL DENSITY MODE.

When copying from one density to the other, for best performance, the "speed change" time delay may be avoided by copying in large blocks, and not copying directly from floppy to floppy. Reading all the desired records into a buffer (memory or to hard disk) and then out to the floppy would invoke the "speed change" time delay only once. Repeated read/write operations between high and low speed floppies would invoke the time delay for each access to a floppy.

### 1.8 **PROGRAMMING CAUTIONS**

Users writing their own drivers should be aware of some functions that need to be handled in software:

### NOTE

These functions have been implemented in Motorola's software drivers.

a. All hard disk media have defective areas which increase with the size of the drive. The user is responsible for determining, with the assistance of the disk drive vendor, the location of defective areas of the hard disk media, and through software, locking out these areas.

- b. It is possible for the MVME320B to incorrectly return a Main Status Code of zero (no error). To be assured of a true "No Error" condition:

- . test Main Status for 00

- . test Extended Status for 00 00

- . for READ/WRITE operations, also verify that the return value of the bytes transferred equals bytes requested.

- . for READ operations, also verify ECC remainder equal to 00 00 (if using ECC).

- c. Command Codes should be verified. The MVME320B ignores invalid codes; therefore, a driver waiting for an interrupt after an invalid code would wait indefinitely.

- d. Verify the Buffer Address. A transfer to an address where no memory is installed may return with an incorrect "No Error" message.

- e. Verify that the Cylinder Number is "in range." An invalid cylinder number causes the current command and the following command to fail.

- f. Verify the Drive Type. An invalid drive type may cause the floppy to be erroneously selected.

- g. Set the Main Status to "Busy" (Code = 07) when issuing commands, and then verify (or wait until) non-busy after the MVME320B returns an interrupt. The MVME320B sometimes interrupts before it updates the ECA.

Busy code = 07 is not used by all drivers. Other codes such as 08 or FF, which will not be confused with an error condition, may be used. Code 07 is used by VERSAdos and is shown in "Main Status Codes," Table 5-1.

- h. Re-try the Recalibrate command at least once if it returns an error (Main Status = 01; Extended Status = 2080). On large drives, it is possible for the Recalibrate to time-out before the head is "home."

- i. Following a successful re-try, the Main Status is cleared, but the Extended Status still reflects the condition that forced the re-try.

- j. Do not attempt to execute concurrent operations; this can generate problems.

- k. Do three to five re-tries in the driver. Many command errors returned by the MVME320B are "soft" errors, meaning that the command may work correctly if tried again. Firmware re-tries, requested through the ECA table entry, only occur for Cycle Redundancy Check/Error Correction Code (CRC/ECC) errors and, occasionally, DMA over/underrun errors. The driver should initiate three to five re-tries for the following error codes:

<u>Main/Extended\_Status</u>

Description

| 01-0002 (NOTE) | CRC Error                             |

|----------------|---------------------------------------|

| 01-0008 (NOTE) | Identifier not found                  |

| 01-0080 (NOTE) | Positioning Error                     |

| 01-0102        | CRC/ECC Error                         |

| 01-2080        | Positioning Error/Data Point Time-out |

| 09-8000        | Throughput error on DMA operation     |

- NOTE: Any combination of these error codes is possible; all other codes appear as shown.

- Do not use the "Sector Out of Range" status bit in the Extended Status Word; it is not implemented. Only those status conditions listed in item "k" above and those listed below are implemented:

| 02-0010 | Drive Not Ready (do not re-try)         |

|---------|-----------------------------------------|

| 06-0040 | Write Protect Violation (do not re-try) |

| 08-1800 | Drive Not Available (do not re-try)     |

| 10-0800 | Command Aborted by Driver               |

### 1.9 RELATED DOCUMENTATION

The following publications may provide additional helpful information. If not shipped with this product, they may be purchased from Motorola's Literature Distribution Center, 616 West 24th Street, Tempe, AZ 85282; telephone (602) 994-6561.

| DOCUMENT TITLE                                       | MOTOROLA<br>PUBLICATION NUMBER |

|------------------------------------------------------|--------------------------------|

| VMEbus Specification Manual                          | HB212/D                        |

| MVME702/MVME702A Disk Interface Module User's Manual | MVME702                        |

| MVME711 Transition Module User's Manual              | MVME711                        |

#

CHAPTER 2 - HARDWARE PREPARATION AND INSTALLATION INSTRUCTIONS

### 2.1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the MVME320B.

### 2.2 UNPACKING INSTRUCTIONS

### NOTE

If the shipping carton is damaged upon receipt, request carrier's agent be present during unpacking and inspection of equipment.

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present. Save packing material for storing and reshipping of equipment.

## 2.3 HARDWARE PREPARATION

### CAUTION

### AVOID TOUCHING AREAS OF INTEGRATED CIRCUITRY; STATIC DISCHARGE CAN DAMAGE CIRCUITS.

-----

The MVME320B contains the following jumper-selectable configuration options. The as-shipped factory jumper configurations are listed in Table 2-1. Header locations are shown in Figure 2-1.

|                                                                                           | TABLE 2-1.   | As-Shipped Jumper Configurations                                                                                                                          |

|-------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEADER                                                                                    |              | INITIAL FACTORY<br>JUMPER PLACEMENT                                                                                                                       |

| J5<br>J6<br>J7<br>J8<br>J9<br>J10<br>J11<br>J12<br>J13<br>J14<br>J15<br>J16<br>J17<br>J18 |              | 1-3, 2-4, 5-6, 7-8, 11-12<br>1-2<br>9-10<br>2-3<br>3-4, 9-10, 11-12<br>2-3<br>1-2, 3-4<br>1-2<br>2-3<br>1-2<br>1-2<br>Not jumpered<br>Not jumpered<br>1-2 |

| NOTE: J                                                                                   | 1, J2, J3, a | and J4 are cable connectors.                                                                                                                              |

2-2

FIGURE 2-1. MVME320B Connector and Header Locations

🕀 MOTOROLA

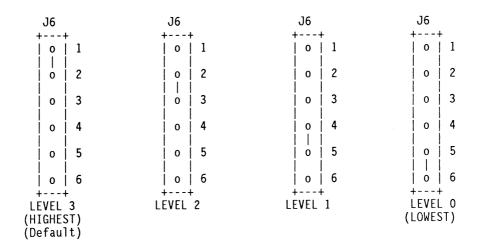

# 2.3.1 Bus Arbitration Level (J5 and J6)

Bus arbitration priority level is selected at headers J5 (BUS GRANT) and J6 (BUS REQUEST).

2

### 2.3.2 Interrupt Level (J7 and J11)

Interrupt level selection is accomplished at headers J7 (IRQ) and J11 (IACK). Please note that both IRQ and IACK must be set at the same interrupt level.

| Interrupt<br><u>Level</u>          |                            | <u>J7</u> | (IRQ)                                  | <u>J11 (IACK)</u>                                                                              |

|------------------------------------|----------------------------|-----------|----------------------------------------|------------------------------------------------------------------------------------------------|

| (highest)<br>(default)<br>(lowest) | 6<br>5<br>4<br>3<br>2<br>1 | 9-<br>11- | 8-4<br>5-6<br>7-8<br>-10<br>-12<br>-14 | (highest) 6 3-4, 5-6<br>5 1-2, 5-6<br>4 5-6<br>(default) 3 1-2, 3-4<br>2 3-4<br>(lowest) 1 1-2 |

| J7                                 |                            |           |                                        | J11                                                                                            |

| 1                                  | 0                          | 0         | 2                                      | 1   00   2                                                                                     |

| 3                                  | 0                          | 0         | 4                                      | 3 00 4                                                                                         |

| 5                                  | 0                          | 0         | 6                                      | 5   0 0   6                                                                                    |

| 7                                  | о                          | 0         | 8                                      | DEFAULT = IACK LEVEL 3                                                                         |

| 9                                  | 0                          | 0         | 10                                     |                                                                                                |

| 11                                 | 0                          | 0         | 12                                     |                                                                                                |

| 13                                 | 0                          | 0         | 14                                     |                                                                                                |

| DEFAUL                             | T = ]                      | IRQ I     | '<br>_EVEL 3                           |                                                                                                |

# 2.3.3 Address Modifier (J8)

The address modifier is selected at header J8.

| To Select<br><u>Address Modifier</u> | Indicating                                   | Jumper<br><u>Pins</u> |

|--------------------------------------|----------------------------------------------|-----------------------|

| 29 or \$2D                           | Short Non-privileged<br>or Supervisor access | 2-3 (DEFAULT)         |

| only \$2D                            | Short Supervisory<br>access only             | 1-2                   |

| , | J8 |   |   |

|---|----|---|---|

| + |    | + |   |

| 1 | 0  |   | 1 |

|   |    |   |   |

|   | 0  |   | 2 |

|   |    |   |   |

|   | 0  |   | 3 |

| + |    | + |   |

|   |    |   |   |

# 2.3.4 Address Decode (J9)

Address decoding is done at header J9, where jumper inserted = 0, no jumper = 1.

|            |             |    | +. | JS | )  | ÷  |                                    |

|------------|-------------|----|----|----|----|----|------------------------------------|

| Address    |             | 1  |    | 0  | 0  | 2  |                                    |

| <u>Bit</u> | <u>Pins</u> |    | İ  |    |    |    |                                    |

|            |             | 3  | 3  | 0  | -0 | 4  |                                    |

| A10        | 11-12       |    |    |    |    |    |                                    |

| A11        | 9-10        | 5  | 5  | 0  | 0  | 6  |                                    |

| A12        | 7-8         |    |    |    |    |    | DEFAULT = 320 #1                   |

| A13        | 5-6         | 7  | '  | 0  | 0  | 8  |                                    |

| A14        | 3-4         |    |    |    |    |    | Short I/O = \$B000                 |

| A15        | 1-2         | 9  |    | 0  | -0 | 10 | A24 = \$FFB000<br>A32 = \$FFFFB000 |

|            |             | 11 |    | 0  | -0 | 12 |                                    |

|            |             |    | +- |    |    | r  |                                    |

|            |               |    |    | J9 |    |                                    |

|------------|---------------|----|----|----|----|------------------------------------|

| Address    |               | 1  | 0  | 0  | 2  |                                    |

| <u>Bit</u> | <u>Pins</u>   | 3  | 0. | 0  | 4  |                                    |

| A10<br>A11 | 11-12<br>9-10 | 5  |    | 0  | 6  |                                    |

| A12        | 7-8           | 5  |    | 0  |    | 320 #2                             |

| A13<br>A14 | 5-6<br>3-4    | 7  | 0- | 0  | 8  | Short I/O = \$ACOO                 |

| A15        | 1-2           | 9  | 0  | 0  | 10 | A24 = \$FFAC00<br>A32 = \$FFFFAC00 |

|            |               | 11 | 0  | o  | 12 | ASE - WITTACOU                     |

|            |               |    | +  | •  | -  |                                    |

# 2.3.5 Reserved (J10)

J10

(Default)

## 2.3.6 PROM Enable (J12)

Pins 1-2 are jumpered with a removable jumper. This header can be used to disable the PROMs for factory test. (The PROMs are disabled if no jumper is installed.)

| J12                             |           |  |  |

|---------------------------------|-----------|--|--|

| ++                              |           |  |  |

| 0   1<br>     <br>  0   2<br>++ | DEFAULT = |  |  |

# 2.3.7 Clock Select (J13)

This header is used to select onboard clock or the system clock (SYSCLK).

| J13                                         | J13          |

|---------------------------------------------|--------------|

| 1 2 3                                       | 1 2 3        |

| 0 00                                        | 00 0  <br>++ |

| USES ONBOARD 16 MHz<br>OSCILLATOR (Default) | USES SYSCLK  |

# 2.3.8 **PROM Size (J14)**

PROM size is selected by J14. The user should not change the configuration.

| J14                  | J14     |

|----------------------|---------|

| ++                   | ++      |

| o   1                | 0   1   |

| 0 2                  | 0 2     |

| 0 3                  | 0 3     |

| ++                   | ++      |

| 4K PROM<br>(Default) | 8K PROM |

# 2.3.9 READY Line (J15)

| J15                     |                                                                                                                         |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1   0  <br>   <br>2   0 | J4-34 is connected to J3-22 (READY line).<br>(Used for floppy disk drives which are ready<br>for access at READY true.) |

| ++<br>(Default)         |                                                                                                                         |

| .115                    |                                                                                                                         |

| J15<br>++     |                                                                                           |

|---------------|-------------------------------------------------------------------------------------------|

| 1   0         | J4-34 is not connected.                                                                   |

|               | (Used for floppy disk drives which are not                                                |

| 2   0  <br>++ | guaranteed to be ready for access at READY true, or for drives which have no READY line.) |

# 2.3.10 J4-4 Option (IN USE/HEAD LOAD) (J16)

J4-4 defined as logic high by 1k ohm pullup resistor to +5 Vdc.

- +---+ 1 | o | | | J4-4 defined as logic low by grounding at J16. 2 | o | +---+

- 2.3.11 J4-2 Option (SPARE/DENSITY) (J17)

|     | J17<br>++     |                                         |

|-----|---------------|-----------------------------------------|

| 1   | 0             | J4-2 is SPARE (n.c.)                    |

| 2   | 0             |                                         |

| 3   | 0             |                                         |

| 4   | 0             |                                         |

| 5   | 0             |                                         |

| (De | ++<br>efault) |                                         |

|     |               |                                         |

|     | J17           |                                         |

| 1   | 0             | DENSITY                                 |

| 2   | 0             | J4-2 is defined as logic high by 1k ohm |

| 3   | 0             | pull-up resistor.                       |

| 4   | 0             |                                         |

| 5   | 0  <br> +     |                                         |

|     |               |                                         |

|        | J17<br>++                   |                                                                                                                                              |

|--------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | 0                           | DENSITY                                                                                                                                      |

| 2      | 0                           | J4-2 is defined as logic low by grounding                                                                                                    |

| 3      | 0                           | at J17.                                                                                                                                      |

| 4      | 0                           |                                                                                                                                              |

| 5      | 0                           |                                                                                                                                              |

| -      | ++                          |                                                                                                                                              |

|        |                             |                                                                                                                                              |

|        | J17                         |                                                                                                                                              |

| 1      | J17<br>++<br>  o            | DENSITY                                                                                                                                      |

| 1<br>2 | ++                          | J4-2 is driven by firmware control register.                                                                                                 |

| -      | ++<br>  0  <br>             | J4-2 is driven by firmware control register.<br>Logic high for 8-inch ECA table; logic low<br>for 5-1/4 inch ECA table, unless J18 jumper is |

| 2      | ++<br>  0  <br>  0  <br>  0 | J4-2 is driven by firmware control register.<br>Logic high for 8-inch ECA table; logic low                                                   |

| 2<br>3 | ++<br>  0  <br>  0  <br>  0 | J4-2 is driven by firmware control register.<br>Logic high for 8-inch ECA table; logic low<br>for 5-1/4 inch ECA table, unless J18 jumper is |

# 2.3.12 Density Mode (J18)

J18

| 1 2<br>++ J4-2 is high for 8-inch ECA table;<br>  oo   J4-2 is low for 5-1/4 inch ECA table.<br>++<br>(Default) |

|-----------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------|

J18

| ++ | 0 | +<br>0 | J4-2 is low for 8-inch<br>J4-2 is high for 5-1/4 |  |

|----|---|--------|--------------------------------------------------|--|

|----|---|--------|--------------------------------------------------|--|

ᄊ MOTOROLA

### 2.4 MVME320B SOFTWARE SPEED CONTROL

To use 5-1/4 inch dual density floppy drives in the high density (1.6Mb, unformatted) and low density modes with the MVME320B and MVME320B-1, under software speed control, do the following:

- a. On the MVME320B module, install a jumper on J17, pins 4 and 5, to connect DENSITY signal to J4, pin 2.

- b. On the MVME320B module, install a jumper on J15, pins 1 and 2, to connect the READY line. Please note that if you are using a drive which asserts READY before the drive is at speed, DO NOT CONNECT JUMPER J15. The MVME320B will then ignore the READY, and assume READY after 1.25 seconds.

- c. The drive must be appropriately jumpered for pin 2 control of DENSITY (speed): 300 R.P.M. = low density, 360 R.P.M = high density. The MVME320B, as shipped, uses pin 2 "high" for high density, and pin 2 "low" for low density. To reverse this, remove the jumper on J18 on the MVME320B.

- d. The ECA table selects the density mode. Refer to Chapter 5 for more information on the ECA table.

DRIVE TYPE, offset address \$2E in the ECA table, defines the density. Drive types 0 and 1 are 8-inch floppy disks. Drive types 4 and 5 are 5-1/4 inch floppy disks. To select high density, set up an 8-inch floppy ECA table. To select low density, set up a 5-1/4 inch floppy ECA table.

- e. The high density mode requires media specially certified for this purpose. Normal media will not suffice. Note that high density media typically will not work in low density mode.

- f. The 5-1/4 inch MOTOR ON (pin 16) is supported in both low and high density mode. Jumper the drive to enable the motor by the MOTOR ON signal (pin 16).

- g. Since the MVME320B controls the MOTOR ON function, the drive need not have the HEAD LOAD function.

- h. If the drive has a HEAD LOAD function, jumper it for HEAD LOAD at MOTOR ON. This avoids excessive "tap-tap" head loading wear on both media and heads.

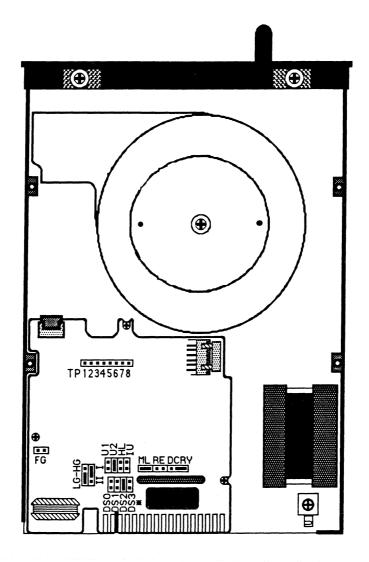

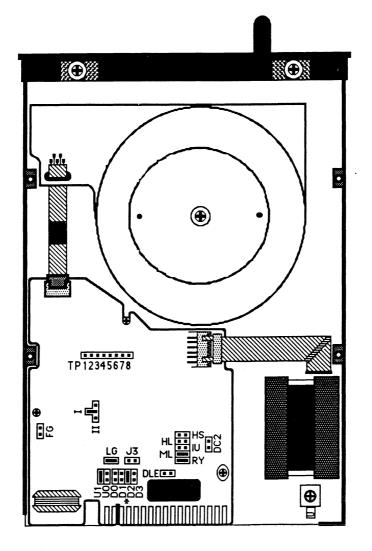

The following examples of disk drive configuration assume that the jumper on J18 on the MVME320B has been removed. TEAC drive FD-55GFV-17-V (Motorola part number 01-W0316B01) is configured as shown in Figure 2-2. TEAC drive FD-55GFR-606-U (Motorola part number 01-W0316B02) is configured as shown in Figure 2-3.

For software selection of speed/density, two jumper changes must be made on the MVME320B: the removal of the jumper on J18 and the installation of a jumper on pins 4-5 of J17 (refer to sections 2.3.11, 2.3.12, and 2.4.c).

FIGURE 2-2. TEAC Drive FD-55GFV-17-V (Motorola Number 01-W0316B01)

For software selection of speed/density, two jumper changes must be made on the MVME320B: the removal of the jumper on J18 and the installation of a jumper on pins 4-5 of J17 (refer to sections 2.3.11, 2.3.12, and 2.4.c).

FIGURE 2-3. TEAC Drive FD-55GFR-606-U (Motorola Number 01-W0316B02)

HARDWARE PREPARATION

2

### 2.5 INSTALLATION CONSIDERATIONS

This section should be read and understood prior to installing the MVME320B.

### WARNING

WHEN HANDLING OR TRANSPORTING THE MVME320B, CARE MUST BE TAKEN TO AVOID STATIC DISCHARGE DAMAGE TO THE INTEGRATED CIRCUITS ON THE MODULE. CONDUCTIVE MATERIALS SUCH AS ALUMINUM FOIL OR SPECIALLY TREATED FOAM IN CONTACT WITH THE SOLDER-SIDE SURFACE OF THE MODULE WILL BE ADEQUATE PROTECTION AGAINST SUCH POTENTIAL DAMAGE.