# Signetics

VMSbus Specification Manual REV A4

Nov. 1983

No. No.

# VMSbus

# (VME SERIAL BUS)

# SPECIFICATION MANUAL

# PRELIMINARY

# PUBLISHED BY

# THE

# VMEbus MANUFACTURERS' GROUP

# Revision A4

# November, 1983

# 1. INTRODUCTION: WHY DO WE NEED THE SERIAL BUS ?

No matter how fast and capable computers and microprocessors become, there always seem to be applications which are just beyond the ability of a particular processor. A processor may not be fast enough to process inputs in "real time", or may not provide fast enough response time to satisfy users, etc. It simply takes too long to "get the job done".

In the past such applications often had to be delayed until a new and faster processor was developed, which was also cost-effective for the application. But recent microprocessors have added hardware features which allow more than one of them to be hooked together in a system. Such <u>multiprocessor</u> systems provide an alternative to waiting for a faster processor to be developed. Two or more processors can share the processing load of the system and provide the necessary "real time" processing, faster response time, and so on.

A well-known and respected lady computer scientist uses an analogy from the early days of oxcarts. When the first oxcart users and engineers encountered a load which was too heavy for their ox to pull, they did not put off moving the load until a larger ox was developed. They simply hooked up two oxen to the cart and did the job. Her message is that multiprocessor systems should be more widely used.

To some extent, multiprocessing is a field in which hardware development has outrun software development. Much of current software thinking and techniques are tied to the single-processor systems for which existent software was developed. Multiple processor systems pose new problems for system software designers, and solutions to these problems are still evolving.

A number of possible ways to design software for multiprocessing have been developed. Single-processor <u>multitasking</u> techniques can be extended for multiple processors. Multitasking can be thought of as the sharing of a processor among several tasks (programs or parts of a program). The processor is first assigned to one task which it executes for a while, then to another task for a while, then to another, etc.

The most straightforward way to extend single-processor multitasking into the multiprocessor environment is to give each processor a more or less fixed set of tasks which it executes. More complex multiprocessor software techniques include "anonymous processor" systems, wherein any available processor can execute any task in the system.

Other computer scientists argue that classic multitasking techniques are unreliable in the multiprocessor environment because the number of ways the processors can interact is very large, and it is too easy for some interactions to be overlooked by system designers. These people say that the only way to assure reliable, fully debugged multiprocessor software is to program all the processors in one program, which specifies and controls all the ways in which the processors can interact.

Alternative approaches will probably continue to be developed and debated for some time. However, in all of the approaches there are certain common needs. If we can design system hardware which helps satisfy these needs, it makes the implementation of multiprocessor systems more straightforward for everyone.

The serial bus is intended to meet the needs of multiprocessor systems. The following sections describe some of these needs and how the serial bus provides for them.

#### 1.1 THE SERIAL BUS ALLOWS THE COMMUNICATION OF EVENTS

An <u>event</u> could be defined as any significant occurrence which is not a direct, immediate, and normal result of what the processor is currently doing. For example, if a program commands a disk controller to start a transfer, we would not consider the fact that the disk controller starts to be an event. The completion of the disk transfer is an event.

We will discuss events as they impact multitasking systems. In such systems there is normally a task for each event that the system recognizes. When an event occurs, the processor may be <u>reassigned</u> from executing one task to executing another.

A <u>task</u> can also cause the reassignment of the processor. For example, the task which is currently being executed by the processor may need to wait for an event to occur before it can proceed. In this case it requests system software to reassign the processor to other tasks until the event occurs. As another example, a task may request that another task be executed. Communication between tasks is often done through such requests.

Each task in a multitasking system has an associated "priority". (All of the tasks can be "rank ordered" from the highest priority to the lowest.) If an event occurs, for which the task priority is higher than that of the task which the processor is currently executing, a reassignment takes place. The processor stops executing the instructions of the old task and starts executing those of the new event's task.

There are two kinds of events: those which occur outside the processor (external events), and those which occur inside the processor (internal events). External events are commonly communicated to the processor by means of <u>interrupts</u>. Internal events don't need to be communicated to the processor, but they may still cause it to be reassigned to a new task. (An example of an internal event is an attempt to divide by zero.)

Microprocessors have a small number of "interrupt request" lines that can be used to communicate events to them. Since there are usually many possible events, they must all share these interrupt request lines. When the processor detects an interrupt, it must gather more information in order to figure out which event has occurred and which task is to be executed. There are several methods for doing this: polling of I/O status registers, reading a "vector" from the interrupting device, etc. In each case the processor does one or more "read cycles" to collect this information.

In some systems, an interrupt requires the processor to read from the status registers of all possible interrupting devices until it finds one that is generating an interrupt. Since a lot of reads may be required, this method is rather inefficient. More recent processors use vectored interrupt techniques.

Vectored interrupts work as follows. Each device capable of generating interrupts is assigned one or more "vectors". Each vector leads to an address where that event's task begins in the processor's memory. When the event occurs and the processor is interrupted, it reads this vector from the interrupting device. This tells the processor the starting address of the new task to execute.

Earlier we said that tasks can communicate with each other to accomplish a common purpose. When there are several processors, it may turn out that a task being executed on one processor may need to communicate with a task which is being (or will be) executed on another. Thus it is important that the processors have a quick way to communicate events BETWEEN EACH OTHER. (It's no longer sufficient to simply communicate all events to a single microprocessor.)

When multiprocessing systems are built using existing backplane buses this may not be possible. For example, backplanes which were designed for single processor systems may have only one interrupt line. When building multiprocessing systems, such an interrupt structure simply won't do the job.

The newer backplane buses have a provision for directing interrupts to several different processors. For example, VMEbus has seven interrupt request lines which can each be monitored by a different processor. If a device in the system needs to communicate an event to a processor, it can request an interrupt on a line that is monitored by that processor.

But even this approach has its limitations. When a processor acknowledges (answers) an interrupt request, the processor typically must read a vector before assigning itself to the new task. If this is done as a transfer on the system bus, the processor may have to <u>request</u> the bus and <u>wait</u> until it becomes available. If other bus masters are using the bus, this delay may be too long or too unpredictable to satisfy the needs of time-critical, high performance applications. Sometimes the problem can be solved by rearranging the priorities of the various bus masters, but the other masters' needs for the bus may be equally or more important to the performance of the system.

We conclude from all this that what is needed is a path specifically designed for communicating events. To be useful in a multiprocessing system, this path must allow any processor to communicate events to any other, as well as permitting other devices in the system to communicate events to any of the processors. Such communication is one of the primary purposes of the serial bus.

## 1.2 THE SERIAL BUS AIDS IN "FAULT TOLERANT" SYSTEM DESIGN

Another trend in microprocessor systems is toward applications which demand "fault tolerance". This simply means that a system must be able to continue operation despite one or more hardware failures. One way to satisfy this need is by using several processors in a system, and providing ways for each processor to observe the operation of all the other boards, to detect when one is malfunctioning. Such systems can also include hardware registers on each board which control the board's backplane bus drivers. If one of the processors detects a malfunctioning board, it can write into a control register on that board and turn off the board's bus drivers, effectively "disconnecting" it from the backplane.

Since even a failure in a processor could be detected by another processor, at first glance this seems like a good answer to the question of fault tolerance. The scheme turns out to be inadequate, however, where there is only one pathway between boards. If the failure on a board is such that it prevents proper operation of the system bus, a processor may be able to detect the failure, but it cannot use the system bus to disable the failed board.

The serial bus provides another pathway between boards, which can be used to prevent a failed module from interfering with the operation of the system bus. The serial bus can be used to disable the drivers of such a board, or direct a board-specific Reset to it. Conversely, if a failed board prevents the proper operation of the serial bus, the system bus can be used to disable the board's access to the serial bus.

#### 1.3 THE SERIAL BUS PROVIDES FOR "INTELLIGENT SEMAPHORES"

The third primary use of the serial bus is again related to multiprocessor systems. When a system includes multiple processors which can simultaneously try to access and use a variety of shared resources (parts of the system), some means must be found to control this access and use. A simple example of such a problem is when two processors simultaneously set out to use a shared hardware device such as a printer or disk. Other cases where interprocessor control is needed include access to: a data file, a data or control table in memory, or a section of program code which must be used by only one processor at a time.

The most widely used solution to these problems is the "semaphore". A semaphore is simply a location in memory which multiple system processors can access, but not simultaneously. A processor first reads the memory location to test whether another processor already has control of the shared resource, and then (if not) it writes to the location to show that it now has control. The system hardware must ensure that these two steps happen without allowing any other processor to access the semaphore location. The newer backplane buses include provisions for semaphore operations.

A semaphore in common memory solves some of the problem but is less than perfect. As the number of processors in a system increases, it becomes more likely that several of them need to use a resource at the same time. Many shared parts of a system such as data and control tables are designed to be in use by a processor for a relatively short time. For such cases, if the associated semaphore is found to be already set by another processor, a common software tactic is simply to rerun the "Read-Modify-Write" (RMW) or "Test and Set" operation until it succeeds. Studies of heavily loaded multiprocessor systems indicate that a significant percentage of processor cycles and cycles on the system bus are wasted on repetitive accesses to semaphore locations. This in turn can reduce the availability of the bus for other uses.

One way to solve this problem is to provide a duplicate copy of each semaphore on each processor board. The copies of the semaphore should, of course, always be kept synchronized. If a processor needs to set a particular semaphore, the corresponding on-board copy is first checked.

If and only if the onboard copy of the semaphore is reset, a RMW operation is run on the system bus, which affects all the copies of the semaphore in the system (including the on-board one). If this RMW "succeeds", all copies of the semaphore are simultaneously set, and the requesting processor is entitled to use the associated resource. (If two processors issue the RMW at the same time, system bus arbitration ensures that only one succeeds.) A scheme like this largely eliminates wasting system bus cycles on polling semaphore locations in memory.

If the local semaphore is set or the RMW operation on the system bus fails, system software has two choices. If the nature of the resource controlled by the semaphore is such that the semaphore will be cleared in a short time, it is more efficient to "loop" testing the <u>local</u> copy of the semaphore until it is cleared. An example of such a "short term" semaphore would be one controlling access to a data or control table in memory.

But if the semaphore will typically stay set for a relatively long time, system software and the processor should go on to other tasks. In this case, onboard hardware must generate an interrupt when the semaphore is cleared so that the processor can retry the RMW on the system bus. Better still, the onboard hardware can itself retry setting the semaphore and interrupt the processor only when it has gained control. An example of such a "long term" semaphore would be one controlling access to a physical device like a printer or a disk.

For "long term" semaphores, the serial bus offers a great improvement. A processor can turn the entire operation of setting the semaphore over to onboard serial bus hardware, and be interrupted only when the semaphore has been set and the associated resource is actually available.

#### 1.4 THE SERIAL BUS ALLOWS TOKEN PASSING SCHEMES

Sometimes a system has a group of several interchangeable resources. If semaphores are used to allocate these resources, then whenever a resource is needed, the semaphores must be polled until one is found to be available. In some cases it may make more sense to have a "token" in the system for each of these interchangeable resources, which is <u>passed around</u> among its "users" while the resource is available, but is <u>retained</u> by a user while it uses the resource. (Such "token passing" operation can be likened to a "daisy chain" in a backplane bus, which has been looped back on itself to make a ring.)

The serial bus allows a large number of such tokens (up to 1024) to be created and passed from board to board with very little software overhead.

#### 1.5 THE SERIAL BUS PROVIDES A LOW COST ALTERNATIVE BUS

The serial bus is a unique new concept in microprocessor system interfacing. Its capabilities make it very attractive for use in complex multiprocessing systems. But in addition to its power, a serial bus interface can be implemented at lower cost than a system bus interface. With the LSI support which will soon be available, serial bus hardware can be implemented in a fraction of the board space required for a parallel backplane bus.

Thus the serial bus offers a very attractive <u>alternative</u> to use of a parallel system bus for boards which do not require a high data rate. It can even be used as the primary system bus in some applications.

## 2. SERIAL BUS OPERATION

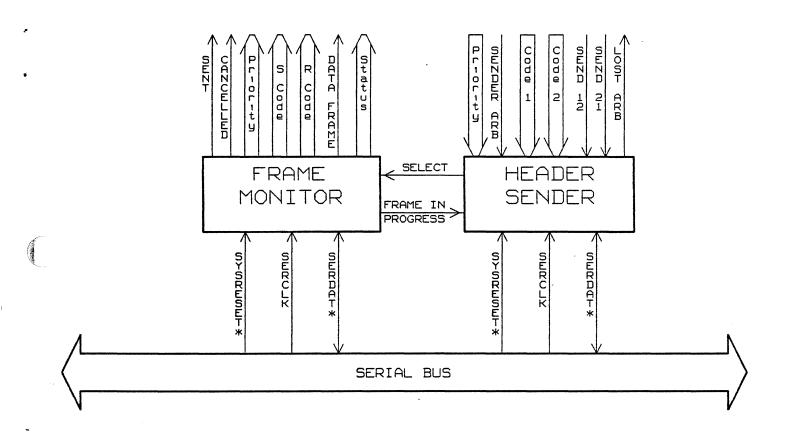

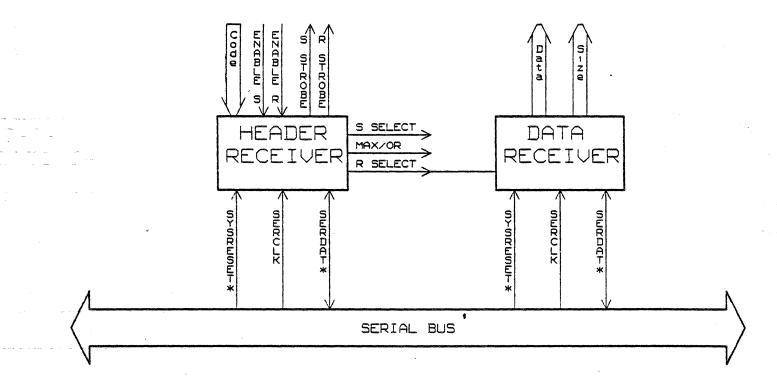

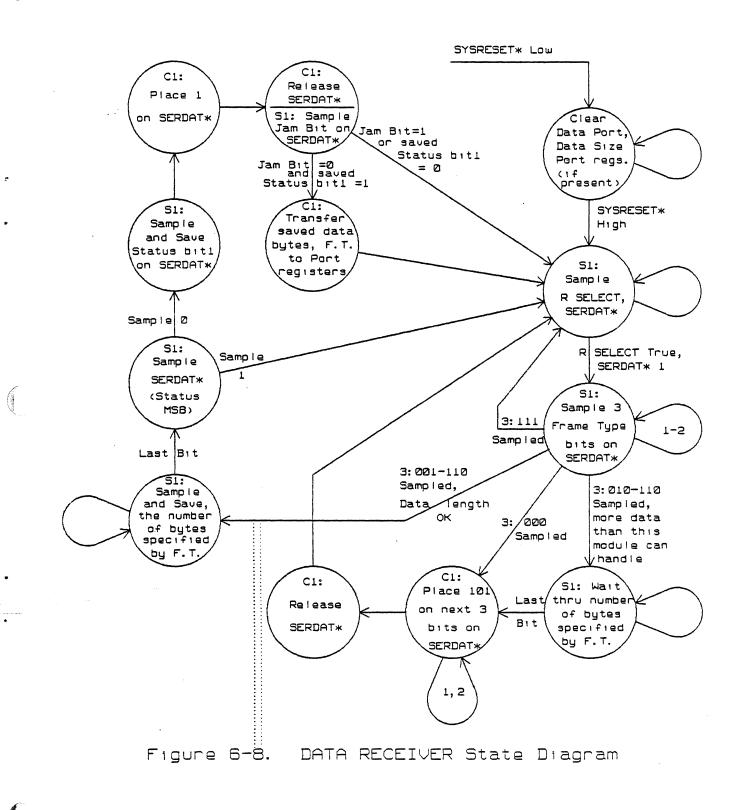

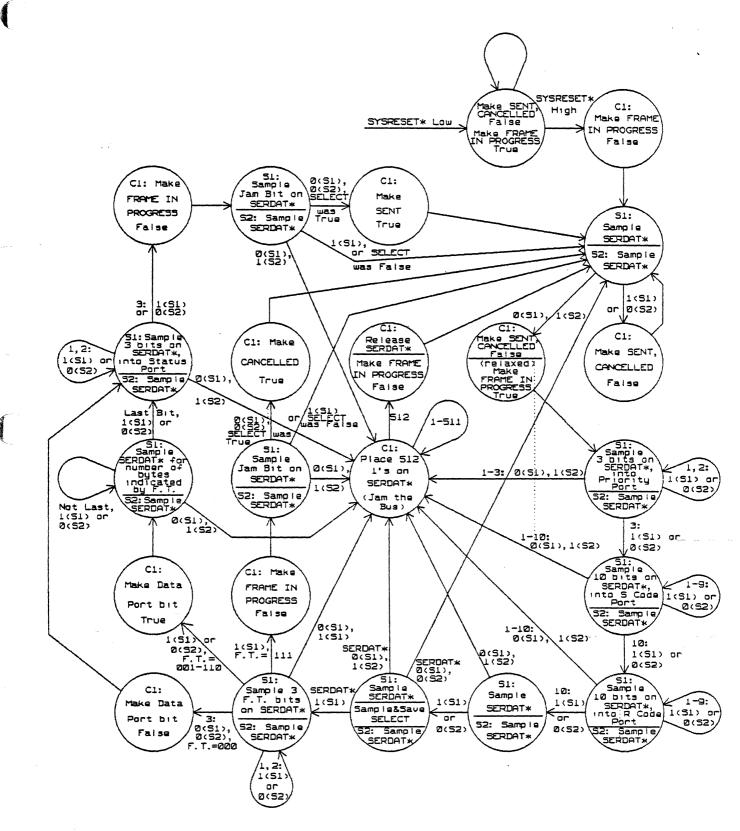

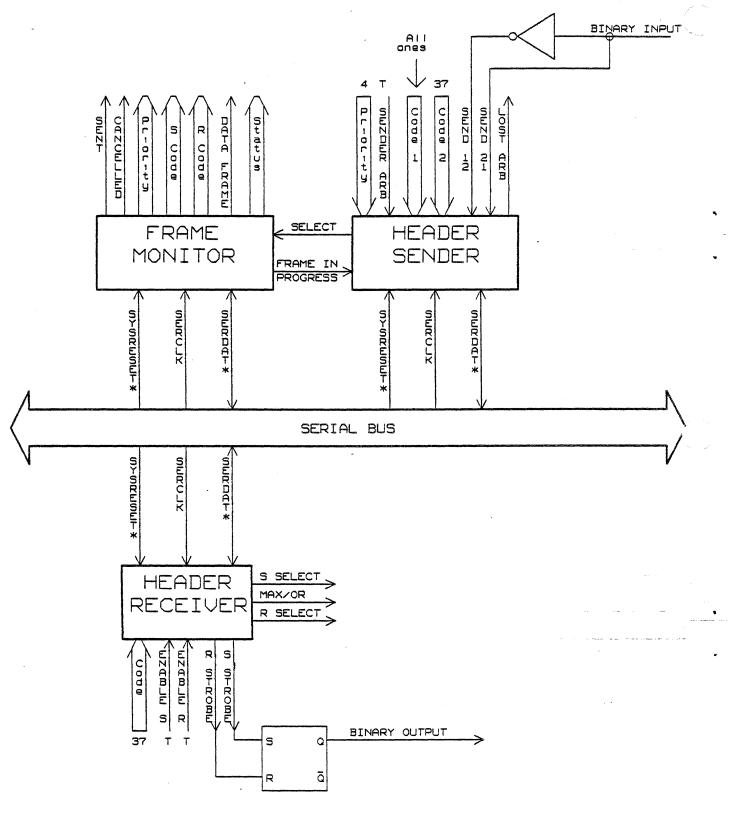

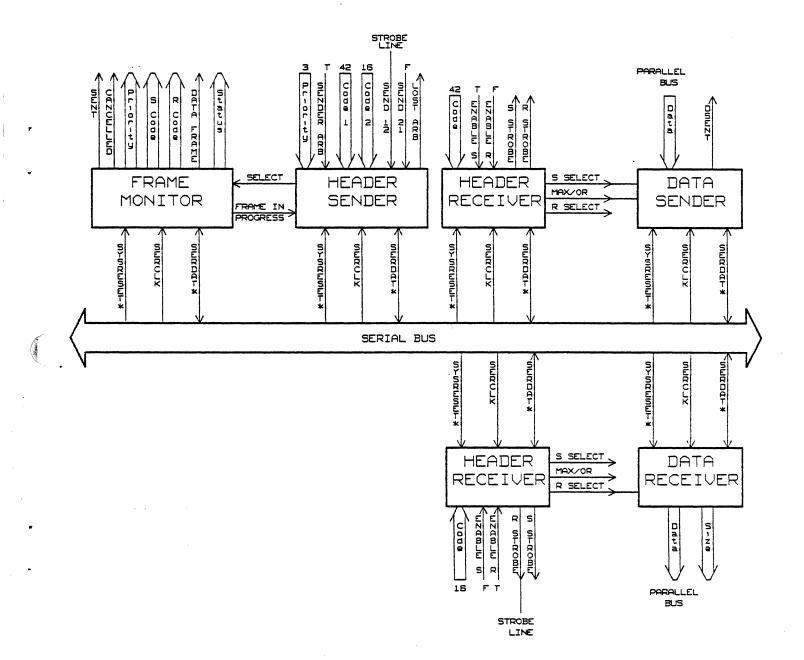

The serial bus interface system consists of two signal lines named SERCLK and SERDAT\* and six module types called HEADER SENDERS, HEADER RECEIVERS, DATA SENDERS, DATA RECEIVERS, FRAME MONITORS and a SERIAL CLOCK. The SERCLK line is driven by a totem pole driver in the SERIAL CLOCK module. The SERDAT\* line can be driven Low by all six module types using open collector drivers. When no module drives SERDAT\* Low, the bus terminating resistors pull it to a High level. The SERDAT\* line is a Low-True signal (i.e. a "one" is represented by a Low level). This fact, plus the open collector characteristics of the drivers, results in "logical OR'ing" when data is placed on SERDAT\* by more than one module.

In some cases on-board signals connect modules on the same board, but most communication between modules is done by sending "frames" on the SERDAT\* line. These frames are composed of "subframes" which are sent by various modules. A frame is initiated when a HEADER SENDER module sends a "Header subframe". The other modules then respond by sending subframes according to a prescribed protocol until the end of the frame is reached.

During the Header subframe transmission, HEADER SENDERS are required to sample each bit on the SERDAT\* line while they are sending. If a HEADER SENDER detects SERDAT\* Low when it is sending a "zero" (i.e. when it isn't driving SERDAT\* Low), it stops sending. This allows other HEADER SENDER(S) to finish sending the Header subframe without interference. This method of arbitration allows several HEADER SENDERS to start sending frames simultaneously, without affecting each others' transmissions. (One of the transmissions will be successful while the others are tried again later.)

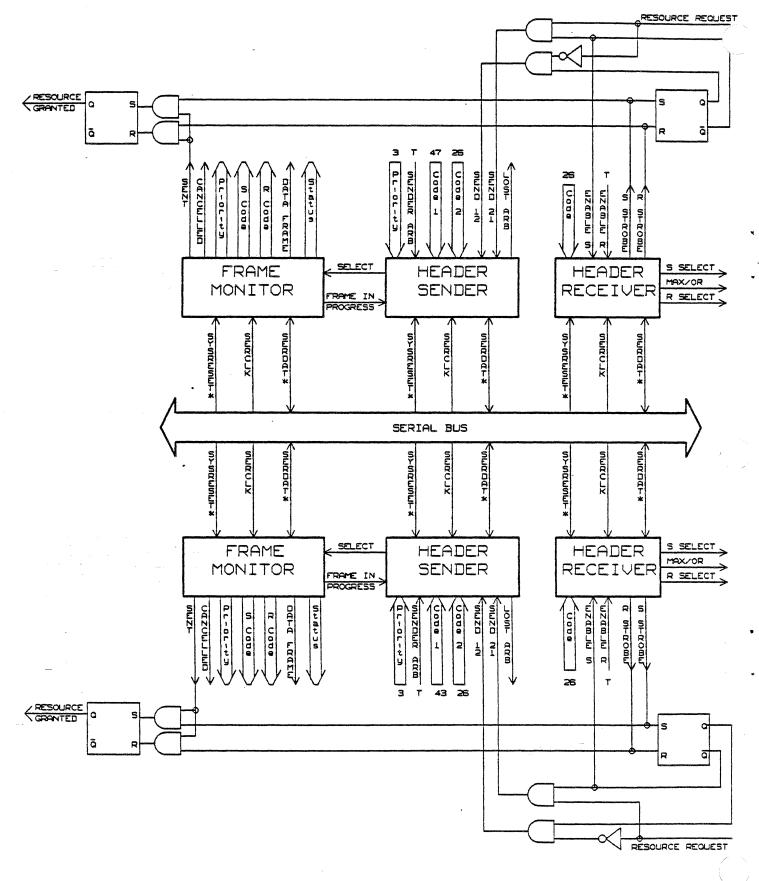

Serial bus modules are found on boards in <u>groups</u>. The following are the most common groups:

TYPE 1) A HEADER SENDER and a FRAME MONITOR

TYPE 2) A HEADER RECEIVER and a flip-flop

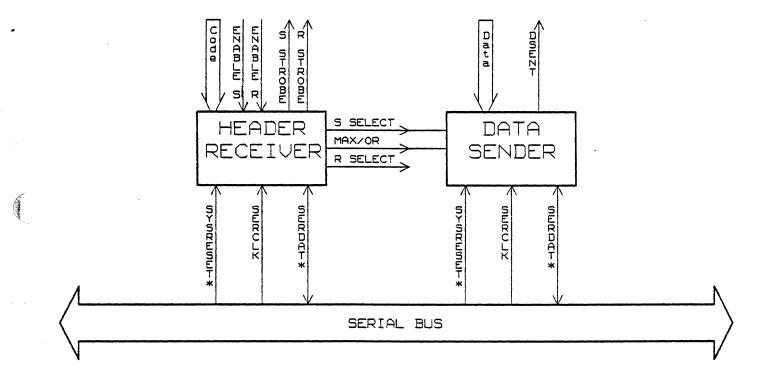

TYPE 3) A HEADER RECEIVER and a DATA SENDER

TYPE 4) A HEADER RECEIVER and a DATA RECEIVER

TYPE 5) A HEADER RECEIVER, a DATA SENDER, and a DATA RECEIVER

A TYPE 1 group is used to initiate frames by sending a "Header subframe". The Header subframe specifies what other modules will participate in the frame transmission by providing two ten bit "selection codes". Each HEADER RECEIVER on the serial bus has a ten bit code which it compares with the two codes in the subframe. If its code matches either of them, depending on the type of group the HEADER RECEIVER is in, it responds by changing the state of its flipflop, by telling its DATA SENDER to send, or by telling its DATA RECEIVER to receive.

### 2.1 USING THE SERIAL BUS TO TRANSFER DATA

The HEADER SENDER can determine whether there is a frame in progress from the FRAME IN PROGRESS signal generated by its FRAME MONITOR. If there is no frame in progress it can initiate one by sending a Header subframe. This subframe has a ten bit "S field" and a ten bit "R field". To transfer data, the HEADER SENDER puts a selection code in the S field that corresponds to some TYPE 3 or TYPE 5 group on the bus, and a selection code in the R field that corresponds to some TYPE 4 or TYPE 5 group. (The actual codes used to select these groups depend on how the system software or firmware has configured the system. There are no selection codes used exclusively to select TYPE 4 groups, etc.)

Each HEADER RECEIVER on the serial bus compares these codes against its code. One or more of the TYPE 3 or TYPE 5 HEADER RECEIVERS finds a match with the S field. It tells its DATA SENDER to send data. In a similar way, one or more of the TYPE 4 or TYPE 5 HEADER RECEIVERS finds a match with the R field and tell its DATA RECEIVER to receive data.

The actual number of bytes transferred is left up to the DATA SENDER. After the HEADER SENDER has sent the Header subframe, the DATA SENDER sends a three bit subframe indicating the number of bytes it intends to send to the DATA RECEIVER, followed by the data bytes. The DATA RECEIVER then responds with an indication that it has received the data bytes.

#### 2.2 USING THE SERIAL BUS TO SET AND RESET FLIP-FLOPS

When a HEADER SENDER is used to set or reset a flip-flop, it sends a Header subframe as in the case described above. Instead of sending codes for TYPE 3, 4 or 5 groups in the S and R fields, however, it sends the code for a TYPE 2 group in one of the fields, and a "dummy" code (all ones) in the other field. If the frame is intended to <u>set</u> a flip-flop, it sends the TYPE 2 code in the S field, and the dummy code in the R field. If the frame is intended to <u>reset</u> a flip-flop, it sends the dummy code in the S field and the code for the TYPE 2 group in the R field.

When the Header subframe is sent, each HEADER RECEIVER on the serial bus compares the codes in the S and R fields to its own code. One or more HEADER RECEIVER(S) in a TYPE 2 group matches the S (or R) field and sets (or resets) its on-board flip-flop.

#### 2.3 OTHER USES FOR THE SERIAL BUS

As we will see later, groups of serial bus modules like those described above can be used as building blocks for very powerful system configurations. For example, the combination of a TYPE 1 and a TYPE 5 group, on each of two boards, can be used by one board to pass an address and read the contents of a memory location on the other. TYPE 2 groups can be used to reinitialize one or more of the boards in a system, or to selectively disconnect a failed board from the system bus. TYPE 2 groups can be also be used to provide "semaphores" which are functionally superior to semaphores in a common memory, or to provide "token passing".

#### 3. SERIAL BUS FRAMES

As we said in Section 2, a frame is actually composed of subframes which are sent by several modules in sequence whenever a HEADER SENDER sends a Header subframe. Depending on the types of module groupings that a frame selects, different modules drive and receive the various subframes, as follows:

Frames that select TYPE 2 module groups...

| Subframe     | Sent By         | Received By      |               |

|--------------|-----------------|------------------|---------------|

| Header       | HEADER SENDER   | HEADER RECEIVER  | FRAME MONITOR |

| Frame Type   | Nobody (000)    | HEADER RECEIVER, |               |

| Frame Status | HEADER RECEIVER | FRAME MONITOR    |               |

Frames that select TYPE 3, 4, and 5 module groups...

| Subframe                                     | Sent By                                                                      | Received By                                                                                                      |

|----------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Header<br>Frame Type<br>Data<br>Frame Status | HEADER SENDER<br>DATA SENDER<br>DATA SENDER<br>DATA SENDER,<br>DATA RECEIVER | HEADER RECEIVER<br>DATA RECEIVER, FRAME MONITOR<br>DATA RECEIVER<br>FRAME MONITOR, DATA SENDER,<br>DATA RECEIVER |

Frames that get cancelled...

Subframe Sent By

Received By

Header Frame Type HEADER SENDER HEADER RECEIVER HEADER RECEIVER FRAME MONITOR, DATA SENDER, DATA RECEIVER

When a Header subframe is sent, modules on the serial bus are selected to interact during the remainder of the frame. This interaction can be seen on the serial bus as a sequence of subframe transmissions. Depending on what module groups are selected, we may see eleven possible kinds of frames.

| 1)  | A Flip-flop Set frame         |

|-----|-------------------------------|

| 2)  | A Flip-flop Reset frame       |

| 3)  | A Semaphore Set frame         |

| 4)  | A Token Passing frame         |

|     | A 1 byte Data Transfer frame  |

| 6)  | A 2 byte Data Transfer frame  |

|     | A 4 byte Data Transfer frame  |

|     | An 8 byte Data Transfer frame |

| 9)  | A 16 byte Data Transfer frame |

| 10) | A 32 byte Data Transfer frame |

| 11) | A Cancelled frame             |

# 3.1 A FLIP-FLOP SET FRAME

A Flip-flop Set frame contains 4 subframes:

| Header                             | Frame<br>Type | Frame<br>Status | Jam Bit |

|------------------------------------|---------------|-----------------|---------|

| S field=TYPE 2<br>R field=all ones | 000           | 010             | 0       |

The Header subframe is sent by a HEADER SENDER. This subframe has two selection code fields in it: the S field and the R field. The Flip-flop Set frame has the selection code of a TYPE 2 group in its S field and all ones in the R field. One (or more) HEADER RECEIVER(S) on the serial bus finds a match between the S field code and its own code, sets its flip-flop, and responds with 010 in the Frame Status subframe.

The Flip-flop Set frame selects TYPE 2 module groups. The HEADER RECEIVER in a simple TYPE 2 module group never drives SERDAT\* during the Frame Type subframe. Since a TYPE 2 module doesn't include a DATA SENDER, no module drives SERDAT\* in the Frame Type subframe. This results in a three bit Frame Type value of 000 (all High). This value tells all of the FRAME MONITORS on the serial bus that there will be no data bytes (i.e. that the Frame Status subframe follows directly, and that the serial bus will be free thereafter). The FRAME MONITORS use this information to signal their HEADER SENDERS when the next frame can begin.

After the Frame Type subframe is complete, the HEADER RECEIVER sends 010 in the Frame Status subframe to indicate that at least one HEADER RECEIVER matched the S field. This acknowledgment is captured by the FRAME MONITOR that is paired with the HEADER SENDER, and reported to its on-board logic.

Since the R field in the header contained a "dummy" code of all ones, no HEADER RECEIVER matches the R field. (The "all ones" code is never used to select modules.) Because of this, the Frame Status subframe is only driven by the HEADER RECEIVER(S) which matched the S field, and remains 010. Since the header was intentionally arranged not to select an "R-module", the 010 value is the expected response.

## 3.2 A FLIP-FLOP RESET FRAME

A Flip-flop Reset frame contains four subframes:

| Header                             | Frame<br>Type | Frame<br>Status | Jam Bit |

|------------------------------------|---------------|-----------------|---------|

| S field=all cnes<br>R field=TYPE 2 | 000           | 001             | 0       |

The Header subframe is sent by a HEADER SENDER. As in the Flip-flop Set frame, this subframe has two selection codes in its S field and R field. The Flip-flop Reset frame, however, has the selection code of a TYPE 2 group in its R field and all ones in the S field. One (or more) HEADER RECEIVER(S) on the serial bus finds a match between the R field code and its own code, resets its flip-flop, and responds with 001 in the Frame Status subframe.

The Flip-flop Reset frame selects TYPE 2 module groups. The HEADER RECEIVER in a simple TYPE 2 module group never drives SERDAT\* during the Frame Type subframe. Since a TYPE 2 module doesn't include a DATA SENDER, no module drives SERDAT\* in the Frame Type subframe. This results in a three bit Frame Type value of 000 (all High). This value tells all of the FRAME MONITORS on the serial bus that there will be no data bytes (i.e. that the Frame Status subframe follows directly, and that the serial bus will be free thereafter). The FRAME MONITORS use this information to signal their HEADER SENDERS when the next frame can begin.

After the Frame Type subframe is complete, the HEADER RECEIVER sends 001 in the Frame Status subframe to indicate that at least one HEADER RECEIVER matched the R field. This acknowledgment is captured by the FRAME MONITOR that is paired with the HEADER SENDER, and is reported to on-board logic.

Since the S field in the header contained a "dummy" code of all ones, no HEADER RECEIVER matches the S field. Because of this, the Frame Status subframe is only driven by the HEADER RECEIVER(S) which matched the R field, and its value remains 001. Since the header was intentionally arranged not to select an "S-module", the 001 value is the expected response.

#### 3.3 A SEMAPHORE SET FRAME

A Semaphore Set frame which is "successful" contains four subframes:

| Header                              | Frame<br>Type | Frame<br>Status | Jam Bit |  |

|-------------------------------------|---------------|-----------------|---------|--|

| S field=TYPE 2<br>R field=Req. Code | 000           | 010             | 0       |  |

The Header subframe is sent by a HEADER SENDER. As in all frames, this subframe has two selection codes in its S field and R field. The Semaphore Set frame has the selection code of a TYPE 2 group in its S field.

The R field of a Semaphore Set frame contains a ten bit code which represents the unique identity of the Requester that caused the frame to be sent. System software should ensure that two HEADER SENDERS are never allowed to send Semaphore Set frames with the same R field code. (In a multitasking system, this could be assured by assigning a unique Requester number to each task in the system.) The uniqueness of these Requester numbers guarantees that if two or more HEADER SENDERS try to set the same semaphore at the same time, only one of them will survive the serial bus arbitration and finish the frame.

A TYPE 2 group used for semaphore operations differs from a simple Type 2 group in having the state of its flip-flop fed back into its HEADER RECEIVER. The HEADER RECEIVER in a TYPE 2 group used for semaphore operations will not accept a Set frame if its flip-flop is already set. Whenever such a frame is sent, the HEADER RECEIVER drives the value lll in the Frame Type field, which "cancels" the frame. (A Cancelled frame is shown below.)

If the HEADER RECEIVER matches the S field, and its flip-flop is reset, operation proceeds as described for a Flip-Flop Set frame.

NOTE 1: Any "Requester code" that is used in the R field of a Semaphore Set frame should be an otherwise unused selection code, so that it doesn't select some HEADER RECEIVER on the bus.

NOTE 2: Semaphores are reset using Flip-flop Reset frames, except that the S field may contain either all ones or the same Requester code used in the Semaphore Set frame.

## 3.4 A TOKEN PASSING FRAME

A Token Passing frame which is "successful" contains four subframes:

| Header                           | Frame<br>Type | Frame<br>Status | Jam Bit |

|----------------------------------|---------------|-----------------|---------|

| S field=TYPE 2<br>R field=TYPE 2 | 000           | 011             | 0       |

The Header subframe is sent by a HEADER SENDER. The Token Passing frame has the selection code of one TYPE 2 group in its S field and the code of another TYPE 2 group in its R field.

As with a TYPE 2 group used for semaphore operations, the HEADER RECEIVER in a TYPE 2 group used for token passing operations will not accept a Set frame if its flip-flop is already set. In addition, it will not accept a Reset frame while its flip-flop is reset. Whenever such a frame is sent, the HEADER RECEIVER "cancels" the frame.

A Token Passing frame is sent to simultaneously clear one flip-flop and set another. (In effect, it is passing a "token bit" from the flip flop it resets to the one it sets.) If the flip-flop it is trying to reset is already reset (i.e. it doesn't have a token to pass) the frame will be cancelled. Likewise, if the flip-flop it is trying to set is already set (i.e. it is already holding a token) the frame will also be cancelled.

These frame cancellation features ensure that a token bit is never lost or created in the process of moving it from one board to another.

In a Token Passing frame, the S field of the header identifies the Type 2 group to which these token is being passed, and the R field identifies the Type 2 group from which it is being passed. Assuming that the HEADER RECEIVER which matches the S-field has its flip-flop reset, it sends 010 in the Frame Status subframe. Assuming that the HEADER RECEIVER which matches the R field has its flip-flop set, it sends 001 in the Frame Status. These two values are logically OR'ed on the serial bus, resulting in the value 011 as the "correct" value reported by the FRAME MONITOR paired with the HEADER SENDER which initiated the frame.

## 3.5 A DATA TRANSFER FRAME

A Data Transfer frame which is "successful" contains five subframes:

| Header                                     | Frame<br>Type | Data     | Frame<br>Status | Jam Bit |

|--------------------------------------------|---------------|----------|-----------------|---------|

| S field=TYPE 3 or 5<br>R field=TYPE 4 or 5 | 001-110       | (Varies) | 011             | 0       |

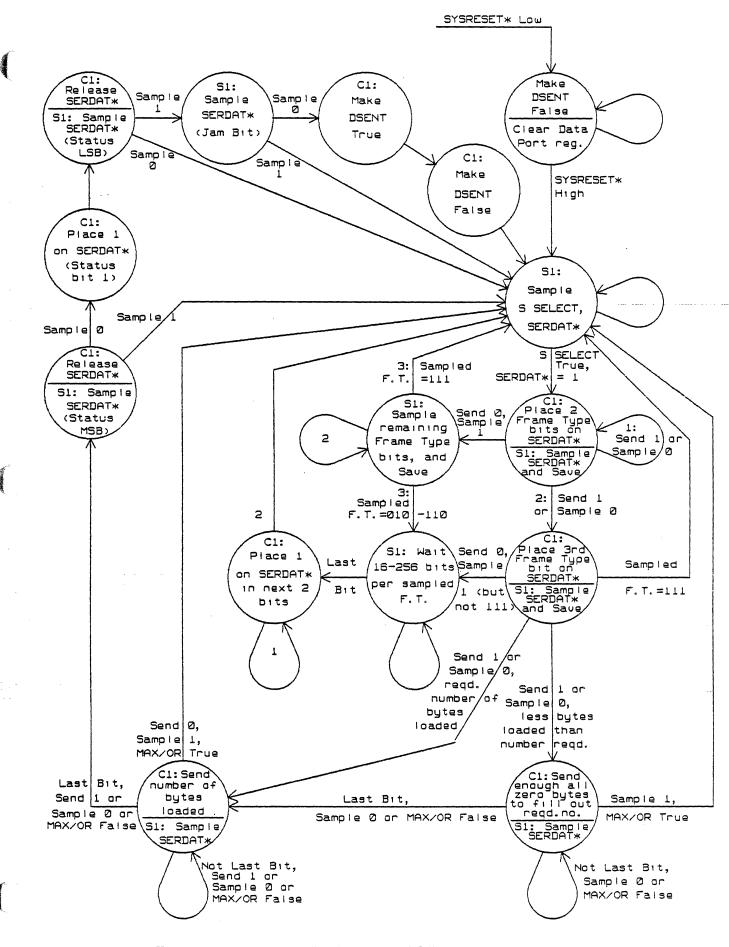

The Header subframe is sent by a HEADER SENDER. As in all frames, this subframe has two selection codes in its S field and R field. The S field has the selection code of a TYPE 3 or Type 5 group, which includes a DATA SENDER. Similarly, the R-field has the selection code of a TYPE 4 or 5 group, which includes a DATA RECEIVER. At the conclusion of the Header subframe, the selected DATA SENDER(S) drive a code on SERDAT\* during the Frame Type subframe, to indicate how many bytes will be sent. While it is sending this code, a DATA SENDER also samples SERDAT\*. If it samples the value 111 in the Frame Type, the frame is "cancelled", and the DATA SENDER terminates its transmission.

Except in a Cancelled frame, the DATA SENDER sends a Data subframe after the Frame Type subframe. The Data subframe may be 1, 2, 4, 8, 16, or 32 bytes long.

If two or more DATA SENDERS are selected by the header subframe, the serial bus protocol requires that they agree on the amount of data to be sent. If a DATA SENDER samples a different value in the Frame Type subframe than the one it sent (other than 111), it sends 110 in the Frame Status subframe which follows the Data subframe, indicating that the two DATA SENDERS tried to send different size Data subframes. If it sampled its own Frame Type value on SERDAT\*, and if no other module sends a "one" in the high-order bit of the Frame Status, a DATA SENDER sends 10 in the the next 2 bits.

Similarly, the serial but protocol requires that DATA RECEIVERS must be able to handle the amount of data sent by DATA SENDERS in a frame. If the frame is not cancelled, and after the Data subframe has been sent, the DATA RECEIVER sends 101 in the Frame Status if the data was too long for it. If the frame was not cancelled, and if no other module sends a "one" in the high-order bit of the Frame Status, a DATA RECEIVER sends 01 in the next 2 bits.

In a successful frame, the Frame Status values from the DATA SENDER and DATA RECEIVER are logically OR'ed by the serial bus to produce Oll. This value is reported by the FRAME MONITOR paired with the HEADER SENDER which initiated the frame.

## 3.6 A CANCELLED FRAME

| Α | Cancelled | frame | contains | anly | three | subframes: |

|---|-----------|-------|----------|------|-------|------------|

|---|-----------|-------|----------|------|-------|------------|

| Header                                        | Frame<br>Type | Jam Bit |

|-----------------------------------------------|---------------|---------|

| S field=TYPE 2, 3 or 5<br>R field=TYPE 4 or 5 | 111           | 0       |

The Header subframe is sent by a HEADER SENDER. It may be intended to set a semaphore or transfer data. In the former case, the cancelling of the frame indicates that the semaphore is already set. In the latter case, the cancelling of the frame indicates that the data transfer cannot be performed because one or more of the DATA SENDERS or DATA RECEIVERS selected by the S and R codes is not ready for the transfer. A selected DATA RECEIVER may not yet have "disposed of" data it received in a previous transmission. Or, a DATA SENDER may not have been loaded with data to send.

In any of these cases, the HEADER RECEIVER with the flip-flop, DATA SENDER or DATA RECEIVER recognizes the problem and "cancels" the frame by driving all three bits of the Frame Type subframe to "one" (Low). In the case of a Data Transfer frame, the selected DATA SENDER(S) samples all three Frame Type bits as ones and doesn't send the data bytes. The lll in the size field tells all selected DATA RECEIVERS and all of the FRAME MONITORS on the serial bus that there will be no data bytes nor any status. All FRAME MONITORS use this fact to signal their HEADER SENDERS that the serial bus is available for another frame. The FRAME MONITOR with the HEADER SENDER which initiated the frame also signals the problem to its onboard logic.

# 3.7 A "JAMMED" FRAME

A "jammed" frame may look like any of the frames described above. It differs from them in that (at least) the final single-bit "Jam Bit subframe" is one rather than zero as shown in the above frames. A Jammed frame occurs when one or more FRAME MONITORS in the system detects that the serial bus is "out of frame synchronization" due to an error induced by system noise, and sends a long series of ones on SERDAT\*. A Jammed frame is ignored by all modules on the serial bus: no HEADER RECEIVER sets or clears an associated flip-flop, no DATA SENDER considers itself to have sent data, nor does any DATA RECEIVER consider itself to have received data. The frame which was jammed will be resent after the serial bus is "resynchronized".

# \*\*\*\*\*\* THIS PAGE INTENTIONALLY LEFT BLANK \*\*\*\*\*\*

. .

#### 4. SERIAL BUS SUBFRAMES

The activity on the serial bus, like a carefully rehearsed drama, can be described in two ways:

- 1) We can use a <u>script</u> which presents all of the words spoken, with marginal comments indicating who speaks at each time. (This is the approach used in this section.)

- 2) We can make a <u>list of cues</u> for each "actor" in the drama that says "WHEN someone says this... THEN you say this..." (This is the approach used in section 6.)

Both approaches are useful to understand how the serial bus works.

#### 4.1 SUBFRAMES COMMON TO ALL FRAMES

All frames start with a Header subframe and a Frame Type subframe, and end with a Jam Bit subframe. The Header subframe determines which modules will participate in the rest of the frame, which in turn determines the type of frame that is sent. The Frame Type subframe makes the type of frame known to all serial bus modules, and specifies the length of the frame. The Jam Bit subframe "validates" the complete frame and ensures "frame synchronization" among all serial bus modules.

4.1.1 The Header Subframe

A Header subframe is composed of 26 bits arranged in 6 fields:

| Start<br>Bit | Message<br>Priority | s  | R  | DATA<br>SENDER<br>Arb<br>enable | HSVAL |

|--------------|---------------------|----|----|---------------------------------|-------|

| 1            | 3                   | 10 | 10 | 1                               | 1     |

The Header subframe consists of the following fields:

- 1) A single "start bit". When the start bit is transmitted, it signals serial bus modules that a frame is beginning.

- 2) A three-bit "Message Priority" field. If two or more HEADER SENDERS attempt to send a frame at the same time, this field is used to arbitrate control of the serial bus so that the frame with higher priority is sent first.

3) A ten-bit S field which contains a selection code for serial bus modules. The code in this field and the type of serial bus frame are interrelated as shown below.

| FRAME TYPE            | CONTENTS OF S FIELD      |

|-----------------------|--------------------------|

| Data Transfer frame   | Sender selection code    |

| Semaphore Set frame   | Semaphore selection code |

| Flip-flop Set frame   | Flip-flop selection code |

| Flip-flop Reset frame | (All ones)               |

| Token Passing frame   | Flip-flop selection code |

In a Data Transfer frame this field specifies which DATA SENDER(S) should send data in the Data subframe which follows. In the Semaphore Set frame, Flip-flop Set frame, and Token Passing frame, this code selects the semaphore(s) or flip-flop(s) that are to be set. (The S code may select several groups of modules if their HEADER RECEIVERS have all been set up to recognize it.)

4) A ten-bit R field which contains a selection code for serial bus modules. The code in this field and the type of serial bus frame are interrelated as follows:

FRAME TYPE

CONTENTS OF R FIELD

| Data Transfer frame   | Receiver selection code  |

|-----------------------|--------------------------|

| Semaphore Set frame   | Requester code           |

| Flip-flop Set frame   | (All ones)               |

| Flip-flop Reset frame | Flip-flop selection code |

| Token Passing frame   | Flip-flop selection code |

In a Data Transfer frame this field specifies which DATA RECEIVER(S) should capture the data in the Data subframe which follows. In a Flip-flop Reset or Token Passing frame, this code selects the flip-flop(s) which are to be reset. In a Semaphore Set frame this code does not select a module, but rather guarantees that only one HEADER SENDER wins the serial bus arbitration and sets the semaphore. (The R code may select several groups of modules if their HEADER RECEIVERS have all been set up to recognize it.)

5) A DATA SENDER arbitration enable bit. When two or more DATA SENDERS share a common selection code, they are both selected to send at the same time. In this case, the resulting Data subframe can contain either the logical OR of their values, or the largest value among the DATA SENDERS. To specify that a logical OR is required, the HEADER SENDER sends a "zero" in this bit position. To specify that the largest value is required, it sends a "one". (A "one" tells each DATA SENDER to stop sending data if it samples a "one" on SERDAT\* in a bit in which it is sending a "zero". A "zero" tells the DATA SENDERS to keep sending regardless.) 6) A HEADER SENDER validation bit. This bit is always sent as a "one" (Low) by the HEADER SENDER at the conclusion of the Header subframe. This bit is specified as part of the Header subframe to insure that some error on the serial bus won't cause all the HEADER SENDERS to think they have lost the arbitration and retire from the bus. If this occurs, it leaves a string of "zeroes" on SERDAT\* for the rest of the Header subframe. This could be misinterpreted by other modules as a valid Header subframe.

The validation bit solves this problem because if all of the HEADER SENDERS retire it will be a "zero", causing all serial bus modules to ignore the frame.

# 4.1.2 The Frame Type Subframe

The second subframe present in all frames is the Frame Type subframe. It is composed of a single 3-bit field:

| bit 2<br>MSB | bit l | bit 0<br>LSB |  |

|--------------|-------|--------------|--|

|--------------|-------|--------------|--|

Although this 3 bit subframe is present in all frames, it is not always driven by a module. For example, when a simple TYPE 2 module group is selected by a Flip-flop Set frame these bits are 000 because a simple TYPE 2 group doesn't send the Frame Type bits.

When one (or more) DATA SENDER(S) is selected by the S code, it sends a three bit Frame Type code in this subframe. This code indicates how many bytes of data the DATA SENDER is planning to send. The figure below shows the meaning of the various Frame Type codes.

| CODE | MEANING                             |

|------|-------------------------------------|

| 000  | No DATA SENDER selected             |

| 001  | l byte data transmission to follow  |

| 010  | 2 byte data transmission to follow  |

| 011  | 4 byte data transmission to follow  |

| 100  | 8 byte data transmission to follow  |

| 101  | 16 byte data transmission to follow |

| 110  | 32 byte data transmission to follow |

| 111  | Frame cancelled                     |

Suppose that a DATA RECEIVER has received data in a previous frame and has not "disposed of" that data yet. In order to keep from "losing" the data from the previous frame, it has signalled its own HEADER RECEIVER that it is not ready for another frame. If a HEADER SENDER sends another frame with the DATA RECEIVER'S code in the R field, before the DATA RECEIVER has "disposed of" the previous data, its HEADER RECEIVER "cancels" the new frame by sending "ones" during all three of the size bits. The DATA SENDER samples the Frame Type subframe as it sends it, and stops sending if it samples a lll. (This "Cancelled" frame ends after the Frame Type bits.)

Suppose a DATA SENDER has not been provided with data by its onboard logic. Like a DATA RECEIVER which has not "disposed of" earlier data, it has signalled its own HEADER RECEIVER of this fact via an onboard signal. If a HEADER SENDER sends a frame with the DATA SENDER'S code in the S field while the DATA SENDER "has no data", its HEADER RECEIVER cancels the frame by sending lll in the Frame Type subframe. The DATA RECEIVER(S) which is selected by the R field sees this code and ignores the frame.

A system can be set up so that more than one DATA SENDER is selected by the same S field code. This allows their data to be logically OR'ed or the largest among their data values to be determined. If multiple DATA SENDERS are selected by the S field and one or more of them is not ready to send, those which are ready see the lll code and don't send any data.

The HEADER RECEIVER in a Type 2 group intended for semaphore or token passing operation may also send lll in the Frame Type subframe to cancel a frame. If it sees its code in the S field and its flip-flop is already set, or (in token passing) if it sees its code in the R field and its flip-flop is already reset, it cancels the frame.

In summary, a HEADER RECEIVER module sends 111 to cancel a frame if that frame contains a matching code in either the S or R field, and its DATA SENDER, DATA RECEIVER, or other onboard logic has signalled that it should cancel such a frame.

When a frame is cancelled, this fact is captured by the FRAME MONITOR which is paired with the HEADER SENDER that initiated the frame, and is reported to its onboard logic.

## 4.1.3 The Jam Bit Subframe

This "subframe" consists of a single bit. It can be regarded as a subframe or as "the bit after a frame". None of the modules which send other subframes ever drive this bit to one (Low), but HEADER RECEIVERS, DATA SENDERS, DATA RECEIVERS, and FRAME MONITORS all sample it to be sure it is a zero. If the Jam Bit is ever sampled by these modules as a one, they ignore the preceding frame transmission. The only way a Jam Bit can ever be one is if one or more FRAME MONITOR(S) detect a start bit in the middle of a frame. This can only occur if some other FRAME MONITOR has become desynchronized due to system noise. In this case, the FRAME MONITOR(S) which detect the condition drive a string of 512 one bits on SERDAT\*. Since all serial bus frames are shorter than 512 bits, this is bound to affect the Jam Bit seen by all serial bus modules.

#### 4.2 THE FRAME STATUS SUBFRAME

While the cancellation of a frame can be determined from the Frame Type field, other problems can arise when a frame is sent. Such problems are also reported to onboard logic by the FRAME MONITOR which is paired with the HEADER SENDER that initiated the frame. The Frame Status subframe is included at the end of every frame except a Cancelled frame, and is used to diagnose problems (exceptional conditions) that might have arisen during the frame's transmission.

The Frame Status subframe is composed of one 3-bit field:

| bit 2<br>MSB | bit l | bit 0<br>LSB |  |

|--------------|-------|--------------|--|

|              |       |              |  |

Whenever a HEADER RECEIVER receives a Header subframe with an S (or R) selection code that matches its own, it makes its S SELECT (or R SELECT) output True. Depending on whether the HEADER RECEIVER is part of a TYPE 2, 3, 4, or 5 module group, these outputs may or may not enable an on-board DATA SENDER (or DATA RECEIVER).

Since the HEADER RECEIVER has no way of knowing which type of module group it is used in, it samples the Frame Type subframe. If a DATA SENDER is selected it will send one of the values 001 through 110 in the Frame Type. If the HEADER RECEIVER samples 001-110, it passes over the Data subframe and samples these three Frame Status bits and the following Jam Detect bit. (In this case the HEADER RECEIVER is simply acting as a "tracker" to reflect how DATA SENDER(S) and DATA RECEIVER(S) on other boards responded to the frame.) If the Frame Status is 011 and the Jam Detect bit is zero, the HEADER RECEIVER pulses its S STROBE or R STROBE output to set or clear an on-board "tracking" flipflop.

If the HEADER RECEIVER samples 000 in the Frame Type, it knows that no DATA SENDER was selected by the frame. It samples the MSB of the (immediately following) Frame Status field and then sends a either a 10 or 01 in the next 2 bits to indicate that it was selected by the S or R field, respectively. It then samples the Jam Detect bit. If the MSB of the Frame Type and the Jam Detect bits are both zero, all is well, and the HEADER RECEIVER pulses its S STROBE or R STROBE output (respectively) to an onboard flip-flop. If two or more DATA SENDERS are selected by the S field code of the Header subframe, the serial bus protocol requires that they agree about how much data is to be sent. As each DATA SENDER sends its code in the Frame Type field to signal how much data it has to send, it also samples SERDAT\* to detect a conflict with other DATA SENDERS. If it samples a "one" in any of the 3 bits while it is sending a "zero", it stops sending any further bits in the Frame Type subframe or Data subframe. However, in this case it does sample all the bits in the Frame Type. If the sampled value is not 111 (i.e. not a cancellation), it uses the value it samples to determine the length of the Data subframe, passes over the data, and thereafter sends 110 during the Frame Status subframe to signify a conflict among selected DATA SENDERS as to size of the Data subframe.

If the DATA SENDER samples the same value in the Frame Type that it is sending, it sends its data. It then samples the MSB of the Frame Status, which indicates a size problem on the part of other DATA SENDERS or RECEIVERS. If the MSB is zero it sends 10 in the next two bits of the Frame Status to indicate that it survived any arbitration in the Data subframe.

Suppose that a DATA SENDER is selected by the S field code of the Header subframe and a DATA RECEIVER is selected by its R code. Let's further suppose that the DATA RECEIVER is only capable of receiving Data subframes up to a certain length (less than 32 bytes).

The DATA RECEIVER samples the Frame Type subframe. If the Frame Type code indicates the DATA SENDER is trying to send more data than it can handle, the DATA RECEIVER counts bits across the size of data indicated by the Frame Type, and then sends 101 in the Frame Status subframe to signal the problem.

If a selected DATA RECEIVER samples 000 in the Frame Type field, there is no DATA SENDER to send data to it. It handles this situation by sending 100 in the Frame Status subframe.

Otherwise (for Frame Types 001-110) the DATA RECEIVER samples the number of bytes of data indicated by the Frame Type. It then samples the MSB of the Frame Status subframe. If the MSB is "zero", it sends 01 in the next 2 bits of the Frame Status to show that it was selected. It then samples the Jam Detect bit. If the MSB of the Frame Status and the Jam Detect bit were both zero, it presents the data it sampled to its onboard logic. The R STROBE output of the paired HEADER RECEIVER indicates the arrival of data to onboard logic.

In summary, the Frame Status value must be interpreted differently for a Data Transfer frame vs. other types of frames. In each case there are 8 possible status values.

STATUS Value

#### Interpretation

FRAME TYPE 000 (Not a Data Transfer frame)

- 000 No HEADER RECEIVER selected by either S or R

- 001 HEADER RECEIVER selected by R only

- 010 HEADER RECEIVER selected by S only

- 011 HEADER RECEIVERS selected by S and R

- 100 RESERVED: should not occur

- 101 DATA RECEIVER selected by R, nothing selected by S

- 110 RESERVED: should not occur

111 DATA RECEIVER selected by R, HEADER RECEIVER (only) selected by S

FRAME TYPE 001-110 (Data Transfer frame)

- 000 No DATA RECEIVER selected by R, all DATA SENDERS selected by S lost Data field arbitration

- 001 DATA RECEIVER selected by R, all DATA SENDERS selected by S lost Data field arbitration

- 010 NO DATA RECEIVER selected by R, DATA SENDERS selected by S completed the Data subframe normally

- 011 Data Transfer completed correctly

- 100 RESERVED: should not occur

- 101 DATA RECEIVER(S) unable to handle data size

- 110 Data size conflict among DATA SENDERS

- 111 (Both 101 and 110 conditions)

#### 4.3 THE DATA SUBFRAME

The length of a Data subframe is specified by the selected DATA SENDER(S) in the Frame Type subframe. There may be 1, 2, 4, 8, 16, or 32 bytes in a Data subframe. As described earlier, there may be one or more DATA SENDER(S) sending in this subframe, depending on how many HEADER RECEIVERS are configured to respond to the S-field code. If several DATA SENDERS are selected, the Data subframe will either contain the logical OR of their data, or the largest value among them. (This is determined by whether the DATA SENDERS' arbitration was disabled or enabled by the Sender Arbitration Enable bit sent during the Header subframe.)

# \*\*\*\*\*\* THIS PAGE INTENTIONALLY LEFT BLANK \*\*\*\*\*\*

#### 5. SERIAL BUS LINES

The serial bus includes three lines: Serial Clock (SERCLK), Serial Data (SERDAT\*), and System Reset (SYSRESET\*).

SYSRESET\* is used to initialize all modules on the serial bus.

SERCLK is driven by a high-current totem-pole driver from the SERIAL CLOCK module, of which there is one per system.

SERDAT\* is a wired-OR line which can be driven with an open-collector driver by any module. A "one" on SERDAT\* results when one or more modules drive it Low. A "zero" results when no module is driving SERDAT\*, so that the backplane terminating resistors pull the signal High.

#### 5.1 SIGNAL TIMING

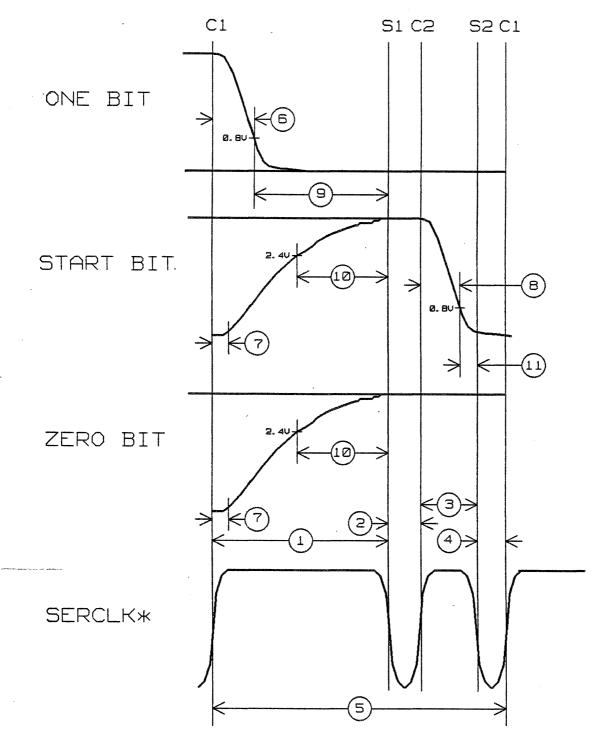

When the serial bus is used with a system bus, there are no prescribed timing constraints between its signals and any of the other signals on the backplane. The various modules on the serial bus <u>change</u> and <u>sample</u> the SERDAT\* signal level when transitions occur on SERCLK. The AC timing characteristics of SERCLK and SERDAT\* are shown in Table 5-1 and Figure 5-1.

## 5.2 BIT TRANSMISSION CODING

Each "bit cycle" of SERCLK is used to send one bit on SERDAT\*, and includes four transitions designated Cl, Sl, C2, and S2. There are three types of bits that can be sent during each bit cycle: a "one bit", a "zero bit", and a "start bit". These bits can be distinguished by serial bus modules by sampling the level of SERDAT\* on both the Sl and S2 transitions.

| TYPE OF<br>BIT | LEVEL SAMPLED<br>AT Sl | LEVEL SAMPLED<br>AT S2 |

|----------------|------------------------|------------------------|

| one            | Low                    | Low                    |

| zero           | High                   | High                   |

| start          | High                   | LOW                    |

If sufficient noise is induced onto the serial bus, the modules may be desynchronized (i.e. they may lose track of where frames begin and end). This condition must be detected and the modules resynchronized before frames are "garbled" and misinterpreted. When desynchronization occurs, one or more of the HEADER SENDERS send a start bit in the middle of a frame.

FRAME MONITORS check for a start bit in every bit cycle of SERCLK. When a FRAME MONITOR detects a start bit when no frame is in progress, it tracks the transmission to the end of the frame. If it samples another "High/Low" bit before it has finished counting out the frame, then it "jams" the frame transmission by holding SERDAT\* Low for at least 512 bit cycles. This ensures that the frame which was in progress won't be accepted as a valid frame.

FIGURE 5-1. PRELIMINARY SERIAL BUS TIMING

$\left( \right)$

| PARAMETER | DESCRIPTION                                              | (SEE<br>MIN | NOTES A | •   | NOTES                                                                                                          |

|-----------|----------------------------------------------------------|-------------|---------|-----|----------------------------------------------------------------------------------------------------------------|

| 1         | C1 to S1                                                 | 175         | 187.5   |     | С                                                                                                              |

| 2         | S1 to C2                                                 | 25          | 31.25   |     | С                                                                                                              |

| З         | C2 to S2                                                 | 50          | 62.5    |     | С                                                                                                              |

| 4         | 52 to C1                                                 | 25          | 31.25   |     | С                                                                                                              |

| 5         | C1 to C1 (SERCLK Cycle)                                  |             | 312.5   |     | C                                                                                                              |

| 6         | C1 to SERDAT* Low                                        | Ø           |         | TBS | D                                                                                                              |

| 7         | C1 to SERDAT* Released                                   | Ø           |         | TBS | D                                                                                                              |

| В         | C2 to SERDAT* Low                                        | Ø           |         | TBS | D                                                                                                              |

| 9         | SERDAT* Low to S1                                        | TBŚ         |         |     | E                                                                                                              |

| 1Ø        | SERDAT* High to S1                                       | TBS         |         |     | E                                                                                                              |

| 11        | SERDAT* Low to S2                                        | TBS         |         |     | E                                                                                                              |

| NOTES:    |                                                          |             |         |     | 1999 - Angel State (1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - |

| A All t   | imes given are in nanoseco                               | onds.       |         |     |                                                                                                                |

| B NOM a   | nd MAX columns apply to 3.                               | 2 Mbit      | /sec ra | te  |                                                                                                                |

|           | ERIAL CLOCK module must gu<br>ween two of its outgoing S |             |         | . – | 9                                                                                                              |

|           | serial bus module must gua<br>ween its incoming and outg |             |         |     |                                                                                                                |

|           | serial bus module is guara<br>ween the specified incomin |             |         |     |                                                                                                                |

TABLE 5-1. PRELIMINARY SERIAL BUS TIMING

ALC: NOT

• .

A desynchronized HEADER SENDER will not consider itself to have sent a start bit at the same time that a "one bit" is being sent by some other module. While it may drive SERDAT\* Low at the C2 edge of SERCLK during a "one", such a start bit will not be visible on SERDAT\*. The HEADER SENDER is required to sample the level of SERDAT\* on the Sl transition of SERCLK in the bit cycle that it sends the start bit. If SERDAT\* is High at Sl then it assumes the start bit was sent successfully and sends the rest of the Header subframe. If it was Low the HEADER SENDER tries again on the next bit cycle.

## EDGE DESIGNATION

- USE

- Cl All serial bus modules <u>change</u> SERDAT\* on this transition when sending "one" bits or "zero" bits.

- Sl All serial bus modules sample SERDAT\* on this transition.

- C2 HEADER SENDER modules <u>change</u> SERDAT on this transition from a High to a Low when sending a "start bit". Other modules maintain the SERDAT\* levels established at Cl.

- S2 HEADER RECEIVER modules <u>sample</u> SERDAT\* on this transition when they are waiting for a new frame to begin (i.e. when they are looking for a "start bit"). FRAME MONITOR modules <u>sample</u> SERDAT\* on every S2 transition, first to detect the beginning of a frame and then to detect a start bit that is sent while a frame is in progress.

The Cl, Sl, C2, and S2 transitions are shown in Figure 5-1.

NOTE: If a board or IC is designed for the serial bus which does not include a FRAME MONITOR module, it is recommended, but not required, that it detect start bits within a frame and "jam" SERDAT\* as described for a FRAME MONITOR. This provides greater security and protection against the effects of signal noise that might be sensed at one point on the serial bus, but not at another.

Onboard outputs from serial bus modules should be changed on the Cl transition of SERCLK, and onboard inputs to serial bus modules should be sampled on the Sl transition. Designers of serial bus hardware must guarantee that there will be no metastability problems when sampling inputs from onboard logic. This can be done by specifying setup and hold times that onboard logic must meet with respect to the Sl transition of SERCLK or, preferably, by providing synchronization logic for each input. In the latter case, it is helpful to specify a setup time to (some edge of) SERCLK, which will guarantee that the new state of an input will be recognized and acted upon.

#### 6. SERIAL BUS MODULES

A serial bus subsystem may include the following functional modules:

One SERIAL CLOCK module HEADER SENDERS HEADER RECEIVERS DATA SENDERS DATA RECEIVERS FRAME MONITORS

NOTE: These "functional modules" are used as vehicles for discussion of the serial bus protocol, and need not be considered a constraint to logic design. For example, a single IC could provide several of these functions.

The following sections describe the behavior of these modules, including their interaction with on-board signals. It is likely that IC's for the serial bus will be designed with various internal architectures and onboard signals. This specification often describes the details of an onboard interface in general terms. For instance, we may say that "onboard logic reads from a DATA RECEIVER" without specifying exactly how this is accomplished. This is done to avoid placing unnecessary constraints on the logic designs of serial bus interface hardware. In some cases actual signal lines are shown, to improve the explanation of the serial bus. Where this is done, the intent is to make clear what information crosses the boundary between the module and other on board logic. Other methods for conveying this same information across the boundary are also permissible.

It is expected that IC's designed for the serial bus will include some of what is described in this specification as "onboard logic". For example, the functional modules described below have several outputs which produce a pulse which is 1 SERCLK cycle in duration. Real IC's might use these "conceptual pulses" to produce outputs of longer duration.

#### 6.1 SERIAL CLOCK Module

The SERIAL CLOCK module must be located on either the Slot 1 board or the board in the highest-numbered slot. It drives the SERCLK signal with a high-current totem-pole driver. Whenever its SYSRESET\* input is True, the SERIAL CLOCK module drives SERDAT\* to "one" (Low). After its SYSRESET\* input goes False, the SERIAL CLOCK module releases SERDAT\* to "zero" (High) on a subsequent Cl edge of SERCLK, in keeping with the timing given in Figure 5-1.

## 6.2 HEADER SENDER Module

Onboard logic uses a HEADER SENDER module to initiate the transmission of a frame on the serial bus. The HEADER SENDER sends only the "Header subframe" portion of a frame: the remainder of the frame is sent by other modules including HEADER RECEIVERS, DATA SENDERS, and DATA RECEIVERS. Basically, the Header subframe sent by this module serves to "select" one or more HEADER RECEIVERS on the serial bus.

A HEADER SENDER must always be paired with a FRAME MONITOR module. Even though a HEADER SENDER often occupies the same board with a HEADER RECEIVER (etc.), these modules only communicate with each other over the serial bus. Because of this, the HEADER SENDER initiates frames involving its on-board HEADER RECEIVER in exactly the same way that it does with off-board HEADER RECEIVERS.

# 6.2.1 HEADER SENDER signals

As shown in Figure 6-1, a HEADER SENDER takes the SYSRESET\* and SERCLK signals from the serial bus as inputs, the SERDAT\* signal as a bidirectional I/O, and the FRAME IN PROGRESS signal from its onboard FRAME MONITOR as an input. It also has the following additional onboard signals:

- Priority Port A set of input lines and associated control signals, through which the 3 bit Message Priority value for subsequent frame transmission(s) is loaded into the HEADER SENDER. This port may consist of dedicated input lines, or a bus interface to an internal Priority register.

- Code 1,2 Ports Two similar sets of signals, through which two 10 bit selection codes for subsequent frame transmissions are loaded.

- Sender Arb Port A similar set of signals, through which the DATA SENDER Arbitration Enable bit for subsequent frame transmissions is loaded into the HEADER SENDER.

NOTE: The Priority, Code 1, Code 2, and Sender Arb Ports will often be implemented as registers that can be loaded from the same "bus interface", which may be connected to an onboard processor or onboard system bus interface.

SEND12, SEND21 Control inputs which cause the HEADER SENDER to send a "Header subframe". SEND12 makes the HEADER SENDER send the value from Code 1 Port in the "S field" of the Header subframe, and the value from Code 2 Port in the "R field". SEND21 makes the HEADER SENDER send the value from Code 2 Port in the "S field" and the value from Code 1 Port in the "R field".

FIGURE 6-1. HEADER SENDER with FRAME MONITOR

NOTE: Implementors of serial bus hardware may be tempted to make this SEND function a bit in an internal register, or "implied" by loading a Header subframe to be transmitted. However, by including one or more actual SEND inputs, an implementation can be made applicable to "dumb" boards as well as "intelligent" ones. The Header subframe to be transmitted can be loaded from a processor via the system bus, and its actual transmission can be "triggered" later by an onboard signal event.

SELECT

An output to a paired FRAME MONITOR module, indicating that this HEADER SENDER has won the serial bus arbitration and initiated the current frame. This causes the FRAME MONITOR to report the result of frame transmission to onboard logic.

LOST ARB

An alternative output to SELECT, indicating that the HEADER SENDER has tried to send a Header subframe, but has lost the arbitration for use of the serial bus to another HEADER SENDER.

NOTE 1: When a HEADER SENDER loses the serial bus arbitration, onboard logic can increase the Priority value for the subsequent retry (e.g. by one, perhaps up to a defined upper limit). This strategy, plus reduction of the Priority value when a frame is Cancelled (see 6.6.1), can ensure that each HEADER SENDER on the serial bus gets a fair share of accessto the bus.

NOTE 2: Information other than LOST ARB, about the results of sending a frame, is available from the outputs of the paired FRAME MONITOR.

6.2.2 HEADER SENDER Initialization

Whenever SYSRESET\* is Low, a HEADER SENDER initializes itself as follows:

- 1) It makes its LOST ARB output False.

- 2) It releases SERDAT\*.

- 3) It discards any Header subframe which was awaiting transmission when SYSRESET\* went Low.

- 4) If any of the Priority, Code 1, Code 2, or Sender Arb Ports are implemented as loadable registers, it clears those registers to zero.

When SYSRESET\* goes High, a HEADER SENDER enters "idle state".

#### 6.2.3 HEADER SENDER Operation

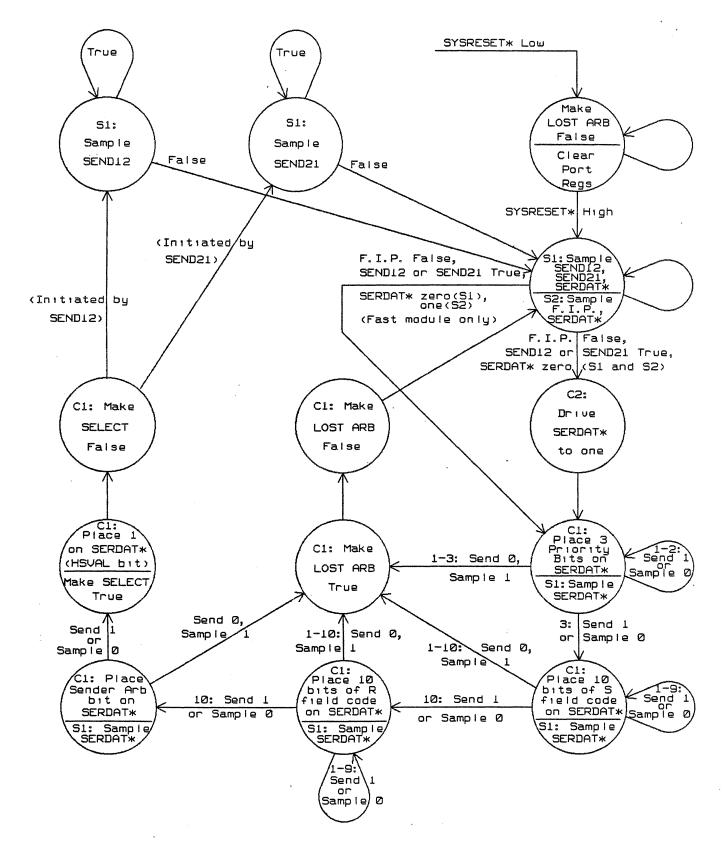

The state diagram of a HEADER SENDER is shown in Figure 6-2. In idle state, the HEADER SENDER samples SEND12, SEND21, and SERDAT\* on each S1 edge of SERCLK, and samples FRAME IN PROGRESS and SERDAT\* on each S2 edge of SERCLK.

la) IF it samples SEND12 or SEND21 True and SERDAT\* "zero" (High) on an Sl edge, and samples FRAME IN PROGRESS False and SERDAT\* "zero" (High) on the following S2 edge (i.e. if it samples a "zero" on SERDAT\*),

THEN it drives SERDAT\* to "one" (Low) at the C2 edge of the next bit cycle, generating a start bit. The HEADER SENDER then proceeds to step 2) below.

1b) IF it samples SEND12 or SEND21 True, and SERDAT\* "zero" (High) on an Sl edge, and samples FRAME IN PROGRESS False, SERDAT\* "one" (Low) on the following S2 edge,

(i.e., if another HEADER SENDER is sending a Start bit, one bit in advance of when this module would have sent one in case la). This can occur only if on-board logic made SEND12 or SEND21 True during the previous SERCLK cycle.)

THEN

IF the logic of this HEADER SENDER is fast enough to send the most significant bit of its Header subframe on the following bit cycle, (i.e. if it can drive SERDAT\* within the time specified from Cl),

THEN it proceeds to step 2, just as if the other HEADER SENDER'S start bit was its own. (The bus arbitration will then decide which HEADER SENDER must retire from the bus and try again.)

ELSE (the HEADER SENDER isn't fast enough to send the first bit of its Header subframe on the next bit cycle) it simply delays one cycle of SERCLK and returns to idle state sampling as described above. At the end of the current frame it will encounter the less demanding case la) above.

- 2) On the next Cl edge of SERCLK following the start bit, the HEADER SENDER places the most significant bit of its Message Priority value on SERDAT\*. Note that other HEADER SENDERS in the system may be doing the same thing.

- 3) On the following Sl edge of SERCLK, the HEADER SENDER samples SERDAT\* as an input.

IF it placed a "zero" on SERDAT\* at Cl, and it samples a "one" (Low) on SERDAT\* on the Sl edge,

THEN this HEADER SENDER has lost the arbitration for use of the serial bus. In this case, it makes its LOST ARB output True for one SERCLK cycle and returns to idle state.

Figure 6-2. HEADER SENDER State Diagram

- 4) The process described in 2-3) is repeated for each of the remaining bits in the Header subframe. This includes the remaining 2 bits of the Message Priority field, the S and R fields which are 10 bits each, the "sender arbitration enable bit", and the HSVAL bit. The HEADER SENDER always sends the HSVAL bit "one".

- 5) On the same Cl edge on which it sends the HSVAL bit, the HEADER SENDER makes its SELECT output True. This output indicates that this HEADER SENDER has won the serial bus arbitration and sent its Header subframe successfully. SELECT True makes the paired FRAME MONITOR report the results of the overall frame transmission to onboard logic.

NOTE: The HSVAL bit guards against the possibility that all HEADER SENDERS dropped out of the arbitration due to noise on the bus. If the HSVAL bit of any message frame is "zero", the frame is ignored by all HEADER RECEIVERS.

6) After sending HSVAL and making SELECT True, on the next SERCLK Cl edge it makes SELECT False. On subsequent Sl edges it samples SEND12 and SEND21, until the signal which initiated the operation (step 1) is made False by onboard logic. It then returns to idle state.

Note that this arbitration method guarantees that the Header subframe from at least one HEADER SENDER is always sent correctly (barring an "all drop out" error due to some externally induced noise glitch). If one considers the contending Header subframes as binary numbers, the subframe which is successfully sent is the one with the highest binary value.

But, if two or more HEADER SENDERS set out to send exactly the same Header subframe, they will not know of each other's presence, and each will proceed as if it had sent the subframe alone. This is fine for some frames. It is not appropriate for other frames (e.g. those which set a "semaphore"). When onboard logic causes a HEADER SENDER to initiate a Semaphore Set frame, it must ensure that the R field contains a code that is not used by by any other HEADER SENDER on the serial bus. If this requirement is met, the normal bus arbitration ensures that all but one HEADER SENDER (the one with the highest "Requester number") will retire from the bus before the Header subframe completes.

## 6.3 HEADER RECEIVER Module

A HEADER RECEIVER module may stand alone or may be paired with a DATA SENDER and/or a DATA RECEIVER. Its primary function is to compare the S and R fields in each Header subframe on the serial bus against its selection code value, and signal its paired modules and/or onboard logic if it finds a match.

### 6.3.1 HEADER RECEIVER Signals

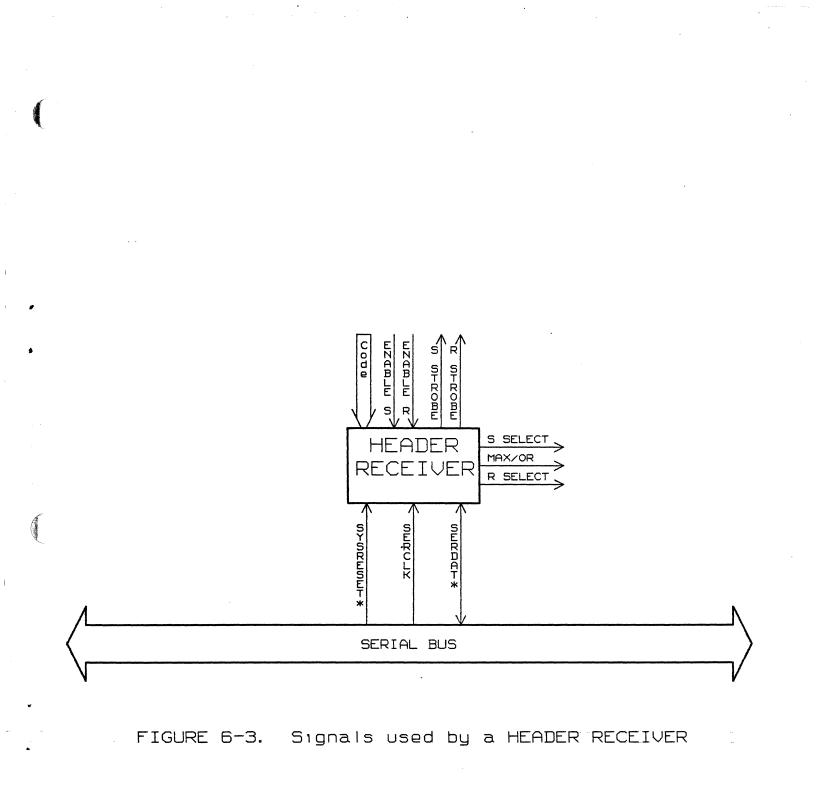

As shown in Figure 6-3, a HEADER RECEIVER takes the SYSRESET\* and SERCLK signals from the serial bus as inputs and the SERDAT\* signal as a bidirectional input/output. It also has a number of additional inputs from, and outputs to onboard logic, as follows:

- Code Port A set of parallel input lines and associated control signals, through which a 10-bit selection code value can be loaded into the HEADER RECEIVER. This may consist of dedicated inputs, or a "bus" interface to an internal selection code register.

- ENABLE S,R Two inputs from onboard logic which indicate whether to accept a frame with this module's selection code in the S or R field, respectively. If the HEADER RECEIVER matches its code in the S (or R) field, and the ENABLE S (ENABLE R) input is False, it "cancels" the frame.

- S,R SELECT Two outputs to a paired DATA SENDER and DATA RECEIVER, respectively, which indicate that the HEADER RECEIVER has detected a Header subframe on the serial bus which includes the selection code from Code Port in the S or R field, respectively. These outputs are made True for 1 SERCLK period.

- S,R STROBE Two outputs to onboard logic, which indicate the same information as S SELECT and R SELECT, but are made True at the end of the frame, and only if the frame is completely successful.

- MAX/OR An output to a paired DATA SENDER, which reflects the state of the "Sender Arbitration" bit in a Header subframe.

### 6.3.2 HEADER RECEIVER Initialization

Whenever SYSRESET\* is Low, a HEADER RECEIVER initializes itself as follows:

- 1) It makes its S SELECT, R SELECT, S STROBE, and R STROBE outputs False.

- 2) It releases SERDAT\*, and ignores it as an input.

- 3) If the Code Port is implemented as a loadable register, it clears the register to zero.

When SYSRESET\* is released, the HEADER RECEIVER enters "idle state".

6--8

# 6.3.3 Programming the Selection Code

If the selection code is implemented as a loadable register, the HEADER RECEIVER must be programmed with the desired value after initialization. For the purposes of this specification, this is considered part of system setup before any frames are sent on the serial bus. Reprogramming a HEADER RECEIVER with a new selection code, while the serial bus is in operation, is allowed but not covered by this specification.

# 6.3.4 HEADER RECEIVER Operation

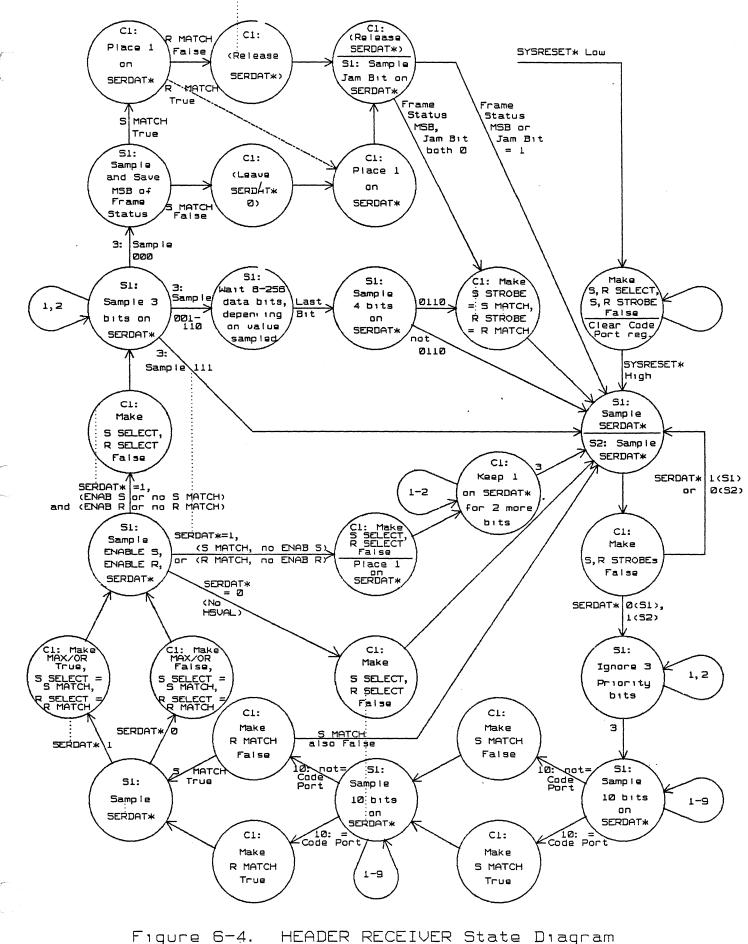

The state diagram of a HEADER RECEIVER is shown in Figure 6-4. Starting from idle state, this module proceeds as follows:

1) It samples SERDAT\* repeatedly on the Sl and S2 edges of SERCLK, until it samples a High on Sl and a Low on S2. This combination indicates a start bit on the serial bus.

NOTE: On the first Cl edge after returning from step 15 or 22 below, a HEADER RECEIVER makes its S STROBE and R STROBE outputs False.

- 2) It then counts off three bit times on SERCLK, thus ignoring the Message Priority field of the frame.

- 3) The HEADER RECEIVER then samples the next 10 bits on SERDAT\*, on Sl edges of SERCLK. As it samples these bits, it compares each to the corresponding bit of its selection code from Code Port. If all 10 bits are equal it makes an internal signal called "S Match" True, if not it makes S Match False.