# Signetics

Í

VMXbus Specification Manual Rev A

Oct. 1983

#### VMXbus

#### SPECIFICATION MANUAL

#### PUBLISHED BY

#### THE

#### VMEbus MANUFACTURERS' GROUP

#### Revision A

#### October, 1983

NOTE: While considerable effort has been expended to make this document comprehensive, reliable and unambiguous, it is still being published in preliminary form for public study and comment. Please direct any comments, or suggestions in writing to the VMEbus Manufacturers' Group secretary:

#### Rick Main Signetics Corporation 811 E. Arques Avenue P.O. Box 409 Sunnyvale, California 94086

. à • • -•

#### TABLE OF CONTENTS

-

Ξ.

| CHAPTER 1                        | INTRODUCTION                                                                                                                                                         |          |                                        |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------|

| 1.1                              | VMXbus SPECIFICATION OBJECTIVES                                                                                                                                      |          |                                        |

| 1.2.1                            | VMXbus STRUCTURE<br>Physical Structure<br>Functional Structure                                                                                                       |          | н<br>1 - страни<br>7 септерия - страни |

| 1.3                              | SIGNAL LINE STATES                                                                                                                                                   |          | -                                      |

|                                  |                                                                                                                                                                      |          |                                        |

| CHAPTER 2                        | VMXbus DATA TRANSFER BUS                                                                                                                                             |          |                                        |

| 2.1                              | SIGNAL LINES                                                                                                                                                         | -<br>-   |                                        |

| 2.2                              | MASTER AND SLAVE MODULES                                                                                                                                             | • .<br>• |                                        |

| 2.2.1<br>2.2.2<br>2.2.3          | D32 MASTERS and D32 SLAVES                                                                                                                                           | S .      |                                        |

| 2.2.4<br>2.2.5                   |                                                                                                                                                                      | LAVES    |                                        |

| 2.2.6                            | IMA MASTERS                                                                                                                                                          |          |                                        |

| CHAPTER 3                        | EXAMPLES OF DATA TRANSFER BUS OPERATIO                                                                                                                               | N        |                                        |

| 3.1                              | DATA TRANSFER CYCLE TYPES                                                                                                                                            |          |                                        |

| 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5 | Single Write Cycle<br>Single Read Cycle<br>Sequential Write Cycle<br>Sequential Read Cycle<br>Indivisible Single Address Cycle<br>Indivisible Multiple Address Cycle |          |                                        |

| CHAPTER 4 MA                     | STER AND SLAVE TIMING SPECIFICATIONS                                                                                                                                 |          |                                        |

4.1 General Information

4.2 Single Write Cycle

٠

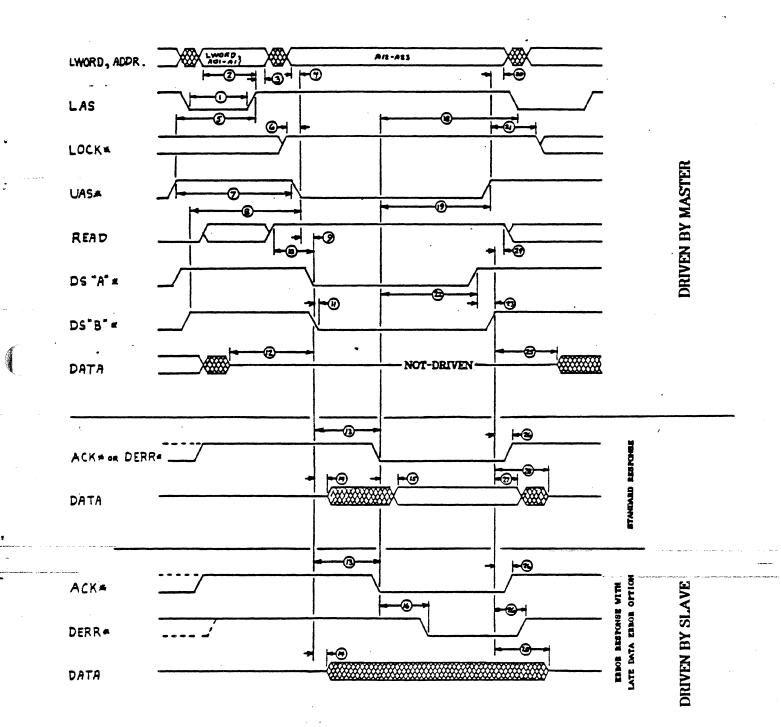

- 4.3 Single Read Cycle

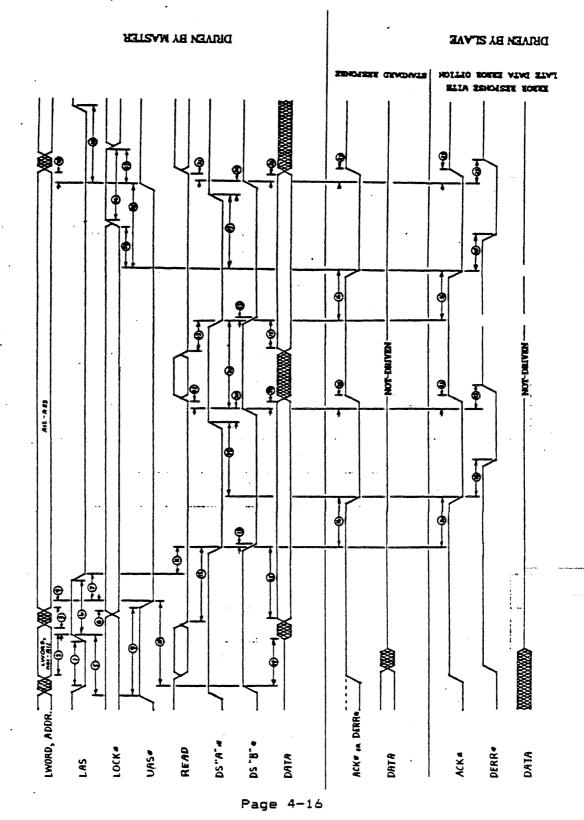

- 4.4 Sequential Write Cycle

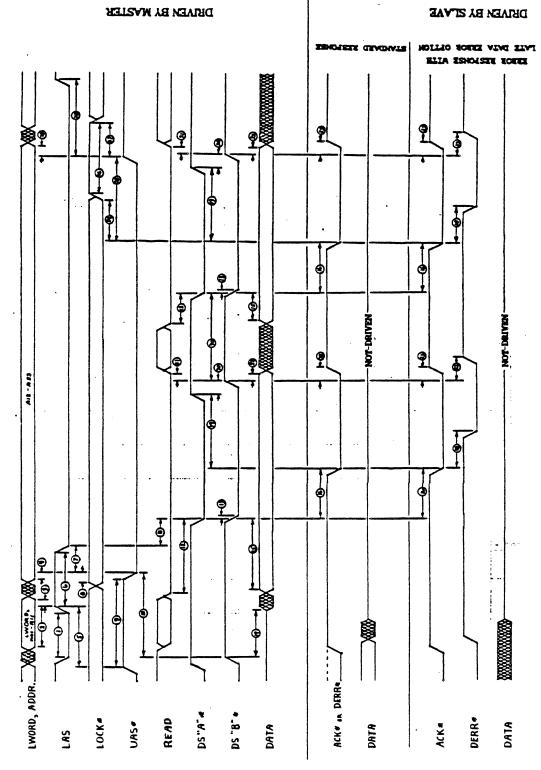

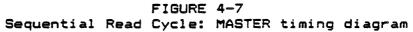

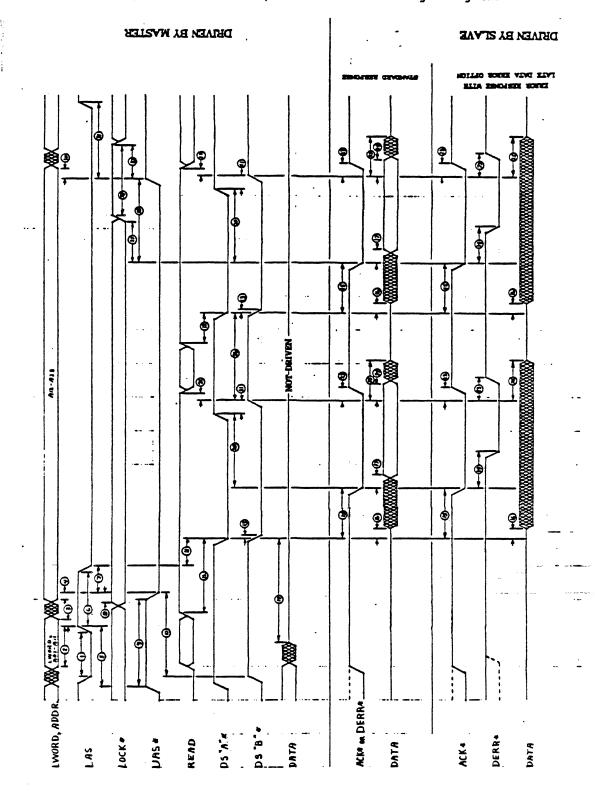

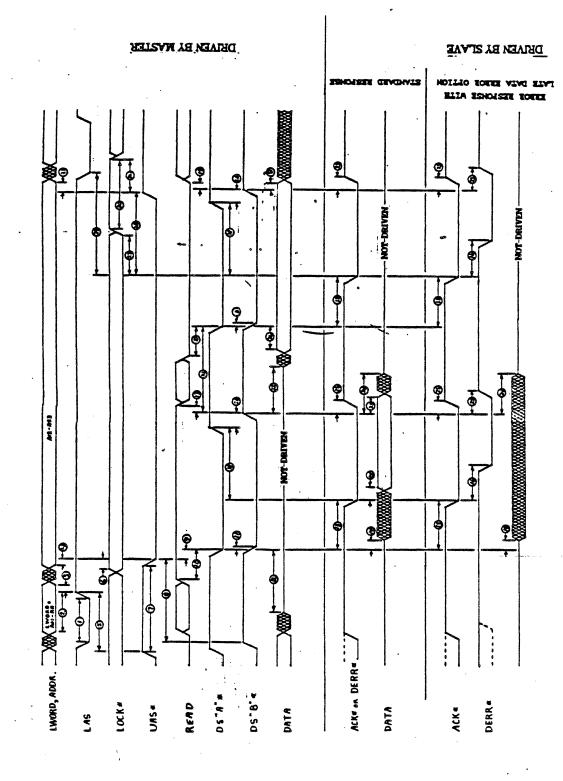

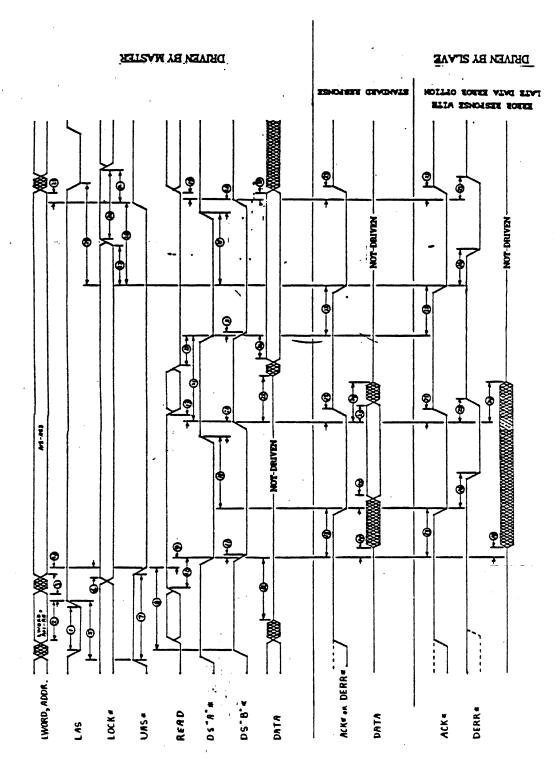

- 4.5 Sequential Read Cycle

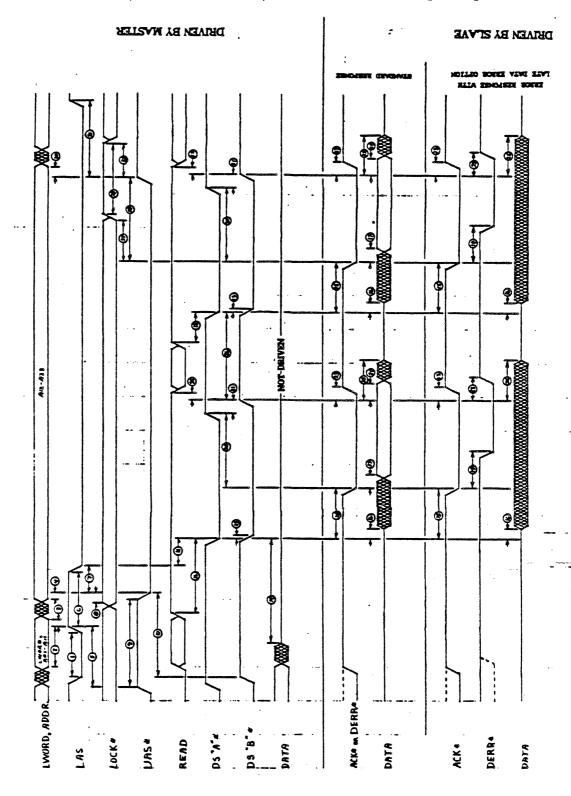

- 4.6 Indivisible Single Address Cycle

- 4.7 Indivisible Multiple Address Cycle

- 4.8 Withdrawn Cycle

CHAPTER 5 VMXbus ARBITRATION PROTOCOL

5.1 SIGNAL LINES

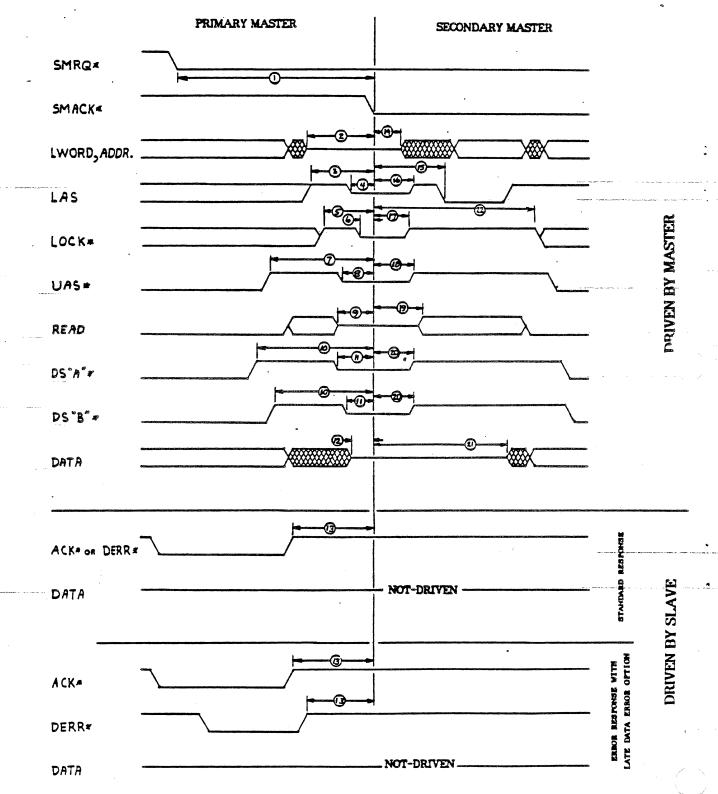

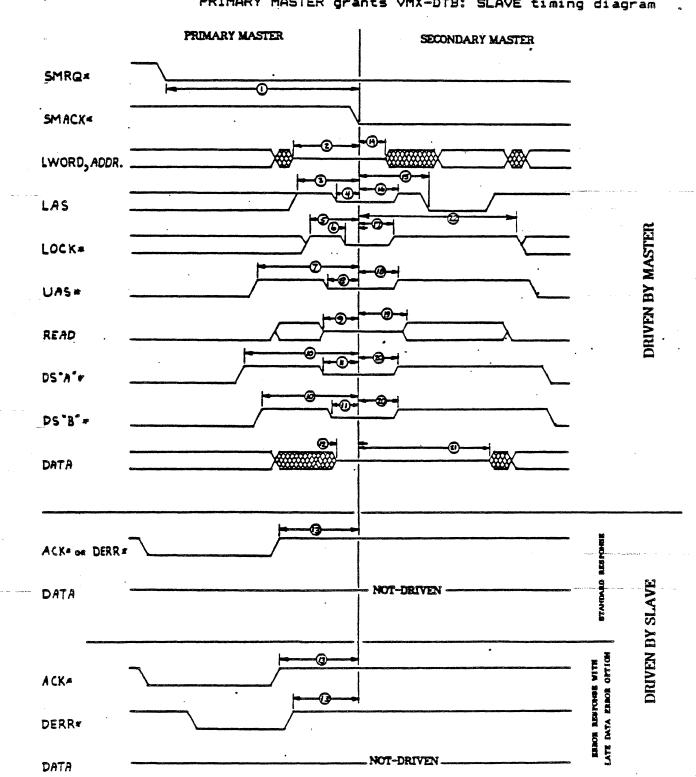

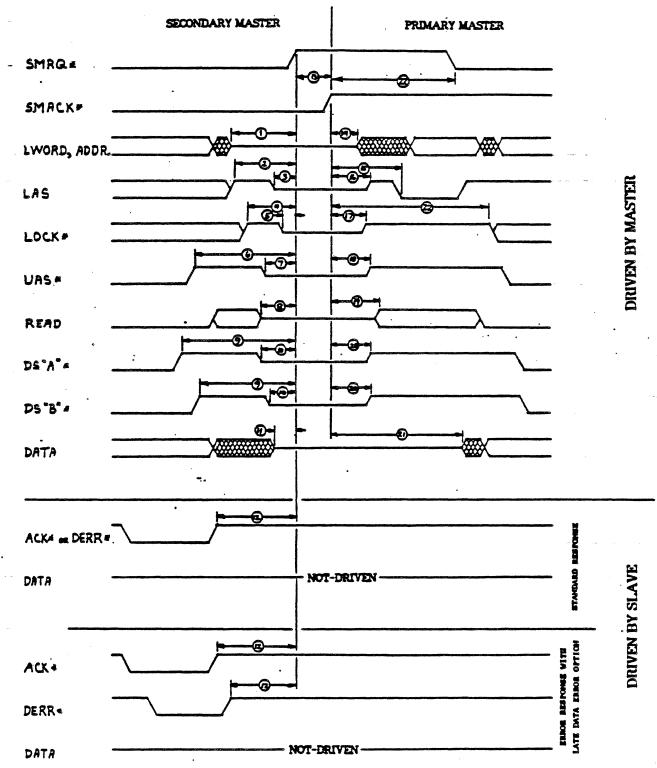

5.2 EXAMPLES OF ARBITRATION OPERATION 5.2.1 PRIMARY MASTER Grants VMX-DTB TO SECONDARY MASTER 5.2.2 PRIMARY MASTER Receives VMX-DTB From SECONDARY MASTER 5.3 ARBITRATION TIMING DIAGRAMS 5.3.1 PRIMARY MASTER Grants VMX-DTB

2 . 2

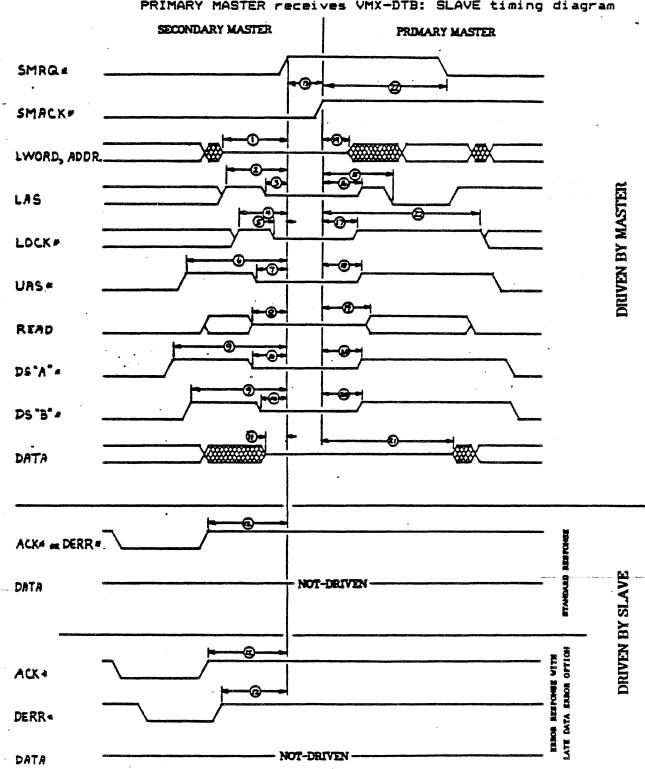

5.3.2 PRIMARY MASTER Receives VMX-DTB

#### CHAPTER 6 ELECTRICAL SPECIFICATIONS

- 6.1 INTRODUCTION

- 6.2 POWER DISTRIBUTION

6.3 ELECTRICAL SIGNAL CHARACTERISTICS

6.4 DRIVER SPECIFICATIONS

- 6.4.1 Totem-pole Drivers

- 6.4.2 Tri-state Drivers

- 6.4.3 Transceivers

- 6.4.4 Open-collector Drivers

- 6.5 RECEIVER SPECIFICATIONS

- 6.6 SIGNAL LINE TERMINATIONS

- 6.7 ISOLATION LINES

- 6.8 BOARD SIGNAL LOADING

- 6.9 BACKPLANE RIBBON CABLE SPECIFICATION

#### CHAPTER 7 MECHANICAL SPECIFICATIONS

7.1 DEFINITION OF TERMS

7.2 VMXbus BACKPLANE DESCRIPTION

7.3 VMXbus EUROCARD DESCRIPTION

7.4 VMXbus PIN ASSIGNMENT

• • • . • • · \_ . • •

## CHAPTER 1

#### 1.1 VMXbus SPECIFICATION OBJECTIVES

The VMXbus is a "subsystem bus" which has been designed for use with VMEbus. It provides a high speed secondary path which is optimized for connecting up to six boards in a subsytem configuration. This subsystem can transfer data from board to board over its VMXbus interface without waiting for and without burdening the primary bus (VMEbus). This specification has been written with the following objectives:

a) To specify the electrical characteristics required to design boards that will reliably transfer data between each other over the VMXbus.

b) To specify the mechanical characteristics required to be compatible with VMEbus systems.

c) To specify protocols that precisely define the interaction between the boards that are interfaced to each other over the VMXbus.

d) To specify the terminology used to describe VMXbus based subsystems.

#### 1.2 VMXbus STRUCTURE

The structure of the VMXbus can be described from two points of view: its physical structure and its functional structure. The following sections describe each in detail.

1.2.1 Physical Structure

The physical structure of the VMXbus is composed of an "expanded" VMEbus card rack, one to six plug-in PC boards, and a backplane ribbon cable. The expanded card rack provides both a P1 backplane and a P2 backplane. The P2 backplane buses only the "b" row of pins on the three-row connectors. (The outer two rows of connector pins are left unbused by the P2 backplane: they typically protrude through the rear of the P2 backplane as wire wrap pins and are bused for VMXbus use with a ribbon cable which is pushed onto the wirewrap pins. This cable has from two to six connectors on it. The cable buses the two outer rows of pins of adjacent P2 connectors allowing the boards in these slots to transfer data over the cable.

A board that is inserted from the front of the card rack may have a VMEbus interface, a VMXbus interface, or both. For example, a global I/O board might have only a VMEbus interface, a CPU or a memory board might have both, and a math processor might have only a VMXbus interface. Any board that has a VMXbus interface uses the two outer rows of the J2 connector.

The use of a ribbon cable to bus the P2 connectors allows any group of up to six adjacent slots to function as a subsystem. The user can install two or more cables to create several VMXbuses in a single card rack. Each of these VMXbus subsystems can operate independently of the primary system bus (VMEbus) and independently of each other. It also permits some slots to be used for other purposes such as I/O signals.

1.2.2 Functional Structure

The VMXbus consists of two groups of signal lines, called the VMXbus Data Transfer Bus (VMX-DTB), an arbitration bus, and a collection of "functional modules" which are configured as required to interface devices to these buses. The functional modules communicate with one another by means of bus signal lines provided by the ribbon cable.

#### NOTE

The "functional modules" defined in the specification are used as vehicles for discussion of the bus protocol, and need not be considered a constraint to logic design. For example, the board designer may choose to design a board which has both a MASTER and a SLAVE module on it.

The VMXbus Data Transfer Bus (VMX-DTB) consists of the data and address pathways and associated control signals. Functional modules called MASTERS and SLAVES use the VMX-DTB to transfer data between each other.

Since there can be two MASTERS in a VMXbus group a means must be provided to transfer control of the VMX-DTB between these two MASTERS in an orderly manner, and to guarantee that only one MASTER controls the VMX-DTB at a given time. The Arbitration Bus is defined to do this.

#### NOTE

The terms PRIMARY MASTER and SECONDARY MASTER are used in this specification to distinguish between the MASTER that arbitrates the VMX-DTB and the MASTER that must request, and be granted, the VMX-DTB before using it.

#### 1.3 SIGNAL LINE STATES

The VMXbus specification describes all activity on its signal lines in terms of levels and transitions. A signal line is always assumed to be in one of two levels or in transition between these levels. Whenever the term "high" is used, it refers to a high TTL voltage level (>= +2.0 V). The term "low" refers to a low TTL voltage level (<= 0.8 V). A signal line is "in transition" when its voltage is moving between + 0.8 V and + 2.0 V.

There are two possible transitions which can appear on a signal line, and these will be referred to as "edges". A RISING EDGE is defined as the time period during which a signal makes its transition from a low level to a high level. A FALLING EDGE is defined as the time period during which a signal line makes its transition from a high level to a low level.

1.4 USE OF THE ASTERISK (\*)

To help define usage of their signal lines, some signal line mnemonics have an asterisk suffix. Depending on the type of signal this suffix has one of three meanings:

1.4.1 Strobe lines

Where an asterisk is used on a strobe line, it indicates that the data being strobed is valid and is sampled on the FALLING edge of the stobe. Strobe lines which fit this category are UAS\*, DS1\*, and DSO\*.

Where there is no asterisk on a strobe line, it indicates that the data being strobed is valid and is sampled on the RISING edge of the strobe. There is one strobe line which fits into this category: LAS.

1.4.2 Bused Signal Lines

The address and data buses carry binary information (i.e. one/zero). The fact that these lines have no asterisk suffix indicates that a "one" is represented by a high level and a "zero" by a low level.

1.4.3 Other Signal Lines

Where an asterisk is used on a signal line other than a strobe line it indicates that a low level on that line represents a "true" state and a high level a "false" state. Signal lines which fit this category are LWORD\*, DERR\*, ACK\*, SMREQ\*, and SMGNT\*.

Where there is no asterisk it indicates that the high level represents a "true" state. Thus the READ signal line

indicates a read operation when high and a write operation when low.

.

#### CHAPTER 2 VMXbus DATA TRANSFER BUS

#### 2.1 SIGNAL LINES

The VMXbus contains a high speed asynchronous parallel Data Transfer Bus (VMX-DTB). This VMX-DTB is used by a PRIMARY MASTER and a SECONDARY MASTER to select SLAVE locations and to transfer data to or from those locations. The PRIMARY MASTER is typically a processor, the SECONDARY MASTER is typically an intelligent I/O controller, and the SLAVE is typically a memory array.

The VMX-DTB can be logically divided into address, data, and control line groups:

LWORD/A12 - A11/A23 (23) Multiplexed Address lines + longword (LDS\* + UDS\* provide a 24th bit)

D00-D31 (32) Data lines

| LAS   | Lower Address Strobe          |

|-------|-------------------------------|

| UAS*  | Upper Address Strobe          |

| LDS*  | Lower (Odd Byte) Data Strobe  |

| UDS*  | Upper (Even Byte) Data Strobe |

| ACK.* | Acknowledge                   |

| DERR* | Data Error                    |

| READ  | Read/Write Control            |

Data is transferred 8 bits, 16 bits, or 32 bits at a time. Eight bit transfers are called "byte transfers". Byte locations which are addressed with an even address are called "even byte locations" and byte locations addressed with an odd address are called "odd byte locations." Byte transfers to even byte locations are conveyed by D08-D15, and byte transfers to odd byte locations are conveyed by D00-D07. Sixteen bit transfers are called "word transfers". These words are conveyed by D00-D15. Thirty-two bit transfers are called "longword transfers". longwords are conveyed by D00-D31.

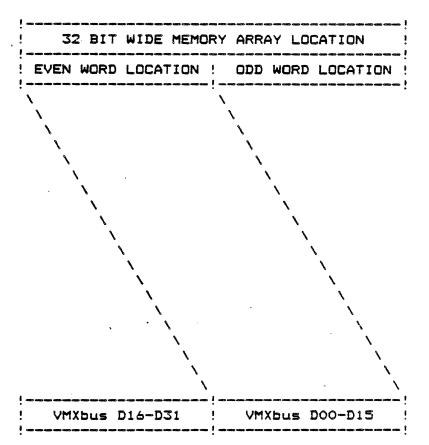

Data is stored into memory 8, 16, or 32 bits a time and then read 8,16, or 32 bits at a time. Figure 2-1 shows that when the most significant 16 bits of a longword location is read from (or written to) the data is transferred over D00-D15instead of D16-D31 as one might expect. This means that 32 bit wide memory boards must have on-board logic to translate the most significant 16 bits of the memory array to the lower 16 data lines of the VMXbus (D00-D15)

#### FIGURE 2-1

WHEN A WORD ACCESS IS DONE THE DATA IS ALWAYS TRANSFERRED ON VMXbus lines DOO-D15.

When 32 bits of data are written they are stored in a single longword location. When reading this data 16 bits at a time the even word address (A01 = 0) corresponds to the longword location bits D16-D31.

Likewise if two 16 bit words of data are stored in adjacent word locations (an even word location and the next higher odd word location) they may be read as a longword with the even word (A01 = 0) forming the most significant 16 bits (D16-D31) Two bytes of data may be stored in each word location. The even byte location is the most significant byte of the word location. The odd byte is the least significant. The even byte is selected when UDS\* is driven low by the MASTER, the odd byte is selected when LDS\* is driven low, and both are selected for a word access when both LDS\* and UDS\* are low. Figure 2-2 summarizes how the various signal lines on VMXbus are used to do 8, 16, and 32 bit transfers.

.

#### FIGURE 2-2

#### SIGNAL LEVELS USED TO ACCESS BYTES, WORDS, AND LONGWORDS

|                                                 |                               | سه هي هه هنه هنه ويه خله جنه هي هي و |                             |                             | an 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 1999 - 199 |  |

|-------------------------------------------------|-------------------------------|--------------------------------------|-----------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| •                                               |                               | LONGWORD LOCATION                    |                             |                             |                                                                                                                 |  |

|                                                 | EVEN WORD                     | LOCATION                             | ! ODD WORD                  | LOCATION                    |                                                                                                                 |  |

|                                                 | ! EVEN BYTE !<br>! LOCATION ! | LOCATION                             | EVEN BYTE                   | ! ODD BYTE<br>! LOCATION    | -                                                                                                               |  |

|                                                 | ! D31-D24 !                   | D23-D16                              | •                           | ! D07-D00                   | 1                                                                                                               |  |

| BYTE ACCESS<br>LWORD<br>AO1<br>UDS*<br>LDS*     | HIGH<br>Low<br>Low<br>HIGH    | HIGH<br>LOW<br>HIGH<br>LOW           | HIGH<br>HIGH<br>Low<br>HIGH | HIGH<br>HIGH<br>HIGH<br>LOW |                                                                                                                 |  |

| WORD ACCESS<br>LWORD<br>A01<br>UDS*<br>LDS*     | HIGH<br>Low<br>Low<br>Low     | Note 1                               | HIGH<br>HIGH<br>Low<br>Low  | Note 1                      |                                                                                                                 |  |

| LONGWORD ACCESS<br>LWORD<br>A01<br>UDS*<br>LDS* | LOW<br>Low<br>Low<br>Low      | Note 2                               | Note 3                      | Notes 2 %                   | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2                     |  |

#### NOTES:

Not legal to access 16 bits of data on an odd byte address.

Not legal to access 32 bits of data on an odd byte address.

Not legal to access 32 bits of data on an odd word address.

#### 2.2 MASTER AND SLAVE MODULES

All VMXbus MASTERS and SLAVES can do 8 bit and 16 bit data transfers. Some MASTERS and SLAVES can also do 32 bit transfers. MASTERS that can only do 8 and 16 bit transfers are called D16 MASTERS, while those that can also do 32 bit transfers are called D32 MASTERS. SLAVES that can handle only 8 and 16 bit transfers are called D16 SLAVES while those that can also handle 32 bit transfers are called D32 SLAVES.

There are four categories of cycles used to transfer data on the VMXbus: single cycles, sequential cycles, indivisible single address cycles, and indivisible multiple address cycles. In order to allow VMXbus board vendors to specify which categories of cycles their boards can do, the following abbrieviated notation has been developed:

| SGL | Single cycles supported                       |

|-----|-----------------------------------------------|

| SEQ | Sequential cycles supported                   |

| ISA | Indivisible single address cycles supported   |

| IMA | Indivisible multiple address cycles supported |

These abbrieviations are added, as suffixes, to the data width to give a complete description of a board. For example a D32 MASTER capable of all cycles would be called a D32, SGL, SEQ, ISA, IMA MASTER.

#### NOTE:

ALL MASTERS MUST SUPPORT, AS A MINIMUM, SINGLE CYCLES. ALL SLAVES MUST SUPPORT, AS A MINIMUM, SINGLE CYCLES, INDIVISIBLE SINGLE ADDRESS CYCLES, AND INDIVISIBLE MULTIPLE ADDRESS CYCLES.

2.2.1 D16 MASTERS And D16 SLAVES

The D16 MASTER definition allows 16 bit processors and 16 bit DMAL devices to be interfaced to the VMXbus. The D16 SLAVE provides 16 bit memory. Since 16 bit processors sometimes access memory one byte at a time, D16 SLAVES must allow their even and odd byte locations to be accessed one byte at a time. Whenever a byte transfer is done to or from an odd byte location, it is done over D00-D07. Whenever a byte transfer is done to or from an even byte location it is done over D08-D15. (Transferring the even and odd bytes over the same data lines that are used in 16 bit transfers minimizes the multiplexing logic required on the D16 memory slave.)

#### 2.2.2 D32 MASTERS And D32 SLAVES

D32 MASTERS can do LONGWORD (32 bit) transfers over D00-D31, but they can also act like D16 MASTERS (i.e. they can do byte transfers and word transfers: they do odd byte transfers over D00-D07, even byte transfers over D08-D15, and word transfers over D00-D15). This means that they can access D16 slaves as well as D32 SLAVES.

D32 SLAVES allow each of their locations to be accessed one byte at a time, one word at a time, or one longword at a time. When doing byte transfers they transfer even bytes over D08-D15, and their odd bytes over D00-D07. When doing word transfers they always use D00-D15. This means that D32 SLAVES must have logic that allows data in the upper 16 bits of its 32 bit memory array to be accessed through D00-D15. Because D32 SLAVES allow access in all of these ways they can be accessed by D16 MASTERS as well as D32 MASTERS.

#### 2.2.3 Mixing D16 and D32 MASTERS and SLAVES.

VMXbus systems can be built with mixtures of D16 and D32 MASTERS and SLAVES. This can be done in any combination, and these boards can still communicate data successfully, with one qualification: if a D32 MASTER attempts a 32 read or write on D16 SLAVE that SLAVE must respond by driving DERR\* low, indicating an error. (The D32 MASTER can still transfer data to and from this SLAVE by doing it 16 bits at a time.)

#### 2.2.4 SEQ MASTERS And SEQ SLAVES.

SEQ MASTERS are able to do sequential access cycles as described in section 3.1.3 and 3.1.4. Most SEQ MASTERS are DMA controllers, but there is no reason why a processor board couldn't be designed to use sequential cycles. (e.g. a processor board with a cache might read blocks of data using the sequential mode.)

SEQ SLAVES are able to respond to sequential access cycles as described in sections 3.1.3 and 3.1.4. During a sequential access cycle a SEQ SLAVE latches the initial address from the bus and then increments that address each time data is read or written. Since there are actually three types of sequential access cycles (byte, word, and longword) the SEQ SLAVE must increment its internal counter in such a way that the next access results in a transfer on the next location in memory. (Since memory SLAVES may have 16, 32 or even 64 bit wide internal memory arrays, the VMXbus spec doesn't dictate how the internal address counter is incremented.)

#### 2.2.5 Mixing SEQ and non-SEQ MASTERS and SLAVES

VMXbus systems can be built with mixtures of SEQ and non-SEQ MASTERS and SLAVES. If an SEQ MASTER attempts a sequential cycle on a non-SEQ SLAVE that SLAVE will respond by driving DERR\* low, indicating an error. (The SEQ MASTER can still transfer data to and from this SLAVE by doing single cycles.

#### 2.2.6 IMA MASTERS

IMA MASTERS are able to do indivisible multiple address cycles as described in sections 3.1.6. These cycles allow a VMXbus MASTER to access VMXbus SLAVE locations while excluding all other MASTERS from access to the same SLAVE locations.

All SLAVES must be able to handle IMA cycles. Many VMXbus SLAVES are "dual ported", allowing VMXbus MASTERS to access their locations through one port and VMEbus MASTERS to access the same locations through the second post. These dual ported boards must be designed so that whenever they respond to an indivisible multiple address cycle on the VMXbus they "lock out" all accesses from VMEbus until all of the "reads" and "writes" of the cycle are completed.

#### CHAPTER 3 EXAMPLES OF DATA TRANSFER BUS OPERATION

#### 3.1 DATA TRANSFER CYCLE TYPES

Putting aside, for the moment, the fact that data may be transferred over VMXbus one byte, two bytes, or four bytes at a time, there are six basic cycle types:

- 1) Single write cycle

- 2) Single read cycle

3) Sequential write cycle

- 4) Sequential read cycle

- 5) Indivisible single address cycle

- 6) Indivisible multiple address cycle

There are some cases in which a MASTER may direct a SLAVE to do something that it cannot do. For example, a D16 SLAVE may be told to do a 32 bit read, or a non-SEQ SLAVE may be told to do a sequential cycle. When this happens the SLAVE "aborts" the cycle. This results in six more cycle types:

- 7) Aborted single write cycle

- 8) Aborted single read cycle

- 9) Aborted sequential write cycle

- 10) Aborted sequential read cycle

- 11) Aborted indivisible single address cycle

- 12) Aborted indivisible multiple address cycle

A SLAVE may acknowledge a cycle from the MASTER and then find itself unable to complete the cycle. For example, it may detect a parity error when retrieving data from its memory array. To indicate this to the MASTER it aborts the cycle. This sequence results in six more cycle types:

13) Late aborted single write cycle

- 14) Late aborted single read cycle

- 15) Late aborted sequential write cycle

- 16) Late aborted sequential read cycle

- 17) Late aborted indivisible single address cycle

- 18) Late aborted indivisible multiple address cycle

If no SLAVE responds (e.g. the SLAVE has malfunctioned, or there is no SLAVE at the address provided) a timer on the MASTER board terminates the cycle, resulting in six more cycle types:

19) Timed-out single write cycle

- 20) Timed-out single read cycle

- 21) Timed-out sequential write cycle

22) Timed-out sequential read cycle

23) Timed-out indivisible single address cycle

24) Timed-out indivisible multiple address cycle

The VMXbus spec allows a MASTER to begin a cycle BEFORE it has determined whether the location it needs to access is on the VMXbus or elsewhere. This feature can improve performance on processor boards where some addresses result in accesses over the VMXbus while others result in on-board accesses or accesses to other buses, such as VMEbus.

The processor begins such a cycle in the usual manner, by sending the "lower address" to the VMXbus SLAVES, before it knows whether or not a VMXbus access is required. If, after decoding the address, it determines that a VMXbus access is not required, then it doesn't proceed with the rest of the cycle. Such a cycle is said to be "withdrawn" by the MASTER. Since all six of the basic cycles types begin in the same way (with the transmission of the lower address) they all result in similar timing when they are withdrawn. This results in one more additional cycle type:

25) Withdrawn cycle

Example flow diagrams are given for the six basic cycle types 1) through 6) in sections 3.1.1 through 3.1.6.

#### 3.1.1 Single Write Cycle

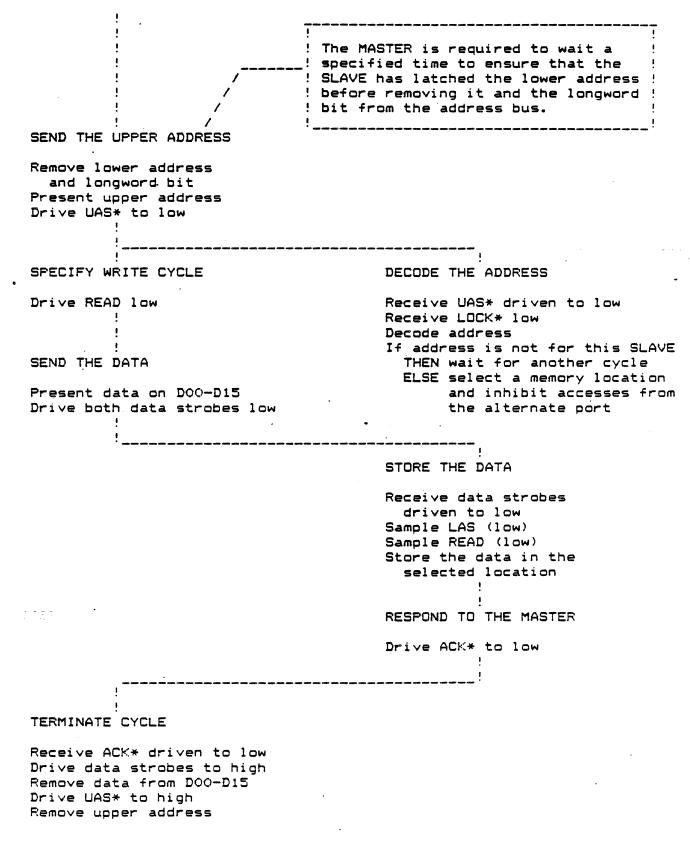

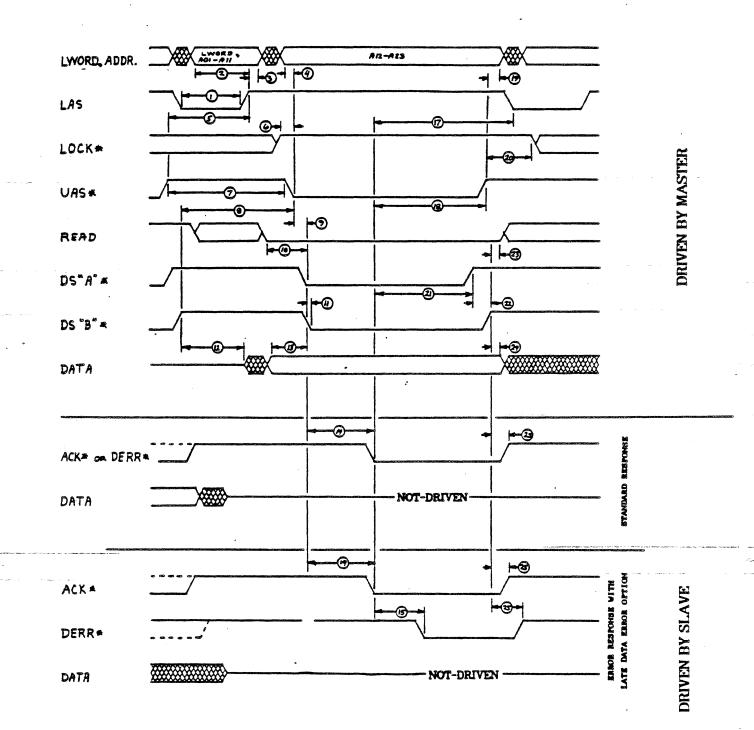

There are three kinds of single write cycles: byte write, word write, and longword write. Figure 3-1 shows the flow diagram for one of these: a single word write cycle, and should be referred to while reading the following cycle flow description.

The cycle begins when the MASTER drives LAS to low. LAS is then held low until the MASTER drives the twelve address bus lines with address bits AO1 through A11, and the "longword" level appropriate for the word transfer (low). All these lines must be valid before LAS is driven to high.

The SLAVE latches the "lower address" and the longword bit on the rising edge of LAS. After a specified hold time, the MASTER removes the lower address and longword bit from the address bus and then places the "upper address" on it. (A12-A23). When these new address bits have stabilized, the MASTER drives UAS\* to low. Each SLAVE, upon receiving the upper address, determines whether it is the one being addressed.

While the SLAVE is decoding the address the MASTER drives READ low to indicate that a write cycle is being done. Then the MASTER places its 16 bits of data on data bus lines D00-D15 and drives the two data strobes low, commanding the SLAVE to write the data into memory.

When the selected SLAVE detects the data strobes driven to low it must respond in three different ways:

1) If it is a D16 SLAVE, and has been directed to do a 32 bit write, it responds by driving DERR\* low.

2) If it is able to handle the required write it drives ACK\* low and stores the data into the selected memory location.

3) If it drives ACK\* low, but then encounters some difficulty in completing the write (for example, writing to a ROM) it drives DERR\* low within a specified time limit to indicate that the write was not successful.

#### NOTE

Some VMXbus MASTERS can handle late-aborted cycles while others cannot. To guarantee compatibility between VMXbus boards all SLAVES should be configurable to operate in the normal aborted cycle mode. Those SLAVE boards which can also be configured to provide late-aborted cycles typically provide a range of ACK\* to DERR\* delays from 0 to 125 nS. The amount of delay may be selected either

statically (e.g. by jumpers) or dynamically (e.g. by control registers.)

Figure 3-1 shows the most likely of these possiblities: the successful write. When the SLAVE responds by driving ACK\* to low the MASTER removes the data from DOO-D15, removes the upper address from the address bus, and drives UDS\*,LDS\* and UAS\* high in preparation for the next cycle.

When the SLAVE detects the data strobes driven to high, it i releases ACK\*, allowing the data bus to be used for the next cycle.

### Figure 3-1 A Single Word Write Cycle

4

.

(

l

1

1

) 1 ٠

10 . 2 -

| VMXbus MASTER                                                                                    | VMXbus SLAVE                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEND THE LOWER ADDRESS                                                                           | •<br>•                                                                                                                                                                           |

| Drive LAS to low<br>Present lower address<br>and longword=low<br>Drive LAS to high<br>!          |                                                                                                                                                                                  |

|                                                                                                  | LATCH THE LOWER ADDRESS                                                                                                                                                          |

|                                                                                                  | Receive LAS driven to high<br>Latch lower address<br>and longword bit                                                                                                            |

|                                                                                                  | The MASTER is required to wait a<br>specified time to ensure that the<br>SLAVE has latched the lower address<br>before removing it and the longword<br>bit from the address bus. |

| SEND THE UPPER ADDRESS                                                                           |                                                                                                                                                                                  |

| Remove lower address<br>and longword bit<br>Present upper address<br>Drive UAS* to low<br>!<br>! |                                                                                                                                                                                  |

| SPECIFY WRITE CYCLE                                                                              | DECODE THE ADDRESS                                                                                                                                                               |

| Drive READ low<br>!<br>SEND THE DATA<br>Present data on D00-D15                                  | Receive UAS* driven to low<br>Decode address<br>If address is not for this SLAVE<br>THEN wait for another cycle<br>ELSE select a memory location                                 |

| Drive both data strobes low<br>!                                                                 |                                                                                                                                                                                  |

|                                                                                                  | STORE THE DATA                                                                                                                                                                   |

|                                                                                                  | Receive data strobes<br>driven to low                                                                                                                                            |

|                                                                                      | Sample LAS (high)<br>Sample READ (low)<br>Store the data in the<br>selected location |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                                                                      | !<br>RESPOND TO THE MASTER                                                           |

|                                                                                      | Drive ACK* to low                                                                    |

| තා හා කා                                         |                                                                                      |

| TERMINATE CYCLE                                                                      |                                                                                      |

| Receive ACK* driven to low<br>Drive data strobes to high<br>Remove data from DOO-D15 |                                                                                      |

| Drive UAS* to high<br>Remove upper address<br>!                                      |                                                                                      |

| • and and any                                    | ACKNOWLEDGE TERMINATION                                                              |

|                                                                                      | Receive data strobes                                                                 |

.

- 15

----

. . . . .

driven to high Release ACK\*

.

---

-

.

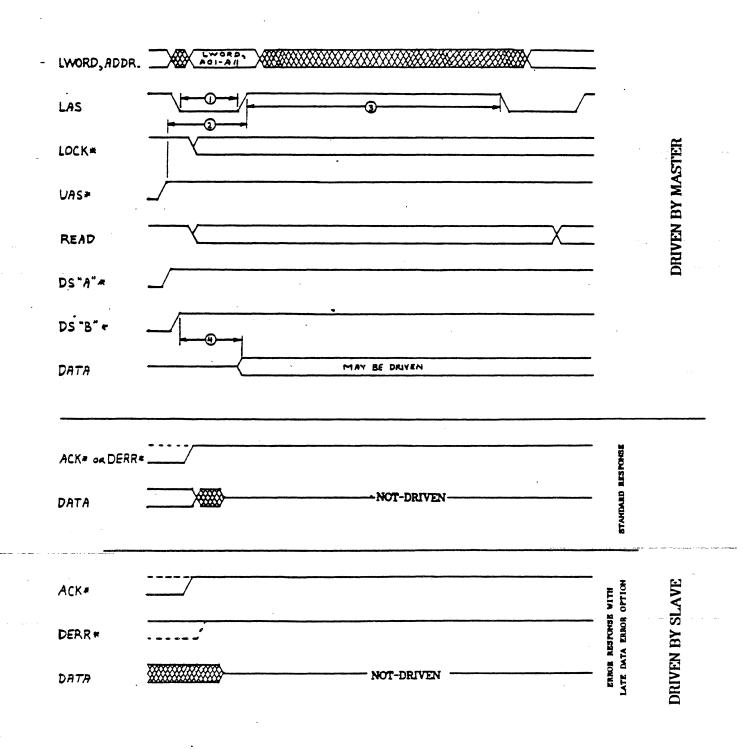

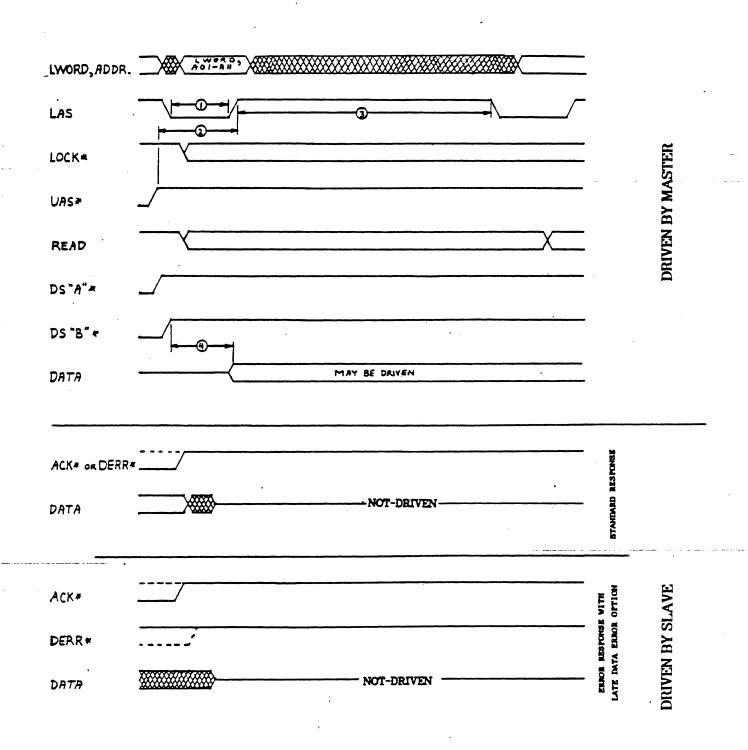

#### 3.1.2 Single Read Cycle

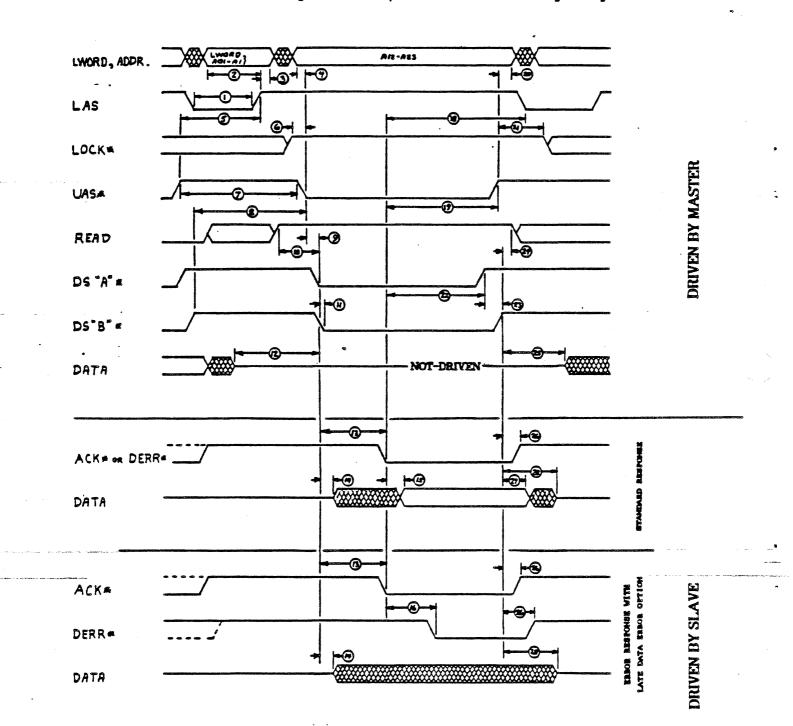

There are three kinds of single read cycles: byte read, word read, and longword read. Figure 3-2 shows the flow diagram for one of these: a single word read cycle, and should be referred to while reading the following cycle flow description.

The cycle begins when the MASTER drives LAS low. LAS is then held low until the MASTER drives the twelve address bus lines with address bits AO1 through A11 and the "longword" level appropriate for the word transfer (low). All these lines must be valid before LAS is driven to high.

The SLAVE latches the "lower address" and the longword bit on the rising edge of LAS. After a specified hold time, the MASTER removes the lower address and the longword but from the address bus and then places the "upper address" on it (A12-A23). When these new address bits have stabilized, the MASTER drives UAS\* to low. Each SLAVE, upon receiving the upper address, determines whether it is the one being addressed.

While the SLAVES are decoding the address the MASTER drives READ high to indicate that a read cycle is being done. Then the MASTER drives the two data strobes to low, commanding the SLAVE to retrieve data from the selected memory location and place it on the bus.

When the selected SLAVE detects the data strobes driven to low it responds in one of three different ways:

1) If it is a D16 SLAVE, and has been directed to do a 32 bit read, it responds by driving DERR\* low.

2) If it is able to handle the required read it drives ACK\* to low, retrieves the data from the selected location, and places it on the data bus.

3) If it drives ACK\* low, but then encounters some difficulty in retrieving data from memory (possibly because of a parity error) it drives DERR\* within a specified time limit to indicate that the data on the data bus is not valid.

NOTE

Some MASTERS require that ACK\* be driven low prior to the time that data has been placed on the bus to give maximum performance, while others must see valid data on the bus when ACK\* falls. To guarantee compatibility between all VMXbus boards, all SLAVES must be configurable so that they present valid data at the same

time they drive ACK\* low. Those SLAVES which can ALSO be configured to drive ACK\* low earlier provide a range of "data valid" to ACK\* delays of 0 to 125 nS. (The amount of delay may be selected either statically (e.g. by jumpers) or dynamically (e.g by control registers) to give optimum performance.

Some VMXbus MASTERS can handle late-aborted cycles while others cannot. To guarantee compatibility between VMXbus boards all SLAVES must be configurable to operate in the normal aborted cycle mode. Those SLAVE boards which can also be configured to provide late-aborted cycles typically provide a range of ACK\* to DERR\* delays from 0 to 125 nS. The amount of delay may be selected either statically (e.g. by jumpers) or dynamically (e.g. by control registers).

Figure 3-2 shows the most likely of these possibilities: the successful read. When the SLAVE responds by driving ACK\* to low, the MASTER captures the data, removes the upper address from the address bus, and drives UDS\*, LDS\*, and UAS\* high in preparation for the next cycle.

When the SLAVE detects the data strobes driven to high, it tri-states its data bus drivers, and releases ACK\* to high, allowing the data bus to be used for the next cycle.

|   | F     | Fi | gure | 3-2  |       |

|---|-------|----|------|------|-------|

| Α | Sinal | le | Word | Read | Cycle |

VMXbus MASTER VMXbus SLAVE SEND THE LOWER ADDRESS Drive LAS to low Present lower address and longword=low Drive LAS to high LATCH THE LOWER ADDRESS Receive LAS driven to high Latch lower address and longword bit. ! The MASTER is required to wait a ! specified time to ensure that the ! SLAVE has latched the lower address ! ! before removing it and the longword ! bit from the address bus. SEND THE UPPER ADDRESS Remove lower address and longword bit Present upper address Drive UAS\* to low ! SPECIFY READ CYCLE DECODE THE ADDRESS Drive READ high Receive UAS\* driven to low Decode address If address is not for this SLAVE REQUEST THE DATA THEN wait for another cycle ELSE select a memory location Drive both data strobes low 1 RETRIEVE THE DATA Receive data strobes driven to low Sample LAS (high)

| Sa        | mp | 1 | e  | RE | :AD | )  | (h | ig | h) | )   |    |     |

|-----------|----|---|----|----|-----|----|----|----|----|-----|----|-----|

| Re        | tr | i | ev | e  | th  | e  | đ  | at | a  | ٠f٣ | OM | the |

|           | se | 1 | ec | te | d   | 10 | c  | at | ic | าก  |    |     |

| <b>P1</b> | ac | e | d  | at | a   | or | ٦  | DO | 0- | -D1 | 5  |     |

|           |    |   |    |    | į   |    |    |    |    |     |    |     |

RESPOND TO THE MASTER

.

Drive ACK\* to low

TERMINATE CYCLE

8

Receive ACK\* driven to low Capture the data on DOO-D15 Remove upper address Drive data strobes to high Drive UAS\* to high

ACKNOWLEDGE TERMINATION

.

Receive data strobes driven to high Tri-state D00-D15 Release ACK\*

#### 3.1.3 Sequential Write Cycle

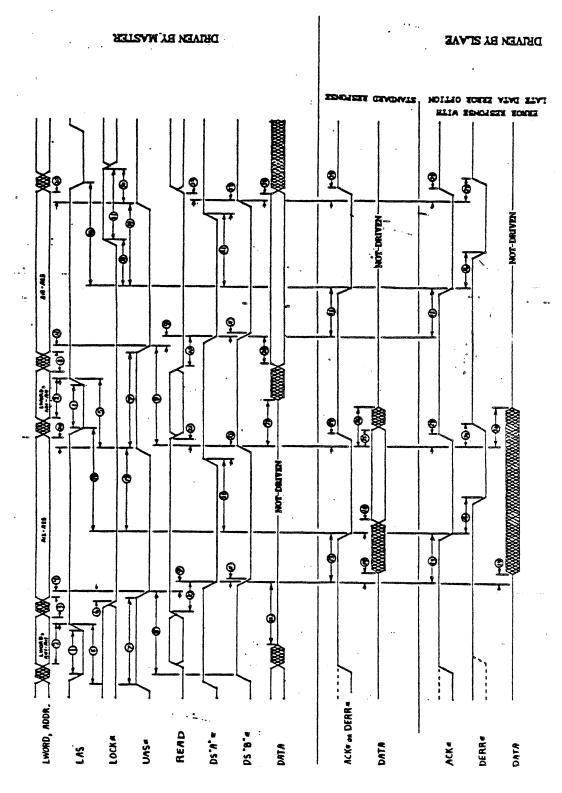

There are three kinds of sequential write cycles: byte write, word write, and longword write. Figure 3-3 shows the flow diagram for one of these: a sequential word write cycle, and should be referred to while reading the following cycle flow description.

The cycle begins when the MASTER drives LAS low. LAS is then held low until the MASTER drives the twelve address bus lines with address bits A01 through A11 and the "longword" level appropriate for the word transfer (low). All these lines must be valid before LAS is driven to high.

The SLAVE latches the "lower address" and the longword bit on the rising edge of LAS. After a specified hold time, the MASTER removes the lower address and longword bit from the address bus and then places the "upper address" on it (A12-A23). When these new address bits have stabilized, the MASTER drives UAS\* to low. Each SLAVE, upon receiving the upper address, determines whether it is the one being addressed.

while the SLAVES are decoding the address the MASTER drives READ low to indicate that a write cycle is being done. In order to indicate that this is a sequential write cycle it drives LAS low again. (LAS is then held low through all of the data transfers to the end of the sequential write cycle.) Then the MASTER places its 16 bits of data on the data bus lines DOO-D15 and drives the two data strobes low, commanding the SLAVE to write the data into memory.

When the selected SLAVE detects the data strobes driven to low it responds in one of three different ways:

1) If it is a D16 SLAVE, and has been directed to do a 32 bit write, or if it is a non-SEQ SLAVE and has been directed to do a sequential access, it responds by driving DERR\* low.

2) If it is able to handle the required write, it drives ACK\* low and stores the data into the selected memory location.

3) If it drives ACK\* low, but then encounters some difficulty in completing the write (for example, writing to a ROM) it drives DERR\* low within a specified time limit to indicate that the write was not successful.

#### NOTE

Some VMXbus MASTERS can handle late-aborted cycles while others cannot. To guarantee compatibility between VMXbus

boards all SLAVES should be configurable to operate in the normal aborted cycle mode. Those SLAVE boards which can also be configured to provide late-aborted cycles typically provide a range of ACK\* to DERR\* delays from 0 to 125 nS. The amount of delay may be selected either statically (e.g. by jumpers) or dynamically (e.g. by control registers.)

Figure 3-3 shows the most likely of these possibilities: the successful write. When the SLAVE responds by driving ACK\* to low, the MASTER removes the upper address from the address bus, and drives the data strobes high, but maintains LAS and UAS\* low. When the SLAVE detects the data strobes driven to high it releases ACK\*, allowing the data bus to be used for the next cycle. When the MASTER sees ACK\* high as well as DERR\* already high it initiates another write cycle. Since LAS has been held low the SLAVE has incremented the address from the last cycle and selected a new location.

This process repeats itself for each write until all of the data has been written. On the last transfer the MASTER responds to the low ACK\* by driving LAS, UDS\*, LDS\* and UAS\* to high in preparation for the next cycle.

|                                                                                                  | al Word Write Cycle                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VMXbus MASTER                                                                                    | VMXbus SLAVE                                                                                                                                                                     |

| SEND THE LOWER ADDRESS                                                                           |                                                                                                                                                                                  |

| Drive LAS to low<br>Present lower address<br>and longword=low<br>Drive LAS to high               |                                                                                                                                                                                  |

| !<br>!                                                                                           | LATCH THE LOWER ADDRESS                                                                                                                                                          |

|                                                                                                  | Receive LAS driven to high<br>Latch lower address<br>and longword bit.                                                                                                           |

| SEND THE UPPER ADDRESS                                                                           | The MASTER is required to wait a<br>specified time to ensure that the<br>SLAVE has latched the lower address<br>before removing it and the longword<br>bit from the address bus. |

| Remove lower address<br>and longword bit<br>Present upper address<br>Drive UAS* to low<br>!<br>! |                                                                                                                                                                                  |

| !<br>SPECIFY WRITE CYCLE                                                                         | DECODE THE ADDRESS                                                                                                                                                               |

| Drive READ low<br>!<br>!<br>SPECIFY SEQUENTIAL CYCLE                                             | Receive UAS* driven to low<br>Decode address<br>If address is not for this SLAVE<br>THEN wait for another cycle                                                                  |

| Drive LAS low<br>!<br>!<br>SEND THE DATA                                                         | ELSE select a memory location                                                                                                                                                    |

| Present data on DOO-D15<br>Drive both data strobes low<br>!                                      | •<br>•                                                                                                                                                                           |

STORE THE DATA Receive data strobes driven to low Sample LAS (low) Sample READ (low) Store the data in the selected location RESPOND TO THE MASTER Drive ACK\* to low 1 TERMINATE FIRST TRANSFER Receive ACK\* driven to low Drive data strobes to high Remove data from DOO-D15 (Maintain UAS\* and LAS low) 1 • • ACKNOWLEDGE TERMINATION Receive data strobes driven to high Release ACK\* INCREMENT THE LATCHED ADDRESS SPECIFY DATA DIRECTION Drive READ low IF LAS is still low THEN increment the latched address SEND THE DATA 1.1 8 Present data on DOO-D15 PROCESS THE ADDRESS IF address is not for this SLAVE Drive both data strobes low THEN wait for another cycle ELSE select a memory location ! STORE THE DATA Receive data strobes driven to low Sample LAS (low)

| ·                                                                                                                                    | Sample READ (low)<br>Store the data in the<br>selected location<br>! |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                                                                                                      | RESPOND TO THE MASTER                                                |

|                                                                                                                                      | Drive ACK* to low<br>!                                               |

| TERMINATE CYCLE                                                                                                                      | <sup>!</sup>                                                         |

| Receive ACK* driven to low<br>Remove data from DOO-D15<br>Drive data strobes to high<br>Drive LAS to high<br>Drive UAS* to high<br>! |                                                                      |

|                                                                                                                                      |                                                                      |

|                                                                                                                                      | ACKNOWLEDGE TERMINATION                                              |

|                                                                                                                                      | Receive data strobes<br>driven to high                               |

driven to high Release ACK\*

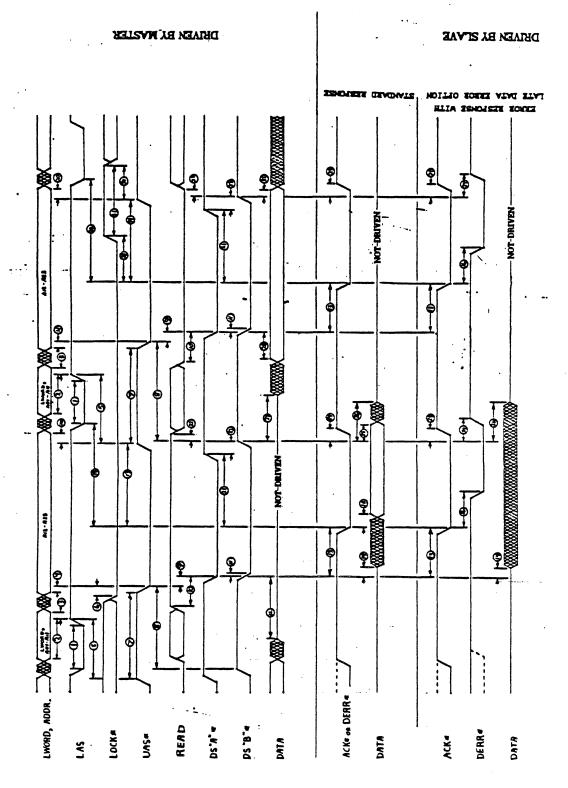

#### 3.1.4 Sequential Read Cycle

- .

e e comercio

There are three types of sequential read cycles: byte read, word read, and longword read. Figure 3-4 shows the flow diagram for one of these: a sequential word read cycle, and should be referred to while reading the following cycle flow description.

The cycle begins when the MASTER drives LAS low. LAS is then held low until the MASTER drives the twelve address bus lines with address bits AO1 through A11 and the "longword" level appropriate for the word transfer (low). All these lines must be valid before LAS is driven to high.

The SLAVE latches the "lower address" and longword bit on the rising edge of LAS. After a specified hold time, the MASTER removes the lower address and the longword bit from the address bus and then places the "upper address" on it. (A12-A23). When these new address bits have stabilized, the MASTER drives UAS\* to low. Each SLAVE, upon receiving the upper address, determines whether it is the one being addressed.

while the SLAVES are decoding the address, the MASTER drives READ high to indicate that a read cycle is being done. In order to indicate that this is a sequential read cycle it drives LAS low again. (LAS is held low through all of the data transfers to the end of the sequential read cycle.) Then the MASTER drives the two data strobes to low, commanding the SLAVE to retrieve data from the selected memory location and place it on the bus.

When the selected SLAVE detects the data strobes driven to low it responds in one of three different ways:

1) If it is a D16 SLAVE, and has been directed to do a 32 bit read, it responds by driving DERR\* low.

2) If it is able to handle the required read, it drives ACK\* to low, retrieves the data from the selected location, and places it on the data bus.

3) If it drives ACK\* low, but then is unable to retrieve data from the memory, (possibly because of a parity error) it drives DERR\* within a specified time limit to indicate that the data is not valid.

#### NOTE

Some MASTERS require that ACK\* be driven low prior to the time that data has been placed on the bus to give maximum performance, while others must see valid data on the bus when ACK\* falls. To guarantee compatibility between all VMXbus boards all SLAVES must be configurable so that they present valid data at the same time they drive ACK\* low. Those SLAVES which can also be configured to drive ACK\* low provide a range of "data valid" to ACK\* delays of 0 to 125 nS. (The amount of delay may be selected either statically (e.g. by jumpers) or dynamically (e.g by control registers) to give optimum performance.

Some VMXbus MASTERS can handle late-aborted cycles while others cannot. To guarantee compatibility between VMXbus boards all SLAVES should be configurable to operate in the normal aborted cycle mode. Those SLAVE boards which can also be configured to provide late-aborted cycles typically provide a range of ACK\* to DERR\* delays from 0 to 125 nS. The amount of delay may be selected either statically (e.g. by jumpers) or dynamically (e.g. by control registers.)

Figure 3-4 shows the most likely of these possiblities: the successful read. When the SLAVE responds by driving ACK\* low, the MASTER captures the data. Then it maintains LAS and UAS\* low, but drives the data strobes to high When the SLAVE detects the data strobes driven to high it tri-states its data bus drivers and releases ACK\* to high. When the MASTER sees ACK\* high as well as DERR\* already high it drives the data strobes low for another read.

This process repeats itself for each read until all of the data has been read. On the last transfer the MASTER responds to the low ACK\* by driving LAS, UDS\*, LDS\*, and UAS\* to high in preparation for the next cycle.

| Figure 3-4<br>A Sequential Word Read Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| VMXbus MASTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VMXbus SLAVE                                                                                                                                                                     |  |  |  |

| SEND THE LOWER ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |  |  |  |

| Drive LAS to low<br>Present lower address<br>and longword=low<br>Drive LAS to high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  |  |  |  |

| * can be and a set of an and an and a set of an an and a set of an an and a set of an an and a set of a set | LATCH THE LOWER ADDRESS                                                                                                                                                          |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Receive LAS driven to high<br>Latch lower address<br>and longword bit.                                                                                                           |  |  |  |

| SEND THE UPPER ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | The MASTER is required to wait a<br>specified time to ensure that the<br>SLAVE has latched the lower address<br>before removing it and the longword<br>bit from the address bus. |  |  |  |

| Remove lower address<br>and longword bit<br>Present upper address<br>Drive UAS* to low<br>!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |  |  |  |

| SPECIFY READ CYCLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DECODE THE ADDRESS                                                                                                                                                               |  |  |  |

| Drive READ high<br>!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Receive UAS* driven to low<br>Decode address                                                                                                                                     |  |  |  |