## MVME6000UM/D1

# MVME6000 VMEbus Interface User's Manual

MVME6000UM/D1

July 1989

# MVME6000 VMEbus INTERFACE USER'S MANUAL

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any product herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

First Edition

Copyright 1989 by Motorola Inc.

### TABLE OF CONTENTS

### CHAPTER 1 INTRODUCTION

| 1.1 | GENERAL                   | 1- | 1 |

|-----|---------------------------|----|---|

| 1.2 | SUMMARY OF MAJOR FEATURES | 1- | 1 |

| 1.3 | TERMINOLOGY               | 1- | 2 |

| 1.4 | RELATED DOCUMENTS         | 1- | 3 |

### **CHAPTER 2 FUNCTIONAL BLOCKS**

| 2.1 | GENERAL INFORMATION           | 2-1 |

|-----|-------------------------------|-----|

| 2.2 | MASTER                        | 2-1 |

| 2.3 | SLAVE                         | 2-3 |

| 2.4 | REQUESTER                     | 2-3 |

| 2.5 | INTERRUPTER                   | 2-4 |

| 2.6 | INTERRUPT HANDLER             | 2-4 |

| 2.7 | SYSTEM CONTROLLER             | 2-5 |

|     | 2.7.1 Arbiter                 | 2-5 |

|     | 2.7.2 IACK Daisy-Chain Driver | 2-5 |

|     | 2.7.3 SYSCLK Driver           | 2-5 |

|     | 2.7.4 Bus Timer               | 2-6 |

|     | 2.7.5 Reset Driver            | 2-6 |

|     |                               |     |

### **CHAPTER 3 SIGNAL LINE DESCRIPTION**

| 3.1 | GENERAL                                           | 3-1 |

|-----|---------------------------------------------------|-----|

| 3.2 | VMEbus SIGNALS                                    | 3-2 |

| 3.3 | LOCAL INTERFACE SIGNALS                           | 3-2 |

|     | 3.3.1 32FILL* - 4-Byte Cache Fill                 | 3-2 |

|     | 3.3.2 ADR24* - Standard Address Space             | 3-2 |

|     | 3.3.3 BRDFAIL* - Board Failed                     | 3-2 |

|     | 3.3.4 BRDRESET* - Board Reset                     | 3-3 |

|     | 3.3.5 CLK - Clock                                 | 3-3 |

|     | 3.3.6 CS* - Chip Select                           | 3-3 |

|     | 3.3.7 DAT16* - Data 16-Bit                        | 3-3 |

|     | 3.3.8 DHB* - Device Has Bus                       | 3-3 |

|     | 3.3.9 DWB* - Device Wants Bus                     | 3-3 |

|     | 3.3.10 HALT* - Halt                               | 3-4 |

|     | 3.3.11 IPL0*-IPL2* - Interrupt Priority Level 0-2 | 3-4 |

|     | 3.3.12 LOCK* - Lock                               | 3-4 |

|     | 3.3.13 MATCH16* - Match A16 Access                | 3-5 |

|     | 3.3.14 MATCH24* - Match A24 Access                | 3-5 |

|     | 3.3.15 MATCH32* - Match A32 Access                | 3-5 |

|     | 3.3.16 MATCHGCSR* - Match GCSR Access             | 3-5 |

|     | 3.3.17 PA00-PA01 - Processor Address Lines 0-1    | 3-6 |

|     | 3.3.18 PA01-PA03 - Processor Address Lines 1-3    | 3-6 |

|     | 3.3.19 PA02-PA07 - Processor Address Lines 2-7                                        |      |

|-----|---------------------------------------------------------------------------------------|------|

|     | 3.3.20 PAS* - Processor Address Strobe                                                | 3-7  |

|     | 3.3.21 PBERR* - Processor Bus Error                                                   | 3-7  |

|     | 3.3.22 PBG* - Processor Bus Grant                                                     | 3-8  |

|     | 3.3.23 PBR* - Processor Bus Request                                                   | 3-8  |

|     | 3.3.24 PD00-PD07 - Local Data Lines 0-7                                               | 3-9  |

|     | 3.3.25 PDS* - Processor Data Strobe                                                   | 3-9  |

|     | 3.3.26 PDSACK0*-PDSACK1* - Data Size Acknowledge 0-1                                  | 3-10 |

|     | 3.3.27 PFC0-FC2 - Processor Function Code 0-2                                         | 3-11 |

|     | 3.3.28 PIACK* - Processor Interrupt Acknowledge                                       | 3-11 |

|     | 3.3.29 PRESET* - Processor Reset                                                      | 3-11 |

|     | 3.3.30 PSIZ0, PSIZ1 - Processor Size Request 0-1                                      | 3-12 |

|     | 3.3.31 PWRITE* - Processor Write                                                      |      |

|     | 3.3.32 RETRY* - Retry                                                                 | 3-13 |

|     | 3.3.33 RMC* - Read-Modify-Write Cycle                                                 | 3-13 |

|     | 3.3.34 SCLK - Synchronization Clock                                                   | 3-14 |

|     | 3.3.35 SCON* - System Controller On                                                   | 3-14 |

|     | 3.3.36 SHORTIO* - Short I/O Cycle                                                     | 3-14 |

|     | 3.3.36 SHORTIO <sup>*</sup> - Short I/O Cycle<br>3.3.37 VMESEL* - Select VMEbus Cycle | 3-14 |

| 3.4 | BUFFER CONTROL SIGNALS                                                                | 3-15 |

|     | 3.4.1 ABIN* - Address Bus In                                                          | 3-15 |

|     | 3.4.2 ABOUT* - Address Bus Out                                                        | 3-15 |

|     | 3.4.3 LATCHIN - Latch In                                                              | 3-15 |

|     | 3.4.4 LATCHOUT - Latch Out                                                            | 3-18 |

|     | 3.4.5 DBOUT - Data Bus Out                                                            |      |

|     | 3.4.6 LDBIN* - Lower Data Bus In                                                      | 3-18 |

|     | 3.4.7 UDBIN* - Upper Data Bus In                                                      | 3-19 |

|     | 3.4.8 DBDIR - Data Bus Direction                                                      | 3-19 |

|     | 3.4.9 ISOEN* - Isolation Enable*                                                      | 3-19 |

|     | 3.4.10 SWPEN* - Swap Enable                                                           |      |

### CHAPTER 4 LOCAL CONTROL AND STATUS REGISTER SET

| 4.1  | GENERAL                                  | 4-1  |

|------|------------------------------------------|------|

| 4.2  | LCSR                                     | 4-1  |

| 4.3  | SYSTEM CONTROLLER CONFIGURATION REGISTER | 4-3  |

| 4.4  | VMEbus REQUESTER                         | 4-4  |

| 4.5  | MASTER CONFIGURATION REGISTER            | 4-5  |

| 4.6  | SLAVE CONFIGURATION REGISTER             | 4-9  |

| 4.7  | TIMER CONFIGURATION REGISTER             | 4-10 |

| 4.8  | SLAVE ADDRESS MODIFIER REGISTER          | 4-12 |

| 4.9  | MASTER ADDRESS MODIFIER REGISTER         | 4-13 |

| 4.10 | INTERRUPT HANDLER MASK REGISTER          | 4-13 |

| 4.11 | UTILITY INTERRUPT MASK REGISTER          | 4-14 |

| 4.12 | UTILITY INTERRUPT VECTOR REGISTER        | 4-15 |

| 4.13 | INTERRUPT REQUEST REGISTER               | 4-16 |

| 4.14 | VMEbus STATUS/ID REGISTER                | 4-17 |

| 4.15 | BUS ERROR STATUS REGISTER                | 4-17 |

| 4.16 | GCSR BASE ADDRESS CONFIGURATION REGISTER | 4-18 |

### CHAPTER 5 GLOBAL CONTROL AND STATUS REGISTER SET

| 5.1  | GENERAL                       | 5-1 |

|------|-------------------------------|-----|

| 5.2  | ADDRESSING THE GCSR           | 5-1 |

| 5.3  | GLOBAL REGISTER 0             | 5-3 |

| 5.4  | GLOBAL REGISTER 1             | 5-4 |

| 5.5  | BOARD IDENTIFICATION REGISTER | 5-6 |

| 5.6  | GENERAL PURPOSE CSR 0         | 5-6 |

| 5.7  | GENERAL PURPOSE CSR 1         | 5-7 |

| 5.8  | GENERAL PURPOSE CSR 2         | 5-7 |

| 5.9  | GENERAL PURPOSE CSR 3         | 5-7 |

| 5.10 | GENERAL PURPOSE CSR 4         | 5-7 |

| APPENDIX A | ELECTRICAL CHARACTERISTICS | A-1 |

|------------|----------------------------|-----|

|            |                            |     |

| APPENDIX B | <b>PINOUT OF THE MVME6000</b> | B-1 |

|------------|-------------------------------|-----|

|            |                               | D-1 |

## LIST OF FIGURES

| Figure |                                                     | Page |

|--------|-----------------------------------------------------|------|

| 2-1    | Block Diagram of the MVME6000                       | 2-2  |

| 3-1    | Signals of the MVME6000                             | 3-1  |

| 3-2    | Connecting PDS*, VMESEL*, and PIACK* to the VMEchip | 3-10 |

| 3-3    | Connecting BRDRESET* and PRESET* to On-Board Logic  | 3-12 |

| 3-4    | Connecting the MVME6000 to External Address Buffers | 3-16 |

| 3-5    | Connecting the MVME6000 to External Data Buffers    | 3-17 |

| 4-1    | MVME6000 LCSR                                       | 4-2  |

| 5-1    | The Organization of the GCSR                        | 5-2  |

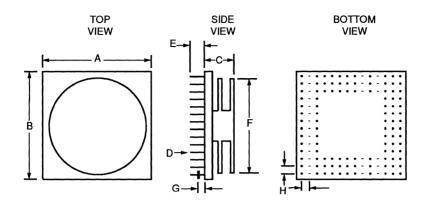

| B-1    | Pin Assignments of the MVME6000                     | B-3  |

| B-2    | MVME6000 Package Dimensions                         | B-4  |

## LIST OF TABLES

Table

Page

| 3-1  | Encoding of IPL0*-IPL2*                           |      |

|------|---------------------------------------------------|------|

| 3-2  | Using PĂ01-PA03 to Determine the Interrupt Level  |      |

| 3-3  | Signaling During VMEbus Read Cycles               |      |

| 3-4  | Signaling During VMEbus Write Cycles              | 3-22 |

| 3-5  | Signaling When Responding to a VMEbus Read Cycle  |      |

| 3-6  | Signaling When Responding to a VMEbus Write Cycle |      |

| 4-1  | The Local Control and Status Register Set         | 4-1  |

| 4-2  | System Controller Configuration Register          | 4-3  |

| 4-3  | Requester Configuration Register                  | 4-4  |

| 4-4  | Selecting The Bus Request Level                   | 4-4  |

| 4-5  | Master Configuration Register                     | 4-5  |

| 4-6  | Determining the Master's AM Code                  | 4-7  |

| 4-7  | Slave Configuration Register                      |      |

| 4-8  | Timer Configuration Register                      | 4-10 |

| 4-9  | Programming the Local Bus Timer                   | 4-10 |

| 4-10 | Programming the VMEbus Access Timer               |      |

| 4-11 | Programming the VMEbus Timer                      | 4-11 |

| 4-12 | Slave Address Modifier Register                   | 4-12 |

| 4-13 | Master Address Modifier Register                  | 4-13 |

| 4-14 | Interrupt Handler Mask Register                   | 4-13 |

| 4-15 | Utility Interrupt Mask Register                   | 4-14 |

| 4-16 | Utility Interrupts and their Assigned Level       |      |

| 4-17 | Utility Interrupt Vector Register                 | 4-15 |

| 4-18 | Encoding of the Utility Interrupt ID              | 4-15 |

| 4-19 | Interrupt Request Register                        | 4-16 |

| 4-20 | Configuring the Interrupt Request Level           |      |

| 4-21 | VMEbus Status/ID Register                         | 4-17 |

| 4-22 | Bus Error Status Register                         | 4-17 |

| 4-23 | GCSR Base Address Configuration Register          | 4-18 |

| 4-24 | MVME6000 GCSA As Viewed From the VMEbus           | 4-18 |

| 5-1  | The Registers of the GCSR                         | 5-2  |

| 5-2  | Global Register 0                                 | 5-3  |

| 5-3  | Location Monitors and their Assigned Addresses    | 5-4  |

| 5-4  | Global Register 1                                 | 5-5  |

|      |                                                   |      |

| A-1  | Maximum Ratings                                             | A-1   |

|------|-------------------------------------------------------------|-------|

| A-2  | Operating Range                                             | A-1   |

| A-3  | DC Electrical Charateristics                                | A-1   |

| A-4  | VMEbus Master: Times Common to Read, Write, and IACK Cycles | A-2   |

| A-5  |                                                             | A-3   |

| A-6  | VMEbus Master: Times Specific to Write Cycles               | A-4   |

| A-7  | VMEbus Master: Releasing VMEbus Mastership                  | _A-5  |

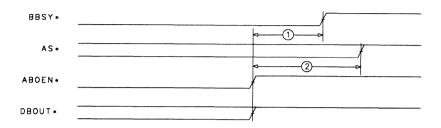

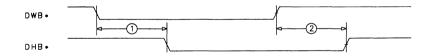

| A-8  | VMEbus Master: DWB*/DHB* Timing                             | _A-5  |

| A-9  | VMEbus Master: Local Bus Retries                            | _A-6  |

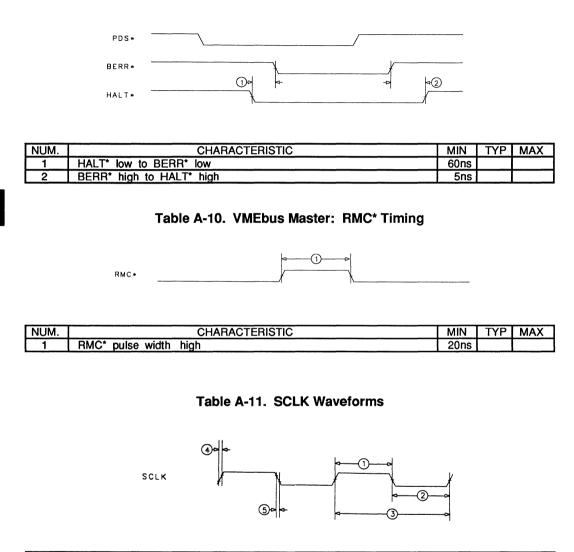

| A-10 | VMEbus Master: RMC* Timing                                  | _A-6  |

| A-11 | SCLK Waveforms                                              | _A-6  |

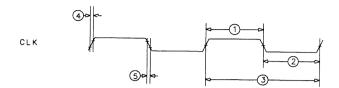

| A-12 | CLK Waveforms                                               | _A-7  |

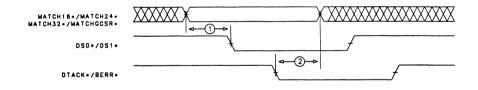

| A-13 | VMEbus Slave: MATCH16*, MATCH24*, MATCH32*,                 |       |

|      | MATCHGCSR* Timing                                           | _A-7  |

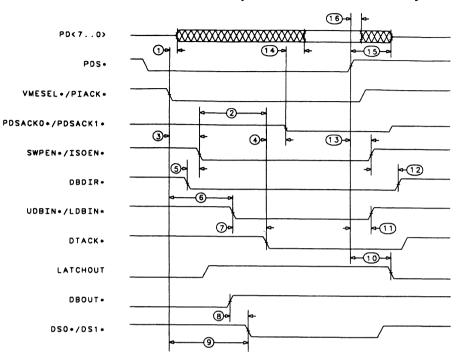

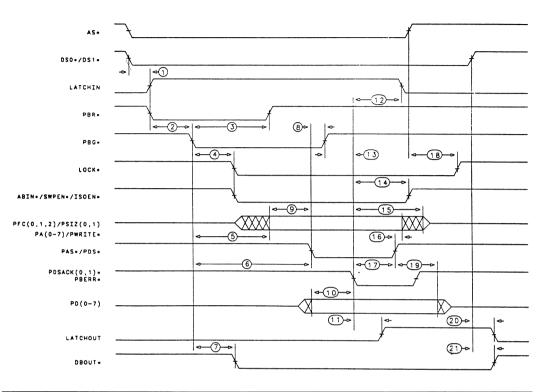

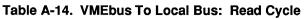

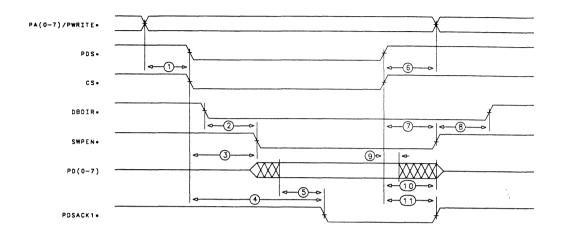

| A-14 | VMEbus to Local Bus: Read Cycle                             | _A-8  |

| A-15 | VMEbus to Local Bus: Write Cycle                            | _A-9  |

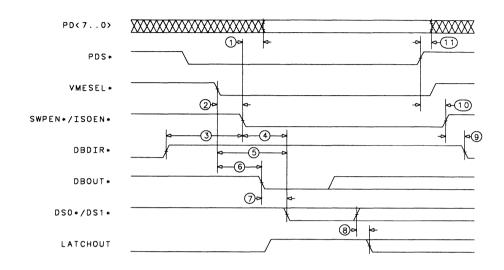

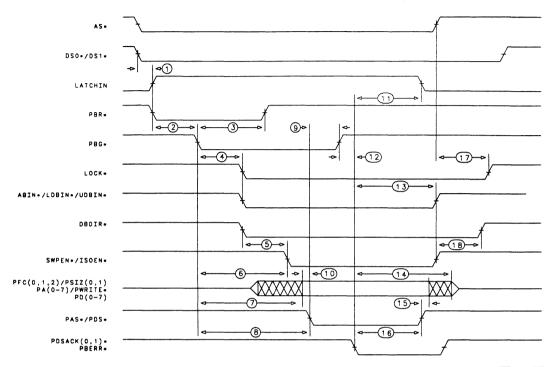

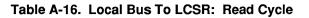

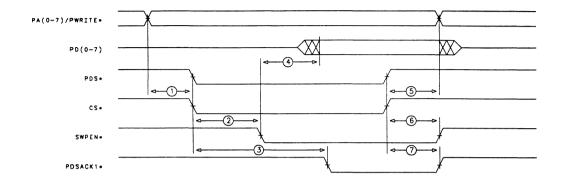

| A-16 | Local Bus to LCSR: Read Cycle                               | _A-10 |

| A-17 | Local Bus to LCSR: Write Cycle                              | _A-11 |

| A-18 | Buffer timing Requirements                                  | _A-12 |

| B-1  | Summary of VMEbus Signal Lines                              | _B-1  |

| B-2  | Summary of Local Signal Lines                               | _B-2  |

|      |                                                             |       |

vi

## CHAPTER 1

## INTRODUCTION

#### 1.1 GENERAL

The MVME6000 is the interface between MC68020 and MC68030 microprocessors and the VMEbus. With external buffers, decoders and oscillators, it provides all of the functions that a CPU board requires to connect to the VMEbus, allowing a significant savings in board space. Using all of the chip's modules, a board can operate as the VMEbus system controller and provide a full master/slave interface. In addition to the VMEbus defined function, the chip includes functions to support some multiprocessor architectures.

### 1.2 SUMMARY OF MAJOR FEATURES

#### • VMEbus Master interface:

- MC68020/MC68030 local CPU interface

- 16-bit or 32-bit local data width

- 16-bit or 32-bit VMEbus data width

- 16-bit, 24-bit, or 32-bit VMEbus address width

- Software programmed AM code

- Software configured VMEbus access watch-dog timer

- Software enabled 4-byte cache fill mode

- Software enabled write-posting mode

#### • VMEbus Slave interface:

- MC68020/MC68030 local CPU interface

- 16-bit or 32-bit local data width

- 16-bit or 32-bit VMEbus data width

- 16-bit, 24-bit or 32-bit VMEbus address width

- Software programmed AM code

- Software enabled write-posting mode

#### • VMEbus Requester:

- Software configured RWD/ROR/RNEVER release modes

- Software configured FAIR/RODWB/ROSELECT request modes

- Software configured BR0\* BR3\* request level

#### • VMEbus Interrupter:

- Software configured IRQ1\* IRQ7\* interrupt request level

- 8-bit Software programmed status/ID register

#### VMEbus interrupt handler:

- Can handle all 7 VMEbus interrupts

- Software programmed individual masks

- MC68020/MC68030 local bus interface

1-1

### • VMEbus System Controller:

- Software configured PRI/RRS/SGL Arbiter

- Software configured Arbitration Timer

- IACK Daisy-Chain Driver

- SYSCLK Driver

- Software configured Bus Timer

- SYSRESET\* Driver

#### Global Register Set:

- Four location monitors

- Global control of locally detected failures

- Global control of local reset

- Two global attention interrupt bits

- An 8-bit Board ID register

- Five 8-bit dual-ported general purpose communication registers

- A 4-bit chip ID number

#### • Utility Interrupt Handler:

- Individually masked interrupts: After completing a VMEbus IACK cycle When SYSFAIL\* is asserted When BERR\* is received during a Master write-posted cycle When Location Monitor 0 or 1 detect a VMEbus cycle When either of the two attention control bits is set

- Unique interrupt vectors for all the above

- MC68020/MC68030 local bus interface

- · A software configured local bus timer

- With the exception of ACFAIL\*, A08-A31 and D08-D31, directly connects to all VMEbus signal lines.

#### 1.3 TERMINOLOGY

The terms *asserted* and *negated* are used extensively in this document to avoid confusion when dealing with a mixture of active-low and active-high signals. The term asserted is used to indicate that a signal is in its active, or true state, regardless of its voltage level. The term negated is used to indicate that a signal is in its inactive, or false, state.

To help define their use, some signal names have an asterisk (\*) suffix. When an asterisk follows the name of a level significant signal it denotes that the signal is valid when it is at a low voltage level. When an asterisk follows the name of a signal that is edge significant it means that the actions initiated by that signal occur when it makes a transition from a high to a low level voltage.

The terms *control bit* and *status bit* are used extensively in this document. *Control bit* is used to describe a bit in a register which can be set and cleared under software control, affecting the operation of the MVME6000. *Status bit* is used to describe a bit in a register which can be read by software to determine operational or exception conditions. The term *true* is used to indicate that a bit is in the state that enables the function it controls. The term *false* is used to indicate that the bit is in the state that disables the function it controls. In all tables, the terms 0 and 1 are used to describe the actual value that should be written to the bit, or the value that it will yield when read.

All numbers given in this document are either decimal or hexadecimal. Hexadecimal numbers are are prefixed by '\$'. For example, '12' is the decimal number twelve, and '\$12' is the decimal number eighteen.

#### **1.4 RELATED DOCUMENTS**

The following publications are applicable to the MVME6000 and may provide additional helpful information. If not shipped with this product, they may be purchased from the Motorola Literature Distribution Center, 616 West 24th Street, Tempe, Arizona 85282; telephone (602) 994-6561.

| <u>MOTOROLA</u><br>PART NUMBER |

|--------------------------------|

| MC68020UM/AD                   |

| MC68030UM/AD                   |

|                                |

The following publication is available from the source indicated:

Versatile Backplane Bus: VMEbus, part number IEEE 1014-87: The Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, NY 10017

## FUNCTIONAL BLOCKS

### CHAPTER 2

### FUNCTIONAL BLOCKS

#### 2.1 GENERAL INFORMATION

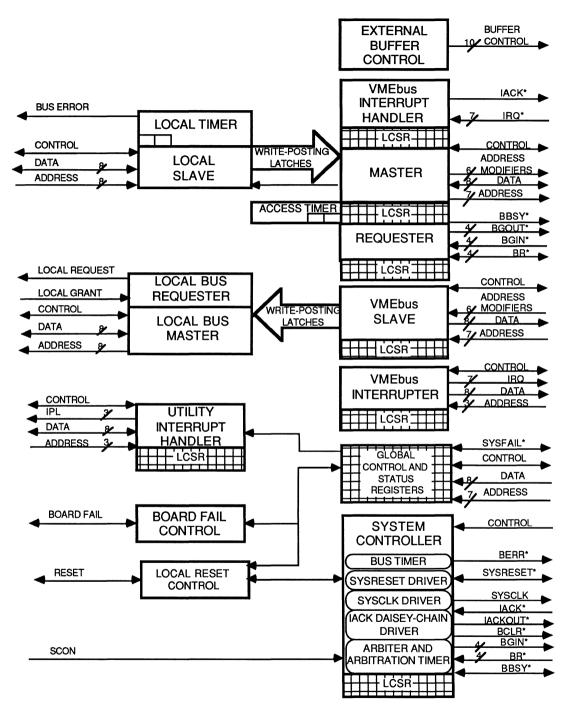

The MVME6000 is composed of nine functional blocks. These are master, slave, requester, arbiter, interrupter, interrupt handler, global and local timers, the local control and status register set, and the global control and status register set. Figure 2-1 shows the block diagram of the chip.

#### 2.2 MASTER

The master provides the signals necessary to interface a microprocessor to the VMEbus. With the exception of ACFAIL\*, data lines D08-D31, and address lines A08-A31, the chip directly connects to all signals that a VMEbus master can drive and monitor. On the local side, the master is designed to easily interface to a 68020 or a 68030 microprocessor. The chip also provides signals to control the external address and data buffers/latches and to automatically enable data swapping buffers when required.

Using input signal lines and register bits, the chip can be configured to interface to either a 16-bit or a 32-bit local data bus. On the VME side, the chip can be configured to provide the following capabilities:

Addressing capabilities: A16, A24, A32 Data transfer capabilities: D08, D16, D32, UAT

The master partially supports the dynamic bus sizing protocols of the 68020/68030 microprocessor. When the microprocessor initiates a quad-byte write cycle to a VMEbus slave that only has the D16 capability, the chip executes a double-byte write cycle on the VMEbus. It will then acknowledge the microprocessor as required for a double-byte slave. The microprocessor can then execute additional cycles as required.

Using the Address-Modifier-Out control register (refer to Chapter 3), the address modifier (AM) code that the master places on the VMEbus can be programmed under software control. Alternately, the AM code reflects the state of the three function code lines driven by the 68020 or 68030 microprocessor.

Included is a software controlled access watch-dog timer. It starts when the chip is requested to do a data transfer or an interrupt acknowledge cycle. The timer stops once the chip has started the data transfer of the relevant VMEbus cycle or if the cycle has been write-posted and the chip has acknowledged the processor. If neither of these conditions happen, the timer will time-out, driving the processor's bus error signal, and setting the appropriate status bit in the Local Control and Status Register (LCSR). Using control bits, the timer can be disabled or it can be enabled to drive the processor's bus error signal after 64 usecs, 1 msec, or 32 msecs.

## FUNCTIONAL BLOCKS

Figure 2-1. Block Diagram of the MVME6000

In addition, software can configure the master to operate in the following modes:

- (a) Write Posting i.e., control the latching of outgoing data and addressing information, provide an early acknowledge to the local microprocessor, and complete the VMEbus write cycle on its own.

- (b) Cache Fill i.e., execute a 4-byte VMEbus read cycle regardless of the amount of data that the local microprocessor requests during a read cycle that accesses a D32 VMEbus Slave.

#### 2.3 SLAVE

The slave provides all the signals necessary to allow a VMEbus Master access to onboard resources. With the exception of data lines D08-D31 and address lines A08-A31 the MVME6000 directly connects to all signals that a VMEbus slave can drive and monitor.

Adhering to the IEEE 1014-87 VMEbus Specification, the slave module can withstand address only cycles, as well as address pipelining. Using input signal lines and control register bits, it can be configured to provide the following VMEbus capabilities:

Addressing capabilities: A16, A24, A32 Data transfer capabilities: D08, D16, D32, UAT

Using the Address-Modifier-In control register (refer to Chapter 3), the slave can be configured under software control to respond to any of the defined AM codes. In addition, the slave can be configured under software control to perform Write-Posting operations. When in this mode the chip will control the latching of incoming data and addressing information, request control of the local bus and provide an early DTACK\* during a VMEbus write cycle that accesses an on-board resource. The chip will then complete the local access after it has been granted the local bus.

#### 2.4 REQUESTER

The requester provides all the signals necessary to allow the local processor to request and be granted use of the VMEbus. The MVME6000 directly connects to all signals that a VMEbus requester can drive and monitor.

Requiring no external jumpers, the MVME6000 provides the means for software to program the MVME6000 to request the bus on any one of the four bus request levels, automatically establishing the bus grant daisy-chains for the three inactive levels.

The requester will request the bus if any of the following conditions occur:

- (a) The local CPU initiates either a data transfer cycle or an interrupt acknowledge cycle to the VMEbus.

- (b) The MVME6000 is requested to acquire control of the VMEbus as defined by either an input signal, or a control bit.

## FUNCTIONAL BLOCKS

Software controls when the requester releases the bus as follows:

- (a) Release When Done (RWD) i.e., after acquiring control of the bus, release it immediately after completing the bus cycle.

- (b) Release-On-Request (ROR) i.e., after acquiring control of the bus, maintain control and monitor all the bus request levels. The requester will then relinquish control of the bus only if a bus request is pending on any of the request lines.

- (c) Release Never (RNEVER) i.e., after acquiring control of the bus, maintain control until the RNEVER bit is cleared.

To minimize the timing overhead of the arbitration process, the requester in the MVME6000 releases the bus early. If it is about to release the bus and it is executing a VMEbus cycle, the requester releases BBSY\* before its associated master completes the cycle. This allows the arbitrent to arbitrate any pending requests, and grant the bus to the next requester, at the same time that the active master completes its cycle.

#### 2.5 INTERRUPTER

The interrupter provides all the signals necessary to allow on-board logic to request interrupt service from a VMEbus Interrupt Handler. The MVME6000 directly connects to all signals that a VMEbus interrupter can drive and monitor.

The MVME6000 requires no external jumpers and permits the software to program the MVME6000 to request an interrupt on any of the seven interrupt request lines. The chip also controls the propagation of the acknowledge on the IACK daisy-chain.

The Interrupter in the MVME6000 operates in the Release-On-Acknowledge (ROAK) mode. An 8-bit control register provides software with the means to provide a dynamically programmed status/ID information. Upon reset, this register is initialized to a status/ID of \$0F (the uninitialized vector in the 68K based environment).

#### 2.6 INTERRUPT HANDLER

The interrupt handler provides all the signals necessary to allow on-board logic to identify and handle VMEbus as well as internally generated utility interrupt requests. The MVME6000 directly connects to all signals that a VMEbus handler can drive and monitor. On the local bus, the interrupt handler is designed to comply with the interrupt handling signaling protocol of the 68K family of microprocessors.

Requiring no external jumpers, the MVME6000 provides the means for software to program the interrupt handler to handle any combination of the seven VMEbus request lines. In addition, the chip provides individual interrupt mask bits which allow software to mask any of the VMEbus or the internally generated utility interrupts.

The MVME6000 can be programmed to request an interrupt from the local processor when any of the following conditions occur:

- a. A VMEbus interrupt request line is asserted.

- b. The MVME6000 has completed a VMEbus interrupt-acknowledge cycle.

- c. The SYSFAIL\* line is asserted.

- d. BERR\* is asserted during a VMEbus write-posted operation.

- e. A VMEbus access was detected to the short I/O address that location monitor 0 or 1 were assigned to monitor.

- f. Another VMEbus master set one of the two global signaling bits in the global register set.

A unique vector is provided by the MVME6000 for all the utility interrupts (cases b through f above). This vector is comprised of a 3-bit pre-assigned source identification code and a 5-bit software programmable base.

#### 2.7 SYSTEM CONTROLLER

With the exception of the optional SERCLK Driver and the Power Monitor, the MVME6000 includes all the functions that a VMEbus System Controller can provide. The System Controller is enabled/disabled with the aid of an external jumper. Figure 2-1 includes a block diagram of the modules that form the system controller (the dotted lines denote signals which are internal to the MVME6000). All of the System Controller's VMEbus signals can be directly connected to the VMEbus.

#### 2.7.1 Arbiter

The arbitration algorithm used by the MVME6000's arbiter is selected by software. All three arbitration modes defined in the VMEbus Specification are supported: Priority (PRI), Round-Robin-Select (RRS), as well as Single (SGL). When operating in the PRI mode, the arbiter asserts the BCLR\* line whenever it detects a request for the bus whose level is higher than the one being serviced.

The MVME6000 includes an arbitration timer, preventing a bus lock-up when no requester assumes control of the bus after the arbiter has issued a grant. Using a control bit, this timer can be enable or disabled. When enabled, it assumes control of the bus by driving the BBSY\* signal after 256 usecs, releasing it after satisfying the requirements of the VMEbus specification, and then re-arbitrating any pending bus requests.

#### 2.7.2 IACK Daisy-Chain Driver

Complying with the latest revision of the VMEbus Specification, the System Controller in the MVME6000 includes an IACK Daisy-Chain Driver, ensuring that the timing requirements of the IACK daisy-chain are satisfied.

#### 2.7.3 SYSCLK Driver

The MVME6000 includes a SYSCLK Driver that provides the required 16MHz system clock signal, and that can be directly connected to the VMEbus SYSCLK signal line. The chip generates the system clock signal using an external 16MHz oscillator.

## FUNCTIONAL BLOCKS

#### 2.7.4 Bus Timer

The Bus Timer in the MVME6000 is enabled/disabled by software to terminate a VMEbus cycle by asserting BERR\* if any of the VMEbus data strobes is maintained in its asserted state for longer than the programmed time-out period, which can be set to 64, 128, or 256 usecs.

In addition to the VMEbus timer, the MVME6000 contains a local bus timer. This timer asserts the local PBERR\* when the local data strobe is maintained in its asserted state for longer than the programmed time-out period. This timer too can be enabled or disabled under software control. The time out period can be programmed for 64, 128, or 256 usecs.

#### 2.7.5 Reset Driver

The MVME6000 includes both a global and a local reset driver. When the MVME6000 operates as the VMEbus System Controller, the reset driver provides a global system reset by asserting the VMEbus signal SYSRESET\*. This is controlled by either an input signal, or with the aid of a control bit, allowing both hardware and software to initiate a global reset sequence. SYSRESET\* will remain asserted for at least 200 mseconds, as required by the VMEbus Specification.

Similarly, the MVME6000 provides an input signal and a control bit to initiate a local reset operation. By setting a control bit, executive software can maintain a board in a reset state, disabling a faulty board from participating in normal system operation. The local reset driver is enabled even when the MVME6000 is not the System Controller.

#### **CHAPTER 3**

#### SIGNAL LINE DESCRIPTION

#### 3.1 GENERAL

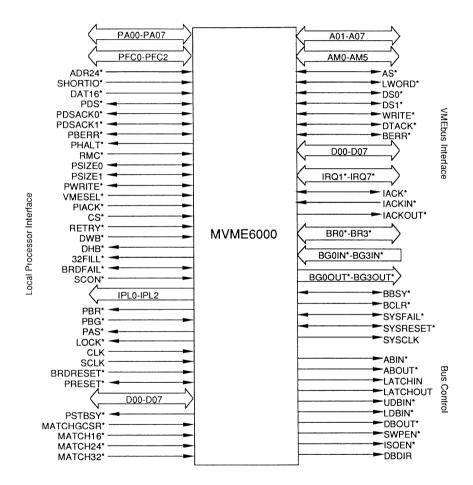

In addition to the power and ground pins, the MVME6000 provides 120 active signals as shown in Figure 3-1. They are divided into three groups: VMEbus signals, buffer control signals, and onboard signals.

Figure 3-1. Signals of the MVME6000

#### 3.2 VMEbus SIGNALS

With the exclusion of A08-A31, D08-D31 and ACFAIL\*, the MVME6000 directly drives and monitors all VMEbus signals. A detailed description of the VMEbus signal lines can be found in the VMEbus Specification, and is not repeated here.

#### 3.3 LOCAL INTERFACE SIGNALS

This chapter describes the signals that the MVME6000 uses to interface to on-board logic.

#### 3.3.1 32FILL\* - 4-Byte Cache Fill

Type: Totem-Pole Output

32FILL\* is asserted by the MVME6000's VMEbus master whenever it is executing a VMEbus BYTE(0-3) read cycle.

The MVME6000 allows software to configure the master to attempt to read 4 bytes of data from a VMEbus slave, regardless of the number of bytes requested by the local processor. This function better supports cache architectures. This is done by setting the CFILL control bit to one as described in paragraph 4.5. As shown in Table 3-3, the chip will execute a 4-byte read cycle regardless of the requested size only if its master is configured to do a 32-bit transfer as defined by the MASD16 control bit (refer to paragraph 4.5) and the DAT16\* signal line (refer to paragraph 3.3.6), and if the CFILL control bit is set to 1.

### 3.3.2 ADR24\* - Standard Address Space

Type: Input

ADR24\* is driven by on-board logic (e.g., an address decoder) to configure the address modifier code that the MVME6000's VMEbus master drives during a VMEbus cycle. The line is asserted to prohibit, and negated to enable the master to drive an extended (A32) address modifier code. However, the AM code that the master actually drives during the VMEbus cycle is determined in one of two ways:

- 1. Dynamically determined from the levels of the ADR24\* and the SHORTIO\* signal lines (refer to paragraph 3.3.35) in conjunction with the MASA24 and MASA16 control bits (refer to paragraph 4.5 and Table 4-6).

- 2. From the contents of the Master Address Modifier register as described in paragraph 4.9.

### 3.3.3 BRDFAIL\* - Board Failed

Type: Input; Open-Collector Output

BRDFAIL\* is driven by the MVME6000 whenever the BRDFAIL bit in the System Controller Configuration register is set to 1 (refer to paragraph 4.3).

BRDFAIL\* can be asserted by other devices on the board to signal a failure. The global status bit BRDFAIL reflects the state of the BRDFAIL\* signal line regardless of who drives it.

#### 3.3.4 BRDRESET\* - Board Reset

Type: Input

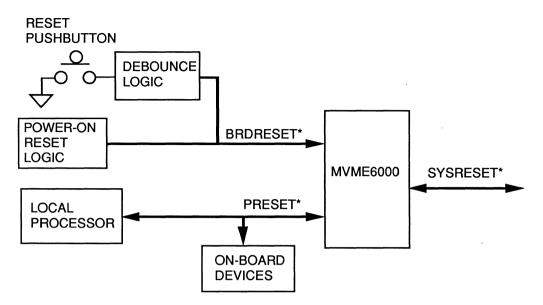

BRDRESET\* is asserted by on-board logic, and causes the MVME6000 to assert PRESET\* (refer to paragraph 3.3.28) and, if the chip is the system controller, assert the VMEbus SYSRESET\* signal. When asserting SYSRESET\* the MVME6000 guarantees that it remains asserted for a minimum of 200 milliseconds. Figure 3-3 is an example of connecting the BRDRESET\* and PRESET\* signals to on-board logic.

#### 3.3.5 CLK - Clock

Type: Input

The CLK input is intended to connect to an external TTL clock source. It is used to generate the timing signal for the internal state machines that control and synchronize the operation of the MVME6000.

#### 3.3.6 CS\* - Chip Select

Type: Input

As described in Chapters 4 and 5, the MVME6000 includes a Local Control and Status Register set (LCSR) and a Global Control and Status Register set (GCSR). Both are accessible to the local processor. In conjunction with the PDS\* signal line (refer to paragraph 3.3.23), the CS\* input signal line, is used to access the GCSR and the LCSR. The specific register is then selected using address lines PA00-PA07 at the offsets defined in Chapters 4 and 5.

#### 3.3.7 DAT16\* - Data 16-Bit

Type: Input

DAT16\* is driven by on-board logic (e.g., an address decoder) to allow dynamic configuration of the chip's VMEbus master to include the D32 data transfer capability. The line is asserted to prohibit, and negated to enable the master to execute a BYTE(1-2), BYTE(0-2), BYTE(1-3), and a BYTE(0-3) VMEbus cycle. However, the master will actually execute such a cycle only if it has been enabled to do so as defined by the MASD16 and the MASUAT control bits (refer to paragraph 4.5, and Tables 3-3 and 3-4).

#### 3.3.8 DHB\* - Device Has Bus

Type: Totem-Pole Output

DHB\* is driven by the MVME6000 in response to the DWB\* input. When DWB\* is asserted and the MVME6000 has VMEbus mastership it asserts DHB\*. DHB\* remains asserted until DWB\* is negated.

#### 3.3.9 DWB\* - Device Wants Bus

Type: Input

DWB\* can be used by on-board logic to request the MVME6000 to acquire and maintain VMEbus mastership. Asserting DWB\* causes the chip to request the bus (if it does not already own it). VMEbus mastership is then maintained DWB\* is negated. After negating DWB\* the MVME6000 might either release or maintain VMEbus mastership in accordance with the configuration of the release modes as described in paragraph 4.4.

#### 3.3.10 HALT\* - Halt

Type: Input; Open-Collector Output

#### <u>NOTE</u>

HALT\* is designed to be directly connected to the HALT\* pin on the MPU (68020/68030).

In conjunction with PBERR\* (refer to paragraph 3.3.19), HALT\* is asserted by the MVME6000 to indicate that the local processor should retry the current cycle. A retry sequence is initiated in response to either of the following two events:

- 1. On-board logic asserts RETRY\* (refer to paragraph 3.3.32) while the chip's VMEbus master is executing a VMEbus cycle.

- A dual-port lockup condition is detected. The MVME6000 determines a lockup condition when a VMEbus master is attempting to access local resources through the MVME6000's VMEbus slave at the same time that the local processor is attempting to access VMEbus resources using the chip's VMEbus master.

#### NOTE

If the 020 bit is set and the RMC\* signal is asserted during either of the two cases, the MVME6000 initiates a bus error, not a retry.

#### 3.3.11 IPL0\*-IPL2\* - Interrupt Priority Level 0-2

Type: Totem-Pole Output

The MVME6000 drives IPL0<sup>\*</sup>-IPL2<sup>\*</sup> to interrupt the local processor. The encoding of the three IPL lines, as well as the interrupt source for each level are shown in Table 3-1. Further information about the utility interrupts can be found in paragraphs 4.11 and 4.12. IPL0<sup>\*</sup>-IPL2<sup>\*</sup> normally are not connected directly to the local MPU if devices other than the MVME6000 can interrupt the local MPU.

| IPL2* | IPL1* | IPL0* | Interrupt Level | VMEbus<br>Interrupt | Utility Interrupt  |

|-------|-------|-------|-----------------|---------------------|--------------------|

| H     | Н     | Н     |                 |                     |                    |

| Н     | н     | L     | 1               | IRQ1*               | Signal low         |

| Н     | L     | Н     | 2               | IRQ2*               | Location monitor 0 |

| н     | L     | L     | 3               | IRQ3*               | VMEbus IACK        |

| L     | н     | н     | 4               | IRQ4*               | Location monitor 1 |

| L     | Н     | L     | 5               | IRQ5*               | Signal high        |

| L     | L     | н     | 6               | IRQ6*               | SYSFAIL*           |

| L     | L     | L     | 7               | IRQ7*               | Write-post BERR*   |

| Table | 3-1. | Encoding | of | IPL0*-IPL2* |

|-------|------|----------|----|-------------|

|-------|------|----------|----|-------------|

#### 3.3.12 LOCK\* - Lock

Type: Totem-Pole Output

LOCK\* is used to signal on-board logic that the MVME6000's slave is in the process of responding to a VMEbus cycle. The MVME6000 asserts the LOCK\* signal when it has been granted control of the local bus, as described in paragraphs 3.3.21 and 3.3.22. It then maintains LOCK\* in its asserted state, negating it after the VMEbus AS\* is negated.

The intended use of the LOCK\* line is to prevent the local processor from accessing local resources when the MVME6000 temporarily releases control of the local bus between the read and write portions of a read-modify-write cycle being performed by a VMEbus master on local resources.

### CAUTION

IF LOCK\* IS USED IN THE MANNER DESCRIBED ABOVE, IT IS THE RESPONSIBILITY OF ON-BOARD LOGIC TO GUARANTEE THE INDIVISIBILITY OF THE ACCESS TO MEMORY, I.E., THAT LOCAL MEMORY IS NOT CHANGED BETWEEN THE READ AND WRITE PORTIONS OF AN INDIVISIBLE CYCLE.

### 3.3.13 MATCH16\* - Match A16 Access

Type: Input

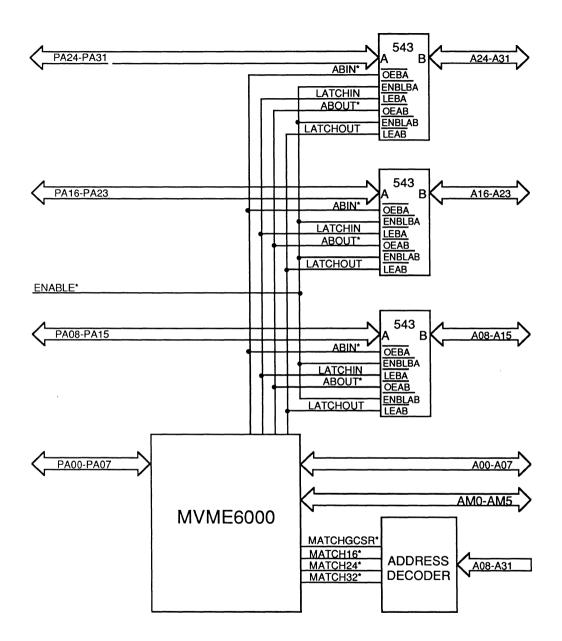

MATCH16\* is used by the MVME6000's VMEbus slave to determine whether the address carried on address lines A01-A15 matches the address of an on-board resource. The line is asserted by an external address decoder when a match is detected. However, the chip's VMEbus slave will respond only if it is configured to respond to cycles in the short address range (refer to paragraph 4.8), and if the cycle is indeed selecting byte locations in the short address range as determined from the AM code carried on AM0-AM5. Figure 3-4 shows how the MATCH16\* signal might be used.

### 3.3.14 MATCH24\* - Match A24 Access

Type: Input

The MATCH24\* input is used by the MVME6000's VMEbus slave to determine whether the address carried on address lines A01-A23 matches the address of on-board resources. The line is asserted by an external address decoder when a match is detected. However, the slave will respond only if it is configured to respond to cycles in the standard address range (refer to paragraph 4.8), and if the cycle is indeed selecting byte location in the standard address range as determined from the AM code carried on AM0-AM5. Figure 3-4 shows how the MATCH24\* input signal might be used.

### 3.3.15 MATCH32\* - Match A32 Access

Type: Input

The MATCH32\* input is used by the MVME6000's VMEbus slave to determine whether the address carried on address lines A01-A31 matches the address of on-board resources. The line is asserted by an external address decoder when a match is detected. However, the slave will respond only if it has been configured to respond to cycles in the extended address range (refer to paragraph 4.8), and if the cycle is indeed selecting byte location in the extended address range as determined from the AM code carried on AM0-AM5. Figure 3-4 shows how the MATCH32\* signal might be used.

### 3.3.16 MATCHGCSR\* - Match GCSR Access

Type: Input

The MATCHGCSR\* input is used by the MVME6000 to determine whether the short address carried on address lines A08-A15 matches the base address of the chip's Global Control and Status Register (GCSR) set. The line is asserted by an external address decoder when a match is detected. Note that the external decoder should not assert MATCH16\* or MATCH24\* or MATCH32\* at the same time it asserts MATCHGCSR\*. Figure 3-4 shows how the MATCHGCSR\* signal might be used.

3-5

#### 3.3.17 PA00-PA01 - Processor Address Lines 0-1 Type: Input; Three-State Output

#### <u>NOTE</u>

PA00-PA01 is designed to be directly connected to the PA00-PA01 pin on the MPU (68020/68030).

PA00-PA01 are received by the chip's VMEbus master when it executes VMEbus cycles. In conjunction with other signal lines and control bits, the master uses PA00 and PA01 to determine the size of the data transfer, and drive the appropriate levels on the VMEbus signals DS0\*, DS1\*, A01, and LWORD\*, as shown in Tables 3-3 and 3-4.

PA00-PA01 are driven by the chip's VMEbus slave when it responds to VMEbus cycles. The slave drives address lines PA00 and PA01 to establish the byte locations accessed, as determined from DS0\*, DS1\*, A01, and LWORD\* (refer to Tables 3-5 and 3-6).

PA00-PA01 are received by the chip's local slave during a local access to the chip's LCSR and GCSR. When the local processor is accessing the chip's registers, address lines PA00-PA01, in conjunction with PA02-PA07, are used to select the specific register that is being accessed.

#### 3.3.18 PA01-PA03 - Processor Address Lines 1-3

Type: Input; Three-State Output

#### <u>NOTE</u>

PA01-PA03 is designed to be directly connected to the PA01-PA03 pin on the MPU (68020/68030).

PA01-PA03 are used by the interrupt handler to determine to which level the local processor is responding during an interrupt acknowledge cycle. If the interrupt acknowledge cycle becomes a VMEbus interrupt acknowledge cycle, then PA01-PA03 are also used to create the value driven onto A01-A03 by the MVME6000 (refer to Table 3-2).

| Table 3-2. Using PA01-PA03 to Determine | e the | Interrupt | Level |

|-----------------------------------------|-------|-----------|-------|

|-----------------------------------------|-------|-----------|-------|

| PA3 | PA2 | PA1 | INTERRUPT BEING<br>ACKNOWLEDGED                                                   | A03 | A02 | A01 |

|-----|-----|-----|-----------------------------------------------------------------------------------|-----|-----|-----|

|     |     |     | None<br>Level 1<br>Level 2<br>Level 3<br>Level 4<br>Level 5<br>Level 6<br>Level 7 |     |     |     |

### 3.3.19 PA02-PA07 - Processor Address Lines 2-7

Type: Input; Three-State Output

#### <u>NOTE</u>

PA02-PA07 is designed to be directly connected to the PA02-PA07 pin on the MPU (68020/68030).

PA02-PA07 are received by the chip's VMEbus master, and driven onto VMEbus address lines A02-A07, when it executes VMEbus cycles.

PA02-PA07 are driven by the chip's VMEbus slave to carry the levels received on VMEbus address lines A02-A07 when it responds to VMEbus cycles.

PA02-PA07 are received by the chip's local slave when the local CPU accesses the LCSR and the GCSR. When the local processor is accessing the chip's registers, address lines PA02-PA07, in conjunction with PA00-PA01, select the register being accessed.

#### 3.3.20 PAS\* - Processor Address Strobe

Type: Three-State Output

PAS\* is driven by the chip's VMEbus slave when it responds to a VMEbus cycle. It is asserted to indicate the start of an access to local resources, and is negated when the access is completed.

### 3.3.21 PBERR\* - Processor Bus Error

Type: Input; Open-Collector Output

#### <u>NOTE</u>

PBERR\* is designed to be directly connected to the PBERR\* pin on the MPU (68020/68030).

PBERR\* is driven by on-board logic and received by the MVME6000's VMEbus slave when it is responding to a VMEbus cycle. On-board logic asserts PBERR\* to indicate that the data transfer request has not completed successfully (e.g., parity error), and is negated to indicate a successful transfer. When the MVME6000's VMEbus slave is responding to a VMEbus cycle, the assertion of PBERR\* causes the MVME6000 to assert the VMEbus' BERR\* signal.

PBERR\*, in conjunction with HALT\* (refer to paragraph 3.3.8), is asserted by the MVME6000 to indicate that the local processor should retry the current VMEbus bound cycle. A retry sequence is initiated in response to the following two events:

- 1. On-board logic asserts RETRY\* (refer to paragraph 3.3.32) while the chip's VMEbus master is executing a VMEbus cycle.

- 2. A dual-port lockup condition is detected. The MVME6000 determines a lockup condition when a VMEbus master is attempting to access local resources through

the MVME6000's VMEbus slave at the same time that the local processor is attempting to access VMEbus resources using the chip's VMEbus master.

#### <u>NOTE</u>

If the 020 bit is set and the RMC\* signal is asserted during either of the two cases, the MVME6000 initiates a bus error, not a retry.

#### 3.3.22 PBG\* - Processor Bus Grant

Type: Input

#### <u>NOTE</u>

PBG\* should not be connected directly to the MPU (68020/68030).

PBG\* is monitored by the MVME6000 to detect when it is granted control of the local bus. PBG\* is asserted by on-board logic to give the MVME6000 mastership of the local bus.

#### 3.3.23 PBR\* - Processor Bus Request

Type: Open-Collector Output

#### <u>NOTE</u>

PBR\* should not be connected directly to the MPU (68020/68030).

PBR\* is asserted by the MVME6000 to request mastership of the local bus. The chip requests mastership of the local bus when it determines that its VMEbus slave was selected to access an on-board resource. The MVME6000 holds PBR\* asserted until its input signal PBG\* is asserted, and the chip has asserted PAS\* and PDS\*.

#### NOTE

If the local processor requests that the MVME6000's master execute a VMEbus cycle after the chip asserts PBR\*, or if the local bus is requested by the chip's VMEbus slave after the chip's VMEbus master was selected to execute a VMEbus cycle, the chip will perform a retry as described in paragraph 3.3.31.

#### 3.3.24 PD00-PD07 - Local Data Lines 0-7

Type: Input; Three-State Output

The MVME6000's VMEbus slave monitors PD00-PD07, driving the binary value they carry onto the VMEbus D00-D07 data lines when it responds to a VMEbus read cycle. When the MVME6000's VMEbus slave responds to a VMEbus write cycle, it drives PD00-PD07 with the binary value carried on the VMEbus D00-D07 data lines.

The chip's VMEbus master monitors PD00-PD07, driving the binary value they carry onto the VMEbus D00-D07 data lines when it executes a VMEbus write cycle. When the MVME6000's VMEbus master executes a VMEbus read cycle, it drives PD00-PD07 with the binary value carried on the VMEbus D00-D07 data lines.

In addition, the local processor uses PD00-PD07 to access the MVME6000's GCSR and LCSR. When the local processor reads the registers, the MVME6000 drives PD00-PD07 with the binary value stored in the accessed register. When the processor writes to the registers, the chip monitors PD00- PD07, and stores the binary value they carry into the accessed register.

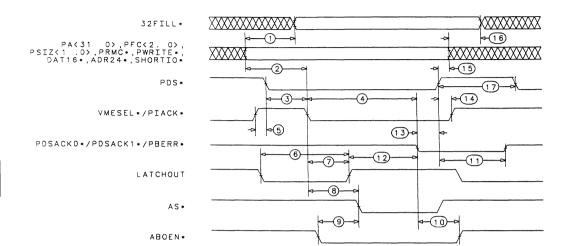

#### 3.3.25 PDS\* - Processor Data Strobe

Type: Input; Three-State Output

#### <u>NOTE</u>

PDS\* is designed to be directly connected to the PDS\* pin on the MPU (68020/68030).

PDS\* is driven by the MVME6000's VMEbus slave to indicate the beginning of an access to local resources. The slave asserts PDS\* when it responds to a VMEbus cycle, but not until after it has been granted mastership of the local bus (refer to paragraphs 3.3.22 and 3.3.23). The slave negates PDS\* after the local resource acknowledges the data access as described in paragraph 3.3.26.

PDS\* is received by the MVME6000's VMEbus master to determine the beginning and end of the VMEbus bound read or write cycle. It begins (or attempts to begin) a VMEbus read/write when both PDS\* and VMESEL are asserted (refer to paragraph 3.3.38). Onboard logic then negates PDS\* to terminate the cycle.

PDS\* is received by the MVME6000's interrupt handler to determine the start and end of an interrupt acknowledge cycle. The VMEbus interrupt-handler begins (or attempts to begin) a VMEbus IACK cycle when it detects both PDS\* and PIACK\* asserted (refer to paragraph 3.3.28). Local logic then negates PDS\* to terminate the interrupt acknowledge cycle.

PDS\* is received by the MVME6000 to determine the start and end of an access to the LCSR and GCSR. The MVME6000 allows access to the registers after it detects both CS\* (refer to paragraph 3.3.6) and PDS\* asserted. The local processor then negates PDS\* to terminate the access to the MVME6000's control and status registers.

### CAUTION

DURING VMEBUS MASTER READ/WRITE/IACK CYCLES, PDS\* MUST REMAIN ASSERTED UNTIL THE MVME6000 ASSERTS PDSACK0\*, PDSACK1\*, OR PBERR\*. ANY VIOLATION OF THIS MAY CAUSE ERRATIC OPERATION.

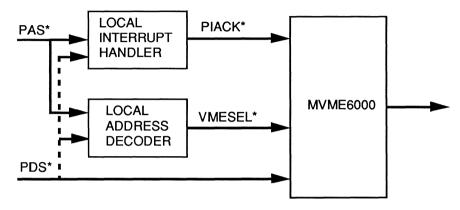

The intended use of PDS\*, PIACK\*, and VMESEL\* is shown in Figure 3-2.

Figure 3-2. Connecting PDS\*, VMESEL\*, and PIACK\* to the MVME6000

#### 3.3.26 PDSACK0\*-PDSACK1\* - Data Size Acknowledge 0-1 Type: Input; Three-State Output

#### <u>NOTE</u>

PDSACK0\*-PDSACK1\* is designed to be directly connected to the PDSACK0\*-PDSACK1\* pin on the MPU (68020/68030).

The MVME6000's VMEbus slave monitors PDSACK0\* and PDSACK1\* to determine when the local device has retrieved the requested data during a read cycle, or when it has stored the data during write cycles. Since the VMEbus does not support dynamic bus sizing, local logic needs only assert one of the two signal lines.

The MVME6000's VMEbus master drives PDSACK0\*-PDSACK1\* to signal the local processor that the VMEbus cycle has been executed. Asserting either PDSACK0\* or PDSACK1\* during a VMEbus read cycle signals that the VMEbus slave has responded to the cycle by asserting DTACK\*, and that the requested data is now valid. When the chip asserts PDSACK0\* or PDSACK1\* during a VMEbus write cycle, it signals the local processor that its request has been acknowledged, and that it can terminate the cycle. However, when the master has been configured to execute write-posting operations, the chip asserts the PDSACK lines as soon as it has latched (or controlled the latching of) the required cycle information, and before the VMEbus slave actually responded to it. The chip drives PDSACK0\*-PDSACK1\* as shown in Tables 3-3 and 3-4.

The MVME6000 asserts PDSACK1\* to indicate to the local processor that its requested access to the LCSR or GCSR has been successfully completed.

### 3.3.27 PFC0-PFC2 - Processor Function Code 0-2

Type: Input; Three-State Output

### <u>NOTE</u>

PFC0-PFC1 is designed to be directly connected to the PFC0-PFC1 pin on the MPU (68020/68030).

PFC0-PFC2 are driven by the chip's VMEbus slave to the binary value carried on the VMEbus AM0-AM2 lines in response to a VMEbus cycle. If the slave's Address Modifier is cleared to zeros the MVME6000 does not drive PFC0-PFC2.

PFC0-PFC2 are monitored by the chip's VMEbus master to dynamically determine the level it is to drive on the VMEbus AM0-AM2 address modifier lines. However, the levels carried on PFC0- PFC2 are actually driven onto AM0-AM2 only if the Masters Address Modifier register is not selected, as described in paragraph 4.9.

### 3.3.28 PIACK\* - Processor Interrupt Acknowledge

Type: Input

The MVME6000 monitors PIACK to determine when the local MPU is acknowledging an interrupt request. When both PIACK\* and PDS\* are asserted, the VMEbus interrupt handler checks for an internal interrupt request. If an internal MVME6000 interrupt request is pending on the acknowledge level, the MVME6000 responds immediately. Otherwise, it waits and performs a VMEbus IACK\* cycle that it uses to respond to the local interrupt acknowledge cycle. Figure 3-2 shows how the on-board logic might use PIACK\*.

#### 3.3.29 PRESET\* - Processor Reset

Type: Input; Open-Collector Output

The MVME6000 asserts PRESET\* when either the local input signal BRDRESET\* (refer to paragraph 3.3.27), or the VMEbus SYSRESET\* signal are asserted. When asserting PRESET\*, the MVME6000 holds it asserted for a minimum of 200 milliseconds.

PRESET\* might also be asserted by external logic. When the MVME6000 detects that PRESET\* is asserted, it initializes some of the control register bits to their default value. The bits that are affected by PRESET\*, as well as the value they are set to, are defined in Chapters 4 and 5. Figure 3-3 shows an example of connecting the BRDRESET\* and PRESET\* signals to onboard logic.

#### Figure 3-3. Connecting BRDRESET\* and PRESET\* to On-Board Logic

#### 3.3.30 PSIZ0, PSIZ1 - Processor Size Request 0-1 Type: Input; Three-State Output

#### <u>NOTE</u>

PSIZ0-PSIZ1 is designed to be directly connected to the PSIZ0-PSIZ1 pin on the MPU (68020/68030).

PSIZ0-PSIZ1 are received by the chip's VMEbus master when it executes a VMEbus cycle. In conjunction with other signal lines and control bits, the master uses PSIZ0 and PSIZ1 to determine the size of the data transfer, and drive the appropriate levels on the VMEbus signals DS0\*, DS1\*, A01, and LWORD\*, as shown in Tables 3-3 and 3-4.

PSIZ0-PSIZ1 are driven by the chip's VMEbus slave when it responds to a VMEbus cycle. The levels driven on PSIZ0 and PSIZ1 establish the byte locations accessed during the cycle, as determined from DS0\*, DS1\*, A01, and LWORD\*, as shown in Table 3-5 and Table 3-6.

#### 3.3.31 PWRITE\* - Processor Write

Type: Input; Three-State Output

#### NOTE

PWRITE\* is designed to be directly connected to the PWRITE\* pin on the MPU (68020/68030).

PWRITE\* is driven by the MVME6000's VMEbus slave in response to a VMEbus cycle. The level that the slave drives PWRITE\* to, is directly derived from the VMEbus signal WRITE\*. The slave asserts PWRITE\* to execute a write cycle to local resources, and negates it to execute a read cycle to local resources. Refer to Tables 3-5 and 3-6.

PWRITE\* is received by the MVME6000's VMEbus master when it executes a VMEbus cycle. The master uses the incoming level on PWRITE\* to determine whether it is to execute a VMEbus read or a VMEbus write cycle. The master executes a write cycle when PWRITE\* is asserted, and a read cycle when it is negated.

PWRITE\* is received by the MVME6000 when its LCSR or GCSR are accessed. The local processor asserts PWRITE\* when it wishes to store data in the registers, and negates PWRITE\* when it wishes to read data from the registers.

#### 3.3.32 RETRY\* - Retry

Type: Input

RETRY<sup>\*</sup> allows on-board logic to request that the local processor retry the cycle. The MVME6000 initiates a retry sequence when it detects RETRY<sup>\*</sup> asserted, when its master is executing a VMEbus cycle, but only if it has not yet asserted the DS1\*/DS0\*. It initiates the retry sequence by asserting both PBERR<sup>\*</sup> and HALT<sup>\*</sup>, adhering to the timing requirements of a 68020 type processor. However, if RMC<sup>\*</sup> is asserted and the 020 bit is set when the chip detects RETRY<sup>\*</sup> asserted, it will only assert PBERR<sup>\*</sup>.

## 3.3.33 RMC\* - Read-Modify-Write Cycle

Type: Input

#### <u>NOTE</u>

RMC\* is designed to be directly connected to the RMC\* pin on the MPU (68020/68030).

RMC\* is asserted by on-board logic in conjunction with VMESEL\* and PDS\* to request that the MVME6000's VMEbus master execute a VMEbus RMW cycle. When the chip detects RMC\* low and PSIZ0 high, it determines that the local processor is requesting a single-address indivisible cycle. In response, the chip's master will maintain the VMEbus AS\* asserted throughout the cycle, toggling the data strobes, and terminating the cycle after RMC\* is negated. If the MPU executes a multiple-address indivisible cycle (PSIZ0 low during the first cycle after RMC\* is asserted), the MVME6000 ignores RMC\* and performs normal read and write cycles as if RMC\* were not asserted.

### NOTE

The PA01 - PA31, PFC0-2, ADR24, SHORTIO, and DAT16 pins should remain valid during both the read and the write portions of read-modify-write cycles.

#### 3.3.34 SCLK - System Clock

Type: Input SCLK is a 16MHz input clock that is used to generate the VMEbus SYSCLK signal.

#### 3.3.35 SCON\* - System Controller On Type: Input

SCON\* is driven by on-board logic to configure the MVME6000 as the VMEbus system controller. When the MVME6000 detects SCON\* asserted, it enables the VMEbus arbiter and arbitration timer, the bus timer, the IACK daisy-chain driver, the SYSCLK driver, and the SYSRESET\* driver. These functions are disabled when SCON\* is negated.

#### NOTE

When SCON\* is high, the MVME6000's SYSRESET\* driver will not drive SYSRESET\* low when BRDRESET\* is driven low. However, the chip will still drive SYSRESET\* low whenever the SRESET control bit in the System Controller Register in the LCSR is set, regardless of the state of SCON\*.

#### 3.3.36 SHORTIO\* - Short I/O Cycle

Type: Input

SHORTIO\* is driven by on-board logic (an address decoder) to configure the address modifier code that the MVME6000's VMEbus master drives during a VMEbus cycle. An A16 address modifier code is driven whenever the line is asserted and the Master Address Modifier register is not selected (paragraph 4.9). When the line is negated, the MVME6000 automatically determines the address modifier code in one of two ways:

- 1. Dynamically from the levels of the ADR24\* signal line (paragraph 3.3.2) and the MASA24 and MASA16 control bits (paragraph 4.5 and Table 4-6).

- 2. From the Master Address Modifier register, if enabled as described in paragraph 4.9.

#### 3.3.37 VMESEL\* - Select VMEbus Cycle

Type: Input

The MVME6000 uses VMESEL\* in conjunction with PDS\* to determine that its VMEbus master is requested to perform a VMEbus cycle, and that mastership of the VMEbus should be obtained. The MVME6000 responds to this request once it detects both VMESEL\* and PDS\* asserted. The on- board logic that drives VMESEL\* should maintain it asserted until after PDS\* is negated. Figure 3-2 shows how on-board logic might use VMESEL\*.

#### 3.4 BUFFER CONTROL SIGNALS

#### 3.4.1 ABIN\* - Address Bus In

Type: Totem-Pole Output

ABIN\* is driven by the chip's VMEbus slave when it responds to a VMEbus cycle. The MVME6000 asserts ABIN\* to indicate that, having been granted mastership of the local bus, it is enabling the VMEbus address bus to be driven onto the local bus.

The intended use of ABIN<sup> $\star$ </sup> is to enable the output of the external buffers that receive address lines A08-A31 of the VMEbus. See Figure 3-4 for an example of connecting the MVME6000 to the 74FCT543 registered transceivers to receive the VMEbus address bus .

### 3.4.2 ABOUT\* - Address Bus Out

Type: Totem-Pole Output

ABOUT<sup>\*</sup> is driven by the chip's VMEbus master when it executes a VMEbus cycle. It also is driven by the chip's VMEbus interrupt handler when it executes VMEbus interrupt acknowledge cycles.

The MVME6000 asserts ABOUT\* to indicate that, having been granted mastership of the VMEbus, the board can now drive the VMEbus address bus.

ABOUT\* is used to enable the output of the external buffers that are used to drive address lines A08-A31 of the VMEbus. The MVME6000 controls the assertion of ABOUT\* to provide the required 35 nanoseconds set-up time of the address bus to AS\* (Timing Parameter 4 in the VMEbus Specification). An example of connecting the MVME6000 to the 74FCT543 registered transceivers to drive the VMEbus address bus is given in Figure 3-4.

#### 3.4.3 LATCHIN - Latch In

Type: Totem-Pole Output

LATCHIN is driven by the chip's VMEbus slave when it responds to VMEbus cycles. It is asserted by the MVME6000 whenever it is responding to a VMEbus data transfer cycle. LATCHIN is used to connect to the latch enable input of external latches (such as the 74FCT543) that are used to receive the VMEbus A08-A31 address lines, and D08-D31 data lines. An example of connecting the MVME6000 to the 74FCT543 registered transceivers to receive the VMEbus address and data buses is given in Figure 3-4 and Figure 3-5.

#### <u>NOTE</u>

Latching the VMEbus data bus into the local registers of the 74FCT543s is only meaningful when the chip is executing a cycle that receives data from the VMEbus and drives it onto the local data bus. The output of the latches is enabled in accordance with the type of cycle the chip executes as described in paragraphs 3.4.6 and 3.4.

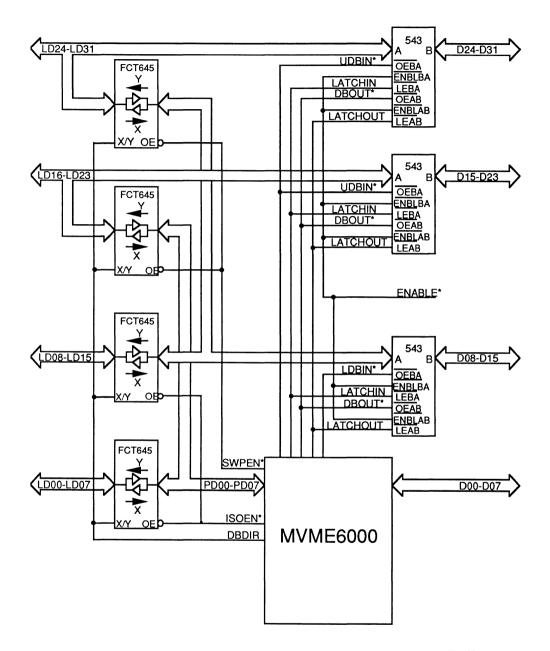

Figure 3-5. Connecting the MVME6000 to External Data Buffers

## SIGNAL LINES

## 3.4.4 LATCHOUT - Latch Out

Type: Totem-Pole Output LATCHOUT is driven by the chip's VMEbus master when it executes VMEbus cycles.

LATCHOUT is driven by the chip's VMEbus interrupt handler when it executes VMEbus interrupt acknowledge cycles.

LATCHOUT is driven by the chip's VMEbus slave when it responds to VMEbus cycles.

LATCHOUT is asserted by the MVME6000 whenever it is initiating or responding to a VMEbus cycle. The intended use of LATCHOUT is to connect to the latch enable input of external latches (such as the 74FCT543) that are used to drive the VMEbus A08-A31 address lines, and D08-D31 data lines. An example of connecting the MVME6000 to the 74FCT543 registered transceivers to drive the VMEbus address and data buses is given in Figures 3-4 and 3-5.

## <u>NOTE</u>

Latching the local data bus into the VMEbus registers of the 74FCT543s is only meaningful when the chip is executing a cycle that drives data from on-board logic onto the VMEbus data lines. The output of the latches is enabled in accordance with the type of cycle that the chip executes as described in paragraph 3.4.5.

## 3.4.5 DBOUT\* - Data Bus Out

Type: Totem-Pole Output

DBOUT\* is asserted by the chip's VMEbus master when it executes a VMEbus write cycle (see Tables 3-3 and 3-4). DBOUT\* is asserted by the chip's VMEbus slave whenever it responds to a VMEbus read cycle (see Tables 3-5 and 3-6).

DBOUT\* is used to enable the buffers that are used to drive the local data lines PD08-PD31 onto the VMEbus data lines D08-D31. See Figure 3-4 for an example of connecting the MVME6000 to the 74FCT543 registered transceivers to drive the VMEbus data bus.

## 3.4.6 LDBIN\* - Lower Data Bus In

Type: Totem-Pole Output

LDBIN\* is driven by the chip's VMEbus master when it executes a VMEbus read cycle. The level to which the chip drives the LDBIN\* signal is determined by the type of the VMEbus read cycle its VMEbus master is executing, as shown in Tables 3-3 and 3-4.

LDBIN\* is driven by the chip's VMEbus slave when it responds to a VMEbus write cycle. The level to which the chip drives the LDBIN\* signal is determined by the type of write cycle its VMEbus slave is responding to, as shown in Tables 3-5 and 3-6.

The intended use of LDBIN\* is to enable the buffers that are used to receive the VMEbus data lines D08-D15 and drive local data lines PD08-PD15. An example of connecting the MVME6000 to the 74FCT543 registered transceivers to receive the VMEbus data bus is given in Figure 3-5.

## 3.4.7 UDBIN\* - Upper Data Bus In

Type: Totem-Pole Output

UDBIN\* is driven by the chip's VMEbus master when it executes a VMEbus read cycle. The level to which the chip drives the UDBIN\* signal is determined by the type of the VMEbus read cycle its VMEbus master is executing as shown in Tables 3-3 and 3-4.

UDBIN\* is driven by the chip's VMEbus slave when it responds to a VMEbus write cycle. The level to which the chip drives the UDBIN\* signal is determined by the type of write cycle to which its VMEbus slave is responding. Refer to Tables 3-5 and 3-6.

The intended use of UDBIN\* is to enable the buffers that are used to receive the VMEbus data lines D16-D31 to drive the local data lines PD16-PD31. An example of connecting the MVME6000 to the 74FCT543 registered transceivers to receive the VMEbus data bus is shown in Figure 3-5.

## 3.4.8 DBDIR - Data Bus Direction

Type: Totem-Pole Output

DBDIR is driven by the chip's VMEbus master, the chip's VMEbus slave, and the chip's local slave to indicate the direction of the data.

DBDIR is driven low by the chip's VMEbus master when it executes a VMEbus read cycle, and high when it executes a VMEbus write cycle (see Tables 3-3 and 3-4).

DBDIR is driven high when the chip's VMEbus slave is responding to a VMEbus read cycle, and low when it is responding to a VMEbus write cycle (see Tables 3-5 and 3-6).

DBDIR is driven low by the chip's local slave when it responds to a local read cycle, and high when it responds to a local write cycle.

The intended use of the DBDIR output signal is to control the direction of the various data buffers that are used to interface the local data bus to the VMEbus data bus. Figure 3-5 is an example of how DBDIR is used.

## 3.4.9 ISOEN\* - Isolation Enable\*

Type: Totem-Pole Output

ISOEN\* is driven by the chip's VMEbus master when it executes VMEbus read or write cycle. The level to which the master drives ISOEN\* is determined by the type of cycle it executes, as well as by the capabilities it was configured to support, as shown in Tables 3-3 and 3-4.

ISOEN\* is driven by the chip's VMEbus slave when it is responding to VMEbus read and write cycles. The level to which the slave drives ISOEN\* is determined by the type of cycle it is responding to, and by the capabilities it includes. See Tables 3-5 and 3-6.

The chip's local slave negates ISOEN\* when it responds to an access to the LCSR and the GCSR.

## SIGNAL LINES

ISOEN\* is used to provide the necessary control required to interface D16 and D08(EO) VMEbus slaves to a 68020/68030 microprocessor. This class of processors access D16 devices over data lines LD16-LD31, while the VMEbus uses data lines D00-D15 to access them. Figure 3-5 shows how ISOEN\* is used to support this requirement. In the example, if ISOEN\* is asserted during cycles that drive data onto the VMEbus, the isolation buffers are enabled to route the local data lines LD00-LD15 onto the VMEbus data lines D00-D15. Similarly, if ISOEN\* is asserted during cycles that receive data from the VMEbus, the VMEbus data lines D00-D15. Similarly, if ISOEN\* is asserted during cycles that receive data from the VMEbus, the VMEbus data lines D00-D15 will be routed onto the local data lines LD00-LD15. When ISOEN\* is negated, the isolation buffers are turned off.

## 3.4.10 SWPEN\* - Swap Enable

Type: Totem-Pole Output

SWPEN\* is driven by the chip's VMEbus master when it executes a VMEbus cycle. The level to which the master drives SWPEN\* is determined by the type of cycle it executes and by the capabilities it was configured to support, as shown in Tables 3-3 and 3-4.

SWPEN\* is driven by the chip's VMEbus slave when it is responding to a VMEbus cycle. The level to which the slave drives SWPEN\* is determined by the type of cycle it is responding to and by the capabilities it was configured to support, as shown in Tables 3-5 and 3-6.

SWPEN\* is asserted by the chip's local slave when it responds to a local access to the LCSR and GCSR.

The intended use of the SWPEN\* signal is to provide the necessary control that will allow to interface D16 and D08(EO) VMEbus slaves to a 68020/68030 microprocessor. This class of processors access D16 devices over data lines LD16-LD31, while the VMEbus uses data lines D00- D15 to access them. Figure 3-5 shows how SWPEN\* is used to support this requirement. In the example, if SWPEN\* is asserted during cycles that drive data onto the VMEbus, the swap buffers are enabled to route the local data lines LD16-LD31 onto the VMEbus data lines D00-D15. Similarly, if SWPEN\* is asserted during cycles that receive data from the VMEbus, the VMEbus data lines D00-D15 will be routed onto the local data lines LD16-LD31.

## SIGNAL LINES

|                       |                       |                  |                  |                                      |                                           |                                           |                                               |             | OUT              | PUT         | SIGN             | IALS             |                  |                            |

|-----------------------|-----------------------|------------------|------------------|--------------------------------------|-------------------------------------------|-------------------------------------------|-----------------------------------------------|-------------|------------------|-------------|------------------|------------------|------------------|----------------------------|

| P<br>S<br>I<br>Z<br>1 | P<br>S<br>I<br>Z<br>O | P<br>A<br>1      | P<br>A<br>0      | CFILL                                | D<br>3<br>2<br>E<br>N                     | M A S<br>U A T                            | PDSACK0*                                      | SWPEN*      | ISOEN*           | U D B I N * | D<br>S<br>1<br>* | D<br>S<br>0<br>* | A<br>0<br>1      | L<br>W<br>O<br>R<br>D<br>* |

|                       |                       |                  |                  | X 0 0 X 0 0 0                        | F T X F T X X                             | X X 0 X 1 X X                             | $H \sqcup H H \sqcup H H$                     |             | HLHHLHH          | HLHHLHH     |                  |                  |                  | HLHHLHH                    |

|                       | H<br>H<br>H<br>H      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 0<br>0<br>0<br>0                     | X<br>X<br>X<br>X                          | X<br>X<br>X<br>X                          | ΗΗΗ                                           | L<br>L<br>L | H<br>H<br>H<br>H | TTTT        | L<br>H<br>L<br>H | H<br>L<br>H<br>L | L<br>L<br>H<br>H | н<br>нн<br>н               |

| нннн                  |                       |                  |                  | 0<br>X<br>0<br>0<br>0<br>0           | X F X T X X                               | X X 0<br>1 X X                            | H H H L H H                                   |             | HHHLHH           | H H H L H H |                  |                  |                  |                            |

| H H H H H H H X       | ннннн                 |                  |                  | 0<br>X<br>0<br>X<br>0<br>X<br>0<br>0 | X<br>F<br>T<br>X<br>F<br>T<br>X<br>X<br>T | 0<br>X<br>1<br>0<br>X<br>1<br>X<br>X<br>X | H $H$ $L$ $H$ $H$ $L$ $H$ $H$ $L$ $H$ $H$ $L$ |             |                  |             |                  |                  |                  |                            |

## Table 3-3. Signaling During VMEbus Read Cycles

Notes: 1. F = False, T = True, H = High, L = Low, X = Don't care 2. D32EN is True if DAT16\* = H and MASD16 = 0. 3. D32EN is False if either DAT16\* = L or MASD16 = 1

4. PDSACK1\* = L, DBDIR = L, LDBIN = L, DBOUT\* = H

During all cycles above.

|                       |                       |                  |             |                         |                       |                                      |                                                   |        | OUT                                               | PUT           | SIGN             | IALS             |             |          |

|-----------------------|-----------------------|------------------|-------------|-------------------------|-----------------------|--------------------------------------|---------------------------------------------------|--------|---------------------------------------------------|---------------|------------------|------------------|-------------|----------|

| P<br>S<br>I<br>Z<br>1 | P<br>S<br>I<br>Z<br>O | P<br>A<br>1      | P<br>A<br>0 | CFILL                   | D<br>3 2<br>E<br>N    | M A S U A T                          | PDSACK0*                                          | SWPEN* | ISOEN*                                            | UDBIN*        | D<br>S<br>1<br>* | D<br>S<br>0<br>* | A<br>0<br>1 | LWORD*   |

|                       |                       |                  | ーーエエエーエ     | *****                   | F T X F T X X         | X X O X 1 X X                        | $H \ L H H \ L H H$                               |        | $H \sqcup H H \sqcup H H$                         | <b>TTTTTT</b> |                  |                  |             | TTLTTT   |

| L<br>L<br>L           | HHHH                  | L<br>L<br>H<br>H | LHLH        | X<br>X<br>X<br>X<br>X   | X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X                | HHHH                                              |        | TTTT                                              | エエエエ          | LHLH             | HLHL             | LLHH        | тттт     |

| нннн                  |                       |                  |             | *****                   | X F X T X X           | X X 0<br>1 X X                       | HHHLHH                                            |        |                                                   | エエエエエエ        |                  |                  |             |          |

| <b>IIIIII</b>         | ****                  |                  |             | × × × × × × × × × × × × | XFTXFTXX              | 0<br>X<br>1<br>0<br>X<br>1<br>X<br>X | H $H$ $L$ $H$ |        | H $H$ $L$ $H$ | ******        |                  |                  |             | TTLTTLTT |

Table 3-4. Signaling During VMEbus Write Cycles

Notes: 1. F = False, T = True, H = High, L = Low, X = Don't care 2. D32EN is True if DAT16\* = H and MASD16 = 0.

3. D32EN is False if either DAT16\* = L or MASD16 = 1

4. PDSACK1\* = L, DBDIR = H, LDBIN = H, DBOUT\* = L During all cycles above.

## SIGNAL LINES

|                                                                         | NPUT<br>D CO |             |                  |                  |                       |                       |             | OUT                 | PUT                   | SIGN                | IALS |             |                         |                                                                                                                                |

|-------------------------------------------------------------------------|--------------|-------------|------------------|------------------|-----------------------|-----------------------|-------------|---------------------|-----------------------|---------------------|------|-------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| S L V D<br>1 6                                                          | LWORD*       | A<br>0<br>1 | D<br>S<br>0<br>* | D<br>S<br>1<br>* | P<br>S<br>I<br>Z<br>1 | P<br>S<br>I<br>Z<br>O | P<br>A<br>1 | P<br>A<br>0         | SWPEN*                | ISOEN∗              |      | U D B I N * | D<br>B<br>O<br>U<br>T * | BYTE<br>LOCATION<br>ACCESSED                                                                                                   |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |              |             |                  | LHLLHLLHLLHL     |                       |                       |             |                     |                       |                     |      | ********    |                         | BYTE(0-3)<br>BYTE(1-3)<br>BYTE(0-2)<br>BYTE(1-2)<br>NONE<br>BYTE(0-1)<br>BYTE(0)<br>BYTE(0)<br>BYTE(2-3)<br>BYTE(3)<br>BYTE(2) |