# APC Hard Disk Subsystem Reference Guide

819-000102-6002 Rev.00 4-83

APC-HARD DISK SUBSYSTEM REFERENCE GUIDE Models APC-H26 and -H27.

Insert this document into your APC System Reference Guide DOC. No. APC D01.

#### LIABILITY DISCLAIMER

NEC Information Systems, Inc. (NECIS) products are warranted in accordance with the terms of the applicable NEC Information Systems, Inc. product specification. Product performance is affected by system configuration, software, the application customer data, and operator control of the system among other factors. While NECIS products are considered to be compatible with most systems, the product functional implementation by customers of the product may vary.

Therefore, the suitability of a product for a specific application must be determined by the customer and is not warranted by NECIS.

This manual is as complete and factual as possible at the time of printing; however, the information in this manual may have been updated since that time. NEC Information Systems, Inc. reserves the right to change the functions, features, or specifications of its products at any time, without notice.

NEC Information Systems, Inc. has prepared this document for use by NECIS employees and customers. The information contained herein is the property of NECIS and shall not be reproduced without prior written approval from NECIS.

Spinwriter<sup>®</sup> is a registered trademark of NEC Corporation.

#### First Printing—March 1983 Revised—April 1983

Copyright 1983 NEC Information Systems, Inc. 5 Militia Drive Lexington, MA 02173

Printed in U.S.A.

#### FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

"WARNING: This equipment generates, uses and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A Computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide protection against such interference. Operation of the equipment in a residential area is likely to cause interference in which case, the user will be required to take whatever measures may be required to correct the interference."

#### Manufacturer's Instructions and User's Responsibilities to Prevent Radio Frequency Interference

#### **Manufacturer's Instructions**

The user must observe the following precautions in installing and operating this device:

- 1. Operate the equipment in strict accordance with the manufacturer's instructions for the model.

- 2. Ensure that the unit is plugged into a properly grounded wall outlet and that the power cord supplied with the unit is used and not modified.

- 3. Ensure that the unit is always operated with the factory-installed cover set on the unit.

- 4. Make no modification to the equipment which would affect its meeting the specified limits of the Rules.

- 5. Properly maintain the equipment in a satisfactory state of repair.

#### **User's Responsibility**

The user has the ultimate responsibility to correct problems arising from harmful radio-frequency emissions from equipment under his control. If this equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one of the following measures. All of these responsibilities and any others not mentioned are exclusively at the expense of the user.

- 1. Change in orientation of the receiving device antenna.

- 2. Change in orientation of the equipment.

- 3. Change in location of equipment.

- 4. Change in equipment power source.

If these attempts are unsuccessful, install one or all of the following devices:

- 1. Line isolation transformers

- 2. Line filters

- 3. Electro-magnetic shielding

If necessary, the user should consult the dealer, NEC, or an experienced radio/television technician for additional suggestions. The user may find the following booklet prepared by the Federal Communications Commission to be helpful: "How to Identify and Resolve Radio-TV Interference Problems." This booklet is available from the U.S. Government Printing Office, Washington, D.C. 20402, Stock No. 004-000-00345-4.

"Note: The operator of a computing device may be required to stop operating his device upon finding that the device is causing harmful interference and it is in the public interest to stop operation until the interference problem has been corrected."

## Contents

| Chapter 1 General Description                                         | Page         |

|-----------------------------------------------------------------------|--------------|

| 1.1 PRINCIPAL FEATURES                                                | 1-1          |

| 1.2 MODELS                                                            | 1-2          |

| 1.3 DISK UNIT/MODULE ORGANIZATION         1.3.1 Sealed Module         | 1-5<br>1-5   |

| 1.3.2 Printed Circuit Board                                           | 1-7          |

| 1.4 POWER SUPPLY                                                      | 1-7          |

| 1.5 ENVIRONMENTAL/FUNCTIONAL CHARACTERISTICS                          | 1-7          |

| 1.5.1 Environmental Considerations                                    | 1-7          |

| 1.5.2 Dimension/Weight                                                | 1-8<br>1-8   |

| 1.5.3 Interface/Interlock Cabling1.5.4 DKU Functional Characteristics | 1-8          |

| Chapter 2 PCB Structure/Functionality                                 |              |

| 2.1 DISK ADAPTER PCB                                                  | 2-1          |

| 2.1.1 Disk Adapter Operational Modes                                  | 2-1          |

| 2.1.2 Disk Adapter Functional Capabilities                            | 2-4          |

| 2.1.2.1 Direct Memory Access Controller (DMAC)                        |              |

| Data Transfers                                                        | 2-4          |

| 2.1.2.2 Error Detect Logic                                            | 2-4          |

| 2.1.2.3 FMT Interface Logic                                           | 2-5          |

| 2.1.2.4 Interrupt                                                     | 2-10         |

| 2.1.2.5 I/O Decoder                                                   | 2-10         |

| 2.1.2.6 Main Bus Controller                                           | 2-10<br>2-11 |

| 2.1.2.7 Main Processor Interrupts (INT) From APC2.1.2.8 Memory Buffer | 2-11         |

| 2.1.2.8 Memory Buller                                                 |              |

| 2.1.3.1 FMT I/O and Processor Memory Accessability                    | 2-11         |

| 2.1.3.2 I/O Commands                                                  | 2-12         |

|                                                                       | ~            |

## Contents (cont'd)

| 2.2 FMT DISK DRIVE CONTROLLER              |      |

|--------------------------------------------|------|

| 2.2.1 FMT PCB Disk Operation               | 2-18 |

| 2.2.2 Firmware Overview                    | 2-19 |

| 2.2.2.1 Firmware Characteristics           | 2-19 |

| 2.2.2.2 Firmware Operational Overview      | 2-23 |

| 2.2.2.3 Firmware Start Up                  | 2-23 |

| 2.2.2.4 Firmware Functional Notations      | 2-25 |

| 2.2.3 Command Functional Overview          | 2-40 |

| 2.2.3.1 Check Command                      | 2-41 |

| 2.2.3.2 Read Data Command                  | 2-41 |

| 2.2.3.3 Read ID                            | 2-43 |

| 2.2.3.4 Recalibrate                        | 2-44 |

| 2.2.3.5 Write Data                         | 2-44 |

| 2.2.3.6 Write ID                           | 2-45 |

| 2.2.3.7 Seek                               | 2-45 |

| 2.2.3.8 Sense Interrupt Status             | 2-46 |

| 2.2.3.9 Sense Unit Status                  |      |

| Chapter 3 Disk Drive Assembly              |      |

| -                                          |      |

| 3.1 PHYSICAL/FUNCTIONAL ORGANIZATION       | 3-2  |

| 3.2 ENVIRONMENTAL CONSIDERATIONS AND       |      |

| FUNCTIONAL SPECIFICATIONS                  | 3-5  |

| 3.3 ADDRESS/POWER/TERMINATOR CONNNECTOR    |      |

| CONSIDERATIONS                             | 3-5  |

| 3.4 INTERFACE LOGIC CIRCUITS               | 3-5  |

| 3.5 INTERFACE CABLING CONSIDERATIONS       | 3-6  |

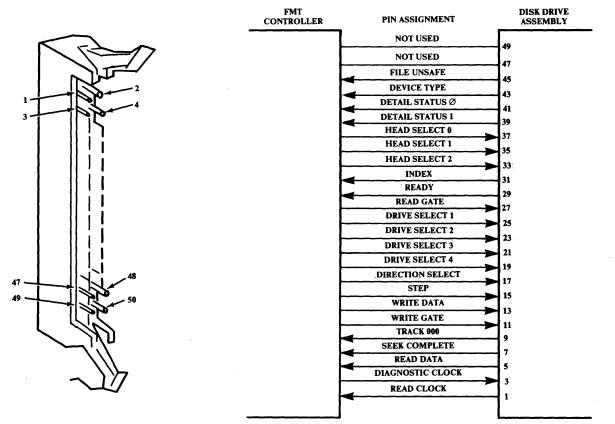

| 3.6 INTERFACE SIGNAL FUNCTIONS             | 3-8  |

| 3.7 DATA RECORD FORMAT                     | 3-10 |

| 3.8 PCB REMOVAL/REPLACEMENT AND ELECTRICAL |      |

| ADJUSTMENTS                                |      |

|                                            | 3-11 |

| 3.8.2 Electrical Adjustments               | 3-12 |

### Page

## List of Illustrations

•

| Figure | Title                                    | Page |

|--------|------------------------------------------|------|

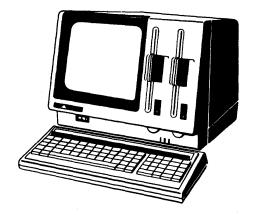

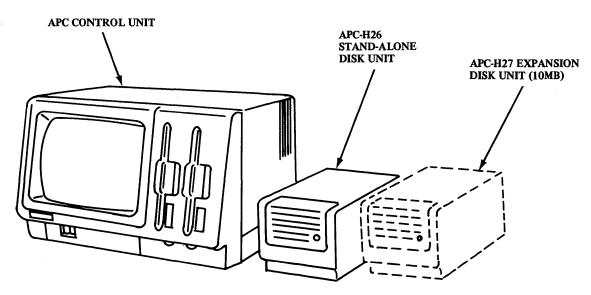

| 1-1    | Typical APC System Configuration         | 1-2  |

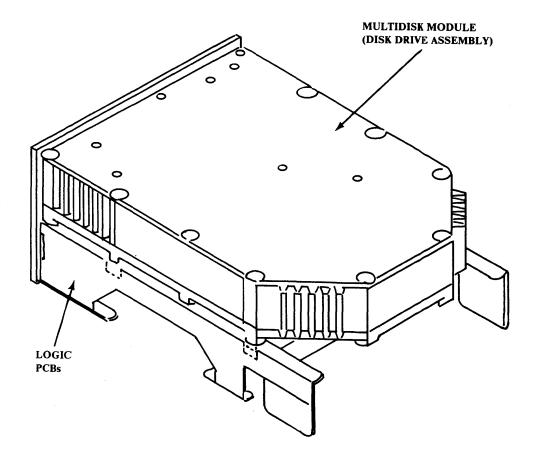

| 1-2    | Multidisk Module (Disk Drive Assembly    | 1-3  |

| 1-3    | APC Stand-Alone/Expansion DKU Functional |      |

|        | Block Diagram                            | 1-4  |

| 1-4    | APC Disk Module (Major Components)       | 1-6  |

| 2-1    | Disk Adapter Functional Block Diagram    | 2-2  |

| 2-2    | Buffer Control Block                     | 2-4  |

| 2-3    | Typical Driver/Receiver Circuit          | 2-5  |

| 2-4    | Interface Signals (Adapter to FMI)       | 2-6  |

| 2-5    | FMT Interface Timing                     | 2-9  |

| 2-6    | DMA Access Riming                        | 2-9  |

| 2-7    | 3302 FMT Block Diagram                   | 2-17 |

| 2-8    | FM7 PCB Physical Configuration           | 2-18 |

| 2-9    | Firmware Hardware Interface              | 2-19 |

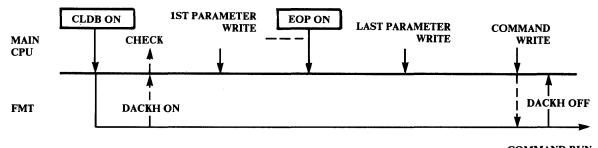

| 2-10   | Command Set                              | 2-24 |

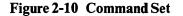

| 2-11   | Receive Result Status                    | 2-24 |

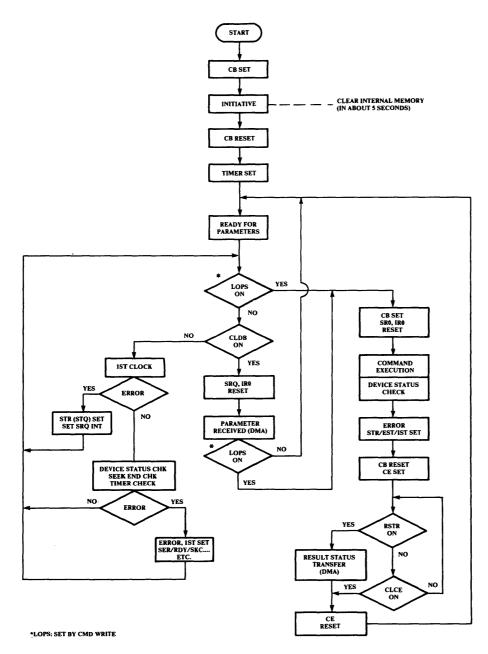

| 2-12   | FMT Firmware Flowchart                   | 2-27 |

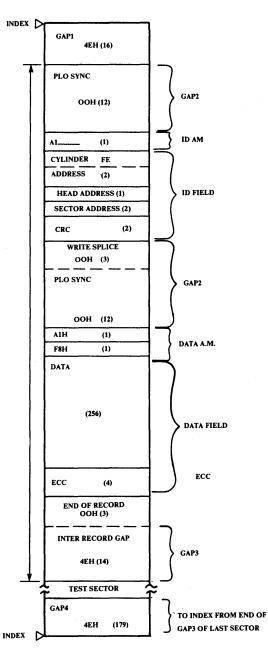

| 2-13   | Sector Map (Disk)                        | 2-28 |

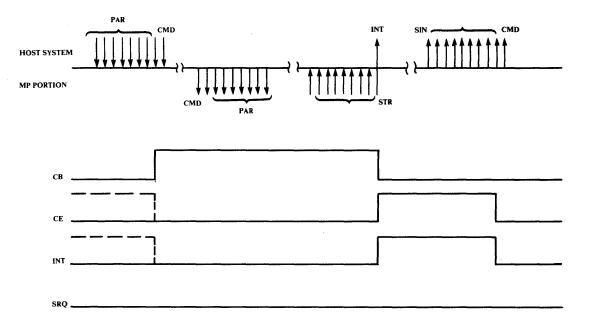

| 2-14   | Record/Write Command Timing              | 2-29 |

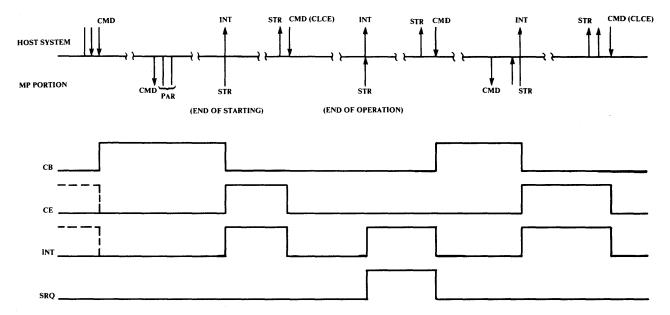

| 2-15   | Seek/Recalibrate Timing                  | 2-29 |

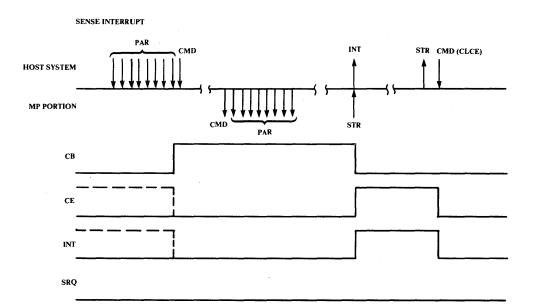

| 2-16   | Sense Interrupt Timing                   | 2-30 |

| 2-17   | Sense Unit Status Timing                 | 2-30 |

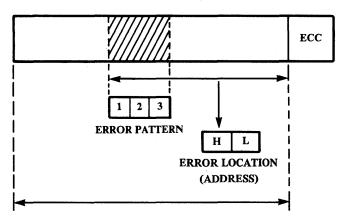

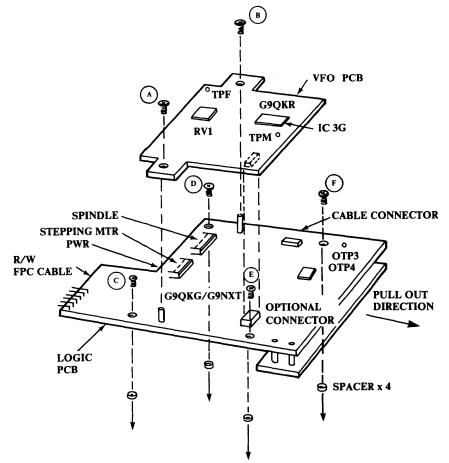

| 3-1    | APC Disk Module (Exploded View)          | 3-3  |

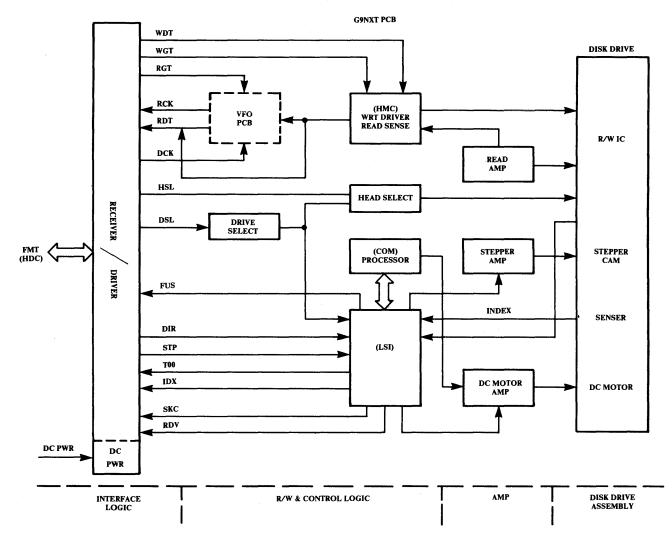

| 3-2    | Functional Block Diagram                 | 3-4  |

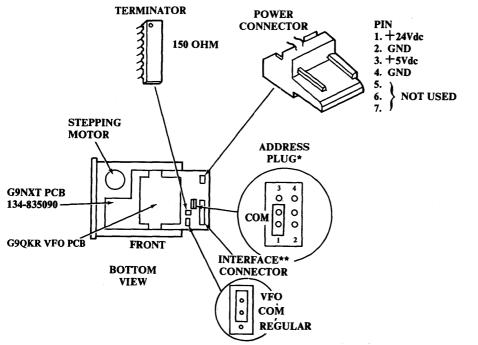

| 3-3    | Terminator/Address Plug Layout           | 3-6  |

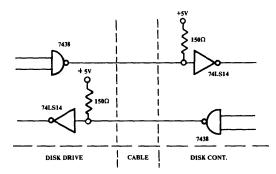

| 3-4    | Typical Interface Logic Circuit          | 3-7  |

| 3-5    | Interface Cable Connector/Pin Assignment | 3-7  |

| 3-6    | PCB Disassembly/Assembly (Disk Drive)    | 3-11 |

## **List of Tables**

| Table | Title                                     | Page |

|-------|-------------------------------------------|------|

| 1-1   | Functional Characteristics                | 1-9  |

| 2-1   | Interface Connector Signal Pin Assignment | 2-6  |

| 2-2   | FMT Control Line Register Select/Function | 2-10 |

| 2-3   | I/O Commands (DMA)*                       | 2-13 |

| 2-4   | I/O Command (HDC/FMT)                     | 2-14 |

| 2-5   | I/O Command (Reset/IWT)                   | 2-14 |

| 2-6   | Read INT/HDEX I/O Command*                | 2-15 |

| 2-7   | INT Mask Set I/O Commands                 | 2-15 |

| 2-8   | FMT I/O Read/Write (Status) Commands      | 2-20 |

| 2-9   | FMT I/O Commands (Read/Write)             | 2-20 |

| 2-10  | IRO Write                                 | 2-21 |

| 2-11  | IRO Read                                  | 2-22 |

| 2-12  | Commands/Status Results                   | 2-31 |

| 2-13  | Parameters                                | 2-35 |

| 2-14  | (STR) Status Register                     | 2-36 |

| 2-15  | (EST) Error Status                        | 2-37 |

| 2-16  | (IST) Interrupt Status                    | 2-38 |

| 2-17  | (US1) Unit Status 1                       | 2-39 |

| 2-18  | (US2) Unit Status 2                       | 2-40 |

### Preface

This manual is written for those who desire an understanding of the Disk Unit (DKU) operations; not only as an external storage device in an APC system configuration, but also its operations within an APC control unit. This information includes the functional capabilities of the DKU, as well as, the status information sent to the APC control unit for interrogation and processing of data and I/O commands. The manual also describes the principal features of the DKU, the applicable environmental considerations, the physical and functional capabilities of the major Printed Circuit Boards (PCB), and the disk drive assembly itself. Maintenance and installation information are mentioned on an as needed basis, only. This type of information is provided in the APC Maintenance Guide and the Hard Disk Subsystem Installation Guide.

### Chapter 1

# **General Description**

The APC disk subsystem is used as an external storage device in an APC system (see Figure 1-1). It comes as a stand-alone Disk Unit (DKU), model APC-H26, and an expansion DKU, model APC-H27. The stand-alone DKU is also referred to as the master and the expansion unit as the slave. Each model provides a disk storage capacity of approximately 10 Megabytes (MB) of formatted data. When installed together they provide an overall storage capacity of approximately 20 MBs. Included in each model is a sealed multidisk module designed to improve the operational reliability by minimizing contaminents on the recording surface (see Figure 1-2). Operational reliability is further improved with the use of magnetic heads with NEC Large Scale Integration (LSI) circuits designed to enhance the weakest signals.

The model APC—H26 contains the interface and control logic for the stand-alone and the expansion DKUs on a single Printed Circuit Board (PCB), called the 3302 Format (FMT) control PCB. Both the stand-alone and expansion DKUs contain their respective disk drive electronics.

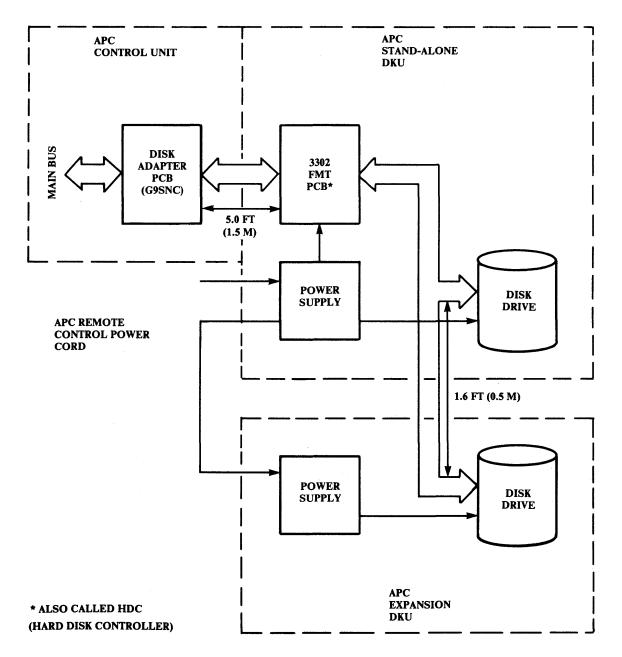

The APC control unit houses a disk controller, called, the Disk Adapter PCB. This adapter connnects directly with the 3302 FMT PCB in the stand-alone DKU (see Figure 1-3), and contains the interface logic to support the appropriate APC system configuration.

#### **1.1 PRINCIPAL FEATURES**

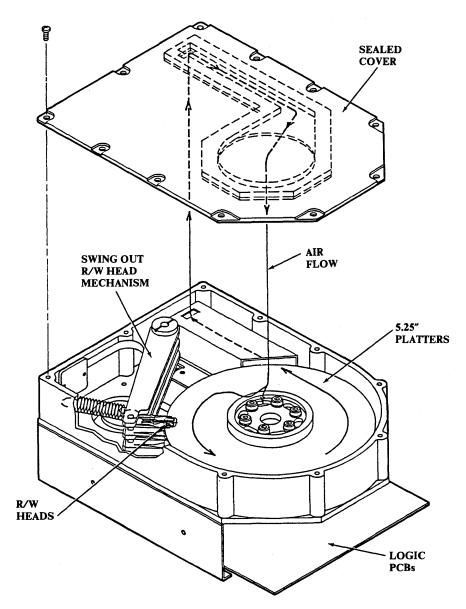

The APC Disk Units (DKU) are compact, fast-access data storage devices designed for use with an APC system. Data is stored on 5.25 inch metal-oxide-coated disks that are mounted on a common rotating spindle and, along with the Read/Write (R/W) heads, are housed in an air-tight, sealed module. This arrangement assures maintenance-free operation, negating maintenance checks. The metal oxide coated disks are also known as platters. Both models contain four 2-sided disks; each disk surface is equipped with a pair of Winchester type magnetic R/W heads. The R/W heads are supplied as standard equipment and are structured on a swing out mechanism driven by a stepping motor assembly. All heads incorporate a preamplifier to improve read data signal-to-noise ratio.

Depending on the disk configuration, that is, a stand-alone only or a stand-alone and an expansion disk unit, the disk system is capable of storing approximately 10 or 20 MBs of formatted data at a maximum recording density of 7480 bits per inch. The recording method used is the Modified Frequency Modulation (MFM) technique, and the data transfer rate is 500 KBytes per second.

#### **1.2 MODELS**

The model disk units currently available for the APC are listed below and are briefly described in the preceding text. A more detailed description is provided in subsequent chapters.

Model APC-H26 Stand-alone DKU (Master Unit).

Figure 1-1 Typical APC System Configuration

Figure 1-2 Multidisk Module (Disk Drive Assembly)

General Description

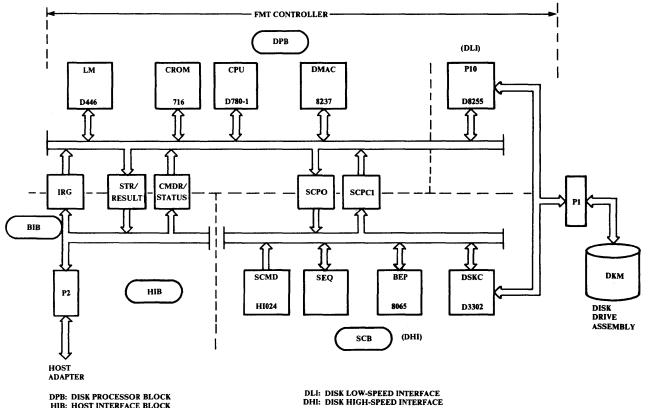

Figure 1-3 APC Stand-Alone/Expansion DKU Functional Block Diagram

#### **1.3 DISK UNIT/MODULE ORGANIZATION**

Figure 1-4 shows the physical layout of the major disk drive components contained in the sealed module within the APC Disk Unit (DKU). They are briefly described below. The associated DKU cabinetry and related components are described in subsequent chapters.

#### 1.3.1 Sealed Module

The sealed module contains a sealing type metal cover, spindle, four 5.25 inch platters, eight Winchester type R/W heads, interface and control logic PCB, and other related components shown in the illustration and described in subsequent sections.

The metal cover seals the module against contaminents from the surrounding environment, and maintains constant filtered air flow through the module. Because the interior is sealed from the environment and kept clean by a circulatory air flow, the APC DKU is assured of stable operation under ordinary office conditions.

#### CAUTION

The cover is normally installed at the factory and should never be removed in the field. When the DKU is defective, return it to the local branch office for service.

The spindle supports and drives the four platters and is driven by a 115 Vac constant drive motor.

The 5.25 inch platters are two-sided magnetic disks that permit the use of Winchester type read and write heads over each surface, resulting in the high storage capabilities in each DKU. That is, each 5.25 inch disk surface has a track density of 220 tracks per inch, resulting in a maximum recording density of 7480 bits per inch. The number of sectors per track is 26 assuming formatted data. When storage is unformatted, the storage capacity and number of sectors are variable up to a maximum storage capacity of approximately 12 MBs. Additional information is provided in subsequent sections. General Description

Figure 1-4 APC Disk Module (Major Components)

Winchester type R/W heads are supported by a swing-arm mechanism which is driven by a 5-phase stepping motor. This arrangement reduces the seek time to less than 2 ms.

#### **1.3.2 Printed Circuit Boards (PCBs)**

The following printed circuit boards are used in the respective APC control unit or DKU as indicated. Functional and cabling information for each PCB is provided in subsequent chapters.

- 1. APC Control Unit G9SNC Disk Adapter (136-432222-B).

- 2. Stand-alone DKU 3302 FMT PCB (808-863492-201-A).

- -G9NXT Disk Drive Package (134-835090).

- -- Power Supply (808-863492-201-A).

- 3. Expansion DKU G9NXT Disk Drive Package (134-835090).

- -Power Supply (808-863492-201-A).

#### **1.4 POWER SUPPLY**

The 115 Vac, 50/60 Hz input power to the power supply simultaneously starts the power supply and fan. The power supply converts the ac input into regulated dc outputs of +5 and +24 Vdc and distributes the dc voltage throughout the DKU.

Ac input power to the DKU(s) is interlocked with the ac input power in the APC control unit. This makes the APC on/off switch the common power on/off element to all the DKU attachments, as well as, the APC control unit. Hence, the DKU attachments are turned on when the APC control unit is turned on, and are turned off when the APC control unit is turned off.

#### **1.5 ENVIRONMENTAL/FUNCTIONAL CHARACTERISTICS**

This section provides the environmental and functional characteristics for the Hard Disk Unit (DKU). This includes the environmental considerations, dimensions, weight, cabling, and an overview of the DKU functional characteristics.

#### **1.5.1 Environmental Considerations**

The environmental considerations are as follows:

- 1. Humidity (Noncondensing)10% to 80%

- 2. Operating Temperature 50° to 90° F

- 3. Vibration (Operating) Less than 0.5 G

#### 1.5.2 Dimension/Weight

The dimensions and weight for the APC DKU are as follows.

- 1. Depth 15.20 inches (380 mm)

- 2. Height 7.00 inches (175 mm)

- 3. Width 10.00 inches (250 mm)

- 4. Weight 25.30 lbs (11.5 Kg)

#### 1.5.3 Interface/Interlock Cabling

Two interface cables and an ac interlock cable, described below, are required to connect the stand-alone DKU to the APC control unit and, when used, the expansion unit to the stand-alone unit. Further cabling information is provided in the APC-H26/-H27 Hard Disk Subsystem Installation Guide.

- 1. Interface Cables

- a. Model APC-H26 Stand-alone DKU—The interface cable comes attached to the stand-alone DKU, is approximately 4.96 feet in length, and connects to the APC control unit.

- b. Model APC-H27 expansion DKU The interface cable comes attached to the expansion DKU, is approximately 1.65 feet in length, and connects to the stand-alone DKU.

- 2. Ac Interlock Cable

| a. Length—between the APC control unit and             |                |  |

|--------------------------------------------------------|----------------|--|

| stand-alone DKU.                                       | 4.96 feet      |  |

| — between the stand-alone DKU and<br>the expansion DKU | 1.65 feet      |  |

| b. Part Numbers                                        |                |  |

| Ac interlock cables                                    |                |  |

|                                                        | Q0Q Q62402 207 |  |

| APC-H26                | 808-863492-207-A |

|------------------------|------------------|

| APC-H27                | 808-863492-208-A |

| Ac power supply cables |                  |

| APC-H26                | 808-863492-209-A |

| APC-H27                | 808-863492-210-A |

#### **1.5.4 DKU Functional Characteristics**

The DKU functional characteristics, summarized in Table 1-1, are estimated at 256 bytes/sector times 26 sectors/track.

| FUNCTION                            | SPECIFICATION               |

|-------------------------------------|-----------------------------|

| 1. Access Time                      |                             |

| a. Average seek time                | 120 msec                    |

| b. Maximum seek time                | 360 msec                    |

| c. Minimum seek time                | 2 msec                      |

| d. Settling time                    | 15 msec                     |

| 2. Data Transfer Rate               | 500 Kbytes                  |

| 3. Disk (Platter) Configuration     |                             |

| a. Cylinders                        | 181 Total                   |

|                                     | 174 Data CYL                |

|                                     | 6 Spare CYL                 |

|                                     | 1 DIAG. CYL                 |

| b. Heads (Read/Write)               | 8                           |

| c. Platters                         | 4 (2 sides each)            |

| 4. Power - 115 Vac input, 50/60 Hz  | ±10%, 1.0A                  |

| a. +5 Vdc (output)                  | $\pm 5\%$ , 1.8A (with VFO) |

| b. $+24$ Vdc (output)               | $\pm 10\%$ , 1.2A (average  |

| 0. · 2 · · 2 · (output)             | 2.2A (starting)             |

|                                     |                             |

| 5. Recording Density                |                             |

| a. Bit density                      | 7480 BPI                    |

| b. Track density                    | 220 TPI                     |

| 6. Recording Format                 | MFM                         |

| 7. Reliability                      |                             |

| a. MTBF                             | 10,000 Power on Hours       |

| b. Error Rate                       |                             |

| <ul> <li>Non-Recoverable</li> </ul> | 1 per 10 <sup>12</sup>      |

| • Recoverable                       | 1 per 10 <sup>10</sup>      |

| • Seek errors                       | 1 per 10 <sup>6</sup>       |

| 8. Rotational Speed                 | 3600 RPM                    |

| 9. Start/Stop Time                  | Less than 10 sec            |

| 10. Storage Capacity                | ]                           |

| a. Formatted                        | 9.27 MB                     |

| • Bytes/Cylinder                    | 53,248                      |

| • Bytes/Track                       | 6,656                       |

| b. Unformatted                      | 12.0 MB                     |

|                                     | l                           |

#### Table 1-1 Functional Characteristics

#### **1.6 TYPICAL DISK DRIVE READ/WRITE OPERATION**

To write data on a disk (platter) the FMT controller, described in Chapter 2, converts 8-bit parallel data characters from the APC control unit (see Figure 1-3) into bit-by-bit serial data characters. The disk drive electronics (see Chapter 3) accepts the serial data from the FMT controller and gates it to the disk drive assembly where it is written, bit-by-bit, into the designated sector (or sectors) on the selected platter. A read operation fetches bit-by-bit serial data to the FMT controller where it is converted back to 8 bit parallel data characters for transmission to the APC control unit.

**Chapter 2**

# **PCB Structure/Functionality**

This chapter provides the structural characteristics for the two major DKU PCBs used in an APC system configuration (see Figures 1-1 and 1-3), and includes a brief description of their functional capabilities. The two major PCBs are as follows.

- G9SNC Disk Adapter (Disk Controller) PCB

- 3302 Format (FMT) Control PCB

#### **2.1 DISK ADAPTER PCB**

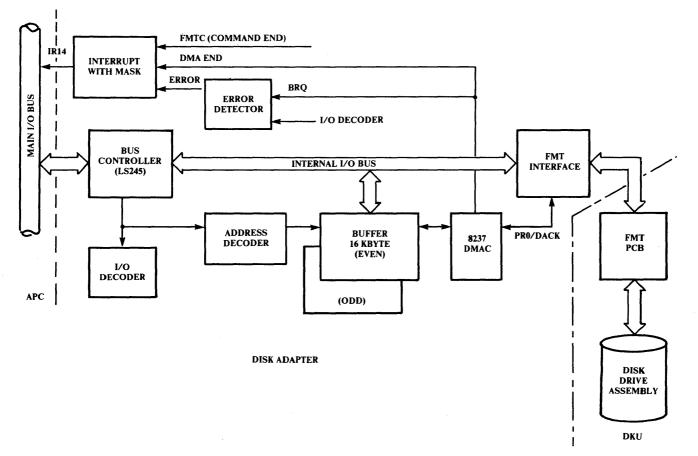

The disk adapter provides the interface and control logic between the APC control unit and the associated DKU attachments (see Figure 1-3). It contains the FMT interface logic and connector, resides in the APC control unit, and consists of the following logic components (see Figure 2-1).

- 8237 DMAC

- 8K Byte Static RAM

- RS422 Formatter Interface

The disk adapter fits into any blank slot in the card cage (mother board) within the APC control unit, and provides the following logic circuits.

- DMA Control Logic

- Error Detect Logic

- I/O Decoder

- Main Bus Control

• Memory Buffer

- FMT Interface Logic

- ace Logic

- Interrupt Logic

#### 2.1.1 Disk Adapter Operational Modes

Functionally the disk operates in two modes.

- a. Internal Bus Mode

- b. Main Bus Mode

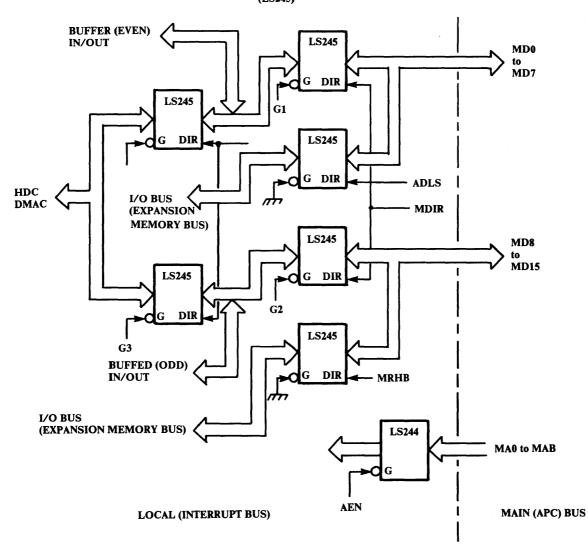

A DISK ADAPTER/DKU BLOCK DIAGRAM

B

DISK ADAPTER BUS CONTROL (LS245)

The internal bus mode performs the read and write operations from the external disk drive through the Format (FMT) control PCB. This mode commences when a disk command is sent to the FMT PCB. Data transfers between the memory buffer in the disk adapter and the FMT PCB in the DKU are completely separated from the main bus in the adapter and operate within the internal bus. Access to the memory buffer, transmission of I/O instructions to the DMA controller and to the FMT PCB are inhibited.

The main access mode accesses data from the RAM in the Disk Adapter.

#### 2.1.2 Disk Adapter Functional Capabilities

This section briefly describes the functional capabilities of the Disk Adapter logic circuits, listed earlier, and shown in the functional block diagram in Figures 2-1 and 2-2.

## 2.1.2.1 DIRECT MEMORY ACCESS CONTROLLER (DMAC DATA TRANSFERS)

DMAC data transfers between the FMT interface and the memory buffer, in demand or single mode, are performed through channel 1 of the DMA controller. In addition, access to the memory buffer and execution of I/O instructions for the DMA controller and FMT interface are inhibited. These operations are detected as errors. All other channels are not used and memory to memory transfers are disallowed.

#### 2.1.2.2 ERROR DETECT LOGIC

The error detect logic monitors the DMAC logic for any possible errors. The error status is sent to the interrupt logic for transmission to the APC control unit where the error status is acted upon accordingly.

Figure 2-2 Buffer Control Block

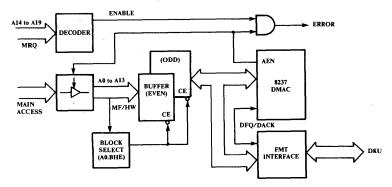

#### 2.1.2.3 DISK ADAPTER FMT INTERFACE LOGIC

The FMT Interface logic within the disk adapter provides the communication link between the disk adapter, specifically the DMA controller, and the FMT PCB. It is connected directly to the format control PCB (3302 FMT) in the DKU (Model APC H-26), and controls the data format to the disk drive.

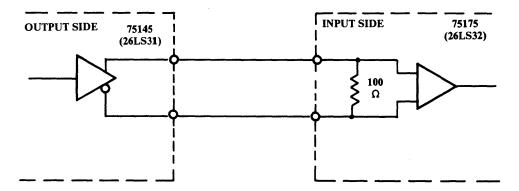

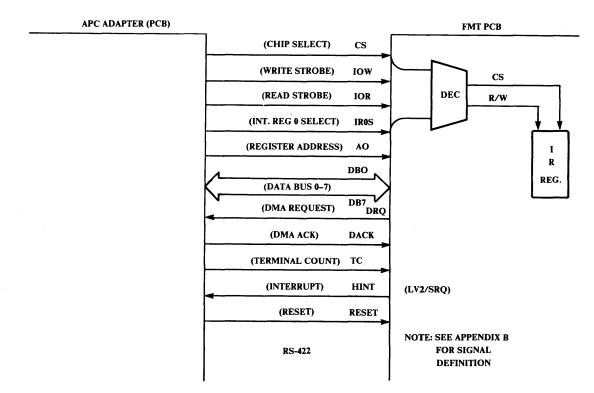

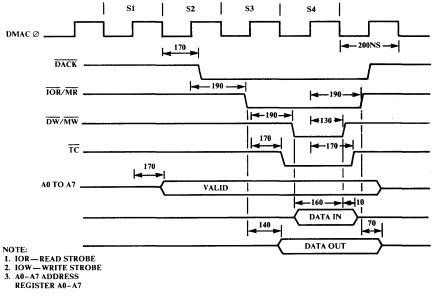

Figures 2-3 and 2-4 show the electrical circuit for the RS422 interface, and Table 2-1 lists the signal-to-pin assignment for the interface connector. In addition, Figures 2-5 and 2-6 show the timing diagrams for the FMT interface and a DMA access operation.

The FMT PCB is seen as an I/O port to the main processor in the APC control unit. This I/O port has three registers, IR0, IR2, and IR3 that are selected by the FMT control lines, and the appropriate register function is also enabled as shown in Table 2-2.

The IR0 register controls the information for an FMT operation.

The IR2 and IR3 registers correspond to the command/status register and parameter/result registers, respectively. For further details refer to FMT in Section 2.2.

DATA TRANSFER LINE FORMS A DIFFERENTIAL TRANSMITTING AND RECEIVING CIRCUIT.

Figure 2-3 Typical Driver/Receiver Circuit

Figure 2-4 Interface Signals (Adapter to FMI)

| PIN NO. | IROS-H (*1)      | POLARITY | DIRECTION |

|---------|------------------|----------|-----------|

| 1<br>26 | GND              |          |           |

| 2<br>27 | IOW-H<br>IOW-L   | -        | <b>→</b>  |

| 3<br>28 | IOR-H<br>IOR-L   | -        | <b>→</b>  |

| 4<br>29 | HDCS-H<br>HDCS-L | -        | <b>_</b>  |

Table 2-1 Interface Connector Signal Pin Assignment

2-6

| PIN NO.  | IROS-H (*1)           | POLARITY | DIRECTION  |

|----------|-----------------------|----------|------------|

| 5<br>30  | TC-H<br>TC-L          | -        |            |

| 6<br>31  | IROS-H (*1)<br>IROS-L | -        | -          |

| 7<br>32  | GND                   |          |            |

| 8<br>33  | AO-H<br>AO-L          | -        | . <b>→</b> |

| 9<br>34  | RESET-H<br>RESET-L    | -        | <b>→</b>   |

| 10<br>35 | DACK-H (*2)<br>DACK-L | -        | <b>→</b>   |

| 11<br>36 |                       |          |            |

| 12<br>37 | GND                   |          |            |

| 13<br>38 | DB7-H<br>DB7-L        | +        | <br>       |

| 14<br>39 | DB6-H<br>DB6-L        | +        | →<br>←     |

| 15<br>40 | DB5-H<br>DB5-L        | +        | →<br>←     |

| 16<br>41 | DB4-H<br>DB4-L        | +        | →<br>←     |

| 17<br>42 | DB3-H<br>DB3-L        | +        | →<br>-     |

Table 2-1 Interface Connector Signal Pin Assignment

| PIN NO.  | IROS-H (*1)      | POLARITY | DIRECTION |

|----------|------------------|----------|-----------|

| 18<br>43 | DB2-H<br>DB2-L   | +        | →<br>↓    |

| 19<br>44 | DB1-H<br>DB1-L   | +        | →<br>←    |

| 20<br>45 | DB0-H<br>DB0-L   | +        | →<br>←    |

| 21<br>46 |                  |          |           |

| 22<br>47 |                  |          |           |

| 23<br>48 | DRQ-H<br>DRQ-L   | + .      | -         |

| 24<br>49 | HINT-H<br>HINT-L | -        | -         |

| 25<br>50 |                  |          |           |

Table 2-1 Interface Connector Signal Pin Assignment

Tl Т2 Т3 **T4** I. I. 1 1 CPUØ \_\_\_\_ 200NS \_\_\_\_\_ **|**← 110 → | A0 to A7 VALID 10 IOR/IOW -35 10 ---IRG/MDCS . 10 DATA IN 20 10 -DATA OUT NOTE: 1. IOR—READ STROBE 2. IOW—WRITE STOCK 3. A0-A7 ADDRESS **REGISTER A0-A7**

#### Figure 2-5 FMT Interface Timing

(1) IR REGISTER ACCESS

Figure 2-6 DMA Access Timing

| Table 2-2 TWIT Control Line Register Select Function |   |                                         |   |        |          |               |  |  |

|------------------------------------------------------|---|-----------------------------------------|---|--------|----------|---------------|--|--|

|                                                      |   |                                         |   |        |          |               |  |  |

| REGISTER<br>SELECT HARD DISK<br>CONTROLLER<br>(HDC)  |   | CONTROLLER ADDRESS STROBE STROBE SELECT |   | SELECT | FUNCTION |               |  |  |

| IR3 READ                                             | 0 | 1                                       | 0 | 1      | 1        | Result Status |  |  |

| IR3 WRITE                                            | 0 | 1                                       | 1 | 0      | 1        | Parameter     |  |  |

| IR2 READ                                             | 0 | 0                                       | 0 | 1      | 1        | Status Reg.   |  |  |

| IR2 WRITE                                            | 0 | 0                                       | 1 | 0      | 1        | Command Reg.  |  |  |

| IR2 READ                                             | 0 | 1                                       | 0 | 1      | 0        | Info. Line    |  |  |

| IR0 WRITE                                            | 0 | 1                                       | 1 | 0      | 0        | Info. Line    |  |  |

Table 2-2 FMT Control Line Register Select/Function

0 — Designates active state of selected signal or register. For example, HDC = 0 and IOR (Read Strobe) = 0, HDC (FMTC) selected and Interrupt Register 3 (IR3 Read) addressed to read the result status.

#### 2.1.2.4 INTERRUPT LOGIC

The interrupt logic processes FMT commands, DMA operations and the current error status for transmission to the APC control unit.

#### 2.1.2.5 I/O DECODER

The I/O decoder monitors the bus controller (LS245) for I/O commands. The resulting command is returned to the bus controller for the appropriate action.

#### 2.1.2.6 MAIN BUS CONTROLLER

The main bus controller (LS245) processes information from or to the internal bus (see Figure 2-1), the main bus in the APC control unit, the I/O decoder, address decoder, memory buffer and the FMT interface.

Two Programmable Array Logic (PAL), also known as the Programmable Logic Array (PLA), chips are used to decode I/O instructions from the main processor in the APC control unit and to control the bus interface.

#### 2.1.2.7 MAIN PROCESSOR INTERRUPTS (INT) FROM THE APC

Interrupts to the main processor in the APC control unit are ORed with a mask designator through channel 14 in the disk adapter. Individual masking is possible with each interrupt. I/O instructions for read interrupt commands are incorporated prior to masking.

Interrupts

- DMIN This interrupt occurs when a DMA data transfer between the FMT and the memory buffer is finished in a specified number of counts.

- HDIN This interrupt designates the completion of a command to the FMT (HDIN = LV2 = CE + SRQ).

- MDER—Denotes error, signifying a memory access operation to the memory buffer from the APC control unit during a DMA operation.

- HDER Denotes an error when a command is issued to HDC during an FMT command (The HDC is called the Hard Disk controller which is another name for the FMT controller described in Section 2.2).

#### 2.1.2.8 MEMORY BUFFER

Memory is an 8K buffer that consists of four NEC 4016-3  $2K \times 8$  bit static RAMs. In the main access mode the buffer is composed of odd and even numbered blocks and is common to the APC control unit. Address assignment is fixed at AC002 to AFFFF.

Under internal mode, the memory address is continuously assigned.

Data transfer between the buffer and FMT interface is controlled by the DMA controller. Access from the APC control unit is prohibited. If accessed by the APC control unit an error is flagged.

#### 2.1.3 Programming Considerations

The programming considerations consist of a working knowledge of the main (APC) processors ability to access the DMA controller, memory buffer, interrupt registers and other related logic circuits in the disk adapter and HDC (or FMT controller).

Included in the programming considerations are the I/O address functions and bit maps, summarized in Section 2.1.3.2, all I/O byte operations to the main processor, and the word or byte formats to access the memory buffer. The following sections briefly describe the above operations and include additional operations, the knowledge of which, is recommended for successful programming of the HDC.

#### 2.1.3.1 FMT I/O AND PROCESSOR MEMORY ACCESSIBILITY

In an HDC R/W data operation, during a DMA data transfer cycle, I/O and memory access operations from the main processor are not allowed. This action is because the disk adapter and main processor are not in sync with each other. Error detection logic is included to flag the respective HDC operation as an I/O access error (HDER) to the HDC, or a DMA memory access error (MAER) within the adapter. The following briefly describes the above error conditions and provides additional FMT/DMA operations.

1. FMT Complete Confirmation (Read Status)

A read status register operation during an HDC operation generates an HDER error. To avoid this, completion of an FMT operation must be verified as follows.

- With a read interrupt from the FMT.

- Confirmation of an on-going HDC operation with a HDEX flag. This flag is set with a write command to FMT and is cleared by a seek Command End (CEL or CEH) or a Sense Interrupt Status Request (SRQ) command from the FMT.

- 2. FMT Operation Without a DMA Operation (for example, Seek Command).

- Memory buffer accessability and I/O command operation to the DMAC allowed.

- FMT I/O command allowed.

- HDER generated with an I/O write command.

- 3. HDER Generation

- Issuance of a DMAC/FMT I/O command during a DMA data transfer.

- A command sent to the HDC before the HDC completes an operation.

- 4. MAER Generation—Access to memory buffer during a DMA data transfer operation.

#### 2.1.3.2 I/O COMMANDS

This section categorizes the I/O commands and provides the appropriate commands, codes and other related information in Tables 2-3 through 2-7. Included are notes that briefly describe the operation and purpose of each command and related function.

| CATE-            | I/O COMMAND DATA FIELD (HIGH BYTE)                                                                                                                                              |                                                                            |                                          |                        |                                     |                        |                                          |                                                  |                             |                                                 |                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------|------------------------|-------------------------------------|------------------------|------------------------------------------|--------------------------------------------------|-----------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------|

| GORY             | NAME                                                                                                                                                                            | ADDRESS                                                                    | D15                                      | D14                    | D13                                 | D12                    | D11                                      | D10                                              | D9                          | D8                                              | FUNCTION                                                                                        |

| DMA<br>Note<br>1 | CHANNEL 1<br>DMA ADR. L<br>DMA ADR. H<br>DMA Count. L<br>DMA Count. H<br>Status<br>Write CMD<br>Register Request<br>Single Mask<br>Mode Register<br>Clear F/F<br>TEMP. Register | A3<br>A3<br>93<br>93<br>A9<br>A9<br>99<br>AB<br>99<br>AB<br>9B<br>AD<br>9D | A7<br>A15<br>C7<br>C15<br>R03<br>KS<br>— | A6<br>A14<br>C6<br>C14 | A5<br>A13<br>C5<br>C13<br>R01<br>WS | A4<br>A12<br>C4<br>C12 | A3<br>A11<br>C3<br>C11<br>TC3<br>TM<br>— | A2<br>A10<br>C2<br>C10<br>TC2<br>LE<br>RE<br>MSK | A1<br>A9<br>C1<br>C9<br>TC1 | A0<br>A8<br>C0<br>C8<br>TC0<br>MM<br>CS0<br>CS0 | Read/Write<br>(Note 3)<br>Read<br>(Note 2)<br>Write<br>Write<br>Write<br>Write<br>Write<br>Read |

|                  | Master Clear                                                                                                                                                                    | 9D                                                                         |                                          |                        |                                     |                        |                                          |                                                  |                             |                                                 | Write                                                                                           |

|                  | All Make                                                                                                                                                                        | 9F                                                                         |                                          |                        |                                     |                        | MB3                                      | MB2                                              | MB1                         | MB0                                             | Write                                                                                           |

Table 2-3 I/O Commands (DMA)\*

\* See (8237) DMA LSI Functional Specifications for details.

NOTES:

- 1. All unused channels (CH) except CH1 must be masked.

- 2. Data for command register is set to all zeroes.

- 3. DMA address bits, A15 and A14, are ignored if memory buffer is 16 KB or less.

|                        |                             |         | 1401 | C <u>2</u> -4 |      | mman |     |     | 1)  |      | · ·       |

|------------------------|-----------------------------|---------|------|---------------|------|------|-----|-----|-----|------|-----------|

| CATE-<br>GORY          | I/O COMMAND                 |         |      |               |      |      |     |     |     |      |           |

|                        | NAME                        | ADDRESS | D7   | D6            | D5   | D4   | D3  | D2  | D1  | D0   | FUNCTION  |

| HDC<br>(3302<br>FMT)   | Result Status               | A0      | D7   | D6            | D5   | D4   | D3  | D2  | D1  | D0   | Read (R)  |

|                        | Parameter                   | A0      | D7   | D6            | D5   | D4   | D3  | D2  | Dl  | D0   | Write (W) |

|                        | Status                      | 92      | CB   | CEH           | CEL  | SRQ  | RBQ | IER | NCI | DBQ  | Read (R)  |

|                        | Write CMD                   | 92      | CC4  | CC3           | CC2  | CC1  | CC0 | UA2 | UAI | UA0  | Write (W) |

| 3302<br>FMT<br>(Notes) | Interface<br>Register (IR)0 | A2      |      | СВ            | DACK | _    | _   | CE  | LV2 | SRQ  | Read (R)  |

|                        | IR0                         | A2      | INTI | CLDB          | RSTR | CLCE | 0   | EOP | 0   | HSR0 | Write (W) |

Table 2-4 I/O Command (HDC/FMT)

NOTES:

1. See 3302 FMT firmware functional specifications for detail. The FMT has the equivalent HDC I/O commands installed.

2. During a DMA operation an HDER is generated when the 3302 FMT is accessed with the execution of a format control operation.

3. LV2 interrupt bit for an IR0 read is the same as the HDIN interrupt bit for a read INT. command.

|                   |                    |         | 1 44 |    | 5 1/01 | - viiiiiui |      |      | ·)   |    |               |

|-------------------|--------------------|---------|------|----|--------|------------|------|------|------|----|---------------|

| CATE-<br>GORY     |                    |         |      |    |        |            |      |      |      |    |               |

|                   | NAME               | ADDRESS | D7   | D6 | D5     | D4         | D3   | D2   | D1   | D0 | FUNCTION      |

| Reset<br>(Note 1) | H/W Reset<br>(RST) | 94      |      |    |        |            |      |      |      |    | RST Write (W) |

| INT<br>Note<br>2  | INT Reset          | 96      |      |    |        |            | HDER | MAER | DMIN |    | RST Read (R)  |

|                   | INI/HDEX           | 96      |      |    | HDEX   | HDER       | MAER | DMIN | HDIN |    | Read (R)      |

|                   | INI Mask Set       | 98      |      |    |        |            | IDER | DMIN | HDIN |    | Set INT MSK   |

#### Table 2-5 I/O Command (RESET/INT)

NOTES:

1. H/W RESET command resets the hardware.

2. Interrupt RESET command data bus bit assignment.

#### **DATA BUS**

#### DESCRIPTION

| BIT | STATUS |                                   |

|-----|--------|-----------------------------------|

| D0  | DMIN   | Interrupt reset by TC during DMA. |

| D1  | MAER   | Reset memory access error.        |

| D2  | HDER   | Reset I/O command timing error.   |

| DATA BUS |        |                         |

|----------|--------|-------------------------|

| BIT      | STATUS | DESCRIPTION             |

| D0       | x      | Don't care              |

| D1       | HDIN   | HDC Interrupt           |

| D2       | DMIN   | TC Interrupt in DMA     |

| D3       | MAER   | Memory Access Error     |

| D4       | HDER   | I/O Timing Error        |

| D5       | HDEX   | HDC In Operation (Note) |

Table 2-6

Read INT/HDEX Command\*

\* The read INT/HDEX I/O command is used to sense an interrupt and an HDC execution.

# NOTE:

The HDEX flag is set when an FMT command write is issued, and reset by an HDC interrupt command complete (CEL, CEH, or SRQ) signal.

| DATA BUS |        |                       |

|----------|--------|-----------------------|

| BIT      | STATUS | DESCRIPTION           |

| D1       | HDIN   | HDC Interrupt Mask    |

| D2       | DMIN   | DMA TC Interrupt Mask |

| D3       | IOER   | MAER and HDER Mask    |

Table 2-7 INT Mask Set I/O Commands

NOTES:

1. Set mask logic "0" (logic "1" nonmask).

2. All mask set at initial reset time.

# 2.2 3302 FMT DISK DRIVE CONTROLLER

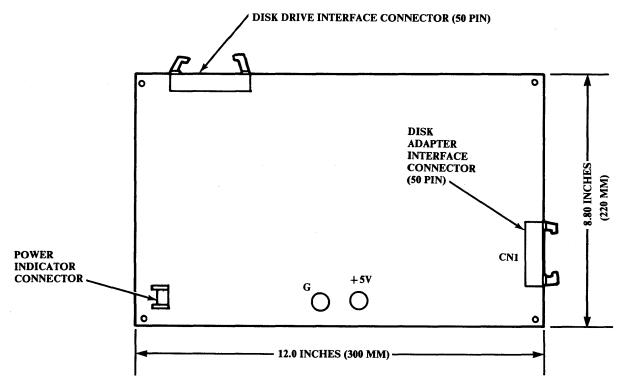

The 3302 FMT disk drive controller, also called the Hard Disk Controller (HDC) or FMT PCB, resides in the model APC-H26 stand-alone DKU and provides the interface and control signals to the disk drive assembly within the stand-alone DKU and the disk adapter in the APC control unit (see Figure 2-7). Also, the FMT PCB provides the interface to the disk drive in the expansion DKU when included in the system. The physical dimensions and attached interface and power connector placements for the FMT PCB are shown in Figure 2-8. The 3302 FMT controller is composed of four sandwiched layers, including the signal ground and dc power plains. The major logic elements are as follows.

- Z80 compatible microprocessor (µPD780).

- 8K RAM of local memory.

- 2K ROM for disk drive firmware.

- D8237 DMA controller that interfaces with the disk adapter, local memory and the disk drive.

- D8255AC Programmable I/O device designed to control the transmission of the disk drive status, the device address/head address, and the step pulse for a seek operation.

- µPD3302 disk control LSI which is controlled by a subcommand sequencer. It (LSI) is intended to perform a serialize/deserialize operation on data to or from the disk drive and to modulate/demoduolate the MFM recorded data.

- 8065 BEP LSI intended to perform polynomial functions and to generate correctable 1 bit burst type errors.

DPB: DISK PROCESSOR BLOCK HIB: HOST INTERFACE BLOCK SCB: SUBCOMMAND BLOCK

Figure 2-8 FMT PCB Physical Configuration

# 2.1.1 FMT Disk Operations

This section summarizes the functional capabilities of the FMT PCB operations. A more detailed description of each operation is provided in subsequent sections.

- 1. Performs seek operations to read or write data on a disk by moving the arm assembly (Read/Write heads) to the specified disk address.

- 2. Recalibrates the disk at head zero, cylinder zero.

- 3. Performs a read address seek operation to the specified disk address for transmission of the address to main memory.

- 4. Reads up to one cylinder of data from the DKU for transmission to main memory.

- 5. Writes up to one cylinder of main memory data into the DKU.

- 6. Verifies the transmission of up to a cylinder of data by checking the CHECK BYTE.

#### 2.2.2 Firmware Overview

This section briefly describes the firmware characteristics and summarizes the firmware operation.

# 2.2.2.1 FIRMWARE CHARACTERISTICS

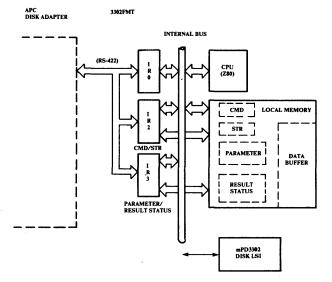

Firmware for the FMT PCB resides in the Z80 microprocessor, also called the Central Processing Unit (CPU), and provides the control procedures for all read/ write and seek operations to the disk drive. It performs these procedures by decoding the main processor I/O instructions from the APC disk adapter. Firmware visibility with the adapter is provided by three registers; IR0, IR2, and IR3, all of which, reside on the FMT PCB (see Figure 2-9 and Table 2-2).

The transfer of data to form the command status and parameter/result status between the adapter and FMT is performed in the IR2 and IR3 registers (see Table 2-8). That is, initially, a disk command and its parameters are set in the IR2 and IR3 registers with an I/O command. The FMT firmware is then started and the data is stored in local memory. The Z80 CPU accepts and executes the I/O command. On completion the status is set in the IR2 and IR3 registers where they are sent to the main memory processor through the disk adapter. The IR0 register is used with firmware to set the command and receive the status (see Tables 2-9 through 2-11). The quantity of data transferred from or to the disk adapter corresponds to the number of sectors specified in the parameter.

Figure 2-9 Firmware Hardware Interface

| FMT COMMAND        | R/W | I/O<br>ADDRESS | 3302 FMT  |

|--------------------|-----|----------------|-----------|

| Result Status Read | R   | AO             | IR3 Read  |

| Parameter Write    | w   | AO             | IR3 Write |

| Status Read        | R   | 92             | IR2 Read  |

| Command Write      | W   | 92             | IR2 Write |

Table 2-8 FMT I/O Read/Write (Status) Commands

Table 2-9 FMT I/O Commands (RD/WR)

|           |     | I/O     |                  | D                | ATA                   | BUS              | (LO | W PA        | RT)         |                  |

|-----------|-----|---------|------------------|------------------|-----------------------|------------------|-----|-------------|-------------|------------------|

| COMMAND   | R/W | ADDRESS | D7               | D6               | D5                    | D4               | D3  | D2          | D1          | D0               |

| IRO Read  | R   | A2      |                  | C<br>B           | D<br>A<br>C<br>K<br>H |                  |     | C<br>E      | L<br>V<br>2 | S<br>R<br>Q      |

| IR0 Write | W   | A2      | I<br>N<br>T<br>I | C<br>L<br>D<br>B | R<br>S<br>T<br>R      | C<br>L<br>C<br>E | 0   | E<br>O<br>P | 0           | H<br>S<br>R<br>Q |

| DATA | NAME       | DESCRIPTION                                                                                            | REMARKS                                                                          |

|------|------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| D0   | HSRQ       | SRQ interrupt mask                                                                                     |                                                                                  |

| D1   | 0          | Must be zero                                                                                           |                                                                                  |

| D2   | ЕОР        | Notifies completion of<br>the access to IR2/IR3 in<br>the command set or sta-<br>tus receive procedure | After setting this bit,<br>procedure completes 2<br>more accesses to<br>IR2/IR3. |

| D3   | 0          | Must be zero                                                                                           |                                                                                  |

| D4   | CLCE       | Interrupt LV2 reset                                                                                    |                                                                                  |

| D5   | RSTR       | Request start of the result status receiving procedure.                                                |                                                                                  |

| D6   | CLDB       | Request start of disk command set procedure.                                                           |                                                                                  |

| D7   | Initialize | Reset for 3302 FMT. Set<br>'ON', next 'OFF'. This<br>signal must be more than<br>$2\mu$ sec.           | AUX command corresponds to RST.                                                  |

# Table 2-10 IR0 Write

| DATA | NAME     | DESCRIPTION                                                                                                                                                                      | REMARKS                                                                    |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| D0   | SRQ      | Seek end, equipment<br>check, ready change: '1'<br>Issue of sense interrupt<br>request command<br>requested. HSRQ mask-<br>ing constitutes a factor<br>in the generation of LV2. | The same as bit<br>4 of STR (IR2, read)                                    |

| Dl   | LV2      | Interrupt signal                                                                                                                                                                 | LV2 = HDIN<br>= CE + SRQ•HSRQ                                              |

| D2   | CE       | End of disk command: '1'<br>Next command setting<br>or CLCE setting: '0'<br>LV2 interrupt factor.                                                                                | CE = CEL + CEH<br>corresponds to bit 6<br>(CEH) and bit 5 (CEL)<br>of STR. |

| D3   |          | Don't care                                                                                                                                                                       |                                                                            |

| D4   | <u> </u> | Don't care                                                                                                                                                                       |                                                                            |

| D5   | DACKH    | '1': CLDB disk com-<br>mand setting mode and<br>RSTR result status<br>receiving mode are<br>started and internal<br>DMA is started for data<br>transfer via IR3 register.        | '1' is given on the com-<br>mand run of read/write<br>data also.           |

| D6   | CB       | Formatter busy.                                                                                                                                                                  | The same as bit 8 of STR.                                                  |

| D7   |          | Don't care                                                                                                                                                                       |                                                                            |

Table 2-11 IR0 Read

# 2.2.2.2 FIRMWARE OPERATIONAL OVERVIEW

There are six operational phases performed by internal firmware. They consist of a Seek Command phase, an Idle phase, a Clear Data Buffer (CLDB) phase, a Run phase, a Control End (CE) phase, and a Result Status Read (RSTR) phase. Each is briefly described below.

| 1. | Seek Command          | - Denotes a seek operation occurred in the idle state<br>and sets LV2 (SRQ) interrupt (usually at end of seek).         |

|----|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| 2. | Idle phase            | - Waits for, accepts, and processes seek commands and associated command parameters.                                    |

| 3. | CLDB phase            | -Stores the command and command parameters and sequence steps for the next phase.                                       |

| 4. | Run phase             | - Executes the command, processes the applicable data, and sets the LV2 (CE) interrupt at the end of the command cycle. |

| 5. | Control End (CE phase | )—Status read into IR0/IR2.                                                                                             |

6. Result Status — Result status read into IR3. Read (RSTR)

#### 2.2.2.3 FIRMWARE START UP

The FMT firmware start up procedure is the same as that for the Hard Disk Controller (HDC) LSI. However, the start up I/O instruction to set the command and receive the status differ somewhat, and must be performed as shown in Figures 2-10 and 2-11 and described below.

- 1. Command Set

- a. Check Status Register for Controller Busy (CB).

- If busy, wait.

- If not busy continue with step b.

- b. Initiate Clear Data Buffer (CLDB) command through the auxiliary command register.

- c. Check status register for DACKH signal being on.

- If on, continue with step d.

- If off, wait.

- d. Send first parameter to Data Buffer Register.

- e. Send each additional parameter, one after the other to the data buffer register. There is a minimum of 2 between transfers.

- f. Before sending the last parameter, initiate an End of Process (EOP) command through the auxiliary command register.

- g. After last parameter is sent, send command to the command register.

- h. Check Status Register for DACKH to be off.

- i. When DACKH is off, The Central Processing Unit (CPU) can perform other operations, because HDC will signal when it is completed by sending an interrupt.

COMMAND RUN

\*2 HDIN = LV2 = CE + SRQ\*HSRQ

- 2. Receive Result Status

- a. Wait for interrupt to occur.

- b. Read interrupt register to determine what type of interrupt occurred.

- c. If an HDC interrupt has occurred, read the status register.

- d. If status/command indicates that it is necessary to read the request Result Status Read (RSTR) command through the auxiliary command register.

- e. Check status to see if DACKH is on.

- If on, continue with step b.

- If off, wait.

- f. Continue to read additional status, one after the other, as the command requires. A minimum of 2 is required between transfers.

- g. After last parameter is read, check status register for DACKH signal to be off. Indicates that the procedure is completed.

- h. Proceed to next command.

# 2.2.2.4 FIRMWARE FUNCTIONAL NOTATIONS

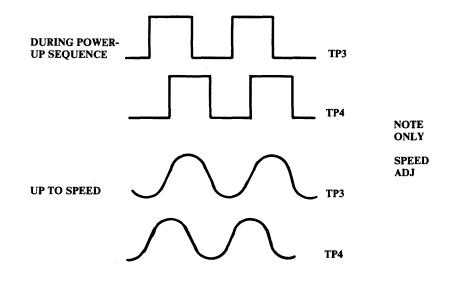

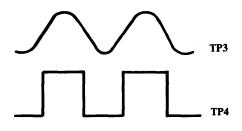

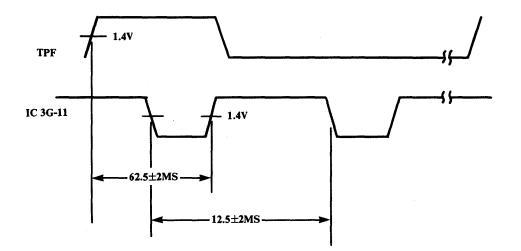

This section highlights the major DKU operations that a user should be aware of to understand the operation of the hard disk. The user should reference Figure 2-12 through 2-17 and Tables 2-12 through 2-18. The figures provide a flowchart of the Firmware operations, the sector format, and the appropriate timing diagrams. The tables provide the command code (Bits D7 through D4) for each command, the command name and resultant parameters, the appropriate parameters for each command, and tabulates the status in the respective status registers. Additional information is provided in Section 2.2.3.

1. A cylinder seek occurs with a Power On Reset operation or with a reset I/O command from the disk adapter (see Figure 2-12).

A recalibrate operation is performed after every reset command.

2. After IRQ CLDB is set in a command set operation, the command operation requires a maximum delay of 50 secs for DACKH to turn on, after which, the command set operation continues. After EOP sets, the command set operation ends with two access operations (last parameter and command) and DACKH turns off.

- 3. The receive status operation also requires a maximum delay of 50 secs for DACKH to turn on. After RSTR sets, the operation is the same as described in step 2 above. With the number of status results determined by an execute I/O command, DACKH turns off after the final status result is read. When the number of read status is smaller than the number of result status, stalls occur causing a wait state.

- 4. In some cases DACKH turns on during the execution of a read/write data command.

- 5. The command set and receive status operations cannot be reset once they are in operation.

- 6. In seek and recalibrate command operations an SRQ interrupt occurs after Control End (CE) is on resulting in a new time difference between the interrupt and CE. A new command can be executed with CE on during any SRQ occurence.

- 7. In systems equipped with two or more DKUs a new command to the second DKU is permissible as the first DKU is performing a seek operation. An SRQ interrupt is sent when the new command ends, but the SRQ status is held until this time. However, the SRQ status is reset if the DKU that ended a seek command commences another command before accepting the SRQ status. Accordingly, a seek command can be sent to the same DKU after the SRQ status is received.

Figure 2-12 FMT Firmware Flowchart

Figure 2-13 Sector Map (Disk)

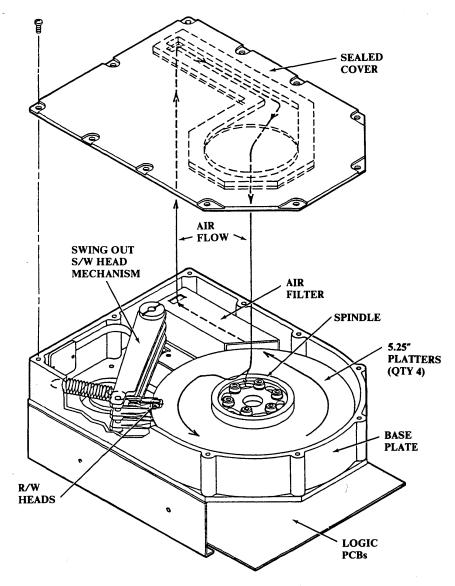

Figure 2-14 Read/Write Command Timing

Figure 2-15 Seek/Recalibrate Timing

# **PCB/Structure Functionality**

SENSE UNIT STATUS

Figure 2-17 Sense Unit Status

|                  | OPERATIONAL              | COMMAND               | Data Register (Low Byte)**                                                           |                                     |

|------------------|--------------------------|-----------------------|--------------------------------------------------------------------------------------|-------------------------------------|

| COMMAND          | PHASE                    | BIT $A0 = X^*$        | D7 D6 D5 D4 D3 D2 D1 D0                                                              | REMARKS                             |

| Recali-<br>brate | Command                  | 0                     | 0 1 0 1 0 UA                                                                         | Command and<br>unit address (UA)    |

|                  | Result 0 Status Register |                       | Status Register<br>(STR)                                                             |                                     |

|                  | Command                  | 0                     | 0 1 1 0 1 UA                                                                         | Command and unit address            |

| Seek             |                          | 1                     | Physical Cylinder Number<br>Physical Cylinder Number                                 | High Byte (PCNH)<br>Low Byte (PCNL) |

|                  | Result                   | 0                     | Status Register                                                                      | STR                                 |

|                  | Command                  | 0                     | 0 1 1 1 0 UA                                                                         | Command and<br>unit address         |

| Write ID         |                          | 1<br>1<br>1<br>1<br>1 | Physical Head Number<br>Sector Count<br>Data Pattern<br>Gap Length 1<br>Gap Length 3 | PHN<br>SCNT<br>DPAT<br>GPL1<br>GPL3 |

|                  | Result                   | 0<br>1                | Status Register<br>End Status<br>Sector Count                                        | STR<br>EST<br>SCNT                  |

|                  | Command                  | 0                     | 1 0 0 1 0 UA                                                                         | Command and unit address            |

| Read ID          |                          | 1<br>1                | Physical Head Number<br>Sector Count                                                 | PHN<br>SCNT                         |

|                  | Result                   | 0<br>1<br>1           | Status Register<br>End Status<br>Sector Count                                        | STR<br>EST<br>SCNT                  |

Table 2-12 Commands/Status Results

| COMMAND   | OPERATIONAL<br>PHASE                                                                                                                                                                                                  | $\begin{array}{c} \text{COMMAND} \\ \text{BIT } A_0 = X^* \end{array}$ | DATA REGISTER (LOW BYTE)**<br>D7 D6 D5 D4 D3 D2 D1 D0                                                                                                | REMARKS                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|           |                                                                                                                                                                                                                       | 0                                                                      | 1 0 1 1 X UA                                                                                                                                         | Command and<br>unit address (UA)                                               |

| Read Data | Command                                                                                                                                                                                                               | 1<br>1<br>1<br>1                                                       | Physical Head Number<br>Logical Cylinder Number<br>Logical Cylinder Number<br>Sector Count                                                           | PHN<br>High Byte (LCNH)<br>Low Byte (LCNL)<br>SCNT                             |

| Ntau Data | 1     Status Register       1     End Status       1     Physical Head Number       1     Logical Cylinder Number       1     Logical Head Number       1     Logical Sector Number       1     Logical Sector Number |                                                                        | End Status<br>Physical Head Number<br>Logical Cylinder Number<br>Logical Cylinder Number<br>Logical Head Number                                      | STR<br>EST<br>PHN<br>High Byte (LCNH)<br>Low Byte (LCNL)<br>LHN<br>LSN<br>SCNT |

|           |                                                                                                                                                                                                                       | 0                                                                      | 1 1 0 0 X UA                                                                                                                                         | Command and UA for CMD set.                                                    |

| Check     | Command                                                                                                                                                                                                               | 1<br>1<br>1<br>1<br>1<br>1                                             | Physical Head Number<br>Logical Cylinder Number<br>Logical Cylinder Number<br>Logical Head Number<br>Logical Sector Number<br>Sector Count           | PHN<br>High Byte (LCNH)<br>Low Byte (LCNL)<br>LHN<br>LSN<br>SCNT               |

|           | Result                                                                                                                                                                                                                | 0<br>1<br>1<br>1<br>1<br>1<br>1                                        | Status Register<br>End Status<br>Physical Head Number<br>Logical Cylinder Number<br>Logical Cylinder Number<br>Logical Sector Number<br>Sector Count | STR<br>EST<br>PHN<br>High Byte (LCNH)<br>Low Byte (LCNL)<br>LSN<br>SCNT        |

| Table 2-12 | Commands/ | 'Status | Results | (cont'd) |

|------------|-----------|---------|---------|----------|

|------------|-----------|---------|---------|----------|

| COMMAND                 | OPERATIONAL<br>PHASE | $\begin{array}{c} \text{COMMAND} \\ \text{BIT } A_0 = X^* \end{array}$ | DATA REGISTER (LOW BYTE)**<br>D7 D6 D5 D4 D3 D2 D1 D0                                                                                                                           | REMARKS                                                                                                      |

|-------------------------|----------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|                         |                      | 0                                                                      | 1 1 1 1 X UA                                                                                                                                                                    | Command and<br>unit address (UA)                                                                             |

| Write<br>Data           | Command              | 1<br>1<br>1<br>1<br>1<br>1                                             | Physical Head Number<br>Logical Cylinder Number 1<br>Logical Cylinder Number 2<br>Logical Head Number<br>Logical Sector Number<br>Sector Count                                  | PHN<br>LCN 1<br>LCN 2<br>LHN<br>LSN<br>SCNT                                                                  |

|                         | Result               | 0<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                   | Status Register<br>End Status<br>Physical Head Number<br>Logical Cylinder Number 1<br>Logical Cylinder Number 2<br>Logical Head Number<br>Logical Sector Number<br>Sector Count | STR<br>EST<br>PHN<br>High Byte (PCNH)<br>Low Byte (PCNL)<br>LHN<br>LSN<br>SCNT                               |

| Sense                   | Command              | 0                                                                      | 0 0 0 1 X X X X                                                                                                                                                                 | For CMD set                                                                                                  |

| Interrupt<br>Status     | Result               | 0<br>1                                                                 | Status Register<br>Interrupt Status                                                                                                                                             | STR<br>IST                                                                                                   |

|                         |                      | 0                                                                      | 0 0 1 1 X UA                                                                                                                                                                    | Command and<br>unit address (UA)                                                                             |

| Sense<br>Unit<br>Status | Command              | 1<br>1                                                                 | Status Number n<br>Status Number n                                                                                                                                              | STN n<br>STN n<br>N=1: Summary Status<br>=2: Detailed Status<br>(HDC Detail 6)<br>Set: Status number<br>only |

|                         | Result               | 0<br>1<br>1                                                            | Status Register<br>Unit Status n<br>Unit Status n                                                                                                                               | STR<br>USTn n=same as<br>USTn above                                                                          |

| Table 2-12 | Commands/Status | <b>Results</b> ( | (cont'd) |

|------------|-----------------|------------------|----------|

|------------|-----------------|------------------|----------|

|                 | OPERATIONAL | COMMAND                         | DATA REGISTER (LOW BYTE)**                                                                                 |                                                                          |  |  |  |

|-----------------|-------------|---------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

| COMMAND         | PHASE       | BIT $A_0 = X^*$                 | D7 D6 D5 D4 D3 D2 D1 D0                                                                                    | REMARKS                                                                  |  |  |  |

| Invalid         | Command     | 0                               | All Zeroes                                                                                                 | Command                                                                  |  |  |  |

| Invalue         | Result      | 0                               | Status Register                                                                                            | STR (60)                                                                 |  |  |  |

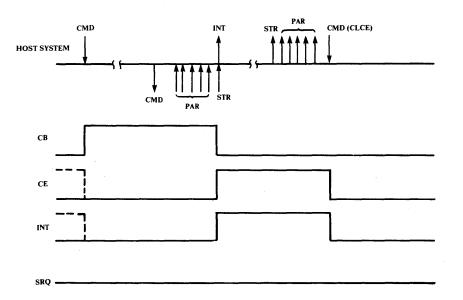

|                 | Command     | 0                               | 0 1 0 0 X X X X                                                                                            | For CMD set                                                              |  |  |  |

| Detect<br>Error | Result      | 0<br>1<br>1<br>1<br>1<br>1<br>1 | Status Register<br>Error Address<br>Error Address<br>Error Pattern 1<br>Error Pattern 2<br>Error Pattern 3 | STR<br>High Byte (ADRH)<br>Low Byte (ADRL)<br>EPAT 1<br>EPAT 2<br>EPAT 3 |  |  |  |

Table 2-12 Commands/Status Results (cont'd)

\* A<sub>0</sub>=0—Command Register or status register access. A<sub>0</sub>=1—Parameter or result status access.

\*\* Data register bits D7 through D4—command code.

| COMMAND                           | PARAMETERS                               |           |  |  |  |  |

|-----------------------------------|------------------------------------------|-----------|--|--|--|--|

|                                   | NAME                                     | HEX VALUE |  |  |  |  |

| SEEK                              | Present Cylinder Number High (PCNH) Byte | 0         |  |  |  |  |

|                                   | Present Cylinder Number Low (PCNL) Byte  | 00 to B4  |  |  |  |  |

| Write ID<br>Write Data<br>Read ID | Present Head Number (PHN)                | 00 to 07  |  |  |  |  |

| Read Data<br>Check                | Sector Count (SCNT)                      | 00 to FF  |  |  |  |  |

|                                   | Data Pattern (DPAT)                      | Any       |  |  |  |  |