# Ontel OP-1/R

## **Reference Manual**

# OP-1/R

OP-1/R

## REFERENCE MANUAL

ONTEL CORFORATION 250 Crossways Park Drive Woodbury, N.Y. 11797

June 12, 1978

## REFERENCE MANUAL

## TABLE OF CONTENTS

SECTION

## TITLE

| lR  | Introduction                                               |

|-----|------------------------------------------------------------|

| 2R  | System Architecture                                        |

| 3R  | Central Processor Unit and I/O Bus                         |

| 4R  | Interrupt Controller                                       |

| 5R  | Fixed Data Switches                                        |

| 6R  | Keyboard and Real Time Clock                               |

| 7R  | Asynchronous I/O Adapter                                   |

| 8R  | Parallel Output Printer Adapter/<br>Parallel Input Adapter |

| 9R  | Display Microprocessor and CRT                             |

| 10R | Alternate I/O Adapter                                      |

| 11R | Word Processing Display<br>Microprocessor and CRT          |

| 12R | Synchronous I/O Adapter                                    |

| 13R | Input/Output Microprocessor                                |

## APPENDIX

| Rl | Available Memory Configurations  |

|----|----------------------------------|

| R2 | Instruction Set Numerical Order  |

| R3 | Instruction Set Functional Order |

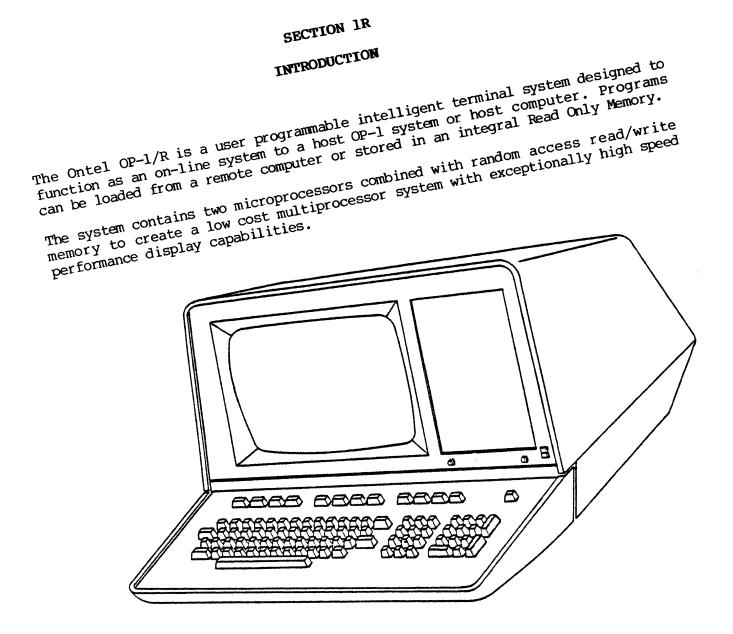

Figure 1R-1. OP-1/R Configuration

The Central Processor Unit can be programmed by the user for any application. The input/output disciplines are program controlled and enable the system to operate with various host computers.

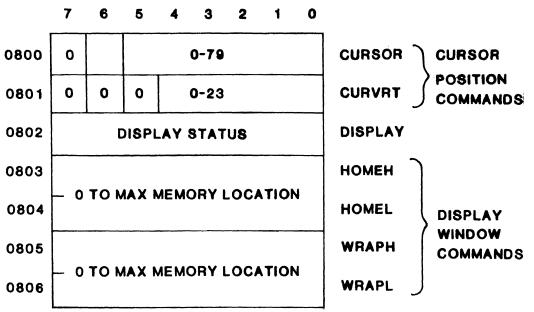

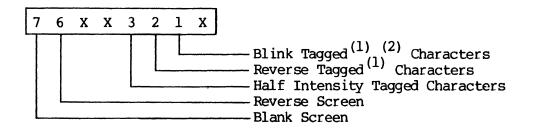

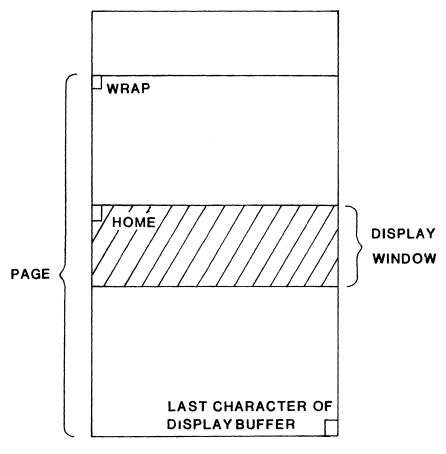

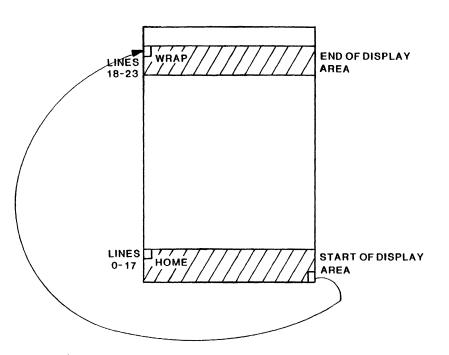

The Display Microprocessor provides a movable window in memory and performs fast roll/scroll and erase operations, as well as display functions such as blinking and video reversal.

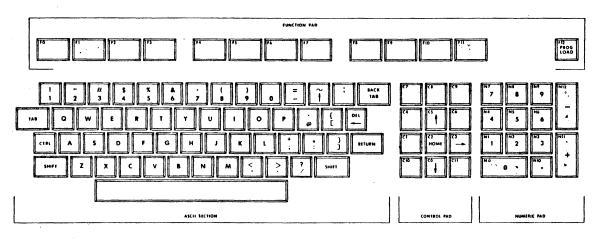

The system features include random access memory available in various configurations; program controlled asynchronous communications up to 19200 bits-per-second; a 14 inch non-glare CRT; and a complete programmable keyboard, arranged in four functional sections that generates unique codes readable by the CPU.

Figure 1R-2. OP-1/R Rear View

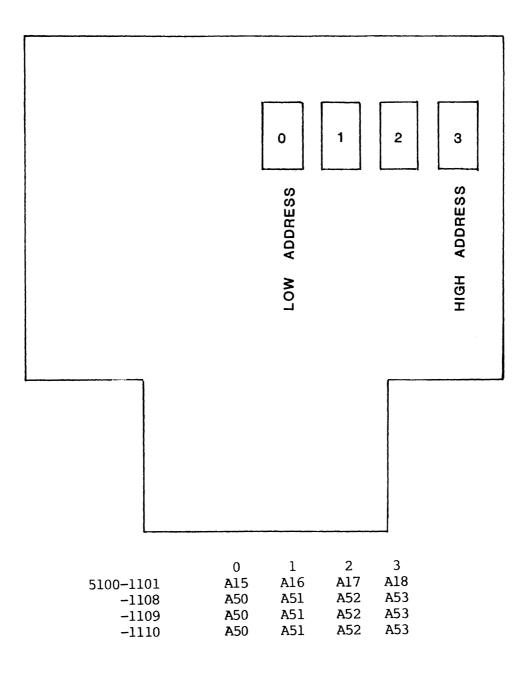

There are four versions of the OP-1/R. The OP-1/R Standard, OP-1/R II, OP-1/RW and the OP-1/RS. See Figure 1R-3 for summary.

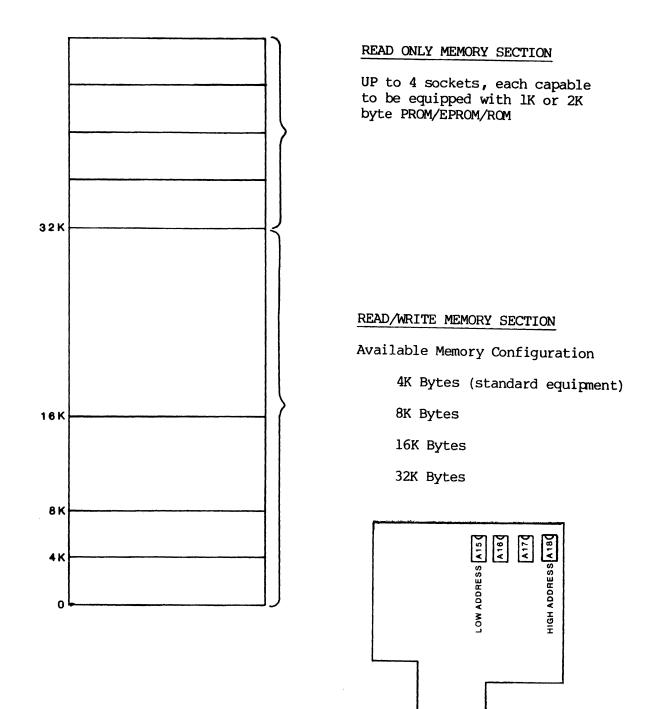

All Boards include:

- a) 8085 CPU

- b) 4K, 8K, 16K, or 32K DYNAMIC RAM

- c) Up to four 2708, 2716 or 2732 ROM, PROM or EROM

- d) Parallel I/O

- e) Two Fixed Data Switches

- f) Support for Alternate I/O Adapter (Optional second board).

#### FEATURES

#### OP-1/R STANDARD (5100-1101)

- 24 Line Display

- Async Communications RS-232, Current Loop or 2 Wire Direct. Programmable up to 19.2K BAUD.

- Will not support IOM and Device Controller.

#### OP-1/R II (5100-1108)

- Same as Standard but will support IOM and Device Controller.

#### OP-1/RW (5100-1109)

- Async Communications RS-232, 2 Wire Direct. Programmable up to 19.2K BAUD.

- Word Processing Display.

- Support IOM and Device Controller.

#### OP-1/RS (5100-1110)

- Synchronous Communications RS-232. Programmable up to 19.2K BAUD.

- 24 Line Display

- Support IOM and Device Controller.

## IOM AND CONTROLLERS

The following controllers can be used on the OP-1/R. Refer to OP-1 Reference Manual.

| Word Move Controller I         | 5000-1170 |

|--------------------------------|-----------|

| Word Move Controller II        | -11101    |

| Synchronous Communications I   | -1104     |

| Synchronous Communications II  | -1193     |

| Bisynchronous Communications I | -1148     |

| Bisynchronous Communication II | -1192     |

| Asynchronous Communications    | -1134     |

| Diskette Controller            | -1135     |

| MPDC II Controller             | -11110    |

| Mini Diskette Controller       | -11118    |

| SDLC                           | -11106    |

These PC Boards are identical to OP-1 Device Controllers except for the additional connection of signal  $\overline{\text{SEL}}$  to I/O Pin 4.

| FEATURE                            | REF. MANUAL<br>SECTION | OP-1/R STD<br>5100-<br>2001 | OP-1/R II<br>5100-<br>2008 | OP-1/RW<br>5100-<br>2009 | OP-1/RS<br>5100-<br>2010 |

|------------------------------------|------------------------|-----------------------------|----------------------------|--------------------------|--------------------------|

| INTERRUPIS                         | 4R                     | 0-3                         | 0-7                        | 0-7                      | 0-7                      |

| MEMORY RAM<br>4K,8K,16K,<br>or 32K | Rl                     | X                           | X                          | x                        | x                        |

| MEMORY ROM (4)<br>1K,2K or 4K      | Rl                     | x                           | x                          | х                        | X                        |

| DISPLAY<br>24 Line                 | 9R                     | X                           | x                          |                          | x                        |

| Word Processing                    | 11R                    |                             |                            | х                        |                          |

| COMMUNICATIONS<br>Asynchronous     | 7R                     | x                           | x                          | x                        |                          |

| Synchronous                        | 12R                    |                             |                            |                          | х                        |

| RS-232                             |                        | X                           | Х                          | Х                        | Х                        |

| Current Loop                       |                        | X                           | X                          |                          |                          |

| 2 Wire Direct                      |                        | x                           | х                          | Х                        |                          |

| FIXED DATA<br>SWITCHES             | 5R                     | x                           | x                          | x                        | x                        |

| PARALLEL 1/0                       | 8R                     | x                           | X                          | x                        | Х                        |

| OPTION BOARDS<br>Alt.I/O Adapter   | 10R                    | x                           | x                          | x                        | x                        |

| IOM                                | 13R                    |                             | x                          | x                        | х                        |

Figure 1R-3

#### SECTION 2R

#### SYSTEM ARCHITECTURE

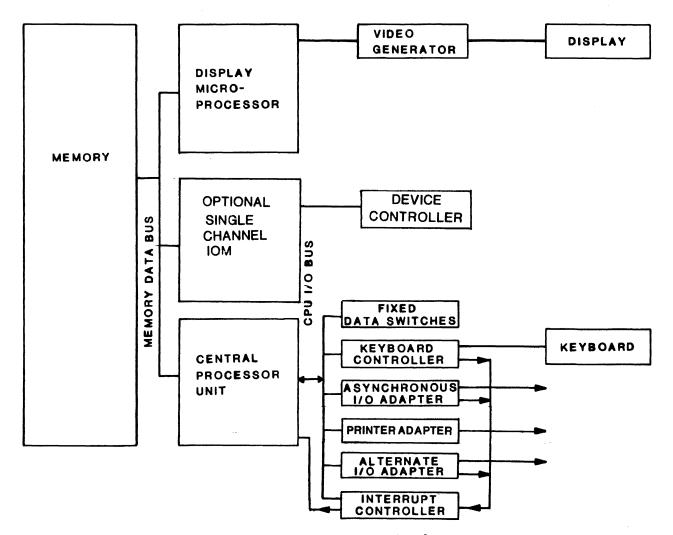

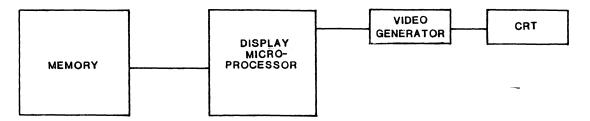

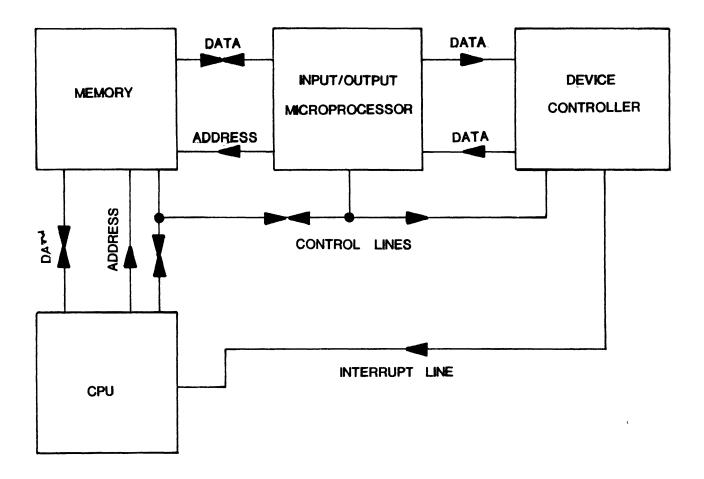

The OP-1/R system is designed for high speed communications and interactive display capability. The system memory is shared by two or three micro-processors:

- 1. Central Processor Unit

- 2. Display Microprocessor

- 3. Optional Input/Output Microprocessor

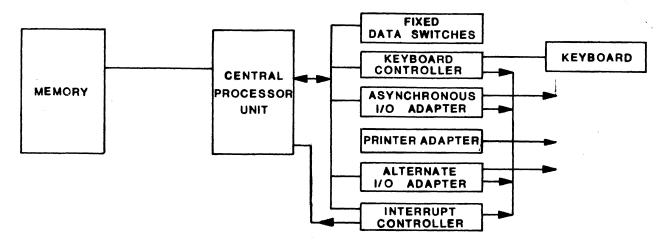

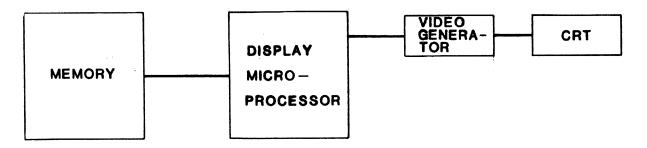

Figure 2R-1 illustrates the system architecture.

Figure 2R-1. OP-1/R System Block Diagram

#### MEMORY

Random access 8-bit byte memory is used. Various combinations of Read/Write or Read Only Memory are available. Bootstrap memory is available for systems equipped with only Read/Write main memory.

The memory can be allocated to any use at the programmer's option for program storage, display or I/O buffers.

#### CENTRAL PROCESSOR UNIT

The Central Processor Unit (CPU) performs the control, arithmetic and logic functions of the OP-1/R. An 8-bit parallel microprocessor with interrupt capability is used as the Central Processor Unit. A bi-directional data bus is used for communications between the CPU, memory and I/O devices.

The instruction repertoire includes Arithmetic/Logic Instructions, Load, Increment/Decrement, Rotate, Jump, Call and Return instructions.

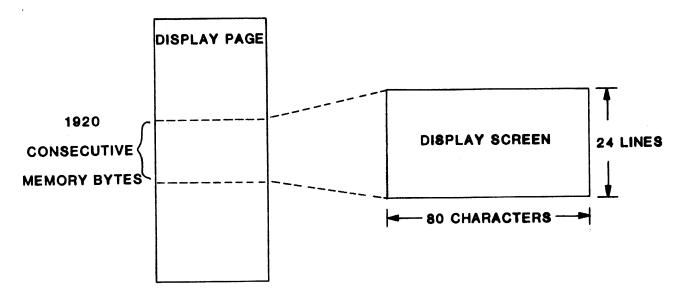

#### DISPLAY MICROPROCESSOR

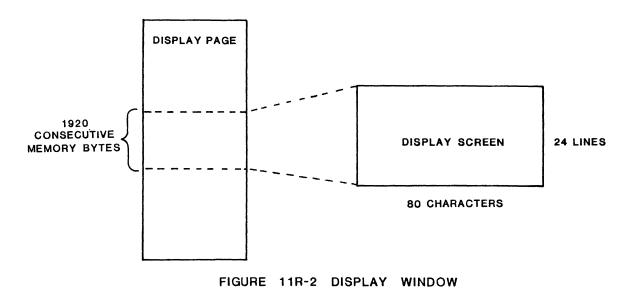

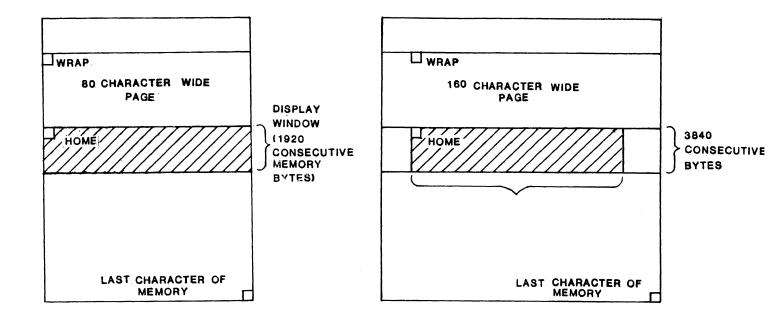

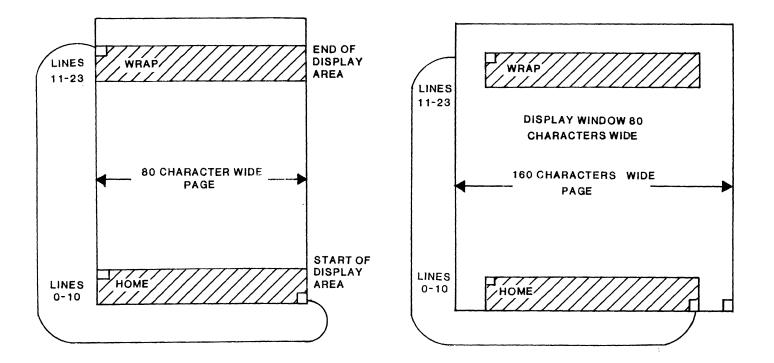

The Display Microprocessor converts the OP-1/R memory into a continous display page. The display screen is a movable window in the page. Any section of the memory can be assigned as a display buffer. Over 400 lines with 80 characters each can be implemented in a 32K byte memory system.

A detailed description of each device controller and device is supplied in the appropriate section.

#### INPUT/OUTPUT MICROPROCESSOR

Refer to Section 13.

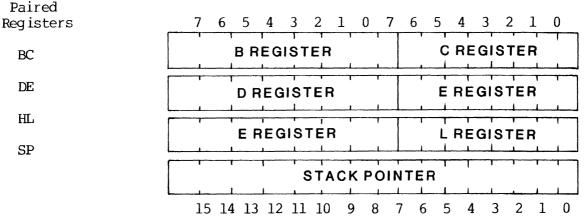

#### SECTION 3R

#### CENTRAL PROCESSOR UNIT AND I/O BUS

This section describes the CPU and the Instruction Repertoire. The basic devices directly connected to the CPU I/O bus: Fixed Data Switches, Keyboard and Asynchronous I/O Adapter, Printer Adapter and Alternate I/O Adapter are described in later sections.

Figure 3R-1. CPU and I/O Bus

#### CENTRAL PROCESSOR UNIT

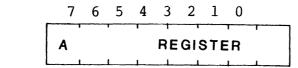

The CPU consists of an Arithmetic/Logic Unit, five condition flags, seven general purpose 8-bit registers, and a pushdown stack pointer and a program counter, each 16 bits long. The CPU is capable of directly addressing up to 64K bytes of main memory.

#### ARITHMETIC/LOGIC UNIT

The Arithmetic/Logic Unit is an 8-bit parallel binary computation device that performs addition, subtraction and logical operations.

All individual register arithmetic and logical operations are carried out between the A Register (Accumulator) and any one of the seven general purpose registers or between the A Register and memory. Register pair addition operations are carried out between the H and L registers and any one of the four register pairs.

#### GENERAL PURPOSE REGISTERS

Seven general purpose registers are used for temporary data storage internal to the CPU:

The A Register (Accumulator) receives the result of individual register arithmetic, logical and rotate operations. The A Register is also used as the Input/Output Register for data and control information exchanged between the CPU

Individual Registers

and the I/O Devices.

Accumulator

7 6 5 4 3 2 1 0 A,B,C,D,E,H,L REGISTER

The A, B, C, D, E, H, and L Registers can be used in conjunction with the Register for individual register arithmetic and logical operations. All registers are independent and can be incremented, decremented or loaded from another register or from memory.

|                   | 7  | 6  | 5  | 4  | 3   | 2  | 1  | 0 | 7 | 6 | 5 | 4 | 3    | 2    | 1   | 0     |  |

|-------------------|----|----|----|----|-----|----|----|---|---|---|---|---|------|------|-----|-------|--|

| Memory Addressing |    | -1 |    | EC | 101 | ER | -1 | T |   |   |   |   |      |      |     |       |  |

| Registers         | 1  |    |    |    | 101 |    |    |   |   | 1 |   | L | . RE | = GI | STI | = R , |  |

| M = (H L)         | 15 | 14 | 13 | 12 | 11  | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3    | 2    | 1   | 0     |  |

The H and L Registers, besides being used individually, are also used to provide memory addressing capability. The L Register contains the eight lower order address bits and H Register the eight higher order address bits of the memory location referenced. The contents of memory pointed to by the H and L registers are denoted by the letter M.

The individual registers can be concatenated in pairs to form a 16-bit register pair. The pair can be used to address memory or can be added to the HL pair. The standard names for the pairs are shown above.

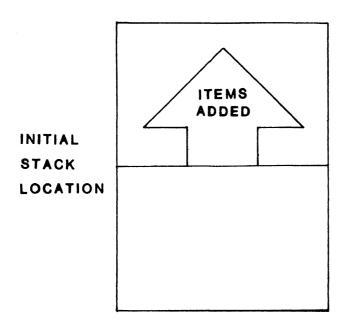

THE STACK

A stack is an area of memory allocated for subroutine or interrupt linkage or for temporary storage. Various data bytes may be "pushed" onto the stack in sequential order and later "popped" or retrieved from the stack in reverse order. To keep track of the last byte pushed to the stack, a stack pointer is provided. The stack pointer (SP) is a 16-bit register which always stores the address of the lst byte in the stack. As illustrated in Figure 3R-3, a stack starts at its initial location and expands linearly toward lower addresses as items are pushed to the stack. It is the programmer's responsibility to initiate the stack pointer register and reserve enough room for stacking purposes so that pushing data to the stack never destroys other data stored in memory. Any portion of the memory can be allocated for stack purposes.

CONTENT OF STACK POINTER REGISTER DECREASES AS ITEMS ARE ADDED TO THE STACK

Figure 3R-3. The Stack

#### BOOTSTRAP MEMORY

When power is turned on, or the PROG key is depressed in conjunction with the SHIFT and CTRL keys, the CPU will execute the program starting at location 8000 of the memory. The OP-1/R can be equipped with a bootstrap memory that can be factory programmed to load a program from a communication line. Alternately, the OP-1/R can be equipped with a fixed program stored in a Read Only Memory (ROM).

#### THE OP-1R INSTRUCTION SET

The OP-IR instruction set includes six different types of instructions:

- \* Data Transfer Group move data between registers or between memory and registers.

- \* Arithmetic Group add, subtract, increment or decrement data in registers or in memory.

- \* Logical Group AND, OR, EXCLUSIVE-OR, compare, rotate or complement data in registers or in memory.

- \* **Branch Group** conditional and unconditional jump instructions, subroutine call instructions and return instructions.

- \* Stack and Machine Control Group intructions for maintaining the stack and internal control flags.

- Input/Output Group instructions to select, input from or output to external devices.

#### Instruction and Data Formats:

Memory for the OP-1R is organized into 8-bit quantities, called Bytes. Each byte has a unique 16-bit binary address corresponding to its sequential position in memory.

The OP-1R can directly address up to 65,536 bytes of memory, which may consist of both read-only memory (ROM) elements and random-access memory (RAM) elements (read/write memory).

Data in the OP-1R is stored in the form of 8-bit binary integers:

DATA WORD (byte)

| T  |                                        |   |   |   |   |   |   |    | T  |

|----|----------------------------------------|---|---|---|---|---|---|----|----|

|    | 7                                      | 6 | 5 | 4 | 3 | 2 | 1 | 0  |    |

|    | ************************************** |   |   |   |   |   |   |    |    |

| MS | SB                                     |   |   |   |   |   |   | LS | SB |

When a register or data word byte contains a binary number, it is necessary to establish the order in which the bits of the number are written. In the OP-1R, BIT 0 is referred to as the Least Significant Bit (LSB), and BIT 7 (of an 8 bit number) is referred to as the Most Significant Bit (MSB).

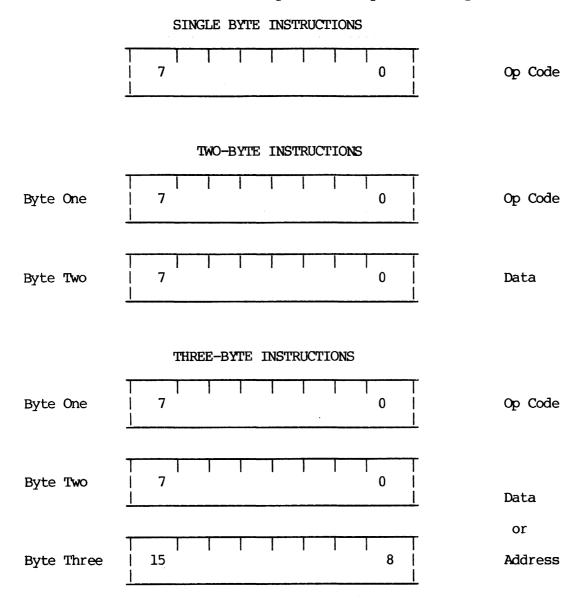

The OP-1R program instructions may be one, two or three bytes in length. Multiple byte instructions must be stored in successive memory locations; the address of the first byte is always used as the address of the instruction. The exact instruction format will depend on the particular operation to be executed.

## Addressing Modes

Often the data that is to be operated on is stored in memory. When multi-byte numeric data is used, the data, like instructions, is stored in successive memory locations, with the least significant byte first, followed by increasingly significant bytes. The OP-1R has four different modes for addressing data stored in memory or in registers:

- \* Direct Bytes 2 and 3 of the instruction contain the exact memory address of the data item (the low-order bits of the address are in byte 2, the high order bits in byte 3).

- \* Register The instruction specifies the register or register pair in which the data is located.

- \* Register Indirect The instruction specifies a register pair which contains the memory address where the data is located (the high order bits of the address are in the first register of the pair, the low order bits in the second.)

- \* Immediate The one or two bytes of data operated on by the instruction immediately follow the instruction in memory.

Unless directed by an interrupt or branch instruction, the execution of instructions proceeds through consecutively increasing memory locations. A branch instruction can specify the address of the next instruction to be executed in one of two ways:

- \* Direct The branch instruction contains the address of the next instruction to be executed. (Except for the 'RST' instruction, byte 2 contains the low order address and byte 3 contains the high order address.)

- \* Register Indirect The branch instruction indicates a register pair which contains the address of the next instruction to be executed. (The high-order bits of the address are in the first register of the pair, the low order bits in the second.)

The RST instruction is a special one-byte call instruction (usually used during interrupt sequences). RST includes a three bit field; program control is transferred to the instruction whose address is eight times the contents of this three bit field.

## Condition Flags

There are five condition flags associated with the execution of instructions on the OP-1R. They are Zero, Sign, Parity, Carry, and Auxiliary Carry, and are each represented by a 1 bit register in the CPU. A flag is set by forcing the bit to 1; reset by forcing the bit to 0.

- Zero:If the result of an instruction execution has the<br/>value 0, this flag is set; otherwise it is reset.Sign:If the most significant bit of the result of an<br/>instruction execution has the value 1, this flag<br/>is set; otherwise it is reset.Parity:If the modulo 2 sum of the bits of the result of<br/>under the parity is a supervision execution is 0. (if the set is the

- an instruction execution is 0, (i.e., if the result has even parity), this flag is set; otherwise it is reset (i.e., the result has odd parity).

- Carry: If the instruction execution resulted in a carry (from addition), or a borrow (from subtraction or a comparison) out of the high order bit, this flag is set; otherwise it is reset.

- Auxiliary Carry: If the instruction execution caused a carry out of bit 3 and into bit 4 of the resulting value, the auxiliary carry is set; otherwise it is reset. This flag is affected by single precision additions, subtractions, increments, decrements, comparisons, and logical operations, but is principally used with additions and increments preceding a DAA (Decimal Adjust Accumulator) instruction.

#### Symbols and Abbreviations

The following symbols and abbreviations are used in the subsequent description of the OP-1R instructions:

| SYMBOLS     | MEANING                                         |

|-------------|-------------------------------------------------|

| accumulator | Register A                                      |

| addr        | 16-bit address quantity                         |

| addr byte   | low or high order byte of address, as indicated |

| data        | 8-bit data quantity                             |

## Symbols and Abbreviations - (CONTINUED)

| SYMBOLS | MEANING                                                                                         |

|---------|-------------------------------------------------------------------------------------------------|

| data 16 | 16 bit data quantity                                                                            |

| byte 2  | The second byte of the instruction                                                              |

| byte 3  | The third byte of the instruction                                                               |

| r,rd,rs | One of the registers A,B,C,D,E,H,L                                                              |

| DDD,SSS | The bit pattern designating one of the registers A,B,C,D,E,H,L (DDD=destination, SSS=source):   |

|         | DDD or SSS REGISTER NAME                                                                        |

|         | 111A000B001C010D011E100H101L                                                                    |

| rp      | One of the register pairs:                                                                      |

|         | B represents the B,C pair with B as the high order register and C as the low order register;    |

|         | D represents the D,E pair with D as the high<br>order register and E as the low order register; |

|         | H represents the H,L pair with H as the high order register and L as the low order register;    |

|         | SP represents the 16 bit stack pointer register.                                                |

| RP      | The opcode bits corresponding to a register pair, as follows:                                   |

|         | B - 00<br>D - 01<br>H - 10<br>SP - 11                                                           |

SYMBOLS

MEANING

| rh          | The first (high order) register of a designated register pair.                                                       |

|-------------|----------------------------------------------------------------------------------------------------------------------|

| rl          | The second (low order) register of a designated register pair.                                                       |

| PC          | 16 bit program counter register (PCH and PCL are used to refer to the high order and low order 8 bits respectively). |

| SP          | 16 bit stack pointer register (SPH and SPL are used to refer to the high order and low order 8 bits respectively).   |

| rm          | Bit m of the register r (bits are number 7 through 0 from left to right).                                            |

| Z,S,P,CY,AC | The condition flags:                                                                                                 |

|             | Z – Zero,<br>S – Sign,<br>P – Parity,<br>CY – Carry,<br>AC – Auxiliary Carry                                         |

| ( )         | The contents of the memory location or registers enclosed in the parentheses.                                        |

| <           | "Is transferred to"                                                                                                  |

| AND         | Logical AND                                                                                                          |

| XOR         | Exclusive OR                                                                                                         |

| OR          | Inclusive OR                                                                                                         |

| *           | Multiplication                                                                                                       |

| +           | Addition                                                                                                             |

| -           | Two's complement subtraction                                                                                         |

| <>          | "Is exchanged with"                                                                                                  |

| ~           | The one's complement (e.g., ~(A))                                                                                    |

| n           | The restart number 0 through 7                                                                                       |

| NNN         | The binary representation 000 though 111 for restart number 0 through 7 respectively.                                |

| W           | (extra) Wait state for memory access                                                                                 |

## Description Format:

The following pages provide a detailed description of the instruction set of the OP-1R. Each instruction is described in the following manner.

- 1. The OP-1 assembler format, consisting of the instruction mnemonic and operand fields, is printed in **BOLDFACE** on the left side of the first line.

- 2. The name of the instruction is enclosed in parentheses on the right side of the first line.

- 3. The next line(s) contains a symbolic description of the operation of the instruction.

- 4. This is followed by a narrative description of the operation of the instruction.

- 5. The following line(s) contain the binary fields and patterns that comprise the machine instruction.

- 6. The last four lines contain incidental information about the execution of the instruction. The number of machine cycles and states required to execute the instruction are listed first. If the instruction has two possible execution times, as in a conditional Jump, both times will be listed, separately by a slash. Next, any significant data addressing modes (see Page 3R4) are listed. The last line lists any of the five Flags that are affected by the execution of the instruction.

## Approximate Timing

The number of microseconds per instruction can be approximated as follows: # microseconds = (# CPU states)\*(.32)

#### DATA TRANSFER GROUP:

This group of instructions transfers data to and from registers and memory. Condition flags are not affected by any instruction in this group.

MOV rd, rs (Move Register) (rd) <-- (rs) The contents of register rs is copied to register rd. ł 0 1 D D D S S S Mem. Cycles: 1 CPU States: 5 (4+1 WAIT (W)) Addressing: register Flags: none MOV r, M (Move from memory) (rl) <--- ((H) (L)) The contents of the memory location, whose address is in registers H and L, is copied to register r. 1 l D D D l 0 1 0 Mem. Cycles: 2 CPU States: 9 (7+2W) reg. indirect Addressing: Flags: none MOV M,r (Move to memory) ((H) (L)) < -- (r)The content of register r is copied to the memory location whose address is in registers H and L. 0 1 1 1 0 S S S Mem. Cycles: 2 CPU States: 9 (7+2W) reg. indirect Addressing:

reg. none

Flags:

MVI r, data (Move Immediate)

(r) <-- (byte 2)

The content of byte 2 of the instruction is copied to register r.</pre>

0 0 D D D 1 1 0 data Mem. Cycles: 2 CPU States: 9(7+2W)Addressing: immediate Flags: none

MVI M, data (Move to memory immediate)

((H) (L)) <--- (byte 2)

The content of byte 2 of the instruction is copied to the memory location whose address is in the register pair HL.

| T |   |   |     |       |     |   |   |   | Τ |

|---|---|---|-----|-------|-----|---|---|---|---|

| 1 | 0 | 0 | 1   | 1     | 0   | 1 | 1 | 0 | Ì |

|   |   |   |     |       |     |   |   |   |   |

| T |   |   | dat | ta by | yte |   |   |   |   |

Mem. Cycles: CPU States: Addressing: Flags:

3 13 (10+3W) immed./reg. indirect none

LXI rp, data 16 (Load register pair immediate)

(rh) <-- (byte 3), (rl) <-- (byte 2)

Byte 3 of the instruction is copied into the high order register (rh) of the register pair rp. Byte 2 of the instruction is copied into the low order register (rl) of the register pair rp.

| <br>  0<br> | 0              | R                             | Р   | 0   | 0   | T | ) 1                      |

|-------------|----------------|-------------------------------|-----|-----|-----|---|--------------------------|

|             |                | :a by                         |     |     |     |   |                          |

| 1           | dat            | a by                          | 7te | (-> | rh) |   |                          |

| CPU         | l Sta<br>Iress | les:<br>ites:<br>ing:<br>ags: |     |     |     |   | (10+3W)<br>mediate<br>me |

#### LDA addr

## (Load Accumulator direct)

(A) <-- ((byte 3)(byte 2))

The content of the memory location, whose address is specified in byte 2 and byte 3 of the instruction, is copied to register A.

| T | 0 | 0 | 1 | 1              | 1 | 0 | 1 | 0 |  |

|---|---|---|---|----------------|---|---|---|---|--|

|   |   |   |   | er ad<br>Jer a |   |   | 5 |   |  |

| Mem. Cycles: | 4          |

|--------------|------------|

| CPU States:  | 17 (13+4W) |

| Addressing:  | direct     |

| Flags:       | none       |

STA addr (Store Accumulator direct)

((byte 3)(byte 2)) <-- (A)

The content of the accumulator is copied to the memory location whose address is specified in byte 2 and 3 of the instruction.

|   | 0                   | 0    | 1     | 1     | 0    | 0    | 1 | 0 |   |  |  |

|---|---------------------|------|-------|-------|------|------|---|---|---|--|--|

| T | low-order addr byte |      |       |       |      |      |   |   |   |  |  |

| T |                     | high | n-ord | ler a | addr | byte | 3 |   | T |  |  |

| Mem. Cycles: | 4          |

|--------------|------------|

| CPU States:  | 17 (13+4W) |

| Addressing:  | direct     |

| Flags:       | none       |

LHLD addr (Load H and L direct)

(L) <-- ((byte 3)(byte 2))

(H) <--- ((byte 3)(byte 2) + 1)

The content of the memory location, whose address is specified in byte 2 and byte 3 of the instruction, is copied to register L. The content of the next (higher) memory location is copied to register H.

| <br> <br> | 0                    | 0   | 1    | 0 | 1 | 0 | 1 | 0 |  |  |

|-----------|----------------------|-----|------|---|---|---|---|---|--|--|

| Ī         | low-order addr byte  |     |      |   |   |   |   |   |  |  |

| 1         | high-order addr byte |     |      |   |   |   |   |   |  |  |

| 1         | Mem.                 | Cyc | les: | : |   | 5 | 5 |   |  |  |

| Mem. Cycles: | 5          |

|--------------|------------|

| CPU States:  | 21 (16+5W) |

| Addressing:  | direct     |

| Flags:       | none       |

## SHLD addr (Store H and L direct)

((byte 3) (byte 2)) <-- (L)

((byte 3)(byte 2) + 1) <-- (H)

The content of register L is copied to the memory location whose address is specified in byte 2 and byte 3. The content of register H is copied to the next (higher) memory location.

|               | 0 | 0 | 1 | 0 | 0             | 0            | 1 | 0 |               |

|---------------|---|---|---|---|---------------|--------------|---|---|---------------|

| $\frac{1}{1}$ |   |   |   |   | ldr h<br>addr | byte<br>byte | 3 |   | $\frac{1}{1}$ |

| Mem. Cycles: | 5          |

|--------------|------------|

| CPU States:  | 21 (16+5W) |

| Addressing:  | direct     |

| Flags:       | none       |

LDAX rp

(Load Accumulator indirect)

(A) <-- ((rp))

The content of the memory location, whose address is in the register pair rp, is copied to register A. Note: only register pairs rp=B (registers B and C) or rp=D (registers D and E) may be specified.

| Τ |   |   |   |   |   |   |   |   | Т |

|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | R | Ρ | 1 | 0 | 1 | 0 |   |

|   |   |   |   |   |   |   |   |   |   |

| Mem. Cycles: | 2             |

|--------------|---------------|

| CPU States:  | 9 (7+2W)      |

| Addressing:  | reg. indirect |

| Flags:       | none          |

STAX rp

#### (Store Accumulator indirect)

((rp)) <-- (A)The content of register A is copied to the memory location whose address is in the register pair rp. Note: only register pairs rp=B (registers B and C) or rp=D (registers D and E) may be specified.

| 0   | 0              | R                                | Р | 0 | 0 | 1                          | 0 |       |

|-----|----------------|----------------------------------|---|---|---|----------------------------|---|-------|

| CPU | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>Lags: | : |   | 1 | 2<br>9 (7-<br>ceg.<br>none |   | irect |

XCHG [Exchange (HL) with (DE] (H) <--> (D) (L) <---> (E) The contents of register pair HL is exchanged with the contents of register pair DE.

| 1  | 1                             | 1    | 0 | 1 | 0 | 1            | 1            |  |

|----|-------------------------------|------|---|---|---|--------------|--------------|--|

| CP | . Cyc<br>J Sta<br>Iress<br>Fl | tes: |   |   | r | (4-<br>regis | +1W)<br>ster |  |

#### Arithmetic Group:

This group of instructions performs arithmetic operations on data in registers and memory.

Unless indicated otherwise, all instructions in this group affect the Zero, Sign, Parity, Carry, and Auxiliary Carry flags according to the standard rules.

All subtraction operations are performed via two's complement arithmetic and set the carry flag to one to indicate a borrow, and clear it to indicate no borrow.

ADD r (Add Register) (A) <- (A) + (r) The content of register r is added to the content of the accumulator. The result is placed in the accumulator.

| 1  | 0                             | 0   | 0 | 0 | S | S                           | s |    |

|----|-------------------------------|-----|---|---|---|-----------------------------|---|----|

| CP | . Cyc<br>J Sta<br>dress<br>F] | tes | : |   | r | L<br>5 (4<br>regis<br>Z,S,I |   | AC |

ADD M (Add memory) (A) <-- (A) + ((H) (L)) The content of the memory location whose address is contained in the HL register pair is added to the content of the accumulator. The result is placed in the accumulator.

| 1   | 0              | 0                                | 0 | 0 | 1 | 1 | 0                     | <br> <br> |

|-----|----------------|----------------------------------|---|---|---|---|-----------------------|-----------|

| CPL | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>Lags: | : |   | r |   | +2W)<br>dire<br>P,CY, |           |

ADI data

(Add immediate)

(A) <-- (A) + (byte 2)

The content of the second byte of the instruction is added to the content of the accumulator. The result is placed in the accumulator.

| 1 | 1         | 1   | 0   | 0 | 0 | 1 | 1 | 0 |  |  |  |  |

|---|-----------|-----|-----|---|---|---|---|---|--|--|--|--|

| Τ | data byte |     |     |   |   |   |   |   |  |  |  |  |

|   | Mem.      | Cva | les |   |   |   | 2 |   |  |  |  |  |

| 2           |

|-------------|

| 9 (7+2W)    |

| immediate   |

| Z,S,P,CY,AC |

|             |

ADC r

(Add Register with carry)

(A) <-- (A) + (r) + (CY)

The content of register r and the content of the carry bit are added to the content of the accumulator. The result is placed in the accumulator.

| 1   | 0                             | 0   | 0 | 1 | S | S                                     | S |    |

|-----|-------------------------------|-----|---|---|---|---------------------------------------|---|----|

| CPI | . Cyc<br>J Sta<br>Iress<br>F] | tes | : |   | r | l<br>5 (4-<br>regis<br>2, <b>S,</b> I |   | AC |

ADC M

(Add memory with carry)

(A) <-- (A) + ((H) (L)) + (CY)

The content of the memory location whose address is contained in the HL register pair and the content of the CY flag are added to the accumulator. The result is placed in the accumulator.

| <br> <br> | 1   | 0              | 0                                | 0 | 1 | 1 | 1 | 0                     |  |

|-----------|-----|----------------|----------------------------------|---|---|---|---|-----------------------|--|

|           | CPU | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>Lags: |   |   | r |   | +2W)<br>indi<br>P,CY, |  |

ACI data (Add immediate with carry)

(A) <-- (A) + (byte 2) + (CY)

The content of the second byte of the instruction and the content of the CY flag are added to the contents of the accumulator. The result is placed in the accumulator.

| 1 | 1 | 0   | 0    | 1   | 1 | 1 | 0 | T |

|---|---|-----|------|-----|---|---|---|---|

|   |   | dat | a by | yte |   |   |   |   |

| Mem. | Cycles:  |  |

|------|----------|--|

| CPU  | States:  |  |

| Addı | cessing: |  |

|      | Flags:   |  |

immmediate Z,S,P,CY,AC

2

9 (7+2W)

SUB r

(Subtract Register)

(A)  $\langle -$  (A) - (r) The content of register r is subtracted from the content of the accumulator. The result is placed in the accumulator.

| 1   | 0              | 0                                | 1 | 0 | S | S                            | S |    |

|-----|----------------|----------------------------------|---|---|---|------------------------------|---|----|

| CPU | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>Lags: |   |   | 1 | L<br>5 (4-<br>cegis<br>Z,S,1 |   | AC |

(Subtract memory)

(A) < -- (A) - ((H) (L))

SUB M

The content of the byte whose address is in register pair HL is subtracted from the accumulator. The result is placed in the accumulator.

Mem. Cycles:2CPU States:9 (7+2W)Addressing:reg. indirectFlags:Z,S,P,CY,AC

SUI data (Subtract immediate)

(A) <--- (A) - (byte 2)

The content of the second byte of the instruction is subtracted from the content of the accumulator. The result is placed in the accumulator.

|           | 0 1 | 0 1 | - 1 |  |  |  |  |  |  |  |

|-----------|-----|-----|-----|--|--|--|--|--|--|--|

| data byte |     |     |     |  |  |  |  |  |  |  |

| Mem. Cycles: | 2           |

|--------------|-------------|

| CPU States:  | 9 (7+2W)    |

| Addressing:  | immediate   |

| Flags:       | Z,S,P,CY,AC |

SBB r (Subtract Register with borrow)

(A) <-- (A) - (r) - (CY)

The content of register r and the content of the CY flag are both subtracted from the accumulator. The result is placed in the accumulator.

| 1  | 0                             | 0   | 1 | 1 | S | S                       | l<br>S |    |

|----|-------------------------------|-----|---|---|---|-------------------------|--------|----|

| CP | . Cyc<br>J Sta<br>Iress<br>F] | tes | : |   | r | 5 (1-<br>regi:<br>2,S,1 |        | AC |

SBB M

#### (Subtract memory with borrow)

(A) < --- (A) - ((H) (L)) - (CY)

The content of the memory location whose address is contained in the HL register pair and the content of the CY flag are both subtracted from the accumulator. The result is placed in the accumulator.

| 1    | 0 | 0    | 1 | 1 | 1 | 1 | 0      |  |

|------|---|------|---|---|---|---|--------|--|

| Mem. |   | les: |   |   |   | 2 | +2141) |  |

| CPU SLALES: | $\mathbf{y} (\mathbf{T} \mathbf{Z} \mathbf{W})$ |

|-------------|-------------------------------------------------|

| Addressing: | reg. indirect                                   |

| Flags:      | Z,S,P,CY,AC                                     |

SBI data (Subtract immediate with borrow)

(A) <-- (A) - (byte 2) - (CY)

The contents of the second byte of the instruction and the contents of the CY flag are both subtracted from the accumulator. The result is placed in the accumulator.

|   | 1   | 1   | 0    | 1    | 1  | 1 | 1 | 0 |   |

|---|-----|-----|------|------|----|---|---|---|---|

| Τ |     |     | data | a by | te |   |   |   | Τ |

|   | Mom | Cyr |      |      |    |   | > |   |   |

| riciu • | cycres.  |  |

|---------|----------|--|

| CPU     | States:  |  |

| Addı    | cessing: |  |

|         | Flags:   |  |

2 9 (7+2W) immediate Z,S,P,CY,AC

#### INR r

(Increment Register)

(r)  $\langle -$  (r) + 1 The content of register r is incremented by one. All conditions flags except CY are affected.

| 0   | 0                             | D     | D | D | 1 | 0                           | 0    |  |

|-----|-------------------------------|-------|---|---|---|-----------------------------|------|--|

| CPU | , Cyc<br>J Sta<br>Iress<br>F] | ates: | : |   | 1 | l<br>5 (4<br>regis<br>Z,S,1 | ster |  |

INR M (Increment memory)

((H) (L)) <-- ((H) (L)) + 1

The content of the memory location whose address is contained in the H and

L registers is incremented by one. All condition flags except CY are

affected.</pre>

0 0 1 1 0 1 0 0 Mem. Cycles: 3 CPU States: 13 (10+3W)Addressing: reg. indirect Flags: Z,S,P,AC DCR r (Decrement Register) (r) < - (r) - 1The content of register r is decremented by one. All condition flags except CY are affected.

| T |   | T |   |   |   |   |   |   | Т |

|---|---|---|---|---|---|---|---|---|---|

| ļ | 0 | 0 | D | D | D | 1 | 0 | 1 | ļ |

|   |   |   | · |   |   |   | - |   | 1 |

| 1        |

|----------|

| 5 (4+1W) |

| register |

| Z,S,P,AC |

|          |

DCR M (Decrement memory)

((H) (L)) <-- ((H) (L)) - 1

The content of the memory location whose address is contained in the HL

register pair is decremented by one. All condition flags except CY are

affected.</pre>

| 0  | 0              | 1                                | 1 | 0 | 1 | 0                                             | 1    |             |

|----|----------------|----------------------------------|---|---|---|-----------------------------------------------|------|-------------|

| CP | J Sta<br>dress | cles:<br>ates:<br>sing:<br>lags: |   |   | 1 | 3<br>13 (1<br>reg.<br>Z <b>,</b> S <b>,</b> 1 | indi | ∛)<br>irect |

INX rp (Increment register pair)

(rh) (rl) <-- (rh) (rl) + 1

The content of the register pair rp is incremented by one. No condition

flags are affected.</pre>

Mem. Cycles: 1 CPU States: 7 (6+1W) Addressing: register Flags: none

Mem. Cvcles: 1

| menn. Cycres: | 1        |

|---------------|----------|

| CPU States:   | 7 (6+1W) |

| Addressing:   | register |

| Flags:        | none     |

|               |          |

DAD rp

(Add register pair to H and L)

(H) (L) <-- (H) (L) + (rh) (rl)

The content of the register pair rp is added to the content of the register pair H and L. The result is placed in the register pair H and L. Only the CY flag is affected. It is set if there is a carry out of the double precision add; otherwise it is reset.

| 0   | 0              | R                                | Р       | 1 | 0 | 0                         | 1              |

|-----|----------------|----------------------------------|---------|---|---|---------------------------|----------------|

| CPU | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>lags: | +<br> - |   |   | L<br>Ll (I<br>regis<br>CY | 10+1W)<br>ster |

**DAA** (Decimal Adjust Accumulator)

The eight-bit number in the accumulator is adjusted to form two four bit Binary-Coded-Decimal digits by the following process:

- 1. If the value of the least significant 4 bits of the accumulator is greater than 9 or if the AC flag is set, 6 is added to the accumulator.

- 2. If the value of the most significant 4 bits of the accumulator is now greater than 9, or if the CY flag is set, 6 is added to the most significant 4 bits of the accumulator.

NOTE: All flags are affected.

| 0   |          |   | <br>1 |   | 1 |  |

|-----|----------|---|-------|---|---|--|

| Mom | <u>^</u> | _ | -     | 1 |   |  |

| ment. Cycres: | T           |

|---------------|-------------|

| CPU States:   | 5 (4+1W)    |

| Flags:        | Z,S,P,CY,AC |

## LOGICAL GROUP:

cleared.

This group of instructions performs logical (Boolean) operations on data in registers and memory and on condition flags.

Unless indicated otherwise, all instructions in this group affect the Zero, Sign, Parity, Auxiliary Carry, and Carry flags according to the standard rules.

#### ANA r (AND Register)

(A)  $\langle$ — (A) AND (r) The content of register r is logically anded with the content of the accumulator. The result is placed in the accumulator. The CY flag is

| 1   | 0              | 1                                | 0 | 0 | S | S                                     | l<br>S |    |

|-----|----------------|----------------------------------|---|---|---|---------------------------------------|--------|----|

| CPL | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>Lags: | : |   | r | L<br>5 (4-<br>regis<br>Z <b>,S,</b> 1 |        | AC |

ANA M (AND memory)

(A) <-- (A) AND ((H) (L))

The contents of the memory location whose address is contained in the H and L registers is logically anded with the content of the accumulator. The reslt is placed in the accumulator. The CY flag is cleared.

| 1   | 0              | 1                                | 0 | 0 | 1 | 1 | 0                       | T<br> <br><u> </u> |

|-----|----------------|----------------------------------|---|---|---|---|-------------------------|--------------------|

| CPL | J Sta<br>dress | cles:<br>ates:<br>sing:<br>Lags: | : |   | 1 |   | +2W)<br>indir<br>P,CY,A |                    |

ANI data (AND immediate)

(A)  $\langle$ — (A) AND (byte 2) The content of the second byte of the instruction is logically anded with the contents of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

|             | 1 | 1  | 1    | 0 | 0           | 1          | 1    | 0 |  |  |

|-------------|---|----|------|---|-------------|------------|------|---|--|--|

| data byte   |   |    |      |   |             |            |      |   |  |  |

|             |   |    | les  |   |             | 2<br>) (7· | +2W) |   |  |  |

| Addressing: |   |    |      |   |             | immediate  |      |   |  |  |

|             |   | F] | lags |   | Z,S,P,CY,AC |            |      |   |  |  |

XRA r

(Exclusive OR Register)

(A) <-- (A) XOR (r) The content of register r is exclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

| 1 | 0    | 1                         | 0 | 1 | S | S                            | S |    |

|---|------|---------------------------|---|---|---|------------------------------|---|----|

|   | ress | les<br>ites<br>ing<br>ags | : |   | 1 | l<br>5 (4-<br>regis<br>2,S,1 |   | AC |

XRA M (Exclusive OR Memory)

(A) <-- (A) XOR ((H) (L)) The content of the memory location whose address is contained in the HL register pair is exclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

| 1 | 0    | 1              | 0 | 1 | 1 | 1          | 0    |            |

|---|------|----------------|---|---|---|------------|------|------------|

|   | -    | cles:<br>ates: |   |   | 2 | 2<br>9 (7· | +2W) |            |

|   | lres | sing:<br>Lags: | : |   | 1 | ceg.       |      | rect<br>AC |

XRI data

(Exclusive OR immediate)

(A) <--- (A) XOR (byte 2)

The content of the second byte of the instruction is exclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

| T         |   |   |   |   |   |   |   |   | Т |

|-----------|---|---|---|---|---|---|---|---|---|

|           | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

|           |   |   |   |   |   |   |   |   |   |

| data byte |   |   |   |   |   |   |   |   |   |

| Mem. Cycles: | 2           |

|--------------|-------------|

| CPU States:  | 9 (7+2W)    |

| Addressing:  | immediate   |

| Flags:       | Z,S,P,CY,AC |

ORA r

(OR Register)

(A) <-- (A) OR (r) The content of register r is inclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

| 1   | 0              | 1                                | 1 | 0 | S | S                            | S |    |

|-----|----------------|----------------------------------|---|---|---|------------------------------|---|----|

| CPL | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>lags: | : |   | 1 | [<br>5 (4-<br>cegis<br>Z,S,I |   | AC |

ORA M (OR memory)

(A)  $\leftarrow$  (A) OR ((H) (L))

The content of the memory location whose address is contained in the HL register pair is inclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

| 1 | 0              | 1 | 1 | 0                                        | 1 | 1 | 0    |  |

|---|----------------|---|---|------------------------------------------|---|---|------|--|

|   | . Cya<br>J Sta |   |   |                                          |   | 2 | +2₩) |  |

|   | ires           |   | 8 | 9 (7+2W)<br>reg. indirect<br>Z,S,P,CY,AC |   |   |      |  |

ORI data

(OR Immediate)

Z,S,P,CY,AC

(A) <-- (A) OR (byte 2)

The content of the second byte of the instruction is inclusive-OR'd with the content of the accumulator. The result is placed in the accumulator. The CY and AC flags are cleared.

|                                | 1 1     | 0          | 1 | 1                  | 0             |

|--------------------------------|---------|------------|---|--------------------|---------------|

| 1                              | data by | <u>/te</u> |   |                    |               |

| Mem. Cyc<br>CPU Sta<br>Address | ates:   |            |   | 2)<br>(7+<br>.mmec | +2W)<br>liate |

Flags:

#### (Compare Register)

$\begin{array}{c} \text{CMP } \mathbf{r} \\ \text{(A)} - \text{(r)} \end{array}$

The contents of register r are logically subtracted from the accumulator. The contents of the accumulator are unchanged. The condition flags are set as a result of the subtraction. The Z flag is set to 1 if (A) = (r). The CY flag is set to 1 if (A) < (r).

| <br> <br> | 1   | 0                           | 1    | 1 | 1 | S | S                            | S |    |

|-----------|-----|-----------------------------|------|---|---|---|------------------------------|---|----|

|           | CPU | Cyc<br>J Sta<br>Iress<br>F] | tes: | : |   | r | [<br>5 (4-<br>regis<br>2,S,I |   | AC |

#### CMP M

(Compare memory)

(A) - ((H)(L))The content of the memory location whose address is contained in the HL register pair is logically subtracted from the accumulator. The contents of the accumulator are unchanged. The condition flags are set as a result of the subtraction. The Z flag is set to 1 if (A) = ((H)(L)). The CY flag is set to 1 if (A) < ((H)(L)).

| T |   |   |   |   | 1 | <u> </u> | T | Τ | Τ |

|---|---|---|---|---|---|----------|---|---|---|

| 1 | 1 | 0 | 1 | 1 | 1 | 1        | 1 | 0 |   |

|   |   |   |   |   |   |          |   |   | 1 |

| Mem. Cycles: | 2             |

|--------------|---------------|

| CPU States:  | 9 (7+2W)      |

| Addressing:  | reg. indirect |

| Flags:       | Z,S,P,CY,AC   |

CPI data

(Compare immediate)

(A) - (byte 2) The contents of the second byte of the instruction are logically subtracted from the accumulator. The contents of the accumulator are unchanged. The condition flags are set by the result of the subtraction. The Z flag is set to 1 if (A) = (byte 2). the CY flag is set to 1 if (A) < (byte 2).

| T | 1    | 1   | 1   | 1     | 1           | 1 | 1 | 0 | T |

|---|------|-----|-----|-------|-------------|---|---|---|---|

| 1 |      |     | dat | ta by | <i>y</i> te |   |   |   | + |

|   | Mem. | Сус | les |       | 2           | 2 |   |   |   |

| Mem. Cycles: | 2           |

|--------------|-------------|

| CPU States:  | 9 (7+2W)    |

| Addressing:  | immediate   |

| Flags:       | Z,S,P,CY,AC |

|              |             |

RLC (Rotate left)  $(^{A}_{n+1}) < -, (^{A}_{n}); (^{A}_{0}) < -, (^{A}_{7})$ (CY) <-- (<sup>A</sup>7) The content of the accumulator is rotated left one position. The low order bit and the CY flag are both set to the value shifted out of the high order bit position. Only the CY flag is affected. 0 0 0 0 0 1 1 1 Mem. Cycles: 1 5 (4+1W) CPU States: Flags: CY RRC (Rotate right)  $\binom{A}{n} < - \binom{A}{n+1}; \binom{A}{7} < - \binom{A}{0}$  $(CY) < - (A_0)$ The content of the accumulator is rotated right one position. The high order bit and the CY flag are both set to the value shifted out of the low order bit position. Only the CY flag is affected. ł 1 0 0 0 0 1 1 1 Mem. Cycles: 1 5 (4+1W) CPU States: CY Flags: (Rotate left through carry) RAL  $(^{A}n+1) < -, (^{A}n); (^{A}0) < -, (CY)$ (CY) <-- (<sup>A</sup>7) The content of the accumulator is rotated left one position through the CY flag. The low order bit is set equal to the CY flag and the CY flag is set to the value shifted out of the high order bit. Only the CY flag is affected. 0 0 1 0 1 1 1 0 Mem. Cycles: 1 CPU States: 5 (4+1W) CY Flags:

| (**7) < (CY)                                                      | (Rotate right through carry)<br>< ( <sup>A</sup> 0)<br>accumulator is rotated right one position through the CY |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| flag. The high order                                              | bit is set to the CY flag and the CY flag is set to<br>of the low order bit. Only the CY flag is affected.      |

|                                                                   |                                                                                                                 |

| Mem. Cycles:<br>CPU States:<br>Flags:                             | 1<br>5 (4+1W)<br>CY                                                                                             |

| CMA<br>(A) <~~(A)<br>The contents of the<br>bits become 0). No fl | (Complement accumulator)<br>accumulator are complemented (zero bits become 1, one<br>ags are affected.          |

|                                                                   |                                                                                                                 |

| Mem. Cycles:<br>CPU States:<br>Flags:                             | 1<br>5(4+1W)<br>none                                                                                            |

| CMC<br>(CY) <~~(CY)<br>The CY flag is comple                      | (Complement carry)<br>emented. No other flags are affected.                                                     |

|                                                                   |                                                                                                                 |

| Mem. Cycles:<br>CPU States:<br>Flags:                             | 1<br>5 (4+1W)<br>CY                                                                                             |

| STC<br>(CY) < 1<br>The CY flag is set to                          | (Set carry)<br>1. No other flags are affected.                                                                  |

|                                                                   |                                                                                                                 |

| Mem. Cycles:<br>CPU States:<br>Flags:                             | 1<br>5 (4+1W)<br>CY                                                                                             |

#### BRANCH GROUP:

This group of instructions alter normal sequential program flow. Condition flags are not affected by any instruction in this group.

The two types of branch instructions are unconditional and conditional. Unconditional transfers simply perform the specified operation on register PC (the program counter). Conditional transfers examine the status of one of the four processor flags to determine if the specified branch is to be executed. The conditions that may be specified are as follows:

| CONDITION                                                                                         | CCC                      |

|---------------------------------------------------------------------------------------------------|--------------------------|

| NZ - not zero $(Z = 0)$<br>Z - zero $(Z = 1)$<br>NC - no carry $(CY = 0)$<br>C - carry $(CY = 1)$ | 000<br>001<br>010<br>011 |

| PO - parity odd (P = 0)                                                                           | 100                      |

| PE - parity even (P = 1)<br>P - plus (S = 0)                                                      | 101<br>110               |

| M - minus (S = 1)                                                                                 | 111                      |

# JMP addr (Jump)

(PC) <-- (byte 3) (byte 2)

Control is transferred to the instruction whose address is specified in bytes 3 and 2 of the current instruction.

| 1 | 1 | 0             | 0     | 0 | 0 | 1 | 1 |               |

|---|---|---------------|-------|---|---|---|---|---------------|

|   |   | low-<br>nigh- | -orde |   |   |   |   | $\frac{1}{1}$ |

| Mem. Cycles: | 3          |

|--------------|------------|

| CPU States:  | 13 (10+3W) |

| Addressing:  | immediate  |

| Flags:       | none       |

#### Jcondition addr

(Conditional jump)

If(CCC),

(PC) <--- (byte 3) (byte 2)

If the specified condition is true, control is transferred to the instruction whose address is specified in bytes 3 and 2 of the current instruction; otherwise, control continues sequentially.

| Ţ | 1 | 1 | С | С     | С | 0 | 1 | 0 |  |

|---|---|---|---|-------|---|---|---|---|--|

|   |   | 1 |   | -orde |   |   |   |   |  |

Mem. Cycles: CPU States: Addressing: Flags: 2/3 9/13 (7+2W/10+3W) immediate none CALL addr (Call)

((SP) -1) <--- (PCH)

((SP) -2) <--- (PCL)

(SP) <--- (SP) -2 (PC) <-- (byte 3) (byte 2)

First, the contents of the Program Counter are PUSHed into the Stack. Next, the two address bytes following the CALL opcode replace the Program Counter, effecting a branch to that address.

| T |                      |   |   |   |   |   |   | 1 | Τ |  |  |  |  |

|---|----------------------|---|---|---|---|---|---|---|---|--|--|--|--|

| 1 | 1                    | 1 | 0 | 0 | 1 | 1 | 0 | 1 |   |  |  |  |  |

|   |                      |   |   |   |   |   |   |   |   |  |  |  |  |

| T | low-order addr byte  |   |   |   |   |   |   |   |   |  |  |  |  |

| T | high-order addr byte |   |   |   |   |   |   |   |   |  |  |  |  |

Mem. Cycles: CPU States: Addressing: Flags:

5 23 (18+5W) immediate/reg. indirect none

#### **Ccondition addr** (Condition call)

If(CCC),

((SP) -1) <--- (PCH) ((SP) -2) <--- (PCL) (SP) <-- (SP) -2 (PC) <-- (byte 3) (byte 2)

If the specified condition is true, the actions specified in the CALL instruction (see above) are performed; otherwise, control continues sequentially.

| 1    | 1    | С     | С     | С     | 1    | 0    | 0 |   |

|------|------|-------|-------|-------|------|------|---|---|

|      | low- | -orde | er ad | ldr h | oyte |      |   | Τ |

|      | high | n-ord | der a | addr  | byte | ē    |   | Τ |

| Morr |      |       |       |       |      | 2 /5 |   |   |

| Mem. Cycles: | 2/5                     |

|--------------|-------------------------|

| CPU States:  | 11/23 (9+2W/18+5W)      |

| Addressing:  | immediate/reg. indirect |

| Flags:       | none                    |

|              |                         |

RET (Return) (PCL) <--- ((SP)) (PCH) <--- ((SP) + 1) (SP) <--- (SP) + 2 The Program Counter is POP'd from the Stack.

1 1 1 0 0 1 0 0 1

Mem. Cycles: 3 CPU States: 13 (10+3W)Addressing: reg. indirect Flags: none

Rcondition

(Conditional return)

If(CCC),

If the specified condition is true, the Program Counter is POP'd from the Stack; otherwise, control continues sequentially.

| 1  | 1              | С                                | С | C | 0 | 0 | 0 |                    |

|----|----------------|----------------------------------|---|---|---|---|---|--------------------|

| CP | J Sta<br>Iress | cles:<br>ates:<br>sing:<br>Lags: | : |   | r |   |   | .W/12+3W)<br>.rect |

RST n (Restart) ((SP) - 1) <-- (PCH) ((SP) - 2) <-- (PCL) (SP) <-- (SP) -2 (PC) <-- 8 \* (NNN) where NNN binary = n decimal The Program Counter is PUSHed onto the Stack, then set to 8\*n.

|                                                      | 1   | 1  | 1  | 1  |    |    |   |   |            |   |    |   |   |   |   |

|------------------------------------------------------|-----|----|----|----|----|----|---|---|------------|---|----|---|---|---|---|

| Mem. Cycles:<br>CPU States:<br>Addressing:<br>Flags: |     |    |    |    |    |    |   |   | 2+3<br>ind |   | ct |   |   |   |   |

| 1                                                    | 5 ] | L4 | 13 | 12 | 11 | 10 | 9 | 8 | 7          | 6 | 5  | 4 | 3 | 2 | 1 |

| 10                                                   | (   | )  | 0  | 0  | 0  | 0  | 0 | 0 | 0          | 0 | N  | N | N | 0 | 0 |

Program Counter After Restart

PCHL

(Jump H and L indirect - move H and L to PC)

0

0

.

(PCH) <--- (H)

(PCL) <-- (L) The content of register H is moved to the high order eight bits of register PC. The content of register L is moved to the low order eight bits of register PC. This effects a branch to the address contained in HL.

| T |   |   |   |   | 1 |   | l | <u> </u> | Т |

|---|---|---|---|---|---|---|---|----------|---|

|   | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0        | 1 |

| 1 |   |   |   |   |   |   |   |          |   |

| Mem. Cycles:<br>CPU States: | 1<br>7 (6+1W) |

|-----------------------------|---------------|

| Addressing:                 | register      |

| Flags:                      | none          |

#### Stack, I/O, and Machine Control Group:

This group of instructions performs I/O, manipulates the Stack, and alters internal control flags.

Unless otherwise specified, condition flags are not affected by any instructions in this group.

#### PUSH rp

(Push)

((SP) - 1) < -- (rh)((SP) - 2) < -- (r1)

(SP) <→ (SP) -2

The content of the high order register of register pair rp is moved to the memory location whose address is one less than the content of register SP. The content of the low order register of register pair rp is moved to the memory location whose address is two less than the content of register SP. The content of register SP is decremented by 2. Register pair rp = SP may not be specified.

| T |   |   | 1 | 1 | 1 |   |   |   | T |

|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | R | Р | 0 | 1 | 0 | 1 | 1 |

| 1 |   |   |   |   |   |   |   |   | 1 |

| Cycles:     |  |

|-------------|--|

| States:     |  |

| Addressing: |  |

| Flags:      |  |

3 15 (12+3W) reg. indirect none

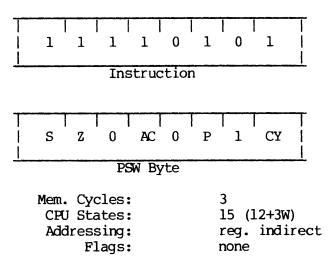

PUSH PSW

(Push processor status word)

$((SP) - 2) \le PSW$ The Accumulator is PUSHed onto the Stack. A Program Status Word (PSW) byte is created from the condition flags and PUSHed onto the Stack.

POP rp (Pop)

(r1) <-- ((SP))

(rh) <-- ((SP) + 1)

(SP) <-- (SP) + 2

The content of the memory location, whose address is specified by the

content of register SP, is moved to the low order register of register pair

rp. The content of the memory location, whose address is one more than the

content of register SP, is moved to the high order register of register

pair rp. The content of register SP is incremented by 2. Register pair rp =

SP may not be specified.</pre>

|   |   |   |   |   | 1 | 1 | 1 |   |

|---|---|---|---|---|---|---|---|---|

| 1 | 1 | R | Р | 0 | 0 | 0 | 1 | 1 |

|   |   |   |   |   |   |   |   |   |

Mem. Cycles: CPU States: Addressing: Flags: 3 13 (10+3W) reg. indirect none

#### POP PSW

(Pop processor status word)

flags <-- (SP) (A) <-- ((SP)) + 1) (SP) <-- (SP) + 2

The PSW byte is POP'd from the Stack and the processor flags are copied from this byte. The Accumulator is POP'd from the Stack.

| Τ |   |   |   |   |   |   |   | [ | Τ |

|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

|   |   |   |   |   |   |   |   |   |   |

Instruction

| Τ |   |   |   | Τ  |   |   |   |    | Т |

|---|---|---|---|----|---|---|---|----|---|

| 1 | S | Z | 0 | AC | 0 | Ρ | 1 | CY |   |

| 1 |   |   |   |    |   |   |   |    |   |

PSW Byte

Mem. Cycles: CPU States: Addressing: Flags: 3 13 (10+3W) reg. indirect Z,S,P,CY,AC (Exchange stack top with H and L)

(L)  $\langle -- \rangle$  ((SP))

(H)  $\langle -- \rangle$  ((SP) + 1)

The content of the L register is exchanged with the content of the memory location whose address is specified by the content of register SP. The content of the H register is exchanged with the content of the memory location whose address is one more than the content of register SP.

Mem. Cycles:5CPU States:21 (16+5W)Addressing:reg. indirectFlags:none

SPHL

XTHL

(Copy HL to SP)

(SP) <— (H) (L)

The contents of register pair HL (16 bits) is copied to double register SP.

| 1   | 1            | 1                                | 1 | 1 | 0 | 0                      | 1            |  |

|-----|--------------|----------------------------------|---|---|---|------------------------|--------------|--|

| Ado | Sta<br>Iress | cles:<br>ites:<br>sing:<br>.ags: | : |   | r | 7 (6-<br>regis<br>none | +1W)<br>ster |  |

EI (Enable Interrupts) The interrupt system is enabled following the execution of the next instruction.

| 1           | 1   | 1                       | 1 | 1 | 0 | 1         | 1    |  |

|-------------|-----|-------------------------|---|---|---|-----------|------|--|

| Mem.<br>CPU | Sta | cles:<br>ates:<br>.ags: |   |   |   | (4<br>one | +1W) |  |

DI (Disable interrupts) The interrupt system is disabled immediately following the execution of the DI instruction.

| 1           | 1   | 1                    | 1 | 0 | 0 | 1           | 1    |  |

|-------------|-----|----------------------|---|---|---|-------------|------|--|

| Mem.<br>CPU | Sta | les:<br>tes:<br>ags: |   |   |   | (4-<br>ione | +1W) |  |

HLT (Halt) The processor is stopped. The registers and flags are unaffected.

| T        |      |     |      |   |   |   |   | 1 | T |

|----------|------|-----|------|---|---|---|---|---|---|

| I        | 0    | 1   | 1    | 1 | 0 | 1 | 1 | 0 | I |

| <u> </u> |      |     |      |   |   |   |   |   |   |

|          | Mem. | Cvo | les: |   |   |   | L |   |   |

| ment. | Cycres. | 1  |        |

|-------|---------|----|--------|

| CPU   | States: | 6  | (5+1W) |

|       | Flags:  | nc | one    |

NOP (No op) No operation is performed. The registers and flags are unaffected.

| T<br> <br> | 0           | 0   | 0                       | 0 | 0 | 0 | 0                  | 0    |  |

|------------|-------------|-----|-------------------------|---|---|---|--------------------|------|--|

|            | Mem.<br>CPU | Sta | cles:<br>ates:<br>Lags: | : |   |   | l<br>5 (4-<br>none | +1W) |  |

#### INPUT/OUTPUT INSTRUCTIONS

All Input/Output instructions on the OP-IR are two byte instructions. The first byte is the operation code (either IN or OUT). The second byte is a code number which indicates a function to be performed. Certain devices also require a data byte in the Accumulator which further specifies the function. Many of the functions operate differently depending upon the devices to which they are directed.

Certain I/O function codes operate independently of any device. These codes are as follows:

| OPCODE | OPERAND | MNEMONIC | FUNCTION                                                                                                                                                                                                                                                |

|--------|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN     | 02      | IIN      | Reads the OP-1R Interrupt<br>Status Register into the<br>Accumulator.                                                                                                                                                                                   |

| IN     | 03      | FIXL     | Reads the contents of FIXED<br>DATA SWITCH 1 into the<br>Accumulator.                                                                                                                                                                                   |

| IN     | 04      | FIX2     | Reads the contents of FIXED<br>DATA SWITCH 2 into the<br>Accumulator.                                                                                                                                                                                   |

| OUT    | 00      | INIT     | Stop all current devices<br>and clears and initializes<br>all devices.                                                                                                                                                                                  |

| OUT    | 01      | SEL      | Causes all subsequent<br>Device Specific I/O<br>instructions to be directed<br>to the device whose add<br>ress is in the Accumulator<br>when OUT O1 is issued.<br>(Selects a device.) This<br>device will be referred to<br>later as the <u>CURRENT</u> |

DEVICE.

| OPCODE | OPERAND | MNEMONIC | FUNCTION                                                         |

|--------|---------|----------|------------------------------------------------------------------|

| OUT    | ОСН     | SMSK     | Sets the current interrupt mask to the value in the Accumulator. |

| OUT    | 0 DH    | BEEP     | Causes the audible (beep) alarm to be sounded.                   |

| OUT    | 0EH     | CLICK    | Causes an audible click.                                         |

Device Specific I/O Instructions should only be issued after a Device has been selected via an OUT Ol instruction.

| OPCODE            | OPERAND        | MNEMONIC             | FUNCTION                                                                                                                                                                                                |

|-------------------|----------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN                | 00             | IFL                  | Reads a byte of status information from the currently selected device into the accumulator.                                                                                                             |

| IN                | 01             | INP                  | Reads a byte of data from the currently selected device into the accumulator.                                                                                                                           |

| OUT               | 02             | OUT                  | Outputs a byte of data to the currently selected device from the Accumulator.                                                                                                                           |

| OUT               | 03             | DVCL                 | Issues a Device Clear Signal which stops and resets the <u>currently</u> selected device                                                                                                                |

| OUT               | 04             | OFL                  | Output a byte of Flags or Control<br>information to the currently<br>selected device from the<br>accumulator.                                                                                           |

| OUT<br>OUT<br>OUT | 05<br>06<br>07 | COM1<br>COM2<br>COM3 | Are used to output different<br>classes of command bytes<br>to the <u>currently selected device</u> .<br>These instructions are usually<br>interpreted differently depending<br>on the device selected. |

Note: The following sections refer to I/O instructions by their mnemonic name. The Ontel assembler recognizes I/O commands only if both opcode (in, out) and operand (i.e. 00H or mnemonic IFL, if IFL is equated to 00H) are specified.

Device Address assignments are listed below.

| ADDRESS | DEVICE                   |

|---------|--------------------------|

|         |                          |

| FO      | Asynchronous I/O Adapter |

| El      | Keyboard                 |

| 2B      | Alternate I/O Adapter    |

| OF      | Parallel Input           |

| 18      | Parallel Output          |

|         | ,                        |

# 3R-42. Device Address Assignments

.

#### SECTION 4R

#### INTERRUPT CONTROLLER

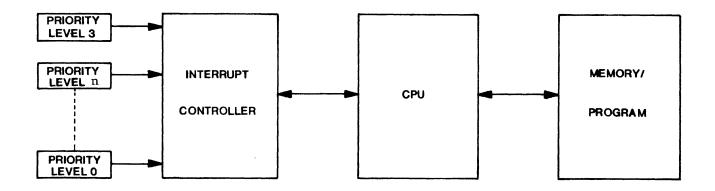

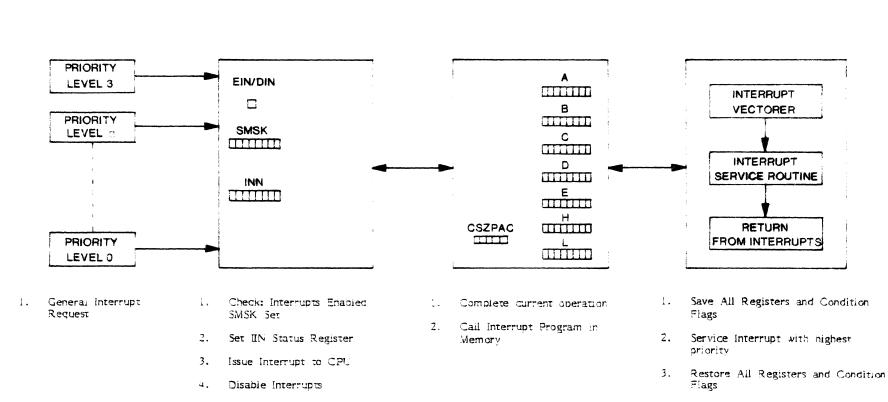

The interrupt controller processes all interrupt requests issued by the individual devices. The OP-1/R is designed for a maximum of four hardware interrupt requests from the main logic board and four more from an option board. The interrupt priorities and selection of device(s) from which to accept interrupts are program controlled. Figure 4R-1 illustrates the OP-1/R interrupt structure.

Figure 4R-1. OP-1/R Interrupt Structure

The following conditions have to be met before the interrupt controller will issue an interrupt request to the CPU:

- 1. Interupt request from a device present.

- 2. Interrupts enabled.

1

3. Interrupt mask bit set corresponding to the interrupt request.

After receiving the interrupt request, the CPU will complete its present instruction and then call location 038 (Interrupt Program) in memory using one level of pushdown stack. The existing CPU environment and registers can be saved during interrupt processing in main memory. If two interrupts occur simultaneously, the priorities are serviced in the order determined by the program. The sequence of interrupt operations is illustrated in Figure 4R-2.

CPU

MEMORY/

PROGRAM

Figure 4R-2. Op-1/R Interrupt Sequence of Operations

4R-2

DEVICE

CONTROLLERS

INTERRUPT

CONTROLLER

<sup>4.</sup> Return to Program in process and Enable Interrupts

#### Table 4R-1 lists standard OP-1/R interruptt assignments:

| PRIORITY LEVEL | FUNCTION                 |

|----------------|--------------------------|

| 4 (highest)    | Alternate I/O Adapter    |

| 3              | Parallel Input/Output    |

| 2              | Asynchronous-Receive     |

| 1              | Asynchronous-Transmit    |

| 0              | Keyboard/Real Time Clock |

### Table 4R-1. OP-1/R Interrupt Assignment

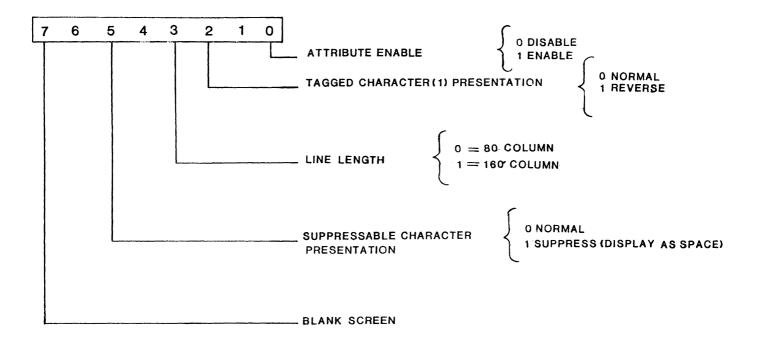

#### COMMANDS

ENABLE INTERRUPTS

Command: EI

Command Byte: None

Enables all interrupts. Interrupt enable is set after the first instruction following EI is executed. It is reset by a DI instruction or by the hardware when any interrupt is processed.

#### DISABLE INTERRUPTS

Command: DT

Command Byte: None

Disables all interrupts.

SET INTERRUPT MASK

Command: OUT SMSK

Command Byte:

- Bit 4 Alternate I/O Adapter

- Parallel Input/Output Bit 3

- Bit 3 Bit 2 Bit 1 Asynchronous-Receive

- Asynchronous-Transmit

- Bit 0 Keyboard/Real Time Clock

Selects the device(s) from which to accept interrupts by setting the corresponding bit(s) in the SMSK Register to a "1".

#### INTERRUPT STATUS

Command: IN IIN

#### Status Byte:

- Bit 4 Alternate I/O Adapter

- Bit 3 Parallel Input/Output

- Bit 2 Asynchronous-Receive

- Bit 1 Asynchronous-Transmit

- Bit 0 Keyboard/Real Time Clock

Loads the contents of the Interrupt Status Register into the accumulator. If the corresponding bit(s) of the SMSK register are set, the Interrupt Status Register bit(s) are set to a "1" when an interrupt request is detected by the CPU. Each bit is reset by the appropriate interrupt Service Routine.

Bits 3-7 will be a "1", if options using these bits are not installed.

#### STORE/RESTORE CPU STATUS

Prior to servicing an interrupt, the status of the CPU can be saved by transferring the condition flags and register contents to the stack by means of the PUSH instruction.

After the interrupt has been serviced, the CPU status can be restored by means of the POP instruction.

#### SECTION 5R

#### FIXED DATA SWITCHES

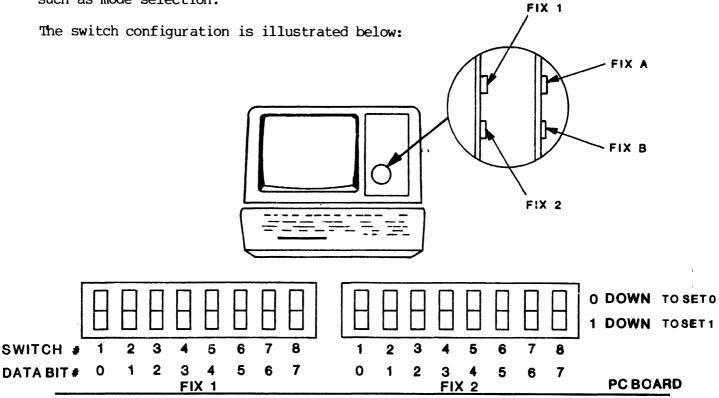

Two eight-bit fixed data switches have been provided for general programming purposes. The switches can be manually set at the time of installation to specify the particular OP-1/R identifying address or any other general function such as mode selection.

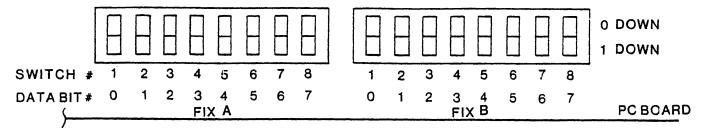

Figure 5R-1. Fixed Data Switches

COMMANDS

The following commands can be executed:

INPUT DATA

Command: IN FIX1

Transfers the contents of the FIX1 switch to the Accumulator. The content of switch Bit n is loaded into Accumulator Bit n-1.

Command: IN FIX2

Transfers the contents of the FIX2 switch to the Accumulator. The content of switch Bit n is loaded into Accumulator Bit n-1.

#### SECTION 6R

#### KEYBOARD AND REAL TIME CLOCK