STD 7000

7705 32K EPROM Memory Card

**USER'S MANUAL**

#### NOTICE

The information in this document is provided for reference only. Pro-Log does not assume any liability arising out of the application or use of the information or products described herein.

This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of Pro-Log, nor the rights of others.

Printed in U.S.A. Copyright © 1981 Pro-Log Corporation, Monterey, CA 93940. All rights reserved. However, any part of this document **may be reproduced** with Pro-Log Corporation cited as the source.

## **STD 7000**

7705 32K EPROM Memory Card

**USER'S MANÙAL**

#### FOREWORD

This manual explains how to use Pro-Log's 7705 32K EPROM Memory Card. It is structured to reflect the answers to basic questions that you, the user, might ask yourself about the 7705. We welcome your suggestions on how we can improve our instructions.

The 7705 is part of Pro-Log's Series 7000 STD BUS hardware. Our products are modular, and they are designed and built with second-sourced parts that are industry standards. They provide the industrial manager with the means of utilizing his own people to control the design, production, and maintenance of the company's products that use STD BUS hardware.

Pro-Log supports its products with thorough and complete documentation. Also, to provide maximum assistance to the user, we teach courses on how to design with, and to use, microprocessors and the STD BUS products.

You may find the following Pro-Log documents useful in your work: *Microprocessor User's Guide* and the *Series 7000 STD BUS Technical Manual*. If you would like a copy of these documents, please submit your request on your company letterhead.

### Contents

$\bigcirc$

.

•

.

.

|                                       | Page |

|---------------------------------------|------|

| Foreword                              |      |

| Figures                               | iv   |

| -                                     |      |

| Section 1 - Purpose and Main Features | 1-1  |

| Section 2 - Installation and Specifications | 2-1 |

|---------------------------------------------|-----|

| Introduction                                | 2-1 |

| Address Mapping                             | 2-3 |

| Jumper Options Affecting MEMEX              | 2-5 |

| Jumper Options Affecting Segment Select     |     |

| Electrical and Environmental Specifications | 2-5 |

| Mechanical Specifications                   | 2-5 |

| Section 3 - Operation and Programming | 3-1  |

|---------------------------------------|------|

| Introduction                          | 3-1  |

| MEMEX                                 |      |

| MEMEX System Memory Example           |      |

| MEMEX Control Software                |      |

| MEMEX Interrupt Control Software      | 3-8  |

| Segment Select                        | 3-10 |

| Segment Select Control Software       | 3-14 |

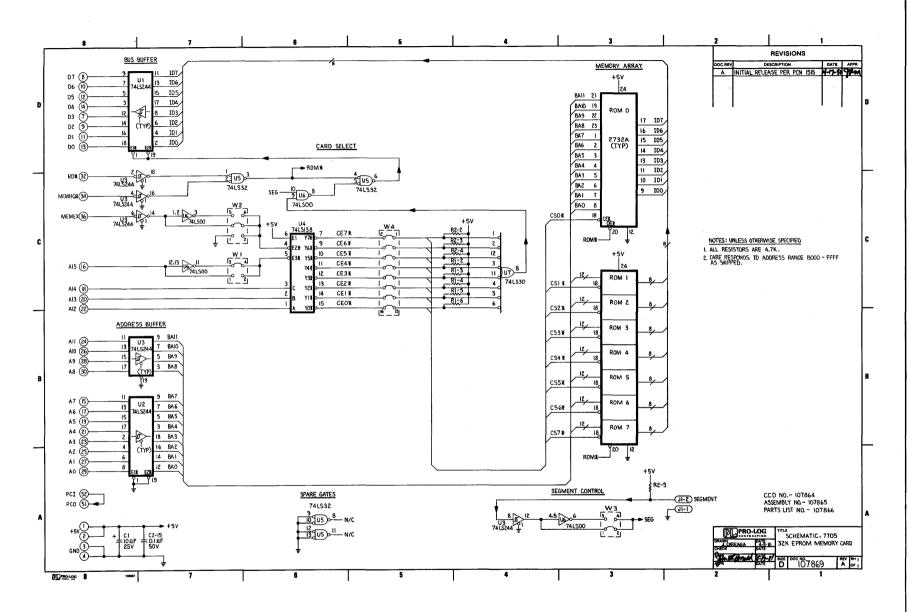

| Section 5 - Maintenance      | 5-1   |

|------------------------------|-------|

| Reference Drawings           | 5-2,3 |

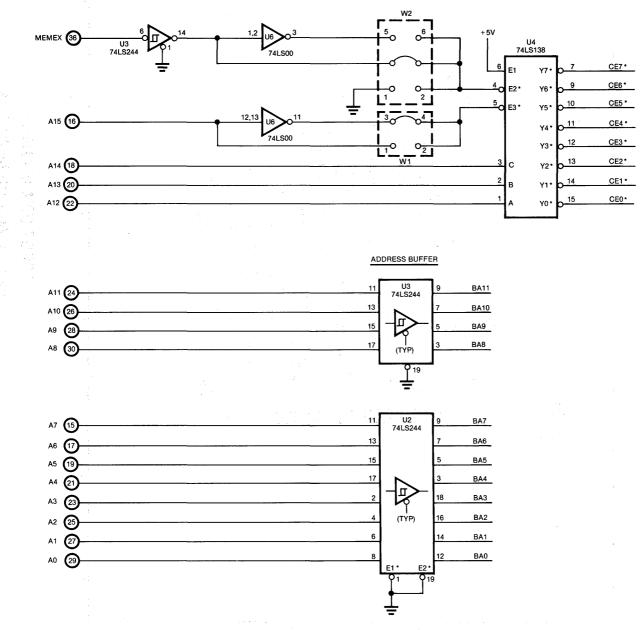

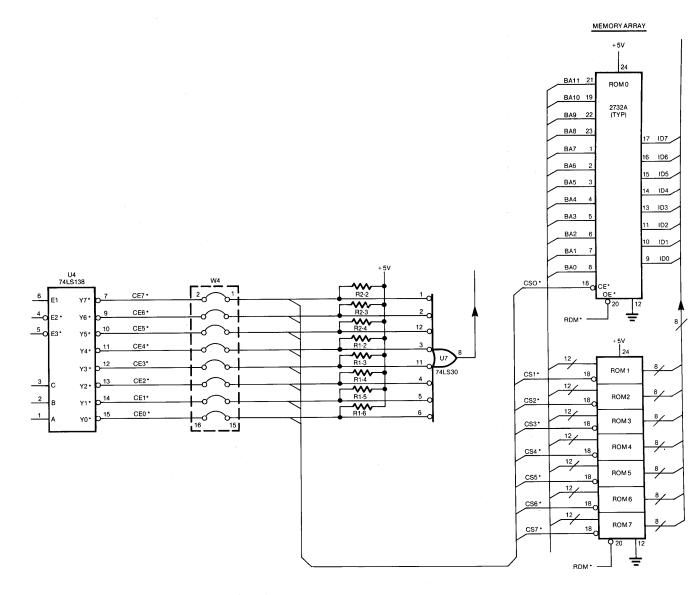

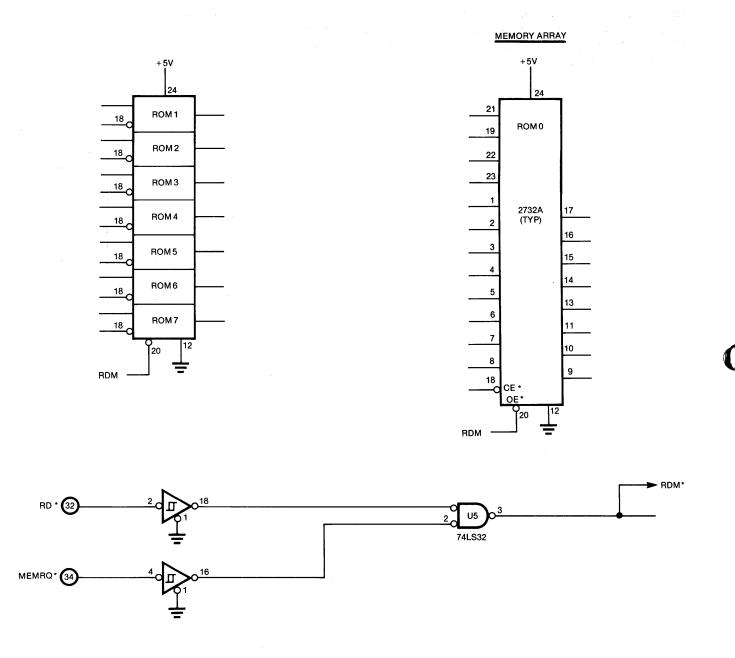

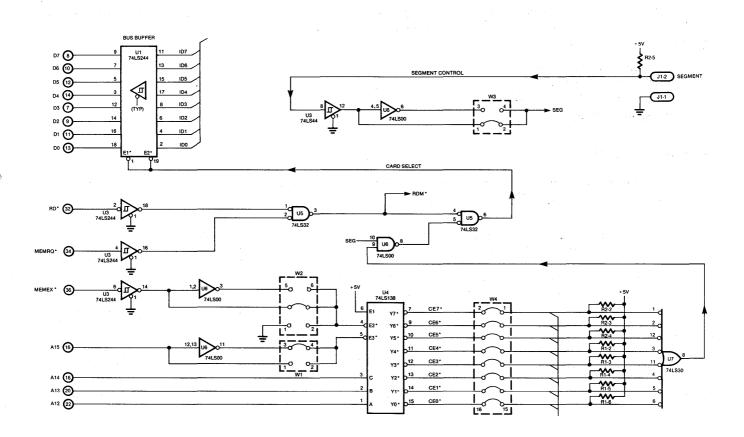

| Address Decoding Circuit     | 5-4   |

| Chip-Enable Circuit          | 5-5   |

| Output-Enable Circuit        |       |

| Data Bus Buffer Circuit      | 5-7   |

| Signal Glossary              | 5-8   |

| Internal Signals             | 5-9   |

| Return for Repair Procedures | 5-10  |

iii

## Figures

I)

•

| F | igure |                                                                                  | Page |

|---|-------|----------------------------------------------------------------------------------|------|

|   | 1-1   | 7705 32K EPROM Memory Card                                                       | 1-1  |

|   | 1-2   | Block Diagram of 7705 32K EPROM Memory Card                                      | 1-2  |

|   | 2-1   | Installation of 7705 Card in STD BUS Card Rack                                   | 2-1  |

|   | 2-2   | Segment Select Connection — 7705 Installation                                    | 2-2  |

|   | 2-3   | Main Components of the 7705                                                      | 2-3  |

|   | 2-4   | Memory Mapping Options for the 7705                                              | 2-4  |

|   | 2-5   | Operating Limits of Electrical and Environmental Parameters for 7705 Card        | 2-6  |

|   | 2-6   | STD BUS Electrical Specifications Over Recommended Operating Limits for the 7705 |      |

| ÷ | 2-7   | 7705 Segment Connector Pin List                                                  | 2-6  |

|   | 2-8   | 7705 Edge Connector Pin List                                                     | 2-7  |

|   | 2-9   | 7705 Address Access Timing                                                       | 2-8  |

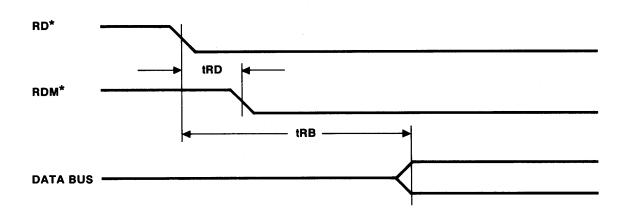

|   | 2-10  | 7705 RD Access Timing                                                            | 2-9  |

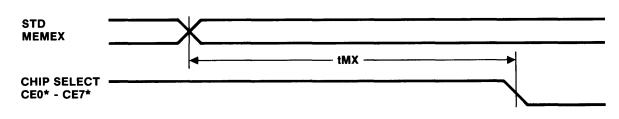

|   | 2-11  | 7705 MEMEX Timing                                                                | 2-9  |

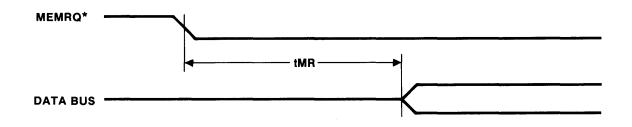

|   | 2-12  | 7705 MEMRQ Timing                                                                | 2-10 |

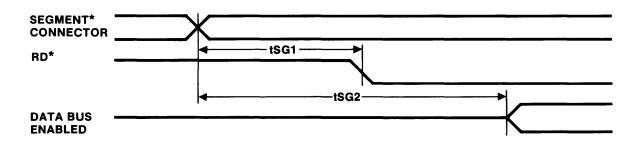

|   | 2-13  | 7705 Segment Timing                                                              | 2-10 |

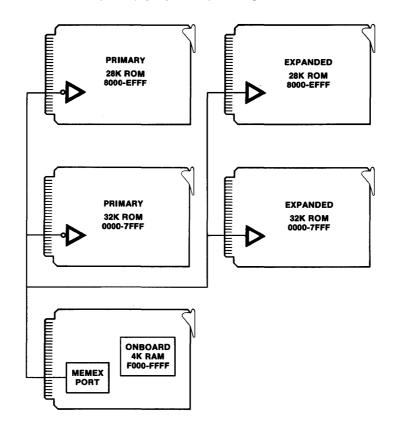

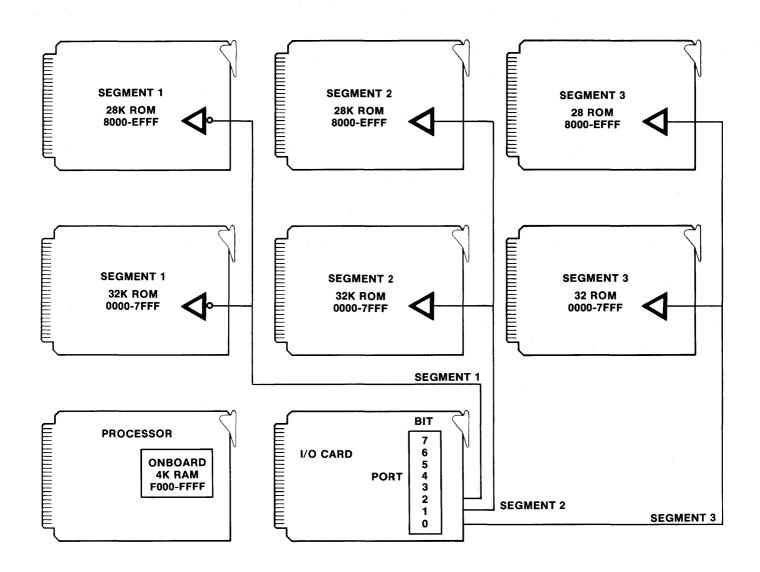

|   | 3-1   | MEMEX Example for the 7705, Showing 124K Memory System                           | 3-1  |

|   | 3-2   | Example 1 of MEMEX Software for the 7705                                         | 3-2  |

|   | 3-3   | Example 2 of MEMEX Software for the 7705                                         |      |

|   | 3-4   | Example 3 of MEMEX Software for the 7705                                         | 3-4  |

|   | 3-5   | Running Example 3 Software for the 7705                                          | 3-5  |

|   | 3-6   | Example 4 of MEMEX Software for the 7705                                         | 3-6  |

|   | 3-7   | Running Example 4 Software for the 7705                                          | 3-7  |

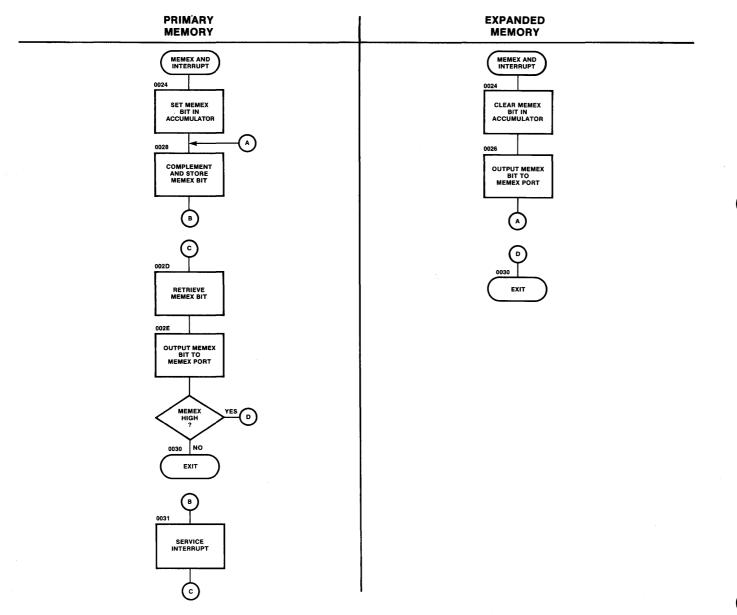

|   | 3-8   | Flowchart — MEMEX Interrupt Control Software                                     | 3-8  |

|   | 3-9   | Example of MEMEX Interrupt Software, Primary Memory, for the 7705                | 3-9  |

|   | 3-10  | Example of MEMEX Interrupt Software, Expanded Memory, for the 7705               | 3-9  |

|   | 3-11  | Example 1 of Segment Select for the 7705                                         | 3-11 |

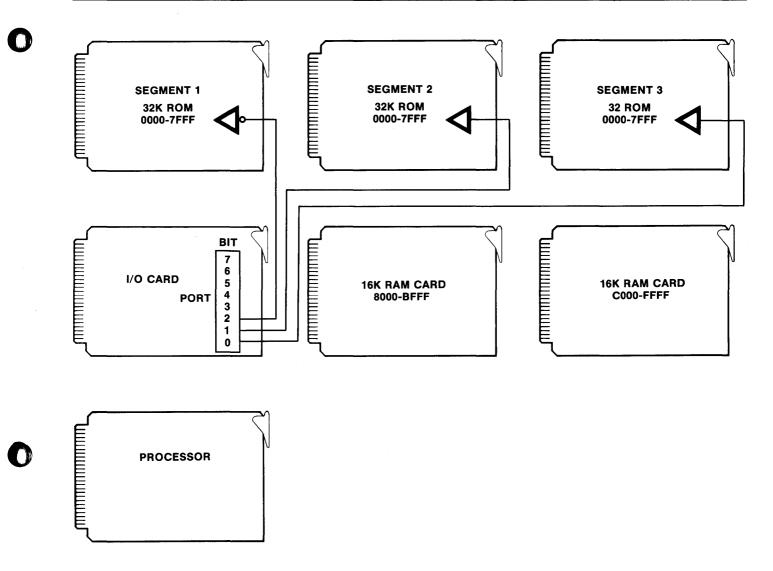

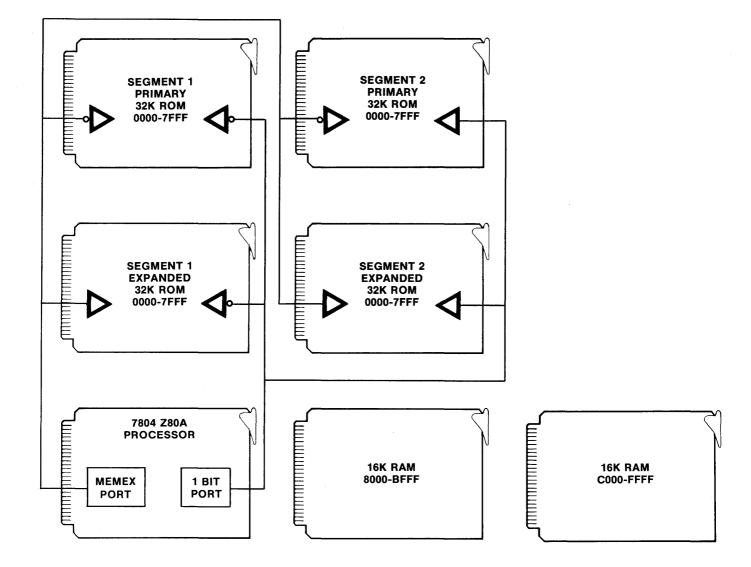

|   | 3-12  | Example 2 of Segment Select for the 7705, Showing 184K Memory System             | 3-12 |

|   | 3-13  | Example 3 of Segment Select Combination for the 7705, Showing 160K Memory System | 3-13 |

| ÷ | 3-14  | Example 1 of Segment Control Software for the 7705                               | 3-14 |

|   | 5-1   | Schematic for 7705 (Reference Only)                                              | 5-2  |

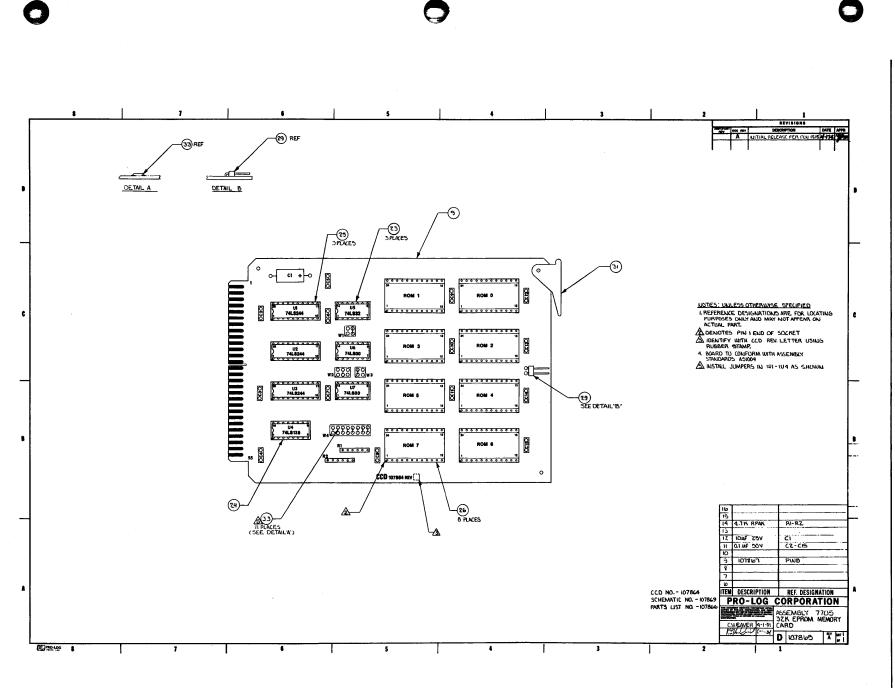

|   | 5-2   | Assembly for 7705 (Reference Only)                                               | 5-3  |

|   | 5-3   | Address Decoding Circuit for the 7705                                            | 5-4  |

|   | 5-4   | Chip-Enable Circuit for the 7705                                                 | 5-5  |

|   | 5-5   | Output-Enable Circuit for the 7705                                               | 5-6  |

|   | 5-6   | Data-Bus Buffer Circuit for the 7705                                             | 5-7  |

## SECTION 1 Purpose and Main Features

#### Purpose

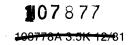

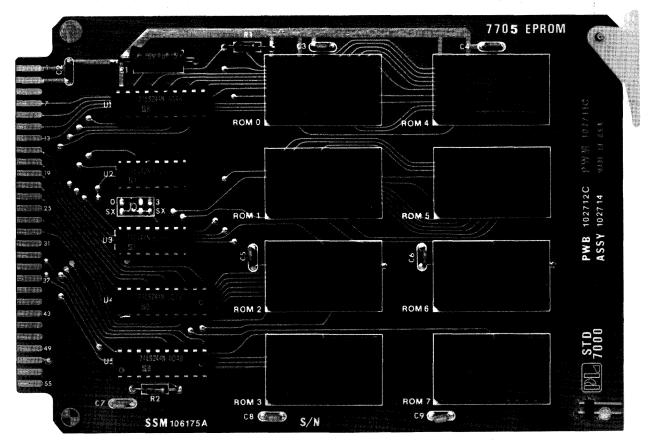

The 7705 Card (Fig. 1-1) provides the user with eight sockets for 2732/2732A EPROMs, giving a total 32K bytes of memory. The memory resides in one continuous block, which can be mapped to either the upper or lower half of a 64K memory system. (See Fig. 1-2 for the block diagram.)

The 7705 can respond to the STD BUS MEMEX line, allowing two cards to reside in the same address field. A system using four 7705 cards, plus a Pro-Log processor card capable of controlling MEMEX, provides 124K bytes of memory with no additional cards or signal lines.

Also, the 7705 can respond to an external segment select line, allowing its use in large-scale bank select schemes. The segment select line can be controlled by a memory segment controller or by I/O ports. One output port controls eight 7705 cards. Also, the 7705 can be tailored to fit small-scale applications. Unused sockets can be disabled, allowing the card to occupy as little as 4K bytes of memory space, which can be mapped anywhere within a 64K-byte system.

#### Main Features

- Eight 2732/A EPROM sockets 32K-byte capacity

- User-selectable memory mapping

- No wasted memory space unused sockets can be disabled

- Responds to STD BUS MEMEX line

- Responds to external segment select line

- Processor independent use with 8085, Z80, 6800, 8088, and others.

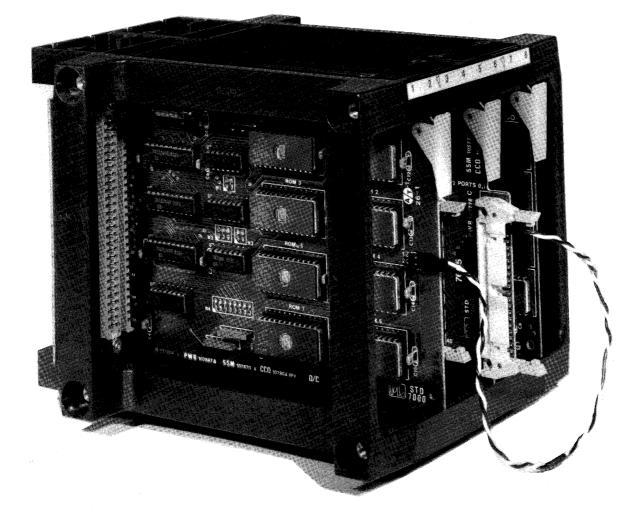

Figure 1-1. 7705 32K EPROM Memory Card

Figure 1-2. Block Diagram of 7705 32K EPROM Memory Card.

## SECTION 2 Installation and Specifications

#### Introduction

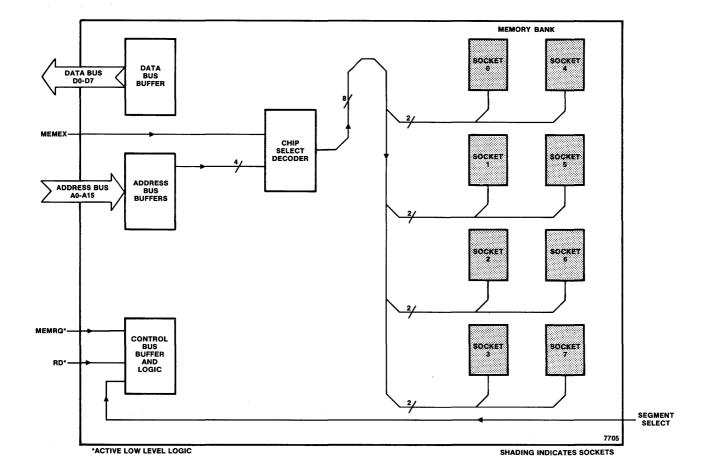

The 7705 operates as part of an STD BUS card rack system. You can plug it directly into the STD BUS backplane, as shown in Fig. 2-1. Optionally, you can extend it from the motherboard with a 7901 card extender. Plug the 7901 into any slot in the card rack and then plug the 7705 into the connector on the 7901; this gives you access to the 7705 for testing or other purposes.

#### CAUTION

To prevent possible damage to your STD BUS system, make sure that power is off before inserting a card into the card rack, or before removing a card from the card rack.

Figure 2-1. Installation of 7705 Card in STD BUS Card Rack.

#### Installation and Specifications

The 7705 can occupy any slot in the card cage. Install it with the card ejector towards the top of the card rack as shown in Fig. 2-1.

If you use the external segment select line, attach it as shown in Fig. 2-2, using a two-pin 0.1-inch center connector. The twisted pair cable (Pro-Log RC704 or equivalent) consists of one signal line and one ground line for added noise immunity. It can connect the 7705 to an I/O card such as Pro-Log's 7605.

Figure 2-2. Segment Select Connection — 7705 Installation.

#### Address Mapping

The 7705 card occupies 32K bytes of memory space. It decodes 16 address lines and can reside in either the upper or lower half of a 64K-memory system.

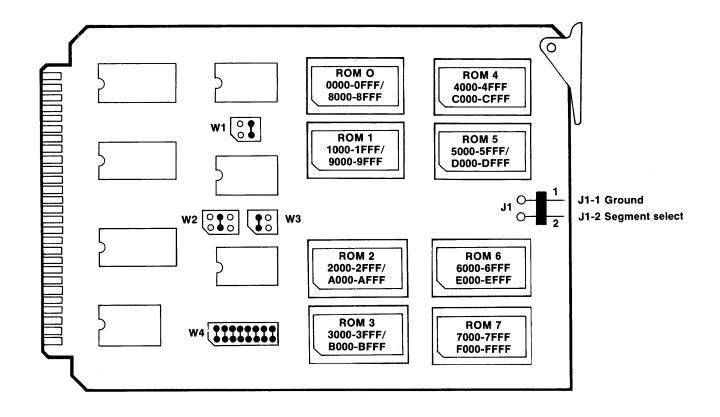

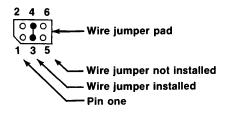

As shipped from the factory, the 7705 occupies memory addresses 8000-FFFF. By way of jumper W1, shown in Fig. 2-3, the card's address mapping can be changed so that it occupies memory addresses 0000-7FFF. If you change it, remove jumper W1 from position 3-4 and replace it with one at position 1-2.

If you use less than the full 32K bytes of memory, disable the unused sockets by removing the proper wire jumpers. Jumper W4, positions 15-16 through 1-2 correspond to sockets 0-7, respectively (Fig. 2-3).

Figure 2-3. Main Components of the 7705

When a socket is disabled, the chip-enable signal is disconnected from the socket. Also, the data-bus buffer no longer responds to memory requests in the address range of the unused socket. This means that memory on other cards in the system can occupy this address space without interference from the 7705 card. For a full description of how this works, see "Chip-Enable Circuit," Section 5.

Any number and combination of sockets may be disabled. By this method, you can configure the 7705 card to occupy as little as 4K of memory space. These 4K blocks can occupy adjacent address fields or they can be widely separated. They can be mapped anywhere within a 64K-memory system on the natural 4K boundaries.

Figure 2-4 shows some of the possible mapping options and how to configure the wire jumpers for each option.

|                         |     |     | JU  | MPE   | RS I | NST   | ALL   | ED    |       |       |                                                                          |  |

|-------------------------|-----|-----|-----|-------|------|-------|-------|-------|-------|-------|--------------------------------------------------------------------------|--|

| ADDRESS<br>RANGE        |     | V1  |     |       | v    | V4 PO | SITIO | N     |       |       | COMMENTS                                                                 |  |

| RANGE                   | 1-2 | 3-4 | 1-2 | 3-4   | 5-6  | 7-8   | 9-10  | 11-12 | 13-14 | 15-16 |                                                                          |  |

| 0000-0FFF               | •   |     |     |       |      |       |       |       |       | •     |                                                                          |  |

| 0000-1FFF               | •   | :   |     |       |      |       |       |       | •     | •     | There are over 500 possible mapping combinations. A few of the most com- |  |

| 0000-2FFF               | •   |     |     |       |      |       |       | •     | •     | • 5   | monly used combinations, and a few examples of how the 7705 can be used  |  |

| 0000-3FFF               | •   |     |     |       |      |       | •     | •     | •     | •     | in situations requiring extreme flexibility are shown here.              |  |

| 0000-4FFF               | •   |     |     |       |      | •     | •     | •     | •     | •     | are shown here.                                                          |  |

| 0000-5FFF               | •   |     | -   |       | •    | •     | •     | •     | •     | •     |                                                                          |  |

| 0000-6FFF               | ٠   |     |     | •     | •    | •     | •     | •     | •. •  | •     |                                                                          |  |

| 0000-7FFF               | ٠   |     | •   | • , • |      |       | •     | •     | •     | •     |                                                                          |  |

| 0000-8FFF               |     | ٠   | -   |       |      |       |       |       | -     | •     |                                                                          |  |

| 8000-9FFF               |     | •   |     | -     | -    |       |       |       | •     | •     |                                                                          |  |

| 8000-AFFF               |     | ٠   |     |       |      |       |       | •     | •     | •     |                                                                          |  |

| 8000-BFFF               |     | ٠   |     |       |      |       | •     | •     | •     | •     |                                                                          |  |

| 8000-CFFF               |     | ٠   |     |       |      | •     | •     | •     | •     | •     |                                                                          |  |

| 8000-DFFF               |     | ٠   |     |       | •    | •     | •     | •     | •     | •     |                                                                          |  |

| 8000-EFFF               |     | ٠   |     | •     | •    | •     | •     | •     | •     | •     |                                                                          |  |

| 8000-FFFF               |     | •   | •   | •     | •    | •     | •.    | •     | •     | •     | Standard configuration                                                   |  |

| 3000-3FFF               | •   |     |     |       |      |       | •     |       |       |       | Example of how minimum 4K can be mapped anywhere.                        |  |

| F000-FFFF               |     | ٠   | •   |       |      |       |       |       |       |       | For 6800 series start-up program or for bootstrap                        |  |

| 0000-0FFF/<br>7000-7FFF | •   |     | •   |       |      |       |       |       |       | •     | Example of noncontinuous memory mapping.                                 |  |

Symbol • means jumper installed.

Figure 2-4. Memory Mapping Options for the 7705.

#### Jumper Options Affecting MEMEX

The function and operation of the MEMEX line are described in Section 3. This subsection explains the jumper options that affect MEMEX.

As shipped, the 7705 card is enabled when MEMEX is low. To reverse the card's polarity, remove jumper W2 from position 3-4 and replace it with one at position 5-6 (see Fig. 2-3 for the jumper's location). When using two 7705 cards that are both going to occupy the same address field, change the polarity on one of the cards.

Make sure that the MEMEX line is not left floating. The line must be either controlled by some other card in the system, or tied to ground on the 7705 itself. Pro-Log's processor cards either control the MEMEX line or simply tie it to ground. If there is no card in the system controlling MEMEX, or if you want the card to disregard MEMEX, remove jumper W2 from position 3-4 and replace it with one at position 1-2; this will tie the line to ground and permanently enable the card.

#### **Jumper Options Affecting Segment Select**

The function and operation of the segment select line are described in Section 3. This subsection explains the jumper options that affect the segment select line.

Segment select is not a part of the STD BUS. It is an external line. When you use it, connect it on the card ejector side of the 7705 (see Fig. 2-2).

Use a two-pin 0.1-inch center connector to attach the line to the 7705. Also, use a twisted pair cable, consisting of one signal line and one ground line for added noise immunity (see Fig. 2-3 for the signal and ground pins).

An I/O card, such as Pro-Log's 7605, along with an RC 704 cable can be used to control the line. One output bit or output line per 7705 card is required. Thus, one output port can control eight 7705 cards.

As shipped, the card is enabled when the segment select line is in the high state. The card's polarity can be reversed by removing jumper W3 from position 1-2 and replacing it with one at position 3-4 (see Fig. 2-3).

With jumper W3 in position 1-2, the segment select line can be left unconnected. A pull-up resistor on the line will hold it in the active condition. However, if jumper W3 is in position 3-4, the line must be controlled in some manner, or the card will remain permanently disabled.

#### **Electrical and Environmental Specifications**

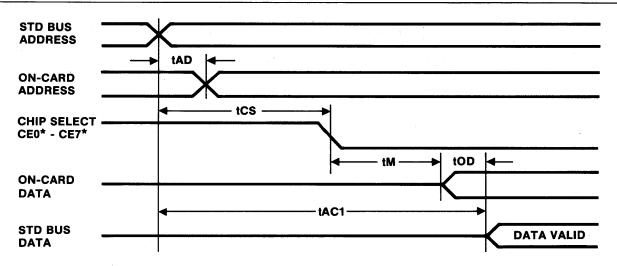

See Figs. 2-5 through 2-8 for the 7705's electrical and environmental specifications. Timing diagrams are shown in Figs. 2-9 through 2-13.

#### **Mechanical Specifications**

The 7705 card meets all general mechanical specifications of the STD BUS.

#### Installation and Specifications

|        |                         | RECOMMEN | IDED OPERAT | TING LIMITS | ABSOLUTE NONOPERATING LIMITS |      |      |  |

|--------|-------------------------|----------|-------------|-------------|------------------------------|------|------|--|

| SYMBOL | PARAMETER               | MIN      | ΤΥΡ         | MAX         | MIN                          | MAX  | UNIT |  |

| Vcc    | Supply voltage          | 4.75     | 5.00        | 5.25        | 0                            | 5.50 | v    |  |

| TA     | Free-air temperature    | 0        | +25         | +55         | -40                          | +75  | °C   |  |

| RH     | Humidity <sup>[1]</sup> | 5        | —           | 95          | 0                            | 95   | %RH  |  |

#### **Electrical and Environmental Specifications**

<sup>[1]</sup> Noncondensing.

#### Figure 2-5. Operating Limits of Electrical and Environmental Parameters for 7705 Card.

| SYMBOL | PARAMETER           | MIN   | ТҮР     | МАХ          | UNIT<br>mA |  |

|--------|---------------------|-------|---------|--------------|------------|--|

| lcc    | Vcc supply current  | —     | 300     | 600          |            |  |

| ·      | STD BUS input load  | See F | ig. 2-8 | See Fig. 2-8 |            |  |

|        | STD BUS output load | See F | ig. 2-8 | See Fig. 2-8 |            |  |

NOTE: Assumes all memory sockets loaded with one selected and seven in standby. For unused 2732A sockets, subtract 150mA maximum selected or 30mA maximum in standby.

Figure 2-6. STD BUS Electrical Specifications Over Recommended Operating Limits for the 7705.

| PIN N                    | UMBER | PIN NUMBER |   |                     |  |

|--------------------------|-------|------------|---|---------------------|--|

| INPUT (LSTTL DRIVE       | E)    | ר          |   | INPUT (LSTTL DRIVE) |  |

| MNEMONIC                 |       |            |   | MNEMONIC            |  |

| SEGMENT <sup>[1]</sup> 5 |       | 2          | 1 | GROUND              |  |

[1] Selectable logic polarity.

#### Figure 2-7. 7705 Segment Connector Pin List.

|                      | PIN NU   | MBER |    |    | PIN NUMBER |      |                     |  |  |

|----------------------|----------|------|----|----|------------|------|---------------------|--|--|

| OUTPUT (LSTTI        | L DRIVE) |      |    |    |            | OUTF | PUT (LSTTL DRIVE)   |  |  |

| INPUT (LSTTL LOAD    | )S)      |      |    |    |            |      | INPUT (LSTTL LOADS) |  |  |

| MNEMONIC             | $\neg$   |      |    |    |            |      | MNEMONIC            |  |  |

| +5V                  | Vcc      |      | 2  | 1  |            | Vcc  | +5V                 |  |  |

| GROUND               | GND      |      | 4  | 3  |            | GND  | GROUND              |  |  |

| -5V                  |          |      | 6  | 5  |            |      | -5V                 |  |  |

| D7                   |          | 55   | 8  | 7  | 55         |      | D3                  |  |  |

| D6                   |          | 55   | 10 | 9  | 55         |      | D2                  |  |  |

| D5                   |          | 55   | 12 | 11 | 55         |      | D1                  |  |  |

| D4                   |          | 55   | 14 | 13 | 55         |      | D0                  |  |  |

| A15                  | 2        |      | 16 | 15 |            | 1    | A7                  |  |  |

| A14                  | 1        |      | 18 | 17 |            | 1    | A6                  |  |  |

| A13                  | 1        |      | 20 | 19 |            | 1    | A5                  |  |  |

| A12                  | 1        |      | 22 | 21 |            | 1    | A4                  |  |  |

| A11                  | 1        |      | 24 | 23 |            | 1    | A3                  |  |  |

| A10                  | 1        |      | 26 | 25 |            | 1    | A2                  |  |  |

| A9                   | 1        |      | 28 | 27 |            | 1    | A1                  |  |  |

| A8                   | 1        | -    | 30 | 29 |            | 1    | A0                  |  |  |

| RD*                  | 1        |      | 32 | 31 |            |      | WR*                 |  |  |

| MEMRQ*               | 1        |      | 34 | 33 |            |      | IORQ*               |  |  |

| MEMEX <sup>[1]</sup> | 1        |      | 36 | 35 |            |      | IOEXP               |  |  |

| MCSYNC*              |          |      | 38 | 37 |            |      | REFRESH*            |  |  |

| STATUS 0*            |          |      | 40 | 39 |            |      | STATUS 1*           |  |  |

| BUSRQ*               |          |      | 42 | 41 |            |      | BUSAK*              |  |  |

| INTRQ*               |          |      | 44 | 43 |            |      | INTAK*              |  |  |

| NMIRQ*               |          |      | 46 | 45 |            |      | WAITRQ*             |  |  |

| PBRESET*             |          |      | 48 | 47 |            | ·    | SYSRESET*           |  |  |

| CNTRL*               |          |      | 50 | 49 |            |      | CLOCK*              |  |  |

| PCI                  | IN       |      | 52 | 51 | OUT        |      | PCO                 |  |  |

| AUX GND              |          |      | 54 | 53 |            |      | AUX GND             |  |  |

| AUX -V               |          |      | 56 | 55 |            |      | AUX +V              |  |  |

\* Active low-level logic

•

•

.

[1] Open-collector driver

| SYMBOL | PARAMETER                         | MIN | ТҮР | МАХ |

|--------|-----------------------------------|-----|-----|-----|

| tAC1   | Minimum safe access time for read | 175 |     |     |

| tAD    | Address buffer time delay         |     | 15  | 30  |

| tCS    | Chip select logic time            |     | 35  | 60  |

| tOD    | Data bus buffer time delay        |     | 15  | 30  |

| tM     | Data buffer enable time           |     | 60  | 100 |

All times given in nanoseconds. Above times assume that RD<sup>\*</sup>, MEMRQ<sup>\*</sup>, MEMEX, and SEGMENT<sup>\*</sup> are active before STD BUS address becomes valid.

Figure 2-9. 7705 Address Access Timing.

| SYMBOL | PARAMETER                             | ТҮР | МАХ |

|--------|---------------------------------------|-----|-----|

| tRD    | Time RD* till RDM*                    | 25  | 50  |

| tRB    | Time RD* till data bus buffer enabled |     | 100 |

All times given in nanoseconds. RD<sup>\*</sup> can go active up to 115 ns after MEMRQ<sup>\*</sup>, and up to 125 ns after address valid, without affecting access time. If RD<sup>\*</sup> comes later, add the time to the minimum access time of the card. Normally RD<sup>\*</sup> goes true during the memory device access time and, therefore, does not affect access time for the card.

Figure 2-10. 7705 RD\* Access Timing.

| SYMBOL | PARAMETER                                | ТҮР | МАХ |

|--------|------------------------------------------|-----|-----|

| tMX    | Time MEMEX active to chip select* active | 45  | 75  |

All times given in nanoseconds. The above parameter is true if all other signals are active before MEMEX goes active.

Figure 2-11. 7705 MEMEX Timing.

| SYMBOL | PARAMETER                                       | ТҮР | МАХ |

|--------|-------------------------------------------------|-----|-----|

| tMR    | Time MEMRQ* active till data-bus buffer enabled |     | 100 |

All times given in nanoseconds.

Figure 2-12. 7705 MEMRQ\* Timing.

| SYMBOL | PARAMETER                                  | ТҮР | MAX |

|--------|--------------------------------------------|-----|-----|

| tSG1   | SEGMENT* active to RD*                     | 40  | 65  |

| tSG2   | SEGMENT* active to data bus driver enabled | 70  | 120 |

All times given in nanoseconds. The above parameters are true if all other signals are active before  $\mathsf{SEGMENT}^*$  goes active.

Figure 2-13. 7705 Segment Timing.

## SECTION 3 Operation and Programming

#### Introduction

This section describes the functions and use of the 7705 card, which is designed to be a versatile part of your memory system.

The 7705 is suitable for both small- and large-scale applications. By using the memory size and mapping options described in Section 2, and the MEMEX and segment select lines described in this section, the 7705 can fill the ROM memory requirements of virtually any system.

#### MEMEX

The MEMEX line is a part of the STD BUS. It is used as a memory bank select line, allowing two banks of memory to occupy the same address field. Only one of the banks is selected at a time, depending on the logic state of the MEMEX line.

MEMEX is normally controlled by a memory segment controller, or by an output port. The segment controller or output port can be either on the processor card, or on some other card in the system. Some Pro-Log processor cards have an onboard output port for controlling MEMEX.

**MEMEX System Memory Example.** An example of how MEMEX can be used is shown in Fig. 3-1. It displays a 124K memory system, comprising 4K of RAM and 120K of ROM. The RAM is on the processor card and is permanently enabled, i.e., it ignores MEMEX. The ROM is in two 60K banks. Each bank consists of two 7705 cards. Only two cards are enabled at a time: two on the left when MEMEX is low, and two on the right when MEMEX is high.

At power-up, the MEMEX port is low; therefore, the primary memory bank is enabled. The processor can then choose primary or expanded memory simply by manipulating the MEMEX line.

Figure 3-1. MEMEX Example for the 7705, showing 124K Memory System.

**MEMEX Control Software.** The software for controlling MEMEX requires some special consideration, to prevent problems with the processor when changing memory banks. These problems can be dealt with in a number of ways, as exemplified in this subsection.

**Example 1:** In many systems that use MEMEX, it will be to your advantage to keep some section of memory permanently enabled, i.e., a section that disregards MEMEX. This may be a section of ROM memory at the low-order addresses, or a section of RAM that stores registers, program variables, and the stack, or a section of ROM that contains interrupt service routines for quick accessibility at all times.

If your system has a permanently enabled section of memory, locate the MEMEX control software in this section. If the section is ROM, the software simply resides in ROM. If the section is RAM, the processor can load the software into RAM. Store the software in ROM, disk, or some other nonvolatile memory. The processor should load the software into RAM as part of the power-up initialization process.

Using the memory system in Fig. 3-1 as a model, a program could be written like the one shown in Fig. 3-2, which depicts two programs: one to jump to a subroutine in expanded memory and one to jump to a subroutine in primary memory. The program assumes that you jump from a main program in one bank to a subroutine in the other bank. The address of the subroutine you are jumping to must be in the H, L register pair. The program selects the proper memory bank and jumps to the subroutine. When the subroutine is exited, the processor returns to the MEMEX control program, which reselects the original bank and then returns to the program from which it came.

| NERMONCTITLE MEMEX SOFTWARE EX. DATEPAGEINSTRMODIFIERTITLE MEMEX SOFTWARE EX.DATEPAGELABELINSTRMODIFIERCOMMENTSCOMMENTSPAGELABELINSTRMODIFIERTSET MEMEX HIGH, ENAPLES101-O1Expanded Memory2D3OPA-XX3XX-XXYPORT ADDRESS4E5PSPH,LTPUSH RETURN ADDRESS521LDP1H,LON TO STACK6EA-N7EF-N8E3XCPTH,LY9E9JPN(H,L)Y9E9JPN(H,L)Y9E9JPN(H,L)Y0XX-XX9E9DAR10XX-XX9PORT ADDRESS10XX-11OO-12D3OPA13XX-140152116D317D318OO19RT19D319OPA10XX10T11OO12D313OPA14Y15EXT16D317D418D                                                           |    |     |        | PRO-LOG   | G CORPORAT | ΓΙΟΝ                                   |      |          | PROGRAM ASSEMBLY FORM                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|--------|-----------|------------|----------------------------------------|------|----------|---------------------------------------|

| FFE03E(TO BXP.)LDAIT SET MEMEX HIGH, ENABLES101-01EXPANDED MEMORY2D3OPA-3XX-XX $\checkmark$ PORT ADDRESS4E5PSPH,LT PUSH RETURN ADDRESS (FFEA)521LDP1H,LON TO STACK6EA-I7EF-I8E3XCPTH,LY9E9JPN(H,L)Y9E9JPN(H,L)Y0XX0XX0XX10XX7EF-0XX7EF-8C0-9OPA-9XX-10XX-7EF-10XX-7EF-10XX-1100-12D3OPA13XX-14E5PSP1521LDPI16FA-17EF-18E3XCPT19H,LT PUSH RETURN ADDRESS (FFFA)10SIDPI11OPAI12D3OPA13XX-14 <td></td> <td></td> <td>IAL</td> <td></td> <td>MNEMONIC</td> <td></td> <td></td> <td>LE I</td> <td>MEMEY SAETWARE BY DATE</td> |    |     | IAL    |           | MNEMONIC   |                                        |      | LE I     | MEMEY SAETWARE BY DATE                |

| 101-0101-012030PA3XX-3XX-4E5PSP4E5PSP521LDPI4H,LN7EF-7EF-8E3XCPT9E9JPN9E9JPN10T9E9JPN11T8E39OPA9PRIMARY MEMORY10-11T11T12D313OPA14-15C16-17F17F18OPA19RTS19RTS10-10-10-11T11T12S13OPA14C15PSP14HAL15PSP15PSP16-17EF18C19DPI19H,L10-11T12DSP13XX14E515PSP14E515PSP14E515PSP <td></td> <td></td> <td>INSTR.</td> <td>LABEL</td> <td>INSTR.</td> <td>MODIFIER</td> <td></td> <td>he (in 1</td> <td>COMMENTS</td>                                                                                                            |    |     | INSTR. | LABEL     | INSTR.     | MODIFIER                               |      | he (in 1 | COMMENTS                              |

| 2D3OPA3XX-XX4E5PSP4E5PSP521LDPI7EF-7EF-8E3XCPT9E9JPN9E9JPN0T9E90C0C0C0C0C0C0C0C0C0C0C0C0C0C0C0C0C0C00C0C0C0C10C11C11C12C13C14C14C15C15C16C17C18C19C19C10C10C11C12C13C14C15C15C16C17C18C19C19C10C10C11C <td>FF</td> <td>E o</td> <td>3E</td> <td>(TO EXP.)</td> <td>LDA</td> <td>I</td> <td></td> <td>7 -</td> <td>SET MEMEX HIGH, ENABLES</td>                                                                                                                                                                           | FF | E o | 3E     | (TO EXP.) | LDA        | I                                      |      | 7 -      | SET MEMEX HIGH, ENABLES               |

| 3XXXX $\checkmark \rightarrow PORT ADDRESS$ 4E5PSPH,LTPUSH RETURN ADDRESS (FFEA)521LDPIH,LON TO STACK6EAN7EFN9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7JPN(H,L)Y9E7DDPRIMARY MEMORY0CD3OPAY                                                                                                                                                                                                                                                         |    | 1   | 01     |           | -          | 01                                     |      |          | EXPANDED MEMORY                       |

| aEsPSPH,LPUSH RETURN ADDRESS (FFEA)521LDPIH,LON TO STACK6EA-I7EF-8E3XCPT9E9JPN9E9JPN0TSET MEMEX LOW ENABLES800-0XX-0XX-7E7E9C0A10XX11T11T12SET MEMEX LOW ENABLES13OPA14C15C16T17F17F18C19A19T10T10T11T11T12A13T14C15T15T16FA17EF18E319C19JPN10T11T12SEROUTINE AT H,L13Y14C15T15LDPI16FA17EF18E319JPN11T11T12SEROUTINE AT H,L13Y14FORT ADDRESS <td></td> <td>2</td> <td>D3</td> <td></td> <td>OPA</td> <td></td> <td></td> <td>1</td> <td></td>                                                                           |    | 2   | D3     |           | OPA        |                                        |      | 1        |                                       |

| 521LDPIH,LON TO STACK6EA07EF08E3XCPTH,LV9E9JPN(H,L)VA3ELDAIA3ELDAITSET MEMEX LOWENABLESBOOCD3OPADXXFFFTSET MEMEX LOW, ENABLESTFFOPRIMARY MEMORY2D3OPAYPRIMARY MEMORY2D3OPA3XXYPRIMARY MEMORY2D3OPA3XXYYPORT ADDRESS4E5PSPH,LTPUSH RETURN ADDRESS (FFFA)521LDPIH,LYSE3XCPTH,LYSESEDDXXPORT ADDRESSBO1ECD3OPAVPORT ADDRESSBO1 </td <td></td> <td>3</td> <td>XX</td> <td></td> <td>-</td> <td>××</td> <td></td> <td>1</td> <td>-PORT ADDRESS</td>                                                                           |    | 3   | XX     |           | -          | ××                                     |      | 1        | -PORT ADDRESS                         |

| 6EA-N7EF-N9E9JPN(H,L)YA3ELDAIASELDAITSET MEMEX LOW ENABLESBOO-OOPAYCD3OPADXX-FIFIFIIOPAFIFIFIIIIIFIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII <t< td=""><td></td><td>4</td><td>E5</td><td></td><td>PSP</td><td>HL</td><td></td><td>- 1</td><td>PUSH RETURN ADDRESS (FFEA)</td></t<>                                                                                                                                                                                         |    | 4   | E5     |           | PSP        | HL                                     |      | - 1      | PUSH RETURN ADDRESS (FFEA)            |

| 7EF-N8E3XCPTH,LY9E9JPN(H,L)YA3ELDAITSET MEMEX LOW ENABLESBOO-CD3OPADXX-XXYPORT ADDRESSEC9RTSF-JOPAF-G3EYPORT ADDRESSEC9RTSEXITF-GSE1OOVPRIMARY MEMORY2D3OPA3XX4E5PSPH,LPORT ADDRESS4E5PSPH,LONTO STACK6FA8E3XCPTH,L9E9JPNHL)YJUMP TO SUBROUTINE ATH,LA 3ELDAISCITH,LYSCITKSCITKSCITKSCITKSCITKKSCITKKKKKKKKKKKK<                                                                                                                                                                                                         |    | 5   | 21     |           | LDPI       | H,L                                    | D    |          | ON TO STACK                           |

| 7EF-N8E3XCPTH,LY9E9JPN(H,L)YA3ELDAITSET MEMEX LOW ENABLESBOO-CD3OPADXX-XXYPORT ADDRESSEC9RTSF-JOPAF-G3EYPORT ADDRESSEC9RTSEXITF-GSE1OOVPRIMARY MEMORY2D3OPA3XX4E5PSPH,LPORT ADDRESS4E5PSPH,LONTO STACK6FA8E3XCPTH,L9E9JPNHL)YJUMP TO SUBROUTINE ATH,LA 3ELDAISCITH,LYSCITKSCITKSCITKSCITKSCITKKSCITKKKKKKKKKKKK<                                                                                                                                                                                                         |    | 6   | EA     |           | -          | ······································ | - IJ |          |                                       |

| A $3E$ LDAIISET MEMEX LOWENABLESB0000PRIMARY MEMORYCD3OPAVPORT ADDRESSEC9RTSEXITF-NF-N1002D3OPA3XX4E5PSP4E5PSP7EF7EF8E3XCPTH,L9E9JPN(HL)4SEBOPAVTEFCPSPH,LV </td <td></td> <td>7</td> <td>EF</td> <td></td> <td>-</td> <td></td> <td>N</td> <td>1</td> <td></td>                                                                                                                                                                                                                                                         |    | 7   | EF     |           | -          |                                        | N    | 1        |                                       |

| A $3E$ LDAIISET MEMEX LOWENABLESB0000PRIMARY MEMORYCD3OPAVPORT ADDRESSEC9RTSEXITF-NF-N1002D3OPA3XX4E5PSP4E5PSP7EF7EF8E3XCPTH,L9E9JPN(HL)4SEBOPAVTEFCPSPH,LV </td <td></td> <td>8</td> <td>E3</td> <td></td> <td>XCPT</td> <td>H,L</td> <td>2</td> <td>1</td> <td></td>                                                                                                                                                                                                                                                   |    | 8   | E3     |           | XCPT       | H,L                                    | 2    | 1        |                                       |

| cD3OPAHDXX-XX $-$ PORT ADDRESSEC9RTSEXITFF100-2D3OPA3XX-4E5PSP4E5PSP7EF7EF8E3XCPTH,L9E9JPN(HL)4SECD3CPRIMARY MEMORYS21LDPIH,LF-7EF8E3XCPTH,LYJUMP TO SUBROUTINE AT H,LA 3ELDAITSOPADXX-EXPANDED MEMORYCD3OPA-DXX-EXIT                                                                                                                                                                                                                                                                                                    |    | 9   | E9     |           | JPN        | (H,L)                                  | 9    | ī        | JUMP TO SUBROTINE AT HIL              |

| cD3OPAHDXX-XX $-$ PORT ADDRESSEC9RTSEXITFF100-2D3OPA3XX-4E5PSP4E5PSP7EF7EF8E3XCPTH,L9E9JPN(HL)4SECD3CPRIMARY MEMORYS21LDPIH,LF-7EF8E3XCPTH,LYJUMP TO SUBROUTINE AT H,LA 3ELDAITSOPADXX-EXPANDED MEMORYCD3OPA-DXX-EXIT                                                                                                                                                                                                                                                                                                    |    | A   | 3E     |           | LDA        | I                                      | 5    | -        | SET MEMEX LOW ENABLES                 |

| cD3OPAHDXX-XX $-$ PORT ADDRESSEC9RTSEXITFF100-2D3OPA3XX-4E5PSP4E5PSP7EF7EF8E3XCPTH,L9E9JPN(HL)4SECD3CPRIMARY MEMORYS21LDPIH,LF-7EF8E3XCPTH,LYJUMP TO SUBROUTINE AT H,LA 3ELDAITSOPADXX-EXPANDED MEMORYCD3OPA-DXX-EXIT                                                                                                                                                                                                                                                                                                    |    | В   | 00     |           |            | 00                                     | 3    |          | PRIMARY MEMORY                        |

| EC9RTS $\land$ EXITFIIT SET MEMEX LOW, ENABLES100-I2D3OPAI3XX-I3XX-I4E5PSPH,L521LDPI4E5PSP7EF-8E3XCPT9E9JPN9E9JPN0-EXPANDED8OPA9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9 <t< td=""><td></td><td>С</td><td>D3</td><td></td><td>OPA</td><td></td><td>1S</td><td></td><td></td></t<>                                                                                                                                                                                      |    | С   | D3     |           | OPA        |                                        | 1S   |          |                                       |

| EC9RTS $\land$ EXITFIIT SET MEMEX LOW, ENABLES100-I2D3OPAI3XX-I3XX-I4E5PSPH,L521LDPI4E5PSP7EF-8E3XCPT9E9JPN9E9JPN0-EXPANDED8OPA9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9F9 <t< td=""><td></td><td>D</td><td></td><td></td><td>-  </td><td>XX</td><td>17</td><td>1</td><td>- PORT ADDRESS</td></t<>                                                                                                                                                                       |    | D   |        |           | -          | XX                                     | 17   | 1        | - PORT ADDRESS                        |

| F 03E(TO PRI.)LDAI $\stackrel{\circ}{}$ SET MEMEX LOW, ENABLES100-0PRIMARY MEMORY2D30PA $\stackrel{\circ}{}$ $\stackrel{\circ}{}$ 3XX- $\stackrel{\circ}{}$ $\stackrel{\circ}{}$ 4E5PSPH,LT521LDPIH,LONTO STACK6FA7EF8E3XCPTH,L $\stackrel{\circ}{}$ 9E9JPN(HL) $\stackrel{\circ}{}$ 9E9JPN(HL) $\stackrel{\circ}{}$ 801- $\stackrel{\circ}{}$ 0 $\stackrel{\circ}{}$ EXPANDED MEMORY0XX- $\stackrel{\circ}{}$ 0XX- $\stackrel{\circ}{}$ 0FA- $\stackrel{\circ}{}$ 10XX- $\stackrel{\circ}{}$ 20RT5EXIT                  |    | E   | ٢٩     |           | RTS        |                                        | 5    |          |                                       |

| 100- $\bigcirc$ PRIMARY MEMORY2D3OPA $\bigcirc$ 3XX- $\bigvee$ PORT ADDRESS4E5PSPH,LPUSH RETURN ADDRESS (FFFA)521LDPIH,LON TO STACK6FA7EF8E3XCPTH,L $\bigvee$ 9E9JPN(HL) $\bigvee$ 9E9JPN(HL) $\bigvee$ A 3ELDAISET MEMEX HIGH, ENABLESBOI-EXPANDED MEMDRYCD3OPAIDXX-IEC9RTSEXIT                                                                                                                                                                                                                                         |    | F   |        |           |            |                                        | h    | 1        | · · · · · · · · · · · · · · · · · · · |

| 2D3OPAN3XX- $X$ PORT ADDRESS4E5PSPH,LT521LDPIH,LONTO STACK6FA7EF8E3XCPTH,LY9E9JPN(HL)Y9E9JPN(HL)YBOI-EXPANDED MEMORYCD3OPAIDXX-YEC9RTSEXIT                                                                                                                                                                                                                                                                                                                                                                               |    | FO  | 3E     | (TO PRI.) | LDA        | I                                      | 3    |          | SET MEMEX LOW, ENABLES                |

| 3XX $-$ YPORT ADDRESS4E5P5PH,LTPUSH RETURN ADDRESS (FFFA)521LDPIH,LON TO STACK6FA $-$ I7EF $-$ I8E3XCPTH,LY9E9JPN(HL)YJEF $-$ IA3ELDAITBOI $-$ EXPANDED MEMORYCD3OPAIDXX $-$ YEC9RTSEXIT                                                                                                                                                                                                                                                                                                                                 |    | 1   | 00     |           | -          |                                        | 0    |          | PRIMARY MEMORY                        |

| 4E5PSPH,LTPUSH RETURN ADDRESS (FFFA)521LDPIH,LON TO STACK6FA7EF8E3XCPTH,LY9E9JPN(HL)YA3ELDAITBOI-EXPANDEDMEMDRYCD3OPAIYPKX-YEC9RTSEXIT                                                                                                                                                                                                                                                                                                                                                                                   |    | 2   | D3     |           | OPA        | · · · · · · · · · · · · · · · · · · ·  | D    |          |                                       |

| 4E5PSPH,LTPUSH RETURN ADDRESS (FFFA)521LDPIH,LON TO STACK6FA7EF8E3XCPTH,LY9E9JPN(HL)YA3ELDAITBOI-EXPANDEDMEMDRYCD3OPAIYPKX-YEC9RTSEXIT                                                                                                                                                                                                                                                                                                                                                                                   |    | 3   | XX     |           |            |                                        | X    | 1        | - PORT ADDRESS                        |

| 6FA-7EF-8E3XCPT9E9JPN $(HL)$ $\forall$ JUMP TO SUBROUTINE AT H, LA3ELDABOI-CD3DXX-EC9RTSEXIT                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 4   | E5     |           | PSP        | H,L                                    |      | 1        |                                       |

| 7EF8E3XCPTH,L9E9JPN(HL)A3ELDAIFEXPANDED MEMORYCD3OPADXXEC9RTSEEXIT                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 5   | 21     |           | LDPI       | H,L                                    |      |          | ONTO STACK                            |

| 8       E3       XCPT       H,L       Y         9       E9       JPN       (HL)       Y       JUMP TO SUBROUTINE AT H,L         A       3E       LDA       I       T       SET MEMEX HIGH, ENABLES         B       OI        EXPANDED MEMDRY         C       D3       OPA       I         E       C9       RTS       EXIT                                                                                                                                                                                                |    | 6   | FA     |           | -          |                                        |      |          |                                       |

| 9     E9     JPN     (HL)     ▼     JUMP TO SUBROUTINE AT H, L       A     3E     LDA     I     T     SET MEMEX HIGH, ENABLES       B     01     -     I     EXPANDED MEMDRY       C     D3     OPA     I       D     XX     -     V - PORT ADDRESS       E     C9     RTS     EXIT                                                                                                                                                                                                                                      |    | 7   | EF     |           | -          |                                        |      |          |                                       |

| A     3E     LDA     I     T     SET     MEMEX     HIGH, ENABLES       B     01     -     EXPANDED     MEMDRY       C     D3     OPA     -     EXPANDED     MEMDRY       D     XX     -     V - PORT     ADDRESS       E     C9     RTS     EXIT                                                                                                                                                                                                                                                                         |    | 8   | E3     |           | XCPT       | H,L                                    |      |          | f                                     |

| B     OI      EXPANDED MEMDRY       C     D3     OPA        D     XX      V     PORT ADDRESS       E     C9     RTS     EXIT                                                                                                                                                                                                                                                                                                                                                                                             |    | 9   | E9     |           | JPN        | (HL)                                   |      | Ī        | JUMP TO SUBROUTINE AT H,L             |

| C     D3     OPA       D     XX        E     C9     RTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | A   | 3E     |           | LDA        | I                                      |      |          | SET MEMER HIGH, ENABLES               |

| D     XX     -     V-     PORT ADDRESS       E     C9     RTS     EXIT                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | В   | 01     |           | -          |                                        |      |          | EXPANDED MEMDRY                       |

| E C9 RTS EXIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | с   | D3     |           | OPA        | · · · · · · · · · · · · · · · · · · ·  |      |          | · · · · · · · · · · · · · · · · · · · |

| E C9 RT3 EXIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | D   | хx     |           | - 1        |                                        |      |          | - PORT ADDRESS                        |

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | E   | 6٦     |           | RT5        |                                        |      |          |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | F   |        |           |            |                                        | 1    | J        |                                       |

Figure 3-2. Example 1 of MEMEX Software for the 7705.

**Example 2:** In the first example, it was assumed that when the program jumped from one bank to the other, it jumped to a subroutine. Example 2 depicts a program that jumps from one bank to the other, but not to a subroutine.

Instead, the program simply changes the state of the MEMEX line and then jumps to the address in the H, L register pair. Again the program is divided up into two sections: one that goes from primary to expanded memory, and one that goes from expanded to primary memory.

|             | PRO-LOG CORPORATION |        |         |          |          | PROGRAM ASSEMBLY FORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-------------|---------------------|--------|---------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| HE          | XADECIN             | AL     |         | MNEMONIC |          | TITLE MEMEX SOFTWARE EX. 2 DATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| PAGE<br>ADR | LINE<br>ADR         | INSTR. | LABEL   | INSTR.   | MODIFIER | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| FF          | FO                  | 3E     | TO EXP. | LDA      | I        | SET MEMER HIGH, SELECTS EXPANDED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|             | 1                   | 0      |         | 1        |          | D MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|             | 2                   | D3     |         | OPA      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 3                   | XX     |         | 1        |          | D     MEMORY       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I <td< td=""></td<> |  |  |  |  |

|             | 4                   | F9     |         | JPN      | (H,L)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 5                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 6                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 7                   |        |         |          |          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|             | 8                   |        |         |          |          | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|             | 9                   | 3E     | TOPRI.  | LDA      | I        | T SET MEMEX LOW, SELECTS PRIMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|             | A                   | 00     |         | -        |          | 3 MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|             | В                   | D3     |         | OPA      |          | δ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|             | С                   | XX     |         |          |          | PORT ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|             | D                   | E9     |         | JPN      | (H,L)    | JUMP TO ADDRESS IN H,L PAIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|             | E                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | F                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 0                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 1                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 2                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 3                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 4                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 5                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 6                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 7                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 8                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | 9                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | A                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | В                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|             | С                   |        |         |          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |