# **Technical Manual**

|           | 0000    | 0000    | 0000     | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00000     |

|-----------|---------|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|           | 0 0 0 0 | 0 0 0 0 | 0 0 0 0  | 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|           | 0000    | 0000    | 0000     | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|           | 0 0 0 0 | 0000    | 0000     | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|           | 0000    | 0000    | 0000     | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|           | 0 0 0 0 | 0000    | 0 0 0 0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 0 0 0 0 |

|           |         |         | 0 0 0 0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|           | 0 0 0 0 | 0 0 0 0 | 0 0 0 0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|           | 0 0 0 0 | 0 0 0 0 | 0000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|           | 0 0 0 0 | 0 0 0 0 |          | 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|           | 0000    | 0000    | 0000     | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|           | 0 0 0 0 | 0 0 0 0 | 0000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|           | 0000    | 0000    | 0000     | and the second se |           |

|           | 0000    | 0 0 0 0 |          | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

|           | 0 0 0 0 |         | 0000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|           |         |         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|           | 0 0 0 0 | 0 0 0 0 |          | 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

| 0 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 0 0 0   |

|           | 0 0 0 0 | 0000    |          | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 0 0 0 0 |

|           | 0 0 0 0 | 0000    | 0000     | 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|           | 0000    |         | 0000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00000     |

|           |         |         | <u> </u> | <u>-0 0-0 0-0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

# Introduction

This manual defines the standards that constitute the STD BUS and the parameters which are common to the Series 7000 cards. The Series 7000 Data Sheets are included to illustrate the compatibility of the Series 7000 cards and provide design guidelines and application information.

It is aimed primarily at the professional design engineer who contemplates using the STD BUS in his company's products.

The STD BUS is a concept conceived by Pro-Log Corporation and developed jointly with MOSTEK as a simple bus structure for 8 bit microprocessors. It is a 56 pin bus, logically organized and easily learned. The number of pins and their use is a well thought out compromise between the simplest possible bus and an infinitely flexible bus. The bus was kept simple to facilitate design, production and maintenance. It was made sufficiently flexible to work with all industry standard 8 bit microprocessors and to be used in both dedicated control and data processing applications.

The company using STD BUS hardware in its products generally wants to control the design, production and maintenance of those products with his existing personnel. Pro-Log's Series 7000 hardware helps him attain this goal because these products are modular, standardized, use only second sourced industry standard parts, are thoroughly documented and have a manufacturing rights option which allows Pro-Log customers to produce the STD 7000 products themselves, if they wish.

Pro-Log also teaches courses on how to design with, and use, Microprocessors and the STD BUS products, instruments such as PROM Programmers and System Analyzers with which to manufacture and service STD BUS products.

# THE STD BUS PROVIDES

- Standard 8-Bit Microprocessor BUS Pin Out

- Standard 56 Pin Connector

- Standard 4½"x6½" Card Size

- Standard 1/2" Card Spacing

# THE STD BUS OFFERS

- Multiple Sources

- Unrestricted Use, Not Trademarked, Copyrighted or Patented

- Function Modularity

- Card Slot Independence

- Separate Digital and Analog Power Busses

# THE SERIES 7000 CARDS ADD

- Motherboard Interconnect

- High Functional Density

- Low Power Consumption

- Industry Standard Components

- Second Sourced Components

- Completely Tested Cards

- Power On Burn-In

- RETMA Rack Mounting Compatible Card Cages

- Choice of Microprocessor

The material in this manual is subject to change, and Pro-Log Corporation reserves the right to change specifications without notice.

Copyright © 1979 by Pro-Log Corporation, Monterey, CA 93940. All rights reserved. Printed in the U.S.A. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, or otherwise, without the prior written permission of the publisher.

The information in this manual has been carefully reviewed and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies.

# Series **7000 STD BUS** Technical Manual

i

# **Table of Contents**

| Section 1 TI             | he STD BUS                                                          |

|--------------------------|---------------------------------------------------------------------|

| Introduction             |                                                                     |

| Organization and         | d Functional Specifications 1-2                                     |

| General Specific         | cations                                                             |

| Mechanical Spe           | cifications                                                         |

| Electrical Specif        | ications                                                            |

|                          | ommon Specifications for Series 7000<br>FD BUS Microprocessor Cards |

| Introduction             |                                                                     |

| Mechanical Spe           | cifications 2-2                                                     |

| Temperature Sp           | ecifications 2-3                                                    |

| <b>Electrical Specif</b> | ications                                                            |

| Series 7000 STD          | BUS Timing                                                          |

| Mapping                  |                                                                     |

| Section 3 Section 3      | eries 7000 Data Sheets                                              |

| 7100 System Sup          | oport Card                                                          |

| 7300 Peripheral          | Interface Cards                                                     |

| 7500 Industrial I/       | /O Cards                                                            |

| 7600 Digital (TTI        | L) I/O Cards                                                        |

| 7700 Memory Ca           | ards                                                                |

|                          | Cards                                                               |

|                          | ls 3-39                                                             |

|                          | icks                                                                |

| Edge Card Conn           | nectors                                                             |

|                          |                                                                     |

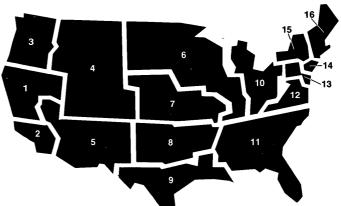

Sales Representatives (Inside Back Cover)

# Section 1 The STD BUS

# Introduction

This section defines the standards that constitute the STD BUS.

The STD BUS standardizes the physical and electrical aspects of modular 8-bit microprocessor card systems, providing a dedicated orderly interconnection scheme. The standardized pinout and 56 pin connector lends itself to a bussed motherboard that permits any card to work in any slot. The STD BUS is dedicated to internal communications, with all other interconnections made via suitable connectors at the I/O interface card edge. The concept gives an orderly signal flow across the cards. Peripheral and I/O devices can be connected to the system according to their own unique connector and cabling requirements.

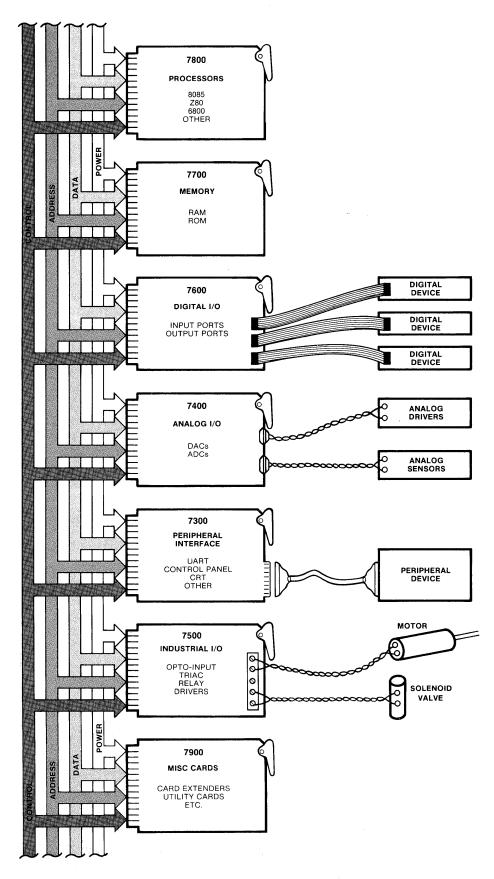

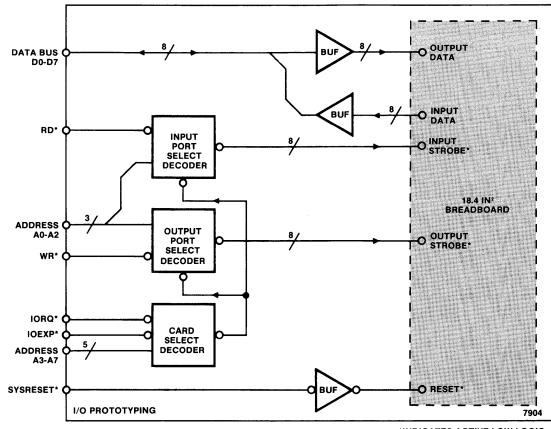

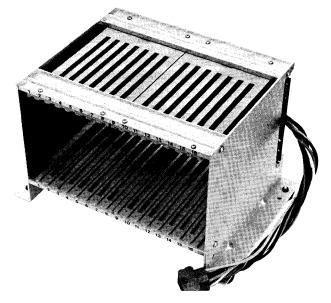

A diagram showing STD BUS implementation with Pro-Log Series 7000 cards is given in Figure 1-1.

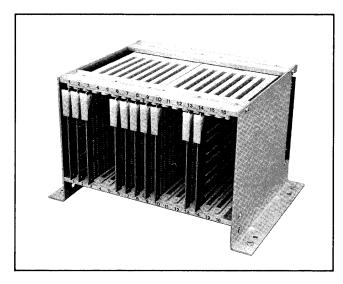

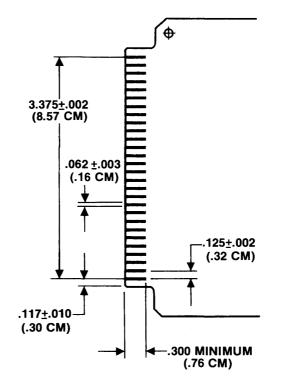

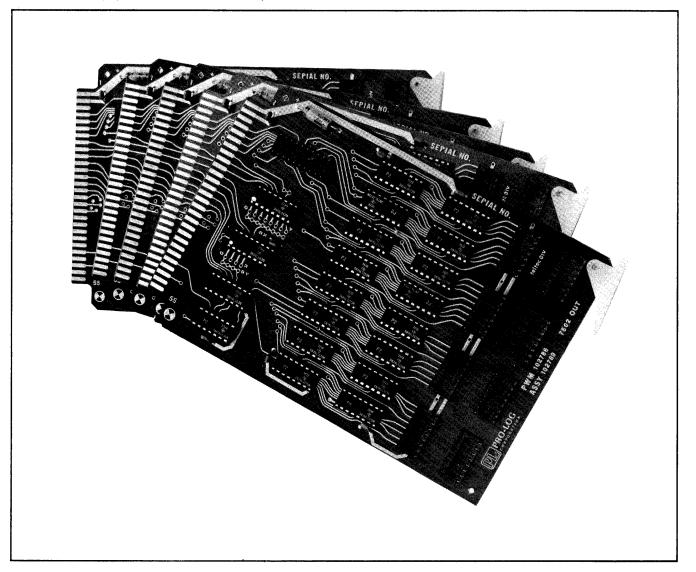

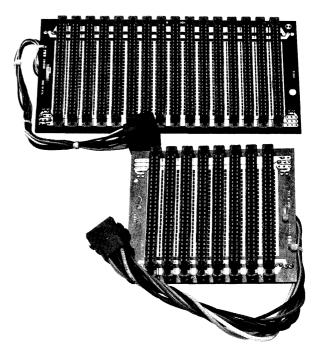

Figure 1-2 and 1-3 show typical hardware implementations of some of the elements of Figure 1-1.

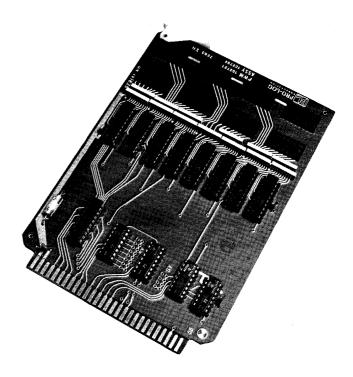

Figure 1-2

# ORGANIZATION AND FUNCTIONAL SPECIFICATIONS (WITH PIN DEFINITIONS)

The STD BUS pinout is organized into five functional groups:

| Logic Power Bus     | Pins 1-6     |

|---------------------|--------------|

| Data Bus            | Pins 7-14    |

| Address Bus         | Pins 15-30   |

| Control Bus         | Pin 31-52    |

| Auxiliary Power Bus | 8 Pins 53-56 |

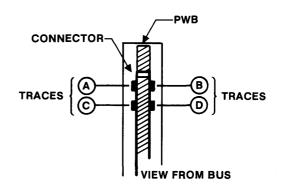

The organization and pinouts are shown in Figure 1-4. This figure gives the mnemonic function and signal flow direction (referenced to the processor card in control of the BUS) for each pin of the STD BUS. The STD BUS is further defined as requiring a 56 pin (dual 28) card edge connector with 0.125 inch pin centers. The connectors are on a standard spacing interval of 0.5 inch centers and accept the standard  $4\frac{1}{2}$ "x $6\frac{1}{2}$ "x0.062" card.

|                       |                                                                |                                                                                                              | COMPONE                                                        | NT SIDE                                                                                                                                                                                                                 |                                                                |                                                                                                  | CIRCUIT                                                   | SIDE                                                                                                                                                                                                                                   |

|-----------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | PIN                                                            | MNEMONIC                                                                                                     | SIGNAL<br>FLOW                                                 | DESCRIPTION                                                                                                                                                                                                             | PIN                                                            | MNEMONIC                                                                                         | SIGNAL<br>FLOW                                            | DESCRIPTION                                                                                                                                                                                                                            |

| LOGIC<br>POWER<br>BUS | 1<br>3<br>5                                                    | +5V<br>GND<br>-5V                                                                                            | ln<br>In<br>In                                                 | +5 Volts DC (Bussed)<br>Digital Ground (Bussed)<br>-5 Volts DC                                                                                                                                                          | 2<br>4<br>6                                                    | +5V<br>GND<br>-5V                                                                                | In<br>In<br>In                                            | +5 Volts DC (Bussed)<br>Digital Ground (Bussed)<br>-5 Volts DC                                                                                                                                                                         |

| DATA<br>BUS           | 7<br>9<br>11<br>13                                             | D3<br>D2<br>D1<br>D0                                                                                         | In/Out<br>In/Out<br>In/Out<br>In/Out                           | Low Order Data Bus<br>Low Order Data Bus<br>Low Order Data Bus<br>Low Order Data Bus                                                                                                                                    | 8<br>10<br>12<br>14                                            | D7<br>D6<br>D5<br>D4                                                                             | In/Out<br>In/Out<br>In/Out<br>In/Out                      | High Order Data Bus<br>High Order Data Bus<br>High Order Data Bus<br>High Order Data Bus                                                                                                                                               |

| ADDRESS<br>BUS        | 15<br>17<br>19<br>21<br>23<br>25<br>27<br>29                   | A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0                                                                 | Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out                  | Low Order Address Bus<br>Low Order Address Bus                    | 16<br>18<br>20<br>22<br>24<br>26<br>28<br>30                   | A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8                                               | Out<br>Out<br>Out<br>Out<br>Out<br>Out                    | High Order Address Bus<br>High Order Address Bus |

| CONTROL<br>BUS        | 31<br>33<br>35<br>37<br>39<br>41<br>43<br>45<br>47<br>49<br>51 | WR*<br>IORQ*<br>IOEXP*<br>REFRESH*<br>STATUS 1*<br>BUSAK*<br>INTAK*<br>WAITRQ*<br>SYSRESET*<br>CLOCK*<br>PCO | Out<br>Out<br>In/Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out | Write to Memory or I/O<br>I/O Address Select<br>I/O Expansion<br>Refresh Timing<br>CPU Status<br>Bus Acknowledge<br>Interrupt Acknowledge<br>Wait Request<br>System Reset<br>Clock from Processor<br>Priority Chain Out | 32<br>34<br>36<br>38<br>40<br>42<br>44<br>46<br>48<br>50<br>52 | RD*<br>MEMRQ*<br>MCSYNC*<br>STATUS 0*<br>BUSRQ*<br>INTRQ*<br>NMIRQ*<br>PBRESET*<br>CNTRL*<br>PCI | Out<br>Out<br>In/Out<br>Out<br>In<br>In<br>In<br>In<br>In | Read to Memory or I/O<br>Memory Address Select<br>Memory Expansion<br>CPU Machine Cycle Sync.<br>CPU Status<br>Bus Request<br>Interrupt Request<br>Non-Maskable Interrupt<br>Push Button Reset<br>AUX Timing<br>Priority Chain In      |

| POWER<br>BUS          | 53<br>55                                                       | AUX GND<br>AUX +V                                                                                            | In<br>In                                                       | AUX Ground (Bussed)<br>AUX Positive (+12 Volts DC)                                                                                                                                                                      | 54<br>56                                                       | AUXGND<br>AUX-V                                                                                  | In<br>In                                                  | AUX Ground (Bussed)<br>AUX Negative (-12 Volts DC)                                                                                                                                                                                     |

### STD BUS

\*Low Level Active Indicator

### LOGIC POWER BUS - PINS 1-6

Provides basic voltage lines for predominant system logic.

- +5V Pins 1 & 2 +5 Logic Voltage, (VCC) Main logic voltage lines (+5 volts). Both pins are bussed together for current capacity.

- GND Pin 3 & 4 Logic Ground Ground for logic power. Both pins are bussed together for current capacity.

- -5V Pin 5 Negative 5 Volt Bias, (VBB) A low current (-5 volt) bias voltage line.

- -5V Pin 6 Negative 5 Volt Bias, (VBB) A secondary low current (-5 volt) bias voltage line.

### DATA BUS - PINS 7-14

An 8-bit bidirectional 3-state bus. (Bidirectional means signals may flow either into or out of any card on the Bus.) Direction of data is normally controlled by the processor card via the Control Bus. The data direction is normally affected by such signals as Read (RD\*), Write (WR\*) and Interrupt Acknowledge (INTAK\*).

The Data Bus uses high-level active logic levels. All cards are required to release the bus to a high impedance state when not in use. The Processor card releases the data bus in response to Bus Request (BUSRQ\*) input from an alternate system controller, as in DMA transfers.

### ADDRESS BUS - PINS 15-30

A 16-bit 3-state high-level active bus. The address will normally originate at the processor card. The processor card releases the Address Bus in response to a Bus Request (BUSRQ\*) input from an alternate controller.

The Address Bus provides 16 address lines for decoding by either memory or I/O. Memory request (MEMRQ\*) and I/O request (IORQ\*) control lines are used to distinguish between the two operations. The particular microprocessor used will determine the number of address lines and how they are used.

Example:

|           | NO. OF MEM. | OF MEM. ADR. LINES | NO. OF I/O ADDRESS LINES |                   |  |  |

|-----------|-------------|--------------------|--------------------------|-------------------|--|--|

| PROCESSOR | ADR. LINES  | DURING REFRESH     | I/O MAPPED I/O           | MEMORY MAPPED I/O |  |  |

| 8080      | 16          |                    | Lower 8 (3)              | 16                |  |  |

| 8085      | 16          | ·····              | Lower 8 (3)              | 16                |  |  |

| Z80       | 16          | Lower 7 (1)        | Lower 8 (2)              | 16                |  |  |

| 6800      | 16          |                    |                          | 16                |  |  |

| 6809      | 16          |                    |                          | 16                |  |  |

- (1) During the REFRESH cycle, A0 through A6 contain the REFRESH Address for dynamic RAMs while A7 is a Logic 0 and the Upper 8 Bits of the Address Bus contain the I register contents.

- (2) During I/O operations the upper 8 address lines output the accumulator contents.

- (3) During I/O operations the upper 8 address lines also output the I/O address.

#### **CONTROL BUS - PINS 31-52**

Provides control signals for memory, I/O, interrupt and fundamental system operations.

Control lines are available for memory expansion, memory mapped I/O, dynamic memory refresh, direct memory access, multi-processing, single-stepping, slow memory, power-fail-restart, fixed interrupt, priority vectored interrupt and bus analysis.

Bus pins have been allocated for special operations. Actual capabilities depend on the processor card used and the capabilities of supporting control cards.

- WR\* Pin 31 Write to Memory or I/O

A 3-state, active-low control line that indicates the BUS holds valid data to be written in the addressed memory or output device.

- RD\* Pin 32 Read from Memory or I/O A 3-state, active-low control line that indicates the processor or other bus controlling device wants to read data from memory or an I/O device. The selected I/O device or memory should use this signal to gate data onto the BUS.

- IORQ\* Pin 33 I/O Address Select

A 3-state, active-low processor output control line. IORQ\* indicates that the address lines hold a valid I/O address for an I/O Read or Write.

- MEMRQ\* Pin 34 Memory Address Select

A 3-state, active-low memory request line. MEMRQ\* indicates that the address bus holds a valid address for

memory read or memory write operations.

- IOEXP\* Pin 35 I/O Expansion An active-low control signal used to expand or enable I/O Port addressing. If this pin is not used its is strapped to logic ground.

- MEMEX\* Pin 36 Memory Expansion An active-low control signal used to expand or enable memory addressing. If this pin is not used it is strapped to logic ground.

Four control signals are provided to handle the timing requirements of various microprocessors. These signals are normally used for interfacing to memory and peripheral devices. They are REFRESH\*, MCSYNC\*, STATUS 0\* and STATUS 1\*.

• REFRESH\* - Pin 37

A 3-state active-low control line normally used to refresh dynamic memory. The signal may be generated on the processor card or on a separate control card. The nature and timing of the singal may be a function of the memory device or the microprocessor.

• MCSYNC\* - Pin 38 - Machine Cycle Sync

A 3-state, active-low Processor output signal that occurs once during each processor machine cycle. (Machine cycle is defined as the sequence that involves Addressing, Data Transfer and Execution.) MCSYNC\* defines the beginning of the machine cycle. The exact nature and timing of this signal is microprocessor dependent.

**Example MCSYNC\***

| PROCESSOR | SIGNAL PIN 37          | PROCESSOR | SIGNAL PIN 38              |

|-----------|------------------------|-----------|----------------------------|

| Z80       | REFRESH*               | 8080      | SYNC                       |

| 8085      |                        | 8085      | ALE (Address Latch Enable) |

| 8080      | Provided by controller | Z80       | (RD+WR+INTAK)              |

| 6800      | on another card        | 6800      | 02*                        |

| 6809      |                        | 6809      | 02*                        |

Example REFRESH\*

- STATUS 1\* Pin 39 Status Control Line 1

- STATUS 0\* Pin 40 Status Control Line 0 Status control lines provide timing information related to special machine cycle operations. Where specifically available, STATUS 1\* is considered to be a signal to identify instruction fetch.

| PROCESSOR | STATUS 1* | STATUS 0* |

|-----------|-----------|-----------|

| 8080      | M1        |           |

| 8085      | S1        | SO        |

| Z80       | M1        | —         |

| 6800      |           | VMA       |

| 6809      | LIC       |           |

BUSAK\* - Pin 41 - BUS Acknowledge Normally an active-low output line from all processors. The controlling processor responds to a BUSRQ\* by releasing the BUS and giving an acknowledge signal on the BUSAK\* line. BUSAK\* normally occurs at the completion of the current machine cycle.

In complex systems this line can be an input, an output or it may be bidirectional, depending on the supporting hardware.

BUSRQ\* - Pin 42 - BUS Request Normally an active-low input line to all processors. A BUSRQ\* causes the controlling processor to suspend operations on the BUS by releasing all 3-state BUS lines for use by another processor. Normally the BUS is released once the current machine cycle is completed.

In complex systems this line can be an input, an output or it may be bidirectional, depending on the supporting hardware.

- INTAK\* Pin 43 Interrupt Acknowledge

An active-low output line from the Processor card that occurs in response to (INTRQ\*). It is used to tell the

interrupting device that the processor card is ready to respond to the interrupt. For vectored interrupts the

vector address is placed on the data bus by the interrupting device during INTAK\*.

- INTRQ\* Pin 44 Interrupt Request

An active-low processor card input line that conditionally interrupts the program. It is masked and ignored

by the Processor unless deliberately enabled by a program instruction. If the Processor accepts the

interrupt, it usually acknowledges by dropping INTAK\* (Pin 43). Other actions depend on the specific

Processor type, interrupt-related program instructions and hardware support of the interrupt mechanism.

- WAITRQ\* Pin 45 Wait Request An active-low input line to the processor that suspends processor operations as long as it remains low. Normally the processor will hold in a state that maintains a valid address on the address bus.

- NMIRQ\* Pin 46 Non-Maskable Interrupt An active-low processor card interrupt input line of highest priority.

- SYSRESET\* Pin 47 System Reset An active-low output from the system reset circuit. The system reset circuit is triggered by power-on detection or by the pushbutton reset. The system reset bus line should be applied to all cards on the bus that have latch circuits requiring initialization.

- PBRESET\* Pin 48 Push Button Reset An active-low input line to the system reset circuit.

- CLOCK\* Pin 49 Clock from Processor

A buffered processor clock signal used for system synchronization or as a general clock source.

- CNTRL\* Pin 50 Control An auxiliary circuit for special clock timing. It may be a multiple of the processor clock signal, a real time clock signal or an external clock input to the processor.

STD BUS SPECIFICATIONS...

- PC0 Pin 51 Priority Chain Out

- PC1 Pin 52 Priority Chain In A priority "daisy chain" bus with a priority chain "in" and a priority chain "out". This is a card slot dependent interrupt structure.

### **AUXILIARY POWER BUS - PINS 53-56**

The Auxiliary Power bus provides interconnection for supplemental voltages.

- AUX GND Pins 53 &54 The ground or return bus for auxiliary power. These pins are bussed together for extra capacity.

- AUX +V Pin 55 Auxiliary positive voltage line (+12V).

- AUX -V Pin 56 Auxiliary negative voltage line (-12V).

# **GENERAL SPECIFICATIONS**

The STD BUS definition includes physical parameters which are an inherent part of the STD BUS specification.

STD BUS cards must meet the mechanical and electrical specifications detailed, in the following pages, over the card's specified temperature range.

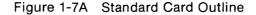

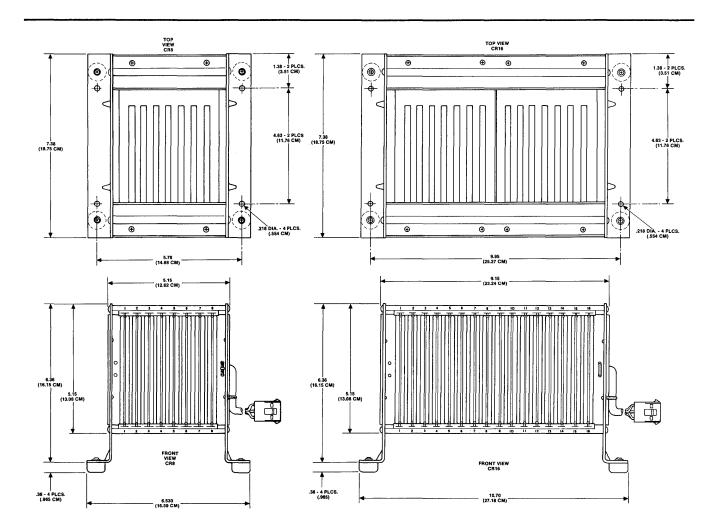

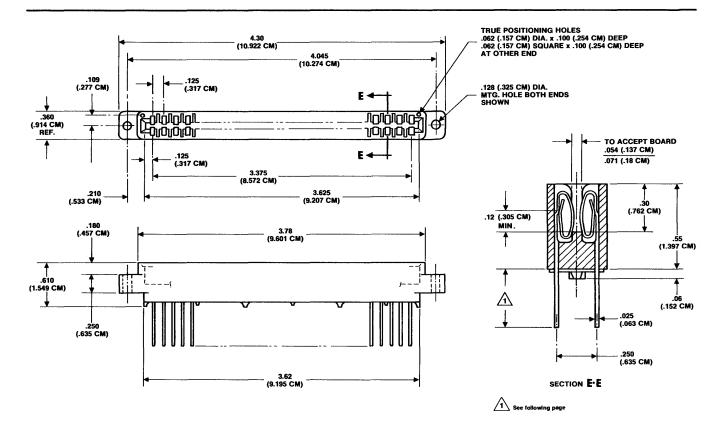

# MECHANICAL SPECIFICATIONS

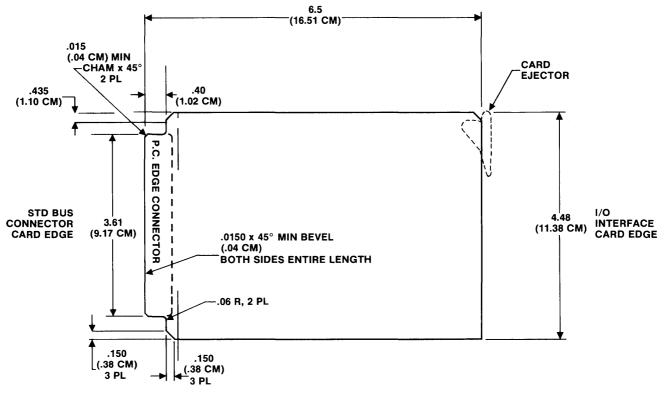

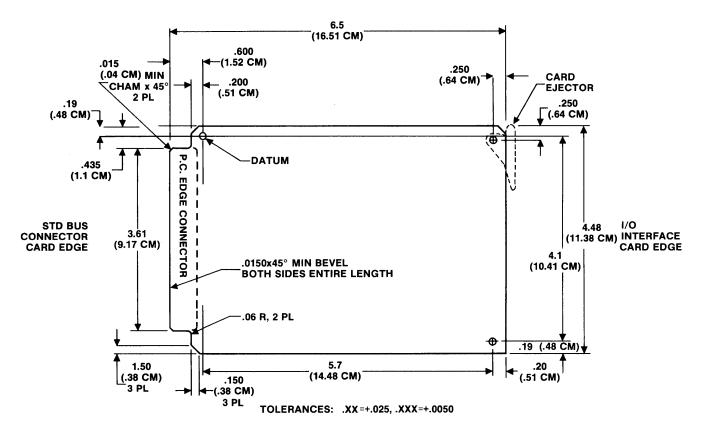

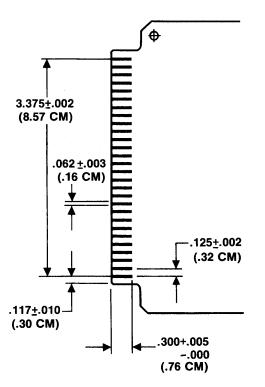

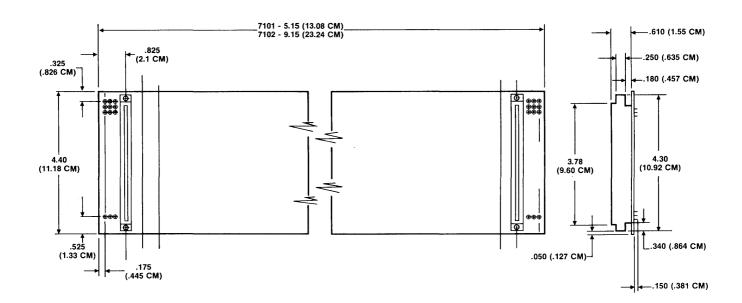

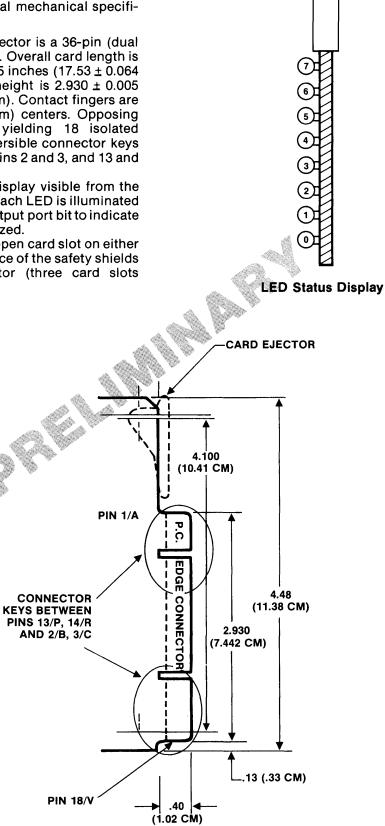

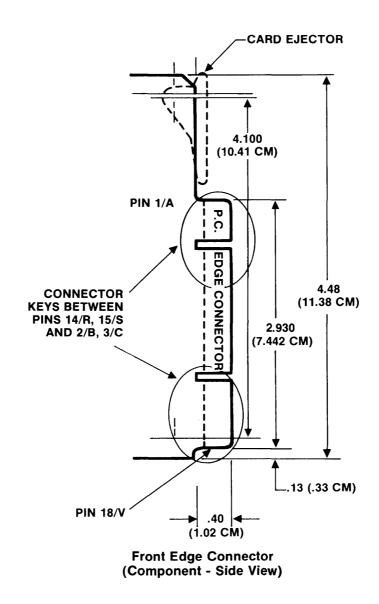

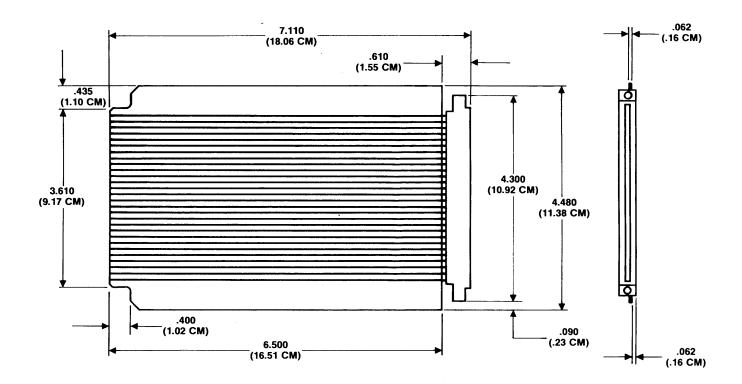

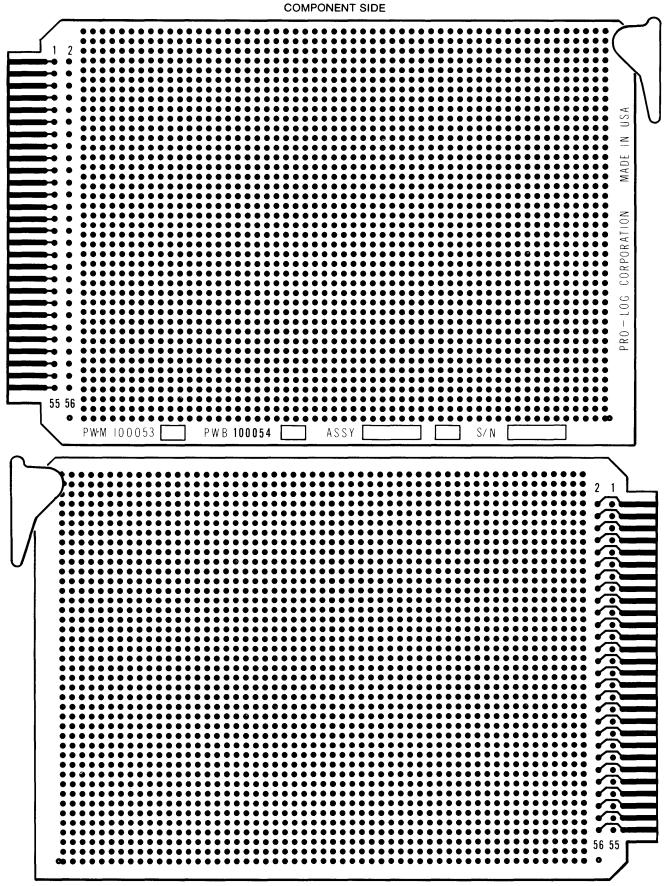

The STD BUS circuit card size and outline are defined by Figure 1-5 and Figure 1-7. The dimensions exclude the card ejector and I/O interface connections. Additional card length is allowed for I/O edge connector interfacing as defined in Figure 1-5.

|                                                                                                             | IN                                        | CHES                                     | CENTIMETERS                                |                                          |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|--|

| STD CARD DIMENSIONS                                                                                         | NOMINAL                                   | TOLERANCE                                | NOMINAL                                    | TOLERANCE                                |  |

| Card Length<br>Card Height<br>Plated Board Thickness<br>Card Spacing<br>Added Length for I/O Edge Connector | 6.500<br>4.480<br>0.062<br>0.500<br>0.400 | ±.025<br>±.0050<br>±.003<br>MIN<br>±.025 | 16.510<br>11.380<br>0.158<br>1.27<br>1.016 | ±.063<br>±.0127<br>±.008<br>MIN<br>±.063 |  |

Figure 1-5 STD Card Dimensions

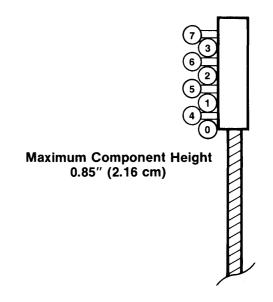

Minimum card spacing requires consideration for component height, lead protrusion and card clearance in addition to the board thickness. Figure 1-6 gives recommended dimensions for these parameters but tradeoffs can be made between component height and lead protrusion. Cards not meeting these requirements may require multiple card slot positions.

| RECOMMENDED DIMENSIONS                                                | INC                | HES     | CENTIMETERS        |          |

|-----------------------------------------------------------------------|--------------------|---------|--------------------|----------|

| FOR MINIMUM CARD SPACING                                              | MAXIMUM            | MINIMUM | MAXIMUM            | MINIMUN  |

| Component Height<br>Component Lead Protrusion Adjacent Card Clearance | 0.375<br>0.040<br> | 0.010   | 0.952<br>.102<br>— | <br>.025 |

The card ejector occupies the top 1.4" (3.56 cm) of the card and protrudes 0.1" (0.254 cm) on each side of the card.

Figure 1-7B Recommended Edge Card Finger Design

# **ELECTRICAL SPECIFICATIONS**

These specifications will assure power supply and logic level compatibility among STD BUS cards.

#### **ABSOLUTE MAXIMUM RATINGS:**

The following specifications are the STD BUS card edge connector pin maximum ratings. They are not recommended operating conditions. Above these values damage to card components is possible. The specific voltage at which damage will occur is component dependent.

| PARAMETER                                                               | LIMIT      | REFERENCE     |

|-------------------------------------------------------------------------|------------|---------------|

| Positive voltage applied to a logic input or disabled 3-state output    | +5.5 Volts | GND pins 3, 4 |

| Negative DC voltage applied to a logic input or disabled 3-state output | -0.4 Volts | pins 3, 4     |

Figure 1-8 Electrical Ratings

#### Note:

Unless otherwise specified, the removal of STD BUS compatible circuit cards or their components parts from sockets is not recommended while operating voltages are applied.

### POWER BUS VOLTAGE TOLERANCES

STD BUS cards normally require +5V for logic operation. Other operating voltages may be needed according to individual card function and device types. The table below shows the STD BUS power busses and voltage values. Note that these voltage values are specified at the card pins, not the back plane traces.

| CARD PIN | SUPPLY VOLTAGE | TOLERANCE   | REFERENCE           |

|----------|----------------|-------------|---------------------|

| 1, 2     | +5V (VCC)      | ±0.25 Volts | GND pins 3, 4       |

| 5, 6     | -5V (VBB)      | ±0.25 Volts | GND pins 3, 4       |

| 55       | AUX +V (+12)   | ±0.5 Volts  | AUX GND pins 53, 54 |

| 56       | AUX -V (-12V)  | ±0.5 Volts  | AUX GND pins 53, 54 |

Figure 1-9 Power Voltages and Tolerances

#### LOGIC SIGNAL CHARACTERISTICS

The STD BUS is designed for compatibility with industry standard TTL logic. These specifications apply over the STD BUS specified temperature range.

| STD BUS CARD PARAMETER                             | TEST CONDITIONS                      | MIN | MAX | UNITS |

|----------------------------------------------------|--------------------------------------|-----|-----|-------|

| VOH High-state output voltage                      | VCC=MIN VIH=2V<br>VIL=0.8V IOH=-15mA | 2.4 |     | Volts |

| V <sub>OL</sub> .Low-state output voltage          | VCC=MIN VIL=0.8V<br>VIH=02V IOL=24mA |     | 0.5 | Volts |

| VIH High-state input voltage                       |                                      | 2.0 |     | Volts |

| VIL Low-state input voltage                        |                                      |     | 0.8 | Volts |

| T <sub>R</sub> , T <sub>F</sub> Risetime, Falltime |                                      | 4   | 100 | ns    |

#### STD UNIT LOADS

The unit load is a convenient method for specifying the input loading and output drive capability of STD BUS cards. In STD BUS systems one unit load is equal to one LSTTL load as follows:

Maximum high level input current:  $20 \,\mu A$ Maximum low level input current:  $-400 \,\mu A$

The STD BUS unit load reflects input current requirements at worst-case conditions over the recommended supply voltage and ambient temperature ranges. An output rated at 60 unit loads can drive 60 STD BUS cards having inputs rated at one unit load.

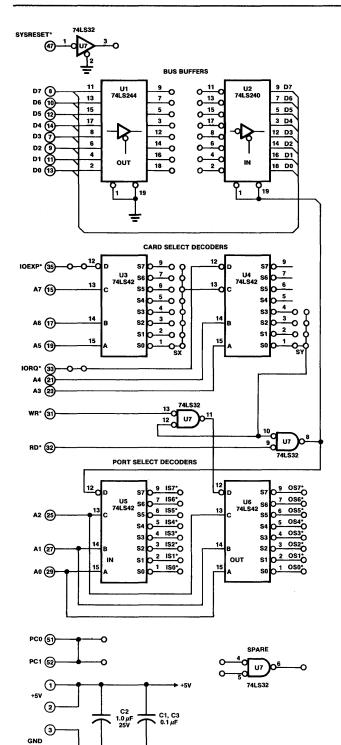

#### **RECOMMENDED BUS DRIVERS & RECEIVERS**

Bus Drivers - 74LS240, 74LS241, 74LS244, 74LS373, 74LS374

Bus Receivers - 74LS240, 74LS241, 74LS244

Bus Transceivers - 74LS242, 74LS243, 74LS245

# **Section 2**

# Common Specifications for Series 7000 STD BUS Microprocessor Cards

# INTRODUCTION

This section contains specifications common to the Series 7000 cards. These specifications, combined with the STD BUS specifications and the individual card data sheets, fully specify each card. Configuring the hardware for a Series 7000 STD BUS system simply requires the defining of the memory size and the number and type of I/O lines needed for the application, together with the selection of the appropriate card rack and special cards. Mapping of the memory and I/O is preassigned, change may be incorporated by moving jumper wire.

This section also contains the memory and I/O mapping information that is used with data sheets for the memory card address assignments and for the port address assignments (mapping).

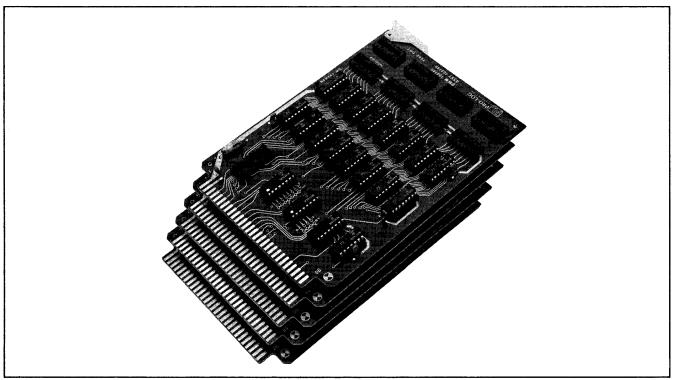

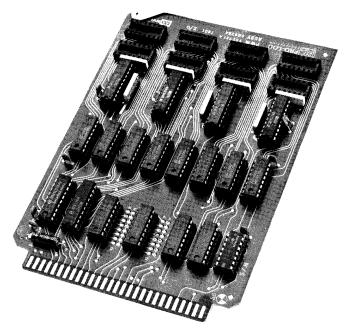

Series 7000 cards combine high functional density with the design options needed for efficient system partitioning.

Series 7000 comprises a wide range of modular microprocessor system elements, including Processor, Memory cards, I/O cards, motherboards, card racks, utility cards and power supplies. The cards are divided into the following categories:

7100 System Support Cards (non-4½"x6½") including Motherboards

7300 Peripheral Interface

7400 Analog I/O

7500 Industrial I/O

7600 Digital (TTL) I/O

7700 Memory

7800 Processors

7900 Utility (extenders, blanks, prototyping aids, etc.)

Series 7000

# **MECHANICAL SPECIFICATIONS**

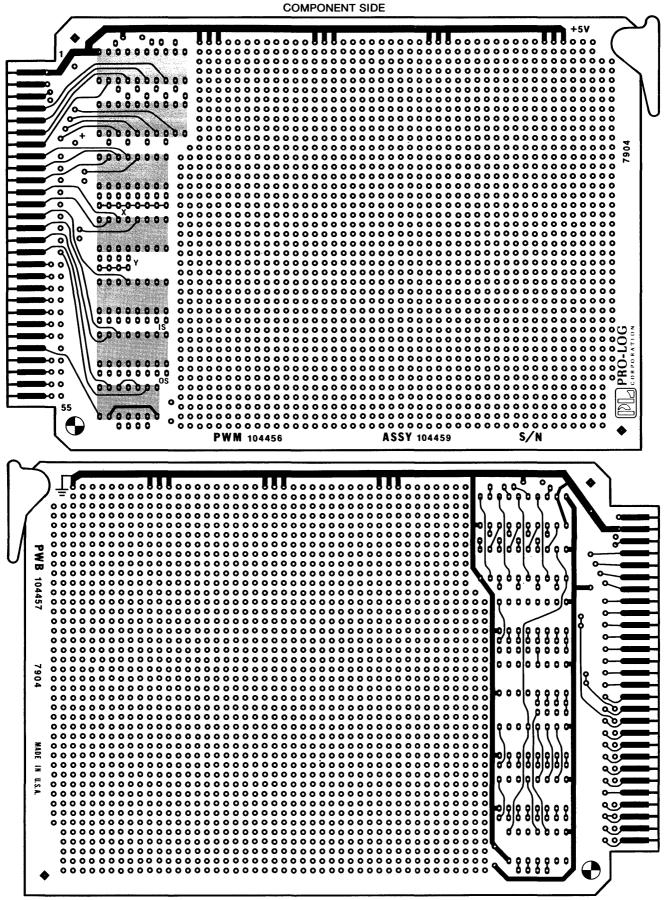

The Series 7000 cards conform to the STD BUS standards, with the following additional requirements, including those shown in Figure 2-1.

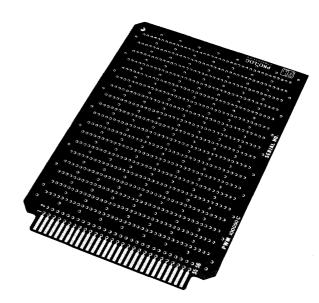

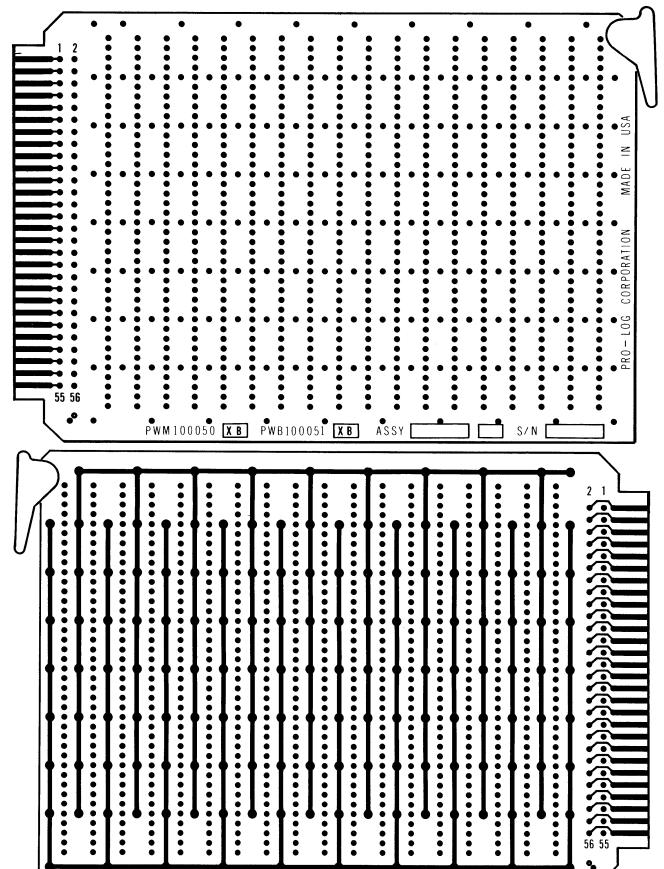

Figure 2-1A Series 7000 STD BUS Standard Card Outline

Figure 2-1B Series 7000 STD BUS Edge Card Finger Specifications

### MATERIALS

The card base material is blue type FR4 laminated epoxy glaze with UL-94-V0 rating. Dual-sided cards have the equivalent of 2 ounces of copper per side, which is 2.4 mils thick, minimum. Edge connector fingers are copper with gold (0.03 mil) over nickel (0.1 mil) in accordance with MIL-G-45204.

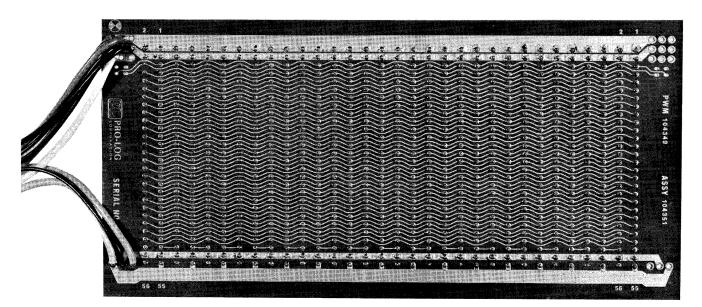

## SOCKETS

All integrated circuits on Series 7000 cards are socketed for ease of maintenance. Socketed ICs also allow for rapid insertion for PROM program development, plug-in of system test programs and expansion of system RAM memory.

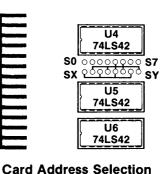

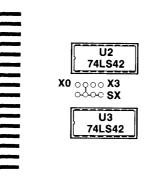

### CARD ADDRESSING OPTIONS

User addressing options are made by a jumper selection on all Processor Memory and I/O cards. These cards have jumper pads adjacent to on-card decoder sockets which allow the user to permanently change the address of the card and on-card elements such as memory chips and ports.

For jumper selection refer to the appropriate Memory or I/O Address Decoder Schematics and corresponding Address Map and Jumper Selection tables provided later in this section.

# TEMPERATURE SPECIFICATION

Pro-Log's Series 7000 microprocessor card systems are designed to meet STD BUS specifications over the temperature range 0°C to 55°C ambient.

# **ELECTRICAL SPECIFICATIONS**

Low-power Schottky (LSTTL) support logic and buffering are used to give the cards low input loading and low power consumption, without sacrificing speed or output drive capability. Most cards use LSTTL buffers with 200 mV of hysteresis for noise immunity.

The Series 7000 cards meet the following STD BUS specifications of Section 1: Absolute Maximum Ratings, Power Supply Voltages, Logic Signal Characteristics, Standard Bus Unit Loads.

One STD load or drive unit is equivalent to the 74LSXX unit load or drive as defined in Section 1.

Series 7000 cards have been divided into two sets of drive and loading specifications in accordance with the following categories:

7800 Processor Cards Memory and I/O Cards

The 7800 Processor cards have 4.7K pullup resistors for each logic input and output. These pullups provide enhanced noise immunity and facilitate system testing. They pull the lines up to the +5V supply when the 3-state drivers are disabled. The pullups slightly reduce the 7800 Processor card's output drive capability and increase the input loading compared to the other card categories.

To determine the number of STD BUS cards possible in a system, first total the number of LSTTL input loads (STD unit loads) on each bus line. Then every output driver on the same line must be capable of driving at least that number of loads. This assures system operation over the worst-case combination of voltage tolerance and ambient temperature.

| PARAMETER          | CARD TYPE                                | MIN | MAX | UNITS |

|--------------------|------------------------------------------|-----|-----|-------|

| INPUT<br>LOADING   | 7800 Processor cards                     |     | 4   | LSTTL |

|                    | Memory & I/O Cards                       | _   | 1   | Loads |

| OUTPUT             | 7800 Processor Cards                     | 55  |     | LSTTL |

| DRIVE              | Memory & I/O Cards                       | 60  | -   | Loads |

| OUTPUT             | 7800 Processor Cards (with 4.7K pullups) | _   | 4   | LSTTL |

| 3-STATE<br>LEAKAGE | Memory & I/O Cards                       | —   | 1   | Loads |

$VCC = +5V \pm 5\%$ , TA = 0-55°C

# SERIES 7000 STD BUS TIMING

The 7800 Processor card generates all Processor and STD BUS timing in normal operation (unless a DMArelated operation has caused the Processor card to relinquish the system bus). The Processor card implements the capability of the microprocessor chip and interfaces it to the STD BUS with the minimum alteration of the chip's characteristics. The timing characteristics of a 7800 Processor card are essentially those of the microprocessor itself with added delays due to buffering.

Unless otherwise specified on individual data sheets, the following propagation delays apply between the 7800 Processor card edge signal pins and the microprocessor chip pins:

VCC = +5V, TA =  $25^{\circ}C$

| PARAMETER                     | MAX | UNITS | CONDITIONS  |

|-------------------------------|-----|-------|-------------|

| Buffer delay, input to output | 20  | ns    | 50 pF, 700Ω |

| 3-state driver enable         | 30  | ns    | 50 pF, 700Ω |

Figure 2-3 Processor Card Buffer Timing

With the above delays added, timing information for 7800 Processor cards is available from the microprocessor manufacturer's data sheet specification.

Multilevel gating is sometimes required on the Processor card to produce STD BUS control signals that are not directly available from the microprocessor. Section 1 gives examples of how these signals may be derived for existing microprocessors. Refer to the processor card schematic and IC manufacturer's data sheets for exact delays.

### SERIES 7000 MEMORY CARD TIMING

Series 7000 cards are designed to communicate over the STD BUS backplane in any combination without user timing considerations. The following information is provided to accommodate the use of pin compatible memory chip variations which can be used in the Series 7000 memory cards.

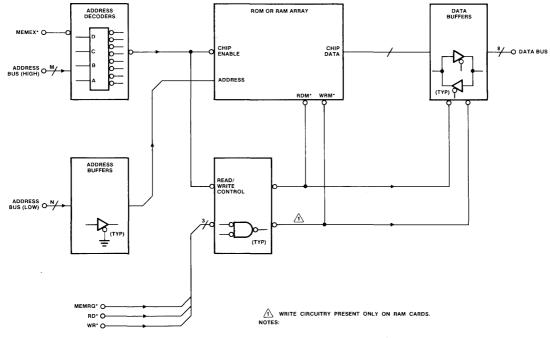

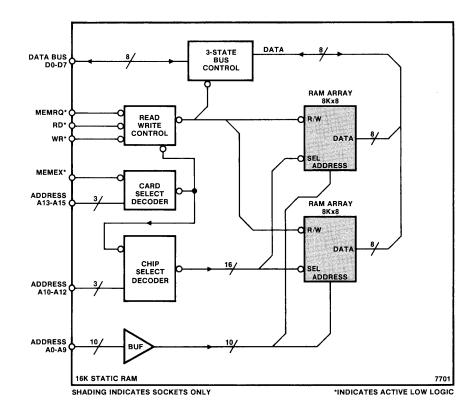

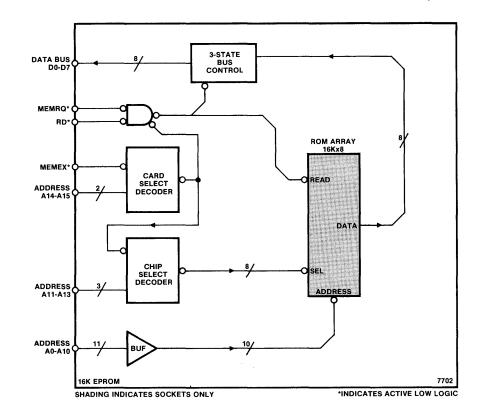

Figure 2-4 shows the functional blocks of the 7700 Memory cards. The delays contributed by these blocks are added to the memory chip delays and access times to determine the AC characteristics of the card. The table in Figure 2-5 gives maximum propagation delays for the memory card. For exact delays use the IC manufacturer's data sheets and the appropriate schematics.

Figure 2-4 Memory Card Functional Blocks

#### VCC = +5V, TA = $25^{\circ}C$

| CIRCUIT                  | Р                                           | ROPAGATION DELAY                                    |       | LOAD CONDITIONS |        |  |  |

|--------------------------|---------------------------------------------|-----------------------------------------------------|-------|-----------------|--------|--|--|

|                          | FROM                                        | CL                                                  | RL    |                 |        |  |  |

| ADDRESS<br>DECODERS      | ADDRESS BUS<br>OR<br>MEMEX*                 | MEMORY CHIP<br>ENABLE<br>OR<br>READ/WRITE<br>ENABLE | 75 ns | 15 pF           | _      |  |  |

| ADDRESS<br>BUFFERS       | ADDRESS<br>BUS                              | MEMORY CHIP<br>ADDRESS                              | 35 ns | 160 pF          |        |  |  |

|                          | MEMORY CHIP<br>DATA (OUT)                   | DATA<br>BUS                                         | 20 ns | 45 pF           | 4.7KΩ  |  |  |

| DATA<br>BUFFERS          | DATA<br>BUS                                 | MEMORY CHIP<br>DATA (IN)                            | 25 ns | 80 pF           | _      |  |  |

|                          | READ WRITE<br>CONTROL                       | VALID OUTPUT<br>ENABLE                              | 30 ns |                 |        |  |  |

| READ<br>WRITE<br>CONTROL | DECODER<br>OUTPUT<br>RD*, WR*,<br>OR MEMRQ* | RDM*<br>OR<br>WRM* (RAMs ONLY)                      | 70 ns | 100 pF          | 4.7K Ω |  |  |

Figure 2-5 Generalized Maximum Delays For Memory Cards

For example, the 2114 RAM chip's specified Data Read access time from an address change (A0-A9) is 450 ns. In the 7701 this is increased by the address buffers (35 ns) and data buffers (20 ns) to 505 ns. In this case the decoding of A10-A15 and the Data Bus buffer control are presumed to occur during the RAM data access time.

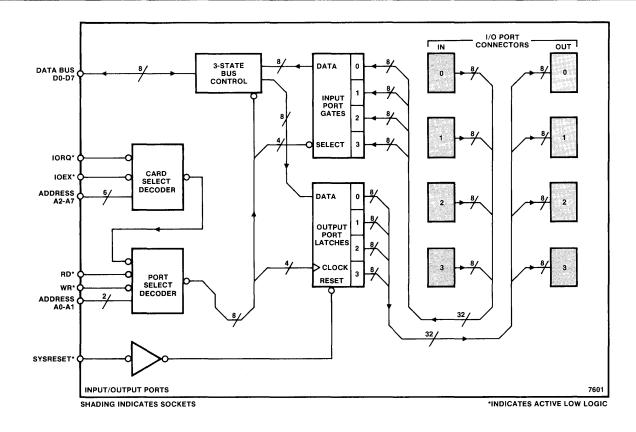

# TTL INPUT/OUTPUT CARD TIMING

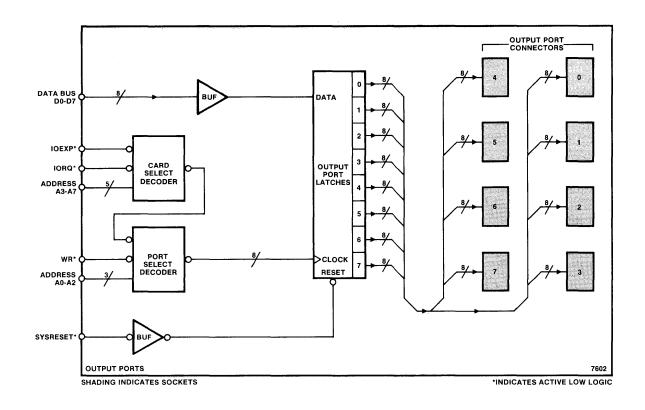

I/O Port read and write operations are under program control and occur in multiples of the Processor's time state as defined by the instruction set. Input Ports are addressable 3-state buffers which, when selected, drive the STD BUS Data Buffer. Output Ports are addressable D type latches which, when selected, copy the STD BUS data and latch it at the rising edge of WR\*.

The following table provides timing information relative to the rising edge of RD\* and WR\* control lines. This information fully defines the TTL I/O Port timing since the following assumptions can be made:

IORQ\*, IOEX\*, DATA & ADR are all stable for more than 150 ns prior to RD\* or WR\* rising and that RD\* and WR\* are active low for more than 150 ns.

|                 | PARAMETER                                                                  | MIN | ΜΑΧ | UNITS |

|-----------------|----------------------------------------------------------------------------|-----|-----|-------|

| тор             | Output Delay:<br>Output port line valid<br>after WR* rises CL=15 pF        | _   | 60  | ns    |

| T <sub>ID</sub> | Input Delay:<br>STD DATA BUS stable<br>after input Data<br>stable CL=50 pF | _   | 40  | ns    |

| т <sub>Н</sub>  | Input Hold Time:<br>Input port data valid<br>after RD* rises               | 0   | -   | ns    |

| VCC = +5V, T | A = 25° | С |

|--------------|---------|---|

|--------------|---------|---|

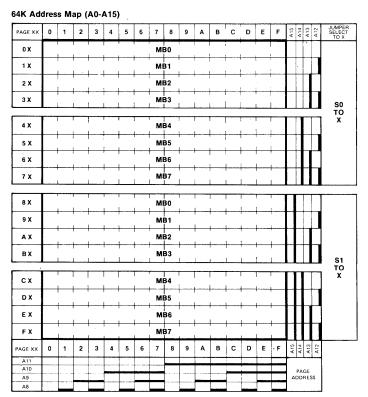

## MAPPING

Each class of Series 7000 cards are mapped at a different address to minimize the need for the users to remap cards. The standard mapping that follows is recommended since software availabe in the future from Pro-Log will utilize this standardized mapping scheme.

All memory cards can be mapped to cover the full 64K memory space and can be bank enabled. All I/O cards decode the lower 8 bits and ports can be mapped anywhere in the 256 Port field without using the I/O expansion pin for port bank switching.

#### STANDARD SERIES 7000 STD BUS MAPPING

The following is the standardized mapping scheme for the Series 7000 cards. The center column gives the mapped address of the first port or memory location on the card. The remainder of the ports or memory locations are consecutive from that point. The second column gives the recommended address locations for additional mapping of the same type of cards.

| CARD TYPE                    | CARD MAPPED AT<br>HEX PORT ADDRESS | ASSIGNED HEX ADDRESS<br>SPACE FOR SYSTEM EXPANSION |

|------------------------------|------------------------------------|----------------------------------------------------|

| 7100 & 7200                  | NA                                 | NA                                                 |

| 7300 Peripheral<br>Interface | C0                                 | C0-CF                                              |

| 7400 Analog I/O              | 80                                 | 80-BF                                              |

| 7500 Industrial<br>I/O       | 40                                 | 40-7F                                              |

| 7600 TTL I/O                 | 00                                 | 00-3F                                              |

| Non-Specified<br>Types       | D0                                 | D0-FF                                              |

| CARD TYPE<br>7700 MEMORY | CARD MAPPED AT<br>HEX MEMORY PAGE | ASSIGNED HEX ADDRESS<br>SPACE FOR SYSTEM EXPANSION |  |  |  |  |  |

|--------------------------|-----------------------------------|----------------------------------------------------|--|--|--|--|--|

| RAM                      | 80                                | 16K space not used by<br>CPU or 16K ROM Card       |  |  |  |  |  |

| ROM                      | 40                                | 16K space not used by<br>CPU or 16K RAM Card       |  |  |  |  |  |

An additional 16K space is available for second memory card without using memory expansion techniques.

Figure 2-8 Standardized Memory Card Mapping

|                | HEXADECIMAL ADDRESSES                                                                   |                 |                 |                 |  |  |  |  |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--|--|--|--|--|--|--|--|--|--|

| CPU TYPE       | CPU MEMORY                                                                              | ROM/PROM        | RAM             | OPTIONAL        |  |  |  |  |  |  |  |  |  |  |

| 8085 &<br>Z80  | ROM 0000-1FFF (8K)<br>RAM 2000-2FFF (4K)<br>UNSUABLE 3000-3FFF (4K)                     | 4000-7FFF (16K) | 8000-BFFF (16K) | C000-FFFF (16K) |  |  |  |  |  |  |  |  |  |  |

| 6800 &<br>6809 | ROM E000-FFFF (8K)<br>RAM D000-DFFF (4K)<br>UNUSABLE C000-CFFF (4K)<br>I/O AT 0000-00FC | 4000-7FFF (16K) | 8000-BFFF (16K) | 0000-3FFF (16K) |  |  |  |  |  |  |  |  |  |  |

$\triangle$

The Processor card's 12K onboard memory may also be disabled, allowing an external 16K memory card to occupy the space assigned.

### **MEMORY MAP**

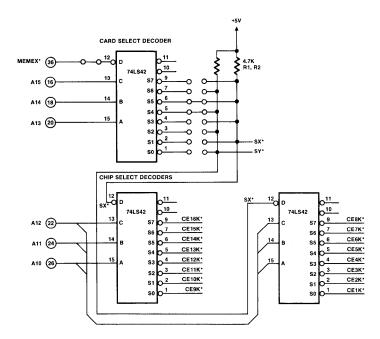

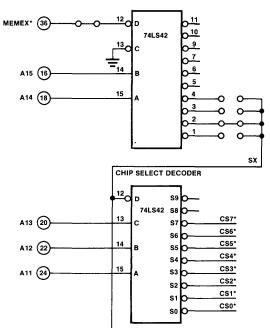

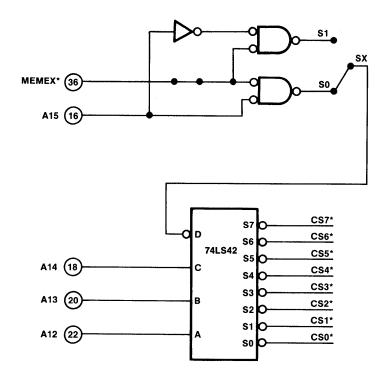

To facilitate memory mapping the following pages contain memory maps, each with an associated address decoding schematic for 1K, 2K & 4K memory blocks. Below each chart is an example of its use. This memory mapping information, and the associated data sheet, summarize the Series 7000 mapping configurations.

The data sheets give the address range to which each card is mapped when shipped. It also has each memory blocks appropriate integrated circuit U-numbers.

If the memory is to be mapped to another location the following procedure is recommended:

- 1. Find the appropriate memory address map and schematic as referenced on the data sheet.

- 2. Find the Hexadecimal address range on the appropriate map and determine from the right hand column of the Memory Address Map and Jumper Selection Table which decoder outputs require jumpers.

- 3. Remove the Jumper (S) shown on the data sheet and solder in bus wire at the newly selected jumper locations.

- 4. Install memory devices.

The memory card is now mapped and ready for use.

| CARD TYPE<br>7700 MEMORY | CARD MAPPED AT<br>HEX MEMORY PAGE | RESERVED HEX ADDRESS<br>SPACE FOR SYSTEM EXPANSION |

|--------------------------|-----------------------------------|----------------------------------------------------|

| RAM                      | 80                                | 16K space not used by<br>CPU or 16K ROM Card       |

| ROM                      | 40                                | 16K space not used by<br>CPU or 16K RAM Card       |

An additional 16K space is available for a second memory card without using memory expansion techniques.

Figure 2-10 Standardized Memory Card Mapping

Figure 2-11A Address Decoder & Schematic For 1K Memory Blocks (16K Memory Card)

| AGE XX | 0 | 1        | 2  | 3 | 4 | 5 | 6  | 7 | 8        | 9 | A  | в          | с | D  | Е  | F | A15    | A14<br>A13 | A12 | JUMPER<br>SELECT<br>TO X, Y |

|--------|---|----------|----|---|---|---|----|---|----------|---|----|------------|---|----|----|---|--------|------------|-----|-----------------------------|

| 0 X    | 1 | м        | во |   |   | M | B1 |   |          | м | 32 |            |   | M  | 33 |   |        |            | Π   | SO                          |

| 1 X    |   | м        | B4 |   |   | M | B5 |   |          | м |    | +          |   | ME | 37 | ! |        |            | Π   | TO<br>SY                    |

| 2 X    |   | м        | BO |   |   | м | B1 | 1 |          | м |    | 1          |   | M  | 33 |   |        |            |     | \$1<br>TO                   |

| 3 X    |   | м        | 84 |   |   | м | B5 |   |          | м | B6 |            |   | M  | 37 | I |        |            | Π   | sx                          |

| 4 X    |   | м        | B0 | 1 |   | м | B1 | 1 | <u> </u> | м | B2 | ¦          |   | M  | 33 | 1 |        | T          | Π   | <b>S</b> 2                  |

| 5 X    |   | м        | B4 | } |   | м | B5 | + |          | м | B6 | ł          |   | M  | 37 | i |        |            |     | TO<br>SY                    |

| 6 X    |   | м        | во | · |   | м | B1 | † |          | м | B2 |            |   | ME | 33 |   |        |            |     | \$3<br>TO                   |

| 7 X    |   |          | B4 |   |   | м | B5 | 1 |          | м | B6 |            |   | M  | 37 | 1 |        |            |     | SX                          |

| 8 X    |   | м        | BO | 1 |   | м | B1 | 1 |          | м | 82 | т <u> </u> |   | M  | 33 |   |        |            | Π   | <b>S</b> 4                  |

| 9 X    |   | M        | B4 | + |   | м | B5 | + |          | м | B6 | i          |   | M  | B7 |   | Π      |            |     | TO<br>SY                    |

| AX     |   | м        | во | 1 |   | м | B1 | 1 |          | м | B2 | 1          |   | ME | 33 |   | Π      |            |     | \$5<br>TO                   |

| вх     |   | м        | B4 | 1 |   | м | B5 |   |          | M | B6 |            |   | м  | B7 | I |        |            |     | sx                          |

| сх     |   |          | B0 |   |   | м | B1 | 1 |          | м | 32 |            |   | м  | 33 | Τ | Π      |            | Π   | <b>S</b> 6                  |

| DX     |   | м        | B4 |   |   | M | B5 | + | <b> </b> | м | 36 | <br>       |   | ME | 37 | + |        | T          |     | TO<br>SY                    |

| ΕX     |   | M        | во |   |   | M | B1 | 1 |          | м | 32 | 1          |   | M  | B3 |   |        |            | Π   | \$7<br>TO                   |

| FΧ     |   | м        | B4 |   |   | м | B5 | - |          | M | в6 |            |   | м  | B7 | 1 | $\Box$ |            | Π   | SX                          |

| AGE XX | 0 | 1        | 2  | 3 | 4 | 5 | 6  | 7 | 8        | 9 | A  | в          | c | D  | E  | F | A15    | A14        | A12 |                             |

| A11    |   | <u> </u> | 1  |   | L |   | 1  | 1 | <u> </u> |   |    | -          | - | -  | _  |   |        | PAGE       |     |                             |

Figure 2-11B Memory Address Map & Jumper Selection Table For 1K Memory Block (16K Memory Cards)

Example:

To remap a 16K memory card with 1K memory blocks from 8000-8FFF to C000-FFFF simply move the jumpers as follows:

(S4-SY) to (S6-SY) & (S5-SX) to (S7-SX)

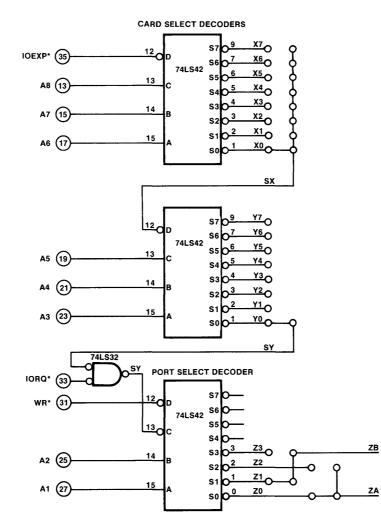

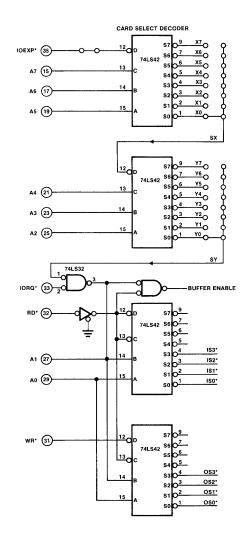

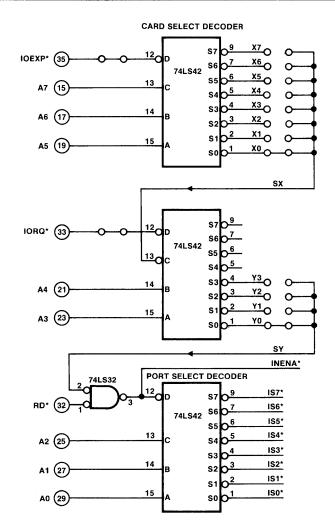

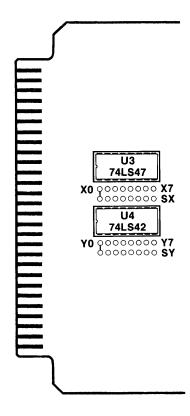

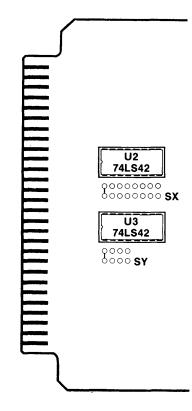

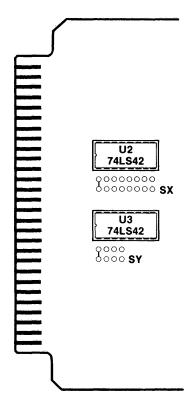

CARD SELECT DECODER

| PAGE XX | 0 | 1            | 2    | 3 | 4      | 5                                            | 6        | 7       | 8 | 9     | A | в | с          | D        | Е      | F | A15 | A14 | A13 | A12 | JUMPER<br>SELECT<br>TO SX |

|---------|---|--------------|------|---|--------|----------------------------------------------|----------|---------|---|-------|---|---|------------|----------|--------|---|-----|-----|-----|-----|---------------------------|

| 0 X 0   |   |              |      |   | во     |                                              |          |         |   | . –   |   | м | 31         | . —      |        |   |     |     |     |     |                           |

| 1 X     |   |              | _    |   | B2     | 1                                            | 1        |         |   | ,     |   | м | <b>B</b> 3 |          |        |   |     |     |     |     | \$0<br>ТО                 |

| 2 X     |   |              |      |   | B4     | 1                                            |          | ,       |   | , —   |   | M | 35         | ,        | 1 .    |   |     |     |     |     | sx                        |

| 3 X     |   | <br>         |      | м | B6     | I                                            | 1<br>L   | 1       |   | l     | l | M |            | 1        |        | 1 |     |     |     |     |                           |

| 4 X     |   |              | 1    |   | B0     |                                              | Γ        |         |   |       | r | м | B1         |          | ,<br>, |   |     |     |     |     |                           |

| 5 X     |   | <del> </del> |      |   | B2     | <del> </del>                                 | <b>├</b> | }       |   | · · · |   | M | 33         |          |        |   | -   |     |     |     | <u>\$1</u>                |

| 6 X     |   |              | <br> | м | B4     | +                                            |          | <br>    |   |       |   | м | B5         |          | 1      |   |     |     |     |     | TO<br>SX                  |

| 7 X     |   |              |      |   | B6     |                                              |          |         |   | !     |   | м | 37         | I        |        |   |     |     |     |     |                           |

| 8 X     |   |              |      | м | во     | <b>,</b>                                     | ,        | r · -   |   |       | 1 | м | B1         |          | I      | - | Π   | Π   |     | 7   |                           |

| 9 X     |   | <b> </b>     |      | м | <br>B2 | +                                            |          |         |   |       |   | м | B3         |          |        |   | Η   |     |     | ٦   | S2                        |

| AX      |   | <b>├</b> ──  |      |   | <br>B4 |                                              | <b>├</b> |         |   |       |   | м | B5         |          |        |   |     |     |     |     | то<br>sx                  |

| вх      |   |              |      | м | B6     |                                              | <br>     |         |   |       | + | м | 37         |          |        | 1 |     |     |     |     |                           |

| сх      |   | <b></b>      |      | м | BO     | T                                            | r        |         |   |       |   | м | 31         | <u> </u> |        |   | Π   | Π   | Π   |     |                           |

| DX      |   |              |      | м | B2     | <u>.                                    </u> |          |         |   |       |   | м | 33         |          |        |   |     |     |     |     | <b>S</b> 3                |

| ЕX      |   |              | <br> | м | B4     |                                              |          |         |   |       |   | м | 35         |          |        |   |     |     |     |     | TO<br>SX                  |

| FX      |   | <br>         |      | M | B6     | (                                            | i        | í<br>L. |   |       |   | М | 37         |          |        |   |     |     |     |     |                           |

| AGE XX  | 0 | 1            | 2    | 3 | 4      | 5                                            | 6        | 7       | 8 | 9     | A | в | с          | D        | E      | F | A15 | A14 | A13 | A12 |                           |

| A11     |   |              |      |   |        |                                              | 1        | 1       |   |       | _ |   |            |          |        |   |     |     |     | 1   |                           |

Figure 2-12B Memory Address Map & Jumper Selection Table For 2K Memory Block (16K Memory Cards)

Example:

To remap a 16K memory card with 2K memory blocks from 4000-7FFF to 8000-BFFF simply move jumper S1 to the S2 position.

Figure 2-13A Address Decoder Schematic For 4K Memory Blocks (32K Memory Card)

Figure 2-13B Memory Address Map & Jumper Selection Table For 4K Memory Block (32K Memory Cards)

To remap a 32K memory card with 4K memory blocks from 0000-7FFF to 8000-FFFF move jumper (S0-SX) to (S1-SX).

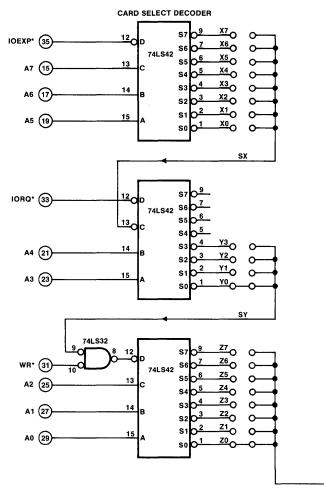

### I/O MAP

To facilitate port mapping (address assignments), the following tables are provided together with associated decoder schematics and examples. This information, along with the appropriate data sheets, fully defines I/O mapping for Series 7000 cards.

These charts provide the most significant Hex address in the left hand column with the least significant Hex address across the top. The jumper selection is taken from the body of the table associated with the proper Hex address. The appropriate address decoder schematic and an example of the use of each chart is provided for each I/O decoder type.

If I/O remapping is required the following procedure is recommended:

- 1. Use the charts by determining how many I/O addresses will be used by the card in question. Remember that many of the boards use the same address for Input ports and Output ports. A card with 4 Input ports and 4 Output ports uses only 4 I/O addresses.

- 2. Find the schematic of the decoding logic that matches that number of port addresses. This logic is common to all boards that use that number of addresses. This schematic indicates the number of jumpers, denoted by X, Y and Z, needed to fully select the address block. However, not every card will require all three jumpers. The jumper locations are shown on the associated data sheets.

- 3. Find the Hexadecimal address range on the appropriate I/O Address Mapping Jumper Selection table.

- 4. Select the desired I/O port address block and consult the matrix of jumper configurations to determine which jumpers are required.

- 5. Remove the existing jumpers and insert jumpers at the new positions found in Step 4.

The I/O card is now mapped and ready for use.

Notice that the Series 7000 boards fully decode the Lower 8 address lines and are manufactured with the jumpers as follows:

| CARD TYPE                    | CARD MAPPED AT<br>HEX PORT ADDRESS | RESERVED HEX ADDRESS<br>SPACE FOR SYSTEM EXPANSION |

|------------------------------|------------------------------------|----------------------------------------------------|

| 7100 & 7200                  | NA                                 | NA                                                 |

| 7300 Peripheral<br>Interface | C0                                 | C0-CF                                              |

| 7400 Analog I/O              | 80                                 | 80-BF                                              |

| 7500 Industrial<br>I/O       | 40                                 | 40-7F                                              |

| 7600 TTL I/O                 | 00                                 | 00-3F                                              |

| Non-Specified<br>Types       | D0                                 | D0-FF                                              |

Figure 2-14 Standard I/O Card Mapping

Figure 2-15A I/O Address Decoder And Schematic For 1 Address Per Card

ŜΖ

| моят        |    |    |    |    | LEA | ST S | IGN | FICA | NT H | EX A | DDRI | ESS |    |    |    |    | JUMPER        |

|-------------|----|----|----|----|-----|------|-----|------|------|------|------|-----|----|----|----|----|---------------|

| SIGNIFICANT | 0  | 1  | 2  | 3  | 4   | 5    | 6   | 7    | 8    | 9    | A    | В   | С  | D  | Е  | F  | X, Y & Z      |

| HEX ADDRESS | Z0 | Z1 | Z2 | Z3 | Z4  | Z5   | Z6  | Z7   | Z0   | Z1   | Z2   | Z3  | Z4 | Z5 | Z6 | Z7 | ← z           |

| 0           |    |    |    | X0 | Y0  |      |     |      |      |      |      | X0  | Y1 |    |    |    | Ν             |

| 1           |    |    |    | X0 | Y2  |      |     |      |      |      |      | X0  | Y3 | _  |    |    |               |

| 2           |    |    |    | X1 | Y0  |      |     |      |      |      |      | X1  | Y1 |    |    |    | ] ]           |

| 3           |    |    |    | X1 | Y2  |      |     |      |      |      |      | X1  | Y3 |    |    |    |               |

| 4.          |    |    |    | X2 | Y0  |      |     |      |      |      |      | X2  | Y1 |    |    |    |               |

| 5           |    |    |    | X2 | Y2  |      |     |      |      |      |      | X2  | Y3 |    |    |    | ]             |

| 6           |    |    |    | ХЗ | Y0  |      |     |      |      |      |      | ХЗ  | Y1 |    |    |    | x             |

| 7           |    |    |    | ХЗ | Y2  |      |     |      |      |      |      | X3  | Y3 |    |    |    | AND           |

| 8           |    |    |    | X4 | Y0  |      |     |      |      |      |      | X4  | Y1 |    |    |    |               |

| 9           |    |    |    | X4 | Y2  |      |     |      |      |      |      | X4  | Y3 |    |    |    | ]   Y         |

| A           |    |    |    | X5 | Y0  |      |     |      |      |      |      | X5  | Y1 |    |    |    | ]             |

| В           |    |    |    | X5 | Y2  |      |     |      |      |      |      | X5  | Y3 |    |    |    | ]             |

| с           |    |    |    | X6 | Y0  |      |     |      |      |      |      | X6  | Y1 |    |    |    | ]             |

| D           |    |    |    | X6 | Y2  |      |     |      |      |      |      | X6  | Y3 |    |    |    | ]             |

| E           |    |    |    | X7 | Y0  |      |     |      |      |      |      | X7  | Y1 |    |    |    | ] ]           |

| F           |    |    |    | X7 | Y2  |      |     |      |      |      |      | X7  | Y3 |    |    |    | $\mathcal{V}$ |

Figure 2-15B I/O Address Mapping And Jumper Selection Table For 1 Address Per Card

# Example:

To jumper a card to operate at I/O port address AB jumper pairs X5, Y1 and Z3.