Sol SYSTEMS MANUAL

# Processor Technology Corporation

7100 Johnson Industrial Drive Pleasanton, CA 94566 Telephone (415) 829-2600 ۰.

Copyright (C) 1976, 1977, 1978, Processor Technology Corporation Fourth Printing, February, 1978 Manual No. 730000

ļ

### PREFACE

This new edition of the Sol Systems Manual contains many revisions and additions made to the third printing. Information which accumulated in the Updates Section was integrated into the text. Parts lists were revised to include Processor Technology parts numbers for all parts, and to include new alternate parts. Several new and revised drawings were included in Section X, which should make assembly even easier. The keyboard, previously a kit, is now supplied as a complete tested subassembly. Sol 10, which consisted of a Sol 20 without the backplane, and with a lighter power supply, has been discontinued. Assembly procedures have improved from the experience of thousands of kitbuilders. An overall parts list for the entire kit has been included to facilitate receiving inspection.

Much effort has gone towards making this manual complete and accurate. The process of updating and revision always continues, however, and we invite your input. If you should find an error, or have suggestions for improving any of our manuals, please submit your suggestions in writing to our Technical Publications Department, and they will be given thorough consideration.

The three-ring binder you are reading from is an "easel" binder. The cover is hinged from side to side, as well as down the spine, so that it may form into an "easel" stand. To use this feature, lay the manual open on a table. Bend the full width of the manual along the creased hinge, until a resistance to further bending is felt. Then set the manual up on the table, with the bottom of the pages down against the table, and the top inclining away from you. In this position your hands are free for building, making measurements, or troubleshooting. A binder set up in this manner is shown below.

#### IMPORTANT

The first part of this manual you should read is at the very end: the Updates Section. If updates sheets have been inserted in this section, make sure to integrate them before you begin building or using your Sol.

### CONTENTS OUTLINE

Detailed contents precede each section.

- I INTRODUCTION and GENERAL INFORMATION

- II Sol POWER SUPPLY ASSEMBLY and TEST

- III Sol-PC ASSEMBLY and TEST

- IV PERSONALITY MODULE ASSEMBLY

- V KEYBOARD ASSEMBLY

- VI SOL CABINET-CHASSIS ASSEMBLY

- VII OPERATING PROCEDURES

- VIII THEORY OF OPERATION

- IX SOFTWARE

- X DRAWINGS

APPENDICES

UPDATES

Sol terminal  $\text{COMPUTER}^{\text{TM}}$

# LIST OF ILLUSTRATIONS

| FIGURE        | TITLE                                                       | PAGE           |

|---------------|-------------------------------------------------------------|----------------|

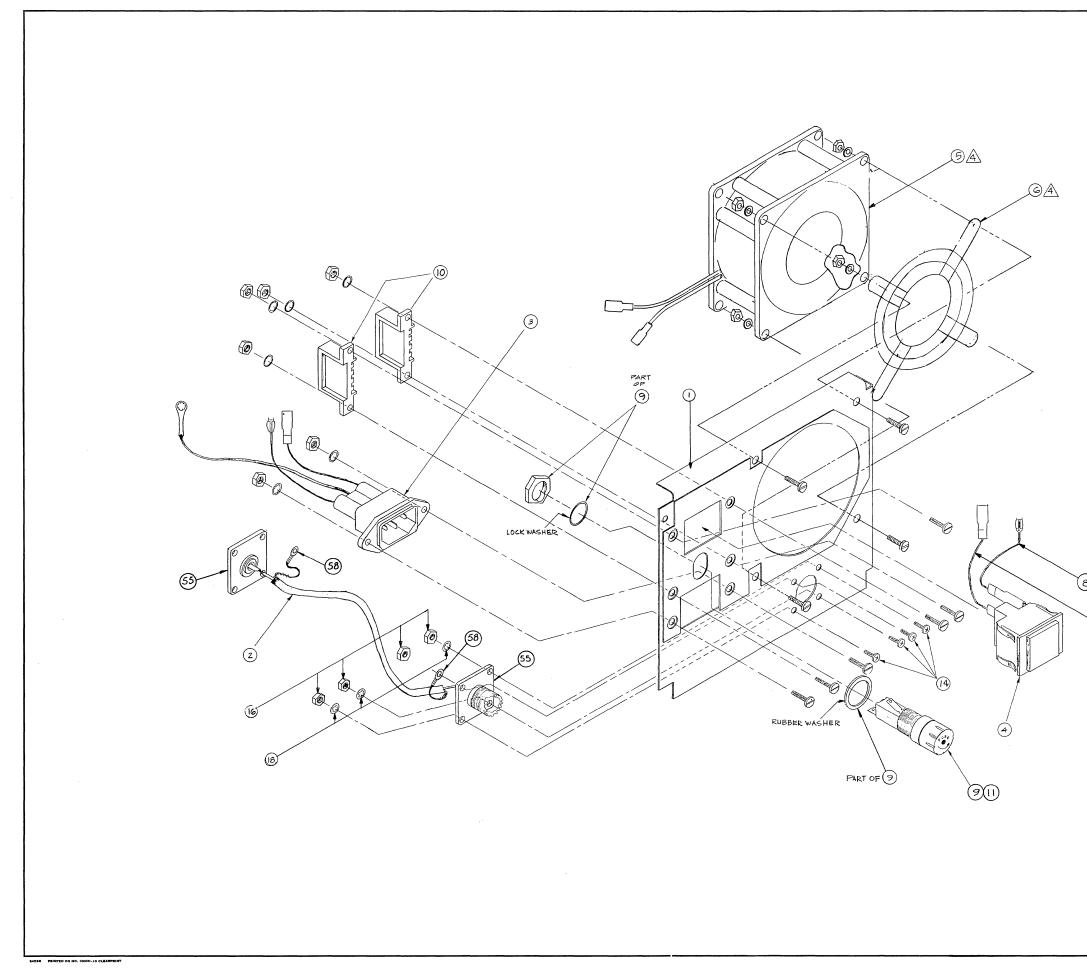

| 2-1           | Sol-20 fan closure plate assembly                           | II-7           |

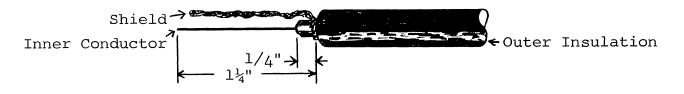

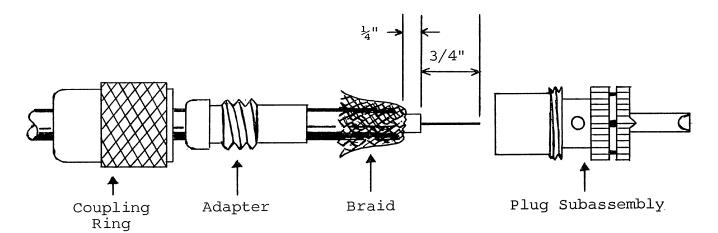

| 2-2           | Coaxial cable preparation                                   | II-9           |

| 2-3           | Aluminum heat sink installation                             | II <b>-</b> 12 |

| 2-4           | Partially assembled Sol-20 power supply subchassis assembly | II-16          |

| 2-5           | Sol-20 power supply subchassis assembly                     | II-17          |

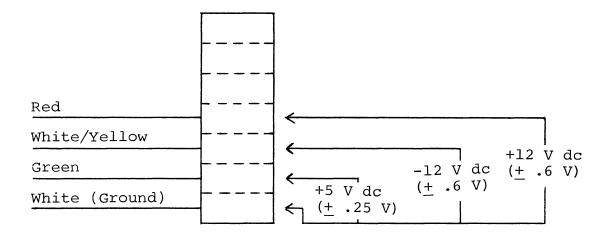

| 2-6           | Sol-PC power connector and voltage measurements             | II-21          |

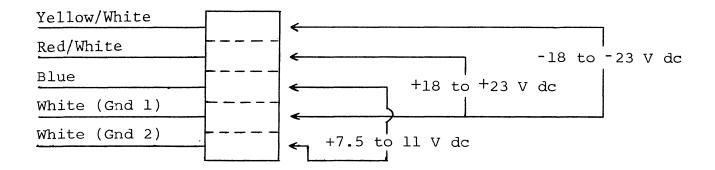

| 2-7           | Sol-20 power connector and voltage measurements             | II-21          |

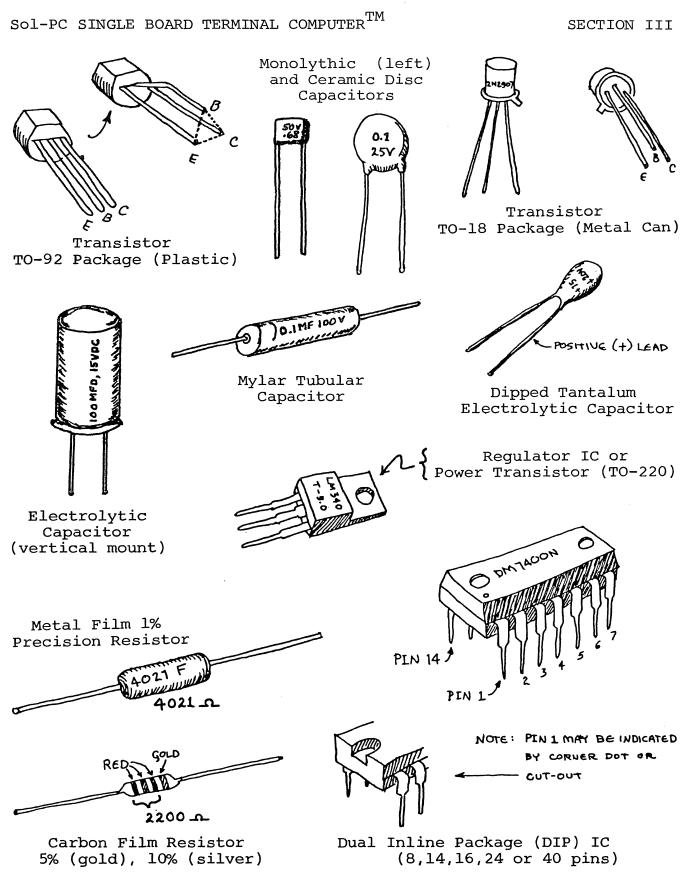

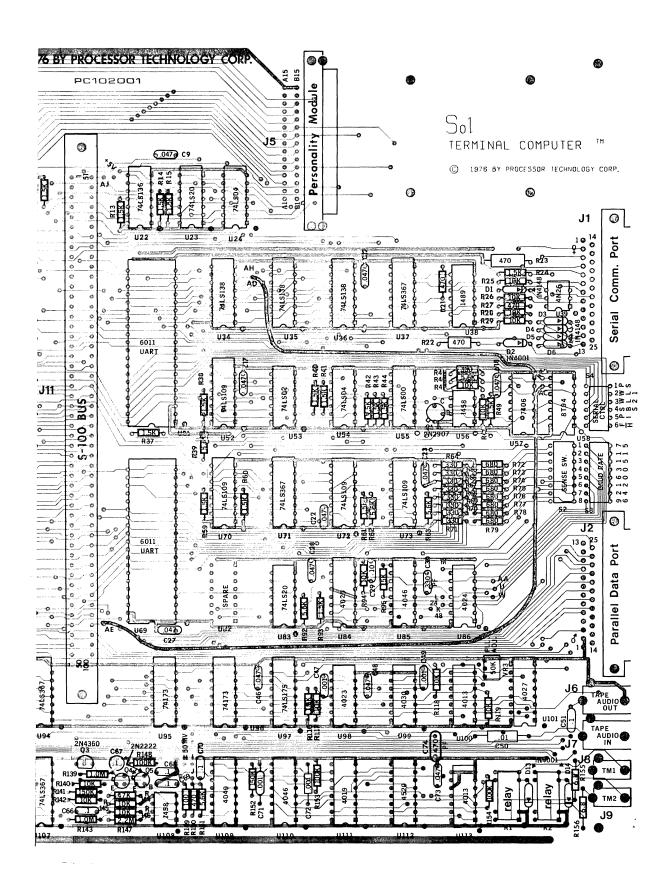

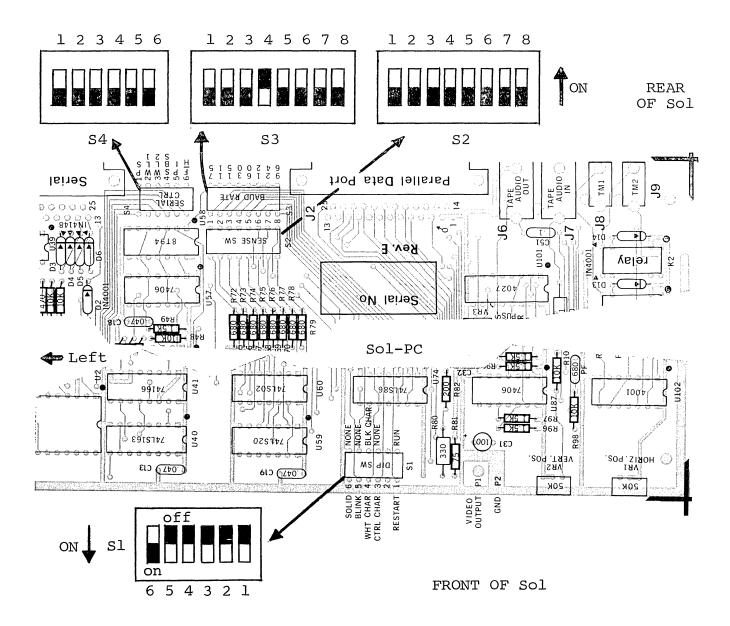

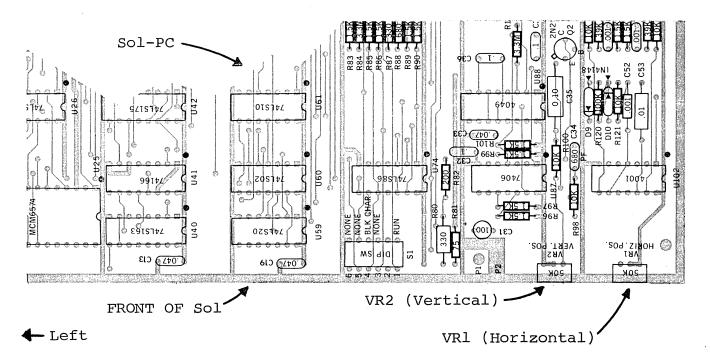

| 3-1           | Identification of components                                | III-8          |

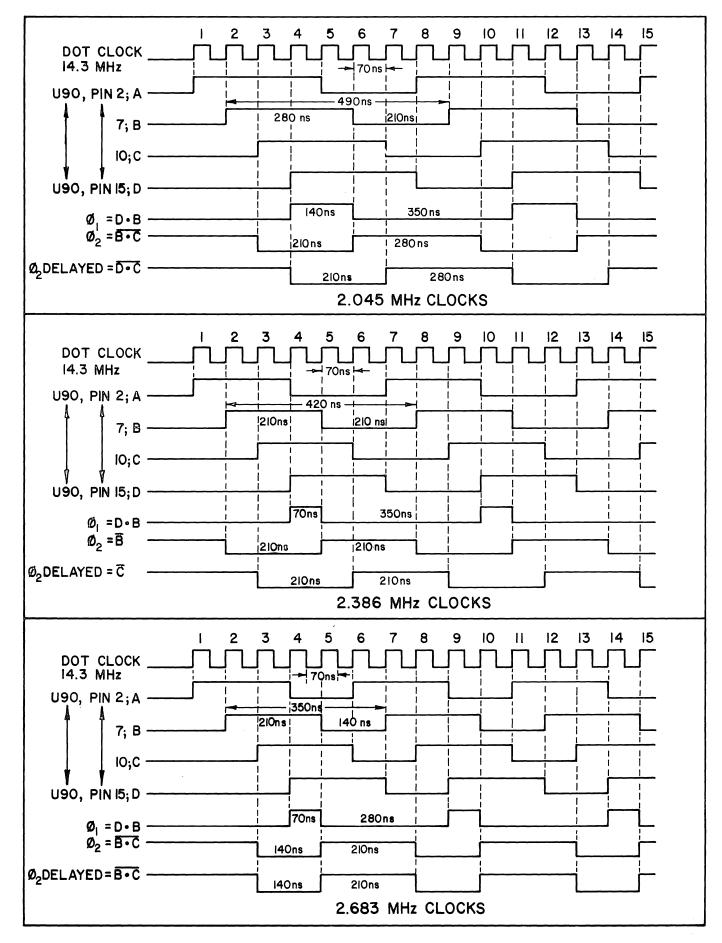

| 3-2           | Clock circuit waveforms                                     | III-18         |

| 3-3           | Deleted                                                     |                |

| 3-4           | Coaxial cable preparation                                   | III-21         |

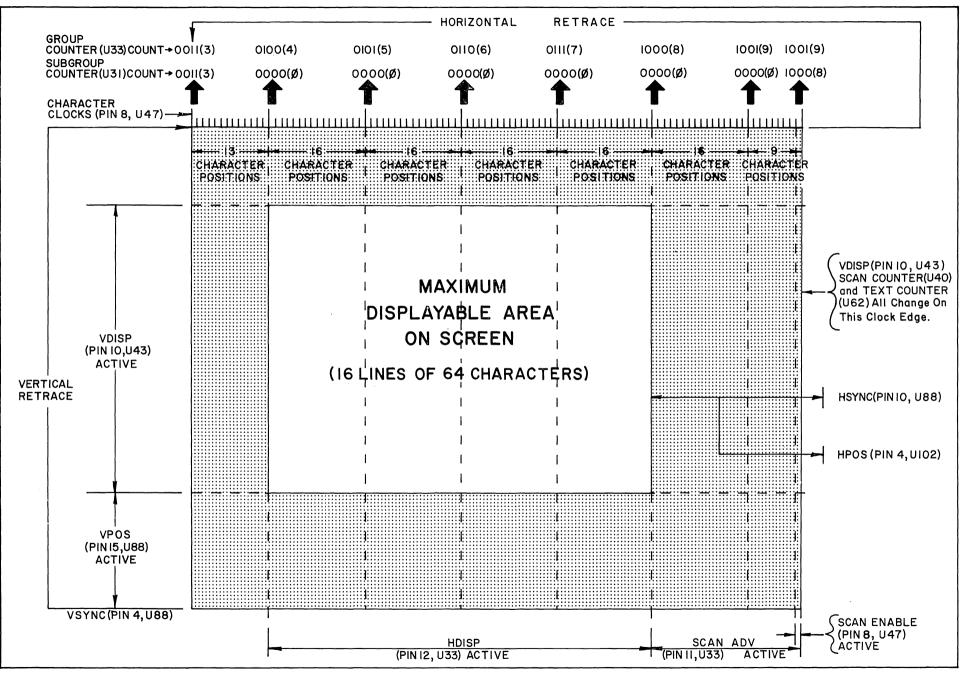

| 3-5           | Display section timing waveforms                            | III-23         |

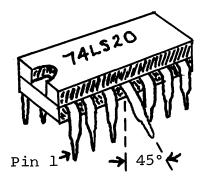

| 3-6           | Bending selected pins on U42, 59 and 75                     | III-25         |

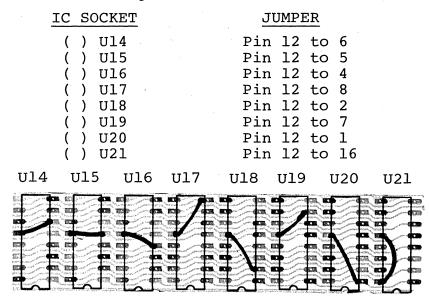

| 3-7           | Ul4 through U21 socket jumpers                              | III-26         |

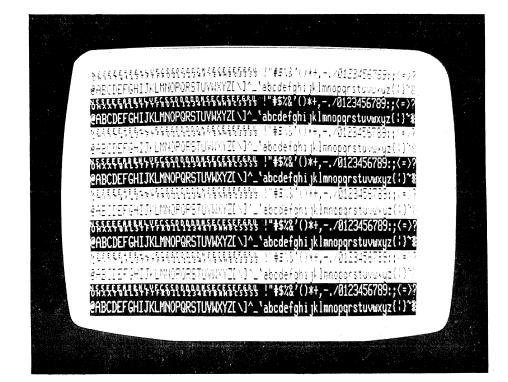

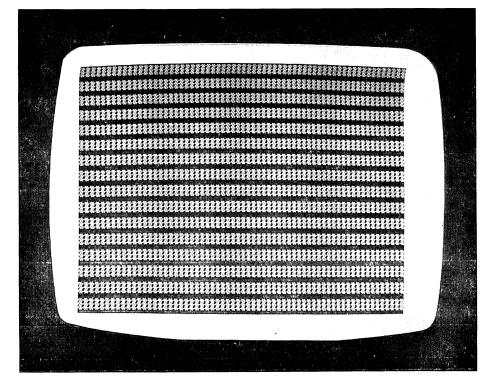

| 3-8           | Display circuits test pattern                               | III-27         |

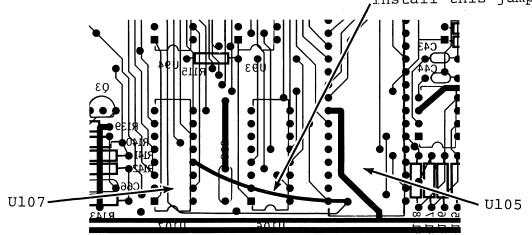

| 3 <b>-</b> 8A | Step 28A jumper installation                                | III-27         |

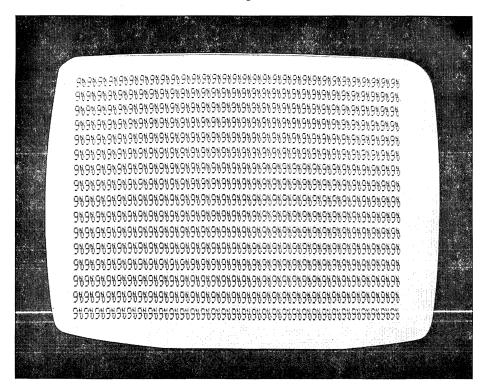

| 3-9           | CPU Functional Test No. 1 display                           | III-32         |

| 3-10          | CPU Functional Test No. 2 display                           | III-34         |

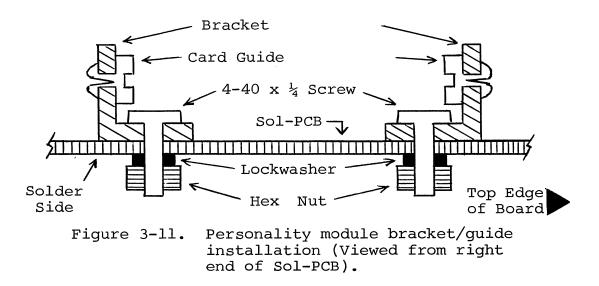

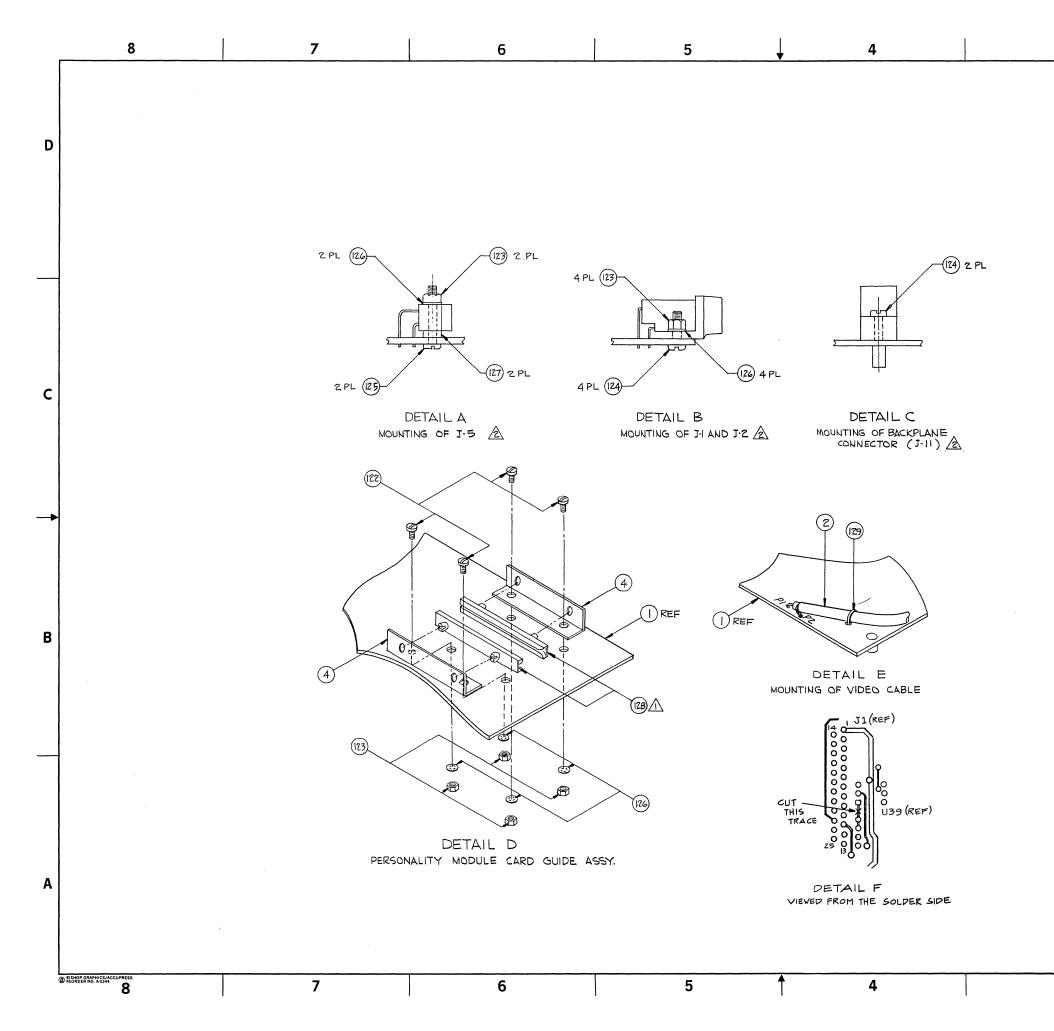

| 3-11          | Personality module bracket/guide installation               | III-34         |

| 3-12          | Installation of vectored interrupt jumpers                  | III-46         |

| 4-1           | Handle bracket installation                                 | IV-6           |

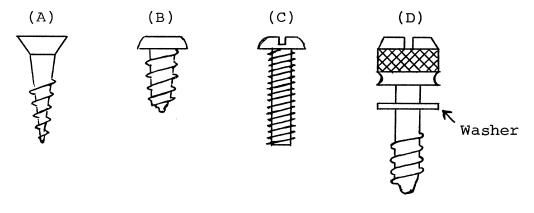

| 6-1           | Types of screws used in Sol cabinet-chassis<br>assembly     | VI-4           |

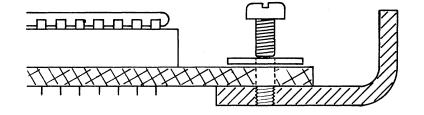

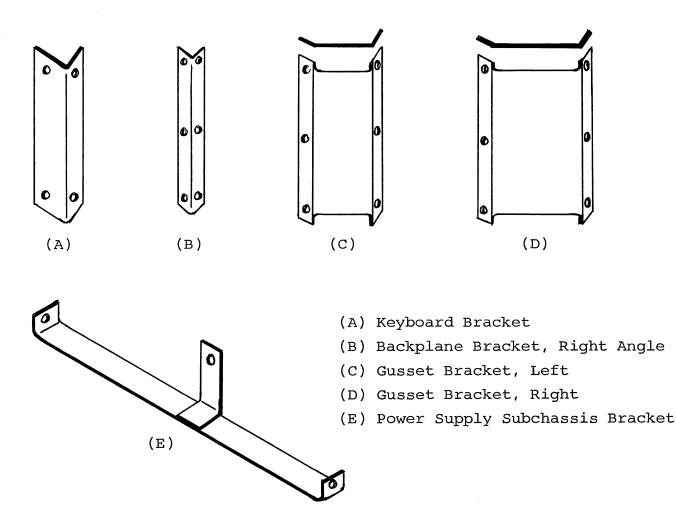

| 6-2           | Brackets used in Sol cabinet-chassis assembly               | VI-4           |

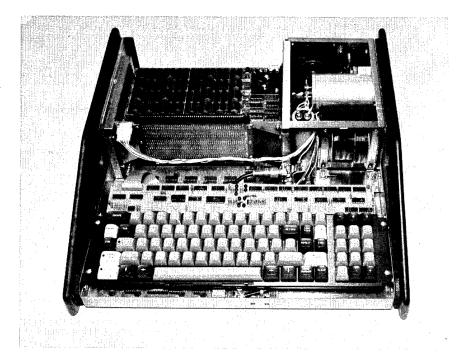

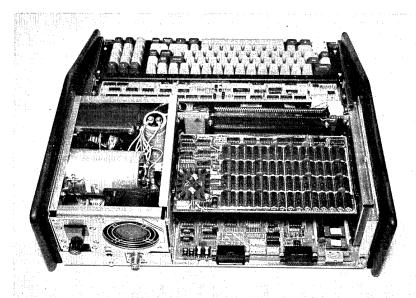

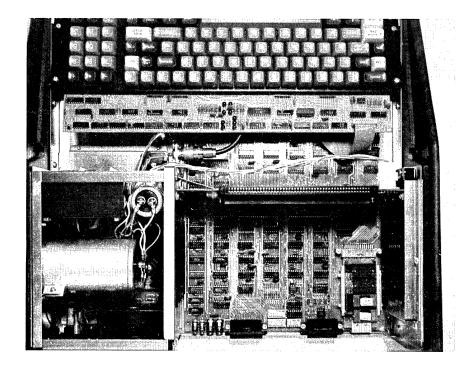

| 6-3           | Sol-20 with covers removed                                  | VI-10          |

| 6-4           | Sol-20 with covers removed                                  | VI-10          |

| 6-5           | Sol-PC coaxial cable connector assembly                     | VI-13          |

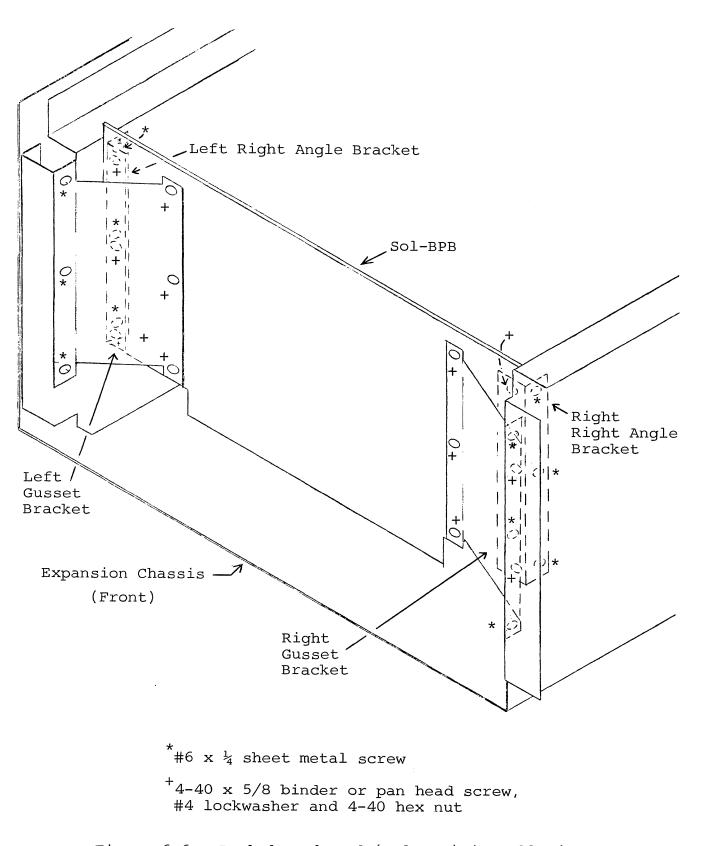

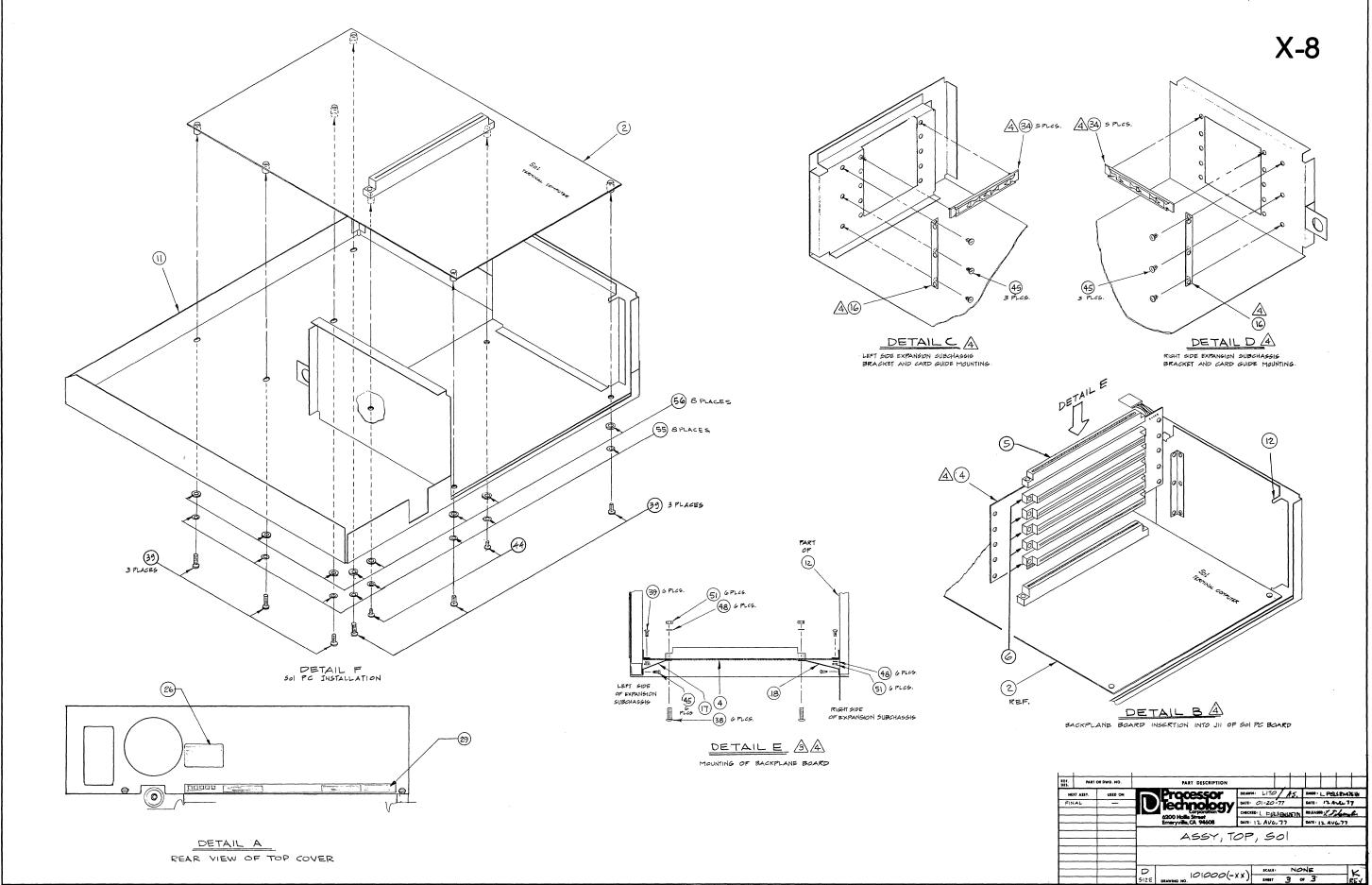

| 6-6           | Backplane board (Sol-BPB) installation                      | VI-15          |

| 6-7           | Backplane board (Sol-BPB) installation                      | VI-16          |

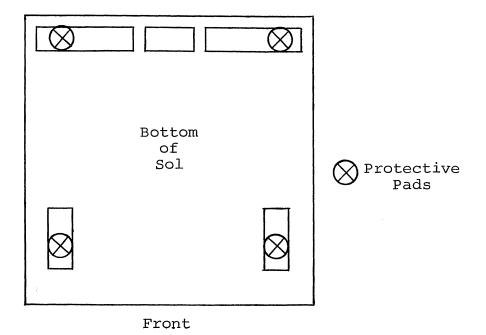

| 6-8           | Protective foot pad installation                            | VI-19          |

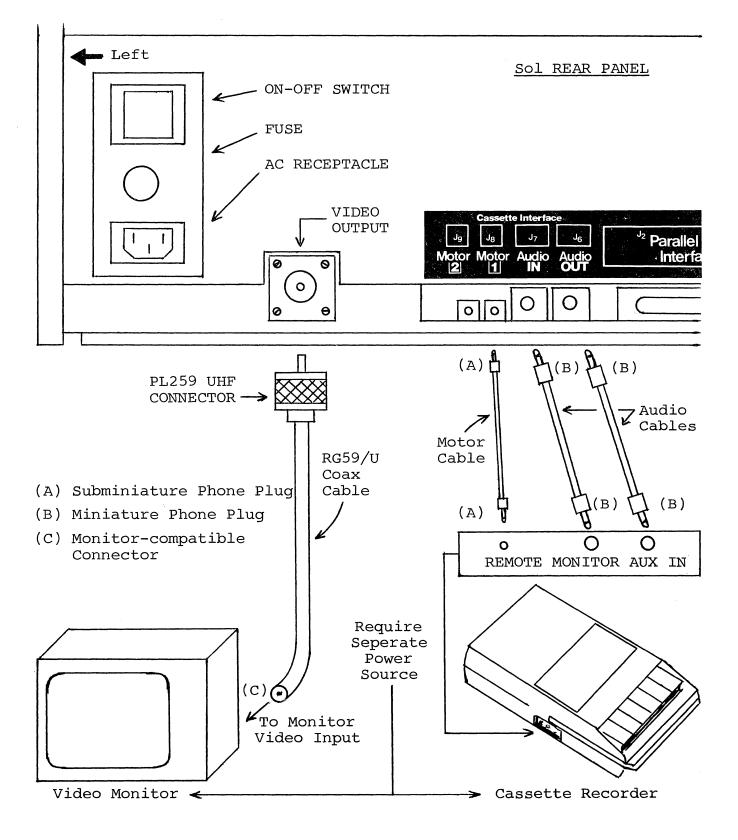

| 7-1           | Connecting the basic Sol system                             | VII-6          |

| 7-2           | Sol control switch settings for terminal mode               | VII-7          |

Sol terminal  $\text{COMPUTER}^{\text{TM}}$

### ILLUSTRATIONS/TABLES

VII-15

VII-23

VII-18-21

| FIGURE | TITLE                                                    | PAGE    |

|--------|----------------------------------------------------------|---------|

| 7-3    | Location of positioning adjustments, VRl and VR2         | VII-8   |

| 7-4    | Deleted                                                  |         |

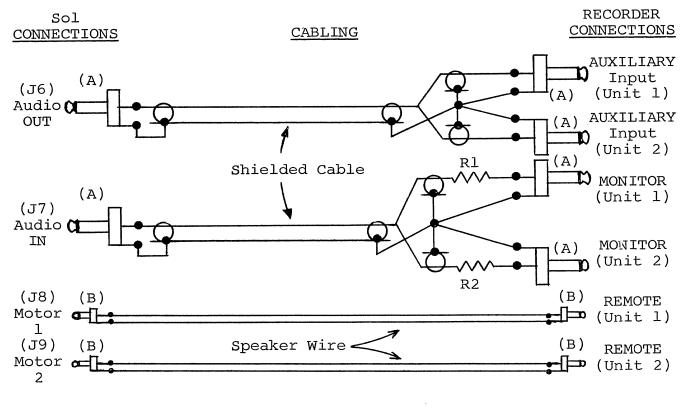

| 7-5    | Connecting Sol to two cassette recorders                 | VII-29  |

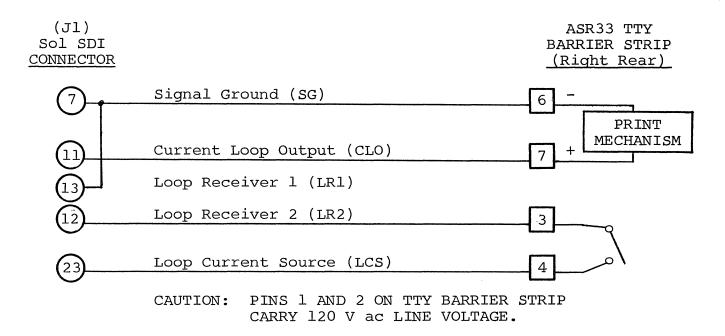

| 7-6    | Connecting Sol SDI to current loop device<br>such as TTY | VII-32  |

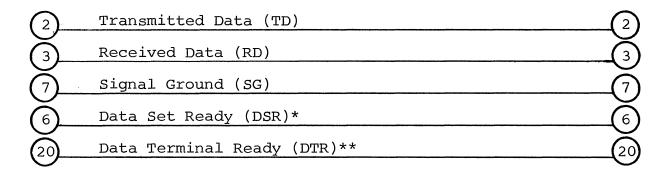

| 7-7    | Connecting Sol SDI to communications modem               | VII-32  |

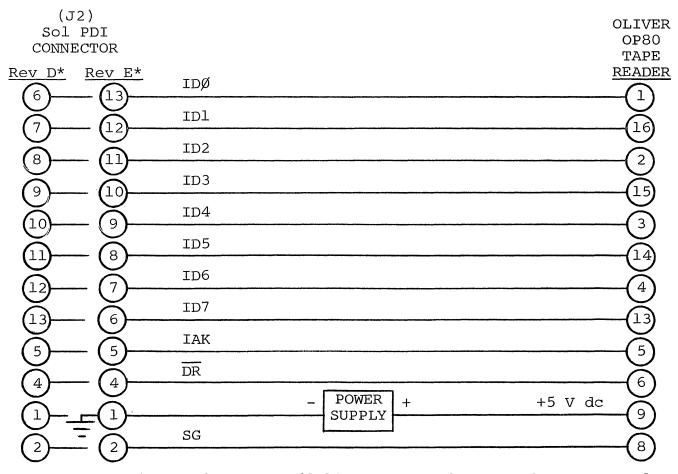

| 7-8    | Connecting Sol PDI to parallel device                    | VII-33  |

| 8-1    | Clock Generator Timing                                   | VIII-11 |

| 8-2    | Example of uppercase character (I) display               | VIII-24 |

| 8-3    | Example of lowercase character (p) display               | VIII-24 |

| 8-4    | Video Display timing                                     | VIII-27 |

| 8-5    | 6574 Character Generator ROM pattern                     | VIII-30 |

| 8-6    | 6575 Character Generator ROM pattern                     | VIII-31 |

| TABLE  | TITLE                                                    | PAGE    |

| 1-1    | Sol-20 Kit Parts List                                    | I-5-13  |

| 1-2    | Sol Systems Parts List                                   | I-14,15 |

| 2-1    | Sol Power Supply Parts List                              | II-2-4  |

| 3-1    | Sol-PC Parts List                                        | III-2-7 |

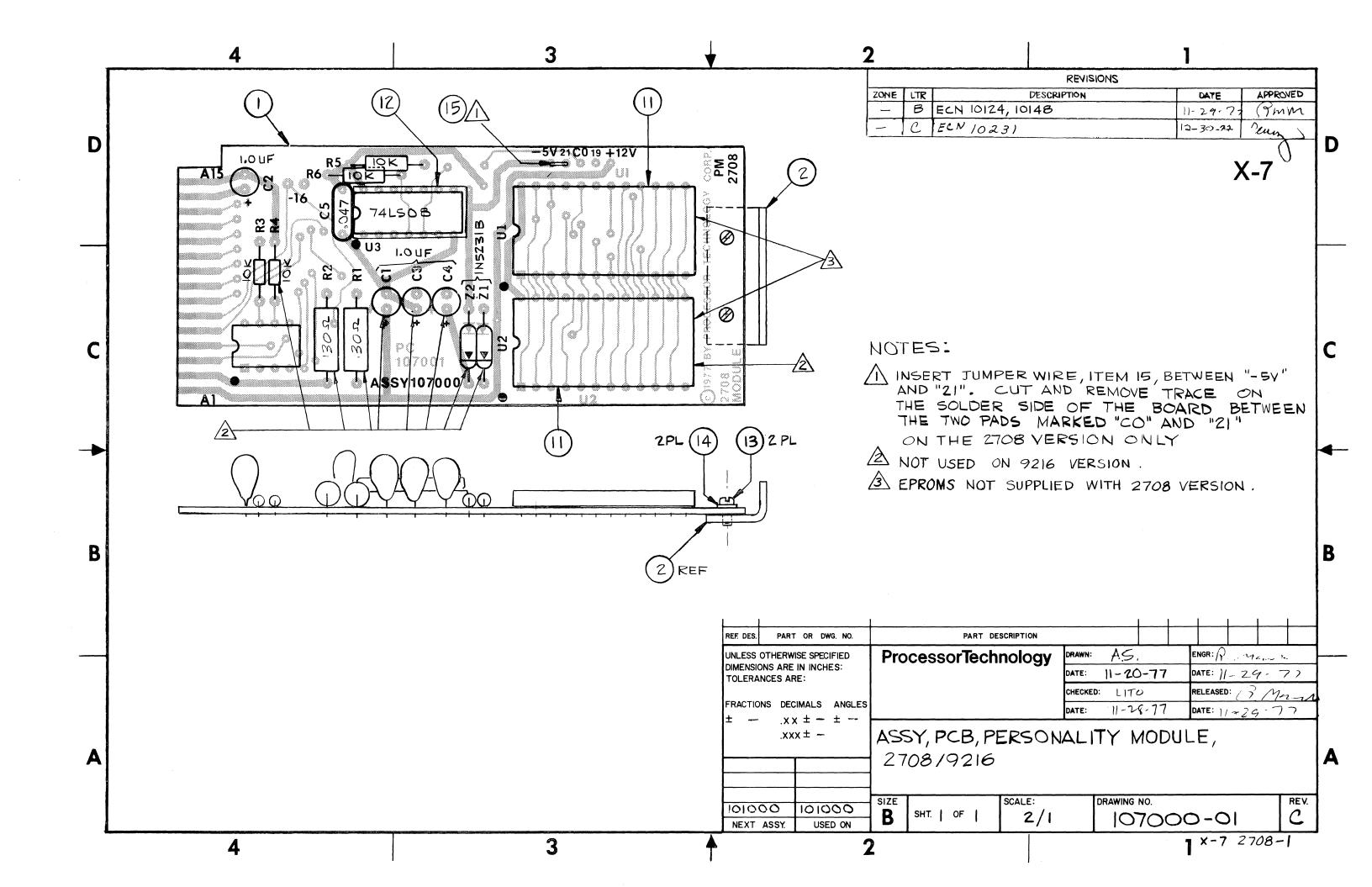

| 4-1    | PM2708/9216 Personality Module Parts List                | IV-2    |

| 6-1    | Sol-20 Cabinet-Chassis Parts List                        | VI-2,3  |

| 7-1    | Sol Operating Controls and Their Functions               | VII-2   |

Baud Rate Selection with Switch S3. . . . . . . . .

Control Character Symbols and Definitions . . . . .

Port Decoder (U35 & 36) Outputs and

Word Length Selection with S4-2 & 3 . . . . . . . . VII-15

REV A

7-2

7-3

7-4

7-5

8-1

# I INTRODUCTION and GENERAL INFORMATION

| 1.1 | Introduction                                                                                                                                        | ·1  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | l.l.l To the Sol Kit Builder                                                                                                                        |     |

| 1.2 | General Information                                                                                                                                 | ·2  |

|     | 1.2.1       Sol-20       Description       I-         1.2.2       Service       I-       I-         1.2.3       Replacement Parts       I-       I- | • 3 |

| 1.3 | Receiving Inspection                                                                                                                                | •4  |

|     | 1.3.1 Sol Kits                                                                                                                                      |     |

| 1.4 | Section X Drawings                                                                                                                                  | ·17 |

| 1.5 | Sol Kit Assembly Order                                                                                                                              | ·17 |

#### Sol SYSTEMS AND COMPONENTS

# 1.1 INTRODUCTION

This manual consists of nine separate sections presented in the preferred order of usage for the kit builder, a section of assembly drawings and schematics, appendices of useful information, and a section of updates.

Integrate the update information into this manual before doing anything else. Then finish reading this section completely, following the suggestions provided and performing the specified inspections.

Sections II, III, IV, V and X primarily supply assembly instructions and aids for the kit builder. The owner of a factory assembled unit, however, will find some of the test procedures and chassis-cabinet assembly instructions and drawings useful when servicing Sol. Operating Procedures (Section VII), Theory of Operation (Section VIII) and Software (Section IX) will be of interest to both the kit builder and assembled unit owner.

Three special features are incorporated in this manual to make it easier and more efficient to use. They are 1) an "easel" binder to facilitate reading while you work with your Sol, 2) an instruction and component installation check-off format to minimize omitting procedural steps, and 3) foldout drawings printed on one side only. The third feature eliminates much page juggling since a drawing, when folded out, is not obscured by the text pages.

### 1.1.1 To the Sol Kit Builder

For the Sol kit builder, this manual supplies the information needed to assemble, test and operate the Sol-PC Single Board Computer and the Sol-20 Terminal Computer Systems. As anxious as you are to assemble your kit, we suggest that you first take the time to read this section and scan the rest of the manual before making any inspections or starting assembly. (The time you take to "get on board Sol," so to speak, will be time well invested.) Then proceed with the receiving inspection and assembly. When assembling your kit, follow the instructions in the order given.

Should you run into a problem during assembly, call on us, or your Sol dealer, for help if necessary. If your completed kit does not work properly, recheck your assembly step by step. Most problems stem from poor soldering, failure to follow the instructions, backward installed components and/or installing the wrong component. Once your are satisfied that your Sol is correctly assembled, feel free to ask us, or your Sol dealer, for assistance if you still have trouble.

### 1.1.2 To Factory Assembled Sol Owners

For those who purchased a factory assembled and tested unit, this manual supplies the information needed to start you on the way

#### Sol SYSTEMS AND COMPONENTS

SECTION I

to using your Sol. It also contains information to help you understand how Sol works and how to service it. As anxious as you are to use Sol, we suggest that you first take the time to read this section and scan Sections VII, VIII, IX and Appendices AVI and AVIII. (The time you take to "get on board with Sol," so to speak, will be time well invested.) Then proceed with the receiving inspection, and, using Section VII as your guide, connect the basic Sol system, place it into operation and get acquainted with Sol by putting it through some simple operations. When doing this, follow the instructions in the order given.

Since your unit was factory assembled and tested before shipment, your Sol should operate correctly. If it doesn't, recheck your interconnect cabling. If a problem persists, feel free to ask us, or your Sol dealer, for assistance.

# 1.2 GENERAL INFORMATION

#### 1.2.1 Sol-20 Description

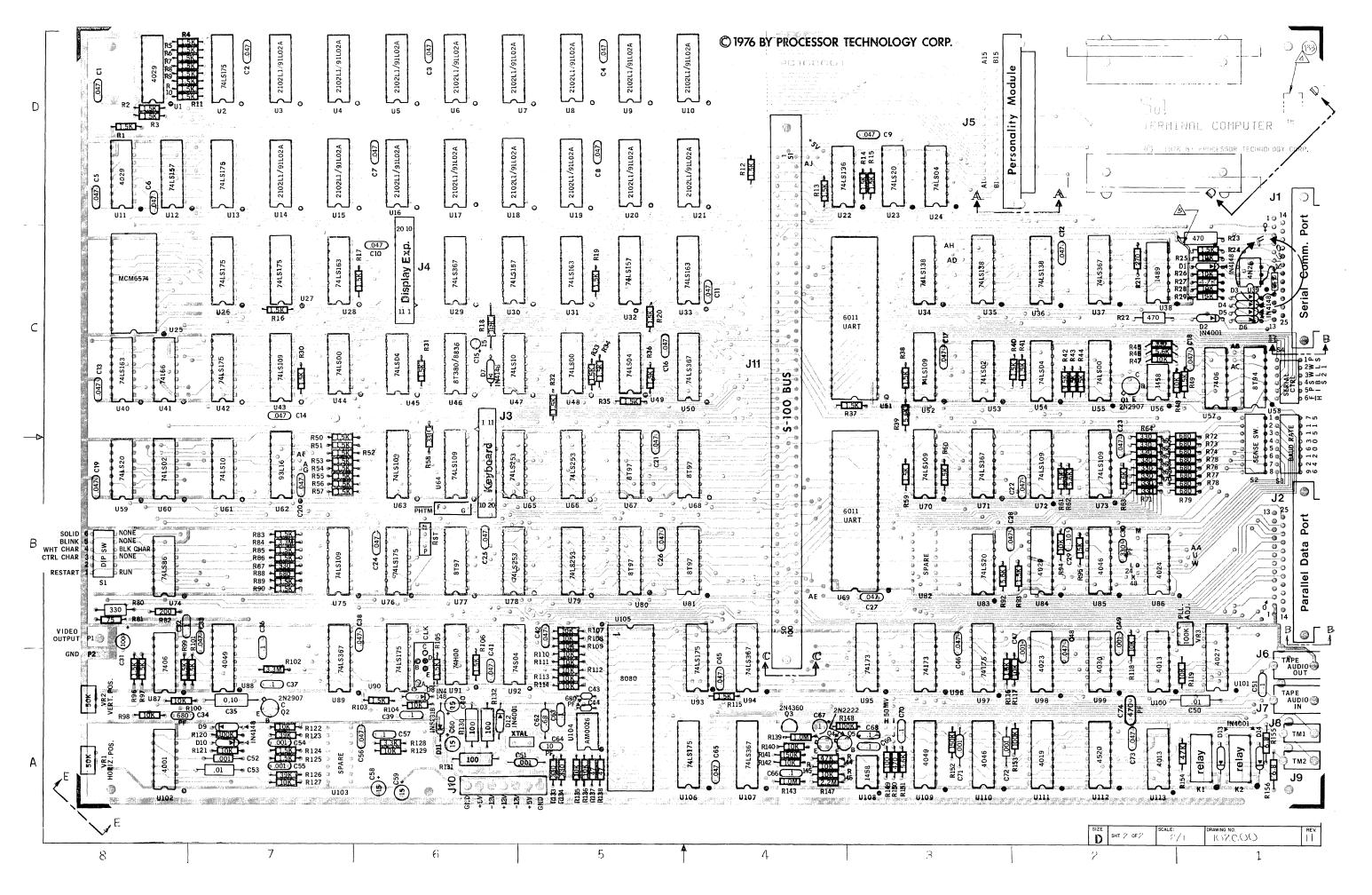

Except for the power supply and keyboard, the Sol-20 Terminal Computer electronics is contained on the Sol-PC. The Sol-20 is built around an 8080 microprocessor. Integral support circuitry permits full implementation of every 8080 function. Use of the popular S-100 bus assures compatibility with a large variety of memory boards and peripheral devices.

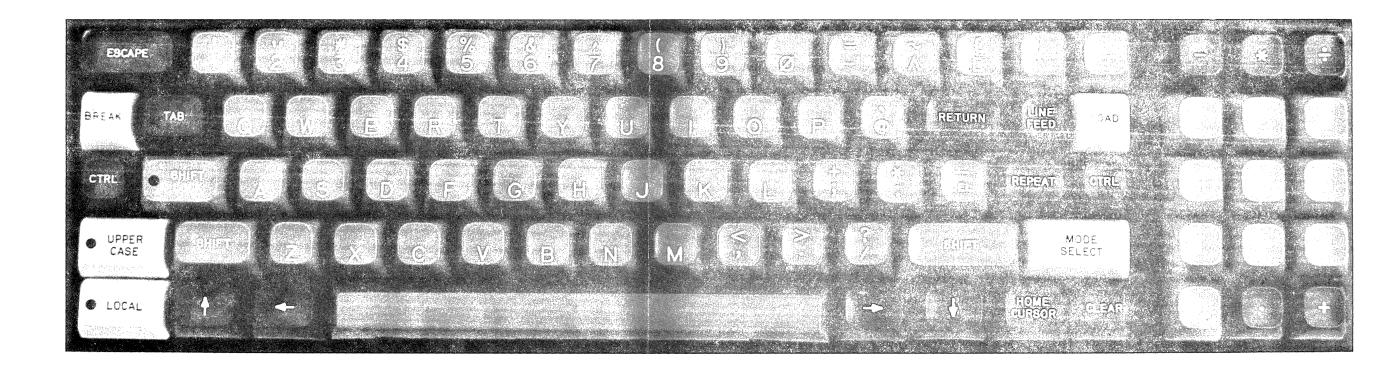

Sol-20 features an 85-key integral keyboard, both parallel and serial communications interfaces, an audio cassette tape interface, a video display generator, 1024 8-bit words of system RAM (random access memory), 1024 8-bit words of display RAM, and a plugin personality module with up to 2048 bytes of stored program on ROM (read only memory).

Parallel interfacing is eight bits each for input and output plus control handshaking signals, and the output bus is tri-stated TTL for bidirectional interfaces. The serial interface includes both asynchronous RS-232 and 20 mA current loop provisions with transmission rates of 75 to 9600 Baud (switch selectable).

The dual rate, 300 or 1200 bps (bits per second), audio cassette interface is program-controlled and self-clocking with a phaselock loop. It includes automatic level control. Recording is CUTS/ Byte Standard compatible, asynchronously Manchester coded at 1200/ 2400 Hz or 600/1200 Hz.

Video display circuitry generates sixteen 64 character lines from data stored in the integral 1024 8-bit word display RAM. Alphanumeric and control characters (the full 128 upper and lower case plu control ASCII character set) are displayed black on white or white on black (switch selectable). Multiple solid video inversion cursors,

### SO1 SYSTEMS AND COMPONENTS

SECTION I

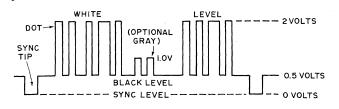

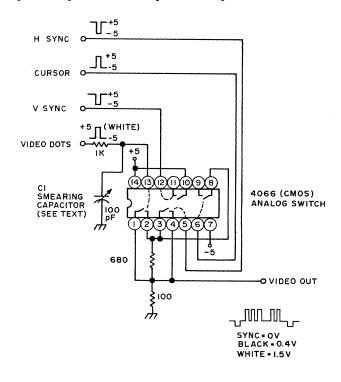

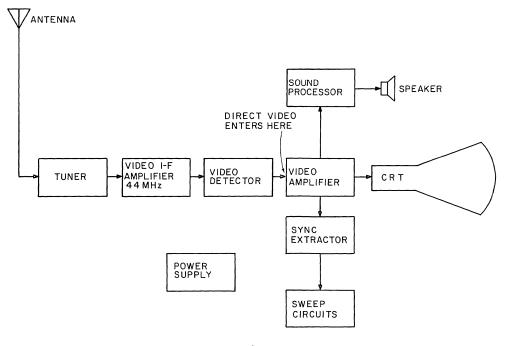

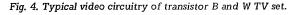

with switch selectable blink, may be programmed. The display output is standard EIA, 1.0 to 2.5 V peak-to-peak with composite negative sync, and a nominal 7 MHz bandwidth. It can thus be used to drive any standard video monitor. (A monochrome TV, converted for video input, can also be used. See Appendix VI.)

Included in the Sol are 1024 words of static, low power system RAM capable of full speed operation and a plug-in personality module that contains the software monitor, or control, program. Three personality modules are available for Sol:

- SOLOS--allows full stand-alone terminal/computer operation. It permits data storage and retrieval, control of electronic instruments and independent calculations. In general, SOLOS is the choice when the Sol system will be "on its own" operating independently of other computers. SOLOS is the standard personality module supplied with the Sol-20.

- PM2708--permits customized software with 2708 EPROMS (not supplied) for special applications.

- BOOTLOAD--same as SOLOS except that the SOLOS "TERMinal" command is replaced with a bootstrap loader program for use with the Helios II disk memory system.

Your Sol Computer power is easily expanded since it is compatible with all S-100 bus products. Sol-20 has a capacity for five expansion modules. Add-on memory and interface modules are available from Processor Technology as well as a host of software cassettes. Processor Technology also has a number of quality peripheral devices to work with Sol, including a TV monitor and cassette recorder.

### 1.2.2 Service

Service of all kinds is the responsibility of the dealer from whom you purchased your Sol-PC or Sol System. Contact the dealer if you have problems completing assembly and testing, or your Sol malfunctions and you cannot correct the problem.

### 1.2.3 Replacement Parts

Order replacement parts from Processor Technology or your Sol dealer. When ordering, specify our part number, component description (74LS109 IC (integrated circuit), 2N2222 transistor, and 680 ohm, 1/4 watt, 5% resistor for example). Processor Technology part numbers for Sol components and assemblies are given in Tables 1-1 and 1-2.

### Sol SYSTEMS AND COMPONENTS

### 1.3 RECEIVING INSPECTION

### 1.3.1 Sol Kits

Examine the shipping container(s) for signs of possible damage to the contents during transit. Then inspect the contents for damage. (We suggest you save the shipping materials for use in returning the kit to Processor Technology should it become necessary to do so.) If your Sol kit is damaged, immediately contact the carrier, and please write us at once describing the condition so that we can take appropriate action.

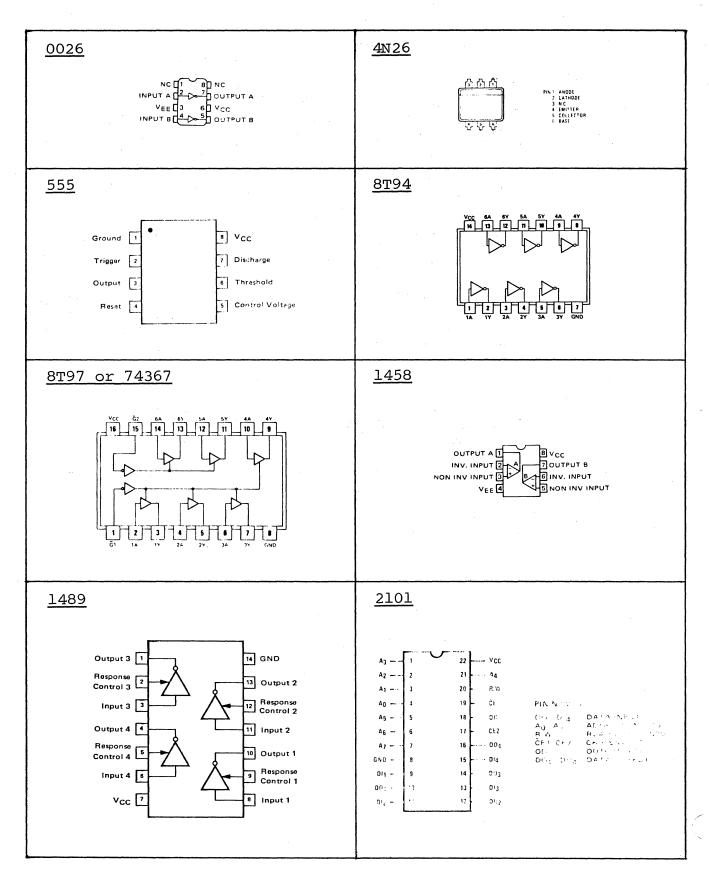

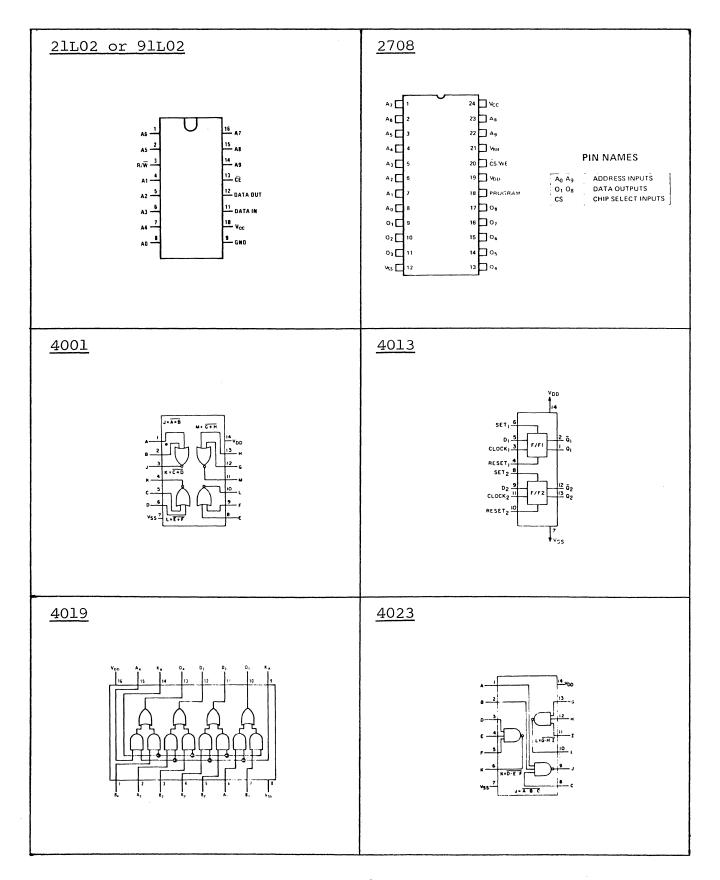

Then check all of the parts and components against Table 1-1 (Table 3-1 if you have a Sol-PC kit). Table 1-1 is a consolidated listing of the parts lists in Sections II, III, IV and VI. It lists the Processor Technology part number, description, alternate (if any), and <u>minimum quantity</u> for each part in the <u>complete</u> Sol-20 Terminal Computer kit. Note that some parts have alternates. An alternate is equivalent to its primary part and may be used in any location for which the primary part is specified. Where indicated in Table 1-1, alternates may be supplied with your kit in lieu of primary parts, and in some cases you may receive, for a given primary part, a combination of the primary and/or alternates. For example, you could receive one 8T97, two 8097 and two 74367 for the five 8T97's specified in Table 1-1; any of these may be used in any place that calls for an 8T97. (Also use Table 1-1 to find our part number for any replacement part you order.)

Figure 3-1 in Section III, Figures 6-1 and 6-2 in Section VI and Drawings X-1 through X-10 will help you identify unfamiliar parts. Should a part be missing, please contact us at once so that we can take appropriate action.

### 1.3.2 Assembled Sol Units

Examine the shipping container(s) for signs of possible damage to the contents during transit. Then inspect the contents for damage. (We suggest that you save the shipping materials for use in returning you Sol unit to Processor Technology should it become necessary to do so.) If your Sol unit is damaged, immediately contact the carrier, and write us at once describing the condition so that we can take appropriate action.

Then check the contents against Table 1-2 to be sure you received everything. Table 1-2 identifies all Sol System assemblies and parts and lists their quantity and Processor Technology part number. Should anything be missing, please contact us at once so that we can take appropriate action. If you need to order a replacement part or assembly sometime in the future, use the parts lists in Section II, III, IV and VI, in conjunction with Tables 1-1 and 1-2, to determine our part number and description.

(Continued on Page I-16.)

# Sol SYSTEMS AND COMPONENTS

# SECTION I

| PART NO. | DESCRIPTION | ALTERNATES     | MINIMUM<br>QUANTITY |

|----------|-------------|----------------|---------------------|

|          | INTEGRATED  | CIRCUITS       |                     |

| 701001   | 0026        | 75369          | 1                   |

| 701013   | 1458        | 72558          | 3                   |

| 701017   | 1489        | 75189          | 1                   |

| 701053   | 4N26        |                | 1                   |

| 701023   | 4001        | 14001          | 1                   |

| 701027   | 4013        | 1413           | 2                   |

| 701031   | 4019        |                | 1                   |

| 701033   | 4023        | 14023          | 1                   |

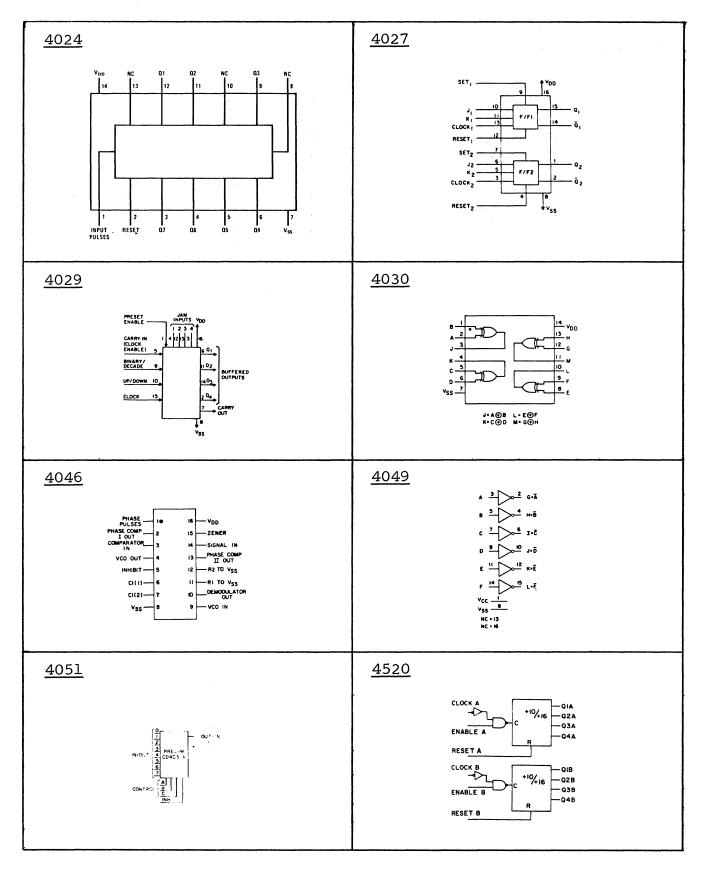

| 701035   | 4024        | 14024          | 1                   |

| 701037   | 4027        | 14027          | 1                   |

| 701039   | 4029        |                | 3                   |

| 701041   | 4030        |                | 1                   |

| 701045   | 4046        | 14046          | 2                   |

| 701047   | 4049        | 14049          | 2                   |

| 701051   | 4520        | 14520          | 1                   |

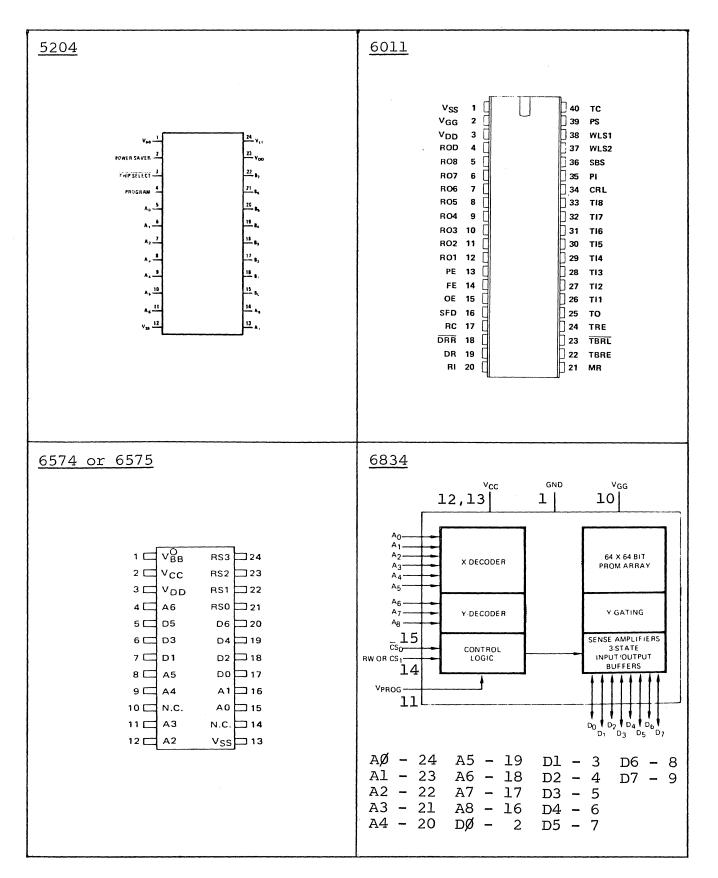

| 701011   | 6011        | 1602,2017,1013 | 2                   |

| 701007   | 6574        | 6575           | 1                   |

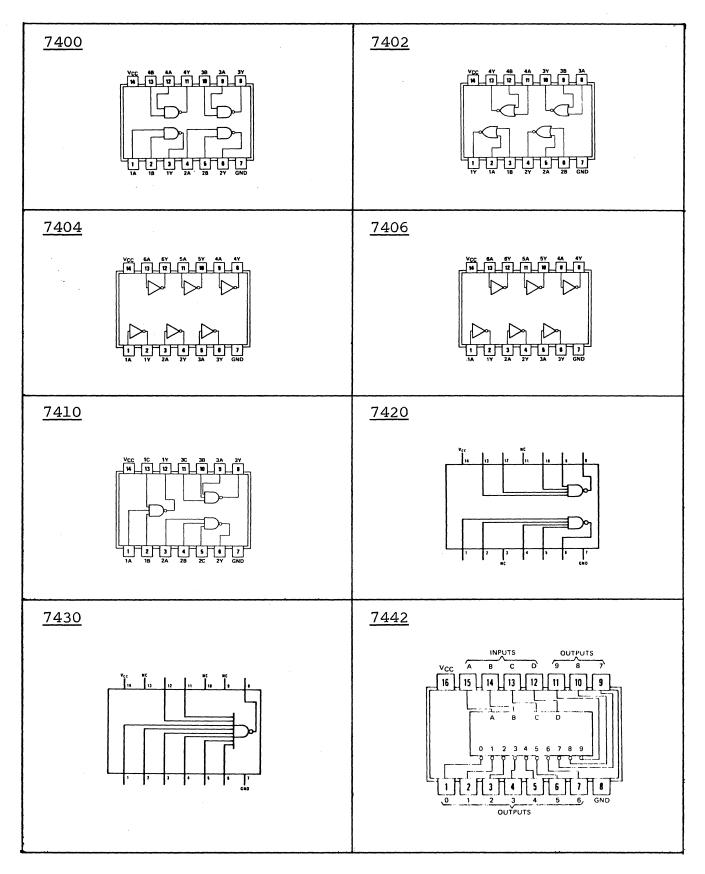

| 701086   | 74H00       |                | 1                   |

| 701090   | 74LS00      |                | 3                   |

| 701092   | 74LS02      | 9LS02          | 2                   |

| 701094   | 74LS04      |                | 4                   |

| 701088   | 74504       |                | 1                   |

| 701061   | 7406        |                | 2                   |

| 701098   | 74LS08      |                | 1                   |

| 701100   | 74LS10      |                | 2                   |

| 701108   | 74LS20      |                | 3                   |

| 701118   | 74LS86      |                | 1                   |

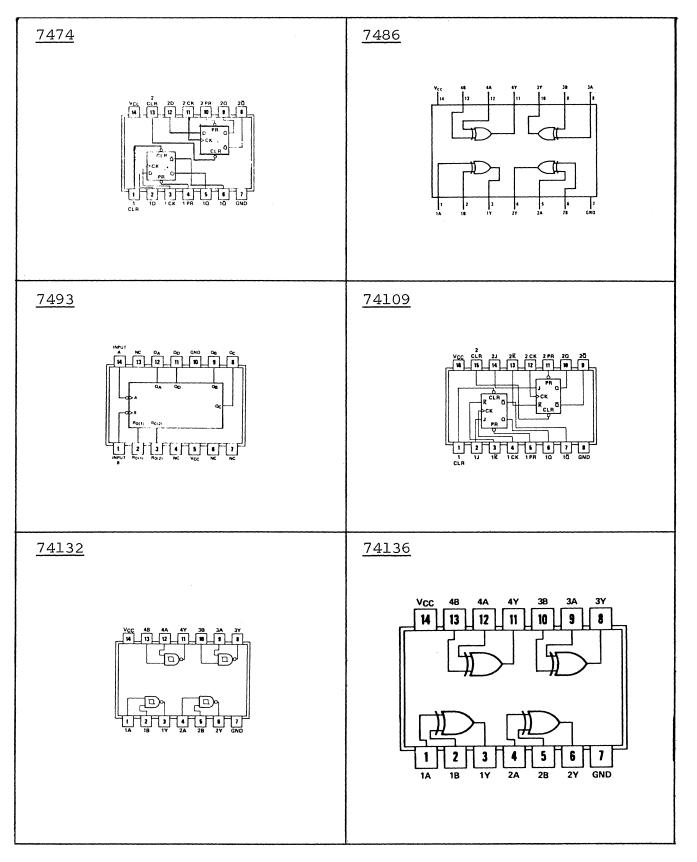

| 701120   | 74LS109     |                | 8                   |

| 701126   | 74LS136     |                | 1                   |

# Table 1-1. Sol-20 Kit Parts List.

SECTION I

| PART NO.   | DESCRIPTION            | ALTERNATES     | MINIMUM<br>QUANTITY |

|------------|------------------------|----------------|---------------------|

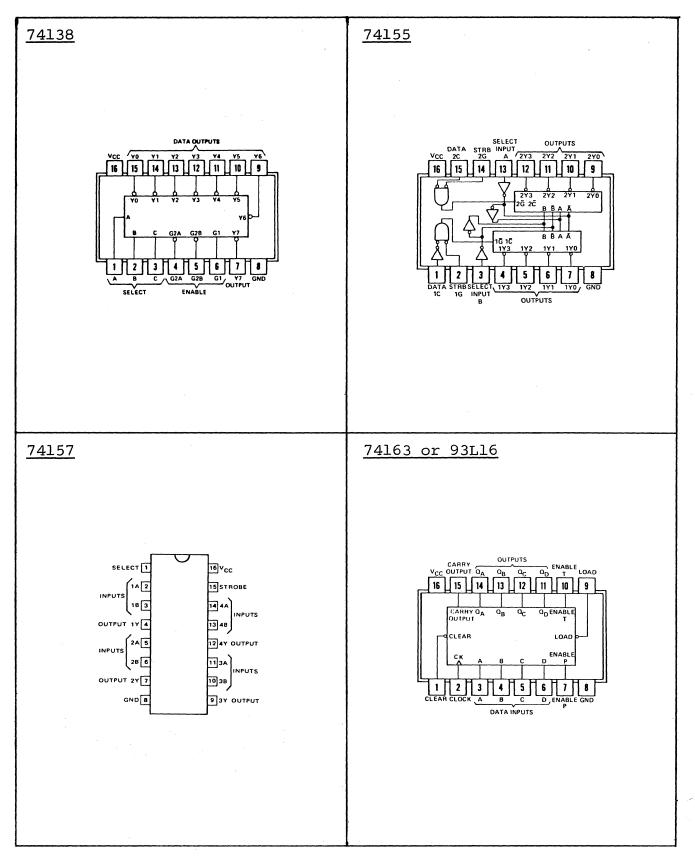

| 701128     | 74LS138                |                | 3                   |

| 701138     | 74LS157                |                | 3                   |

| 701142     | 74LS163                | 25LS163        | 4                   |

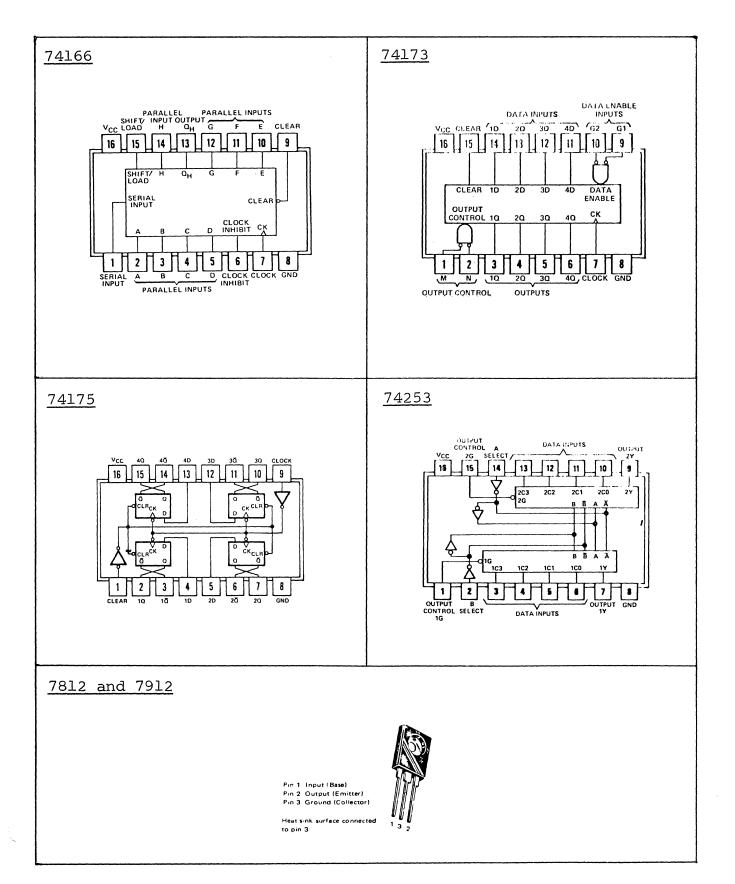

| 701075     | 74166                  |                | l                   |

| 701077     | 74173                  | 8110           | 2                   |

| 701079     | 74175                  |                | 1                   |

| 701146     | 74LS175                | 25LS175        | 9                   |

| 701150     | 74LS253                |                | 4                   |

| 701158     | 74LS367                |                | 7                   |

| 701164     | 7812                   |                | l                   |

| 701166     | 7912                   |                | l                   |

| 701184     | 8194                   |                | 1                   |

| 701186     | 8197                   | 8097, 74367    | 5                   |

| 701178     | 8 <b>1</b> 380         | 8836           | 1                   |

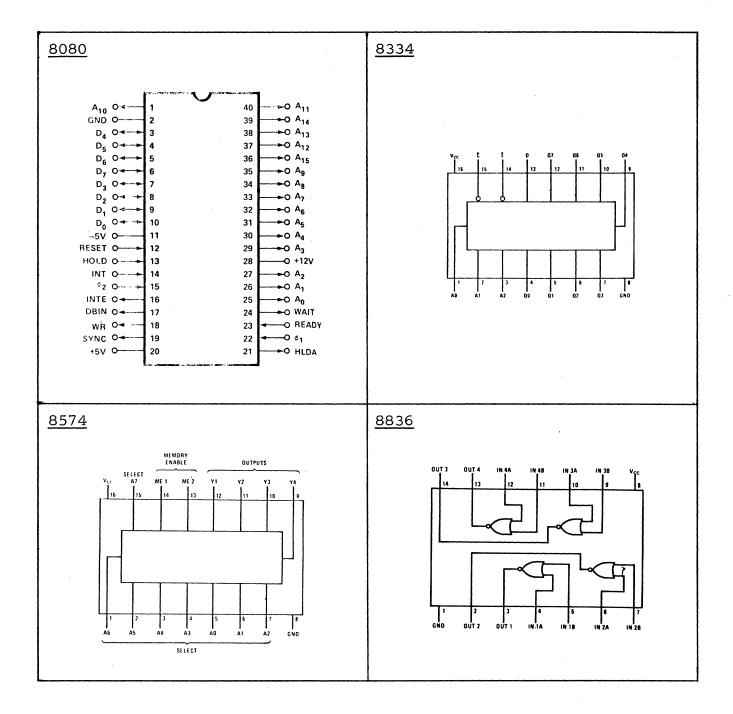

| 701170     | 8080A                  | 9080,8080      | 1                   |

| 701019     | 91L02                  | 2102, 21L02    | 16                  |

| 726004     | 9216* (marked "SOLOS") |                | 1*                  |

| 701192     | 93L16                  |                | 1                   |

| *9216 Pers | sonality Module only.  |                |                     |

|            | TRANSIS                | STORS          |                     |

| 702016     | TIP41                  |                | 1                   |

| 702002     | 2N2222                 |                | 4                   |

| 702004     | 2N2907                 |                | 2                   |

| 702010     | 2N4360                 |                | 1                   |

|            | DIODES and BRII        | DGE RECTIFIERS | •                   |

| 703001     | ln270                  |                | 1                   |

| 703003     | 1N4001                 |                | 6                   |

| 703005     | lN4148                 | 1N914          | 10                  |

Table 1-1. Sol-20 Kit Parts List. (Continued)

REV A

SECTION I

| Table 1-1. Sol-20 Kit Parts List. (Continue |

|---------------------------------------------|

|---------------------------------------------|

| PART NO.   | DESCRIPTION                     | ALTERNATES | MINIMUM<br>QUANTITY |

|------------|---------------------------------|------------|---------------------|

| 703011     | 1N5231                          |            | 2*                  |

| 703029     | 101                             |            | 1                   |

| 703027     | 106-2                           | 10632      | 1                   |

| 703031     | 970-1                           |            | 1                   |

| 703033     | 980-1                           |            | 1                   |

| *4 if 2708 | Personality Module is supplied. |            |                     |

|            | RESIST                          | TORS       |                     |

| 705002     | 0.1 ohm, wire wound, 5W         |            | 1                   |

| 705005     | 6.8 ohm, 1/2 W, 5%              |            | 2                   |

| 705009     | 39 ohm, 2 W, 5%                 |            | 1                   |

| 705011     | 47 ohm, 1/4 W, 5%               |            | 3                   |

| 705013     | 68 ohm, 1/4 W, 5%               |            | l                   |

| 705015     | 75 ohm, 1/4 W, 5%               |            | 1                   |

| 705017     | 100 ohm, 1/4 W, 5%              |            | 2                   |

| 705019     | 100 ohm, 1/2 W, 5%              |            | 3                   |

| 705018     | 130 ohm, 1/2 W, 5%              |            | 2*                  |

| 705023     | 200 ohm, 1/4 W, 5%              |            | 1                   |

| 705026     | 270 ohm, 1/4 W, 5%              |            | 1                   |

| 705025     | 330 ohm, 1/4 W, 5%              |            | 15                  |

| 705027     | 330 ohm, 1/2 W, 5%              |            | 1                   |

| 705031     | 470 ohm, 1/4 W, 5%              |            | 1                   |

| 705033     | 470 ohm, 1/2 W, 5%              |            | 2                   |

| 705035     | 680 ohm, 1/4 W, 5%              |            | 9                   |

| 705041     | 1K ohm, 1/4 W, 5%               |            | 2                   |

| 705043     | 1.5K ohm, 1/4 W, 5%             |            | 63                  |

| 705045     | 1.69K ohm, 1/4 W, 1%            |            | 1                   |

| 705052     | 3.3K ohm, 1/4 W, 5%             |            | 1                   |

| 705053     | 4.02K ohm, 1/4 W, 1%            |            | 1                   |

\*2708 Personality Module Only.

### Sol SYSTEMS AND COMPONENTS

### SECTION I

# Table 1-1. Sol-20 Kit Parts List. (Continued)

| PART NO.       | DESCRIPTION                         | ALTERNATES | MINIMUM<br>QUANTITY |

|----------------|-------------------------------------|------------|---------------------|

| 705055         | 4.7K ohm, 1/4 W, 5%                 |            | 1                   |

| 705057         | 5.6K ohm, 1/4 W, 5%                 |            | 6                   |

| 705061         | 10K ohm, 1/4 W, 5%                  |            | 38**                |

| 705065         | 15K ohm, 1/4 W, 5%                  |            | 2                   |

| 705071         | 39K ohm, 1/4 W, 5%                  |            | 2                   |

| 705072         | 47K ohm, 1/4 W, 5%                  |            | 2                   |

| 705073         | 50K ohm, variable                   |            | 2                   |

| 705075         | 56K ohm, 1/4 W, 5%                  |            | 1                   |

| 705081         | 100K ohm, 1/4 W, 5%                 |            | 3                   |

| 705074         | 100K ohm, variable                  |            | 1                   |

| 705083         | 150K ohm, 1/4 W, 5%                 |            | 2                   |

| 705085         | 1M ohm, 1/4 W, 5%                   |            | 2                   |

| 705089         | 2.2M ohm, 1/4 W, 5%                 |            | 1                   |

| 705091         | 3.3M ohm, 1/4 W, 5%                 |            | 2                   |

| **<br>39 if 27 | 708 Personality Module is supplied. |            |                     |

### CAPACITORS

| 707001 | 10 pf, Disc Ceramic   | l  |

|--------|-----------------------|----|

| 707005 | 330 pf, Disc Ceramic  | 1  |

| 707009 | 470 pf, Disc Ceramic  | 1  |

| 707011 | 680 pf, Disc Ceramic  | 3  |

| 707015 | .001 µf, Disc Ceramic | 6  |

| 707017 | .001 µf, Mylar        | 2  |

| 707021 | .Ol µf, Mylar         | 2  |

| 707023 | .047 µf, Disc Ceramic | 39 |

| 707025 | .l µf, Disc Ceramic   | 14 |

| 707027 | .l μf, Mylar          | 1  |

| 707029 | .68 µf, Mono Ceramic  | 1  |

| 707032 | l µf, Tantalum        | 2* |

| 707036 | 15 µf, Tantalum       | 8  |

|        |                       |    |

\*5 if 2708 Personality Module is supplied.

REV A

### SECTION I

1

| PART NO.   | DESCRIPTION ALTERNATE             | S MINIMUM<br>QUANTITY |

|------------|-----------------------------------|-----------------------|

| 707038     | 100 µf, Aluminum                  | l                     |

| 707041     | 2500 μf, Aluminum                 | 2                     |

| 707047     | 18,000 µf, Aluminum               | 1                     |

| 707049     | 54,000 µf, Aluminum               | 1                     |

|            | SOCKETS, CONNECTORS and HEADERS   |                       |

| 713002     | DIP, 8-pin                        | 2                     |

| 713004     | DIP, 14-pin                       | 30                    |

| 713006     | DIP, 16-pin                       | 74                    |

| 713012     | DIP, 24-pin                       | 2*                    |

| 713014     | DIP, 40-pin                       | 3                     |

| 717002     | Header, Male, 20-pin              | 2                     |

| 717019     | Header, Male, 7-pin               | 1                     |

| 717011     | Socket, Female, 25-pin            | 1                     |

| 717013     | Socket, Male, 25-pin              | 1                     |

| 717044     | Socket, Phone Jack, Miniature     | 2                     |

| 717045     | Socket, Phone Jack, Subminiature  | 2                     |

| 717042     | Socket, Coax, 75 ohm              | 2                     |

| 717043     | Plug, Coax 75 ohm                 | 1                     |

| 717047     | Sleeve, Adapter, Coax             | 1                     |

| 719001     | Connector, PC, 100-pin            | 1                     |

| 719002     | Connector, PC, 100-pin            | 6                     |

| 719003     | Connector, PC, 30-pin             | 1                     |

| 724005     | Commoning Block, 5 position       | 2                     |

| *3 if 2708 | 3 Personality Module is supplied. |                       |

|            | SWITCHES, RELAYS and HOLDERS      |                       |

| 723002     | Switch, DIP, 6 Section            | 2                     |

| 723003     | Switch, DIP, 8 Section            | 2                     |

| 723005     | Switch, AC Power                  | 1                     |

| 723010     | Relay, DIP, 500 ohm Reed          | 2                     |

|            |                                   |                       |

# Table 1-1. Sol-20 Kit Parts List. (Continued)

REV A

724007

Holder, Fuse

I-9

SECTION I

Table 1-1. Sol-20 Kit Parts List. (Continued)

| PART NO.                | DESCRIPTION                           | ALTERNATES | MINIMUM<br>QUANTITY |

|-------------------------|---------------------------------------|------------|---------------------|

|                         | PRINTED CIRCUIT BOARDS                |            |                     |

| 105010                  | Sol-REG                               |            | l                   |

| 102002                  | Sol-PC                                |            | 1                   |

| 107001                  | 2708/9216 Personality Module          |            | l                   |

| 103001                  | Backplane                             |            | 1                   |

|                         | WIRE, CABLE and CABLE ASSEME          | BLIES      |                     |

| 716000                  | Wire, 24 AWG                          |            | 7"*                 |

| 716008                  | Wire, 24 AWG                          |            | 1'                  |

| 716005                  | Cable, Coaxial, 75 ohm                |            | 4'                  |

| 718002                  | Cable Assembly, Flat, 20-Wire         |            | l                   |

| 105012                  | Cable, Sol PC DC Power, 5-Wire        |            | l                   |

| 105007                  | Cable, Sol 20 DC Power, 4-Wire        |            | l                   |

| 718001                  | Cord, AC Power, 3-Wire                |            | 1                   |

| 105013                  | Cable Assembly, C-8                   |            | l                   |

| 105018                  | Cable Assembly, AC Connector          |            | 1                   |

| 105024                  | Assembly, Fuse Lead, AC Switch        |            | 1                   |

| 105025                  | Assembly, Neutral Lead, AC Switch     |            | 1                   |

| 103003                  | Cable Assembly, Sol Backplane         |            | 1                   |

| <sup>*</sup> 6" if 2708 | 3 Personality Module is not supplied. |            |                     |

|                         | HANDLES, BRACKETS and CARD GU         | JIDES      |                     |

| 102004                  | Bracket, Mounting, Sol PC, 2"         |            | 2                   |

| 101016                  | Bracket, Backplane, Right-Angle       |            | 2                   |

| 101017                  | Bracket, Gusset, Left Side            |            | 1                   |

| 101047                  | Bracket, Gusset, Right Side           |            | 1                   |

| 101005                  | Bracket, Connecting                   |            | 1                   |

| 101006                  | Bracket, Keyboard Support             |            | 2                   |

| 107009                  | Handle, Personality Module            |            | 1                   |

| 722007                  | Card Guide, 2-1/2"                    |            | 2                   |

| 722009                  | Card Guide, 4"                        |            | 10                  |

| REV A                   | I-10                                  |            |                     |

### SECTION I

Table 1-1. Sol-20 Kit Parts List. (Continued)

| PART NO.       | DESCRIPTION                      | ALTERNATES | MINIMUM<br>QUANTITY |

|----------------|----------------------------------|------------|---------------------|

|                | CHASSIS, COVERS and LABEL        | 5          |                     |

| 101003         | Chassis, Main                    |            | 1                   |

| 105019         | Subchassis, Power Supply         |            | 1                   |

| 101004         | Subchassis, Expansion            |            | 1                   |

| 101002         | Cover, Keyboard                  |            | 1                   |

| 101020         | Cover, Top                       |            | 1                   |

| 101015         | Cover, Logo, Plexiglass          |            | 1                   |

| 105020         | Plate, Fan Closure               | . :        | 1                   |

| 101007         | Assembly, Side Panel, Left       |            | l                   |

| 101008         | Assembly, Side Panel, Right      |            | 1                   |

| 101012         | Label, Serial Number             |            | 1                   |

| 101014*        | Label, Sol Logo*                 |            | 1*                  |

| 101032         | Label, Connector                 |            | 1                   |

| 101019         | Label, Fingerwell, Black         | ч.<br>1    | 2                   |

| *<br>May be pa | ackaged under logo cover.        |            |                     |

|                | HARDWARE                         |            |                     |

| 720074         | Machine Screw, 2-56 x 3/16       |            | 2                   |

| 720075         | Lockwasher, Internal Tooth, #2   |            | 2                   |

| 720002         | Machine Screw, 4-40 x 1/4        |            | 4                   |

| 720001         | Machine Screw, 4-40 x 3/16       |            | 4                   |

| 720003         | Machine Screw, 4-40 x 5/16       |            | 22                  |

| 720013         | Machina Saray $4-40 \times 7/16$ |            | 7                   |

| 720013 | Machine Screw, 4-40 x 7/16     | 7  |

|--------|--------------------------------|----|

| 720014 | Machine Screw, 4-40 x 5/8      | 9  |

| 720049 | Spacer, 4-40 x 1/4             | 2  |

| 720038 | Lockwasher, Internal Tooth, #4 | 36 |

| 720025 | Lockwasher, Spring, #4         | 8  |

| 720040 | Flat Washer, Nylon, #4         | 2  |

| 717051 | Lug, #4                        | 2  |

| 720010 | Hex Nut, 4-40                  | 32 |

|        |                                |    |

# Sol SYSTEMS AND COMPONENTS

### SECTION I

# Table 1-1. Sol-20 Kit Parts List. (Continued)

| PART NO. | DESCRIPTION AI                   | TERNATES | MINIMUM<br>QUANTITY           |

|----------|----------------------------------|----------|-------------------------------|

| 720020   | Machine Screw, Metal, 6-32 x 1/2 |          | 24                            |

| 720019   | Machine Screw, Nylon, 6-32 x 1/2 |          | 2                             |

| 720022   | Machine Screw, 6-32 x 3/4        |          | 1                             |

| 720023   | Sheetmetal Screw, #6 x 1/4       |          | 32                            |

| 720026   | Self-tapping Screw, #6 x 5/16    |          | 5                             |

| 720041   | Lockwasher, Internal Tooth, #6   |          | 30                            |

| 720067   | Flat Washer, #6                  |          | 18                            |

| 720011   | Hex Nut, 6-32                    |          | 19                            |

| 720032   | Machine Screw, 8-32 x 1/2        |          | 3                             |

| 720051   | Lockwasher, Internal Tooth, #8   |          | 3                             |

| 720012   | Hex Nut, 8-32                    |          | 3                             |

| 720036   | Machine Screw, 10-24 x 3/8       |          | 8                             |

| 720079   | Machine Screw, 10-24 x 1         |          | 2                             |

| 717053   | Lug, #10                         |          | 2                             |

| 720042   | Screw, Quick Connect, Knurled    |          | 2                             |

|          | MISCELLANEOUS                    |          |                               |

| 709004   | Crystal, 14.31818 MHz            |          | 1                             |

| 105033   | Fan Assembly                     |          | 1                             |

| 722003   | Finger Guard, Fan                |          | 1                             |

| 105028   | Transformer, Sol 20              |          | 1                             |

| 105034*  | Transformer, 220/240 V*          | 5        | 1*                            |

| 104000   | Keyboard Assembly, 85 Key        |          | · <b>1</b>                    |

| 723018   | Fuse, 3.2A, Slo-Blo              |          | 1                             |

| 105011   | Heatsink                         |          | · · · 1                       |

| 721004   | Heatsink                         |          | 1                             |

| 721006   | Heatsink                         |          | · · · <b>1</b>                |

| 721000   | Heatsink Compound                |          | 1                             |

| 713018   | Augat Pins                       |          | 15                            |

| 720060   | Clamp, 1-1/2                     |          | <sup>1</sup> · · · · <b>1</b> |

|          |                                  |          |                               |

\*Sol 20/220 and Sol 20/240 only.

| PART NO. | DESCRIPTION            | ALTERNATES | MINIMUM<br>QUANTITY |

|----------|------------------------|------------|---------------------|

| 720061   | Clamp, 2-1/2"          |            | 1                   |

| 720046   | Washer, Mica, TO-220   |            | 2                   |

| 720062   | Washer, Mica           |            | 1                   |

| 722011   | Tie, Cable             |            | 5                   |

| 716004   | Tubing, PVC            |            | 3"                  |

| 722017   | Foot, Rubber, Adhesive |            | 4                   |

| 716001   | Solder, 60/40, 20SWG   |            | 31'                 |

| 727000   | Basic 5 Package        |            | 1                   |

| 730000   | Manual, Sol Systems    |            | 1                   |

Table 1-1. Sol-20 Kit Parts List. (Continued)

•

Sol SYSTEMS AND COMPONENTS

SECTION I

Table 1-2. Sol Systems Parts List.

| PART NO.  | DESCRIPTION              | QUANTITY |

|-----------|--------------------------|----------|

|           | <u>Sol-20/8</u>          |          |

| 101000-02 | Sol-20 Terminal Computer | 1        |

| 202000-01 | 8KRA Memory Module       | . 1      |

| 723018    | Fuse, 3.2A Slo-Blo       | . 2      |

| -         | Cap, Fuse Holder         | 1        |

| 718001    | Cord, AC Power, 3-Wire   | 1        |

| 727000    | Basic 5 Package          | 1        |

| 730000    | Manual, Sol Systems      | 1        |

| 730002    | Manual, 8KRA             | 1        |

|           |                          |          |

|           | <u>Sol-20/16</u>         |          |

| 101000-02 | Sol-20 Terminal Computer | 1        |

| 203000-01 | 16KRA Memory Module      | 1        |

| 723018    | Fuse, 3.2A Slo-Blo       | 2        |

| -         | Cap, Fuse Holder         | 1        |

|        | oup, rube norder       |   |

|--------|------------------------|---|

| 718001 | Cord, AC Power, 3-Wire | 1 |

| 727000 | Basic 5 Package        | 1 |

| 730000 | Manual, Sol Systems    | 1 |

| 730003 | Manual, 16KRA          | 1 |

|        |                        |   |

# Sol System I

| 400400-01           | Sol-20/8 Terminal Computer   | 1 |

|---------------------|------------------------------|---|

| 722016              | TV Monitor                   | 1 |

| 722019              | Cassette Recorder            | 1 |

| 718005 or<br>101034 | Video Cable Assembly         | 1 |

| 718006 or<br>101041 | Audio Cable Assembly         | 1 |

| 718007 or<br>101042 | Motor Control Cable Assembly | 1 |

# Sol SYSTEMS AND COMPONENTS

# SECTION I

Table 1-2. Sol Systems Parts List. (Continued)

| PART NO.            | DESCRIPTION                                                         | QUANTITY |

|---------------------|---------------------------------------------------------------------|----------|

|                     | Sol System II                                                       |          |

| 400500-01           | Sol-20/16 Terminal Computer                                         | 1        |

| 722016              | TV Monitor                                                          | 1        |

| 722019              | Cassette Recorder                                                   | 1        |

| 718005 or<br>101034 | Video Cable Assembly                                                | l        |

| 718006 or<br>101041 | Audio Cable Assembly                                                | 1        |

| 718007 or<br>101042 | Motor Control Cable Assembly                                        | 1        |

|                     | Sol System III                                                      |          |

| 400500-01           | Sol-20/16 Terminal Computer                                         | 1        |

| 203100              | 32KRA Memory Module (or two 16KRA<br>Memory Modules, P/N 203000-01) | l        |

| 300000-01           | Helios II                                                           | 1        |

| 722016              | TV Monitor                                                          | l        |

| 718005 or<br>101034 | Video Cable Assembly                                                | l        |

| 727036              | Extended Disk Basic Package                                         | 1        |

| 730009              | Manual, Helios II                                                   | 1        |

### Sol SYSTEMS AND COMPONENTS

SECTION I

Before applying power to your factory assembled Sol unit, use the following procedure to internally inspect the unit, and if required, install the memory module:

### CAUTION

DO NOT TOUCH ANY OF THE SOL-PC COMPONENTS, OR SOL-20 INTERNAL COMPONENTS, UNTIL IN-STRUCTED TO DO SO IN THE FOLLOWING PRO-CEDURE.

- 1. On the Sol-20, remove the two knurled quick connect screws (located on back of Sol) that hold the top cover in place.

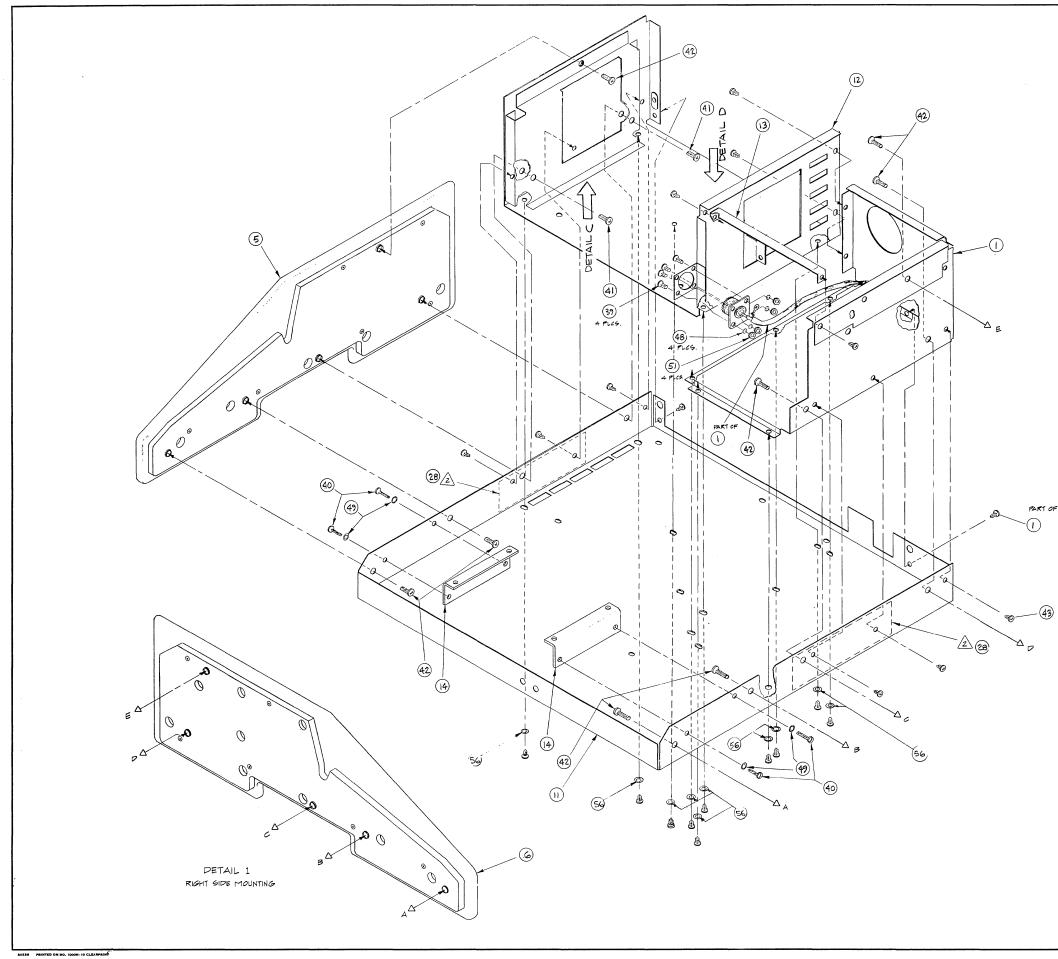

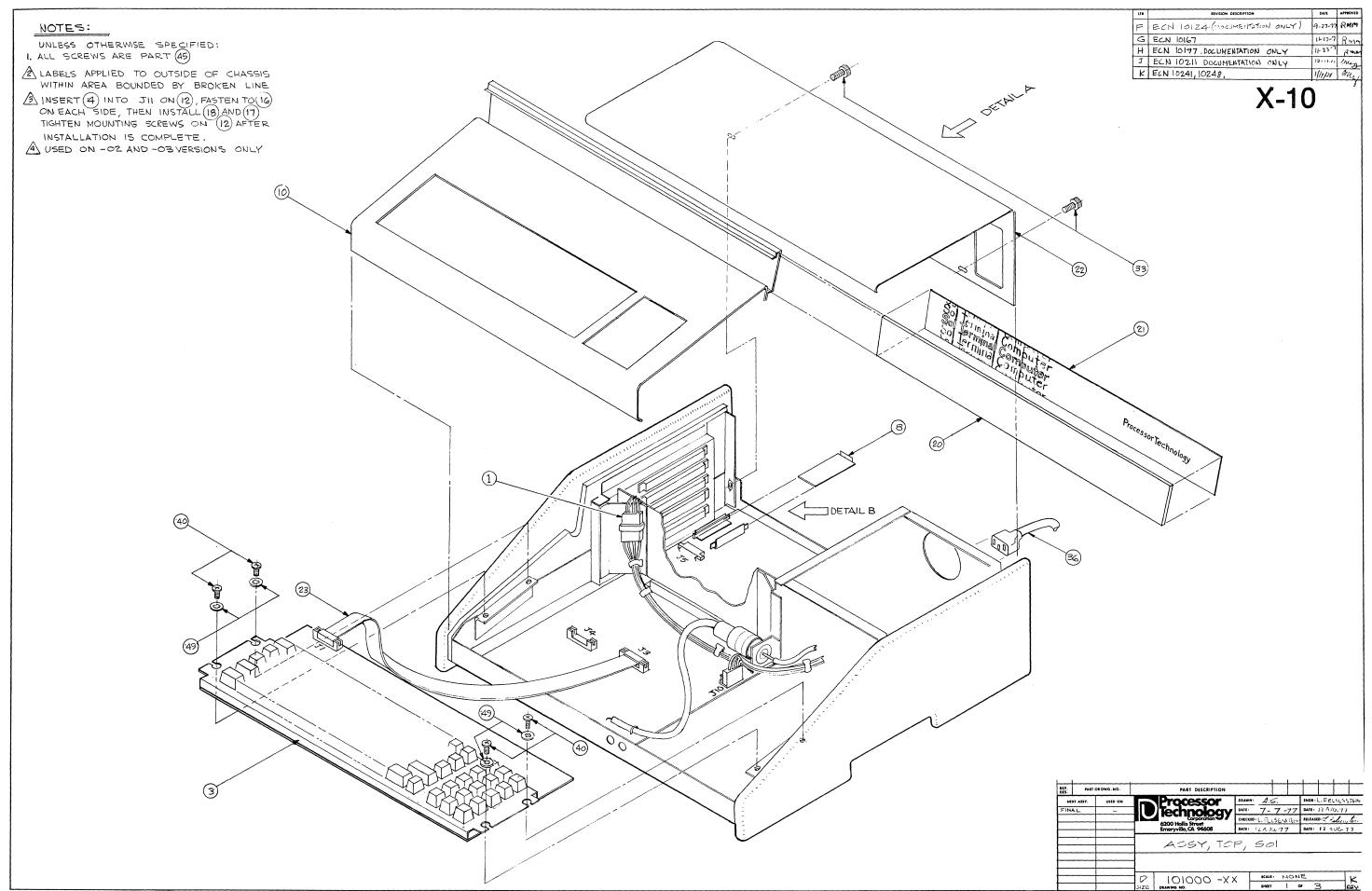

- On the Sol-20, refer to Drawing X-10 in Section X and carefully swing the top cover up, unhook it from the back edge of the keyboard cover, and set it to one side.

- 3. On the Sol-20, carefully swing keyboard cover up, unhook it from the front edge of the main chassis, and set it to one side.

- 4. On the Sol-20, touch the chassis to discharge any static electricity. (On the Sol-PC this may be accomplished by touching the ground trace along the edge of the board.) Visually inspect all IC's, the personality module and cable connectors to see if they are firmly seated. Secure any loose cable connectors and push gently down on any loose IC's until they are fully seated in their socket. If the personality module is loose, push on its handle (see Drawing X-7 in Section X) to seat the module firmly in its socket.

- 5. On the Sol-20, install the memory module(s) in the expansion chassis (located in left rear corner of Sol as viewed from the front). You may install the module(s) in any of the five card slots. With the component side up, insert edge connector side of module in card guides and carefully slide the module in until the edge connector is fully seated in the backplane (the vertical circuit board on the front side of the expansion chassis) connector.

- 6. For the Sol-20, reassemble it by hooking the keyboard cover under the front edge of the main chassis and lowering it over the keyboard, hooking the top cover over the back edge of the keyboard cover and lowering it down into place over the rear of the unit, and installing the two knurled quick connect screws.

- 7. Insert a fuse in the fuse cap, push the assembly into the fuse post (see Figure 7-1 in Section VII), and turn cap one-guarter turn clockwise.

### Sol SYSTEMS AND COMPONENTS

With AC power cord not plugged into a 110 V ac outlet, connect power cord to AC connector on Sol rear panel (see Figure 7-1).

If you have a Sol-PC, it is now ready to use with a keyboard and TV monitor. If you have a Sol-20, you are now ready to simultaneously test the Sol functions and get acquainted with its operation. Information in Section VII ("Sol Operating Procedures") and IX ("Software") will guide you.

Should you have any problem getting Sol to respond as described in Sections VII and IX, make sure that you faithfully followed all of the instructions. If that does not remedy the situation, feel free to seek help from us or your Sol dealer.

### 1.4 SECTION X DRAWINGS

This overview of the drawings section in this manual (Section X) is intended to help you better utilize the drawings supplied therein.

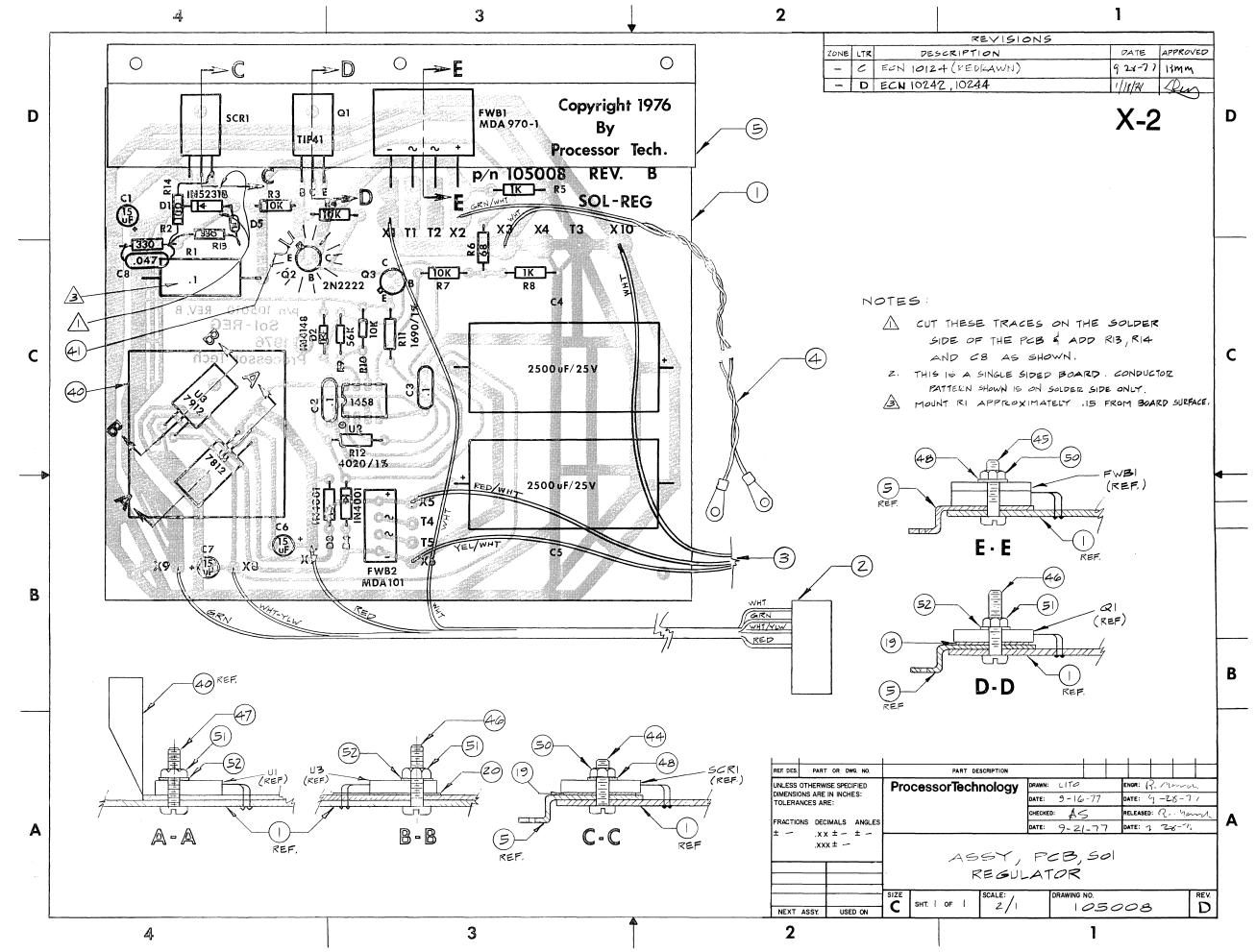

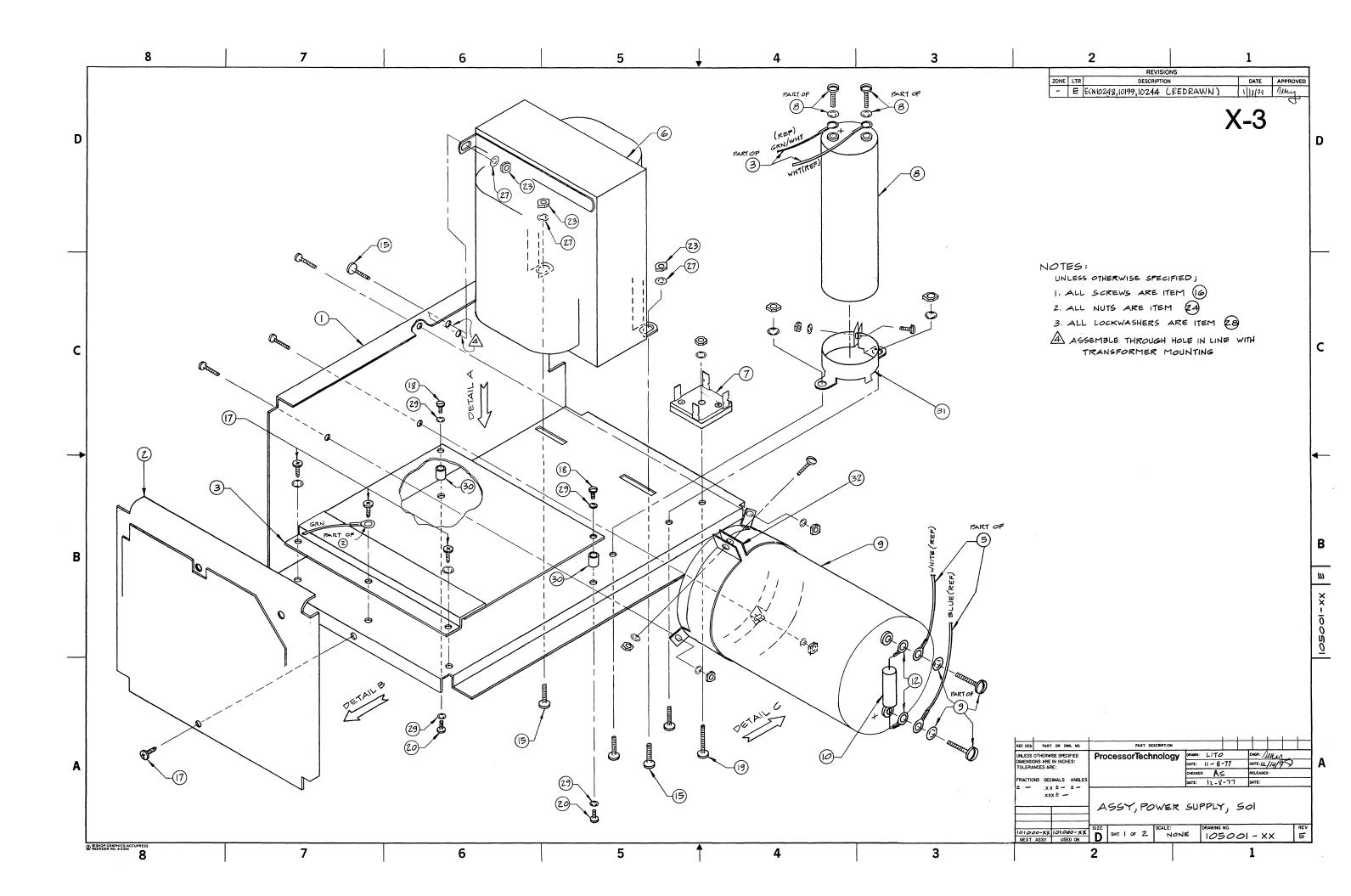

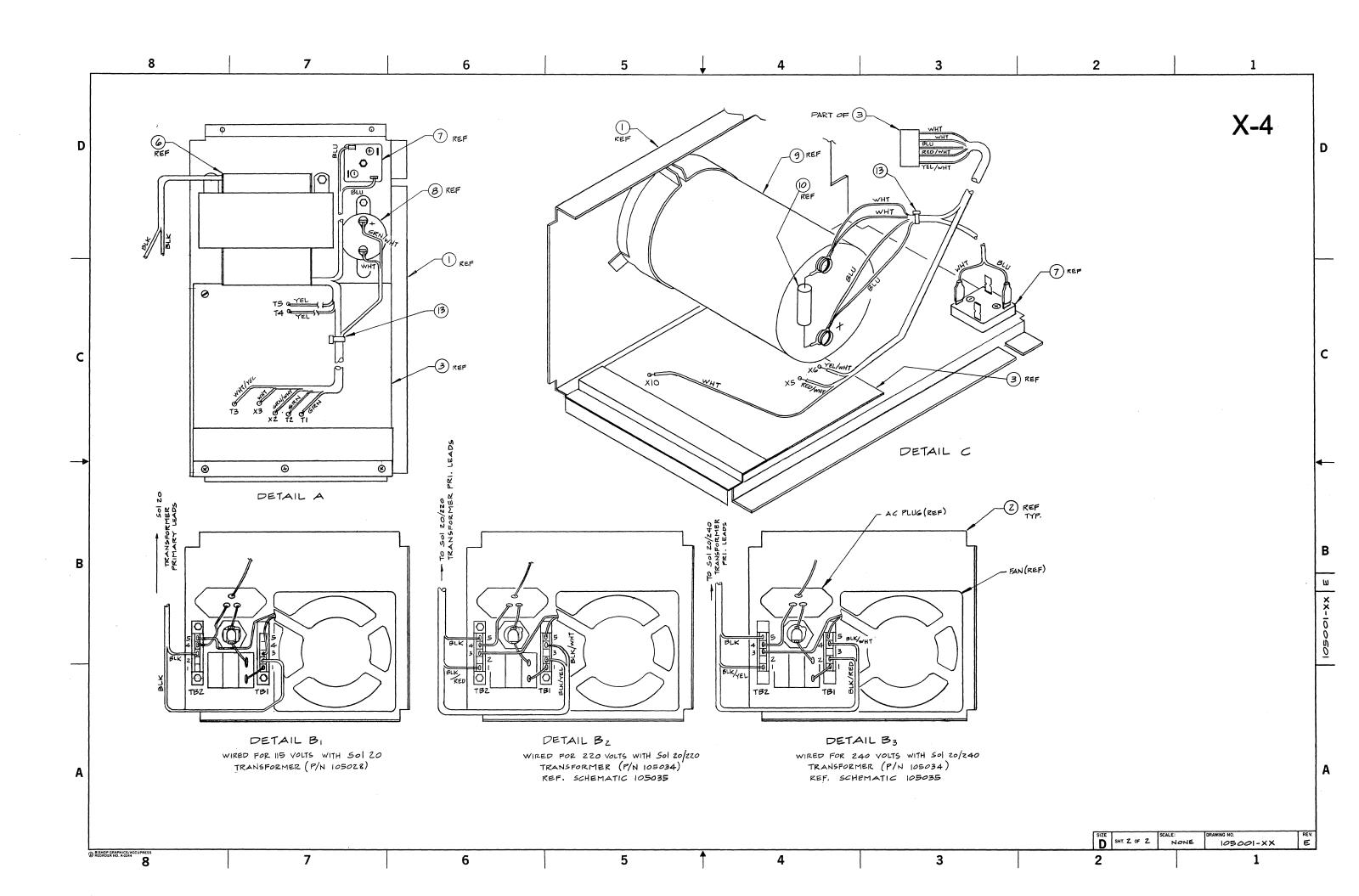

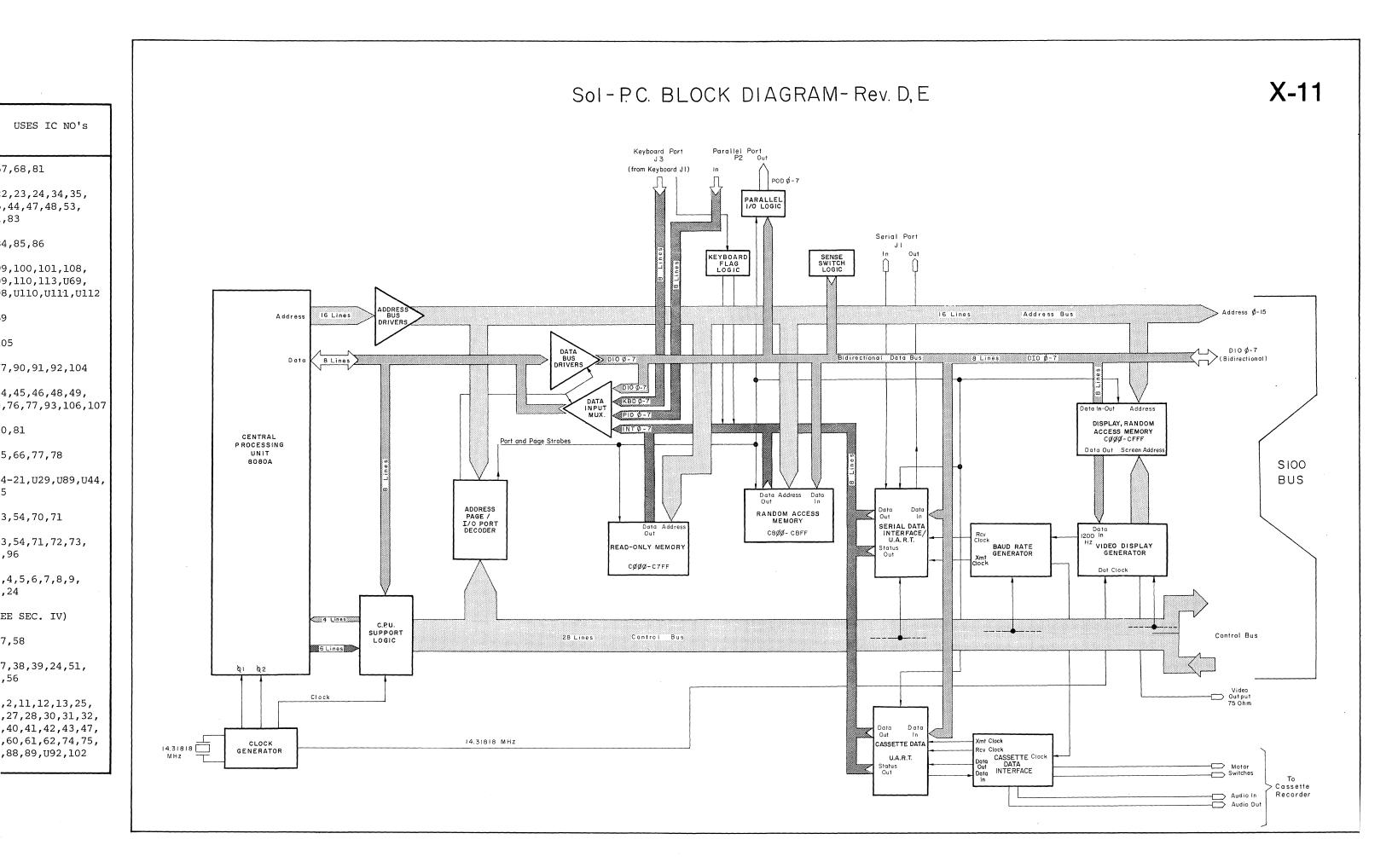

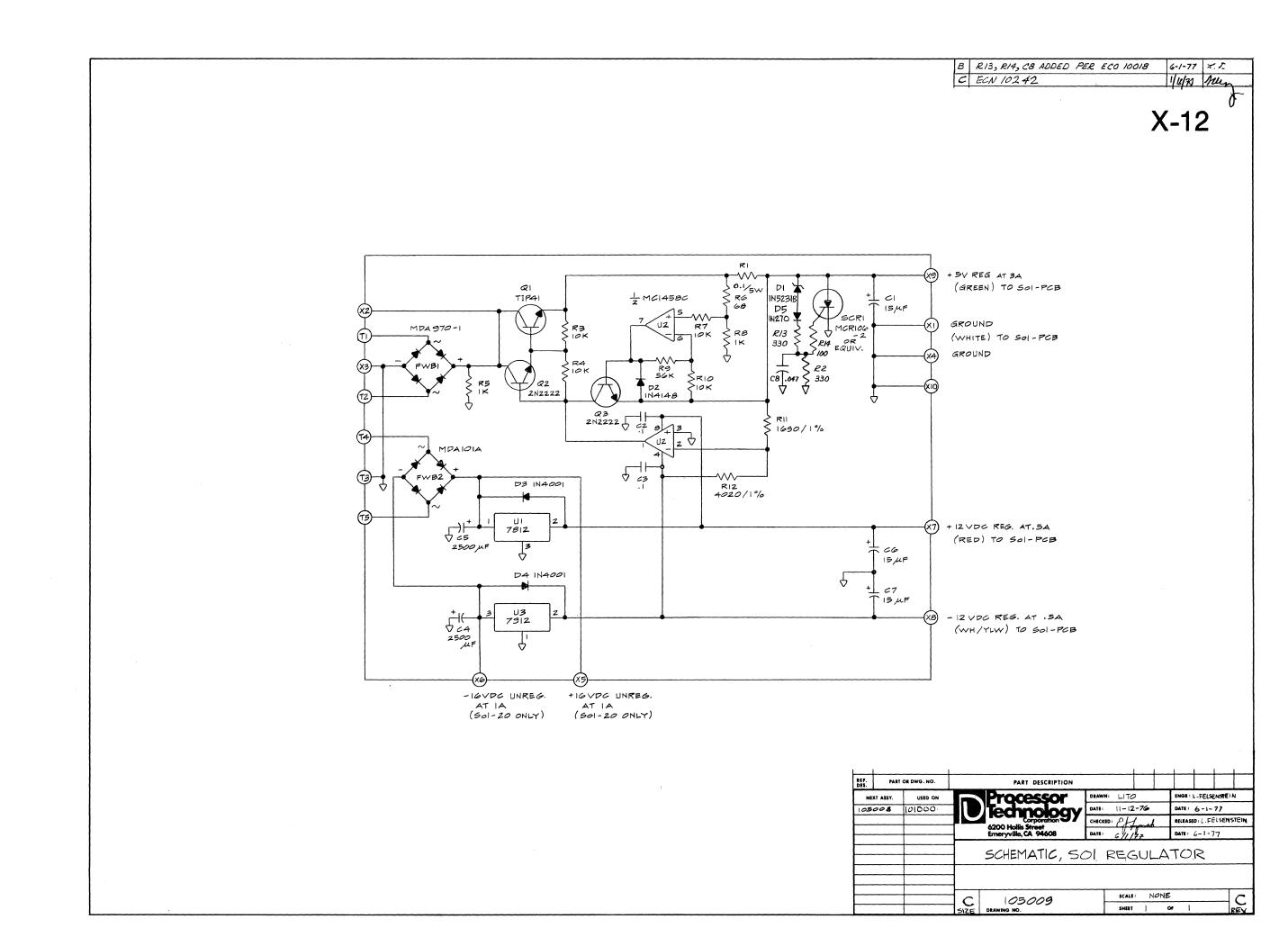

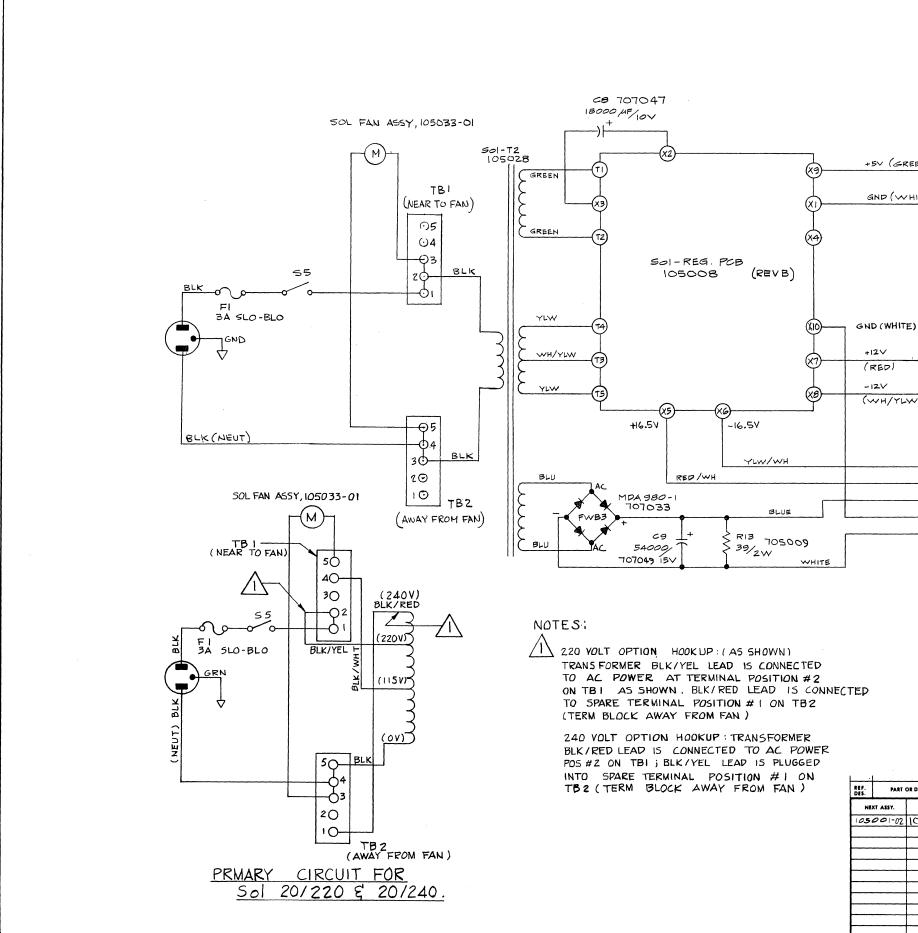

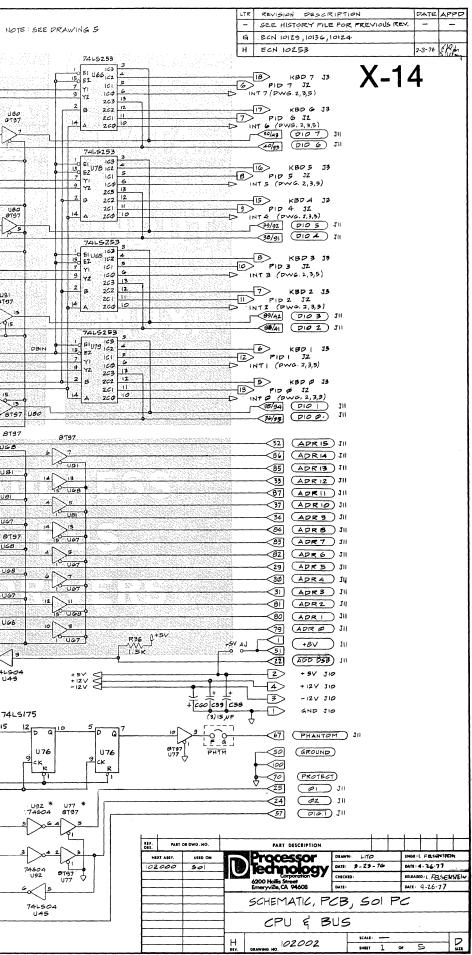

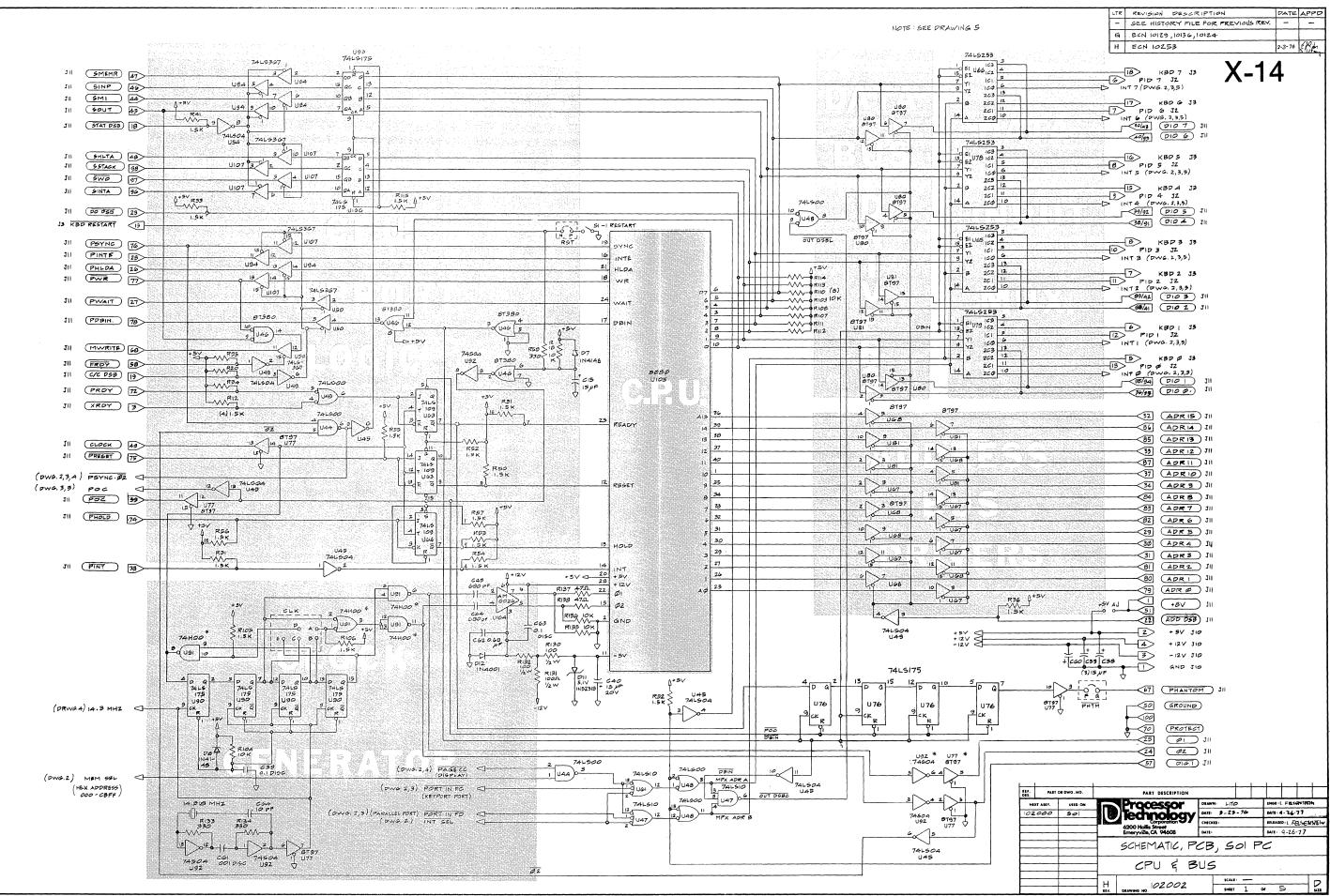

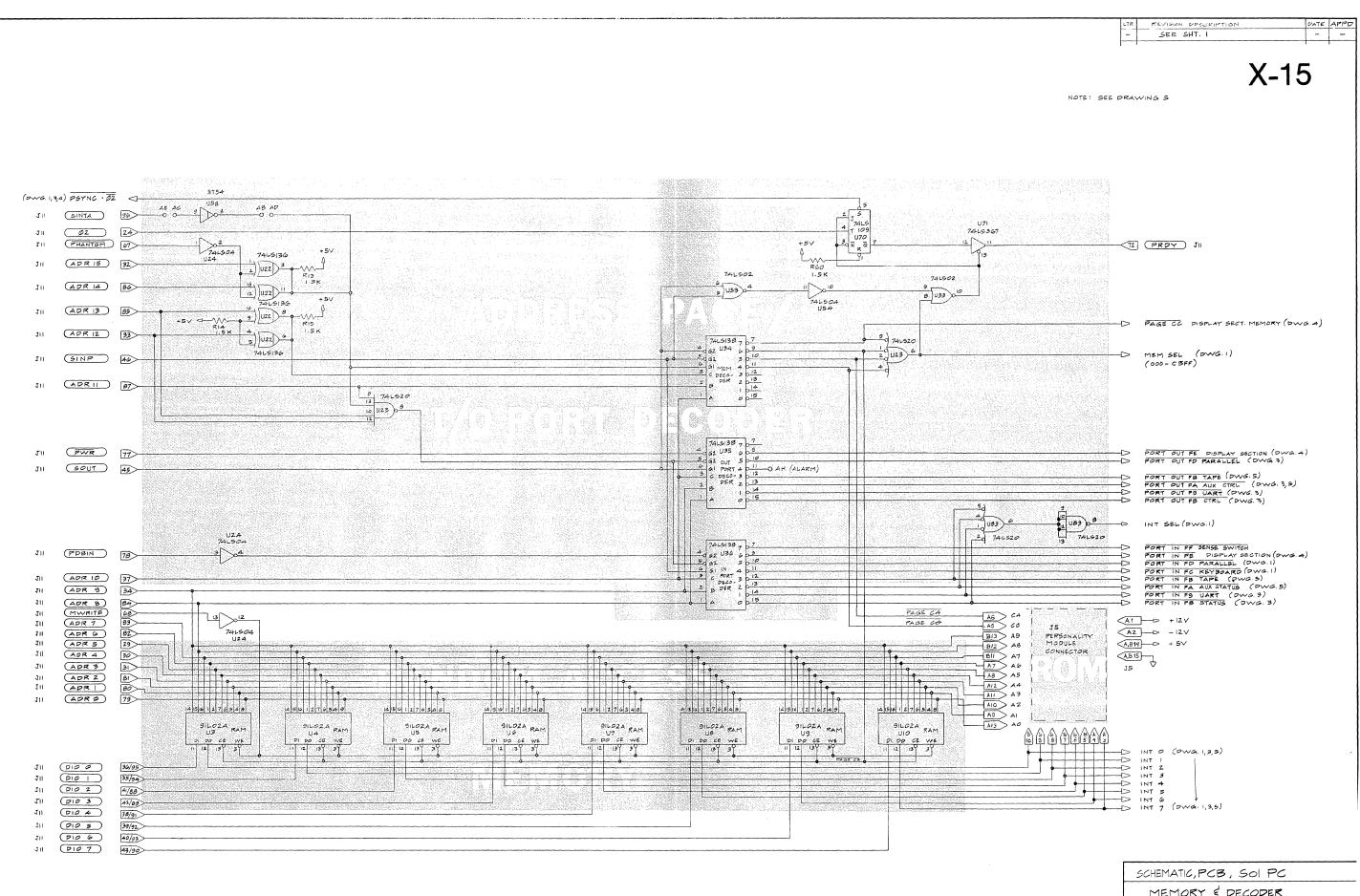

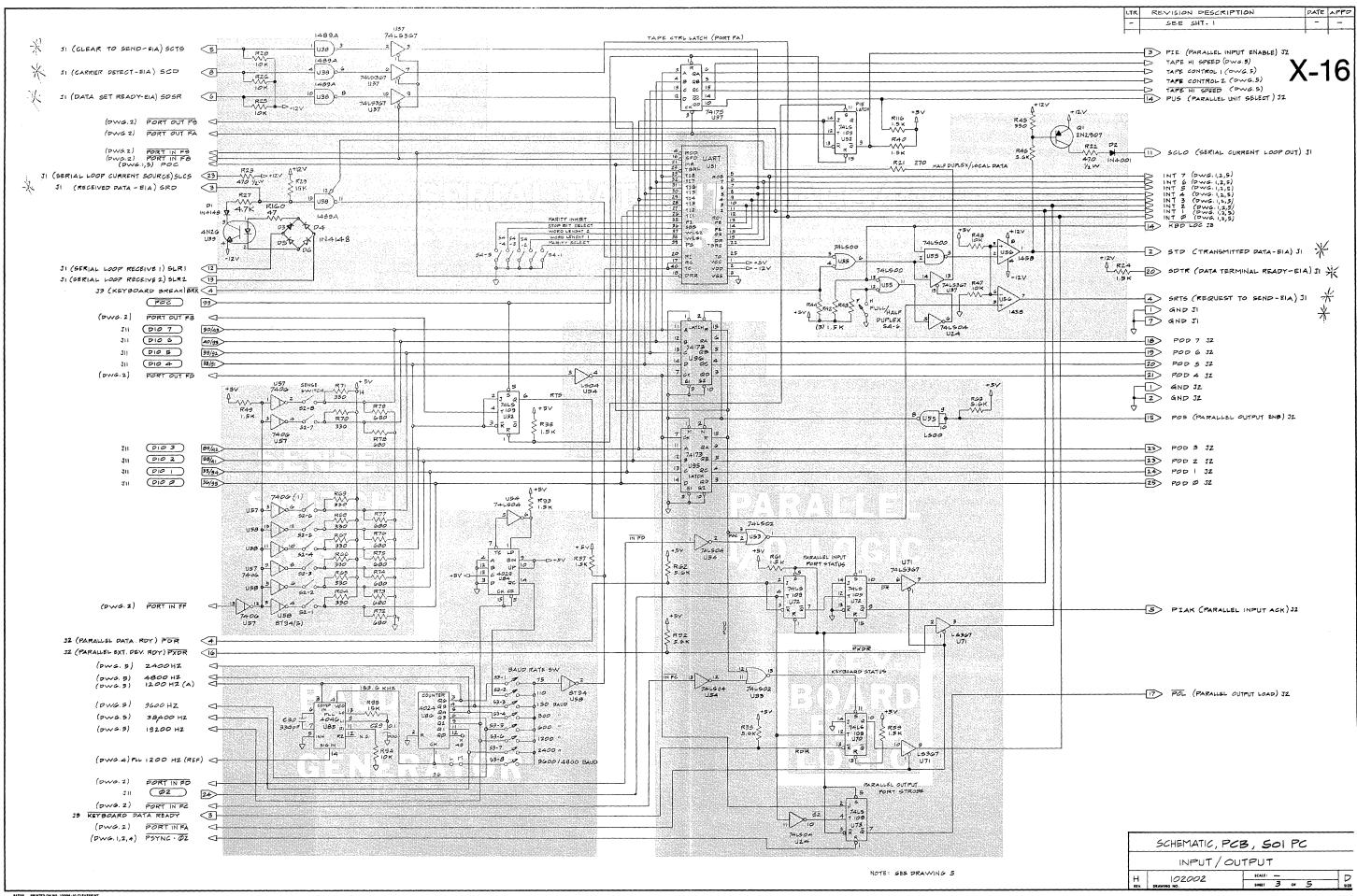

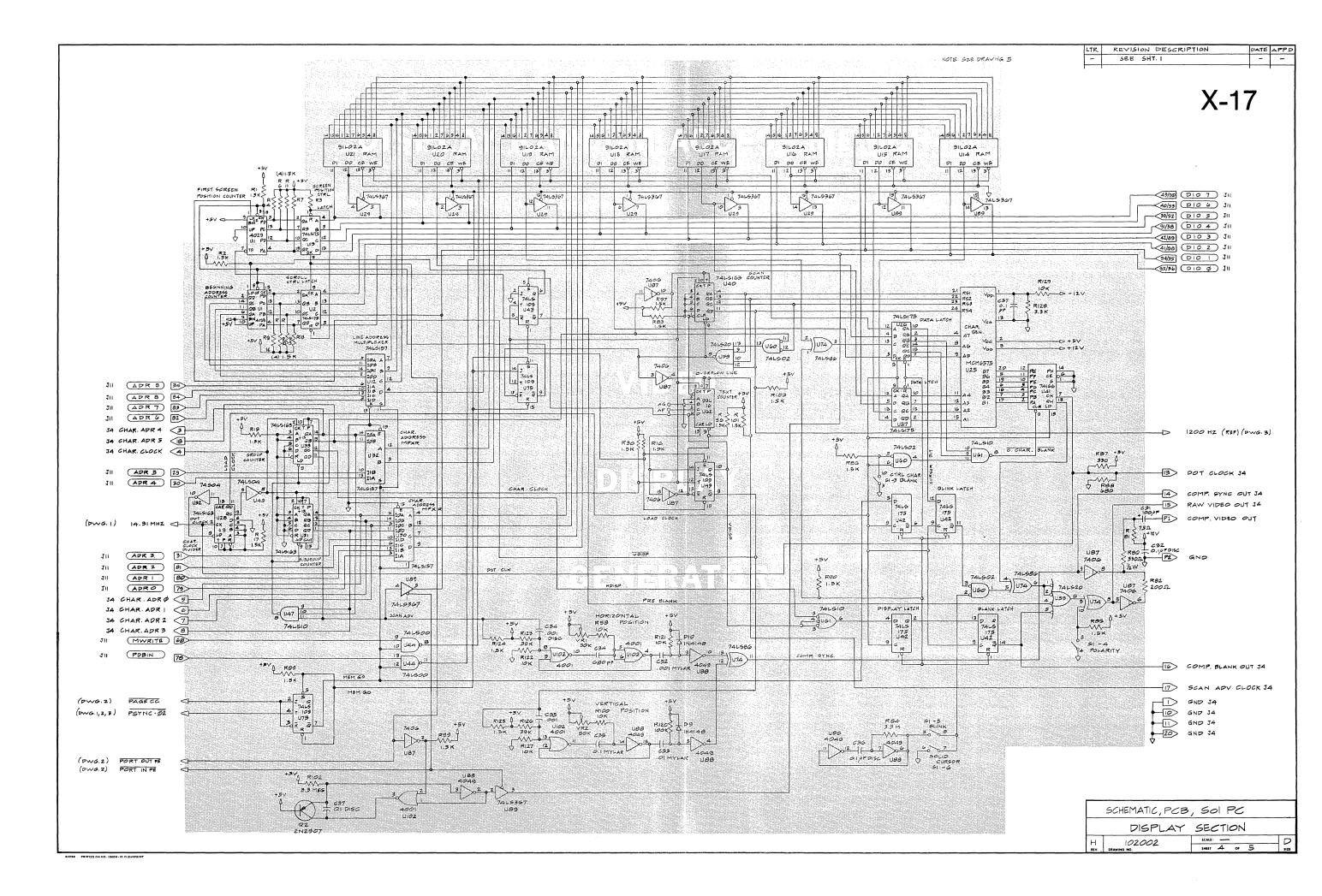

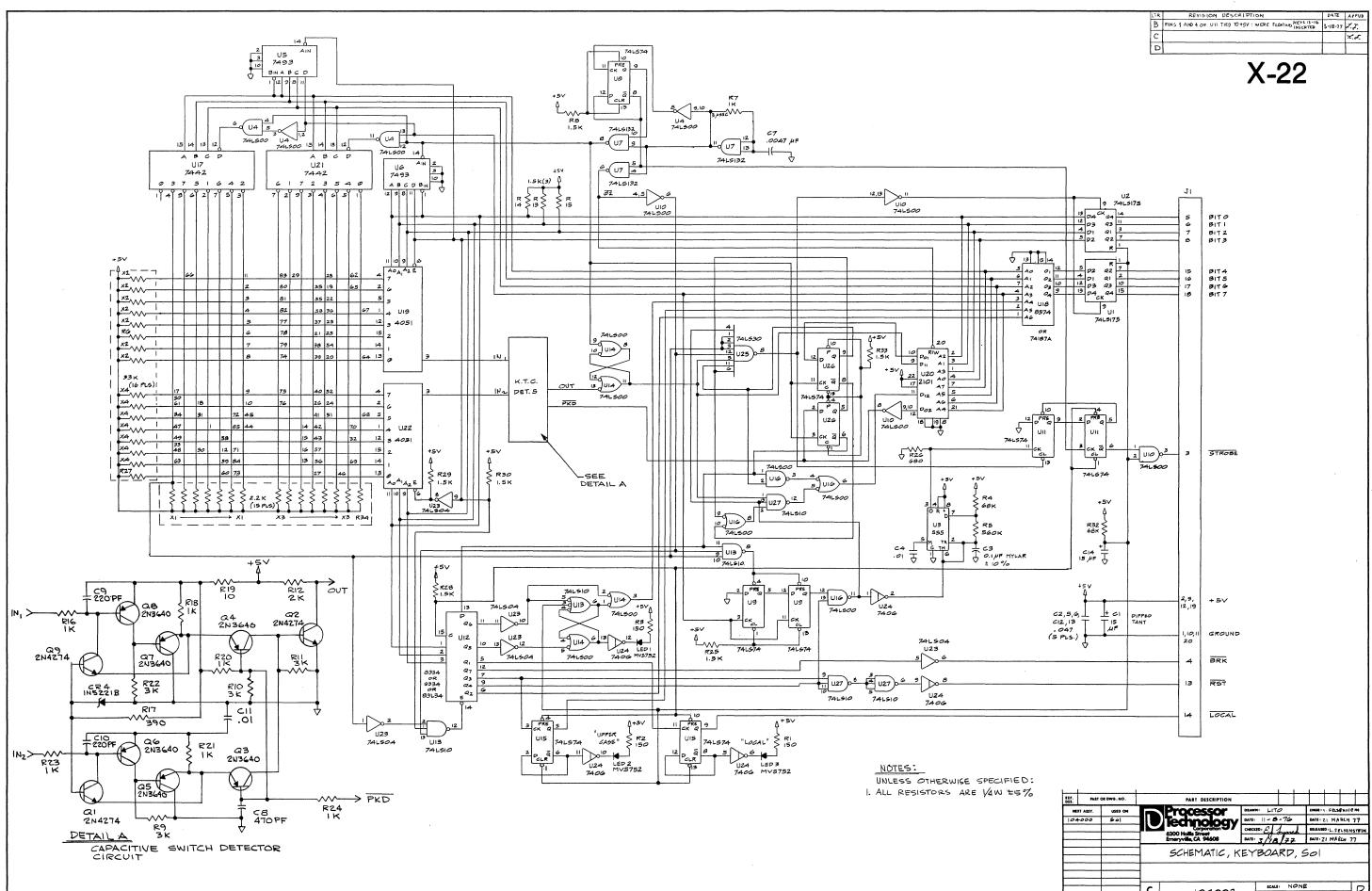

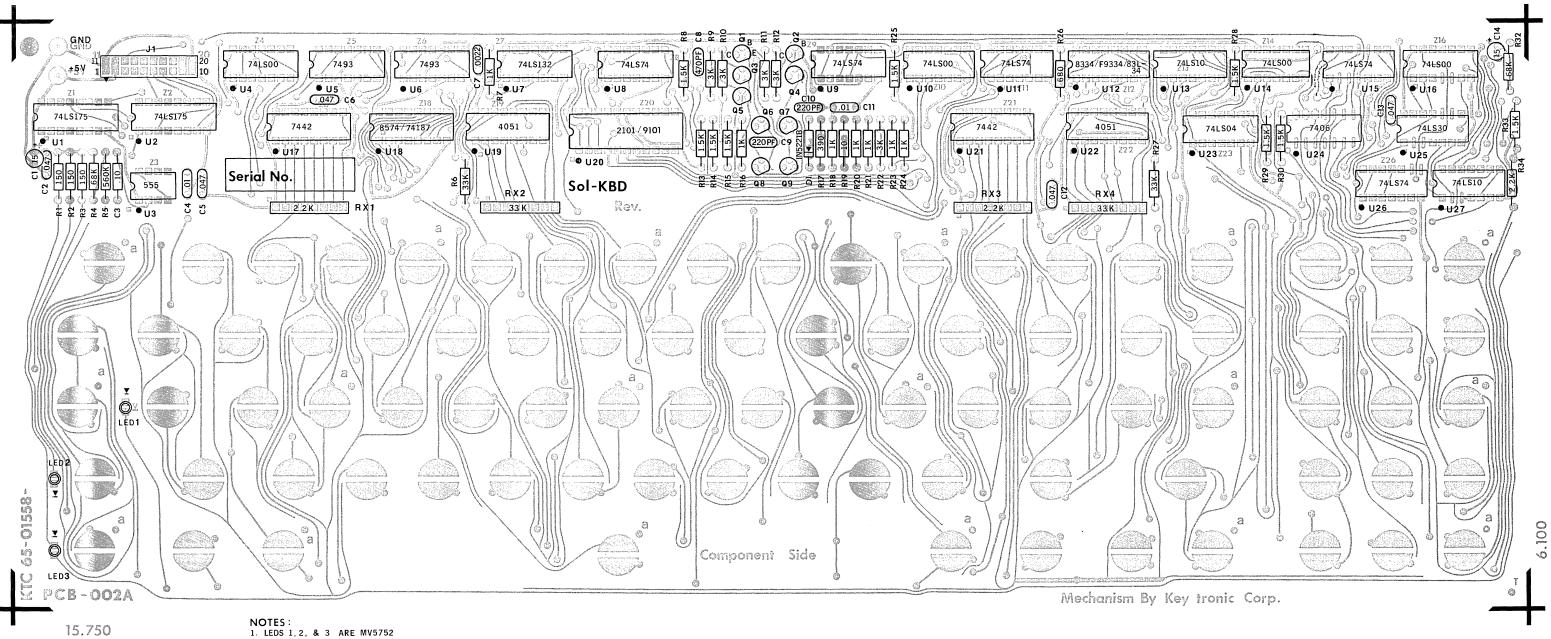

The first 10 drawings (X-1 through X-10) are assembly drawings which the kit builder will use to assemble his kit. They also provide information that will be useful when servicing the Sol-PC or Sol-20. Drawing X-11 is a functional block diagram of the Sol-PC, the primary "home" for the Sol electronics. This diagram includes a table that relates the functional blocks with the applicable schematic(s) and the IC's used. Drawings X-12 and 13 are schematics of the Sol Regulator and Power Supply, respectively.

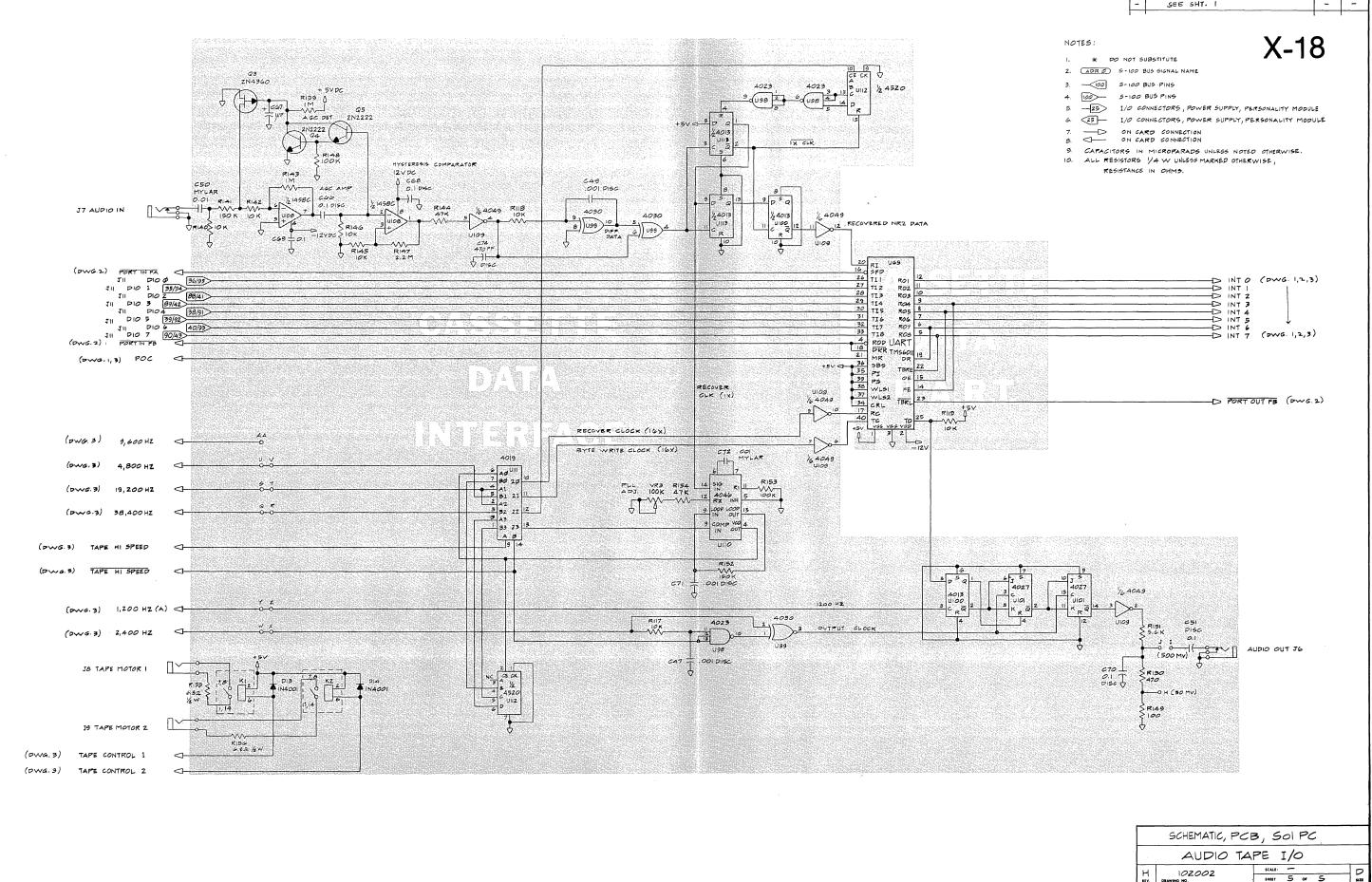

The Sol-PC schematic is separated by functional sections into five separate schematic drawings (X-14 through X-18). Notes that apply to all five schematics are provided on Drawing X-18. To assist you in relating the schematics to the block diagram, each schematic incorporates grey, identified blocks for each functional block on Drawing X-11.

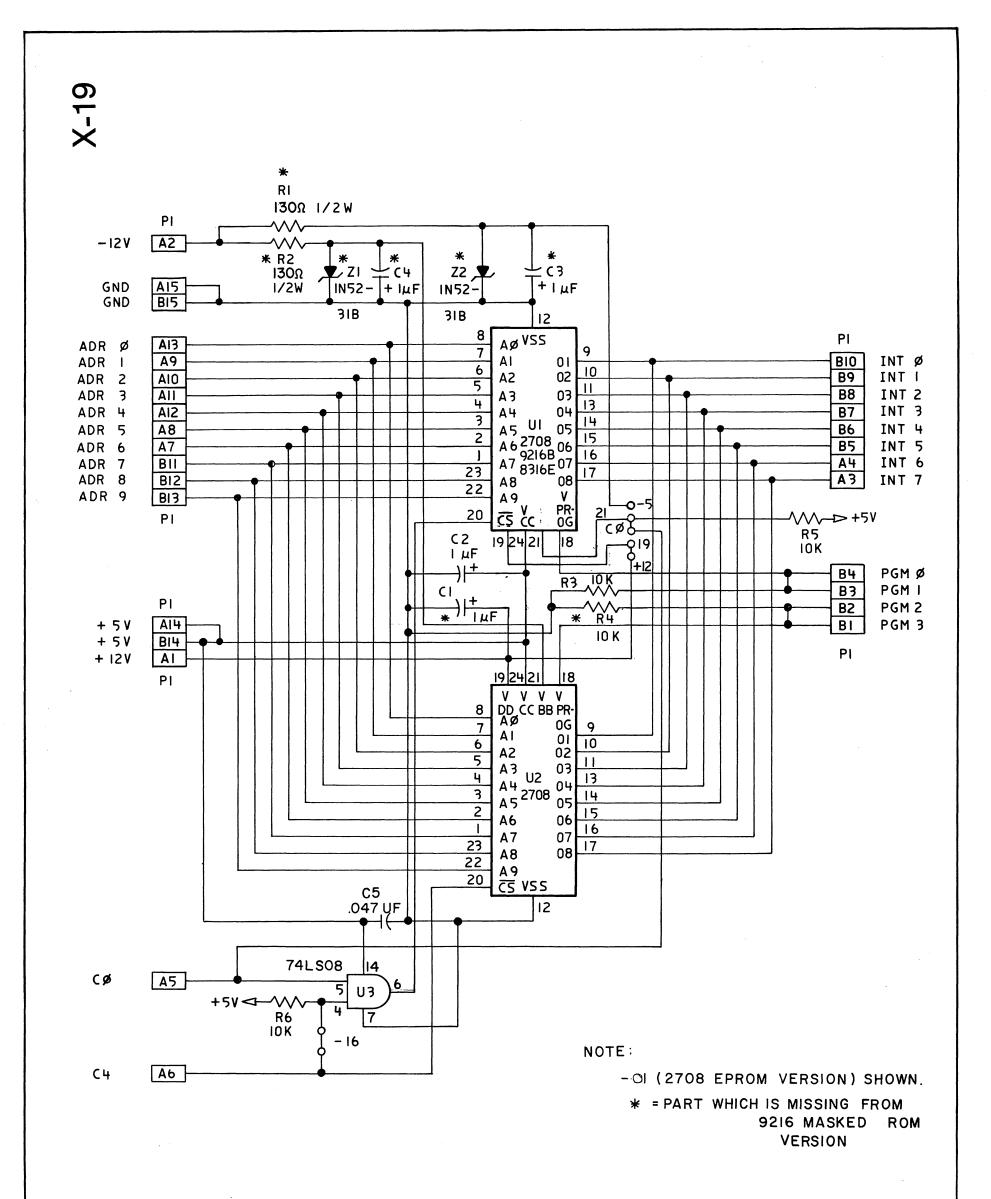

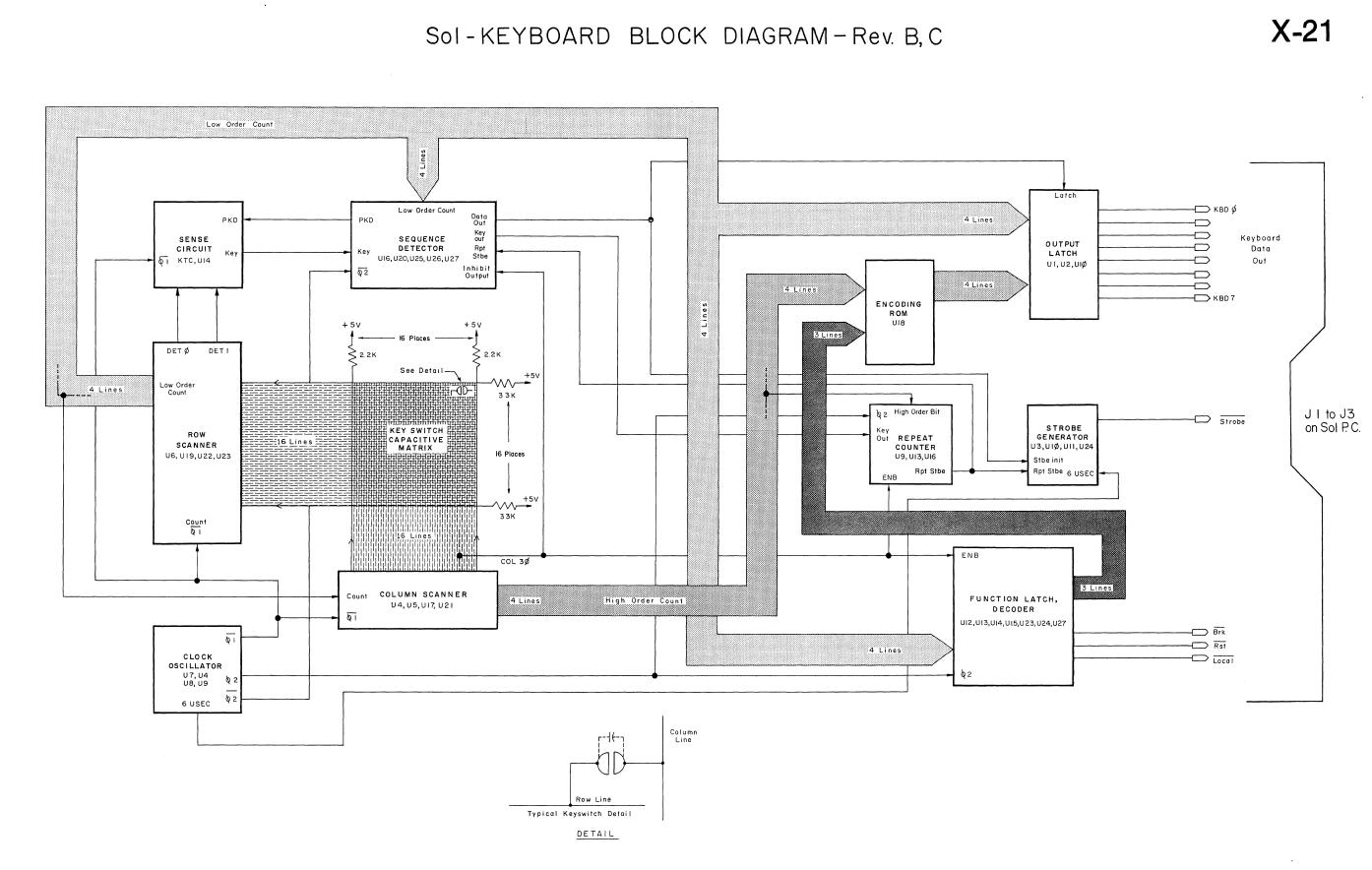

Drawing X-19 is the schematic for the 2708/9216 Personality Module, and the remaining drawings (X-20 through X-23) pertain to the Keyboard Assembly.

### 1.5 SOL KIT ASSEMBLY ORDER

If you are building a Sol-PC, either start assembly with Section III (Sol-PC) or IV (Personality Module). The assembly of these two parts is inter-related, so you may begin with either one.

The recommended assembly order for the Sol-20 is to first build the power supply. You then have the option of starting to build the Personality Module (Section IV) or the Sol-PC (Section III) since the assembly of these two parts is inter-related. Having

# Sol SYSTEMS AND COMPONENTS

SECTION J

completed the power supply, Sol-PC and Personality Module, it is time to assemble the chassis-cabinet (Section VI) which includes building the expansion backplane board. Once your Sol is finished, you are ready to put it through some simple operations and functional tests as described in Section VII.

| 2.1 | Introduction II-                                                                                             | 1  |

|-----|--------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Parts and Components                                                                                         | 1  |

| 2.3 | Assembly Tips                                                                                                | 5  |

|     | 2.3.1 Electrical                                                                                             |    |

| 2.4 | Assembly Precautions II-                                                                                     | 6  |

| 2.5 | Required Tools, Equipment and Materials II-                                                                  | 6  |

| 2.6 | Orientation                                                                                                  | 6  |

|     | 2.6.1Sol-REG PC Board.II-2.6.2Fan Closure PlateII-                                                           |    |

| 2.7 | Assembly-Test                                                                                                | 7  |

|     | 2.7.1 Fan Closure Plate Assembly II-<br>2.7.2 Sol-REG Assembly and Test II-<br>2.7.3 Power Supply Subchassis |    |

|     | Assembly and Test II-                                                                                        | 14 |

# II SOl POWER SUPPLY ASSEMBLY and TEST

Sol POWER SUPPLY

# 2.1 INTRODUCTION

The Sol power supply consists of a regulator board plus additional chassis-mounted components. This section covers assembly and test of the complete power supply.

#### 2.2 PARTS AND COMPONENTS

You will need the parts listed in Table 2-1 to assemble your Sol power supply. Select and separate the needed parts from those supplied with your Sol kit before starting assembly. If you have any difficulty in identifying any parts by sight, refer to Figure 3-1 in Section III, Figure 6-1 in Section VI and the "Standard Color Code for Resistors and Capacitors" chart in Appendix III. The assembly drawings in Section X will also be useful in identifying parts.

To guide you in selecting and identifying parts, Table 2-1 lists each part, its description, quantity and reference designation on the drawing(s) you will use in assembling the power supply. You will encounter two types of reference designators in Table 2-1 (and parts lists in Section III, IV and VI as well): alphanumeric and encircled numeric designators.

Alphanumeric designators (Cl, R5, U3, D4, etc.) are used to identify electronic components such as capacitors, resistors, integrated circuits and diodes. Encircled designators ((1), (6), (9), etc. are used to identify the other parts used in the Sol (chassis, cables, screws, washers, covers, heat sinks, etc.). Two examples of how to use the information in Table 2-1 follow:

- 1. Alphanumeric Designators. The first integrated circuit (IC) entry in Table 2-1 indicates its reference designator is U2 and that U2 will be installed using Drawing X-2 in Section X. In looking at Drawing X-2, we can see that U2 (a 1458) is an 8-pin dual inline package (DIP) IC that will be installed in the near center of the Sol-REG board.

- 2. Encircled Numeric Designators. The next to last entry in Table 2-1, a #10 lug, has a reference designator 12 and indicates that the two lugs will be installed using Drawing X-3 in Section X. In looking at Drawing X-3, we can see what these lugs look like and determine that they will be installed on resistor leads.

# Sol POWER SUPPLY

# SECTION II

# Table 2-1. Sol Power Supply Parts List.

|               |                                |          | RE      | FERENCE                               |

|---------------|--------------------------------|----------|---------|---------------------------------------|

|               |                                |          | Drawing | · · · · · · · · · · · · · · · · · · · |

| PART          | DESCRIPTION                    | QUANTITY | No.     | Designator                            |

| Circuit Board | Sol-REG                        | 1        | X-2     | l                                     |

| IC            | 1458 or 72558                  | 1        | x-2     | U2                                    |

| IC            | 7812                           | 1        | X-2     | Ul                                    |

| IC            | 7912                           | 1        | x-2     | U3                                    |

| Transistor    | TIP41                          | 1        | X-2     | Ql                                    |

| Transistor    | 2N2222                         | 2        | X-2     | Q2&3                                  |

| Diode         | ln270                          | 1        | X-2     | D5                                    |

| Diode         | ln4001                         | 2        | X-2     | D3&4                                  |

| Diode         | 1N4148 or 1N914                | 1        | X-2     | D2                                    |

| Diode         | ln5231                         | 1        | X-2     | Dl                                    |

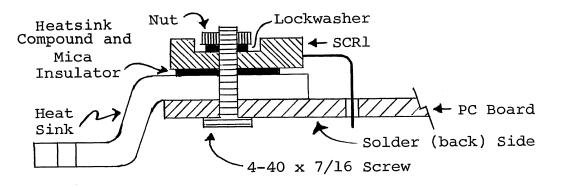

| SCR           | 106-2 or 10632                 | 1        | X-2     | SCR1                                  |

| Bridge Rect.  | 101                            | 1        | X-2     | FWB2                                  |

| Bridge Rect.  | 970-1                          | 1        | X-2     | FWB1                                  |

| Bridge Rect.  | 980-1                          | 1        | X-3     | FWB3                                  |

| Resistor      | 0.1 ohm, Wire Wound, 5W        | 1        | X-2     | Rl                                    |

| Resistor      | 39 ohm, 2W, 5%                 | 1        | X-3     | 10                                    |

| Resistor      | 68 ohm, 1/4W, 5%               | 1        | X-2     | R6                                    |

| Resistor      | 100 ohm, 1/4W, 5%              | 1        | x-2     | R14                                   |

| Resistor      | 330 ohm, 1/4W, 5%              | 2        | X-2     | R2&13                                 |

| Resistor      | 1K ohm, 1/4W, 5%               | 2        | X-2     | R5&8                                  |

| Resistor      | 1690 ohm, 1/4W, 1%             | l        | X-2     | Rll                                   |

| Resistor      | 4020 ohm, 1/4W, 1%             | 1        | X-2     | R12                                   |

| Resistor      | 10K ohm, 1/4W, 5%              | 4        | X-2     | R3,4,7&10                             |

| Resistor      | 56K ohm, 1/4W, 5%              | 1        | X-2     | R9                                    |

| Capacitor     | .047 µf, Disc Ceramic          | 1        | X-2     | C8                                    |

| Capacitor     | .1 $\mu$ f, Disc Ceramic       | 2        | X-2     | C2&3                                  |

| Capacitor     | 15 μf, Tantalum, 20V           | 3        | X-2     | C1,6&7                                |

| Capacitor     | 2500 μ <b>f, Aluminum,</b> 25V | 2        | X-2     | C4&5                                  |

| Capacitor     | 18,000 µf, Aluminum, 10V       | 1        | X-3     | 8                                     |

| Capacitor     | 54,000 μf, Aluminum, 15V       | 1        | X-3     | 9                                     |

# Sol POWER SUPPLY

# SECTION II

# Table 2-1. Sol Power Supply Parts List (Continued)

|              |                                                |          | REF            | ERENCE     |

|--------------|------------------------------------------------|----------|----------------|------------|

| PART         | DESCRIPTION                                    | QUANTITY | Drawing<br>No. | Designator |

| Transformer  | Power, Sol T-2                                 | 1        | <b>X-3</b>     | 6          |

| Transformer* | Power, Sol 220/240*                            | 1*       | X-3            | 6          |

| Fan Assembly | Rotron 428056 or<br>Peewee Boxer PWS2107FL-2-M | 1        | X <b>-</b> 5   | 5          |

| Connector    | AC Power Receptacle                            | 1        | x-1            | 3          |

| Socket       | Coax, 75 ohm                                   | 2        | X-1            | 55         |

| Holder       | Fuse                                           | 1        | X-1            | 9          |

| Switch       | AC Power, Alternate Action                     | 1        | X-1            | 4          |

| Block        | Commoning, 5 Position                          | 2        | X-1            | 10         |

| Fuse         | 3.2A, Slo-Blo                                  | 1        | -              | -          |

| Heat Sink    | Bar, For SCR1, Q1 & FWB1                       | 1        | X-2            | 5          |

| Heat Sink    | Rectangular, For Ul & U3                       | l        | X-2            | 40         |

| Heat Sink    | Circular, For Q2                               | 1        | X-2            | 41         |

| Cable        | Coaxial, 75 ohm                                | 15"      | X-1            | 2          |

| Cable        | C8 Cable Assembly, 2-Wire                      | l        | X-2            | 4          |

| Cable        | Sol-PC Power, 4-Wire                           | 1        | X-2            | 2          |

| Cable        | Sol 20 DC Power, 5-Wire                        | 1        | X-4            | 5          |

| Cord         | AC Power, 3-Wire                               | 1        | X-10           | 36         |

| Lead         | Fuse Lead to AC Switch, 3"                     | 1        | X-1            | 7          |

| Lead         | Neutral Lead, AC Switch, 3-1/4"                | 1        | X-1            | 8          |

| Guard        | Finger                                         | 1        | X-1            | 6          |

| Cable Tie    | Plastic                                        | 4        | X-4            | 13         |

| Clamp        | C-8, 1-1/2"                                    | 1        | X-3            | 31         |

| Clamp        | C-9, 2-1/2"                                    | 1        | X-3            | 32         |

| Insulator    | Mica Washer                                    | 1        | X-2            | 20         |

| Insulator    | Mica Washer, TO-220                            | 2        | X-2            | 19         |

| Plate        | Fan Closure                                    | 1        | X-1            | l          |

| Subchassis   | Power Supply                                   | 1        | <b>X-</b> 3    | 1          |

\*Supplied only with 220 and 240 Vac versions of Sol.

Sol POWER SUPPLY

# SECTION II

REFERENCE

# Table 2-1. Sol Power Supply Parts List (Continued)

|            |                                   |          | Drawing     |            |

|------------|-----------------------------------|----------|-------------|------------|

| PART       | DESCRIPTION                       | QUANTITY | No.         | Designator |

| Screw      | Machine, 4-40 x 3/16              | 2        | x-3         | 20         |

|            |                                   |          | x-1         | 14         |

| Screw      | Machine, $4-40 \ge 5/16$          | 6        | <b>X-</b> 3 | 18         |

| Screw      | Machine, 4-40 x 7/16              | 1        | x-2         | 44         |

| Screw      | Machine, 4-40 x 5/8               | 1        | X-2         | 45         |

| Spacer     | Tapped, 4-40 x 1/4                | 2        | X-3         | 30         |

|            |                                   | _        | X-1         | 18         |

| Lockwasher | Internal Tooth, #4                | 9        | X-2<br>X-3  | 48<br>29   |

|            |                                   |          | x-1         | 16         |

| Hex Nut    | 4-40                              | 6        | x-2         | 50         |

| Lug        | #4                                | 2        | x-1         | 58         |

|            |                                   |          | x-1         | 13         |

| Screw      | Machine, Metal, $6-32 \times 1/2$ | 16       | x-2<br>x-3  | 47<br>16   |

|            |                                   | 2        |             |            |

| Screw      | Machine, Nylon, 6-32 x 1/2        | 2        | X-2         | 46         |

| Screw      | Machine, Metal, $6-32 \times 3/4$ | 1        | X-3         | 19         |

| Screw      | Self-tapping, #6 x 5/16           | 4        | X-3         | 17         |

|            |                                   |          | X-1         | 17         |

| Lockwasher | Internal Tooth, #6                | 22       | X-2<br>X-3  | 52<br>28   |

|            |                                   |          |             |            |

| Hex Nut    | 6-32                              | 22       | X-1<br>X-2  | 15<br>51   |

|            |                                   |          | <b>X-3</b>  | 24         |

| Screw      | Machine, Metal, 8-32 x 1/2        | 3        | X-3         | 15         |

| Lockwasher | Internal Tooth, #8                | 3        | X-3         | 27         |

| Hex Nut    | 8-32                              | 3        | <b>X-</b> 3 | 23         |

| Lug        | #10                               | 2        | <b>X-3</b>  | 12         |

| Compound   | Heatsink                          | l        | -           | -          |

| Solder     | 60/40, 20 SWG                     | -        | -           | -          |

|            |                                   |          |             |            |

REV A

II-4

Sol POWER SUPPLY

2.3 ASSEMBLY TIPS

2.3.1 Electrical

For the most part the assembly tips given in Paragraph 3.2 of Section III (Page III-1) apply to assembling the Sol regulator board and power supply.

In addition, scan Section II completely before you start to assemble the power supply.

2.3.2 Mechanical

1. If you do not have the proper screwdrivers (see Paragraph 2.5), we recommend that you buy them rather than using a knife point, a blade screwdriver on a Phillips screw, and other makeshift means. Proper screwdrivers minimize the chances of stripping threads, disfiguring screw heads and marring decorative surfaces.

2. To assure a correct fit and tight assembly, be sure you use the screws specified in the instructions.

3. Lockwashers are widely used in the power supply assembly so that screws will not loosen when subjected to stress or vibration. When a lockwasher is specified, do not omit it and make sure you install it correctly.

4. Some instructions call for prethreading holes. This is done to make assembly easier by giving you maximum working space for installing relatively hard-to-drive sheet metal screws. If you bypass prethreading instructions you will only make subsequent cabinet-chassis assembly more difficult.

To prethread a hole, insert specified screw in the hole and position it as straight as possible. While holding the screw in this position, drive it into the metal with the proper screwdriver. If started straight the screw will continue to go straight into the metal so that the head and sheet metal surfaces are in full contact.

5. The diameter of the shank (threaded portion) of a screw increases in relation to its number. For example, a 6-32 screw is larger in diameter than a 4-40 screw. Also, a #8 lockwasher is larger than a #4 lockwasher.

6. Heat sink compound is supplied with this kit in a small clear plastic package. It is a thick white substance which improves heat transfer between components and their heat sinks. To use the compound, pierce a small hole near the edge of the top surface of the plastic package, using a pin or sharp knife point. Squeezing the package will cause a small amount of the compound to ooze out

Sol POWER SUPPLY

SECTION II

out of the hole, which may then be applied with a toothpick or small screwdriver blade. Spread a thin film of the compound on the mating surfaces of both the heat-generating component and the heat sink surface which it will contact. Then assemble as directed.

### 2.4 ASSEMBLY PRECAUTIONS

The precautions concerning soldering and the installation and removal of integrated circuits given in Paragraph 3.3 of Section III (Page III-9) also apply to assembling the Sol regulator board.

# 2.5 REQUIRED TOOLS, EQUIPMENT AND MATERIALS

The following tools, equipment and materials are recommended for assembling the Sol regulator board:

- 1. Needle nose pliers

- 2. Diagonal cutters

- 3. Sharp knife

- 4. Screwdriver, thin 1/4" blade

- 5. Screwdriver, #2 Phillips

- 6. Controlled heat soldering iron, 25 watt

- 7. Volt-ohm meter

- 8. Ruler

# 2.6 ORIENTATION

2.6.1 Sol-REG PC Board

Location C5 (2500 ufd capacitor) will be located in the lower right-hand corner of the circuit board when locations SCR1, Ql and FWB1 are positioned along the top of the board. In this position the component (front) side of the board is facing up and the horizontal legends will read from left to right; the other legends will read from bottom to top. Subsequent position references related to the Sol-REG board assume this orientation.

# 2.6.2 Fan Closure Plate

The large circular cutout will be located in the upper right quadrant of the plate when the heavy gauge doubler plate is facing up. In this position the rectangular cutouts are on the left, the <u>front side</u> of the plate is facing down, the back side is facing up, and the <u>small</u> circular cutout is at the bottom. We suggest you label the two sides.

### Sol POWER SUPPLY

SECTION II

2.7 ASSEMBLY-TEST

# 2.7.1 Fan Closure Plate Assembly

Refer to Assembly Drawings on Pages X-1 and 4 in Section X. (Figure 2-1 shows a completed fan closure plate assembly.)

Figure 2-1. Sol-20 fan closure plate assembly. (Top of plate in foreground.)

() Step 1. Mount cooling fan and guard to fan closure plate.

Insert four 6-32 x 1/2" binder or pan head screws from back side (side with doubler plate) of fan closure plate. (Use the holes positioned in each quadrant of the large circular cutout.) Slip fan guard over screws on front side of plate (side without doubler plate side). Position fan with motor support struts away from front side of closure plate and with its leads next to the rectangular cutouts in the plate. Place #6 lockwasher on each screw and secure with 6-32 hex nut.

### WARNING

FAILURE TO INSTALL FAN GUARD MAY RESULT IN DAMAGE TO THE Sol AND/OR PERSONAL INJURY.

() <u>Step 2</u>. Install power on-off switch in <u>upper</u> rectangular cutout in fan closure plate.

(Step 2 continued on Page II-8.)

Sol POWER SUPPLY

SECTION II

Bend four retainer tabs on switch in and position switch with terminals facing front side of fan closure plate. Push switch unit from back side of plate through mounting hole and bend retainer tabs outward if needed to hold switch in place.

() Step 3. Install commoning blocks (Item 10 on drawing on Page  $\overline{X-1}$ ) on front side of fan closure plate, one on each side of on-off switch.

Position each block with terminal #1 at top and terminal #5 at bottom and attach each block to front side of fan closure plate with two  $6-32 \times 1/2$  binder or pan head screws. Insert screws from back side of plate, place block over screws, on front side of plate, put #6 lockwasher on each screw and secure with 6-32 hex nut.

() <u>Step 4.</u> Install fuse holder in mounting hole located between the two rectangular cutouts in the fan closure plate.

Insert fuse holder from back side of plate, position large tab at top, next to on-off switch, and secure holder to plate with the large lockwasher and nut supplied with holder.

() Step 5. Install AC Power cord receptacle on fan closure plate.

Position receptacle on front side of fan closure plate over the rectangular cutout below fuse holder. Orient receptacle with green lead at the bottom and align the receptacle and closure plate mounting holes. Insert two  $6-32 \times 1/2$  binder or pan head screws from back side of plate through each mounting hole, put #6 lockwasher on each screw and secure with 6-32 hex nut. Be sure receptacle is properly seated in cutout before tightening to avoid damage.

() Step 6. Install female coaxial connector on fan closure plate.

Insert connector from front side of plate so that the threaded end projects through to the back side. Then insert four 4-40 x 5/16 binder or pan head screws from back side of plate through the four connector and plate mounting holes. Place #4 lockwasher on each screw except the upper one which is closest to the AC receptacle. Secure with 4-40 hex nuts. (Leave upper nut closest to receptacle loose.)

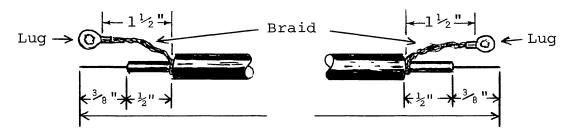

() Step 7. Prepare RG59/U coaxial cable. (See Figure 2-2.)

Cut a 15" piece of coaxial cable from that supplied. Strip away 1-1/2 inch of the outer insulation at both ends to expose shield. Unbraid shield at one end and loosely twist it into a single lead. Do the same thing at the other end. Tin shield lead at each end and solder a #4 lug to each lead. Then remove one inch of the inner conductor insulation at both ends and cut inner conductor to 3/8" length.

Figure 2-2. Coaxial cable preparation.

() <u>Step 8</u>. Connect coaxial cable to coaxial connector installed in Step 6.

Solder inner conductor on one end to the pin of the connector. Remove hex nut on upper connector mounting screw closest to AC receptacle, place lug (coaxial shield) on screw and reinstall hex nut.

- () <u>Step 9</u>. Connect fan closure plate wiring. (See Drawing X-4.)

- () Install the 3" power switch-to-commoning block cable. Connect the female spade lug end to the upper terminal of the on-off switch and the commoning block lug end to the #1 terminal of the commoning block closest to the fan. <u>NOTE</u>: To install commoning block lugs, position lug with its open side facing away from the terminal numbers on the block. Then gently push lug into appropriate terminal receptacle until it is fully seated.

- () Install the 3-1/4" fuse holder-to-power switch cable. (This cable has female spade lugs at both ends.) Connect one end to the bottom terminal of the on-off switch and the other to the longer male spade lug on the fuse holder.

- () Connect the AC receptacle wire closest to the fan to the other fuse holder lug. NOTE: The green AC receptacle wire will be connected later.

- () Connect other AC receptacle wire to terminal #4 on the commoning block furthest away from the fan (TB2).

- () Connect upper wire of fan cord to terminal #3 of the commoning block closest to fan (TB1).

- () Connect lower wire of fan cord to terminal #5 of commoning block furthest from fan.

- () Put fan closure assembly aside.

Sol POWER SUPPLY

(

SECTION II

2.7.2 Sol-REG Assembly and Test

Circuit references, values and outlines are printed on the component side of the board to assist in assembly. Also refer to Drawing X-2 in Section X.

() <u>Step 10</u>. Visually check Sol-REG board for solder bridges (shorts) between traces, broken traces and similar defects.

If visual inspection reveals any defects, return the board to Processor Technology for replacement. If the board is not defective, proceed to next paragraph.

() <u>Step 11</u>. Install the following resistors in the indicated locations. Bend leads to fit distance between mounting holes, insert leads, pull down snug to board, solder and trim.

| LOCATION VALUE (ohms)         | COLOR CODE                                                       |

|-------------------------------|------------------------------------------------------------------|

|                               | ne<br>ange-orange-brown<br>own-black-orange                      |

| () R4 10 K "<br>() R5 1 K brc | wn-black-red                                                     |

|                               | ıe-gray-black<br>own-black-orange                                |

| () R8 1 K brc                 | own-black-red<br>een-blue-orange                                 |

| () R11 1690 brc               | own-black-orange<br>own-blue-white-brown<br>llow-black-red-brown |

Mount Rl approximately 0.15" from board surface.

- () <u>Step 12</u>. Install U2 (1458) in its location between C2 and C3. U2 is positioned with pin 1 in the lower left-hand corner and soldered into place. See "Loading DIP Devices" in Appendix IV.

- () <u>Step 13</u>. Install diodes Dl (1N5231), D2 (1N4148), D3 and D4 (1N4001). Bend leads to fit distance between mounting holes, insert leads, pull down snug to board, solder and trim. BE SURE to position Dl with its cathode (dark band) to the left, D2 and D3 with their cathode at the bottom, and D4 with its cathode at the top.

- () <u>Step 14</u>. Install the following capacitors in the indicated locations. Take care to observe the proper value, type and orientation, if applicable, for each installation. Bend leads outward on solder (back) side of board, solder and trim.

(See NOTE on Page II-11.)

REV C

### NOTE

Disc capacitor leads are usually coated with wax during the manufacturing process. After inserting leads through mounting holes, remove capacitor and clear the holes of any wax. Reinsert and install.

|     | LOCATION | <u>VALUE (ufd)</u> | TYPE     | ORIENTATION           |

|-----|----------|--------------------|----------|-----------------------|

| ( ) | Cl       | 15                 | Tantalum | "+" lead bottom right |