# **Scientific Control Corporation**

\$

# SPL Assembler Manual 650

© SCC 1966

# SCIENTIFIC CONTROL CORPORATION

## 650 SPL REFERENCE MANUAL

# TABLE OF CONTENTS

| SECTI | ON                                                 | PAG                                                                                                                                                                                                          | E |

|-------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| I.    | INT                                                | RODUCTION                                                                                                                                                                                                    |   |

| II.   | GEN                                                | ERAL DESCRIPTION                                                                                                                                                                                             |   |

|       | A.<br>B.                                           | Program                                                                                                                                                                                                      |   |

|       |                                                    | 1. Symbolic Addresses                                                                                                                                                                                        |   |

|       |                                                    | a. Symbolic Labels                                                                                                                                                                                           |   |

|       |                                                    | 2. Location Field 6                                                                                                                                                                                          |   |

|       |                                                    | 3. Operation Field 6                                                                                                                                                                                         |   |

|       |                                                    | a. Indirect Address                                                                                                                                                                                          |   |

|       |                                                    | 4. Variable Field (Address, Tag Field) 7                                                                                                                                                                     |   |

|       |                                                    | 5. Comments Field                                                                                                                                                                                            |   |

|       | C.                                                 | Literals                                                                                                                                                                                                     |   |

|       | D.                                                 | Data Items                                                                                                                                                                                                   |   |

|       |                                                    | <ol> <li>Octal Integers</li></ol>                                                                                                                                                                            |   |

| 111.  | PSE                                                | UDO-OPERATIONS                                                                                                                                                                                               |   |

|       | A.<br>B.<br>C.<br>D.<br>E.<br>F.<br>G.<br>H.<br>I. | BCI       11         BSS       12         CALL       12         DEC       12         EQU       12         EQU       13         END       13         EVEN       14         JMP       14         NAME       14 |   |

SECTION

•

| J.  | ORG                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| К.  | PAR                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| L.  |                                                                                                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MAC | CHINE INSTRUCTIONS                                                                                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Α.  | Symbol Table                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B.  | Data Transfer Instructions                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| C.  |                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D.  |                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Ε.  | Shift Instructions                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| F.  |                                                                                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| G.  |                                                                                                             | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H.  |                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| I.  |                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| J.  |                                                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 1. Arithmetic                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                                                                                                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| v   | Tanut (Output Tantauctions                                                                                  | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| K.  | Input/output instructions                                                                                   | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ASS | EMBLER OPERATION                                                                                            | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Α.  | Program Listing                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Β.  |                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| С.  | Assembly Information                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D . | Source Tape Updating Procedure 4                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | K.<br>L.<br>MAC<br>A.<br>B.<br>C.<br>D.<br>E.<br>F.<br>G.<br>H.<br>I.<br>J.<br>K.<br>A.SS<br>A.<br>B.<br>C. | K. PAR       1         L. Operation Definitions       1         MACHINE INSTRUCTIONS       1         A. Symbol Table       1         B. Data Transfer Instructions       2         C. Arithmetic Instructions       2         D. Control and Test Instructions       2         E. Shift Instructions       2         F. Register Change Instructions       2         G. Literal Instructions       2         H. Micro-Operate Instructions       3         J. 650 Extended Operate Instruction Code       3         J. 650 Extended Operation Codes       3         I. Arithmetic       3         Z. Shifts       3         K. Input/Output Instructions       3         ASSEMBLER OPERATION       3         A. Program Listing       4         B. Error Indications       4         G. Assembly Information       4 |

# APPENDICES

| Α | MNEMONIC OPERATION CODES         | 44 |

|---|----------------------------------|----|

| В | SCC 650 MACHINE INSTRUCTIONS     | 45 |

| С | SCC 650 STANDARD CHARACTER CODES | 46 |

PAGE

#### GENERAL DESCRIPTION

II.

Programs written in SPL assembly language are processed into object programs by the SPL assembler. The SPL assembler accepts assembly language programs from either the paper tape reader or the typewriter. A listing of the assembled programs may be obtained on the typewriter. The assembled programs are punched onto paper tape in one of two forms: Relocatable binary format or Absolute binary format.

#### A. PROGRAM

An SPL assembly language program consists of a series of one or more lines, the last of which must be an END directive.

A line contains a symbolic assembler delcaration, a machine instruction, or a symbolic instruction.

A program may contain fixed or relative instructions and addresses. Fixed instructions and addresses refer to a fixed memory location when the program is loaded. Relative instructions and addresses are relative to the program and are relocated by the Loader when the program is loaded. The type fixed or relative is defined by an ORG declaration.

#### B. SYMBOLIC INSTRUCTION FORMAT

A symbolic instruction line consists of a location field, an operation field, a variable field (address, tag field), and a comments field. A line is one logical unit and the fields within a line are defined as being in fixed character positions or columns. For paper tape and typewriter, a line consists of a string of up to 80 character positions terminated by a carriage return. The fields within a line may be defined as starting at a fixed character position or may be defined by a tab character to the position.

The format of a line is as shown on the coding form, on the following page.

# SCIENTIFIC CONTROL SYSTEMS, INC. 14008 DISTRIBUTION WAY

| 80 COLUMN CODING             | AND DATA      | A FORM                   |                                       |                                 |                                           | NAME                                |                        |

|------------------------------|---------------|--------------------------|---------------------------------------|---------------------------------|-------------------------------------------|-------------------------------------|------------------------|

| PROGRAM                      |               |                          |                                       |                                 |                                           | UNI T                               | DATE                   |

| ROUTINE                      |               |                          |                                       |                                 |                                           | EXT.                                | PAGE OF                |

| STATE- C<br>MENT N<br>NO. T. | STATEMEN      | iT                       |                                       |                                 |                                           | FORTRAN                             | IDENTIFICATION         |

| LOCATION OPER                | TION          | ADDRESS, TAG             |                                       | COMMENTS                        |                                           | SPL                                 |                        |

| 1 2 3 4 5 6 7 8 9 10 1       | 1 12 13 14 15 | 16 17 18 19 20 21 22 23  | 4 25 26 27 28 29 30 31 32 33 34 35 36 | 37 38 3940 41 42 43 44 45 46 47 | 7 48 49 50 5 1 52 53 54 55 56 57 58 59 66 | 61 62 63 64 65 66 67 68 69 70 71 72 | 7374 75 76 77 78 79 80 |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 | ┶╾┼┼╋┼┼┼┼┼┼┼                              |                                     |                        |

|                              |               |                          |                                       |                                 |                                           | ╊╶┼╼╄╌┝╶┼╌╄╌┾╴╄╶┾╸╋╶┽╴              |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           | ╏┼┼┼┼┼┼┦┼╸                          |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           | ┨╶┤╶┼╸┾╌┼╴╀╼┼╶┤╴┦╸╀╌                |                        |

|                              |               |                          |                                       |                                 |                                           | ╊╶┽ <sup>╶</sup> ╇┈┽╴┼╶┽╼┞╌┼╶┤╶╊╶┽  |                        |

|                              |               |                          |                                       |                                 | ╶┿╴┾╌╄┲╄╌┦╴┽╺╄╌╄╌╄╌╄╌╄                    |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              |               |                          |                                       |                                 |                                           |                                     |                        |

|                              | ┼╌┼╌┠╴┠       |                          |                                       |                                 | ┼┼┼╏┼┼┼┼┼┼┼                               | ╏╎┊╎╎╷╎╎╎                           |                        |

|                              | ┼┼┼╂┨         |                          | ┽┽┾┿┿┽╋┼┿╶┾┿┿                         |                                 |                                           |                                     |                        |

|                              | ┼┼┼╊╊         |                          | ┽┽┿┼┾┼╊┿┽┼┼┼                          |                                 |                                           |                                     |                        |

| 1 2 3 4 5 6 7 8 9 10 11      | 12 13 1415    | 16 17 18 19 20 2 1 22 23 |                                       |                                 | 7 48 49 50 51 52 53 54 55 56 5758 5960    |                                     |                        |

• •

· •

#### 1. Symbolic Addresses

A symbolic address is a collection of characters which serves as a name for a location used by the program. The assembly process will assign a unique location to each symbol appearing in the program. We shall distinguish four types of addresses which may appear in a program: (1) Symbolic, (2) Program point, (3) Absolute, and (4) Special.

a. Symbolic Labels

A symbolic label consists of one to six non-blank, alphanumeric characters. The first character must be an alphabetic character (the currency symbol, '\$', is considered to be alphabetic). Each symbol used must receive a memory location as its assignment. This may be accomplished in one of two manners - it may appear in the location field or it may be defined by the EQU pseudo-operation described later. In either case, a symbol must be defined precisely once.

b. Program Point Addresses

Program point addresses provide the assembler with short-term memory for symbols as opposed to the long-term memory provided by symbolic labels. When written in the location field, the program point takes the form of a decimal point followed by a single letter, in the address field, by + or - followed by a single letter. The operand address "+L" refers to the next cell to be defined as ".L"; the operand address "-L" refers to the cell most recently defined as ".L". Program point addresses may be defined only by appearing in the location field and may be re-defined in this manner indefinitely.

c. Absolute Addresses

An absolute address (machine address) consists of one to five decimal digits or 1-5 octal digits preceded by a "'" character. If desired, leading zeros need not be written. The assembler will use the given number rather than treat the address as symbolic. Absolute addresses may not appear in the location field.

d. Special Address

The symbol '\*' acting as an address indicates the address of the instruction being assembled. The symbol '\*\*' forces a zero address, but indicates that the address may be changed by the program. Special address may not appear in the location field.

#### 2. Location Field

The location field occupies column 1-6; column 7 is always blank. The location field may contain any allowable symbolic address as a label, or may be left blank.

As asterisk character '\*' in column one of the location field defines the line as being a comment line. A comment line is not processed by SPL except for listing purposes. Comment lines may appear anywhere within a program.

#### 3. Operation Field

Operation codes are written using the standard mnemonic abbreviations. They should be written starting in column 8 of the operation field. If desired, a 1 or 2 digit octal operation code may be written. The operation field will also be used for pseudo-instructions which will be described later.

#### a. Indirect Address

The specification that the operand address of an instruction is an indirect address is signified by the presence of an asterisk character '\*' immediately following the operation code.

#### 4. Variable Field (address, Tag Field)

The variable field begins in column 16 and is terminated by the first blank character after column 16.

The variable field consists of a symbolic address or a symbolic address followed by a '+' or '-' followed by a decimal or octal integral increment. Octal increments are written with an "'" followed by an octal digit string. The variable field may be left blank if not required by the instruction. Following the variable field, a comma followed by an X or D may occur if other than the relative or relative indirect mode of addressing is required. The D indicates the direct mode while the X indicates the indexed mode.

The index mode designated (X) does not cause a modification to the current line instruction and is introduced only to make the symbolic code line more readable.

#### 5. Comments Field

The comments field follows the variable field and may extend to column 80 of a line.

The comments field may contain programmer remarks and is not processed by SPL except for listing purposes.

#### C. LITERALS

A literal is a symbol referenced as a constant to be defined by SPL. A literal may appear only in the variable field of a line and only for the four mnemonic literal instructions, ANL, XOL, LDL, and ADL. It cannot be indexed, and may not appear in an expression.

A literal is a one to two digit optionally signed decimal or octal integer or any single character preceded by the '=' character.

For the literal instructions, LDL and ADL, the 6-bit literal address Y is considered to be a signed integer, with  $-!40=-32 \le Y \le 31=!37$ . (The apostrophe prefixed number indicates an octal number as written for SPL.) Negative values have the 6-bit two's complement of the integer value placed in the address portion of the literal instruction.

For the literal instructions ANL and XOL, the 6-bit literal address Y is considered to be a non-negative integer, with  $00 \le Y \le 63=177$ .

If the literal address is represented with an '=' followed by a single character, then SPL places the equivalent 6-bit binary configuration for that character as the literal instruction address.

#### Examples:

| LDL | 1   |

|-----|-----|

| ADL | -5  |

| ANL | 77י |

| ANL | =A  |

| XOL | 140 |

#### D. DATA ITEMS

Three types of data items are processed by SPL: Octal, Decimal, and alphanumeric. They are specified by pseudo-operations PAR, DEC and BCI (see III PSEUDO OPERATIONS).

#### 1. Octal Integers

An octal data items consists of one word containing from one to four octal digits. The octal data item is converted to binary. If the item is preceded by a minus sign, the two's complement of the binary number is generated.

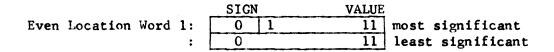

#### 2. Double Precision Decimal Integers

Double precision decimal integers are represented internally as two word two's complement data items. The most significant part of the number is contained in the first word and the least significant part is contained in the next successive word. The first word must be at an even machine location. A double precision, I, must be in the range  $-33554432 = -2^{24} \neq I = 2^{24} - 1 = 33554431$ .

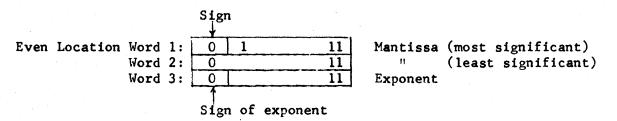

#### 3. Double Precision Floating Point Numbers

A floating point number is a decimal number which is expressed as either of the following: A signed or unsigned decimal number containing a decimal point optionally followed by an exponent part consisting of the letter E followed by a signed or unsigned decimal integer.

A signed or unsigned decimal integer <u>optionally</u> containing a decimal point, followed by an exponent part consisting of the letter E followed by a signed or unsigned decimal integer.

The number following the letter E is the power of ten to which the number is to be raised when it is converted.

Examples:

1.57 1.57E6 157E-6

Double precision floating point numbers are represented internally as three word two's complement data items. The data item consists of a 2-word 23 bit mantissa plus sign, where most significant part is carried in an even machine location, followed by a 1-word twelve bit signed binary exponent. The magnitude of a double precision floating point number, F, must be in the range  $2^{-2048} \leq F \leq 2^{2048}$ . The mantissa of the number must be less than  $2^{24}$ -1=33554431.

#### 4. Alphanumeric Data

An alphanumeric data item is composed of from one to two characters. These characters are converted to six-bit character codes and stored as one word data items. (The character codes are listed in Appendix B.

#### PSEUDO-OPERATIONS

III

Pseudo-operations are operation codes which direct the assembler to perform operations on the program. Pseudo-operations do not normally cause actual machine instructions to be output, but cause memory allocations, constant definitions, symbolic definitions, or external program linkages.

Pseudo-operations are written similar to normal operations, with any exception to be noted under the description of the particular pseudo-operation. The location field of any pseudo-operation may contain a symbolic name which (with the exception of EQU) will be assigned the next address in sequence, prior to any effects the pseudo-operation might have on subsequent address assignments.

A. BCI

The BCI pseudo-operation specifies words of data expressed as 6-bit BCD characters packed two per word.

The variable field contains a word count followed by a comma followed by a string of characters. The word count specifies the number of 2 character words present in the character string. Blanks are counted as significant characters in the string.

Examples:

A BCI 2, DATA B BCI 6, DATA WORDS

#### B. BSS

The BSS pseudo-operation declares a data area which is reserved by the program.

The variable field contains a symbolic address which defines the number of words to be reserved. The value of the symbolic address must have an absolute value.

Examples:

| A<br>C | BSS<br>EQU | 5<br>י75    |

|--------|------------|-------------|

|        | •          |             |

|        | •          |             |

| В      | BSS        | <b>20</b> 0 |

|        | BSS        | . <b>C</b>  |

#### C. CALL

The CALL pseudo-operation creates a link to an external subprogram CALL generates a two word link to an object time transfer routine and indicates, to the Loader, the name of the required subprogram.

Programs using CALL must not be absolute and may not use direct addresses

D. DEC

The DEC pseudo-operation specifies words of data expressed as double precision decimal or floating point numbers. The first word of the data will be set to an even location in the machine.

The variable field contains one or more double precision, decimal integers or floating point numbers separated by commas. Negative numbers will be converted to two's complement. As many items as desired may be specified in the variable field. The format of decimal numbers is described in Section II, D., 2.

Examples:

| Α | DEC | 1,6 |    |       |      |    |

|---|-----|-----|----|-------|------|----|

| В | DEC | 25, | 1, | 7E-8, | 2E5, | 3. |

| С | DEC | -27 |    |       |      |    |

#### E. EQU

The EQU pseudo-operation specifies the equivalence of symbols within a program.

The location field contains a label which is set as having the value or address specified in the variable field.

The variable field contains a symbolic address. Any symbolic labels must be defined prior to appearing within the EQU pseudo-operation. That is, any symbolic labels appearing in the variable field must have appeared in the location field of a previous instruction. Examples:

| Α | EQU | Х       |

|---|-----|---------|

| В | EQU | Y + 100 |

| С | EQU | B-20    |

#### F. END

The END pseudo-operation signifies the end of the program and must be present. The variable field defines the execution address of the program. This field may be left blank if a subprogram is being assembled. Example:

START

Х

END

LDA

START

Designates the end of the program, and an execution address at START.

The EVEN pseudo-operation causes the location of the next SPL instruction to be set even. This may result in one memory location being skipped at most.

H. JMP

The JMP pseudo-operation permits programmers to write jump instructions without deciding whether the desired location is forward or backward.

A JMF or JMB will be generated.

I. NAME

The NAME pseudo-operation specifies and defines the names of locations in the program which may be referenced by external programs.

The variable field contains a list of all labels contained within the program which may be referenced by external programs.

Example:

|   | NAME | А, В |

|---|------|------|

| Α | PAR  | ø    |

|   | •    |      |

|   | •    |      |

|   | •    |      |

| В | DEC  | 2    |

The labeled locations, A and B, may be referenced by external programs.

J. ORG

The ORG pseudo-operation defines the origin or loading address of a sequence of instructions or data. This may be either a relative or absolute value, but relocatable programs may not use absolute 'ORG' declarations except for areas 00000-00077 and 07701-07777. The variable field defines the starting address of following instructions or data and may contain any symbolic address type, except that symbolic labels must have been previously defined.

The first line of every program should be an 'ORG' pseudo-operation, to indicate the type of program being assembled. 'ORG n' indicates an absolute program starting at location n, where n is a decimal or octal address. 'ORG \*' indicates a relocatable program of less than 4096 words in length, while 'ORG \*+n' indicates a partially relocatable program starting at location n in a bay. If the initial ORG line is omitted, 'ORG \*+Ø' is assumed.

Examples:

|   | ORG | *    | Indicates a relocatable program    |

|---|-----|------|------------------------------------|

| Α | LDA | В    | A is assigned address relative Ø   |

| B | ORG | *+2Ø | Defines origin as relative forward |

|   | •   |      | 2Ø                                 |

|   | •   |      |                                    |

|   | •   |      | r                                  |

|   | ORG | B+1  | Defines origin as relative 2       |

#### K. PAR

The PAR pseudo-operations specifies words of data expressed as symbolic addresses, or decimal or octal integers.

The variable field contains one or more symbolic address. The resulting word will contain the 12-bit address assigned to the corresponding symbolic address.

Examples:

#### PAR A, B+2, C, 2, '4Ø PAR '27, \*+5

(Note: In the second example, the second word would be assigned an address equal to its address plus 5, not the starting address of PAR plus 5.)

# L. OPERATION DEFINITIONS

In order to expand the allowable symbolic operation code set, symbolic operation codes not defined by the assembler may be defined by writing the symbolic operation to be defined in the op-code field with a variable field started by an "=" signed and followed by any symbolic address (normally an octal number). If a symbolic label is used, it must be absolute and have been previously defined. In any case, the resulting 12-bit value will be used as the basic operation code, to which the symbolic address is added when the new symbol is used as an operation. Example:

| ABC='22ØØ | ABC | has an | operation code of '2200                                       |

|-----------|-----|--------|---------------------------------------------------------------|

| DEF=A+7   |     |        | operation code consisting<br>current address of A plus seven. |

# MACHINE INSTRUCTIONS

IV

This section describes the instruction repertoire of the SCC 650 computer.

The word format of a machine instruction is as follows:

**Basic Instruction Format**

| ø | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

|---|---|---|---|---|---|---|---|---|---|----|----|

|   | 0 | P |   | I | R |   |   | Y | , |    |    |

where

OP is the basic 4-bit operation code

I is the indirect address bit

R is the mode bit

Y is the 6-bit instruction operand address

The descriptions of each of the instructions is headed by the information in the following format:

| MNM | Name       | Timing                                                                                                                                            |  |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | Code I R Y |                                                                                                                                                   |  |

|     | MNM        | is the SPL mnemonic assigned to the instruction                                                                                                   |  |

|     | Name       | is the instruction name.                                                                                                                          |  |

|     | Timing     | is the number of machine cycles used by the in-<br>struction. Each level of indirect addressing adds<br>one cycle to the instruction.             |  |

|     | Code       | is the octal operation code of the instruction; and<br>in some cases the complete 4-digit octal code in-<br>struction word will be given.         |  |

|     | I          | is present if the instruction can optionally contain<br>an indirect address bit. Otherwise, the numeric<br>value of I is placed in this position. |  |

|     | R          | is present if the instruction can optionally contain a mode bit.                                                                                  |  |

Y

## Timing

is present if the instruction contains an operand address. Otherwise, the octal value of Y is placed in this position.

Table IV, A. contains a list of symbols and their definitions used in the instruction description. The instructions are categorized into sections according to function.

Operand is defined as being the contents of the effective operand address.

A. TABLE

# NOTATION

| SYMBOL   | DEFINITION                                                                           |  |  |

|----------|--------------------------------------------------------------------------------------|--|--|

| Α        | The main arithmetic register, or Accumulator                                         |  |  |

| X        | The index register and left hand Accululator extension                               |  |  |

| Y        | Operand address of instruction                                                       |  |  |

| M        | Effective operand address of instruction                                             |  |  |

| <b>P</b> | The location counter. Contains the address of the instruction to be executed.        |  |  |

| ()       | Contents of. Signifies the contents of the symbol enclosed within the parentheses.   |  |  |

| >        | Replacement designator. The value on the left is placed into the value on the right. |  |  |

| +        | Add                                                                                  |  |  |

|          | subtract                                                                             |  |  |

| 1        | Divide                                                                               |  |  |

| x        | Multiply                                                                             |  |  |

| J.       | Logical AND                                                                          |  |  |

|          | Logical OR                                                                           |  |  |

|          | Exclusive OR                                                                         |  |  |

|          | Absolute value                                                                       |  |  |

| <u> </u> | One's complement                                                                     |  |  |

| <        | Less than                                                                            |  |  |

| >        | Greater than                                                                         |  |  |

| =        | Equal                                                                                |  |  |

| ≡        | Equivalent by definition                                                             |  |  |

| Β.           | DATA T                 | RANSFER INSTRUCTIONS                                        |

|--------------|------------------------|-------------------------------------------------------------|

| ·            | LDA                    | Load A Timing: 2                                            |

| n<br>Talanta | tyster fra de          | <u>60 I R Y</u>                                             |

|              |                        | $(M) \rightarrow A$                                         |

|              | n e staar<br>Alexandre | The operand is placed in A. The contents of memory at M     |

|              |                        | remains unchanged. (See also literal instruction LDL.)      |

|              | STA                    | Store A Timing: 2                                           |

|              |                        | <u>34 I R Y</u>                                             |

| · ·          |                        | $(A) \rightarrow M$                                         |

|              |                        | The contents of A are placed into memory at M.              |

|              |                        | The contents of A remains unchanged.                        |

|              | LDX                    | Load Index Timing: 2                                        |

|              |                        | <u>10 I R Y</u>                                             |

|              |                        | (M) → X                                                     |

|              |                        | The operand is placed into the index register. The contents |

|              |                        | of M remains unchanged.                                     |

|              | STX                    | Store Index Timing: 2                                       |

|              |                        | <u>14 I R Y</u>                                             |

|              |                        | (X)→ M                                                      |

|              |                        | The contents of the index register is placed into M. The    |

| ÷т.          |                        | contents of the index register remains unchanged.           |

|              |                        |                                                             |

TOANCEED INCTDUCTIONS

DATA

# C. ARITHMETIC INSTRUCTIONS

Arithmetic operations are performed in two's complement arithmetic. Overflow and carry conditions cause the setting of machine flip-flops which may be tested or used for double precision arithmetic. The flipflops and conditions are as follows: Overflow flip-flop. Any arithmetic operation which causes the sign of the result to be wrong (i.e., a carry into the sign position) causes this flip-flop to be set. For example, addition of two positive numbers resulting in a negative number causes the overflow flip-flop to be set.

Carry flip-flop - Any addition or subtraction which causes a carry from bit position 0 (i.e., a 13 bit result) causes the carry flip-flop to be set.

ADD Add

Timing: 2

$(A) + (M) \rightarrow A$

<u>44 I R Y</u>

The operand is added to the contents of A and the sum is placed in A. The contents of M remains unchanged.

This instruction may cause the overflow, and carry flip-flops to be set.

#### Subtract

#### Timing: 2

Timing: 3

<u>64 I R Y</u>

(A) - (M)→A

The operand is subtracted from the contents of A and the difference is placed in A. The operand at M remains unchanged.

This instruction may cause the overflow, and carry flip-flops to be set.

Memory Increment

$(M) + 1 \rightarrow M$

If (M) = 0,  $(P) + 2 \rightarrow P$ , otherwise  $(P) + 1 \rightarrow P$ .

One is added to the operand and placed into memory at M. If the result is zero the next instruction is skipped. Otherwise, the next instruction is taken in sequence.

This instruction will never affect the contents of the carry or overflow flip-flops.

AND Logical AND

#### Timing: 2

<u>74 I R Y</u>

(A) (M)-A

Forms the logical AND of the operand and the contents of A and places the result in A. The contents of memory at M remains unchanged.

XOR Exclusive OR Timing: 2

<u>54 I R Y</u>

(A)  $\odot$  (M)  $\leftrightarrow$  (A)  $\odot$  (M) = (A)  $\leftrightarrow$  (M)  $\rightarrow$  A

Forms the exclusive OR of the operand and the contents of A and places the result in A. The contents of M remains unchanged.

D. CONTROL AND TEST INSTRUCTIONS

HLT Halt

Timing: 1

0000

Halt

The computer halts awaiting manual intervention from the console. P contains the address of the next instruction following the HLT instruction.

The address, index, and indirect fields of this instruction are not used.

NOP No Operation

Timing: 1

0002

No operation is performed.

```

JMF Jump Forward

```

Timing: 1

<u>20 I R Y</u>

$M \rightarrow P$

The next instruction is taken at the effective operand address, M,

where if I=0 and:

R=0, then M=Y; R=1, Index State =0, then M=(P)+Y; R=1, Index State =1, then M=(X)+Y;

while if I=l and:

R=0, then M=(Y); R=1, Index State=0, then M=((P)+Y); R=1, Index State=1, then M=((X)+Y).

JMB Jump Backward

Timing: 1

<u>24 I R Y</u>

$M \longrightarrow P$

Same as for Jump Forward above with -Y replacing Y.

JSL Jump and Store Location Counter Timing: 3

<u>50 I R Y</u>

$(P)+1 \rightarrow M$ , Status  $\rightarrow M+1$ , M+2  $\rightarrow P$

The location counter address plus one, (P)+1, is placed in the effective operand address, M, and the Status Register is placed in M+1.

The next instruction is taken from location M+2.

JRT Return Jump

Timing: 3

<u>70 I R Y</u>

$(M+1) \rightarrow Status,$

$(M) \rightarrow P$

The contents of M+1 are placed into the Status Register. The next instruction is taken from location M, where the effective address M is as described in Jump Backward above.

SHIFT INSTRUCTIONS Ε.

> All shift instructions are 1 bit shift and use bits 4-11 of the instruction word to indicate the type of shift.

SPL automatically sets the shift type bits in the instruction according to the mnemonic.

SAR Short Arithmetic Shift Right Timing: 1

0014

(A) right 1 place  $\rightarrow$  A

The contents of A is shifted right one binary place. Bit  $A_{11}$  is lost. Bit 0 of A is not shifted but is copied into the vacated bit position, bit 1, on its right.

SRR Short Rotate Right Timing: 1

0010

(A) rotate right 1 place  $\rightarrow$  A

The contents of A is rotated right one binary place. Bit  $A_{11}$ enters A<sub>o</sub>.

SLR Short Logical Shift Right Timing: 1

0114

(A) right 1 place  $\rightarrow$  A

The contents of A is shifted right one binary place Bit  $A_{11}$  is lost. Vacated bit position  $A_0$  is filled with a zero.

SCR Short Circulate Right

#### Timing: 1

0110

(CO,A) right 1 place \_\_\_\_ A

The coupled CO- and A-registers, with CO preceding bit  $A_0$ , is rotated right one binary place. Bit CO enters  $A_0$  and bit  $A_{11}$ enters CO.

LAR Long Arithmetic Shift Right Timing: 1

<u>0214</u>

(A,X) right 1 place  $\rightarrow$  A,X

The contents of A and X are shifted right one binary place. Bit  $A_{11}$  enters  $X_0$ . Bit  $X_{11}$  is lost. Bit 0 of A is not shifted but is copied into the vacated bit position bit 1 on its right.

LRR Long Rotate Right

Timing: 1

0210

(A,X) right cycle 1 place  $\rightarrow$  A,X

The contents of A and X are rotated right one binary place. Bit  $A_{11}$  enters  $X_0$ . Bit  $X_{11}$  enters  $A_0$ .

<u>LLR</u> Long Logical Shift Right Timing: 1 (A,X) right 1 place  $\rightarrow$  A,X The contents of A and X are shifted right one binary place. Bit

$X_{11}$  is lost. Bit  $A_{11}$  enters  $X_0$ . Vacated bit position  $A_0$  is filled with a zero.

LCR Long Circulate Right Timing: 1

0310

(CO, A, X,) right 1 place  $\rightarrow A, X$

The coupled CO-, A- and X-registers, with CO preceding bit  $A_0$ and  $A_{11}$  preceding  $X_0$ , is rotated right one binary place. Bit CO enters  $A_0$ , bit  $A_{11}$ , enters  $X_0$  and bit  $X_{11}$  enters CO. <u>SAL</u> Short Arithmetic Shift Left Timing: 1

0016

(A) left 1 place  $\rightarrow$  A

The contents of A is shifted left one binary place. Bit  $A_0$  is lost. Vacated bit position  $A_{11}$  is filled with a zero.

If the sign of A, A<sub>o</sub>, changes, the overflow flip-flop is set. <u>SRL</u> Short Rotate Left Timing: 1

0012

(A) left cycle 1 place  $\rightarrow A$

The contents of A is rotated left one binary place. Bit  $A_0$  enters  $A_{11}$ .

SLL Short Logical Shift Left Timing: 1

0116

(A) left 1 place  $\rightarrow A$

The contents of A is shifted left one binary place. Bit  $A_0$  is lost. Vacated bit position  $A_{11}$  is filled with a zero.

SCL Short Circulate Left

Timing: 1

0112

(A,CO) left 1 place  $\rightarrow$  A

The coupled A- and CO-registers, with CO following bit  $A_{11}$ , is rotated left one binary place. Bit CO enters  $A_{11}$  and bit  $A_{0}$ enters CO.

#### 0216

(A,X) left 1 place  $\rightarrow$  A,X

The contents of A and X are shifted left one binary place. Bit  $X_0$  enters  $A_{11}$ . Bit  $A_0$  is lost. Vacated bit position  $X_{11}$  is filled with a zero.

Timing: 1

If the sign of A, Ao, changes, the overflow flip-flop is set.

LRL Long Rotate Left Timing: 1

0212

(A,X) left cycle l place  $\rightarrow A,X$

The contents of A and X are rotated left one binary place. Bit  $X_0$  enters  $A_{11}$ . Bit  $A_0$  enters  $X_{11}$ .

LLL Long Logical Shift Left

Timing: 1

0316

(A,X) left 1 place  $\rightarrow$  A,X

The contents of A and X are shifted left one binary place. Bit  $A_0$  is lost. Bit  $X_0$  enters  $A_{11}$ . Vacated bit position  $X_{11}$  is filled with a zero.

LCL Long Circulate Left Timing: 1

0312

(A,X,CO) left 1 place  $\rightarrow A,X$

The coupled A-, X- and CO-registers, with CO following bit  $X_{11}$ and  $A_{11}$  preceding  $X_0$ , is rotated left one binary place. Bit CO enters  $X_{11}$ , bit  $X_0$  enters  $A_{11}$  and Bit  $A_0$  enters CO. F. REGISTER CHANGE INSTRUCTIONS

Register change instructions use the operand address portion of the instructions to specify operations. Indexing and indirect addressing are not permitted. SPL automatically sets the operand address bits from the mnemonic operation code.

CLA Clear A Timing: 1 0003 0------A The contents of A are set to zero CLX Clear X Timing: 1 0007 0**→**X The contents of X are set to zero CAX Copy A to X Timing: 1 0240  $(A) \longrightarrow X$ The contents of A are placed into the index register. A is unchanged. CXA Copy X to A Timing: 1 0140  $(X) \rightarrow A$ The contents of the index register are placed into A. X is unchanged. XAX Exchange X and A Timing: 1 0040  $(X) \rightarrow A$ ,  $(A) \longrightarrow X$ The original contents of X are placed into A.

The original contents of A are placed into X.

#### Timing: 1

0020

$(A_{0-5}) \rightarrow A_{6-11}, (A_{6-11}) \rightarrow A_{0-5}$

The original contents of  $A_{0-5}$  are placed into  $A_{6-11}$ .

The original contents of  $A_{6-11}$  are placed into  $A_{0-5}$ .

G. LITERAL INSTRUCTIONS

The literal instruction uses the literal value Y, with or without its sign- or most significant-bit extended, as its operand.

ANL Logical AND Literal

Timing: 1

<u>3Ø Y</u>

$(A_{0-5}) \longrightarrow A_{0-5},$  $(A_{6-11}) \odot Y \longrightarrow A_{6-11}$

Forms the logical AND of the address Y and the contents of  $A_{6-11}$ and places the result in  $A_{6-11}$ .  $A_{0-5}$  remains unchanged. XOL EXCLUSIVE OR Literal Timing: 1

<u>31 Y</u>

$(A_{0-5}) \rightarrow A_{0-5}$   $(A_{6-11}) \odot \overline{Y} \oplus (A_{6-11}) \odot Y = (A_{6-11}) \odot Y \rightarrow A_{6-11}$ Forms the EXCLUSIVE OR of the address Y and the contents of  $A_{6-11}$ and places the result in  $A_{6-11}$ .  $A_{0-5}$  remains unchanged.

Timing: 1

LDL Load A Literal

<u>32 Y</u>

$Y_o \equiv$  Sign-bit of  $Y \rightarrow A_{0-5}$  $Y \equiv Y_{0-5} \rightarrow A_{6-11}$

The most significant bit of the 6-bit address Y (considered as the sign-bit) is placed into  $A_{0-5}$  and Y is placed into  $A_{6-11}$ , i.e., Y with sign extended is placed in A.

Timing: 1

#### <u>33 Y</u>

(Let  $Y_0 \equiv$  Sign-bit of  $Y \rightarrow Y_{0-5}$ ,  $Y \equiv Y_{0-5} \rightarrow Y_{6-11}^{'}$ ,) then (A)+Y' \rightarrow A

The 6-bit address Y, with its most significant bit taken as the sign-bit, extended, as Y', is added to the contents of A and the sum is placed in A.

This instruction may cause the overflow, and carry flip-flops to be set.

#### H. MICRO-OPERATE INSTRUCTIONS

The "SCC 650" provides the ability in a one word "micro-instruction" to perform an operation involving the A and/or X registers, and then, optionally, test the result. SPL facilitates the usage of micro-instructions by assembling the proper codes from the information supplied in the following format.

OP F.T

#### where:

OP is the mnemonic SRA or SRX if the A or X is to be the "selected register." It is convenient to denote the selected register by SR, and the unselected register by USR.

F is a one digit code which specifies the desired function, as follows:

F=0 - test the SR only.

1 - increment the SR by one.

- 2 an add is performed with SR and USR; the result is left in the SR.

- 3 the SR is exclusively OR'd with USR replacing the SR.

- 4 one's complement of SR replaces SR.

- 5 two's complement of SR replaces SR.

- 6 one's complement of SR exclusively OR'd with USR replaces SR.

- 7 SR subtracted from USR replaces SR.

T is a one letter mnemonic (P,N, or Z) which is present if the result of the function F is to be tested, as follows:

- T=G skip the next instruction if the SR is greater than zero.

- N skip the next instruction if the SR is negative.

Z - skip the next instruction if the SR is zero.

#### I. PROGRAMMED-OPERATE INSTRUCTION CODE

SCF Set CO OFF Timing: 1

0022

Resets the carry-out bit to be  $\emptyset$  in the CO Register

SCN Set CO ON Timing: 1

0122

Sets the carry-out bit to 1 in the CO Register.

SIF Set Interrupt Control OFF Timing: 1

#### 0222

Resets the Interrupt Control Register bit to be  $\emptyset$ .

|      | SIN        | Set Interrupt Control ON                 | Timing:     | 1    |

|------|------------|------------------------------------------|-------------|------|

|      |            | <u>0322</u>                              |             |      |

|      |            | Sets the Interrupt Control Register bit  | to 1.       |      |

|      | <u>oft</u> | Overflow Test                            | Timing:     | 1    |

|      |            | 0024                                     |             | •    |

|      |            | If Overflow Register ON, reset it to OFF | , and (P)+1 | >P;  |

|      |            | otherwise (P)+2 $\longrightarrow$ P.     |             |      |

|      | <u>SBK</u> | Set Bank Flag                            | Timing:     | 1    |

|      |            | <u>0026</u>                              |             |      |

|      |            | Sets inhibit IB-Register Flag ON.        |             |      |

|      | RBK        | Restore Bank Flag                        | Timing:     | 1    |

| <br> |            | <u>0126</u>                              |             |      |

|      |            | Resets the Inhibit IB-Register flag to O | FF.         |      |

| •    | CLI        | Clear Interrupt                          | Timing:     | 1    |

|      |            | <u>0226</u>                              |             |      |

|      |            | Resets the interrupt.                    |             |      |

|      | COT        | CO Carry-Out Test                        | Timing:     | 1    |

|      |            | <u>0032</u>                              |             |      |

|      |            | If (CO)=Ø, (P)+1>P; otherwise, if (CO    | )=1, (P)+2- | —>P. |

|      | <u>XSS</u> | Index Status Set                         | Timing:     | 1,   |

|      |            | 0034                                     |             |      |

|      |            | Sets the Index Status Register to 1.     |             |      |

|      | XSR        | Index Status Reset                       | Timing:     | 1    |

|      |            | 000/                                     |             |      |

<u>0234</u>

Resets the Index Status Register to  $\emptyset$ .

# 32.

| LIA        | Load IB Register                                                   | Timing: 1                                    |  |  |  |

|------------|--------------------------------------------------------------------|----------------------------------------------|--|--|--|

|            | 0036                                                               |                                              |  |  |  |

|            | (A <sub>9-11</sub> )→IB                                            |                                              |  |  |  |

| na y tan.  | Stores (A <sub>9-11</sub> ) into the IB Register                   |                                              |  |  |  |

| AAX        | Logical AND A with X                                               | Timing: 1                                    |  |  |  |

|            | 0242                                                               | v                                            |  |  |  |

|            | $(X) \odot (A) \rightarrow A$                                      |                                              |  |  |  |

|            | The logical product of $(X) \odot (X)$                             | A) is placed in A.                           |  |  |  |

| AOX        | Logical OR A with X                                                | Timing: 1                                    |  |  |  |

|            | 0042                                                               |                                              |  |  |  |

|            | $(X) \bigoplus (A) \longrightarrow A$                              |                                              |  |  |  |

|            | The logical sum of (X) $\oplus$ (A) i                              | s placed in A.                               |  |  |  |

| MPT        | Memory Protect Test                                                | Timing: 1                                    |  |  |  |

|            | 0044                                                               | · · · · · · · · · · · · · · · · · · ·        |  |  |  |

|            | If Memory Protect ON, reset it to OFF, and $(P)+1 \rightarrow P$ ; |                                              |  |  |  |

|            | otherwise, if OFF, $(P)+2 \rightarrow P$ .                         |                                              |  |  |  |

| <u>10T</u> | Input/Output Error Test                                            | Timing: 1                                    |  |  |  |

|            | 0046                                                               |                                              |  |  |  |

|            | IF I/O Error Register ON, rese                                     | t it to OFF, and $(P)+1 \longrightarrow P$ ; |  |  |  |

|            | otherwise, if OFF, $(P)+2 \rightarrow P$ .                         |                                              |  |  |  |

| LAS        | Load from Switch Register                                          | Timing: 1                                    |  |  |  |

|            | 0050                                                               |                                              |  |  |  |

|            | $(Switch) \rightarrow A.$                                          |                                              |  |  |  |

|            | The content of the Switch Regi                                     | ster is placed in A.                         |  |  |  |

#### Timing: 1

## <u>0054</u>

$(A) + (CO) \rightarrow A$

The CO Register bit is added to the contents of A and the sum is placed in A. The contents of CO remains unchanged.

SST Store Status Register Timing: 1

# 0060