# MPX-32 <sup>™</sup>

**Resident Modules and Handlers**

**Revision 3.5**

Technical Manual Volume !!

April 1990

# **Limited Rights**

This manual is supplied without representation or warranty of any kind. Encore Computer Corporation therefore assumes no responsibility and shall have no liability of any kind arising from the supply or use of this publication or any material contained herein.

## **Proprietary Information**

The information contained herein is proprietary to Encore Computer Corporation and/or its vendors, and its use, disclosure, or duplication is subject to the restrictions stated in the standard Encore Computer Corporation License terms and conditions or the appropriate third-party sublicense agreement.

# **Restricted Rights**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at 252,227,7013.

Encore Computer Corporation 6901 West Sunrise Boulevard Fort Lauderdale, Florida 33313

TM MPX-32 is a trademark of Encore Computer Corporation

® CONCEPT/32 is a registered trademark of Encore Computer Corporation

Copyright © 1990 by Encore Computer Corporation ALL RIGHTS RESERVED Printed in the U.S.A.

## **Revision 3.5**

Technical Manual Volume II(A)

**April** 1990

```

H.ADA

H.ALOC

H.BKDM

H.EXEC

H.EXSUB

H.FISE

H.IOCS

H.IP?? and H.SVC?

H.MDT

H.MEMM

H.MEMM2

H.MONS

H.MVMT

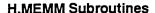

H.PTRAC

H.REMM

H.REXS

H.SURE

H.TAMM

H.TSM

H.VOMM

System Macros Cross-Reference

```

• •

# **History**

The MPX-32 Release 3.2 Technical Manual, Publication Order Number 322-001550-000, was printed September, 1983.

Publication Order Number 322-001550-100, (Revision 1, Release 3.2B) was printed March, 1985.

Publication Order Number 322-001550-101, (Change 1 to Revision 1, Release 3.2C) was printed December, 1985.

The MPX-32 Release 3.3 Technical Manual Volume I, Publication Order Number 322-001552-200, was printed December, 1986.

Publication Order Number 322-001552-300, (Revision 3, Release 3.4) was printed January, 1988.

Publication Order Number 322-001552-400, (Revision 3.4U03) was printed October, 1989.

Publication Order Number 322-001552-500, (Revision 3.5) was printed April, 1990

This manual contains the following pages:

Title page Copyright page Title page (A) v through xi/xii

Overview

1-1 through 1-2

H.ADA

Title page iii/iv 1-1/1-2

2-1 through 2-3/2-4

3-1/3-2

**H.ALOC**

Title page iii/iv 1-1/1-2 2-1 through 2-9/2-10

3-1/3-2

H.BKDM

Title page iii/iv 1-1/1-2 2-1/2-2

3-1 through 3-5/3-6

H.EXEC

Title page iii through vi 1-1 through 1-3/1-4 2-1 through 2-25/2-26 3-1 through 3-31/3-32

**H.EXSUB**

Title page iii and iv 1-1/1-2

2-1 through 2-26

# History

| H.FISE                                       | H.MVMT                    |

|----------------------------------------------|---------------------------|

| Title page                                   | Title page                |

| iii and iv                                   | iii/iv                    |

| 1-1 and 1-2                                  | 1-1/1-2                   |

| 2-1 through 2-11/2-12                        | 2-1 and 2-2               |

| H.IOCS                                       | H.PTRAC                   |

| Title page                                   | Title page                |

| iii through v/vi                             | iii and iv                |

| 1-1 through 1-3/1-4<br>2-1 through 2-15/2-16 | 1-1 and 1-2               |

| 3-1 through 3-27/3-28                        | H.REMM                    |

| •                                            | Title page                |

| H.IP?? and H.SVC?                            | iii and iv                |

| Title page                                   | 1-1 through 1-3/1-4       |

| iii/iv                                       | 2-1 through 2-6           |

| 1-1/1-2<br>2-1 through 2-3/2-4               | 3-1 through 3-23/3-24     |

| 3-1 through 3-16                             | H.REXS                    |

|                                              |                           |

| H.MDT                                        | Title page iii through vi |

| Title page                                   | 1-1 through 1-4           |

| iii/iv                                       | 2-1 through 2-24          |

| 1-1/1-2                                      | 3-1 through 3-8           |

| 2-1 through 2-5/2-6<br>3-1 through 3-12      | H.SURE                    |

| 5-1 unough 5-12                              |                           |

| H.MEMM                                       | Title page<br>iii/iv      |

| Title page                                   | 1-1/1-2                   |

| iii and iv                                   | 2-1/2-2                   |

| 1-1 and 1-2                                  |                           |

| 2-1 through 2-4                              | H.TAMM                    |

| 3-1 through 3-14                             | Tide page                 |

| H.MEMM2                                      | . iii/iv<br>1-1/1-2       |

| Title page                                   | 2-1 through 2-6           |

| iii/iv                                       | 3-1 through 3-8           |

| 1-1/1-2                                      |                           |

| 2-1 through 2-6                              | H.TSM                     |

| H.MONS                                       | Title page<br>iii/iv      |

| Title page                                   | 1-1/1-2                   |

| iii through v/vi                             | 2-1 through 2-8           |

| 1-1 through 1-3/1-4                          | 3-1 through 3-3/3-4       |

| 2-1 through 2-26                             |                           |

|                                              |                           |

#### H.VOMM

Title page iii and iv

1-1 through 1-3/1-4

2-1 through 2-8

3-1 through 3-29/3-30

#### System Macros Cross-Reference

A-1 through A-11

Title page (B)

#### H.DCSCI

Title page iii through v/vi 1-1/1-2

2-1 through 2-12

3-11/3-12

#### H.DCXIO

Title page

iii through vii/viii

1-1 through 1-3/1-4

2-1 through 2-12

3-1 through 3-15/3-16

#### H.DPXIO

Title page

iii through vii/viii

1-1 through 1-3/1-4

2-1 through 2-10

3-1 through 3-23/3-24

#### H.F8XIO

Title page

iii/iv

1-1/1-2

2-1 through 2-7/2-8

#### **H.GPMCS**

Title page

iii/iv

1-1 and 1-4

2-1 through 2-13/2-14

#### H.HSDG

Title page

iii/iv

1-1/1-2

2-1 through 2-10

3-1 through 3-6

#### H.IBLG

Title page

iii/iv

1-1/1-2

2-1 through 2-8

3-1 through 3-7/3-8

#### H.MDXIO

Title

iii and iv

1-1 through 1-2

2-1 through 2-7/2-8

3-1/3-2

#### H.MTSCI

Title page iii throuh v/vi

1-1/1-2

2-1 through 2-14

3-1 through 3-12

#### H.XIOS

Title page

iii through vi

1-1/1-2

2-1 through 2-11/2-12

3-1 through 3-7/3-8

4-1 through 4-3/4-4

· •

# **Documentation Conventions**

Conventions used in directive syntax, messages, and examples throughout the MPX-32 documentation set are described below.

## Messages and Examples

Text shown in this distinctive font indicates an actual representation of a system message or an example of actual input and output. For example,

VOLUME MOUNT SUCCESSFUL

or

TSM>!ACTIVATE MYTASK TSM>

#### Lowercase Italic Letters

In directive syntax, lowercase italic letters identify a generic element that must be replaced with a value. For example,

**\$NOTE** message

means replace message with the desired message. For example,

\$NOTE 10/12/89 REV 3

In system messages, lowercase italic letters identify a variable element. For example,

\*\*BREAK\*\* ON: taskname

means a break occurred on the specified task.

# **Uppercase Letters**

In directive syntax, uppercase letters specify the input required to execute that directive. Uppercase bold letters indicate the minimum that must be entered. For example,

\$ASSIGN lfc TO resource

means enter \$AS or \$ASSIGN followed by a logical file code, followed by TO and a resource specification. For example,

\$AS OUT TO OUTFILE

In messages, uppercase letters specify status or information. For example,

TERMDEF HAS NOT BEEN INSTALLED

## **Documentation Conventions**

# Brackets []

An element inside brackets is optional. For example,

means supplying an argument (arg) is optional.

Multiple items listed within brackets means enter one of the options or none at all. The choices are separated by a vertical line. For example,

```

$SHOW [CPUTIME|JOBS|USERS]

```

means specify one of the listed parameters, or none of them to invoke the default.

Items in brackets within encompassing brackets or braces can be specified only when the other item is specified. For example,

indicates if *eofs* is supplied as a parameter, FIL- or FILES- can precede the value specified.

Commas within brackets are required only if the bracketed element is specified. For example,

```

LIST [taskname][,[ownername][,pseudonym]]

```

indicates that the first comma is required only if ownername and/or pseudonym is specified. The second comma is required only if pseudonym is specified.

# Braces { }

Elements listed inside braces specify a required choice. Choices are separated by a vertical line. Enter one of the arguments from the specified group. For example,

[BLOCKED=

$$\{Y | N\}$$

]

means Y or N must be supplied when specifying the BLOCKED option.

# Horizontal Ellipsis ...

The horizontal ellipsis indicates the previous element can be repeated. For example,

means one or more parameters (par) separated by commas can be entered.

# **Vertical Ellipsis**

The vertical ellipsis indicates directives, parameters, or instructions have been omitted. For example,

```

$DEFM SI,ASSEMBLE,NEW,OP

.

.

.

$IFA %OP ASSM

```

means one or more directives have been omitted between the \$DEFM and \$IFA directives.

## Parentheses ()

In directive syntax, parentheses must be entered as shown. For example, (value)

means enter the proper value enclosed in parentheses; for example, (234).

# **Special Key Designations**

The following are used throughout the documentation to designate special keys:

```

<ctrl> control key

<ret> or <CR> carriage return/enter key

<tab> tab key

<br/>

```

When the <ctrl> key designation is used with another key, press and hold the control key, then press the other key. For example,

```

<ctrl>C

```

means press and hold the control key, then press the C.

# **Change Bars**

Change bars are vertical lines (|) appearing in the right-hand margin of the page for your convenience in identifying the changes made in MPX-32 Revision 3.5.

When an entire chapter has been changed or added, change bars appear at the chapter title only. When text within figures has changed, change bars appear only at the top and bottom of the figure box.

|  |   | Ó |

|--|---|---|

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   |   |

|  |   | O |

|  | • |   |

|  |   | • |

# 1 Technical Manual Volume II Overview

# 1.1 Using the Manual

The information in this manual is divided into two parts:

Module Descriptions

Handler Descriptions

Each module has a self-contained description that is prefaced by a tab. The following list includes the modules which are described in this manual:

H.ADA **H.ALOC H.BKDM** H.EXEC **H.EXSUB** H.FISE H.IOCS H.IP?? and H.SVC? H.MDT **H.MEMM** H.MEMM2 **H.MONS** H.MVMT **H.PTRAC** H.REMM H.REXS

Each module description has the following format as applicable:

Overview

H.SURE H.TAMM H.TSM H.VOMM

**Entry Points**

Subroutines

# **Using the Manual**

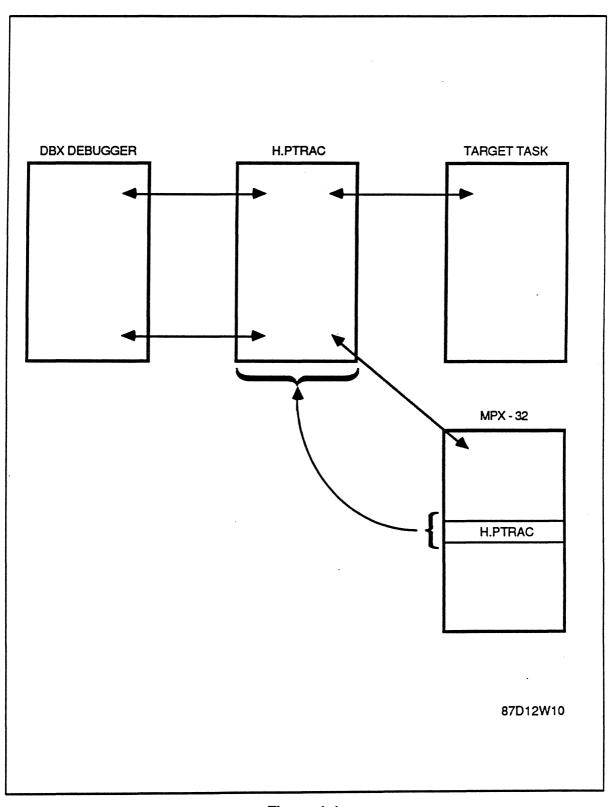

Each handler has a self-contained description that is prefaced by a tab. The following list includes the handlers which are described in this manual.

H.DCSCI

H.DCXIO

H.DPXIO

H.F8XIO

H.GPMCS

H.HSDG

H.IBLG

H.MDXIO

H.MTSCI

H.XIOS

Each handler description has the following format, as applicable:

Overview

Usage

Entry Points

Subroutines

To customize this manual to a particular system, remove the descriptions of modules or handlers that are not installed on the system.

Ada Programming Language

Support Module (H.ADA)

MPX-32 Technical Manual

Volume II

| • |   |  | • |

|---|---|--|---|

|   | · |  | 0 |

|   |   |  |   |

|   |   |  |   |

|   |   |  |   |

| • |   |  |   |

|   |   |  |   |

|   |   |  |   |

|   |   |  |   |

|   |   |  |   |

|   |   |  |   |

|   |   |  |   |

|   |   |  | O |

|   |   |  |   |

|   |   |  |   |

# **Contents**

|   |     | Pa                                                | ge |

|---|-----|---------------------------------------------------|----|

| 1 | H.A | ADA Overview                                      |    |

|   | 1.1 | General Information1                              | -1 |

|   | 1.2 | Ada Callable SVC Summary                          | -1 |

|   | 1.3 | Subroutine Summary                                | -1 |

| 2 | H.A | ADA - Ada Callable SVCs                           |    |

|   | 2.1 | SVC 2,X'A4' - Allocate Signal Stack Space         | -1 |

|   | 2.2 | SVC 2,X'A5' - Exit From Signal/Exception State    | -1 |

|   | 2.3 | SVC 2,X'A6' - Call Any SVC Service                |    |

|   | 2.4 | SVC 2,X'A7' - Return to Current Working Volume    |    |

| 3 | H.A | ADA Subroutines                                   |    |

|   | 3.1 | Subroutine S.ADA1 - Reserved                      | -1 |

|   | 3.2 | Subroutine S.ADA2 - Arithmetic Exception Handling |    |

|   | 3.4 | Subroutine S.ADA3 - Reserved                      |    |

|   | 3.4 | Subroutine S.ADA4 - Reserved                      | -1 |

•

# **1** H.ADA Overview

#### 1.1 General Information

The Ada Programming Language Support Module (H.ADA) provides support for the Ada environment on MPX-32. This support includes arithmetic exception processing and abort processing. All system services are channeled through this module to provide the Ada/MPX-32 interface.

# 1.2 Ada Callable SVC Summary

| SVC Number | Description                                    |

|------------|------------------------------------------------|

| 2,X'A4'    | allocate signal stack space                    |

| 2,X'A5'    | exit from signal/exception state               |

| 2,X'A6'    | call any SVC service                           |

| 2,X'A7'    | return to current working volume and directory |

# 1.3 Subroutine Summary

| Subroutine | Description                        |

|------------|------------------------------------|

| S.ADA1     | dispatch task                      |

| S.ADA2     | arithmetic exception handling      |

| S.ADA3     | dispatch control to abort receiver |

| S.ADA4     | end-action processing              |

|   |  |  |  | • |   |

|---|--|--|--|---|---|

|   |  |  |  | , |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

| , |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

|   |  |  |  |   | 0 |

|   |  |  |  |   |   |

|   |  |  |  |   |   |

# 2 H.ADA - Ada Callable SVCs

# 2.1 SVC 2,X'A4' - Allocate Signal Stack Space

This routine allocates space to an Ada task for arithmetic exception processing.

#### **Entry Conditions**

#### **Calling Sequence**

**SVC**

2.X'A4'

#### Registers

**R**3

logical address of stack

R4

number of bytes to use for stack

#### **Exit Conditions**

#### **Return Sequence**

M.RTRN

#### Registers

All registers unchanged.

#### Status

If CC1 is set, the address is invalid.

# 2.2 SVC 2,X'A5' - Exit From Signal/Exception State

This routine restores the task registers and PSD for proper return to the Ada task.

#### **Entry Conditions**

#### Calling Sequence

SVC

2,X'A5'

#### Registers

None

#### **Exit Conditions**

#### **Return Sequence**

M.RTRN

## SVC 2,X'A6' - Call Any SVC Service

# 2.3 SVC 2,X'A6' - Call Any SVC Service

This routine intercepts all MPX-32 SVCs called by Ada tasks. This routine checks for recursive SVC calls and verifies the destination address. The SVC is then executed from this routine with the return address inside the entry point. After the SVC is executed, the routine builds the condition codes and registers into the current TSA stack frame and returns via M.RTRN.

#### **Entry Conditions**

#### **Calling Sequence**

SVC 2.X'A6'

#### Registers

R1 address of an 8-word register block

R2 address of a 9-word out-register block with condition codes left justified

in the ninth word

R3 right 16 bits of the SVC instruction type and number

#### **Exit Conditions**

#### **Return Sequence**

M.RTRN

#### **Status**

CC1 if zero, no registers are affected

CC1 if one, R3 contains one of the following error codes:

| Code | Meaning                             |

|------|-------------------------------------|

| 1    | invalid in-register buffer address  |

| 2    | invalid out-register buffer address |

| 3    | recursive call to SVC               |

# 2.4 SVC 2,X'A7' - Return to Current Working Volume

This routine restores the Ada task environment before returning to the task.

#### **Entry Conditions**

#### **Calling Sequence**

**SVC**

2,X'A7';

#### **Registers**

R1

address of buffer to receive volume name

R2

address of buffer to receive directory name

#### **Exit Conditions**

#### **Return Sequence**

M.RTRN

#### **Status**

Normal return

if the volume and directory names are stored in the buffers

Error return

if either buffer contains an invalid address, then the volume and directory names are not stored in the buffer. No error is reported.

.

# **3** H.ADA Subroutines

#### 3.1 Subroutine S.ADA1 - Reserved

# 3.2 Subroutine S.ADA2 - Arithmetic Exception Handling

This subroutine uses the argument list in H.IPOF.

#### **Entry Conditions**

#### **Calling Sequence**

BL

S.ADA2

#### Registers

R1

address of H.IPOF's argument list

R3

TSA address

R4

Ada exception handler routines

R6

PSD is being built

#### **Exit Conditions**

#### **Return Sequence**

No return.

**LPSD**

address of Ada task exception handler

## 3.3 Subroutine S.ADA3 - Reserved

# 3.4 Subroutine S.ADA4 - Reserved

# Resource Allocator (H.ALOC) MPX-32 Technical Manual Volume II

# Contents

|   |      | e de la companya del companya de la companya del companya de la c | Page |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1 | H.A  | LOC Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|   | 1.1  | General Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1  |

|   | 1.2  | Entry Point Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|   | 1.3  | Subroutine Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-1  |

| 2 | H.A  | LOC Entry Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|   | 2.1  | Entry Point 1 - Construct TSA and DQE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-1  |

|   | 2.2  | Entry Point 2 - Task Activation Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1  |

|   | 2.3  | Entry Point 3 - Task Exit Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-1  |

|   | 2.4  | Entry Point 4 - Allocate Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-1  |

|   | 2.5  | Entry Point 5 - Deallocate Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-1  |

|   | 2.6  | Entry Point 6 - Allocate File/Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-1  |

|   | 2.7  | Entry Point 7 - Deallocate File/Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-3  |

|   | 2.8  | Entry Point 8 - Get Dynamic Extended Data Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-4  |

|   | 2.9  | Entry Point 9 - Free Dynamic Extended Indexed Data Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-4  |

|   | 2.10 | Entry Point 10 - Get Dynamic Task Execution Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-4  |

|   | 2.11 | Entry Point 11 - Free Dynamic Task Execution Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-4  |

|   | 2.12 | Entry Point 12 - Share Memory With Another Task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-5  |

|   | 2.13 | Entry Point 13 - Get Shared Memory (INCLUDE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-5  |

|   | 2.14 | Entry Point 14 - Free Shared Memory (EXCLUDE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-6  |

|   | 2.15 | Entry Point 15 - Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-6  |

|   | 2.16 | Entry Point 16 - Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-6  |

|   | 2.17 | Entry Point 17 - Allocate Disk File By Space Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-6  |

|   | 2.18 | Entry Point 18 - Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-7  |

|   | 2.19 | Entry Point 19 - Unlock and Dequeue Shared Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-7  |

|   | 2.20 | Entry Point 20 - Deallocate Memory Due to Swapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-8  |

|   | 2.21 | Entry Point 21 - Locate Allocated FPT/FAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-8  |

|   | 2.22 | Entry Point 99 - SYSGEN Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-9  |