# **6100 Disk Controller User's Guide**

PB6100-9001-02

.

7

~

1855 Barber Lane Milpitas, CA 95035, USA

System Industries has prepared this manual for use by System Industries personnel, licensees, and customers. The information contained herein is the property of System Industries and shall neither be reproduced in whole nor in part without prior written approval from System Industries.

System Industries reserves the right to make changes, without notice, to the specifications and materials contained herein, and shall not be responsible for any damages (including consequential) caused by reliance on the material as presented, including, but not limited to, typographical, arithmetic, and listing errors.

# LIMITED WARRANTY

**Disk Controller.** System Industries warrants that its products are free from defects in materials and workmanship and meet System Industries' performance specifications. The warranty period is ninety (90) days from the date of shipment to Buyer. This warranty is limited by the paragraphs below.

Return to Factory. If Buyer discovers a defect in a System Industries product covered by this agreement, Buyer's exclusive remedy is to ship the product back to System Industries' Milpitas factory where System Industries will, at its option, either repair or replace the product. This remedy applies if System Industries receives the returned product on or before the tenth day after the expiration of the warranty period and Buyer notifies System Industries of the defect before returning the product.

Cost to Buyer of Repairs or Replacement. Buyer must prepay freight charges to System Industries. System Industries will pay return freight to Buyer. There is no other charge for repair or replacement during the warranty period.

**Transferrable Disk Drive Warranty.** In addition to the foregoing warranty, System Industries also provides to Buyer the transferrable warranty, if any, provided to System Industries by the disk drive manufacturer. (NOTE: Neither System Industries nor disk drive manufacturers warrant read/write heads or subsequent damage sustained as a result of head/disk interference. Head/disk interference can be prevented by carefully following the disk drive and disk pack manufacturers' recommended operating and preventive maintenance procedures.)

**Limitation of Warranty and Liability.** The foregoing constitutes System Industries' entire warranty, expressed, implied, and/or statutory (except as to title), and states the full extent of System Industries' liability to Buyer or to any other party for any breach of such warranty and for damages, whether direct, special, incidental, or consequential. OTHER THAN AS EXPRESSLY PROVIDED IN THIS DOCUMENT, NO WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING ANY WARRANTY OF MER-CHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE MADE. NO EMPLOYEE, REPRESENTATIVE, OR AGENT OF SELLER HAS ANY AUTHORITY, EXPRESSED OR IMPLIED, TO ALTER OR TO SUPPLEMENT THE TERMS OF THIS WARRANTY.

# LIST OF EFFECTIVE PAGES

Changes, deletions, and additions to information in this manual are indicated by bars (1) in the margins. A bar by the page number indicates pagination rather than change of page content.

| PAGE                                                                                                                    | REVISION                                           | PAGE | REVISION | PAGE | REVISION |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|----------|------|----------|

| 1-1 through 1-4<br>2-1<br>3-1 through 3-3<br>4-1 through 4-10<br>5-1 through 5-3<br>A-1 through A-22<br>B-1 through B-3 | 02<br>02<br>02<br>02<br>02<br>02<br>02<br>02<br>02 |      |          |      |          |

|                                                                                                                         |                                                    |      |          |      |          |

|                                                                                                                         |                                                    |      |          |      |          |

|                                                                                                                         |                                                    |      |          | •    |          |

|                                                                                                                         |                                                    |      |          |      |          |

|                                                                                                                         |                                                    |      |          |      |          |

# **REVISION RECORD**

| REVISION<br>NUMBER | DATE               | DESCRIPTION                            | EO<br>NUMBER |

|--------------------|--------------------|----------------------------------------|--------------|

| 01<br>02           | 9/08/81<br>2/23/82 | Initial Release<br>Pages Affected: All | 1504         |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

|                    |                    |                                        |              |

# PREFACE

This manual contains sufficient information to enable the end user to install, test, and operate the System Industries 6100 Single Board Disk Controller.

The technical contents of this manual have been prepared based on the following assumptions of reader knowledge:

- 1. The reader should have a working knowledge of Digital Equipment Corporation PDP-11 processor hardware.

- 2. The reader should be familiar with disk structures and hardware.

- 3. The reader should be familiar with standard installation, power, grounding and peripheral cabling procedures.

The information in this manual is presented in five major sections. The contents of these sections are as follows:

| Section 1.0 | System Overview, describes 6100 board features, capabilities, and system configurations supported.              |

|-------------|-----------------------------------------------------------------------------------------------------------------|

| Section 2.0 | Physical Description, describes and illustrates the 6100 Controller PCB.                                        |

| Section 3.0 | Functional Description, describes and illustrates the functional operation of the 6100 board.                   |

| Section 4.0 | Installation, describes and illustrates the procedures required to install the 6100 board and cable the drives. |

| Section 5.0 | Diagnostics, describes the diagnostics compatible with the 6100 Controller.                                     |

Other publications applicable to the 6100 Controller are as follows:

| <b>Publication Number</b> | Title                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------|

| N/A                       | PDP-11 Processor Handbook                                                             |

| EK-RM023-UG-002           | DEC® RM02/3 Disk Subsystem User's Guide                                               |

| 64712400                  | CDC Flat-Cable Interface Specification for SMD, MMD, and CMD Families                 |

| 64709300                  | CDC Product Specification for the Flat-Cable Interface Storage<br>Module Drive Family |

| B03P-4580-0100B           | Fujitsu M228X Fixed Disk Unit Customer Engineering Manual                             |

| 83322200                  | CDC Storage Module Drive BK4XX, BK5XX Hardware Reference<br>Manual                    |

| 83322320                  | CDC Storage Module Drive BK6XX, BK7XX Hardware Reference<br>Manual                    |

| PB9901-9001-01            | System Industries Disk Drive User's Guide                                             |

DEC is a trademark of Digital Equipment Corporation.

# **TABLE OF CONTENTS**

| 1.0        | SYSTEM OVERVIEW         1.1       Features         1.2       Configuration         1.2.1       Software Compatibility         1.2.2       Drive Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-1<br>1-1<br>1-1<br>1-1<br>1-2                                                                                     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 2.0        | PHYSICAL DESCRIPTION         2.1       Power Requirements         2.2       Drive Interface         2.2.1       A-Cable         2.2.2       B-Cable         2.3       Computer Interface         2.3.1       UNIBUS Interface         2.3.2       Device, Interrupt, and Address Configuration Switches                                                                                                                                                                                                                                                                                            | 2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1                                                         |

| <b>3.0</b> | FUNCTIONAL DESCRIPTION         3.1       Priority Levels         3.2       Overlapped Seeks         3.3       Dual Port Drive Compatibility         3.4       Contiguous Transfers         3.5       RPS Look-Ahead         3.6       Search Command         3.7       Error Correction         3.8       Controller Registers                                                                                                                                                                                                                                                                     | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-3                                                         |

| 4.0        | INSTALLATION         4.1 Visual Inspection         4.2 Switch Settings         4.2.1 DMA Throttle Count Switch         4.2.2 Register Set Address Switch (CS1)         4.2.3 Drive Type Switches         4.2.4 Interrupt Vector Switch         4.3 Installation of the Controller Board         4.3.1 Index and Sector Jumpers         4.3.2 Priority Jumpers         4.3.3 Non-Processor Grant (NPG) Jumpers         4.4 Physical Installation of 6100 Board         4.5 Drive Sector Count         4.6 Index and Sector Signal Configuration         4.7 Disk Drive Cabling         4.8 Power-up | 4-1<br>4-1<br>4-3<br>4-3<br>4-3<br>4-4<br>4-5<br>4-5<br>4-5<br>4-5<br>4-5<br>4-7<br>4-7<br>4-7<br>4-7<br>4-9<br>4-9 |

| 5.0        | DIAGNOSTICS         5.1       Internal Diagnostics         5.2       System Industries Disk Exerciser         5.3       DEC Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-1<br>5-1<br>5-1<br>5-3                                                                                            |

|            | ENDIX A Instructions and Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A-1<br>B-1                                                                                                          |

# **LIST OF FIGURES**

.

| Figure |                            |

|--------|----------------------------|

| 1-1    | Disk Drive Configuration   |

| 1-2    | Dual Port Configuration    |

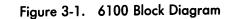

| 3-1    | 6100 Block Diagram         |

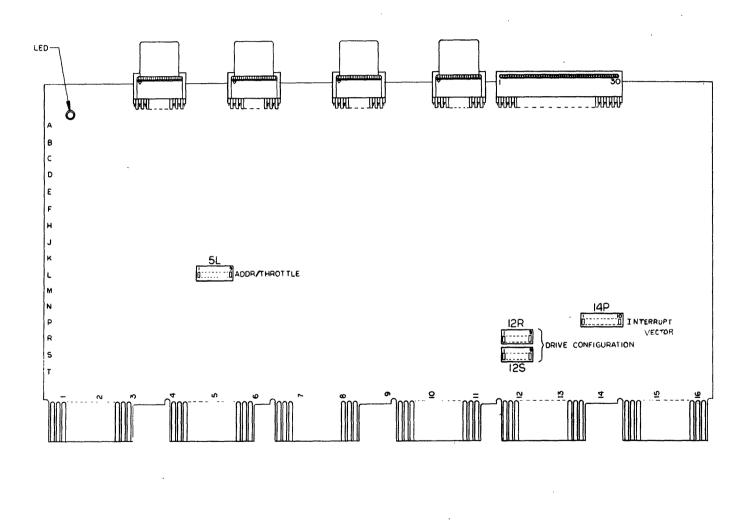

| 4-1    | Controller Switches        |

| 4-2    | Priority Jumpers           |

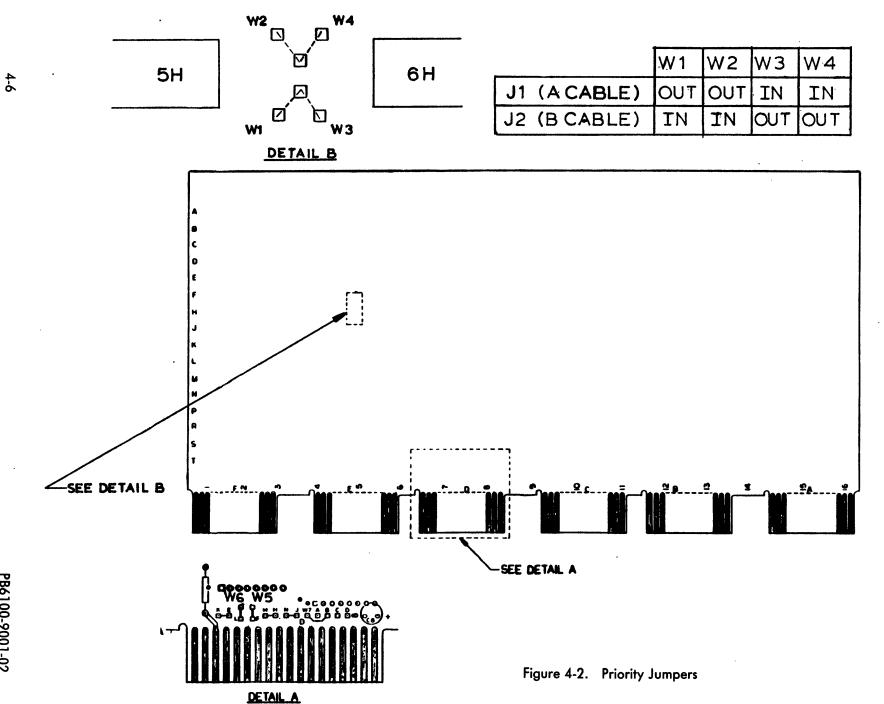

| 4-3    | NPG Jumper Location        |

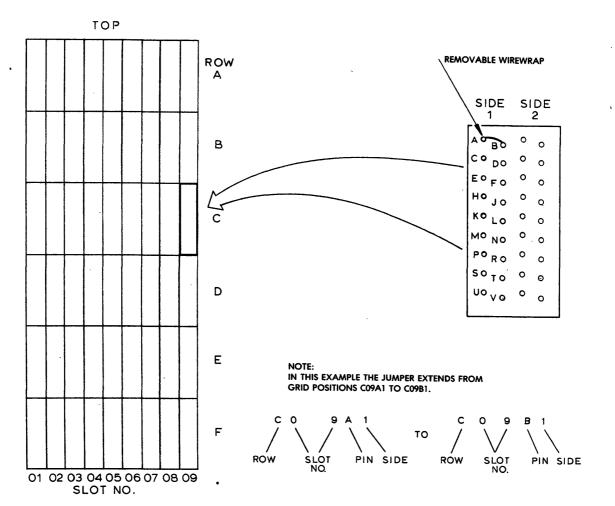

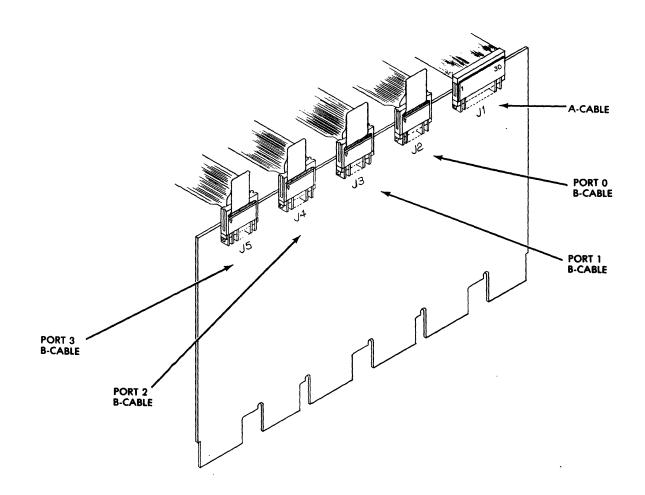

| 4-4    | Controller Cable Placement |

# **LIST OF TABLES**

| Table |                                           |

|-------|-------------------------------------------|

| 1-1   | Drive Configurations                      |

| 3-1   | Registers and UNIBUS Addresses            |

| 4-1   | 6100 Switches                             |

| 4-2   | Throttle Count Switch Settings            |

| 4-3   | Register Set Address Switch Settings      |

| 4-4   | Drive Switches                            |

| 4-5   | Drive Type Switch Settings                |

| 4-6   | Standard Interrupt Vector Switch Settings |

| 4-7   | Priority Jumper Settings                  |

.

.

# **1.0 SYSTEM OVERVIEW**

The System Industries 6100 Controller is a single board disk controller that allows for the exact emulation of the DEC PDP-11 series RM02/03/05 disk drive subsystem.

The controller interfaces to the PDP-11 UNIBUS by plugging into any standard, small peripheral controller hex interface slot of the backplane or an expansion box.

The controller allows for the control of up to four industry standard storage module drives .

### 1.1 Features

The controller includes the following standard features:

- DEC operating system software transparency

- DEC RM03 and RM05 media compatibility

- Four sector static RAM data buffering (2048 bytes)

- Header verification and CRC checking

- Overlapped seeks on all attached drives

- Dual port drive support

- Contiguous sector data transfers up to 64K words

- RPS look ahead

- Search command for disk rotational position synchronization

- Switch selectable device and vector addressing

- Switch selectable burst data error correction

- Internal microprocessor, data RAM, and register file tests

- DEC diagnostic compatibility

### 1.2 Configuration

The controller can be configured to support multiple disk drives by daisy-chaining. The controller can control up to four physical drives or eight logical drives. The drives currently supported by this controller are the SI 9762, 9766, and 9775, and SI 9784. The controller, when used with these drives, is software transparent.

### **1.2.1 Software Compatibility**

The Controller is software transparent when used as an RM03 with an SMD 80 megabyte disk drive or when used as an RM05 with an SMD 300 megabyte disk drive. The controller is also software transparent when used as RM03s with a 160 megabyte disk drive configured as two logical 80 megabyte disk drives or as RM05s with a 675 megabyte disk drive configured as two 300 megabyte disk drives.

The controller maintains transparent software compatibility when used with the following DEC operating systems:

- RSX-11M PLUS

- RSX-11M

- RSX-11D/IAS

- RSTS/E

UNIBUS is a trademark of Digital Equipment Corporation.

## **1.2.2 Drive Configurations**

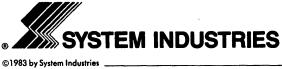

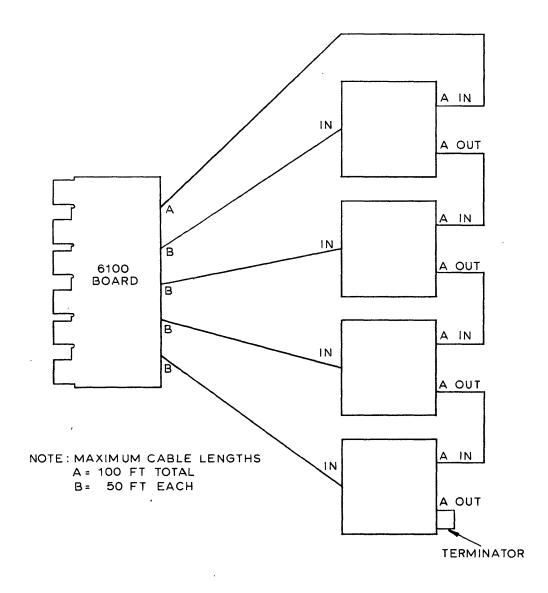

The disk drive interface conforms to standard flat cable specifications for SMD drives of Control Data Corporation and System Industries. The SI 9775 drive may emulate two 9766 drives and the SI 9784 may emulate two SI 9762 drives. Table 1-1 lists the drive configurations supported. Figure 1-1 illustrates the disk/controller cabling. Figure 1-2 illustrates cabling for dual port configurations.

| DRIVE<br>TYPE | CAPACITY<br>MBYTE | DIRECT/<br>MAPPED | MAX. NUMB | ER OF UNITS<br>PHYSICAL |

|---------------|-------------------|-------------------|-----------|-------------------------|

| SI 9762       | 80                | Direct            | 4         | 4                       |

| SI 9784       | 160               | Direct            | 4         | 4                       |

| SI 9784       | 160               | Mapped<br>(2×80)  | 8         | 4                       |

| SI 9766       | 300               | Direct            | 4         | 4                       |

| SI 9775       | 675               | Mapped<br>(2×300) | 8         | 4                       |

Table 1-1

Drive Configurations

ĺ

Figure 1-1. Disk Drive Configuration

.

Figure 1-2. Dual Port Configuration

•

# 2.0 PHYSICAL DESCRIPTION

The controller is a standard, 16 by 9-inch, single hex-slot board, incorporating a unique high-speed bipolar microprocessor design that exactly emulates the DEC PDP-11 RM02 Controller. The board contains four DIP switches used for such functions as device and vector addressing. The board also contains one LED that is used for internal diagnostics. Refer to Section 4.0 for installation, cabling, and switch procedures.

### 2.1 **Power Requirements**

The following voltages are required to operate the controller.

+ 5 Vdc ±5% @ 11 Amps Maximum

-15 Vdc  $\pm 5\%$  @ 0.7 Amps Maximum

# 2.2 Drive Interface

The disk drive interfaces to the controller board via two flat cables referred to as cables A and B.

# 2.2.1 A-Cable

The A-cable is a 60-pin twisted pair flat cable that connects the first physical disk drive to the controllerboard and is additionally used to daisy-chain disk drives.

### 2.2.2 B-Cable

The B-cable is a 26-pin ribbon flat cable that is radially connected from each disk drive to one of the four B-cable connectors on the controller board.

### 2.3 Computer Interface

The following subsections describe the controller interface to the PDP-11 computer.

### 2.3.1 UNIBUS Interface

The controller interfaces to the PDP-11 UNIBUS by plugging into any standard DEC Small Peripheral Controller (SPC) interface slot of the PDP-11 backplane.

### 2.3.2 Device, Interrupt, and Address Configuration Switches

Device, interrupt vector, and register group addresses are all switch selectable. By setting these switches the controller can be configured to allow for the emulation and mapping of several devices, the establishment of the device interrupt vector, and the starting address of the controller's control register group.

1

# 3.0 FUNCTIONAL DESCRIPTION

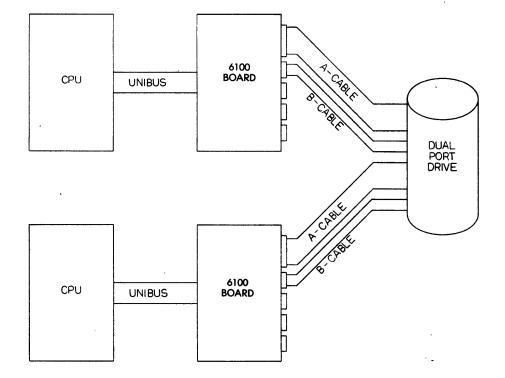

This section provides a brief description of the functional operation of the controller features. Figure 3-1 shows a simplified functional block diagram of the controller.

# 3.1 **Priority Levels**

The controller's priority level is jumper selectable. Priority levels enable the controller to generate a processor interrupt request on one of the bus request levels, BR4 through BR7. Availability of the bus request is determined by receipt of a corresponding bus grant level, BG4 through BG7. Section 4.0 describes the priority level jumpering procedure. The controller is preset at a priority level of 5.

# 3.2 Overlapped Seeks

Overlapped seeks may be performed on all attached drives. This capability is provided by maintaining separate registers in the register file for each logical drive. Seeks are issued as they are received if a data transfer is not currently active on any drive. When a data transfer is in progress, a seek command to another drive is issued when the end of a cylinder is detected.

# 3.3 **Dual Port Drive Compatibility**

The controller can support dual port drives. This support is designed to be software transparent.

### 3.4 Contiguous Transfers

Contiguous transfers of sector data allow up to 64K bytes to be transferred in response to a single drive command.

### 3.5 RPS Look-Ahead

The RPS feature is compatible with DEC's look-ahead feature. The controller maintains a current sector count for each disk drive attached to it, this feature provides the programmer with a means of optimizing disk accesses by minimizing rotational delay.

### 3.6 Search Command

The search command is compatible with the DEC RMOX search, and combines a seek with a search for the desired sector. This feature is used by the software to synchronize the disk rotational positioning with the issuing of data transfer commands.

### 3.7 Error Correction

Burst and data error correction is accomplished by the use of the AMD Z8065 Burst Error Processor (BEP). The BEP detects all errors and allows for correction of error bursts up to 11 bits in length. The error information is loaded into the ECC registers (RMEC1 and RMEC2) and the correction can be made by the system software.

(SIMPLIFIED VERSION)

FUNCTIONAL DESCRIPTION

6100 USER'S GUIDE

3-2

1

An uncorrectable error is defined as any error field larger than the 11-bit burst. If an uncorrectable error is detected, a bit is set in the error register (RMER1) and the data transfer operation is aborted. The maximum delay time for correctable data errors is 2 milliseconds.

The controller's attempt to correct a burst data error is transparent to the operating system when the ECC switch (location 5L, switch 2) is set. Refer to Section 4.2.4 for a description of these switch settings.

### **3.8 Controller Registers**

The controller communicates with the system's disk driver program via 19 registers located on the controller. The contents of these registers may be accessed by their UNIBUS address. A detailed description of the controller registers is contained in Appendix A and a register summary is contained in Appendix B. The registers and their UNIBUS addresses are shown in Table 3-1.

| Register |                        | UNIBUS Address |

|----------|------------------------|----------------|

| RMCS1    | (Control and Status 1) | 776700         |

| RMWC     | (Word Count)           | 776702         |

| RMBA     | (UNIBUS Address)       | 776704         |

| RMDA     | (Disk Address)         | 776706         |

| RMCS2    | (Control and Status 2) | 776710         |

| RMDS     | (Drive Status)         | 776712         |

| RMER1    | (Error 1)              | 776714         |

| RMAS     | (Attention Summary)    | 776716         |

| RMLA     | (Look-Ahead)           | 776720         |

| RMDB     | (Data Buffer)          | 776722         |

| RMMR1    | (Maintenance 1)        | 776724         |

| RMDT     | (Drive Type)           | 776726         |

| RMSN     | (Serial Number)        | 776730         |

| RMOF     | (Offset)               | 776732         |

| RMDC     | (Desired Cylinder)     | 776734         |

| RMHR     | (Holding)              | 776736         |

| RMMR2    | (Maintenance 2)        | 776740         |

| RMER2    | (Error 2)              | 776742         |

| RMEC1    | (ECC Position)         | 776744         |

| RMEC2    | (ECC Pattern)          | 776746         |

Table 3-1 Registers and UNIBUS Addresses

# 4.0 INSTALLATION

This section describes the procedures required to install, cable, and set the four DIP switches on the controller. This section also contains procedures that may be required for modification of the PDP-11 and SMD disk drives.

### 4.1 Visual Inspection

Before attempting to install the controller board or perform cabling operations, a visual inspection of the controller board, cables, disk drives, and PDP-11 backplane must be performed to determine the following:

- All components on the controller board are in place, secure, and not cracked or broken

- Pin connections for A- and B-cables are not bent or broken

- Any jumper wires installed on the board are connected properly and securely

- A- and B-cables are not bent or cut, and pin receptacles are secure

- Disk drive(s) is (are) configured for 32 sectors

- Terminators are removed from all but the last disk drive

- Index and sector jumpers are set for B-cable

- Bus grant continuity jumper board is removed from the controller SPC slot

### 4.2 Switch Settings

The controller board has four DIP switches that must be checked and/or set to conform to specific installation requirements. The switch locations on the board are shown in Figure 4-1. Table 4-1 lists the switch name and type.

| SWITCH           | ТҮРЕ                                                  | BOARD LOCATION |

|------------------|-------------------------------------------------------|----------------|

| Throttle Count   | Two positions (SW1-SW2) of<br>9-position DIP switch   | 5L             |

| Starting Address | Seven positions (SW3–SW9) of<br>9-position DIP switch | 5L             |

| Drive Type       | Two 8-position DIP switches                           | 12R, 12S       |

| Interrupt Vector | One 10-position DIP switch                            | 14P            |

#### Table 4-1 Controller Switches

.

# Figure 4-1. Controller Switches

6100 USER'S GUIDE

PB6100-9001-02

### 4.2.1 DMA Throttle Count Switch

The throttle count switch determines how many words of data the controller will transfer, per NP request, onto the UNIBUS. The throttle count only uses switches 1 and 2 of the 9-position DIP switch at grid location 5L. Table 4-2 shows the throttle count switch settings.

| SW1 | SW2 | DESCRIPTION                                                                                                                       |

|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| OFF | OFF | Throttle burst rate of 2 words per NP request. Simulates SACK.                                                                    |

| OFF | ON  | Throttle at microprogram control.                                                                                                 |

| ON  | OFF | Throttle at burst rate until SACK. If a higher priority request is received, the controller relinquishes the bus and asserts NPR. |

| ON  | ON  | Invalid setting.                                                                                                                  |

| Table 4-2 Throttle Count Switch Settings |

|------------------------------------------|

|------------------------------------------|

Switch **ON**=0=closed Switch **OFF**=1=open

### 4.2.2 Register Set Address Switch (CS1)

The register set address switch determines the starting address of the controller register group. The register set address switch uses switches 3 through 9 of the same DIP switch used for the throttle count switch. Table 4-3 describes the standard switch settings for normal operation.

| REGISTER SET<br>STARTING ADDRESS | 12<br>SW3 | 11<br>SW4 | 10<br>SW5 | 09<br>SW6 | 08<br>SW7 | 07<br>SW8 | 06*<br>SW9 |

|----------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|------------|

| 776700<br>OR                     | OFF       | OFF       | OFF       | ON        | OFF       | OFF       | OFF        |

| 776300                           | OFF       | OFF       | OFF       | ON        | ON        | OFF       | OFF        |

Table 4-3

Register Set Address Switch Settings

NOTE: Selectable address range is 760000 to 777700

Switch ON=0=closed Switch OFF=1=open

\*UNIBUS address

### 4.2.3 Drive Type Switches

Two 8-position DIP switches (at grid locations 12R and 12S) are used to determine the drive type emulation and mapping. Table 4-4 illustrates which switches correspond to which physical drive numbers, and Table 4-5 illustrates the drive types configured by those switches. Each of the four drive type switch settings is polled, regardless of whether or not a physical drive is attached.

#### NOTE

In a mapped or combined configuration, the logical drive numbers of some drives will not be the same as their physical drive numbers.

#### Table 4-4 Drive Switches

| DRIVE NO. | SWITCHES       |  |  |  |  |

|-----------|----------------|--|--|--|--|

| 0         | 12R 5–8        |  |  |  |  |

| 1         | 12R 1-4        |  |  |  |  |

| 2         | <u>12</u> 5 –8 |  |  |  |  |

| 3         | 12S 1-4        |  |  |  |  |

Table 4-5 Drive Type Switch Settings

|   |     | SW  | ІТСН |     |                   |

|---|-----|-----|------|-----|-------------------|

|   | 8   | 7   | 6    | 5   |                   |

| _ | 4   | 3   | 2    | 1   | EMULATION/MAPPING |

|   | OFF | ON  | ON   | ON  | RM03 80 Direct    |

|   | OFF | ON  | ON   | OFF | RM03 160 Mapped   |

|   | OFF | ON. | OFF  | ON  | RM03 160 Direct   |

|   | OFF | ON  | OFF  | OFF | RM03 300 Direct   |

|   | OFF | OFF | ON   | ON  | RM03 675 Mapped   |

|   | ON  | ON  | ON   | ON  | RM05 80 Direct    |

|   | ON  | ON  | ON   | OFF | RM05 160 Mapped   |

|   | ON  | ON  | OFF  | ON  | RM05 160 Direct   |

|   | ON  | ON  | OFF  | OFF | RM05 300 Direct   |

|   | ON  | OFF | ON   | ON  | RM05 675 Mapped   |

**NOTE:** All other codes are reserved.

### 4.2.4 Interrupt Vector Switch

The interrupt vector switch is a 10-position DIP switch (located at grid location 14P) that sets the 3-digit octal word of the interrupt vector location. The standard interrupt vector location is 254 octal. Other disk interrupt vectors are defined in the DEC PDP-11 Peripherals Handbook. Table 4-6 shows the switch setting for the standard and alternate interrupt vectors.

| SWITCH                                                                     | 1        | 2    | 3     | 256<br>4 | 128<br>5 | 64<br>6 | 32<br>7 | 16<br>8 | 8<br>9 | 4<br>10 |

|----------------------------------------------------------------------------|----------|------|-------|----------|----------|---------|---------|---------|--------|---------|

| 254 Octal                                                                  | Reserved | ECC* | Spare | ON       | OFF      | ON      | OFF     | ON      | OFF    | OFF     |

| 150 Octal                                                                  | Reserved | ECC* | Spare | ON       | ON       | OFF     | OFF     | ON      | OFF    | ON      |

| Switch ON=0=closed<br>Switch OFF=1=open                                    |          |      |       |          |          |         |         |         |        |         |

| *Internal ECC Correction= <b>OFF</b><br>External ECC Correction= <b>ON</b> |          |      |       |          |          |         |         |         |        |         |

Table 4-6

Standard Interrupt Vector Switch Settings

## 4.3 Installation of the Controller Board

The controller board can be installed in any PDP-11 Small Peripheral Controller (SPC) backplane hex slot. The following procedures should be followed to ensure proper installation.

# CAUTION

Be sure to power down the system before continuing with the installation procedure.

#### 4.3.1 Index and Sector Jumpers

The controller is normally configured to receive index/sector signals on the B-cable. For convenience under unusual circumstances, one (1) drive, and only one, can be allowed to transmit index/sector signals, via J-1 on the A-cable. In this case, that drive's B-cable must be connected to J-2 for proper controller operation. Additional drives whose B-cables are connected to J-3, J-4, or J-5 must have index/sector signals transmitted on their respective B-cables. The jumpers which allow index/sector selection between J-1 and J-2 are labeled W1 and W2 for J-2 and W3 and W4 for J-1. The jumpers will be either in W1, W2 or in W3, W4, but not both. They are located at 5H. See Figure 4-2.

### 4.3.2 Priority Jumpers

Before physically installing the controller board, determine the priority level to be established. The controller board's standard priority level is set at 5. This priority level is etched on the PCB board (BR5 and BG5) at the factory. To change the priority level, the preset board etches must be cut and jumper wires installed (e.g., to change to a setting of BG4 from a setting of BG5, cut etches at W5-F, W6-L, and E-K, and add jumpers at W5-E, W6-K, and F-L). Refer to Table 4-7 for BR-BG priority jumper settings. Refer to Figure 4-2 for an illustration of jumper installation.

PB6100-9001-02

INSTALLATION

| LEVEL | JUMPE |      |     | <u> </u> |     |

|-------|-------|------|-----|----------|-----|

| BR4   | W7-A  |      |     |          |     |

| BR5*  | W7-B  |      |     |          |     |

| BR6   | W7-C  |      |     |          |     |

| BR7   | W7-D  |      |     |          |     |

| BG4   | W5-E  | W6-K | F-L | H-M      | J-N |

| BG5*  | W5-F  | W6-L | E-K | H-M      | J-N |

| BG6   | W5-H  | W6-M | F-L | E-K      | J-N |

| BG7   | W5-J  | W6-N | F-L | E-K      | H-M |

\*BR5 - BG5 is standard feature and etched on PCB.

### 4.3.3 Nonprocessor Grant (NPG) Jumpers

The NPG *IN* signal on the wirewrap side of the PDP-11 backplane and the NPG *OUT* signal must not be jumpered together in the slot occupied by the controller board. Normally PDP-11 backplanes come with jumper wires installed. Similarly, all other NPG *IN* and NPG *OUT* pins must be connected through wire jumpers in all empty SPC slots. Figure 4-3 shows the pin location for the wirewrap side of the backplane.

When a DMA device (e.g., the 6100 Controller) is installed in an SPC slot of a backplane (type DD11-B or later), the wire from C01A1 to C01B1 must be removed from the slot.

#### 4.4 Physical Installation of Controller Board

Before the controller board can be placed in the SPC slot, it may be necessary to remove the small board (bus grant continuity jumper board) in the slot. When all the foregoing procedures have been completed, the board may be physically installed. The board can be placed in any available SPC slot. The board is installed by pressing it firmly into the selected SPC slot with the component side facing in the same direction as the components on the other boards.

#### 4.5 Drive Sector Count

The controller requires that the drives be set up for 32 sectors. Refer to the System Industries Disk Drive User's Guide for drives sector information.

#### 4.6 Index and Sector Signal Configuration

The controller requires the continuous presence of drive index/sector signals on the B-Cable. Refer to the System Industries Disk Drive User's Guide for correct drive configuration for continuous (nongated) index/sector signals on the B-Cable.

Figure 4-3. NPG Jumper Location

6100 USER'S GUIDE

### 4.7 Disk Drive Cabling

Disk drives must be cabled correctly to insure proper transfer and retrieval of data. Figure 4-4 illustrates the correct placement of the A- and B-cables on the controller board. This subsection details the procedures necessary to connect System Industries drives in a daisy-chain configuration.

### NOTE

When installing the cables, take care to ensure that pin one (1) on the controller is aligned through the cable(s) to pin one (1) on the drive(s).

In a daisy-chain configuration, each drive communicates to the controller through a discrete B-cable and a common A-cable. The A-cable is attached to connector J1. The free end of this cable is then attached to the first drive in the daisy-chain. One is connected between connector J2 on the controller board and the first drive in the daisy-chain. Additional B-cables are attached to the controller on connectors J3 through J5. The drive connected to J2 is designated as drive 0 and drives connected to J3 through J5 are designated as drives 1 through 3 respectively. The free end of each cable is attached to the disk drive as specified for each drive type.

#### NOTE

The total A-cable length must not exceed 100 feet and the maximum length of each B-cable must not exceed 50 feet.

Refer to System Industries Disk Drive User's Guide for cabling information for specific System Industries drives.

#### 4.8 Power-Up

The system is now ready to be powered up. Refer to the PDP-11 Processor and System Industries Disk Drive manuals for exact power-up procedures.

# 5.0 DIAGNOSTICS

The controller has internal diagnostics that are compatible with the DEC diagnostics listed in this section.

### 5.1 Internal Diagnostics

The controller contains in-PROM internal diagnostics. After power-up, the controller performs the following diagnostic tests:

- 1. Microprocessor self-test

- 2. Data RAM test

- 3. Register file test

During testing, the LED on the controller board is on. If the diagnostic tests indicate no failures, the controller turns the LED off. If there is a failure, the LED remains on, indicating a controller error.

### 5.2 System Industries Disk Exerciser

The System Industries disk exerciser program is EXOR11. This program is on a magnetic tape and is provided by System Industries with every 6100 Controller. When the program is loaded on the system, the title

### TITLE JIMZAP — DISC EXERCISER V1.6 EXOR11 6 - AUG - 1981

appears followed by the first program prompt. Possible prompts and responses are described in this section. The operator responds to the prompts by entering an octal number followed by a carriage return.

| PROMPT                     | RESPONSE                                                                                                                                                                                              |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FILL COUNT                 | 10 for CRT, 0 or 2 for teletype (default is 4)                                                                                                                                                        |

| STATUS                     | Beginning address of status registers (default is 176700)                                                                                                                                             |

| VECTOR                     | Interrupt vector number (default is 254)                                                                                                                                                              |

| ENTER TEST<br>TO BE RUN    | There are seven tests:<br>bit 0 = format<br>bit 1 = read entire disk<br>bit 2 = read/write<br>bit 3 = random read/write<br>bit 4 = seek<br>bit 5 = interrupt<br>all tests = 77 (default is all tests) |

| ENTER<br>PATTERN<br>NUMBER | This prompt is printed only when read/write test is<br>selected. There are five patterns:<br>0 = address of buffer location<br>1 = 133333<br>2 = 125252<br>3 = 177777<br>4 = 000000 (default is 0)    |

| PROMPT                          | RESPONSE                                                                                                                                                                                                                                                                                                                |              |            | ······································ |  |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|----------------------------------------|--|--|--|--|--|

| ENTER RUN<br>PARAMETERS         | The run parameters are:<br>bit $0 = $ short pass<br>bit $1 = $ do not type errors<br>bit $2 = $ format every pass<br>bit $3 = $ halt on error<br>bit $4 = $ loop on error<br>bit $5 = $ do not type test names or pass numbers<br>bit $6 = $ timeout switch<br>(default is 0, format first pass and test all cylinders) |              |            |                                        |  |  |  |  |  |

| enter<br>Number of<br>Cylinders | This prompt is printed only when short pass is selected.<br>Enter number of cylinders to test. (NO DEFAULT)                                                                                                                                                                                                             |              |            |                                        |  |  |  |  |  |

| enter<br>Starting<br>Cylinder   | This prompt is only printed when short pass is selected.<br>Enter starting cylinder number. (NO DEFAULT)                                                                                                                                                                                                                |              |            |                                        |  |  |  |  |  |

| disks to<br>Test                | There are seven                                                                                                                                                                                                                                                                                                         | i possible u | nits, ente | r the value number:                    |  |  |  |  |  |

|                                 | Unit                                                                                                                                                                                                                                                                                                                    | # Bit #      | Value      |                                        |  |  |  |  |  |

|                                 | . 0                                                                                                                                                                                                                                                                                                                     | 0            | 1          |                                        |  |  |  |  |  |

|                                 | 1                                                                                                                                                                                                                                                                                                                       | 1            | 2          |                                        |  |  |  |  |  |

|                                 | 2                                                                                                                                                                                                                                                                                                                       | · 2          | 4          |                                        |  |  |  |  |  |

|                                 | 3                                                                                                                                                                                                                                                                                                                       | 3            | 10         |                                        |  |  |  |  |  |

|                                 | 4                                                                                                                                                                                                                                                                                                                       | . 4          | 20         |                                        |  |  |  |  |  |

|                                 | 5                                                                                                                                                                                                                                                                                                                       | 5            | 40         |                                        |  |  |  |  |  |

|                                 | 6                                                                                                                                                                                                                                                                                                                       | 6            | 100        |                                        |  |  |  |  |  |

|                                 | 7                                                                                                                                                                                                                                                                                                                       | 7            | 200        |                                        |  |  |  |  |  |

|                                 | (NO DEFAULT)                                                                                                                                                                                                                                                                                                            |              |            |                                        |  |  |  |  |  |

The operator always has control of the CPU from the console. The following commands are available.

| CTRL | B = Boot (for boot options type "?") |

|------|--------------------------------------|

| CTRL | C = Restart at level 0               |

| CTRL | D = Restart at level 0               |

| CTRL | E = Restart at level 2               |

| CTRL | F = Print cylinder, head, and sector |

| CTRL | H = Toggle halt on error             |

| CTRL | L = Toggle loop on error             |

| CTRL | N = Print current ECIB               |

| CTRL | O = Toggle print error messages      |

| CTRL | P = Print the ECIB table             |

|      |                                      |

CTRL Q = Proceed CTRL R = Restart with same arguments CTRL S = Halt CTRL T = Toggle timeout flag CTRL U = Toggle print pass number + test titles CTRL X = Print all registers

### **RESTART ADDRESSES**

1600 = Same as CTRL C 1604 = Same as CTRL R 1610 = Same as CTRL B

### 5.3 **DEC Diagnostics**

The controller is compatible with the following DEC formatters and diagnostics for 80 and 160 Mbyte (mapped) drives without modification:

| PROGRAM NAME | EMULATION | DESCRIPTION              |

|--------------|-----------|--------------------------|

| CZRMACO      | RM03/RM02 | Formatter                |

| CZRMBBO      | RM03/RM02 | Performance Exerciser    |

| CZRMECO      | RM03/RM02 | Functional Test 3, 2     |

| CZRMFBO      | RM03/RM02 | Extended Drive Test      |

| CZRMIBO      | RM03/RM02 | Drive Compatibility Test |

The controller is compatible with the CZRMCB2 Functional Test 1 for RM03/RM02 with the following changes:

| TEST | LOCATION | IS   | CHANGE TO |

|------|----------|------|-----------|

| 11   | 12036    | 4    | 137       |

|      | 12040    | 240  | 13110     |

| 36   | 24212    | 4    | 137       |

|      | 24214    | 240  | 24776     |

| 41   | 26600    | 1007 | 407       |

| 53   | 32260    | 4    | 137       |

|      | 32262    | 240  | 32646     |

| 61   | 35570    | 1406 | 406       |

| 64   | 37002    | 4    | 137       |

|      | 37004    | 240  | 37362     |

# **APPENDIX A**

A register bit followed by an asterisk indicates a bit whose function differs from DEC definitions. Registers are referred to by their name and UNIBUS address.

# Control and Status 1 Register (RMCS1) (776700)

RMCS1 register is used to store the current disk command function code and operational status of the controller.

| 15 | 14  | 13   | 12 | _11 | 10   | 09  | 08 | 07  | 06 | 05 | 04 | 03 | 02   | 01         | 00 |

|----|-----|------|----|-----|------|-----|----|-----|----|----|----|----|------|------------|----|

| sc | TRE | MCPE | 0  | DVA | PSEL | A17 | A1 | RDY | IE | F4 | F3 | F2 | _ F1 | <b>F</b> O | GO |

| Bit   | Name                                          | Туре       | Function                                                                                                                                                                                                                                                      |  |  |

|-------|-----------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15    | Special condition<br>(SC)                     | Read only  | Set when TRE or any drive ATA bit is set. Cleared by clearing the TRE or ATA conditions.                                                                                                                                                                      |  |  |

| 14    | Transfer error<br>(TRE)                       | Read/write | Set when one or more RMCS2 bits (08-15) are set,<br>or a drive error occurs during a data transfer.<br>Cleared by UNIBUS INIT, controller clear, loading<br>a data transfer command with GO bit set, or by<br>writing a 1 to this bit causing an error clear. |  |  |

| 13*   | MASSBUS control<br>bus parity error<br>(MCPE) | Read only  | Set to 0 by controller.                                                                                                                                                                                                                                       |  |  |

| 12    | Not used                                      |            | Always read as 0.                                                                                                                                                                                                                                             |  |  |

| 11*   | Drive available<br>(DVA)                      | Read only  | Set to 1 by controller.                                                                                                                                                                                                                                       |  |  |

| 10*   | Port select (PSEL)                            | Read/write | Read/write for diagnostic purposes and has no<br>effect on controller operation. Cleared by UNIBUS<br>INIT, controller clear, or by writing a 0 in this bit.                                                                                                  |  |  |

| 09-08 | A17-A16 UNIBUS<br>address extension<br>bits   | Read/write | Upper extension bits of the RMBA register. Cleared<br>by UNIBUS INIT, controller clear, or by writing 0 in<br>these bit positions. Cannot be modified while con-<br>troller is performing a data transfer.                                                    |  |  |

| 07    | Ready (RDY)                                   | Read only  | RDY normally = 1. During data transfers,<br>RDY = 0. When a data transfer command code<br>(51-73) is written into RMCD1, RDY is reset. At the<br>termination of the data transfer, RDY is set.                                                                |  |  |

MASSBUS is a trademark of Digital Equipment Corporation.

### **RMCS1** (continued)

| Bits        | Name Type                |    |    | e          | Function |     |                                                                                                                                                |                                                                                                                                                                                                   |

|-------------|--------------------------|----|----|------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06          | Interrupt enable<br>(IE) |    |    | Read/write |          | gro | is a control bit that can be set only under pro-<br>am control and enables an interrupt to occur<br>en the following conditions are satisfied. |                                                                                                                                                                                                   |

|             |                          |    |    |            |          | 1.  | Upon termination of a data transfer if IE is set when RDY becomes asserted.                                                                    |                                                                                                                                                                                                   |

|             |                          |    |    |            |          |     | 2.                                                                                                                                             | If SC, IE, and RDY are all asserted.                                                                                                                                                              |

|             |                          |    |    |            |          |     | 3.                                                                                                                                             | If the program writes a 1 into IE and RDY at the same time.                                                                                                                                       |

|             |                          |    |    |            |          |     | au<br>rec<br>by                                                                                                                                | eared by UNIBUS INIT, controller clear, or<br>tomatically cleared when an interrupt is<br>cognized by the CPU. When a 0 is written into IE<br>the program, any pending interrupts are<br>ncelled. |

| 05-01<br>00 | F4-F0 and GO bit         |    |    | Read/write |          |     | F0 and the GO bit (00) are function (command)<br>de control bits.                                                                              |                                                                                                                                                                                                   |

|             | F4                       | F3 | F2 | F1         | F0       | GO  | Octal                                                                                                                                          |                                                                                                                                                                                                   |

|             | 0                        | 0  | 0  | 0          | 0        | 1   | 01                                                                                                                                             | No operation                                                                                                                                                                                      |

|             | 0                        | 0  | 0  | 1          | 0        | 1   | 05                                                                                                                                             | Seek command                                                                                                                                                                                      |

|             | 0                        | 0  | 0  | 1          | 1        | 1   | 07                                                                                                                                             | Recalibrate                                                                                                                                                                                       |

|             | 0                        | 0  | 1  | 0          | 0        | 1   | 11                                                                                                                                             | Drive clear                                                                                                                                                                                       |

|             | 0                        | 0  | 1  | 0          | 0        | 1   | 11                                                                                                                                             | Drive clear                                                                                                                                                                                       |

|             | 0                        | 0  | 1  | 0          | 1        | 1   | 13                                                                                                                                             | Release (dual sort operation)                                                                                                                                                                     |

|             | 0                        | 0  | 1  | 1          | 0        | 1   | 15                                                                                                                                             | Offset command                                                                                                                                                                                    |

|             | 0                        | 0  | 1  | 1          | 1        | 1   | 17                                                                                                                                             | Return to centerline                                                                                                                                                                              |

|             | 0                        | 1  | 0  | 0          | 0        | 1.  | 21                                                                                                                                             | Read-in preset                                                                                                                                                                                    |

|             | 0                        | 1  | 0  | 0          | 1        | 1   | 23                                                                                                                                             | Pack acknowledge                                                                                                                                                                                  |

|             | 0                        | 1  | 1  | 0          | 0        | 1   | 31                                                                                                                                             | Search command                                                                                                                                                                                    |

|             | 1                        | 0  | 1  | 0          | 0        | 1   | 51                                                                                                                                             | Write check data                                                                                                                                                                                  |

|             | 1                        | 0  | 1  | 0          | 1        | 1   | 53                                                                                                                                             | Write check header and data                                                                                                                                                                       |

|             | 1                        | 1  | 0  | 0          | 0        | 1   | 61                                                                                                                                             | Write data                                                                                                                                                                                        |

|             | 1                        | 1  | 0  | 0          | 1        | 1   | 63                                                                                                                                             | Write header and data                                                                                                                                                                             |

|             | 1                        | 1  | 1  | 0          | 0        | 1   | 71                                                                                                                                             | Read data                                                                                                                                                                                         |

|             | 1                        | 1  | 1  | 0          | 1        | 1   | 73                                                                                                                                             | Read header and data                                                                                                                                                                              |

The GO bit (RPCS1, bit 0) must be set to cause the controller to respond to a command. The GO bit is reset by the controller after command execution.

.....

#### Word Count Register (RMWC) (776702)

RMWC is the word count register. It is loaded by the program with the two's complement of the number of words to be transferred. During a data transfer, it is incremented by 1 each time a word is transmitted to or from memory. A maximum of 65,535 words can be transferred at one time.

| 15 | 14 | 13   | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|----|------|----|----|----|----|----|----|----|----|----|----|----|----|----|

| wc | WC | L MC | wc |

|       | •               |            |                                                                                                                                                                                                                                                                                                   |

|-------|-----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Name            | Туре       | Function                                                                                                                                                                                                                                                                                          |

| 15-00 | Word count (WC) | Read/write | Set by the program to specify the number of words<br>to be transferred (two's complement form). Cleared<br>only by writing zeros into all bits. RMWC is updated<br>by the controller at the end of each complete sector<br>transferred, or after each word of a sector of less<br>than 256 words. |

#### **UNIBUS Address Register (RMBA) (776704)**

RMBA register is used to address the memory location in which a transfer is to take place. The RMBA register forms the lower 16 bits of the address that combine with bit-09 and bit-08 of the control register RMCS1 to create the 18-bit memory address. The register is loaded with the starting memory address by the program. Each time a DMA transfer is made, the register is incremented by 2. If the BAI (bus address increment inhibit) bit (bit-03 of RMCS2) is set, the incrementing of the register is inhibited and all transfers take place to or from the starting memory address.

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| BA | 0  |

| Bit   | Name                   | Туре       | Function                                                                                                                                                                                                              |

|-------|------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-01 | UNIBUS address<br>(BA) | Read/write | Loaded by the program to specify the memory<br>address of a transfer. Cleared by UNIBUS INIT, or<br>by controller clear. The RMBA register is<br>incremented by 2 after each transfer of a word to<br>or from memory. |

| 0     | Not used               | _          | Always read as 0.                                                                                                                                                                                                     |

#### Disk Address Register (RMDA) (776706)

RMDA register is used to address the sector and track on the disk to or from which a transfer is desired. The RMDA register is associated with the drive whose unit number appears in bits 00-02 of the status register RMCS2. Before a transfer, the RMDA register is loaded by the program with the address of the first block to be transferred. RMDA is incremented each time a block of data has been transferred so that consecutive blocks are automatically addressed when the word count indicates that more than one block is to be transferred.

| 15 | 14 | 13 | 12   | 11  | 10  | 09  | 08  | 07 | 06 | 05 | 04   | 03  | 02  | 01  | 00  |

|----|----|----|------|-----|-----|-----|-----|----|----|----|------|-----|-----|-----|-----|

| 0  | 0  | 0  | TA16 | TA8 | TA4 | TA2 | TA1 | 0  | 0  | 0  | SA16 | SA8 | SA4 | SA2 | SA1 |

| Bit   | Name                   | Туре       | Function                                                                                                                                                                |

|-------|------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-13 | Not used               | Read/write |                                                                                                                                                                         |

| 12-08 | Track address<br>(TA)  | Read/write | Set by the program to specify the track on which a<br>transfer is to start. Cleared by read-in preset com-<br>mand. Updated by controller at the end of each<br>sector. |

| 07-05 | Not used               | Read/write |                                                                                                                                                                         |

| 04-00 | Sector address<br>(SA) | Read/write | Set by the program to specify the sector on which a transfer is to start. Cleared by read-in preset command. Updated by controller at the end of each sector.           |

#### Control and Status 2 Register (RMCS2) (776710)

RMCS2 register indicates the status of the controller and contains the drive unit number. The unit number specified in bits 00-02 of this register indicates which of the possible 4 physical or 8 logical drives is selected.

| 15  | 14  | 13  | 12  | 11  | 10  | 09  | 08   | 07 | 06 | 05  | 04  | 03  | 02 | 01   | 00 |

|-----|-----|-----|-----|-----|-----|-----|------|----|----|-----|-----|-----|----|------|----|

| DLT | WCE | UPE | NED | NEM | PGE | MXF | MDPE | OR | IR | CLR | PAT | BAI | U2 | _ บา | UO |

| Bit | Name                       | Туре       | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15* | Data late (DLT)            | Read only  | Set to 0 by controller.                                                                                                                                                                                                                                                                                                                                                                   |

| 14  | Write check error<br>(WCE) | Read only  | Set when the controller is performing a write/check<br>operation and a word on the disk does not match<br>the corresponding word in memory. Cleared by<br>UNIBUS INIT, controller clear, error clear, or<br>loading a data transfer command with GO bit set.                                                                                                                              |

|     |                            |            | WCE causes TRE to be set. If a mismatch is detected<br>during a write-check command execution, the<br>transfer terminates and the WCR bit is set. The<br>memory address displayed in RPBA (and extension)<br>is the address of the word following the one that did<br>not match (if BAI is not set). The mismatched data<br>word from the disk is displayed in the data buffer<br>(RPDB). |

| 13  | Parity error (UPE)         | Read/write | Set if a UNIBUS parity error is detected during a<br>write or write-check command. This bit may be set<br>and cleared for diagnostic purposes by writing to it.<br>Cleared by UNIBUS INIT, controller clear, error<br>clear, or loading a data transfer command with<br>GO bit set.                                                                                                       |

| 12  | Nonexistent drive<br>(NED) | Read only  | Set when the program reads or writes a register<br>associated with a drive that does not exist, or is<br>powered down. Cleared by UNIBUS INIT, con-<br>troller clear, error clear, or loading a data transfer<br>command with GO bit set. NED sets TRE.                                                                                                                                   |

.

.

#### RMCS2 (continued)

| Bit | Name                                       | Туре       | Function                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | Nonexistent<br>memory (NEM)                | Read only  | Set when the controller is performing a DMA<br>transfer and the memory address specified in RPBA<br>is nonexistent (does not respond to MSYN within 10<br>microseconds. Cleared by UNIBUS INIT, controller<br>clear, error clear, or loading a data transfer com-<br>mand with GO bit set. NEM sets TRE. The RPBA<br>contains the address+2 of the memory location<br>causing the error. |

| 10  | Program error<br>(PGE)                     | Read only  | Set when the program attempts to initiate a data<br>transfer operation while the controller is currently<br>performing one. Cleared by UNIBUS INIT, con-<br>troller clear, error clear, or loading a data transfer<br>command with GO bit set. PGE sets TRE. The data<br>transfer command code is inhibited from being<br>written.                                                       |

| 09  | Missed transfer<br>(MXF)                   | Read/write | Set if a data transfer command is loaded with ERR<br>set in RMDS, or if DMA transfers between the<br>UNIBUS and the controller's data buffer fail to<br>complete. This bit may be set or cleared for<br>diagnostic purposes by writing to it. Cleared by<br>UNIBUS INIT, controller clear, error clear, or<br>loading a data transfer command with GO bit set.<br>MXF sets TRE.          |

| 08* | MASSBUS data bus<br>parity error<br>(MDPE) | Read only  | Set to 0 by controller.                                                                                                                                                                                                                                                                                                                                                                  |