TANDY

# Service Manual

TANDY® MODEL 2000 PERSONAL COMPUTER

CUSTOM MANUFACTURED IN U.S.A. BY RADIO SHACK, A DIVISION OF TANDY CORPOF

### TANDY® MODEL 2000 COMPUTER

Copyright 1984 Tandy Corporation

All Rights Reserved

Reproduction or use, without express written permission from Tandy Corporation, or any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Tandy Corporation assumes no liability resulting from any errors or omissions in this manual, or from the use of the information contained herein.

# Table Of Contents

| 1 Introduction                                                                                        | 1                                |

|-------------------------------------------------------------------------------------------------------|----------------------------------|

| 2 Specifications                                                                                      | 7<br>7<br>7<br>7                 |

| 2.4 Optional Features                                                                                 | 8                                |

| 3 Disassembly/Assembly 3.1 Main Unit                                                                  | 9<br>1,0<br>11<br>12<br>13       |

| 4/ Adjustments 4.1 Power Supply 4.2 PLL Adjustment 4.3 Video Adjustment                               | 15<br>15<br>15<br>15             |

| 5/ Cabling Diagram/Pinout Connections                                                                 | 17                               |

| 6 Troubleshooting Procedures                                                                          | 39<br>39<br>39                   |

| 7/ Theory of Operation Block Diagram 7.1 Main Logic Board 7.1.1 General 7.1.2 CPU 7.1.3 Bus Interface | 41<br>42<br>43<br>43<br>44<br>5Ø |

| 7.1.4 Video System                                                                                    | 58<br>68<br>63<br>64<br>66       |

| 7.1.7 Clock/PLL                                                                                       | 72<br>77<br>77                   |

# Table Of Contents

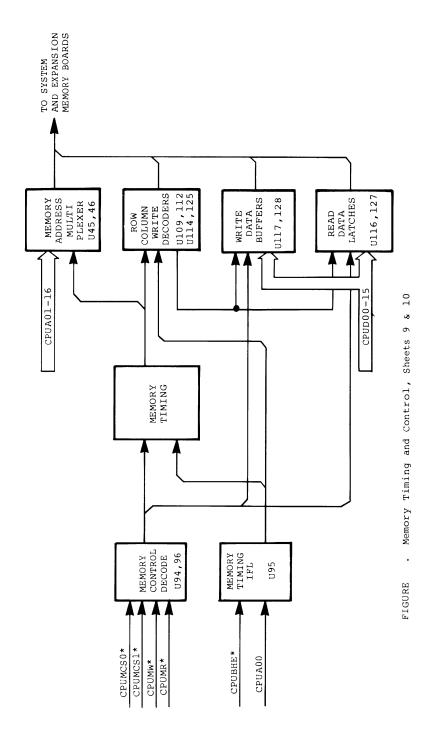

| 7.1.8.2 Memory Timing Circuit              | 77  |

|--------------------------------------------|-----|

| 7.1.8.3 Parity Testing                     | 79  |

| 7.1.8.4 Refresh Control                    | 8ø  |

| 7.1.8.5 Memory Control                     | 81  |

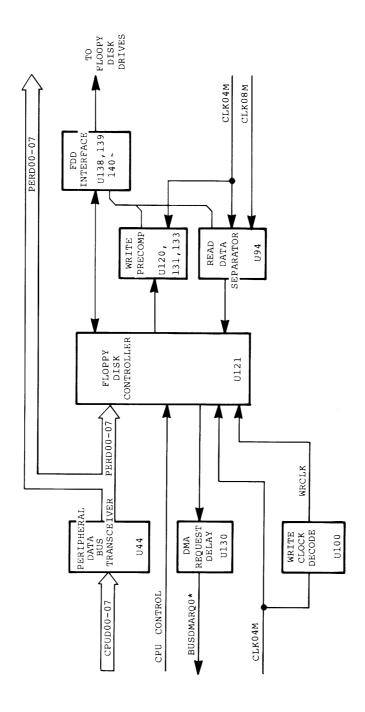

| 7.1.9 Floppy Disk Controller               | 83  |

| 7.1.9.1 Data Bus Interface                 | 83  |

| 7.1.9.2 FDC Port Specifications            | 83  |

| 7.1.9.3 DMA Request and Acknowledge        | 85  |

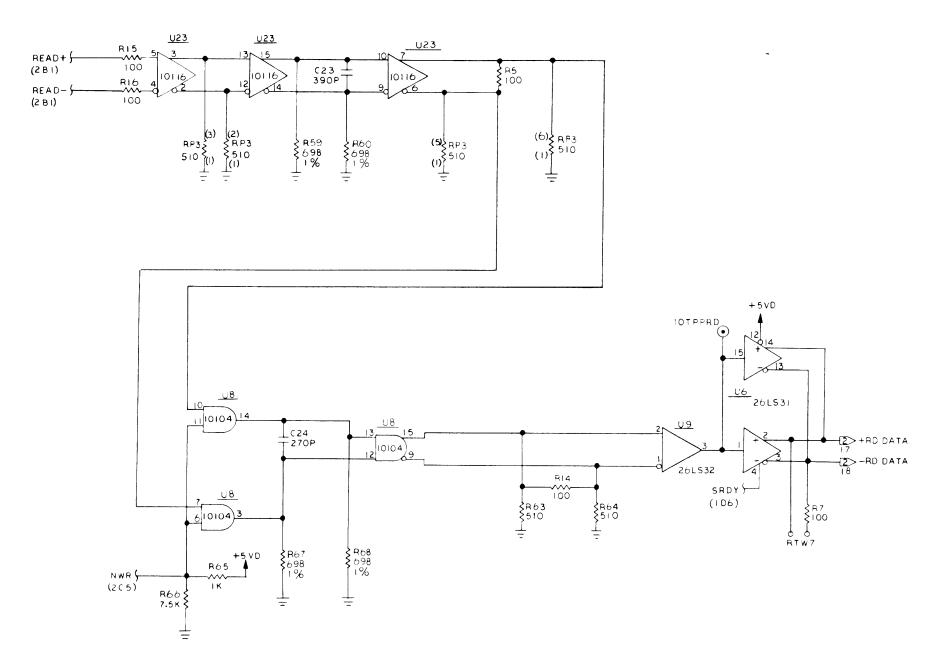

| 7.1.9.4 FDD Read Data Sequence             | 85  |

| 7.1.9.5 FDD Write Data Sequence            | 86  |

| 7.1.9.6 FDC/FDD Interface                  | 89  |

| 7.1.9.7 Drive Select Decode                | 9ø  |

| 7.1.9.8 READ/WRITE and SEEK Control        | 9ø  |

| 7.1.9.9 FDC Reset Control                  | 91  |

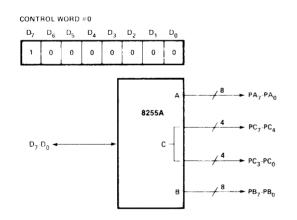

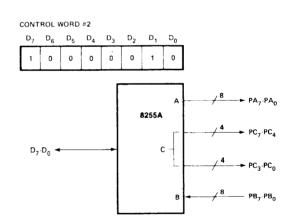

| 7.1.10 Parallel/Keyboard Interface         | 92  |

| 7.1.10.1 Printer Port                      | 92  |

| 7.1.10.2 Keyboard Interface                | 94  |

| 7.1.10.3 Revision Port                     | 95  |

| 7.1.11 Serial Interface/Programmable Timer | 96  |

| 7.1.11.1 Serial Interface                  | 96  |

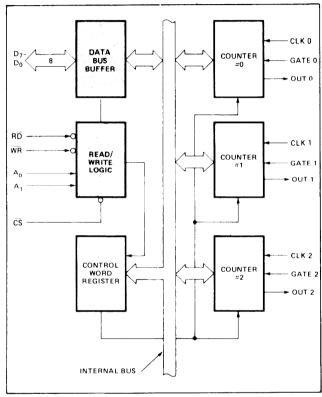

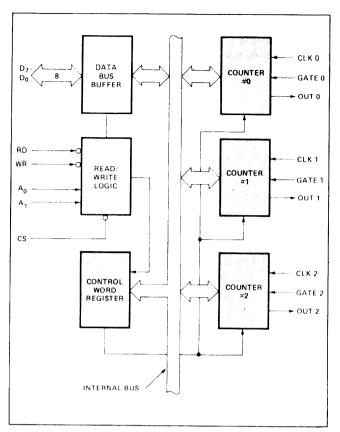

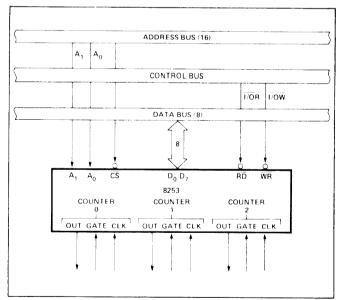

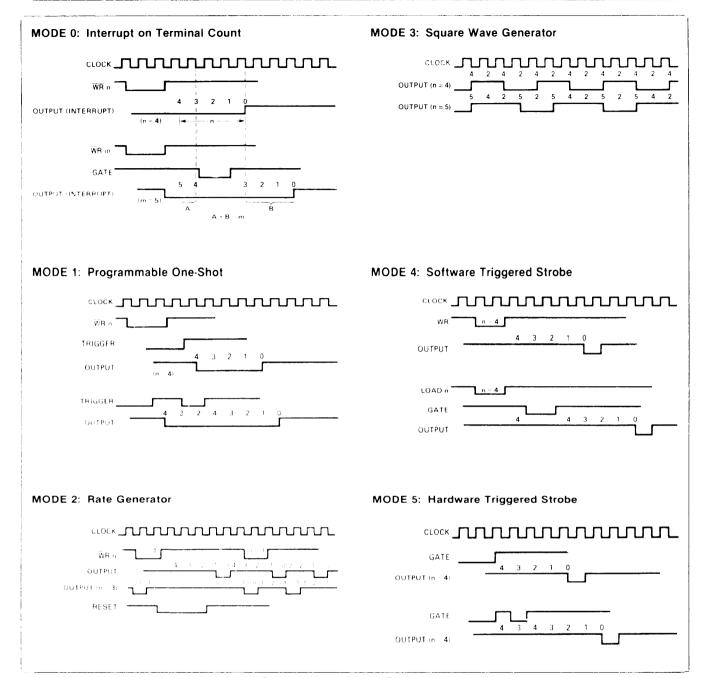

| 7.1.11.2 Counter/Timer Chip                | 97  |

| 7.1.11.3 RS-232 Operation                  | 98  |

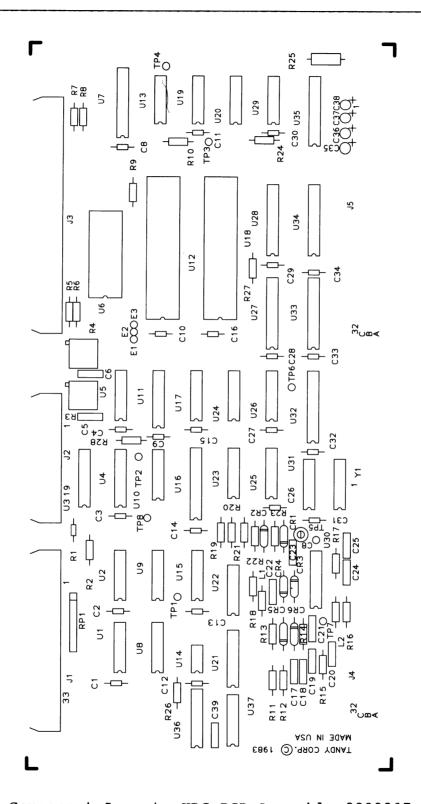

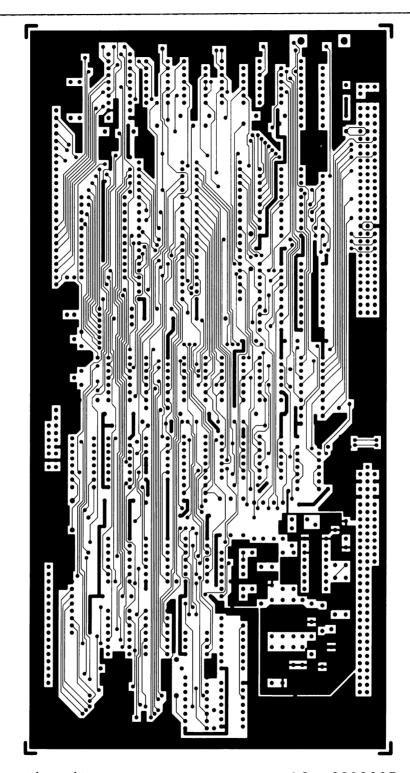

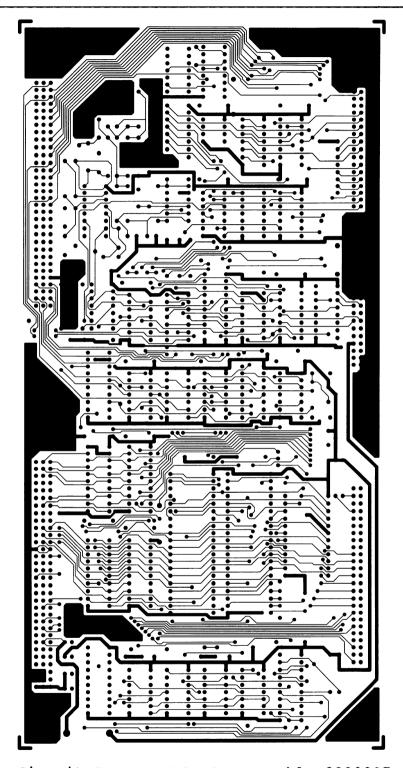

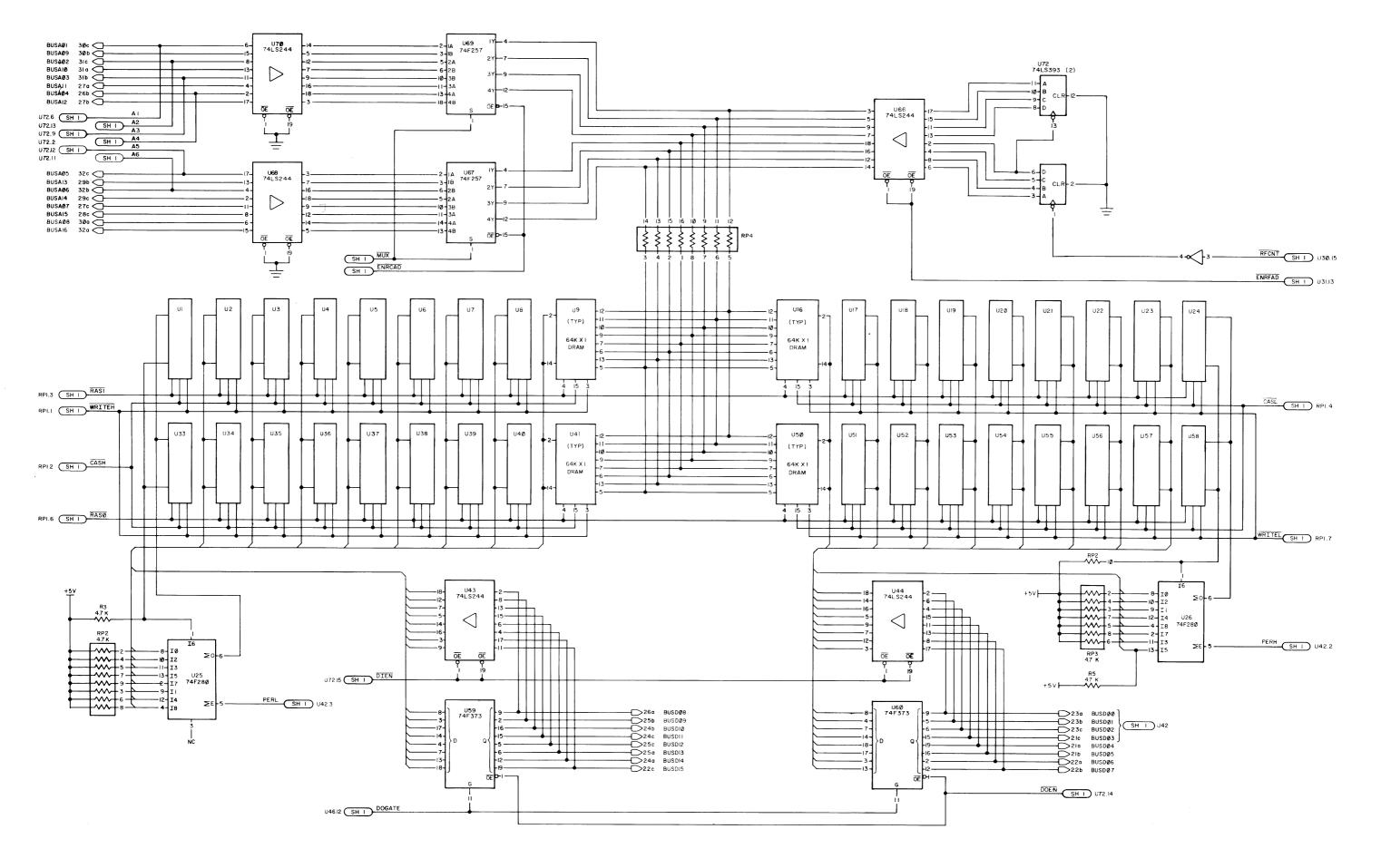

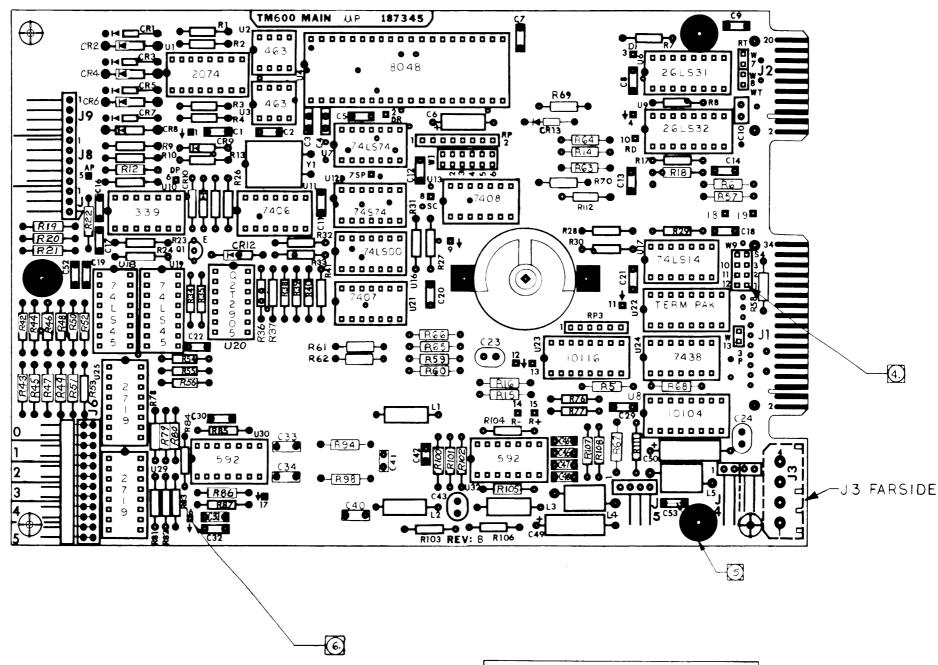

| Schematic 8000203, Main Logic Board        | 1Ø1 |

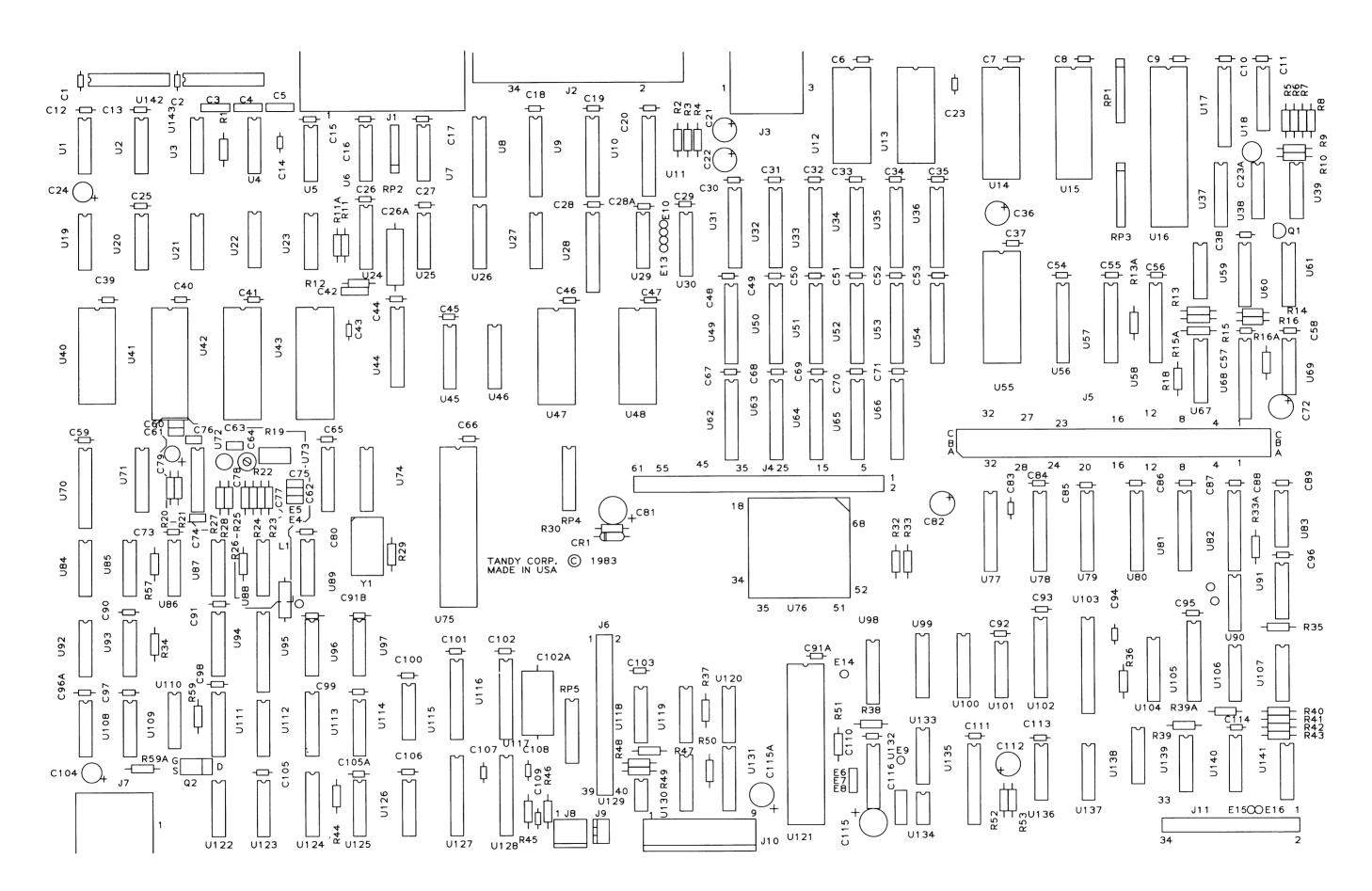

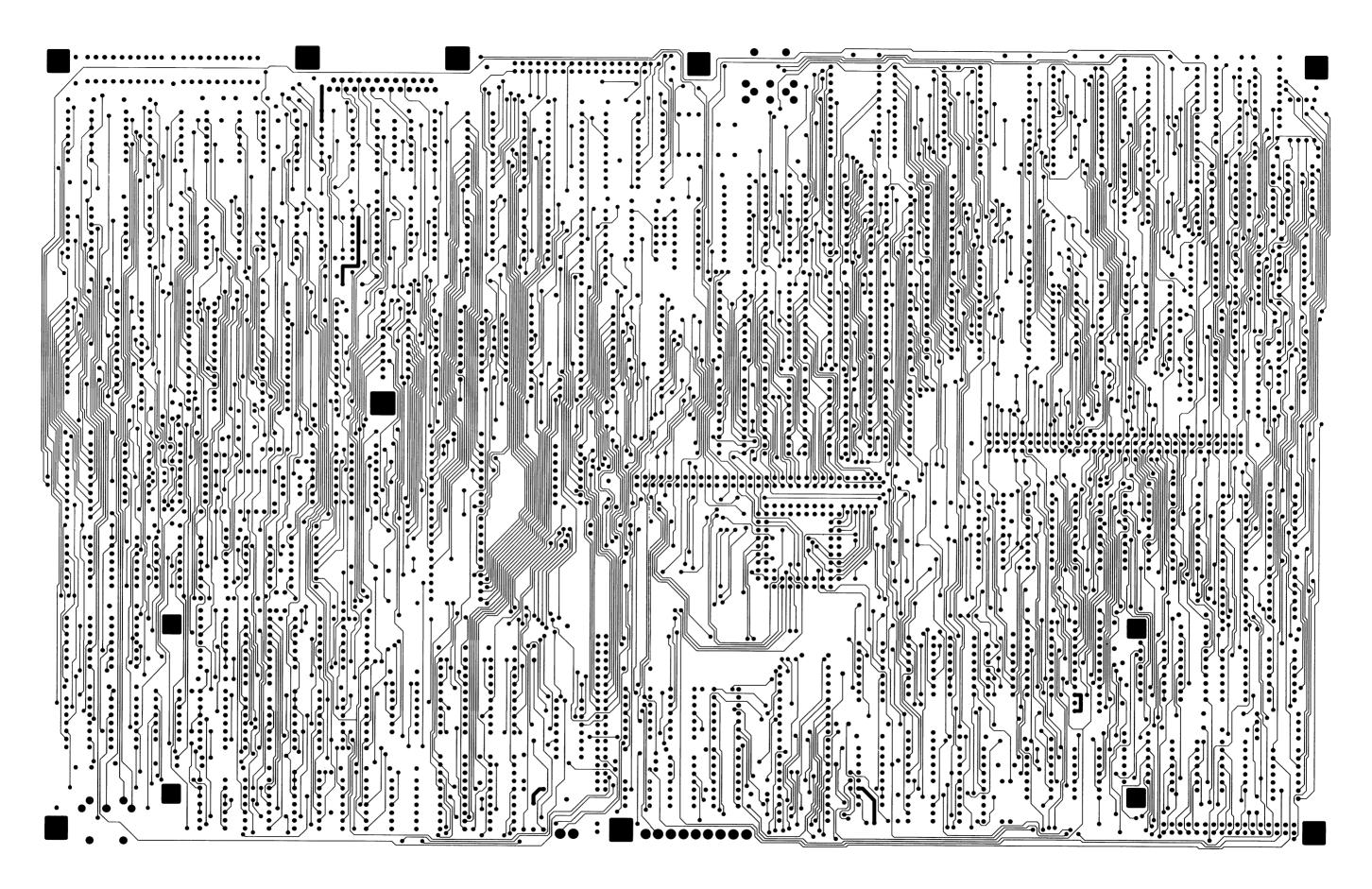

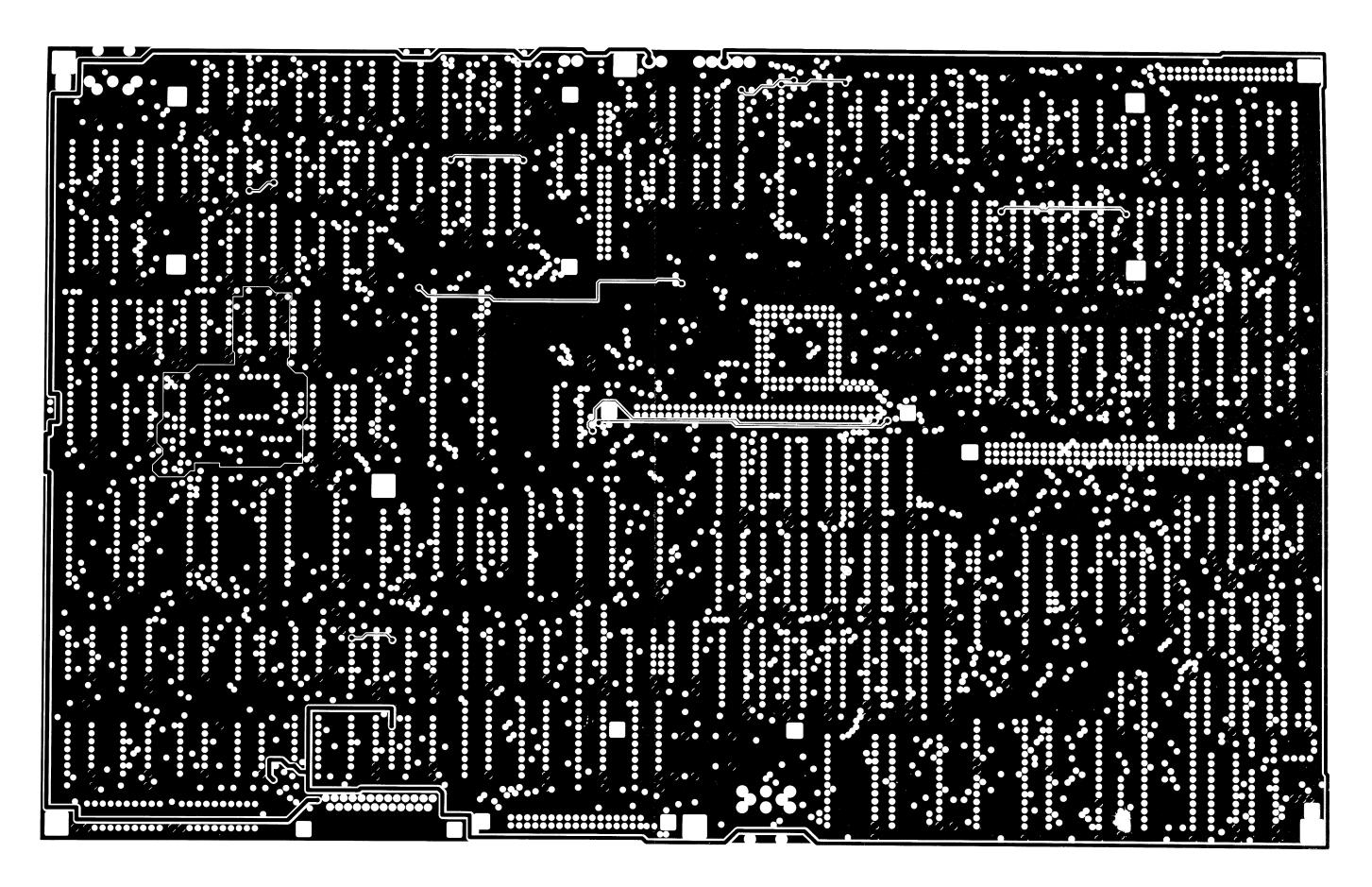

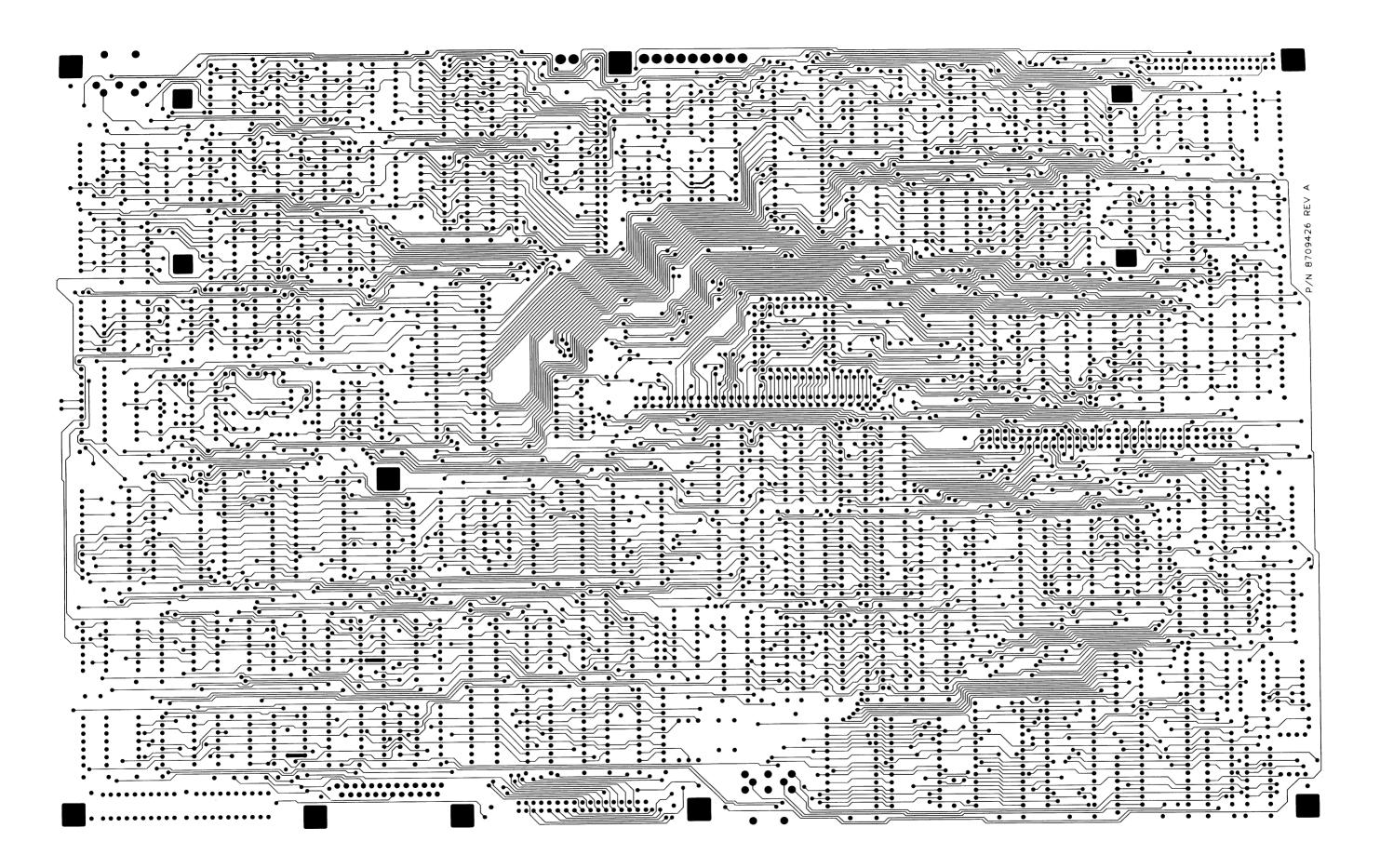

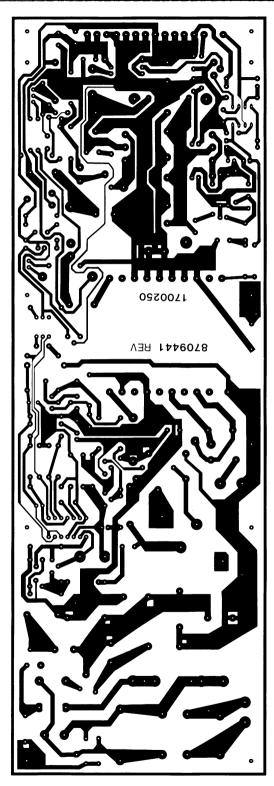

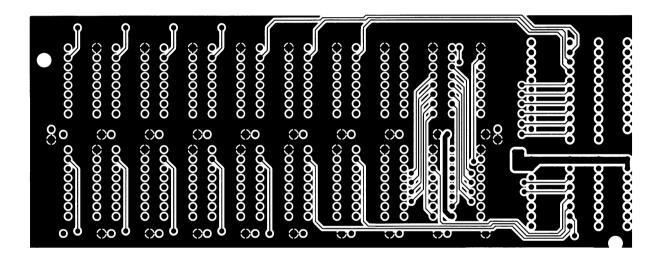

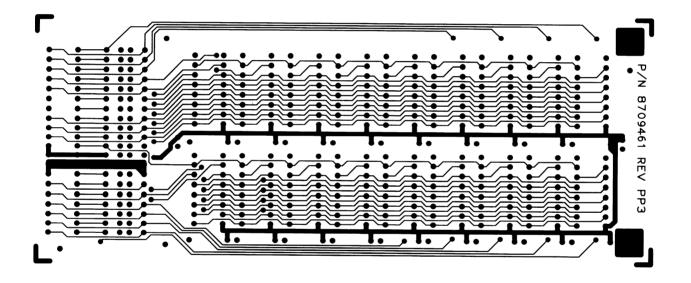

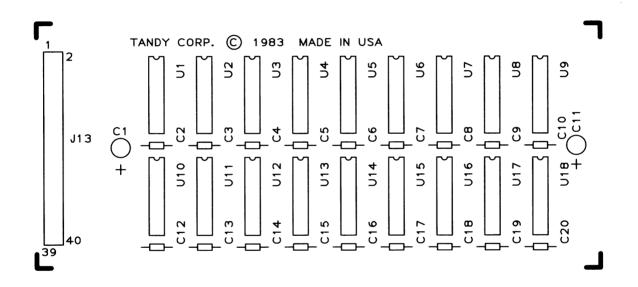

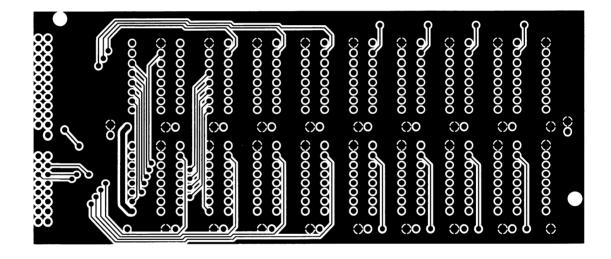

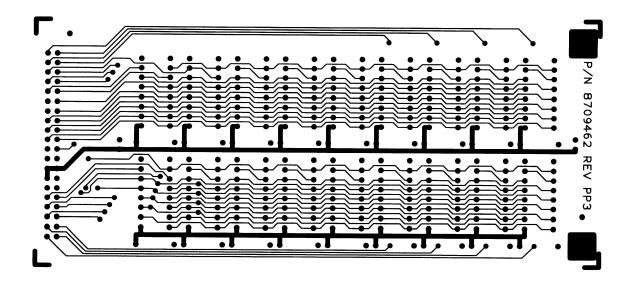

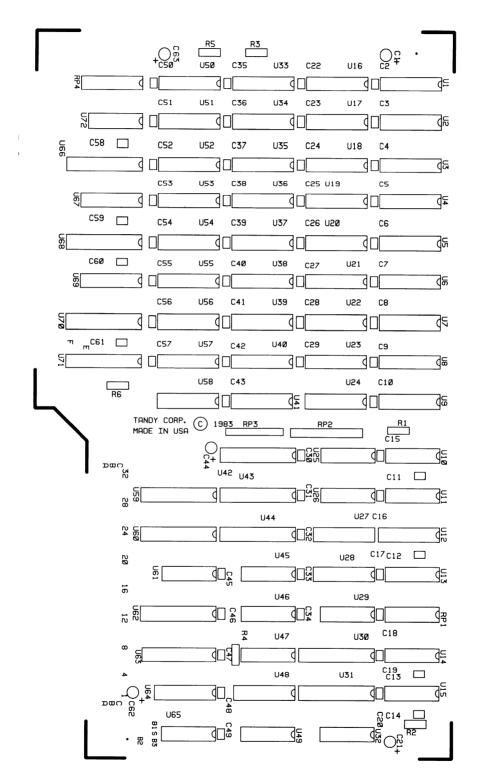

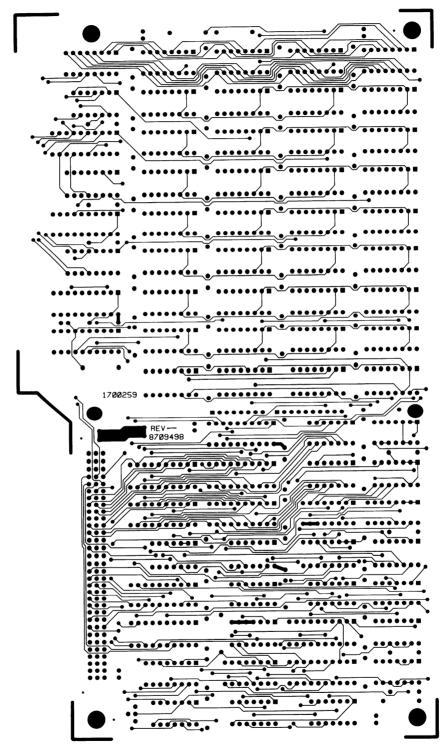

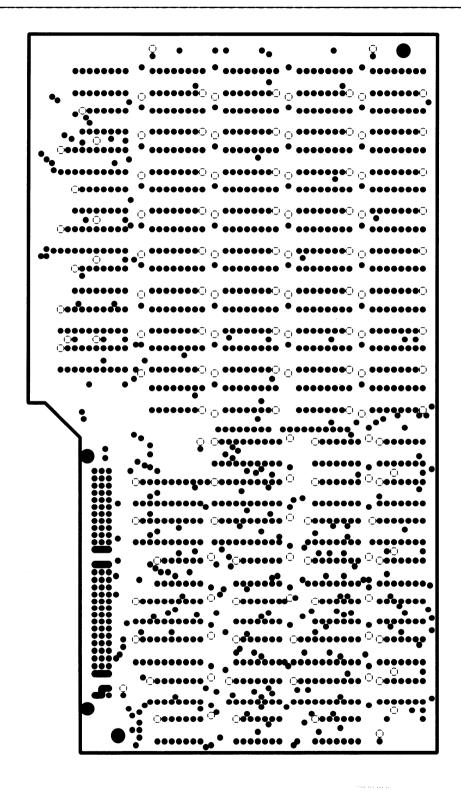

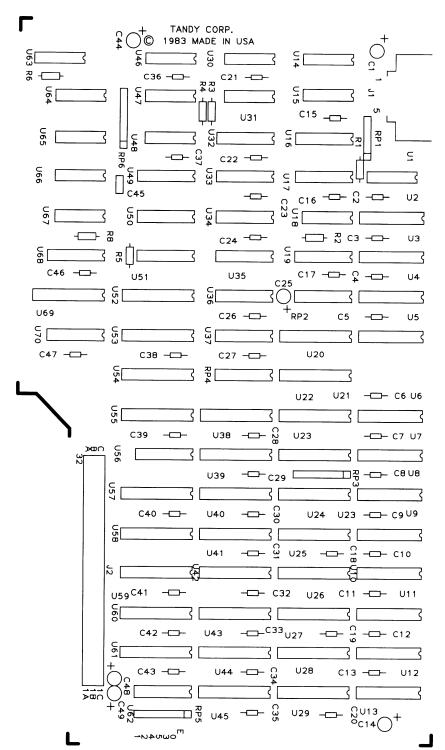

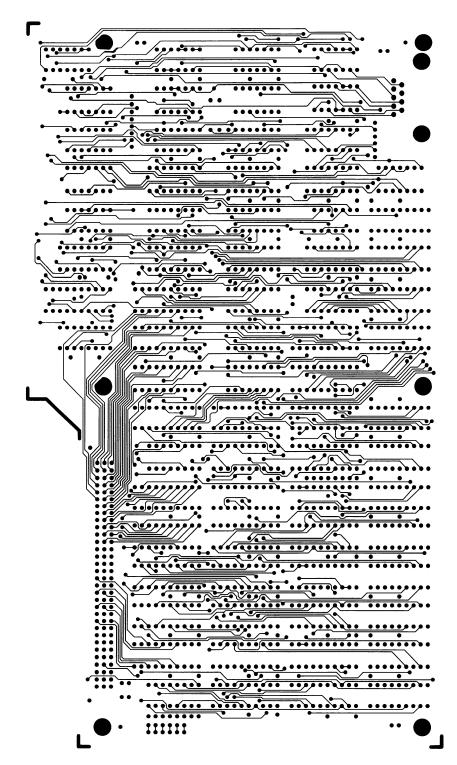

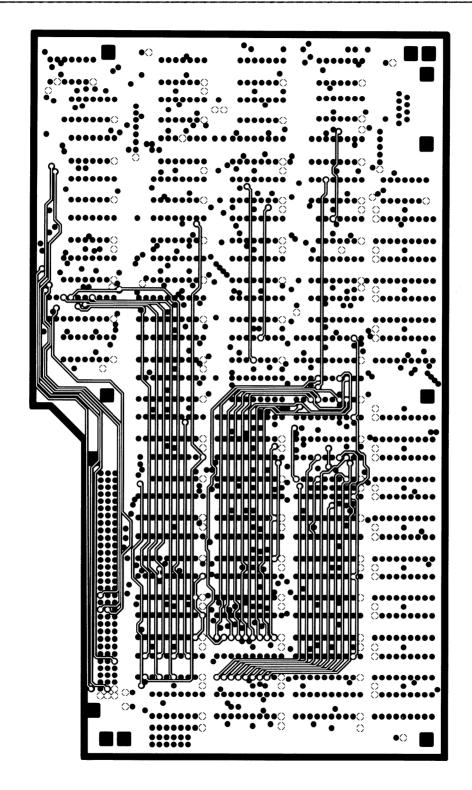

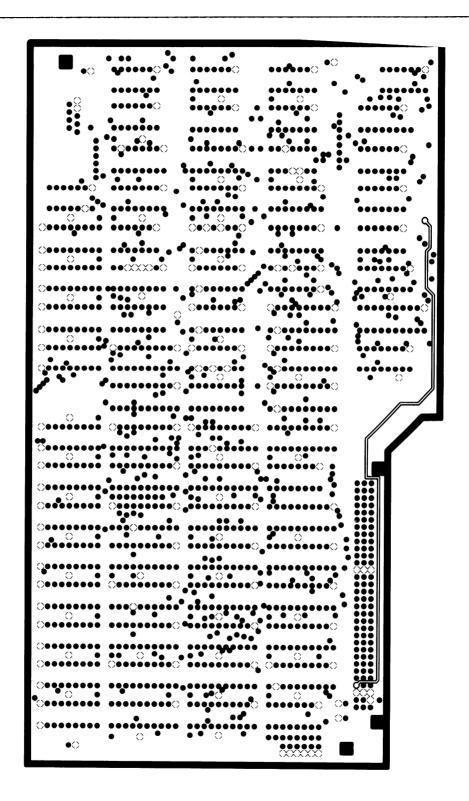

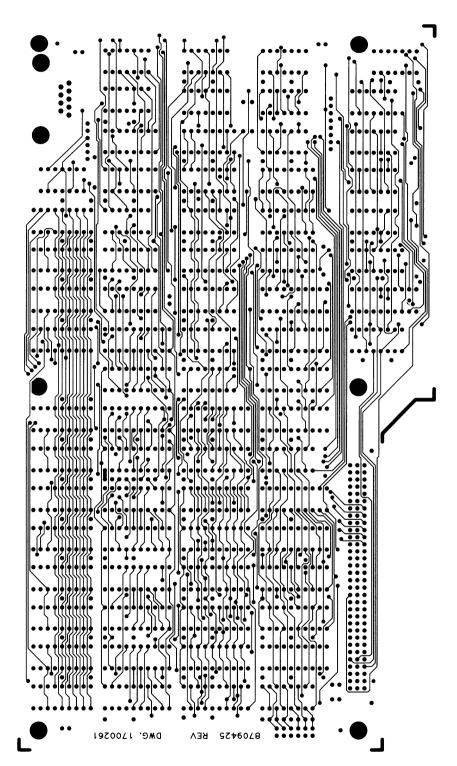

| Component Layout/Ckt Trace 1700245         | 127 |

| Parts List, Main Logic PCB                 | 133 |

|                                            |     |

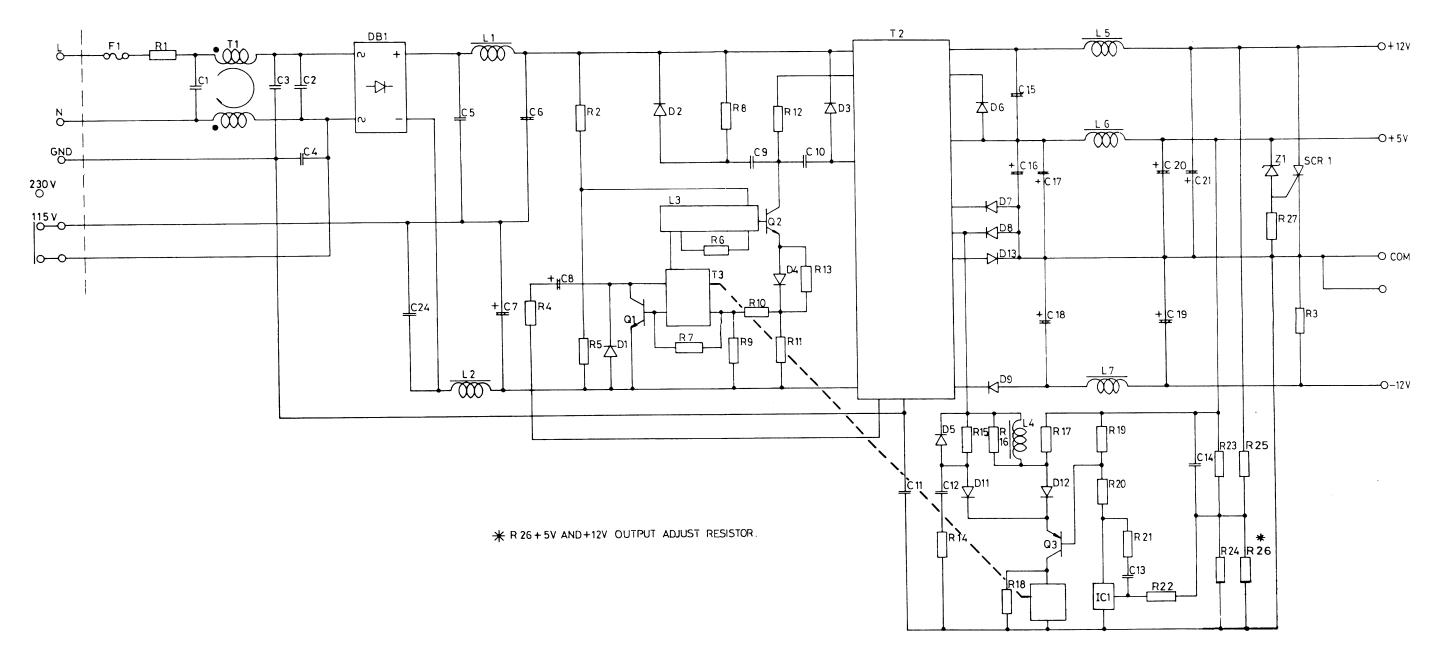

| 7.2 Power Supplies                         | 143 |

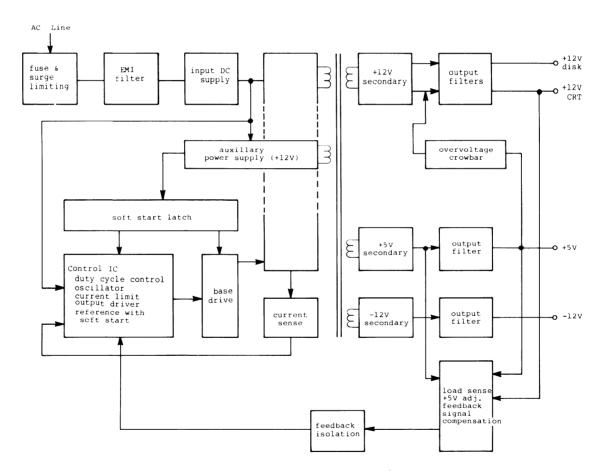

| 7.2.1 Main Power Supply (95W)              | 143 |

| 7.2.1.1 Technical Specifications           | 144 |

| 7.2.1.2 Troubleshooting The Power Supply   | 146 |

| 7.2.1.3 Performance Test                   | 152 |

| 7.2.1.4 System Description                 | 153 |

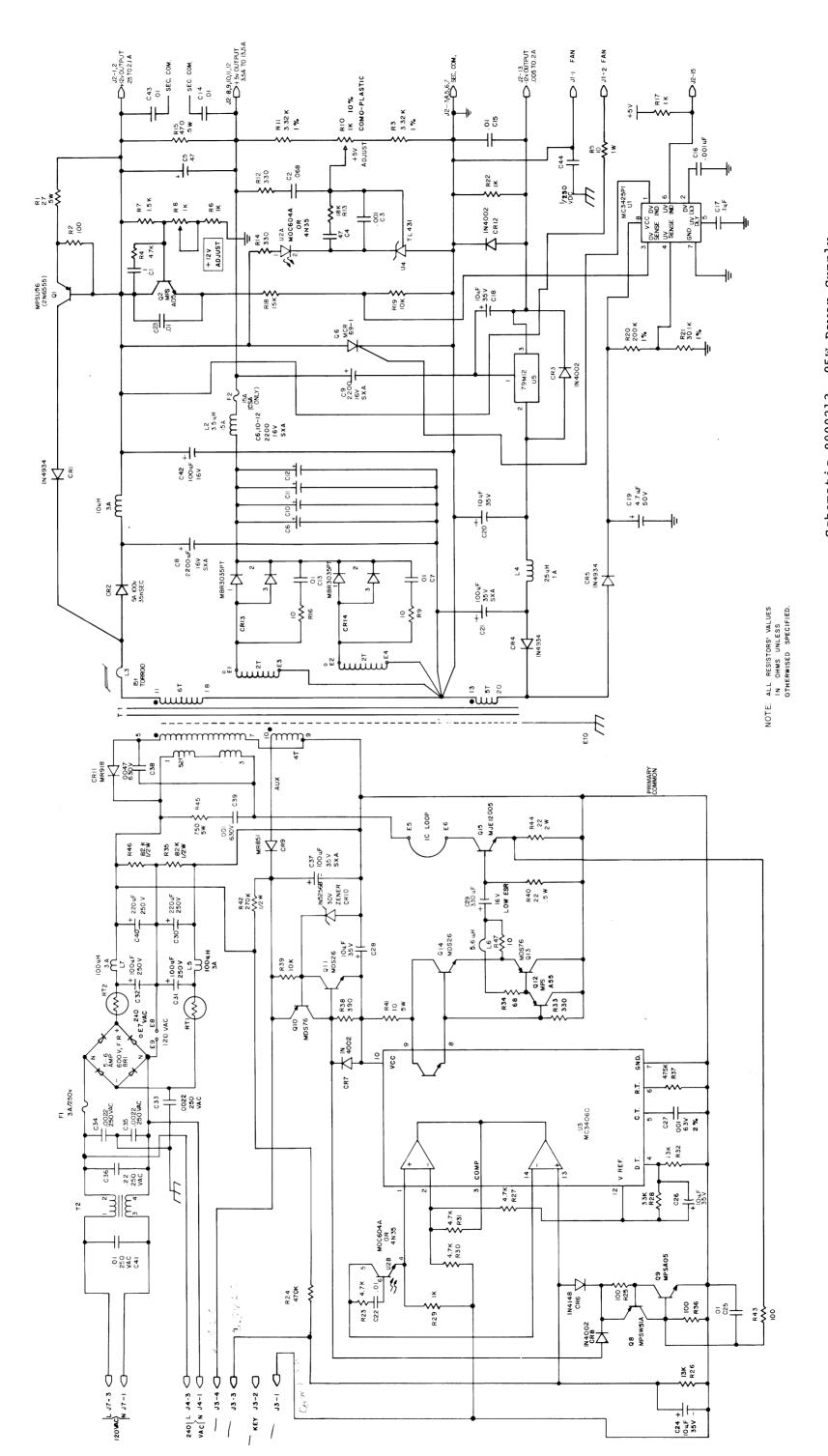

| Schematic 8000213, 95W Power Supply        | 161 |

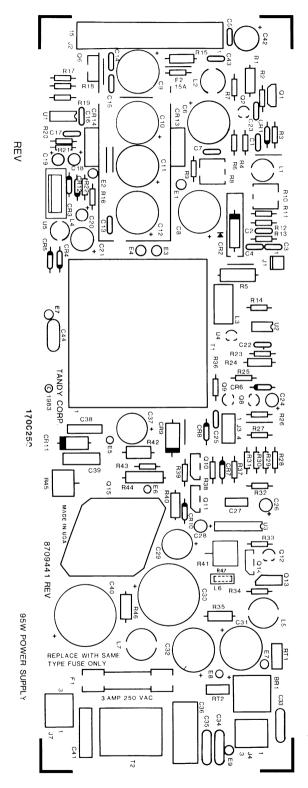

| Component Layout 1700250, 95W Power Supply | 163 |

| Parts List                                 | 165 |

| 7.2.2 Auxiliary Power Supply               | 171 |

| (38W, Hard Disk Drive Only)                |     |

| 7.2.2.1 Troubleshooting The Power Supply   | 171 |

| Schematic, 38W Power Supply 879ØØ25        | 177 |

| 7.2.2.2 Parts List                         |     |

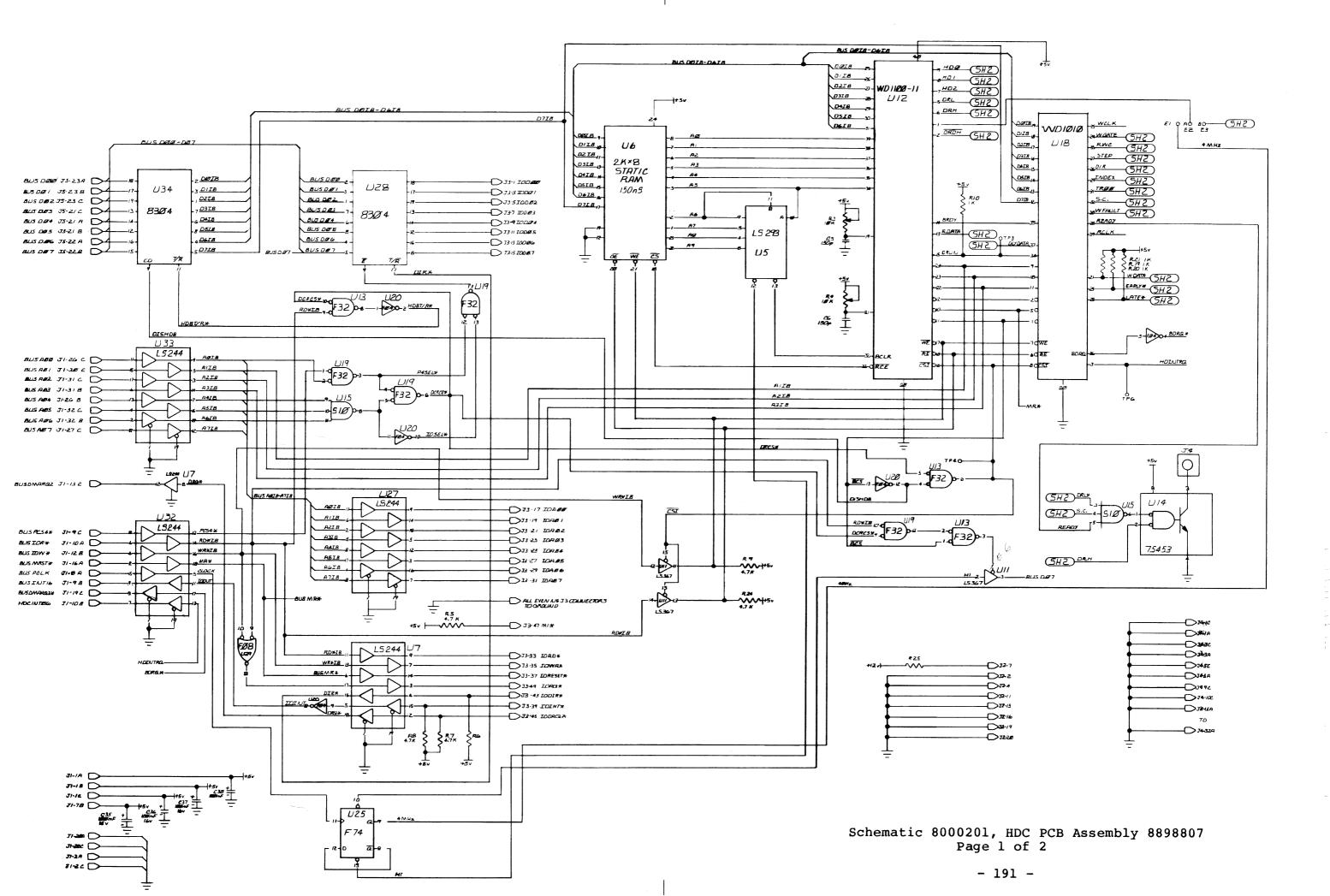

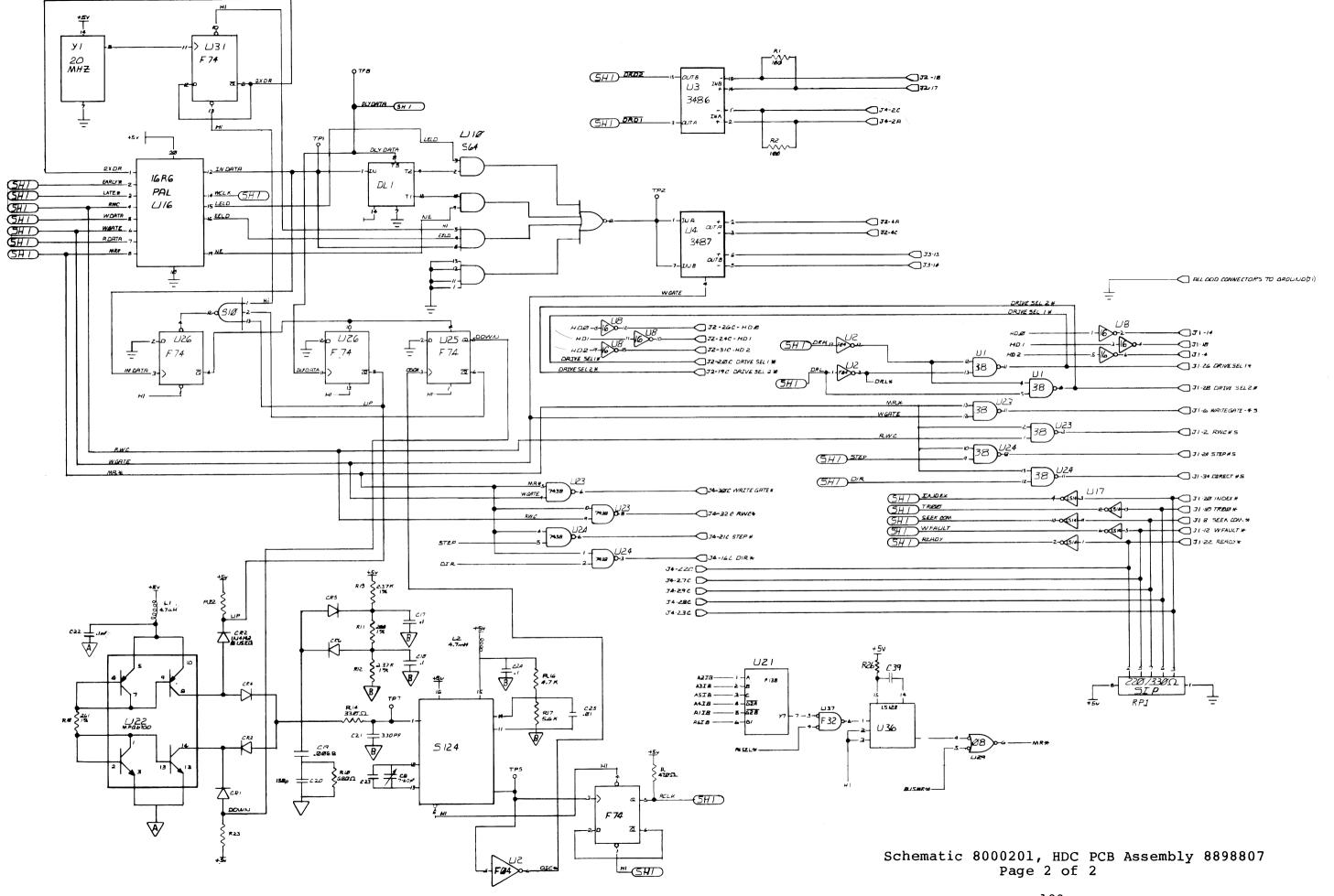

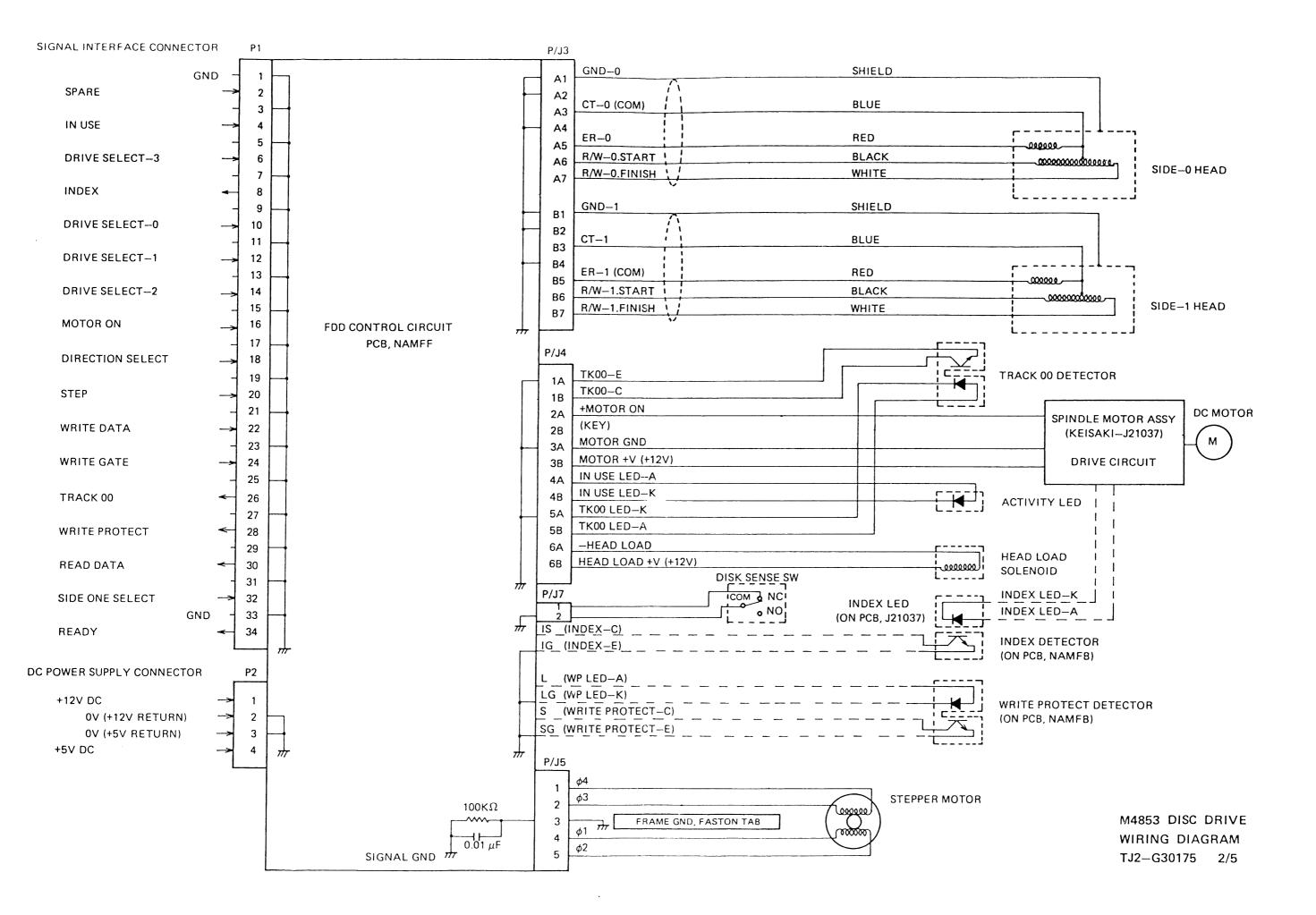

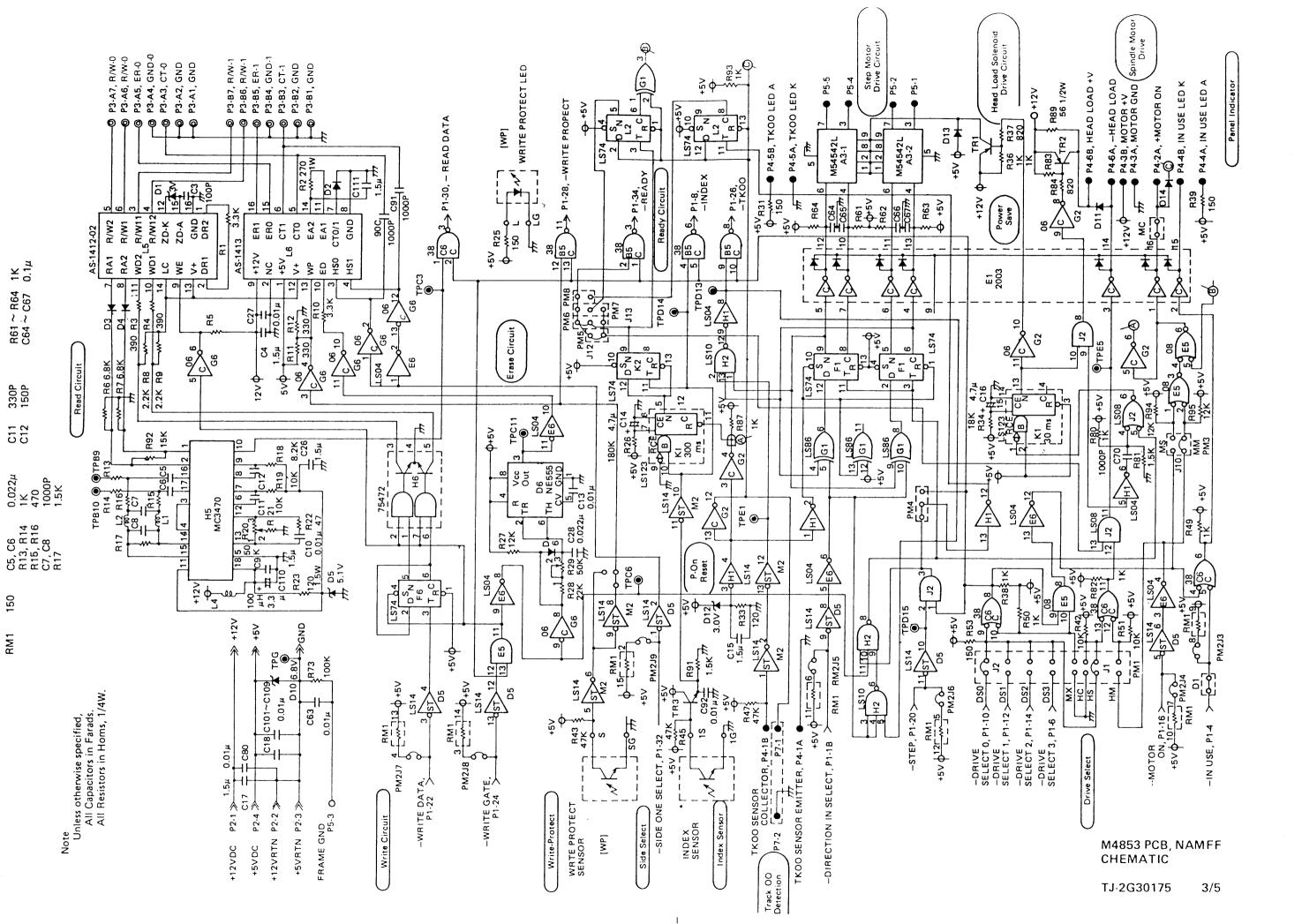

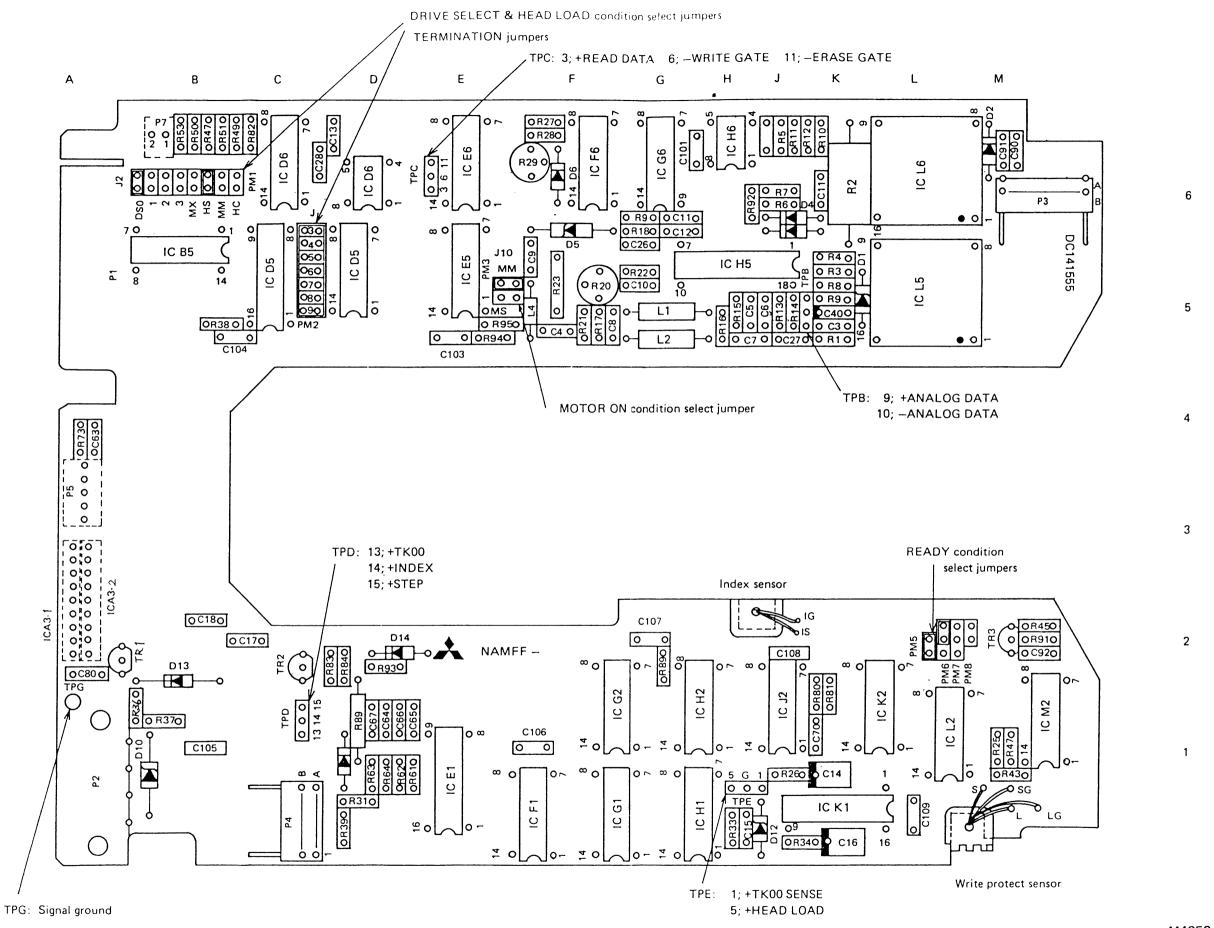

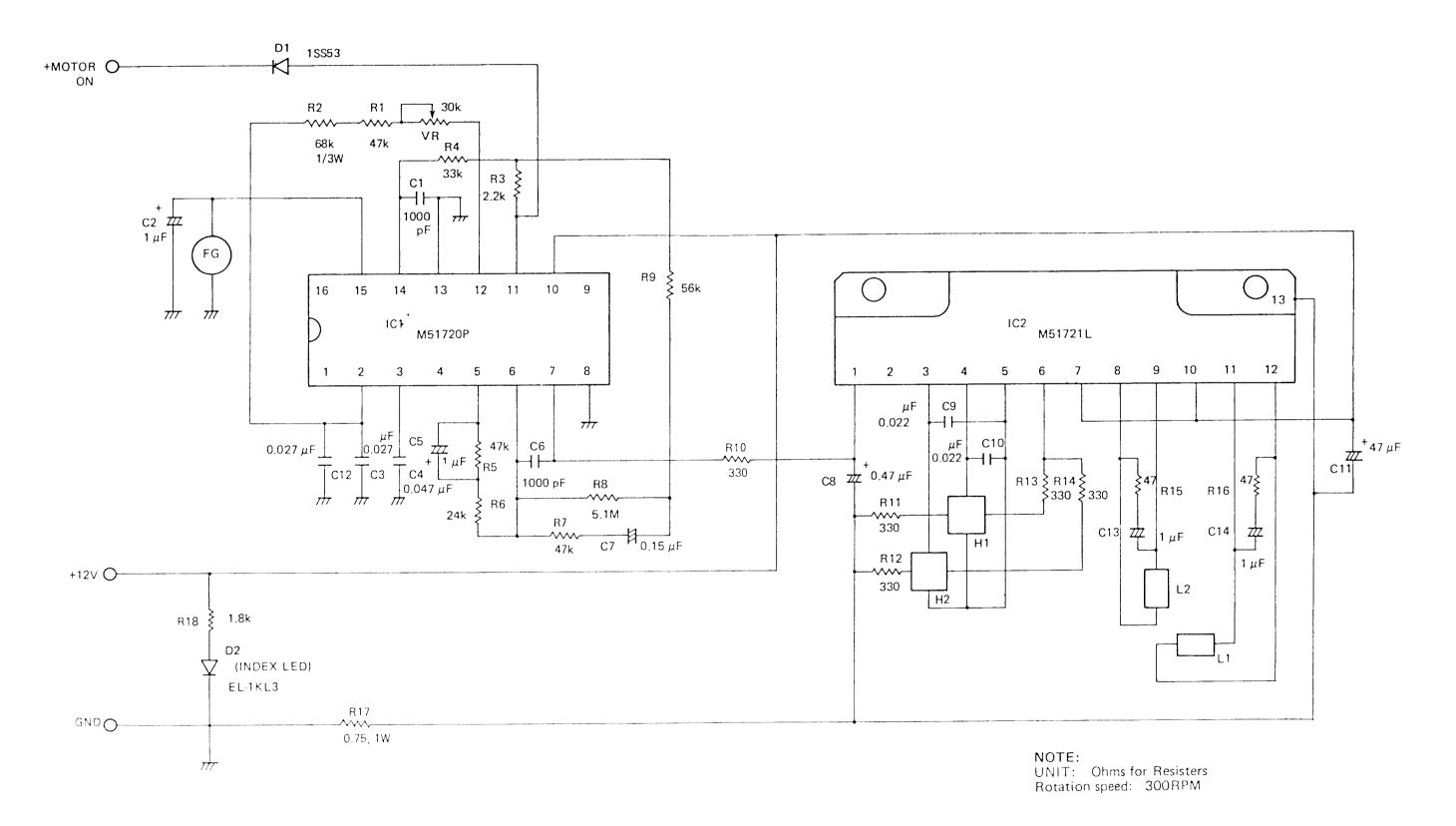

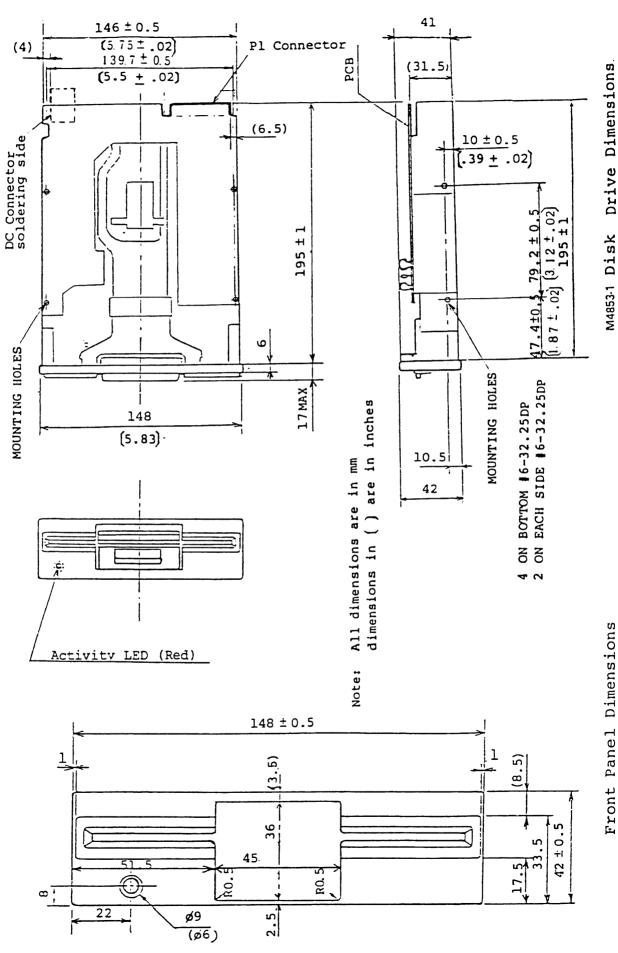

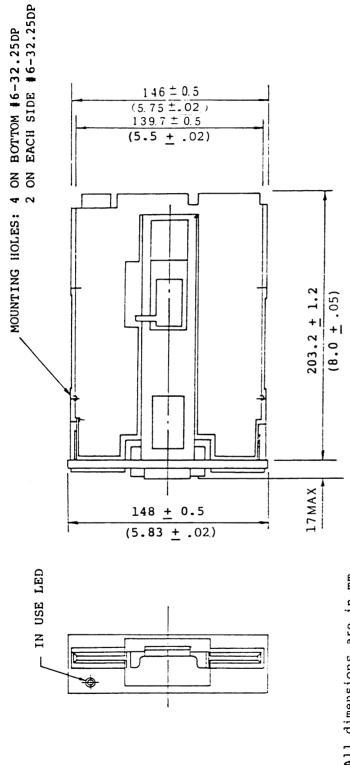

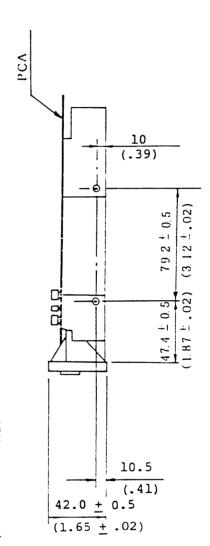

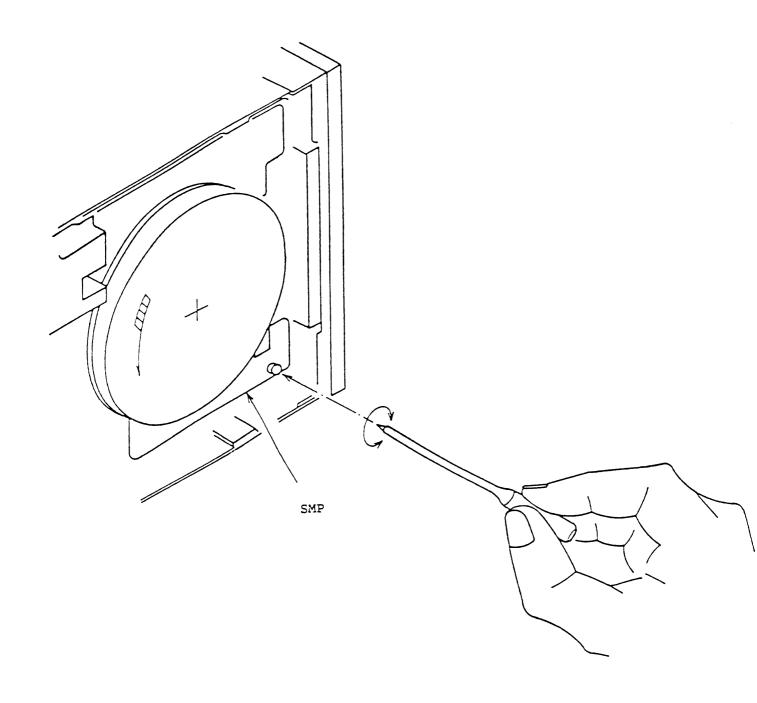

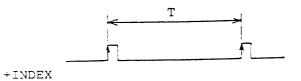

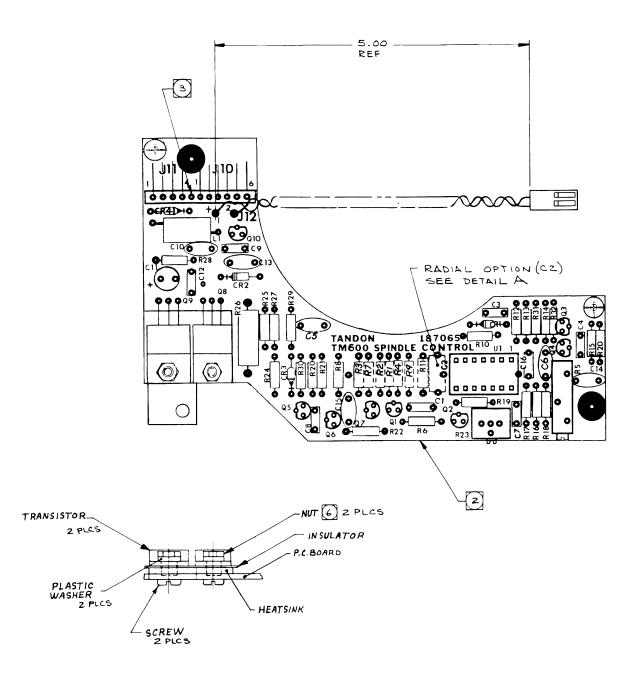

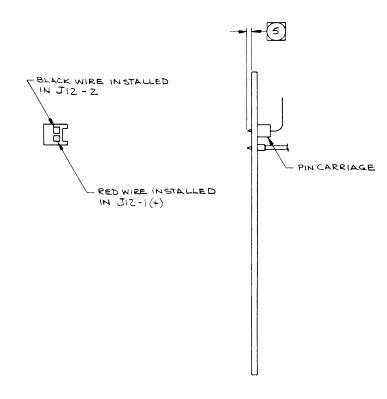

| 7.3 Disk Drives 7.3.1 Floppy Disk Drive 7.3.2 Hard Disk Drive 7.3.3 Hard Disk Controller PCB 7.3.3.1 Port Decoding 7.3.3.2 Drive Control Logic 7.3.3.3 Data Recovery 7.3.3.4 Controller Alignment 7.3.3.5 HDC Register Specifications Schematic 8000201 Component Layout 1700258, Hard Disk Controller Parts List | 183                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 7.4 Motherboard                                                                                                                                                                                                                                                                                                   | 2Ø3<br>2Ø5<br>2Ø7<br>21Ø                      |

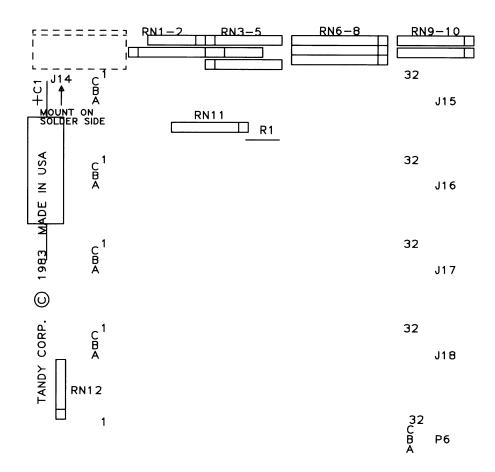

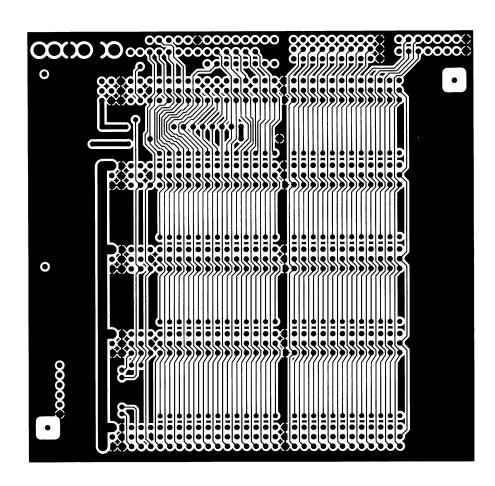

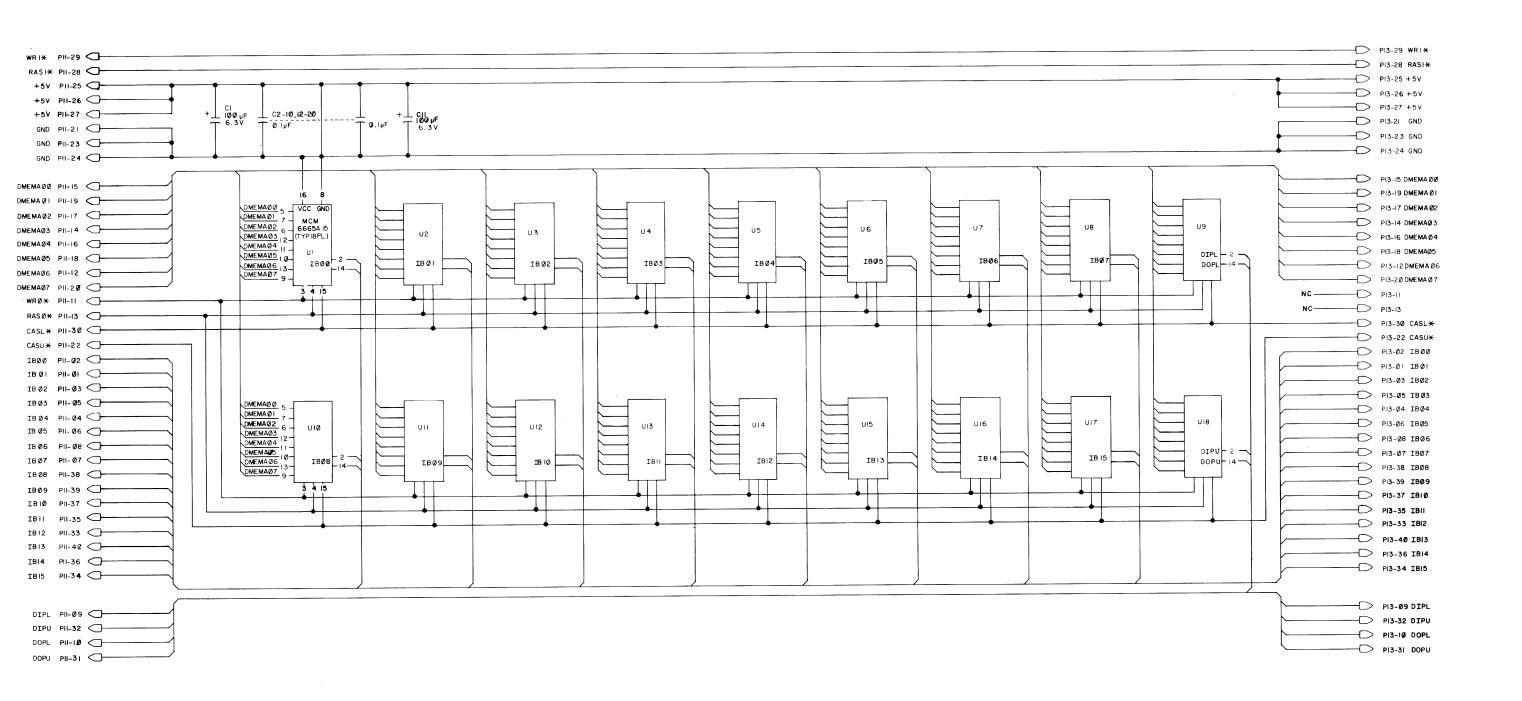

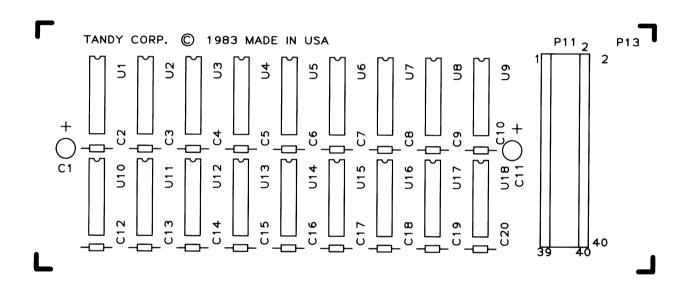

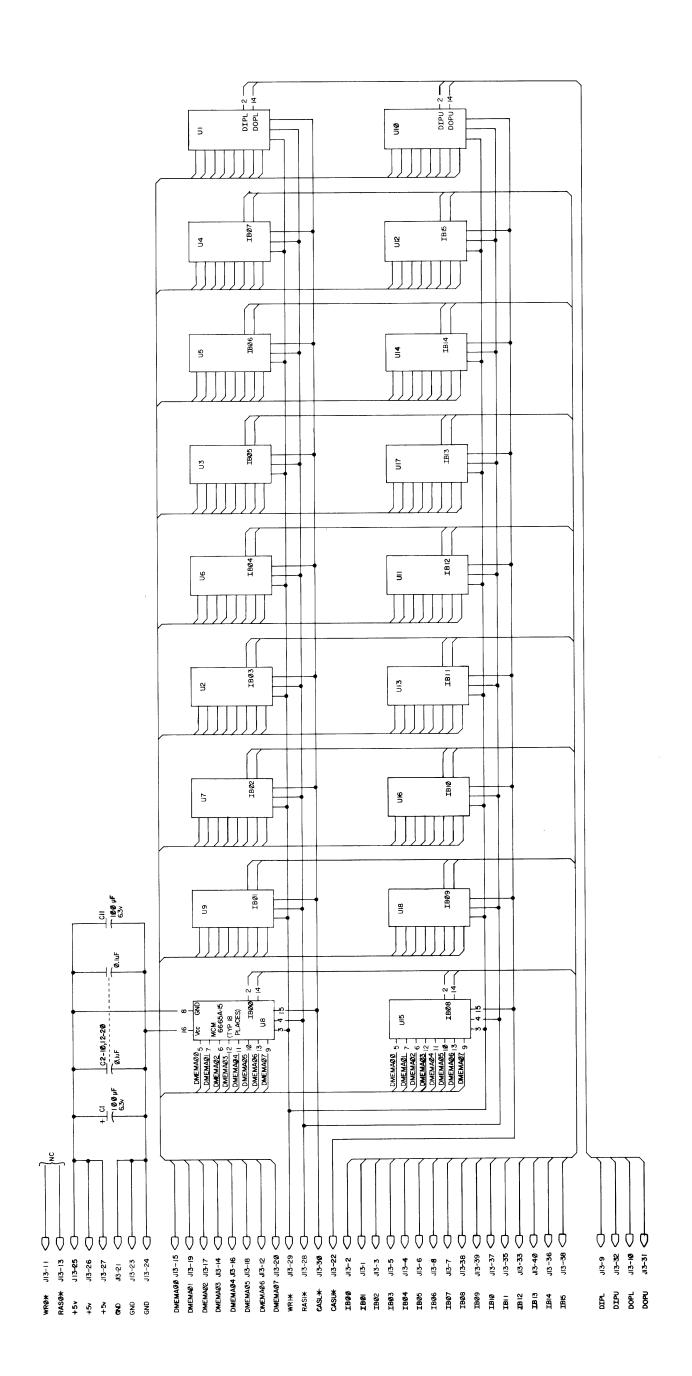

| 7.5 128K RAM Board (Schematic 8000204) 7.5.1 Introduction                                                                                                                                                                                                                                                         | 211<br>211<br>211<br>211<br>212<br>217<br>219 |

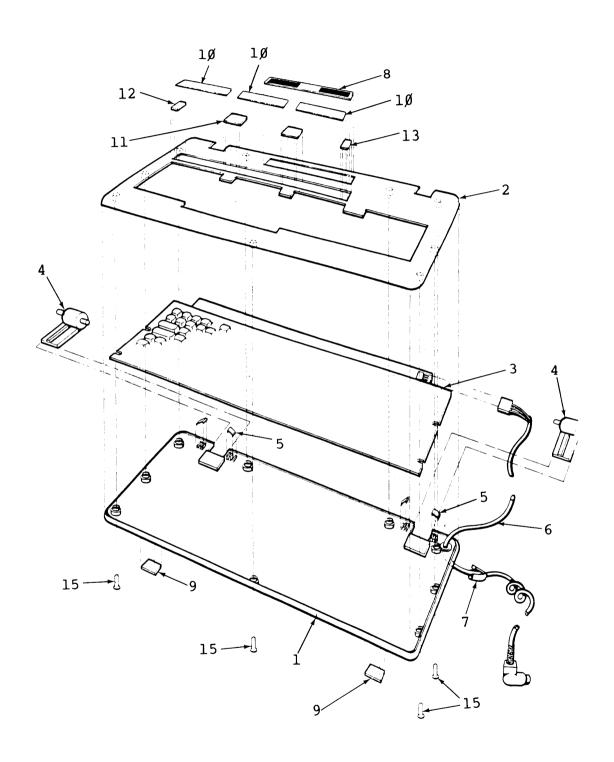

| 7.6 Keyboard Assembly                                                                                                                                                                                                                                                                                             | 223<br>224<br>225<br>227<br>228               |

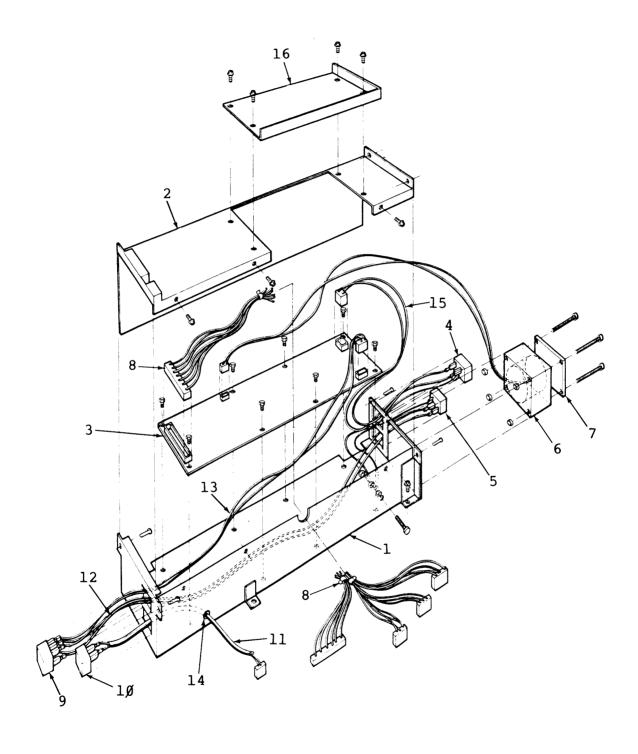

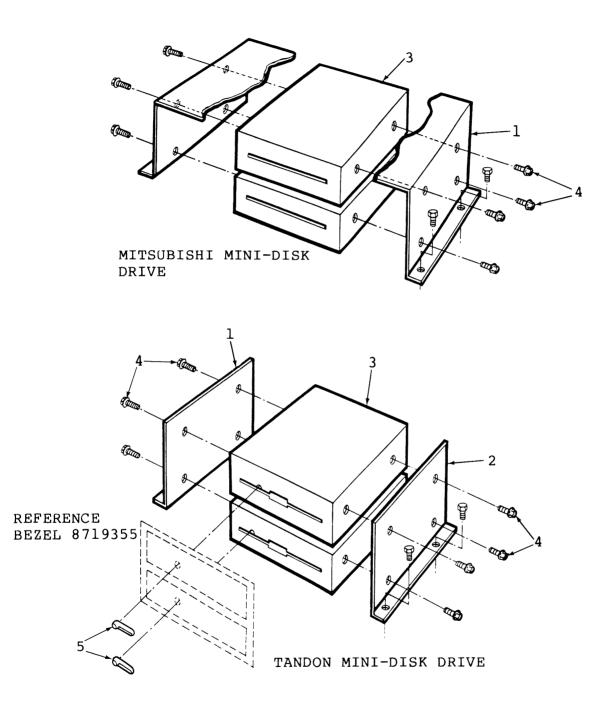

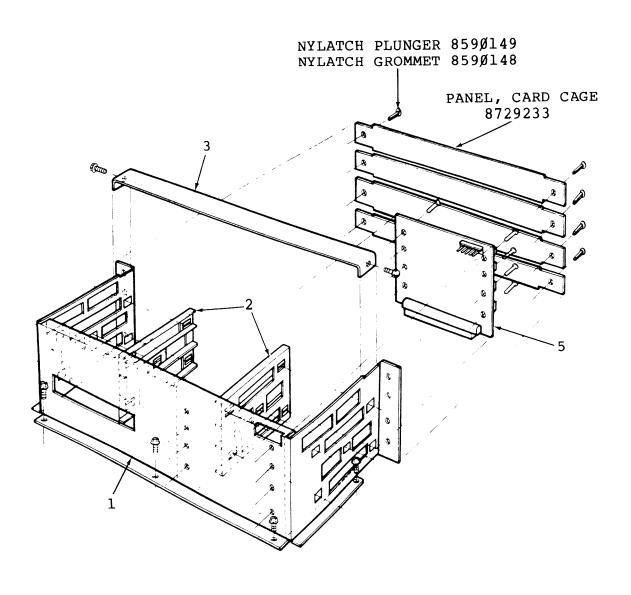

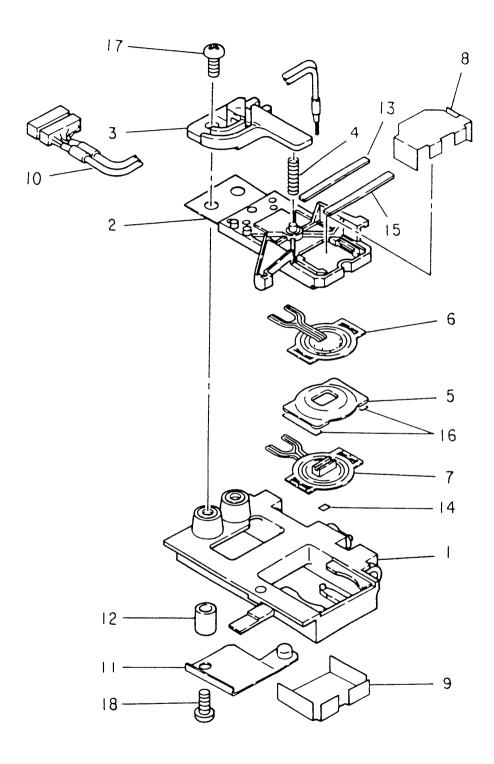

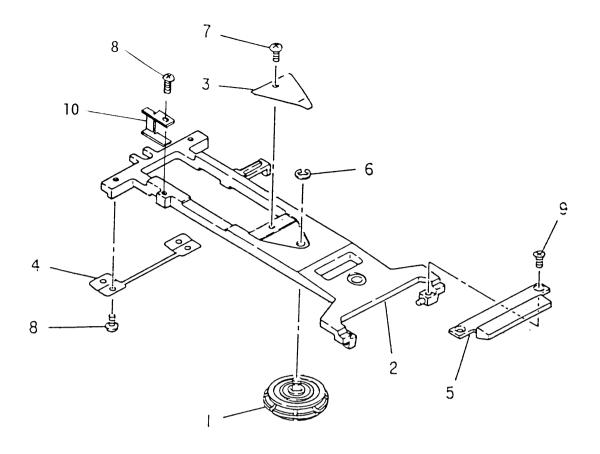

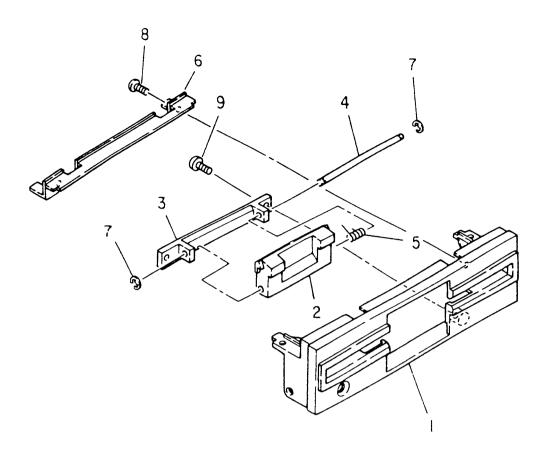

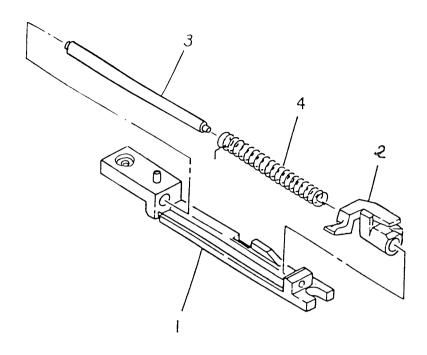

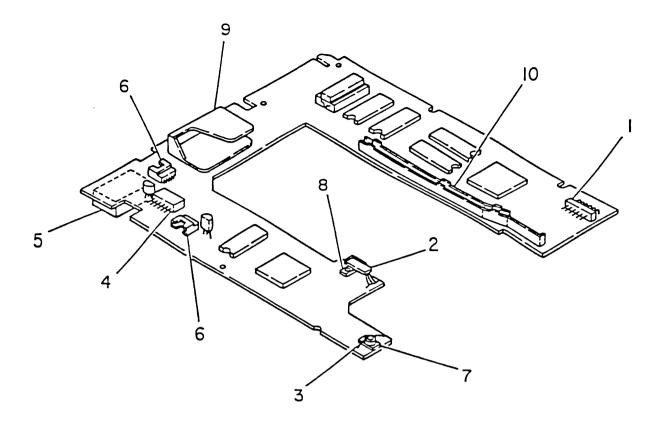

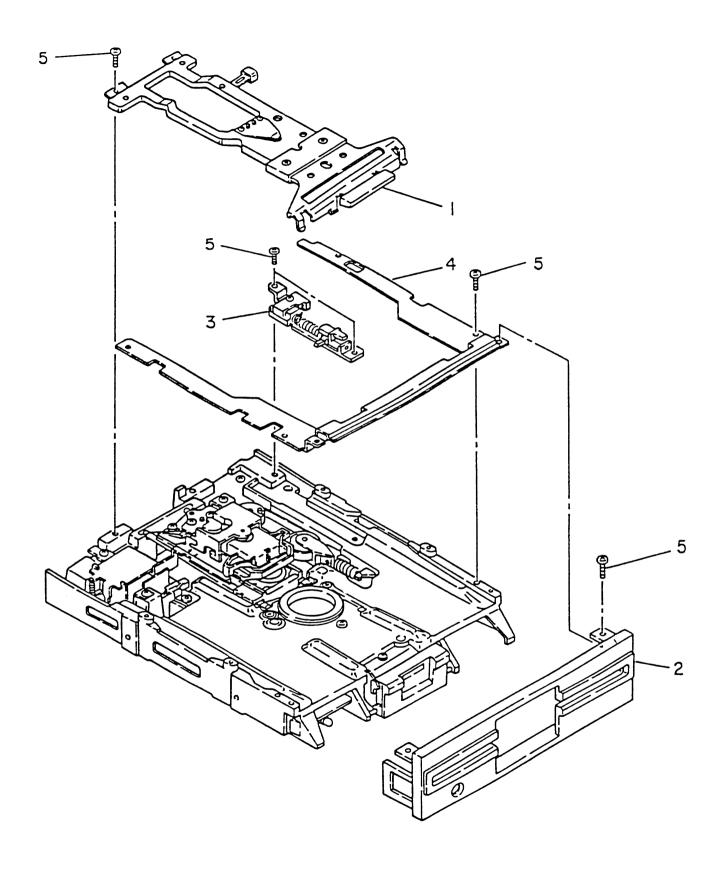

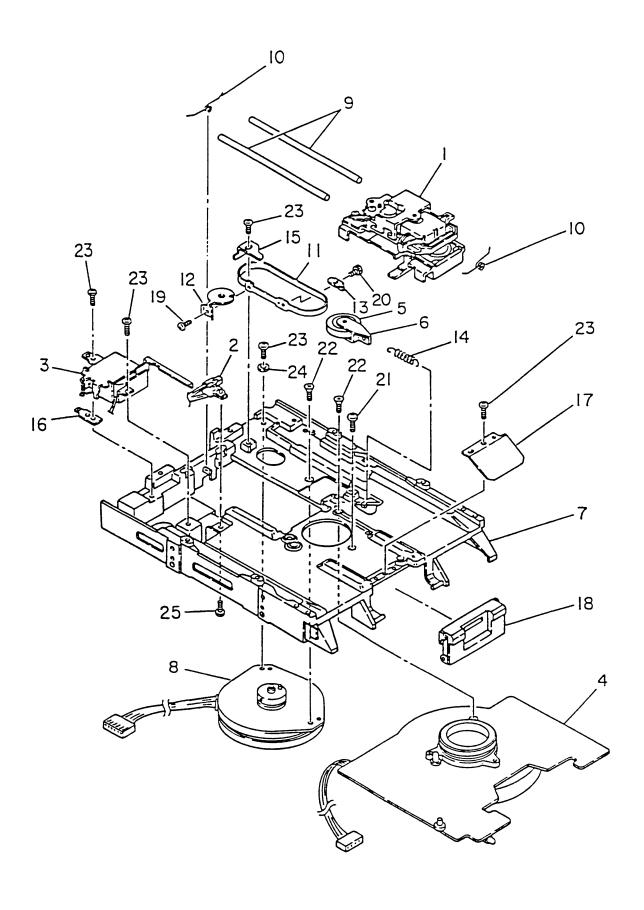

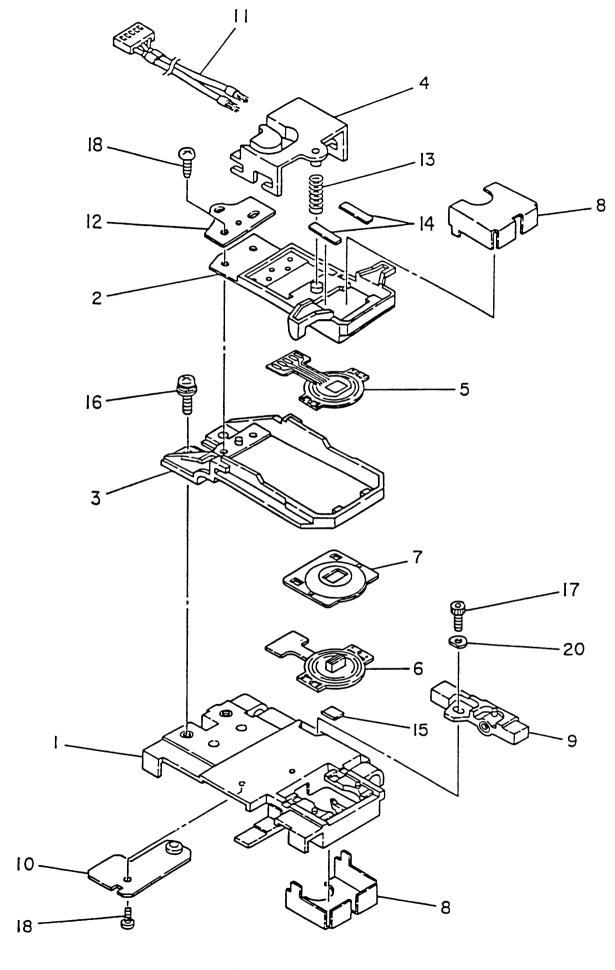

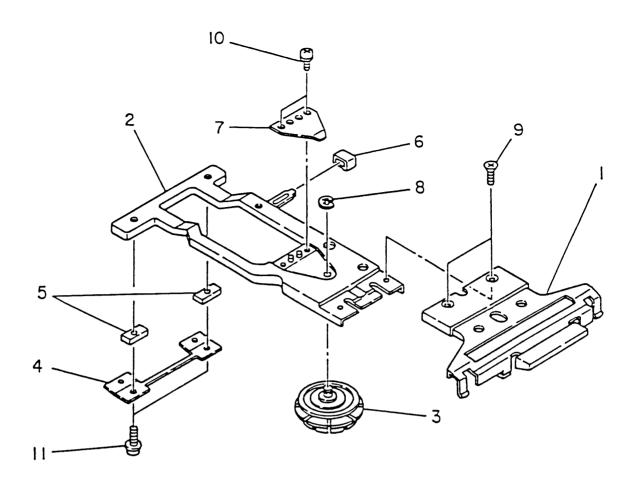

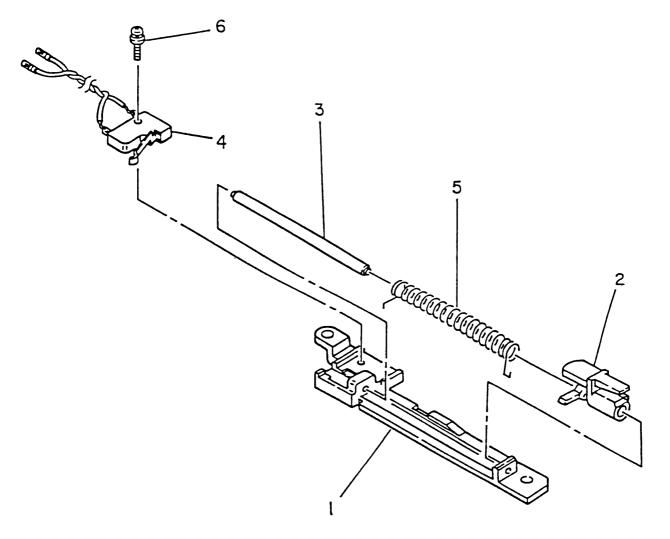

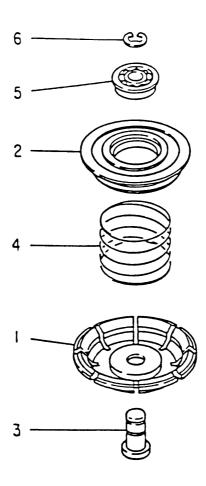

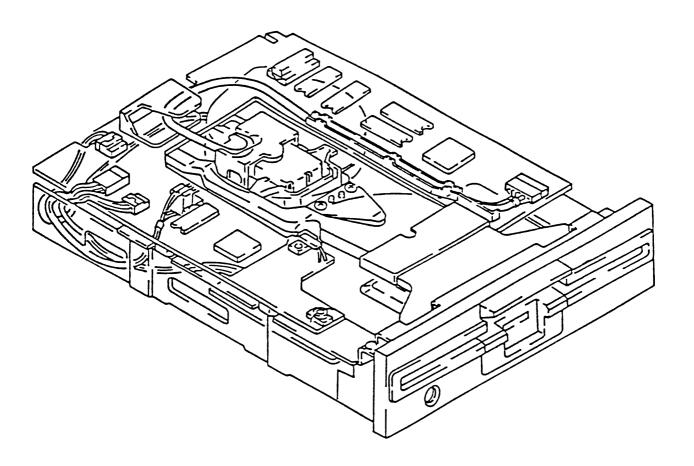

| 8/ Parts Lists/Exploded Views Main Logic Unit Assembly Power Supply Assembly (95W) Disk Drive Assemblies Card Cage Assembly Keyboard Assembly Display Unit                                                                                                                                                        | 232<br>234<br>236<br>238<br>24Ø               |

| 9/ Optional Features 9.1 Internal 128K Expansion RAM                                                                                                                                                                                                                                                              | 247<br>249                                    |

| 9.2 External Memory Board                                                                                                                                                                                                                                                                                         | 252                                           |

|    | Comp  | ponent Lay               | yout, 1          | 128/256K<br>28/256K E                         | xternal          | RAM      |      | <br>267 |

|----|-------|--------------------------|------------------|-----------------------------------------------|------------------|----------|------|---------|

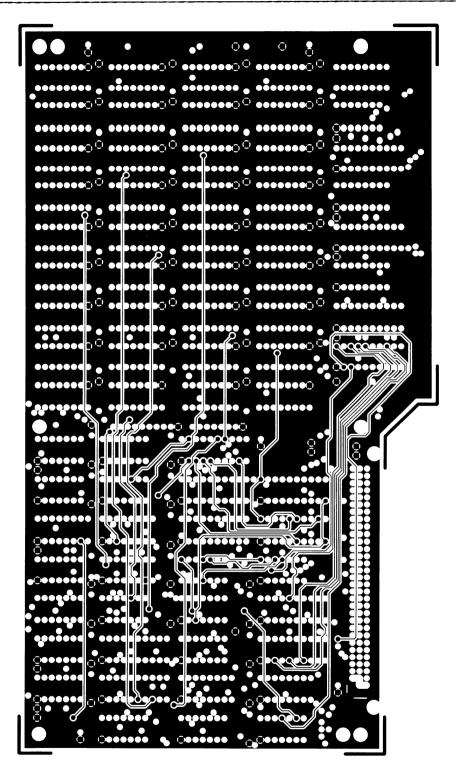

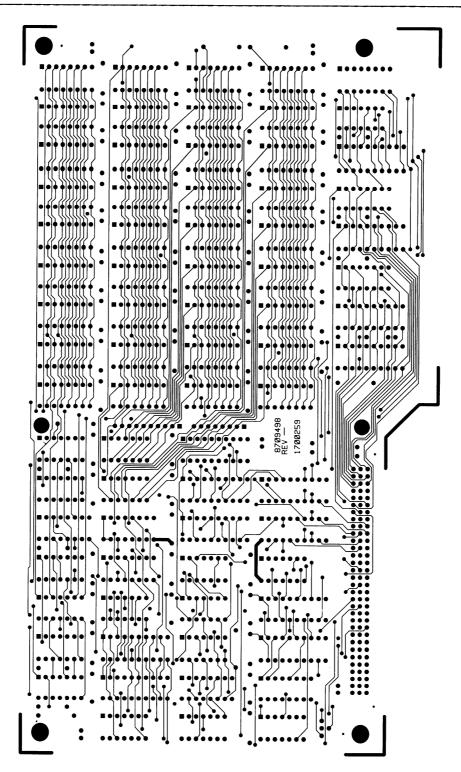

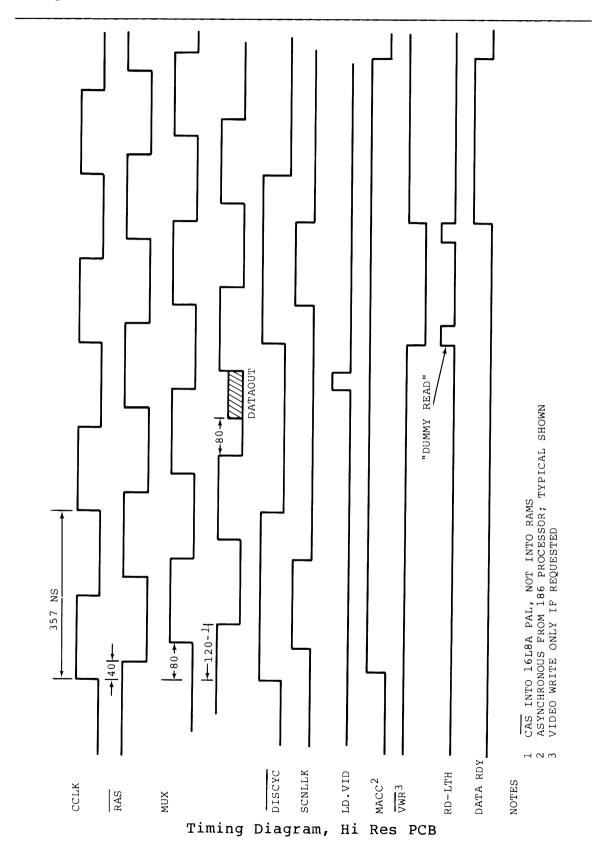

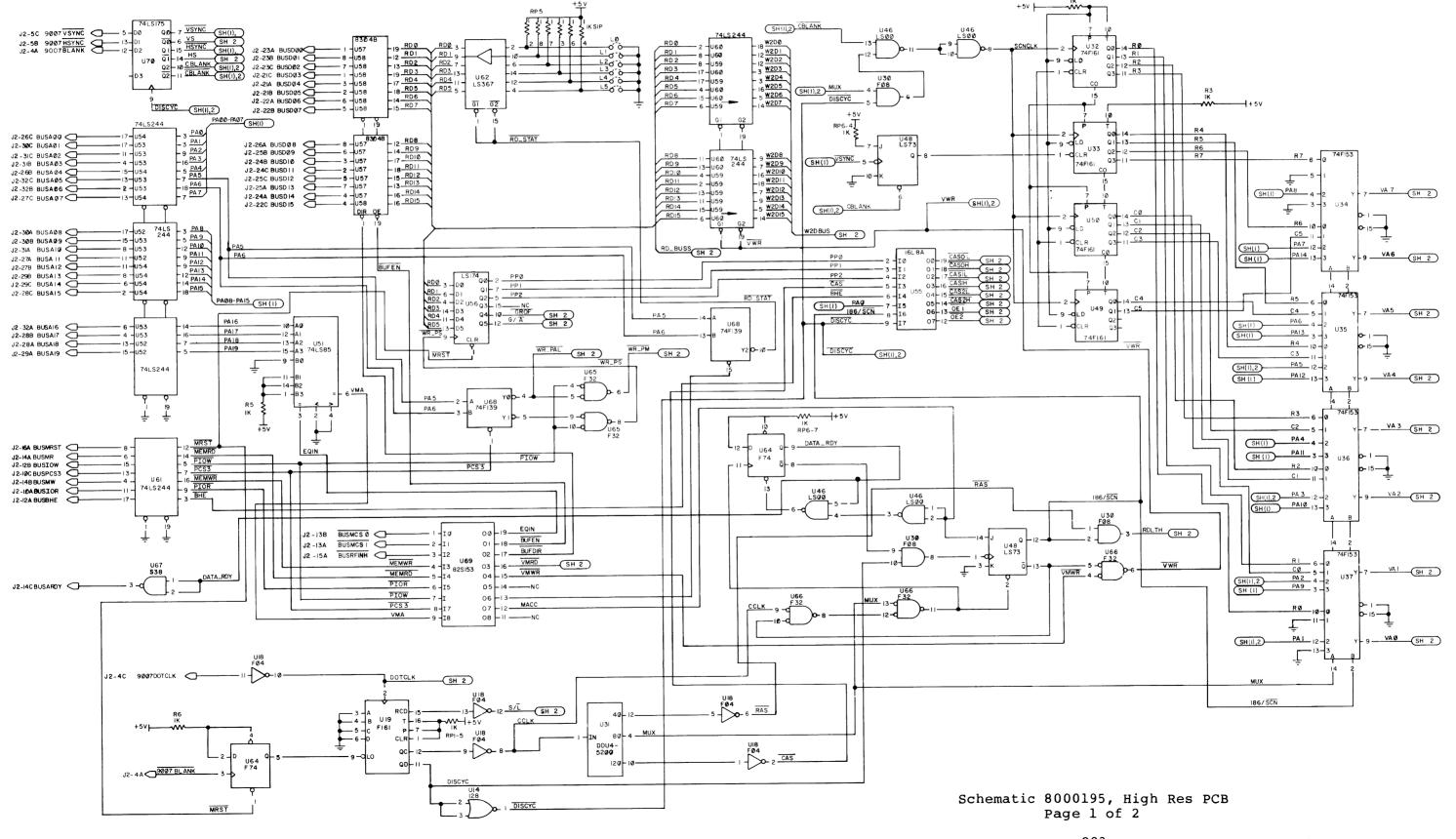

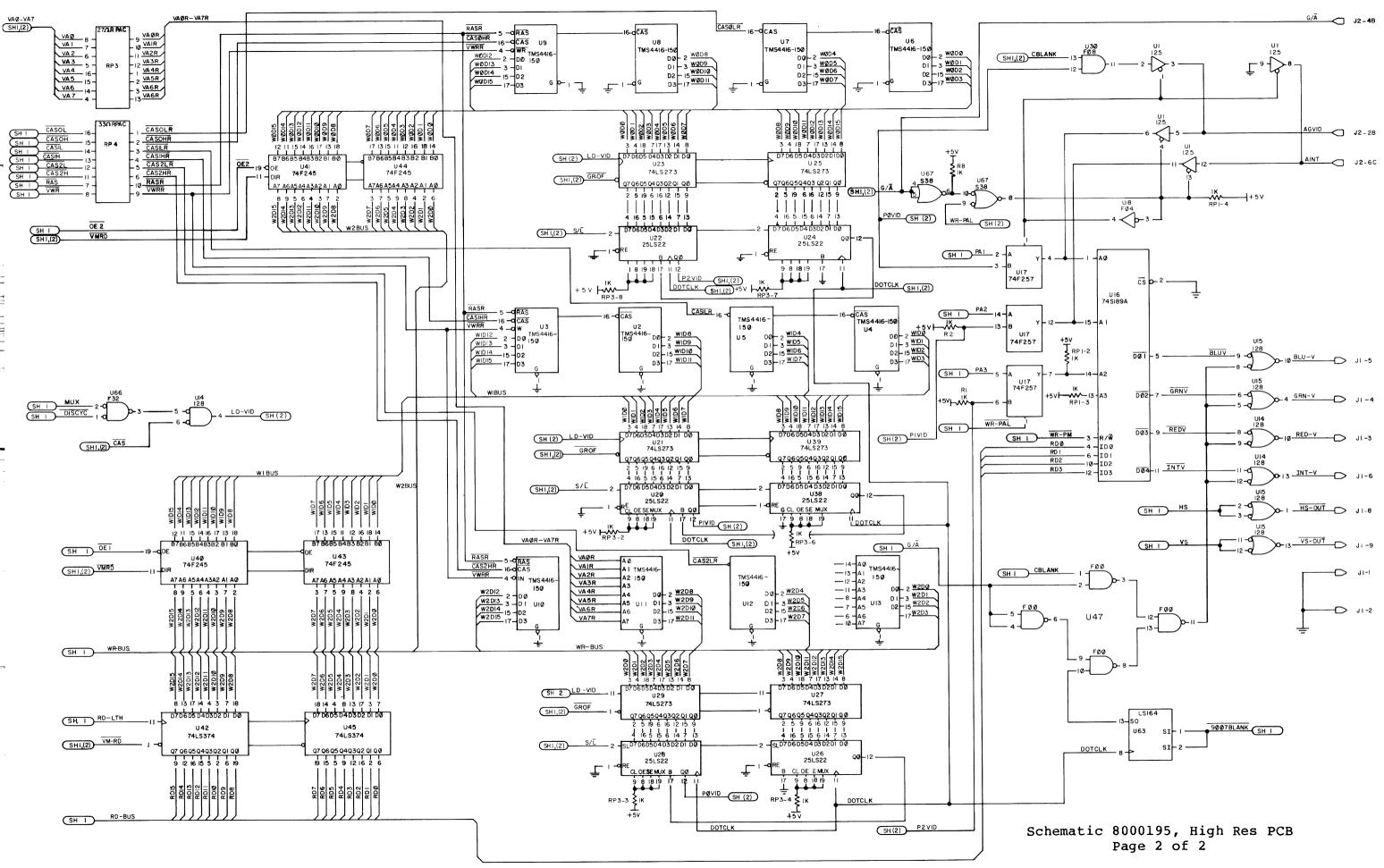

|    | Sch   | ematic 80)<br>ponent Loc | ØØ195,<br>cation | Graphics<br>Hi-Res Gr<br>1700261.<br>Graphics | aphics<br>Hi-Res | Graphics | 3    | <br>287 |

| Aj | ppend | lices                    |                  |                                               |                  |          |      |         |

|    | A/    |                          |                  | - Mitsubi<br>- Mitsubi                        |                  |          |      |         |

|    | B/    | Service 1                | Manual           | - Tandon                                      | Hard Di          | sk Drive | 9    |         |

|    | C/    | Intel Co                 | cporati          | on Specif                                     | ication          | Sheets   |      |         |

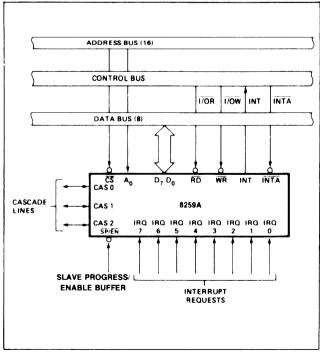

|    |       | iAPX186<br>8272          | 8259             | 8251                                          | 8Ø               | 87       | 8253 | 8253    |

|    | D/    | Standard<br>Specifica    |                  | ystems Co<br>heets                            | rporati          | on       |      |         |

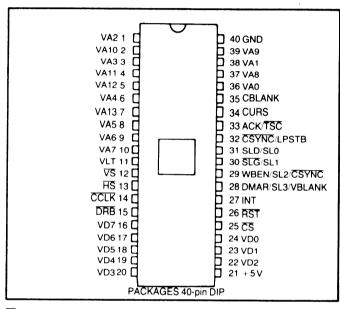

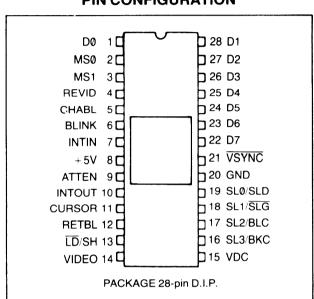

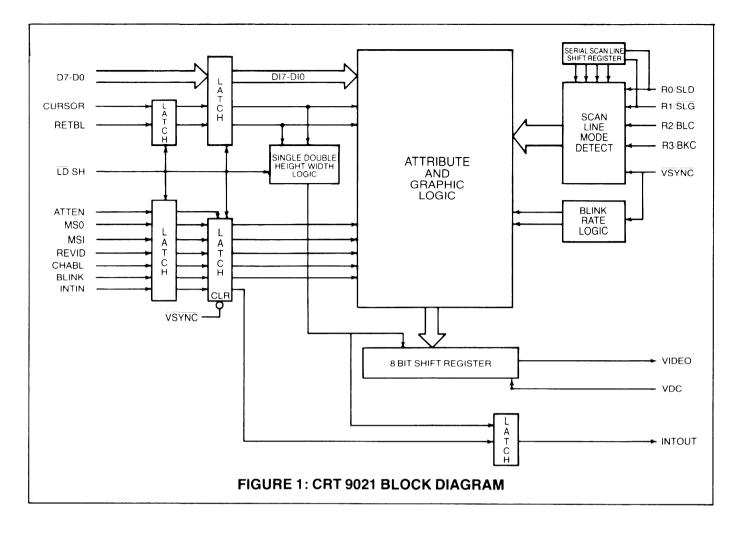

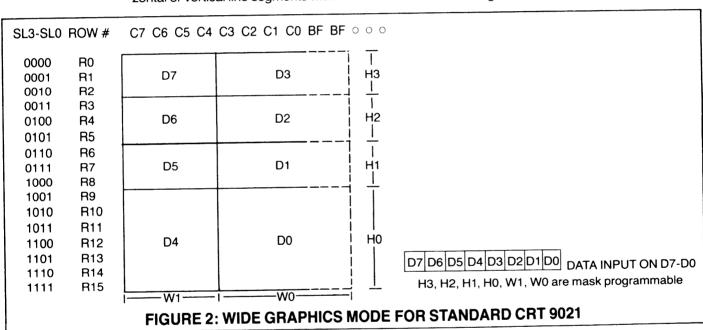

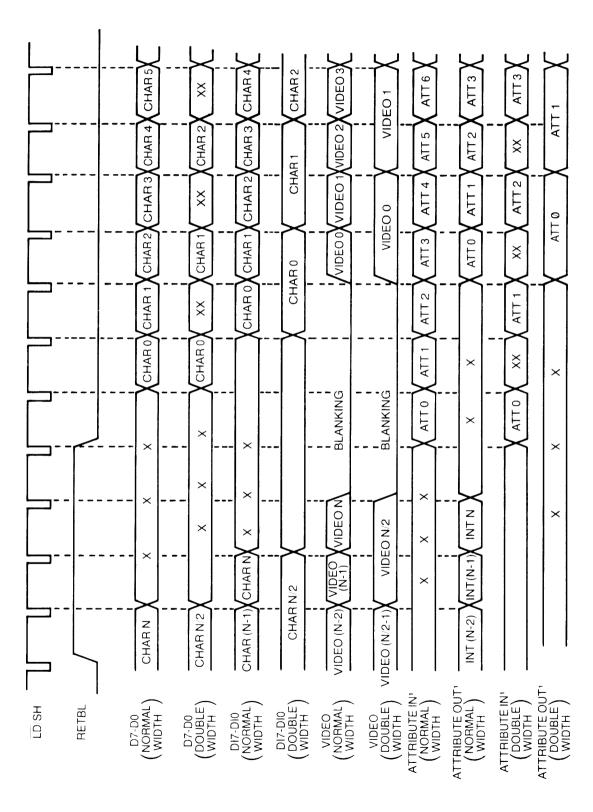

|    |       | 9ØØ7                     | 9212             | 9Ø21                                          | 92               | 16B      |      |         |

|    | E/    | Model 200                | ØØ Port          | Specific                                      | ations           |          |      |         |

# List of Figures

| Fig. | No. | Description                           | Page    | No.        |

|------|-----|---------------------------------------|---------|------------|

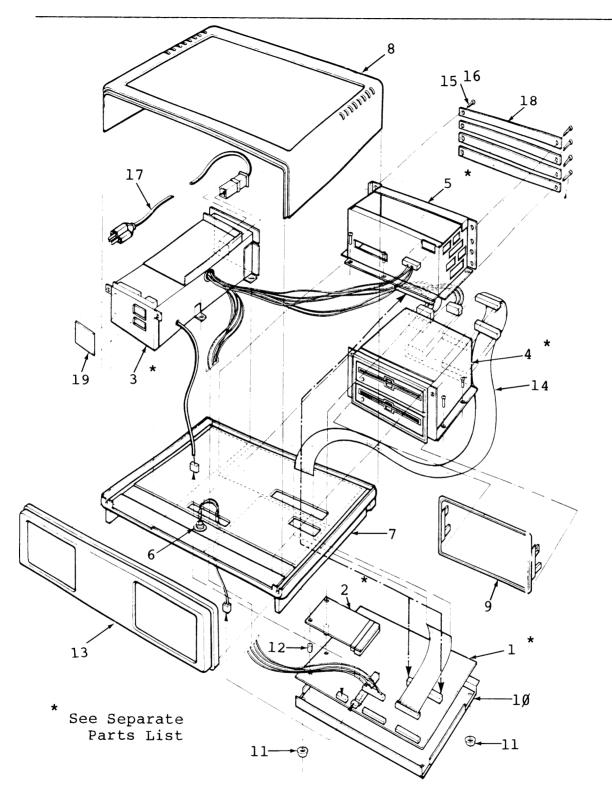

| 1    | .1  | Model 2000 Computer Assembly          |         | 2          |

| 1    | . 2 | Model 2000 Major Copmponent Subassemb | olies   | 3          |

|      | . 3 | External Plug-in Option Cards         |         | 6          |

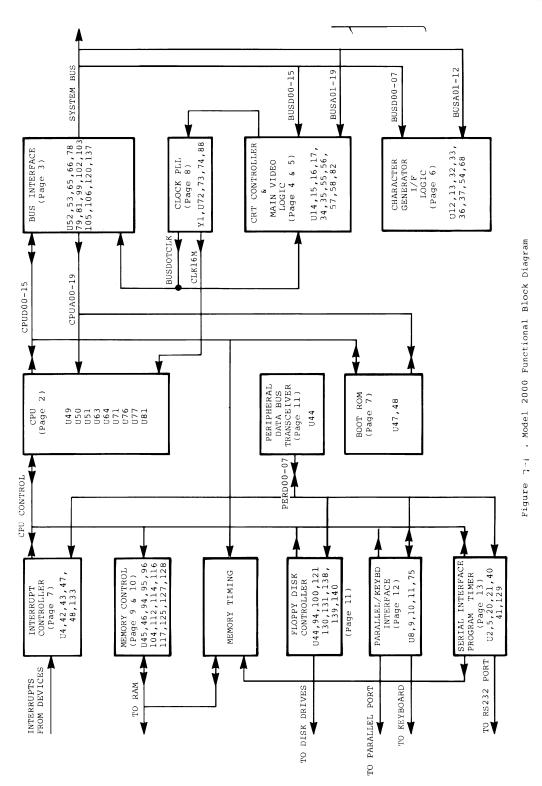

| 7    | .1  | Model 2000 Functional Block Diagram . |         | 42         |

|      | .la | CPH Block Diagram                     |         | 45         |

|      | . 2 | 80186 Programmed Chip Selects         |         | 46         |

|      | . 3 | Peripheral Chip Select 0 Address      |         | 47         |

|      | . 4 | DMA Acknowledge Address Assignments   |         | 47         |

|      | .5  | DMA Channel Control REgister          |         | 49         |

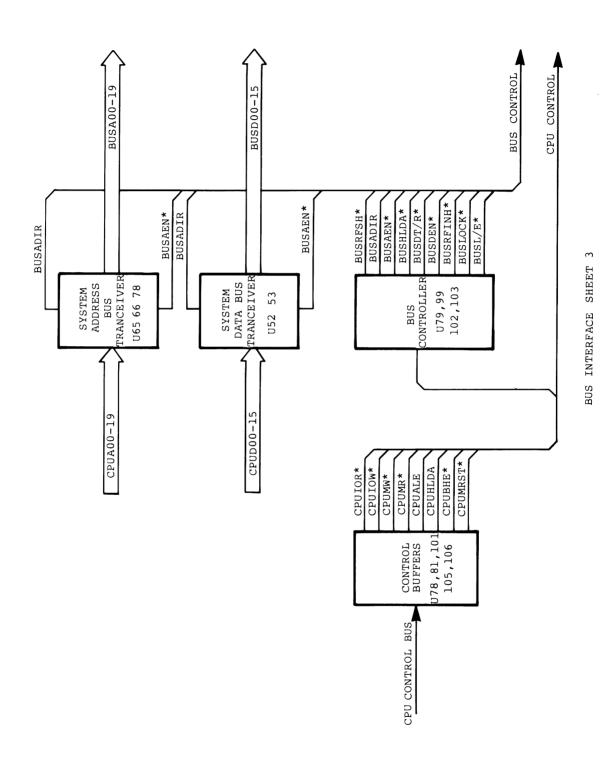

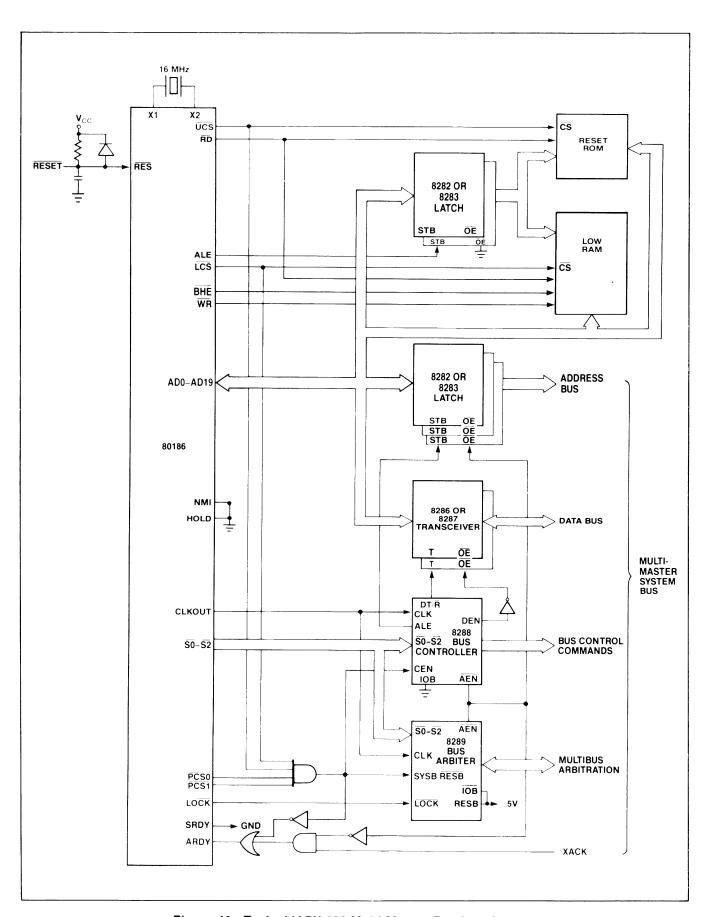

|      | .6  | Bus Interface Block Diagram           |         | 51         |

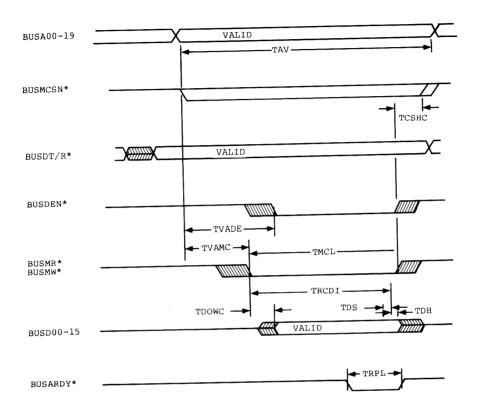

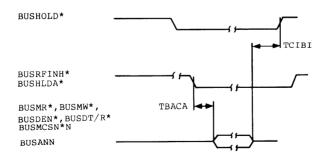

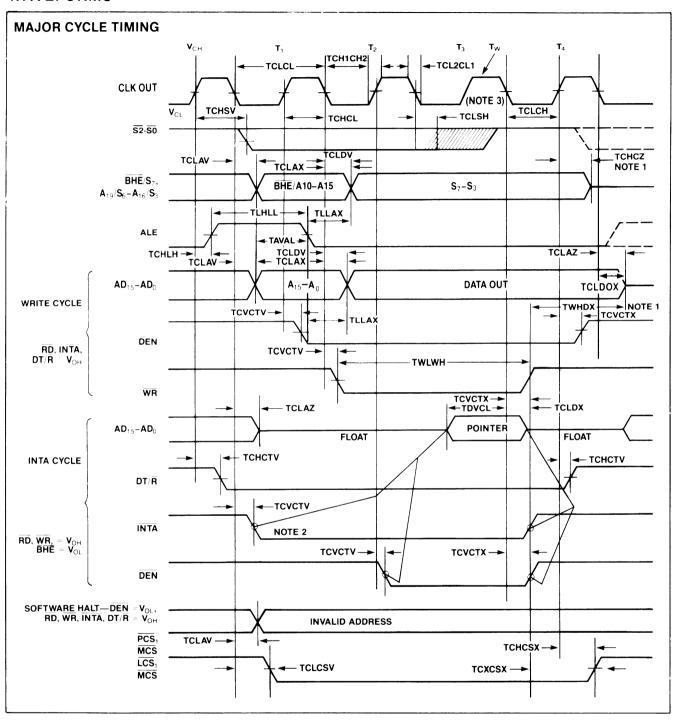

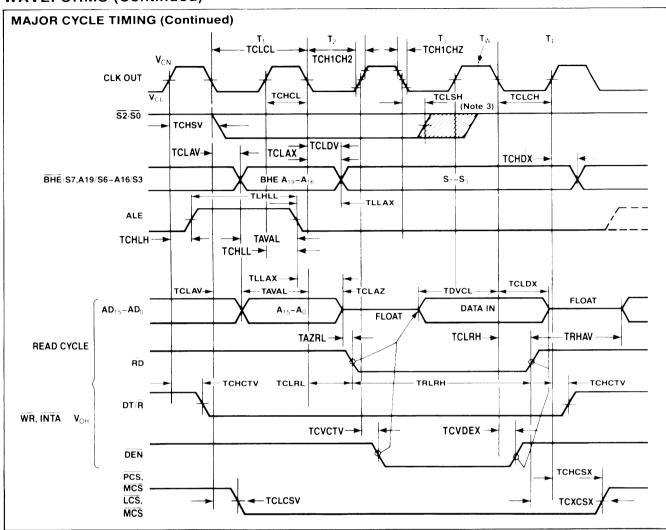

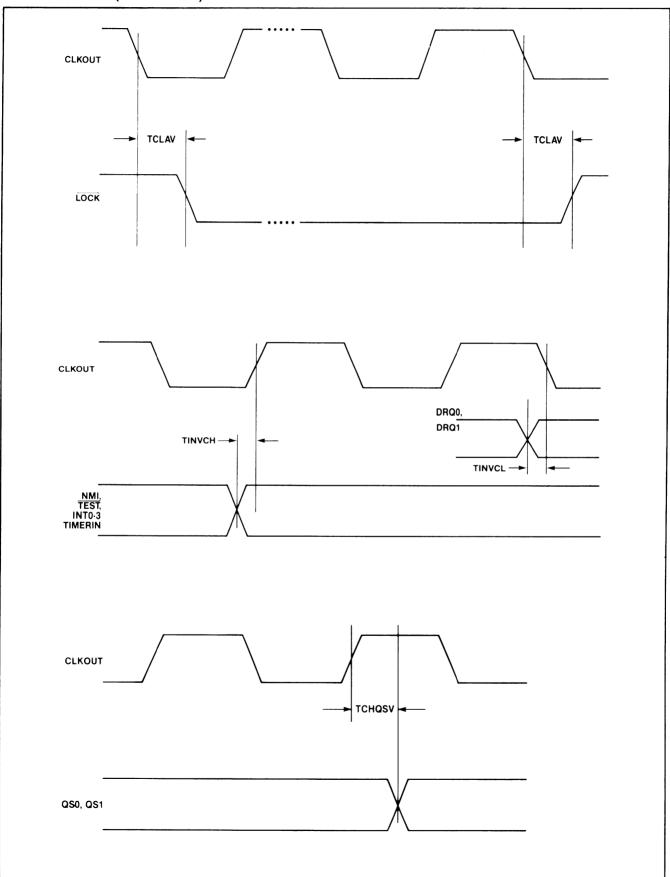

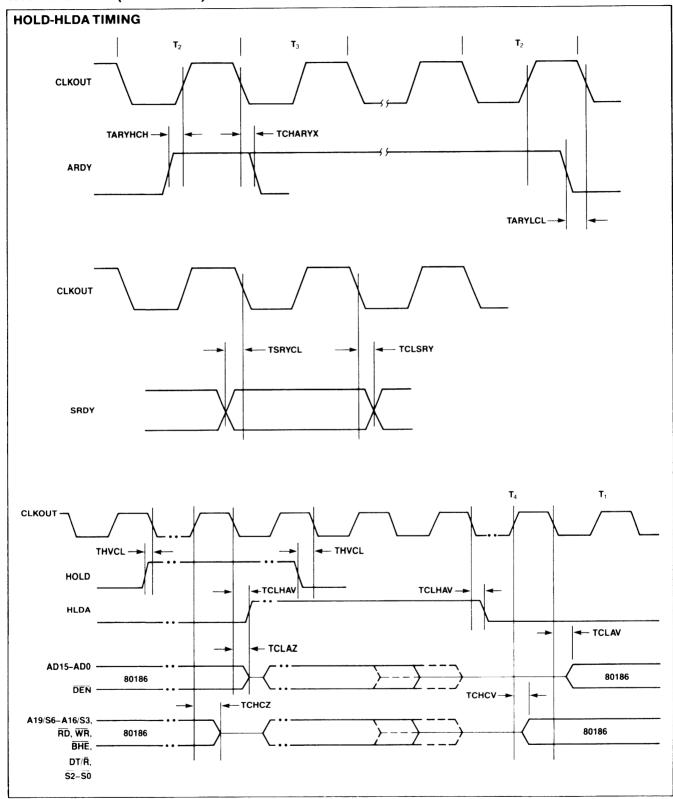

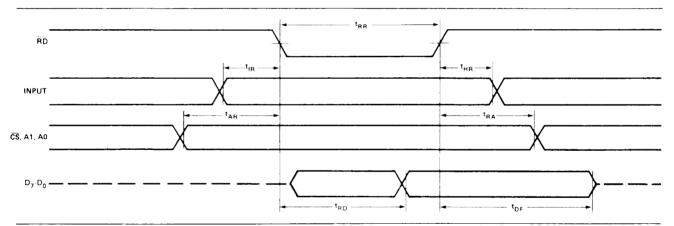

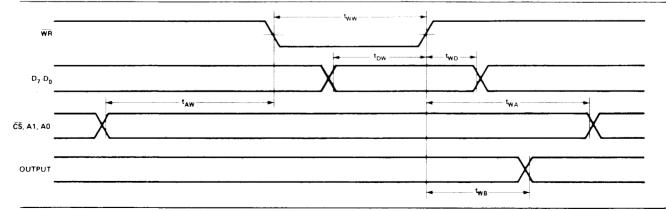

| 7    | . 7 | Timing Parameter Diagram              |         | 57         |

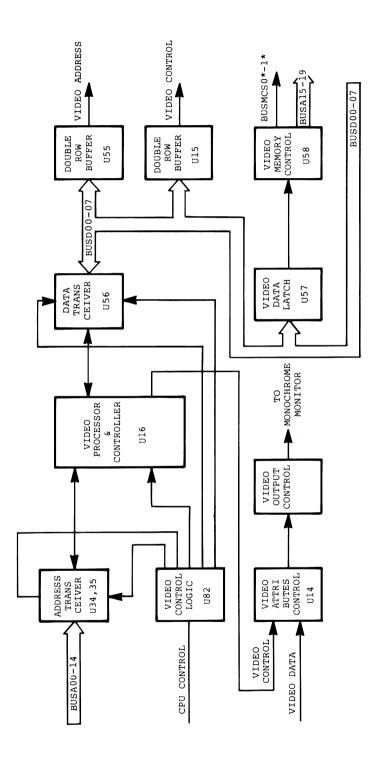

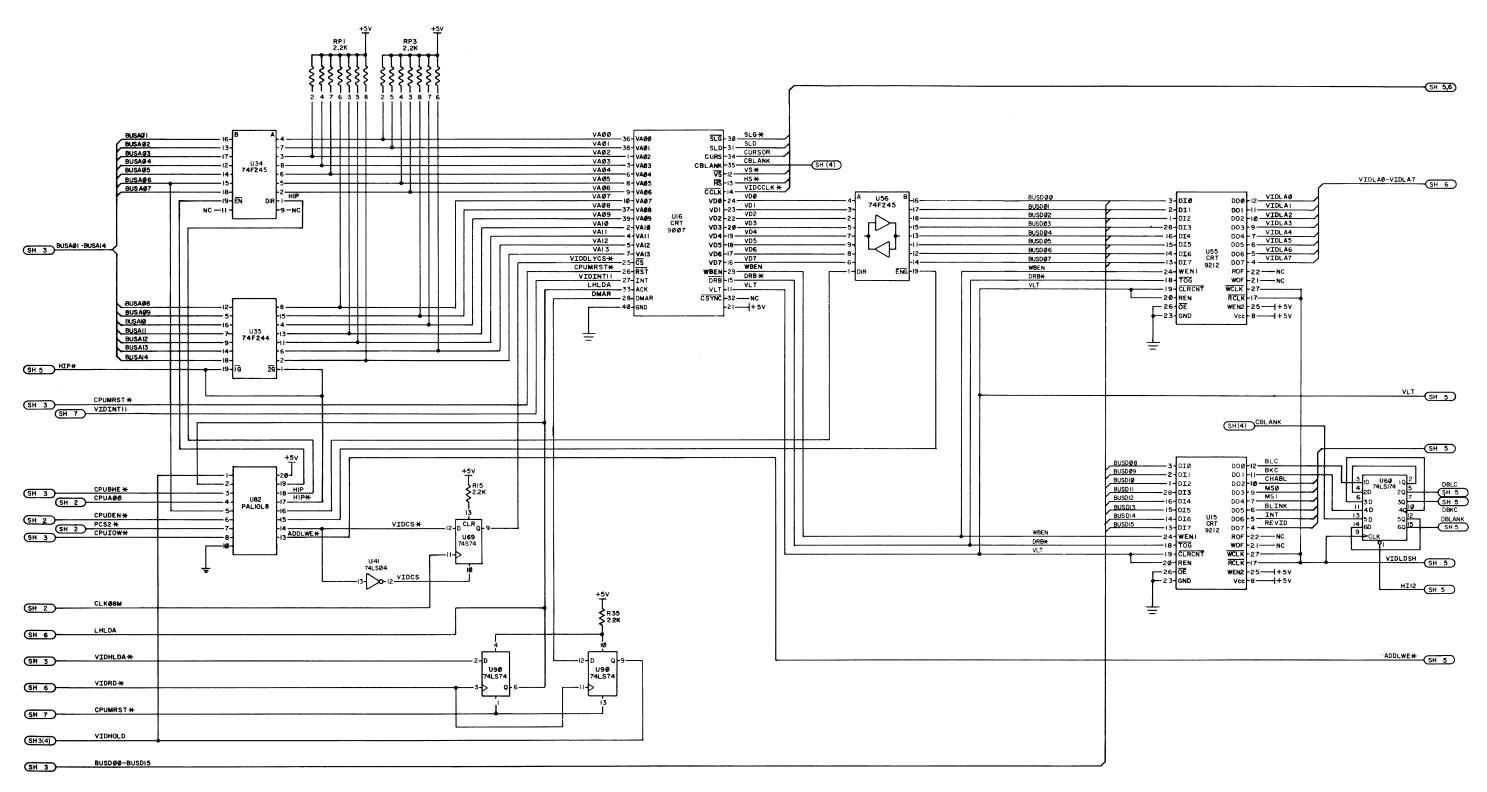

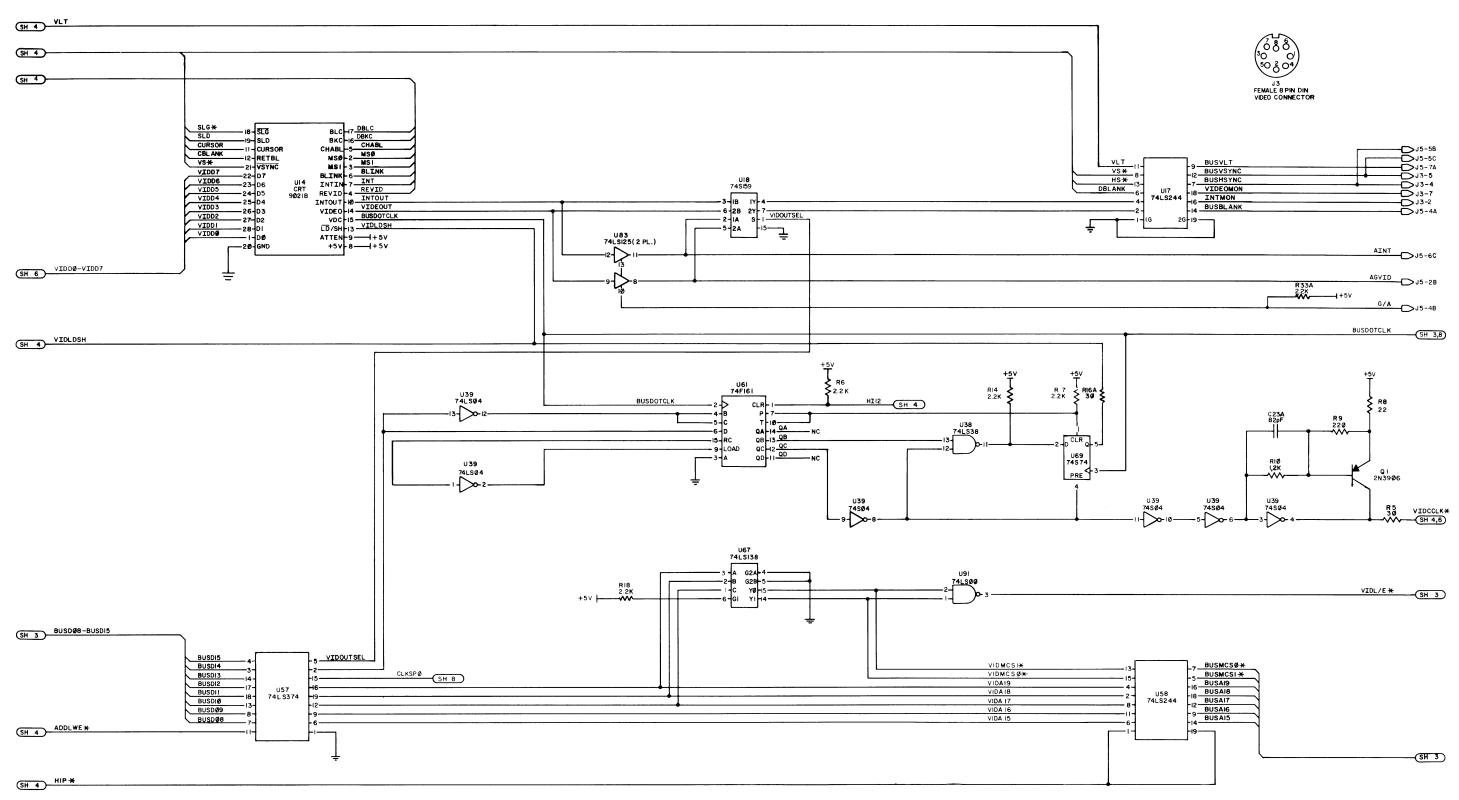

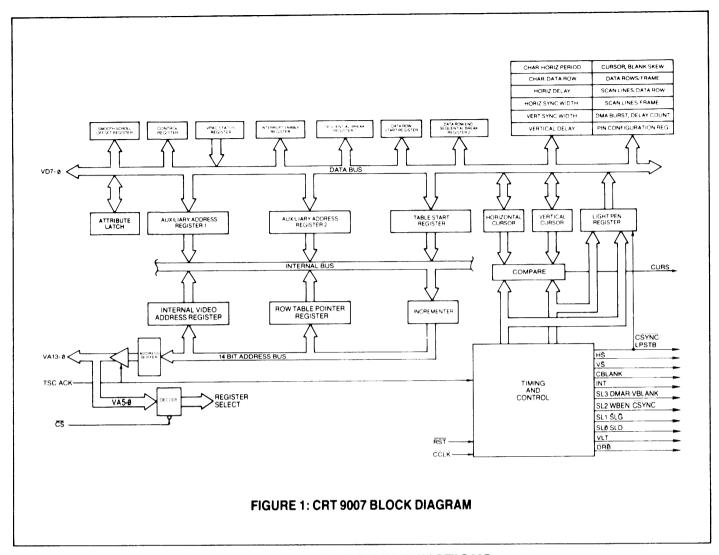

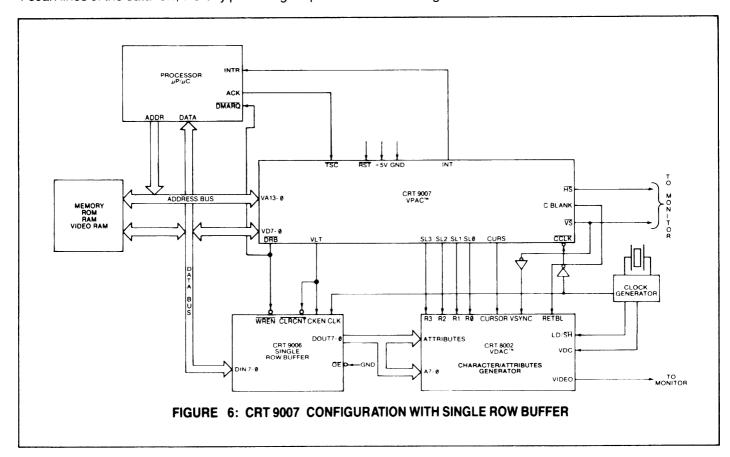

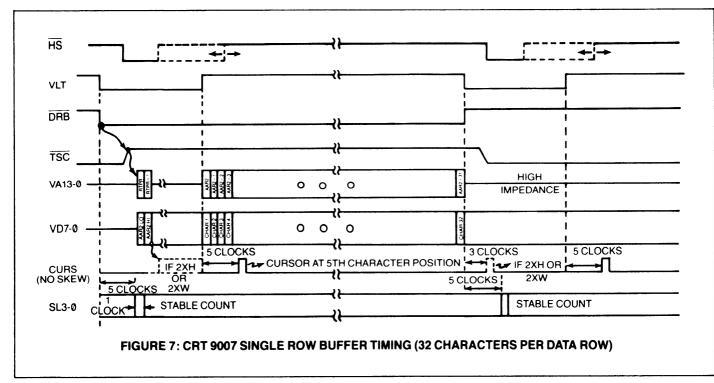

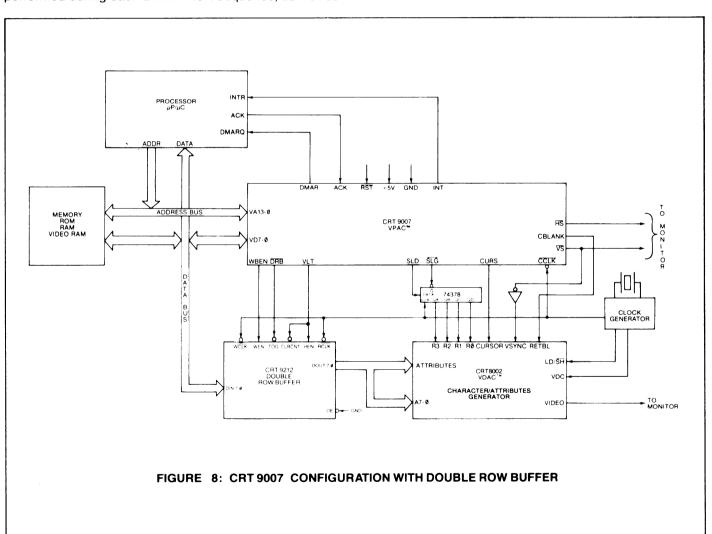

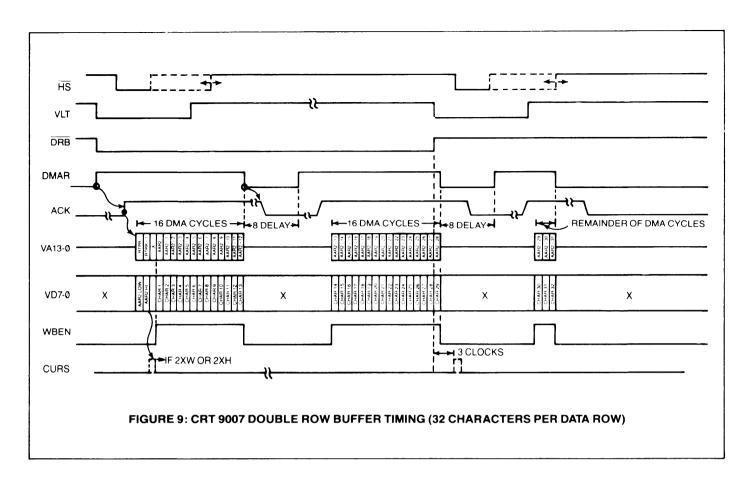

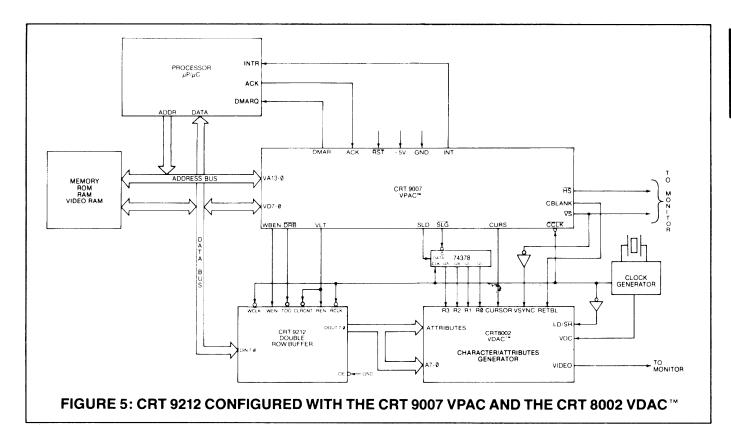

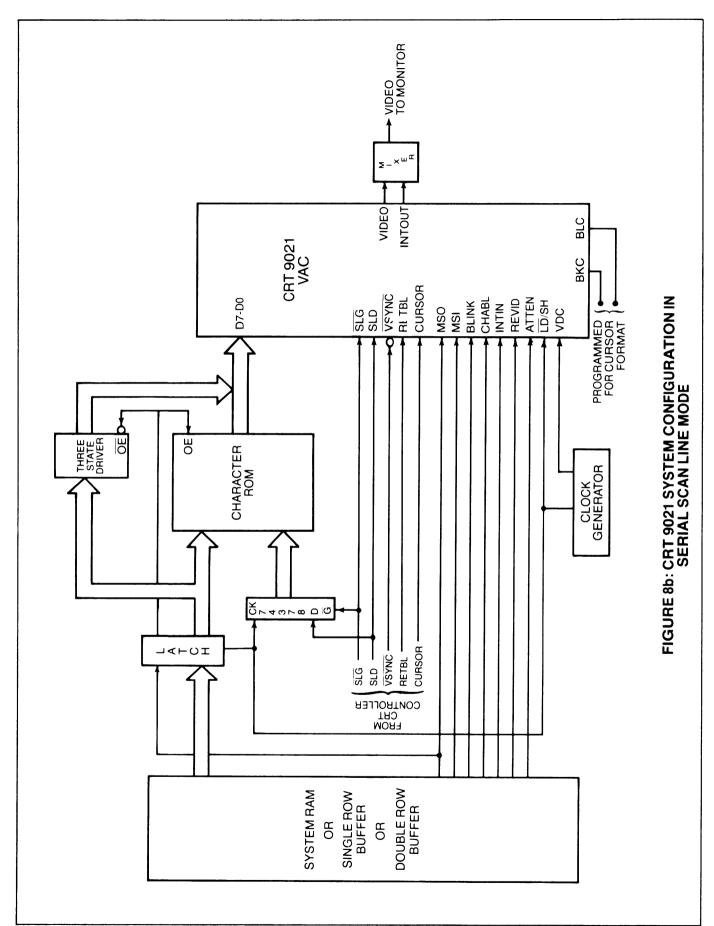

|      | . 8 | CRT Controller/Main Video Logic       |         | 59         |

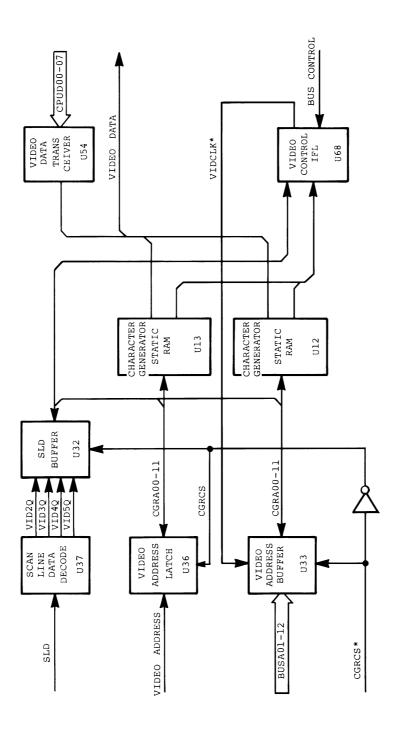

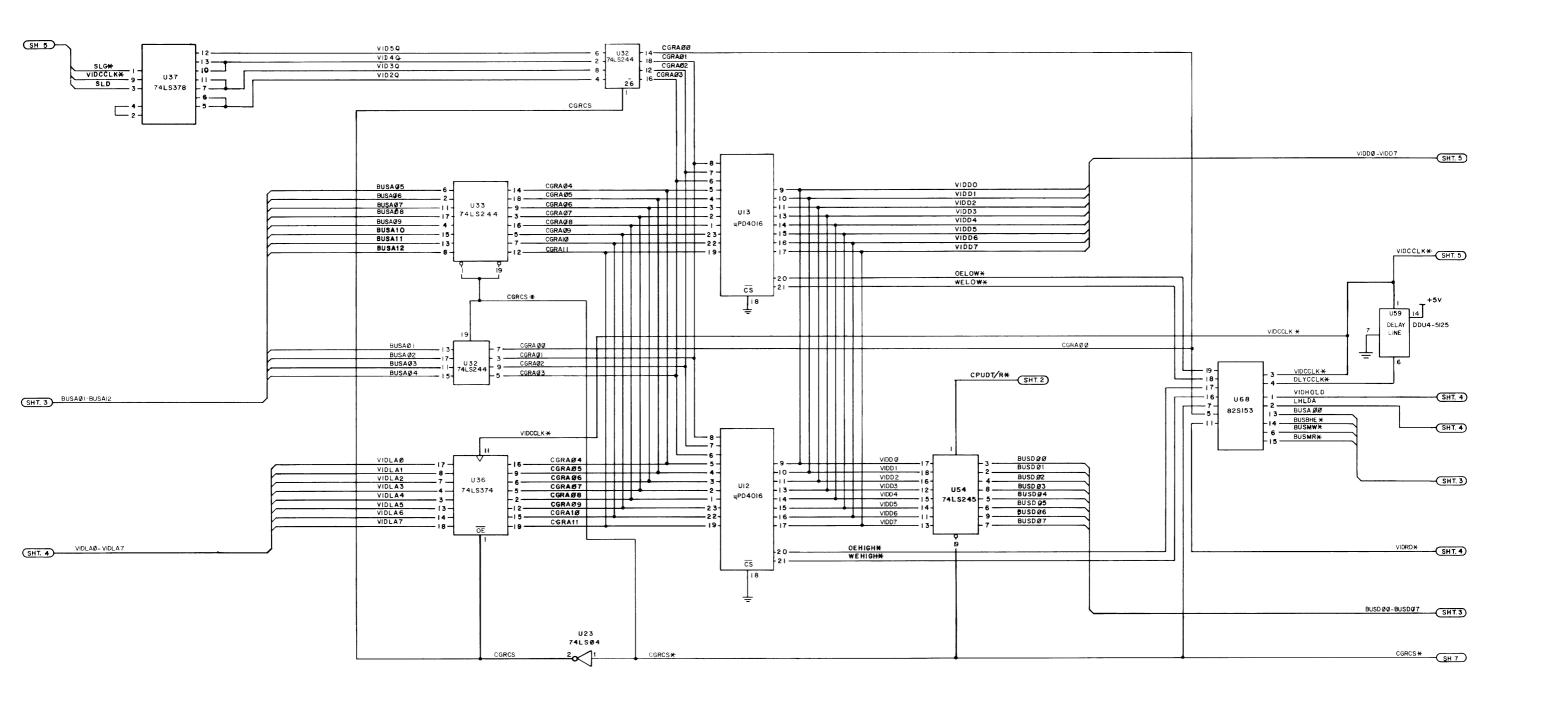

|      | . 9 | Character Generator                   |         | 67         |

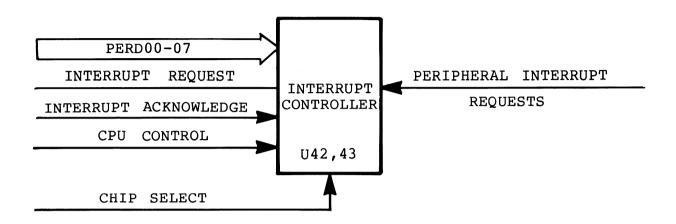

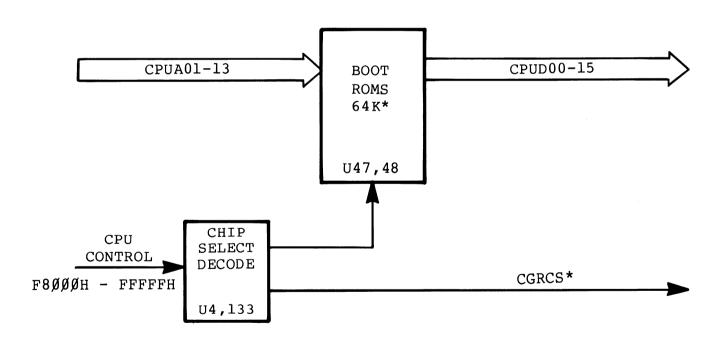

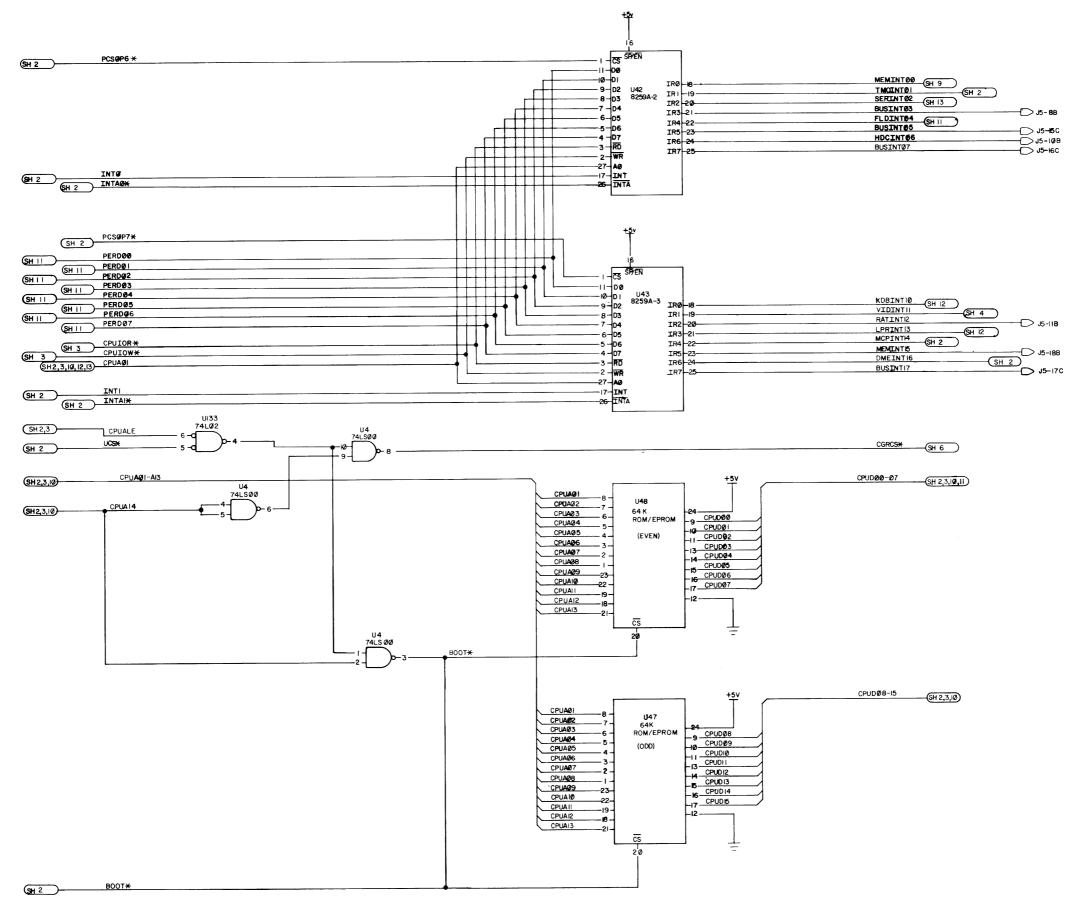

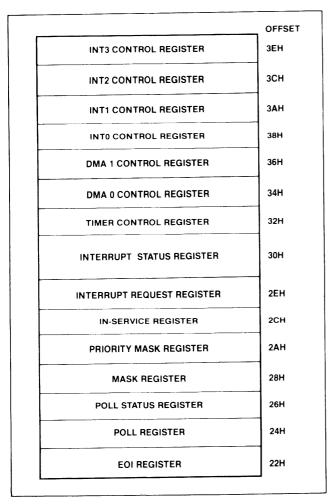

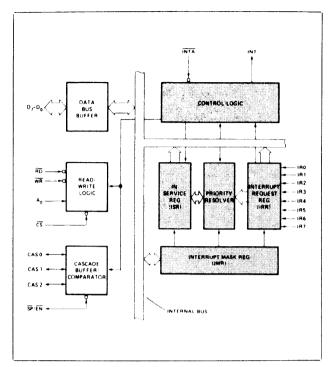

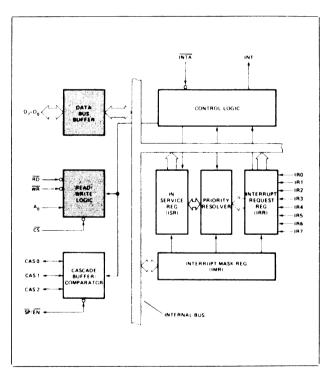

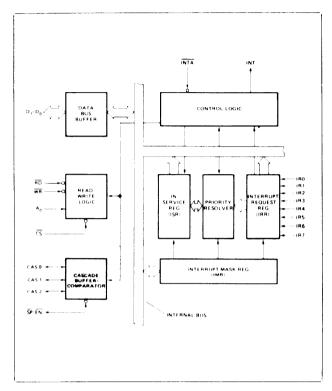

| 7    | .10 | Interrupt Controller/Boot ROM         | • • • • | 69         |

| 7    | .11 | Interrupt Controller Register Assignm | nents   | 70         |

| 7.   | /12 | Interrupt Controller Input Assignment | ts .    | 71         |

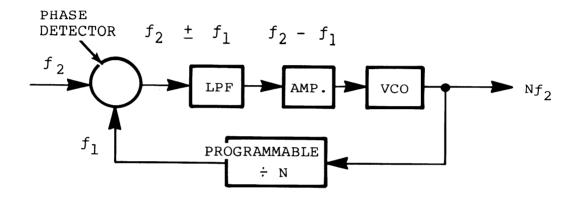

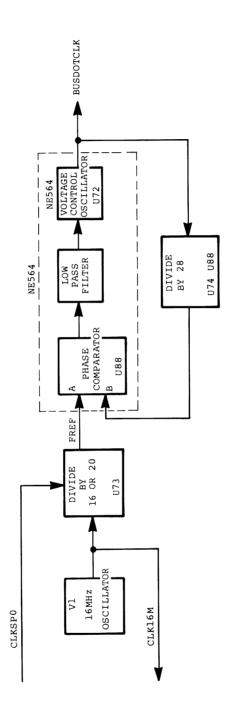

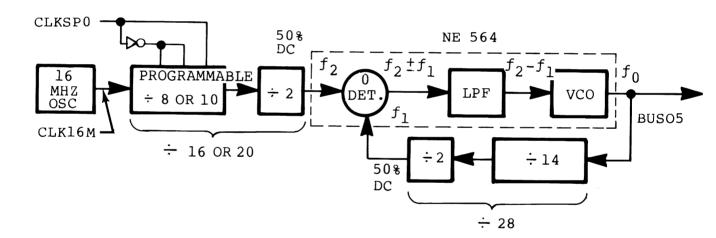

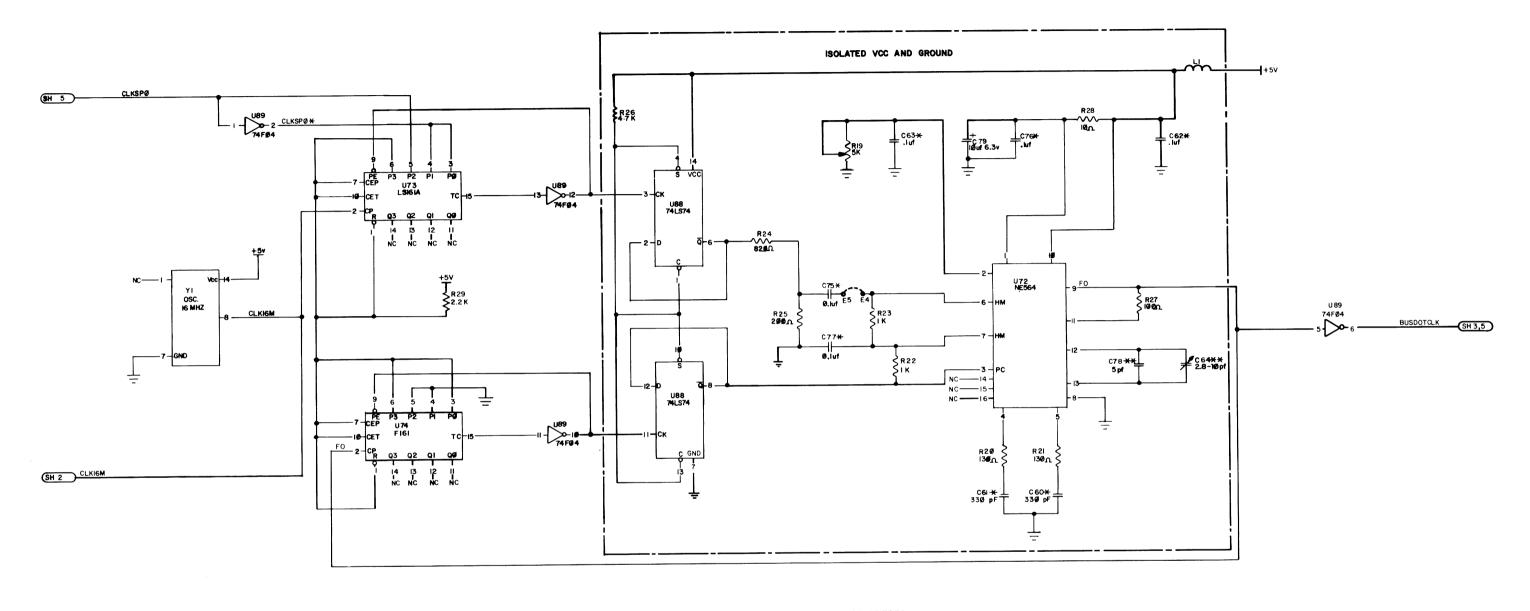

| 7    | .13 | Block Diagram, Clock/PLL              |         | 72         |

| 7    | .14 | Block Diagram, Clock/PLL (sheet 8) .  | • • • • | 73         |

| 7    | .15 | Model 2000 PLL Block Diagram          | • • • • | 74         |

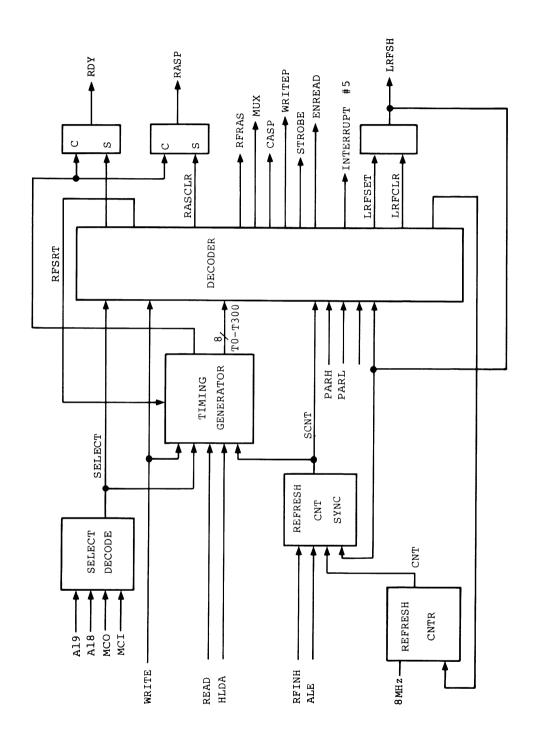

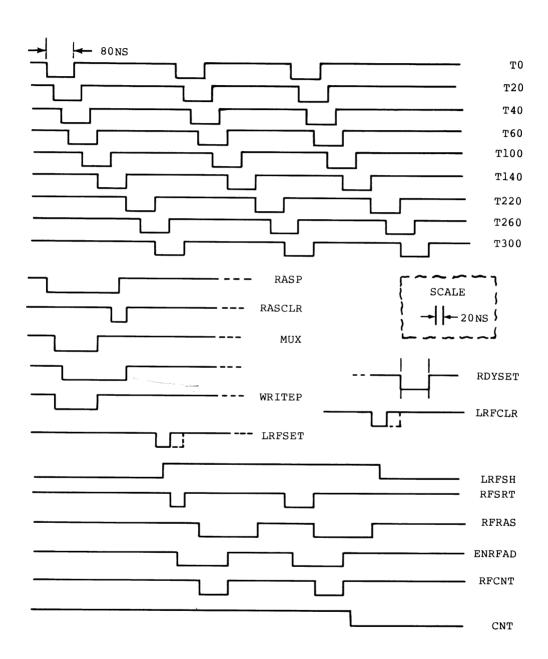

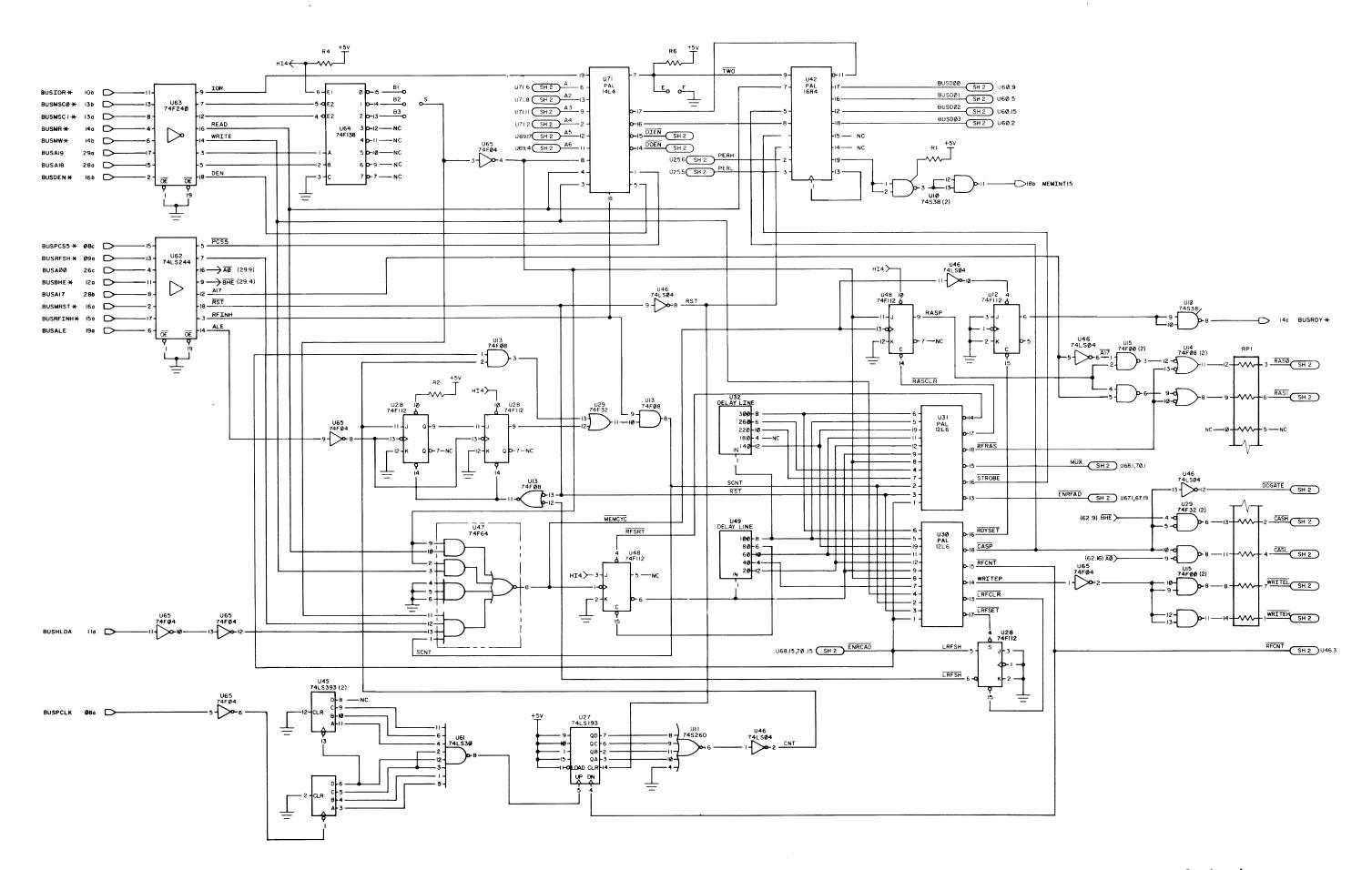

| 7    | .16 | Memory Timing and Control             |         | 78         |

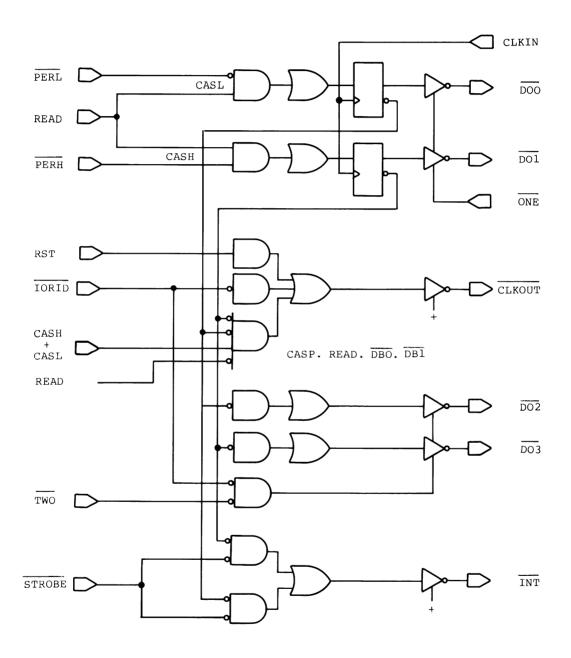

|      | .17 | RAM Controller IFL Output Definitions | s       | 79         |

| 7    | .18 | Floppy Disk Controller                |         | 84         |

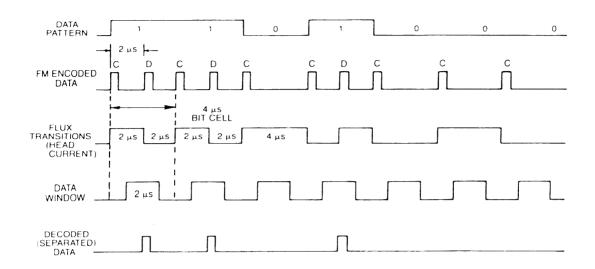

|      | .19 | FM Encoding Scheme                    | • • • • | 87         |

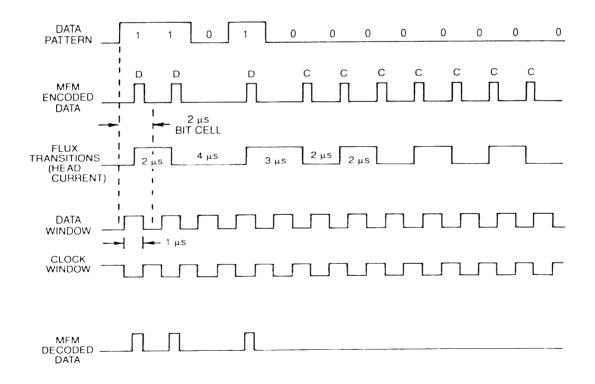

|      | .20 | MFM Encoding Scheme                   | • • • • | 87         |

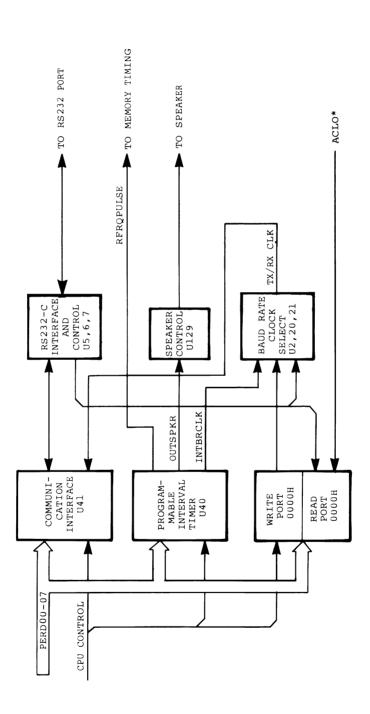

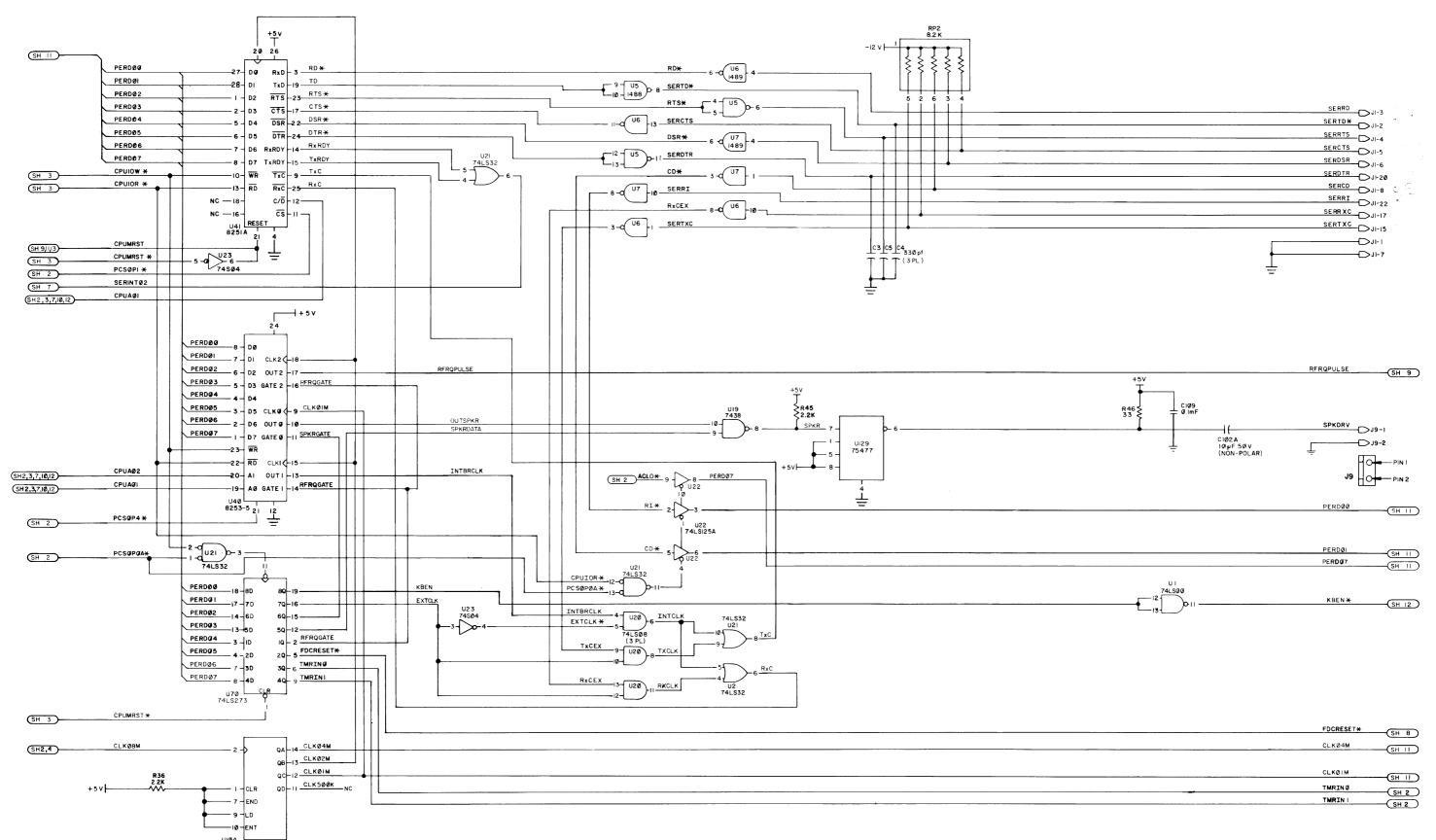

|      | .21 | Serial Interface/Programmable Timer   |         | 88         |

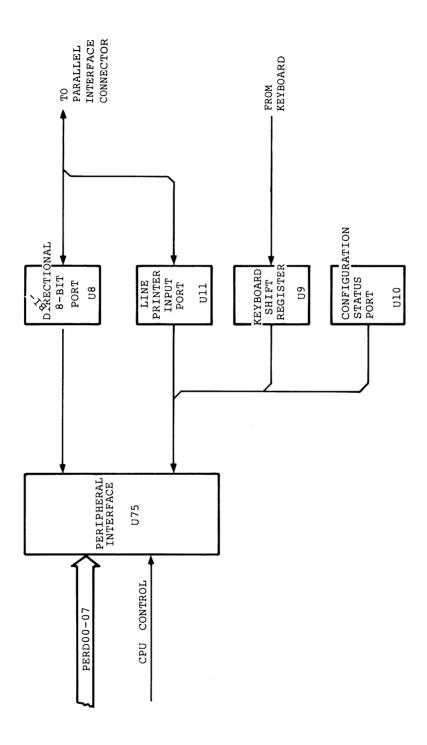

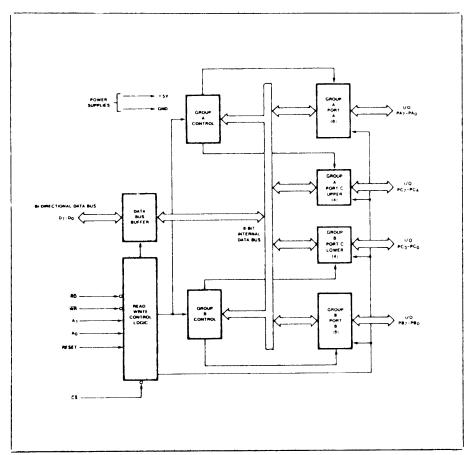

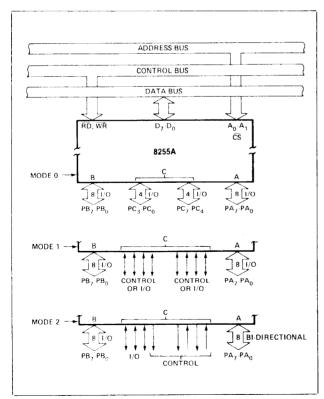

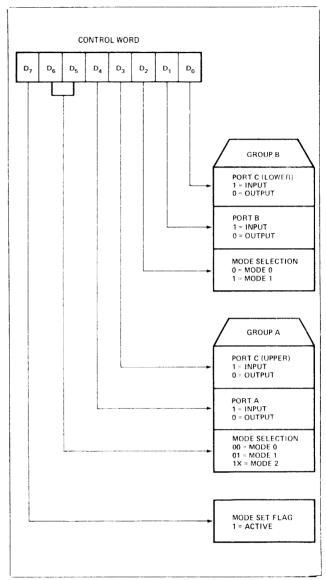

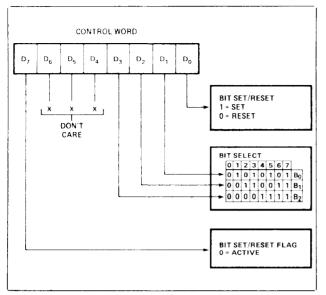

|      | .22 | Parallel/Keyboard Interface           |         | 93         |

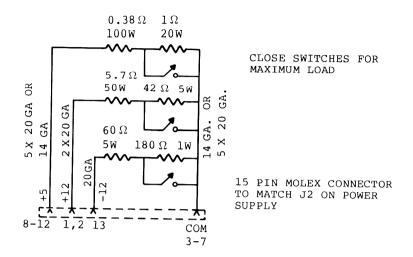

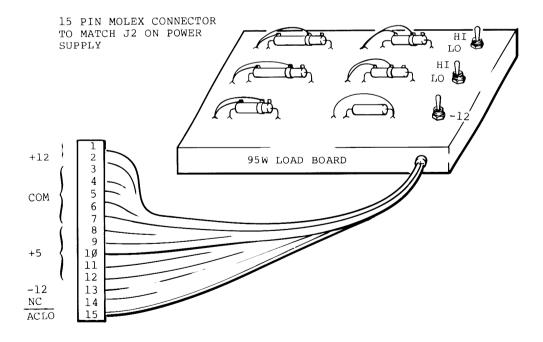

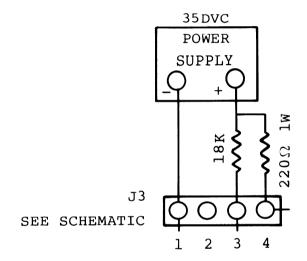

|      | .23 | Load Box                              |         | 147        |

|      | .24 | Load Box Assembly                     |         | 147        |

|      | .25 | Test Circuit                          |         | 148<br>148 |

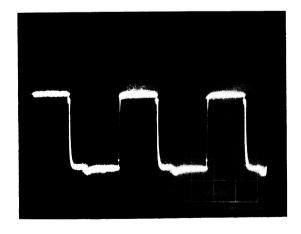

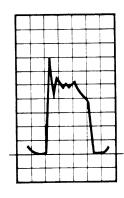

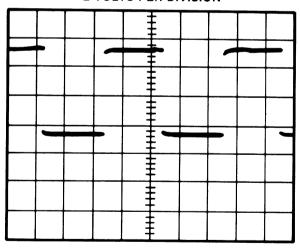

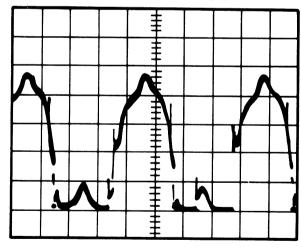

|      | .26 | Waveform                              | •       | 149        |

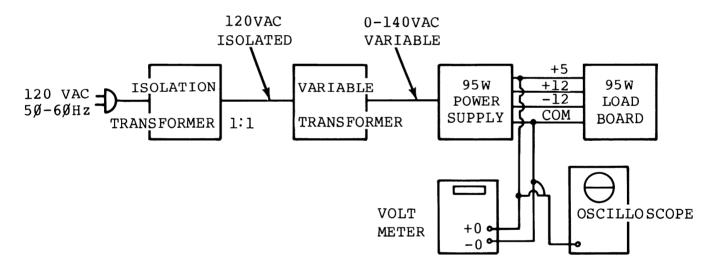

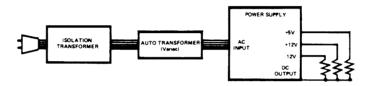

|      | .27 | Test Equipment Setup                  |         |            |

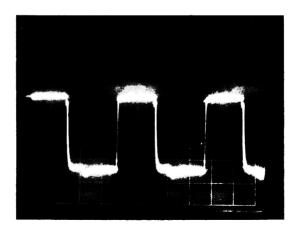

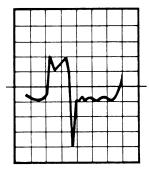

|      | .28 | Base of Q15                           |         | 150        |

|      | .29 | Q15 Collector Waveform                |         | 151        |

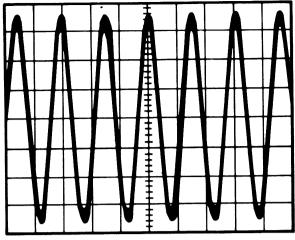

|      | .30 | Waveform of U3, Pin 8                 |         | 151        |

|      | .31 | Chip Oscillator, Pin 5                |         | 152        |

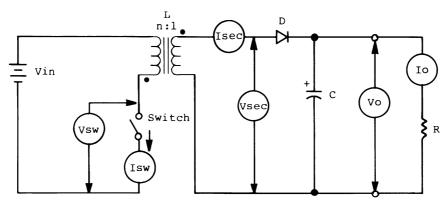

| 7    | .32 | Basic Flyback Converter               | • • • • | 153        |

# List of Figures

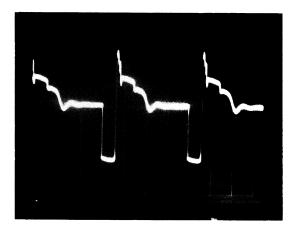

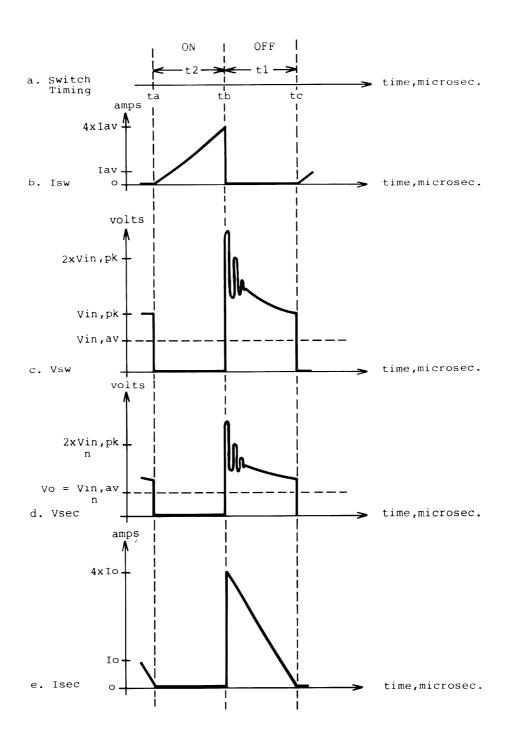

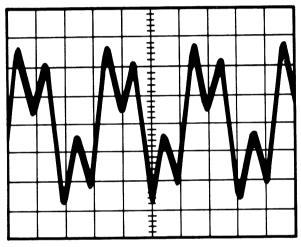

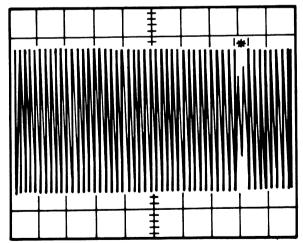

| 7.33 | Waveforms for Figure 7.32            | 154 |

|------|--------------------------------------|-----|

| 7/34 | Block Diagram                        | 156 |

| 7.35 | Test Setup                           | 172 |

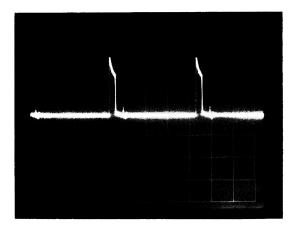

| 7.36 | Q2 Collector Waveform                | 174 |

| 7.37 | Q2 Base Waveform                     | 174 |

| 7.38 | Power Pin Assignments                | 175 |

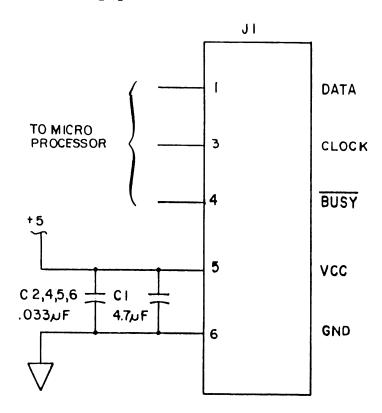

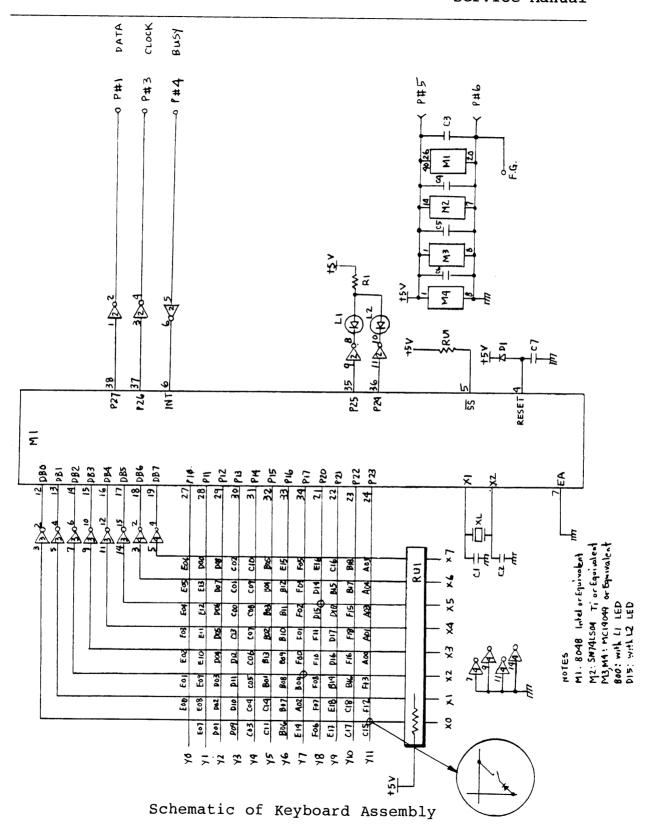

| 7.39 | Keyboard Assembly Connector          | 223 |

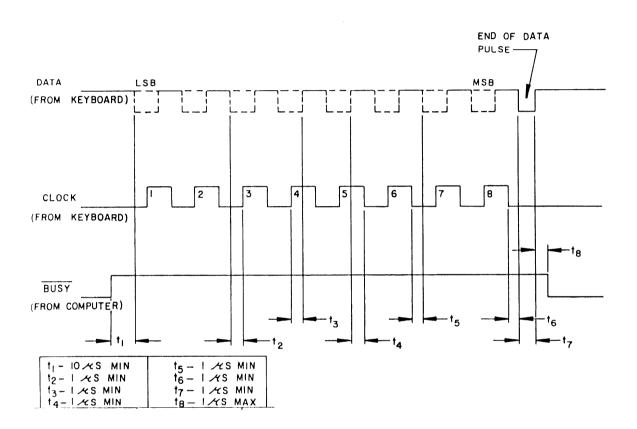

| 7.40 | Keyboard Assembly Timing Chart       | 227 |

| 7.41 | Keyboard Identification              | 228 |

| 7.42 | Key Number Identification            | 228 |

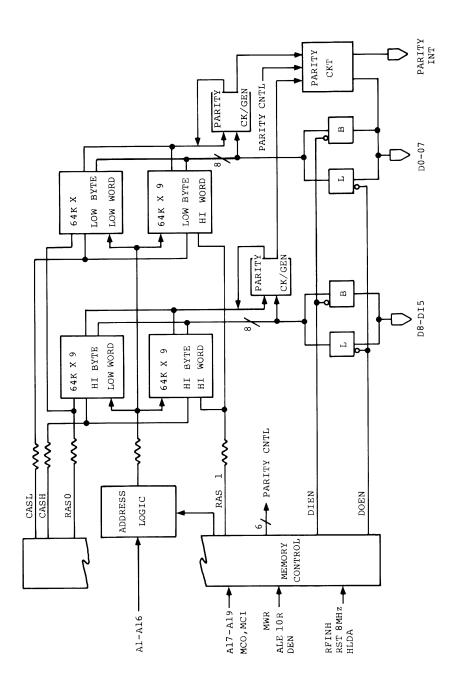

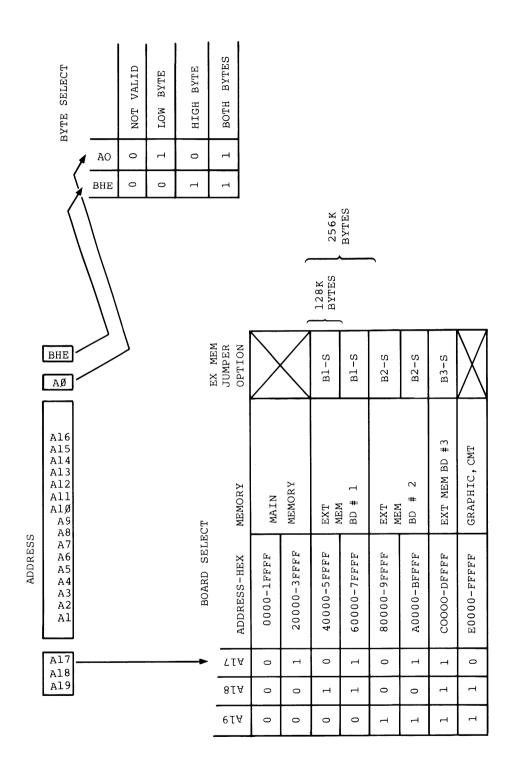

| 9.1  | Block Diagram, External Memory Board | 258 |

| 9.2  | Board Select                         | 259 |

| 9.3  | Memory Control Block Diagram         | 260 |

|      |                                      |     |

| 9.4  | Normal Cycle Plus Refresh Cycle      | 261 |

| 9.5  | U42 Diagram                          | 262 |

### 1/ Introduction

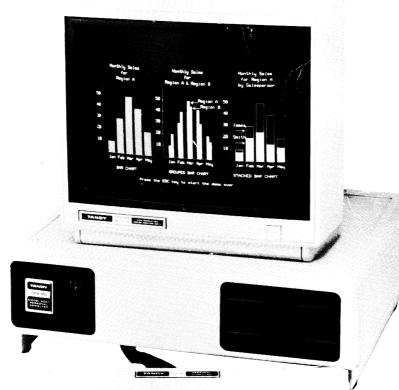

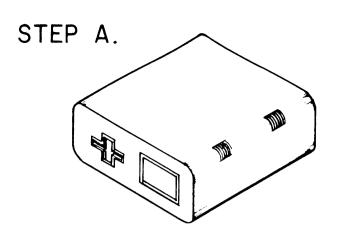

The Radio Shack Model 2000 Personal Computer is modular in design to allow maximum flexibility in system configuration. The basic computer consists of a Main Unit, a detached keyboard with coiled cable for positioning the keyboard in the most convenient location, and a monitor. The Main Unit may be supplied with two internal floppy disk drives or one floppy disk drive and one internal hard disk drive. The standard monitor used with the Model 2000 is a monochrome display (green phosphor) which has a standard screen format of 80 characters width and 25 lines vertical. Since this unit is modular, it may be placed on top of the Main Unit or at any location convenient to the operator.

Internal floppy diskette storage is provided by either one or two 5-1/4" floppy disk drives. If the unit is supplied with two of these units, total internal memory storage capacity is 1.46 Mbytes. When supplied with the internal hard disk and one floppy disk storage unit, total internal memory storage becomes 10.73 Mbytes.

An optional Color Monitor may be used with the Model 2000 to provide up to eight of sixteen different colors on the screen at one time. This optional feature requires the use of a color monitor PCB assembly which plugs into one of the mother board slots at the rear of the Main Unit.

An internal 128K RAM board is standard on the Model 2000. An option to the Model 2000 is an additional 128K RAM board which provides expansion to 256K. Both boards are mounted internal to the Main Unit. An additional optional feature is a 256K RAM board which connects to the internal motherboard of the Main Unit. It is populated with 128K RAM which may be expanded to 256K RAM with the addition of RAM ICs. Two of these boards can be installed into the motherboard in the unit's card cage assembly. With all these options installed, the Model 2000 then has internal RAM memory capacity of 768K bytes.

Other options include a TV/Joystick input, a mouse/clock option which allows input from a hand-positioned interface, a monitor pedestal, black and white graphics option, and a floor unit which mounts the Main Unit vertically.

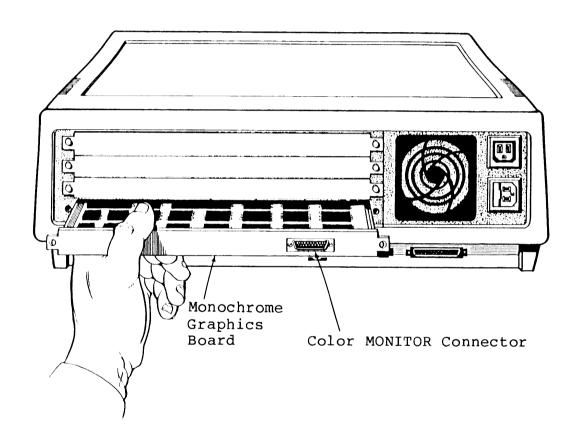

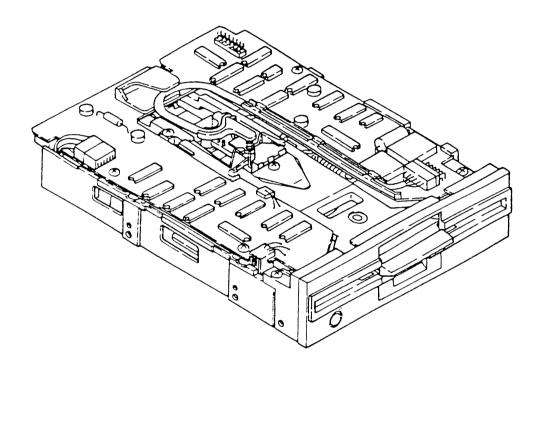

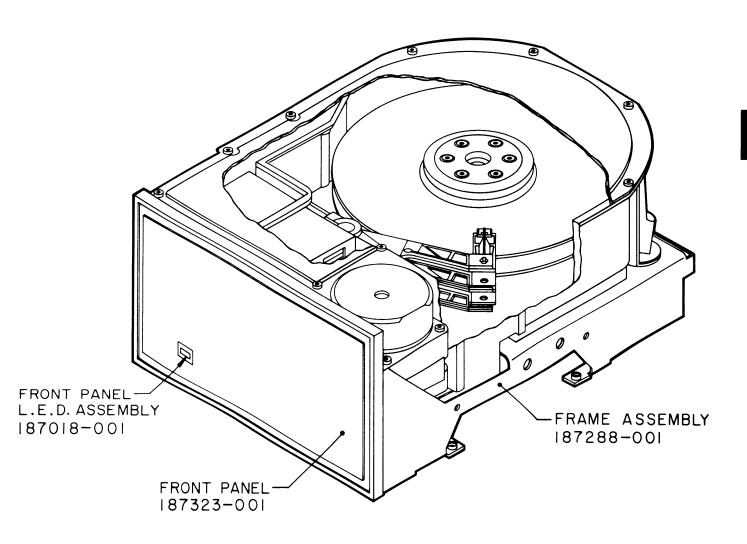

Figure 1.1 Model 2000 Computer Assembly

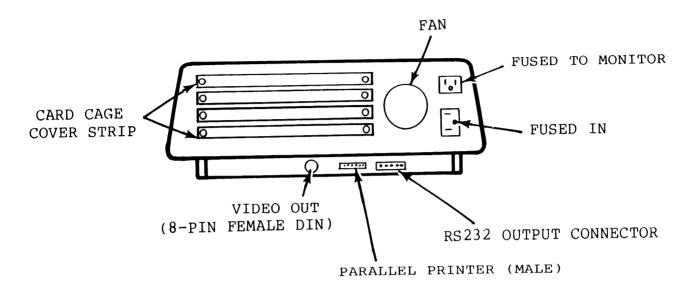

### REAR VIEW

Figure 1.2 Model 2000 Major Component Subassemblies

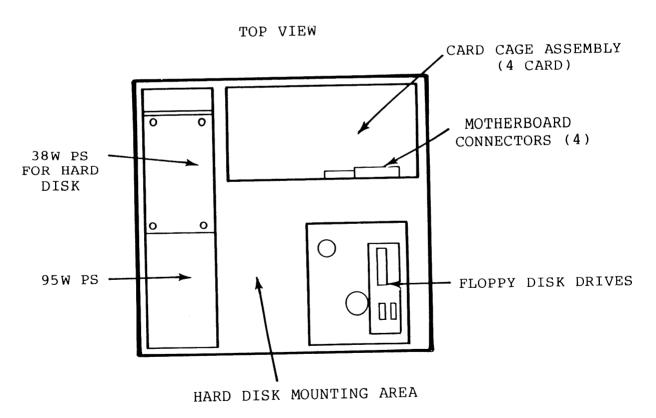

The Main Unit is the heart of the Radio Shack Model 2000 microcomputer. It houses the microprocessor, Read-Only Memory (ROM - 16K for system start-up), system power supply, RAM boards and expansion slots for optional features, floppy disk drives (either one or two), and the internal hard disk drive and power supply.

The Main Logic Assembly is a large board mounted to the bottom of the Main Unit and interconnected to the keyboard, power supply, motherboard, and disk drives by a series of cables. A system block diagram is shown in Figure 1-1 showing the major components of the Model 2000 and the interconnecting cables. Both standard and optional features are included in this figure to provide a complete overall interconnection diagram of the unit.

The standard Power Supply for the Model 2000 microcomputer is a 95W switching regulator type, designed to provide adequate capacity for most all add-on features of the computer. When the system is supplied with the hard disk option, however, an additional 38W power supply is required to power the hard disk assembly separately.

The Model 2000 has a detachable keyboard which is connected to the Main Unit with a lightweight coiled cable which allows the keyboard to be used up to 3 feet away from the Main Unit for operator convenience. The keyboard features 90 keys in a standard typewriter keyboard layout with additional keys for numbers and functions.

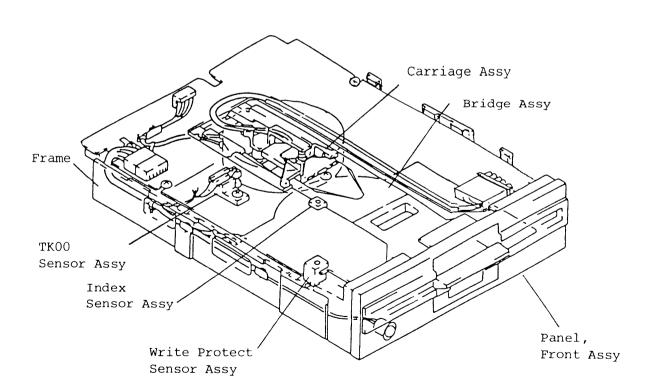

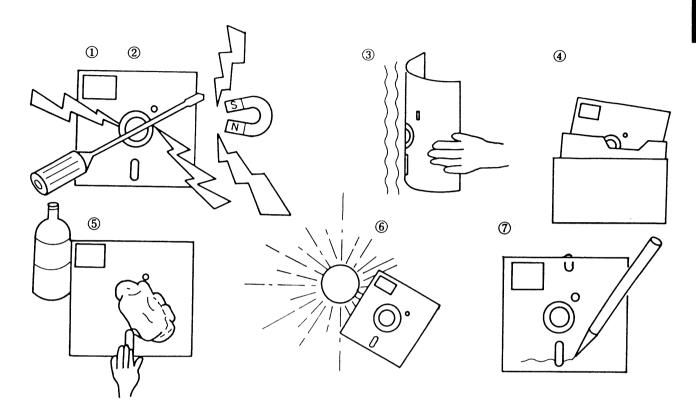

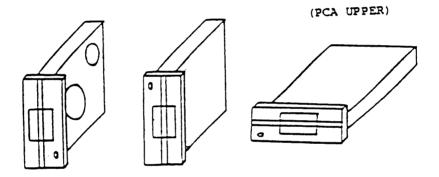

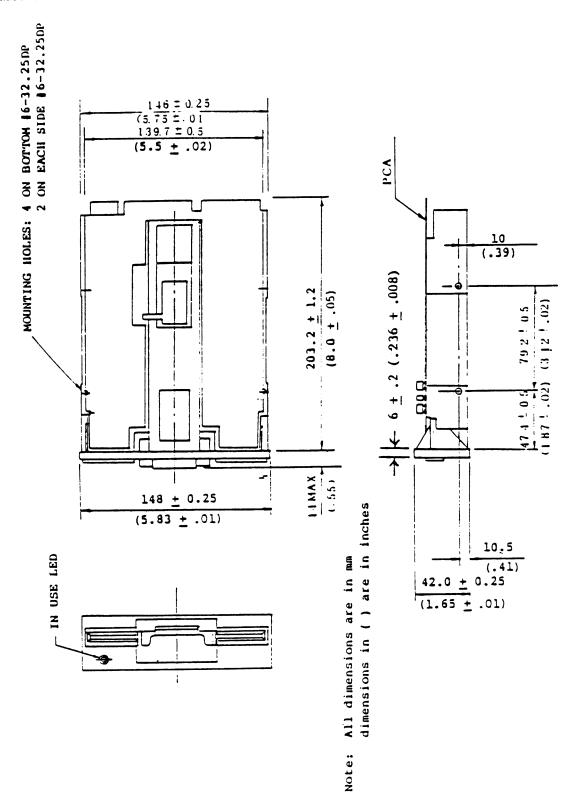

The Floppy Diskette Drive uses special 5-1/4" double-sided, double-density diskettes to read, write or store data. These are 96 TPI soft sector diskettes. Two Disk Drive assemblies are installed in the standard unit, or it may contain one floppy disk drive and one internal hard disk drive assembly. Each of the floppy diskettes stores approximately 730 Kbytes of data. The hard disk drive is capable of storing 10 Mbytes of data. All system programs, with the exception of the system startup sequence, are stored on diskette.

The monitor used on the Radio Shack Model 2000 may be either a monochrome (#26-5111) or color (#26-5112) display. The monochrome monitor is a high resolution green phosphor display which provides excellent visual quality. It features a 12" screen with an anti-glare surface for improved viewing. The display is 25 lines of 80 characters each with the capability of displaying 256 different letters or characters. The characters are formed using a 7 x 9 matrix dot pattern.

Also available as an enhancement of the black and white monitor is a B/W graphics option board (26-5140). This feature allows the presentation of graphic material on the display monitor with individually addressed pixels. A color monitor (26-5112) is available which utilizes a 14" color screen, a color graphics option (26-26-5141), and the B/W graphics option to provide 8 color presentations at one time on the monitor.

Standard internal RAM memory consists of a plug-in 128K board. This board plugs into the Main Logic board and may be expanded to provide 256K of RAM with an additional 128K board (26-5160). In addition to this memory up to two 26-5161 boards (considered external since they are accessible from the outside of the Main Unit) may be plugged into the motherboard located at the rear of the Main Unit. These boards are populated with 128K of RAM and may be further expanded to 256K each with additional 64K x 1 RAM chips (option 26-5162). When all of these boards are incorporated into the system, they provide a total RAM capacity of 784K bytes of memory.

The TV/Joystick Board allows attachment of user-supplied Joy Sticks or paddles. Two joysticks may be attached to the Model 2000 for use with games available in the software library of the Model 2000.

The Mouse/Clock option board allows input with an external input device called a "mouse" as well as providing the time of day with a battery backup clock/calendar chip. The mouse is a unit which is rolled along a desk top and encodes a digital input to the computer.

A built-in RS-232 asynchronous interface allows communication with external devices through the use of a modem. These devices may be local or remote, using a telephone line to co'm@unicate. The option supports 50 to 9600 BPS transmission speeds and utilizes a 25-pin D connector located on the rear panel of the Main Unit.

Figure 1.3 External Plug-in Option Cards

### 2/ Specifications

### 2.1 Physical Characteristics

```

Main Unit

Width 19.0 inches (48.26 cm)

Height 6.0 inches (15.24 cm)

Depth 16.0 inches (40.64 cm)

Weight

26-5103 23.0 pounds (10.4 kgm)

26-5104 26.5 pounds (12.0 kgm)

Monochrome Monitor

Width 16.25 inches (41.28 cm)

Height 11.4 inches (29.0 cm)

```

# Keyboard

Width 16.25 inches (41.28 cm) Height 1.2 inches (3.05 cm) Depth 7.875 inches (20.0 cm) Weight 2.8 pounds (1.3 kgm)

Depth 12.2 inches (31.0 cm) Weight 15.4 pounds (7.0 kgm)

# 2.2 System Operating Characteristics

```

Storage Temperature - -40 to +160°F (-40 to 71°C)

Ambient Temperature - 55 to 95°F (12 to 35°C)

Voltage Range (USA) - 95 to 135 Vac

(Europe) - 190 to 270 Vac

```

Current Drain - USA - AC Main Unit/Convenience Outlet

Model 26-5103 - 3.0 Amperes

Model 26-5104 - 3.5 Amperes

European - AC current Main Unit only Model 26-5103 - 0.94 Ampere Model 26-5104 - 1.2 Amperes

Line Frequency - 47 to 63 Hz

### 2.3 Peripheral Interfaces

RS232C Connector - DB25 socket connector accessible at the rear of the main unit. Pinout connections are shown in Section 5 of this manual.

### 2.3 Peripheral Interfaces (con't)

- Parallel Printer Connector 34-pin connector for connection of parallel printer or modem for conversion to serial transmission. Pinout connections are shown in Section 5 of this manual.

- Monochrome Monitor Connector 8-pin socket DIN connector accessible at the rear of the Main Unit.

- Motherboard accessible from the rear of the Main Unit allows up to four optional boards to be plugged into main unit. Existing cover strip and Nylatch latches are removed and optional board is inserted and latched into place with Nylatch hardware.

### 2.4 Optional Features

- Internal 128K RAM Board plugs into existing 128K RAM board to give 256K bytes of internal RAM storage. Requires disassembly of the main unit for installation. See Section 2 on disassembly procedures.

- External 256K Board plugs into slot on Motherboard at rear of main unit. Supplied with 128K, but may have another 128K added for total of 256K bytes of external RAM.

- TV/Joystick Board plugs into slot on Motherboard and allows use of Joysticks for games available in software library of Model 2000.

- Mouse/Clock Option Board plugs into slot on Mother-board. Provides real time clock displayed on monitor screen as well as input from external "mouse" option, a hand-positioned transducer which translates "X" and "Y" position into digital encoded signal.

# 3/ Disassembly/Assembly

Since the Model 2000 is modular in its construction, disassembly/assembly procedures are simplified. The main modules which make up the Model 2000 are the Main Unit, the keyboard, and the display monitor. These three units may be supplemented by various I/O devices such as printers, modems, memory devices or additional monitors. Disassembly of each module will be described in the following paragraphs. Exercise case when handling the modules to prevent damage to internal components or exterior surfaces.

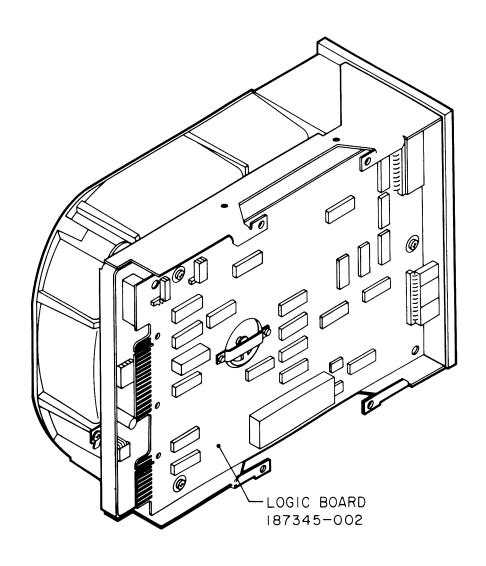

### 3.1 Main Unit

The Main Unit contains the Power ON-OFF switch and indicator, the disk drives and the system power supply. cables interconnect this unit with external devices. Most cables are connected to the rear terminal panel of the Main Unit but there are some connections to the front panel of the Main Unit, such as the keyboard connector. Attached to the bottom of the main unit is a metal chassis which houses the main logic PCB assembly. Turn the Main Unit assembly on either the left or right side to gain access to the mounting There are four screws which attach this assembly to the Main Unit housing. When properly positioned, the logic board provides interconnection from this base PCB to the Mother Board which is used for interconnecting optional feature boards. In addition to this 96-pin connector, there are other connectors which tie to the PCB. When the screws are removed from the base cover, swing the rear of the cover away from the main unit. This will allow the connectors which are at the front of the unit to be removed without damaging them.

Disconnect all connections to the main logic PCB (these include the power input, reset, and sound). With these connectors disconnected, the base assembly may be removed completely from the Main Unit assembly. The PCB is attached to the metal base assembly with nine screws. There is an insulating separator to prevent possible shorting of any of the components on the PCB to the metal base assembly.

The Main Unit housing contains the Power Supply, the Disk Drive Assemblies (either two floppy disk drives or 1 floppy and 1 hard disk drive) and the Motherboard for system options. To gain access to the interior of this unit, remove two mounting screws at the lower rear of the Main

Unit. After removing these two screws, slide the top cover forward to release the catches at the front, then lift the top cover off the assembly. The back panel portion of the case housing remains a part of the Main Unit base as well as the power switch/reset and indicator.

### 3.1.1 Power Supply

The 95W main power supply for the Model 2000 is located at the left side of the Main Unit and is accessible when the cover is removed from the Main Unit as noted previously. The power supply is attached to the base of the Main Unit with 6 screws, 4 of which are screwed into the bottom of the base and 2 of which are attached to the backside of the front bezel If the Main Unit has a Hard Disk assembly installed, it must be detached to provide access to the connectors which connect the power supply to the Main Logic PCB.

- 1. Remove the connectors attached to the Motherboard, disk drives, and Main Logic PCB.

- 2. Remove 4 screws which attach the power supply assembly to the base plastic.

- 3. Remove the two screws which connect the power supply to the front bezel assembly.

- 4. Lift the power supply from the Main Unit.

- 5. Remove 3 screws from the RH side of the power supply to allow the upper enclosure to be lifted off the supply.

- 6. Remove 4 connectors which attach to the power supply PCB.

- 7. Remove 8 screws which attach the PCB to the lower enclosure weldment.

- 8. Cable replacement is accomplished by removing the connectors from the enclosure weldment. All connectors are clip-mounting type connectors which allow replacement without special tools. Remove wires attached to the connector and then depress retaining clips from inside the enclosure. Slide connector out of enclosure weldment.

Assemble the power supply in the reverse order of disassembly. Ensure that the power supply is properly operating before reinstalling it in the Main Unit. See Section 7.2 for checkout procedures for the main power supply.

The 38W Hard Disk power supply assembly is attached to the underside of the power supply cover and nests above the main power supply PCB. It is accessible when the cover is removed from the main supply.

- 1. Remove the cover from the main unit as noted in Paragraph 3.1.

- 2. Remove the main power supply cover by removing the 4 mounting screws.

- 3. Remove the mating connectors to the 38W power supply there are two connectors. One is for AC input and

the other for DC output. There are three DC output

connectors on the PCB. The DC output connector may be

attached to any one of the three on reassembly.

- 4. Remove the 38W power supply board from the cover by removing the 4 mounting screws.

Reassembly of the power supply is in the reverse order of disassembly. Ensure that the orientation of the supply is the same as it was prior to disassembly to prevent interference with the main power supply PCB components.

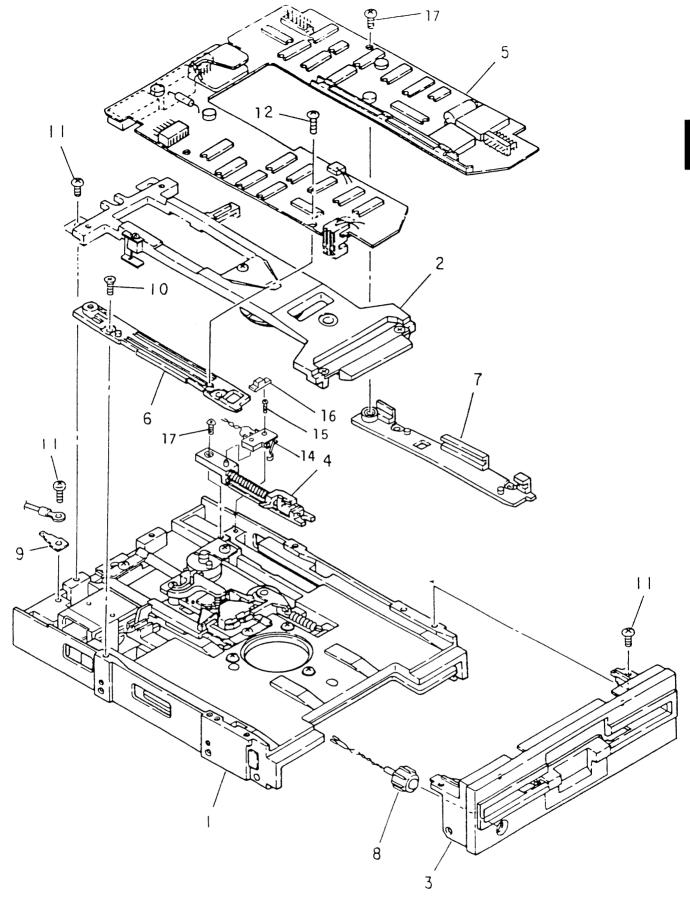

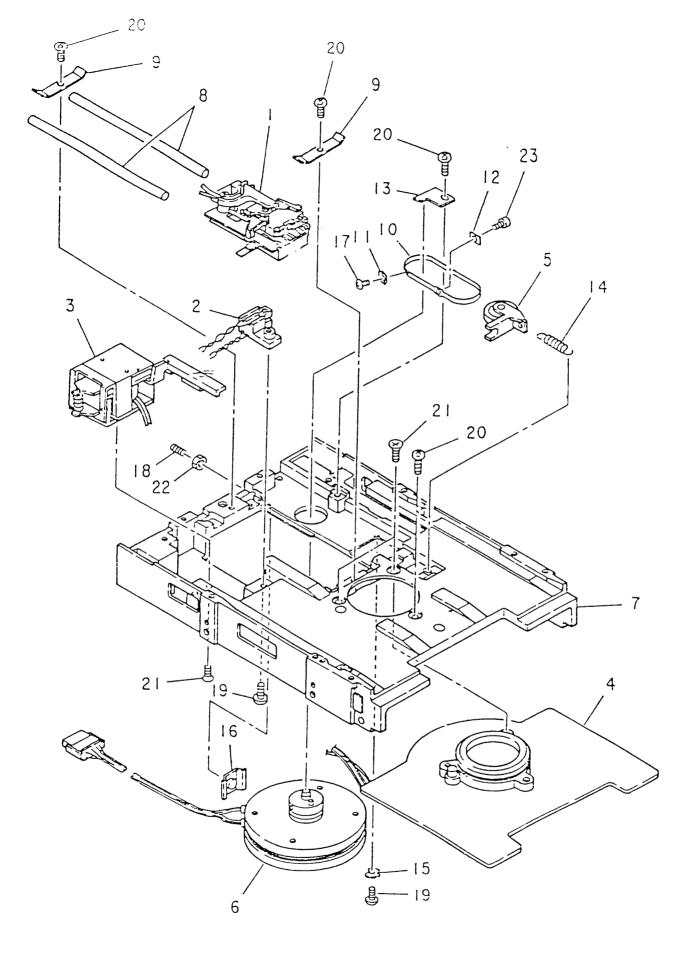

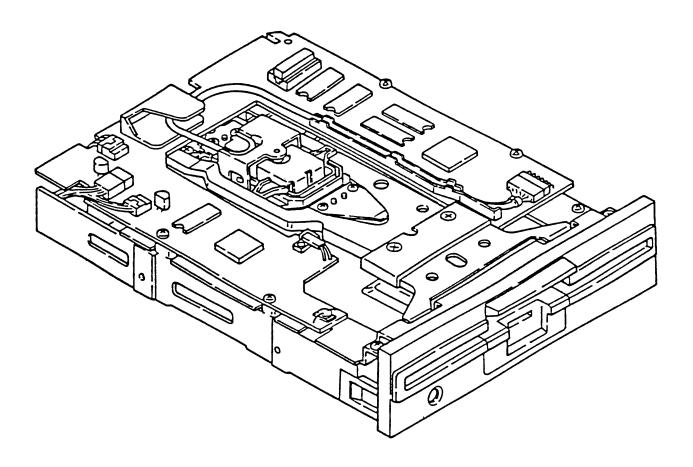

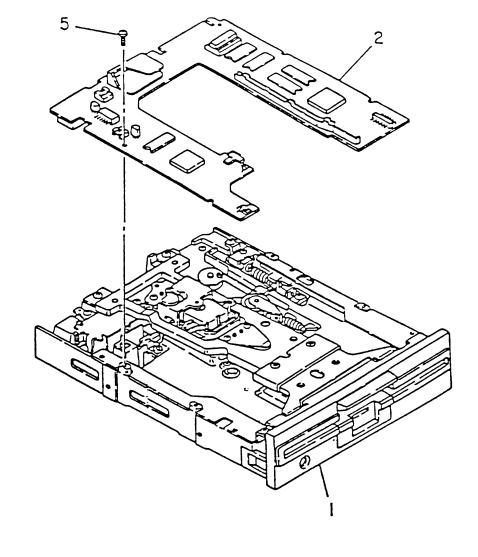

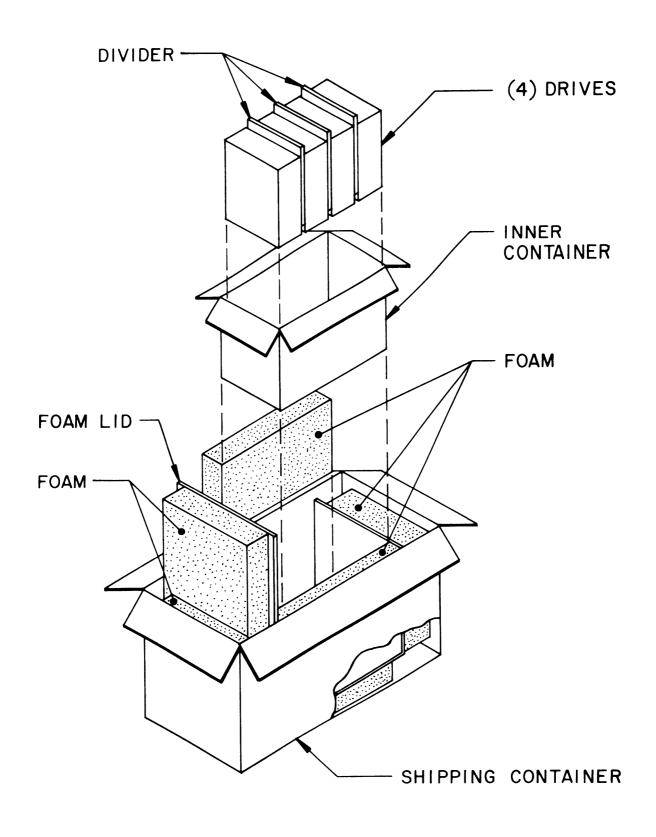

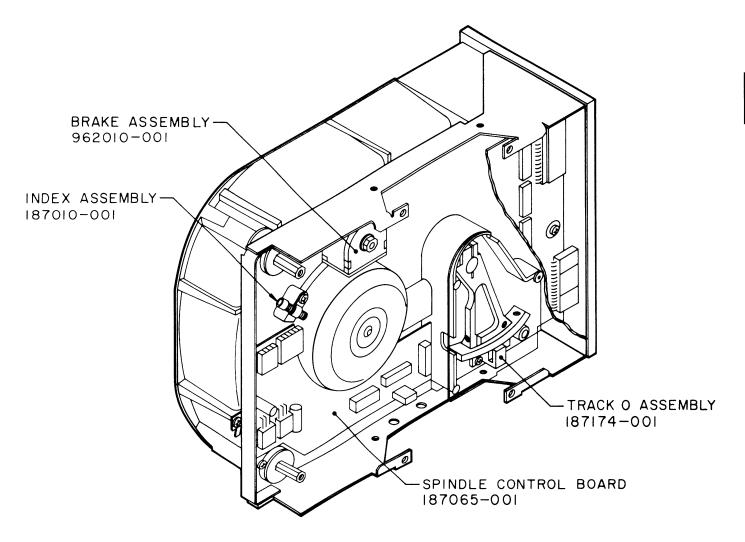

### 3.1.2 Disk Drives

The floppy disk drives are mounted at the right side of the Main Unit, attached to the base of the main unit with a mounting bracket on either side of the drives. The drive assemblies (including mounting brackets) may be removed from the Main Unit base by removing 4 screws in the base. After these screws and cables connected to the drives are removed, the drive assembly may be removed completely from the Main Unit

The hard disk assembly is mounted to the left of the floppy disk drive assemblies. If the unit contains a hard disk drive assembly, it is removed from the Main unit by removing the four mounting screws and attached cables.

# 3.2 Keyboard Assembly

The keyboard assembly is connected by a coiled cable attached to the left side of the front plate of the Main Unit. Disconnect this connector to completely detach the keyboard assembly. Disassemble the keyboard as noted below.

### 3.2.1 Disassembly

- 1. After removing the connector from the Main Unit, turn the keyboard assembly upside down on a soft surface to prevent scratching the surface or keys.

- 2. Remove three screws from the front of the keyboard. Keep separate so that they may be replaced in the front 3 mounting holes.

- 3. Remove remaining 6 screws from the sides and back of the keyboard assembly.

- 4. Hold the top and bottom of keyboard assembly together and turn the assembly rightside up.

- 5. Lift the top cover off the assembly, exposing the keyboard printed circuit board.

- 6. Disconnect the cable connector at the right rear of the keyboard assembly and remove the keyboard PCB.

- 7. Lift the keyboard supports from the rear of the keyboard. These are positioned over the support springs in the keyboard base (two on each side).

- 8. The cable is secured to keyboard base with a strain relief. If necessary, squeeze the strain relief to remove the cable from the base.

- 9. The cable wire connections must be removed from the connector to replace the cable assembly. Use a small tool to depress spring clip in the connector and pull the wire/clip end from the connector.

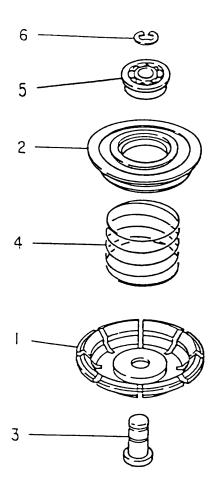

- 10. The four keyboard support springs slide into the base from the outside of the plastic holders. See the exploded view in Section 8 if required.

# 3.2.2 Assembly

The keyboard is assembled in the reverse order of disassembly. Ensure that the keyboard supports are properly positioned on the support springs prior to installing the top cover. Also ensure that the shorter mounting screws are used in the front positions of the keyboard assembly to prevent damage to the keyboard plastic.

### 3.3 Display Unit

The Display Unit for the Tandy Model 2000 computer may be either monochrome or color, depending on individual requirements. Servicing either of the two units is covered in the service manual for the particular type monitor used. See the supplemental sections at the end of this Model 2000 service manual for servicing information.

- 13 -

## 4/ Adjustments

### 4.1 Power Supply Adjustment

Adjustment of voltage sources required by the Model 2000 is contained in Paragraph 7.2.1.3 Performance Test. These voltages include +5 Vdc, +12 Vdc, and -12 Vdc.

### 4.2 PLL Adjustment

Adjustment of the PLL circuitry is accomplished by the adjustments noted in Paragraph 7.1.7.4.

# 4.3 Video Adjustment

Adjustments to the video circuits should be made according to the alignment instructions noted in the supplements contained in Section 10 of this manual. Instructions are included for both the Monochrome and Color Monitors.

# 5/ Cabling Diagrams/Pinout Connections

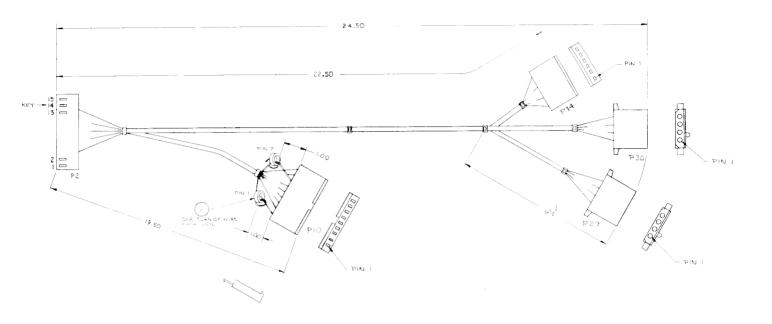

This section of the manual contains connector diagrams and pin out descriptions of the connectors used in the Model 2000 microcomputer. Figure 7-1 shows an interconnecting wiring diagram and identifies the connectors by symbol number. The following pages then show physical representation of the connector and corresponding pin designations.

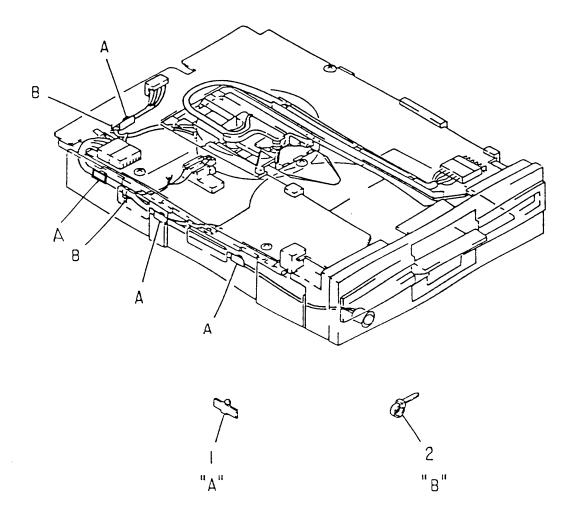

### CONNECTOR SYMBOLS RING TONGUE TERMINAL (TO EARTH GROUND) CARD EDGE EXPANSION RAM SNAP SPADE TONGUE 128K SYSTEM RAM (PART NO. 8896806) TERMINAL QUICK DISCONNECT TERMINAL (FASTON) P6 MOTHER BOARD / SERIAL (RS-232) CARD CAGE ASSEMBLY (PART NO.8898893) J2 🛆 HARD DISK PARALLEI TO SLAVE ⅓ INTERFACE / CONTROLLER (TOP SLOT ONLY) (PART NO.8898807) HARD DISK EXTERNAL INTERFACE MONOCHROME MAIN LOGIC BOARD (PART NO. 889B 001) ARCNET KEYBOARD ARCNET J16 (ANY SLOT) (P/N8040087) P4 J5 > DC POWER SUPPLY SUBASSEMBLY 256 K RAM (EXPANSION) (FOR 26-5103 USE P/N8898003) J17 (FOR 26-5104 USE P/N 8898013) DC FAN SWITCH HI RES GRAPHICS COLOR (BOTTOM SLOT ONLY) (PART NO.88988ØI) $(\circ)$ POWER SUPPLY (P/N879ØØ56) REFERENCE 35 WATT DESCRIPTION CABLE NO DRAWING NO. HARD DISK POWER SUPPLY DC POWER, MAIN DC POWER, HARD DISK /N879ØØ25) 6ØØ8Ø58 6ØØ8Ø59 8709444 8709446 W3 W4 SIGNAL, FLOPPY DISK SIGNAL HARD DISK 6**00**8057 **6008082** 8709447 87**09485** 6008075 6008008 SIGNAL, RESET 870-9464 W6 W9 GROUND-HARD DISK GROUND-AC OUTPUT .870-9518 POWER 6008093 8709492 EIØ, P22 P25 P25 GROUND-AC INPUT 870-9468 P29 \ \( \bigcap \) P3@ 🔨 🗘 W 12 OWER SUPPLY TO AC OUTPUT 60/08/078 879-9466 POWER SWITCH TO POWER SUPPLY POWER SWITCH TO AC INPUT 6008079 870-9467 870-9471 W 13 W 14 HD GND W 15 SIGNAL, SPEAKER 6008070 87Ø-947Ø W 16 GROUND, 95 WATT POWER SUPPLY RFI GROUND 8709493 GROUND 38 WATT POWER SUPPLY 6008092 5 I/4 FLOPPY DISK DRIVE MASTER 5 I/4 FLOPPY GROUND RFI 600843 87095 \*\* GROUND ACCOMPLISHED THROUGH HARDWARE FASTENER. 8709507 Ū<sub>A</sub> DISK DRIVE HARD DISK (DSI) DRIVE (DSØ) NOTES (UNLESS OTHERWISE SPECIFIED): . E5 🛡 AMP CONNECTOR REQUIRED FOR COMPATIBILITY. ◬ AC INPUT CONNECTOR HAS INTEGRAL FUSE (4A,125V 4X29 MM EUROPEAN TYPE P/N8479921) AC INPUT AC OUTPUT CONNECTOR PIS IS MOUNTED ON CARD CAGE ADJACENT TO JIS ON MOTHER BOARD ASSEMBLY. E3 ATTACHES TO SCREW ON POWER SUPPLY CHASSIS AC CONNECTIONS

L=LINE N=NEUTRAL

E=EARTH GROUND

Figure 5.1 Connector/Cable Interconnection Diagram 8000206 Model 2000 Computer

Tandy® Model 2000

Service Manual

Connector/Cable Interconnection Diagram 8000206A Model 2000 Computer

|                  | V-/15 | VIKE       | LIS  | JUEZ     | TO / | PIN | ##  |

|------------------|-------|------------|------|----------|------|-----|-----|

| FUNCTION         | AWG   | count      | 1 12 | P        | P14  | P29 |     |

| +12V             |       | CRG        |      |          |      | I   |     |

| 1                | 20    |            | 1    |          |      |     | - 1 |

| *                | .20   | •          | . 2  | 1        |      |     |     |

| +12 V            | 20    | ORG        | 2    |          | ı    |     |     |

| GND              | 18    | BLK        | 3    |          | 4.   | 2   |     |

|                  |       |            | 3    | -        |      | 3   |     |

|                  |       |            | 4    |          |      |     | 2   |

|                  |       |            | 4    |          |      |     | 3   |

|                  |       |            | 5    | 5        |      |     |     |

|                  |       |            | 5    | 6        |      |     |     |

|                  |       |            | 6    | 8        |      |     |     |

|                  |       | •          | 7    |          | 3    |     |     |

| GND              |       | BLK        | 7    | <u> </u> | 5    |     |     |

| + 5Y             |       | RED        | 8    | 3        |      |     |     |

|                  |       |            |      | 4        |      |     |     |

|                  | - +   | +++-       | 10   | -        |      | 4   | 4   |

|                  |       | 1          | - 11 | +        | 2    |     | -   |

| + 5V             | 18    | RED        | 12   |          | 4    |     | - " |

| - 12 V<br>- 12 V | 20    | werr<br>.± | 13   | 7        |      |     |     |

| - 12 V           | 20    | . 🖈 📖      | 13   | -        | 6    |     | _   |

| KEY<br>ACLO      | şo    | GRY        | 15   | _2       |      |     |     |

| PARTS LIST |     |                          |                          |                    |  |  |  |

|------------|-----|--------------------------|--------------------------|--------------------|--|--|--|

| DES        | ΩTY | DESCRIPITION             | MEG / PART NO.           | REMARKS            |  |  |  |

| P 2        | 1   | CONN, SACKET 15 POSITION | MOLEX / 09 - 50 - 3151   |                    |  |  |  |

|            | 1.5 | CONTACT                  | MALEX /08-50-0105        | FEMALE PIN         |  |  |  |

| PIC        | 1   | CONU SOCKET 9 POSITION   | MALEX/09-50-3091         |                    |  |  |  |

|            | 9   | CONTACT                  | MOLEX / 28-50-0105       |                    |  |  |  |

| P14        | 1   | COUN SOCKET & POSITION   | MOLEX / 09-50-3061       |                    |  |  |  |

|            | 6   | CONTACT                  | MOLEX / 08-50-0105       |                    |  |  |  |

| P24 P30    | 2   | COUN SOCKET 4 POSITION   | AMP / 1-480424-0         |                    |  |  |  |

|            | ā   | COUTAC T                 | AMP / 61117-1            |                    |  |  |  |

|            | 1   | KEY                      | MOLEX / 9-04-0219        |                    |  |  |  |

| - 1        | 2   | COIL, TORID              | FAIR-RITE / 594 3 000201 | - 2V & -12V CN PIO |  |  |  |

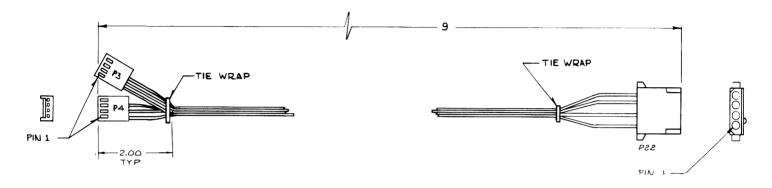

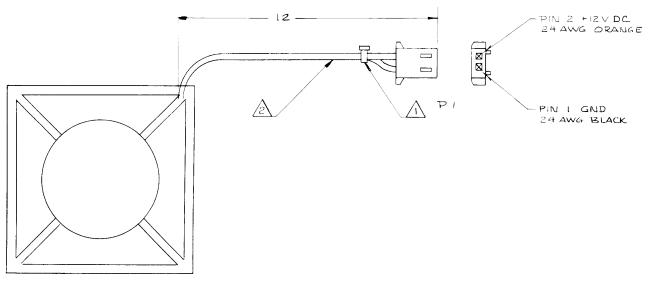

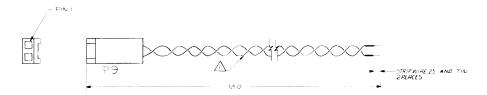

Cable Assembly Wl (6008058)

| WIRE LIST |     |       |   |      |      |      |     |     |  |

|-----------|-----|-------|---|------|------|------|-----|-----|--|

| FUNC-     | WI  | RE    |   | CONI | VECT | OR / | PIN | NΔ. |  |

| TIDN      | AWG | COLOR |   | P22  |      | P3   |     | P4  |  |

| +127      | 20  | ORG.  |   | 1    |      | 3    |     | _   |  |

| +12 Y     | 20  | OR4.  |   |      |      | ı    |     | m   |  |

| GND       | 20  | BLK   |   | 2    |      | 2    |     | -   |  |

| GND       | 20  | BLK   | • | 3    |      | ı    |     | 2   |  |

| +57       | 50  | RED   |   | 4    |      | 1    |     | -   |  |

| +57       | 20  | RED   |   | 4    |      | -    |     | 1   |  |

|           |     |       |   |      |      |      |     |     |  |

|           |     |       |   |      |      |      |     |     |  |

|       |     | PARTS                    | LIST               |          |

|-------|-----|--------------------------|--------------------|----------|

| DES   | ΔTY | DESCRIPTION              | MFG PART NO.       | EEMIARKS |

| PZZ   | 1   | CONN. SOCKET, 4 POSITION | AMP / 1-480424-0   |          |

|       | 4   | CONTACT                  | AMP/ 61117-1       |          |

| P4/P3 | 2   | CONN. SOCKET, 4 POSITION | MOLEX / 22-01-3047 |          |

|       | A   | CONTACT                  | MOLEX / 08-50-0113 |          |

|       |     |                          |                    |          |

|       |     |                          |                    |          |

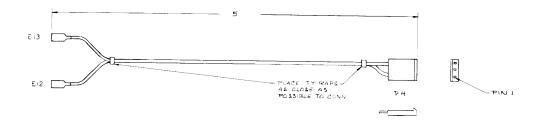

Cable Assembly W2 (6008059)

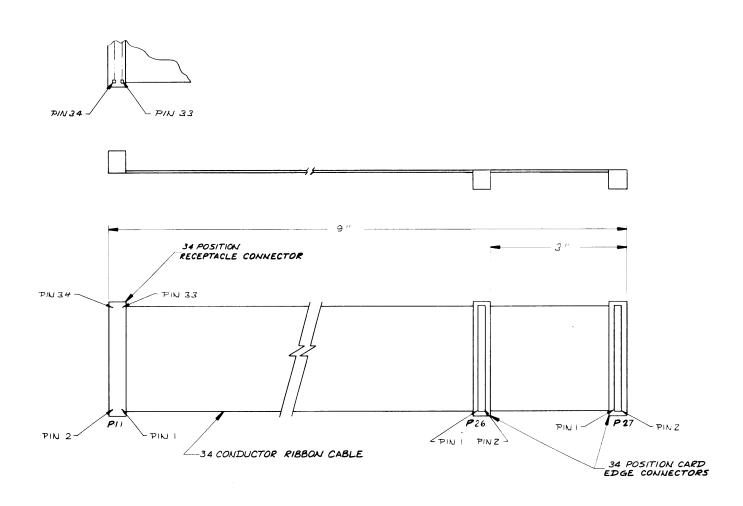

| PARTS LIST |     |                           |                    |                          |  |  |  |  |  |

|------------|-----|---------------------------|--------------------|--------------------------|--|--|--|--|--|

| DES        | aty | DESCRIPTION               | MEG/PART NO.       | KEMARKS                  |  |  |  |  |  |

| PII        | 1   | CONN. 34-PIN RECEPTACLE   | MOLEX / 15-29-3343 | STRAIN RELIEF 15-25-1543 |  |  |  |  |  |

| P26,27     | Z   | CONN., 34- PIN EDGE CARD  | 3M / 3463-0001     |                          |  |  |  |  |  |

|            | 1   |                           | AMP/ 499930-3      |                          |  |  |  |  |  |

|            |     | CABLE 34-COND.,.050 PITCH |                    |                          |  |  |  |  |  |

|            |     |                           |                    |                          |  |  |  |  |  |

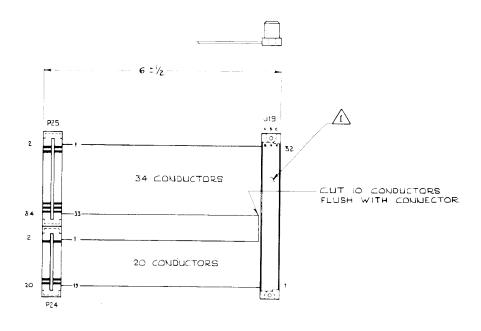

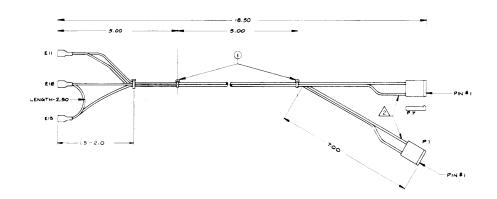

Cable Assembly W3 (6008057)

|             |      | PARTS                                 | LIST   |                  |                   |

|-------------|------|---------------------------------------|--------|------------------|-------------------|

| DESIGNATION | QTY. | DESCRIPTION                           | MFG.   | PART NUMBER      | REMARKS           |

| J19         | . 1  | 96 PIN EURO CONNECTOR                 | BURNDY | BPS3B96Ac RaFaZ1 | ROWS A & C LOADED |

|             |      |                                       | BERG   | 75860-001        |                   |

|             |      |                                       | CANNON | GOGM96P3BLBL-004 |                   |

| P24         | 1    | 20 Position EDGE CARD CONNECTOR       | AMP    | 499930-6         |                   |

|             |      |                                       | 3 M    | 3461-0001        |                   |

| IP25        | 1    | 34 POSITION EDGE CARD CONNECTOR       | AMP    | 499930-3         |                   |

|             |      |                                       | 3M     | 3463-0001        |                   |

| w٤          | 1    | 64 COND. FLAT CABLE . 050 PITCH CABLE |        |                  |                   |

Cable Assembly W4 (6008082

| PARTS' LIST |      |                                                             |       |            |                   |  |  |  |

|-------------|------|-------------------------------------------------------------|-------|------------|-------------------|--|--|--|

| DESIGNATION | QTY. | DESCRIPTION                                                 | MFG.  | PART Nº    | REMARKS           |  |  |  |

| X1          | 1    | E1- P7,2 : BLK. 20 AWE GND.<br>E1- P7,1 : GRAY 20 AWE RESET |       |            | . /2 LENGTH TOLES |  |  |  |

| E1, E2      | 2    | QUICK DISCONNECT                                            | AMP   | 2-350803-2 | FULLY INSULATED   |  |  |  |

| P8          | 1    | HOUSING, 2 PIN                                              | MOLEX | 09-50-3021 | W/LOCKING RAMP    |  |  |  |

|             | 2    | CONTACT                                                     | MOLEX | 08 50 0105 |                   |  |  |  |

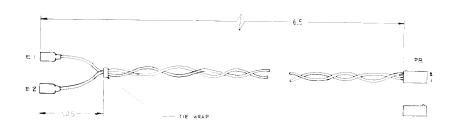

Cable Assembly W5 (6008075)

|      |      | PARTS' LIS                                       | Т    |          |

|------|------|--------------------------------------------------|------|----------|

| DES. | QTY. | DESCRIPTION                                      | MF4. | P/ N     |

| E14  | 1    | RING TERMINAL                                    | ДМР  | 350981-2 |

| E16  | 1    | SNAPSPADE TERM.                                  | AMP  | 640769-1 |

|      | 1    | WIRE, 18 AWG.<br>GRN. W/YELLOW<br>STRI <b>PE</b> |      |          |

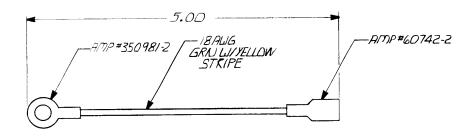

Cable Assembly W9 (6008093)

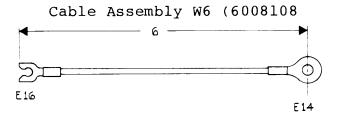

Cable Assembly W10 (6008074)

|          |     | WII   | ZE                | LI       | ST |    |   |    |

|----------|-----|-------|-------------------|----------|----|----|---|----|

| FUNCTION | Wi  | RE    | CONNECTOR / PIN * |          |    |    |   | V# |

| 002 1230 | AWG | COLDE |                   |          | P4 | T  | Ĺ |    |

| LINE     | 18  | BEN   |                   | E 16     | 1  |    |   | _  |

| NEUTRAL  | IA  | ВШ    |                   | E13      | 3  |    |   |    |

|          | 1   |       |                   | $\vdash$ |    | Η- | - | _  |

| DES     | ΔTY | DESCRIPTION                | MFG/PART NO.       | REMARKS         |

|---------|-----|----------------------------|--------------------|-----------------|

| P 4     | T   | 3 CKT HOUSING W/LOCK RAMP  | MOLEX / 09 50-3031 |                 |

|         | 2   | CONTACTS                   | MOLEX / 08-50-0105 |                 |

| EIZ EIS | 2   | QUICK DISCOUNIECT (25x.03) | MP 2-520183-2      | FULLY INSULATED |

Cable Assembly W12 (6008078

|          | ١.  | NIRE LIST |                 |    |     |     |     |  |

|----------|-----|-----------|-----------------|----|-----|-----|-----|--|

| FUNCTION | w   | RE        | CONNECTOR PIN # |    |     |     |     |  |

| FUNCTION | AWG | COLOR     | P7              | P1 | EIQ | EII | E15 |  |

| LINE     | 18  | BROWN     | 1               |    | 1   |     |     |  |

| LINE     | 18  | BROWN     |                 |    | 1   |     | 1   |  |

| LINE     | 18  | SPOWN     |                 | 1  |     |     | 1   |  |

| NEUTRAL  | 16  | BLUE      | 3               | Ι. |     | 1   |     |  |

| NEUTRAL  | 18  | BLUE      |                 | 3  | 1   | T   | [   |  |

| PARTS LIST    |     |                            |       |            |                 |  |  |  |

|---------------|-----|----------------------------|-------|------------|-----------------|--|--|--|

| DESIGNATION   | QTY | DESCRIPTION                | MFG   | PART NO.   | REMARKS         |  |  |  |

| P7, P1        | 2   | 3 POS CONN, N/LOCKING EAMP |       | Ø9-5Ø-3Ø31 |                 |  |  |  |

|               | 4   | CONTACT                    | MOLEX | 68-50-8125 | <del></del>     |  |  |  |

| E10, E11, E15 | 3   | 14 X 4 QUICK DISCONNECT    | AMP   | 3-3508/9-2 | FULLY INSULATES |  |  |  |

|               | 2   | TIE WRAP                   | _     |            |                 |  |  |  |

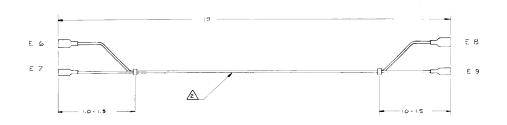

Cable Assembly W13 (6008079)

| WIRE LIST  |                   |       |   |                    |     |  |  |  |  |

|------------|-------------------|-------|---|--------------------|-----|--|--|--|--|

| CHAIC TIVE | WIRE<br>AND COLDE |       |   | CONNECTOR / PIN NO |     |  |  |  |  |

| CHAC HON   | AWG               | COLDE |   |                    |     |  |  |  |  |

| LINE       | 18                | BRN   |   | Ĕ6                 | € 8 |  |  |  |  |

| NEUT       | 18                | BLU   |   | E?                 | E.9 |  |  |  |  |

|            |                   |       | - | -                  |     |  |  |  |  |

|            | ⊢                 | _     | _ |                    |     |  |  |  |  |

|            |                   |       |   |                    |     |  |  |  |  |

| PARTS LIST |     |                          |     |            |                 |  |  |  |

|------------|-----|--------------------------|-----|------------|-----------------|--|--|--|

| DE.S       | ΔTY | DESCRIPTION              | ME  | G/PART NO. | REMARKS         |  |  |  |

| £6-E9 4    | 4   | QUICK DISCONNECT .25x.03 | AMP | 2-356803-2 | FULLY INSULATED |  |  |  |

|            | 2   | TIE WRAP                 |     |            |                 |  |  |  |

|            | _   |                          |     |            | -               |  |  |  |

|            | ├-  |                          |     |            | +               |  |  |  |

|            | -   |                          |     |            |                 |  |  |  |

|            | 1   |                          |     |            |                 |  |  |  |

Cable Assembly W14 (6008071)

| FULCTION | WI   | 35    | CONNECTOR / PIN NO. |                       |  |  |  |

|----------|------|-------|---------------------|-----------------------|--|--|--|

| FUNCTION | AWC. | COLOR | P-9                 |                       |  |  |  |

| SPKROUT  | 24   | GRY   | ſ                   | TO SPEAKER + TERMINAL |  |  |  |

| GND      | 24   | BLK   | 2                   | TO SPEAKER - TERMINAL |  |  |  |

| DES | WTY.     | DESLE PTION       | VIFG / PAET NO.    | REMARKS |

|-----|----------|-------------------|--------------------|---------|

| P)  |          | ZIMN GUCLET Z POS | VOLEX / 22-01-3027 |         |

|     | 2        | CONTAC*           | MOLEX / 68-50-0113 |         |

|     |          |                   |                    |         |

|     | ļ        |                   | -                  |         |

|     | <u> </u> |                   |                    |         |

|     | L        |                   |                    |         |

Cable Assembly W15 (6008070

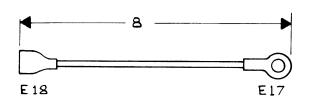

Cable Assembly W16 (6008080

|      | PARTS' LIST |                                      |      |          |             |  |  |

|------|-------------|--------------------------------------|------|----------|-------------|--|--|

| DES. | QTY.        | DESCRIPTION                          | MFG. | P/N      | REMARKS     |  |  |

| E18  | 1           | 1/4 x 1/32 QUICK DISCONECT           | AMP  | 42-400-2 | INS. BARREL |  |  |

| E17  |             | RING TERMINAL                        | AMP  | 350981-2 | ING, BARREL |  |  |

|      |             | IB GL. GRN. W/YELLOW<br>STRIPE WIRE. |      |          |             |  |  |

Cable Assembly W17 (6008092)

| PARTS LIST |     |                               |               |                        |  |

|------------|-----|-------------------------------|---------------|------------------------|--|

| DES        | ATY | DESCRIPTION                   | MFG / P.N.    | REMARKS                |  |

| EI         | 1   | RING TERMINAL                 | AMP / 61793-1 | OR EQUIVALENT          |  |

| PI         | 1   | .250 FASTON RECEPTACLE        | AMP/ 42400-2  | OR EQUIVALENT          |  |

| W1         | 1   | AWG 12/65 STRANDS OF<br>30 GA |               | GREEN W/ YELLOW STRIPE |  |

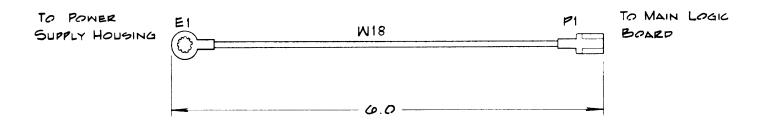

Cable Assembly W18 (6008103)

| WIRE LIST |     |       |     |                    |  |   |   |    |

|-----------|-----|-------|-----|--------------------|--|---|---|----|

| FUNCTION  | W   | RE    | COI | CONNECTOR / PIN NO |  |   |   | NQ |

| FUNCTUN   | AWK | COLOR | P7  | PI                 |  |   |   |    |

| KBDDAT    | 26  | BLK   | 1   | 1                  |  |   |   |    |

| KBDCLK    |     |       | 4   | 3                  |  |   |   |    |

| K BDBSY*  |     |       | 2   | 4                  |  | L |   |    |

| + 5V DC   | 26  | RED   | 5   | 5                  |  |   |   |    |

| GUD       | 22  | BARE  | 3   | 6                  |  |   |   |    |

|           |     |       |     |                    |  |   | I |    |

|           |     |       |     |                    |  |   |   |    |

|           |     |       | Τ.  |                    |  |   |   |    |

|     | PARTS' LIST |                         |                     |                     |  |  |

|-----|-------------|-------------------------|---------------------|---------------------|--|--|

| DES | ΔTY         |                         | MFG/PART NO         | REMARKS             |  |  |

| P7  | 1           | COUN SPIN DIN TET ANKLE | LUSHIDEN/479879342R |                     |  |  |

| PΙ  | 1           | 6 CKT HOUSING           | MOLEX / 22-01-3069  | MOLDED KEY IN POS 2 |  |  |

|     | 5           | CONTACT                 | MOLEX / 08-50-0113  |                     |  |  |

|     |             |                         |                     |                     |  |  |

|     |             |                         |                     |                     |  |  |

|     |             |                         |                     |                     |  |  |

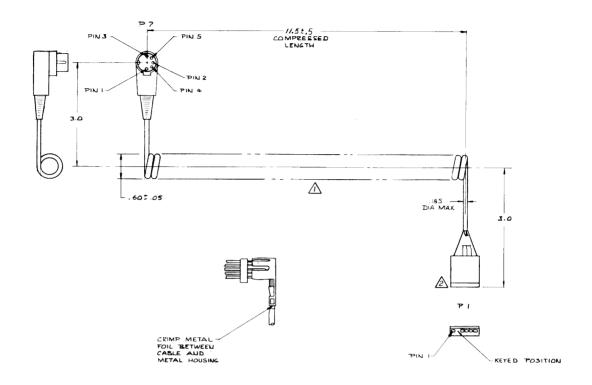

Keyboard Cable Assembly 6008072

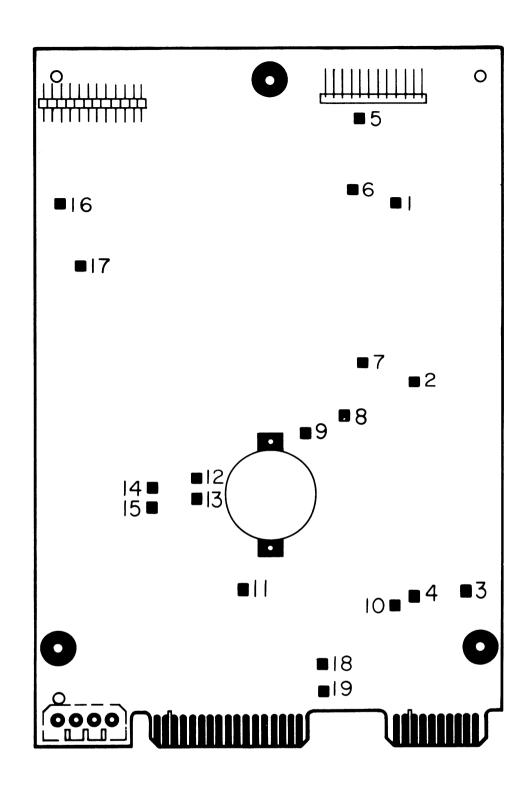

# MAIN LOGIC PCB REV. @

```

J1 - SERIAL INTERFACE (RS-232C)

(25-PIN FEMALE RT. ANGLE DB25)

```

| 01 | GROUND        | 02 | SERTD*        |

|----|---------------|----|---------------|

| 03 | SERRD         | 04 | SERRTS        |

| 05 | SERCTS        | 06 | SERDSR        |

| 07 | GROUND        | 80 | SERCD         |

| 09 | NO CONNECTION | 10 | NO CONNECTION |

| 11 | NO CONNECTION | 12 | NO CONNECTION |

| 13 | NO CONNECTION | 14 | NO CONNECTION |

| 15 | SERTXC        | 16 | NO CONNECTION |

| 17 | SERRXC        | 18 | NO CONNECTION |

| 19 | NO CONNECTION | 20 | SERDTR        |

| 21 | NO CONNECTION | 22 | SERRI         |

| 23 | NO CONNECTION | 24 | NO CONNECTION |

| 25 | NO CONNECTION |    |               |

|    |               |    |               |

#

| 01 | LPRDATSTB | 02 | GROUND    |

|----|-----------|----|-----------|

| 03 | LPRD0     | 04 | GROUND    |

| 05 | LPRD1     | 06 | GROUND    |

| 07 | LPRD2     | 08 | GROUND    |

| 09 | LPRD3     | 10 | GROUND    |

| 11 | LPRD4     | 12 | GROUND    |

| 13 | LPRD5     | 14 | GROUND    |

| 15 | LPRD6     | 16 | GROUND    |

| 17 | LPRD7     | 18 | GROUND    |

| 19 | LPRACK*   | 20 | GROUND    |

| 21 | LPRBSY    | 22 | GROUND    |

| 23 | LPRPAEM   | 24 | GROUND    |

| 25 | LPRSEL*   | 26 | STROBEIN  |

| 27 | GROUND    | 28 | LPRFLT*   |

| 29 | LPRINO    | 30 | LPRIN1    |

| 31 | GROUND    | 32 | LPRIN2 @  |

| 33 | GROUND    | 34 | INBUFFULL |

|    |           |    |           |

#### MAIN LOGIC PCB REV. PP2

- J3 MONOCHROME VIDEO

(8-PIN DIN RT. ANGLE)

- 1 NO CONNECTION

- 2 GROUND

- 3 INTMON

- 4 BUSHSYNC

- 5 BUSVSYNC

- 6 NO CONNECTION

- 7 VIDEOMON

- 8 NO CONNECTION

J4 - MATH CO-PROCESSOR CONNECTOR

(DUAL 31-PIN, 0.100" GRID)

| 01 | + 5 VOLTS     | 02  | GROUND   |

|----|---------------|-----|----------|

| 03 | S0*           | 04  | Sl*      |

| 05 | S2*           | 06  | RESET    |

| 07 | CLKOUT        | 8 0 | BHE*     |

| 09 | AD19          | 10  | AD18     |

| 11 | AD17          | 12  | AD16     |

| 13 | AD15          | 14  | AD07     |

| 15 | AD14          | 16  | AD06     |

| 17 | AD13          | 18  | AD05     |

| 19 | AD12          | 20  | AD04     |

| 21 | AD10          | 22  | ADll     |

| 23 | AD09          | 24  | AD03     |

| 25 | AD08          | 26  | AD02     |

| 27 | AD00          | 28  | AD01     |

| 29 | RD*           | 30  | RD*      |

| 31 | WR*           | 32  | WR*      |

| 33 | ALE           | 34  | ALE      |

| 35 | ARDY          | 36  | ARDY     |

| 37 | HOLD          | 38  | HOLD     |

| 39 | MCS0*         | 40  | MCS0*    |

| 41 | DT/R*         | 42  | DT/R*    |

| 43 | NO CONNECTION | 44  | MCS2*    |

| 45 | NO CONNECTION | 46  | MCS3*    |

| 47 | MCS1*         | 48  | MCSl*    |

| 49 | GROUND        | 50  | TEST*    |

| 51 | HLDA          | 52  | HLDA     |

| 53 | DEN*          | 54  | DEN*     |

| 55 | SRDY IN       | 56  | DRQ0     |

| 57 | SRDY OUT      | 58  | DRQ1     |

| 59 | LATCHED SRDY  | 60  | MCPINT14 |

| 61 | +5 VOLTS      | 62  | GROUND   |

|    |               |     |          |

NOTE: SIGNALS INTERCEPTED AND REGENERATED BY THE MATH CO-PROCESSOR ARE INDICATED BY BOLD FACE PRINT. A JUMPER TO THE CORRESPONDING SIGNAL IS REQUIRED WHEN THE MATH CO-PROCESSOR IS NOT USED. THESE JUMPERS ARE INCORPORATED ON THE PCB ARTWORK ON THE SOLDER SIDE OF THE BOARD AND MUST BE CUT WHEN INSTALLING THE MATH CO-PROCESSOR.

# MAIN LOGIC PCB REV. PP2

# J5 - MOTHER BOARD CONNECTOR (96-PIN MALE EUROCONNECTOR)

|     |               |     |               | 0.7 | NO CONNECTION |

|-----|---------------|-----|---------------|-----|---------------|

| 0la | NO CONNECTION | 01b | NO CONNECTION | 01c | NO CONNECTION |

| 02a | GND           | 02b | AGVID         | 02c | NO CONNECTION |

| 03a | GND           | 03b | GND           | 03c | GND           |

| 04a | BUSBLANK      | 04b | G/A           | 04c | BUSDOTCLK     |

| 05a | BUSCLK        | 05b | BUSHSYNC      | 05c | BUSVSYNC      |

| 06a | NMI*          | 06b | GND           | 06c | AINT          |

| 07a | BUSVLT        | 07b | NO CONNECTION | 07c | NO CONNECTION |

| 08a | BUSPCLK       | 08b | BUSINT03      | 08c | BUSPCS5*      |

| 09a | BUSRFSH*      | 09b | BUSINT16      | 09c | BUSPCS4*      |

| 10a | BUSIOR*       | 10b | HDCINT06      | 10c | BUSPCS3*      |

| lla | BUSHLDA*      | llb | RATINT12      | llc | BUSLOCK*      |

| 12a | BUSBHE*       | 12b | BUSIOW*       | 12c | BUSDMARQ1*    |

| 13a | BUSMCS1*      | 13b | BUSMCS0*      | 13c | BUSDMARQ2*    |

| 14a | BUSMR*        | 14b | BUSMW*        | 14c | BUSARDY*      |

| 15a | BUSRFINH*     | 15b | BUSL/E*       | 15c | BUSINT05      |

| 16a | BUSMRST*      | 16b | BUSDEN*       | 16c | BUSINT07      |

| 17a | BUSDT/R*      | 17b | BUSDMACK3*    | 17c | BUSINT17      |

| 18a | BUSDMACK2*    | 18b | MEMINT15      | 18c | BUSDMACK1*    |

| 19a | BUSALE        | 19b | BUSHOLD*      | 19c | BUSDMARQ3*    |

| 20a | GND           | 20b | GND           | 20c | GND           |

| 2la | BUSD04        | 21b | BUSD05        | 21c | BUSD03        |

| 22a | BUSD06        | 22b | BUSD07        | 22c | BUSD15        |

| 23a | BUSD00        | 23b | BUSD01        | 23c | BUSD02        |

| 24a | BUSD14        | 24b | BUSD10        | 24c | BUSD11        |

| 25a | BUSD13        | 25b | BUSD09        | 25c | BUSD12        |

| 26a | BUSD08        | 26b | BUSA04        | 26c | BUSA00        |

| 27a | BUSAll        | 27b | BUSA12        | 27c | BUSA07        |

| 28a | BUSA18        | 28b | BUSA17        | 28c | BUSA15        |

| 29a | BUSA19        | 29b | BUSA13        | 29c | BUSAl4        |

| 30a | BUSA08        | 30b | BUSA09        | 30c | BUSA01        |

| 3la | BUSA10        | 31b | BUSA03        | 31c | BUSA02        |

| 32a | BUSA16        | 32b | BUSA06        | 32c | BUSA05        |

|     |               |     |               |     |               |

#### MAIN LOGIC PCB REV. PP2

```

J6 - SYSTEM RAM INTERFACE

(40-PIN MALE HEADER, STRAIGHT)

01

IB01

02

IB00

03

IB02

04

IB04

05

IB03

06

IB05

07

IB07

80

IB06

09

DIPL

10

DOPL

11

WR0*

12

DMEMA06

13

RAS0*

14

DMEMA03

15

DMEMA00

16

DMEMA04

17

DMEMA02

18

DMEMA05

19

DME@A01

20

DMEMA07

21

GND

22

CASU*

23

GND

24

GND

25

+5 VOLTS

26

+5 VOLTS

27

+5 VOLTS

28

RAS1*

29

WR1*

30

CASL*

31

DOPU

32

DIPU

33

IB12

34

IB15

35

IBll

36

IB14

37

IB10

38

IB08

39

IB09

40

IB13

J7 - KEYBOARD INTERFACE

(5-PIN DIN, RT. ANGLE)

01

KBDDAT

02

KBDBSY*

03

GROUND

04

KBDCLK

05

KBDPOWER

J8 - RESET

(2-PIN MOLEX W/FRICTION LOCK)

01

RES*

02

GROUND@

J9 - SPEAKER

(2-PIN MALE HEADER, POLARIZED)

01

SPKDRV

02

GROUND

```

29

31

33

GROUND

**GROUND**

GROUND

```

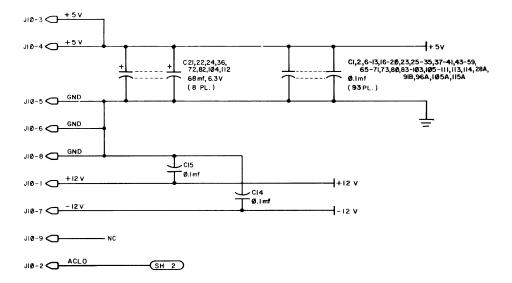

J10 - DC POWER

(9-PIN MALE HEADER, POLARIZED)

01

+12 VOLTS

02

ACLO*

03

+5 VOLTS

04

+5 VOLTS

05

GND

06

GND

07

-12 VOLTS

80

.GND

09

NO CONNECTION

J11 - FLOPPY DISK CONTROLLER INTERFACE

(34-PIN MALE HEADER, STRAIGHT)

01

02

NO CONNECTION

GROUND

0.4

FLDINUSE*

03

GROUND

05

GROUND

06

NO CONNECTION

07

80

FLDIDX*

GROUND

10

09

FLDDS0*

GROUND

12

11

FLDDS1*

GROUND

13

14

NO CONNECTION

GROUND

15

16

FLDMTRON*

GROUND

17

18

FLDDIR*

GROUND

20

FLDSTP*

19

GROUND

22

21

FLDWRDAT*

GROUND

23

GROUND

24

FLDWE*

26

25

FLDTRK0*

GROUND

27

28

FLDWRPRT*

GROUND

```

30

32

34

FLDRDDAT\*

FLDSDSEL\*

FLDRDY\*

| EXPANSION RAM PIN DEFINITIONS (J13 - EXPANSION RAM BD.) |               |    |          |  |  |

|---------------------------------------------------------|---------------|----|----------|--|--|

| 01                                                      | IB01          | 02 | IB00     |  |  |

| 03                                                      | IB02          | 04 | IB04     |  |  |

| 05                                                      | IB03          | 06 | IB05     |  |  |

| 07                                                      | IB07          | 08 | IB06     |  |  |

| 09                                                      | DIPL          | 10 | DOPL     |  |  |

| 11                                                      | NO CONNECTION | 12 | DMEMA06  |  |  |

| 13                                                      | NO CONNECTION | 14 | DMEMA03  |  |  |

| 15                                                      | DMEMA00       | 16 | DMEMA04  |  |  |

| 17                                                      | DMEMA02       | 18 | DMEMA05  |  |  |

| 19                                                      | DMEMA01       | 20 | DMEMA07  |  |  |

| 21                                                      | GND           | 22 | CASU*    |  |  |

| 23                                                      | GND           | 24 | GND      |  |  |

| 25                                                      | +5 VOLTS      | 26 | +5 VOLTS |  |  |

| 27                                                      | +5 VOLTS      | 28 | RAS1*    |  |  |

| 29                                                      | WRl*          | 30 | CASL*    |  |  |

| 31                                                      | DOPU          | 32 | DIPU     |  |  |

| 33                                                      | IB12          | 34 | IB15     |  |  |

| 35                                                      | IBll          | 36 | IB14     |  |  |

| 37                                                      | IB10          | 38 | IB08     |  |  |

| 39                                                      | IB09          | 40 | IB13     |  |  |

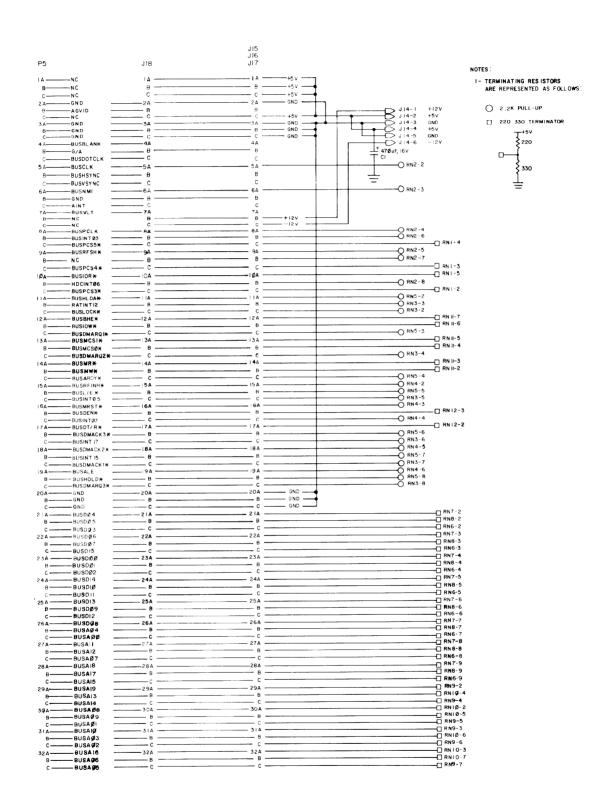

OPTION CARD CONNECTOR PIN ASSIGNMENTS (96-PIN EUROCONNECTOR)

| 01a | +5 VOLTS   | 01b | +5 VOLTS   | 01c | +5 VOLTS   |

|-----|------------|-----|------------|-----|------------|

| 02a | GND        | 02b | AGVID      | 02c | +5 VOLTS   |

| 03a | GND        | 03b | GND        | 03c | GND        |

| 04a | BUSBLANK   | 04b | G/A        | 04c | BUSDOTCLK  |

| 05a | BUSCLK     | 05b | BUSHSYNC   | 05c | BUSVSYNC   |

| 06a | NMI*       | 06b | GND        | 06c | AINT       |

| 07a | BUSVLT     | 07b | +12 VOLTS  | 07c | -12 VOLTS  |

| 08a | BUSPCLK    | 08b | BUSINT03   | 08c | BUSPCS5*   |

| 09a | BUSRFSH*   | 09b | BUSINT16   | 09c | BUSPCS4*   |

| 10a | BUSIOR*    | 10b | HDCINT06   | 10c | BUSPCS3*   |

| lla | BUSHLDA*   | llb | RATINT12   | llc | BUSLOCK*   |

| 12a | BUSBHE*    | 12b | BUSIOW*    | 12c | BUSDMARQ1* |

| 13a | BUSMCS1*   | 13b | BUSMCS0*   | 13c | BUSDMARQ2* |

| 14a | BUSMR*     | 14b | BUSMW*     | 14c | BUSARDY*   |

| 15a | BUSRFINH*  | 15b | BUSL/E*    | 15c | BUSINT05   |

| 16a | BUSMRST*   | 16b | BUSDEN*    | 16c | BUSINT07   |

| 17a | BUSDT/R*   | 17b | BUSDMACK3* | 17c | BUSINT17   |

| 18a | BUSDMACK2* | 18b | MEMINT15   | 18c | BUSDMACK1* |

| 19a | BUSALE     | 19b | BUSHOLD*   | 19c | BUSDMARQ3* |

| 20a | GND        | 20b | GND        | 20c | GND        |

| 2la | BUSD04     | 21b | BUSD05     | 21c | BUSD03     |

| 22a | BUSD06     | 22b | BUSD07     | 22c | BUSD15     |

| 23a | BUSD00     | 23b | BUSD01     | 23c | BUSD02     |

| 24a | BUSD14     | 24b | BUSD10     | 24c | BUSD11     |

| 25a | BUSD13     | 25b | BUSD09     | 25c | BUSD12     |

| 26a | BUSD08     | 26b | BUSA04     | 26c | BUSA00     |

| 27a | BUSAll     | 27b | BUSA12     | 27c | BUSA07     |

| 28a | BUSA18     | 28b | BUSA17     | 28c | BUSA15     |

| 29a | BUSA19     | 29b | BUSA13     | 29c | BUSA14     |

| 30a | BUSA08     | 30b | BUSA09     | 30c | BUSA01     |

| 3la | BUSA10     | 31b | BUSA03     | 31c | BUSA02     |

| 32a | BUSA16     | 32b | BUSA06     | 32c | BUSA05     |

|     |            |     |            |     |            |

```

MOUSE INTERFACE

(9-PIN "D" TYPE, FEMALE RT. ANGLE)

01

GROUND

02

+5 VOLTS

03

S3*

04

ΧA

05

06

S2*

XВ

07

Sl*

80

YΑ

09

YΒ

```

# COLOR MONITOR PIN ASSIGNMENT (GRAPHICS BD.)

- 1 GROUND

- 2 GROUND

- 3 RED

- 4 GREEN

- 5 BLUE

- 6 INTENSITY

- 7 NO CONNECTION

- 8 HSYNC

- 9 VSYNC

#### 6/ Troubleshooting Procedures

#### 6.1 Power Supply

General diagnostics can be performed on the power supply without removing it from the chassis.

To check the power supply for correct outputs to the logic board and floppy disk, simply remove the top cover of the main unit and disconnect the power connector (P30) from the top floppy disk drive. Check for +12 Vdc (pin 1) and +5 Vdc (pin 4). If these voltages are present, replace the plug and remove the power connector (P10) from the main logic board. Check for +12 Vdc (pin 1), -12 Vdc (pin 7), and +5 Vdc (pins 3 and 4).

#### CAUTION

DO NOT DISCONNECT BOTH PLUGS at the same time. To function properly, the power supply must have a minimum load.

If any of the voltages do not conform to the specifications contained in Paragraph 7.2.1.1, the power supply and/or harness may be defective. Remove the power supply and troubleshoot using Paragraph 7.2.1.2.

For troubleshooting the power supply assembly, see Section 7.5.4.

#### 6.2 Other Components

If all voltages are present as described in Paragraph 6.1 and the unit is still inoperative, replace first the RAM board and then the CPU to correct the problem. Refer to Paragraph 7.5.2 for a theory of operation on the RAM boards and 7.1.2 for the CPU theory.

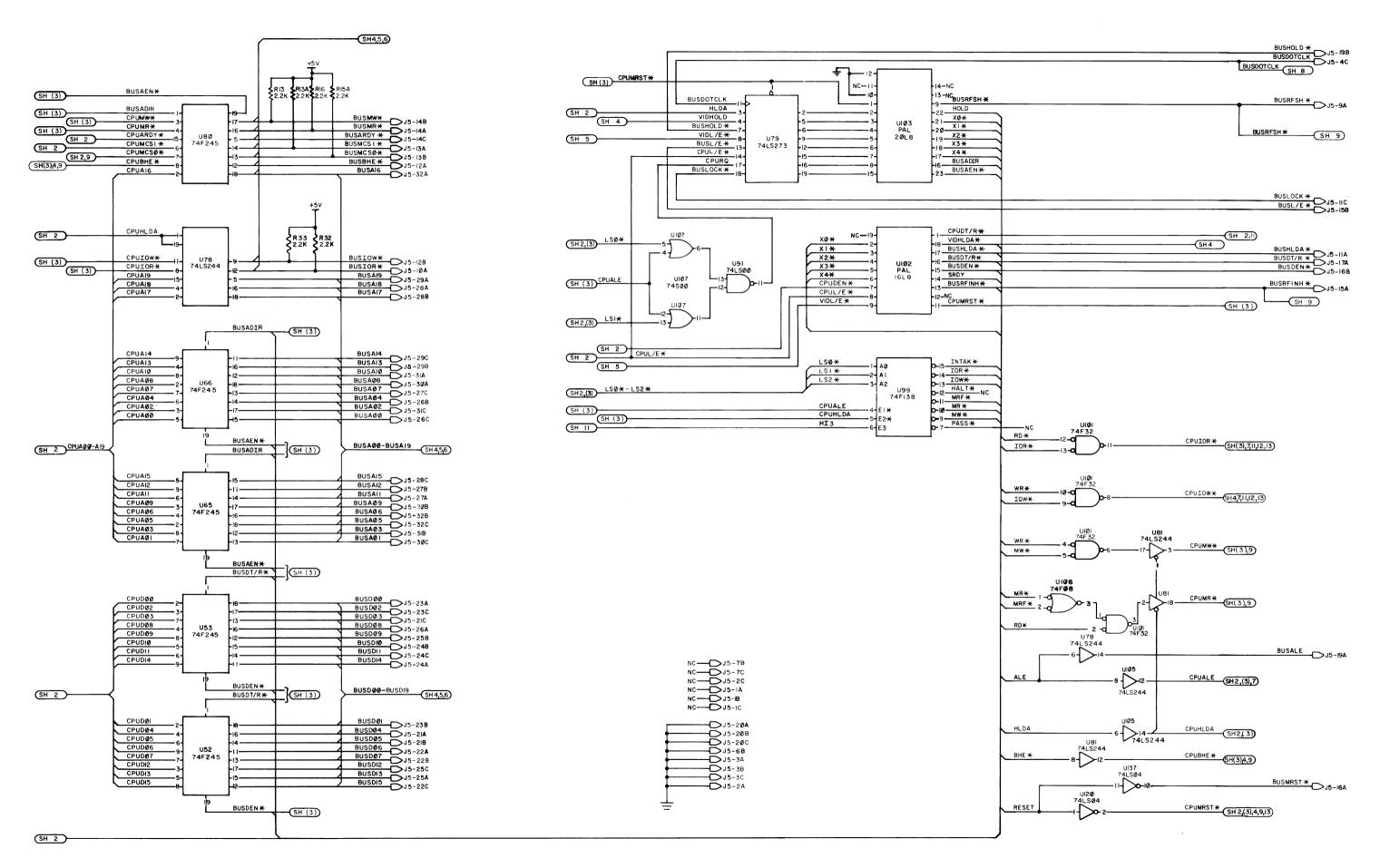

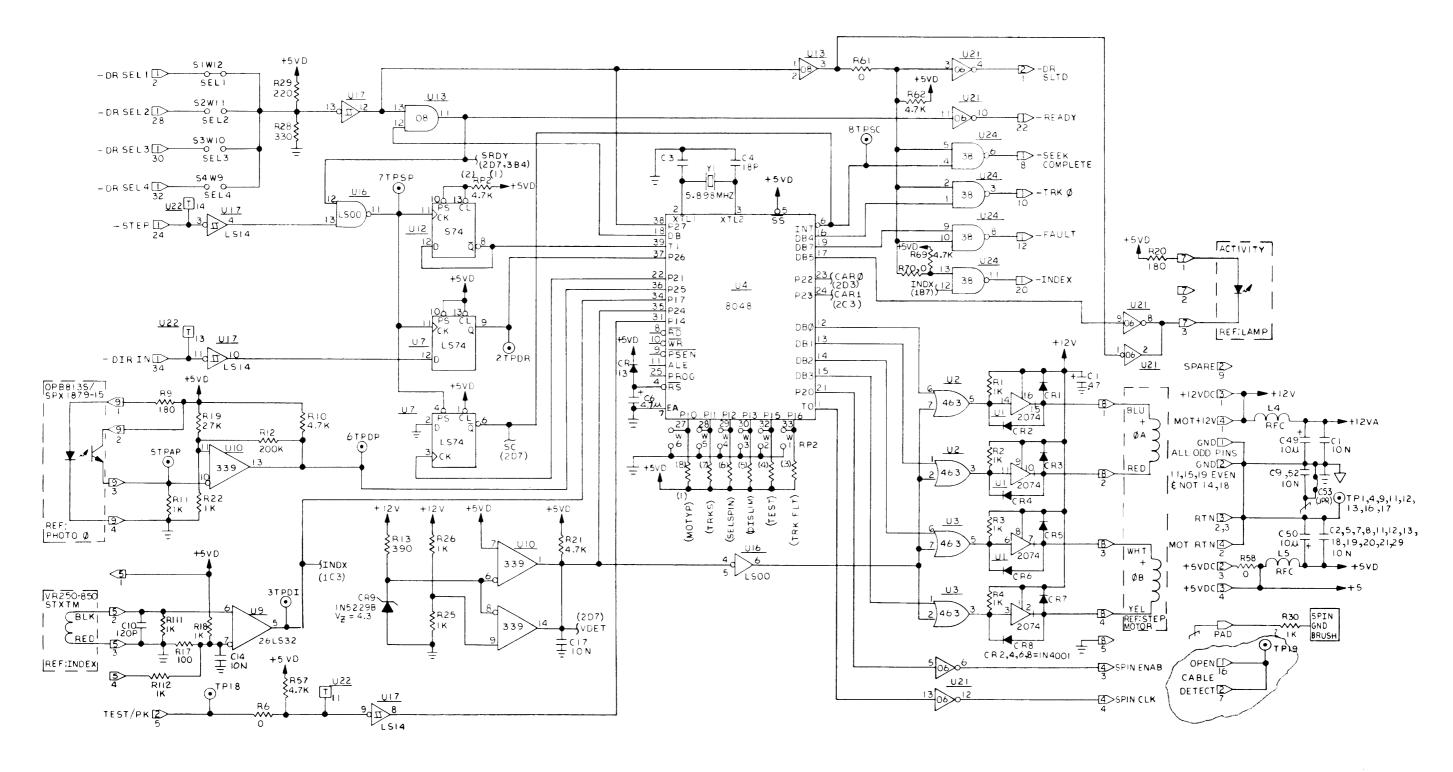

# 7/ Theory of Operation

This section of the manual contains an explanation of the components used in the Model 2000 Microcomputer. It includes a discussion of the Main Logic Board, Power Supply Board(s), and optional boards. The discussions on the Main Logic Board are related to the overall block diagram shown in Figure 7.1. Each subsection contains a simplified block diagram, referenced to a specific page of schematic. The complete schematic of the Main Logic Board is located at the end of Section 7.1. The Power Supply used in the Model 2000 is described in Paragraph 7.2, as well as the supply required for the addition of a Hard Disk Drive Assembly. The Disk Drive Assembly description is contained in Paragraph 7.3. Information concerning the Card Cage Assembly and Motherboard is contained in Paragraph 7.4.

Discussion of optional features, such as 128K Add-On Memory, B/W Graphics Board, Color Graphics Option, Color Monitor, TV/Joystick Board, and Mouse/Clock Board is contained in the manual covering the specific option.

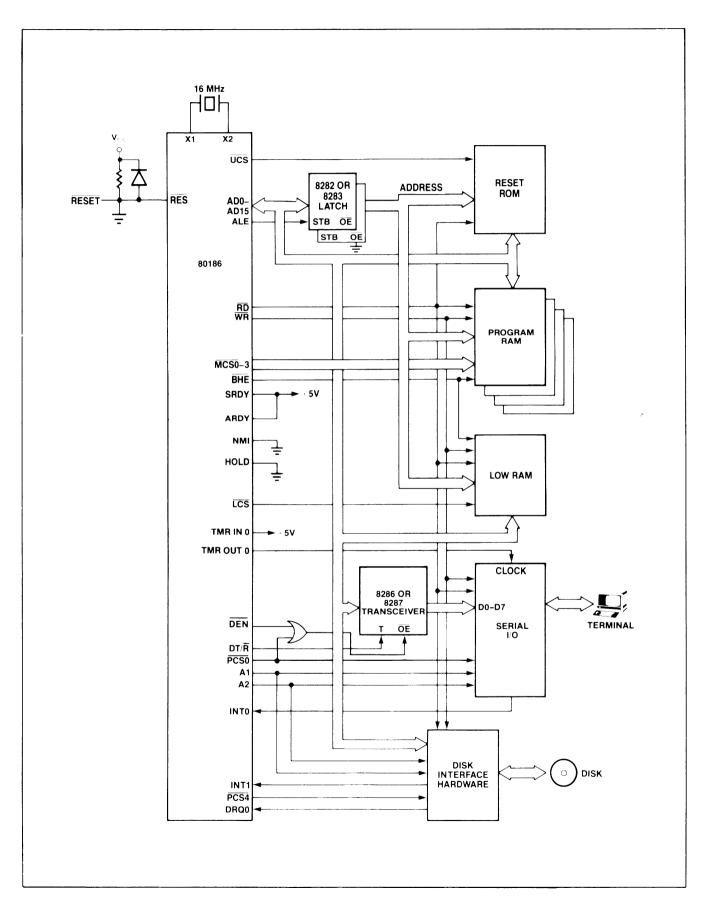

Figure 7.1 Model 2000 Functional Block Diagram

# 7.1 Main Logic Board

# 7.1.1 General

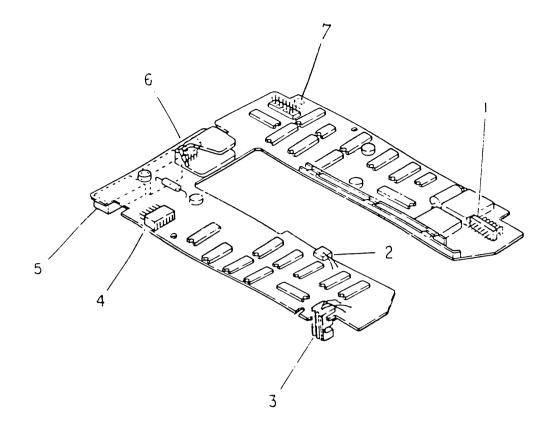

The Main Logic Board is mounted to the underside of the Main Unit and is accessible from the underside. It is mounted to a pan assembly which provides protection and support for the board which is approximately 10" x 16". It contains connectors which allow it to be interconnected to the power supply, disk drives, reset circuitry, and motherboard assembly for optional boards.

See Section 3 for disassembly procedures for the Main Logic Board.

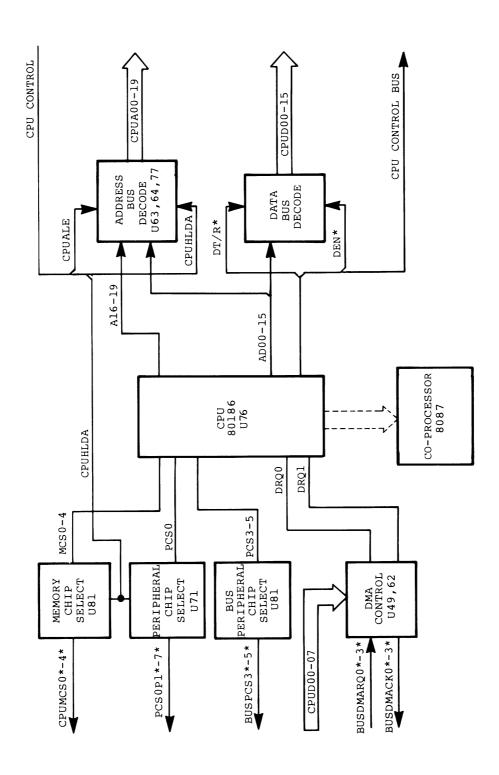

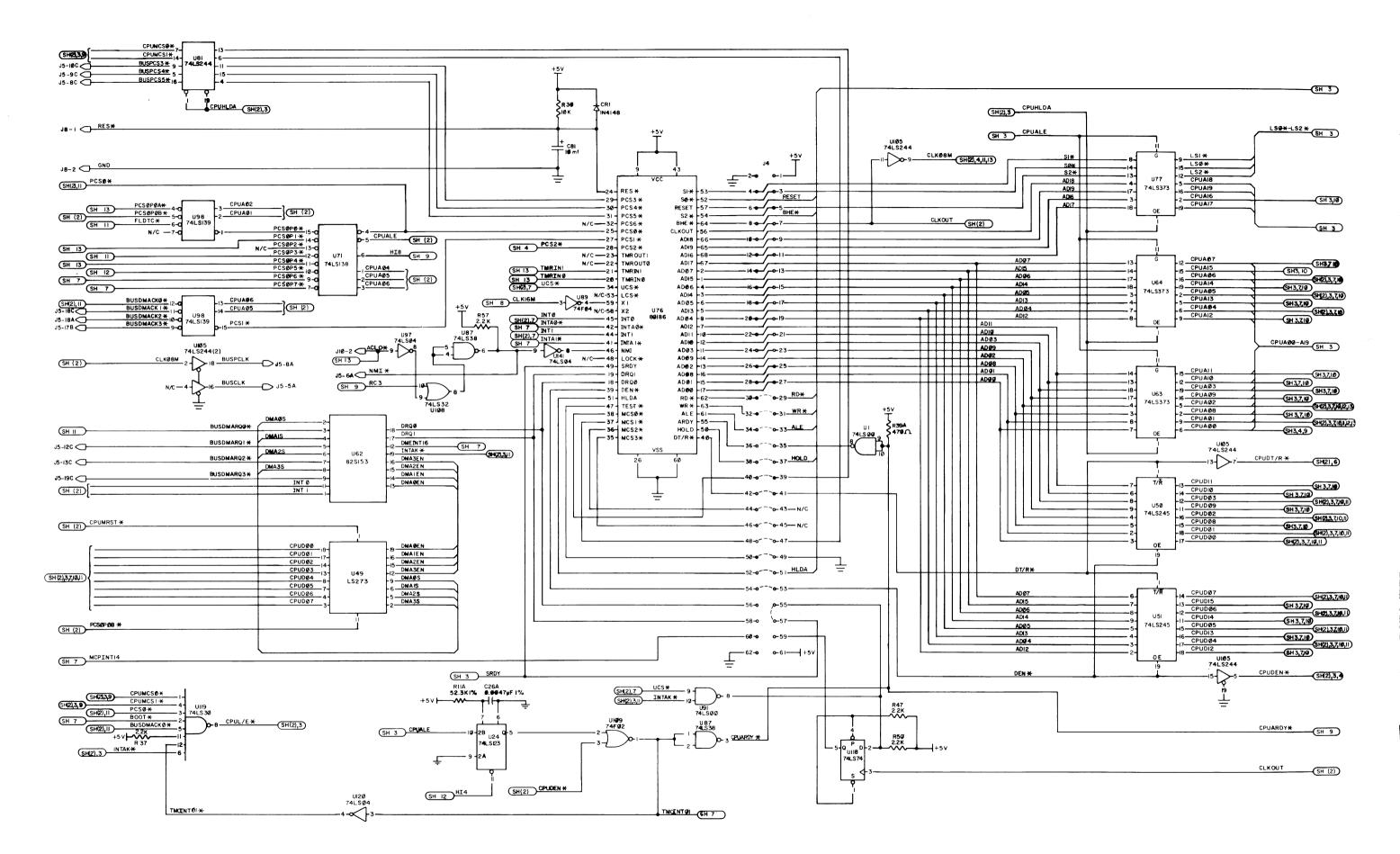

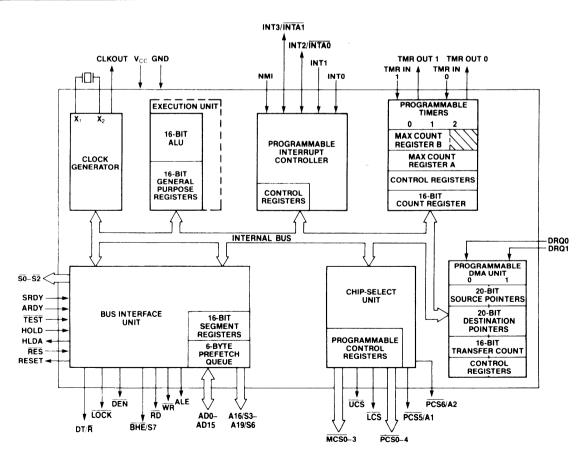

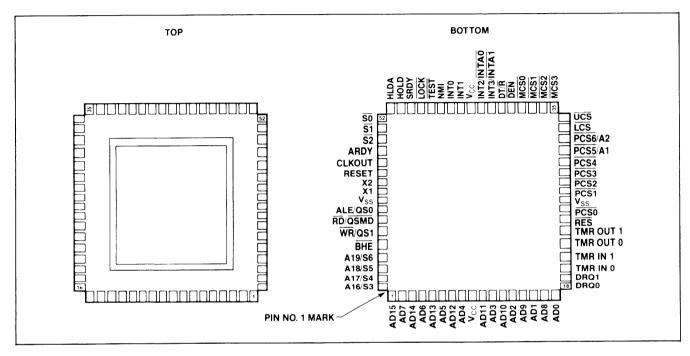

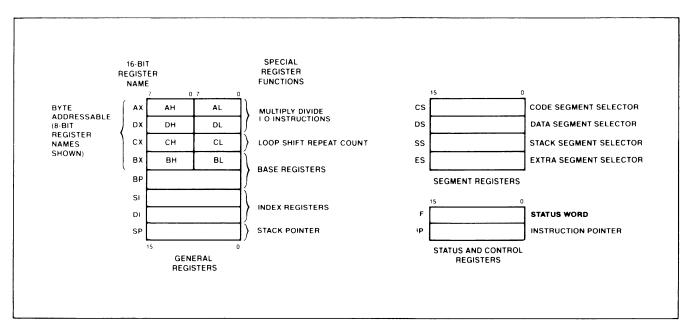

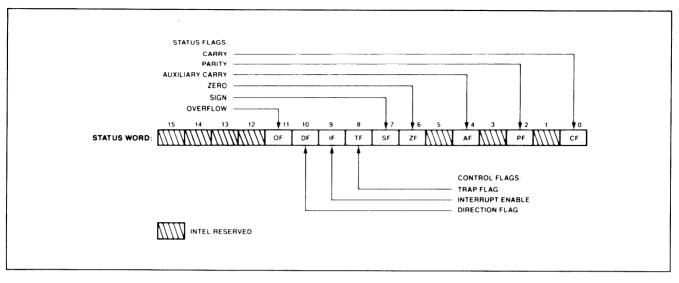

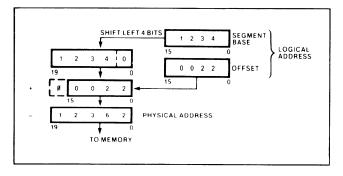

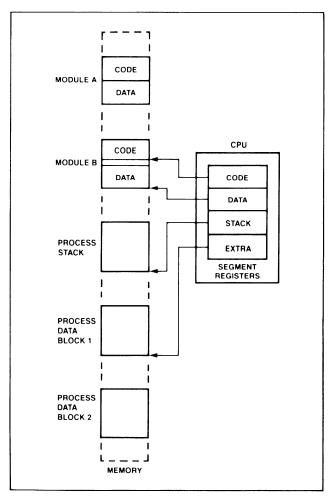

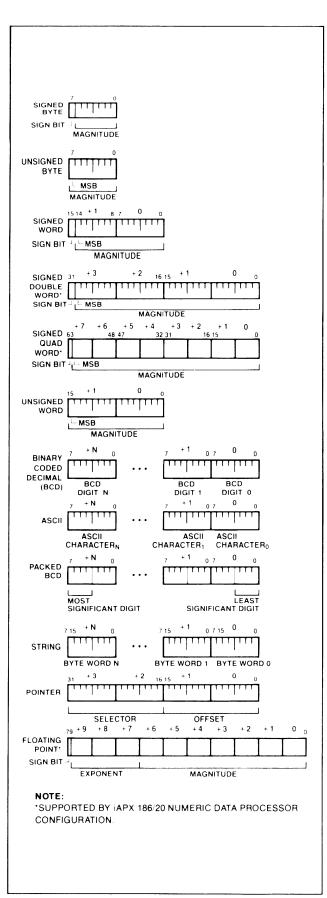

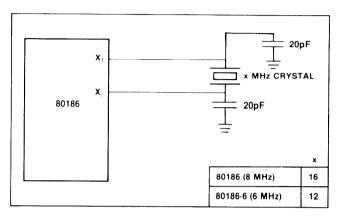

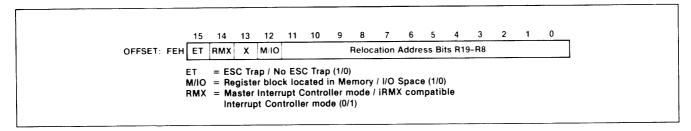

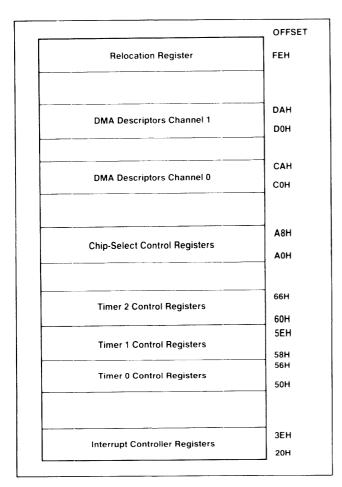

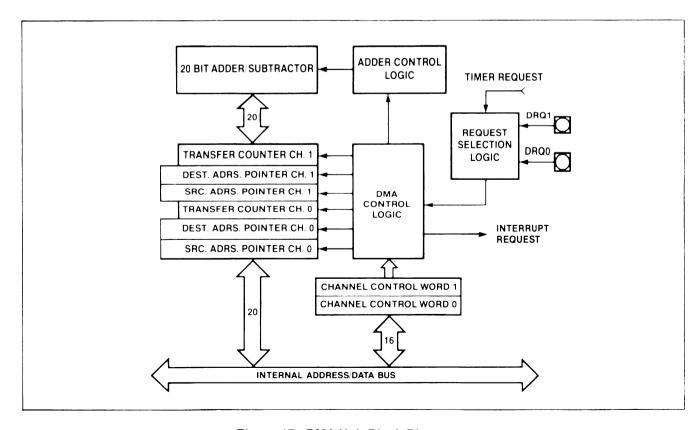

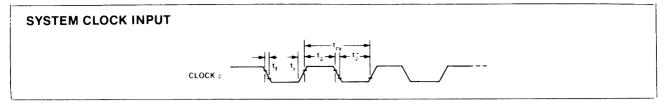

#### 7.1.2 CPU (Sheet 2)

The CPU (Central Processing Unit) revolves around an Intel 80186 microprocessory chip with a clock input of 16 MHz (this yields a 125 nsec machine cycle or "T" state). It is assumed that the reader is familiar with 80186 timing and interfacing. For more information, refer to Intel literature. The CPU section includes logic to buffer and latch all data and address signals. All chip selects (except the boot ROM and character generator) are generated by this section also. A "fail safe" memory timeout circuit prevents the 80186 from waiting forever for a non-existent memory or port address to respond. A programmable DMA (Direct Memory Access) multiplexer maps four bus DMA channels into the two channels resident on the 80186. Logic that directs the bus controller to point the system buses in the right direction is contained here also.

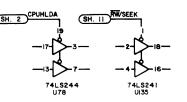

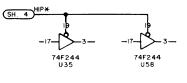

# 7.1.2.1 CPU Buffering

The Intel 80186 uses a multiplexed address-data bus. The bus is demultiplexed using 74SL373 8-bit transparent latches and 74LS245 octal bi-directional bus drivers. The 74LS373 is enabled for output by CPUHLDA (CPU HoLD Acknowledge, active high) so that it may drive the address bus while the 80186 has the control of the system. The latches are controlled by CPUALE (CPU Address Latch Enable, active high). The falling edge of CPUALE locks the data into the latches for the entire memory cycle. Al6 - Al9 are not multiplexed with data but require latching as do S0\* - S2\* (Processor Status bits 0 - 2).

The data buffers are controlled by 80186 generated signals DEN\* (Data ENable, active low) and DT/R\* (Data Transmit/Receive, high for write cycles, low for read cycles). Within the first T state, DT/R\* is set to point the data buffers in the right direction, and DEN\* goes low when data appears on the bus.

# 7.1.2.2 CPU Address Decoding

Address decoding falls into two categories: memory and peripheral. Each is identified by unique read and write status codes on S0\* - S2\*. The 80186 is software programmable to generate select signals to both spaces. The Model 2000 will always be programmed as shown in Figure 1.

Figure 7-1. CPU Block Diagram

| Signal    | Memory/Peripheral | Address Range   |

|-----------|-------------------|-----------------|

| LCS*      | М                 | Not Used        |

| MCS0*     | M                 | 00000H - 1FFFFH |

| MCS1*     | М                 | 20000H - 3FFFFH |

| MCS2*     | M                 | 40000H - 5FFFFH |

| (not used | )                 |                 |

| MCS3*     | M                 | 60000н - 7ғғғғн |

| (not used | )                 |                 |

| UCS*      | M                 | F8000H -FFFFFH  |

|           |                   |                 |

| PCS0*     | P                 | 0000н - 007гн   |

| PCS1*     | P                 | 0080H - 00FFH   |

| PCS2*     | P                 | 0100H - 017FH   |

| PCS3*     | P                 | 0180H - 01FFH   |

| PCS4*     | P                 | 0200H - 027FH   |

| PCS5*     | P                 | 0280H - 02FFH   |

| PCS6*     | P                 | 0300н - 037ғн   |

| (not used | )                 |                 |

#### NOTE:

MCSn\* address areas are programmed to insert 0 wait states and use 80186 ready inputs. The UCS\* address area is programmed to insert 3 wait states and ignore 80186 ready inputs. All PCSn\* areas are programmed to insert 2 wait states and ignore 80186 ready inputs.

Figure 7-2. 80186 Programmed Chip Selects

Most internal peripherals are mapped into PCSO\* space. This space is split into eight 16-byte active low chip selects by a 74LS138. Both PCSO\* and CPUALE condition the 74LS138 to guarantee the subsequent chip selects are valid only when all address bits are stable. The first block of 16 addresses is further broken into four 2-byte blocks (mirrored twice) by 1/2 of a 74LS139. Address assignments are given in Figure 7-4.

| Address                                                                                                                                                                                | Name                                              | Devic                                | e                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000H - 0001H<br>0002H - 0003H<br>0004H - 0005H<br>0006H - 0007H<br>0010H - 001F<br>0020H - 002FH<br>0030H - 003FH<br>0040H - 004FH<br>0050H - 005FH<br>0060H - 006FH<br>0070H - 007FH | PCS<br>FLD<br><br>PCS<br>PCS<br>PCS<br>PCS<br>PCS | 60P0B* DTC* G0P1 60P2 60P3 60P4 60P5 | Speaker/clocks control DMA Multiplexer control Floppy Disk Term. Count Unused (no connect) 8251A Unused (no connect) 8272A 8253-5 8255A-5 8259A (Controller 0) 8259A (Controller 1) |

Figure 7-3. Peripheral Chip Select 0 Address Assignments

Four DMA acknowledge channels are generated at a base address of 0080H in CPU peripheral address space (See Figure 3). Each one is thrity-two bytes in length. BUSDMACK0\* (BUS DMA ACKnowledge 0, active low) is dedicated to the internal floppy disk controller and BUSDMACK3\* is dedicated to the internal hard disk. BUSDMACK1\* - BUSDMACK3\* are routed to the expansion bus connector.

| Address                     | Name | Device     |                      |  |  |

|-----------------------------|------|------------|----------------------|--|--|

| 0080H - 009FH               |      | BUSDMACK0* | Internal Floppy Disk |  |  |

| Controller<br>00A0H - 00BFH |      | BUSDMACK1* | No assignment        |  |  |

| 00C0H - 00DFH               |      | BUSDMACK2* | No assignment        |  |  |

| 00E0H - 00FFH               |      | BUSDMACK3* | Hard Disk Controller |  |  |

Figure 7-4. DMA Acknowledge Address Assignments

An additional level of decoding is required to support the Model 2000 bus structure. The CPUL/E\* (CPU Local/External, high for local, low for external) is generated by a 74LS30 8-input NAND gate. The decoded chip selects for CPUMCS0\*, CPUMCS1\*, PCS0\*, BOOT\*, and BUSDMACK0\* as well as INTAK\* and TMOINT01\* constitute local addresses. All other addresses are external.

### 7.1.2.3 Synchronous and Asynchronous Ready

Addressed memory and peripherals handshake with the CPU indicates that a transaction is complete by pulling CPUARDY\* (CPU Asynchronous ReaDY, active low wire OR bus) low. Devices not required to handshake in this manner are those which are selected by a memory or peripheral chip select that ignores external ready inputs (See Figure 7.1), with the exceptions being the boot ROM and any interrupt acknowledge cycle (see next paragraph). CPURDY\* is then inverted and connected to the ARDY (Asynchronous ReaDY, active high) input on the CPU. Once synchronized inside the CPU, ARDY is ORed with the SRDY (Synchronous ReaDY, active high) so that if either input is a logic "l", the CPU will assume that the addressed device is ready to complete the transaction.

The SRDY input to the CPU is handled differently. When the CPU is reset, UCS\* (Upper memory Chip Select, active low from which the boot ROM chip select is generated) will have three wait states inserted automatically and will include external ready inputs. Because no logic provision was included for a UCS\* addressed device to respond to the CPUARDY\* bus, the CPU will wait indefinitely. A corresponding situation exists for INTAK\* (INTerrupt AcKnowledge, active low). To overcome this, UCS\* and INTAK\* are logically ORed together to generate an active high signal whenever either input is active low. This signal is routed directly to the CPU SRDY input as well as to a 74LS74 which synchronizes it to the CPU clock for use with a co-processor.

#### 7.1.2.4 Memory Timeout

A safeguard circuit is included to prevent the CPU from waiting an excessive amount of time for memory to respond with a ready. Revolving around a 74LS123 timer set for approximately 100 usec, the circuit begins timing a transaction at the leading edge of CPUALE. This forces the timer's Q output to a logical "l". The Q output is gated with CPUDEN\* to form TMOINTOl (TiMeOut INTerrupt controller 0, level 1, active high) which goes active only if the timer times out while a transaction is still in progress (signaled by CPUDEN\* remaining active low). TMOINTOl is inverted by an open collector gate and output in the correct sense to the CPUARDY\* bus and remains low until CPUDEN\* goes inactive, indicating that the CPU acknowledges the handshake. Concurrent with this operation, CPUL/E\* is forced to the local state (logic "l") so that the bus

drivers are forced inactive. This action prevents a contention on the CPUARDY\* bus. If the transaction completes before a timeout, the time will continue until it is restarted by another CPUALE or until it times out. (The system will not see this timeout because CPUDEN\* is inactive.)

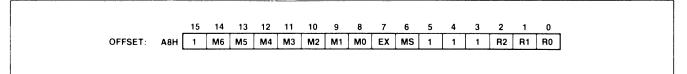

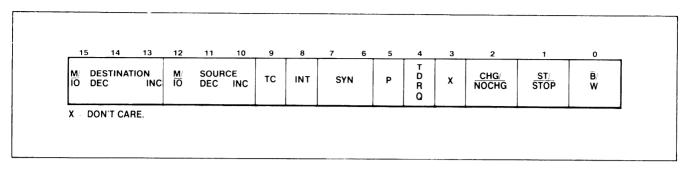

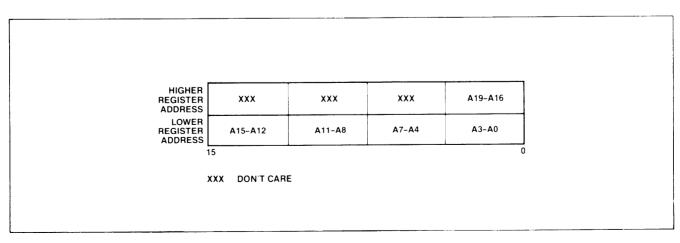

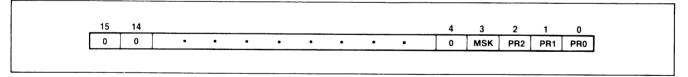

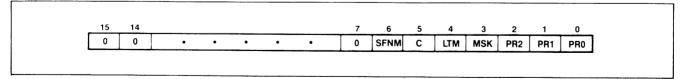

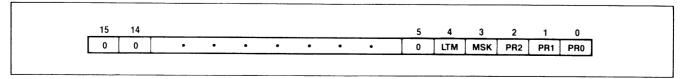

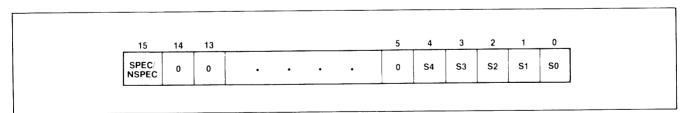

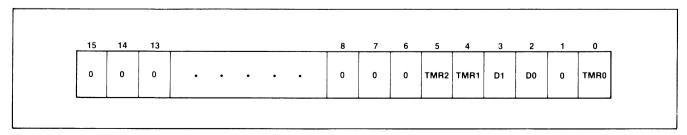

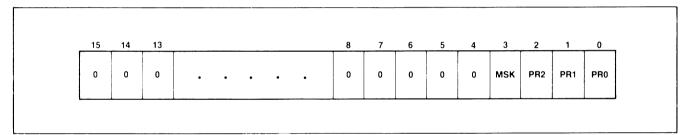

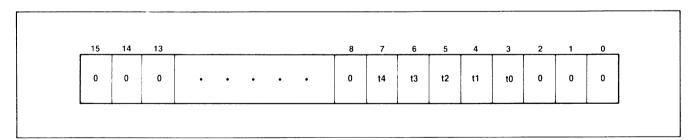

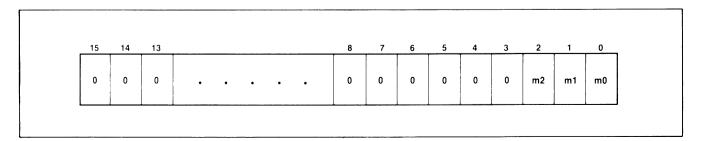

### 7.1.2.5 Four Channel DMA Multiplexer

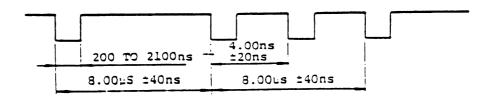

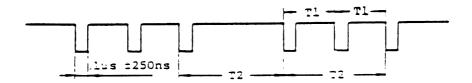

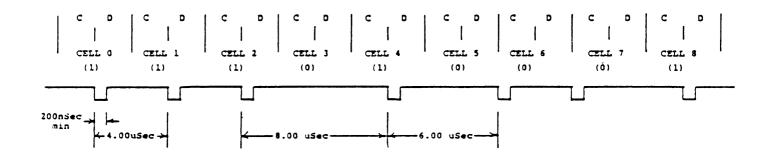

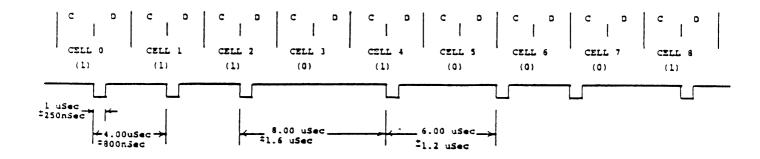

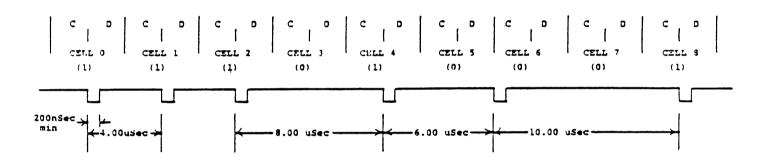

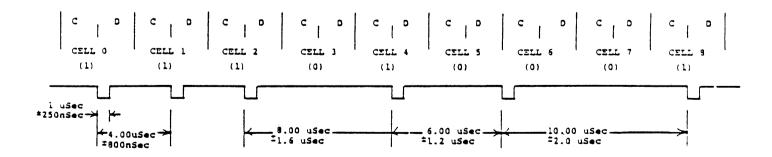

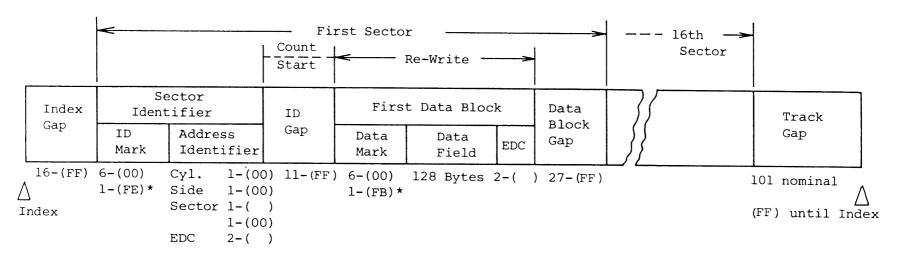

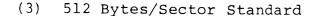

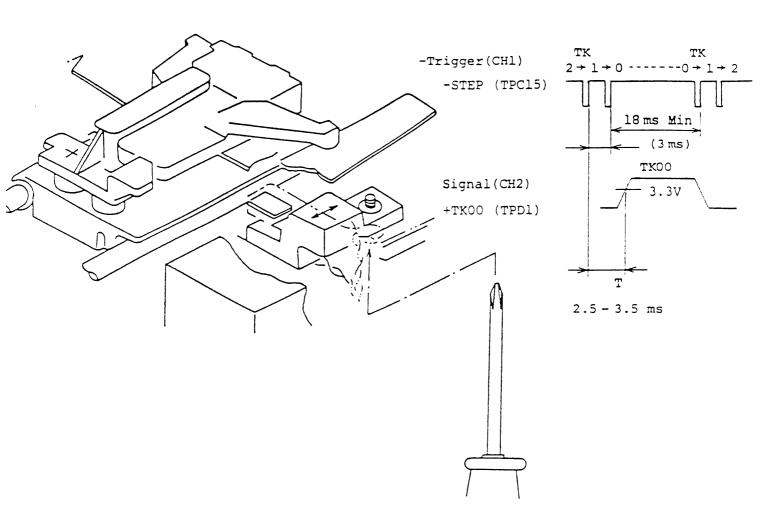

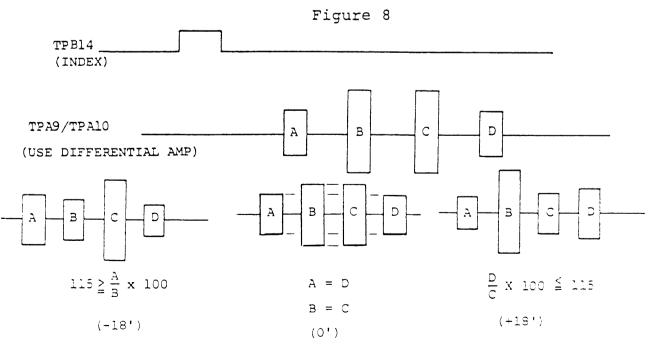

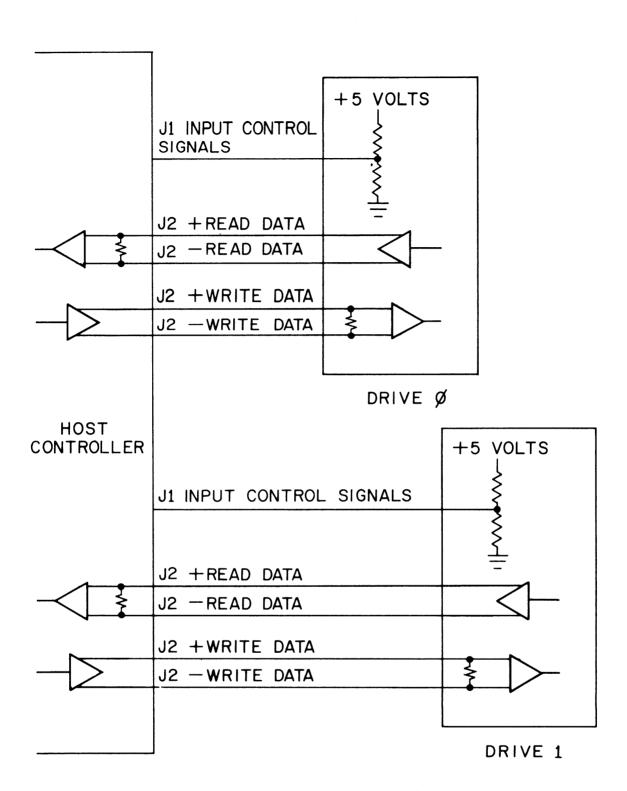

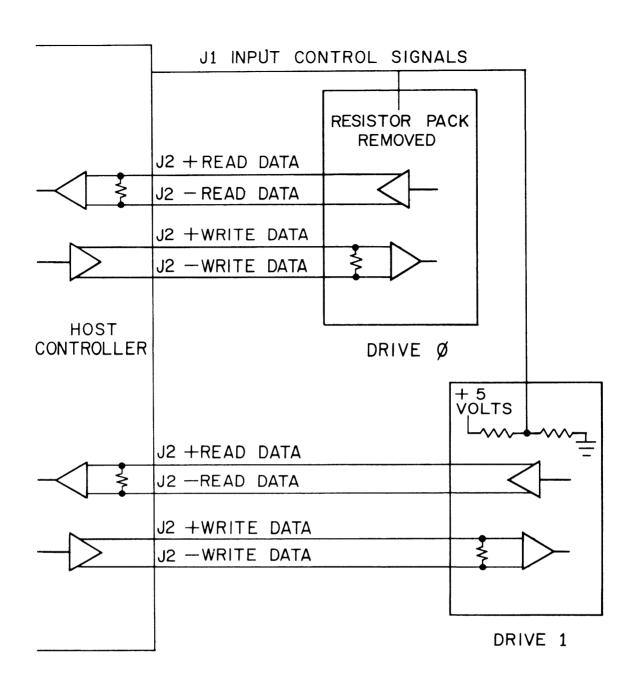

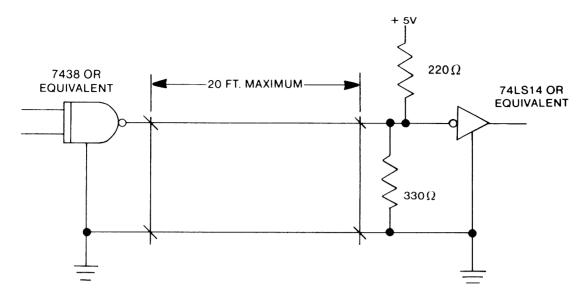

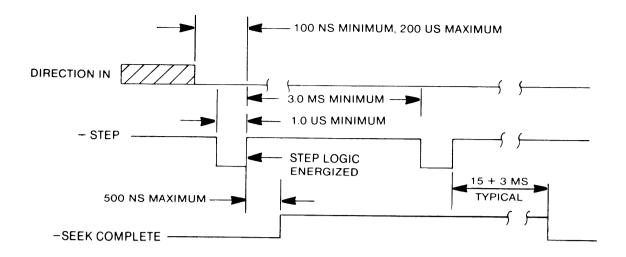

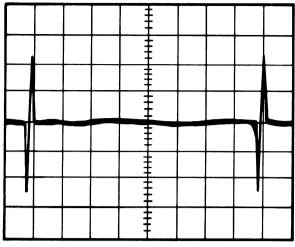

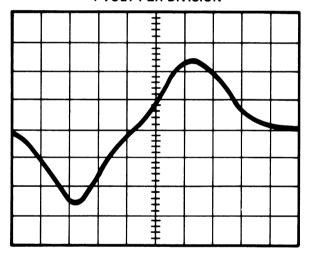

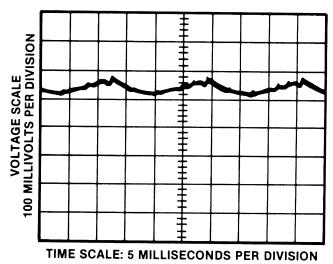

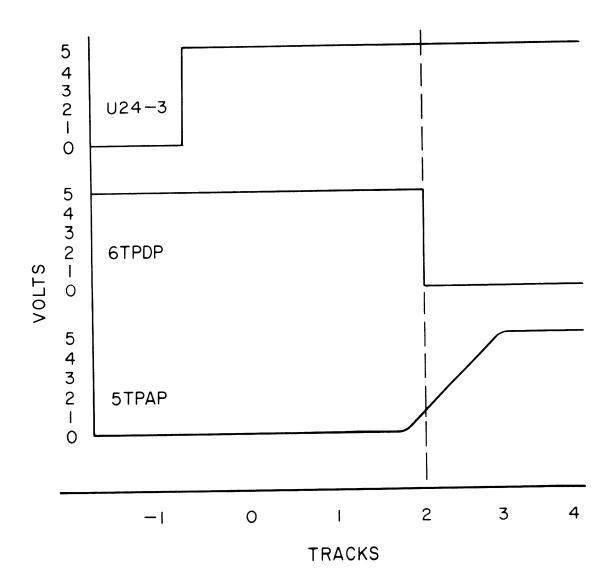

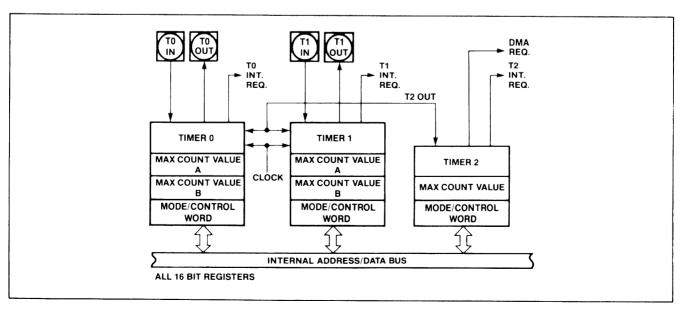

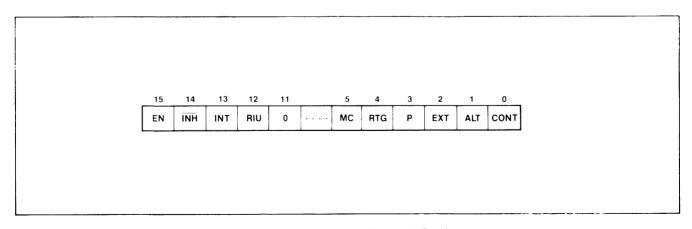

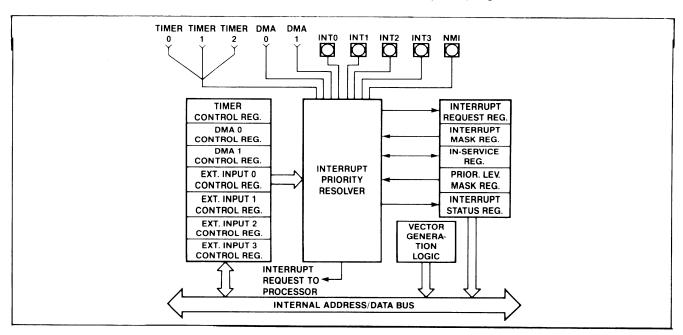

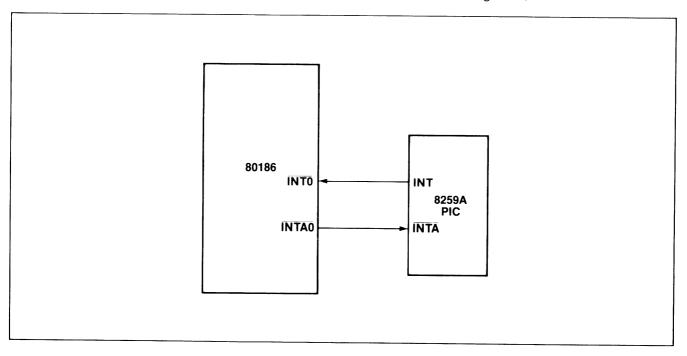

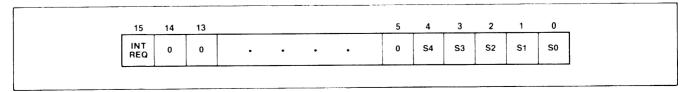

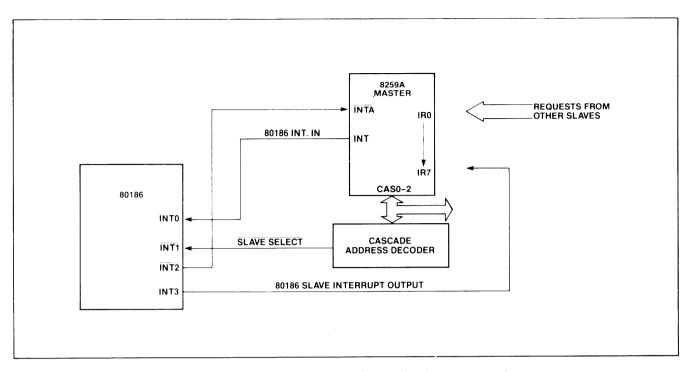

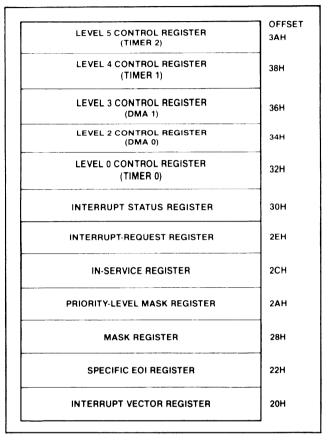

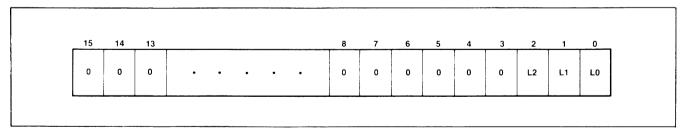

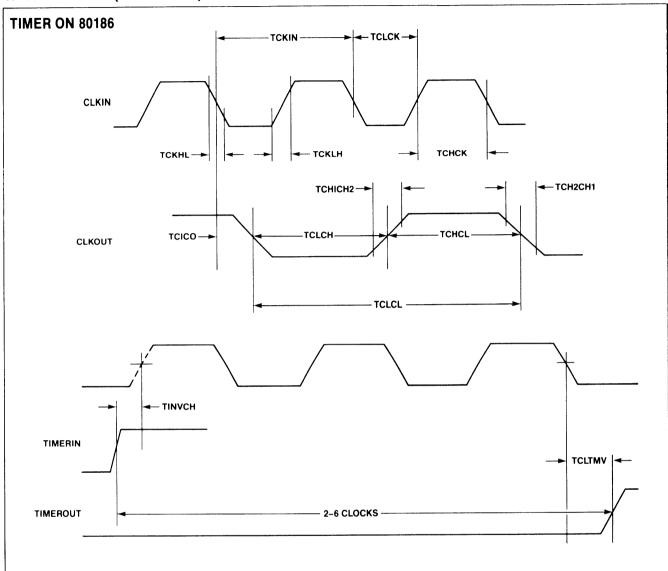

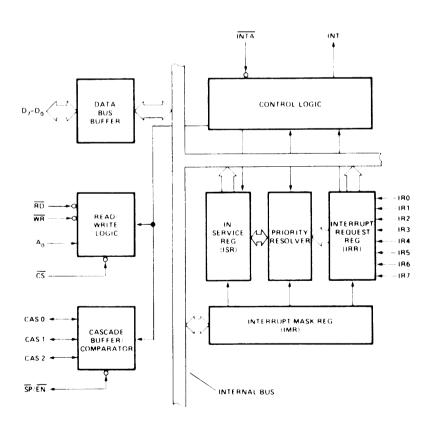

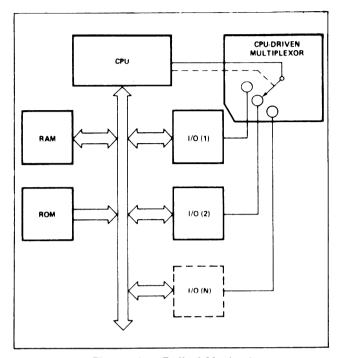

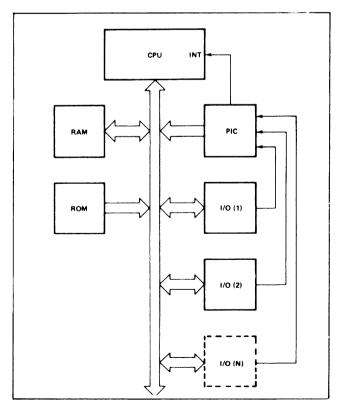

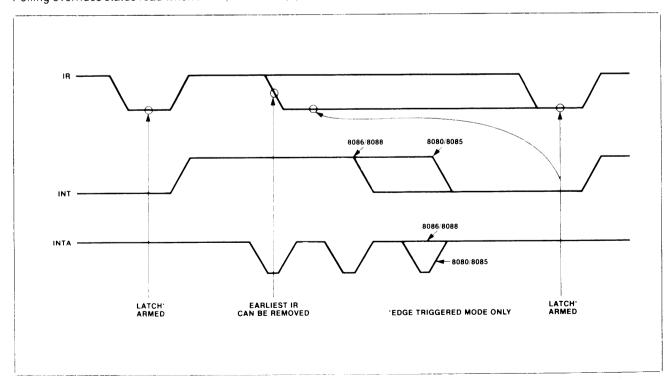

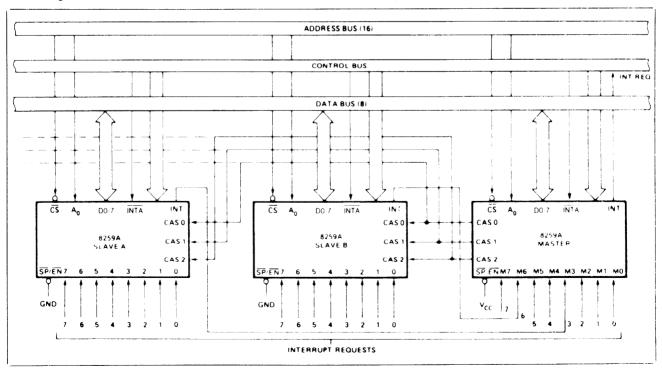

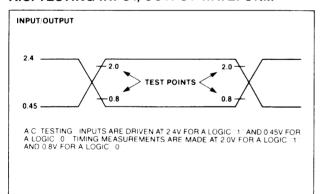

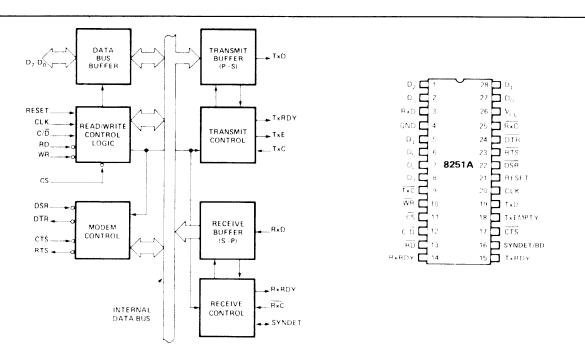

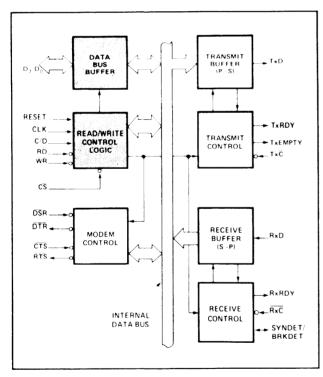

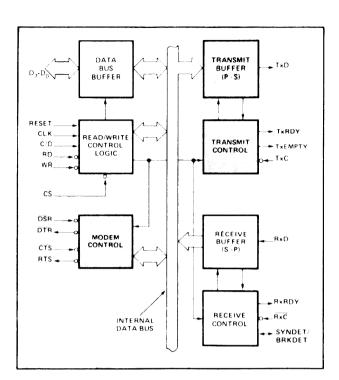

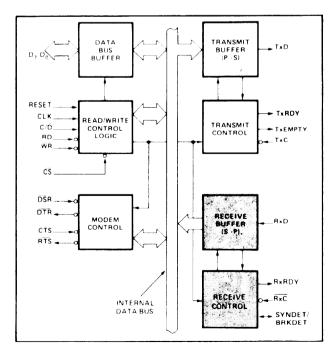

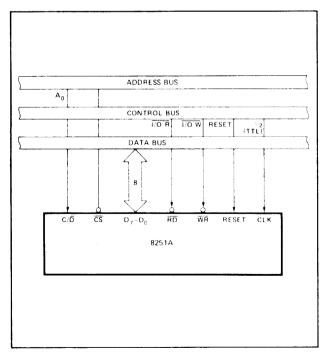

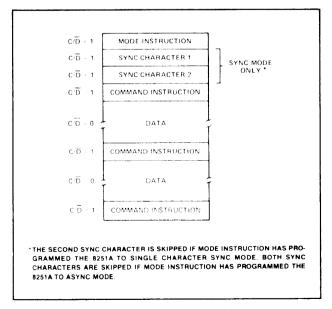

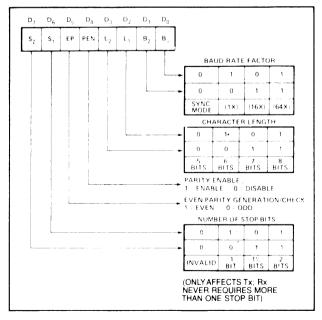

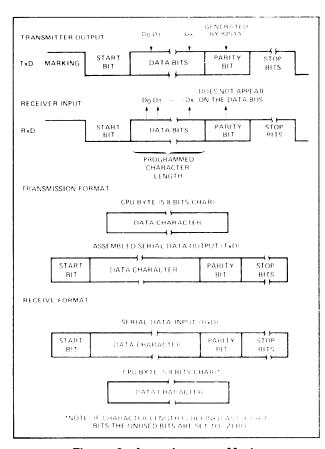

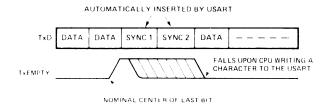

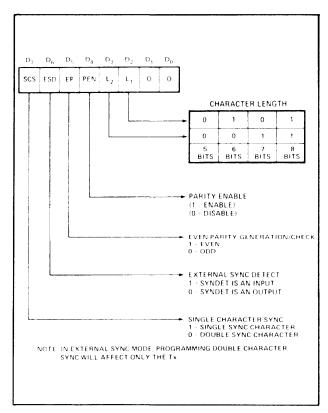

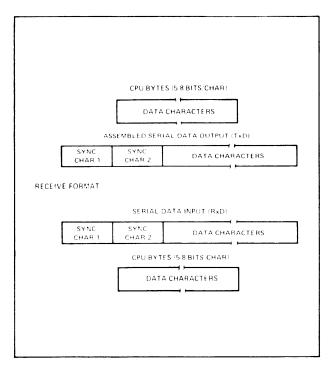

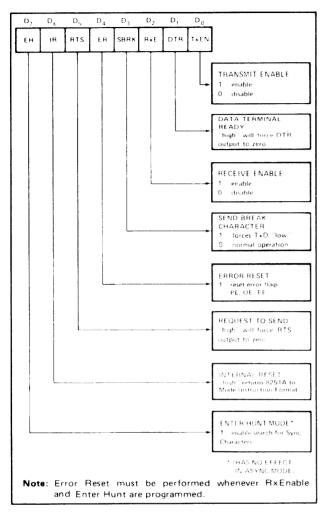

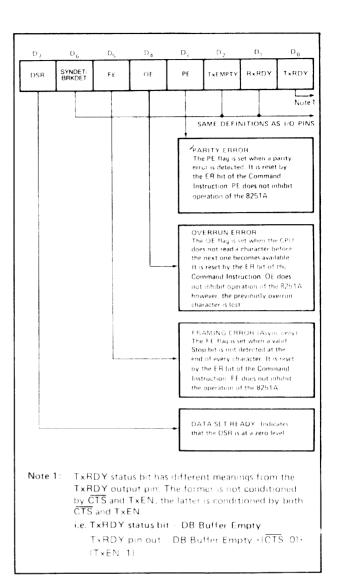

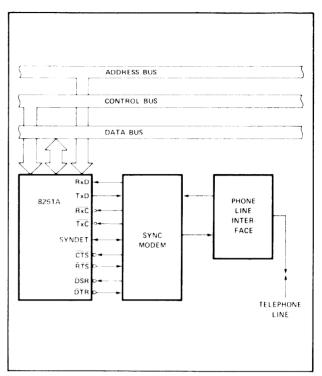

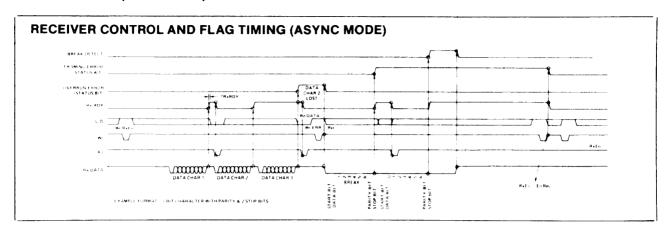

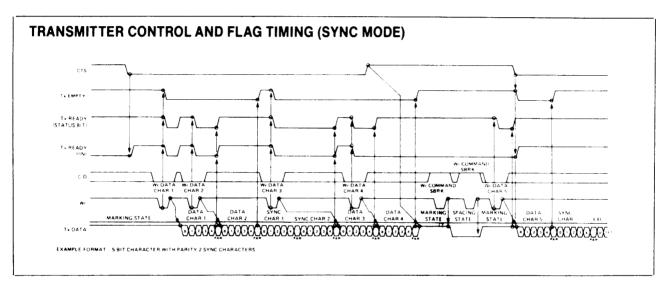

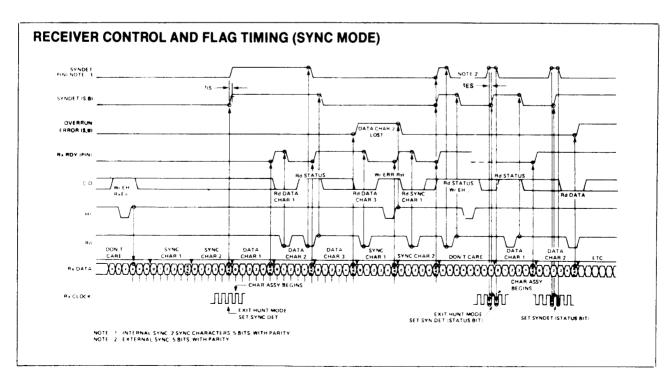

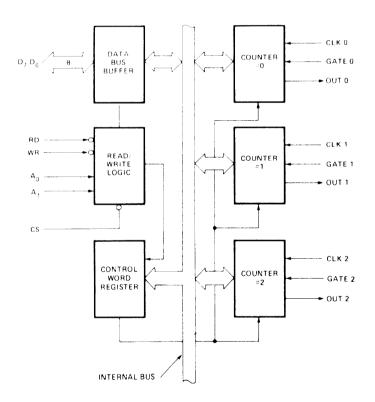

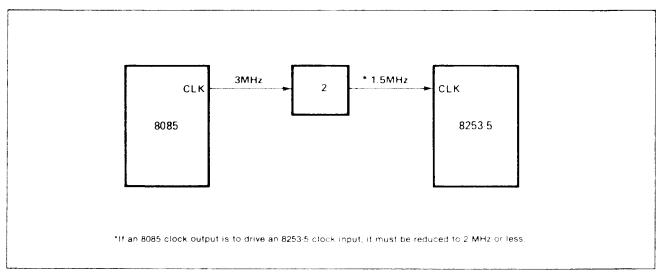

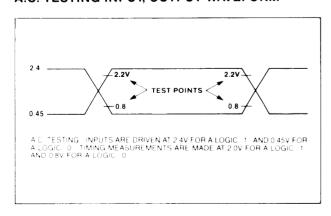

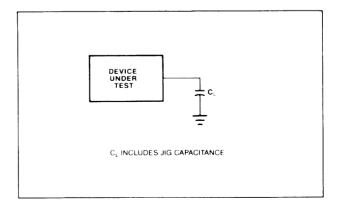

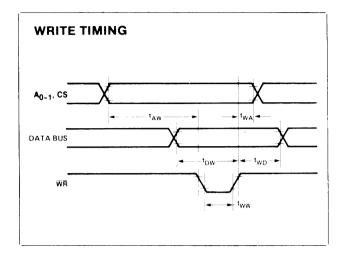

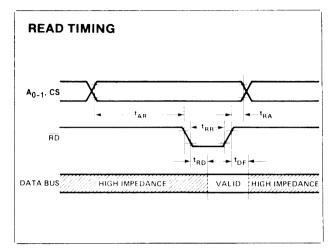

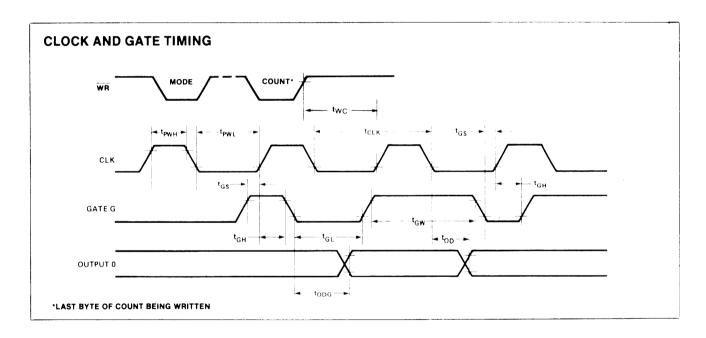

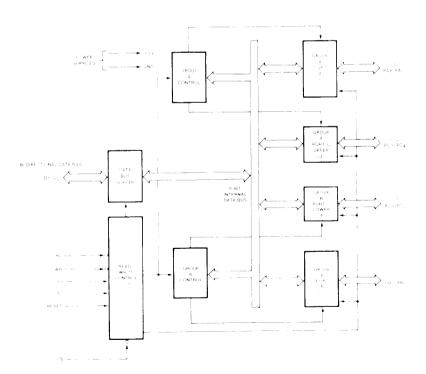

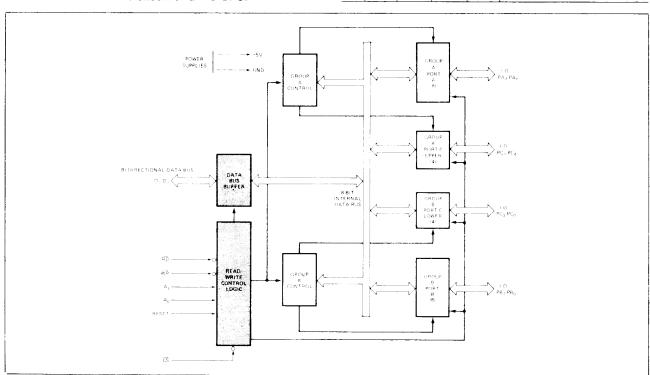

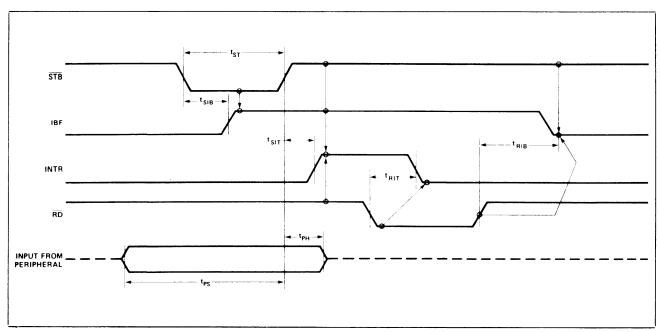

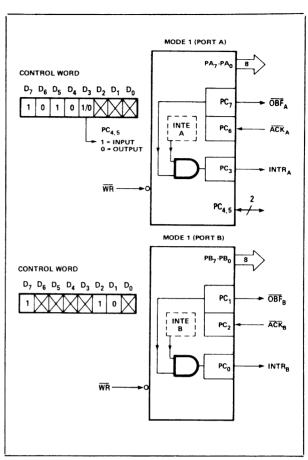

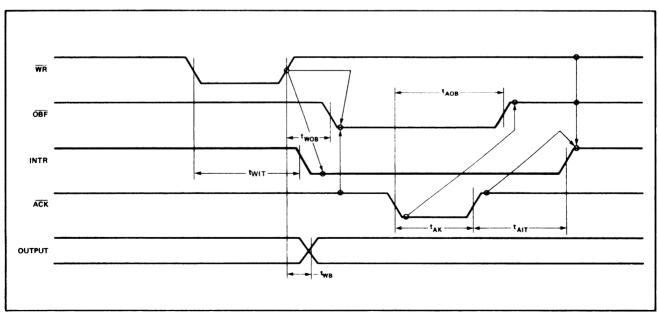

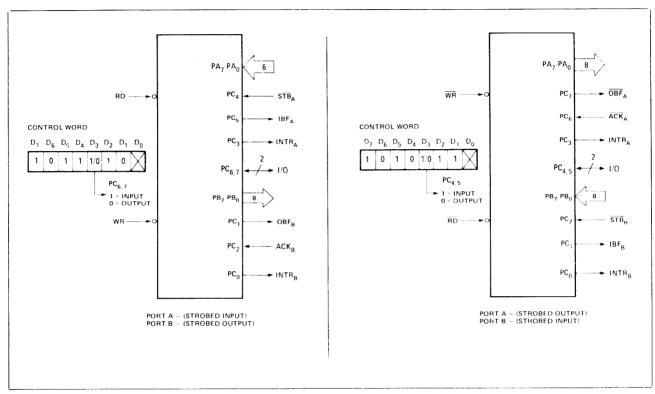

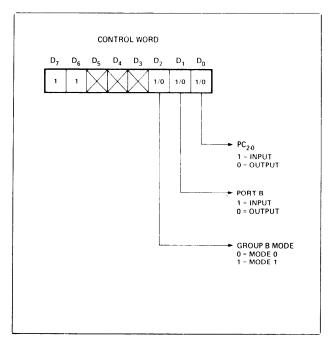

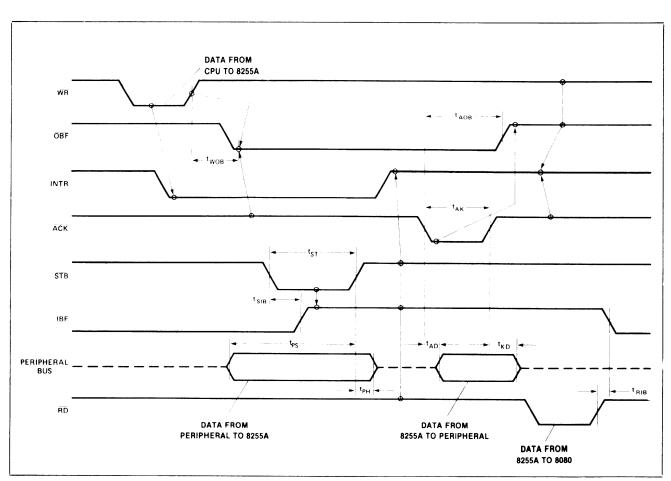

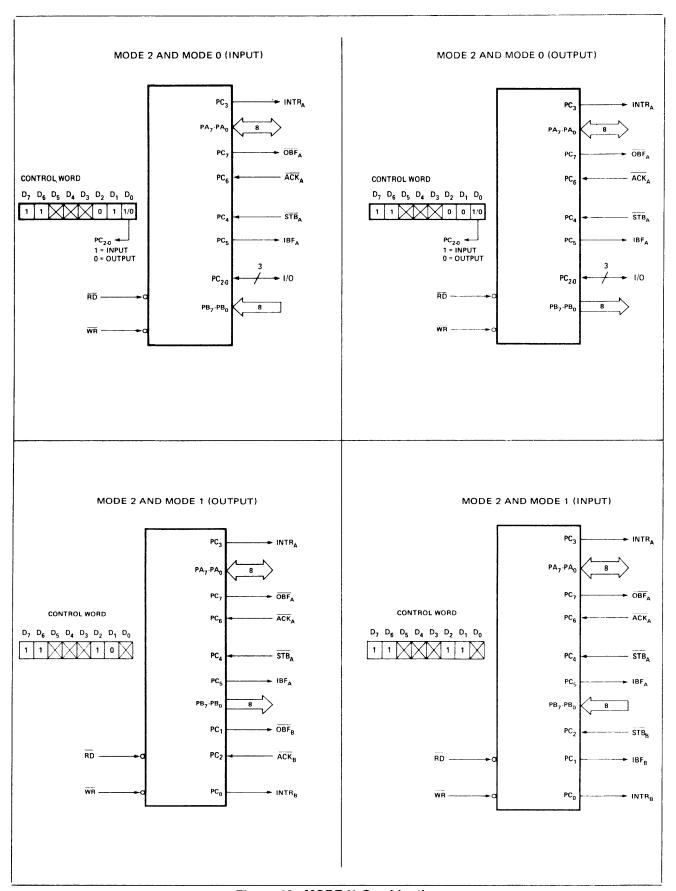

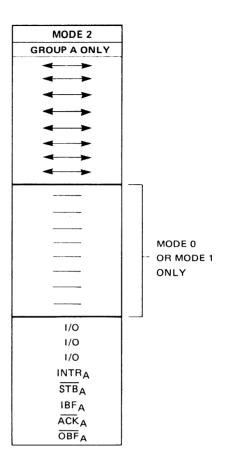

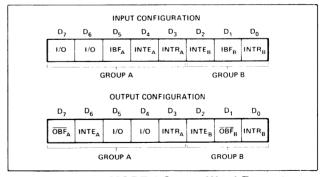

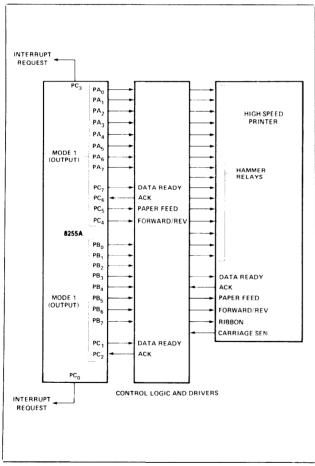

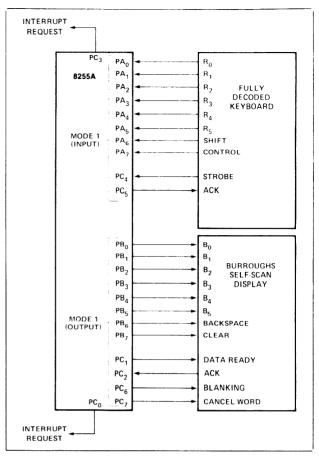

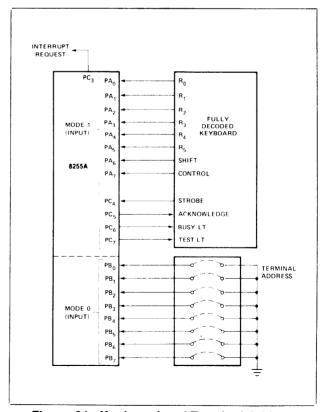

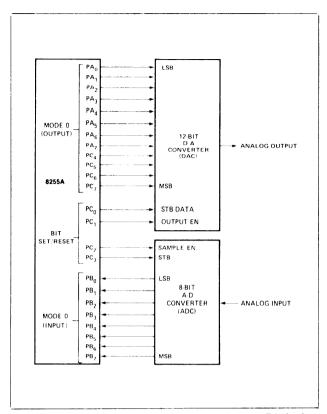

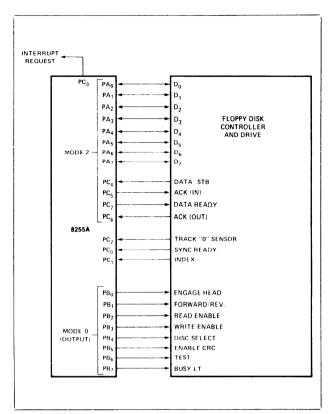

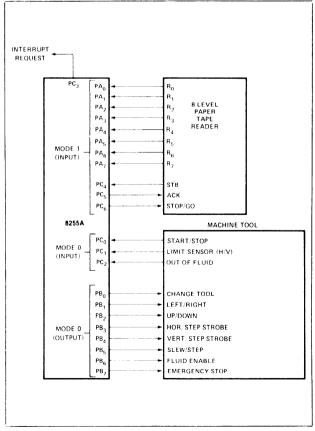

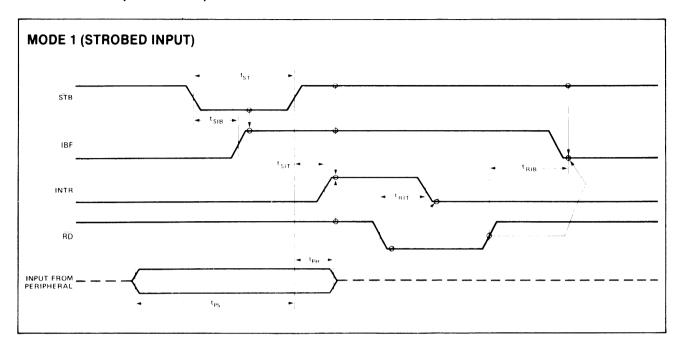

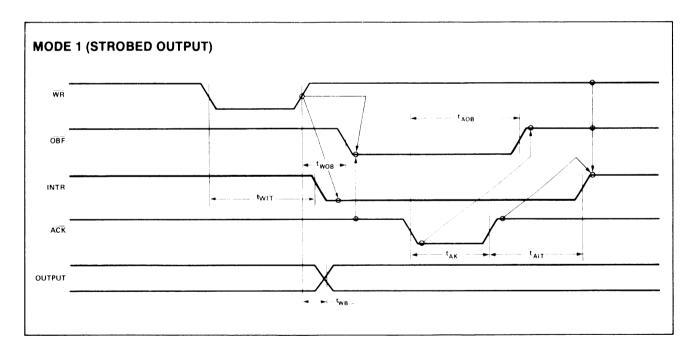

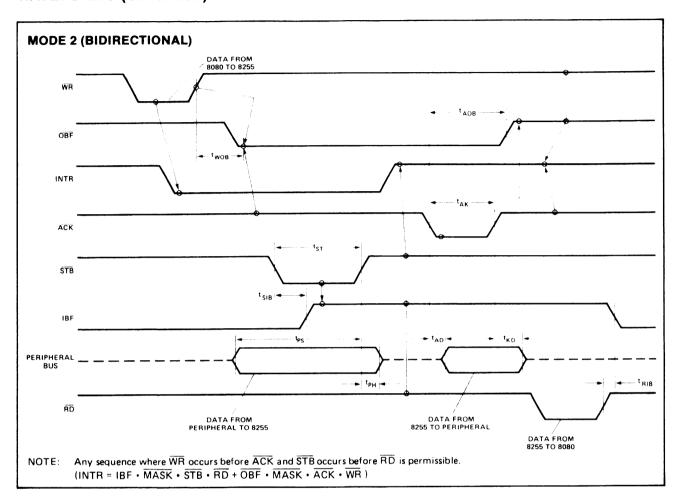

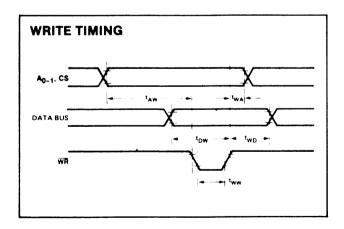

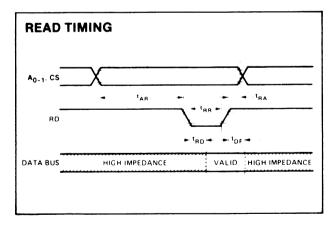

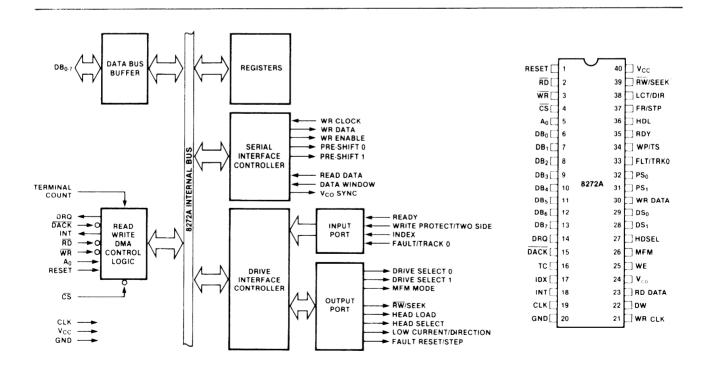

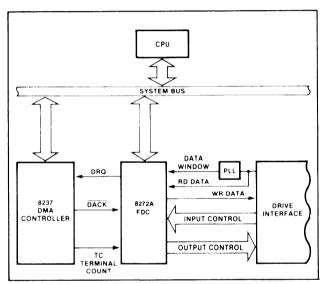

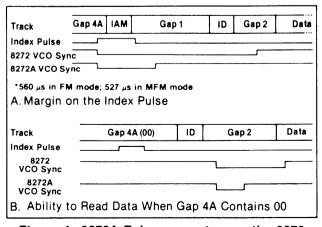

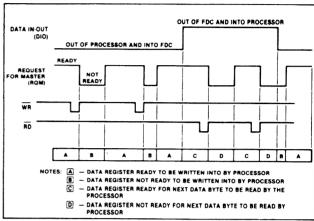

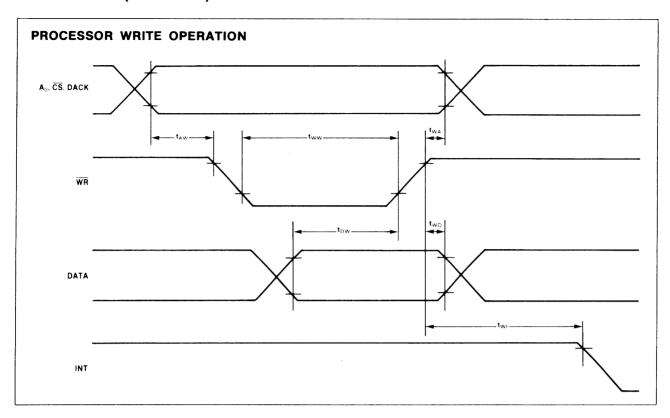

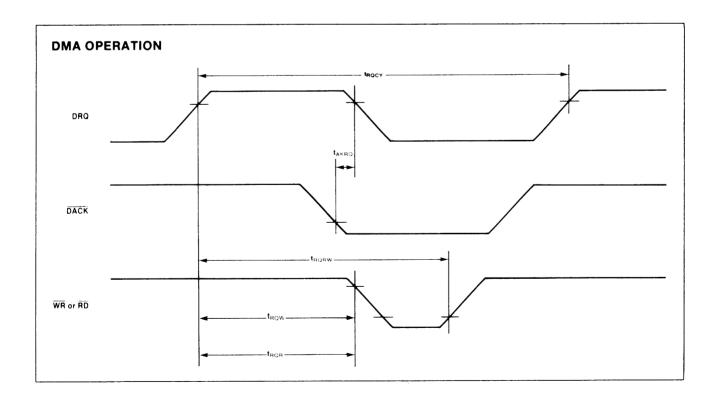

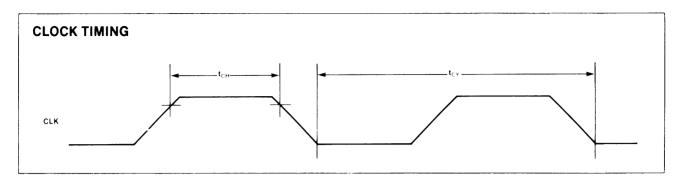

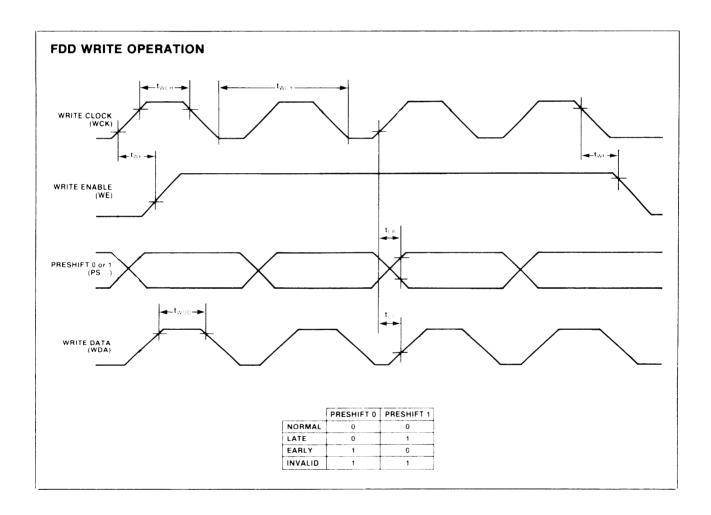

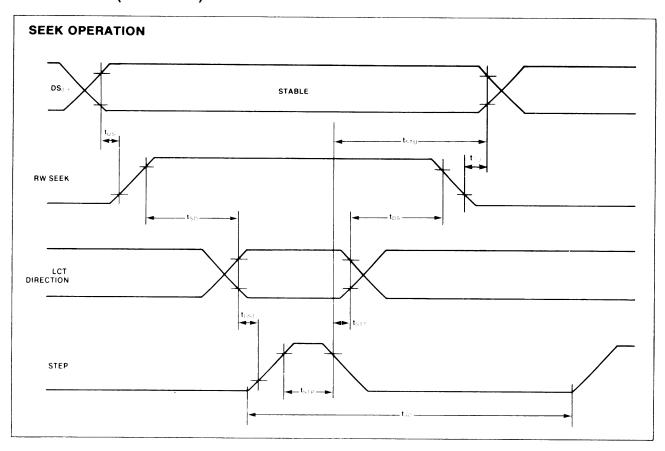

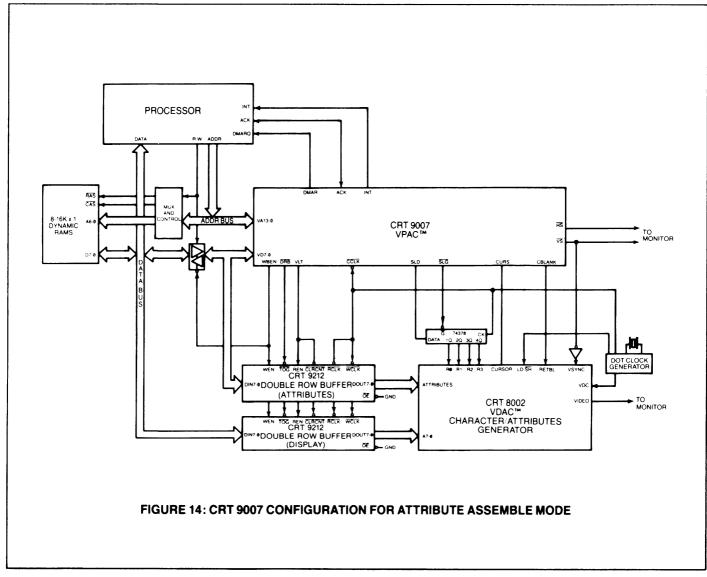

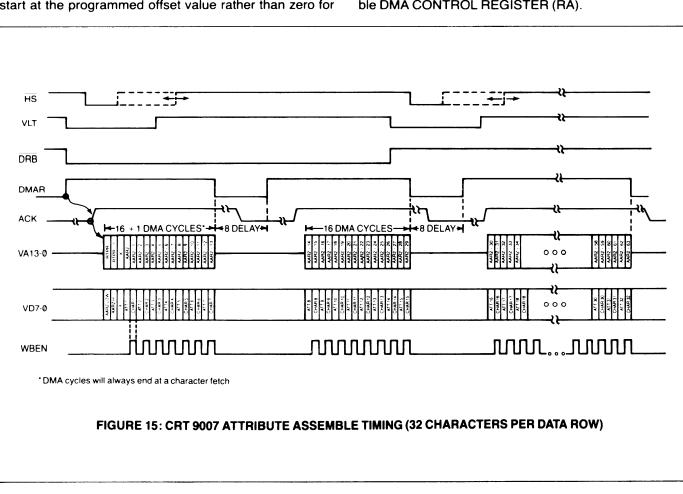

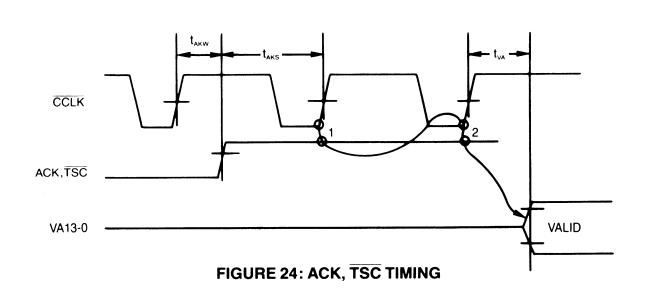

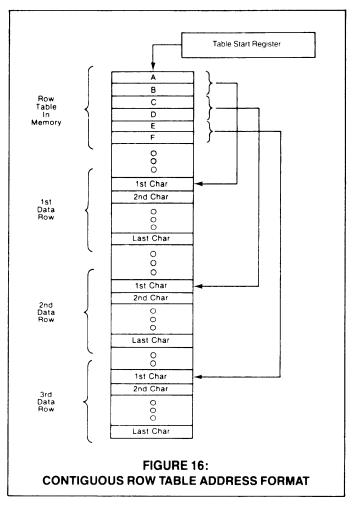

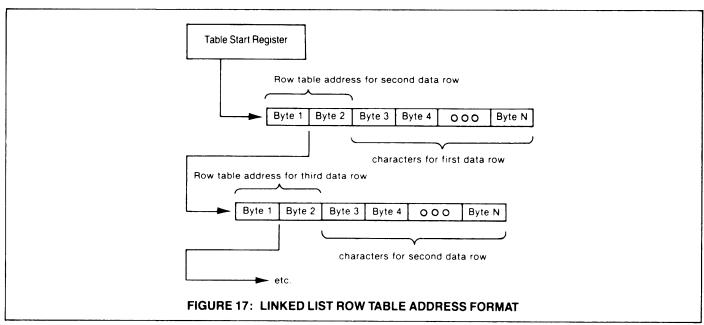

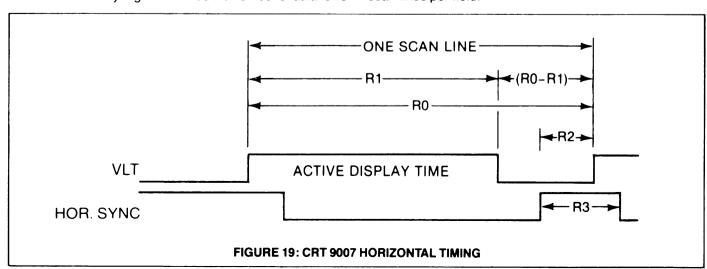

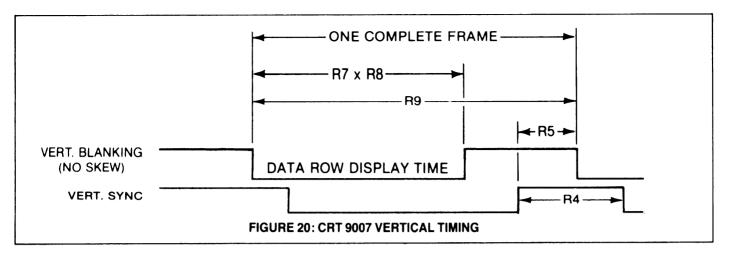

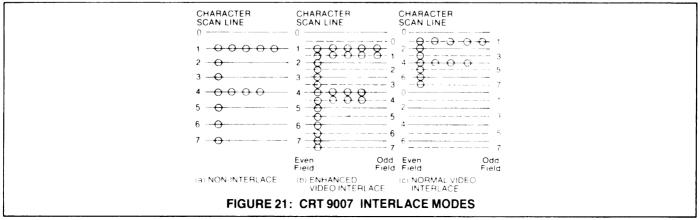

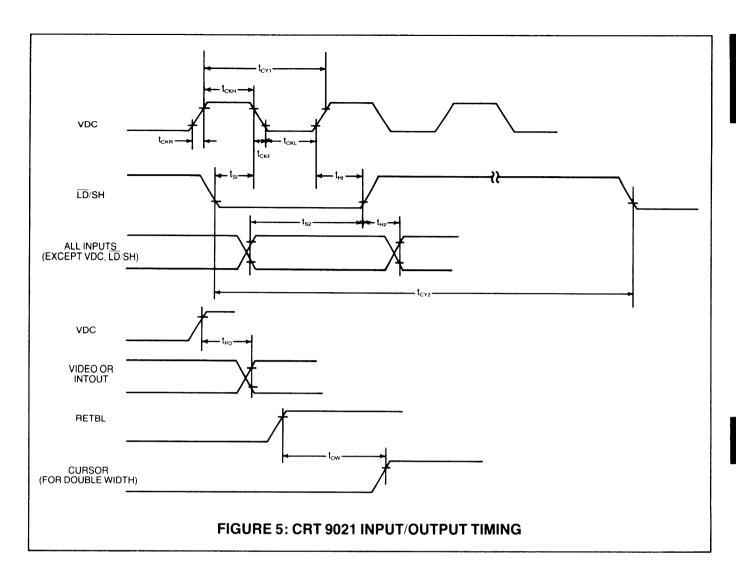

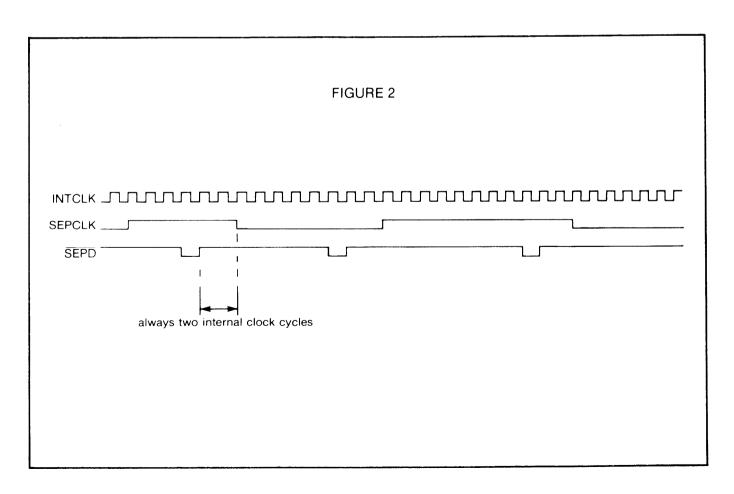

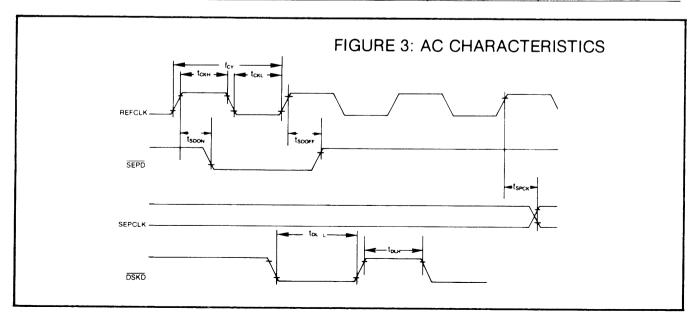

The Model 2000 has provisions for multiplexing four BUSDMARQn\* (BUS Direct Memory Access ReQuest n, active low) into the two 80186 resident DMA channels, DRQn (DMA ReQuest An 8-bit write only register, located at n, active high). 0002H in CPU peripheral address space, controls the multiplexing process (bit assignments are given in Figure This register is cleared after a system reset. input channel has both an enable bit (to enable the corresponding channel for requests), and a select bit (to select the 80186 channel to which the incoming request is The DMEINT16 (DMA Error INTerrupt controller 1, level 6, active high) signal is used to indicate to software that an invalid programming condition has occured (more than two enabled channels routed to the same 80186 channel). DMEINT16 will remain active until the error condition is removed. DRQn are forces low while INTAK\* is active low due to a logic error in early versions of the 80186.