# **TEKTRONIX**®

# 4051 GRAPHIC SYSTEM

SERVICE MANUAL

VOLUME 1

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

# WARNING

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO.

Copyright © 1977 by Tektronix, Inc. Beaverton, Oregon. Printed in the United States of America. All rights reserved. Contents of this publication may not be reproduced in any form without permission of Tektronix, Inc.

This instrument, in whole or in part, may be protected by one or more U.S. or foreign patents or patent applications. Information provided on request by Tektronix, Inc., P.O. Box 500, Beaverton, Oregon 97077.

TEKTRONIX is a registered trademark of Tektronix, Inc.

This manual supports the following versions of this product: B010100-up

#### **MANUAL REVISION STATUS**

| REV. | DATE  | DESCRIPTION    |

|------|-------|----------------|

| @    | 5 '77 | Original Issue |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

|      |       |                |

# **CONTENTS**

| Section 1 | INTRODUCTION                               | Page |

|-----------|--------------------------------------------|------|

|           | Purpose of Manual                          | 1-1  |

|           | Standard Components                        |      |

|           | 4051 Graphic System                        | 1-1  |

|           | Special Test Aids                          |      |

|           | Special Test Alus                          | 1-0  |

| Section 2 | SPECIFICATIONS                             | Page |

|           | Introduction                               | 2-1  |

|           | Specifications                             |      |

|           | Physical Measurements                      |      |

|           | Environmental Specifications               |      |

|           | Power Specifications                       | 2-2  |

|           | Operator Interface                         | 2-3  |

|           | Alphanumeric Keyboard                      |      |

|           | Line Editing Keys                          | 2-6  |

|           | Program Development Keys                   | 2-7  |

|           | Status Lights                              | 2-7  |

|           | Display                                    | 2-8  |

|           | Magnetic Tape Unit                         | 2-12 |

|           | Magnetic Tape Media                        | 2-14 |

|           | Data Format and Recording Method           | 2-14 |

|           | Microprocessor System Specifications       | 2-16 |

|           | Motorola Devices                           | 2-16 |

|           | Memory (ROM and Peripheral Devices)        | 2-17 |

|           | Memory (RAM for Program and Data Storage)  | 2-17 |

|           | Memory Address Allocation                  | 2-17 |

|           | Bank Switch                                | 2-19 |

|           | BASIC Language Format                      | 2-19 |

|           | Line Number                                | 2-19 |

|           | Keyword                                    | 2-20 |

|           | I/O Address                                | 2-20 |

|           | General Purpose Interface Bus              | 2-24 |

|           | The GPIB Connector                         | 2-24 |

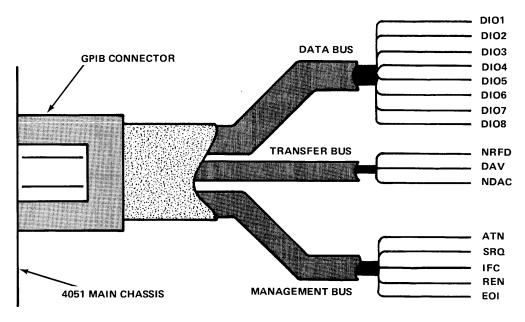

|           | The GPIB Interfacing Concept               | 2-24 |

|           | GPIB Signal Definitions                    | 2-26 |

|           | Data Bus                                   | 2-26 |

|           | Management Bus                             | 2-26 |

|           | The Transfer Bus                           | 2-27 |

|           | GPIB Data Formats                          | 2-28 |

|           | Transferring ASCII Data                    | 2-28 |

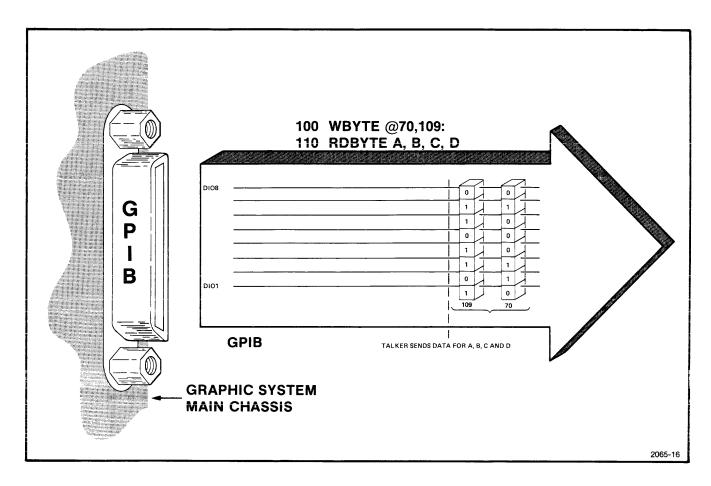

|           | Transferring Machine Dependent Binary Code | 2-28 |

|           | Transferring One Data Byte at a Time       |      |

| Section 2 | SPECIFICATIONS (cont)                            | Page |

|-----------|--------------------------------------------------|------|

|           | GPIB-to-IEEE Compatibility                       | 2-29 |

|           | Introduction                                     | 2-29 |

|           | GPIB Interfacing Compatibility in Detail         | 2-30 |

|           | General Purpose GPIB Commands                    | 2-30 |

| Section 3 | MAINTENANCE                                      | Page |

| Section 3 | Routine Maintenance                              | 3-1  |

|           | General                                          |      |

|           | Cleaning                                         |      |

|           | Surface Cleaning                                 |      |

|           |                                                  |      |

|           | Cleaning the Fan Filter                          |      |

|           | Cleaning the Tape Head                           |      |

|           | Cleaning Electrical Contacts                     |      |

|           | System Verification Software                     |      |

|           | Cartridge Respooling                             |      |

|           | Static-Free Work Station                         |      |

|           | Disassembly/Assembly                             |      |

|           | Removing the Cover and Backpack                  |      |

|           | Keyboard Access                                  |      |

|           | CRT Filter Access                                |      |

|           | CRT and Deflection Yoke Removal and Installation |      |

|           | CRT Removal                                      |      |

|           | Deflection Yoke Replacement                      |      |

|           | CRT Installation                                 |      |

|           | Power Supply Access                              |      |

|           | CPU Board/Memory Board Access                    |      |

|           | Display Board Access                             |      |

|           | Magnetic Tape Assembly Access                    | 3-28 |

| Section 4 | 4051 CALIBRATION                                 | Page |

|           | General                                          | 4-1  |

|           | Power Supply                                     |      |

|           | Display Calibration                              | 4-4  |

|           | Hard Copy Adjustments                            | 4-7  |

|           | Magnetic Tape Calibration                        | 4-9  |

| Section 5 | TROUBLESHOOTING AIDS                             | Page |

| -         | General                                          | _    |

|           | 4051 Troubleshooting Aids                        |      |

|           | Adjustment Locator Aids                          |      |

| Section 5 | TROUBLESHOOTING AIDS (cont)              | Page |

|-----------|------------------------------------------|------|

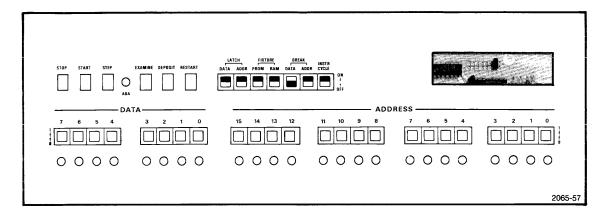

|           | System Test Fixture                      | 5-11 |

|           | 4051 Tests Using the System Test Fixture |      |

|           | System Test Fixture Switch Functions     |      |

|           | 4051 RAM Test                            |      |

|           | 4051 ROM Test                            |      |

|           | 4051 GPIB Test                           | 5-21 |

|           | 4051 Display Test                        | 5-25 |

|           | 4051 Tape Circuitry Test                 | 5-27 |

|           | Tape Tests—A Brief Description           | 5-31 |

| Section 6 | 4051 CIRCUIT DESCRIPTION                 | Page |

|           | System Architecture                      | 6-1  |

|           | System Addressing                        | 6-7  |

|           | 4051 Timing                              | 6-9  |

|           | 4051 Keyboard Operation                  | 6-13 |

|           | ·                                        | 6-17 |

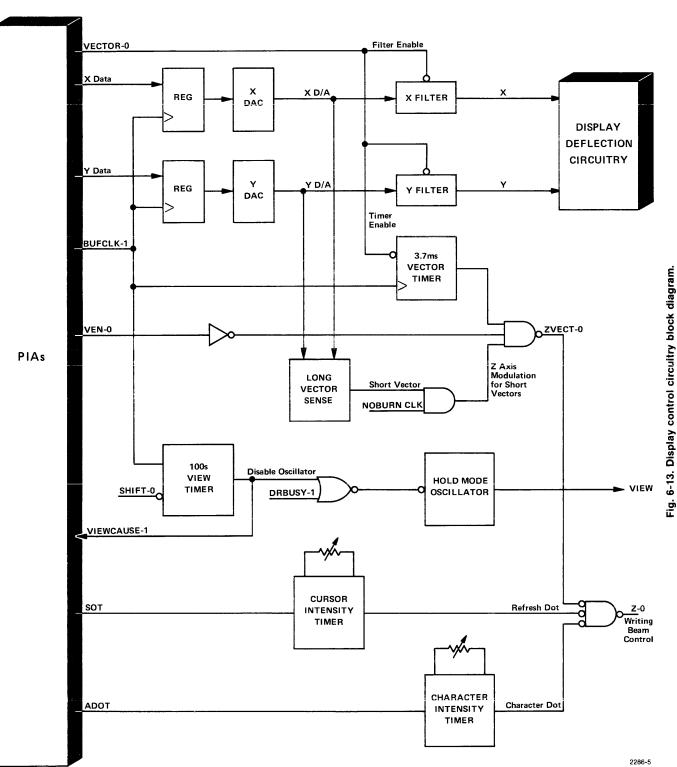

|           | Display Control                          | 6-18 |

|           | •                                        | 6-20 |

|           | ·                                        | 6-22 |

|           | Long Vector Sense Circuit                |      |

|           | Alphanumeric Display                     | 6-24 |

|           |                                          | 6-24 |

|           | • •                                      | 6-24 |

|           | • •                                      | 6-27 |

|           | •                                        | 6-28 |

|           | ·                                        | 6-29 |

|           | Geometry Correction Multipliers          |      |

|           | Deflection Amplifier                     |      |

|           | Storage and Erase Control Circuits       | 6-29 |

|           | •••                                      | 6-30 |

|           | 9                                        | 6-30 |

|           | · ·                                      | 6-31 |

|           |                                          | 6-31 |

|           | Flood Gun Control                        |      |

|           | High Voltage Circuits                    | 6-32 |

|           | · · ·                                    | 6-33 |

|           | Focus Supply                             |      |

|           | Filament Supply                          |      |

|           | High Voltage Supply                      |      |

|           | Control Grid Supply                      |      |

|           | Intensity Control and Z Signal Amplifier | 6-35 |

| Section 6  | 4051 CIRCUIT DESCRIPTION (cont)                                                                                                                                                                                        | Page                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|            | Hard Copy Operations                                                                                                                                                                                                   | . 6-37<br>. 6-46<br>. 6-48      |

| Section 7  | BACKPACK CIRCUITS  Firmware Backpack (020-0147-00)  Backpack Addressing  Communications Backpack (021-0188-00)  Communication Circuitry  Communication Cable  Self-Test Adapter  Communication Interface Test "CMTEST" | 7-1<br>7-4<br>7-4<br>7-8<br>7-9 |

| Appendix A | INDEX OF SIGNAL NAMES                                                                                                                                                                                                  |                                 |

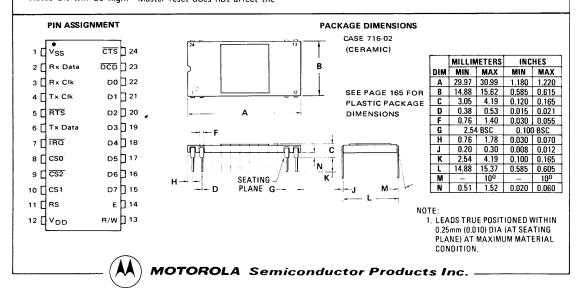

| Appendix B | MOTOROLA SPECIFICATIONS                                                                                                                                                                                                |                                 |

| Appendix C | ASCII CODE CHART                                                                                                                                                                                                       |                                 |

| Index      |                                                                                                                                                                                                                        |                                 |

Change Information

# **ILLUSTRATIONS**

| Figure                   | Illustration                                                               | Page |

|--------------------------|----------------------------------------------------------------------------|------|

| 1-1<br>1-2<br>1-3<br>1-4 | 4051 Graphic System                                                        | 1-5  |

|                          | System                                                                     | 1-7  |

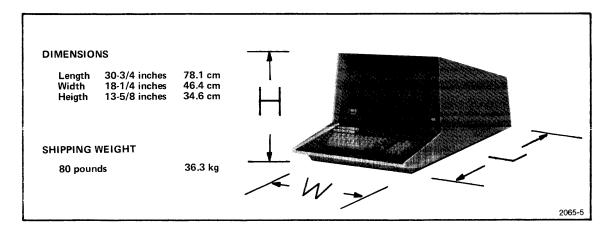

| 2-1                      | 4051 Dimensions                                                            | 2-1  |

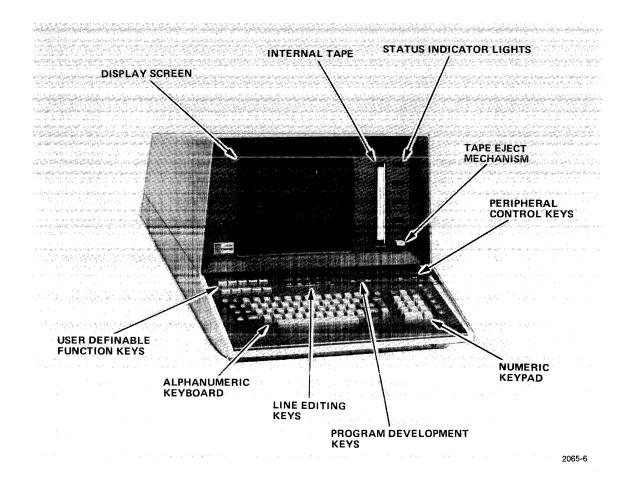

| 2-2                      | Operator controls and system indicators                                    | 2-3  |

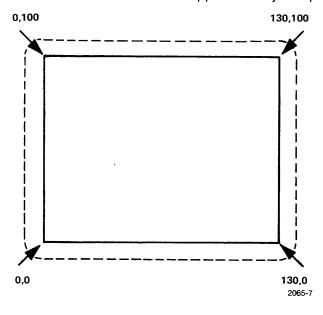

| 2-3                      | Default graphic coordinate limits                                          | 2-8  |

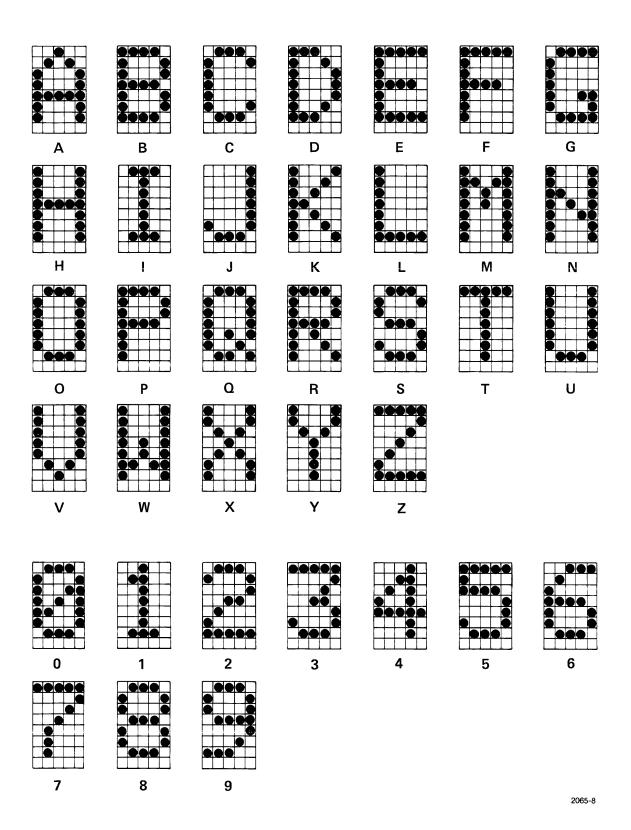

| 2-4                      | US ASCII Character Font (Upper Case Letters and Numbers)                   | 2-9  |

| 2-5                      | US ASCII Character Font (Lower Case Letters)                               | 2-10 |

| 2-6                      | US ASCII Character Font (Special Symbols)                                  | 2-11 |

| 2-7                      | NON-US ASCII Character Font (Special Symbols)                              |      |

| 2-8                      | Standard data cartridge for the 4051                                       |      |

| 2-9                      | 4051 magnetic tape cartridge recording format                              |      |

| 2-10                     | 4051 memory address space allocation map                                   |      |

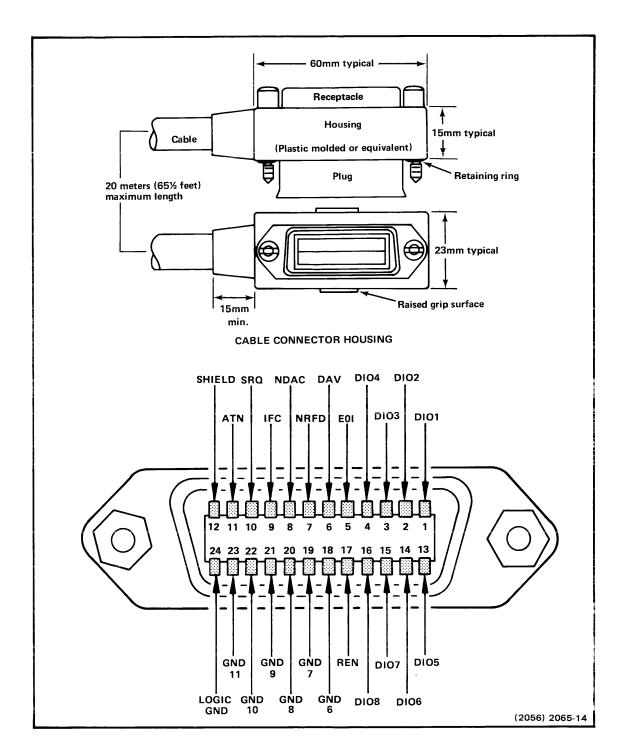

| 2-11                     | GPIB connector(s) and pin assignments                                      |      |

| 2-12                     | GPIB bus structure diagram                                                 |      |

| 2-13                     | Reading data from a device on the GPIB                                     | 2-31 |

| 2-14                     | Transmitting data to a device on the GPIB followed by the universal        |      |

|                          | commands of UNTALK and UNLISTEN                                            | 2-32 |

| 2-15                     | A procedure to initiate data transfer between two GPIB devices and waiting |      |

|                          | until the data transfer is completed                                       | 2-33 |

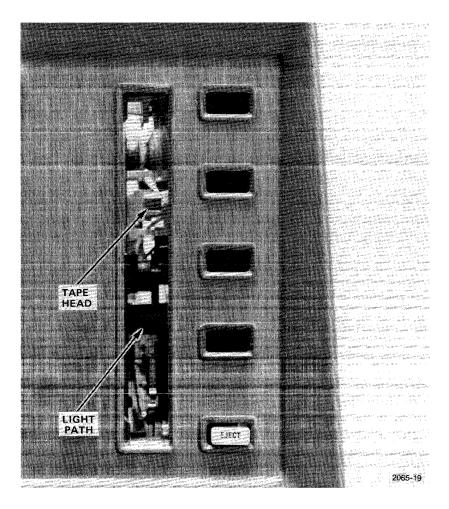

| 3-1                      | Tape head and tape status light path                                       |      |

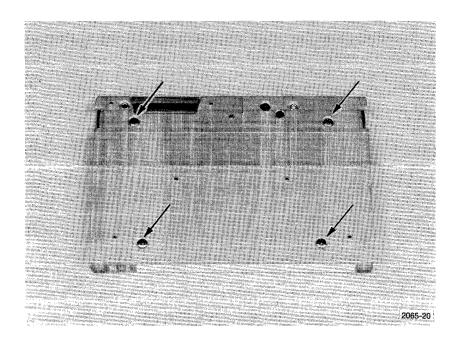

| 3-2                      | Cartridge assembly screws                                                  |      |

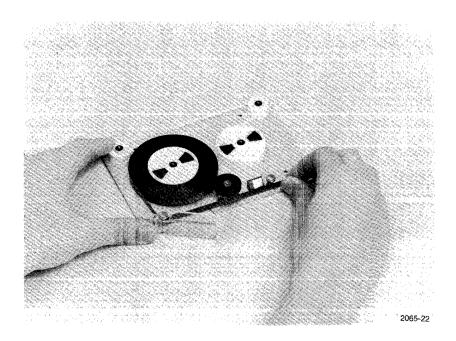

| 3-3                      | Disassembling the tape cartridge                                           |      |

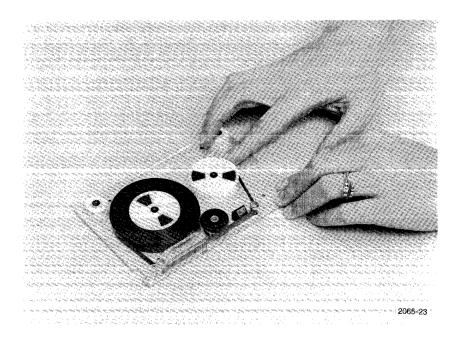

| 3-4                      | Tape positioning within the cartridge                                      |      |

| 3-5                      | Beginning the tape winding                                                 | 3-7  |

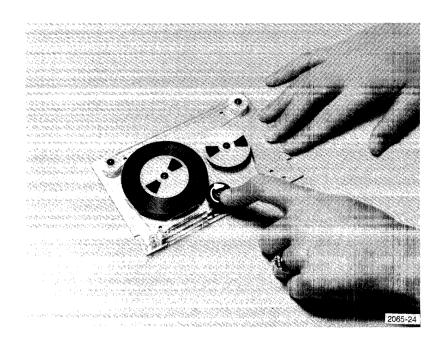

| 3-6                      | Winding the tape                                                           |      |

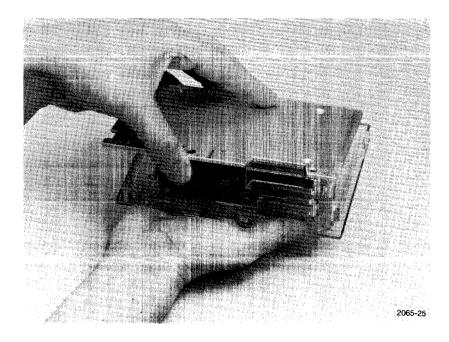

| 3-7                      | Assembling the tape cartridge                                              |      |

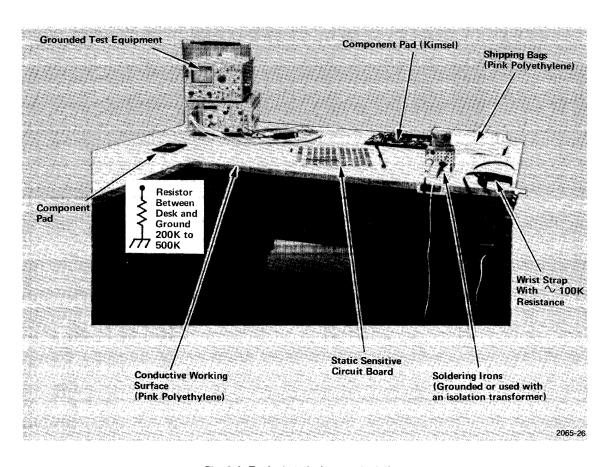

| 3-8                      | Typical static-free work station                                           |      |

| 3-9                      | Approved warning label for outside of shipping cartons                     |      |

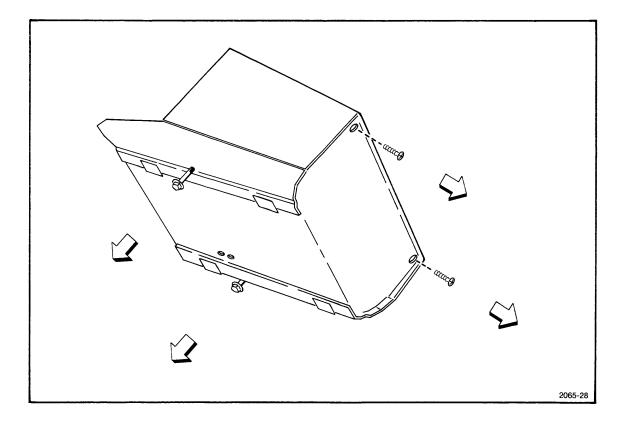

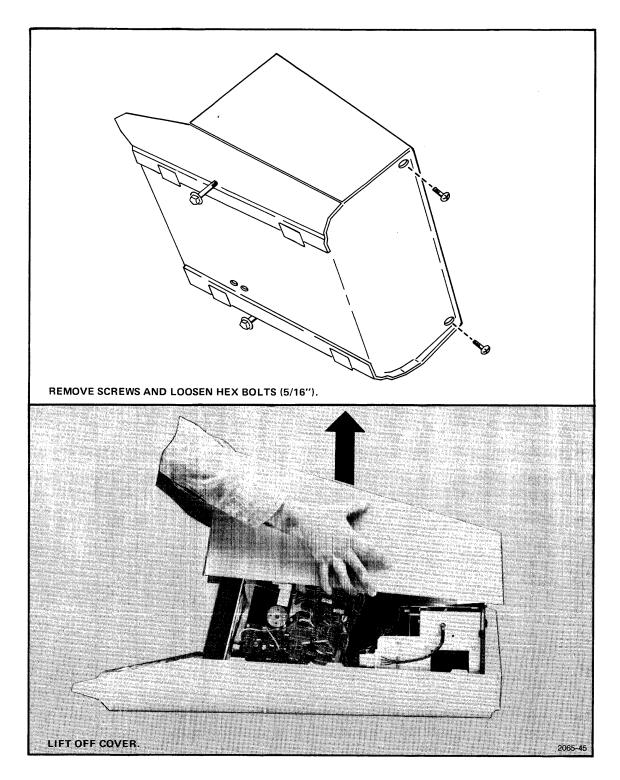

| 3-10                     | Cover mounting bolts                                                       |      |

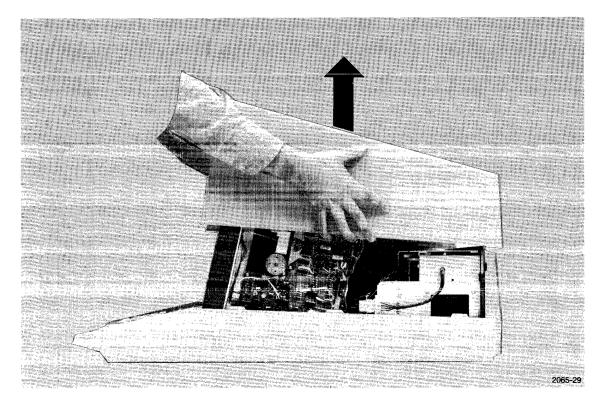

| 3-11                     | Cover removal                                                              | 3-11 |

| Figure      | Illustrations (cont)                                                                                                 | Page |

|-------------|----------------------------------------------------------------------------------------------------------------------|------|

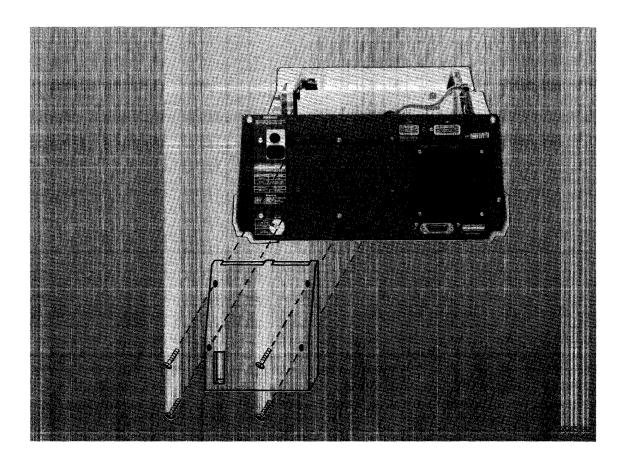

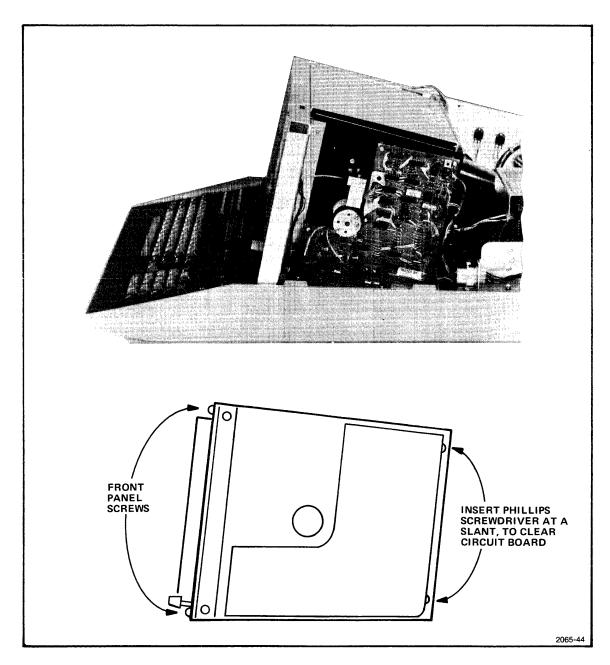

| 3-12        | Backpack removal                                                                                                     | 3-12 |

| 3-13        | Font coverplate removal to gain access to crt, keyboard, cpu board and                                               |      |

|             | memory board                                                                                                         | 3-13 |

| 3-14        | Keyboard screws                                                                                                      |      |

| 3-15        | Keyboard removal to gain access to cpu board and memory board                                                        |      |

| 3-16        | CRT filter access and removal                                                                                        | 3-16 |

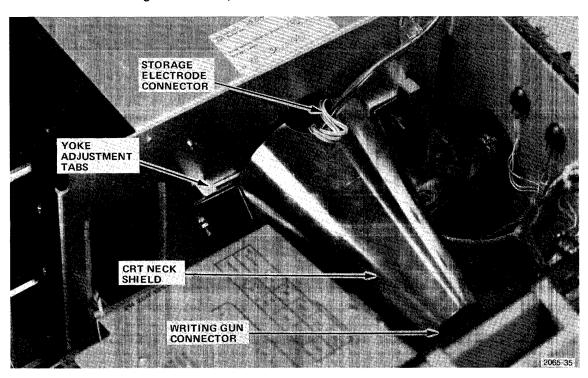

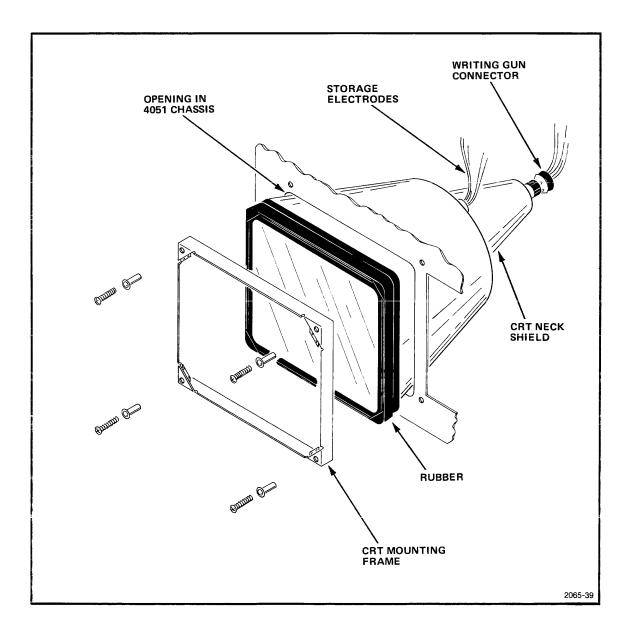

| 3-17        | CRT neck shield, crt electrodes and yoke adjustment assembly                                                         |      |

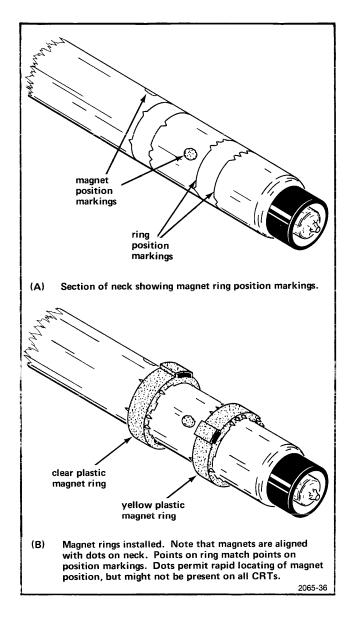

| 3-18        | CRT magnet ring location details                                                                                     |      |

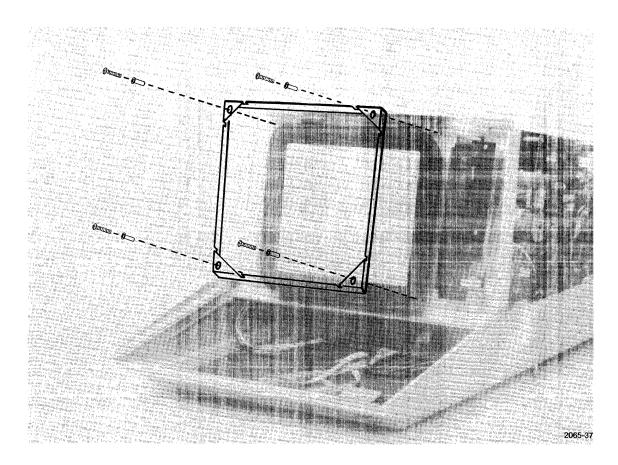

| 3-19        | Removing the crt faceplate mounting frame                                                                            | 3-20 |

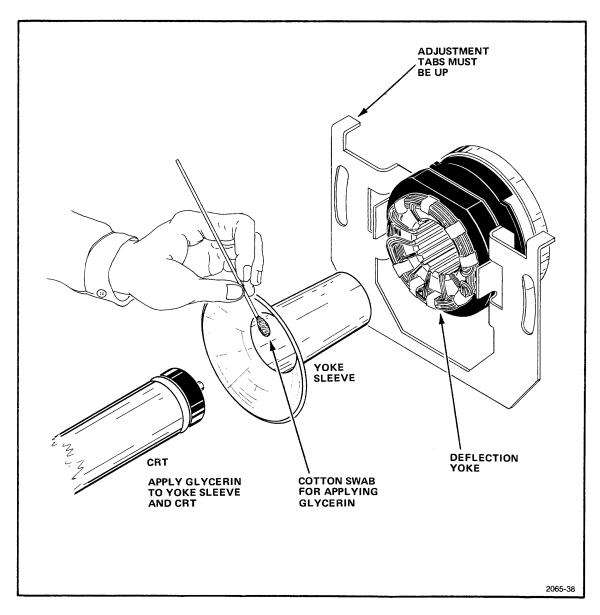

| 3-20        | Lubrication and installation of the crt as part of the installation procedure.                                       |      |

| 3-21        | Mounting the crt into the 4051                                                                                       |      |

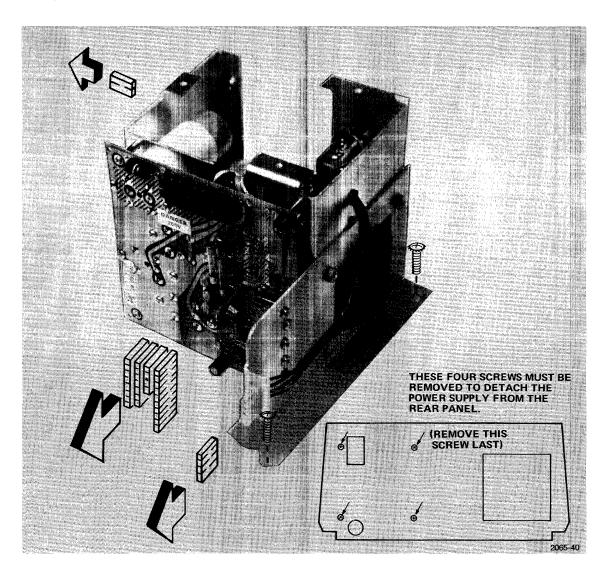

| 3-22        | Power supply removal procedure                                                                                       | 3-24 |

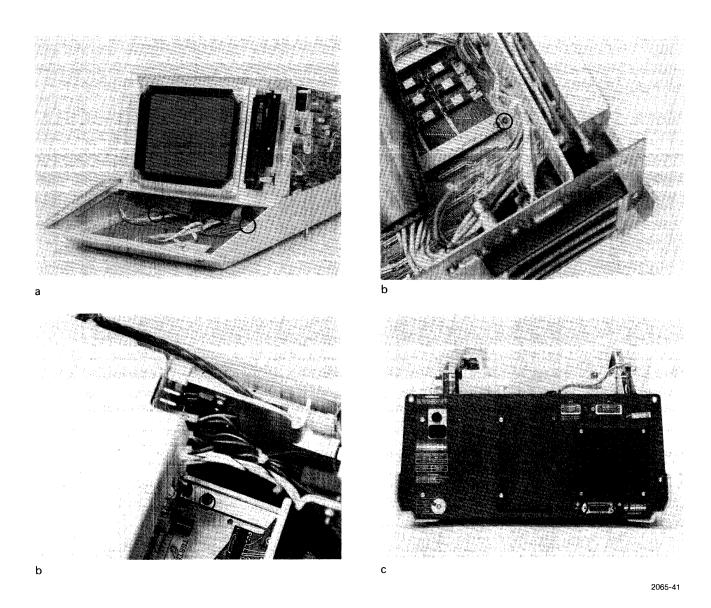

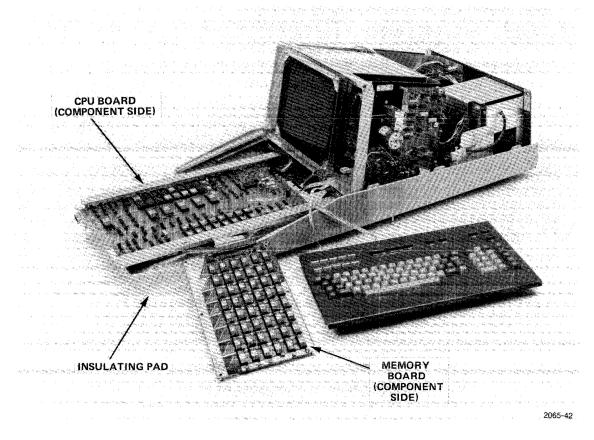

| 3-23        | Screw pairs securing the cpu board                                                                                   | 3-26 |

| 3-24        | Service layout for cpu board and memory board                                                                        | 3-27 |

| 3-25        | CRT writing gun connector removal                                                                                    | 3-27 |

| 3-26        | Tape unit assembly with pointers to the mounting screws                                                              | 3-28 |

| 4-1         | Remove the cover from the 4051 to gain access to most of the circuit                                                 | 4.0  |

| 4.0         | adjustments.                                                                                                         |      |

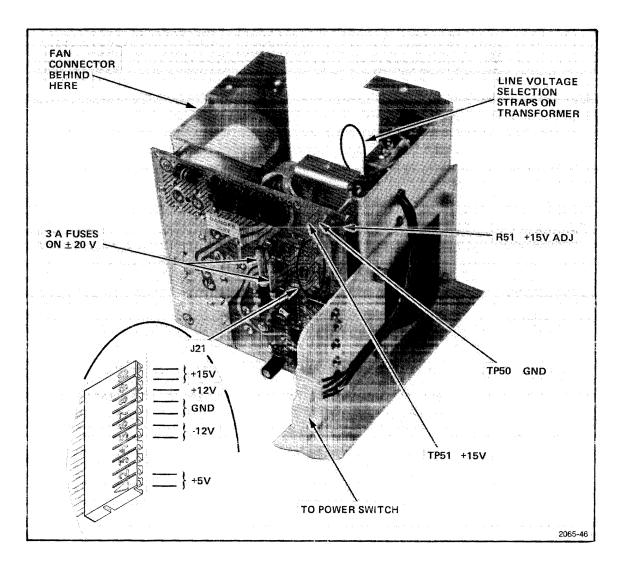

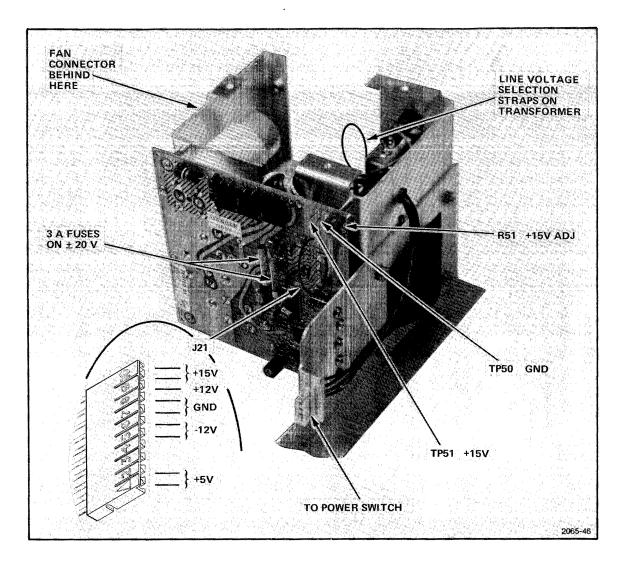

| 4-2<br>4-3  | Power supply check points and adjustments.                                                                           |      |

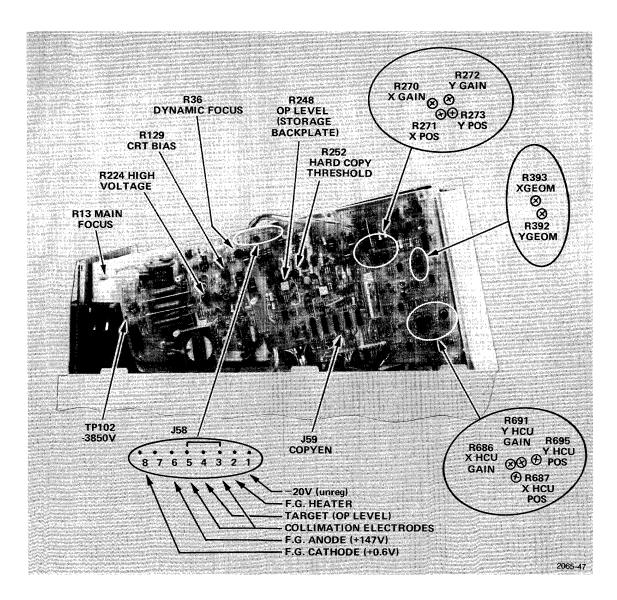

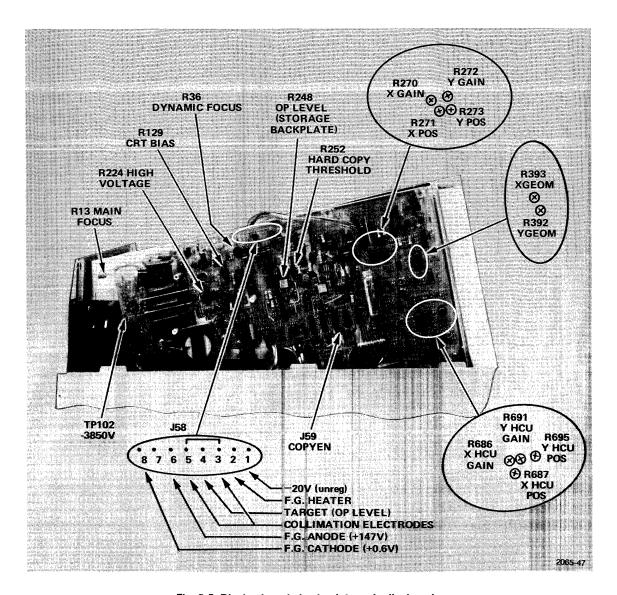

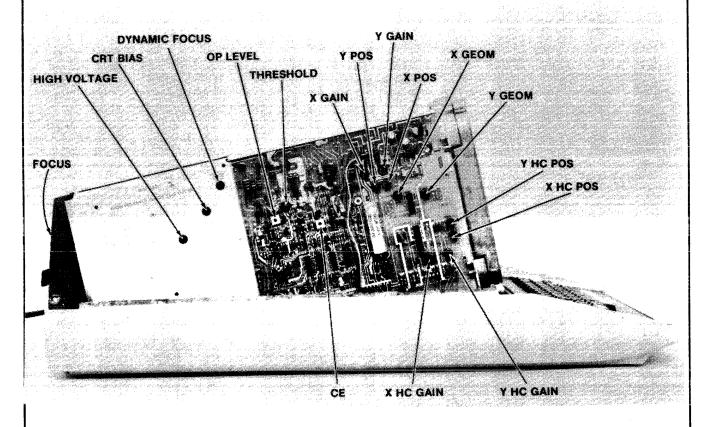

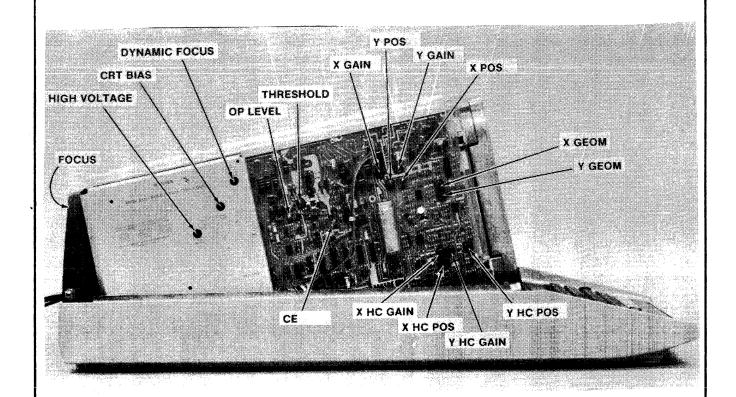

|             | Display board check points and adjustments                                                                           | 4-4  |

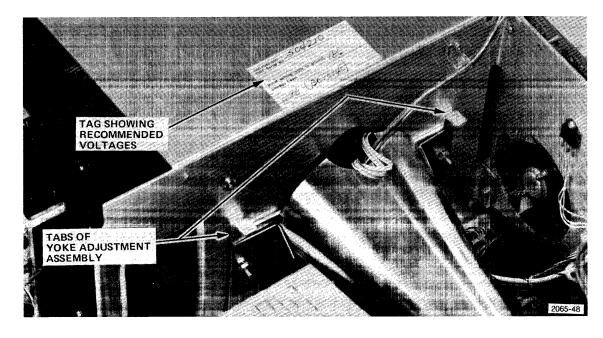

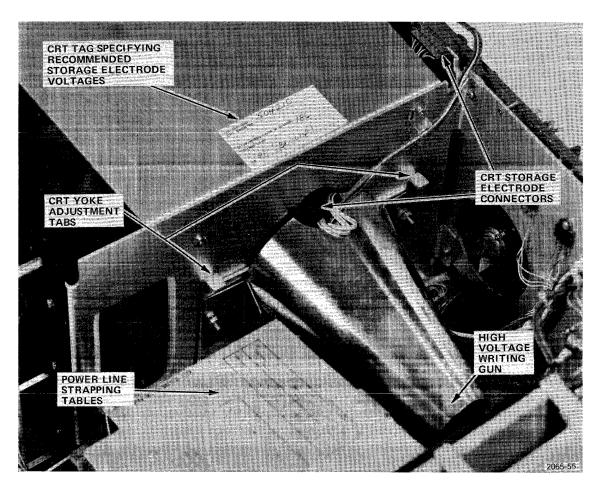

| 4-4         | CRT shield with tag showing recommended electrode voltages. The deflection yoke adjustment rabs are also illustrated | 4-5  |

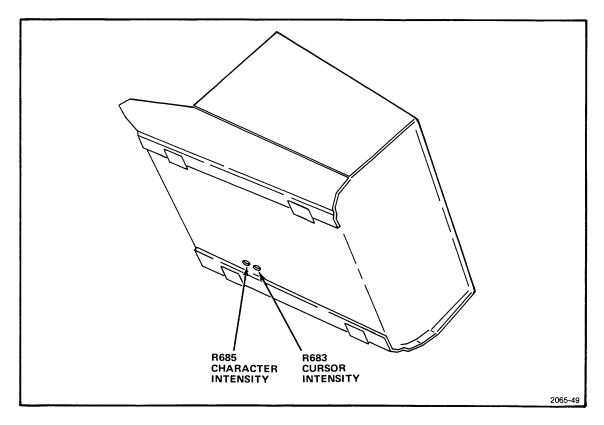

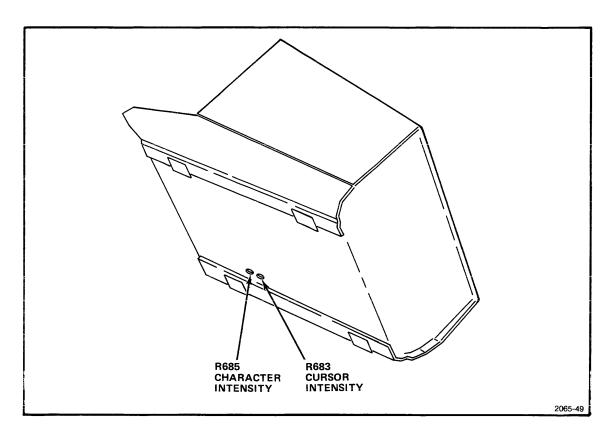

| 4-5         | Intensity adjustments underneath the 4051                                                                            |      |

| 4-6         | Hard copy threshold with no information stored on the 4051 display                                                   |      |

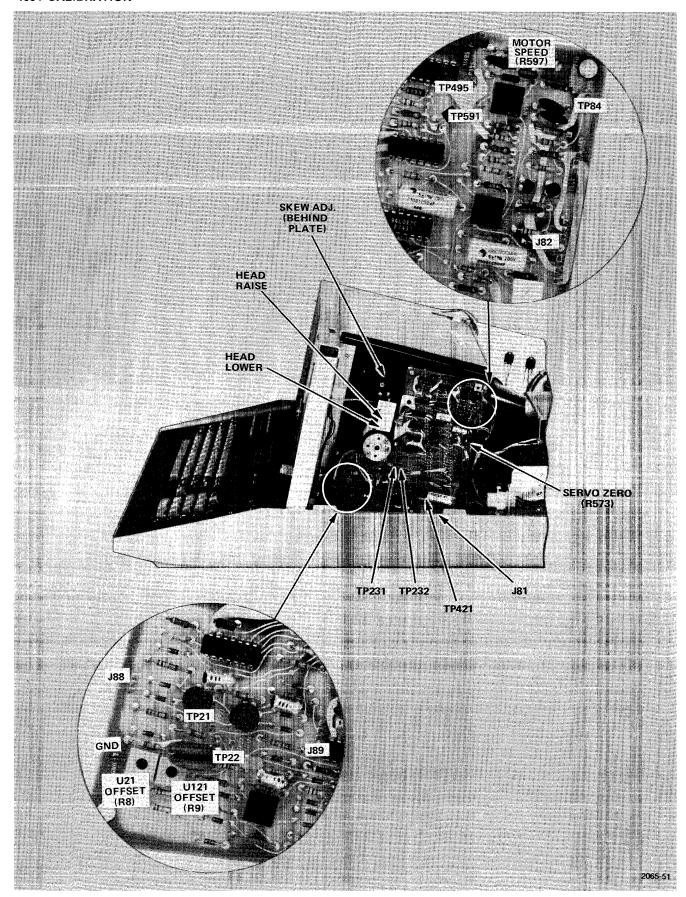

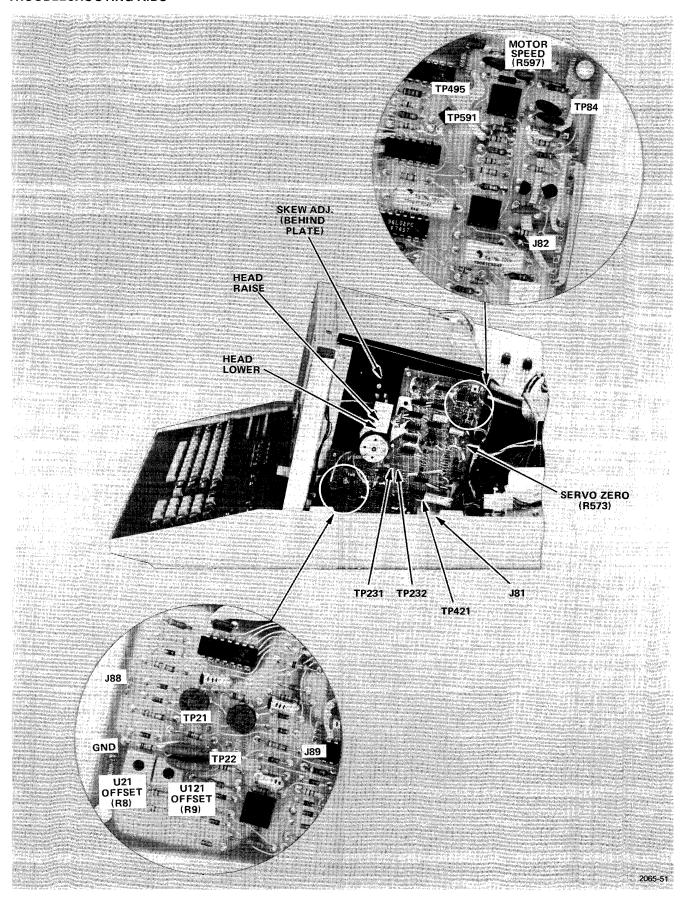

| 4-0<br>4-7  | Tape unit check points and adjustments                                                                               |      |

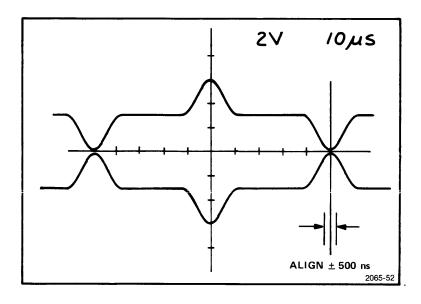

| 4- <i>7</i> | Magnetic tape skew waveforms.                                                                                        |      |

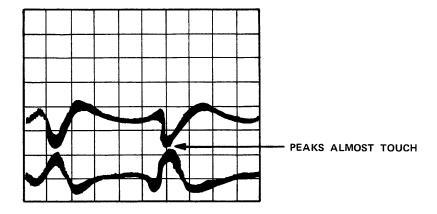

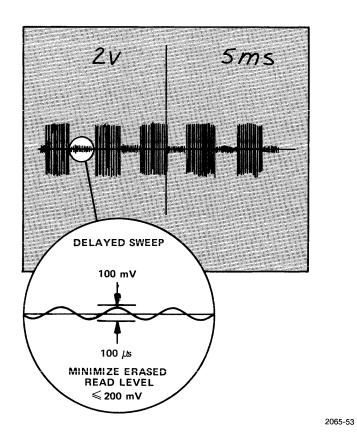

| 4-0<br>4-9  | Magnetic tape skew wavelorms                                                                                         | 4-11 |

| 4-9         | adjustments                                                                                                          | 4-13 |

|             |                                                                                                                      |      |

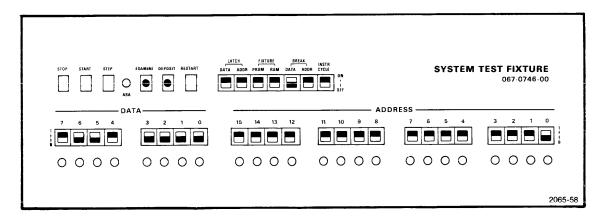

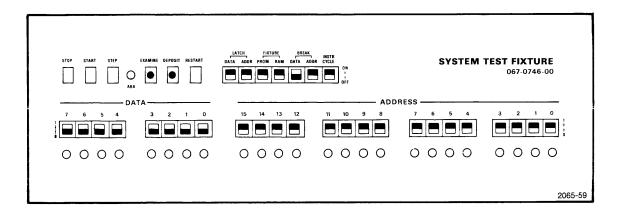

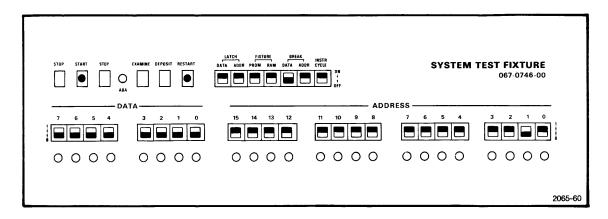

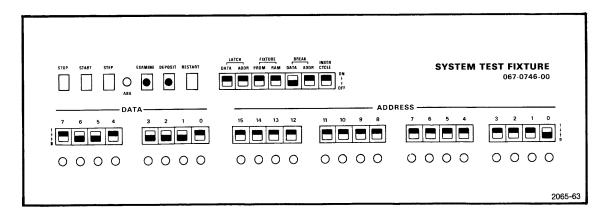

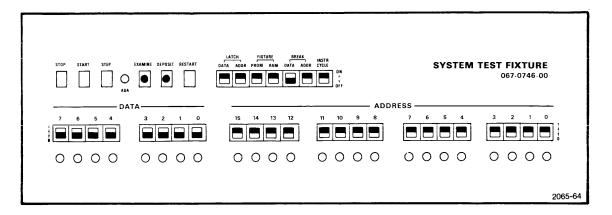

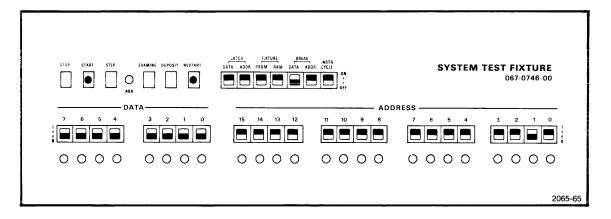

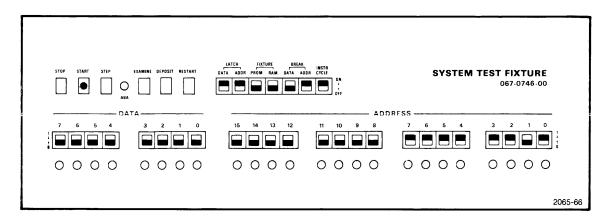

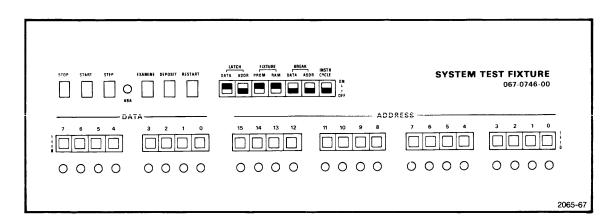

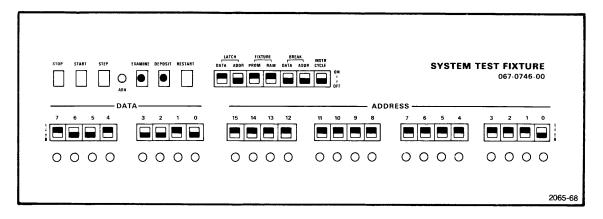

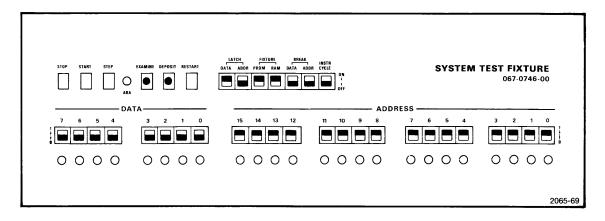

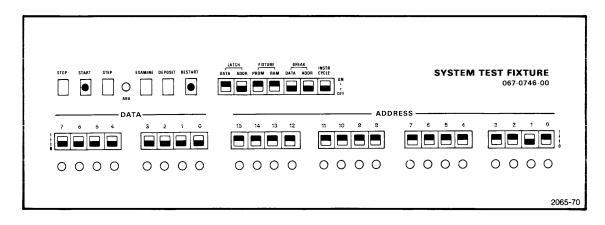

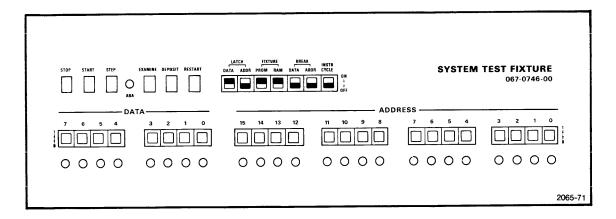

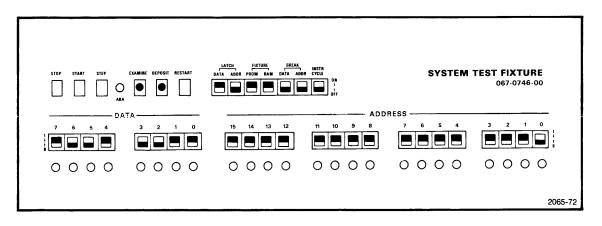

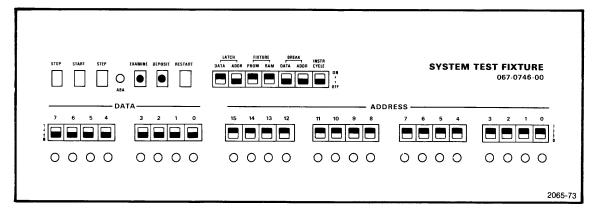

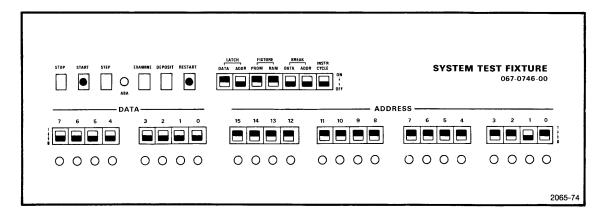

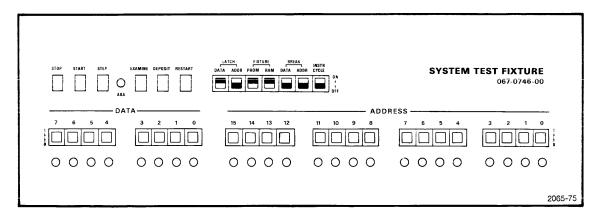

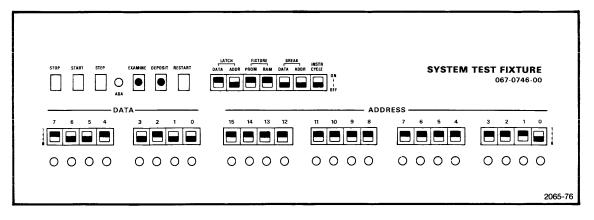

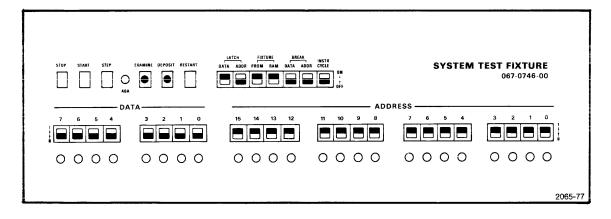

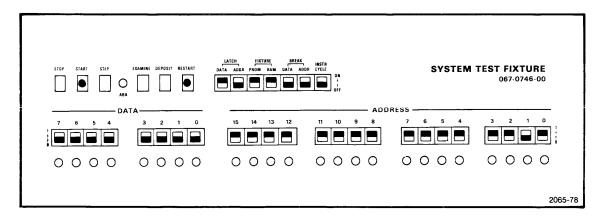

| 5-1         | Test fixture for use with the 4051 Graphic System                                                                    | 5-2  |

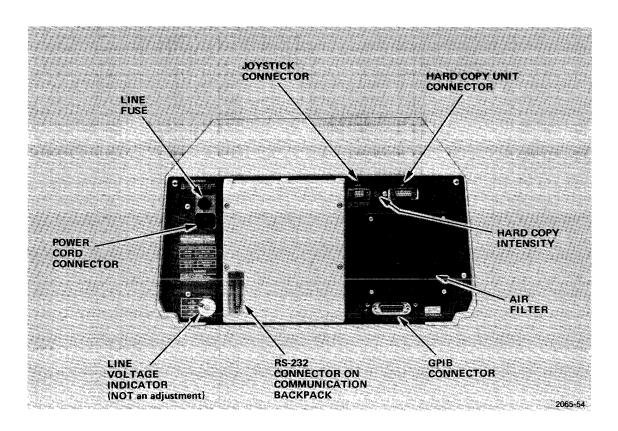

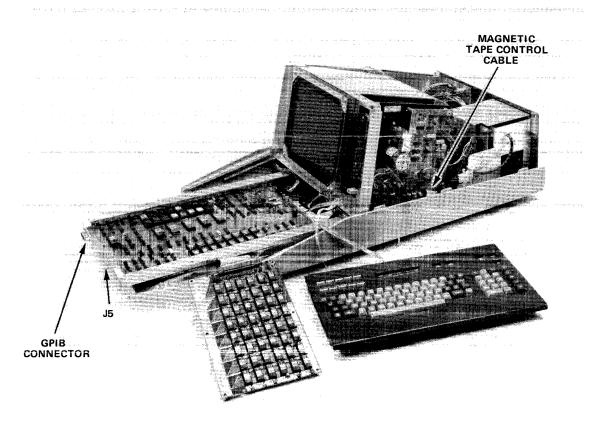

| 5-2         | Rear panel check points and connectors                                                                               | 5-5  |

| 5-3         | Power supply check points and adjustments                                                                            | 5-6  |

| 5-4         | CRT electrodes, yoke adjustment and power line strapping tables                                                      | 5-7  |

| 5-5         | Display board checkpoints and adjustments                                                                            |      |

| 5-6         | Cursor and character intensity adjustments                                                                           |      |

| 5-7         | Tape unit check points and adjustments                                                                               |      |

| 5-8         | 4051 cpu board and memory board brought outside the system for                                                       |      |

|             | component servicing                                                                                                  | 5-11 |

| Figure | Illustrations (cont)                                                     | Page             |

|--------|--------------------------------------------------------------------------|------------------|

| 5-9    | RAM test                                                                 | 5-15             |

| 5-10   | RAM test                                                                 |                  |

| 5-11   | RAM test                                                                 |                  |

| 5-12   | RAM test                                                                 |                  |

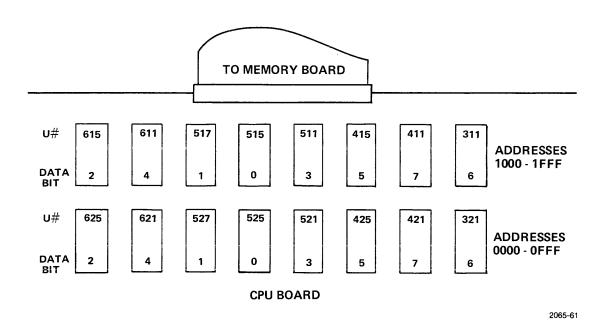

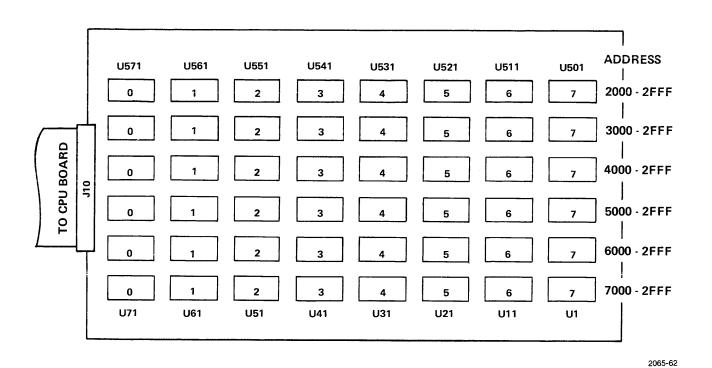

| 5-13   | Random access memory (RAM) layout for the cpu board                      | 5-17             |

| 5-14   | Random access memory (RAM) layout for the memory board                   | 5-17             |

| 5-15   | ROM test                                                                 |                  |

| 5-16   | ROM test                                                                 | 5-19             |

| 5-17   | ROM test                                                                 | 5-19             |

| 5-18   | ROM test                                                                 |                  |

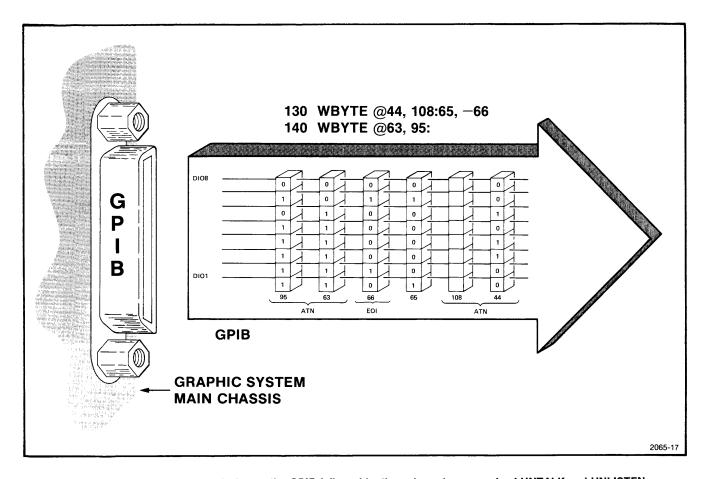

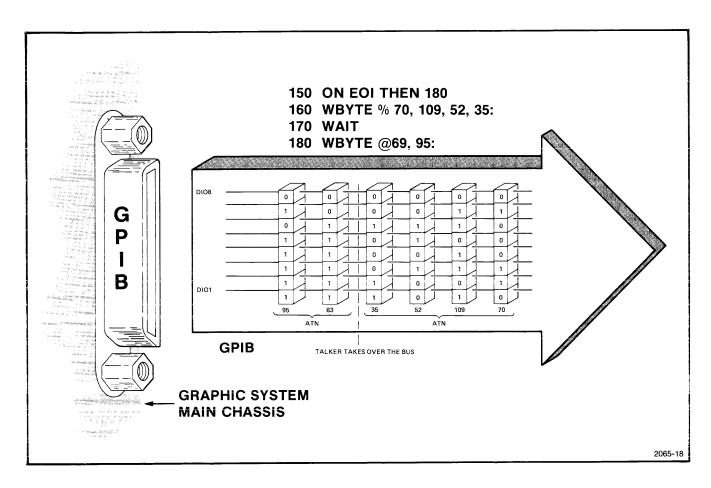

| 5-19   | GPIB test                                                                | 5-21             |

| 5-20   | GPIB test                                                                |                  |

| 5-21   | GPIB test                                                                |                  |

| 5-22   | GPIB test                                                                |                  |

| 5-23   | Display test                                                             |                  |

| 5-24   | Display test                                                             |                  |

| 5-25   | Display test                                                             |                  |

| 5-26   | Display test                                                             | 5-26             |

| 5-27   | Tape Test                                                                |                  |

| 5-28   | Tape Test                                                                |                  |

| 5-29   | Tape Test                                                                |                  |

| 5-30   | Tape Test                                                                |                  |

|        |                                                                          |                  |

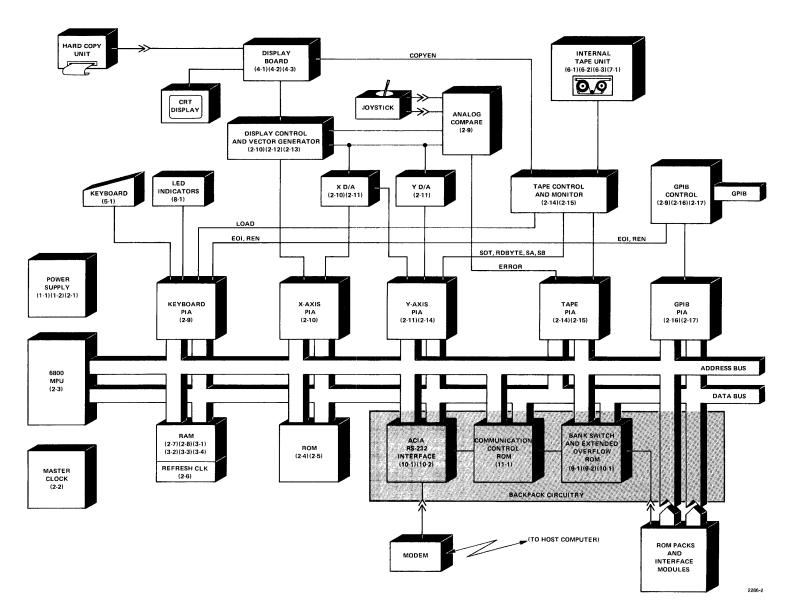

| 6-1    | 4051 Graphic System block diagram                                        | 6-2              |

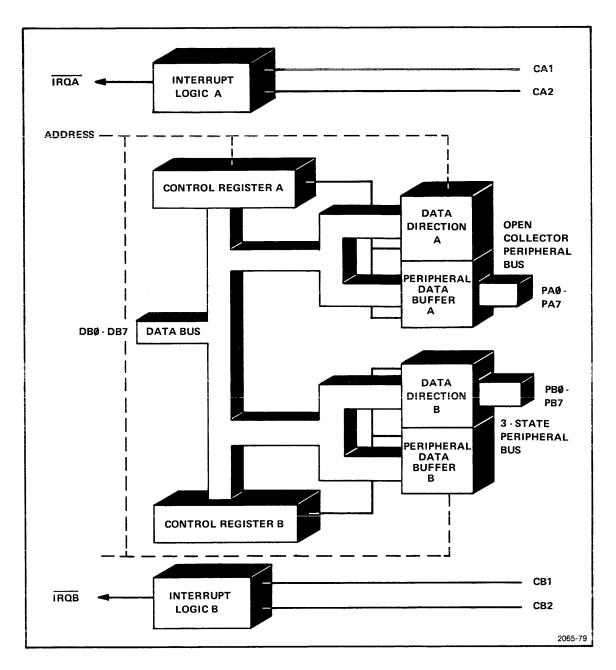

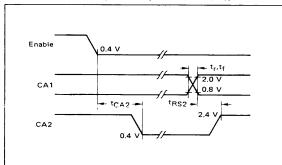

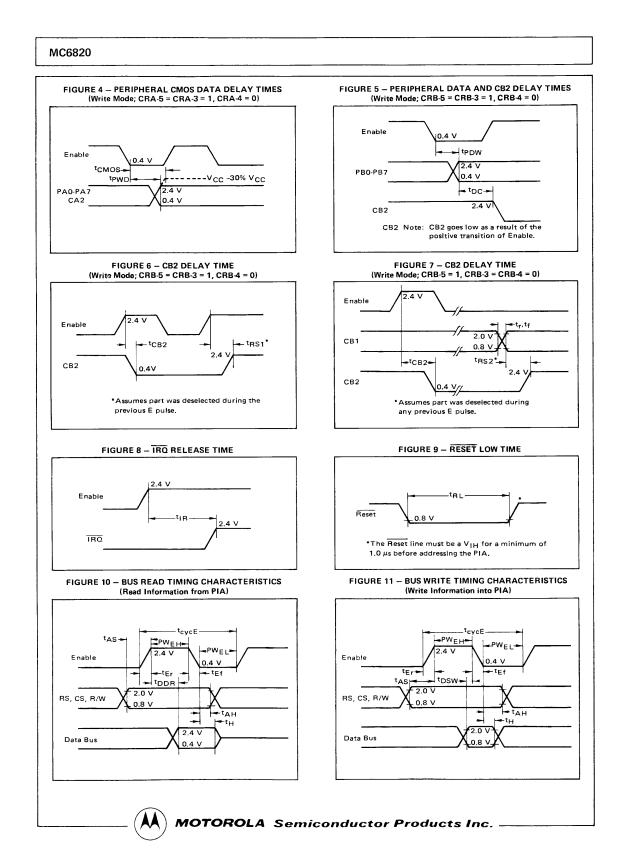

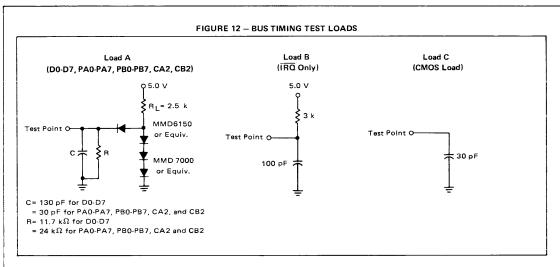

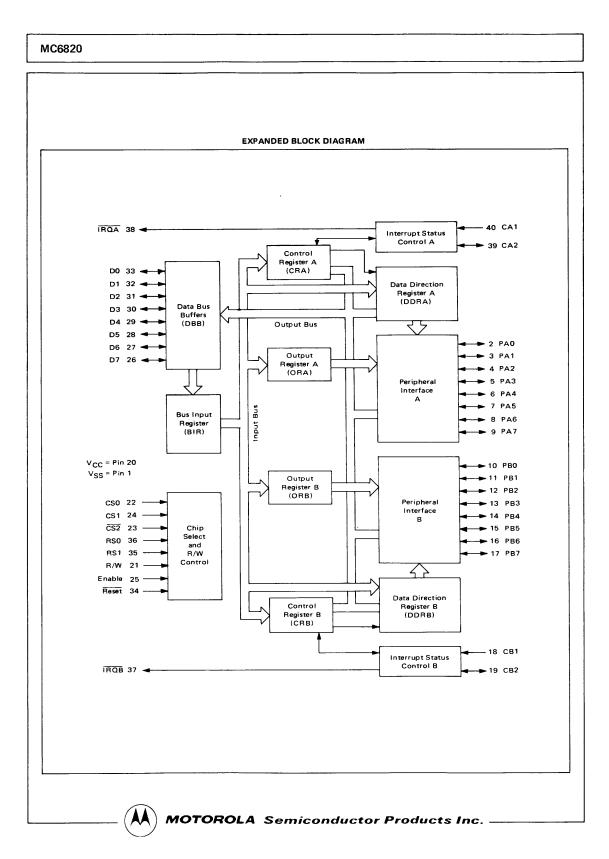

| 6-2    | Peripheral Interface Adapter (PIA) block diagram                         |                  |

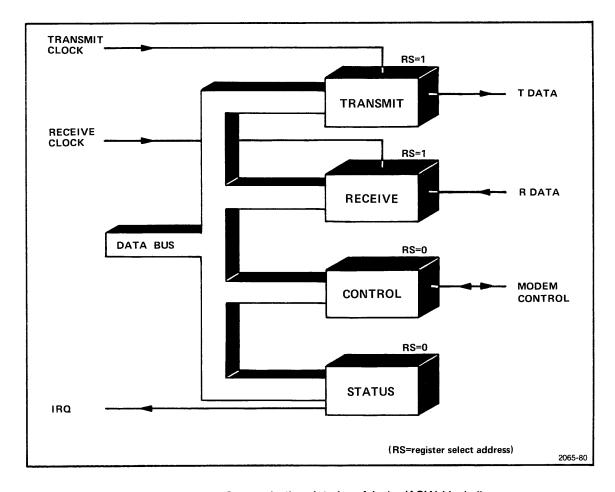

| 6-3    | Asynchronous Communications Interface Adapter (ACIA) block diagram.      |                  |

| 6-4    | Memory allocation map for the 4051                                       |                  |

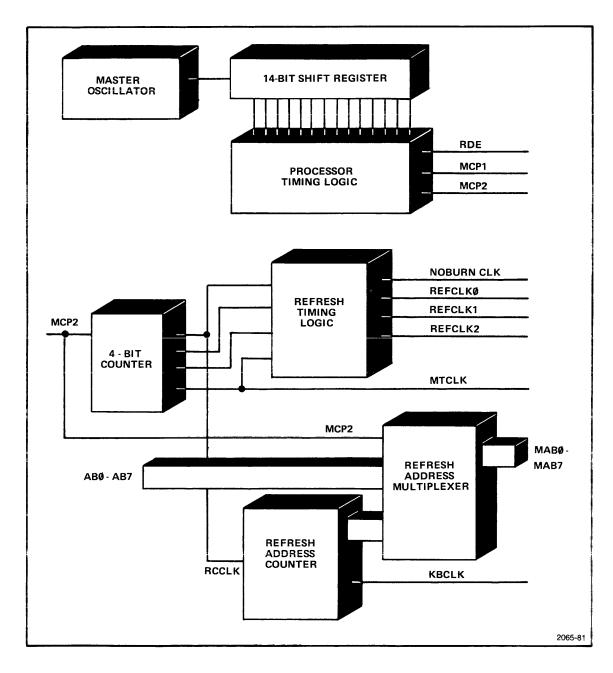

| 6-5    | Block diagram of system timing circuits                                  |                  |

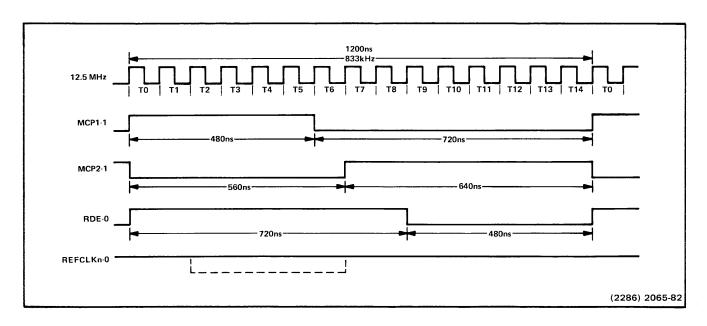

| 6-6    | Processor timing                                                         |                  |

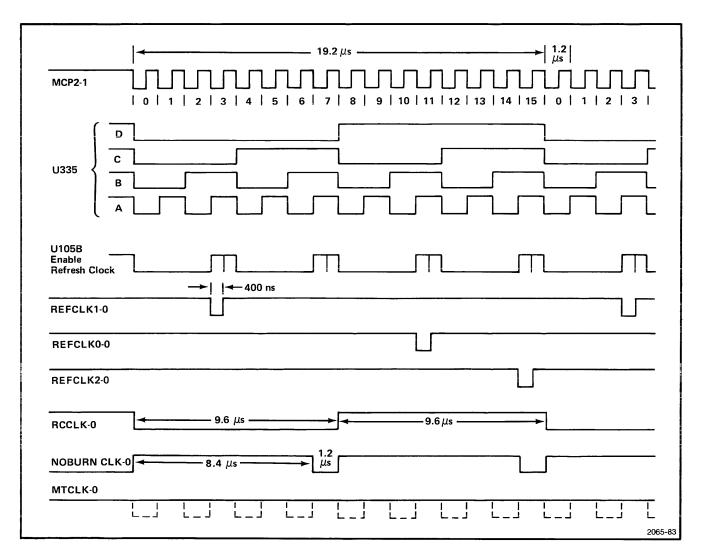

| 6-7    | Memory refresh timing                                                    |                  |

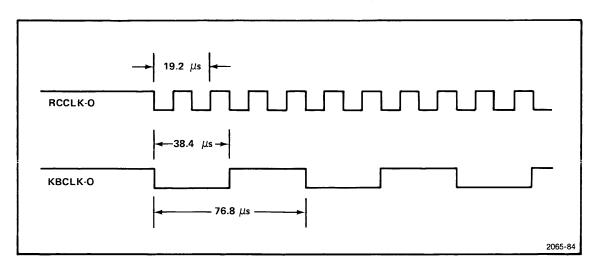

| 6-8    | Keyboard timing                                                          |                  |

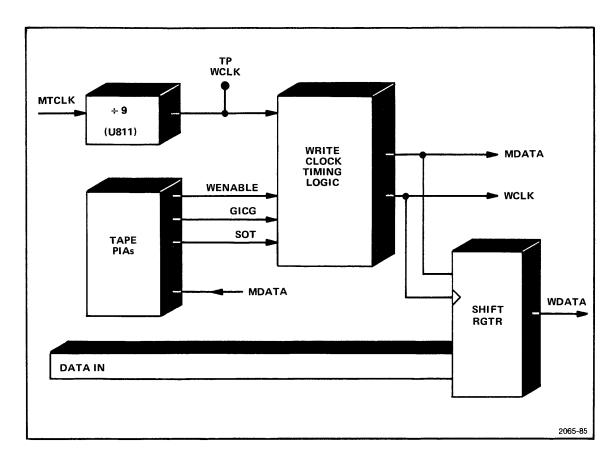

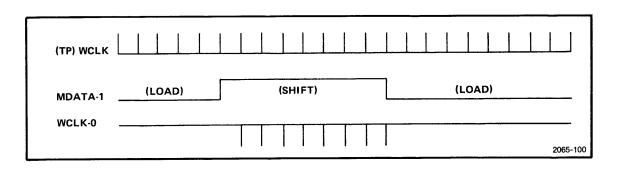

| 6-9    | Tape write timing circuits—block diagram                                 |                  |

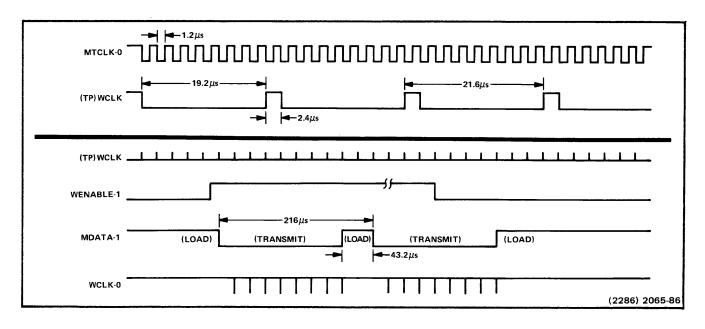

| 6-10   | Tape timing for writing data to the tape                                 |                  |

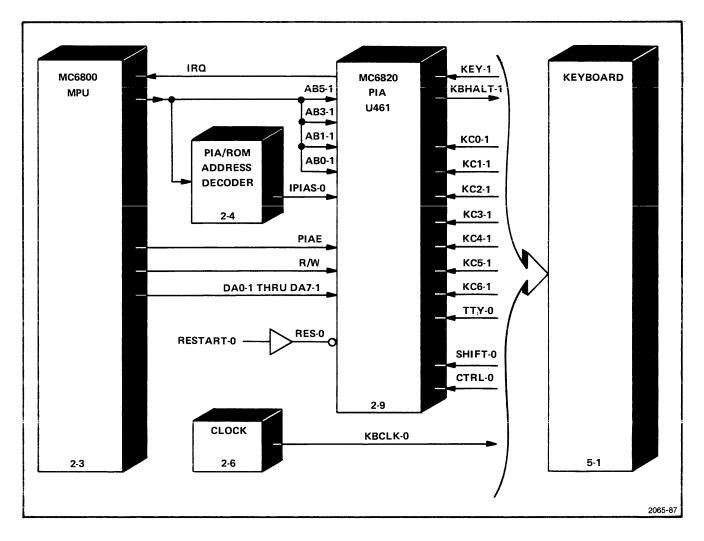

| 6-11   | Keyboard control circuitry block diagram                                 |                  |

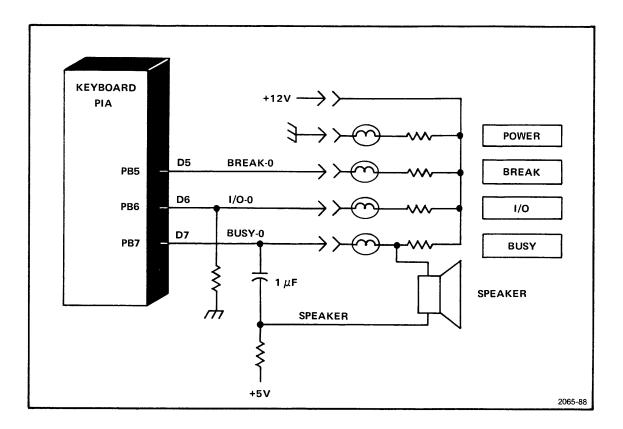

| 6-12   | Indicator board control circuitry                                        |                  |

| 6-13   | Display control circuitry block diagram                                  |                  |

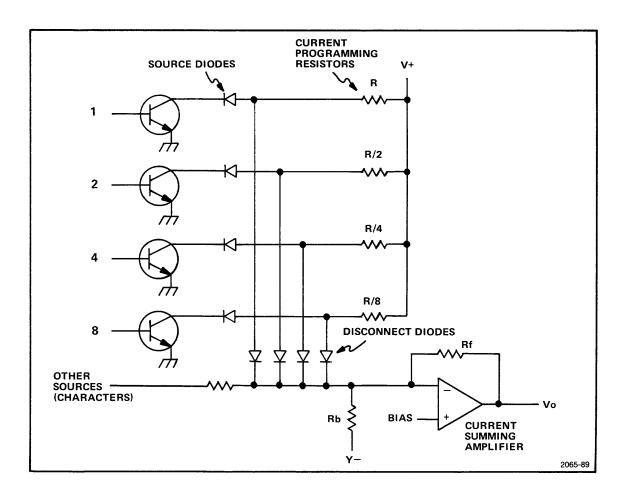

| 6-14   | Typical D/A converter using proportioned resistors and a current summing | <del>-</del>     |

|        | amplifier                                                                | 6-20             |

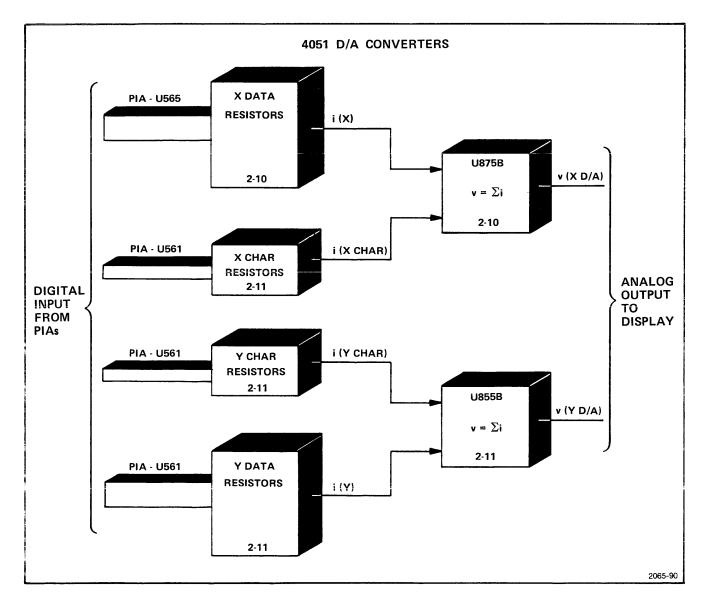

| 6-15   | Data and information flow through the X and Y digital-to-analog          | - <del>- •</del> |

|        | converters                                                               | 6-21             |

| Figure | Illustrations (cont)                                                       | Page |

|--------|----------------------------------------------------------------------------|------|

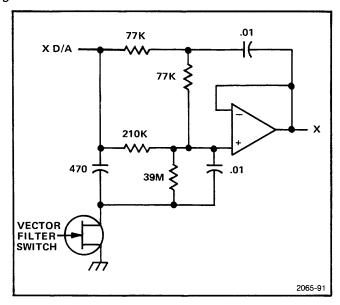

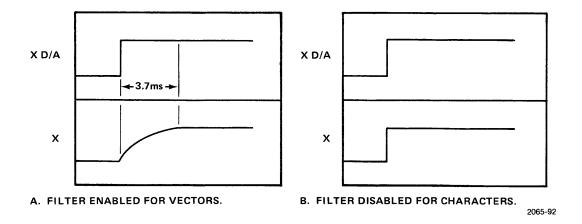

| 6-16   | Filter circuit to provide vector writing delay on the X axis               | 6-22 |

| 6-17   | Vector filtering response curves                                           | 6-22 |

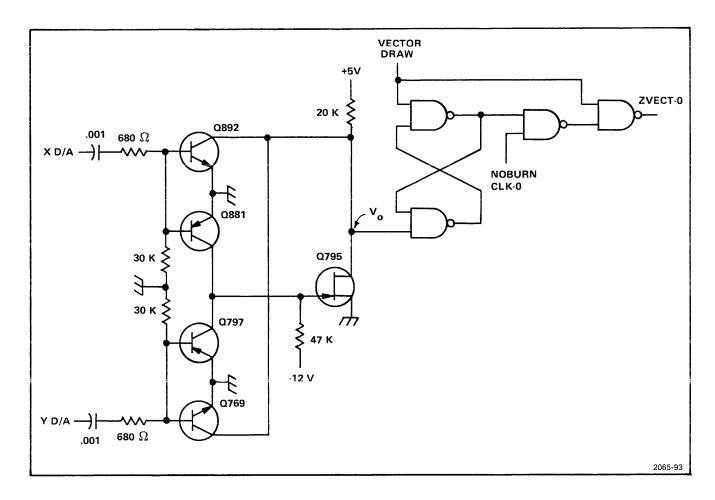

| 6-18   | Long vector sense circuit                                                  |      |

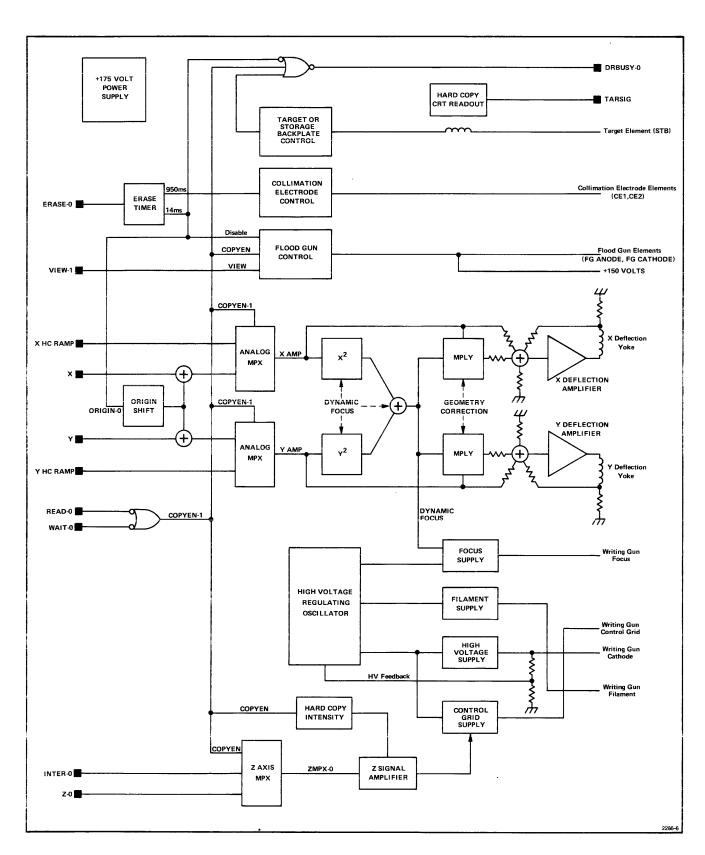

| 6-19   | Display board block diagram                                                | 6-25 |

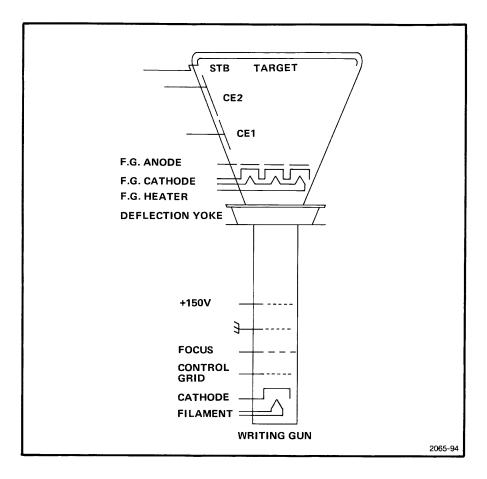

| 6-20   | Direct view storage tape (DVST) crt schematic                              | 6-26 |

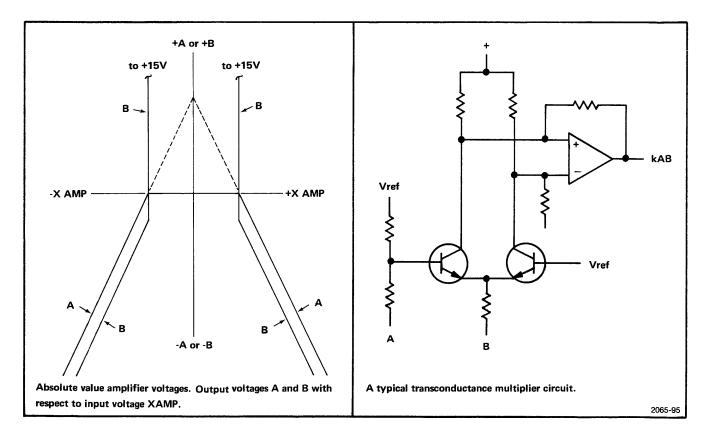

| 6-21   | Transconductance amplifier for dynamic focus and geometry correction.      | 6-28 |

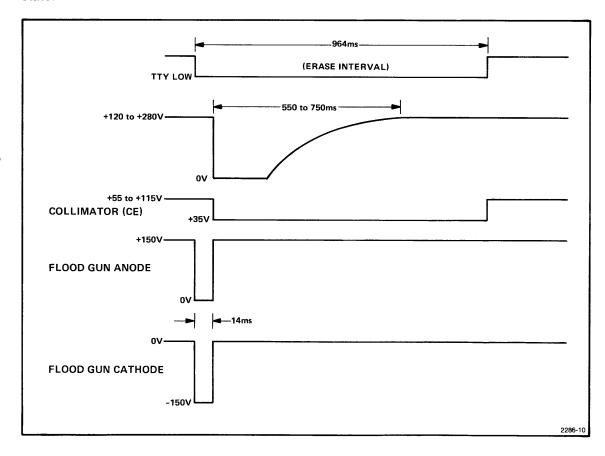

| 6-22   | Erase timing and voltage waveforms                                         | 6-30 |

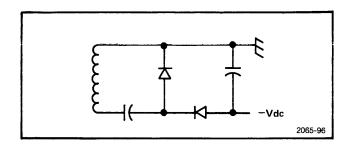

| 6-23   | A typical voltage doubler network                                          | 6-33 |

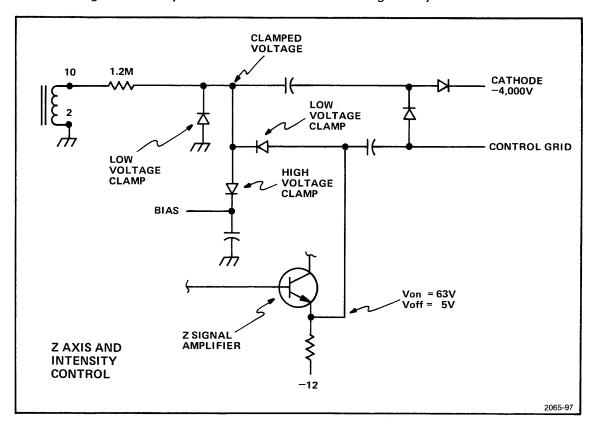

| 6-24   | Z axis control grid circuitry used to regulate the writing beam intensity. | 6-34 |

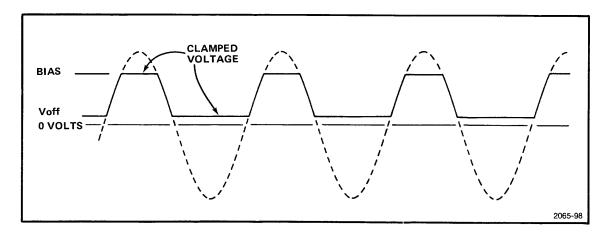

| 6-25   | Wavefrom used to establish the crt control grid voltage level              | 6-34 |

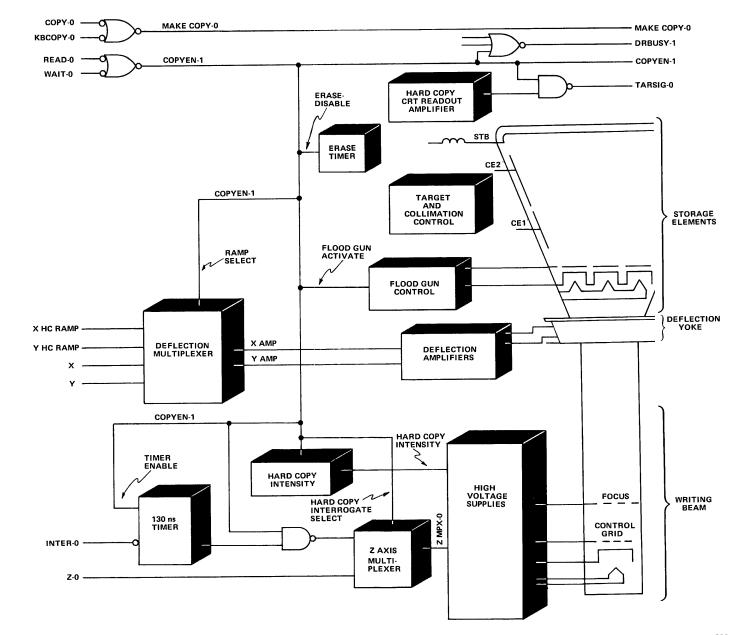

| 6-26   | Hard copy circuitry block diagram                                          | 6-36 |

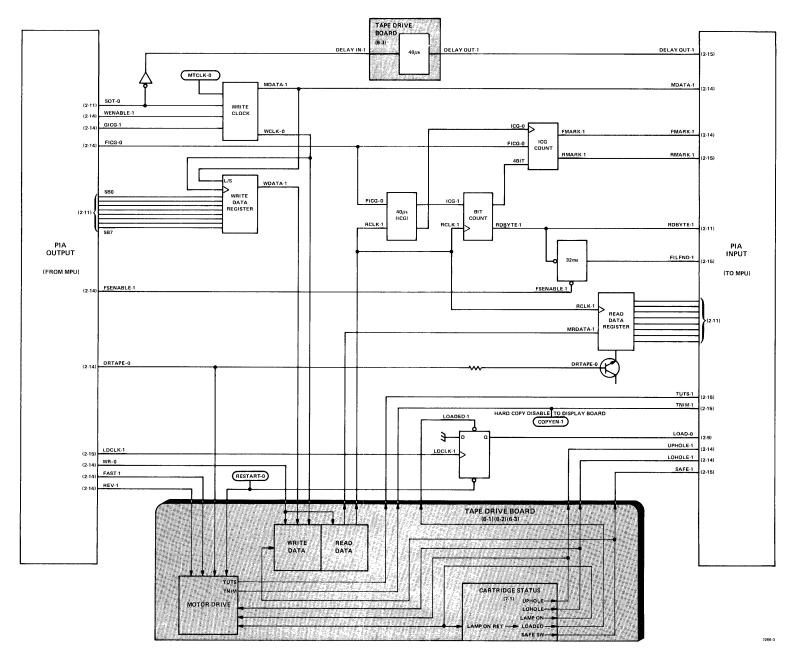

| 6-27   | Block diagram of the 4051 tape drive control circuitry                     | 6-38 |

| 6-28   | Magnetic tape recording format                                             | 6-39 |

| 6-29   | Timing signals for writing data to tape                                    | 6-40 |

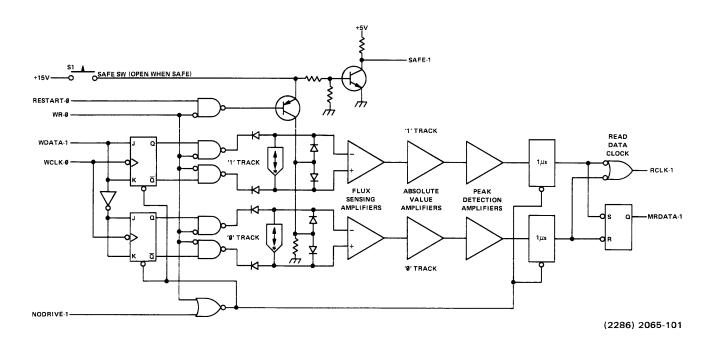

| 6-30   | Tape drive read/write circuits on the tape drive board                     | 6-43 |

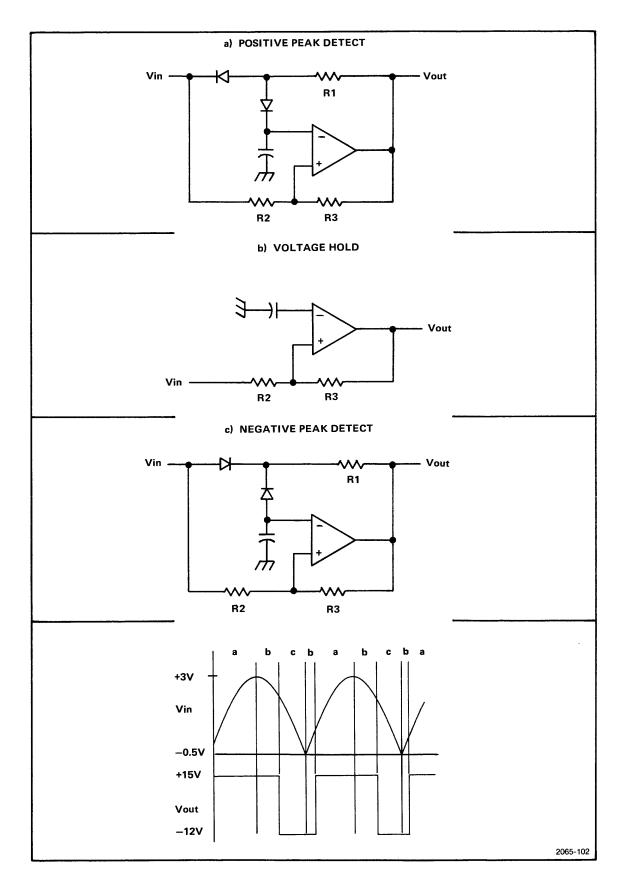

| 6-31   | Peak detection amplifier operation                                         | 6-44 |

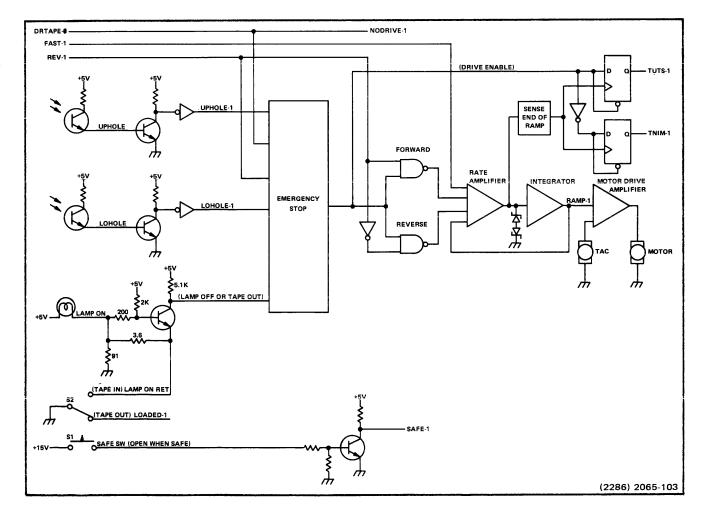

| 6-32   | Block diagram of tape status and motor drive circuitry                     | 6-45 |

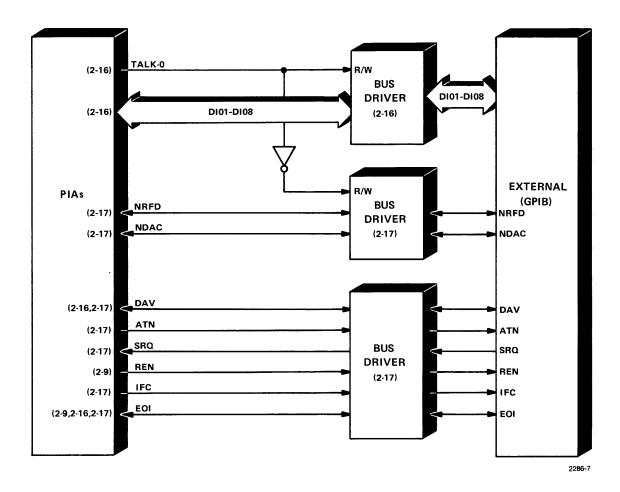

| 6-33   | Block diagram for general purpose interface bus (GPIB) circuitry on the    |      |

|        | 4051                                                                       | 6-48 |

| 7-1    | Block diagram of the Firmware Backpack circuitry                           | 7-2  |

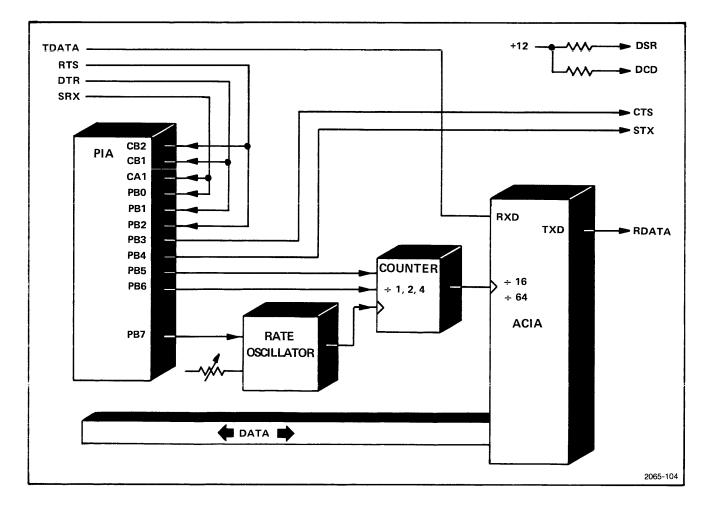

| 7-2    | Communication Interface Block Diagram                                      | 7-5  |

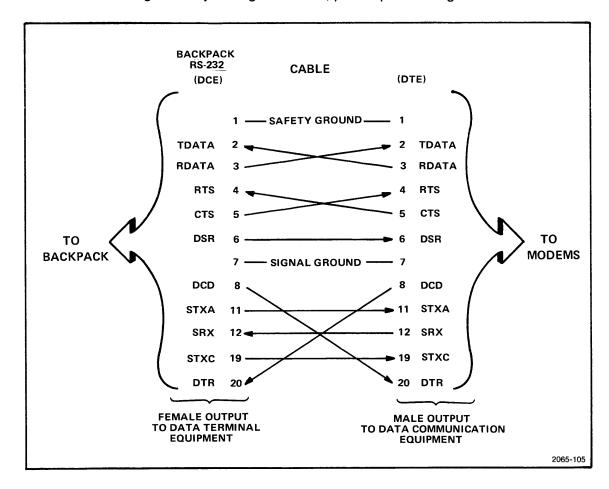

| 7-3    | Communication cable for the 4051 Communication Backpack                    | 7-8  |

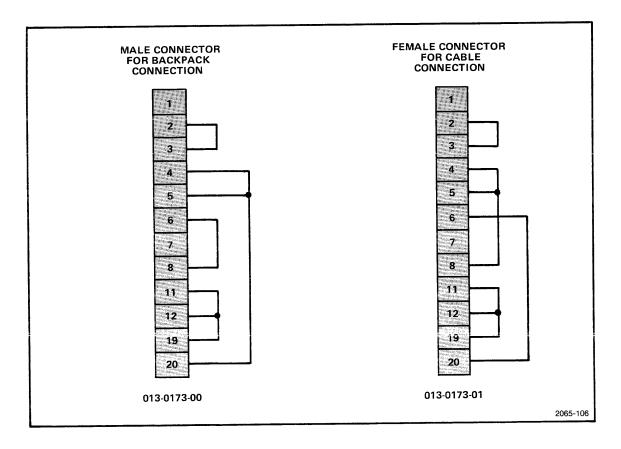

| 7-4    | Self-test adapters for use with the communication backpack                 | 7-9  |

| 7-5    | Message displayed on the crt for "CMTEST" when no self test adapter is     |      |

|        | installed                                                                  | 7-10 |

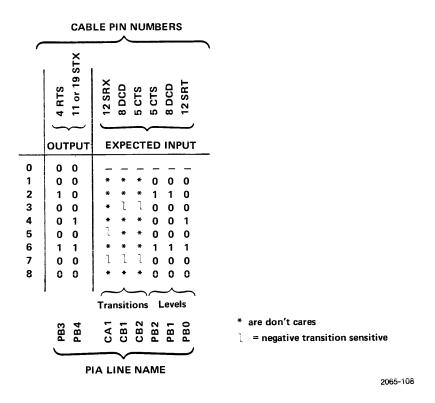

| 7-6    | Active data lines, expected transitions and expected data during the first |      |

|        | test in the "CMTEST" program                                               | 7-11 |

| 7-7    | Display output of "CMTEST" when the self-test adapter is used and no       |      |

|        | errors are present                                                         | 7-11 |

## **TABLES**

| Number                                        | Name of Table                                                                                                                                                                                                       | Page                                 |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7 | Magnetic Tape Format Specifications  System Building Blocks  Bank Switch Data Word  Device Number Assignments  Internal Device Numbers  GPIB Primary Device Address Assignments  GPIB Secondary Address Assignments | 2-17<br>2-19<br>2-20<br>2-21<br>2-22 |

| 5-1                                           | Hexadecimal-to-Binary                                                                                                                                                                                               | 5-12                                 |

| 5-2                                           | Size of 4051 Systems                                                                                                                                                                                                |                                      |

| 5-3                                           | 4051 Firmware Checksums                                                                                                                                                                                             |                                      |

| 5-4                                           | Checksums for Backpack ROMS                                                                                                                                                                                         |                                      |

| 5-5                                           | Communication Backpack                                                                                                                                                                                              | 5-21                                 |

| 6-1                                           | Data Equivalence For Decimal, Hexadecimal and Binary Codes                                                                                                                                                          |                                      |

| 6-2                                           | Key Codes (KC0 Thru KC6) For The 4051 Keyboard                                                                                                                                                                      |                                      |

| 6-3                                           | Mag Tape Format Specifications                                                                                                                                                                                      | 6-41                                 |

| 7-1                                           | Bank Switch and Peripheral Control Addresses                                                                                                                                                                        |                                      |

| 7-2                                           | Bank Switch Select Data                                                                                                                                                                                             |                                      |

| 7-3                                           | RS-232 Definitions                                                                                                                                                                                                  |                                      |

| 7-4                                           | Oscillator Frequency                                                                                                                                                                                                |                                      |

| 7-5                                           | Frequency Dividing Counter                                                                                                                                                                                          |                                      |

| 7-6                                           | Baud Rate Selection                                                                                                                                                                                                 |                                      |

| 7-7                                           | Bits 1-0 Specify Baud Rate Clock Division                                                                                                                                                                           |                                      |

| 7-8                                           | Bits 4-2 Specify Parity Encoding/Decoding                                                                                                                                                                           | 7-7                                  |

| 7-9                                           | Bits 6-5 Enable or Disable Transmit Buffer Empty Interrupt and Break—                                                                                                                                               | 7 7                                  |

| 7-10                                          | Spacing of Data Transmission                                                                                                                                                                                        |                                      |

X

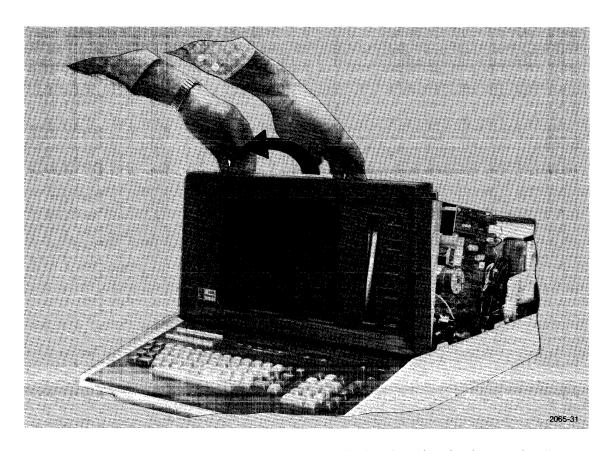

Fig. 1-1. 4051 Graphic System.

#### Section 1

## INTRODUCTION

#### **PURPOSE OF MANUAL**

The purpose of this manual is to provide a service technician with the required data for performing routine maintenance on a 4051 Graphic System. It is also intended to be a guide for troubleshooting and repairing 4051 Graphic Systems that require service.

The service documentation is divided into two volumes. Volume 1 provides preventive maintenance information, calibration and adjustment procedures, troubleshooting and service information, specialized test procedures, and descriptions of circuit operation for the 4051. Portions of the text refer to schematics and diagrams found in Volume 2.

Volume 2 contains system block diagrams, timing diagrams, schematics, cross reference tables, wire lists, and replaceable parts lists for the 4051 Graphic System and attached devices. Service information for peripheral products is to be found in the appropriate manual written for the peripheral product.

#### STANDARD COMPONENTS

Standard components of the 4051 include the following:

- (1) Full ASCII keyboard, plus calculator key pad, user-definable keys, and editing keys.

- (2) 11" DVST (direct view storage tube) display with a capacity of 35 lines of alphunumeric characters, 74 characters per line. Vector resolution is approximately 120 points per inch.

- (3) A magnetic tape unit, capable of storing 300K bytes of data and organized into a sequential-file structure. Tape format is programmable to support TEKTRONIX 4923-type tapes as well as 4051-type tapes.

- (4) A GPIB bus connector, allowing interfacing to devices compatible with IEEEE standard #488-1975.

- (5) Joystick connector, allowing the user to input graphic coordinates with optional joystick.

(6) Hard copy compatibility, allowing the user to obtain a copy of the displayed information via an optional TEKTRONIX 4631 or 4610 Hard Copy Unit.

#### **4051 GRAPHIC SYSTEM**

The TEKTRONIX 4051 (Fig. 1-1) is a desk-top unit that combines the visual display of a graphic terminal with the computational power of a scientific probrammable calculator. The 4051 can be used as a stand-alone programmable calculator, or, with the addition of the optional Communications Backpack, as an intelligent graphic terminal. The standard 4051 contains an eight-bit microprocessor, an 8K byte random access memory, an eleven-inch direct-view storage tube (with hardcopy compatibility), a built-in magnetic tape unit, and an extended BASIC language interpreter. The 4051 can handle the same processing functions normally handled by other computer-based computational systems.

The 4051 keyboard is the primary input device. The keyboard is similar to a TEKTRONIX 4012 terminal keyboard with a separate numeric keypad for data entry. Editing keys, peripheral control keys, and 10 user-definable keys are also included.

BASIC language statements are used to program the 4051. The 4051 BASIC language is an extended version of the Dartmouth College Timeshare BASIC (Beginner's All-purpose Symbolic Instruction Code) with extensions in the areas of graphic primitives, unified I/O handling of the General Purpose Interface Bus (GPIB), matrices, strings, and high level language interrupt handling.

Keyboard entries are displayed on an eleven-inch direct-view storage tube (DVST). Both upper and lower case letters are printed with a maximum of 72 characters per line. The display also features full graphic capability. Drawing lines (called vectors) on the screen is accomplished by typing BASIC graphic commands from the keyboard or executing BASIC statements under program control. The storage tube is hard copy compatible, which allows an attached hard copy unit to make a paper copy of displayed information. (The hard copy unit is optional.)

The 4051 memory is divided into a Random-Access Memory (RAM) and a Read Only Memory (ROM). The standard RAM has an 8K byte storage capacity of which 6K bytes are accessible by the user for storing programs and data. The RAM storage capacity can be increased up to 32K bytes by adding optional 8K byte memory increments.

The 4051 ROM has 36K locations that hold processor firmware, peripheral control addresses, and an 8K byte section for firmware bank swapping used by extended firmware modules (i.e., ROM packs). The Firmware Backpack or the optional Communications Backpack each provides the user with two slots for ROM packs. With the use of a device called a ROM Expander unit, the number of available ports for ROM packs can be increased to sixteen. The microprocessor has access to code in the ROM packs through use of a bank switch scheme.

Data and program instructions can be transferred onto magnetic tape and reentered into the RAM via a built-in magnetic tape unit. The storage medium is a standard data cartridge with approximately a 300K byte capacity depending upon the length of each data file.

Four rear panel connectors allow the 4051 to interface to a variety of peripherals. The General Purpose Interface Bus (GPIB) connector allows the 4051 to exchange data with devices such as disk storage units, digital X-Y plotters, and instrumentation systems. Data transfers over the GPIB are in byte-serial, bit parallel format (eight bits per byte). The GPIB is compatible with the IEEE Standard #488-1975.

Another rear panel connector is part of the optional Communications Backpack and is compatible with RS-232 devices (i.e., computer modems). This allows the 4051 to exchange data with devices such as computer terminals, printers, and modems. The RS-232 communications interface features asynchronous full-duplex or half-duplex operation. Data exchange rate is selectable by the user through program control for one of the following: 110, 150, 300, 600, 1200, or 2400 baud.

The other two connectors are utilized by an optional joystick and a Hard Copy Unit.

#### **Power Requirements**

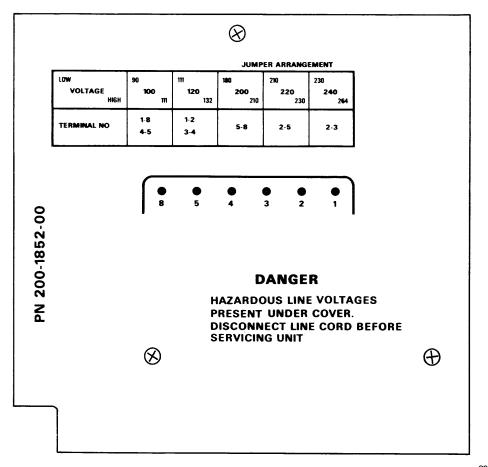

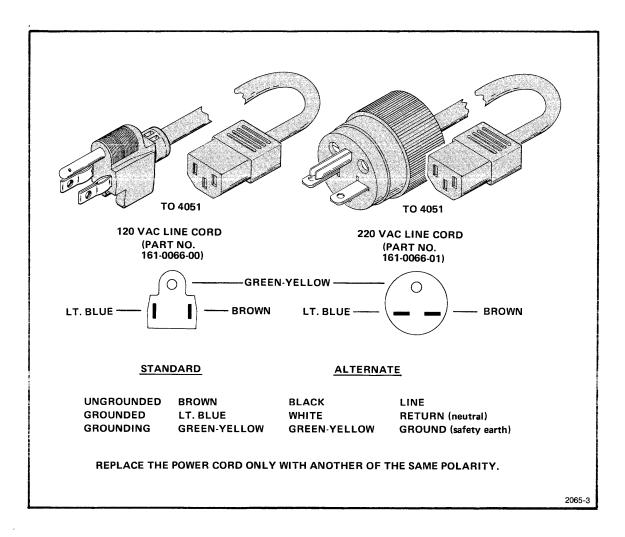

The 4051 Graphic System will perform properly at 50 Hz or 60 Hz line frequencies using voltages of 120 Vac or 220 Vac. The 4051 is normally shipped from the factory strapped for 120 Vac operation. To convert the 4051 to 220 Vac operation, the cover of the 4051 must be removed; the transformer jumpers must be changed in accordance with a table inscribed on the transformer shield (Fig. 1-2); a 0.8 ampere line fuse must be installed; and a 220 volt power cable must be used (Fig. 1-3).

2065-2

Fig. 1-2. Power Supply Transformer Shield.

Fig. 1-3. Replaceable power cords for the 4051.

#### **Special Test Aids**

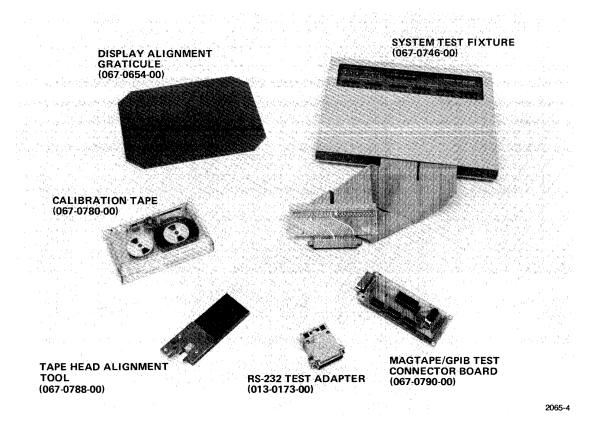

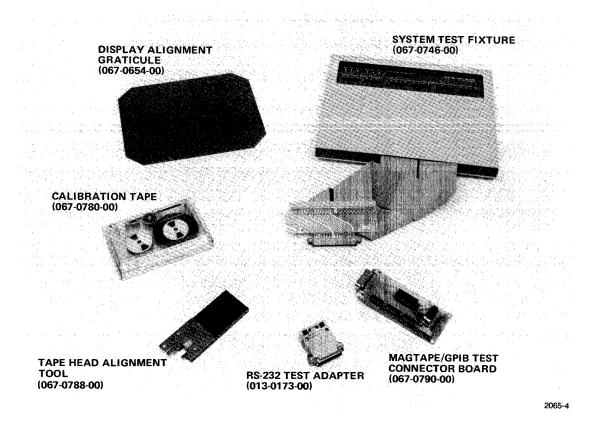

Most troubleshooting of 4051 electronics can be performed using standard general purpose test equipment found in most repair stations. A number of test and adjustment procedures require special test figures (Fig. 1-4) and devices; therefore, Tektronix has developed a calibration tape to help align and calibrate the magnetic tape unit, and a 4051 Test Fixture to exercise the Motorola 6800 microprocessor and perform tests on memory.

Fig. 1-4. Special test aids for calibrating and troubleshooting the 4051 Graphic System.

#### Section 2

## **SPECIFICATIONS**

#### INTRODUCTION

This section gives a brief review of 4051 operations with special emphasis placed on physical and electrical specifications of the system. Hardware performance specifications are tabulated for quick reference. Some explanatory text is also incorporated. BASIC language statements are described in detail in the 4051 Graphic System Reference Manual. Refer to the Reference Manual for detailed operation information. (Duplication of information is not the intent of the service documents.)

#### **SPECIFICATIONS**

#### PHYSICAL MEASUREMENTS

Dimensions (see Fig. 2-1)

Length 30.75 inches or 78.1 cm

18.25 inches or 46.4 cm

Width Height

13.625 inches or 34.6 cm

Shipping Weight

80 pounds or 36.3 kg

Fig. 2-1. 4051 dimensions.

#### **ENVIRONMENTAL SPECIFICATIONS**

Temperature

Operation

+10°C to +40°C

Storage

$-40^{\circ}$ C to  $+65^{\circ}$ C (tape limited to  $+45^{\circ}$ C)

Altitude

Operating

to 15,000 feet

Storage

to 50,000 feet

Humidity (maximum)

Operating

80% non-condensing (tape limited to 20% min. and 80% max.)

Storage

95% non-condensing (tape limited to 20% min. and 80% max.)

Shock

Non-operating

30 g's.

#### **POWER SPECIFICATIONS**

#### Line Voltages

| •              |                   |

|----------------|-------------------|

| Voltage        | Fuse              |

| 100 V ±10%     | 1.6 A medium-blow |

| 120 V ±10%     | 1.6 A medium-blow |

| 200 V +5% -10% | 0.8 A medium-blow |

| 220 V ±5%      | 0.8 A medium-blow |

| 240 V +10% -5% | 0.8 A medium-blow |

Maximum Line Voltage

132 Vac or 264 Vac

Line Frequency Range

48 Hz to 66 Hz

**Power Comsumption**

200 watts maximum

Dielectric Breakdown Greater than 2000 Vac RMS (60 Hz) between power line and accessible conductive components.

#### Power Supply Voltages

| Voltage                | Regulation | Ripple <sup>1</sup> | Current<br>Demand | Current<br>Limit   |

|------------------------|------------|---------------------|-------------------|--------------------|

| +5.1 V ±2%             | ±1%        | 5 mV                | 4.0 A             | 4.5 A              |

| +12 V ±5%              | ±3%        | 5 mV                | 450 mA            | 1.0 A (temp. dep.) |

| +15 V ±1%              | ±0.2%      | 5 mV                | 200 mA            | 600 mA             |

| +20 V                  | unreg.     |                     | 3 A               | 3 A fused          |

| +185 V                 | unreg.     |                     | 100 mA            |                    |

| +295 V                 | unreg.     |                     | 50 mA             |                    |

| −12 V ±2%              | ±0.5%      | 5 mV                | 250 mA            | 600 mA             |

| −20 V                  | unreg.     |                     | 3 A               | 3 A fused          |

| 40 V (-20 to +20) ±10% | unreg.     |                     | 400 mA            |                    |

Note: Ripple is measured at the supply with X1 probe on 7A26 limited to 20 MHz, with probe GND connected to supply chassis, load was resistive dummy drawing at current demand specified from all supplies.

#### **OPERATOR INTERFACE**

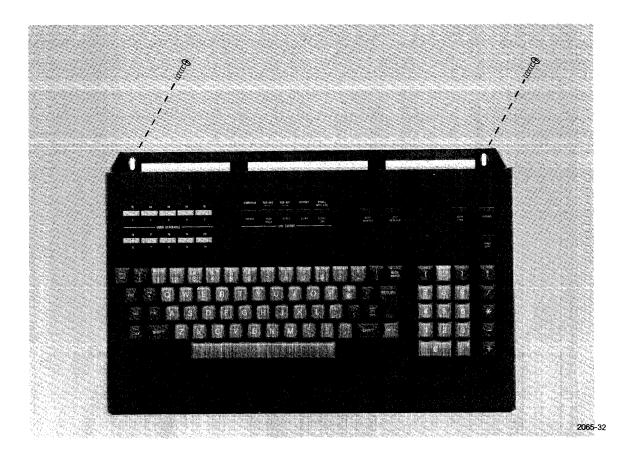

The front of the 4051 is divided into ten functional areas. These areas are illustrated by Fig. 2-2.

A display screen is used to present both graphic and alphanumeric or program information in a visible form.

The internal tape is used to store BASIC language program statements and data of various types on an industry-standard data cartridge.

The status indicator lights tell when power is applied to the system, when the system is busy doing calculations, when the system is performing input/output operations, and when waiting to stop at the end of the current BASIC language instruction in response to pressing the BREAK key.

Fig. 2-2. Operator controls and system indicators for 4051 Graphic Systems.

The eject mechanism removes a tape cartridge from the 4051 Graphic System internal tape unit.

User-definable function keys allow the operator to branch to any of 20 specified BASIC program locations when pressing one of these keys. There are ten keys to specify ten program locations. Another ten locations are used if the keys are pressed in conjunction with holding down a SHIFT key.

The alphanumeric keyboard is used for entry of BASIC program language statements and data. If a communication backpack is installed on your 4051, these keys can be used for data entry into a host computer.

Line editing keys allow convenient editing of BASIC program statements without having to retype the entire command string.

Program development keys can be used to sequentially enter BASIC statement numbers when programs are being created or modified. They can also be used to debug or troubleshoot a BASIC language program.

The numeric keypad provides convenience when entering numeric data into the system. The basic calculator functions are also readily available. When used as a calculator without running a BASIC program, the RETURN key causes the calculated result to print on the display.

Peripheral control keys offer limited control of the tape unit and optional Hard Copy Unit.

#### **ALPHANUMERIC KEYBOARD**

ALPHANUMERIC KEYS The alphanumeric keys (letters, numbers and symbols) are used to

enter BASIC statements and generate ASCII control characters.

Keys 0-9 can also be used to enter numeric data.

SPACE BAR When the space bar is pressed, the display cursor moves one

horizontal space to the right. No character is printed. If the cursor is

at the right margin, no operation is performed.

SHIFT This key is similar to the SHIFT key on a typewriter keyboard. It

determines which one of two characters are printed when an alphanumeric key is depressed. If used alone, this key brings the

display out of Hold Status.

TTY LOCK Causes all lower case letters to be transformed to upper case when

keyed.

TAB When this key is pressed, the keyboard issues the ASCII control

> character TAB, regardless of the SHIFT key position. When the TAB function is executed, the display cursor moves to the right and stops in column 1, 19, 37, 55, 1, etc. TAB spacing can be modified if a

PRINT USING statement is executed.

**CTRL** When pressed in combination with a letter key and sometimes the

> SHIFT key, the keyboard issues an ASCII control character. At statement entry time, all control characters are echoed to the display as an underlined letter (except for CR and RUBOUT). At statement execution time, some control characters cause machine display

functions to be executed.

**ESC** When this key is pressed, the keyboard issues the ASCII control

character ESC regardless of the SHIFT key position.

HOME PAGE If pressed alone, the display is erased and the cursor returns to the

> Home position. If pressed in combination with the SHIFT key, the cursor returns to the Home position and the display is not erased.

**BACK SPACE** Moves the cursor to the left by one space.

**RETURN** Pressing this key generates an ASCII control character CR

> (Carriage Return). The display cursor returns to the left margin and moves one vertical space down. This key causes the machine to evaluate the information on the previous line. If the line contains a line number, the statement is entered into memory and is not executed. If the statement does not contain a line number, it is

executed immediately.

RUBOUT Pressing RUBOUT usually causes the display cursor to move one

> space to the left and write a full 5 x 8 dot matrix over any character in that location. The character underneath the cursor is logically removed from memory and replaced by the space character. The next time the line is printed, a space appears instead of the 5 x 8 matrix. If the cursor is over a non-blank character, the cursor does

not move but rubs out the present position.

The first time the BREAK key is pressed, the BREAK indicator on the

front panel lights up and the machine stops program execution after the present line is completed. This is referred to as a "BREAK pending" condition. The indicator goes out when the program halts.

If the BREAK key is depressed while the BREAK light is on, program execution is aborted immediately and the program line pointer returns to the starting position.

**BREAK**

#### LINE EDITING KEYS

The five program line editing keys at the top center of the keyboard are each dual purpose. The primary function is lettered below each key while the secondary function is printed above each key.

The primary function is performed by pushing the key directly. The secondary function is performed by pressing the key and at the same time holding the SHIFT key. All operations are performed on the current line which is stored in a 72-character line buffer.

EXPAND This key is used for insert operations. All characters to the right of

the cursor, including that character where the cursor is positioned, are moved to the extreme right of the line buffer. On the screen, the line appears to split into left and right portions separated by a gap.

The cursor finishes at the extreme left of the gap.

Characters may now be inserted.

COMPRESS This key (actually the simultaneous pushing of the EXPAND key and

SHIFT key), is the inverse of EXPAND. COMPRESS removes adjacent spaces to the right. The portion of line to the right of the

screen is shifted to the current position of the cursor.

BACKSPACE This key moves the cursor one character position to the left.

RUBOUT This key is equivalent to pressing RUBOUT.

SPACE This key is equivalent in function to the SPACE bar on the main

keyboard and is provided in this set for convenience. The cursor is positioned one character space to the right until the right margin is

reached.

RUBOUT ——— This key is equivalent to RUBOUT except it moves to the right

instead of to the left.

CLEAR empties the contents of the current line buffer without

affecting information already stored in RAM.

REPRINT This key duplicates the current contents of the line buffer one

position below the current display. The position of the cursor relative to the buffer is unchanged. This is a useful key to use when,

due to overwriting, the storage display is difficult to read.

RECALL LINE This key recalls a program line previously stored in RAM. The

number of the line to be recalled is entered prior to pushing this key. The line is called and the cursor finishes one position beyond it.

RECALL NEXT LINE This key is similar in function to the RECALL LINE, but instead of

calling the line with the line number currently in the display, the line

with the next greater number is called.

#### PROGRAM DEVELOPMENT KEYS

The AUTO NUMBER function is provided as an operator **AUTO NUMBER**

convenience during program statement entry time. Pressing the key

once places the 4051 in a mode where line numbers are

automatically provided for each BASIC statement entry from the keyboard. The first time the key is pressed, line number 100 is placed in the line buffer and appears on the display. The operator enters a BASIC statement and presses the RETURN key. The machine then places line number 110 in the line buffer for the next statement entry. The line number increment is automatically set at 10. To start the auto number sequence with a line number other than 100, the line number is entered into the line buffer from the keyboard and then the AUTO NUMBER key is pressed. The 4051 then provides line numbers from that starting point in increments of 10. To exit the auto number mode, the operator presses the AUTO NUMBER key again.

The STEP PROGRAM key causes the 4051 to execute the current STEP PROGRAM

BASIC program one step at a time. Each time the key is pressed, one line in the program is executed. This feature allows the keyboard operator to monitor the execution sequence of the program during debugging operations. Normally, the program starts one step execution from the beginning; however, the program line counter can be set to any line in the program by using the GOTO statement and then pressing the STEP PROGRAM key causes one step execution from that point. For example, entering GOTO 500 and pressing the RETURN key sets the program line counter to line number 500. The program can then execute one step at a time from that point by pressing the PROGRAM STEP key again and again.

The AUTO LOAD key causes the internal magnetic tape unit to **AUTO LOAD**

rewind and load a BASIC program from the magnetic tape cartridge into the Random Access Memory. There must be a valid ASCII

program stored on the tape, otherwise an error occurs.

Pressing the REWIND key causes the 4051 to rewind the tape REWIND

cartridge in the internal magnetic tape unit. Pressing the REWIND

key is the same as executing the BASIC statement FIND 0.

Pressing the MAKE COPY key causes an attached Hard Copy Unit to MAKE COPY

make a paper copy of the information on the 4051 display. Pressing this key is the same as executing the BASIC statement COPY.

#### STATUS LIGHTS

4051 is busy transferring or processing data. **BUSY**

Input/output operations are in progress. 1/0

BREAK A break in program execution is pending. The BREAK light goes out

after program execution halts at the end of the current line.

POWER Indicates that power is supplied to the 4051.

**DISPLAY**

The display is an 11 inch Direct View Storage Tube (DVST) crt.

HOLD STATUS Reduced intensity after 90 seconds of no display activity occurs to

maintain the currently stored image for redisplay.

AUTOMATIC ERASE After 30 minutes of idle machine time, the crt erases.

GRAPHICS

Coordinates are specified by a pair of decimal fractions. The default coordinate limits are 0—100 on the vertical (Y) axis and 0—130 on the horizontal (X) axis (Fig. 2-3). Vectors are drawn using MOVE and DRAW commands to move the writing beam to a specified coordinate location or to draw a line from the current beam reference position to the indicated coordinate location. The coordinate limits can be changed by executing the WINDOW command. Resolution is approximately 120 points per inch.

Fig. 2-3. Default graphic coordinate limits.

ALPHANUMERIC CHARACTERS

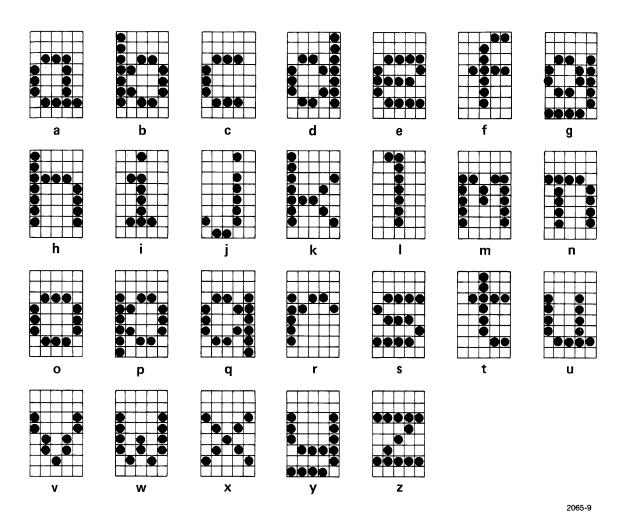

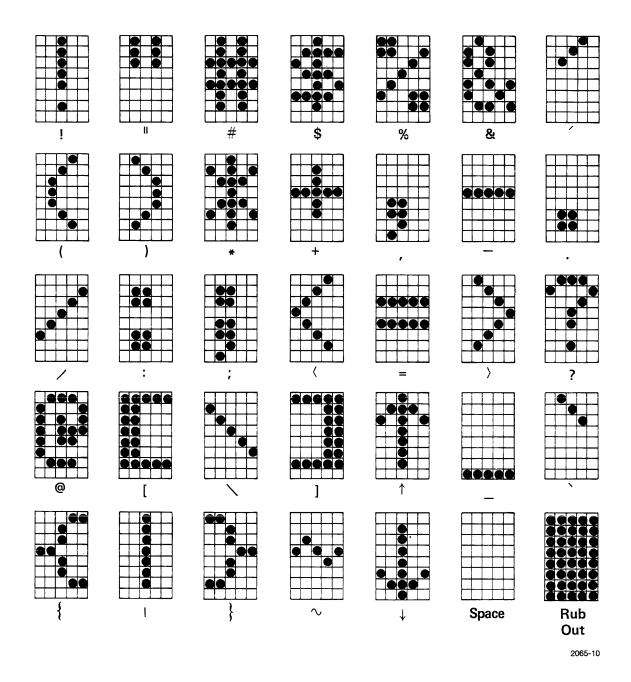

Full ASCII 96 printable characters set (upper and lower case) printed using a 5 X 8 dot matrix (see Figures 2-4, 2-5, 2-6 and 2-7).

72 characters/line

35 lines/display

2590 characters/display

Automatic return and linefeed (CR-LF) at the right margin to display lines longer than 72 characters in length.

Fig. 2-4. US ASCII Character Font (Upper Case Letters and Numbers).

Fig. 2-5. US ASCII Character Font (Lower Case Letters).

Fig. 2-6. US ASCII Character Font (Special Symbols).

Fig. 2-7. NON-US ASCII Character Font (Special Symbols).

#### **MAGNETIC TAPE UNIT (Built In Unit)**

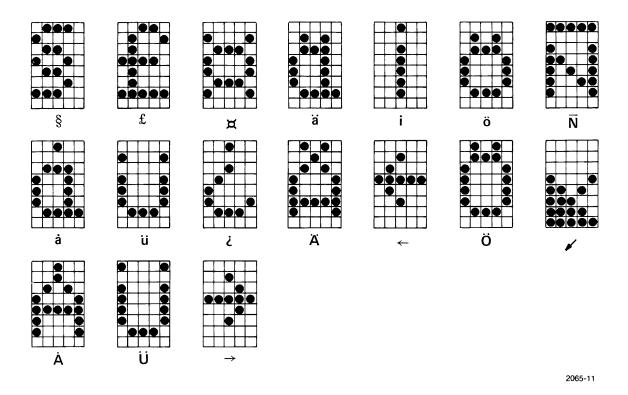

The tape unit uses an industry standard data cartridge with approximately 300 feet of 1/4 inch computer grade tape having a storage capacity of 300K bytes of data (Fig. 2-8).

Input/output operations with the tape unit are normally performed by executing the BASIC language commands FIND, OLD, SAVE, APPEND, INPUT, OUTPUT, PRINT, READ, and WRITE. Many of the commands require the tape unit address @32. Two keyboard keys, REWIND and AUTO LOAD, provide minimal control of tape operations. Magnetic tape operations are defined in detail in the 4051 Graphic System Reference Manual.

Fig. 2-8. Standard data cartridge for the 4051.

| Recording Method | NRZ self clocking (NRZ = Non Return to Zero) |

|------------------|----------------------------------------------|

| Bit Density      | 1600 bits per inch                           |

| Tracks           | 2                                            |

| Head Type        | Single 2-track read/write head               |

| неао туре                    | Single 2-trac       | k read/write nead       |                        |

|------------------------------|---------------------|-------------------------|------------------------|

|                              | Tape Speed          | Accel/Decel Time        | Accel/Decel Tape Dist. |

| Normal Read/Write            | 30 ips<br>76.2 cm/s | 25 ms                   | 0.375 in $\pm$ 10%     |

| Fast Forward/Reverse         | 90 ips<br>228.6 cm/ | 90 ms<br>/s             | 1.125 in $\pm$ 10%     |

| Rewind                       | 90 ips<br>228.6 cm  | 90 ms<br>/s             | 1.125 in ±15%          |

| Life Expectancy              |                     |                         |                        |

| Drive Motor and<br>Tape Head | ≥1000 hc            | ours of read/write ope  | ration.                |

| Operating Time               | 6 hours o           | f tape drive read/write | e activity, or every   |

| Between Head<br>Cleanings    | 1000 hou            | rs of standard 4051 us  | age.                   |

#### **MAGNETIC TAPE MEDIA**

The tape units use an industry standard data cartridge.

3M Company type: DC 300 A

Tektronix Part Number 119-0680-00

Data Capacity 300K bytes

Minimum Life 5000 passes

Tape Markers B.O.T. (Beginning Of Tape)

(See Diagram) Load Point

Early Warning Point E.O.T. (End Of Tape)

#### DATA FORMAT AND RECORDING METHOD

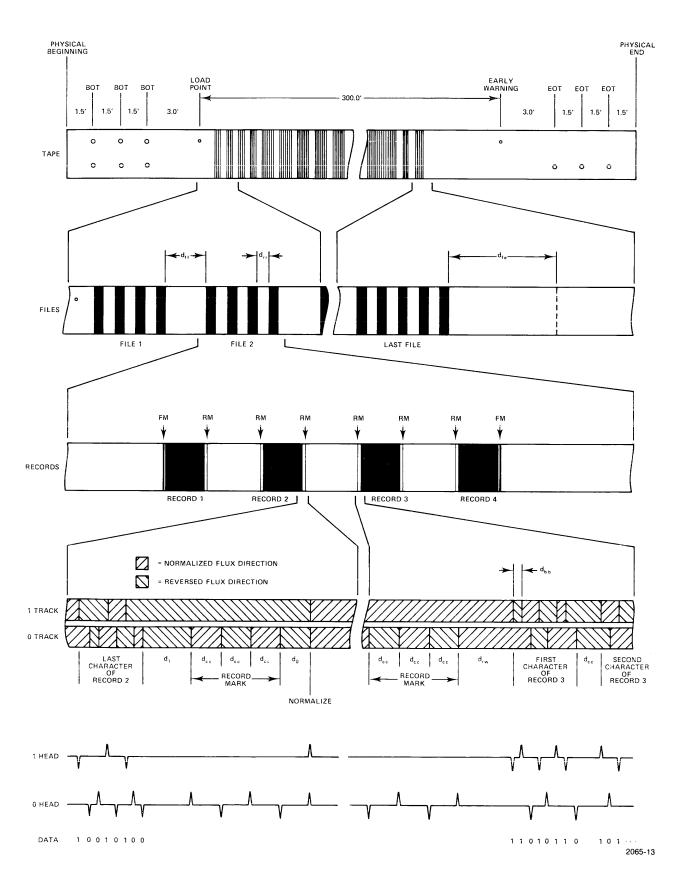

The data format is determined by 4051 system firmware (Fig. 2-9). Data timing is tabulated in Table 2-1. Information on the tape is divided into files that contain a minimum of 3 records. The standard record length is 256 bytes of data characters, but a 128 character format may be selected using the PRINT @33,0: statement. The 128 character format is compatible with standard 4923 tape unit operations.

The tape formatting process occurs with the MARK n,m statement where n is the number of files to be marked and m is the number of bytes per file. Areas of the tape are demarcated by means of record marks and file marks.

Binary data bits are represented as reversals in flux direction (magnetic domain boundaries) on either the 1 track or 0 track. In reading the tape, the tape head is sensitive to flux reversals. The determination of a 1 or 0 depends upon which track had the flux reversal. This is the NRZ data recording system.

Special Data Sequences Data is held at zero during record and file marks. Flux reversals

occur only on track zero for these sequences.

Record Mark 4 flux reversals separated by intervals about three times longer than

data bit separations. The longer intervals are called intercharacter

gaps. The shorter intervals are interbit gaps.

File Mark 8 flux reversals separated by intervals about three times longer than

data bit separations.

Fig. 2-9. 4051 magnetic tape cartridge recording format. See table 2-1 for timing and distance specifications.

Table 2-1

MAGNETIC TAPE FORMAT SPECIFICATIONS

| Characteristic                        | Symbol          | ol Distance |      |       |       | Time (at 30 ips max.) |      |      |                 |

|---------------------------------------|-----------------|-------------|------|-------|-------|-----------------------|------|------|-----------------|

|                                       |                 | min.        | nom. | max.  | units | min.                  | nom. | max. | units           |

| erase after<br>last file              | d <sub>fe</sub> | 9           | -    | _     | in    | 300                   | -    | -    | ms              |

| interfile gap                         | d <sub>ff</sub> | 3.17        | 3.60 | 4.03  | in    | 172                   | 195  | 218  | ms <sup>2</sup> |

| interrecord gap                       | dπ              | 1.06        | 1.20 | 1.34  | in    | 57                    | 65   | 73   | ms³             |

| read-to-write gap                     | $d_{\rm rw}$    | 4.35        | 8.18 | 12.00 | mil   | 145                   | 272  | 400  | μs              |

| first intercharacter gap after record |                 |             |      |       |       |                       |      | 100  |                 |

| data                                  | d <sub>i</sub>  | 1.50        | -    | 3.90  | mil   | 50                    | -    | 130  | μs              |

| intercharacter gap                    | d∝              | 1.50        | 2.25 | 3.00  | mil   | 50                    | 70   | 100  | μs              |

| normalizing gap<br>after EOR mark     | d <sub>o</sub>  | -           | -    | 3.00  | mil   | -                     | -    | 100  | μs              |

| interbit gap                          | dы              | .57         | .65  | .73   | mil   | 19                    | 21   | 24   | μs              |

<sup>2</sup>Speed is not constant at 30 ips during the interfile gap (Fig. 2-9).

<sup>3</sup>Speed is not constant at 30 ips during the interrecord gap (Fig. 2-9).

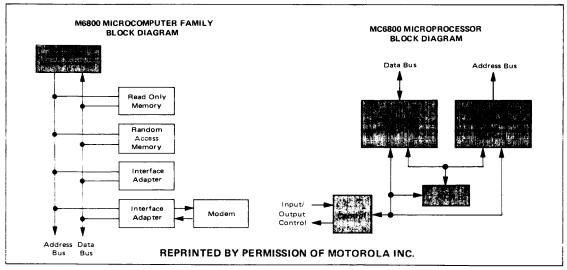

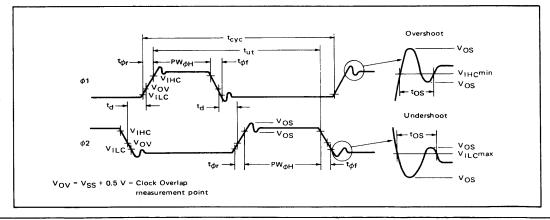

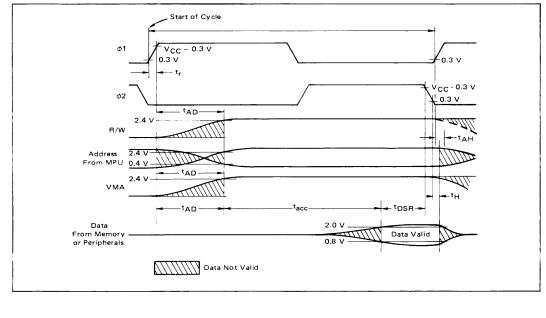

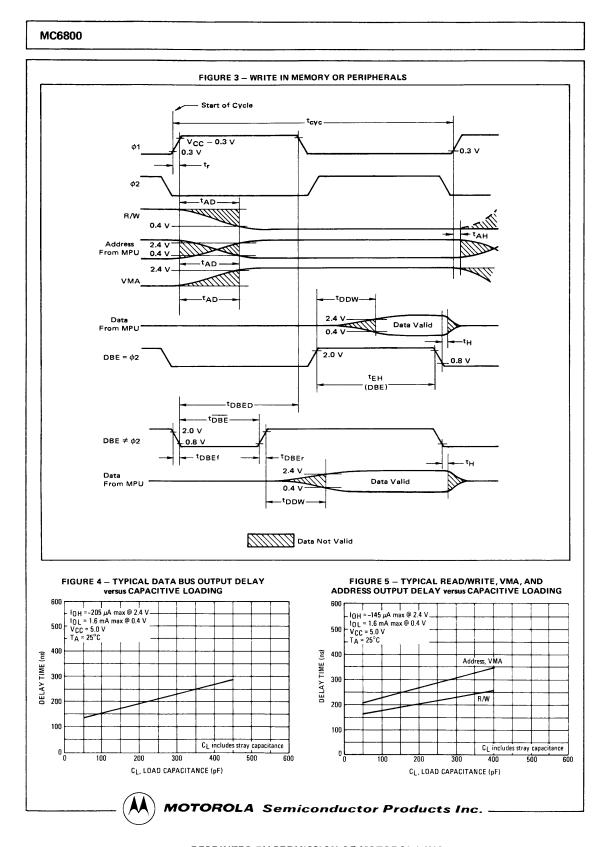

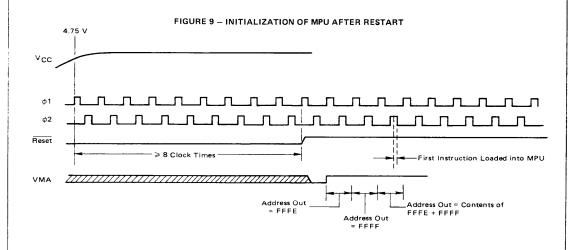

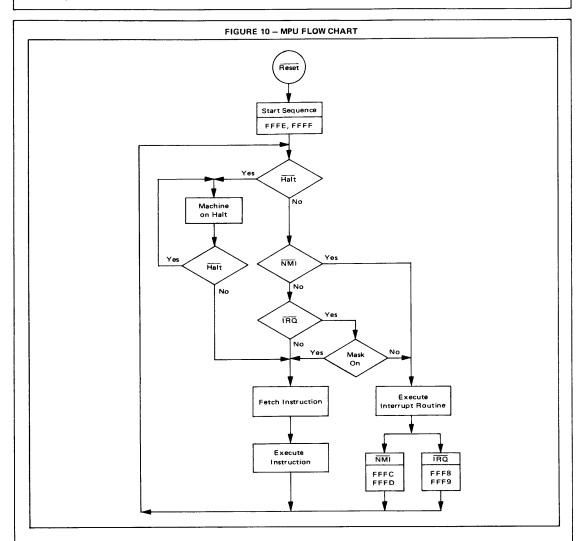

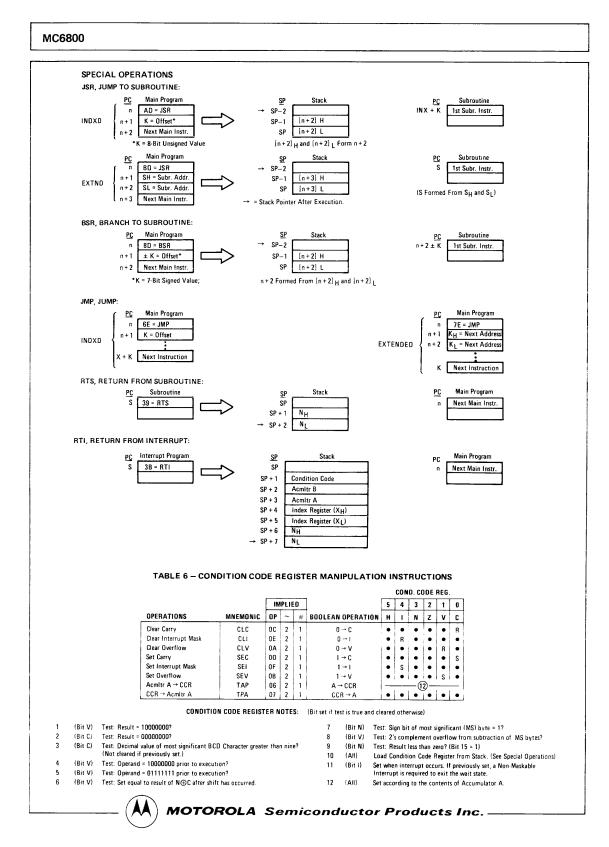

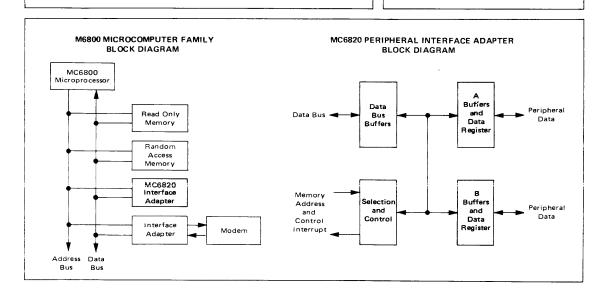

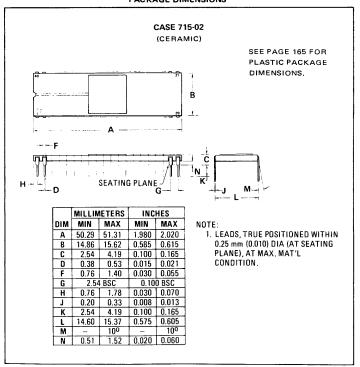

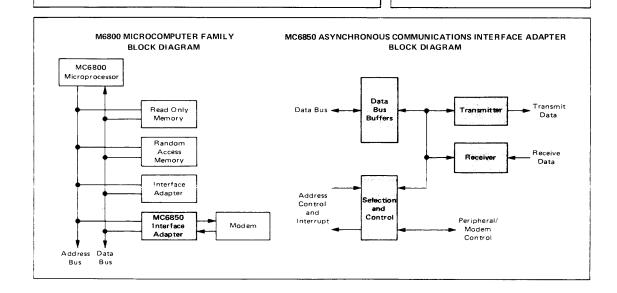

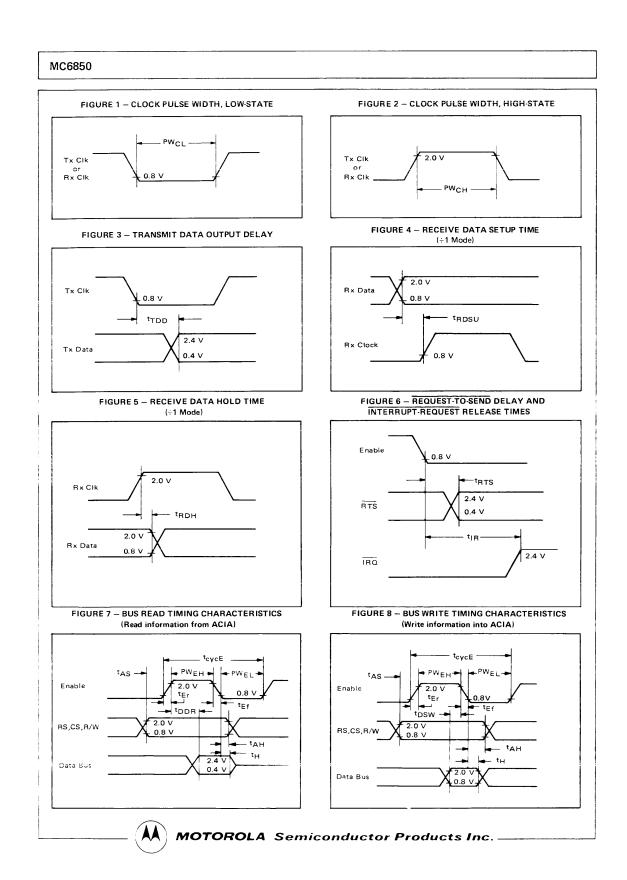

# MICROPROCESSOR SYSTEM SPECIFICATIONS MOTOROLA DEVICES

The 4051 Graphic System is based on a Motorola 6800 microcomputer system. Specific system building blocks are listed in Table 2-2.

Table 2-2

| SYSTEM BUILDING BLOCKS                               |          |                                                                                                                                                           |  |  |

|------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Microprocessing Unit (MPU)                           | MC6800   | Used as mainframe central processing unit.                                                                                                                |  |  |

| Peripheral Interface<br>Adapter (PIA)                | MC6820   | Used as peripheral device controllers (i.e., tape control, keyboard control, display control, joystick control, GPIB controls, Bank Switch control, etc.) |  |  |

| Asynchronous Communications Interface Adapter (ACIA) | MC6850   | Used for RS-232 communications interface.                                                                                                                 |  |  |

| Read Only Memory (ROM)                               | MCM6832L | Mask programmable ROM used in all 4051 firmware and firmware products.                                                                                    |  |  |

| Random Access Memory RAM)                            | MCM6605L | Dynamic Random Access Memory used for temporary program and data storage within the 4051 mainframe.                                                       |  |  |

For detailed specifications on each of these devices, see the appendix that incorporates reprinted Motorola specification sheets.

#### **MEMORY (ROM and Peripheral Devices)**

36K bytes for firmware and peripheral control addresses. Included are 8K bytes for a switchable firmware bank.

#### **MEMORY (RAM for Program and Data Storage)**

8K bytes minimum (2K of which are used by system tables). Additional 8K byte increments may be added up to a maximum address space of 32K.

#### **MEMORY ADDRESS ALLOCATION**

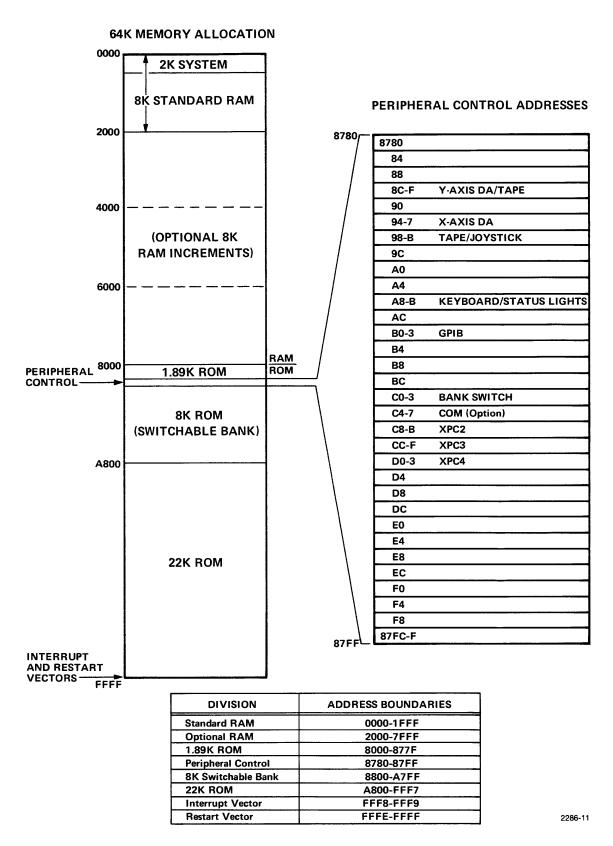

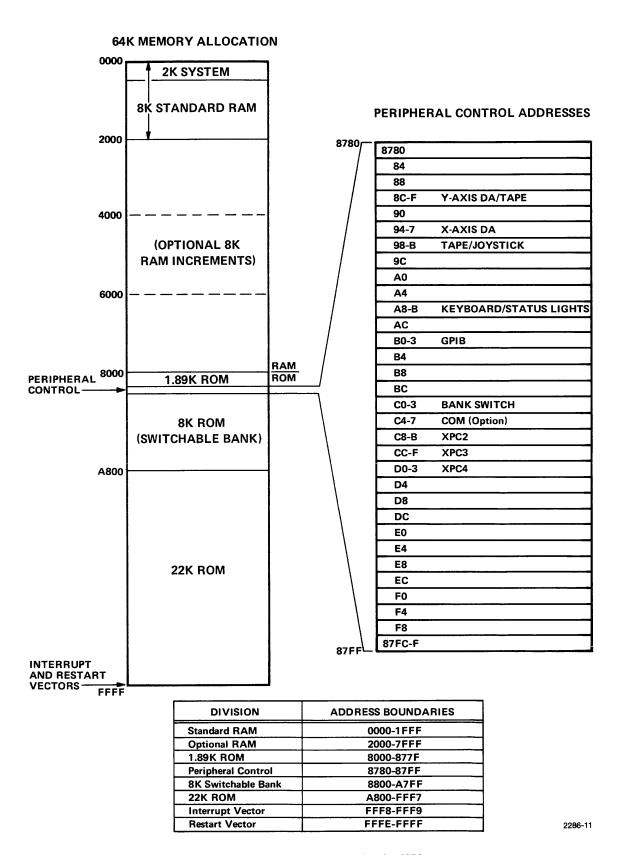

Figure 2-10 is a map of the 4051 memory address space. The total address space comprises 64K memory locations. The lower 32K is reserved for random access memory (RAM). The upper 32K is predominently read only memory (ROM) with a few addresses reserved for interfaces, most of which are peripheral interface adapters (PIAs).

Fig. 2-10. 4051 Memory address space allocation map.

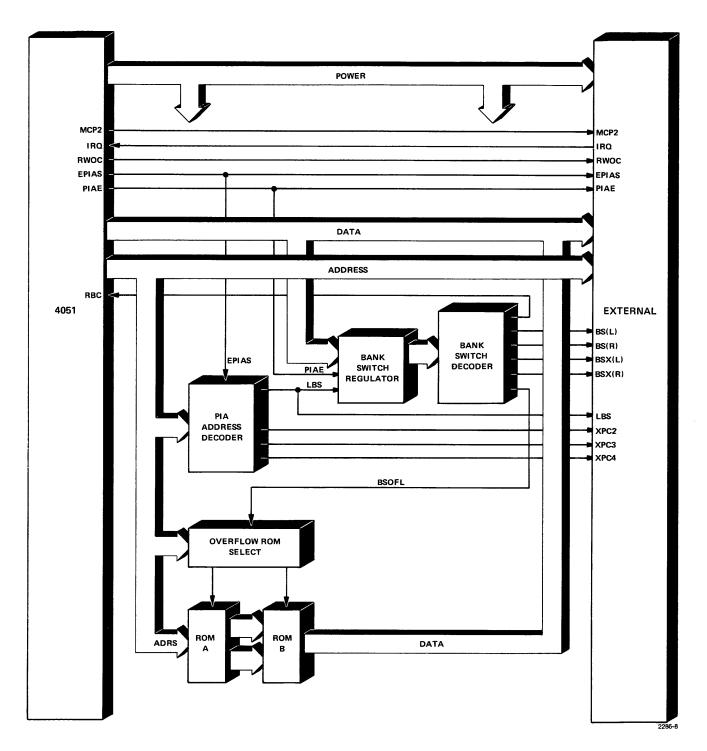

#### **BANK SWITCH**

Of the ROM addresses available to the 4051, there is a bank of 8K that is switch selectable. The particular 8K bank that is selected to reside in the switchable address space is determined by data stored in a bank switch register. Table 2-3 shows the meaning of the 8-bit data to be stored into the bank switch register or memory location. The letter X defines a don't care condition. The letter D defines ROM Expander Unit data.

Table 2-3

BANK SWITCH DATA WORD

| 76 | 543 | 210 |                                                        |

|----|-----|-----|--------------------------------------------------------|

| XX | 000 | XXX | RBC (ROM Bank Control)                                 |

| XX | 001 | XXX | BSOFL (Bank Switch Overflow—Select Overflow ROMs)      |

| XX | 010 | XXX | BSCOM (Bank Switch Communication—Select Communi-       |

|    |     |     | cation ROM)                                            |

| XX | 011 | XXX | _                                                      |

| XX | 100 | XXX | BS(L) (Bank Switch Left—Select Left ROM Pack)          |

| XX | 101 | XXX | BS(R) (Bank Switch Right—Select Right ROM Pack)        |

| XX | 110 | DDD | BSX(L) (Bank Switch Expander—Select Left ROM Expander  |

|    |     |     | Unit)                                                  |

| XX | 111 | DDD | BSX(R) (Bank Switch Expander—Select Right ROM Expander |

|    |     |     | Unit)                                                  |

DDD = ROM EXPANDER SLOT ADDRESS

# **BASIC LANGUAGE FORMAT**

(Line Number) KEYWORD  $\binom{\%}{@}$  (I/O Addresses:)

### LINE NUMBER

The line number determines the order of statement execution. If a line number is present, the statement is executed when the system is placed under program control. If the line number is not present, the statement is executed as soon as the statement is entered into the line buffer and the RETURN key is pressed.

### **KEYWORD**

The KEYWORD is an alphabetical code that tells the BASIC interpreter what function to perform. This code represents a set of instructions for the BASIC interpreter only and is never seen by the peripheral device involved in the transfer. A list of operations for each BASIC keyword can be found in the 4051 Graphic System Reference Manual.

### I/O ADDRESS

The I/O address is a two-part numeric code that presents instructions to the peripheral device. The I/O address is sent to the peripheral device before the data transfer begins.

The I/O address follows the keyword in the statement and is specified as an "at" sign (@) or a percent sign (%), followed by a primary address, followed by a comma, followed by a secondary address, and terminated with a colon (:).

The "at" sign (@) or the percent sign (%) specifies which delimiters are to be used during the I/O operation. Some applications involving GPIB input/output operations use the percent sign (%) to logically disconnect the 4051 from the GPIB. Refer to the 4051 Graphic System Reference Manual for details.

The primary address is specified as a peripheral device number between 1 and 255. When the statement is executed, the peripheral device number is converted to a primary talk address or a primary listen address, whichever is appropriate for the keyword, and issued to the specified peripheral device. The primary address tells the peripheral device that it has been selected to either send data to or receive data from the random access memory. Peripheral device numbers for the system are divided into categories as shown in Table 2-4.

Table 2-4

DEVICE NUMBER ASSIGNMENTS

| Device Number | Peripheral Device  System Disc (mass storage device)                           |  |  |

|---------------|--------------------------------------------------------------------------------|--|--|

| 0             |                                                                                |  |  |

| 1-30          | External peripheral devices on the<br>General Purpose Interface Bus            |  |  |

| 31-39         | Internal peripheral devices connected directly to the microprocessor bus lines |  |  |

| 40-255        | Reserved for future use                                                        |  |  |

Internal peripheral devices are preassigned the following peripheral device numbers:

Table 2-5

INTERNAL DEVICE NUMBERS

| Device Number | Peripheral Device  |

|---------------|--------------------|

| 31            | GS keyboard        |

| 32            | GS display         |

| 33            | Magnetic Tape Unit |

| 34            | DATA Statement     |

| 35            | Unassigned         |

| 36            | Unassigned         |

| 37            | Processor Status   |

| 38            | Unassigned         |

| 39            | Unassigned         |

Peripheral device numbers can be specified as a numeric expression in a statement as long as the BASIC interpreter can reduce the expression to a numeric constant and round the constant to an integer within the range 1 to 255. This means that the primary address can be specified as a numeric variable; by changing the value assigned to the variable, different peripheral devices can be selected as the input source or output destination without changing the BASIC statement itself.

The secondary address in an I/O address is issued immediately after the primary address and tells the peripheral device what the data transfer is all about. Since the peripheral device never sees the keyword in the statement, the secondary address provides the only way to tell the peripheral device what function is being performed by the BASIC interpreter. A secondary address is specified as a number from 0 through 32. Each number has a predefined meaning. For example, secondary address 12 means that the BASIC interpreter is executing a PRINT statement; secondary address 13 means that the BASIC interpreter is executing an INPUT statement, and secondary address 0 means that the BASIC interpreter is sending status information. The following table lists the secondary address assignments for each I/O function performed by the BASIC interpreter.

Table 2-6

GPIB PRIMARY DEVICE ADDRESS ASSIGNMENTS

| PERIPHERAL      | PRIMARY LISTEN ADDRESS |               |     | PRIMARY TALK ADDRESS |                 |  |  |  |  |  |

|-----------------|------------------------|---------------|-----|----------------------|-----------------|--|--|--|--|--|

| DEVICE          | DECIMAL DIO BUS        |               |     | DECIMAL              | DIO BUS         |  |  |  |  |  |

|                 | VALUE                  |               |     | VALUE                |                 |  |  |  |  |  |

|                 |                        | 8 7 6 5 4 3 2 | 2 1 |                      | 8 7 6 5 4 3 2 1 |  |  |  |  |  |

| Device 0        | 32                     | 0 0 1 0 0 0 0 | 0 0 | 64                   | 0 1 0 0 0 0 0 0 |  |  |  |  |  |

| Device 1        | 33                     | 001000        | 1   | 65                   | 0 1 0 0 0 0 0 1 |  |  |  |  |  |

| Device 2        | 34                     | 001000        | 1 0 | 66                   | 0 1 0 0 0 0 1 0 |  |  |  |  |  |

| Device 3        | 35                     | 001000        | 1 1 | 67                   | 0 1 0 0 0 0 1 1 |  |  |  |  |  |

| Device 4        | 36                     | 001001        | 0 0 | 68                   | 0 1 0 0 0 1 0 0 |  |  |  |  |  |

| Device 5        | 37                     | 001001        | ) 1 | 69                   | 0 1 0 0 0 1 0 1 |  |  |  |  |  |

| Device 6        | 39                     | 0 0 1 0 0 1   | 1 0 | 70                   | 0 1 0 0 0 1 1 0 |  |  |  |  |  |

| Device 7        | 39                     | 0 0 1 0 0 1   | 1   | 71                   | 0 1 0 0 0 1 1 1 |  |  |  |  |  |

| Device 8        | 40                     | 001010        | 0 0 | 72                   | 0 1 0 0 1 0 0 0 |  |  |  |  |  |

| Device 9        | 41                     | 001010        | ) 1 | 73                   | 0 1 0 0 1 0 0 1 |  |  |  |  |  |

| Device 10       | 42                     | 001010        | 1 0 | 74                   | 0 1 0 0 1 0 1 0 |  |  |  |  |  |

| Device 11       | 43                     | 0 0 1 0 1 0   | 1 1 | 75                   | 0 1 0 0 1 0 1 1 |  |  |  |  |  |

| Device 12       | 44                     | 0 0 1 0 1 1 ( | 0 0 | 76                   | 0 1 0 0 1 1 0 0 |  |  |  |  |  |

| Device 13       | 45                     | 001011        | ) 1 | 77                   | 0 1 0 0 1 1 0 1 |  |  |  |  |  |

| Device 14       | 46                     | 001011        | 1 0 | 78                   | 0 1 0 0 1 1 1 0 |  |  |  |  |  |

| Device 15       | 47                     | 0 0 1 0 1 1   | 1 1 | 79                   | 0 1 0 0 1 1 1 1 |  |  |  |  |  |

| Device 16       | 48                     | 001100        | 0 0 | 80                   | 0 1 0 1 0 0 0 0 |  |  |  |  |  |

| Device 17       | 49                     | 001100        | ) 1 | 81                   | 0 1 0 1 0 0 0 1 |  |  |  |  |  |

| Device 18       | 50                     | 0 0 1 1 0 0   | 1 0 | 82                   | 0 1 0 1 0 0 1 0 |  |  |  |  |  |

| Device 19       | 51                     | 0 0 1 1 0 0   | 1 1 | 83                   | 0 1 0 1 0 0 1 1 |  |  |  |  |  |

| Device 20       | 52                     | 001101        | 0 0 | 84                   | 0 1 0 1 0 1 0 0 |  |  |  |  |  |

| Device 21       | 53                     | 001101        | ) 1 | 85                   | 0 1 0 1 0 1 0 1 |  |  |  |  |  |

| Device 22       | 54                     | 0 0 1 1 0 1   | 1 0 | 86                   | 0 1 0 1 0 1 1 0 |  |  |  |  |  |

| Device 23       | 55                     | 0 0 1 1 0 1   | 1 1 | 87                   | 01010111        |  |  |  |  |  |

| Device 24       | 56                     | 0 0 1 1 1 0   | 0 0 | 88                   | 0 1 0 1 1 0 0 0 |  |  |  |  |  |

| Device 25       | 57                     | 0 0 1 1 1 0   | ) 1 | 89                   | 0 1 0 1 1 0 0 1 |  |  |  |  |  |

| Device 26       | 58                     | 0 0 1 1 1 0   | 1 0 | 90                   | 0 1 0 1 1 0 1 0 |  |  |  |  |  |

| Device 27       | 59                     | 0 0 1 1 1 0   | 1 1 | 91                   | 0 1 0 1 1 0 1 1 |  |  |  |  |  |

| Device 28       | 60                     | 0 0 1 1 1 1 ( | 0 0 | 92                   | 0 1 0 1 1 1 0 0 |  |  |  |  |  |

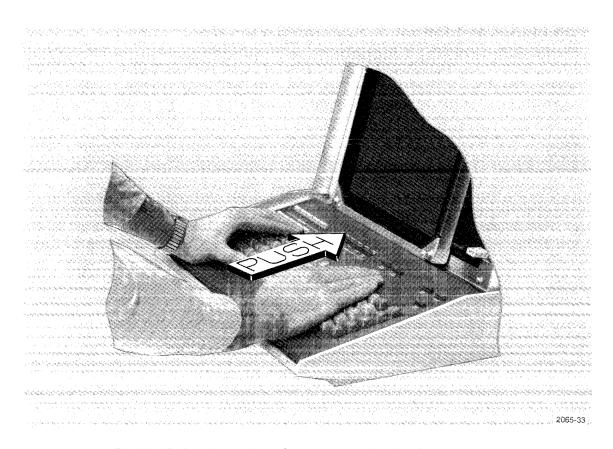

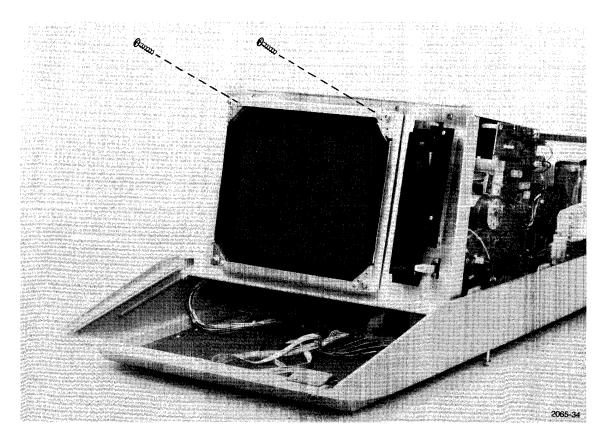

| Device 29       | 61                     | 0 0 1 1 1 1   | ) 1 | 93                   | 0 1 0 1 1 1 0 1 |  |  |  |  |  |