# I ourth Annual Telesis User Group Meeting

**Technical Proceedings**

Making Technology Work for You October 1986

# FOURTH ANNUAL INTERNATIONAL TELESIS USER GROUP MEETING

#### PROCEEDINGS

| CC | ONTENTS                                                                                          | P | PAGE |

|----|--------------------------------------------------------------------------------------------------|---|------|

| GI | ENERAL INFORMATION                                                                               | • | I    |

| US | SER CAUCUSES                                                                                     | • | II   |

| s: | YSTEM MANAGEMENT                                                                                 |   |      |

| Ф  | Monitoring CAD System Performance Mike Hayden, Broadcast Electronics                             | • | 1    |

| Ф  | Justifying Capital Equipment Expenditures Linda Stegall, Scan Optics                             | • | 11   |

| Ф  | Effective Communication for System Implementation Arn Buck, Transcom Electronics                 | • | 29   |

| •  | Space Requirements for Hard Disk, Floppy Disk, and Magnetic Tape Media Bob Rough, Owens-Illinois | • | 39   |

| C  | OMPUTER-AIDED ENGINEERING                                                                        |   |      |

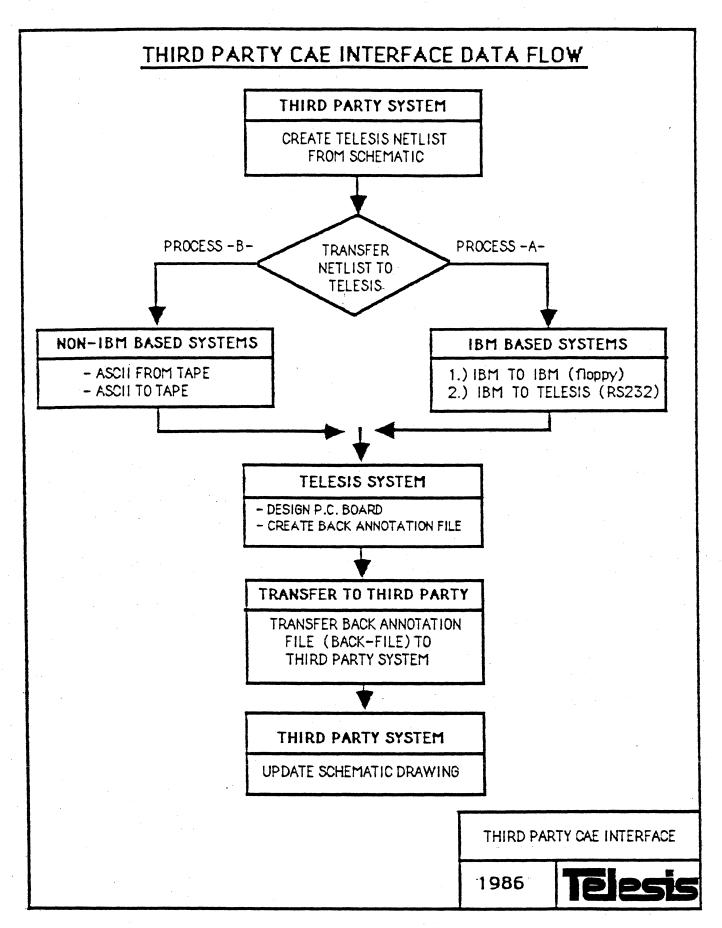

| •  | Telesis Third Party CAE Interface Frank Boyle, Telesis Systems Corporation                       | • | 65   |

| •  | Introduction to Simulation Kyle Krauss, Telesis Systems Corporation                              | • | 113  |

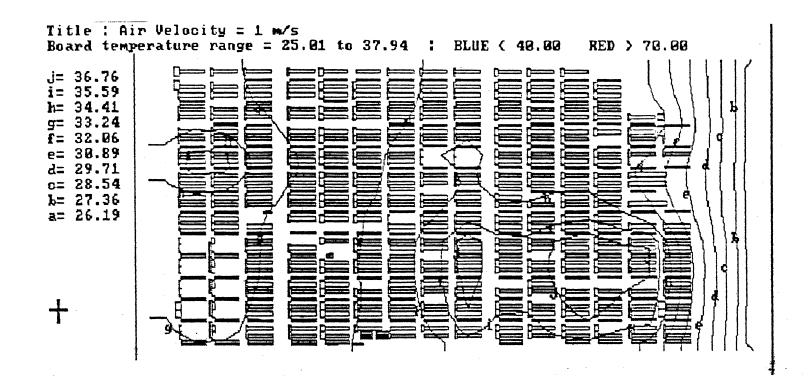

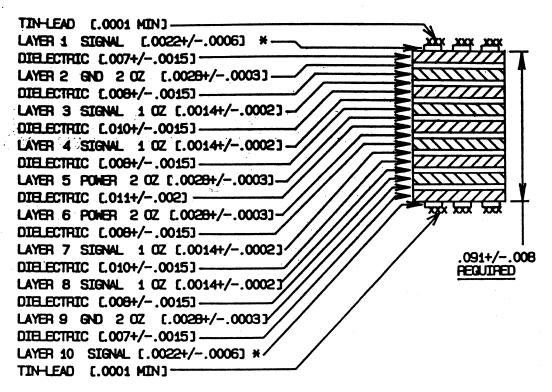

| •  | Thermal Analysis Kyle Krauss, Telesis Systems Corporation John Vagrin, AT & T                    | • | 123  |

| •  | Glossary of Simulation Terms Telesis Systems Corporation                                         |   | 133  |

#### DESIGN APPLICATIONS

| <b>(</b>     | Analog Design Kevin Sedlak, Telesis Systems Corporation                                                  | N/A |

|--------------|----------------------------------------------------------------------------------------------------------|-----|

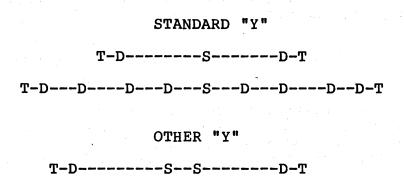

| Ф            | ECL Rules Management Buck Titherington, Scientific Computer Systems                                      | 139 |

| Ф            | Using Automatic Terminator Assignment Paul Gillis, Telesis Systems Corporation                           | 151 |

| •            | Flex Circuits Joanne Vigil, Miniscribe                                                                   | 161 |

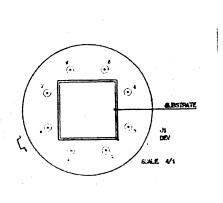

| Ф            | Generating Artwork for Special Applications Penelope Le Vario, Micro-Rel                                 | 165 |

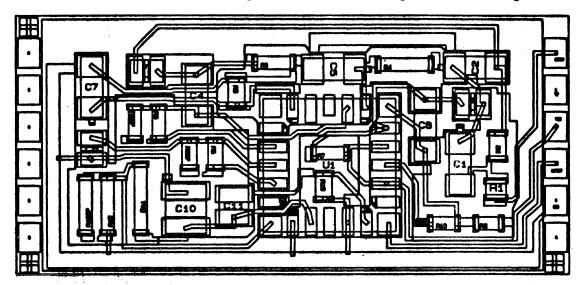

| Ф            | Hybrids Kim Patterson, National Semiconductor                                                            | 175 |

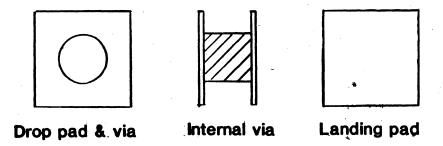

| <b>&amp;</b> | SMT Considerations for the Telesis System Don DiMatteo, Telesis Systems Corporation                      | 179 |

| <b>(</b>     | Care Package for SMT Arn Buck, Transcom Electronics                                                      | 187 |

| <b>•</b>     | Advanced Design Capture on the EDA-1000 Carmen Serna, Larse Corporation                                  | 199 |

| •            | Comparing the EDA-1200 with Dash IV Tom Miller, Telesis Systems Corporation                              | 229 |

| •            | Basic Steps for PC Board Design Debbie Carrier, Telesis Systems Corporation                              | 235 |

| <b>&amp;</b> | Glossary of PC Board Design Charles Powderly, Telesis Systems Corporation                                | 243 |

| SI           | PECIAL APPLICATIONS & TECHNOLOGIES                                                                       |     |

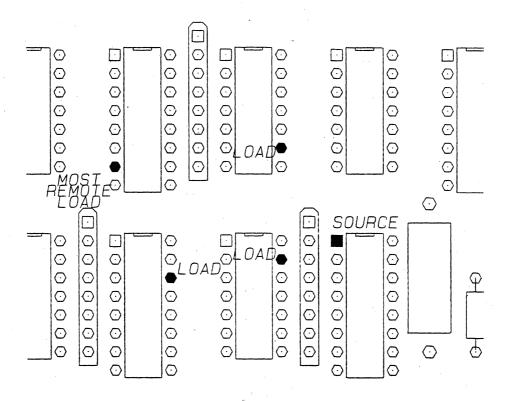

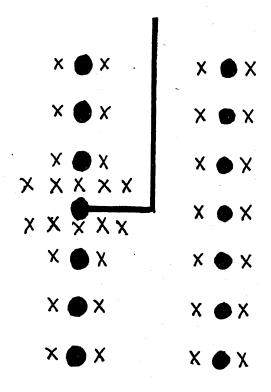

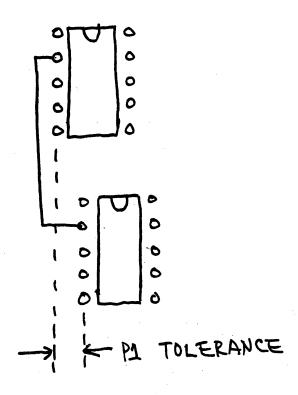

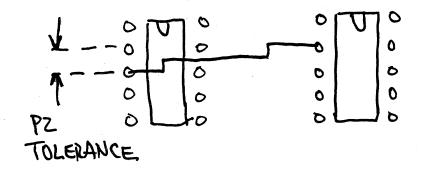

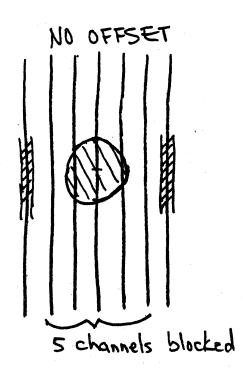

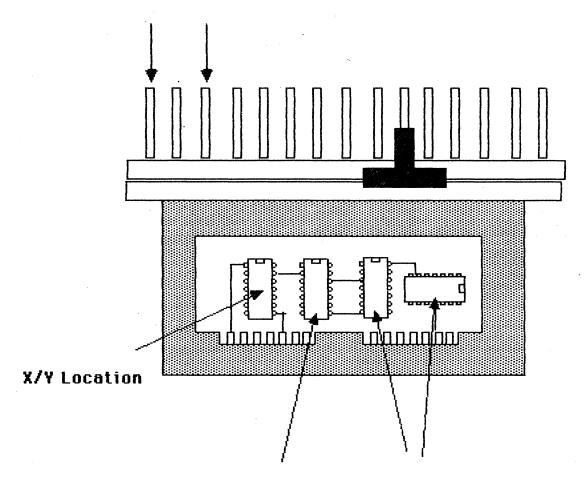

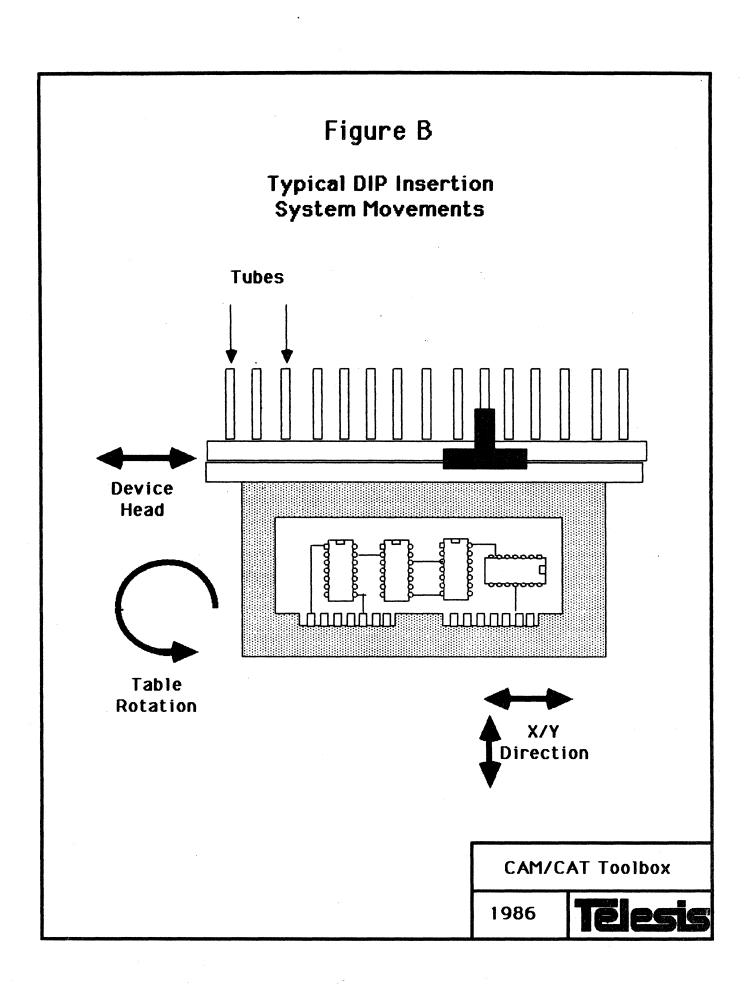

| Ф            | Automatic Placement Garrett Cavanaugh, Telesis Systems Corporation                                       | 255 |

| •            | Telesis Placement Improvement Using Function Swap - Pin Swap Debbie Carrier, Telesis Systems Corporation | 265 |

| Ф            | New Router Features in 3.0 Roger Cleghorn, Telesis Systems Corporation                                   |     |

| •        | Bob Fisher, Telesis Systems Corporation                                                           | 291   |

|----------|---------------------------------------------------------------------------------------------------|-------|

| <b>•</b> | Multiple Router Executions<br>Roger Cleghorn, Telesis Systems Corporation                         | 3Ø1   |

| <b>(</b> | Corouter Testing Results Bobbi Smith, Gould/SEL                                                   | 309   |

| <b>Φ</b> | Advanced Text Editing Garrett Cavanaugh, Telesis Systems Corporation                              | 315   |

| Ф        | Creating the Net-Data-Base<br>Don Deily, Frank Boyle, Telesis Systems Corporation                 | 327   |

| Ф        | Device Files Don Deily, Telesis Systems Corporation                                               | 3 4 5 |

| <b>•</b> | EDA-1000 Symbols and Device Files Garrett Cavanaugh, Telesis Systems Corporation                  | 369   |

| •        | A History of Split Planes on the Telesis System Jay Kenney, Telesis Systems Corporation           | 3 83  |

| F:       | ILE MANAGEMENT AND NETWORKING                                                                     |       |

| •        | A Beginners Guide to Networking<br>Christina Runtagh, Telesis Systems Corporation                 | 401   |

| •        | File Management Using Wild Cards and All Files Option Debbie Carrier, Telesis Systems Corporation | 415   |

| Ф        | Archival Procedure Arn Buck, Transcom Electronics                                                 | 419   |

| •        | Increasing Productivity Through Better File Management Bonnie Persinger, Annapolis Micro Systems  | 445   |

| P        | DSTPROCESSING                                                                                     |       |

| <b>⊕</b> | Cad-to-Cam for Telesis Users                                                                      | 453   |

|          | Joe Prang, Telesis Systems Corporation                                                            | 453   |

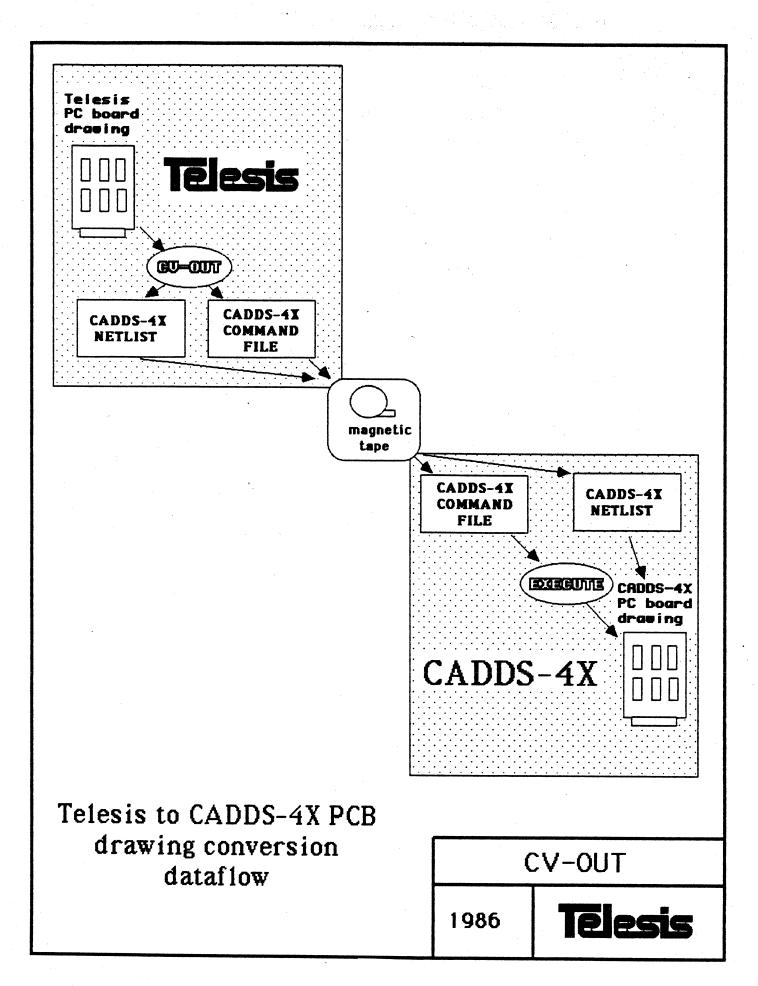

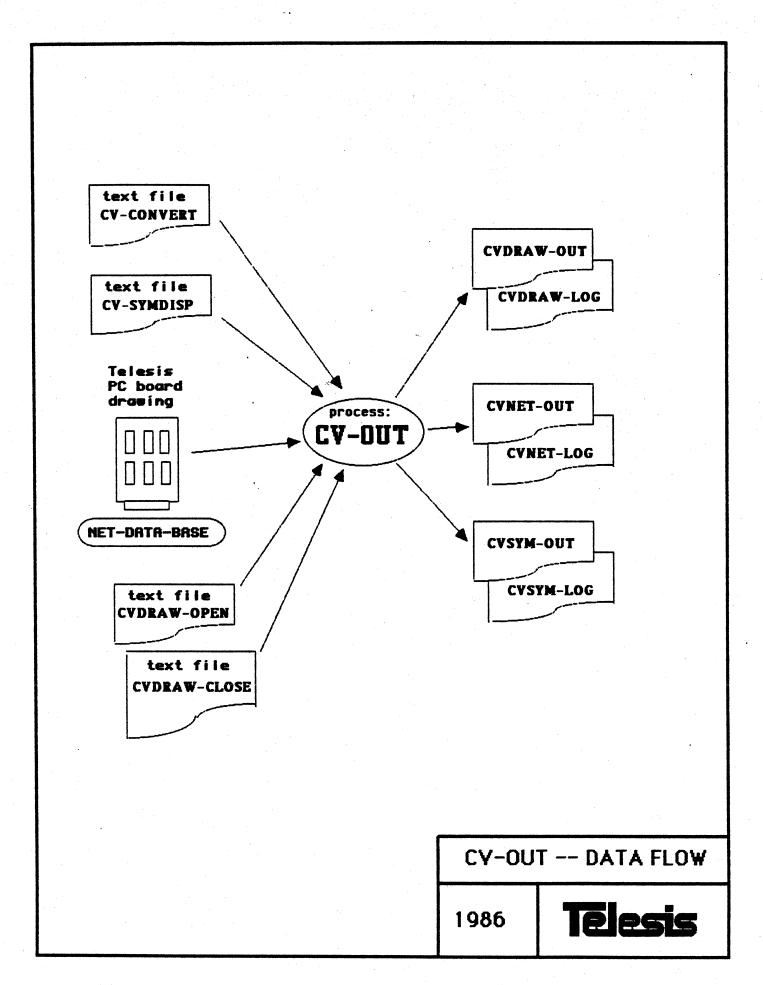

|  | OUT Telesis to CADDS/4X C<br>Deily, Telesis Systems C | ompatibility orporation | 507 |

|--|-------------------------------------------------------|-------------------------|-----|

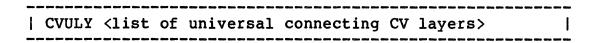

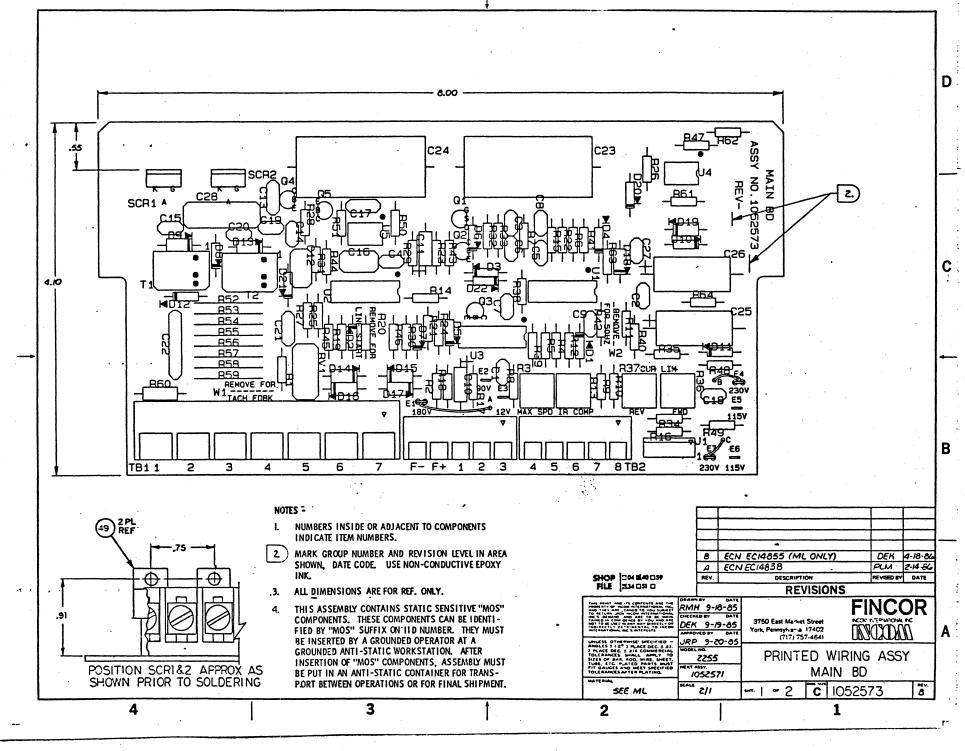

|  | Postprocessing Procedure<br>Zellers, Doug Kuhn, Finc  | or                      | 533 |

#### GENERAL INFORMATION

#### REGISTRATION & INFORMATION CENTER

HOURS: Tuesday, October 14 - Noon to 6 pm

Wednesday, October 15-7:00 am to 7:00 pm Thursday, October 16-7:00 am to 7:00 pm Friday, October 17-7:00 am to 2:00 pm

MESSAGES: A message board will be located near the Regis-

tration area. All calls, messages, and last minute schedule changes will be posted. Please

check the board on a regular basis.

BADGES: Attendees should wear their badges to all

scheduled events.

TRANSPORTATION: There is a limo service available to and from

the airport. There is also a bus that makes a loop through Disney World from the hotel -- you

will need your hotel pass for this free service.

CREDITS AND

DISCLAIMERS: Permission to reproduce these papers and

proceedings in part, or in full, with credit given to the author and references may be obtained by contacting Telesis Systems Corporation at 617/256-2300, Attention: Mr. Charlie

Powderly.

#### **USER CAUCUSES**

#### SESSION CHAIRPERSONS

#### EASTERN CHAPTER

- Arn Buck, Transcom Electronics

- Paul Gingras, Telesis Systems Corporation

#### MIDWEST CHAPTER

- Mike Gilman, Research, Inc.

- Charles Powderly, Telesis Systems Corporation

#### WESTERN CHAPTER

- Real Beaudette, Larse Corporation

- Garrett Cavanaugh, Telesis Systems Corporation

#### INTERNATIONAL USERS

- Daihachiro Kusunoki, Keihin Artwork & Company, Ltd.

- Paul Gingras, Telesis Systems Corporation

#### MONITORING CAD SYSTEM PERFORMANCE

Michael A. Hayden

Manager Engineering Services

Broadcast Electronics, Inc.

Quincy, Illinois

#### **ABSTRACT**

Cad system managers must assume many responsibilities to insure that their computer-aided design systems perform efficiently and productively. One of these responsibilities is monitoring system performance. The following paper provides the system manager with a method for accumulating, storing and retrieving data in a format that is use-ful for system performance evaluation.

#### INTRODUCTION

Communication between the system manager and the workstation operators is key in monitoring system performance. When a workstation crashes, the system manager needs to be informed of the sequence of events occurring prior to the crash. If too much time elapses between when the crash occurs, and when the system manager is informed, important details may be lost and go unreported.

The system manager must also have a means of tracking system performance problems. While some problems happen frequently enough to indicate that a trend is developing, other performance trends are not so obvious. This is where it becomes especially important for the system manager to have a tracking method in place.

The customer copies of the Telesis System Performance Reports are useful for tracking system performance, however, they are distributed monthly which hinders the ability to determine a possible trend developing.

In addition, unless the system manager has a way to pull system performance data together, the ability to evaluate overall system performance is hampered as well.

#### TWO-STEP APPROACH

In the two-step approach, the operator first records performance data as problems occur. Next, the system manager collects the data and formats it so that it's easily analyzed. This method allows the system manager to determine possible trends, and provide feedback to the system operators.

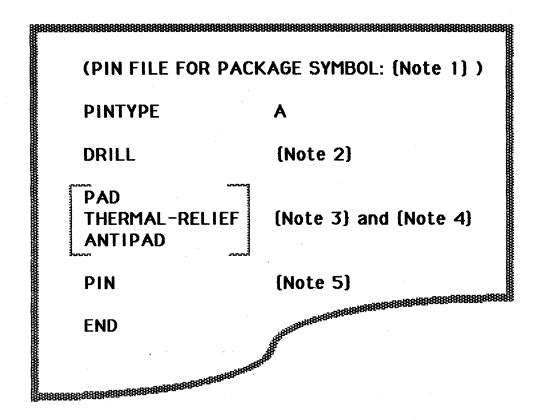

The first step is to provide the operator with a form to record all system performance information. Figure 1 illustrates a sample in-house performance report that may be customized to suit the particular needs of the user.

The upper left hand corner of the form contains information about each work-station. The information is itemized by workstation and includes the serial number, hardware revision, software revision, and software version. (This information is useful to have handy when contacting Telesis Customer Support). When filling out the report, the operator circles the applicable workstation number.

The report should be filled out as completely as possible and include the following items:

- 1. System operator

- Date and time

- 3. Active software (Mechanical Design, Printed Circuit, or Computer-Aided Engineering)

- 4. Project name and revision

- 5. Drawing or file name and revision

- 6. Nature of the problem (Software, Hardware, or Documentation). Note that the nature of the problem may not be known at the time a problem occurs. Once a solution has been found, it's important to remember to record the nature of the problem

- 7. Operation being performed (Draw Schematic, Draw Symbol, Design Board, or Other)

- 8. Last command used

- 9. Error message List any error messages displayed on the system or monitor

#### 10. Description of the problem

Once a solution or workaround has been found, the operator should describe this in the appropriate location on the form. Additionally, the operator should also indicate whether or not Telesis Customer Support was contacted and if so, record the event number from the system performance report.

Finally, there is an area near the bottom of the report for any notes that might be applicable. Once the report has been completed it is turned into the system manager.

In the second step, the system manager takes the individual reports and assembles them into a common database using a personal computer and a database management software package. There are several quality database management packages on the market, however, the one used to create the report summaries shown in this paper is REFLEX from Borland/Anayltica, Inc.

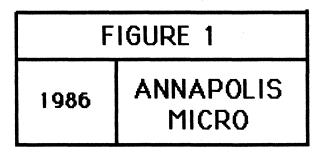

Figure 2 shows a summary of in-house reports over a six-month period. The type and amount of information entered into the database may vary depending on the needs of the individual user. In this case the following information was extracted from the in-house reports.

- 1. Date and time

- 2. Workstation serial number

- System operator

- 4. Active software

- 5. Nature of the problem

- 6. Project name

- 7. Drawing or file name

- 8. Last command used

- 9. Error message or description of the problem

- 10. Whether or not Telesis Customer Support was contacted

- 11. Event number from the Telesis System Performance Report

The REFLEX database management software used to generate this report can accomodate up to 128 field names and each field name can have a maximum of 70 characters. The form is designed to fit the user's needs and may be stored away as a "blank" form for future data input.

When the system manager receives the completed report from the operator, the appropriate details are input into the database management software using the "blank" form. Each completed form is then stored away in the software as a record. The records may be displayed individually using "form" view, or in their entirety using the software's "list", "graph", "crosstab", or "report" views.

Figures 2, 3A, 3B, 4A and 4B are all displayed using the "list" view. The data in the summary in Figure 2 was sorted by date and time. This is simply a chronological listing of reports received over a six-month period.

Figure 3A shows the same data sorted by workstation number. Here the number of reports per workstation during the six-month period are evenly split. It can also be noted that workstation number two had four problems in one month, all on the same project.

In Figure 3B, the data was sorted by the nature of the problem. In this instance, the greatest number of problems were software in nature. Further sorting by error message and problem description was done in Figure 4A. This information indicates that there was a three-time occurrence of the same error message during the six-month period. In addition, the error message occurred on both systems.

A sort by project name and drawing or file name was performed in Figure 4B. As shown in Figure 3A, one project had four problems in one month.

#### CONCLUSION

While filling out the in-house performance report and logging the information into a common database doesn't require a great deal of time, the benefits derived from this process are endless. One such example would be the occurence of the error message "SEND ERROR -2 TO TASK" three times in a six-month period. The reoccurence of the same error message, on different workstations, in more than one command sequence would indicate a trend. The system manager should call attention to this by contacting the Telesis Customer Support personnel.

The ideal situation would be to have a system that would always perform perfectly. However, this isn't the case with any computer-aided design systems in ther real world. There will always be hardware and software problems, but system managers owe it to themselves and to those working for them to be knowledgeable of how well their systems are performing. Using an in-house performance report and database management software is one way of accomplishing this goal.

# TELESIS SYSTEM IN-HOUSE PERFORMANCE REPORT

| WORKSTATION NO. (CIRCLE)<br>SERIAL NO. 1 | 1 2<br>447 1349             | SYSTEM OPERATOR  | DATE         |

|------------------------------------------|-----------------------------|------------------|--------------|

| HARDWARE REV                             | 2.1 2.1                     |                  | TIME P.M.    |

| SOFTWARE REV<br>VERSION: EDA 3000 2      | G I<br>2.1 2.1              | ACTIVE SOF       |              |

| EDA 3100 2                               | 2.1 2.1<br>2.1 2.1<br>1.1 — | MD PC            | CAE          |

| PROJECT NAME / REV                       |                             | NATURE OF PROBLE |              |

| /                                        | SOFTWARE                    | HARDWARE D       | OCUMENTATION |

| DWG OR FILE NAME / REV                   | DRAW S                      | YM DRAW SCH      | DESIGN BD    |

| /                                        | OTHER [                     |                  |              |

| LAST COMMANDS USED                       | ERROR MES                   | SSAGE            |              |

| LAST:                                    |                             |                  |              |

| NEXT:                                    |                             |                  |              |

| NEXT:                                    |                             |                  | •            |

| NEXT:                                    |                             |                  |              |

|                                          |                             | ·                |              |

| DESCRIPTION OF PROBLEM                   |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

| SOLUTION/WORK AROUND                     |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

| ·                                        |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

| TELESIS CUSTOMER SUPPORT                 |                             | P YES NO         |              |

| TELESIS COSTOMER SOPPORT                 |                             |                  |              |

| NOTES                                    | L NEPUNI E                  | VLINI INU.       |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          |                             |                  |              |

|                                          | -6                          |                  |              |

|                                          |                             | <u> </u>         |              |

BROADCAST ELECTRONICS, INC.

TELESIS SYSTEM IN-HOUSE PERFORMANCE REPORT SUMMARY

|   | DATE     | TIME  | WKSTA | OPERATOR | SFTWR | NATofPROB | PROJECT NAME | DWGorFILE NAME | Last Command USED       | ERROR MESSAGEorDESCofPROB       | TCS? | EVENT# |

|---|----------|-------|-------|----------|-------|-----------|--------------|----------------|-------------------------|---------------------------------|------|--------|

|   |          |       |       |          |       |           |              |                |                         |                                 |      |        |

|   | 1/14/86  | 11:00 | 1     | MJ       | PC    | SFTWR     | 917-0065     | SCH            | EXTRACT NETLIST         | DEVICE FILE PROBLEM             | Y    | 522    |

|   | 2/07/86  | 2:45  | 2     | MICHELE  | PC    | SFTWR     | 917-0063     | PIN FILE       | CANCEL ACTIVE FILE      | SEND ERROR -2 TO TASK           | Y    | 1078   |

|   | 2/11/86  | 11:10 | 1     | MJ       | PC    | SFTWR     | 917-0064     | SCH            | EXTRACT NETLIST         | DUPLICATE REF DES ON 3 SHT SCH  | Y    | 1121   |

|   | .2/19/86 | 10:50 | 2     | MICHELE  | PC    | SFTWR     | 917-0063     | PCB            | RELOCATE DRAWING ORIGIN | PASCAL MULTIPLE ERRORS DETECTED | Y    | 1802   |

|   | 2/28/86  | 8:34  | 2     | MICHELE  | PC    | SFTWR     | 917-0063     | PCB            | DEASSIGN REF DES        | SYSTEM READS OLD CAPACITOR      | Y    | 1440   |

|   | 3/03/86  | 4:30  | 2     | MICHELE  | PC    | HDWR      | 917-0063     | PCB            | NA                      | RAN DUTOFSPACEONHARD DISK       | Y    | 1491   |

| Ĩ | 3/12/86  | 2:30  | 1     | MICHELE  | PC    | SFTWR     | 917-0065     | PCB            | COMPRESS DRAWING        | DATA BASE ERRORS DETECTED       | Y    | 1673   |

|   | 3/24/86  | 8:30  | . 1   | MIKE     | PC    | DOC       | NA           | NA             | NA                      | ?onDOC SENT w/FLOPPY PATCH      | Y    | 1882   |

|   | 4/04/86  | 4:02  | 2     | MIKE     | NA    | HDWR      | NA           | NA             | NA                      | TAPE DRIVE TAKEUP REEL BROKEN   | Y    | 3029   |

|   | 4/23/86  | 3:05  | 1     | MICHELE  | PC    | SFTWR     | 916-0006     | TEXT FILE      | DELETE TEXT FILE        | SEND ERROR -2 TO TASK           | Y    | 3413   |

|   | 4/24/86  | 11:20 | 1     | MICHELE  | PC    | SFTWR     | 916-0006     | PCB            | SAVE DRW SAME RV        | SEND ERROR -2 TO TASK           | Y    | 3438   |

|   | 6/09/86  | 11:05 | 2     | MIKE     | PC    | SFTWR     | 910-0038     | PCB            | CREATE GROUP            | TASK "DISPLA" TERMINATED.       | Y    | 4184   |

|   | 6/11/86  | 11:15 | 2     | MIKE     | PC    | SFTWR     | 910-0038     | PCB            | UPDATE TEXT             | TASK "DISPLA" TERMINATED.       | Y    | 4257   |

|   | 7/07/86  | 11:20 | 1     | MICHELE  | PC    | DOC       | 911-0015     | SCH            | EXTRACT NETLIST         | PROGRAM ERROR IN EXTRACTION-LOG | γ    | 5105   |

|   |          |       |       |          |       |           |              |                |                         |                                 |      |        |

## å

# BROADCAST ELECTRONICS, INC. TELESIS SYSTEM IN-HOUSE PERFORMANCE REPORT SUMMARY

| WKSTA | DATE    | TIME  | OPERATOR | SFTWR | NATafPROB | PROJECT NAME | DWGorFILE NAME | LAST COMMAND USED       | ERROR MESSAGEorDESCofPROB       | TCS? | EVENT# |

|-------|---------|-------|----------|-------|-----------|--------------|----------------|-------------------------|---------------------------------|------|--------|

|       |         |       |          |       |           |              |                |                         |                                 |      |        |

| 1     | 1/14/86 | 11:00 | MJ       | PC    | SFTWR     | 917-0065     | SCH            | EXTRACT NETLIST         | DEVICE FILE PROBLEM             | Y    | 522    |

| 1     | 2/11/86 | 11:10 | MJ       | PC    | SFTWR     | 917-0064     | SCH            | EXTRACT NETLIST         | DUPLICATE REF DES ON 3 SHT SCH  | Y    | 1121   |

| 1     | 3/12/86 | 2:30  | MICHELE  | PC    | SFTWR     | 917-0065     | PCB            | COMPRESS DRAWING        | DATA BASE ERRORS DETECTED       | Y    | 1673   |

| 1     | 3/24/86 | 8:30  | MIKE     | PC    | DOC       | NA           | NA             | NA                      | ?onDOC SENT w/FLOPPY PATCH      | Y    | 1882   |

| 1     | 4/23/86 | 3:05  | MICHELE  | PC    | SFTWR     | 916-0006     | TEXT FILE      | DELETE TEXT FILE        | SEND ERROR -2 TO TASK           | Y    | 3413   |

| 1     | 4/24/86 | 11:20 | MICHELE  | PC    | SFTWR     | 916-0006     | PCB            | SAVE DRW SAME RV        | SEND ERROR -2 TO TASK           | Y    | 3438   |

| 1     | 7/07/86 | 11:20 | MICHELE  | PC    | DOC       | 911-0015     | SCH            | EXTRACT NETLIST         | PROGRAM ERROR IN EXTRACTION-LOG | Y    | 5105   |

| 2     | 2/07/86 | 2:45  | MICHELE  | PC    | SFTWR     | 917-0063     | PIN FILE       | CANCEL ACTIVE FILE .    | SEND ERROR -2 TO TASK           | Y    | 1078   |

| 2     | 2/19/86 | 10:50 | MICHELE  | PC    | SFTWR     | 917-0063     | PCB            | RELOCATE DRAWING ORIGIN | PASCAL MULTIPLE ERRORS DETECTED | Y    | 1802   |

| 2     | 2/28/86 | 8:34  | MICHELE  | PC    | SFTWR     | 917-0063     | PCB            | DEASSIGN REF DES        | SYSTEM READS OLD CAPACITOR      | Y    | 1440   |

| 2     | 3/03/86 | 4:30  | MICHELE  | PC    | HDWR      | 917-0063     | PCB            | NA                      | RAN OUTOFSPACEONHARD DISK       | Υ    | 1491   |

| 2     | 4/04/86 | 4:02  | MIKE     | NA    | HDWR      | NA           | NA             | NA                      | TAPE DRIVE TAKEUP REEL BROKEN   | Y    | 3029   |

| 2     | 6/09/86 | 11:05 | MIKE     | PC    | SFTWR     | 910-0038     | PCB            | CREATE GROUP            | TASK "DISPLA" TERMINATED.       | Y    | 4184   |

| 2     | 6/11/86 | 11:15 | MIKE     | PC    | SFTWR     | 910-0038     | PCB            | UPDATE TEXT             | TASK "DISPLA" TERMINATED.       | Y    | 4257   |

FIGURE 3A. IN-HOUSE PERFORMANCE REPORT SUMMARY SORTED BY WORKSTATION NUMBER

# BROADCAST ELECTRONICS, INC. TELESIS SYSTEM IN-HOUSE PERFORMANCE REPORT SUMMARY

| NAT@FPROB | WKSTA | DATE    | TIME  | OPERATOR | SFTWR | PROJECT NAME | DWGorFILE NAME | LAST COMMAND USED       | ERROR MESSAGEonDESCofPROB       | TCS? | EVENT# |

|-----------|-------|---------|-------|----------|-------|--------------|----------------|-------------------------|---------------------------------|------|--------|

| DOC       | 1     | 3/24/86 | 8:30  | MIKE     | PC    | NA           | NA             | NA                      | ?onDOC SENT w/FLOPPY PATCH      | Y    | 1882   |

| DOC       | 1     | 7/07/86 | 11:20 | MICHELE  | PC    | 911-0015     | SCH            | EXTRACT NETLIST         | PROGRAM ERROR IN EXTRACTION-LOG | Y    | 5105   |

| HDWR      | 2     | 3/03/86 | 4:30  | MICHELE  | PC    | 917-0063     | PCB            | NA                      | RAN DUTOFSPACEONHARD DISK       | Y    | 1491   |

| HDWR      | 2     | 4/04/86 | 4:02  | MIKE     | NA    | NA           | NA             | NA                      | TAPE DRIVE TAKEUP REEL BROKEN   | Y    | 3029   |

| SFTWR     | 1     | 1/14/86 | 11:00 | MJ       | PC    | 917-0065     | SCH            | EXTRACT NETLIST         | DEVICE FILE PROBLEM             | Y    | 522    |

| SFTWR     | 1     | 2/11/86 | 11:10 | MJ       | PC    | 917-0064     | SCH            | EXTRACT NETLIST         | DUPLICATE REF DES ON 3 SHT SCH  | Y    | 1121   |

| SFTWR     | 1     | 3/12/86 | 2:30  | MICHELE  | PC    | 917-0065     | PCB            | COMPRESS DRAWING        | DATA BASE ERRORS DETECTED       | Y    | 1673   |

| SFTWR     | 1     | 4/23/86 | 3:05  | MICHELE  | PC    | 916-0006     | TEXT FILE      | DELETE TEXT FILE        | send error -2 to task           | Y    | 3413   |

| SFTWR     | 1     | 4/24/86 | 11:20 | MICHELE  | PC    | 916-0006     | PCB            | SAVE DRW SAME RV        | SEND ERROR -2 TO TASK           | Y    | 3438   |

| SFTWR     | 2     | 2/07/86 | 2:45  | MICHELE  | PC    | 917-0063     | PIN FILE       | CANCEL ACTIVE FILE      | send error -2 to task           | Y    | 1078   |

| SFTWR     | 2     | 2/19/86 | 10:50 | MICHELE  | PC    | 917-0063     | PCB            | RELOCATE DRAWING ORIGIN | PASCAL MULTIPLE ERRORS DETECTED | Y    | 1802   |

| SFTWR     | 2     | 2/28/86 | 8:34  | MICHELE  | PC    | 917-0063     | PCB            | DEASSIGN REF DES        | SYSTEM READS OLD CAPACITOR      | Y    | 1440   |

| SFTWR     | 2     | 6/09/86 | 11:05 | MIKE     | PC    | 910-0038     | PCB            | CREATE GROUP            | TASK "DISPLA" TERMINATED.       | Y    | 4184   |

| SFTWR     | 2     | 6/11/86 | 11:15 | MIKE     | PC    | 910-0038     | PCB            | UPDATE TEXT             | TASK "DISPLA" TERMINATED.       | Y    | 4257   |

#### -9-

# BROADCAST ELECTRONICS, INC. TELESIS SYSTEM IN-HOUSE PERFORMANCE REPORT SUMMARY

| ERROR MESSAGEorDESCofPROB       | WKSTA | DATE    | TIME  | OPERATOR | SFTWR | NATofPROB | PROJECT NAME | DWGorFILE NAME | LAST COMMAND USED       | TCS? | EVENT# |

|---------------------------------|-------|---------|-------|----------|-------|-----------|--------------|----------------|-------------------------|------|--------|

|                                 |       |         |       |          |       |           |              |                |                         |      |        |

| ?onDOC SENT w/FLOPPY PATCH      | 1     | 3/24/86 | 8:30  | MIKE     | PC    | DOC       | NA           | NA             | NA                      | Y    | 1882   |

| DATA BASE ERRORS DETECTED       | 1     | 3/12/86 | 2:30  | MICHELE  | PC    | SFTWR     | 917-0065     | PCB            | COMPRESS DRAWING        | Y    | 1673   |

| DEVICE FILE PROBLEM             | 1     | 1/14/86 | 11:00 | MJ       | PC    | SFTWR     | 917-0065     | SCH            | EXTRACT NETLIST         | Y    | 522    |

| DUPLICATE REF DES ON 3 SHT SCH  | 1     | 2/11/86 | 11:10 | MJ       | PC    | SFTWR     | 917-0064     | SCH            | EXTRACT NETLIST         | Y    | 1121   |

| PASCAL MULTIPLE ERRORS DETECTED | 2     | 2/19/86 | 10:50 | MICHELE  | PC    | SFTWR     | 917-0063     | PCB            | RELOCATE DRAWING DRIGIN | Y    | 1802   |

| PROGRAM ERROR IN EXTRACTION-LOG | 1     | 7/07/86 | 11:20 | MICHELE  | PC    | DOC       | 911-0015     | SCH            | EXTRACT NETLIST         | Y    | 5105   |

| RAN OUTofSPACEonHARD DISK       | 2     | 3/03/86 | 4:30  | MICHELE  | PC    | HDWR      | 917-0063     | PCB            | NA                      | Y    | 1491   |

| SEND ERROR -2 TO TASK           | 1     | 4/23/86 | 3:05  | MICHELE  | PC    | SFTWR     | 916-0006     | TEXT FILE      | DELETE TEXT FILE        | Y    | 3413   |

| SEND ERROR -2 TO TASK           | 1     | 4/24/86 | 11:20 | MICHELE  | PC    | SFTWR     | 916-0006     | PCB            | SAVE DRW SAME RV        | Y    | 3438   |

| SEND ERROR -2 TO TASK           | 2     | 2/07/86 | 2:45  | MICHELE  | PC    | SFTWR     | 917-0063     | PIN FILE       | CANCEL ACTIVE FILE      | Y    | 1078   |

| SYSTEM READS OLD CAPACITOR      | 2     | 2/28/86 | 8:34  | MICHELE  | PC    | SFTWR     | 917-0063     | PCB            | DEASSIGN REF DES        | Y    | 1440   |

| TAPE DRIVE TAKEUP REEL BROKEN   | 2     | 4/04/86 | 4:02  | MIKE     | NA    | HDWR      | NA           | NA             | NA                      | Y    | 3029   |

| TASK "DISPLA" TERMINATED.       | 2     | 6/09/86 | 11:05 | MIKE     | PC    | SFTWR     | 910-0038     | PCB            | CREATE GROUP            | Y    | 4184   |

| TASK "DISPLA" TERMINATED.       | 2     | 6/11/86 | 11:15 | MIKE     | PC    | SFTWR     | 910-0038     | PCB            | UPDATE TEXT             | Y    | 4257   |

FIGURE 4A. IN-HOUSE PERFORMANCE REPORT SUMMARY SORTED BY ERROR MESSAGE

## BROADCAST ELECTRONICS, INC. TELESIS SYSTEM IN-HOUSE PERFORMANCE REPORT SUMMARY

| PROJECT NAME | DWGorFILE NAME | ERROR MESSAGEorDESCofPROB       | WKSTA | DATE    | TIME  | OPERATOR | SFTWR | NATofPROB     | LAST COMMAND USED       | TCS? | EVENT# |

|--------------|----------------|---------------------------------|-------|---------|-------|----------|-------|---------------|-------------------------|------|--------|

| 910-0038     | PCB            | TASK "DISPLA" TERMINATED.       | 2     | 6/09/86 | 11:05 | MIKE     | PC    | SFTWR         | CREATE GROUP            | Y    | 4184   |

| 910-0038     | PCB            | TASK "DISPLA" TERMINATED.       | 2     | 6/11/86 | 11:15 | MIKE     | PC    | SFTWR         | UPDATE TEXT             | Y    | 4257   |

| 911-0015     | SCH            | PROGRAM ERROR IN EXTRACTION-LOG | 1     | 7/07/86 | 11:20 | MICHELE  | PC    | DOC           | EXTRACT NETLIST         | Y    | 5105   |

| 916-0006     | PCB            | SEND ERROR -2 TO TASK           | 1     | 4/24/86 | 11:20 | MICHELE  | PC    | SFTWR         | SAVE DRW SAME RV        | Y    | 3438   |

| 916-0006     | TEXT FILE      | SEND ERROR -2 TO TASK           | 1     | 4/23/86 | 3:05  | MICHELE  | PC    | SFTWR         | DELETE TEXT FILE        | Y    | 3413   |

| 917-0063     | PCB            | PASCAL MULTIPLE ERRORS DETECTED | 2     | 2/19/86 | 10:50 | MICHELE  | PC    | SFTWR         | RELOCATE DRAWING ORIGIN | Y    | 1802   |

| 917-0063     | PCB            | RAN OUTOFSPACEONHARD DISK       | 2     | 3/03/86 | 4:30  | MICHELE  | PC    | HD <b>W</b> R | NA                      | Y    | 1491   |

| 917-0063     | PCB            | SYSTEM READS OLD CAPACITOR      | 2     | 2/28/86 | 8:34  | MICHELE  | PC    | SFTWR         | DEASSIGN REF DES        | Y    | 1440   |

| 917-0063     | PIN FILE       | SEND ERROR -2 TO TASK           | 2     | 2/07/86 | 2:45  | MICHELE  | PC    | SFTWR         | CANCEL ACTIVE FILE      | Y    | 1078   |

| 917-0064     | SCH            | DUPLICATE REF DES ON 3 SHT SCH  | 1     | 2/11/86 | 11:10 | MJ       | PC    | SFTWR         | EXTRACT NETLIST         | Y    | 1121   |

| 917-0065     | PCB            | DATA BASE ERRORS DETECTED       | 1     | 3/12/86 | 2:30  | MICHELE  | PC    | SFTWR         | COMPRESS DRAWING        | Y    | 1673   |

| 917-0065     | SCH            | DEVICE FILE PROBLEM             | 1     | 1/14/86 | 11:00 | MJ       | PC    | SFTWR         | EXTRACT NETLIST         | γ    | 522    |

| NA           | NA             | ?onDOC SENT w/FLOPPY PATCH      | 1     | 3/24/86 | 8:30  | MIKE     | PC    | DOC           | NA                      | Y    | 1882   |

| NA           | NA             | TAPE DRIVE TAKEUP REEL BROKEN   | 2     | 4/04/86 | 4:02  | MIKE     | NA    | HDWR          | NA                      | Y    | 3029   |

# JUSTIFYING

CAPITAL

EQUIPMENT

EXPENDITURES

# HOW TO

SPEND

THE BOSSES

MONEY

THIS PAPER WAS WRITTEN TO PROVIDE A PROCEDURAL FRAMEWORK FOR THOSE INTERESTED IN PROCURING AN EDA-620 CO-ROUTER.

IN TODAYS HIGH TECH WORLD, BUILDING A QUALITY PRODUCT PRESENTS MANY CHALLENGES:

THE CONSTANT TIME PRESSURE FOR NEW DESIGNS,

THE SCRUTINY OF UPPER MANAGEMENT OF THE GROUP'S OVERALL

PRODUCTIVITY,

AND THE TEAM'S OWN DESIRE TO PRODUCE "PERFECT" DESIGNS THAT WILL FLOW EASILY INTO FABRICATION AND MANUFACTURING.

#### **OVERHEAD**

- 1. DETERMINE WHETHER YOU THINK YOU NEED A CO-ROUTER.

- 2. CALL YOUR SALES REPRESENTATIVE WHO WILL CONVINCE YOU THAT YOU NEED A CO-ROUTER.

- 3. COST COMPARISONS:

OUTSIDE DESIGN SERVICE COSTS

VS

IN-HOUSE DESIGN COSTS

٧S

CAPITAL EQUIPMENT CO-ROUTER COSTS

- 4. LIST YOUR PAST P.C. BOARD ACCOMPLISHMENTS

- P.C. BOARD DESIGNS (BOARD SIZE AND DENSITY)

VS

#### ACTUAL TIMES

- 5. PROJECTED WORK FLOW

- 6. CAPITAL EQUIPMENT PROPOSAL PACKAGE

DO YOU NEED A CO-ROUTER?

DETERMINE HOW MANY NEW PRINTED CIRCUIT BOARDS ARE DESIGNED IN A YEAR.

WHAT TYPE OF BOARDS NEED TO BE DESIGNED:

- ANALOG

- DIGITAL

- HIGH SPEED

- SIZE

- DENSITY

- SURFACE MOUNT, ETC.

CALCULATE MANHOURS THAT ARE SPENT EACH YEAR "REWORKING" THE ELECTRICAL ENGINEERS FIX TO HIS "PERFECT" DESIGN OF LAST YEAR.

IF YOU ONLY DESIGN SINGLE-SIDED, 2" X 3" PCB'S WITH TWO DIP IC'S, 25 DISCRETES AND ONE RELAY, WITH HIGH PRODUCTION QUANTITIES AND LOW COSTS, THEN A CO-ROUTER MAY NOT BE FOR YOU.

#### OVERHEAD

#### SALES INQUIRIES

CALL YOUR TELESIS SALES REPRESENTATIVE (HE'S THE GUY WHO ALWAYS CALLS WHEN YOUR SYSTEM IS DOWN AND ASKS "HOW'S IT GOING?"). HE WILL ASSIST YOU IN DETERMINING YOUR PARTICULAR NEEDS.

#### OBTAIN THE FOLLOWING:

- QUOTES

- TRAINING SCHEDULES

- DELIVERY

- MAINTENANCE AGREEMENTS

#### OVERHEAD

#### COST COMPARISONS

#### OVERHEAD

CO-ROUTER COMPARISONS

REQUEST A DEMONSTRATION ON AN EDA-620 VS YOUR PRESENT SYSTEM WITH A BOARD THAT YOU HAVE ROUTED TO OBTAIN A "ROUTER COMPARISON."

NOW THAT YOU ARE CONVINCED, AND TELESIS HAS YOUR CO-ROUTER ON THEIR SHIPPING DOCK IT'S TIME TO DEMONSTRATE TO MANAGEMENT THE BENEFITS OF THE EDA-620.

#### OVERHEAD

PAST P.C. DESIGN ACCOMPLISHMENTS

#### OVERHEAD

PROJECTED WORK FLOW

#### OVERHEAD

#### COST SAVINGS

THE COST ANALYSIS IS ACCOMPLISHED BY:

ASSIGNING AVERAGE TIME ESTIMATES TO THE TASKS

PRODUCTIVITY GAINS TO DETERMINE POTENTIAL TIME

TRANSLATE THESE PRODUCTIVITY GAINS INTO DOLLARS AND TIME

SAVINGS

#### **OVERHEAD**

CAPITAL EQUIPMENT PROPOSAL PACKAGE

#### CONCLUSION:

I LIKE TO POINT OUT AT THIS TIME THE PRICES STATED ARE TELESIS LIST PRICES.

THE BOTTOM LINE IN EVALUATING ANY ADDITIONAL PIECE OF EQUIPMENT IS THE EFFICIENCY OF THE TOOL AND ITS APPLICABILITY TO THE DESIGN PROBLEM.

EFFORTS EXPENDED EARLY IN YOUR JUSTIFICATION FOR THE EDA-620 WILL PAY OFF WITH INCREASED PRODUCTIVITY, COST SAVINGS AND YOUR CHIEF EXECUTIVE OFFICERS' SIGNATURE ON YOUR PURCHASE REQUESTION.

- 1 DO YOU NEED A CO-ROUTER?

- 2 CALL YOUR SALES REPRESENTATIVE

- 3 COST COMPARISONS

· 11.79

- 4 PAST P.C. DESIGN ACCOMPLISHMENTS

- 5 PROJECTED WORK FLOW

- 6 CAPITAL EQUIPMENT PROPOSAL PACKAGE

#### **EXAMPLE QUOTATION**

| Prepai           | ed For:                         |                                                  |                                                                | Prepared By:                                                    |                    |                                         |

|------------------|---------------------------------|--------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------|--------------------|-----------------------------------------|

| 22 Pre           | Optics,<br>estige (<br>Hartford | Circle                                           |                                                                | <br>  Telesis Systems (<br>  Two Omni Way<br>  Chelmsford, MA ( | •                  |                                         |

| Attn:            |                                 | inda Stegall<br>er, Engineering S                | Services                                                       | <br>  Sales Representa<br>                                      | tive: Heath W      | heeler                                  |

|                  | THANK YO                        | OU FOR YOUR INQU                                 | IRY. WE                                                        | ARE PLEASED TO QUO                                              | TE YOU AS FOLL     | DWS:                                    |

| ITEM             | QTY                             | PART NUMBER                                      | DE:                                                            | SCRIPTION                                                       | *******            | NET AMOUNT                              |

| 1                | 1                               | 7010298-001                                      | EDA-620 I                                                      | Routing Accelerato                                              | r                  | \$ 53,200.00                            |

|                  |                                 |                                                  | * 2 Mb  <br>  * 85 Mb<br>  * EDA-6:<br>  * EDA-7:<br>  * Wyse- | •                                                               | re                 | <br>                                    |

|                  |                                 | <br>                                             |                                                                |                                                                 |                    | <br> <br> <br> <br> <br> <br> <br> <br> |

|                  | i<br> <br>                      | <br>                                             | <br> <br>                                                      |                                                                 |                    | <br> <br>                               |

| data             | hereof,                         | on shall remain unless modified prior to our acc | in writi                                                       |                                                                 | SUBTOTAL<br>       | !                                       |

| offer and i      | . This                          | quotation is sul<br>ned by standard              | bject to                                                       | credit approval                                                 | INSTALLATION       | •                                       |

|                  |                                 | resulting from                                   |                                                                |                                                                 | MAINTENANCE        | \$ 5,320.00                             |

|                  |                                 | TELESIS' corpora epresentative.                  | LE OTTICE                                                      | by a duty                                                       | <br> NET TOTAL<br> | \$ 59,052.00<br>                        |

| <br>  ESTIM      | ATED DE                         | LIVERY SCHEDULE                                  | (Subject                                                       | to Modification by                                              | Telesis )          |                                         |

| <br>  DATE       | OF ISSU                         | E:                                               |                                                                |                                                                 | PAGE 1 of 1        | -                                       |

| <br>  DEI_IV<br> | ERY DAT                         | ES WILL BE CONFI                                 | RMED UPON                                                      | ACCEPTANCE OF YOU                                               | IR CONTRACT OFF    | ER                                      |

|                  |                                 | ~~~~~~~                                          |                                                                |                                                                 |                    |                                         |

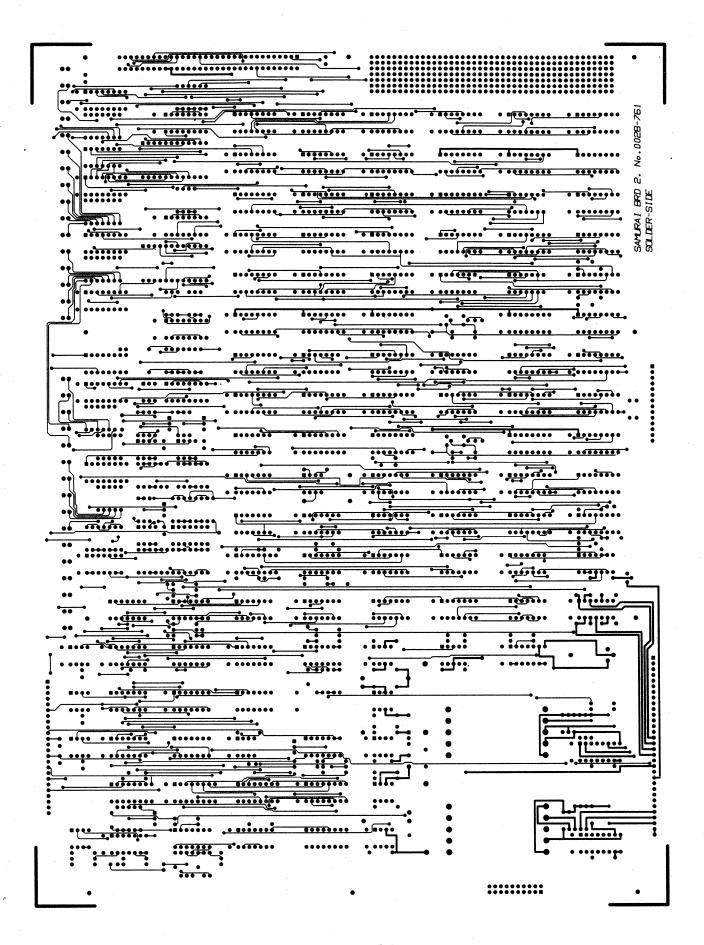

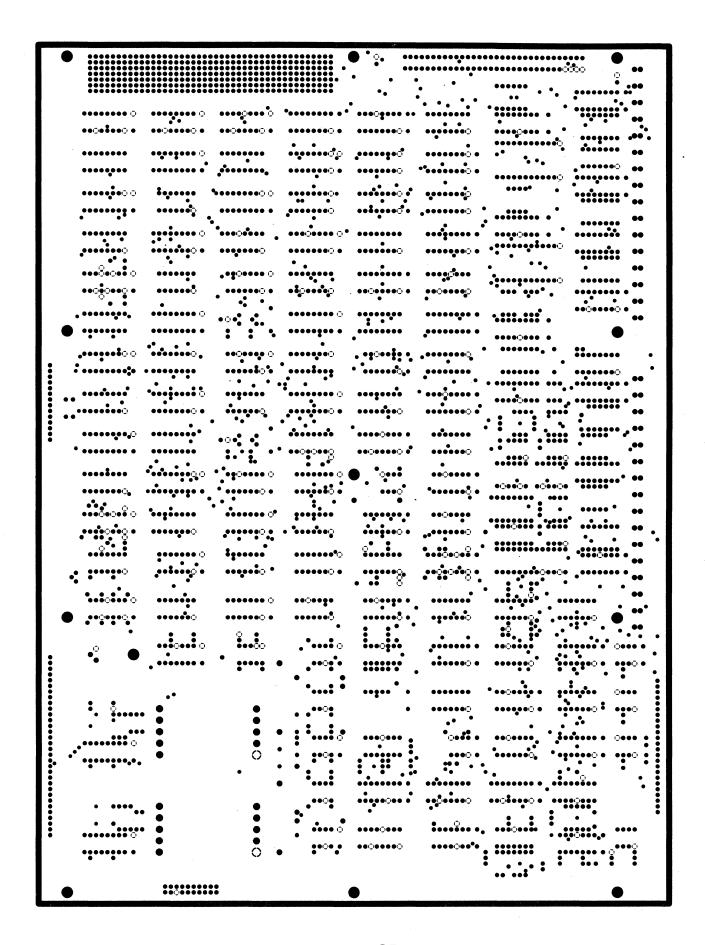

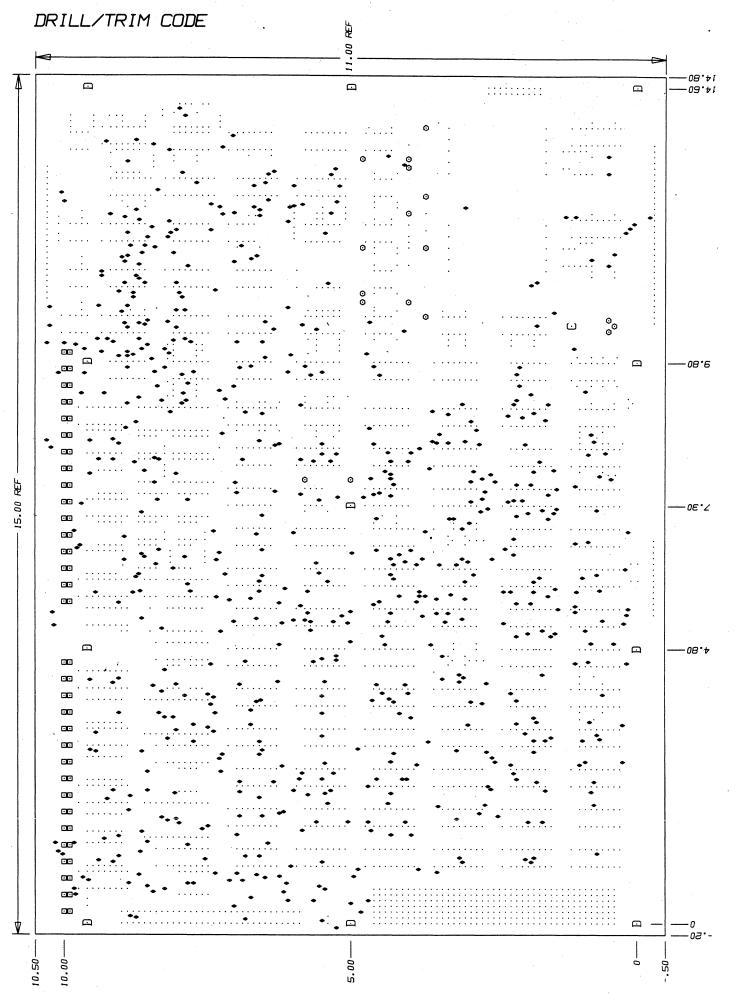

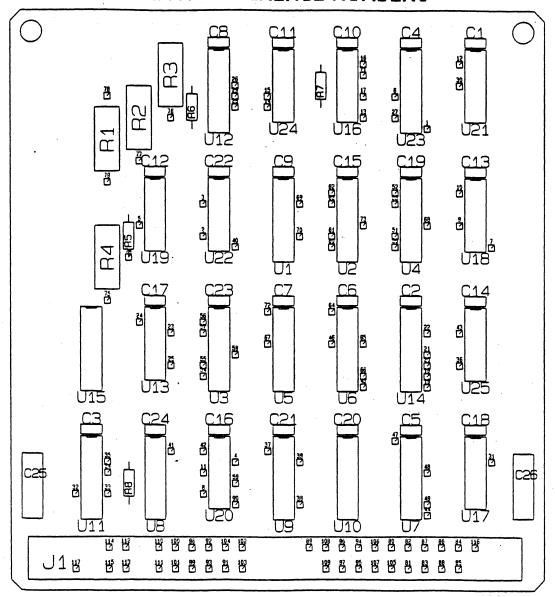

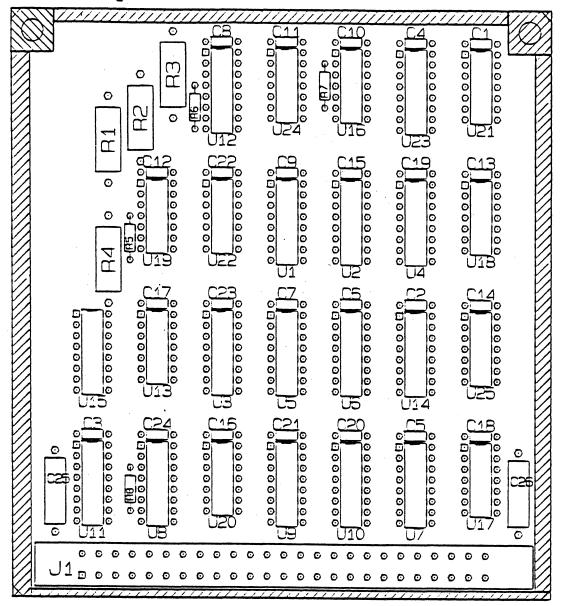

PCB NAME:

TERMINAL CONTROLLER I/F

DWG. NO.

600ML577-1

DESIGNER.

SHERRY RIO

# OUTSIDE DESIGN SERVICE COSTS

DESIGN

PHOTOPLOT

DRILL TAPES

DOCUMENTATION

\$ 16,607.00

# IN-HOUSE COSTS

#### LABOR

ENTRY 152 HOURS \$ 3720.36

DESIGN + DOCUMENTATION 106 HOURS \$ 2976.29

PHOTOPLOTTING + DRILL TAPE \$ 2000.00

TOTAL COST \$ 8696.65

SUPPLIES + MAINTENANCE

\$ 11,559 X 258 HOURS = \$ 1434.48

TOTAL IN-HOUSE COSTS \$ 10131.13

## SAVINGS

IN-HOUSE COSTS

DESIGN SERVICE COSTS

\$ 10, 131.13

16,607.00

TOTAL SAVINGS

\$ 6, 475.37

#### ROUTER COMPARISON

#### EDA-620 (co-router) vs EDA-300

Master Controller

EIC = 111density = .71

conns = 538

|   | EDA                 | -620     |       |       | EDA-300 |             |

|---|---------------------|----------|-------|-------|---------|-------------|

|   |                     | minutes  | conn. | comp. | minutes | conn. comp. |

| S | et-up               | 5        | •••   |       | 20      | _           |

| p | pass 1&2            | .5       | 238   | 3     | 49      | 221         |

|   | eass 5<br>4 execute | 36<br>s) | 279   | )     | 163     | 280         |

EDA-620 routed to 96.10% in 41.5 minutes

EDA-300 routed to 93.87% in 232 minutes

Mother Board

EIC = 619

density = .41 conns = 2788

| ED                  | A-620        |             | EDA-300 |             |  |

|---------------------|--------------|-------------|---------|-------------|--|

|                     | minutes      | conn. comp. | minutes | conn. comp. |  |

| set-up              | 33           | <b>-</b>    | 68      | _           |  |

| pass 1&2            | 6            | 2104        | 128     | 2258        |  |

| pass 5<br>(10 execu | 128<br>ites) | 631         | **      |             |  |

<sup>\*\*</sup>Pass 5 not run

Schematic

Start

Date

Schematic

Completion

Date

Design

Complete

Photoplot

Complete

CAD Lib.

Number

145

Board Size,

No. of Holes,

No. of Comp.

Designer/

Engineer

Dave S./

Wayne

Status

PCB

16. Reset Control & Configuration

VME

5 1/C

#### COMPLETED PCB's

| РСВ                                            | Designer/<br>Engineer | Status | Board Size,<br>No. of Holes,<br>No. of Comp. | Est.<br>Density | CAD-CAM<br>Library<br>Number | Schematic<br>and Design<br>Actual<br>Time | Released<br>to<br>Production                 |

|------------------------------------------------|-----------------------|--------|----------------------------------------------|-----------------|------------------------------|-------------------------------------------|----------------------------------------------|

|                                                |                       |        | 5 x 6 (2 layer)                              |                 |                              |                                           | 7.0 7 .0 .0 .0 .0 .0 .0 .0 .0 .0 .0 .0 .0 .0 |

| l. * Gate Pulse Driver<br>P/N 600565-1         | Mike/<br>B. Millar    | Done   | 484 holes<br>41 comp.                        | 1.03 ic/in      | 104                          | 96 hrs.<br>2.4 wks.                       | 12-06-85                                     |

| Relay Driver Test<br>Circuit P/N 600559-1      | Mike/<br>B. Millar    | Done   | 5 x 6 (2 layer)<br>322 holes                 | 1.03 ic/in      | 103                          | 84 hrs.<br>2.1 wks.                       | 12-06-85                                     |

| Mag Tape Controller<br>CCI P/N 600529-1        | Jonathan/<br>Mike J.  | Done   | 10 x 12<br>(8 layer)<br>3,252 holes          | 1.97 ic/in      | 115                          | 413.5 hrs.<br>10.3 wks.                   | 12-11-85                                     |

| 1. * Stacker Clutch Driver<br>P/N 600551-1     | Mike F./<br>Bruce     | Done   | 5 x 5                                        |                 | 102                          | 171 hrs.<br>4.275 wks.                    | . 12-06-85                                   |

| G. Grant Continuity P/N 600536-1               | D. Fincher/<br>Stone  | Done   | 10 x 12                                      | N/A             | 116                          | 51.3 hrs.<br>1.3 wks.                     | 10-11-85                                     |

| 5. * Kebus Prototype Bd.<br>P/N 600537         | Jonathan/<br>Stone    | Done   | 10 x 12                                      | N/A             | 117                          | 142.9 hrs.<br>3.6 wks.                    | Ø5 <b>-</b> 1Ø-85                            |

| Peripheral Controller P/N 600523-1             | Jonathan/<br>Art      | Done   | 7 x 11.5                                     | N/A             | 118                          | 660.5 hrs.<br>16.5 wks.                   | Ø5 <b>–</b> 3Ø–85                            |

| . * Jam Logic<br>P/N 600521 (Wire List Entry)  | Jonathan/<br>Art      | Done   | 7 x 11.5                                     |                 |                              | 561.5 hrs.<br>14.0 wks.                   | 10-23-85                                     |

| SP370-2 Repl<br>P/N 600550-l                   | Mike                  | Done   | 1.8 x 2.6                                    | N/A             | 110                          | 99 hrs.<br>2.5 wks.                       |                                              |

| 11/73 Interface<br>0. P/N 600541-1             | Jonathan<br>Mike J.   | Done   | 10.5 x 12.5                                  | 1.25 ic/in      |                              | 240 hrs.<br>6 wks.                        | Ø2 <b>–</b> 21–85                            |

| SMCA/DMA<br>1. P/N 600525-1                    | Jonathan/<br>Stone    | Done   | 10 x 12                                      | .87 ic/in       | 119                          | 260 hrs.<br>6.5 wks.                      | 10-11-85                                     |

| Kebus Extender<br>2. P/N 600543-1              | Jonathan/<br>Stone    | Done   | 10 x 12                                      | N/A             | 120                          | 53.9 hrs.<br>1.3 wks.                     |                                              |

| 3. Edit Terminal I/O Panel P/N 600567-1 REV. A | Mike/<br>Joe          | Done   | 16.5 x 5.5<br>2 layers<br>1,358 holes        | .87 ic/in       | 106                          | 154 hrs.                                  | Ordered 1-23-                                |

| 4. VFD Protocol Converter P/N 600574-1         | Mike/<br>Dave G.      | Done   |                                              |                 | 111                          | 20 hrs.<br>.5 wks.                        | ,                                            |

|   | ı |

|---|---|

| r | ٥ |

| 4 | > |

|   |   |

| 15.  | Mack Rack Addr. Xlator<br>P/N 600575-1                                  | Sherri/<br>Joe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Done               | 1.4 x 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        | 109                                           | 5.5 hrs.<br>.2 wks.                       | Protos Inhouse                              |

|------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------|-------------------------------------------|---------------------------------------------|

| 16.  | Strobe Board<br>P/N 600572-1                                            | Sherri/<br>Paul B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Done               | 2.5 x 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        | 114                                           | 9 hrs.<br>.2 wks.                         | Protos Inhouse                              |

| 17.  | Dual Channel Interface<br>Printer Adapter<br>P/N 600558-1               | Mike/<br>Stone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Done               | (2 layers)<br>627 holes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.15 ic/in             | 105                                           | 84 hrs.<br>2.1 wks.                       | Protos Inhouse                              |

| 18.  | Master Controller<br>P/N 600ML522-1                                     | Mike/<br>Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Done               | 6.5 x 11.5<br>2,300 holes<br>153 Comp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .71 in/ic              | 101                                           | +Telesis<br>190 hrs.<br>Total<br>4.8 wks. |                                             |

| 19.  | Dual Channel Interface<br>P/N 600ML554-1                                | Jonathan/<br>Stone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Done               | 12.5 x 13.5<br>(8 layers)<br>4,585 holes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.06 ic/in             | 122                                           | 862 hrs<br>Total<br>21.5 wks.             | Protos ordered 1/31/86<br>Ship Date 2/28/86 |

| 20.* | *Terminal Controller I/F<br>P/N 600ML577-1                              | Sherri/<br>Joe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Done               | 12.5 x 13.5<br>(10 layers)<br>5,115 holes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.84 ic/in             | 108                                           | 342 hrs.<br>Total<br>8.5 wks.             | Ordered 1/23/86<br>Ship Date 2/21/86        |

| 21.  | Control Panel Adaptor PCB<br>P/N 600549-1<br>530/540 Appearance Upgrade | Mike/<br>Paul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Done               | 6.5 x 11.5<br>2 layers<br>1,218 holes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.09 ic/in             | 112                                           | 170 hrs.<br>Total<br>4.3 wks.             | Protos Inhouse                              |

| 22.  | B-Bus Convertor<br>(Classifier Project)<br>P/N 600ML576-1               | Sherri/<br>Brian T.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Done               | 6 layers<br>LRL Size<br>150 Comp.<br>Digital                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .61 in/ic              | 113                                           | 244 hrs.<br>Total<br>6.1 wks.             | Ordered 2/21/86<br>Ship Date 3/7/86         |

| 23.  | B-Bus Driver<br>(Classifier Project)<br>P/N 600ML578                    | Mike/<br>Sherri/<br>Brian T.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Done               | 5 X 8<br>20 IC's<br>Digital<br>(8 layers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.1 ic/in<br>.41 in/ic | 125                                           | 119 hrs.<br>Total<br>2.975 hrs.           | Protos Ordered 1/31/86<br>Ship Date 2/28/86 |

| 24.  | Terminal Controller Remote Panel<br>P/N 600ML568-1                      | Mike/<br>Joe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Done               | 4 layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        | 107                                           | 120 hrs.<br>Total<br>3 wks.               | Ordered 1/23/86<br>Ship Date 2/21/86        |

| 25.  | Euro Cards Mother Board<br>P/N 600NL580                                 | Fred B./<br>Wayne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Done               | W/L Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        | 124                                           | Telesis/<br>Sherri                        | Ordered 2/13/86                             |

| 26.  | Double Document Detector<br>Update 700186-1<br>P/N 600071               | Art/<br>Wayne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Done               | 5 X 5<br>15 IC's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        | 128                                           | 94 hrs.<br>Total<br>2.4 wks.              | Ordered 2/18/86<br>Ship Date 3/17/86        |

| 27.  | PC 9 Overlength                                                         | Art <sup>-</sup> /<br>Wayne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Done               | 5 X 5<br>12 IC's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        | 127                                           | 72 hrs.                                   | Ordered 2/18/86                             |

|      | 16. 17. 18. 19. 20.* 21. 22. 23.                                        | 16. Strobe Board P/N 600572-1  Dual Channel Interface 17. Printer Adapter P/N 600558-1  18. Master Controller P/N 600ML522-1  Dual Channel Interface 19. P/N 600ML554-1  20.**Terminal Controller I/F P/N 600ML577-1  21. Control Panel Adaptor PCB P/N 600549-1 530/540 Appearance Upgrade  22. B-Bus Convertor (Classifier Project) P/N 600ML576-1  23. B-Bus Driver (Classifier Project) P/N 600ML578  24. Terminal Controller Remote Panel P/N 600ML580  25. Euro Cards Mother Board P/N 600ML580  26. Double Document Detector Update 700186-1 | P/N 600575-1   Joe | P/N 600575-1  16. Strobe Board P/N 600572-1  Dual Channel Interface Mike/ Done Printer Adapter P/N 600558-1  18. Master Controller Mike/ Done Printer Adapter P/N 600558-1  Dual Channel Interface Mike/ Done P/N 600558-1  Dual Channel Interface Mike/ Art Done P/N 600ML522-1  Dual Channel Interface Jonathan/ Stone  20.**Terminal Controller I/F Sherri/ Done P/N 600ML577-1  Control Panel Adaptor PCB P/N 600549-1 Joe Done P/N 600549-1 S30/540 Appearance Upgrade Paul  22. B-Bus Convertor Sherri/ Done Printer Printer Project) Brian T. P/N 600ML576-1  Mike/ Sherri/ Done P/N 600ML578  24. Terminal Controller Remote Panel P/N 600ML578  25. Euro Cards Mother Board Fred B./ Done P/N 600ML580 Wayne  26. Double Document Detector Update 700186-1 Wayne P/N 6000TL | P/N 600575-1   Joe     | P/N 600575-1   Joe   Paul B.   Done   Paul B. | P/N 600575-1   Joe                        | F/N 600575-1   Joe   2 wks.                 |

ASSIGNING AVERAGE TIME ESTIMATES TO THE TASKS

PRODUCTIVITY GAINS TO

DETERMINE POTENTIAL TIME

TRANSLATE THESE PRODUCTIVITY

GAINS INTO DOLLARS

AND TIME SAVINGS

#### PROPOSAL

TO: J. Belhumeur

FROM: L. Stegall

DATE: February 24, 1986

SUBJECT: Purchase of an EDA-620 Routing Station

In March of 1985, the second CAD/CAM System was purchased at a cost of \$69,900.00. With the acquisition of the second system and a second shift that began in September 1985, a total of 15 printed circuit boards were designed and our outside design service costs were reduced to \$28,943.00 compared to 1984 design services of \$83,976.00 a savings of \$55,033.00. Since then, I've been greatly concerned about our system efficiencies, and have taken a look at where things might be improved. One general conclusion is we can improve our throughput and cost efficiencies by moving our routing of printed circuit boards "off" to a co-router which would free our present systems to be used as a design station only.

The third system would consist of an EDA-620 Routing Station. The EDA-620 is used as an add-on to Telesis workstations which shortens project design time, improves individual user productivity and speeds overall system throughput. Based on Sun Microsystems' Sun-3 hardware architecture the accelerator speeds routing tasks by four to eleven times over execution rates on the Telesis EDA-300 workstation.

Attached is a brief synopsis justifying these purchases. This is broken down as follows:

Exhibit A - Quotation and EDA-620 Routing Brochure

Exhibit B - PC Board accomplishments for 1985

Exhibit C - Router comparison on the EDA-620 vs. EDA-300.

(Note: Scan-Optics was invited to Telesis and use the EDA-620 to get this comparison.)

Exhibit D - Capital Equipment Request and Purchase Requisition

Exhibit E - 1986 known new PC designs

Conclusion: Twelve (12) new printed circuit boards must be designed and fabricated by April 31, 1986 for the High Speed Image Capture Module and to meet this schedule the EDA-620 Routing Station is needed.

#### LS/tld

cc: J. Aucoin

- G. Dwyer

- R. Gocht

- D. Newton

### SCAN-OPTICS, INC.

## CAPITAL. EQUIPMENT REQUEST

| CER | <b>#</b> . |  |

|-----|------------|--|

| MER | #          |  |

| Originator: Linda Stegall                             | Dept. # 622                                                             | User Der              | ot_ ≠ 622                       |

|-------------------------------------------------------|-------------------------------------------------------------------------|-----------------------|---------------------------------|

| Capital Asset Account #:                              | 622-1790                                                                |                       |                                 |

| Capital Equipment Descri                              | ption - To Be Comple                                                    | eted By The Orig      | inator                          |

| Purpose of the Expenditu                              | Te To purchase an EDA-6<br>and cost efficiencie<br>circuit boards "off" | s by moving our routi | our throughput<br>ng of printed |

|                                                       |                                                                         |                       |                                 |

| Recommended Vendors: Li                               | st 3 and Price Quota                                                    | ations:               |                                 |

| 1. Telesis - \$59,052.00                              |                                                                         |                       |                                 |

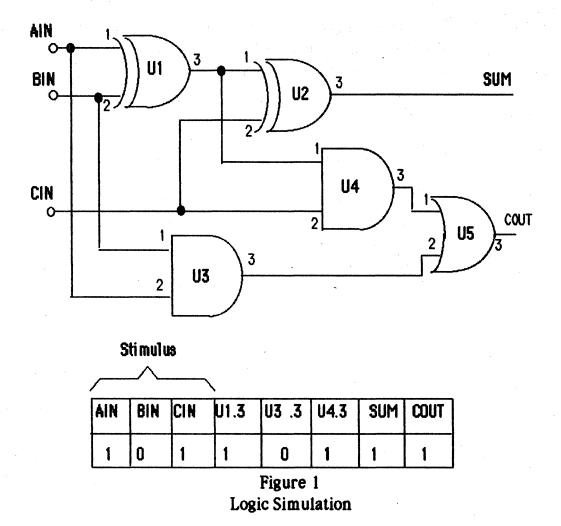

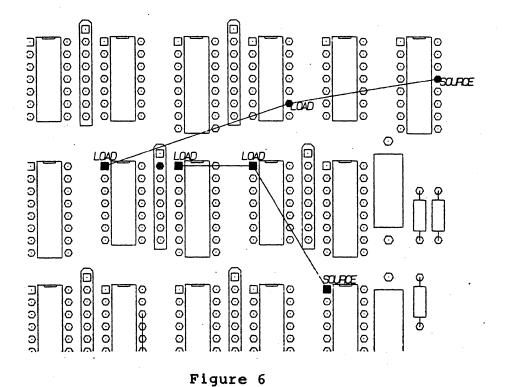

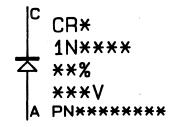

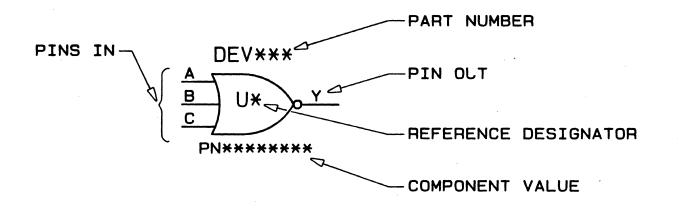

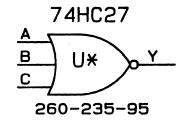

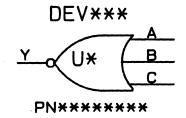

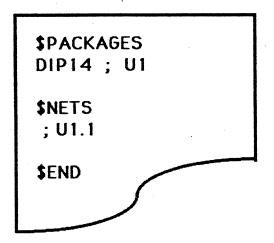

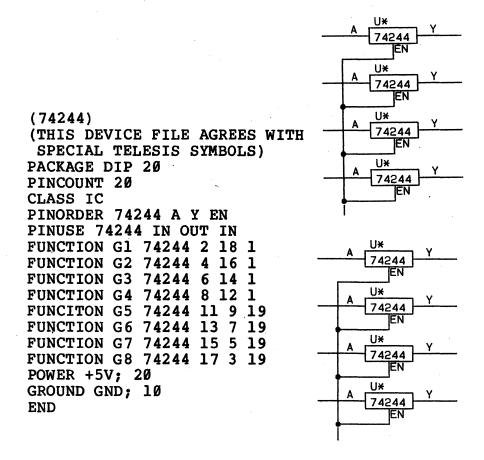

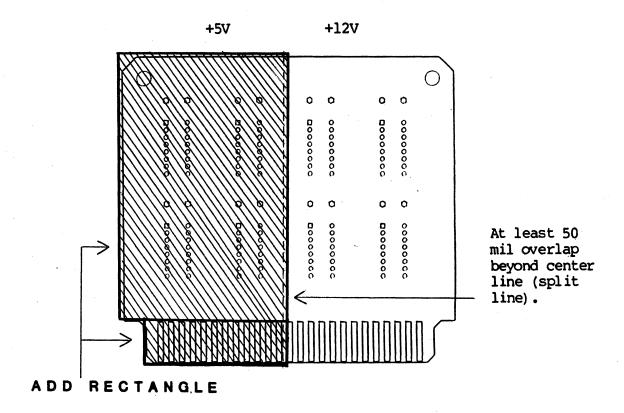

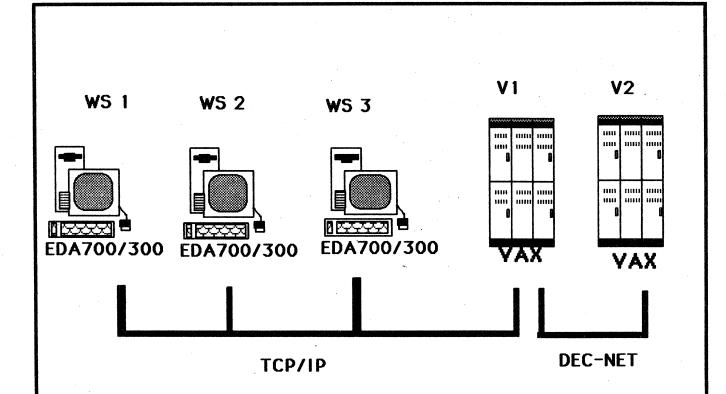

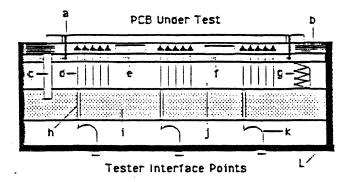

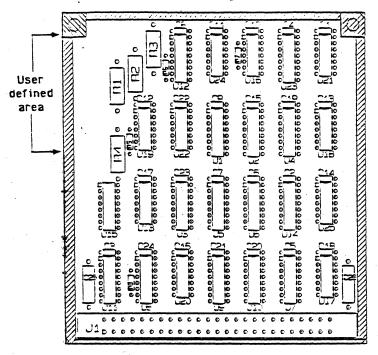

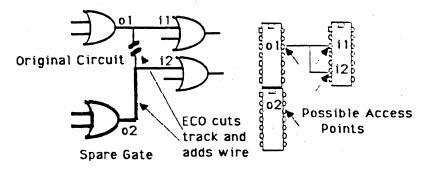

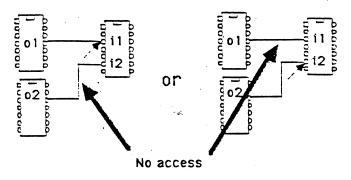

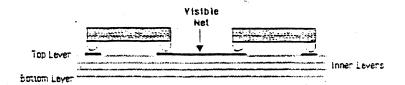

| 2.                                                    |                                                                         |                       |                                 |