**Basic Circuitry of the** MIDAC and MIDSAC

by J. E. De Turk, H. L. Garner, J. Kaufman, H. W. Bethel, R. E. Hock

The work reported herein was supported by The Boeing Airplane Company under the sponsorship of the U. S. Air Force

> May 1954 1947-2-T

University of Michigan Engineering Research Institute Willow Run Research Center Willow Run Airport Ypsilanti, Michigan

## UNIVERSITY OF MICHIGAN \_\_\_\_\_

1947-2-T

### TABLE OF CONTENTS

| Section | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| I       | List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | iii                                                                                                |

|         | List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | vi                                                                                                 |

|         | Forward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I-1                                                                                                |

| Ι       | Description of Computer Plug-In Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I-3                                                                                                |

|         | <ul> <li>J.1 Functional Organization of Circuits</li> <li>1.2 Descriptions of Package Types <ol> <li>2.1 Gate-Amplifier Package</li> <li>2.2 Delay Package</li> <li>2.3 Termination Package</li> <li>2.4 Or-Gate Package</li> </ol> </li> <li>Interconnection of Packages</li> <li>1.4 Circuit Operation <ol> <li>4.1 The Diode Gates</li> <li>4.2 Amplifier</li> <li>4.3 Output Buffer</li> <li>4.4 Pulse Delay Units</li> </ol> </li> <li>Electrical Specifications <ol> <li>5.1 Voltage and Current Requirements</li> </ol> </li> </ul> | I-3<br>I-9<br>I-15<br>I-15<br>I-16<br>I-16<br>I-22<br>I-22<br>I-22<br>I-22<br>I-28<br>I-29<br>I-32 |

|         | of Packages<br>1.5.2 Component Tolerances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I-32<br>I-33                                                                                       |

| II      | Assembly of Standard Packages to Obtain Functional<br>Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | II-1                                                                                               |

|         | <ul> <li>2.1 Storage Loop</li> <li>2.2 Timing-Pulse Generator</li> <li>2.3 Shift Register</li> <li>2.4 Comparator</li> <li>2.5 Complementor</li> <li>2.6 Adder<sup>-</sup></li> <li>2.7 Counter</li> </ul>                                                                                                                                                                                                                                                                                                                                 | II-1<br>II-2<br>II-8<br>II-10<br>II-10<br>II-13<br>II-17                                           |

## UNIVERSITY OF MICHIGAN \_\_\_\_\_

19**47-2-**T

## TABLE OF CONTENTS (Continued)

| Section  |     | Title                                                                                                                                                            | Page                                                              |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| III      |     | mple of a Computer Subsystem: A Serial thmetic Unit                                                                                                              | III-1                                                             |

|          | 3.2 | Inputs and Outputs<br>Functions of Sub-Units<br>Operation of Sub-Units                                                                                           | III-1<br>III-2<br>III-2                                           |

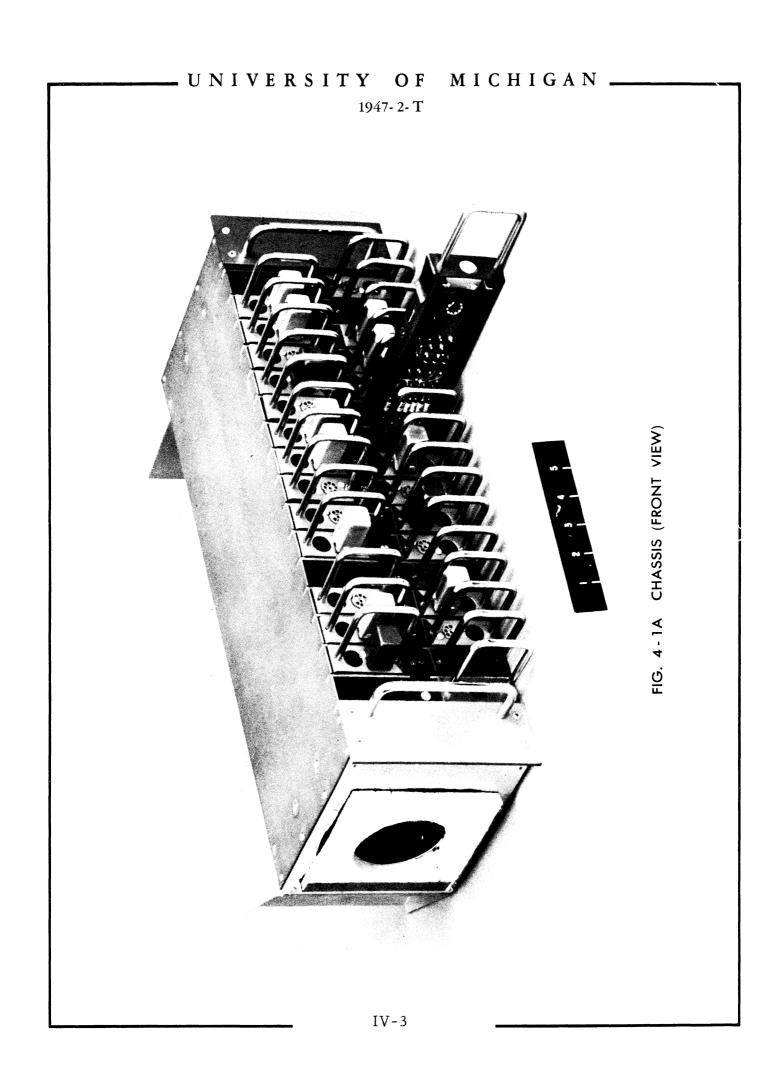

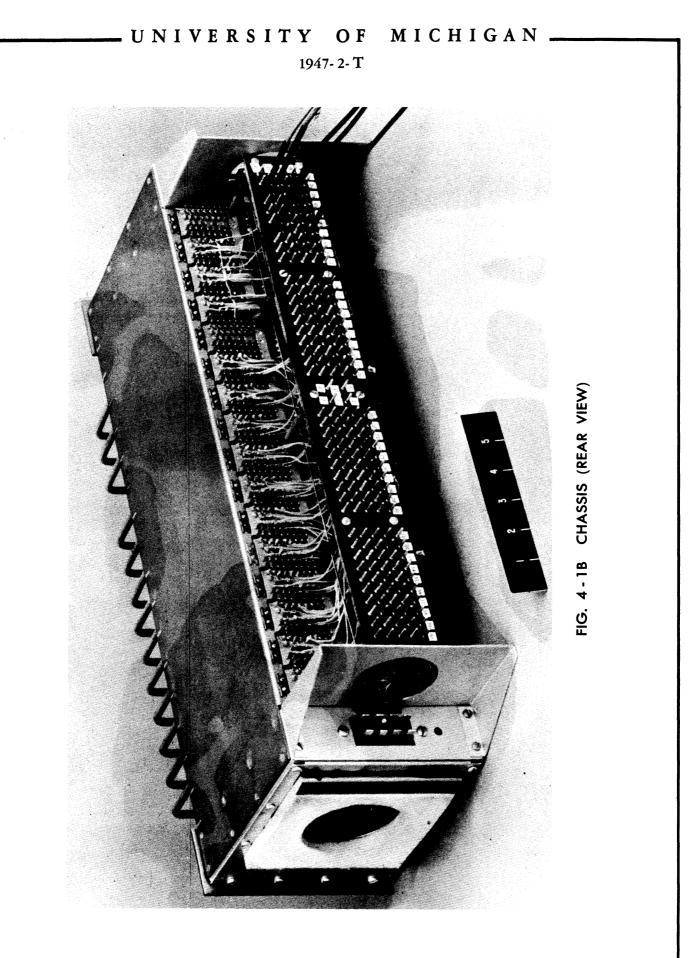

| IV       | Med | chanical Design                                                                                                                                                  | IV-1                                                              |

|          | 4.2 | General Description<br>Development<br>4.2.1 Packages<br>4.2.2 Chassis<br>4.2.3 Racks<br>Suggested Improvements<br>4.3.1 Packages<br>4.3.2 Chassis<br>4.3.3 Racks | IV-2<br>IV-2<br>IV-9<br>IV-10<br>IV-12<br>IV-12<br>IV-13<br>IV-13 |

| Appendix | x A | Rules and Data for Using Packages                                                                                                                                | A-1                                                               |

| Appendix | кВ  | Some Design Factors and Effects of<br>Component Tolerances                                                                                                       | B-1                                                               |

|          |     | References                                                                                                                                                       | B-18                                                              |

|          |     | Distribution                                                                                                                                                     | B-19                                                              |

## \_\_\_\_\_ UNIVERSITY OF MICHIGAN \_\_\_\_\_

1947**-**2-T

## LIST OF FIGURES

| Number | Title                                                                 | Page          |

|--------|-----------------------------------------------------------------------|---------------|

| 1-1    | Symbolic Representations of Gates                                     | I-4           |

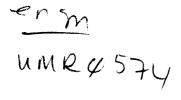

| 1-2    | Levels of Logical Function Associated with One<br>Pulse Amplifier     | I-6           |

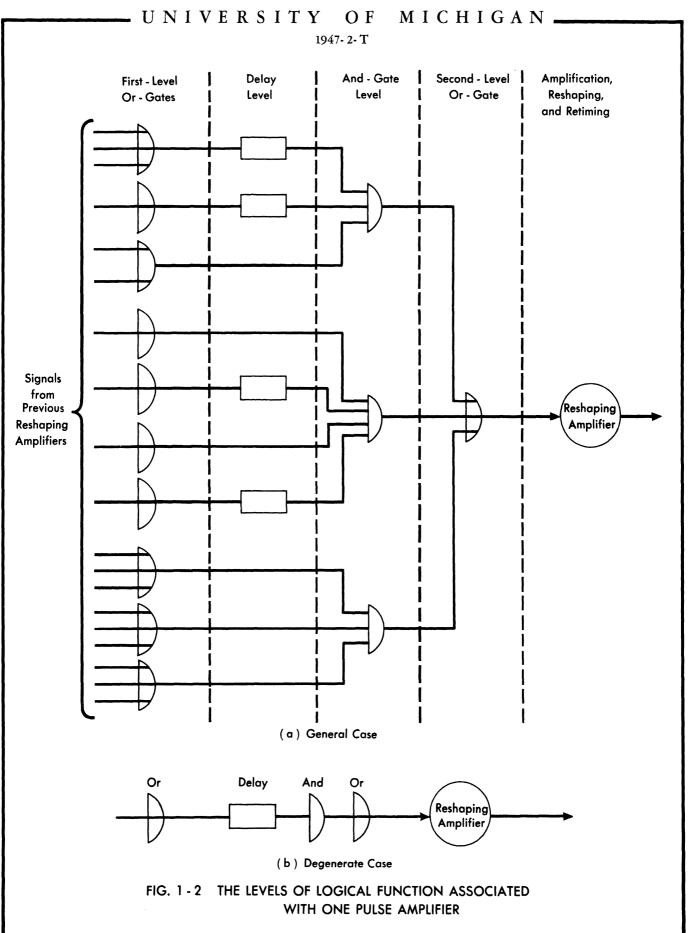

| 1-3    | Gate-Amplifier Package                                                | I <b>-</b> 7  |

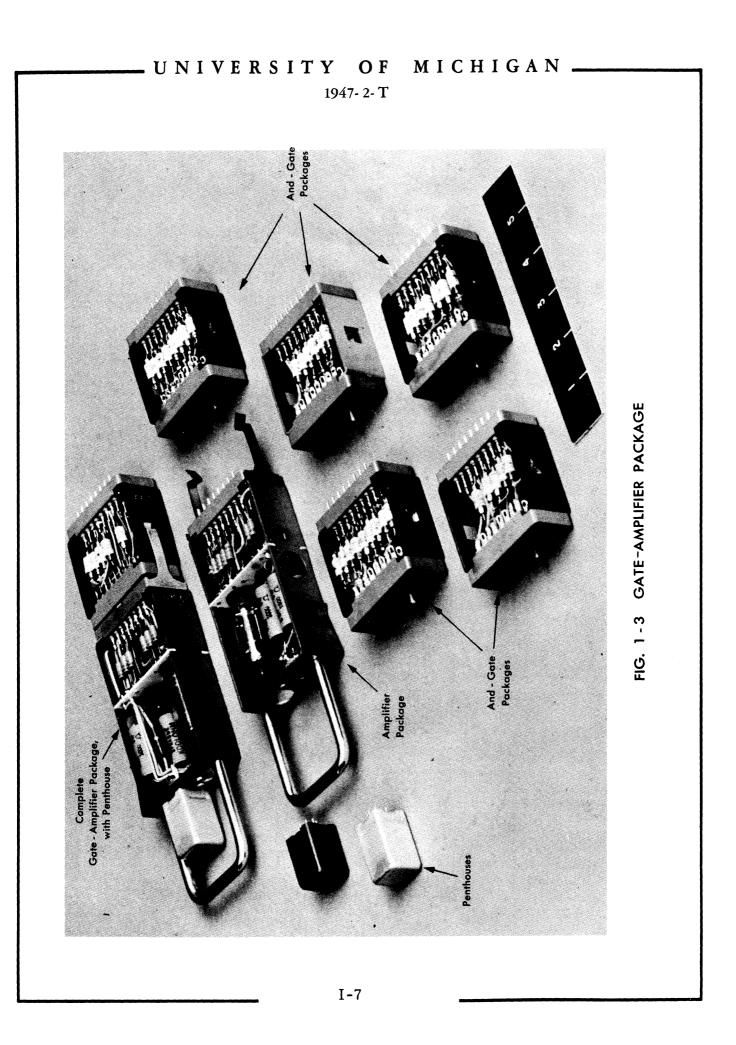

| 1-4    | Delay-Line and Termination Packages                                   | I-8           |

| 1-5    | Gate-Amplifier Package                                                | I-10          |

| 1-6    | Use of Multi-Phase Clock to Standardize Delay in<br>Cascaded Circuits | I-11          |

| 1-7    | Outputs of Amplifier Package                                          | I-13          |

| 1-8    | Examples of And-Gate Inhibition                                       | I-17          |

| 1-9    | Interconnecting Networks with Degenerate First-<br>Level Or-Gates     | I-18          |

| 1-10   | Interconnecting Networks with Non-Degenerate<br>First-Level Or-Gates  | I-19          |

| 1-11   | Interconnecting Networks Using Long Delay Lines                       | I-20          |

| 1-12   | Circuits of Gate-Amplifier Packages                                   | I-23          |

| 1-13   | Operation of And-Gate                                                 | I-24          |

| 1-14   | Operation of Or-Gate                                                  | I-25          |

| 1-15   | Amplifier Output Circuits                                             | I-26          |

| 1-16   | Pulse Delay Circuits                                                  | I-31          |

| 2-1    | Serial Storage Loop for N Pulses                                      | II <b>-</b> 3 |

| 2-2    | Flip-Flop                                                             | II-3          |

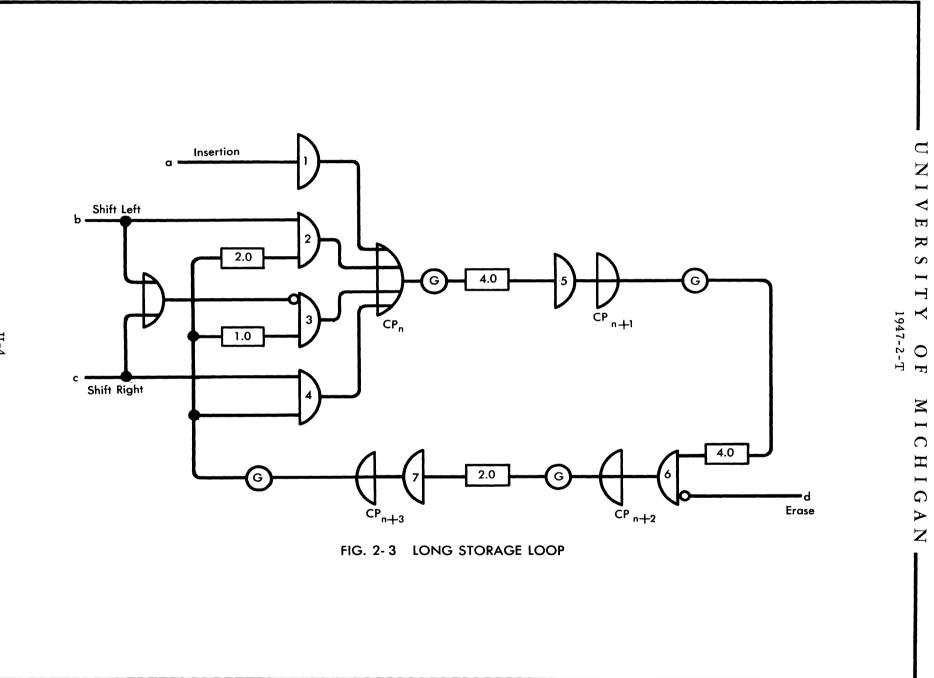

| 2-3    | Long Storage Loop                                                     | II -4         |

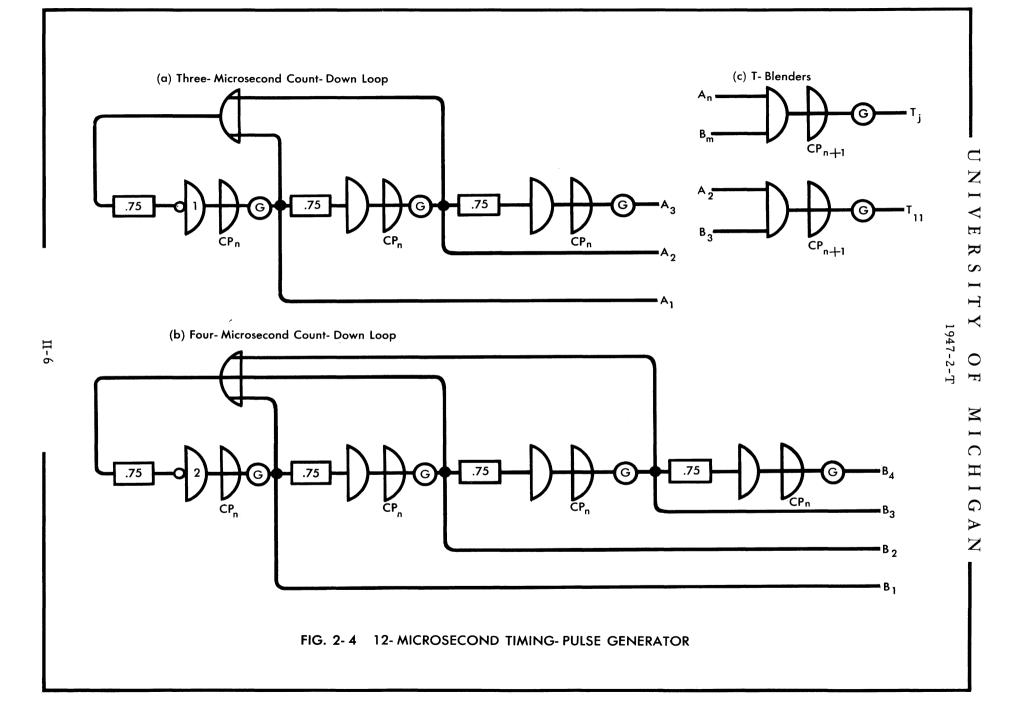

| 2-4    | 12-Microsecond Timing Pulse Generation                                | II-6          |

# UNIVERSITY OF MICHIGAN \_\_\_\_\_

1947-2-T

## LIST OF FIGURES (Continued)

| Number        | Title                                    | Page  |

|---------------|------------------------------------------|-------|

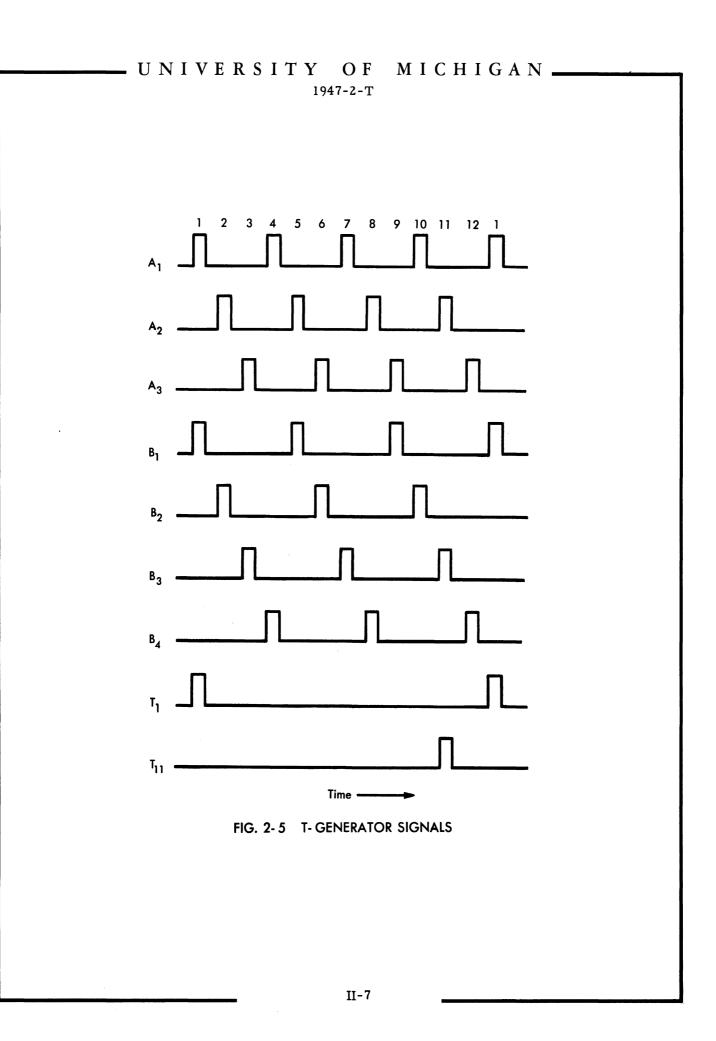

| 2-5           | T-Generator Signals                      | II-7  |

| 2-6           | Shift Register                           | II-9  |

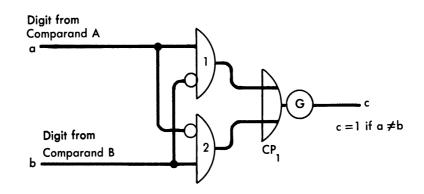

| 2-7           | Simple Comparator                        | II-11 |

| 2-8           | Comparator (Inequality)                  | II-11 |

| 2-9           | Comparator (Equality)                    | II-12 |

| 2-10          | Twos-Complementor                        | II-12 |

| 2-11          | Adder                                    | II-15 |

| 2-12          | Three-Input Adder                        | II-16 |

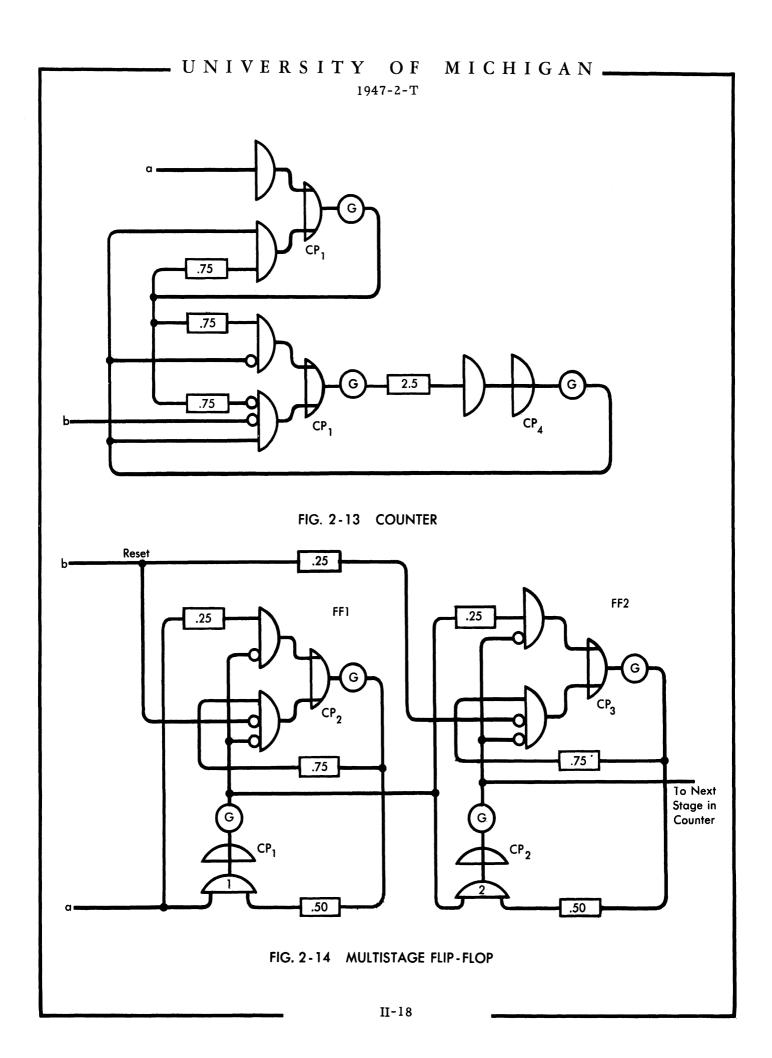

| 2-13          | Counter                                  | II-18 |

| 2-14          | Multistage Flip-Flop                     | II-18 |

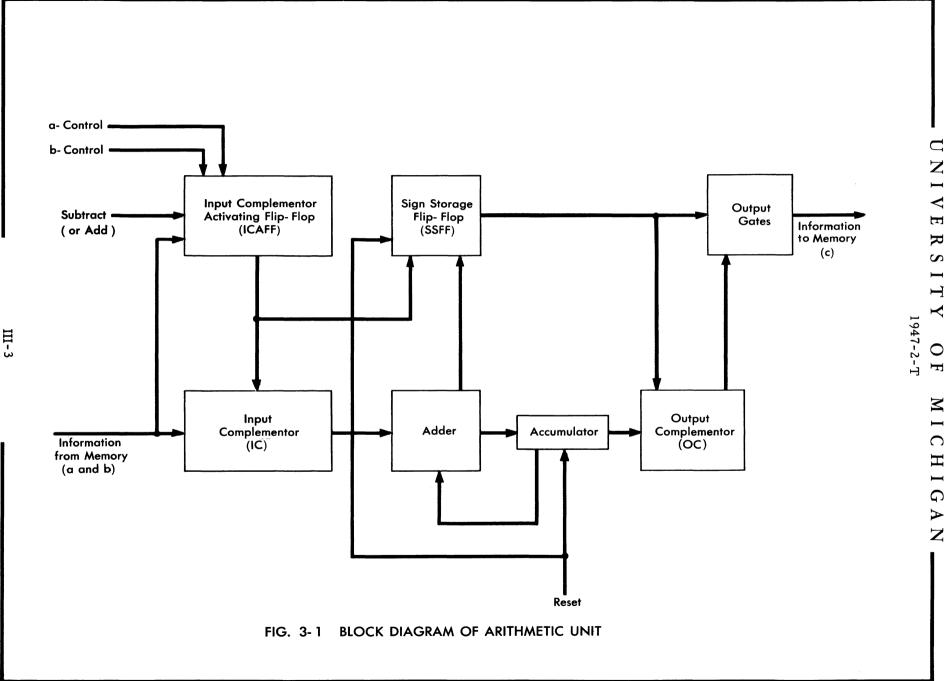

| 3-1           | Block Diagram of Arithmetic Unit         | III-3 |

| 3-2           | Logical Schematic of Arithmetic Unit     | III-4 |

| 4 <b>-</b> 1A | Chassis (Front View)                     | IV-3  |

| 4 <b>-</b> 1B | Chassis (Rear View)                      | IV-4  |

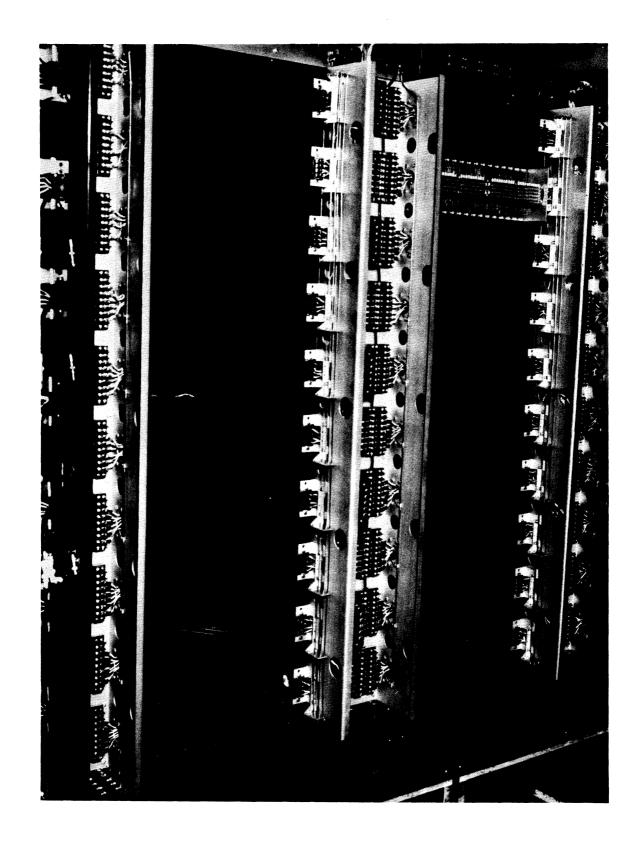

| 4-2           | Rack (Rear View)                         | IV-5  |

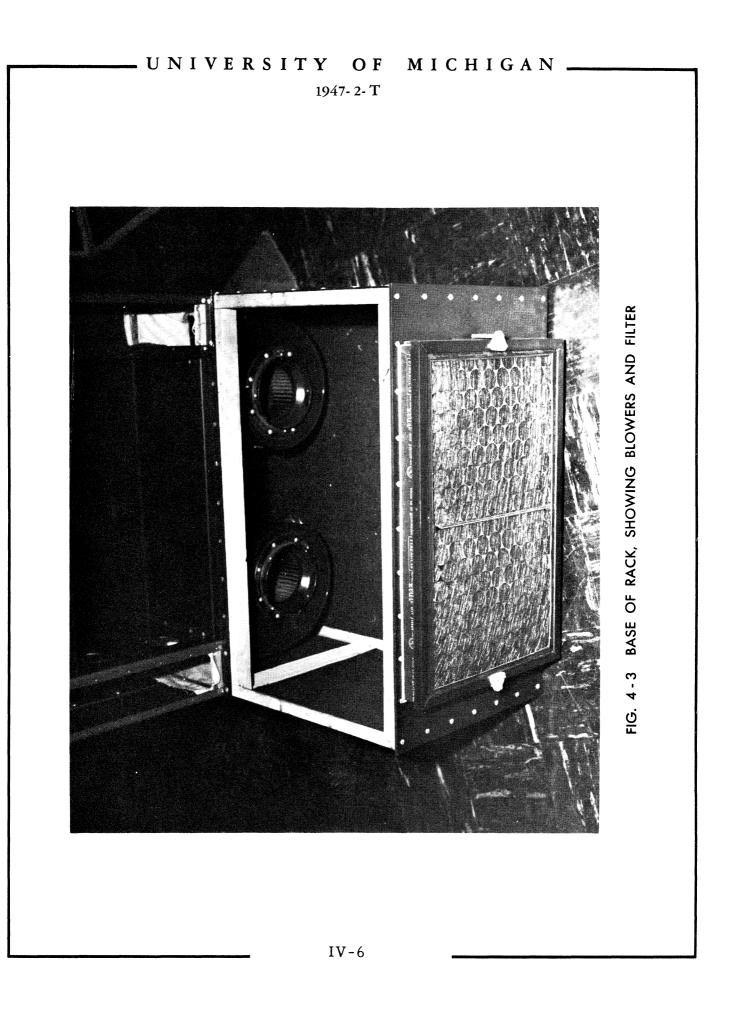

| 4-3           | Base of Rack, Showing Blowers and Filter | IV-6  |

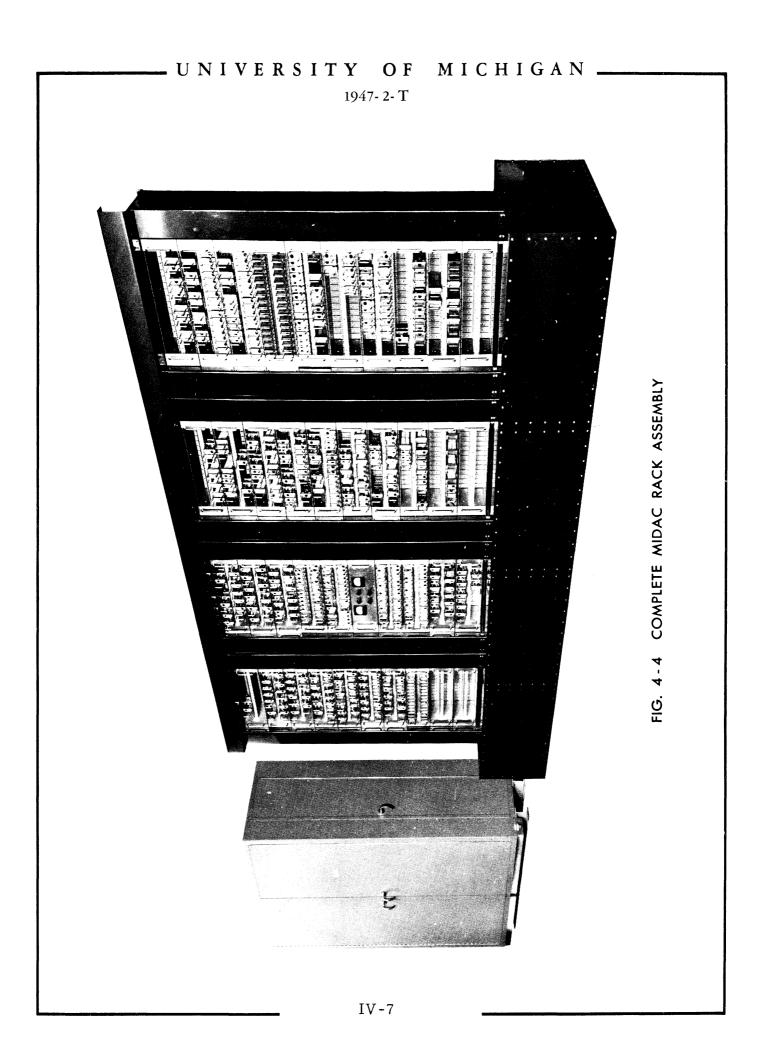

| 4-4           | Complete Midac Rack Assembly             | IV-7  |

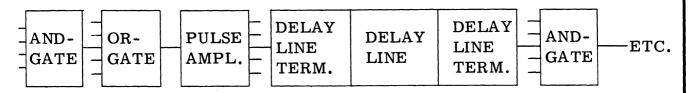

| 4-5           | Connection of Basic Packaged Circuits    | IV-8  |

| 4-6           | Rear Plate of Horizontal Air Duct        | IV-10 |

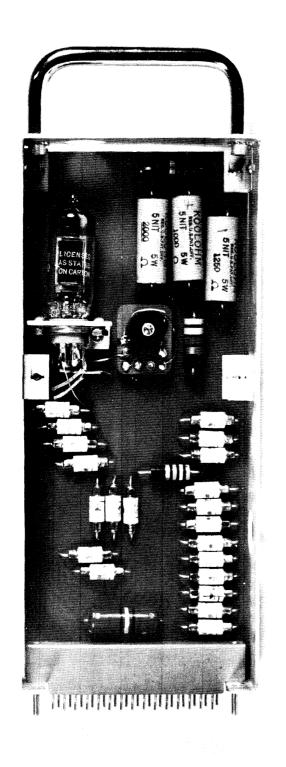

| 4-7           | Interior of Printed Circuit Package      | IV-14 |

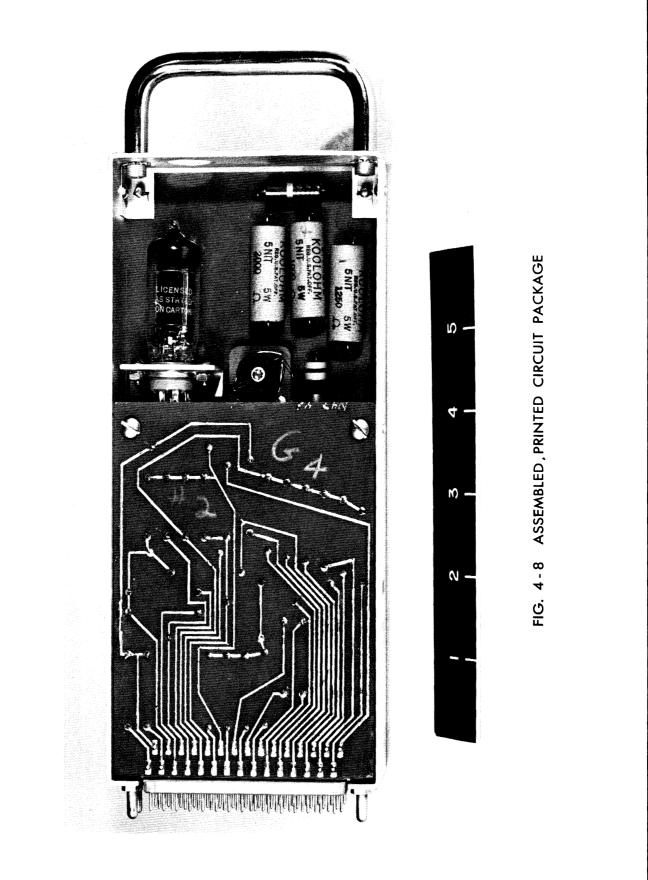

| 4-8           | Assembled Printed Circuit Package        | IV-15 |

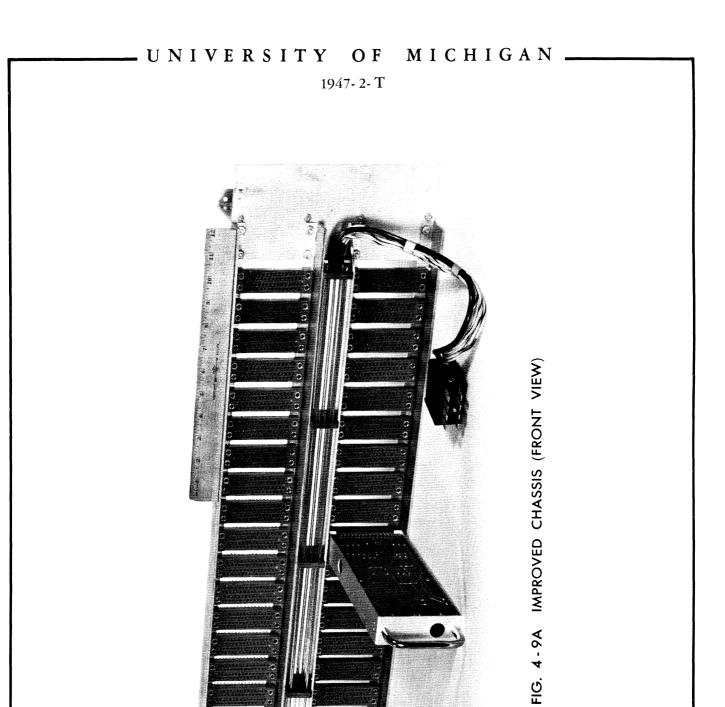

| <b>4-</b> 9A  | Improved Chassis (Front View)            | IV-16 |

# \_\_\_\_\_ UNIVERSITY OF MICHIGAN \_\_\_\_\_

1947-2-T

# LIST OF FIGURES (Continued)

| Number        | Title                                                     | Page  |

|---------------|-----------------------------------------------------------|-------|

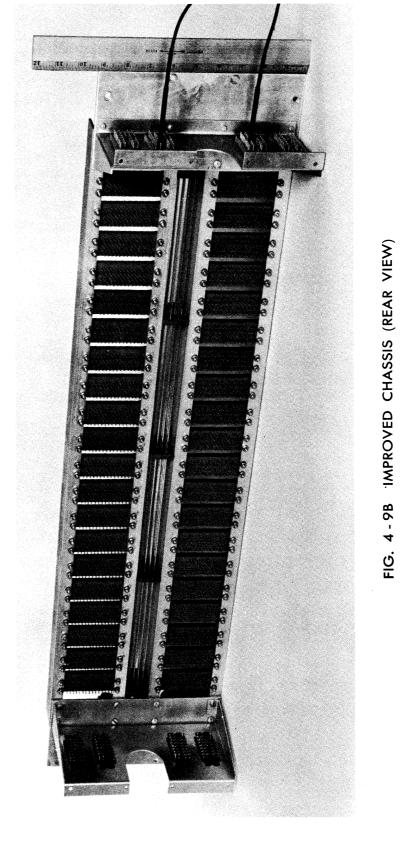

| 4 <b>-</b> 9B | Improved Chassis (Rear View)                              | IV-17 |

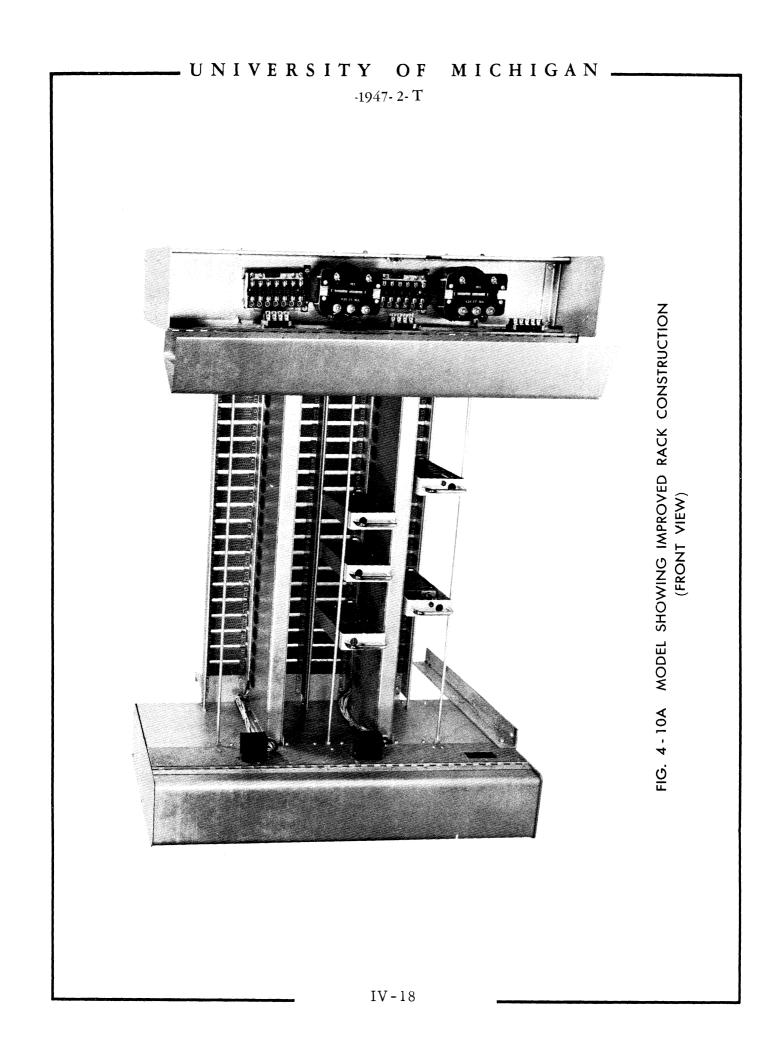

| 4-10A         | Model Showing Improved Rack Construction (Front View)     | IV-18 |

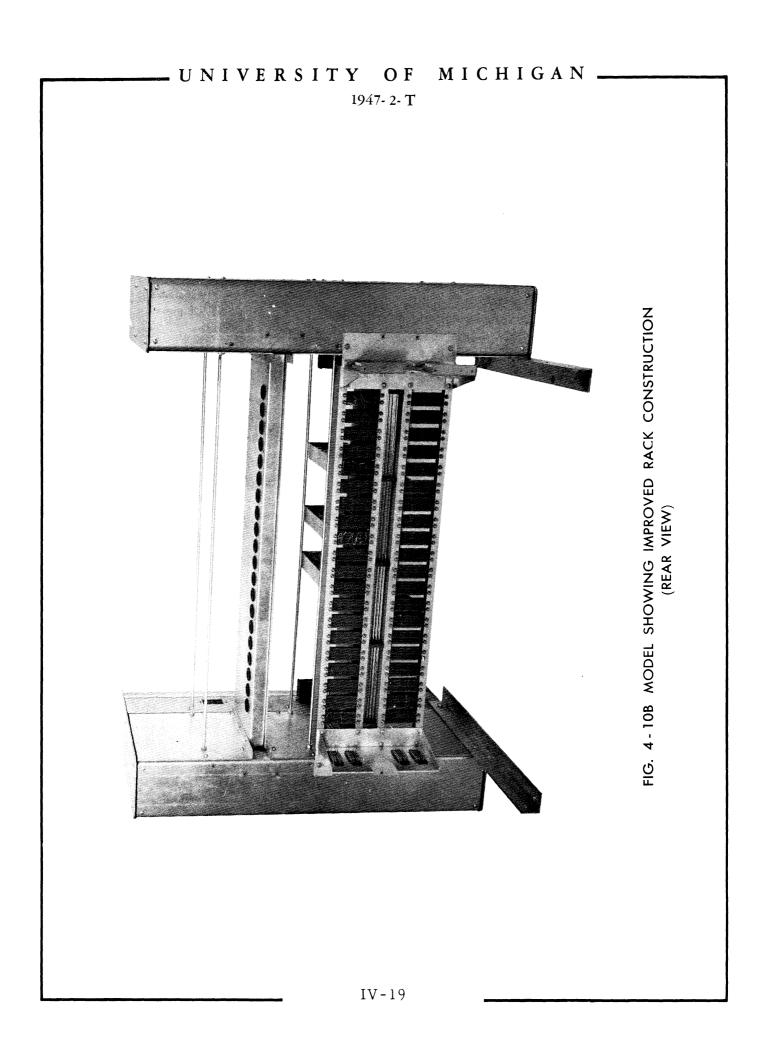

| 4-10B         | Model Showing Improved Rack Construction (Rear View)      | IV-19 |

| B-1           | Diode Gate Structure                                      | B-2   |

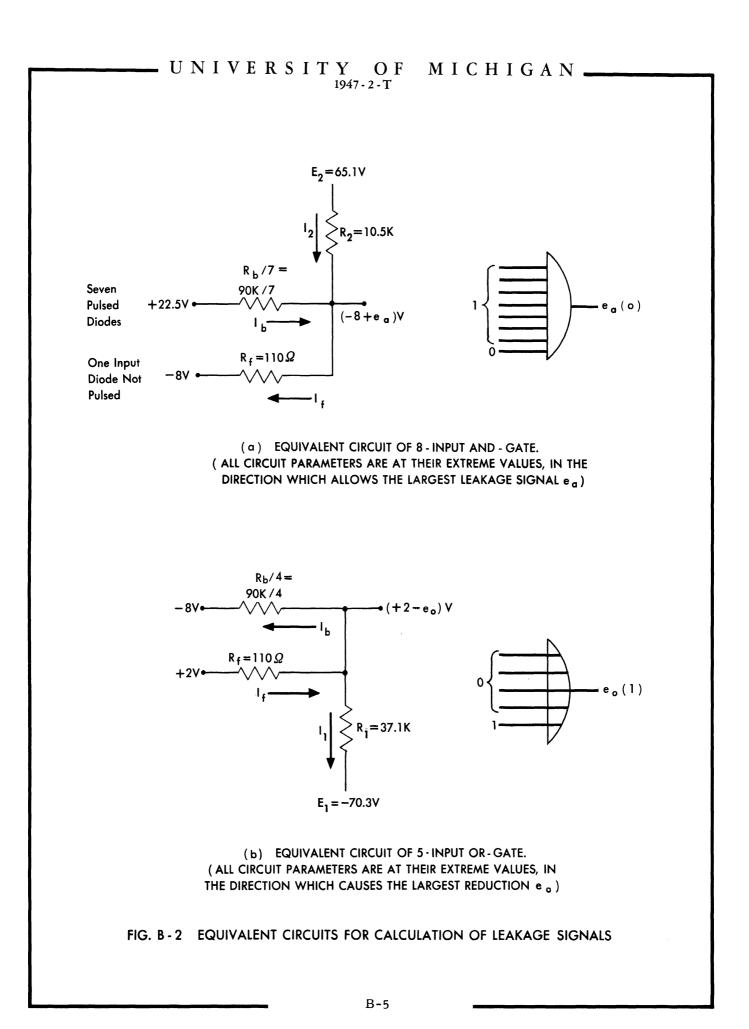

| B-2           | Equivalent Circuits for Calculation of Leakage<br>Signals | B-5   |

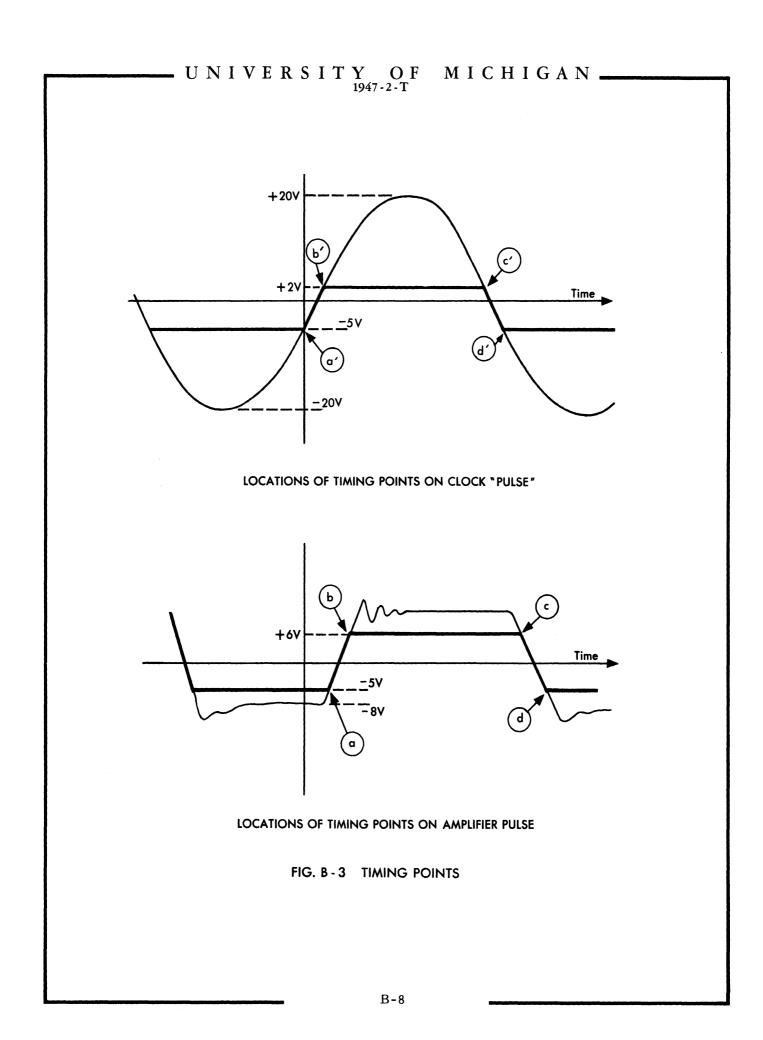

| B-3           | Timing Points                                             | B-8   |

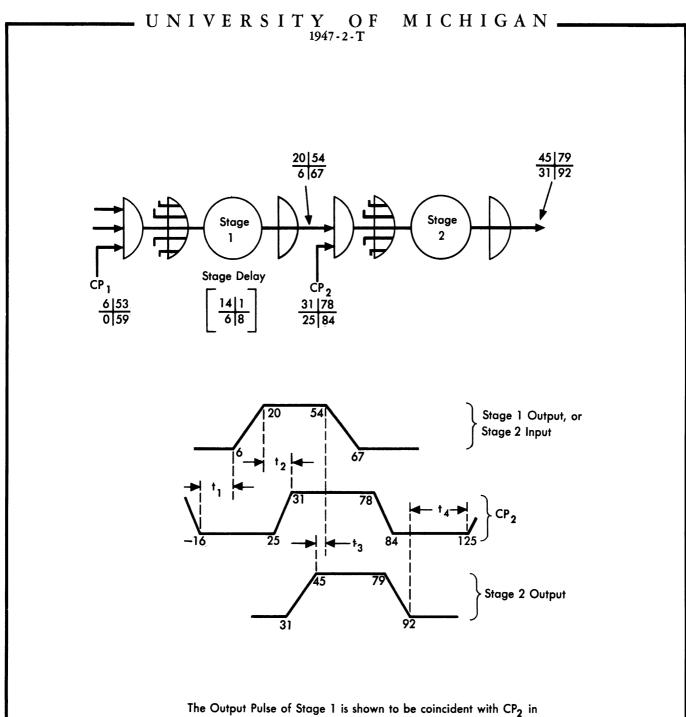

| B <b>-4</b>   | Timing of Positive Pulses                                 | B-13  |

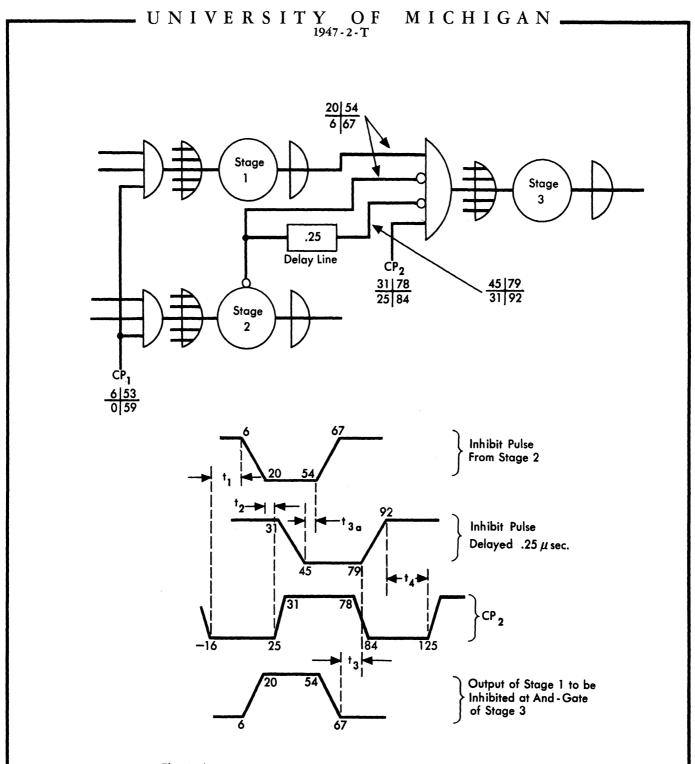

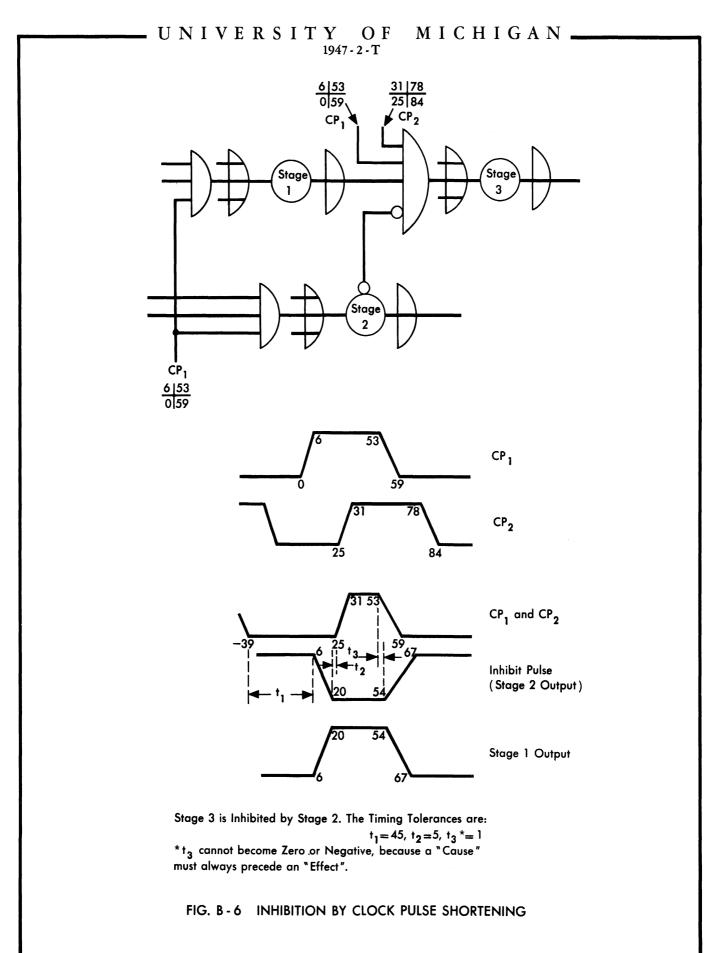

| B-5           | Inhibition by Pulse Stretching                            | B-14  |

| B-6           | Inhibition by Clock Pulse Shortening                      | B-15  |

# UNIVERSITY OF MICHIGAN \_\_\_\_\_

19**47-2-**T

## LIST OF TABLES

| Number      | Title                                                     | Page  |

|-------------|-----------------------------------------------------------|-------|

| 1 - 1       | Types of And-Gate Packages                                | I-12  |

| 1-2         | Equivalent Gate Load Ratings                              | I-14  |

| 1-3         | Types of Delay Packages                                   | I-15  |

| 1-4         | Maximum Power Requirements of Gate-Amplifier<br>Packages  | I-32  |

| 1-5         | Power Requirements of Termination and Or-Gate<br>Packages | I-33  |

| 2-1         | Truth Table for Half-Adder                                | II-13 |

| 2-2         | Digit Combinations                                        | II-14 |

| 3-1         | Operation of Sign Storage Flip-Flop                       | III-7 |

| A-1         | Physical Locations of First-Level Or-Gates                | A-2   |

| A-2         | Output Capability in Equivalent Gate Drives               | A-3   |

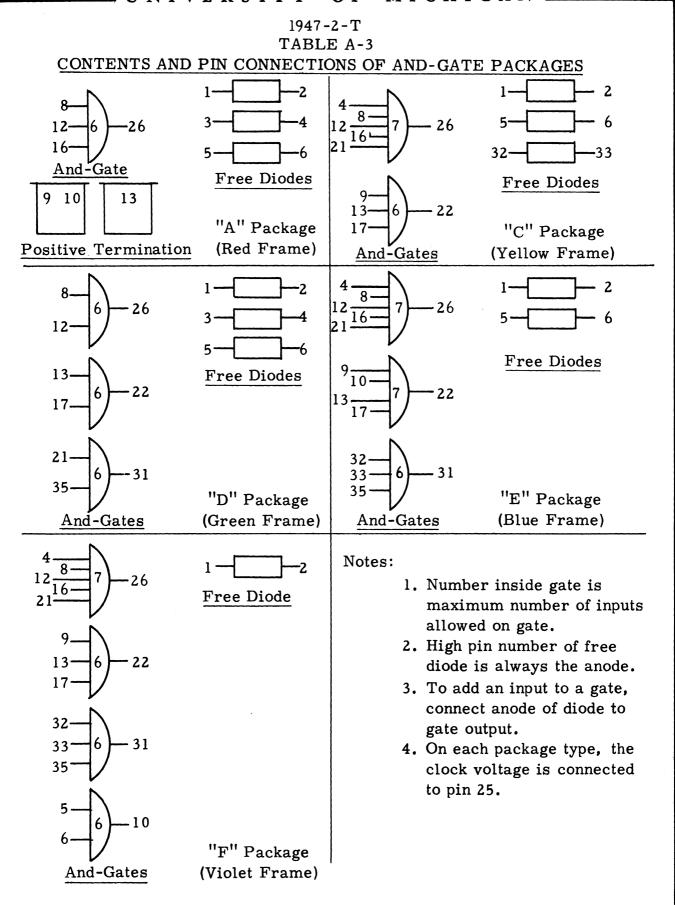

| A-3         | Contents and Pin Connections of And-Gate<br>Packages      | A-4   |

| A <b>-4</b> | Power Connections To Gate-Amplifier Package               | A-5   |

| A-5         | Contents and Pin Connections of Delay Line<br>Packages    | A-6   |

| A-6         | Contents and Pin Connections of Termination<br>Packages   | A-7   |

| A-7         | Contents and Pin Connections of Or-Gate Package           | A-8   |

| B-1         | Timing Numbers of Clock Pulses                            | B-9   |

## UNIVERSITY OF MICHIGAN

1947-2-T

#### FOREWORD

During the years 1951 to 1953, several digital computing equipments were developed at the University of Michigan,Willow Run Research Center (WRRC), under sponsorship of the United States Air Force. These included the Michigan Digital Automatic Computer, MIDAC, which is a general purpose electronic calculator (Ref. 1, 2, and 3), and the Michigan Digital Special Automatic Computer, MIDSAC, designed for realtime operation as an element of an automatic control system (Ref. 4). One aspect of the computer program concerned the development of a flexible and highly standardized set of electronic computing circuits which served as the principal building blocks for both computer designs. This report describes the results of that work.

The computing circuits consist of a group of pulse circuits which operate at a 1-Mc pulse repetition rate. The circuits provide, in conveniently packaged form, the functions of logical switching, pulse amplification, and delay storage. Each of the computers mentioned above uses more than one thousand of these packages to implement all computer functions with the exception of the memory and the input-output functions.

At the outset of the development program, it was apparent that several research laboratories had independently developed computing circuits which were potentially capable of meeting the requirements of the projected Michigan computers. Rather than repeat the initial work of these laboratories, it was decided that the University of Michigan group should select the existing circuit techniques which showed the most promise of quick and reliable operation, and devote its energies to the engineering improvement of these techniques.

After preliminary studies, the computing circuits developed by the National Bureau of Standards for use in the SEAC computer were selected as most appropriate to the present needs (Ref. 5). A cooperative development program was initiated involving WRRC and the National Bureau of Standards Electronic Computers Laboratory. A research and development group at the Air Force Missile Test Center at Cocoa Beach, Florida,

### UNIVERSITY OF MICHIGAN \_\_\_\_

1947-2-T

was also interested in furthering the NBS techniques, and constituted a third party in the cooperative effort.

This report describes the final packaged circuitry as used by WRRC in the MIDAC and MIDSAC computers. The report is in four parts. Part I describes the function, operation, and design of the packages, and includes a set of rules governing permissible interconnections between packages. Part II contains several examples of functional units within a computer which may be implemented by using the packaged circuits. Part III describes a simplified serial-binary arithmetic unit which can be assembled using the basic functional building blocks described in Part II. Part IV describes the constructional features of the packages and of the chassis and racks in which the packages are mounted.

In addition to the listed authors of this report, many other persons contributed to the circuit development at WRRC. Circuit design work was primarily carried out by J. Kaufman with assistance from R. Hock and B. Smith. Mechanical design was done by H. Bethel with assistance from W. Sutton. H. L. Garner was primarily responsible for the preparation of this report. The development program was under the technical supervision of J. E. DeTurk.

Ι

### DESCRIPTION OF COMPUTER PLUG-IN CIRCUITS

### 1.1 FUNCTIONAL ORGANIZATION OF CIRCUITS

Three functional types of equipment are generally required in the design of an electronic digital computer. These are the memory equipment, which is employed to store large quantities of numerical or instructional information for indefinite periods; the input-output portions, which provide a means for communication between the computer and the persons who operate it; and, finally, the pulse switching circuits, which govern the flow and manipulation of information within the machine. The packaged electronic circuits described in this report are of the third category; i.e., they perform elementary switching functions which can be compounded to yield the arithmetic, control, and timing operations which are essential to a digital computer.

Two theoretical requirements apply to circuitry for this purpose. The first is a requirement for logical completeness; i. e., enough different types of switches should be employed so that any conceivable logical structure can be implemented. The second theoretical requirement makes it necessary to store, or remember, an event (pulse) over some part of the computation time. In the circuits to be described, the logical operations "and", "or", and "not" are used to provide completeness. The physical circuits which implement these functions are called gates; the three types of gates employed are shown symbolically in Figure 1-1. The second essential property, that of memory, is obtained by means of electrical delay line.

In addition to the theoretical requirements, several practical considerations affect the design of computer circuitry. Imperfections in the physical structures which implement the logic cause pulse deterioration in the form of amplitude attenuation, pulse shape distortion, and variations in pulse timing. Thus there is a need for complete re-standardization of the power level, shape, and timing of every pulse after the pulse has passed through a few logical structures. In the MIDAC circuits, a maximum of three cascaded levels of logical switching operation and one level of logical

# UNIVERSITY OF MICHIGAN

1947- 2- T Symbol **Boolean Identity** Meaning a 🕳 Signal x occurs b • x when a or b or a+b+c+d=xc or d is present. с. d • Or - Gate a Signal y occurs b• У when a and b and  $a \cdot b \cdot c \cdot d = y$ c and d are present. C • d • And - Gate (with only positive inputs) a Signal y<sup>1</sup>occurs Ь when a and b ÿ١  $a \cdot b \cdot c \cdot d \cdot \overline{e} = y^{1}$ and c and not -d С and not -e are present 4 And - Gate (with three positive and two negative inputs) FIG. 1 - 1 SYMBOLIC REPRESENTATIONS OF GATES

delay are permitted before pulse amplification, retiming, and reshaping occur. Figure 1-2 (a) suggests the type of configuration in which these levels are assembled. (In a given configuration, the delay level may sometimes be omitted.) Circuit design factors require that the and-gate level and the two levels of or-gates occur in all but a few situations. Figure 1-2 (b) illustrates a situation where each gate associated with an amplifier is degenerate (has only one input).

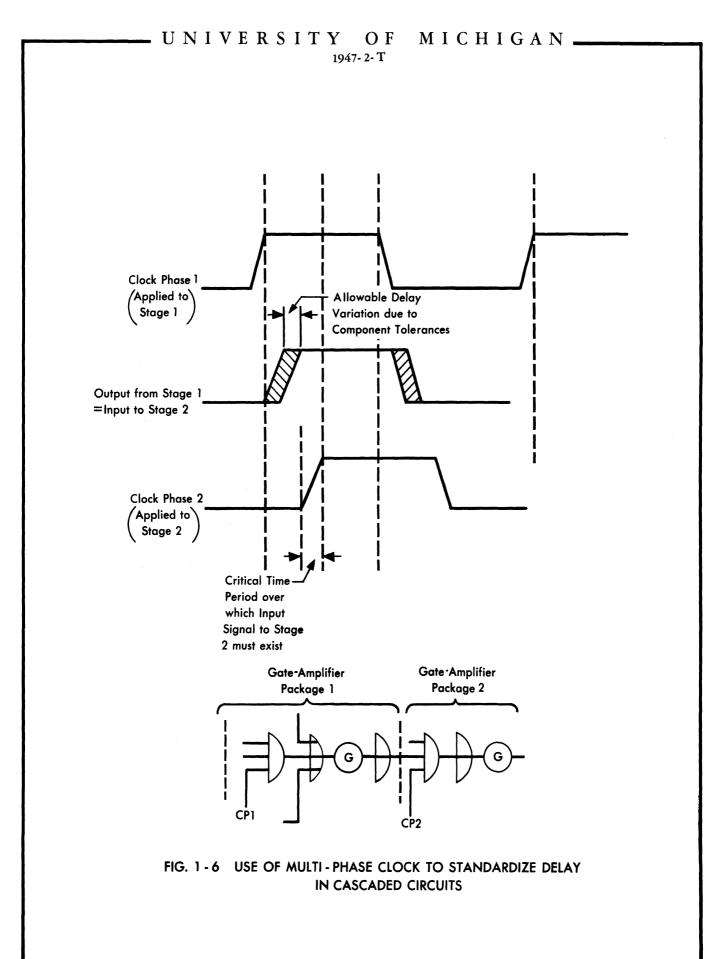

Some unavoidable delay occurs as a pulse is propagated through switching and amplification circuits. To avoid an uncontrolled accumulation of delay in a large ensemble of circuits, each configuration is operated so as to have a standardized delay of 1/4 microsecond, exclusive of the delay due to the logical delay elements. This delay is controlled by synchronizing each circuit with a master clock which operates continuously at 1 Mc. The master clock provides separate outputs at four equally spaced phases (i. e., at one-quarter-microsecond intervals), and successive circuits are synchronized with progressively advanced clock phases.

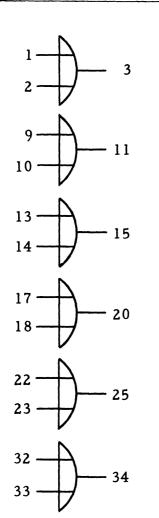

Five basic types of plug-in units are designed to implement configurations of the type shown in Figure 1-2. An amplifier package (Fig. 1-3) contains a second-level or-gate, an amplifier, and a degenerate, firstlevel or-gate (the latter gate is not always used). An and-gate package (Fig. 1-3) contains all functional and-gates which may be associated with a given amplifier. The and-gate package design has several variants, differing in the number of gates included (from one to four) and in the number of signal inputs to each gate (from one to seven). One amplifier package and one and-gate package plug together to form an integral plugin unit, and are always used in this combination. Such a combined unit is called a gate-amplifier package. Smaller packages, called "penthouses" (Fig. 1-3), are sometimes plugged into the amplifier package to augment the current capability of the degenerate or-gate at the amplifier output.

A delay package (Fig. 1-4) contains several pieces of electrical delay line which are used to delay pulses by discrete time intervals. A delay termination package (Fig. 1-4) consists of several terminating networks used to provide proper terminating impedances for the delay lines in delay

I-6

## UNIVERSITY OF MICHIGAN.

1947-2-T

packages. An or-gate package (Fig. 1-4) consists of several or-gates which may be used as needed to provide first-level or-gates.

### 1.2 DESCRIPTIONS OF PACKAGE TYPES

### 1.2.1 Gate-Amplifier Package

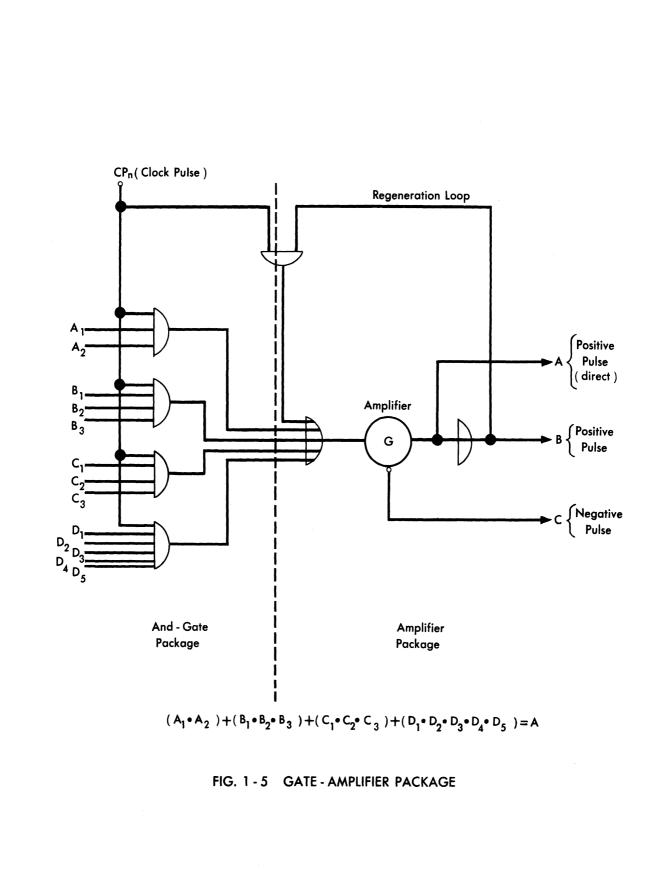

Figure 1-5 shows a symbolic representation of the gate-amplifier unit. The gates are implemented by passive networks consisting of germanium diodes and resistors. The amplifier is a single-tube pentode pulse amplifier with transformer-coupled output. Both positive and negative outputs are provided, and the positive output may be obtained either directly or through the degenerate or-gate.

Two features of this circuit provide for the standardization of the output pulse shape and the amplifier time delay. First, the clock signal is applied to one input of each and-gate; this procedure ensures that the leading edge of the amplifier excitation pulse cannot occur before the leading edge of the clock pulse. Second, the output of the amplifier is coupled to its own input through an and-gate which is clocked with the same clock phase. The resulting regeneration loop ensures that the excitation pulse, if once initiated, will continue for the entire duration of the clock pulse.

The clocking and regeneration action allows the package to produce a standardized output signal even though the signal inputs to the package are distorted in shape and are not precisely timed. Figure 1-6 illustrates the time relationships between two cascaded gate-amplifier circuits.

### 1.2.1.1 Package Variations

There are no variations of the amplifier package. There are five variations of the and-gate package, as indicated in Table 1-1.

The letters in the first column of the table identify each and-gate package type. The second column describes the package types in terms of the number of and-gates and the number of permanent inputs on each gate; for example, "5, 3" in the second line means that the Type C package contains two and-gates with five and three inputs respectively. As indicated in the third column, each package contains some "free diodes" which 1947- 2- T

### TABLE 1-1

### TYPES OF AND-GATE PACKAGES

| Package<br>Type | Permanently<br>Connected<br>Gate inputs | Free<br>Diodes | Maximum<br>Number of<br>Gate inputs |

|-----------------|-----------------------------------------|----------------|-------------------------------------|

| Α               | 3                                       | 3              | 6                                   |

| С               | 5,3                                     | 3              | 7,6                                 |

| D               | 2,2,2                                   | 3              | 6,6,6                               |

| $\mathbf{E}$    | 5,4,3                                   | 2              | 7,7,6                               |

| F               | 5, 3, 3, 2                              | 1              | 7,6,6,6                             |

are not connected directly to the gate circuits, but are, instead, independently connected to the package base pins. By means of jumper wires on the package receptacles, these diodes may be used to augment the number of signal inputs to the and-gates, at the rate of one diode for each added input. Column four indicates the maximum number of inputs which can be tolerated on each and-gate. When free diodes are used to augment gate inputs, they should be located in the same package as the gate (or in adjacent packages); otherwise excessive wiring capacitance will prohibit using the maximum number of inputs listed.

In addition to the listed components, the Type A package contains a positive delay-line termination network.

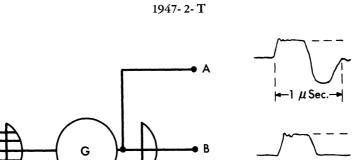

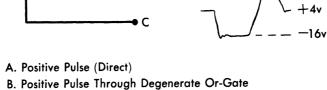

### 1.2.1.2 Amplifier Package Outputs

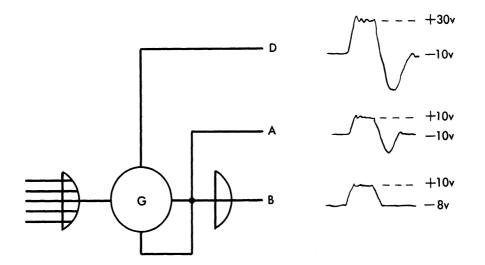

The output terminals of the amplifier package may be connected in either of two ways. The usual manner of connection provides three types of output signals, as illustrated in Figure 1-7 (a). The second type of connection, shown symbolically in Figure 1-7 (b), causes the two transformer output windings to be connected in series aiding. This connection makes available a positive pulse output, D (which has twice the amplitude of the normal positive output) in addition to the two positive outputs of normal amplitude. Note that with this connection the negative pulse output is not available.

# - UNIVERSITY OF MICHIGAN -

+10v \_10v

+10v

-8v

C. Negative Pulse

a. NORMAL OUTPUT LINES AVAILABLE FROM AMPLIFIER PACKAGE

- D. Double Amplitude Positive Pulse

- A. Positive Pulse (Direct)

- B. Positive Pulse Through Degenerate Or-Gate

b. OUTPUT OF AMPLIFIER PACKAGE USING SERIES CONNECTION OF SECONDARIES

#### FIG. 1-7 OUTPUTS OF AMPLIFIER PACKAGE

## UNIVERSITY OF MICHIGAN -

### 1947-2-T

Each of these outputs is used to drive a particular type of load. Output A is used to drive positive short-delay lines<sup>1</sup> and first-level or-gates. Output B is used to drive and-gates directly. Output C is used to drive negative short-delay lines and inhibit inputs to and-gates. Output D is used exclusively for driving positive long-delay lines.

For convenience, the amplifier power output requirements for all types of loads are expressed as integral multiples of a unit called an equivalent gate load. One equivalent gate load is a load which requires the same current as a single and-gate input. Table 1-2 shows the equivalent gate load ratings of the inputs to various circuits.

#### TABLE 1-2

### EQUIVALENT GATE LOAD RATINGS

| Type of Load                                                      | Number of equivalent gate loads |

|-------------------------------------------------------------------|---------------------------------|

| Single and-gate input                                             | 1                               |

| Positive (or negative) short-delay line                           | 2                               |

| Long-delay line                                                   | 8                               |

| Positive (or negative) or-gate driving<br>a single and-gate input | 1                               |

| Positive (or negative) or-gate driving<br>a short-delay line      | 2                               |

The amplifier package is capable of driving a maximum of sixteen equivalent gate loads from the combination of all output terminals. The degenerate or-gate output, B, is normally capable of driving only four and-gate inputs, leaving twelve equivalent gate drives for outputs A and C or A and D. The addition of one of two types of "penthouse" units (described in the following paragraph) increases the drive capability of terminal B to either ten or sixteen drives, leaving either six drives or no drives available at A or C.

<sup>1</sup>Short-delay lines provide from 0.25 microseconds to 2.00 microseconds delay, and long-delay lines provide from 2.25 microseconds to 4.00 microseconds delay.

# UNIVERSITY OF MICHIGAN.

1947-2-T

### 1.2.1.3 Penthouse Units

Penthouses (Fig. 1-3) are external plug-in units which are added to the amplifier package when more than four equivalent gates are to be driven from output B. A penthouse contains additional diodes which augment the current-carrying capacity of the degenerate or-gate output. A type P<sub>1</sub> penthouse is used when five to ten equivalent gate drives are required, and a type P<sub>2</sub> penthouse is used when eleven to sixteen equivalent gate drives are required.

### 1.2.2 Delay Package

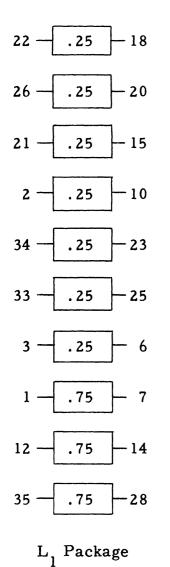

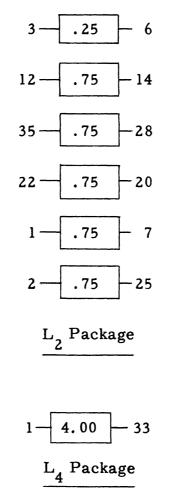

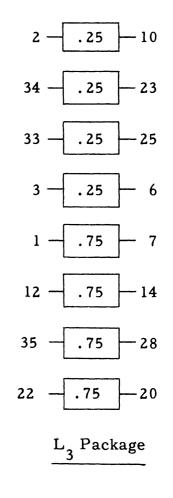

The delay package (Fig. 1-4) contains sixteen "sticks" of distributedparameter delay line. Each delay line stick provides a pulse delay of 0.25 microseconds. There are four variations of this package, differing only in the way the delay line sticks are pre-connected. Table 1-3 lists the delay combinations in the four types of delay packages.

### TABLE 1-3

| Package<br>Type | Number of 1/4-micro-<br>second delays | Number of 3/4-micro-<br>second delays | Number of<br>4-microsec-<br>ond delays |  |

|-----------------|---------------------------------------|---------------------------------------|----------------------------------------|--|

| L <sub>1</sub>  | 7                                     | 3                                     | 0                                      |  |

| L <sub>2</sub>  | 1                                     | 5                                     | 0                                      |  |

| L <sub>3</sub>  | 4                                     | 4                                     | 0                                      |  |

| $L_4$           | 0                                     | 0                                     | 1                                      |  |

### TYPES OF DELAY PACKAGES

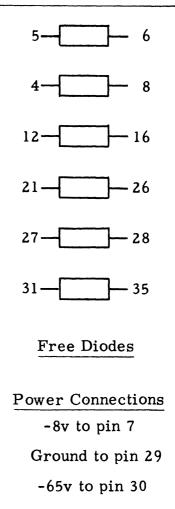

### 1.2.3 Termination Package

Each termination package (Fig. 1-4) consists of ten sets of dioderesistor networks. Each set provides the proper electrical terminations for both the input and output of one delay line. The termination networks contained in any package are of two types, one for positive pulses and the

other for negative pulses. There are two variations of the termination package. The  $T_1$  package contains eight sets of termination networks for positive pulses and two sets for negative pulses. The  $T_2$  package contains five sets of termination networks for positive pulses and five sets for negative pulses.

A portion of the termination network consists of a degenerate or-gate which drives the delay line input. The number of signal inputs to this or-gate can be augmented by free diodes, thus providing the ability to drive a single delay line from several independent packages. This augmentation applies to both positive and negative termination networks. Positive termination networks can also be converted to multiple-input, first-level or-gates suitable for driving and-gates.

### 1.2.4 Or-Gate Package

The or-gate (Type R) package is employed when termination networks or free diodes are not available for constructing first-level or-gates. An or-gate package contains six two-input or-gates for positive pulses, and six free diodes; the free diodes may be used to augment the number of gate inputs.

### 1.3 INTERCONNECTION OF PACKAGES

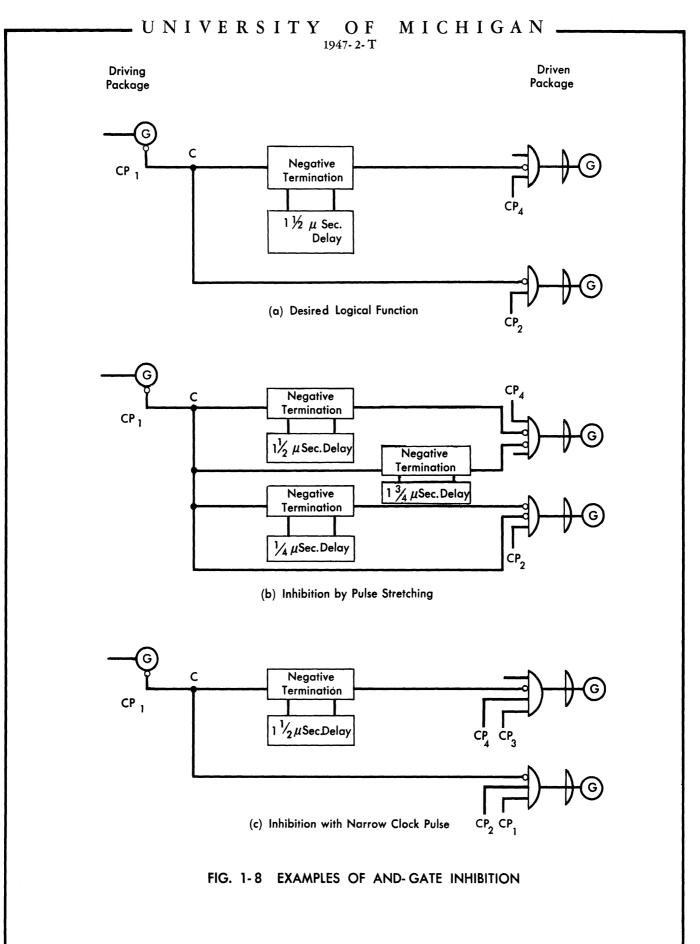

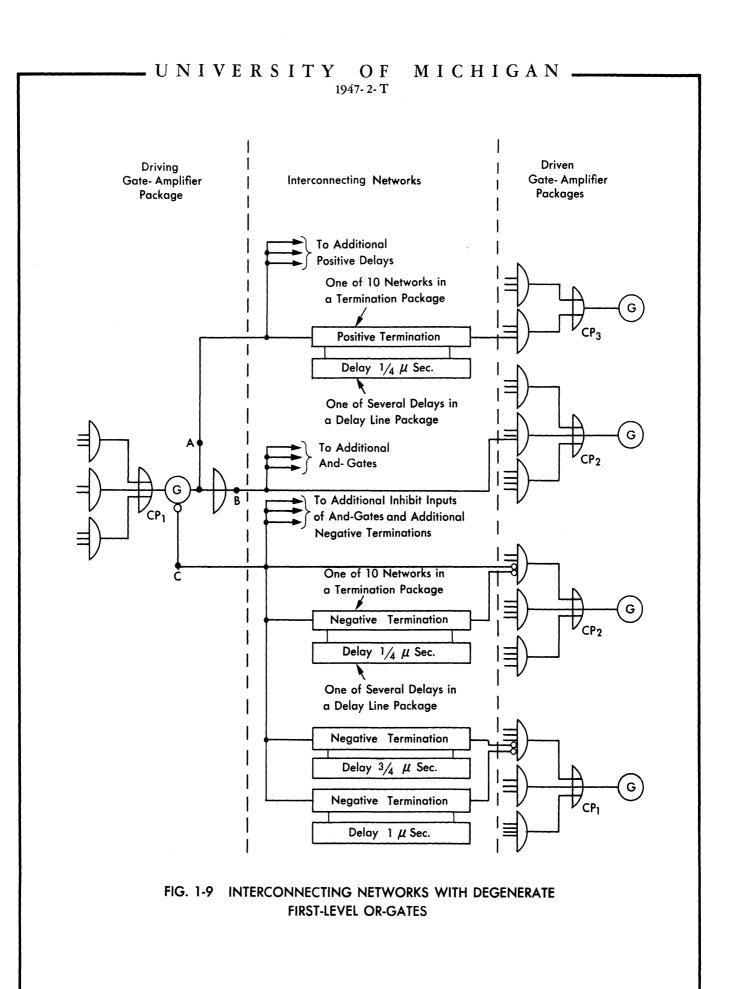

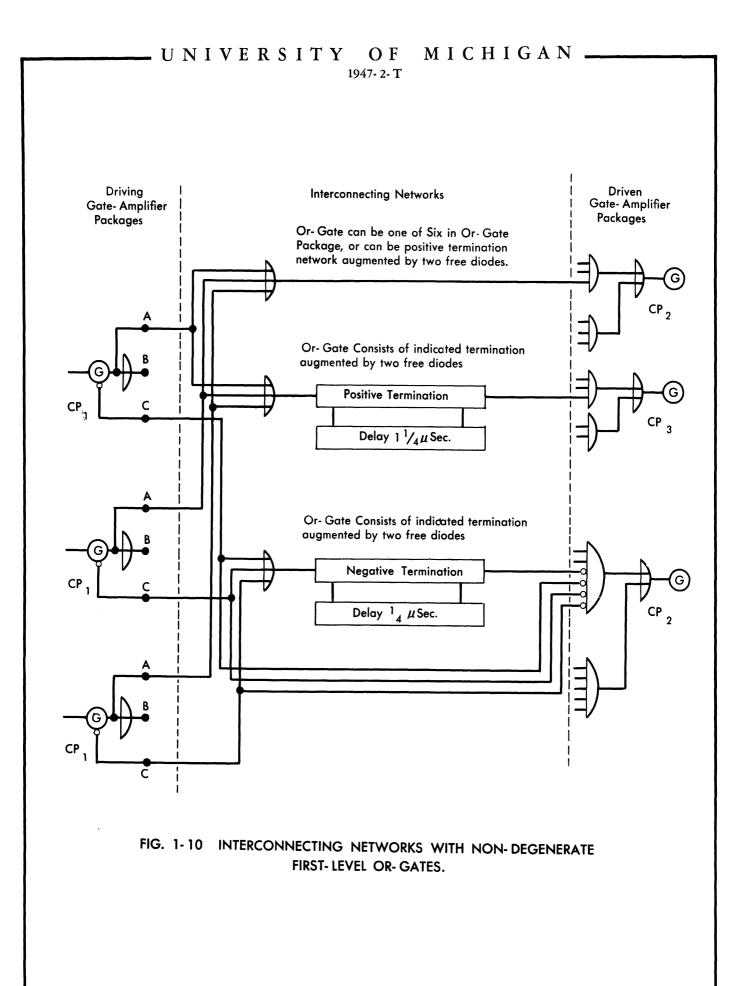

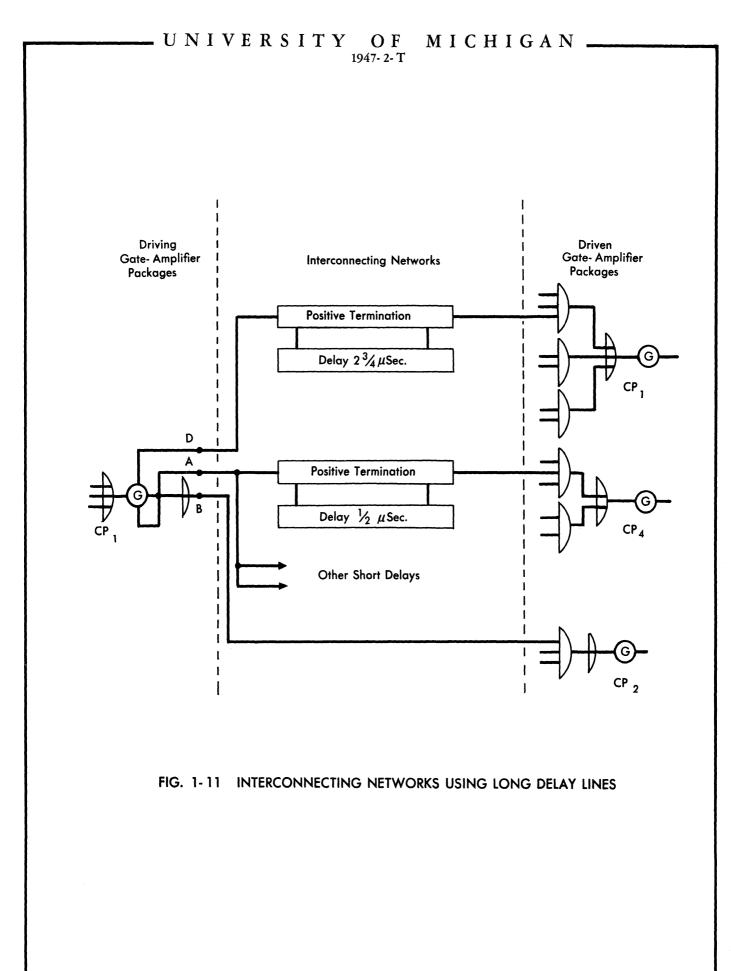

The permissible ways in which packages may be interconnected are illustrated in Figures 1-8, 1-9, 1-10, and 1-11.

Figure 1-8 illustrates important rules concerning the application of negative pulses to and-gates in order to realize the "not" function. Figure 1-8 (a) shows a desired logical function involving inhibition of two and-gates of different clock phases. Parts (b) and (c) of Figure 1-8 show two different methods for using the packaged circuits to realize this function. In Figure 1-8 (b), each and-gate to be inhibited requires two separate paths from the driving package to two separate inputs of the gate. One of these paths is the functional path shown in part (a) of the figure. The other path contains an additional delay of 1/4 microsecond. The effect of the delay path is to increase the duration of the negative signal at the driven gate, thus ensuring that reliable inhibition occurs.

I-19

## UNIVERSITY OF MICHIGAN -1947-2-T

Figure 1-8(c) shows an alternative method for achieving the functions shown in part (a). Here, each gate to be inhibited is clocked with two adjacent clock phases. One clock input is the normal clock input to all gates of the package. The second clock input is to the particular gate being inhibited. The effect is to decrease the period during which the gate is sensitive, thereby ensuring that reliable inhibition occurs.

Figure 1-9 shows examples of interconnections in which first-level or-gates are degenerate and delays are two microseconds or less. Figure 1-10 shows examples of interconnections in which non-degenerate, first-level or-gates occur and delays are, again, two microseconds or less. Figure 1-11 shows examples of interconnections in which longdelay lines occur. These figures illustrate most of the rules for interconnecting packages. They also illustrate correct usage of the clock pulses, and indicate the methods for obtaining first-level or-gates.

There are restrictions on the length of signal wires which can be used to interconnect packages. Consequently the computer designer must exercise skill and judgment in planning the location and utilization of packages. Important factors influencing package groupings are:

- 1. Signal wires should not be shielded,

- 2. The wires connected to the output terminals of an amplifier package can be up to fifty feet in length,

- 3. All other signal wires should be short,

- 4. Free diodes should be located in the same package as the gate which they are used to augment, or in an adjacent package,

- 5. A delay line package should be adjacent to the package containing its terminations,

- 6. The signal wire from a delay line output to the and-gate which it drives should be not more than one or two "inter-package" distances in length.

## UNIVERSITY OF MICHIGAN.

1947-2-T

### 1.4 CIRCUIT OPERATION

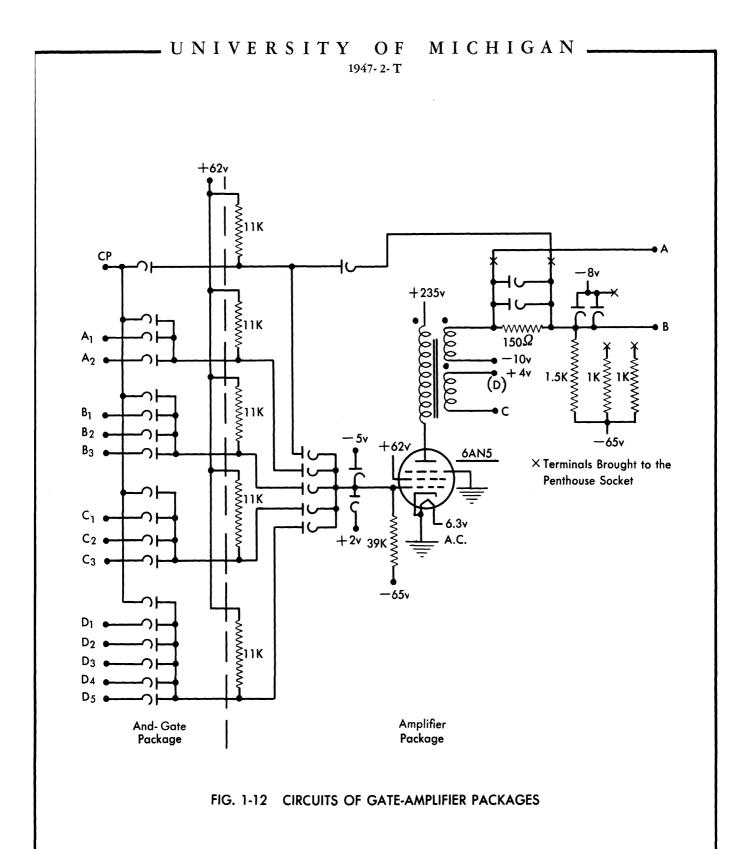

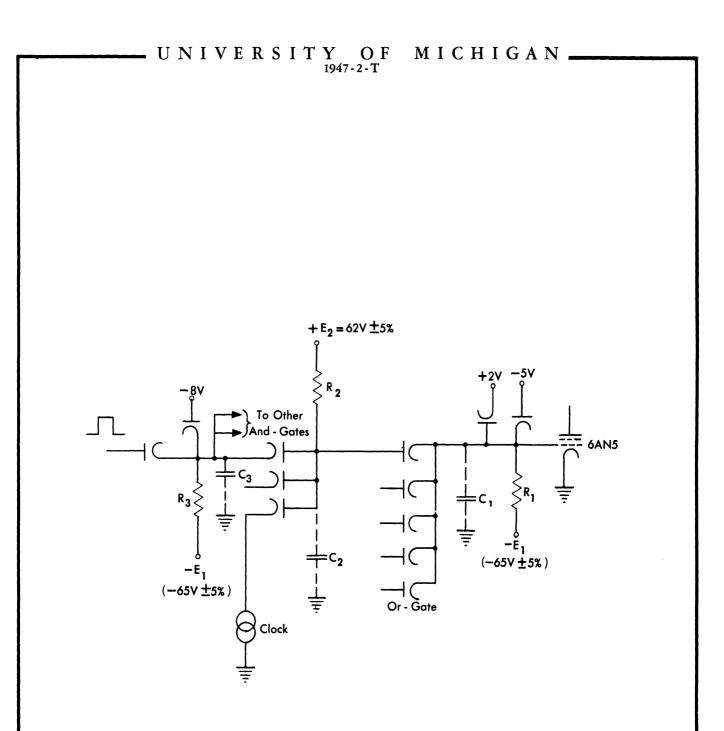

Figure 1-12 shows schematically the circuit of the gate-amplifier package which was symbolically represented in Figure 1-5. Elements to the left of the dashed line are located in the and-gate package and those to the right are in the amplifier package.

### 1.4.1 The Diode Gates

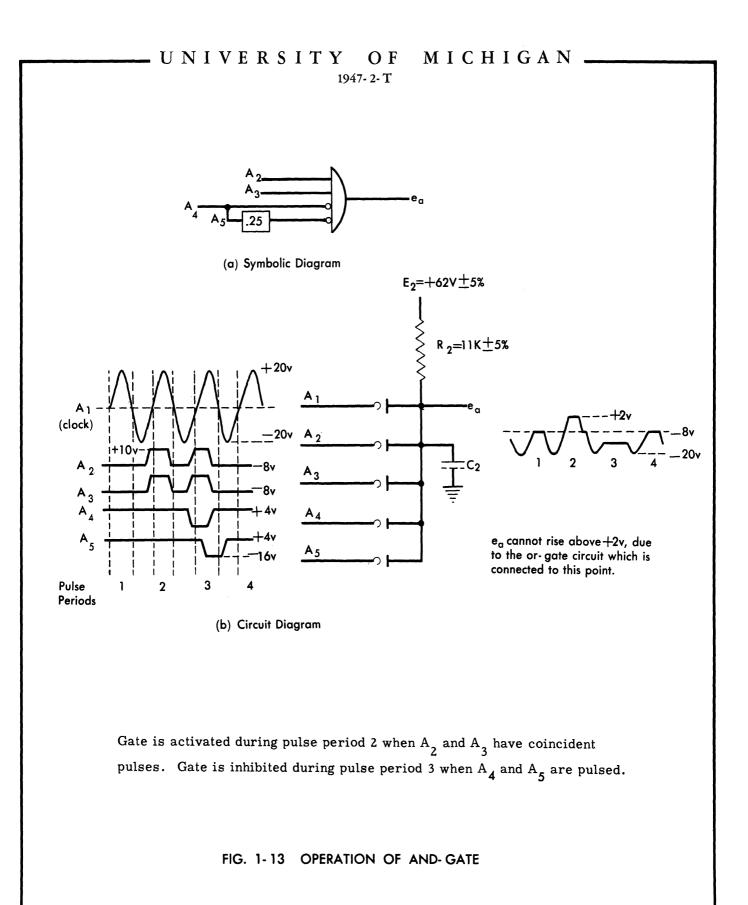

An and-gate is shown in Figure 1-13. If the diodes are assumed to be ideal and the circuit is assumed to have no external load or shunt capacitance, then the output voltage  $e_a$  is equal to the most negative of the several input voltages. An output pulse will occur only when all inputs are simultaneously pulsed positive. The waveforms on the figure illustrate the operation of the gate under actual conditions. With the gate closed, the output follows the clock voltage during negative half-cycles of the sinusoidal clock signal. During positive half-cycles of the clock, the output is prevented from rising above -8v in the absence of positive pulses at other signal inputs. When positive signals are present at all signal inputs, the gate output tends to follow the positive half-cycle of the clock voltage. It is prevented from rising above +2v by a bumper diode not shown in Figure 1-13.

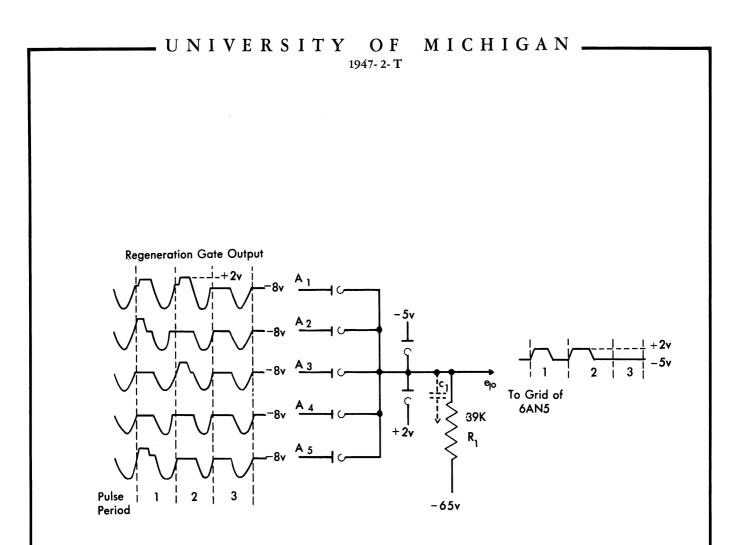

Under ideal conditions, the output signal of the or-gate of Figure 1-14 is always equal to the voltage of the most positive input. A positive pulse on any input will appear as a pulse at the output. The or-gate output is clamped at -5v, which is three volts positive with respect to the most positive input expected under no-signal conditions with ideal components. Thus 3v of spurious signals or noise, due to imperfections in the andgate or stray couplings between signal wires, can be tolerated. A bumper diode at the or-gate output limits the signal to a peak value of +2v.

## 1.4.2 Amplifier

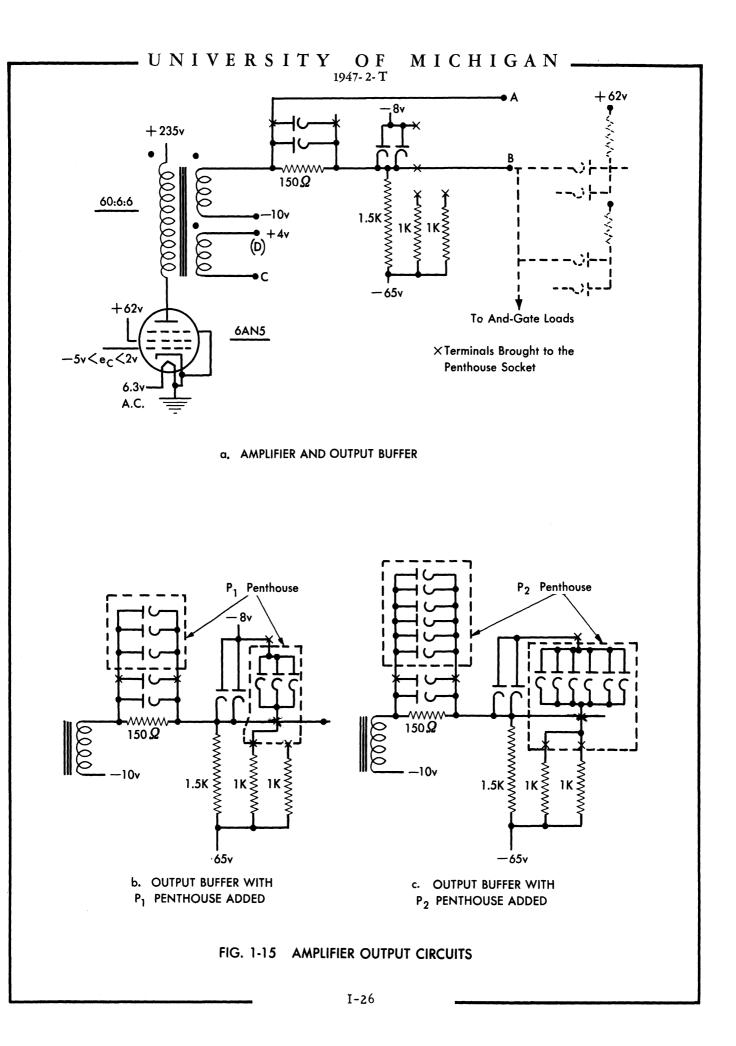

The amplifier uses a type 6AN5 high-transconductance pentode in the circuit shown in Figure 1-15. The two piece core of the pulse transformer is a miniature pot type made from a manganese-zinc ferrite material, and is designated as Part No. 7F160 by its manufacturer, Ferrox-cube Corporation of America. The windings are on a ring-shaped nylon

I-24

Or-gate pulses during time 1 and 2, due to pulses on  $\rm A_2$  and  $\rm A_5$  at time 1, and pulses on  $\rm A_3$  at time 2.

$A_1$  is the output of the regeneration gate which spreads the output pulse  $e_0$  to a full pulse width.

### FIG. 1-14 OPERATION OF OR-GATE

bobbin which has a slot for each of the three windings. The primary winding consists of 60 turns of No. 38 A.W.G. triple Formax coated wire. The two secondaries each have 6 turns of No. 31 A.W.G. triple Formax coated wire. The primary inductance is between 3 and 4.5 millihenries (measured at 250 kc). The Q averages about 52, and must be at least 35. The ferrite core has very low core loss and high effective permeability at 1 Mc. The method of construction of the pulse transformer keeps the leakage inductances at a minimum.

The circuit parameters of the amplifier stage are chosen so that the tube operates along a load line giving optimum power output. Maximum power output would be obtained by choosing the operating point of the tube at the knee of the plate characteristic. The actual operating point is chosen so that low-limit<sup>1</sup> tubes in conjunction with a three-millihenry primary inductance will operate just at the knee. Thus, all tubes will bottom, i.e., operate with plate voltage swinging below the knee.

The turns ratio was chosen to deliver maximum current to the load, consistent with the required rise time of 0.1 microsecond and a voltage swing of 20v. The largest resistance which loads the secondary is 1500 ohms, the value of the pull-down resistor in the output buffer. If a P 2 penthouse is used, this resistance is decreased to 375 ohms. The corresponding maximum load is a peak positive current of 160 ma. The capacitive load on the secondary may be as much as 300 micromicrofarads for a maximum and-gate load.

At the completion of a positive pulse, the plate current drops to a very small value and the plate resistance of the tube becomes essentially infinite. In addition, the load impedance on the secondary is decoupled by the diodes of the output buffer. The magnetizing current left in the transformer now excites an oscillation of the open circuit inductance and the plate capacitance. This oscillation carries the pulse to a negative peak of about -40v. The period of this oscillation is slightly longer

<sup>1</sup>A low-limit tube is one which conducts 45 ma of plate current when  $E_{plate} = E_{screen} = +62v$ ,  $E_{grid} = +2v$ , and  $E_{fil} = 5.7v$  (Sec. 1.5.2).

I-27

than 1 microsecond. If the oscillation were permitted to go unchecked, a spurious positive pulse would be picked up through the regeneration gate, which would broaden it to an almost full-sized output pulse. A damping resistor placed across the output buffer diodes is used to prevent such spurious outputs from occurring. The damping resistor is chosen so that the pulse is slightly underdamped instead of critically damped, allowing a small positive bump to appear following a single pulse. However, the bump is never enough to trigger the regeneration loop, since at least a 2v pulse is required to decouple the bumper diodes at the output buffer.

If the damping resistance in series with the bumper diodes of the output buffer is too low, then at the next pulse time the over damped transformer will have a magnetizing current which subtracts from the charging current available at the beginning of the next pulse. Since the open circuit inductance of the transformer is allowed to vary from 3.0 to 4.5 millihenries and the damping impedance depends on the characteristics of the diodes of the output buffer, it is obvious that it is not always possible to have zero magnetizing current at the beginning of the next pulse. In a train of pulses, the residual magnetizing current at the beginning of each pulse increases with each pulse until it approaches a stable value. The leading edge of the Nth pulse is then delayed by a measurable amount when N is larger than five or six (Sec. B. 3.4 of Appendix B). The output pulse suffers additional delay due to the time necessary to charge the plate and load capacitance and also due to the effect of the leakage inductance.

### 1.4.3 Output Buffer

The normal method of driving and-gates from the output of the amplifier package is through the output buffer. An important consideration in the design of the buffer is the value of the pull-down resistor. The resistor value must be chosen low enough to give the output pulse a fall rate of at least 75v per microsecond. Since the normal load is the and-gates of other packages, the capacitive load is the wiring capacity of the leads to the and-gates as well as the stray capacity,  $C_2$ , at the and-gate itself. With no penthouse added, the pull-down current is approximately 40 ma. And-gates which the buffer drives require somewhat less

than 10 ma per input, and the pull-down current is enough to accommodate a four and-gate load as an external load in addition to the and-gate associated with the package internal regeneration loop. A  $P_1$  penthouse increases the pull-down current to 100 ma; when a  $P_2$  penthouse is used instead, it increases the pull-down current to 160 ma. As shown in Figure 1-15, the diodes added to the output buffer by the penthouse units are to accommodate the additional forward current when more than four gates are to be driven.

# 1.4.4 Pulse Delay Units

Pulse delays in integral multiples of 0.25 microsecond up to a maximum of 4.00 microseconds are obtained through the use of the delay line and termination packages. Each delay line package contains sixteen sticks of electrical delay line, each with 0.25 microseconds delay. Because of the frequent occurrence of certain delay times, the 16 sticks are preconnected within the package to provide the four package types described in Section 1.2.2.

The delay-line sticks are cut from a continuous roll of distributedparameter delay line manufactured by the James Millen Company. The distributed inductance is formed by a single layer helix of fine Formax insulated wire which is wound on flexible plastic tubing. Covering the helix is a layer of thin Teflon tape, and surrounding this is a wire braid. The distributed capacity is that between the helix and the braid. In addition, the helix is covered by a thin layer of aluminum paint, which introduces mutual capacity between coils to compensate for the inductance lost as frequency increases. The wire braid is grounded through a loop of wire soldered around one end of the braid. Care must be taken not to ground the braid at other points, for this will affect the characteristics of the line. At one end of the delay-line stick, the grounded braid is cut back so that a section of the helix is exposed. The exposed helix forms a small inductor which tends to compensate for the wiring capacity of the long lead-in wire at this end.

The 0.25-microsecond delay-line sticks are calibrated to an accuracy of  $\pm 0.003$  microsecond. Thus the maximum error for four microseconds of delay is  $\pm 0.048$  microsecond. The characteristic impedance of the

# UNIVERSITY OF MICHIGAN.

1947-2-T

line is 1350 ohms and the length of a 0.25-microsecond stick is approximately 5-3/4 inches.

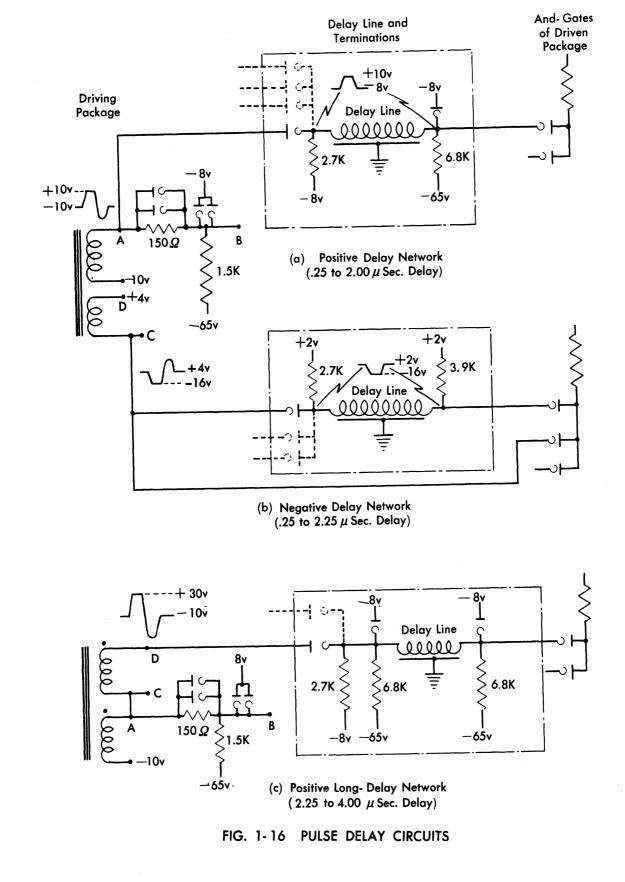

Figure 1-16 shows the circuits used to terminate delay lines and delay-line interconnections to the gate-amplifier packages.

For positive pulses, the output termination is a 6.8K resistor to -65v. Reflections which occur due to the impedance mismatch at the output end of the delay line are attenuated in the line and almost completely absorbed in the 2.7K input termination resistor. This resistance should be as large as possible, consistent with minimizing reflections, so that unnecessarily large driving currents are not required. A buffer diode at the input disconnects the pulse transformer during the negative backswing. The input termination may be used as an or-gate by the addition of free diodes as indicated by the dotted lines in Figure 1-15 (a).

For negative pulses, a 3.9K resistor is used as an output termination. Again, any returning reflections are sufficiently absorbed in the 2.7K input termination. A buffer diode at the input disconnects the pulse transformer during the positive backswing. An or-gate for negative pulses may be made by adding free diodes to the input termination as shown by the dotted lines in the figure.

For positive pulse delays greater than 2 microseconds, the pulse attenuation becomes too great to allow the use of pulses of normal amplitude. A series connection of the two-pulse transformer secondaries in the driving package is then used to provide a pulse of twice the normal amplitude. This connection, Figure 1-16(c), provides sufficient drive for delay lines whose delay is between 2 and 4 microseconds.

Attenuation, distortion, and the accumulation of time delay errors become larger as the length of a delay is increased. These factors limit the maximum permissible delay between any two amplifier packages to 4.00 microseconds. 1947- 2- T

I-31

# UNIVERSITY OF MICHIGAN.

# 1947-2-T

### 1.5 ELECTRICAL SPECIFICATIONS

### 1.5.1 Voltage and Current Requirements of Packages

Nine voltages are required to operate the gate-amplifier package. The maximum current requirements (Table 1-4) occur when an F package is used in conjunction with an amplifier package. These current values are taken with the package either pulsing continuously or not at all, depending on which condition draws the greater current. All supply voltages must be within  $\pm 5$  per cent of the values given in Table 1-4.

### TABLE 1-4

### MAXIMUM POWER REQUIREMENTS OF GATE-AMPLIFIER PACKAGES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6.3v a-c          | -65v             | -10v             | -8v              | -5v               | +2 v           | +62v           | +235v          | Total<br>Power       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|------------------|-------------------|----------------|----------------|----------------|----------------------|

| <b>N</b> ew 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 199 |                   |                  | (mill            | iampe            | eres)             |                |                |                | (watts)              |

| No penthouse $P_1$ penthouse $P_2$ penthouse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 450<br>450<br>450 | 42<br>100<br>160 | 40<br>6.2<br>-30 | 80<br>110<br>130 | 1.4<br>1.4<br>1.4 | 10<br>10<br>10 | 52<br>50<br>48 | 24<br>27<br>30 | 15.8<br>20.1<br>25.0 |

The negative output winding of the pulse transformer is usually returned to +4v. If the maximum load is applied to this winding, a maximum current of 50 ma is required; and, if no load is applied, the current is zero. For this reason the requirement on the +4v supply is not included in the table.

The delay line package requires only a ground connection. The termination packages require -8v, +2v, and -65v, and the or-gate package requires -8v and -65v. Approximate maximum current requirements for these packages are shown in Table 1-5. These values are for a continuous train of pulses.

# UNIVERSITY OF MICHIGAN -

# 1947-2-T

### TABLE 1-5

POWER REQUIREMENTS OF TERMINATION AND OR-GATE PACKAGES

|                             | -8v | +2v<br>(milliamperes) | -65v |

|-----------------------------|-----|-----------------------|------|

| Package Type T <sub>1</sub> | 70  | 11                    | 90   |

| Package Type T <sub>2</sub> | 44  | 27                    | 55   |

| Package Type R              | 44  | 0                     | 55   |

### 1.5.2 Component Tolerances

All resistors must be  $\pm 5$  per cent grade and should be rated at twice the operating power dissipation.

The 6AN5 tubes must, when operated with +62v on both screen and plate, pass the following tests:

- 1. Plate current must be more than 45 ma when the grid is at +2v and filament at 5.7v,

- 2. The difference between the plate current with the grid at +2v and filament at 5.7v and the plate current with the grid at -6v and filament at 5.7v must be more than 42 ma,

- 3. The plate current must not exceed 10 ma with the grid at -6v and the filament at 5.7v,

- 4. The difference between the plate current with the grid at +2v and the filament at 6. 3v from the plate current with the grid at +2v and the filament at 5. 7v must not be greater than 6 ma. However, if the plate current in the first test is greater than 55 ma, a decrease of 8 ma is permissible.

The diodes must pass the following tests:

1. The voltage drop with 20 ma of forward current must be less than 2v before soldering into the circuit and less than 2.2v after soldering,

# \_UNIVERSITY OF MICHIGAN \_\_\_\_\_

### 1947-2-T

- 2. With 40v of inverse voltage, the current must not be greater than

- a. 250 microamperes before soldering,

- b. 300 microamperes after soldering into package,

- c. 350 microamperes in operational use.

The pulse transformer must have a primary inductance not less than 3.0 nor more than 4.5 millihenries and must have a Q greater than thirty-five.

### UNIVERSITY OF MICHIGAN

1947-2-T

Π

### ASSEMBLY OF STANDARD PACKAGES TO OBTAIN FUNCTIONAL UNITS

The purpose of this section is to illustrate how functional structures of a computer are constructed from the basic packaged circuits described in the previous section. These include and-gates, or-gates, delay lines, and amplifier packages.

The symbolism which is employed in this section is similar to that of Section I. For brevity, the regeneration loop between the amplifier output and input is not shown in any of the diagrams in this section. However, it is to be understood that this loop always exists. For further simplification, both positive and negative amplifier outputs are represented by one line. This should cause no confusion since only an output which drives an inhibit input to a gate must be the negative output of the amplifier. It is also to be understood, but not indicated, that delay lines longer than 2 microseconds are driven with double-amplitude pulses. A rectangular symbol is used to indicate a delay line and its termination networks. The number inside the rectangle is the delay in microseconds. The general rules stated in the previous section, concerning maximum gate-drive capabilities and timing, are applicable to the following discussion and indeed must be rigidly adhered to.

In presenting the basic circuits, the logical symbols "and" and "or" (Fig. 1-3) are used, since this type of presentation provides a concise and compact representation of the circuit function. Because a delay of one clock phase occurs in each amplifier package the notation  $CP_n$  (n = 1,2,3,4) is used at package inputs and outputs to indicate relative pulse times. The simpler circuits are discussed first; then combinations of the simple circuits are used to obtain more elaborate functional units.

### 2.1 STORAGE LOOP

A storage loop provides for the recirculation of N information pulses in a closed loop N microseconds long at a pulse repetition frequency of one megacycle. The ability to read out, read in, or modify stored 1947-2-Т

information is also provided. Electromagnetic delay lines are used as the storage elements. The other requirements are obtained by proper configurations of and-gates and or-gates. An amplifier is required because of the losses encountered in the gates and the delay line.

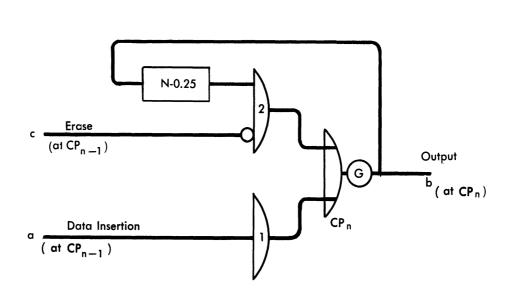

The basic storage loop is shown in Figure 2-1. Pulses in the storage loop (composed of the delay line, the amplifier, and gate 2) continue to circulate unless an inhibit pulse is applied on line  $\underline{c}$  at phase  $CP_{n-1}$ . The information in the loop is available at the output of the amplifier at  $CP_n$ . Modification of stored information is accomplished by applying information pulses on  $\underline{a}$  at  $CP_{n-1}$  and simultaneous inhibit pulses on  $\underline{c}$ .

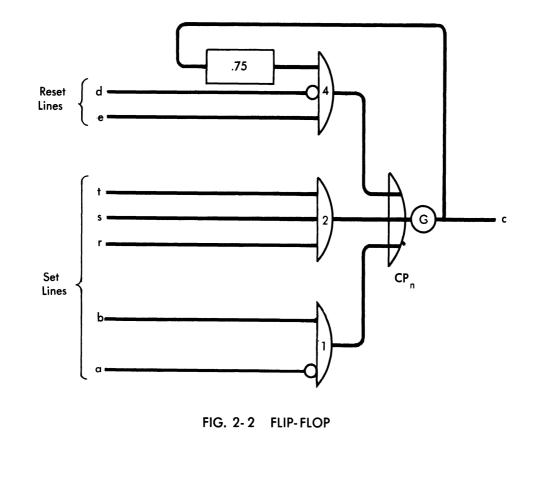

If N = 1 (for which case a .75-microsecond delay line is used), the simple storage loop becomes a "dynamic flip-flop". This flip-flop is set to its pulsing state, called its "one" state, by a pulse on <u>a</u> at  $CP_{n-1}$ . The output is then a train of pulses at  $CP_n$ . The flip-flop is reset to its quiescent state, called its "zero" state, by an inhibit on <u>c</u> at  $CP_{n-1}$ . In this state the output provides no pulses. Thus the flip-flop has two stable states, the output being either a train of one-megacycle pulses or no pulses.

An example of a flip-flop is shown in Figure 2-2. This flip-flop is set to its "one" state by  $(t \cdot s \cdot r) + (b \cdot \bar{a})$  at  $CP_{n-1}$ , and is reset to its zero state by  $(\bar{e} + d)$  at  $CP_{n-1}$ .

Figure 2-3 is an example of a long storage loop. Information is entered into the loop at gate 1. An information pulse is erased from the loop by a pulse on <u>d</u> at  $CP_{n+1}$ . The length of the loop is either 11, 12, or 13 microseconds, depending on the control pulses on <u>b</u> and <u>c</u>. Such provision for shortening or lengthening the loop permits information in the loop to be shifted right or left relative to some set of timing pulses.

### 2.2 TIMING-PULSE GENERATOR

In serial computing systems it is necessary to be able to identify specific digits within a word. This is accomplished by providing a unique timing pulse corresponding to each digit position. Such pulses are provided by a timing-pulse (T-pulse) generator.

II-4

As an example of a timing-pulse generator we shall discuss a generator having a 12-microsecond period. An economical method for obtaining these pulses uses a 3-microsecond count-down loop in conjunction with a 4-microsecond count-down loop. Specific outputs of the two loops can be combined in and-gates, to provide a T-pulse at any pulse time in the 12-microsecond period. The package containing the and-gate used in this manner is referred to as a "T-blender".

Figure 2-4 shows the logic of the count-down loops, and the T-blender packages. The operation of the 3-microsecond count-down loop is as follows. Initially there are no pulses in the loop, and gate 1 is not inhibited. Therefore, the first stage of the loop produces, on line  $A_1$ , a pulse at a time denoted by the symbol  $1CP_n$ . One microsecond later, at a time called  $2CP_n$ , a pulse appears on  $A_2$ , while the previous output,  $A_1$ , which has been delayed, inhibits gate 1. At time  $3CP_n$ , a pulse appears on  $A_3$ , and the delayed pulse  $A_2$  inhibits gate 1. The inhibiting of gate 1 ends at  $3CP_n$  so that at  $4CP_n$  a pulse again passes gate 1 and appears on  $A_1$ . The cycle then repeats. The 4-microsecond count-down loop is similar in operation, except that it starts a new cycle every four microseconds rather than every three. Figure 2-5 shows the time relationships of the  $A_n$  and  $B_m$  pulses.

T-pulses are generated by coincidences between selected  $A_n$  and  $B_m$  pulses in the T-blenders, as shown in Figure 2-4. The method of determining the proper combination of  $A_n$  and  $B_m$  to provide  $T_j$  is as follows:

$n = j \mod 3$  $m = j \mod 4$ .

For example, consider  $T_9$ :

n = 9 modulo 3 = 3 m = 9 modulo 4 = 1  $\therefore$  T<sub>9</sub> = A<sub>3</sub>  $\therefore$  B<sub>1</sub>.

For  $T_{11}$ :

n = 11 modulo 3 = 2 m = 11 modulo 4 = 3  $\therefore$  T<sub>11</sub> = A<sub>2</sub>  $\therefore$  B<sub>3</sub>

2.3 SHIFT REGISTER

Transfer of information frequently requires either a change in data rate or a serial-parallel conversion. These operations may be accomplished by the use of a shift register.

The logic of a typical three-stage shift register is shown in Figure 2-6. Gates 1 and 2 of each stage, in conjunction with the amplifier and delay line, form a dynamic flip-flop. Gates 3 and 4 in each stage are used to shift the information in each flip-flop to the right or left. The shift register is characterized by the following features:

- 1. Information can be inserted or extracted in serial or parallel fashion.

- 2. Information can be inserted or extracted serially from either end of the register; i.e., left or right shift.

- 3. Information can be inserted or extracted at any rate up to one megacycle per second.

Any movement of information to, from, or within the shift register must be accompanied by a sync pulse on the appropriate line; that is:

- 1. Parallel insertion of information on the lines  $P_1$ ,  $P_2$ , and  $P_3$  must be accompanied by a signal on line a.

- 2. Insertion of information on line  $\underline{d}$  must be accompanied by a signal on line  $\underline{b}$ .

- 3. Insertion of information on line  $\underline{e}$  must be accompanied by a signal on line  $\underline{c}$ .

P.3 P\_2 P<sub>1</sub> a Parallel-Load Sync. Reset UNIV .75 .75 .75 SR2 SR3 SR1 Η R S Γ H 2 Y OF 1947-2-T K G G G f Shift Right Output .75 .75 d Shift Right Input 3 Ċ₽ CP, CP1 Ι C HIGAN .75 Shift Right Sync. Pulse .75 Ь c Shift Left Sync. Pulse Shift Left 9 Output Shift Left e Input FIG. 2-6 SHIFT REGISTER

II-9

1947-2-Т

# 2.4 COMPARATOR

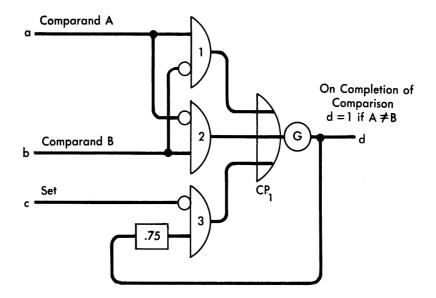

It is often necessary to compare the magnitudes of two numbers to determine whether equality or inequality exists. Figure 2-7 shows the logic of a simple comparator. This circuit provides an output on inequality and no output on equality, since the output C is given by:

$C = (a \cdot \overline{b}) + (\overline{a} \cdot b).$

To detect the inequality of two words, each consisting of several serial pulses, the comparator is used to test the digits of the two words sequentially, and a dynamic flip-flop is incorporated to serve as a memory device. This is most conveniently accomplished by the method shown in Figure 2-8. Before comparison begins, input <u>c</u> is pulsed to clear the dynamic flip-flop. The two words are then compared digit by digit. If equality exists for each digit pair, the flip-flop is not set. However, if an inequality exists for any digit pair, the flip-flop is set and a series of ones appears at output d until the circuit is reset at input c.

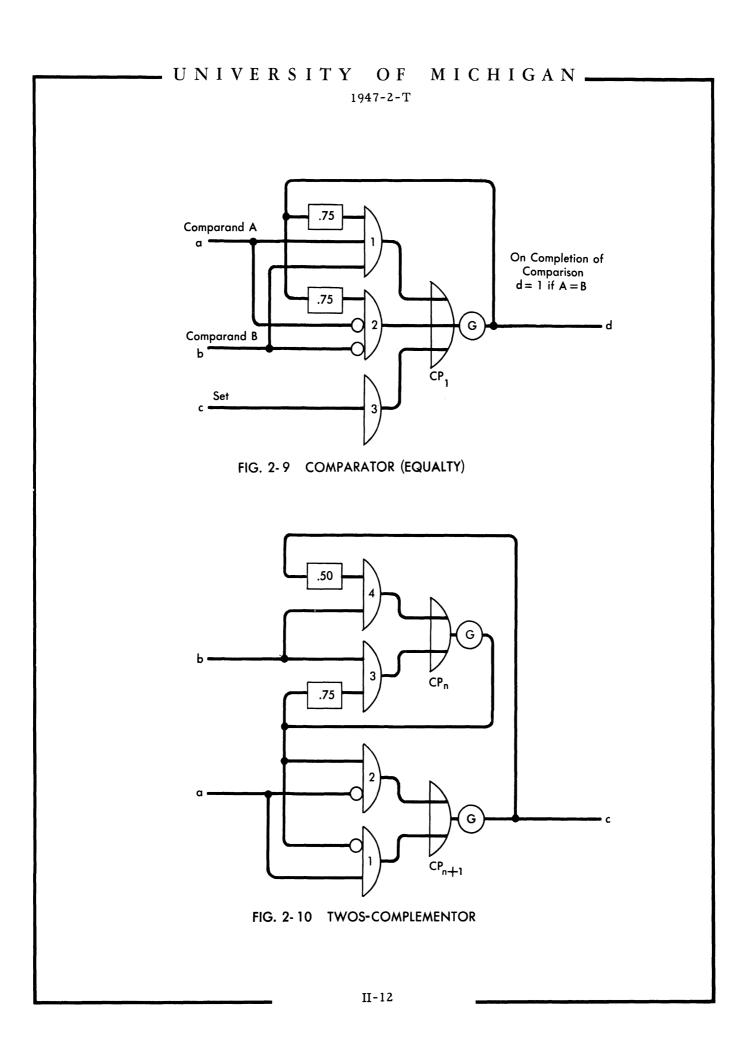

Figure 2-9 shows the logic of a serial equality comparator. The circuit is basically a dynamic flip-flop which is set by input  $\underline{c}$  before the start of a comparison operation. An inequality existing at inputs  $\underline{a}$  and  $\underline{b}$  resets the dynamic flip-flop by stopping the recirculation of the stored "one".

# 2.5 COMPLEMENTOR

In digital computation a negative number is often represented by the complement of its absolute value. In binary arithmetic, two types of complements are frequently employed. The "diminished radix" or ones-complement of a number x is defined by

$$y = N - |x|$$

where N is the maximum value which x can take. An examination of the definition reveals that the ones-complement is obtained by changing all zero digits of x to one, and all one digits to zero. The basic comparator circuit shown in Figure 2-7 performs ones-complementation of one input if a sequence of pulses is applied to the other input.

1947 - 2 - T

FIG. 2-8 COMPARATOR (INEQUALTY)

# UNIVERSITY OF MICHIGAN \_\_

### 1947-2-T

The "radix complement" or twos-complement is defined by

$y = N + 2^{p} - |x|$

It may be obtained by the following procedure.

The low order digits are observed first, but no digits are changed until a "one" is encountered. The first "one" digit is not changed, but the remaining digits are ones-complemented. The logic of a twoscomplementor for serial numbers is shown in Figure 2-10. It can be seen that gates 1 and 2 form a basic comparator circuit used as a onescomplementor while gates 3, 4, the associated tube, and the .75-microsecond delay line form a flip-flop which stores the fact that a one digit has occurred. To form the twos- complement of a number, pulses are fed to input <u>b</u>. The number to be complemented is fed to <u>a</u>. Gates 1 and 2 form no complements until the flip-flop is set. The flip-flop is set by the first one digit and thereafter gates 1 and 2 form the ones-complement. The twos-complement of the number appears serially at c.

### 2.6 ADDER

The rules for binary addition may be expressed simply by use of a "truth" table. The correct logic for operation on each digit pair is shown in Table 2-1.

#### TABLE 2-1

| Addend | Augend     | Partial Sum | Partial Carry |

|--------|------------|-------------|---------------|

| (a)    | <u>(b)</u> | <u>(S')</u> | (c')          |

| 1      | 1          | 0           | 1             |

| 1      | 0          | 1           | 0             |

| 0      | 1          | 1           | 0             |

| 0      | 0          | 0           | 0             |

|        |            |             |               |

### TRUTH TABLE FOR HALF-ADDER

# UNIVERSITY OF MICHIGAN.

### 1947-2-T

The circuit which implements this truth table is termed a half-adder. The half-adder provides no means for operation on the carry digits to produce the true sum. It may be seen from Table 2-1 that the basic half-adder consists of a simple comparator (Fig. 2-7) and a two-input and-gate. The comparator logic produces the partial sum while the twoinput and-gate determines the partial carry digit.

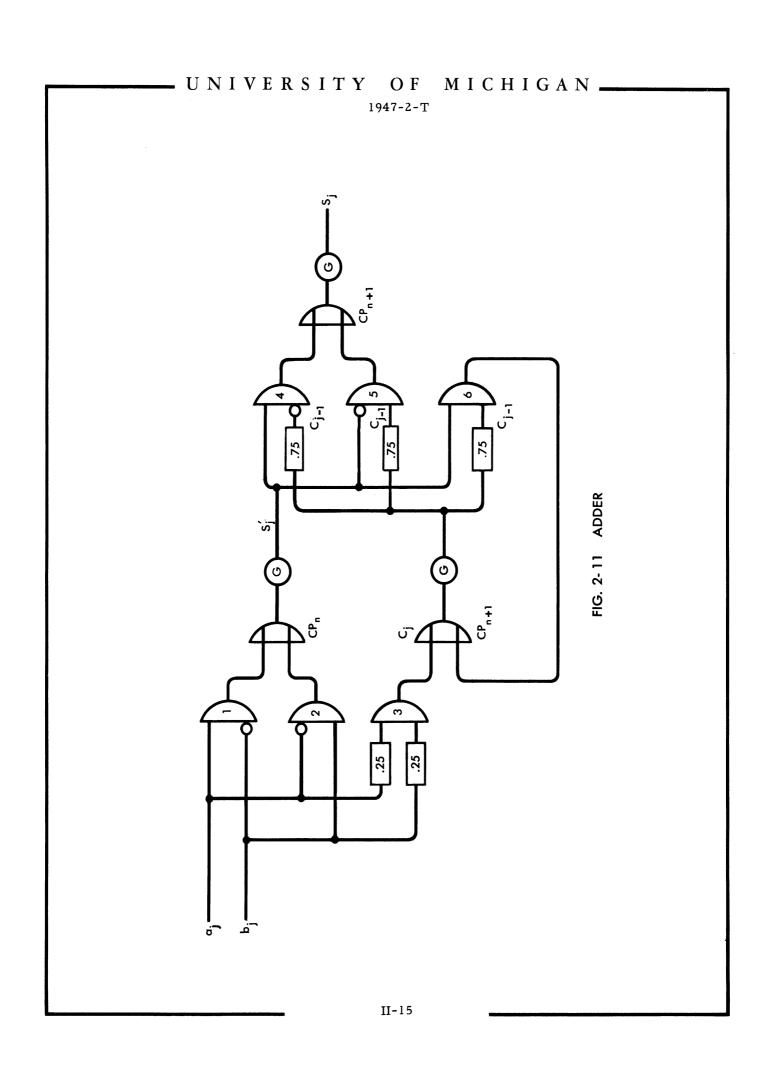

A complete two-input adder may be formed from two half-adders, as shown in Figure 2-11. This two-input adder gives the complete sum.

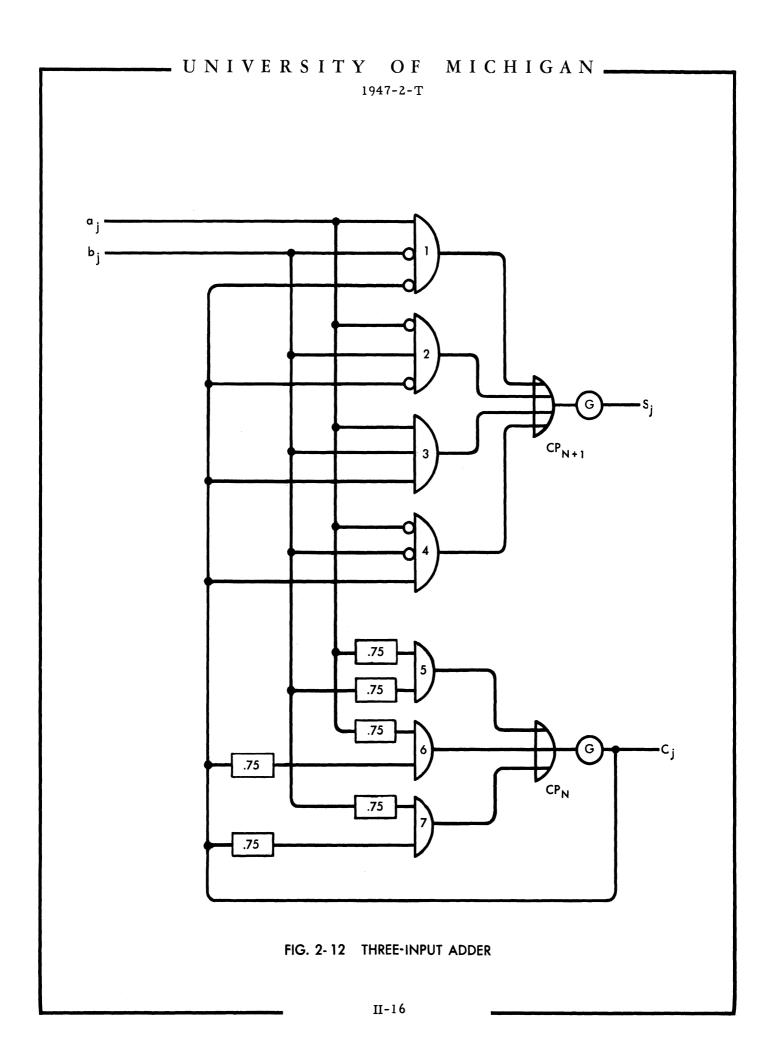

Among the many other designs for serial adders is the so-called "three-input adder" shown in Figure 2-12. The operation of this adder is essentially the same as that of the two-input adder.

For the sum S to be correct, either adder must satisfy the eight possible combinations of two input digits and one carry digit, as shown in Table 2-2. The subscript refers to the j-th digit of an N-digit number. The columns at the right indicate the gates used in each case.

### TABLE 2-2

|   | a <sub>j</sub> I | - b <sub>j</sub> + | ° <sub>j-1</sub> = | = S_ aı<br>j | nd c <sub>j</sub> | Gates<br>Fig. 2-11 | Gates<br>Fig. 2-12 |

|---|------------------|--------------------|--------------------|--------------|-------------------|--------------------|--------------------|

| 1 | 0                | 0                  | 0                  | 0            | 0                 |                    |                    |

| 2 | 1                | 0                  | 0                  | 1            | 0                 | 1•4                | 1                  |

| 3 | 0                | 1                  | 0                  | 1            | 0                 | 2•4                | 2                  |

| 4 | 0                | 0                  | 1                  | 1            | 0                 | 5                  | 4                  |

| 5 | 1                | 1                  | 0                  | 0            | 1                 | 3                  | 5                  |

| 6 | 1                | 0                  | 1                  | 0            | 1                 | 1•6                | 6                  |

| 7 | 0                | 1                  | 1                  | 0            | 1                 | 2•6                | 7                  |

| 8 | 1                | 1                  | 1                  | 1            | 1                 | 3•5                | 3 • 5 • 6 • 7      |

### DIGIT COMBINATIONS

### 2.7 COUNTER

It is often necessary to count the occurrences of some signal in a computer in order to know when some other process or event should be initiated.

An economical counter structure makes use of a circulating storage loop, in which the binary count is stored. The circulating loop includes a circuit capable of adding unity to the stored count once during each circulation. The maximum counting rate for such a device is the reciprocal of the circulation time. Thus,

$$f_{\max} = \frac{10^6}{\log_2(N+1)}$$

where  $f_{max}$  is the maximum counting rate in counts per second and N is the maximum count which can be registered.

Figure 2-13 illustrates such a circuit for the case N = 7 in which a 3-microsecond loop is employed.

The input to the counter is on line a, and must satisfy the condition that its period is some multiple of 3 microseconds, though not necessarily always the same multiple. Pulses to be counted on line a, must be in time synchronization with the least significant digit of the stored count if the circuit is to operate properly. The counter is reset by means of line <u>b</u>. Line <u>b</u> must remain on for at least 3 microseconds to ensure full reset. This serial-type counter is especially useful where the count in the counter is fed to a serial comparator to be compared with a control parameter.

The multi-stage flip-flop counter of Figure 2-14 requires more equipment but is capable of handling counting rates up to  $10^6$  counts per second. This counter is made up of identical flip-flop stages and can be extended to as many stages as desired. The input is applied to line <u>a</u>. An output signal is sent to the next stage each time a stage is reset from one to zero. The reset signal is generated by gates 1 and 2 in the two-stage counter

# UNIVERSITY OF MICHIGAN ....

### 1947-2-T

shown. The count stored in the counter is indicated by the condition of the flip-flops (FF1 and FF2) in the various stages. Particular counts can be sensed by means of and-gates not included in Figure 2-14; e.g., a count of three would be sensed by feeding the outputs of FF1 and FF2 into an and-gate. A change of state propagates through the stages of the counter at a rate of one stage for each quarter-microsecond. In sensing the accumulated count, care must be exercised to avoid erroneous sensing during a change of state.

III

# EXAMPLE OF A COMPUTER SUBSYSTEM: A SERIAL ARITHMETIC UNIT

This section illustrates how the functional units described in Section II may be interconnected to function as a subsystem of a complete computer. The example used is a serial arithmetic unit that can add and subtract tendigit binary numbers.

# 3.1 INPUTS AND OUTPUTS