# PUBLICATIONS RELEASE

MAPPER 10/System 11

**Type 3065**

**Processor and Storage**

Reference

UP-9955

This Library Memo announces the release and availability of *Type 3065, Processor and Storage, Reference,* UP-9955.

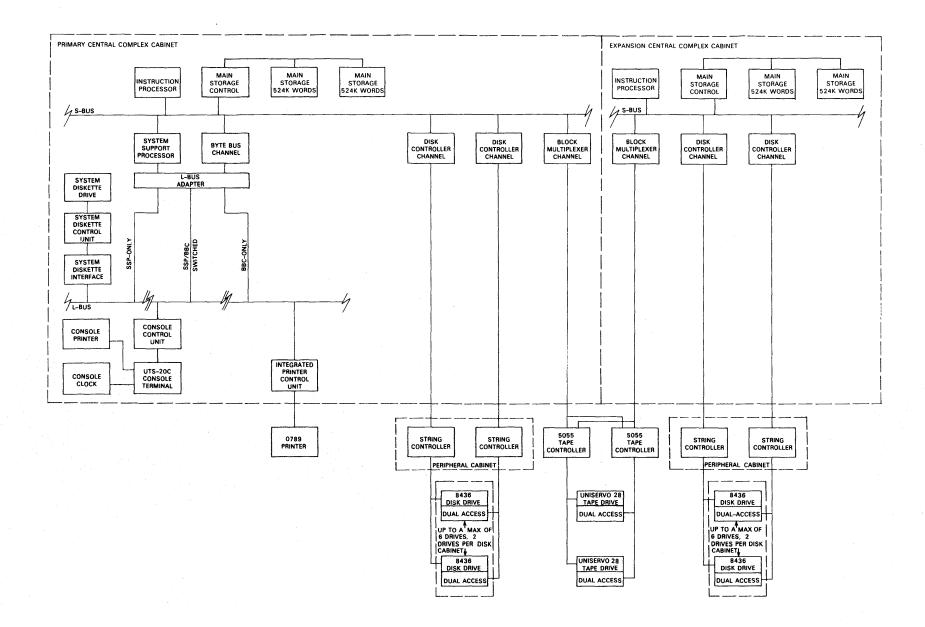

The Type 3065 central complex components described in this manual are required components in some smaller Series 1100 Systems (for example, the Distributed Data Processing System 11).

This manual provides hardware-oriented information for the following Type 3065 central complex components:

- **■** K3649 Instruction Processor

- K3650 Disk Controller Channel

- K3651 Byte Bus Channel

- K3652 Block Multiplexer Channel

- K3653 Main Storage Unit

This manual also includes information for the integrated Streaming Tape Subsystem; and in the appendices, a listing of instructions by function code and mnemonic.

This manual is intended for system programmers and system analysts who are familiar with similar equipment.

This manual consists of:

- 1. Introduction

- 2. Instruction Processor

- 3. Channel Input/Output Processors

- 4. Main Storage Unit

- 5. Integrated Streaming Tape Subsystem

Appendix A. Instructions Listed by Function Code

Appendix B. Instructions Listed by Mnemonic

Appendix C. Abbreviations, Acronyms, and Symbols

Index

Copies of the manual may be requisitioned through your Sperry representative.

# To Mailing Lists AC, BZ, CZ (less DE, GZ, HA), MZ, 8, 30, 38, 62, MBR, MIO0, and MI40. LIBRARY MEMO AND ATTACHMENTS THIS SHEET IS Library Memo plus UP-9955 (283 pages and cover) to Mailing Lists DE, GZ, HA, and 82. RELEASE DATE: April 1984

# Type 3065 Processor and Storage

Reference

This document contains the latest information available at the time of preparation. Therefore, it may contain descriptions of functions not implemented at manual distribution time. To ensure that you have the latest information regarding levels of implementation and functional availability, please consult the appropriate release documentation or contact your local Sperry representative.

Sperry reserves the right to modify or revise the content of this document. No contractual obligation by Sperry regarding level, scope, or timing of functional implementation is either expressed or implied in this document. It is further understood that in consideration of the receipt or purchase of this document, the recipient or purchaser agrees not to reproduce or copy it by any means whatsoever, nor to permit such action by others, for any purpose without prior written permission from Sperry.

FASTRAND, SPERRY, SPERRY, SPERRY UNIVAC, SPERRY UNIVAC, UNISCOPE, UNISERVO, UNIVAC, and are registered trademarks of the Sperry Corporation. ESCORT, MAPPER, PAGEWRITER, PIXIE, SPERRYLINK, and UNIS are additional trademarks of the Sperry Corporation.

# **Page Status Summary**

| Section            | Pages  | Update |

|--------------------|--------|--------|

| Cover/Disclaimer   |        |        |

| PSS                | 1      |        |

| Preface            | 1 - 2  |        |

| Contents           | 1 – 10 |        |

| Section 1          | 1 – 11 |        |

| Section 2          | 1 - 87 |        |

| Section 3          | 1 – 83 |        |

| Section 4          | 1 – 24 |        |

| Section 5          | 1 – 28 |        |

| Appendix A         | 1 – 22 |        |

| Appendix B         | 1 – 5  |        |

| Appendix C         | 1 – 3  |        |

| Index              | 1 – 5  |        |

| User Comment Sheet |        |        |

|                    |        |        |

|                    |        |        |

|                    |        |        |

|                    |        |        |

|                    |        |        |

|                    |        |        |

|                    | ,      |        |

|                    |        |        |

|                    |        |        |

|                    |        |        |

|                    |        |        |

|                    |        |        |

| Section | Pages | Update |

|---------|-------|--------|

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

| ·       |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

|         |       |        |

| 4       |       |        |

|         |       |        |

|         |       |        |

|         | ·     |        |

|         |       |        |

|         | :     |        |

|         |       |        |

| ·       |       |        |

| L       |       |        |

**Preface**

The Type 3065 central complex components described in this manual are required components in some smaller Series 1100 Systems (for example, the Distributed Data Processing System 11).

This manual provides hardware-oriented information for the following Type 3065 central complex components: Instruction Processor, Channel Input/Output Processors, and Main Storage Unit. This manual also includes information for the integrated Streaming Tape Subsystem.

This manual is intended for system programmers and system analysts who are familiar with similar equipment.

This manual consists of:

#### SECTION

#### CONTENTS

1 Introduction

Presents an overview of the central complex components, and provides illustrations of the standard system configurations.

2 Instruction Processor

Describes general operation, including: processor state, storage structures, processor operation, interrupt processing, classes, and status.

3 Channel Input/Output Processors

Describes input/output operations, including: I/O order code initiation and operation, channel command word operation, and status tabling operation.

4 Main Storage Unit

Describes general main storage operation, including: functional characteristics, system bus, addressing modes, and storage instructions. Error reporting, error detection, and error handling are also described.

#### SECTION

#### **CONTENTS**

5 Integrated Streaming Tape Subsystem

Describes the integrated Streaming Tape Subsystem functions and commands.

Appendix A Instructions Listed by Function Code

Lists the instructions in order of function code, and provides a brief description of each instruction.

Appendix B Instructions Listed by Mnemonic

Lists the instructions by mnemonic in alphabetical order with a cross reference to the function code for both basic and extended modes.

Appendix C Abbreviations, Acronyms, and Symbols

Provides an alphabetically arranged list of definitions of terms, abbreviations, and acronyms used in this manual.

Index

Lists key terms used in this manual with corresponding subsection and page numbers for each significant occurrence.

Documents referenced in this manual are:

- Series 1100 Assembly Instruction Mnemonics (AIM), Supplementary Reference, UP-9047 (applicable version\*)

- System Support Processor (SSP), Operator Reference, UP-9123 (applicable version\*)

- 8436 Disk Subsystem, Reference, UP-10058.

- \* Use the version needed for the software level in use at your site.

## **Contents**

# Page Status Summary

# Preface

## **Contents**

| 1. | Introduction                               | 1-1 |

|----|--------------------------------------------|-----|

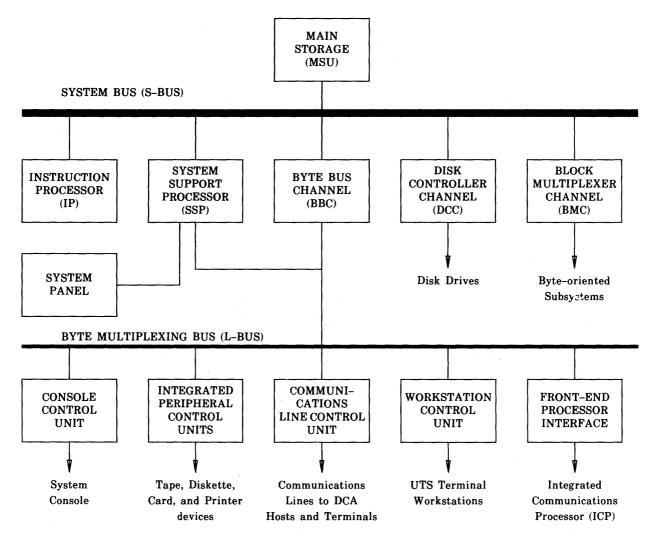

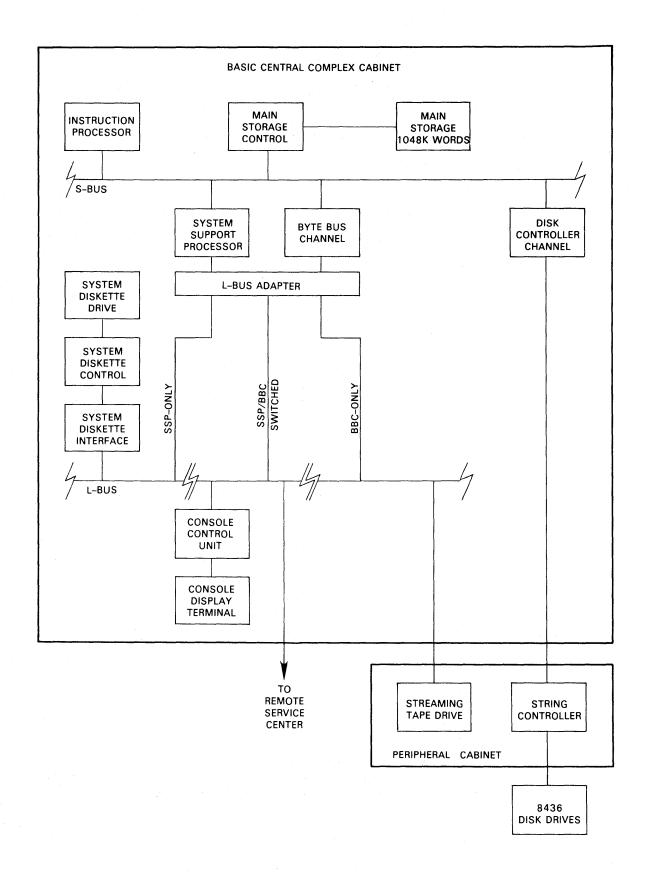

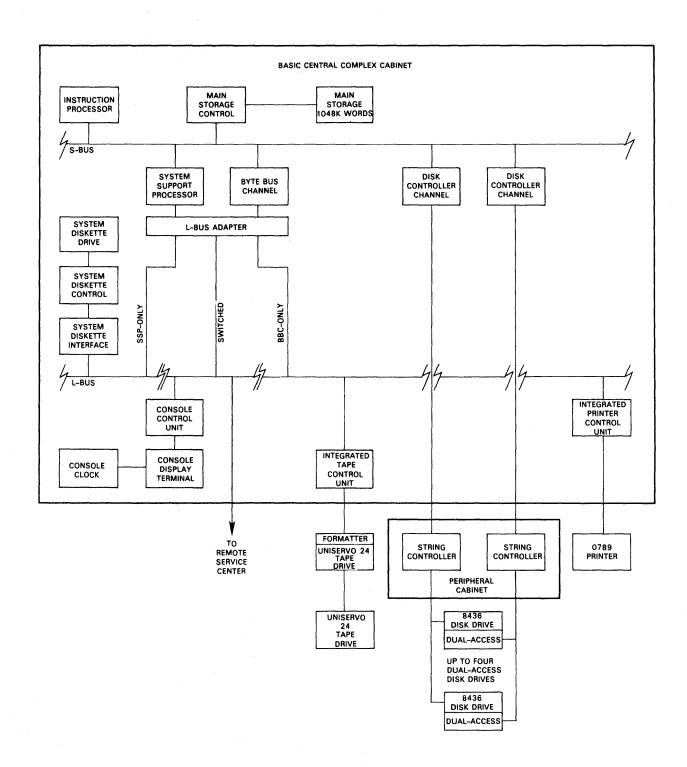

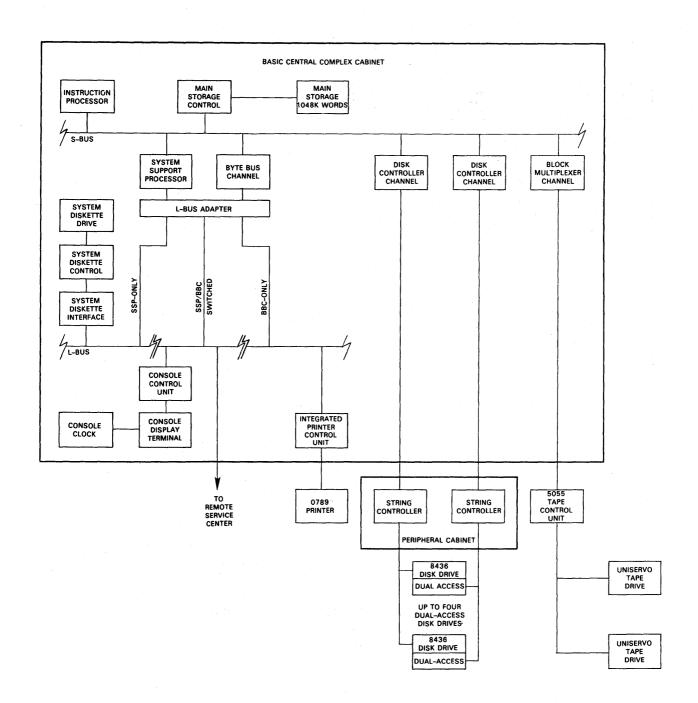

|    | 1.1. Functional Description                | 1–1 |

|    | 1.1.1. Instruction Processor               | 1-1 |

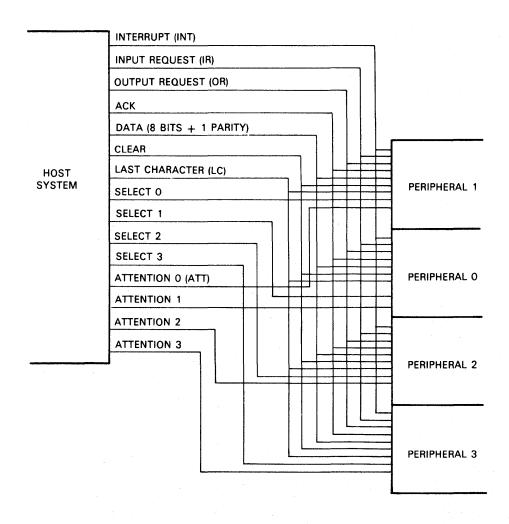

|    | 1.1.2. Channel Input/Output Processors     | 1-3 |

|    | 1.1.3. Main Storage Unit                   | 1-5 |

|    | 1.1.4. System Support Processor            | 1-5 |

|    | 1.1.5. System Bus                          | 1-6 |

|    | 1.1.6. Byte Multiplexing Bus               | 1-6 |

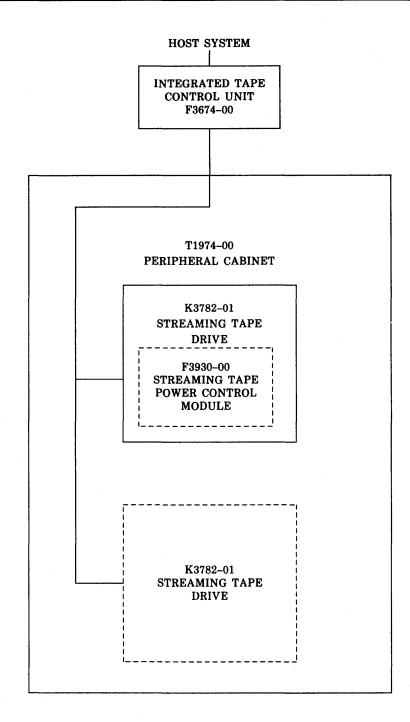

|    | 1.1.7. Integrated Streaming Tape Subsystem | 1-7 |

|    | 1.2. Instructions                          | 1-7 |

|    | 1.3. Major System Components               | 1-7 |

|    | 1.4. Standard System Configurations        | 1-7 |

| 2. | Instruction Processor                      | 2-1 |

|    | 2.1. General                               | 2–1 |

|    | 2.2. Operands                              | 2–1 |

|    | 2.2.1. Data Formats                        | 2-1 |

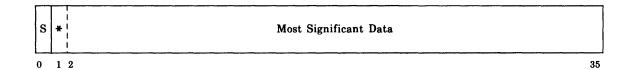

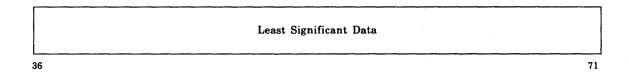

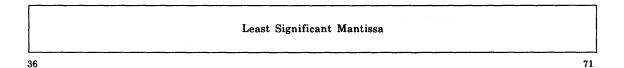

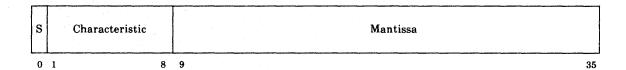

|    | 2.2.1.1. Single-Precision Binary           | 2-2 |

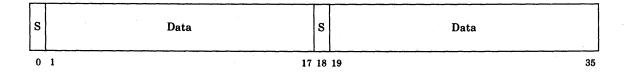

|    | 2.2.1.2. Fractional-Precision Binary       | 2-2 |

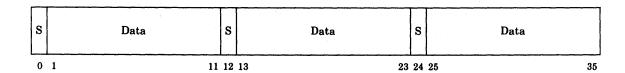

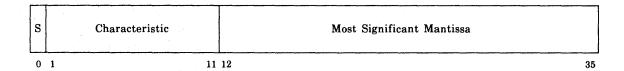

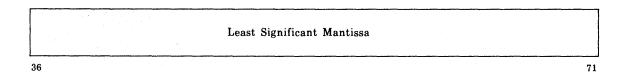

|    | 2.2.1.3. Double-Precision Binary           | 2-3 |

|    | 2.2.1.4. Decimal Data                      | 2-3 |

|    | 2.3. General Register Set                  | 2-4 |

|    | 2.3.1. Index (X) Registers                 | 2-6 |

|    | 2.3.2. Arithmetic (A) Registers            | 2-6 |

|    | 2.3.3. Special (R) Registers               | 2-7 |

|    | 2.3.3.1. Repeat Count Register (R1)        | 2-7 |

|    | 2.3.3.2. Mask Register (R2)                | 2-7 |

|    | 2.3.4. Register Selection Designator       | 2-8 |

|    |                                            | - 0 |

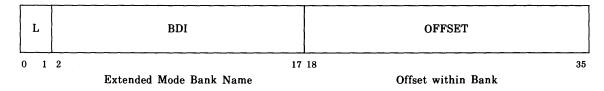

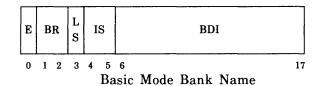

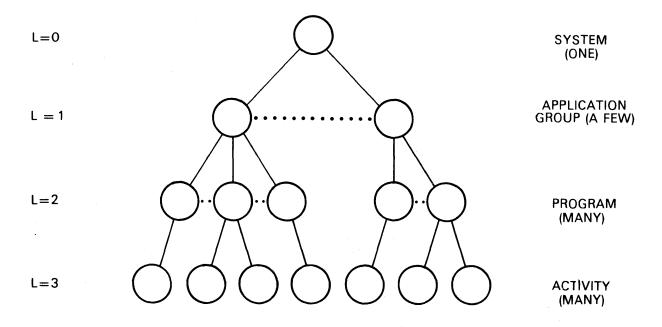

| 2.4. Virtual Address Space                                                         | 2-8  |

|------------------------------------------------------------------------------------|------|

| 2.4.1. Address Control                                                             | 2-10 |

| 2.4.2. Storage Objects                                                             | 2-11 |

| 2.4.2.1. Banks                                                                     | 2–11 |

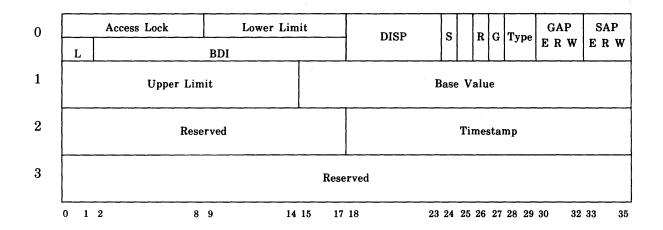

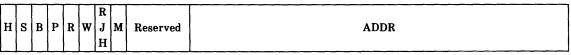

| 2.4.2.1.1. Bank Descriptors                                                        | 2–11 |

| 2.4.2.1.2. Bank Descriptor Format                                                  | 2–12 |

| 2.4.2.1.3. Banks Larger Than 262,143 Words                                         | 2–13 |

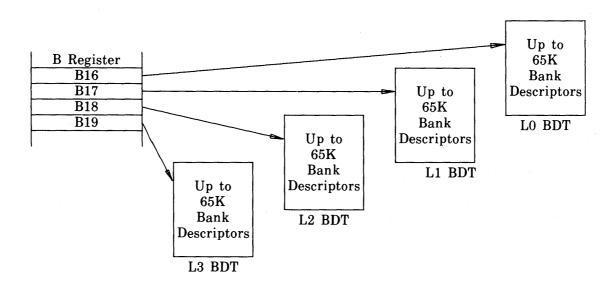

| 2.4.2.1.4. Bank Descriptor Tables                                                  | 2-14 |

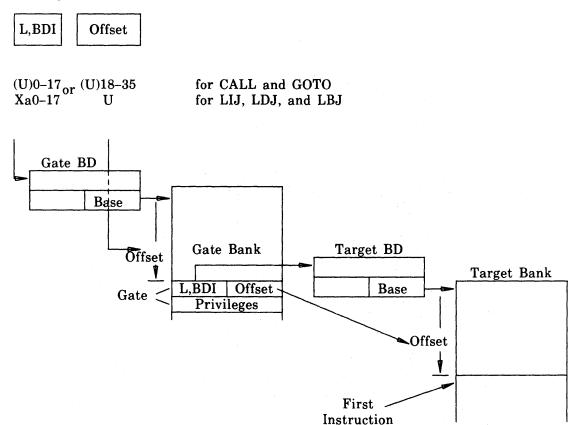

| 2.4.2.2. Gates                                                                     | 2-14 |

| 2.4.2.2.1. Gate Use                                                                | 2-15 |

| 2.4.2.2.2. Gate Format                                                             | 2-15 |

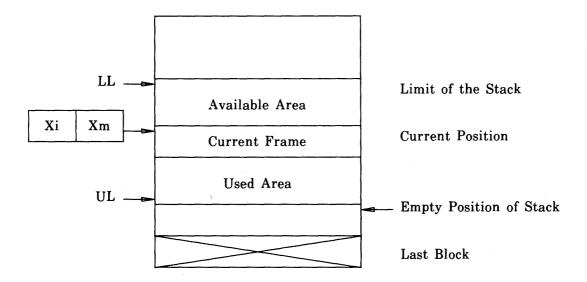

| 2.4.2.3. Storage Stacks                                                            | 2-17 |

| 2.4.2.3.1. Stack Structure                                                         | 2-17 |

| 2.4.2.3.2. Stack Manipulation                                                      | 2-18 |

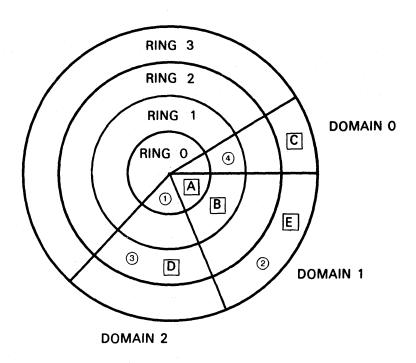

| 2.4.3. Operand Protection                                                          | 2-18 |

| 2.4.3.1. Access Key                                                                | 2-19 |

| 2.4.3.2. Accesss Lock                                                              | 2-19 |

| 2.4.3.3. Access Permission                                                         | 2-19 |

| 2.4.3.4. Access Permission Field Selection                                         | 2-19 |

| 2.4.3.5. Address Control and Access Control                                        | 2-21 |

| 2.5. Base Registers                                                                | 2-21 |

| 2.5.1. Base Register Properties                                                    | 2-21 |

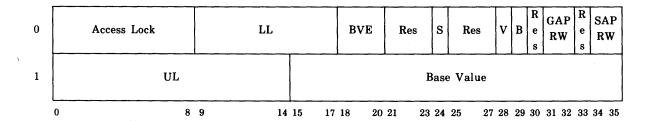

| 2.5.2. Base Register Format                                                        | 2-22 |

| 2.5.3. Fixed Base Register Assignments                                             | 2-24 |

| 2.0.0. Fixed base negister Assignments                                             | 2-24 |

| 2.6. Base-Relative Address Space                                                   | 2-25 |

| 2.7. General Registers as Storage Operand Locations                                | 2-25 |

| 2.8. Immediate Operands                                                            | 2-25 |

| 2.9. Sequence of Operand References                                                | 2-26 |

| 2.10. Instruction Execution Mode                                                   | 2-26 |

| 2.11. Instruction Word Formats                                                     | 2-27 |

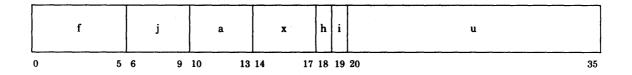

| 2.11.1. Basic Mode Instruction Word Format                                         | 2-27 |

| 2.11.1.1. Function Code f-Field                                                    | 2-27 |

| 2.11.1.2. Partial-Word or Immediate-Operand Designator j-Field                     | 2-27 |

| 2.11.1.3. Control Register Designator a-Field                                      | 2-30 |

| 2.11.1.4. Index Register Designator x-Field                                        | 2-30 |

| 2.11.1.5. Index Incrementation Designator h-Field                                  | 2-31 |

| 2.11.1.6. Indirect Address Designator i-Field                                      | 2-31 |

| 2.11.1.7. Operand Address u-Field                                                  | 2-31 |

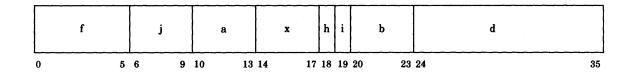

| 2.11.2. Extended Mode Instruction Word Format                                      | 2-31 |

| 2.11.2.1. Operand Address d-Field                                                  | 2-32 |

| 2.11.2.1. Operand Address d-Field 2.11.2.2. Index Register Format Selector i-Field | 2-32 |

| 2.11.2.2. Index register rurmat beletter i-rieu                                    | 4-04 |

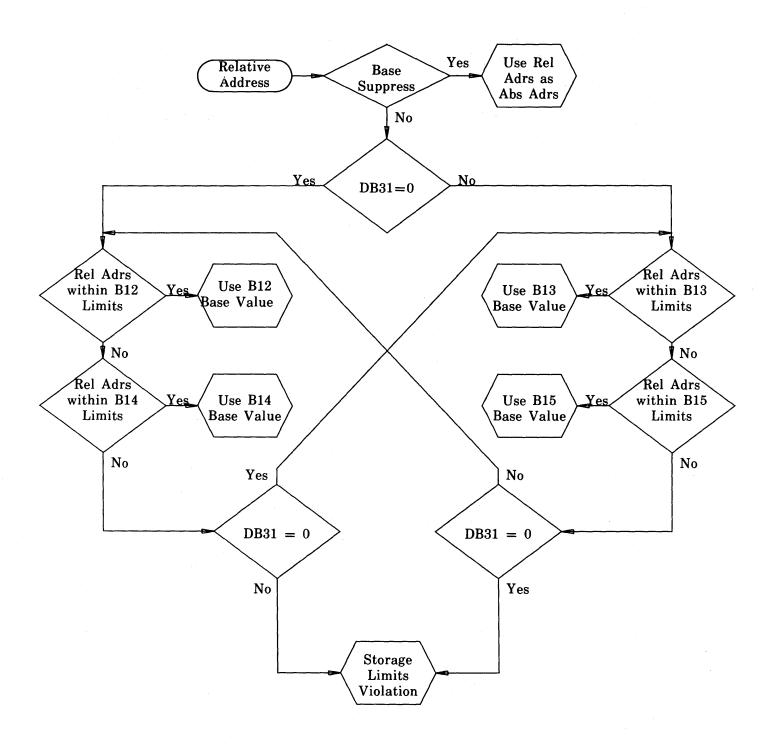

| 2.12. Base Register Selection                                                      | 2-33 |

| 2.12.1. Explicit Base Register Selection                                           | 2-33 |

| 2.12.2. Implicit Base Register Selection                                           | 2-33 |

| 0.10 A 41 14 C4 4 TO -1 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

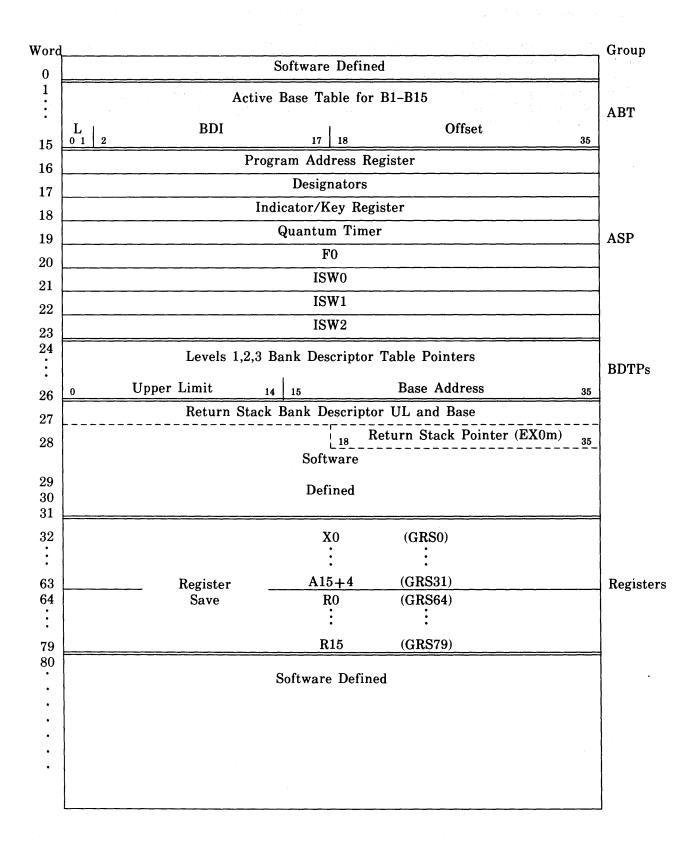

| 2.13. Activity State Packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-35                                                                                                     |

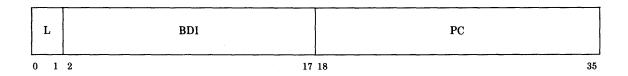

| 2.13.1. Program Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-35                                                                                                     |

| 2.13.2. Designator Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-36                                                                                                     |

| 2.13.3. Indicator/Key Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-39                                                                                                     |

| 2.13.4. Quantum Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-42                                                                                                     |

| 2.13.5. Current Instruction Register (F0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-43                                                                                                     |

| 2.13.6. Interrupt Status Words (ISW0-2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-43                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                          |

| 2.14. Instrumentation State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-44                                                                                                     |

| 2.14.1. Address Breakpoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-44                                                                                                     |

| 2.14.1.1. Breakpoint Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-44                                                                                                     |

| 2.14.1.2. Breakpoint Register Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-44                                                                                                     |

| 2.14.2. Jump History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-46                                                                                                     |

| 2.14.2.1. Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-46                                                                                                     |

| 2.14.2.2. Entry Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-46                                                                                                     |

| 2.14.2.3. Main Storage Buffer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-48                                                                                                     |

| 2.14.3. Software Performance Monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-49                                                                                                     |

| a.i.i.o. Soloware religible interioring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |

| 2.15. Instruction Interrupt Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-50                                                                                                     |

| and and a mile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |

| 2.16. GRS Conflicts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-51                                                                                                     |

| 9.15 0 4 1.04 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 =0                                                                                                     |

| 2.17. Control Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-52                                                                                                     |

| 2.17.1. Interrupt Control Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-52                                                                                                     |

| 2.17.2. Return Control Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-52                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                          |

| 2.17.3. User Stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-52                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-52<br>2-53                                                                                             |

| 2.17.3. User Stacks 2.17.4. Activity Save Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2–53                                                                                                     |

| 2.17.3. User Stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

| 2.17.3. User Stacks 2.17.4. Activity Save Area 2.18. Dayclock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-56<br>2-56                                                                                             |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2–53                                                                                                     |

| 2.17.3. User Stacks 2.17.4. Activity Save Area 2.18. Dayclock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-56<br>2-56<br>2-57                                                                                     |

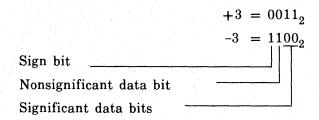

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-53<br>2-56<br>2-57<br>2-57<br>2-57                                                                     |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> <li>2.19.1.2. Data Word Complement</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-53 2-56 2-57 2-57 2-57 2-58                                                                            |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> <li>2.19.1.2. Data Word Complement</li> <li>2.19.1.3. Absolute Values</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-53 2-56 2-57 2-57 2-58 2-58                                                                            |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> <li>2.19.1.2. Data Word Complement</li> <li>2.19.1.3. Absolute Values</li> <li>2.19.2. Main Adder Characteristics</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-58 2-56 2-57 2-58 2-58 2-58 2-58                                                                       |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> <li>2.19.1.2. Data Word Complement</li> <li>2.19.1.3. Absolute Values</li> <li>2.19.2. Main Adder Characteristics</li> <li>2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-58 2-58 2-58 2-58 2-58 2-58 2-58 2-58                                                                  |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> <li>2.19.1.2. Data Word Complement</li> <li>2.19.1.3. Absolute Values</li> <li>2.19.2. Main Adder Characteristics</li> <li>2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions</li> <li>2.19.3.1. Overflow</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-58 2-58 2-58 2-58 2-58 2-58 2-58 2-58                                                                  |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-53 2-56 2-57 2-58 2-58 2-58 2-58 2-58 2-58 2-58                                                        |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> <li>2.19.1.2. Data Word Complement</li> <li>2.19.1.3. Absolute Values</li> <li>2.19.2. Main Adder Characteristics</li> <li>2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions</li> <li>2.19.3.1. Overflow</li> <li>2.19.3.2. Carry</li> <li>2.19.3.3. Arithmetic Interrupt</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-53 2-56 2-57 2-58 2-58 2-58 2-58 2-58 2-58 2-58 2-58                                                   |

| <ul> <li>2.17.3. User Stacks</li> <li>2.17.4. Activity Save Area</li> <li>2.18. Dayclock</li> <li>2.19. Arithmetic Operations</li> <li>2.19.1. General Operation</li> <li>2.19.1.1. Data Word</li> <li>2.19.1.2. Data Word Complement</li> <li>2.19.1.3. Absolute Values</li> <li>2.19.2. Main Adder Characteristics</li> <li>2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions</li> <li>2.19.3.1. Overflow</li> <li>2.19.3.2. Carry</li> <li>2.19.3.3. Arithmetic Interrupt</li> <li>2.19.4. Fixed-Point Division</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            | 2-53 2-56 2-57 2-57 2-58 2-58 2-58 2-58 2-58 2-60 2-60                                                   |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-53 2-56 2-57 2-58 2-58 2-58 2-58 2-58 2-60 2-60 2-60                                                   |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-53 2-56 2-57 2-58 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-60                                              |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats                                                                                                                                                                                                                                                                                                                                                                                              | 2-53 2-56 2-57 2-58 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-60 2-60                                         |

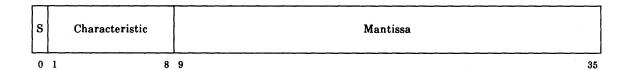

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers                                                                                                                                                                                                                                                                                                                                            | 2-53 2-56 2-57 2-57 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-61                                         |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers                                                                                                                                                                                                                                                                                          | 2-53 2-56 2-57 2-57 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-62 2-63                                    |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers 2.19.7.3. Negative Floating-Point Numbers                                                                                                                                                                                                                                                | 2-53 2-56 2-57 2-58 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-62 2-63 2-63                               |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers 2.19.7.3. Negative Floating-Point Numbers 2.19.7.4. Residue                                                                                                                                                                                                                              | 2-53 2-56 2-57 2-58 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-62 2-63 2-63 2-63                          |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers 2.19.7.3. Negative Floating-Point Numbers 2.19.7.4. Residue 2.19.8. Normalized/Unnormalized Floating-Point Numbers                                                                                                                                                                                                         | 2-53 2-56 2-57 2-57 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-63 2-63 2-63 2-63                          |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers 2.19.7.3. Negative Floating-Point Numbers 2.19.7.4. Residue 2.19.8. Normalized/Unnormalized Floating-Point Numbers 2.19.9. Floating-Point Characteristic Overflow/Underflow                                                                                                              | 2-53 2-56 2-57 2-57 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-63 2-63 2-64 2-64 2-64                     |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers 2.19.7.3. Negative Floating-Point Numbers 2.19.7.4. Residue 2.19.8. Normalized/Unnormalized Floating-Point Numbers 2.19.9. Floating-Point Characteristic Overflow/Underflow 2.19.9.1. Floating-Point Characteristic Overflow                                                             | 2-53 2-56 2-57 2-57 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-63 2-63 2-64 2-64 2-64                     |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers 2.19.7.3. Negative Floating-Point Numbers 2.19.7.4. Residue 2.19.8. Normalized/Unnormalized Floating-Point Numbers 2.19.9. Floating-Point Characteristic Overflow/Underflow 2.19.9.1. Floating-Point Characteristic Overflow/Underflow 2.19.9.2. Floating-Point Characteristic Underflow | 2-53 2-53 2-57 2-57 2-58 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-62 2-63 2-63 2-64 2-64 2-64 2-64 2-64 |

| 2.17.3. User Stacks 2.17.4. Activity Save Area  2.18. Dayclock  2.19. Arithmetic Operations 2.19.1. General Operation 2.19.1.1. Data Word 2.19.1.2. Data Word Complement 2.19.1.3. Absolute Values 2.19.2. Main Adder Characteristics 2.19.3. Fixed-Point Arithmetic Overflow and Carry Conditions 2.19.3.1. Overflow 2.19.3.2. Carry 2.19.3.3. Arithmetic Interrupt 2.19.4. Fixed-Point Division 2.19.5. Fixed-Point Multiplication 2.19.6. Floating-Point Arithmetic 2.19.7. Floating-Point Numbers and Word Formats 2.19.7.1. Single-Precision Floating-Point Numbers 2.19.7.2. Double-Precision Floating-Point Numbers 2.19.7.3. Negative Floating-Point Numbers 2.19.7.4. Residue 2.19.8. Normalized/Unnormalized Floating-Point Numbers 2.19.9. Floating-Point Characteristic Overflow/Underflow 2.19.9.1. Floating-Point Characteristic Overflow                                                             | 2-53 2-56 2-57 2-57 2-58 2-58 2-58 2-58 2-60 2-60 2-60 2-61 2-63 2-63 2-64 2-64 2-64                     |

3.

| 2.19.12. Double-Precision Floating-Point Addition                 | 2-66         |

|-------------------------------------------------------------------|--------------|

| 2.19.13. Floating-Point Subtraction (Add Negative)                | 2-66         |

| 2.19.14. Floating-Point Multiplication                            | 2-67         |

| 2.19.15. Floating-Point Division                                  | 2-67         |

| 2.19.16. Floating-Point Zero                                      | 2-67         |

| 2.13.10. Ploating-1 Onit Zero                                     | 2-01         |

| 2.20. Universal Processor Interface                               | 2-67         |

| 2.20.1. UPI Number Assignments                                    | 2-68         |

| 2.20.2. UPI Instructions                                          | 2-68         |

| 2.20.3. External Interrupt Distribution                           | 2-69         |

| 2.20.3.1. Broadcast Interrupt Request Sequence                    | 2-69         |

| 2.20.3.2. Directed Interrupt Request Sequence                     | 2-70         |

|                                                                   |              |

| 2.21. Interrupts                                                  | 2-70         |

| 2.21.1. Interrupt Processing                                      | 2-70         |

| 2.21.2. Interrupt Classes and Status                              | 2-71         |

| 2.21.2.1. Hardware Default - Class 0                              | 2-75         |

| 2.21.2.2. Unretryable Hardware Check - Class 1                    | 2-75         |

| 2.21.2.3. Reference Violation - Class 8                           | 2-75         |

| 2.21.2.4. Addressing Exception - Class 9                          | 2-77         |

| 2.21.2.5. Interrupt Stack Overflow Warning - Class 10             | 2-81         |

| 2.21.2.6. Return Control Stack/Generic Stack Underflow/Overflow - | 2-01         |

| Class 11                                                          | 2-81         |

| 2.21.2.7. Signal - Class 12                                       | 2-82         |

| 2.21.2.8. Test and Set - Class 13                                 | 2-82         |

| 2.21.2.9. Invalid Instruction – Class 14                          | 2-82         |

|                                                                   | 2-82<br>2-83 |

| 2.21.2.10. Arithmetic Exception - Class 16                        |              |

| 2.21.2.11. Character Manipulation Exception - Class 17            | 2-84         |

| 2.21.2.12. Breakpoint - Class 19                                  | 2-84         |

| 2.21.2.13. Quantum Timer - Class 20                               | 2-85         |

| 2.21.2.14. Critical Alert - Class 22                              | 2-85         |

| 2.21.2.15. General Alert - Class 23                               | 2-85         |

| 2.21.2.16. Software Break - Class 24                              | 2-85         |

| 2.21.2.17. Jump History Full - Class 25                           | 2-85         |

| 2.21.2.18. Delayed Hardware Check - Class 26                      | 2-86         |

| 2.21.2.19. Dayclock - Class 27                                    | 2-86         |

| 2.21.2.20. Initial Program Load - Class 29                        | 2-86         |

| 2.21.2.21. UPI Initial - Class 30                                 | 2-86         |

| 2.21.2.22. UPI Normal - Class 31                                  | 2-87         |

| Ziziinizzi. Oli ittorinar Olass VI                                | 20.          |

| Channel Input/Output Processors                                   | 3-1          |

| 9.1 Company                                                       | 0.1          |

| 3.1. General                                                      | 3-1          |

| 3.1.1. Error Detection                                            | 3-1          |

| 3.1.2. Interface                                                  | 3–2          |

| 3.2. Input/Output Operations                                      | 3-2          |

| 3.2.1. Subchannel Addressing                                      | 3-2          |

| 3.2.2. Control Information                                        | 3-4          |

|                                                                   |              |

| 3.2.3. Sequence of Events                                         | 3-4          |

| 3.2.4. Order Code Initiation                                      | 3-6          |

| 3.2.5. I/O Order Codes                                            | 3-6          |

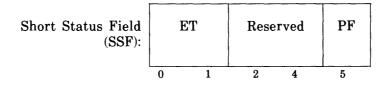

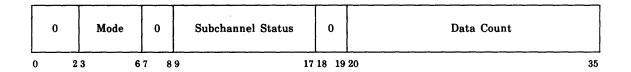

| 3.2.5.1. Subchannel Status                                        | 3-7          |

| 3.2.5.2. Order Code Response                                      | 3-8          |

| 326 Order Code Operations                                         | 3_8          |

| 3.2.6.1. Start I/O Fast Release start I/O fast release | 3-8           |

|--------------------------------------------------------|---------------|

| 3.2.6.2. Test Subchannel                               | 3-11          |

| 3.2.6.3. Halt Subchannel                               | 3-15          |

| 3.2.6.4. Clear Subchannel                              | 3-16          |

| 3.2.6.5. Clear Channel                                 | 3-17          |

| 3.2.6.6. Load Interrupt Mask Register                  | 3-18          |

| 3.2.6.7. Load Control Table Address                    | 3-20          |

| 3.2.6.8. Activate Status Table                         | 3-21          |

| 3.2.6.9. Stop Status Table                             | √ <b>3–22</b> |

| 3.2.6.10. Update Status Stable                         | 3-23          |

| 3.2.6.11. Read Fault Log                               | 3-25          |

| 3.2.6.12. Load Device Path Selection Base Register     | 3-27          |

| 3.2.6.13. Select Device Path Selection                 | 3-28          |

| 3.2.6.14. Write Channel Descriptor Table               | 3-29          |

| 3.2.6.15. Inject MSU Fault                             | 3-32          |

| 3.2.6.16. Inject I/O Internal Fault                    | 3-35          |

| 3.2.6.17. Select Status Tabling                        | 3-42          |

| 3.2.6.18. Enable/Disable Subchannel                    | 3-44          |

| 3.2.6.19. Read Channel Descriptor Table                | 3-45          |

|                                                        |               |

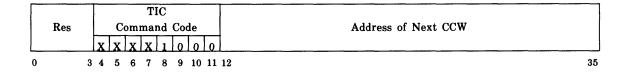

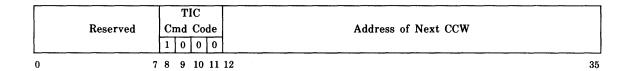

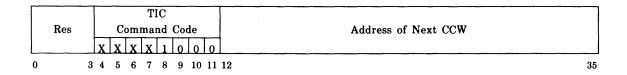

| 3.3. Channel Command Word                              | 3-48          |

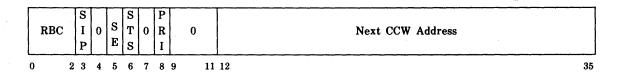

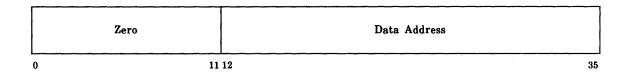

| 3.3.1. Format                                          | 3-48          |

| 3.3.2. Internally Specified Index Word Channel         | 3-48          |

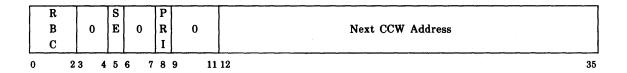

| 3.3.3. Block Multiplexer                               | 3-50          |

| 3.3.4. Unconditional Branching                         | 3-53          |

| 3.3.5. Conditional Branching                           | 3-53          |

| 3.3.5.1. Command Chaining                              | 3-54          |

| 3.3.5.2. Data Chaining                                 | 3-54          |

| 5000 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5                 | 0 02          |

| 3.4. Status Reporting                                  | 3-55          |

| 3.4.1. Input/Output Interrupts                         | 3-55          |

| 3.4.2. Status Table Presented CSW                      | 3-56          |

| 3.4.3. Fault Log Entry Presented CSW                   | 3-58          |

| 3.4.4. BBC and BMC Status Words                        | 3-60          |

| 3.4.5. DCC Status Words                                | 3-63          |

| 5.4.0. DOO Status Words                                | 000           |

| 3.5. Automatic Sense Information Retrieval             | 3-67          |

| 9.0 Chalan Walling                                     | 0.05          |

| 3.6. Status Tabling                                    | 3-67          |

| 3.6.1. Description                                     | 3-67          |

| 3.6.2. Operation                                       | 3–68          |

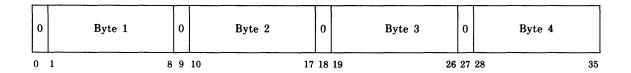

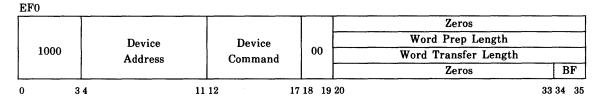

| 3.7. Data Word Formats                                 | 3-69          |

| 3.8. Channel Descriptor Table                          | 3–71          |

| 3.8. Channel Descriptor Table                          | 3-11          |

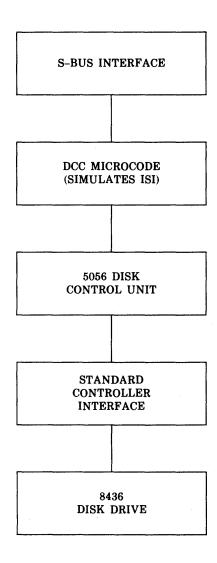

| 3.9. Disk Controller Channel                           | 3-73          |

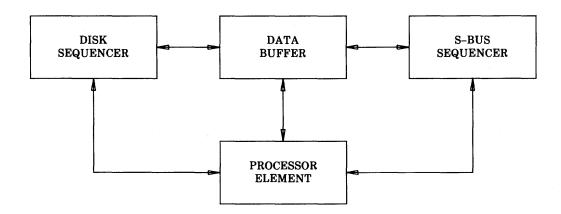

| 3.9.1. Functional Description                          | 3-73          |

| 3.9.1.1. Processor Element                             | 3-74          |

| 3.9.1.2. Data Buffer                                   | 3-74          |

| 3.9.1.3. S-Bus Sequencer                               | 3-74          |

| 3.9.1.4. Disk Sequencer                                | 3-74          |

| 3.9.2. DCC Characteristics                             | 3-75          |