# SPERRY

# V70 Series Floating Point Processor Operation and Service Manual

**Mini-Computer Operations**

2722 Michelson Drive P.O. Box C-19504 Irvine, California 92713

. UP-8642

## SPERRY + UNIVAC®

.

### V70 SERIES FLOATING POINT PROCESSOR OPERATION AND SERVICE MANUAL

UP-8642 98A 9906 113

FEBRUARY 1978

The statements in this publication are not intended to create any warranty, express or implied. Equipment specifications and performance characteristics stated herein may be changed at any time without notice. Address comments regarding this document to Sperry Univac, Mini-Computer Operations, Publications Department, 2722 Michelson Drive, P.O. Box C-19504, Irvine, California, 92713.

#### © 1978 SPERRY RAND CORPORATION

Sperry Univac is a division of Sperry Rand Corporation

| Page<br>Number        | lssue<br>Date                  | Change Description                                                                                                                                                                                                                                  |

|-----------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Various               | 11-77                          | Deleted all references to Varian.                                                                                                                                                                                                                   |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

| •                     |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

|                       |                                |                                                                                                                                                                                                                                                     |

| Change Proc           | edure:                         |                                                                                                                                                                                                                                                     |

|                       |                                | this manual, updated pages are issued to replace the obsolete                                                                                                                                                                                       |

| pages. C<br>change an | On each upda<br>ad a letter is | this manual, updated pages are issued to replace the obsolete<br>ted page, a vertical line is drawn in the margin to flag each<br>added to the page number. When the manual is revised and<br>the vertical line and page-number letter are removed. |

### CHANGE RECORD

96A0730-000A

| LIST OF | <b>EFFECTIV</b> | 'E PAGES |

|---------|-----------------|----------|

|---------|-----------------|----------|

| Page Number | Change in Effect   |

|-------------|--------------------|

| A11         | Complete revision. |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

| ς.          |                    |

|             |                    |

|             |                    |

|             |                    |

|             |                    |

.

## TABLE OF CONTENTS

.

| Section | Title                                                   |                                                       | Page                                                                                   |

|---------|---------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1       | GENERAL DES                                             | CRIPTION                                              | 1-1                                                                                    |

| 2       | INSTALLATIO                                             | N                                                     | 2-1                                                                                    |

|         | 2.2<br>2.3                                              | Inspection                                            | 2 - 1<br>2 - 1<br>2 - 1<br>2 - 1                                                       |

| 3       | OPERATION .                                             |                                                       | 3-1                                                                                    |

|         | 3.2                                                     | FPP Instructions                                      | 3-1<br>3-1                                                                             |

|         |                                                         | Number Format                                         | 3-1                                                                                    |

|         | 3.2.3<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4 | Number Format<br>Integer Format<br>Program Interrupts | 3 - 5<br>3 - 5<br>3 - 5<br>3 - 6<br>3 - 6<br>3 - 8<br>3 - 8<br>3 - 8<br>3 - 8<br>3 - 8 |

| 4       | THEORY OF O                                             | PPERATION                                             | 4 - 1                                                                                  |

|         | 4.2                                                     | General                                               | 4 - 1<br>4 - 1                                                                         |

|         | 4.2.1                                                   | Data Buffer, Address Output, and<br>I/O Selection     | 4 - 1                                                                                  |

|         | 4.2.3<br>4.2.4<br>4.2.5<br>4.2.6                        | Decoder                                               | 4 - 1<br>4 - 2<br>4 - 3<br>4 - 3<br>4 - 3                                              |

|         |                                                         | Clock Control                                         | 4 - 3<br>4 - 4                                                                         |

.

## TABLE OF CONTENTS (continued)

| Section | Title                                                            |                                                                                                                                                                  | Page                                                                |

|---------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

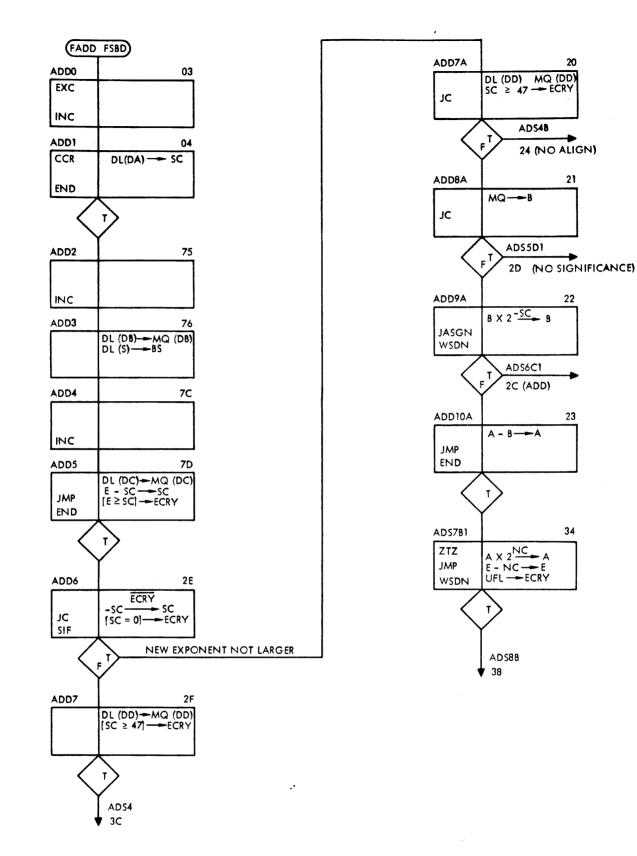

|         | 4.3<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.4.1 | FPP Detailed Block DiagramMicroinstruction FormatMicroprogram RoutinesFLD RoutineFLDD RoutineFLT RoutineFLT RoutineFAD/FSB RoutineMicroinstructions ADSO through | 4 - 4<br>4 - 4<br>4 - 9<br>4 - 2 5<br>4 - 2 7<br>4 - 2 8<br>4 - 3 1 |

|         | 4.5.4.2                                                          | ADS2                                                                                                                                                             | 4 - 35<br>4 - 38                                                    |

|         | 4.5.4.3                                                          | ADS6                                                                                                                                                             | 4 - 39                                                              |

|         | 4.5.4.4                                                          | Microinstructions ADS3A through<br>ADS6A                                                                                                                         | 4 - 40                                                              |

|         | 4.5.4.6                                                          | ADS6B                                                                                                                                                            | 4 - 4 0                                                             |

|         | 4.5.5<br>4.5.6                                                   | ADS8C2                                                                                                                                                           | 4 - 4 1<br>4 - 4 2<br>4 - 4 4                                       |

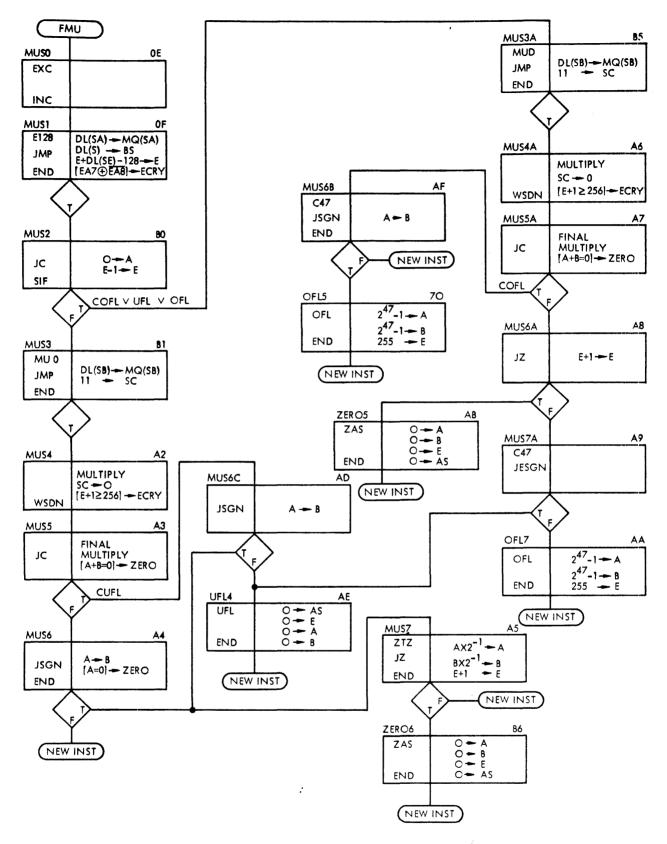

|         | 4.5.6.1                                                          | EMU Routing                                                                                                                                                      | 4 - 46                                                              |

|         | 4.5.6.2                                                          | Microinstructions MUS3 through<br>MUS7 and ZERO6                                                                                                                 | 4 - 50                                                              |

|         | 4.5.6.4                                                          | MUS7A and OFL7; MUS6B and OFL5;<br>and ZER05                                                                                                                     | 4 - 52                                                              |

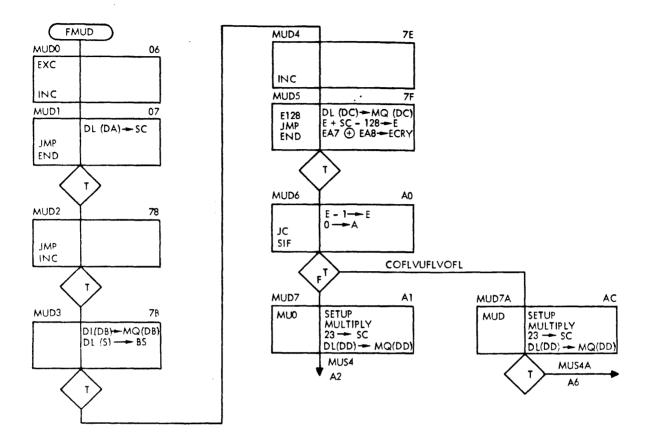

|         | 4.5.7<br>4.5.8<br>4.5.8.1                                        | struction MUS6C and Microinstruc-<br>tion UFL4                                                                                                                   | 4 - 53<br>4 - 54<br>4 - 55                                          |

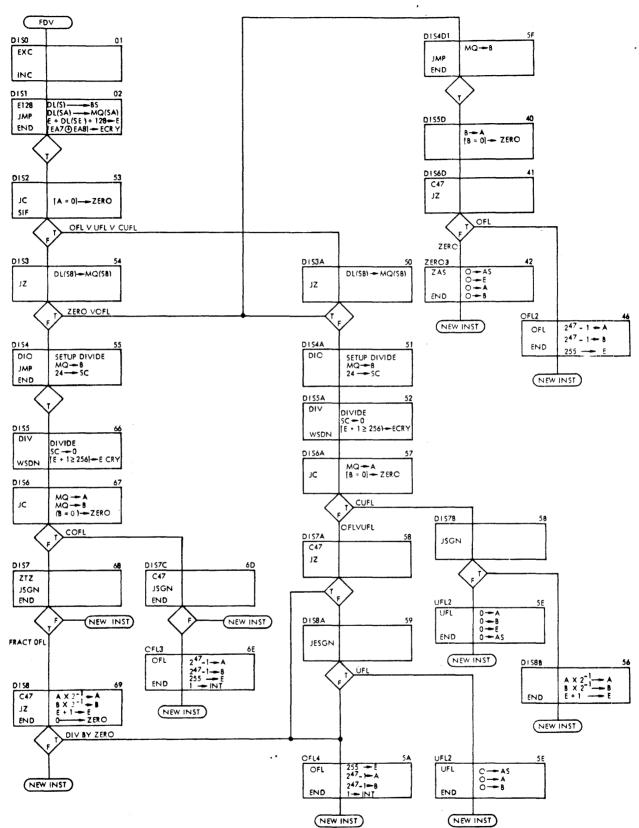

|         | 4.5.8.2                                                          | DIS2                                                                                                                                                             | 4 - 58                                                              |

|         | 4.5.8.3                                                          | DIS8 and OFL2                                                                                                                                                    | 4-61                                                                |

|         | 4.5.8.4                                                          | and UFL2                                                                                                                                                         | 4 - 63                                                              |

|         |                                                                  | DIS6D, ZERO3, and OFL2                                                                                                                                           | 4 - 64                                                              |

TABLE OF CONTENTS (continued)

| Section | Title                                                |                                                                                                                                        | Page                                                     |

|---------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

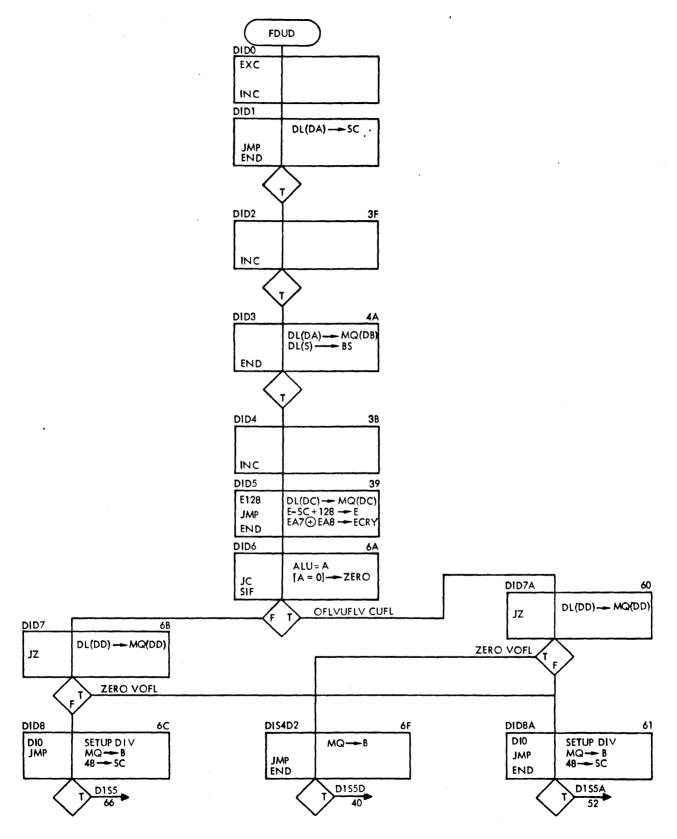

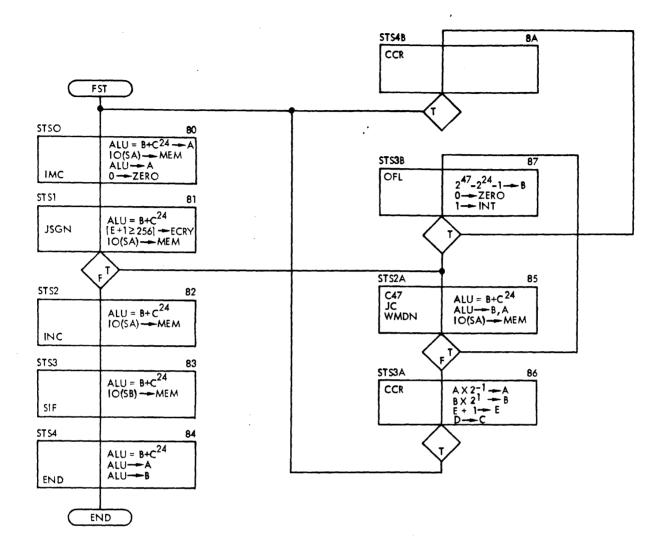

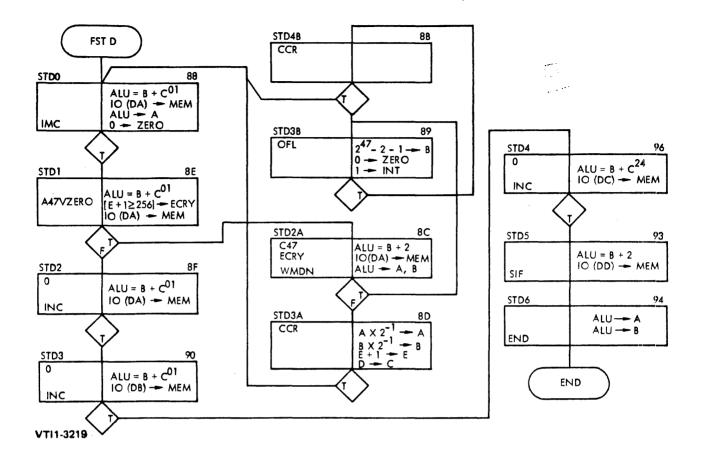

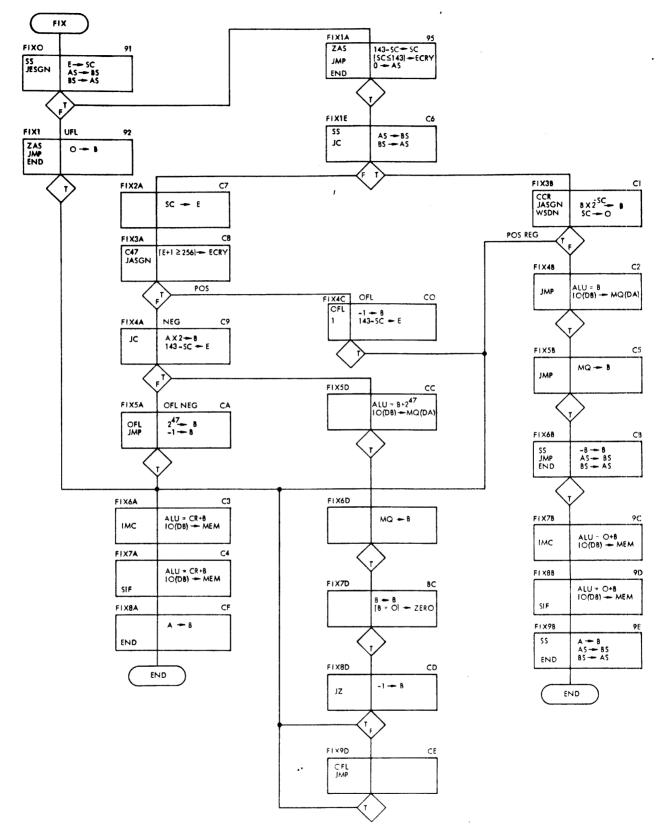

|         | 4.5.9<br>4.5.10<br>4.5.11<br>4.5.12<br>4.5.13<br>4.6 | FDVD Routine                                                                                                                           | 4 - 64<br>4 - 66<br>4 - 69<br>4 - 69<br>4 - 75<br>4 - 78 |

|         | 4.6.1<br>4.6.2<br>4.6.3<br>4.6.4                     | Central Processor Control<br>Priority Control                                                                                          | 4 - 79<br>4 - 82<br>4 - 86<br>4 - 88                     |

|         | 4.6.5<br>4.6.6<br>4.6.7                              | Memory Control                                                                                                                         | 4 - 89<br>4 - 93<br>4 - 96                               |

|         | 4.6.8<br>4.6.9<br>4.6.10                             | Arithmetic Clock Control Logic<br>Data Latch and Address Output<br>Instruction Latch, Instruction<br>Register, and Instruction Decoder | 4-98<br>4-103<br>4-104                                   |

|         | 4.6.11<br>4.6.12<br>4.6.13                           | Control Store Address Loop<br>Jump Condition Multiplexor<br>Control Store Memory, Register,                                            | 4-106<br>4-108                                           |

|         | 4.6.14<br>4.6.15<br>4.6.16                           | and Decoder                                                                                                                            | 4-108<br>4-111<br>4-117<br>4-123                         |

|         | 4.6.17<br>4.6.18<br>4.6.19                           | A, B Control Encoder                                                                                                                   | 4-127<br>4-130<br>4-132                                  |

|         | 4.6.20<br>4.6.21<br>4.6.22<br>4.6.23                 | Sign and Zero Flags                                                                                                                    | 4-133<br>4-135<br>4-136<br>4-138                         |

|         | 4.6.23.1<br>4.6.23.2                                 | Exponent Operations for Floating<br>Multiplication                                                                                     | 4-139<br>4-141                                           |

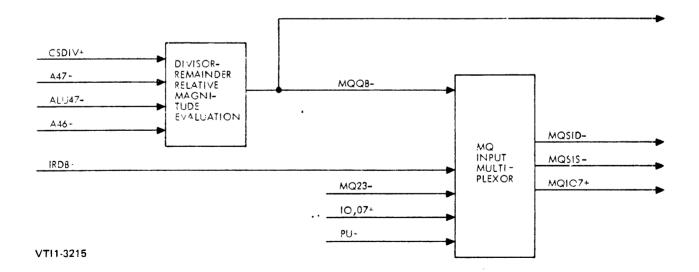

|         | 4.6.24<br>4.6.25                                     | Division                                                                                                                               | 4 - 143<br>4 - 148                                       |

| 5       | MAINTENANC                                           | Ε                                                                                                                                      | 5-1                                                      |

|         | 5.1<br>5.2<br>5.3                                    | Test Equipment                                                                                                                         | 5-1<br>5-1<br>5-1                                        |

i

## TABLE OF CONTENTS (continued)

| Section | Title     |      |      |       |     |     |    |    |     |     |   |   |   |   |   |   |   |   | Page  |

|---------|-----------|------|------|-------|-----|-----|----|----|-----|-----|---|---|---|---|---|---|---|---|-------|

| . 6     | MNEMONICS | •••  | • •  | •     | •   | •   | •  | •  | •   | •   | • | • | • | • | • | • | • | • | 6 - 1 |

| 7       | TEST PROG | RAMS | • •  | •     | •   | •   | •  | •  | •   | • • | • | • | • | • | • | • | • | • | 7-1   |

|         | 7.1       |      | nera |       |     |     |    |    |     |     |   |   |   |   |   |   |   |   | 7 - 1 |

|         | 7.2       |      | st I |       |     |     |    |    |     |     |   |   |   |   |   |   |   |   | 7-1   |

|         | 7.2.1     |      | erat |       |     |     |    |    |     |     |   |   |   |   |   |   |   |   | 7 - 1 |

|         | 7.2.2     | Fa   | ult  | Тe    | st  | •   | •  | •  | •   | •   | • | • | • | • | • | • | • | • | 7 - 1 |

|         | 7.2.3     | Se   | quer | nce   | Τe  | est |    | •  |     |     | • |   | • | • | • |   |   | • | 7-1   |

|         | 7.3       | Pr   | ogra | 1 m-' | Гаг | )e  | Lo | ad | lin | g   |   |   | • |   |   | • |   | • | 7 - 2 |

|         | 7.4       | Se   | nse  | Sw    | itò | he  | S  | •  |     |     | • |   |   |   |   |   |   | • | 7 - 2 |

|         | 7.5       |      | erat |       |     |     |    |    |     |     |   |   |   |   |   |   |   |   | 7 - 3 |

|         | 7.6       |      | ror  |       |     |     |    |    |     |     |   |   |   |   |   |   |   |   | 7 - 4 |

|         | 7.7       | TT   | Y Pi | cin   | toi | it  | Ēx | am | ip1 | e   | • | • | • | • | • | • | • | • | 7 - 4 |

••

LIST OF ILLUSTRATIONS

| Figure         | Title                                        | Page           |

|----------------|----------------------------------------------|----------------|

| 2 - 1<br>3 - 1 | FPP Board                                    | 2 - 2          |

| 3-2            | FPP Instruction Format                       | 3 - 3          |

| 3-3            |                                              | 3-3            |

| 3-3            |                                              | 3-4            |

| 3-4            | Examples of Single Precision Numbers         | 3-6            |

| 3-6            |                                              | 3-7            |

| 4-1            | Integer Format                               | 3 - 8<br>4 - 2 |

| 4 - 2          | FPP Simplified Functional Block Diagram      |                |

| 4 - 2          | FPP Detailed Block Diagram                   | 4 - 5          |

| 4 - 4          | Microinstruction Word Formats                | 4-12           |

| 4 - 4          | Flow Chart Microinstruction Block Format     | 4 - 25         |

| 4-5            | FLD Routine Flowchart                        | 4 - 26         |

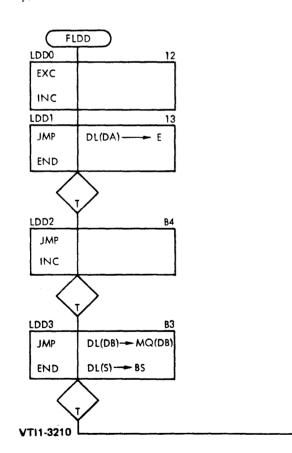

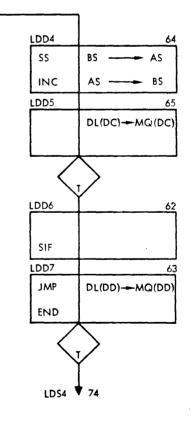

| 4-0            | FLDD Routine Flowchart                       | 4 - 27         |

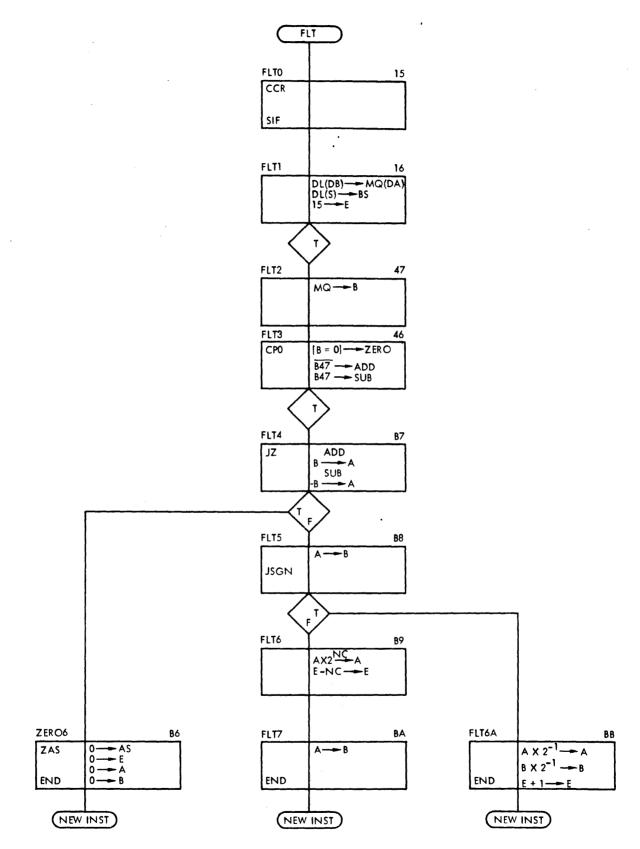

| 4 - 7          |                                              | 4 - 29         |

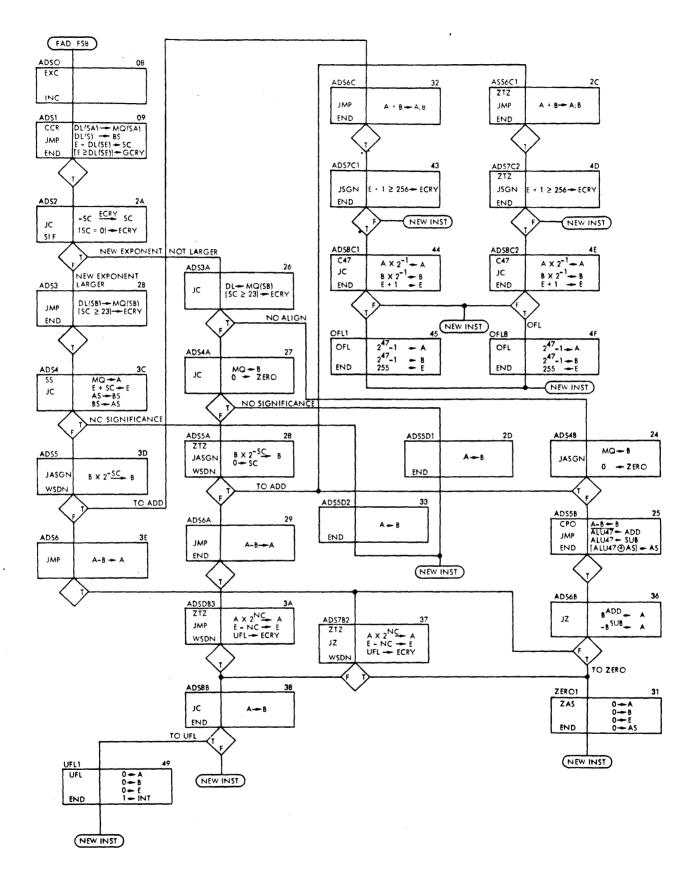

| 4 - 8<br>4 - 9 |                                              | 4-32           |

| 4-9<br>4-10    |                                              | 4 - 33         |

|                |                                              | 4 - 36         |

| 4-11           |                                              | 4 - 4 3        |

| 4-12           |                                              | 4 - 4 5        |

| 4-13           | FMU Example $(+1/2)$ $(1 1/4) = 5/8$         | 4 - 4 7        |

| 4 - 1 4        | Example of Fraction Multiplication Procedure | 4 40           |

| 4 1 5          | $(1/2 \times 5/8)$                           | 4 - 49         |

| 4-15           |                                              | 4 - 5 5        |

| 4-16           | FDV Routine Flowchart                        | 4 - 56         |

| 4-17           |                                              | 4-59           |

| 4-18           | Fraction Division Procedure Example          | 4-61           |

| 4-19           | FDVD Routine Flowchart                       | 4-65           |

| 4 - 20         | FST Routine Flowchart                        | 4-67           |

| 4-21           | FSTD Routine Flowchart.                      | 4 - 70         |

| 4 - 22         | FIX Routine Flowchart                        | 4 - 7.2        |

| 4 - 23         | FIX Example                                  | 4 - 76         |

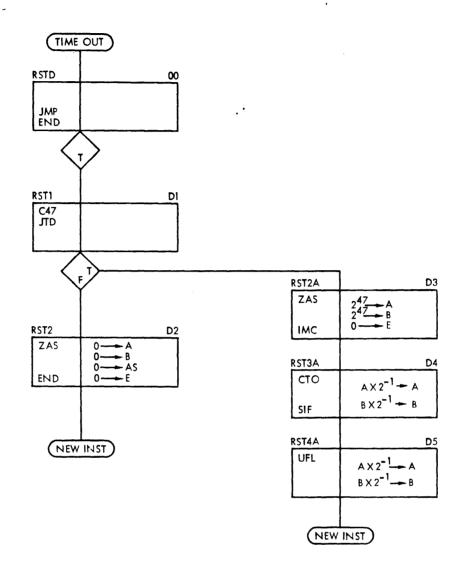

| 4 - 24         | System Reset/Time-Out Routine Flowchart      | 4 - 77         |

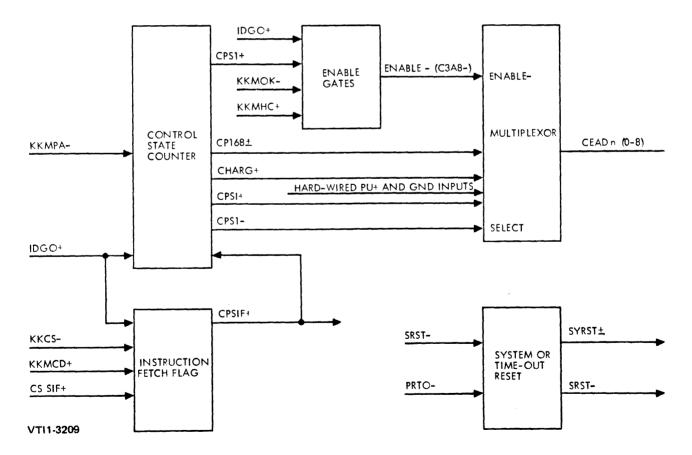

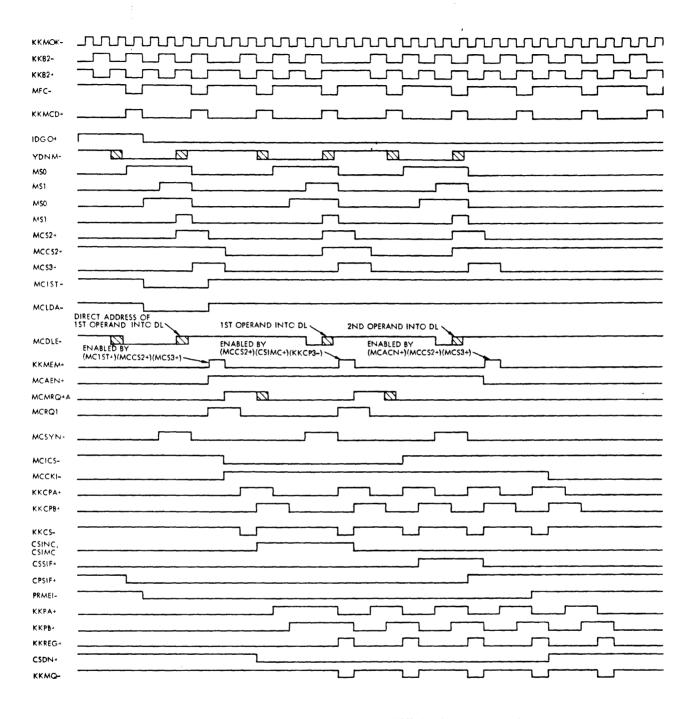

| 4 - 25         | Central Processor Control, Block Diagram     | 4-79           |

| 4 - 26         | Central Processor Control Timing             | 4-80           |

| 4 - 27         | Priority Control, Block Diagram              | 4 - 83         |

| 4 - 28         | FLD Instruction, Timing Diagram              | 4 - 85         |

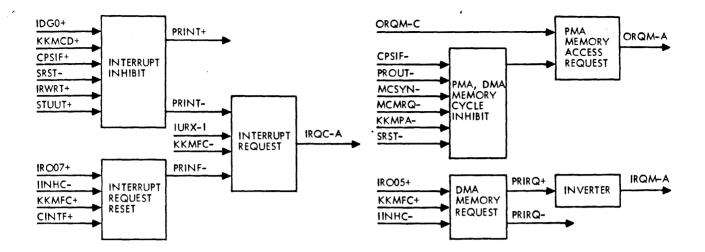

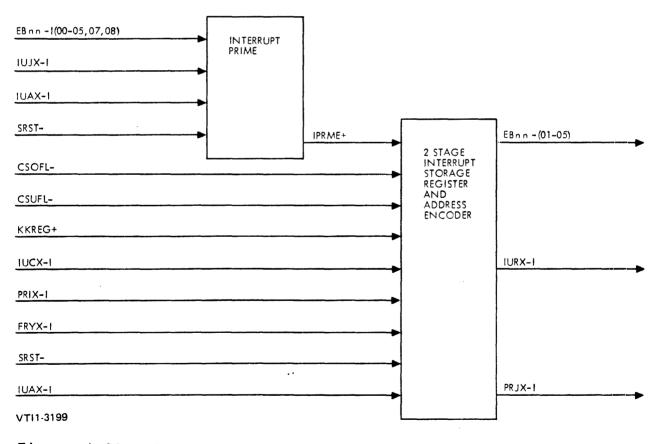

| 4 - 29         | Interrupt Interface, Block Diagram           | 4-86           |

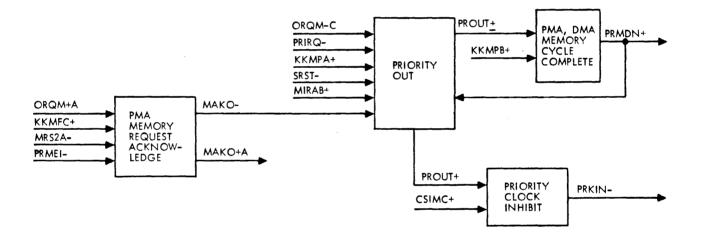

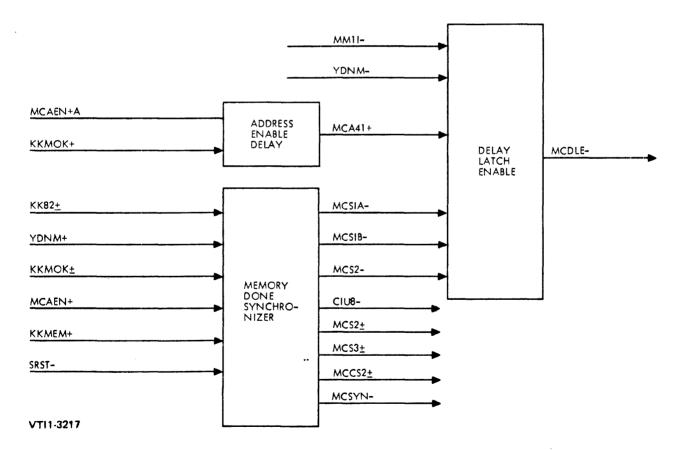

| 4 - 30         | emory Sequencer, Block Diagram               | 4 - 88         |

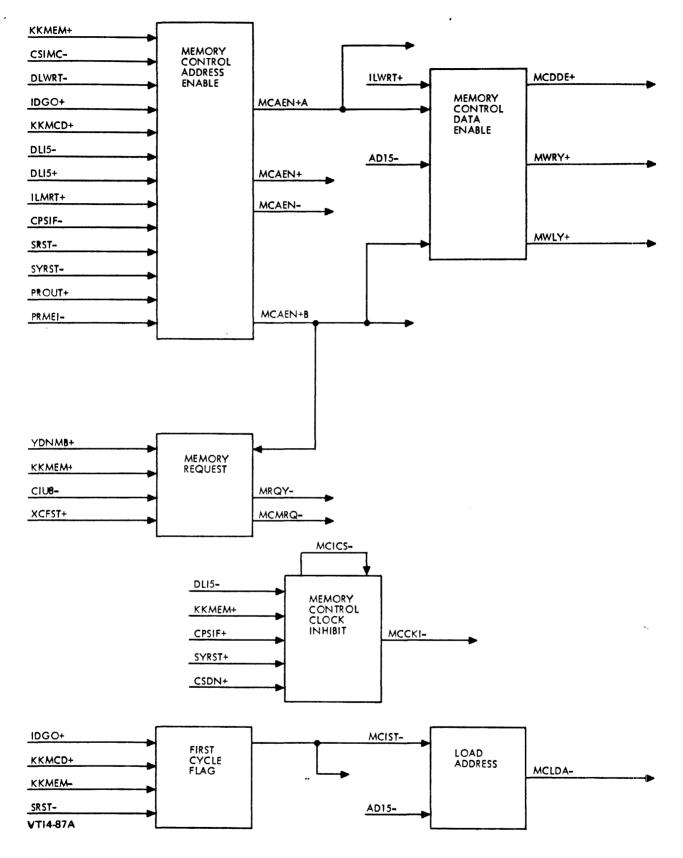

| 4 - 31         | Memory Control, Block Diagram                | 4-90           |

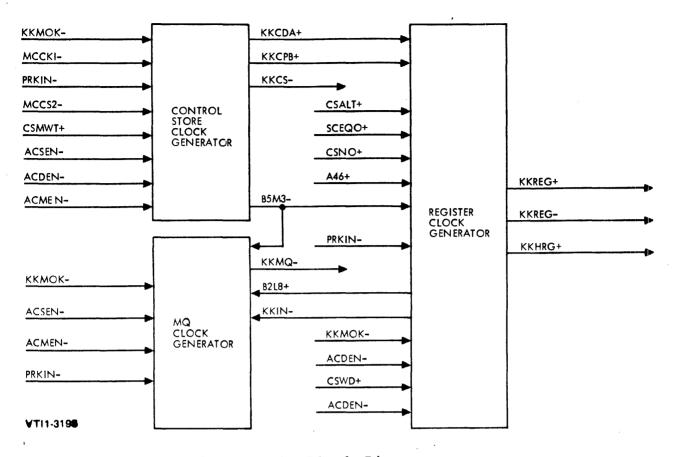

| 4 - 32         | Clock Control, Block Diagram                 | 4-94           |

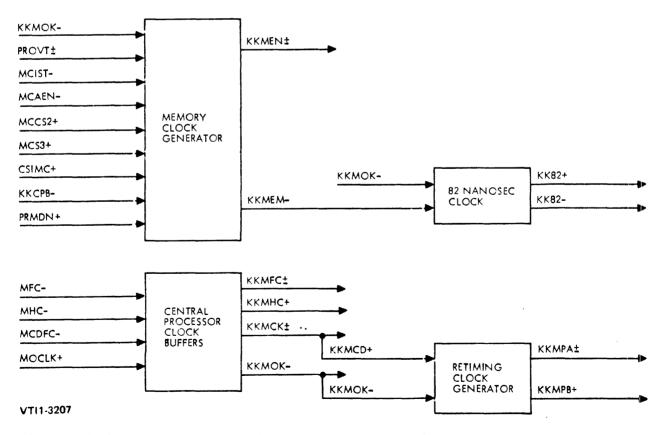

| 4 - 33         | System Clock Generator, Block Diagram        | 4-96           |

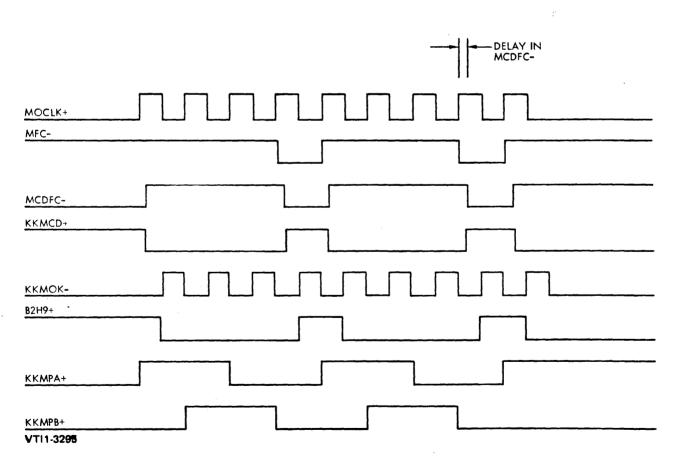

| 4 - 34         | Retiming Clock Generator Waveforms           | 4-97           |

| 4 - 35         | Arithmetic Clock Control, Block Diagram      | 4-99           |

| 4 - 36         | Align Microinstruction Timing                | 4-100          |

.

### LIST OF ILLUSTRATIONS (continued)

| Figure  | Title                                        | Page     |

|---------|----------------------------------------------|----------|

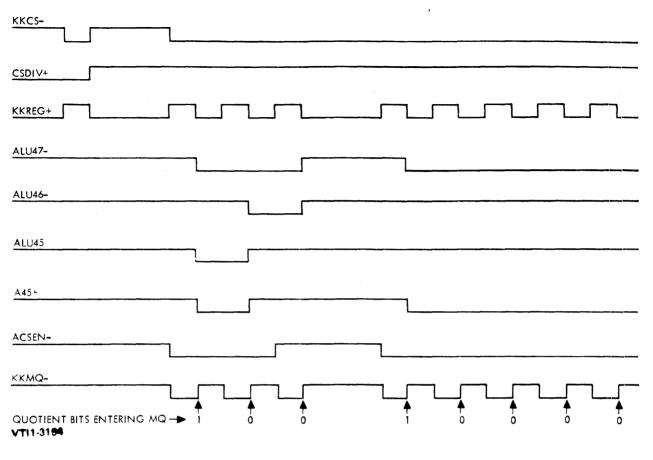

| 4 - 37  | Timing at Start of CSDIV Microinstruction    | 4-102    |

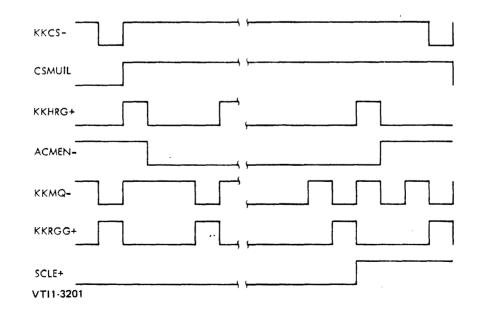

| 4-38    | Timing of ACMEN                              | 4-102    |

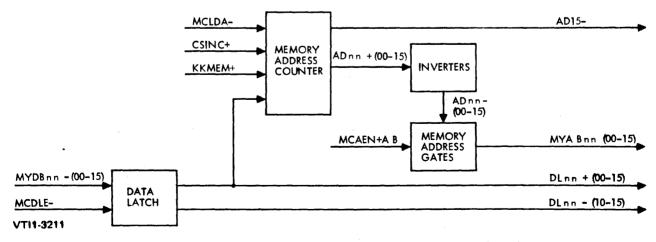

| 4-39    | Data Latch and Address Output, Block Diagram | 4 - 1.03 |

| 4 - 40  | Instruction Latch, Instruction Register and  |          |

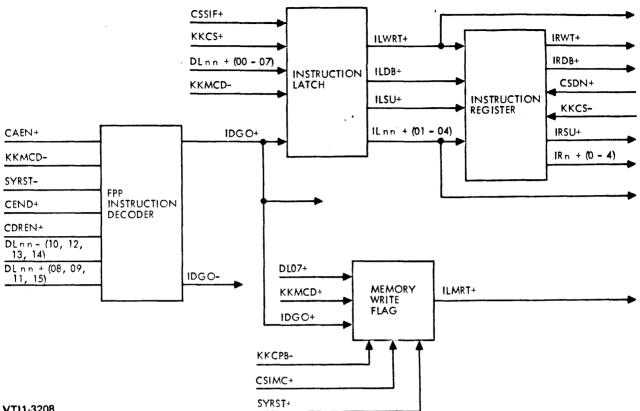

|         | Instruction Decoder, Block Diagram           | 4-105    |

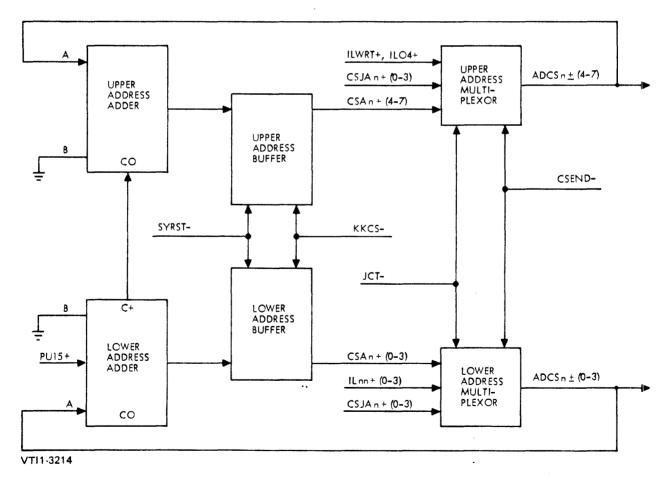

| 4 - 41  | Control Store Address Loop, Block Diagram    | 4 - 106  |

| 4 - 4 2 | Control Store Memory, Register, and          |          |

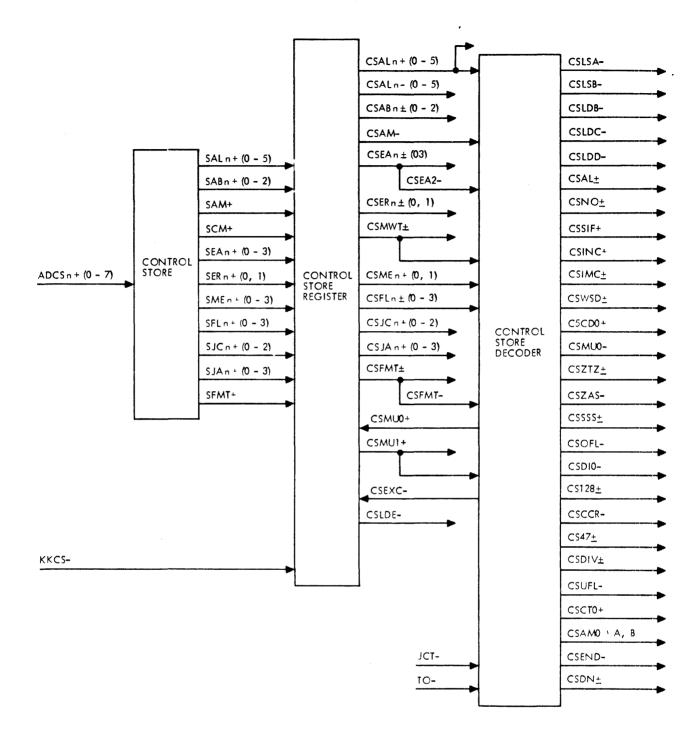

|         | Decoder, Block Diagram                       | 4-110    |

| 4 - 4 3 | I/O Data Multiplexors, Block Diagram         | 4-115    |

| 4 - 4 4 | Data Loop, Block Diagram                     | 4-117    |

| 4 - 4 5 | Data Loop Register Usages                    | 4-119    |

| 4 - 46  | MQ Register Loading Formats                  | 4-120    |

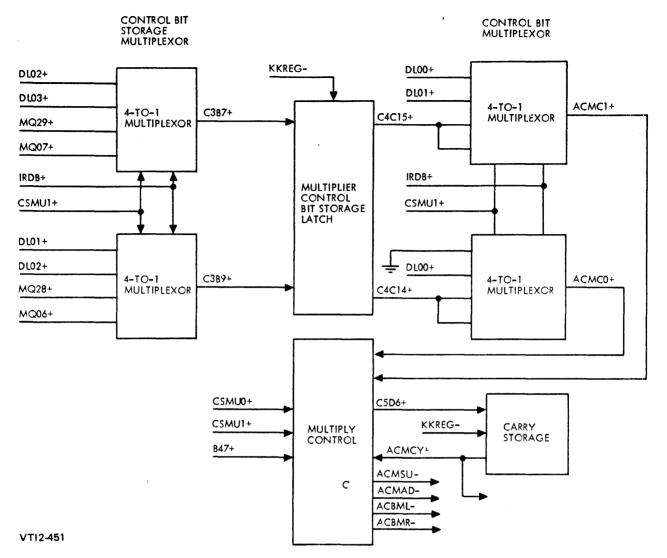

| 4 - 4 7 | Multiply Control, Block Diagram              | 4 - 124  |

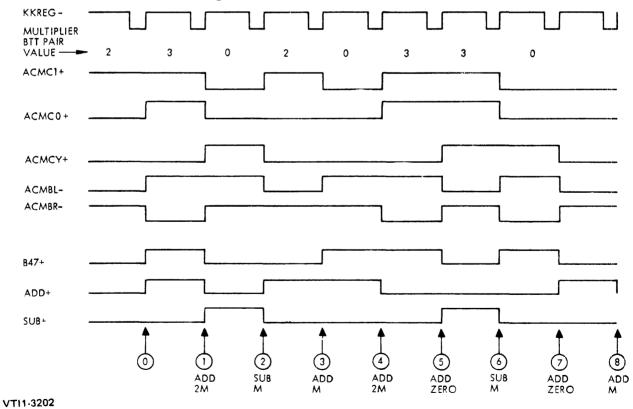

| 4 - 48  | Example of Multiply Control Timing           | 4-126    |

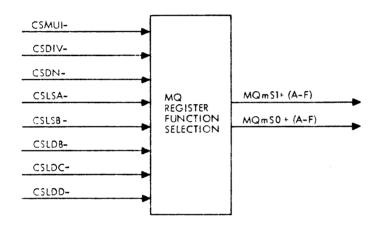

| 4 - 4 9 | MQ Control, Block Diagram                    | 4 - 130  |

| 4 - 50  | ALU Control, Block Diagram                   | 4-132    |

| 4-51    | Sign and Zero Flags, Block Diagram           | 4-134    |

| 4 - 5 2 | Constant and Conditional Inverter, Block     |          |

|         | Diagram                                      | 4-136    |

| 4 - 5 3 | Exponent Loop, Block Diagram                 | 4-137    |

| 4 - 54  | Exponent Control                             | 4-144    |

|         | •                                            | 4 - 148  |

### LIST OF TABLES

| Table   | Title                                     | Page      |

|---------|-------------------------------------------|-----------|

| 1-1     | FPP Specifications                        | 1-3       |

| 2-1     | FPP Board                                 | 2 - 2     |

| 3-1     | FPP Instructions                          | 3 - 2     |

| 4 - 1   | Nomenclature Correlation                  | 4-10      |

| 4 - 2   | Microinstruction Field Formats            | 4-13      |

| 4 - 3   | Special Flowchart Notations               | 4 - 24    |

| 4 - 4   | Control Store Address Multiplexor Outputs | 4-107     |

| 4 - 5   | Jump Condition Selections                 | 4-109     |

| 4 - 6   | Control Store and Control Store Register  |           |

|         | Outputs                                   | 4-112     |

| 4 - 7   | Control Store Decoder Signals             | 4-113     |

| 4 - 8   | I/O Data Multiplexor Selections           | 4-116     |

| 4 - 9   | ALU Functions                             | 4-118     |

| 4-10    | MQ, A, and B Register Function Selection  | 4 - 1 2 0 |

| 4-11    | A Multiplexor Selections                  | 4 - 1 2 3 |

| 4-12    | Multiplier Control Bit Selections         | 4-126     |

| 4 - 1 3 | Multiple Control                          | 4 - 1 2 8 |

|         | •                                         |           |

## LIST OF TABLES (continued)

| Table   | Title                                    | Page  |

|---------|------------------------------------------|-------|

| 4 - 1 4 | A, B Control Encoder                     | 4-129 |

| 4-15    | Exponent Operations for Floating         |       |

|         | Multiplication                           | 4-140 |

| 4-16    | Exponent Operations for Floating Divison | 4-142 |

| 4-17    | Exponent Additions and Subtractions      | 4-146 |

| 4-18    | Exponent Loop ALU Function Selection     | 4-147 |

| 4-19    | Stored Constants                         | 4-150 |

| 7-1     | SENSE Switch Settings                    | 7 - 2 |

| 7 - 2   | Test Selection Directives                | 7 - 3 |

| 7 - 3   | Sequence Test Commands                   | 7 - 5 |

| 7 - 4   | Error Messages                           | 7-9   |

| 7 - 5   | Sample TTY Printout                      | 7-10  |

SECTION 1 GENERAL DESCRIPTION

The SPERRY UNIVAC V70 Series Floating Point Processor Manual describes the Floating Point Processor (FFP) and its interface with other 70 series system components.

The manual is divided into the following seven sections:

- General Description (Introduction to the FPP, related publications, and specifications)

- o Installation

- o Operation

- o Theory of operation

- o Maintenance

- o Mnemonics list

- o Test programs

There is also a system documentation package which is assembled when the hardware is shipped and reflects the configuration of a specific system. It contains engineering documents such as logic and installation drawings.

The following list contains the part numbers of other manuals pertinent to the SPERRY UNIVAC 70 series computers (the x at the end of each document part number is the revision number and can be any digit 0 through 9):

| V70 Series Architecture Reference Manual | 98A 9906 00x |

|------------------------------------------|--------------|

| Processor Manual                         | 98A 9906 02x |

| Option Board Manual                      | 98A 9906 05x |

| Microprogramming Guide                   | 98A 9906 07x |

| Writable Control Store Manual            | 98A 9906 08x |

| Memory Map Manual                        | 98A 9906 10x |

| V76 System Reference Manual              | 98A 9906 23x |

| V77-600 System Reference Manual          | 98A 9906 40x |

| MAINTAIN III Manual                      | 98A 9952 07x |

The FPP is a high-speed, special-purpose processor which performs the arithmetic operations on single and double precision real numbers represented in V70 series floating point format. It also performs conversions between floating point and integer formats.

When the FPP is installed in a V70 series system, its 56-bit floating point accumulator and floating point instruction set are fully integrated into the computer architecture both at the machine language programming level and at the FORTRAN level. This minimizes the overhead associated with passing control between the FPP and the central processor. Pipelining of instructions is implemented in order to increase throughput. Direct memory access is used to obtain operands and store results.

The basic FPP clock period is 165 nanoseconds; however, fast shift operations occur during 82 nanosecond clock periods. This provides faster average execution times by minimizing the time spent in shifting the contents of the accumulator in connection with alignment or normalization.

Specifications for the FPP are listed in table 1-1.

Table 1-1. Floating Point Processor Specifications

| Parameter                                                      | Specification                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic<br>operations                                       | Addition, subtraction, multiplication, or<br>division of single or double precision<br>floating point representations of real<br>numbers. (Mixed precision operations such<br>as addition of single precision operand to<br>double precision operand can be<br>performed.)          |

| Format<br>conversions                                          | Conversions between floating point format<br>and 16-bit twos complement integer<br>formats. (Operands in integer format<br>must be converted to floating point<br>format prior to performing arithmetic.<br>Results can be converted to integer<br>format before storage in memory. |

| Number range<br>(magnitude                                     | Largest magnitude: Single precision:<br>$2^{127}(1 - 2^{-22})$                                                                                                                                                                                                                      |

| ranges are<br>same for<br>positive and<br>negative<br>numbers) | Double precision:<br>$2^{127}(1 - 2^{-45})$                                                                                                                                                                                                                                         |

| numbers)                                                       | Smallest non-zero magnitude: 2 <sup>-129</sup>                                                                                                                                                                                                                                      |

|                                                                | Zero is also a valid magnitude.                                                                                                                                                                                                                                                     |

| Normalization                                                  | All result values except zero are<br>normalized before storage. All<br>operand values except zero are<br>normalized.                                                                                                                                                                |

| Round off                                                      | Results are rounded off before storage.                                                                                                                                                                                                                                             |

| Out of range<br>indication                                     | The FPP initiates an interrupt when an<br>out of range result occurs. (The<br>interrupt is also initiated if a string<br>of FPP instructions does not end with a<br>store instruction within 500 micro-<br>seconds).                                                                |

·...

## Table 1-1. Floating Point Processor Specifications (continued)

| Parameter                       | Specification                                                                                                                                                                      |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt<br>inhibit            | The FPP inhibits all interrupts when it is<br>executing a sequence of instructions. (A<br>sequence is defined to end when an<br>instruction which stores a result is<br>executed.) |

| Software<br>operating<br>system | Normally VORTEX I or VORTEX II. Will<br>operate in any environment which provides<br>required instruction, address, and operand<br>formats.                                        |

| Interrupt<br>address            | 076 (octal).                                                                                                                                                                       |

| Priority<br>assignment          | Between real-time clock and highest<br>priority PIM (for VORTEX I or VORTEX II<br>environment).                                                                                    |

| Basic cycle<br>time             | 165 Nanoseconds.                                                                                                                                                                   |

| Fast shift<br>cycle time        | 82.5 Nanoseconds.                                                                                                                                                                  |

| Dimensions                      | Contained on a 15.6 by 19 inch (39.6 by<br>48.3 cm) wire-wrap board.                                                                                                               |

| Installation                    | Plugs into V70 series mainframe chassis<br>using three module slots.                                                                                                               |

| Input power                     | +5V dc at 16 amperes.                                                                                                                                                              |

| Operational<br>environment      | 0 to 50 degrees C, 0 to 90 percent relative humidity without condensation.                                                                                                         |

• •

SECTION 2 INSTALLATION

#### 2.1 INSPECTION

The FPP has been packed and inspected to ensure its arrival in good working order. To prevent damage, take care during unpacking and handling. Check the shipping list to ensure that all equipment has been received. Immediately after unpacking, inspect the equipment for shipping damage. Ascertain that wires are neither loose nor broken and that hardware is secure. If damage exists:

- a. Notify the transportation company.

- b. Notify Sperry Univac.

- c. Save all packing material.

#### 2.2 PHYSICAL DESCRIPTION

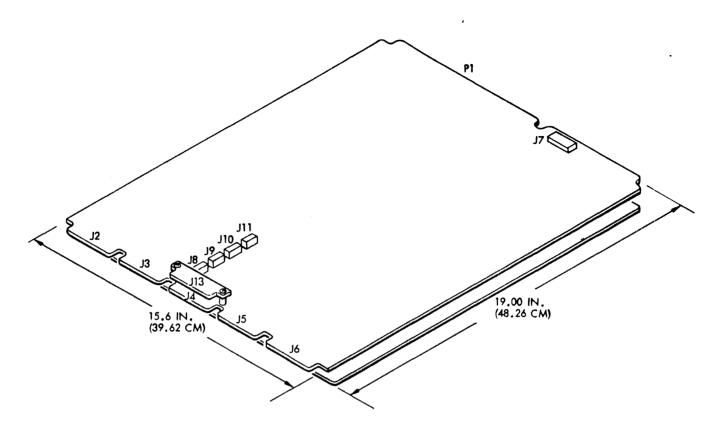

The FPP circuits are on a 15.6 by 19 inch wire-wrap circuit board (p/n 44P0723). Figure 2-1 shows dimensions and connectors of the FPP board.

#### 2.3 DISCRETIONARY WIRING

Some of the FPP board wiring is dependent upon the system configuration in which the floating point processor is used. The wiring required for the particular application is normally installed at the factory. If a change in the system configuration is required, refer to FPP option drawing 01A1682 (in the system documentation package) for information concerning optional wiring.

#### 2.4 INTERCONNECTION

The FPP board plugs into the V70 series mainframe chassis using three module slots. The FPP board is essentially connected in parallel with the central processor board. The only exception to this involves three I/O control signals which pass directly between the central processor and the option board when an FPP board is not used but which are modified by the FPP when an FPP board is used.

The FPP board operates from a +5-volt power source and draws 16 amperes.

VTI1-3205

Figure 2-1. FPP Board

For details of signal and power interconnection for any system configuration refer to FPP option drawing 01A1682 (in the system documentation package).

SECTION 3 OPERATION

The FPP contains no operating controls or indicators. The FPP is normally operated in a VORTEX or VORTEX II environment using FORTRAN. However, the FPP can operate in any environment which supplies instructions, addresses, and operands in appropriate formats.

#### **3.1** FPP INSTRUCTIONS

When so directed by the user, the FORTRAN compiler provides the FPP instructions listed in table 3-1. The user also has the option of coding FPP instructions directly in assembly language using the octal codes specified by table 3-1 or defining macros and using the table 3-1 mnemonics.

Table 3-1 gives minimum and maximum execution times for both semiconductor memory and core memory. The maximum times do not include unusual cases such as overflow.

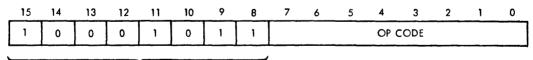

Figure 3-1 illustrates the format of the FPP instruction word. The address format is illustrated in figure 3-2. There is no specific limitation on the number of levels of indirect addressing. However, the time allotted for the execution of any string of FPP instructions, including all required memory accesses, is 500 microseconds.

A string of FPP instructions is defined as any sequence during which operands are obtained and processed and a result is stored in memory. Thus, an FST, FSTD, or FIX instruction is always the last instruction of an FPP string.

3.2 NUMBER FORMATS

#### 3.2.1 Single Precision Floating Number Format

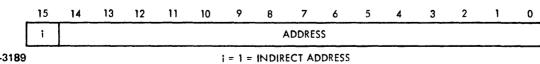

As illustrated in figure 3-3, each single precision real floating point number is stored in memory in two consecutive word locations. The first word contains the sign bit (S), the exponent (in excess-128 format), and the seven high order bits of the fraction. The second word contains the 15 low order bits of the fraction (bit 15 is always zero).

|               |               |                                                                                           | Execution<br>(Nanoseco  |                |

|---------------|---------------|-------------------------------------------------------------------------------------------|-------------------------|----------------|

| Mne-<br>monic | Octal<br>Code | Description                                                                               | Semiconductor<br>Memory | Core<br>Memory |

|               |               | Memory Reference                                                                          |                         |                |

| FLD           | 105420        | Load floating point<br>accumulator with<br>single precision<br>number.                    | 1815                    | 2723           |

| FLDD          | 105522        | Load floating point<br>accumulator with<br>double precision<br>number.                    | 2475                    | 4043           |

| FST           | 105600        | Store floating<br>point accumulator<br>in memory in single<br>precision format.           | 1980                    | 2888           |

| FSTD          | 105710        | Store floating<br>point accumulator<br>in memory in double<br>precision format.           | 2640                    | 4208           |

| FLT           | 105425        | Reformat single<br>precision integer<br>and load into float-<br>ing point<br>accumulator. | 1485-2475               | 2063-2723      |

| FIX           | 105621        | Reformat floating<br>point accumulator<br>and store integer<br>in memory.                 | 1980-3960               | 2558-4538      |

|               | <b>.</b>      | Arithmetic Instructio                                                                     | ns                      |                |

| FAD           | 105410        | Add single<br>precision memory<br>to floating ṗoint<br>accumulator.                       | 1815-3300               | 2723-3878      |

,

### Table 3-1. FPP Instructions

|               |               |                                                                  | Execution<br>(Nanosecon |                |

|---------------|---------------|------------------------------------------------------------------|-------------------------|----------------|

| Mne-<br>monic | Octal<br>Code | Description .                                                    | Semiconductor<br>Memory | Core<br>Memory |

| FADD          | 105503        | Add double precision<br>memory to floating<br>point accumulator. | 2475-5940               | 4043-7178      |

| FSB           | 105450        | Single precision<br>floating point<br>subtraction.               | 1815-3300               | 2723-3878      |

| FSBD          | 105543        | Double precision<br>floating point<br>subtraction.               | 2475-5940               | 4043-7178      |

| FMU           | 105416        | Single precision<br>floating point<br>multiply.                  | 2970-3300               | 3383-3713      |

| FMUD          | 105506        | Double precision<br>floating point<br>multiply.                  | 5445-5775               | 6518-6848      |

| FDV           | 105401        | Single precision<br>floating point<br>divide.                    | 3465-5280               | 4043-5693      |

| FDVD          | 105535        | Double precision<br>floating point<br>divide.                    | 6105-9735               | 7343-10973     |

'

Table 3-1. FPP Instructions (continued)

FPP CODE

Figure 3-1. FPP Instruction Format

VTI1-3189

I = I = INDIKECT ADDRI

Figure 3-2. Operand Address Format

|                  | 15 | 14 | 13 | 12 | 11   | 10      | 9  | 8    | 7    | 6     | 5 | 4    | 3      | 2     | 1 | 0 |

|------------------|----|----|----|----|------|---------|----|------|------|-------|---|------|--------|-------|---|---|

| 1ST<br>WORD (SA) | s  |    |    | E× | PONE | NT + 1: | 28 |      |      |       |   | FRAC | TION ( | HIGH) |   |   |

| 2ND<br>WORD (SB) | 0  |    |    |    | -    |         |    | FRAC | TION | (LOW) |   |      |        |       |   |   |

A. FIELDS

| s                  | 128             | 64              | 32        | 16        | 8         | 4         | 2          | 1          | 1/2               | 1/4              | 1/8              | 1/16             | 1/32             | 1/64             | 1/128            |

|--------------------|-----------------|-----------------|-----------|-----------|-----------|-----------|------------|------------|-------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 0                  | <u>1</u><br>256 | <u>1</u><br>512 | 1<br>1024 | 1<br>2048 | 1<br>4096 | 1<br>8192 | 1<br>16384 | 1<br>32768 | <u>1</u><br>65536 | 2 <sup>-17</sup> | 2 <sup>-18</sup> | 2 <sup>-19</sup> | 2 <sup>-20</sup> | 2 <sup>-21</sup> | 2 <sup>-22</sup> |

| B. DECIMAL WEIGHTS |                 |                 |           |           |           |           |            |            |                   |                  |                  |                  | 4                |                  |                  |

| 4. | 194, | 304 |

|----|------|-----|

| •• |      |     |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

EXPONENT + 128 = 128 + 8

| EXPONENT     | = 8                           |

|--------------|-------------------------------|

| FRACTION     | = 1/2 + 1/4 + 1/64 + 1/256    |

| VALUE OF NO. | - 2 <sup>E</sup> X (FRACTION) |

$= 2^8 (1/2 + 1/4 + 1/64 + 1/256)$

= 256 (1/2 + 1/4 + 1/64 + 1/256)

= 128 + 64 + 4 + 1 = 213

C. EXAMPLE OF POSITIVE NUMBER (213)

| WORD<br>CONTAINING | 1 | 0 | 1 | 1 | ١     | 0      | 1      | 1      | ١      | 0     | 0        | 1     | ١ | 1 | 0 | 1                               |

|--------------------|---|---|---|---|-------|--------|--------|--------|--------|-------|----------|-------|---|---|---|---------------------------------|

| COMPLEMENT<br>FORM | 0 | 1 | 0 | 0 | 0     | 0      | 0      | 0      | 0      | 0     | 0        | 0     | 0 | 0 | 0 | 0                               |

|                    |   |   |   | 1 | NOTE: | THIS I | s -213 | . SAM  | E AS C | EXCEP | TNEG     | ATIVE |   |   |   | in a generation of a stranged i |

|                    |   |   |   |   | D     | . EXA  | MPLE C | DF NEC | GATIVE | NUME  | BER (-21 | 13)   |   |   |   |                                 |

| VTI2-443           |   |   |   |   |       | • ·    |        |        |        |       |          |       |   |   |   |                                 |

Figure 3-3. Single Precision Number Format

.

The value of a floating point number is  $2^{E}$  X (FRACTION), where E = exponent. The 8-bit exponent code provides an exponent range of +127 (1111 1111) through -128 (0000 0000). Unless the value of a number is zero, the fraction must be normalized; that is, the most significant 1 of the fraction must be in the  $2^{-1}$  bit position. The range of values that can be expressed by the fraction is thus  $2^{-1}$  (represented by a 1 in the  $2^{-1}$  bit position followed by all zeros) through  $(1 - 2^{-22})$  (represented by all ones). Combining the exponent and fraction ranges, the largest magnitude that can be represented is  $2^{127}$  X  $(1 - 2^{-22})$ and the smallest non-zero magnitude is  $2^{-128}$  X  $2^{-1} = 2^{-129}$ . A negative number is represented in the same manner as the corresponding positive number except that the entire word containing the sign bit is in one's complement form.

Figure 3-4 illustrates the representation of various numbers within the allowable range. Notice that the zero which always appears in bit position 15 of the second operand word is not shown in the binary representation since it is not a component of the fraction. It is, however, a component of the second operand word format, shown in octal format.

#### 3.2.2 Double Precision Floating Point Number Format

As illustrated in figure 3-5, each double precision real floating point number is stored in memory in four consecutive word locations. The first word contains the exponent in excess-128 code. The second word contains the sign bit and the 15 most significant bits of the fraction. The range of values that can be represented by the double-precision fraction is  $2^{-1}$  through  $(1 - 2^{-45})$ . The double precision words thus provide a non-zero magnitude range from  $2^{-128} \times 2^{-1} = 2^{-129}$  through  $2^{127} \times (1 - 2^{-45})$ . For a negative number, the entire second operand word is in one's complement form (since this is the word containing the sign bit).

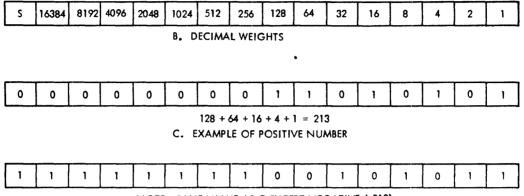

#### 3.2.3 Integer Format

As illustrated in figure 3-6, the integer format employs a single 16-bit word. Positive numbers appear in absolute form and negative numbers appear in two's complement form.

#### 3.3 PROGRAM INTERRUPTS

The FPP normally inhibits program interrupts from the time that the first instruction of an FPP string is received until the final instruction of the string is executed, regardless of intervening instructions. However, the FPP can only inhibit interrupts for a maximum interval of 500 microseconds after which interrupts are again enabled and the FPP generates a fault interrupt. The FPP also generates a fault interrupt

|          |                        | VALUE OF NUMBER                             | s | EXPONENT | HIGH<br>FRACTION | LOW<br>FRACTION                         | 1ST<br>OPERAND<br>WORD<br>(OCTAL) | 2ND<br>OPERAND<br>WORD<br>(OCTAL) |

|----------|------------------------|---------------------------------------------|---|----------|------------------|-----------------------------------------|-----------------------------------|-----------------------------------|

| T        | LARGEST<br>MAGNITUDE   | $2^{127} \times (1 - 2^{-22})$              | 0 | 1111111  | 111111           | 11111111111111111                       | 077777                            | 077777                            |

| POSITIVI | F                      | $2^{127} \times 2^{-1} = 2^{126}$           | 0 | 1111111  | 1000000          | 000000000000000000000000000000000000000 | 077700                            | 000000                            |

| RANGE    | -                      | $2^{1} \times 2^{-1} = 1$                   | 0 | 10000001 | 1000000          | 000000000000000000000000000000000000000 | 040300                            | 000000                            |

|          | SMALLEST<br>MAGNITUDE  | $2^{-128} \times 2^{-1} = 2^{-129}$         | 0 | 00000000 | 1000000          | 000000000000000000000000000000000000000 | 000100                            | 000000                            |

|          | ZERO                   | $2^{-128} \times 0 = 0$                     | 0 | 00000000 | 0000000          | 000000000000000000000000000000000000000 | 000000                            | 000000                            |

| Ī        | SMALLEST<br>MAGN ITUDE | $-2^{-128} \times 2^{-1} = -2^{-129}$       | 1 | 11111111 | 0111111          | 000000000000000000000000000000000000000 | 177677                            | 000000                            |

| NEGATIV  | VE                     | $-2^1 \times 2^{-1} = -1$                   | 1 | 01111110 | 0111111          | 000000000000000000000000000000000000000 | 137477                            | 000000                            |

| RANGE    |                        | $-2^{127} \times 2^{-1} = -2^{-126}$        | 1 | 00000000 | 0111111          | 000000000000000000000000000000000000000 | 1000 <i>77</i>                    | 000000                            |

|          | LARGEST<br>MAGNITUDE   | -2 <sup>127</sup> × (1 - 2 <sup>-22</sup> ) | 1 | 00000000 | 0000000          | 1111111111111111                        | 100000                            | 077777                            |

VTI1-3212

Figure 3-4. Examples of Single Precision Numbers

following the completion of any FPP string during which a fault condition has been sensed.

#### 3.4 FAULT CONDITIONS

#### 3.4.1 Exponent Overflow

Exponent overflow can occur during the execution of any arithmetic instruction. It can also occur, in connection with round-off, during the execution of the memory reference instruction which stores the result. When an overflow is detected, the magnitude of the result is set to the largest possible in-range value and the sign of the number is not changed.

Figure 3-5. Double Precision Number Format

NOTE: SAME AS C EXCEPT NEGATIVE D. EXAMPLE OF NEGATIVE NUMBER

VT12-445

WORD CONTAINING SIGN IS IN COMPLEMENT FORM

C. EXAMPLE OF POSITIVE NUMBER (242 + 2-2)

$= 2^{43} \times (2^{-1} + 2^{-45}) = 2^{42} + 2^{-2}$

| 0       | )                                                   | 0 | 0 | o | 0 | 0 | o | ο | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |

|---------|-----------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 6       | )                                                   | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| (       | )                                                   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| (       | )                                                   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| <b></b> | +4,398,046,511,104.25 = 2 <sup>E</sup> X (FRACTION) |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

S 16384 32768 2<sup>-29</sup> 2<sup>-19</sup> 2<sup>-21</sup> 2<sup>-22</sup> 2<sup>-24</sup> 2<sup>-25</sup> 2-17 2<sup>-18</sup> 2<sup>-26</sup> 2<sup>-28</sup> 2<sup>-30</sup> 2<sup>-20</sup> 2<sup>-23</sup> 2<sup>-27</sup> 2<sup>-33</sup> 2<sup>-38</sup> 2<sup>-39</sup> 2<sup>-40</sup> 2-41 2<sup>-43</sup> 2<sup>-44</sup> 2<sup>-45</sup> 2<sup>-31</sup> 2<sup>-32</sup> 2<sup>-34</sup> **-3**5 2<sup>-36</sup> 2<sup>-37</sup> 2-42 B. DECIMAL WEIGHTS 35, 184, 372, 088, 832

6 <sup>.</sup> 5 1ST WORD (DA) 2ND ZEROS EXPONENT + 128 WORD FRACTION (HIGH) S (DB) 3RD WORD (DC) 4TH FRACTION (MID) WORD FRACTION (LOW) (DD)

A. FIELDS

s

MAGNITUDE

A. FIELDS

NOTE: SAME VALUE AS C EXCEPT NEGATIVE (-213) D. EXAMPLE OF NEGATIVE NUMBER

Figure 3-6. Integer Format

#### 3.4.2 Exponent Underflow

Exponent underflow can occur during the execution of any arithmetic instruction. When an underflow is detected, the result is set to zero.

#### 3.4.3 Integer Overflow

Integer overflow can occur during the FIX instruction. When a positive integer overflows, the integer is set to the largest positive in-range value. When a negative integer overflows, the integer is set to the most negative in-range value.

#### 3.4.4 Divide by Zero

When an attempt to divide by zero is sensed, the result is set to the largest possible in-range value and the sign of the result is not changed.

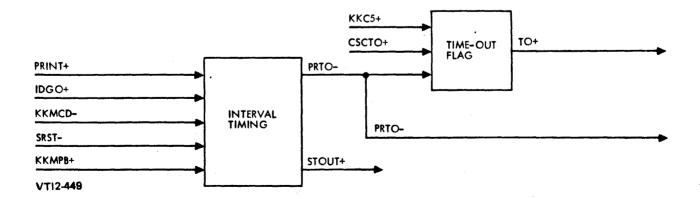

#### 3.4.5 Time-out

If the execution of an FPP instruction string is not completed within 500 microseconds, time-out is sensed. The result is then set to an illegal value to flag the type of fault that has led to the fault interrupt. (The fraction is set to the non-zero, non-normalized value, 0.01000...0. The exponent field is set to all zeros. The sign is not changed.) SECTION 4 THEORY OF OPERATION

#### 4.1 GENERAL

This section begins with a description of the major FPP functions and of the manner in which the FPP interfaces with the central processor and other components of the computer system. This is followed by a description of the microprogram facilities of the FPP. This includes information about the microinstruction word format as well as descriptions of the various FPP instruction microprogram routines. Flow charts are provided for each microprogram routine. The remainder of the section provides a more detailed description of the functional circuits which implement the various operations required to interface with the other system components and to execute the steps in the microprogram routines.

#### 4.2 OVERALL FPP OPERATION AND SYSTEM INTERFACE

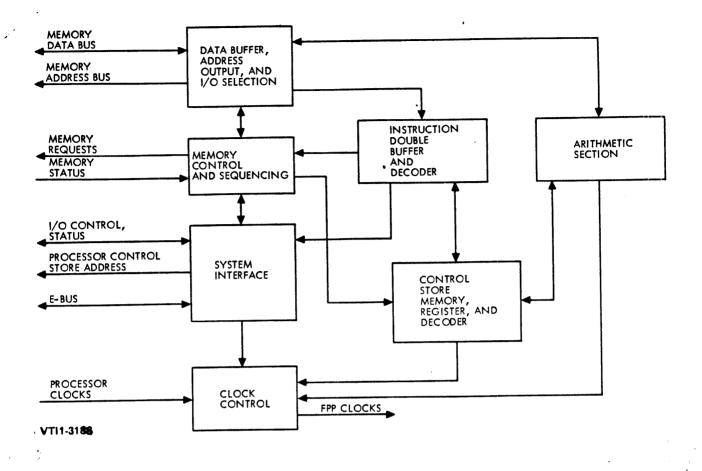

Figure 4-1 illustrates the FPP in terms of seven major functions.

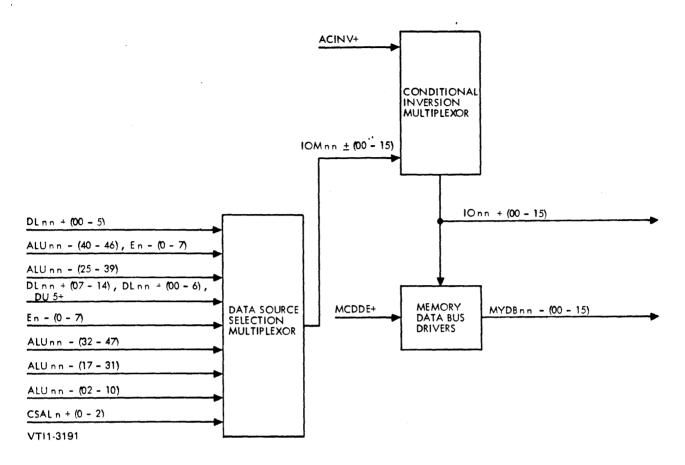

#### 4.2.1 Data Buffer, Address Output, and I/O Selection

This function provides a buffer register which can hold one instruction, address, or operand word received from memory. It provides an address counter. It provides multiplexing required to distribute operand words to the arithmetic section and to select result words from the arithmetic section for transfer to memory.

#### 4.2.2 Instruction Double Buffer and Decoder

This function provides storage for two FPP instruction OP codes. It also provides a decoder which recognizes the FPP code. Every instruction fetched by the central processor is loaded into the FPP data buffer at the same time that it is loaded into the central processor instruction buffer. When an FPP instruction is fetched, the next instruction fetch brings the starting operand address into the central processor instruction buffer. Just before this occurs, the decoder recognizes the FPP code of the instruction held in the FPP data buffer. This recognition causes the OP code of the instruction to be transferred to the instruction double buffer at the time that the starting operand address is loaded into the data buffer. A double buffer is provided so that a second OP code can be loaded while the previously received instruction is still being executed.

Figure 4-1. FPP Simplified Functional Block Diagram

#### 4.2.3 System Interface

· . .

This section provides the facilities for passing program control back and forth between the central processor and the FPP. It inhibits interrupts during the execution of an FPP instruction It transmits an interrupt after a fault condition has string. been recognized. It resolves contention for memory access. The system interface passes program control to the FPP by forcing the central processor microprogram to a control store address containing a no-operation (NOP) microinstruction. The central processor microprogram is held at this address until the portion of the FPP microprogram which requires memory access has been completed. The system interface then forces the central processor microprogram to a location containing a microinstruction which leads to another instruction fetch. This allows the central processor to fill its instruction pipeline while the FPP is completing the execution of an FPP instruction microprogram routine. If the next instruction is an FPP instruction, the central processor microprogram is again forced to the location containing a NOP at the time that it fetches the starting operand address. Thus,

during the execution of a string of FPP instructions, the central processor activity is limited to the fetching of instructions and associated operand starting addresses. From the time that the first instruction of the string is recognized by the FPP decoder until control is passed back to the central processor during the execution of the final instruction of the string, the system interface inhibits interrupts. An instruction string ends when an instruction which stores a result in memory is executed. During FPP memory accesses, the system interface controls various interface lines so as to prevent other system facilities from accessing memory. At the end of an FPP memory access cycle or if an FPP memory access is not currently in progress, the system interface yields memory access priority if a direct memory access (DMA) or priority memory access (PMA) request is pending. If the FPP requires memory access and does not have memory access priority, it suspends the activity that requires the memory access until memory access priority is again available.

ي بريدين بيو المراجد ال

#### 4.2.4 Memory Control and Sequencing

This section initiates memory requests, recognizes the completion of memory cycles, and provides the signal which loads the data from the memory data bus into the data buffer. During central processor instruction fetches, the memory control merely steers a central processor control signal to the data buffer as required to load it. In this way, first an FPP instruction and then the associated operand address are loaded into the data buffer. Ιf the operand address is an indirect address, the memory control is now responsible for initiating as many memory access requests as may be necessary to obtain a direct address. For an instruction during which an operand must be obtained from memory, the memory control is also responsible for initiating the memory access required to obtain the first operand word. These memory accesses can be accomplished without intervention of the FPP microprogram. Th s, they can occur while a previous instruction microprogram routine is still being executed.

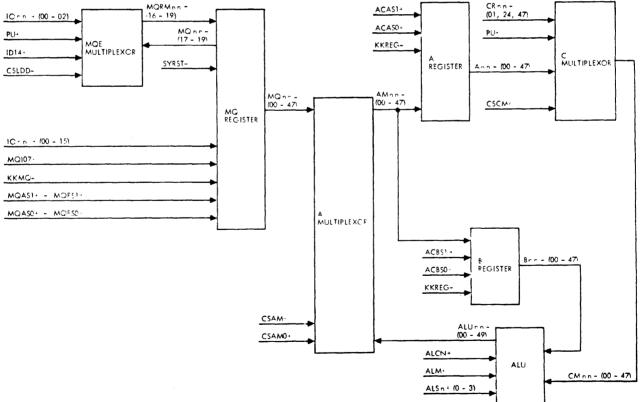

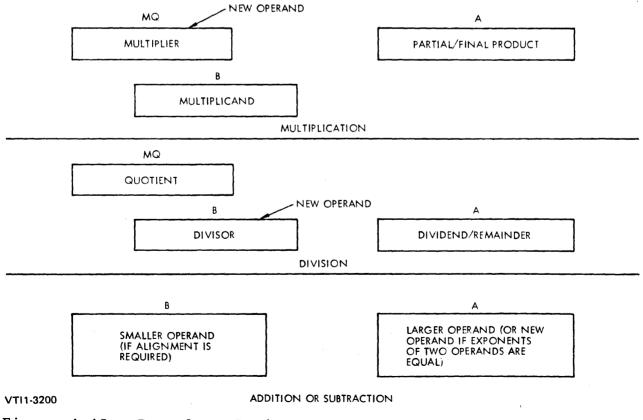

#### 4.2.5 Arithmetic Section

This section provides the registers and arithmetic/logic units (ALUs) required to perform floating point arithmetic as well as associated control circuits.

#### 4.2.6 Control Store Memory, Register, and Decoder

This function provides the control store read-only memory in which the FPP microprogram is stored. It provides an address counter which determines the order in which microinstructions are executed, a register which holds the instruction currently being executed, and circuits which decode certain microinstruction fields. The OP code of each FPP instruction points to the starting address of the associated microinstruction routine. Within the routine, microinstructions are executed in sequential order except when a jump alters the contents of the address counter. The microprogram initiates the memory accesses required to obtain operand words (with the exception of the first operand word), controls the transfer of operand words into the arithmetic section, and controls the sequence of operations within the arithmetic section. During the execution of an instruction which stores a result in memory, the microprogram initiates the memory accesses required to store each of the operand words.

#### 4.2.7 Clock Control

This function provides the clock signals which time parallel data transfers, serial shifts of data, transitions of control signals, and advancement of the microprogram. All of the FPP clock rates are derived from clock rates received from the central processor. The clock control section exercises control over the timing of microprogram execution by inhibiting the clock which times the microprogram advancement. When the microprogram initiates a memory access, the clock is inhibited until the required memory cycle has been completed. The clock is also inhibited during certain operations of the arithmetic section until the required number of iterations of the operation have been completed. When the final microinstruction of a routine reaches the control store register, the clock is inhibited until the next valid FPP instruction OP code is available in the instruction buffer. Another function of clock control is to select the fast shift clock rate. The fast shift clock period is 82.5 nanoseconds as compared to the basic clock rate of 165 nanoseconds.

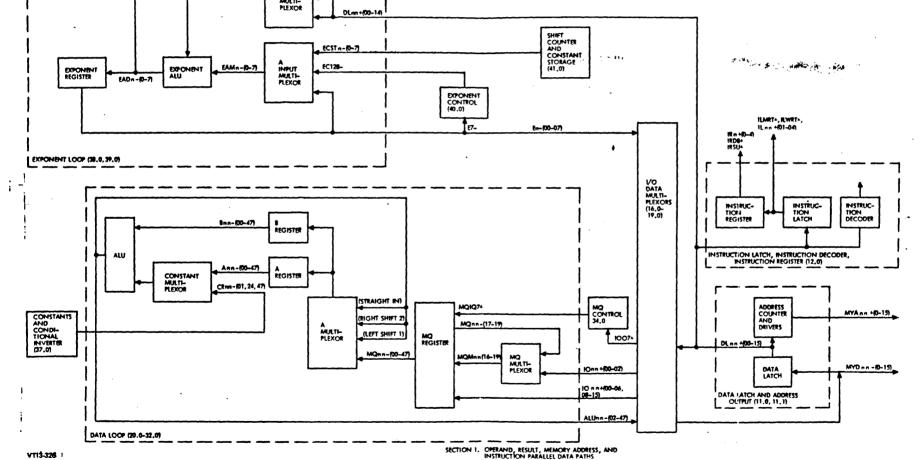

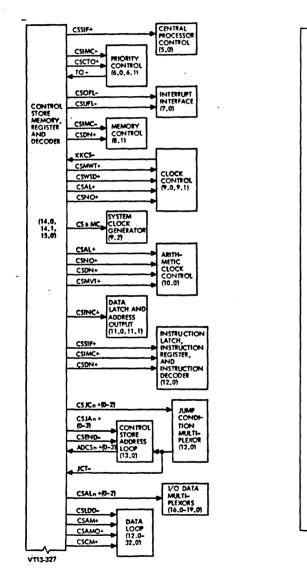

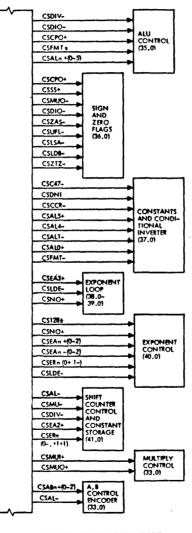

#### 4.3 FPP DETAILED BLOCK DIAGRAM

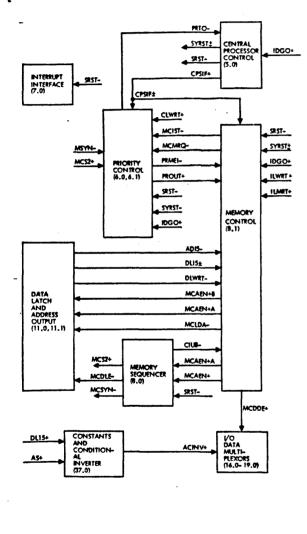

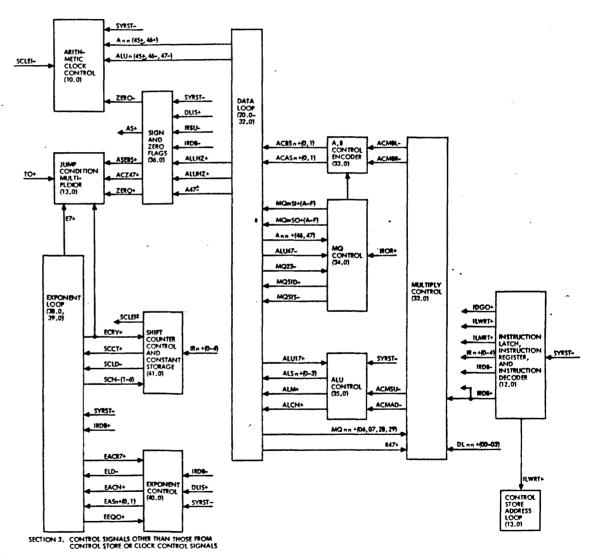

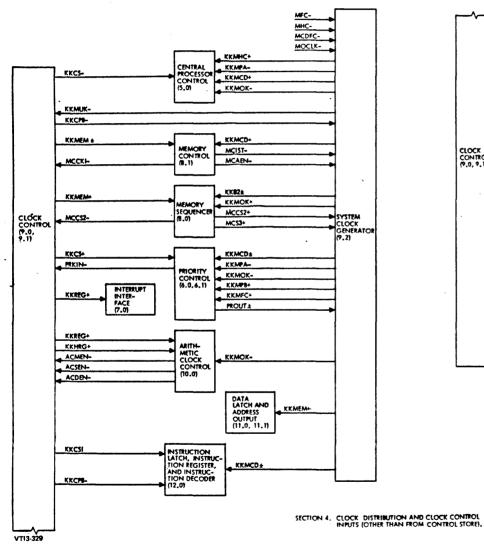

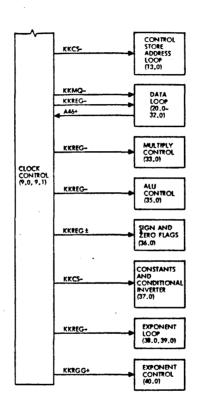

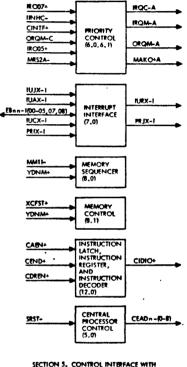

Figure 4-2 is a multi-sheet block diagram which illustrates the FPP in terms of 24 functional blocks. Section 1 illustrates the operand, result, memory address, and instruction data parallel paths. Section 2 illustrates the interface between the control store function and the other functional blocks. Section 3 illustrates the control signals, other than control store signals, which pass between the various functional blocks. Section 4 illustrates the distribution of clock signals and shows clock control inputs other than those from the control store function. Section 5 illustrates the control interface with the central processor and option board.

Figure 4-2. FPP Detailed Block Diagram (Sheet 1 of 4)

.

4 - 5

•

.

.

1

.

•

· ·

. .

SECTION 2. CONTROL STORE SIGNALS

Figure 4-2. FPP Detailed Block Diagram (Sheet 2 of 4)

٠.

1

.

VTI3-328

Figure 4-2. FPP Detailed Block Diagram (Sheet 3 of 4)

4 - 7

.

~

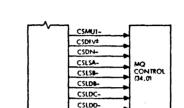

SECTION 5. CONTROL INTERFACE WITH CENTRAL PROCESSOR AND OPTION BOARD

Figure 4-2. FPP Detailed Block Diagram (Sheet 4 of 4)

.

Functions shown in figure 4-2 correspond in most cases with functions which are separately identified in FPP logic diagram 91C0499. The instruction latch, instruction register, and instruction decoder block shown on figure 4-2 corresponds to the instruction double buffer and decoder block shown in figure 4-1. Other blocks shown in figure 4-2 are subsidiary to blocks shown in figure 4-1. Table 4-1 summarizes the correlation between nomenclature used on figure 4-1 and 4-2 and nomenclature used on the FPP logic diagram.

Numbers within parenthesis in figure 4-2 refer to sheets of FPP logic diagram 91C0499.

#### 4.4 MICROINSTRUCTION FORMAT

· · · · ·

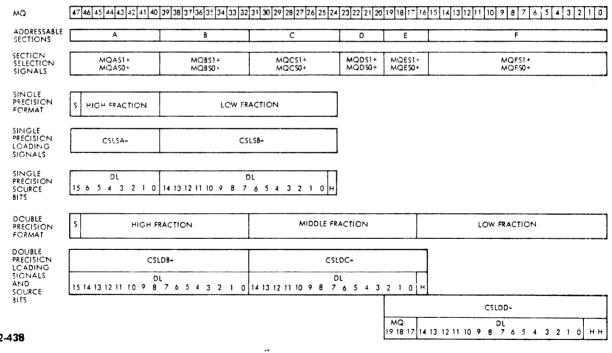

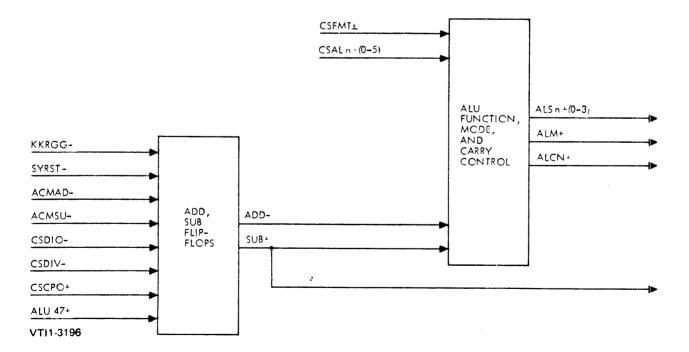

Figure 4-3 illustrates the two formats used in microinstruction words. The mnemonic assigned to each of the 32 bits of the microinstruction word are shown at the left of the figure. If CSFMT+ is low, then format 0 is designated. If CSFMT+ is high, then format 1 is designated. The only difference between the two formats is in the interpretation of the status of the CSALn+ (0-5) bits. In format 0, bits CSALn+ (3-5) constitute the IN field while bits CSALn+ (0-2) constitute the IO field. In format 1, the six CSALn+ (0-5) bits constitute the ALU field.

Table 4-2 lists the various active codes used in each microinstruction field. Each active code associated with a field is assigned a mnemonic which is listed in the FLOW CHART MNEMONIC column of the table. This mnemonic is either used directly on the microprogram flow charts or else is used on supporting documents to indicate the field codes associated with particular operations.

Where a field code is represented by an explicit decoding signal, the decoding signal mnemonic is listed. (In many cases, the field code bits are supplied to function selection inputs of ALUs or registers or to address inputs of multiplexors so that separate decoding is not required.)

#### 4.5 MICROPROGRAM ROUTINES

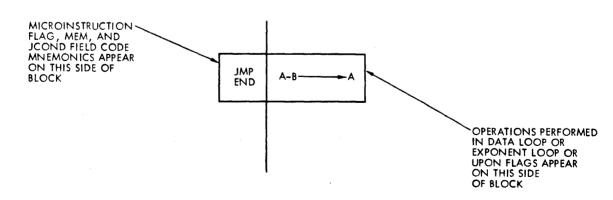

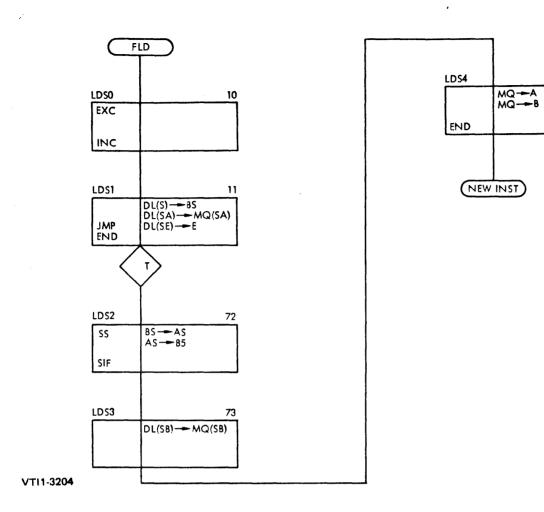

The paragraphs which follow provide descriptions of each of the routines contained in the FPP microprogram. Each description is supported by a flow chart. Figure 4-4 illustrates the micro-instruction block format that is used on the flow charts and table 4-3 lists special notations that are used on the flow charts.

Table 4-1. Nomenclature Correlation

.

| Figure 4-1                                           | Figure 4-2                                                                | FPP Logic Diagram                                                                  |

|------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Instruction double<br>buffer and decoder             | Instruction latch,<br>instruction<br>register, and<br>instruction decoder | Instruction register<br>(sheet 12.0)                                               |

| System interface                                     | Central processor<br>control                                              | Central processor<br>control (sheet 5.0)                                           |

|                                                      | Priority control                                                          | Priority control<br>(sheet 6.0, 6.1)                                               |

|                                                      | Interrupt interface                                                       | Interrupt interface (sheet 7.0)                                                    |

| Memory control<br>and sequencing                     | Memory sequencer                                                          | Memory sequencer<br>(sheet 8.0)                                                    |

|                                                      | Memory control                                                            | Memory control<br>(sheet 8.1)                                                      |

| Clock control                                        | Clock control                                                             | Clock control<br>(sheets 9.0, 9.1)                                                 |

|                                                      | System clock<br>generator                                                 | System clock genera-<br>tor (sheet 9.2)                                            |

| Data buffer,<br>address output,<br>and I/O selection | Data latch and<br>address output                                          | Data latch and<br>address output<br>(sheets 11.0, 11.1)                            |

|                                                      | I/O data multi-<br>plexors                                                | Input/output data<br>(sheets 16.0<br>through 19.0)                                 |

| Control store<br>memory, register,<br>and decoder    | Control store<br>memory, register,<br>and decoder                         | Control store<br>register, control<br>store decoder<br>(sheet 14.0, 14.1,<br>15.0) |

|                                                      | Control store<br>address loop                                             | Control store address<br>loop (sheet 13.0)                                         |

|                                                      | Jump condition<br>multiplexor                                             |                                                                                    |

| Figure 4-1         | Figure 4-2                                         | FPP Logic Diagram                                                             |

|--------------------|----------------------------------------------------|-------------------------------------------------------------------------------|

| Arithmetic section | Data loop                                          | Data loop<br>(sheets 20.0<br>through 32.0)                                    |

|                    | Arithmetic clock<br>control                        | Arithmetic control<br>clock logic<br>(sheet 10.0)                             |

|                    | Multiply control                                   | Arithmetic control<br>(A, B and multiply)<br>(sheet 33.0)                     |

|                    | A, B control<br>encoder                            |                                                                               |

|                    | MQ control                                         | Arithmetic control<br>(MQ) (sheet 34.0)                                       |

|                    | ALU control                                        | Arithmetic control<br>(ALU) (sheet 35.0)                                      |

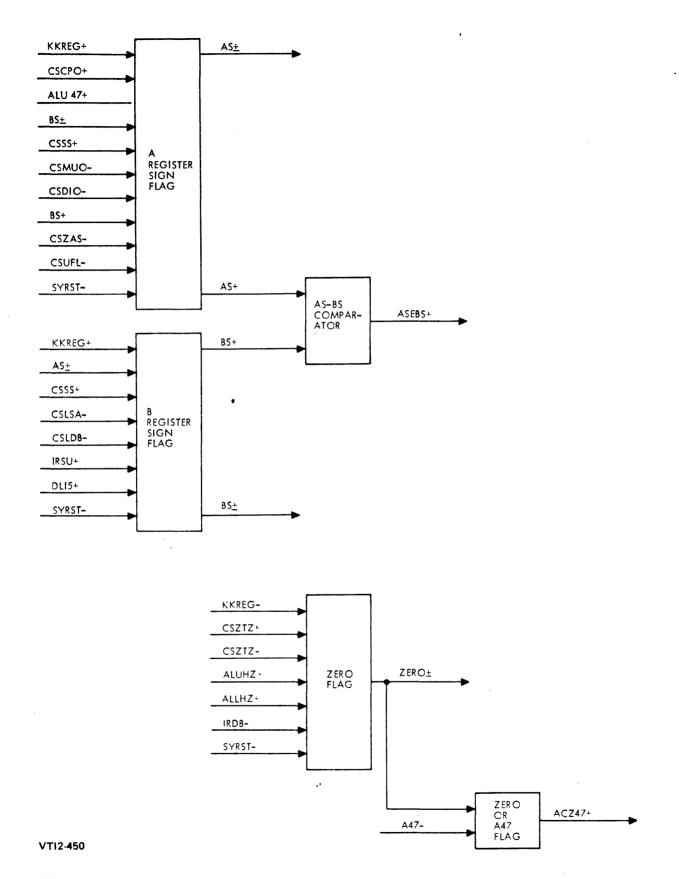

|                    | Sign and zero flags                                | Arithmetic control<br>(Sign and Zero Flags)<br>(sheet 36.0)                   |

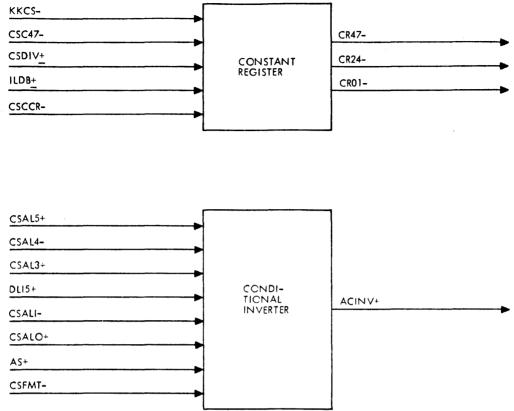

|                    | Constants and con-<br>ditional inverter            | Arithmetic control<br>(constants and con-<br>ditional invert)<br>(sheet 37.0) |

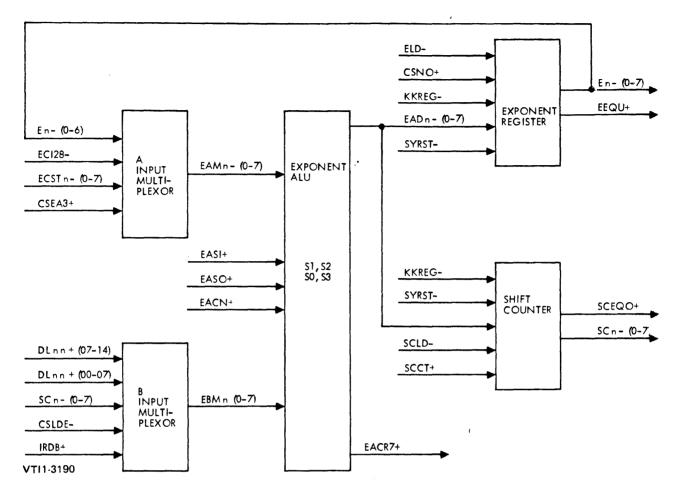

|                    | Exponent loop                                      | Exponent loop<br>(sheets 38.0, 39.0)                                          |

|                    | Exponent control                                   | Exponent control<br>(sheet 40.0)                                              |

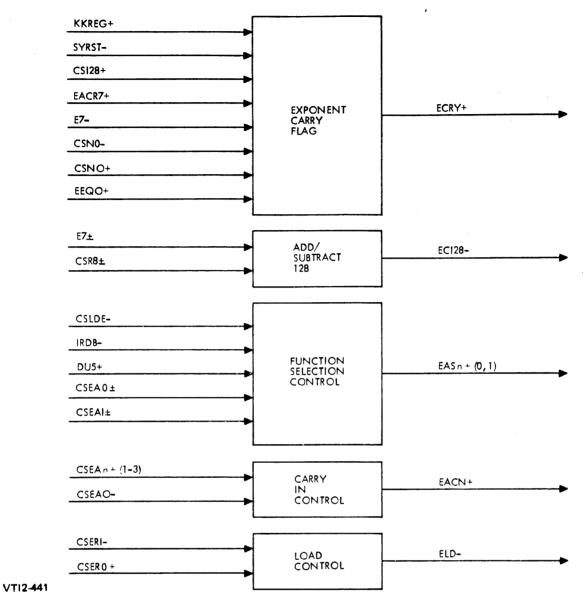

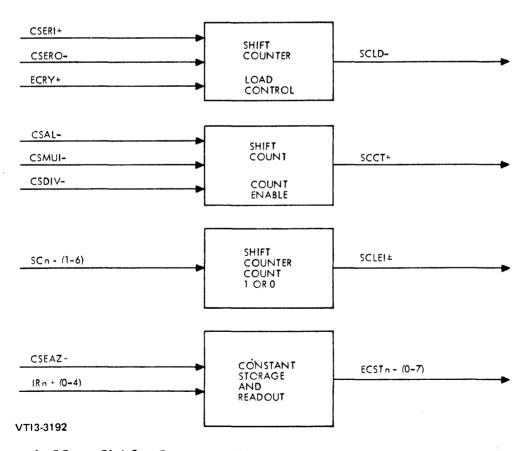

|                    | Shift counter con-<br>trol and constant<br>storage | Exponent control,<br>shift counter and<br>constant (sheet 41.0)               |

----

Table 4-1. Nomenclature Correlation (continued)

| BIT<br>MNEMONIC*                 | FIELD<br>MNEMONIC<br>FORMAT 0 | FIELD<br>MNEMONIC<br>FORMAT 1 |

|----------------------------------|-------------------------------|-------------------------------|

| CSAL5<br>CSAL4<br>CSAL3          | IN                            | ALU                           |

| CSAL2<br>CSAL1<br>CSAL0          | ю                             |                               |

| CSAB2<br>CSAB1<br>CSAB0          | Ав                            | AB                            |

| CSAM<br>CSCM                     | AC                            | AC                            |

| CSEA3<br>CSEA2<br>CSEA1<br>CSEA0 | EADD                          | EADD                          |

| CSER1<br>CSER0                   | EREG                          | EREG                          |

| CSMWT<br>CSME1<br>CSME0          | MEM                           | MEM                           |

| CSFL3<br>CSFL2<br>CSFL1<br>CSFL0 | FLAG                          | FLAG                          |

| CSJC2<br>CSJC1<br>CSJC0          | JCOND                         | JCOND                         |

| CSJA3<br>CSJA2<br>CSJA1<br>CSJA0 | DDAL                          | JADD                          |

| CSFMT                            | <br>FMTO                      | FMTI                          |

VT12-437

Figure 4-3. Microinstruction Word Formats

| 1                      |                                                                                                                   |                                               |                                                                                                                                                                                               |

|------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|