# Maintain III Test Programs User Manual

**Mini-Computer Operations**

2722 Michelson Drive P.O. Box C-19504 Irvine, California 92713

UP-8672 Rev. 1

# MAINTAIN III TEST PROGRAMS USER MANUAL

UP-8672 Rev. 1 98A 9952 075 Update A OCTOBER 1980

The statements in this publication are not intended to create any warranty, express or implied. Equipment specifications and performance characteristics stated herein may be changed at any time without notice. Address comments regarding this document to Sperry Univac, Mini-Computer Operations, Publications Department, 2722 Michelson Drive, P.O. Box C-19504, Irvine, California, 92713.

COPYRIGHT © 1978, 1979 by SPERRY CORPORATION ALL RIGHTS RESERVED Sperry Univac is a division of Sperry Corporation

Printed in U.S.A.

### PAGE STATUS SUMMARY

ISSUE: Update A - UP-8672 Rev. 1

| Part / Section | Page<br>Number | Update<br>Level | Part/Section | Page<br>Number | Update<br>Level | Part/Section | Page<br>Number | Update<br>Level |

|----------------|----------------|-----------------|--------------|----------------|-----------------|--------------|----------------|-----------------|

| Cover          |                |                 |              | 4 thru 7       | Orig.           |              |                |                 |

| Title Page     |                | А               |              | 8              | А               |              |                |                 |

| PSS            | 1              | А               |              | 9 thru 16      | Orig.           |              |                |                 |

| CR             | 1              | А               | 15           | l thru 6       | Orig.           |              |                |                 |

| Preface        | 1              | Orig.           | 16           | l thru 5       | Orig.           |              |                |                 |

| Contents       | 1 thru 10      | Orig.           | 17           | 1, 2           | Orig.           |              |                |                 |

| 1              | 1, 2           | Orig.           |              | 3              | А               |              |                |                 |

| 2              | 1 thru 17      | Orig.           |              | 4 thru 9       | Orig.           |              |                |                 |

| 3              | 1 thru 12      | Orig.           |              | 10, 11         | А               |              |                |                 |

| 4              | l thru 6       | Orig.           |              | 12             | Orig.           |              |                |                 |

| 5              | l thru 6       | Orig.           | 18           | l thru 6       | Orig.           |              |                |                 |

| 6              | l thru 4       | Orig.           | 19           | l thru 4       | Orig.           |              |                |                 |

| 7              | l thru 4       | Orig.           | Appendix     | l thru 7       | Orig.           |              |                |                 |

| 8              | l thru 7       | Orig.           | A            |                |                 |              |                |                 |

| 9              | l thru 8       | Orig.           |              |                |                 |              |                |                 |

| 10             | l thru 5       | Orig.           |              |                |                 |              |                |                 |

| 11             | 1 thru 13      | Orig.           |              |                |                 |              |                |                 |

| 12             | l thru 6       | Orig.           |              |                |                 |              |                |                 |

| 13             | 1 thru 15      | Orig.           |              |                |                 |              |                |                 |

| 14             | 1, 2           | Orig.           |              |                |                 |              |                |                 |

|                | 3              | А               |              |                |                 |              |                |                 |

\*New pages

All the technical changes are denoted by an arrow ( $\rightarrow$ ) in the margin. A downward pointing arrow ( $\oint$ ) next to a line indicates that technical changes begin at this line and continue until an upward pointing arrow ( $\clubsuit$ ) is found. A horizontal arrow ( $\rightarrow$ ) pointing to a line indicates a technical change in only that line. A horizontal arrow located between two consecutive lines indicates technical changes in both lines or deletions.

# CHANGE RECORD

| Change<br>Designation | lssue<br>Date         | Change Description                                                       |

|-----------------------|-----------------------|--------------------------------------------------------------------------|

|                       | June 1977             | Inserted new sections. Renumbered sections. Deleted reference to Varian. |

|                       | Jan 1978              | Deleted, corrected, and added information to Sections 2, 7, 12, and 14.  |

| Update A              | June 1979             | Adds magnetic tape, disk, and V77–800 test information.                  |

| Rev. l                | Sept 1979             | Typeset Sections 15 thru 18 and added Section 19.                        |

| Update A              | Oct 1980 <sup>.</sup> | Added subtests to Section 17.                                            |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

|                       |                       |                                                                          |

| Change Proc           | edure:                |                                                                          |

When changes are made to this manual, updated pages are issued. These updated pages are either added to this manual or used to replace obsolete pages. The specific pages affected by each change are identified on the PAGE STATUS SUMMARY page.

# PREFACE

OVETER

This manual describes the MAINTAIN III test-program system for verifying the correct operation and detecting and isolating malfunctions in Sperry Univac computer systems.

The reader should be familar with the instruction set of the system for which he uses these programs and some assembly-language programming. The person who runs these tests should also know the operating procedures for the control panel and peripheral devices on his system.

The organization of this manual is based on the organization of the test system. The first chapter presents an overview of the entire system. The following chapters present the components of the system. In a chapter for a specific component the reader finds an overview in more detail and a definition of the minimal hardware necessary for using the component, a description of its design and structure, followed by the information needed to use the test in the order needed: first the preliminary procedures such as loading and setting sense switches, then the execution procedures, followed by an explanation of any error indication that may occur during execution or cause termination, and finally examples of the program input and output.

As new systems are developed, the existing test system is expanded to include the new systems. In those cases where tests are applicable to more than one system, reference is made to those systems. Unless specifically called out, the terms 620, V70, and V77 should be applied as indicated in the following listing.

| NUMBER | MODEL NUMBERS                         |

|--------|---------------------------------------|

| 620    | 620/f, 620/i, 620/l                   |

| V70    | V72, V73, V75 and V76 plus V77 series |

| V77    | V77-200, V77-400, V77-600, V77-800    |

### **RELATED DOCUMENTATION**

The V70 Series Architecture Manual provides a complete description of the instruction set, word formats, and addresing modes. Each computer is documented by a system reference manual and manuals for each of the major components: processor, memory, memory map (or megamap), writable control store, and cache. Peripheral controllers are also documented separately. These manuals include information concerning installation, operation, theory of operation, and maintenance.

### **GENERAL OPERATING DESCRIPTIONS**

In this manual references to the instruction register designate the I register of the 620/f and the U register on other 620-series computers. Similarly, references to START on the 620/f are the same as RUN on other systems. RESET is SYSTEM RESET on 620 computers except the 620/f which is RESET. The applicable system handbook gives detailed descriptions of control-panel switches and indicators and general operating procedures.

### CONTENTS

### PREFACE

### RELATED DOCUMENTATION GENERAL OPERATING DESCRIPTIONS

### SECTION 1 SYSTEM OVERVIEW

| 1.1 | STRUCTURE            | 1. | 1 |

|-----|----------------------|----|---|

| 1.2 | MAINTENANCE CONCEPTS | 1. | 1 |

# SECTION 2 TEST EXECUTIVE PROGRAM

| 2.1 COMPONENTS OF THE SYSTEM       | ~ •    |

|------------------------------------|--------|

|                                    |        |

| 2.2 OPERATING PROCEDURES           | . 2.2  |

| 2.2.1 Preliminary Procedures       | . 2-2  |

| 2.2.2 Operating the Test Executive |        |

| 2.2.2.1 Magnetic Tape Commands     | . 2-9  |

| 2.2.2.2 Disk Commands              | 2-10   |

| 2.2.2.3 Writing Disk Files         | 2-10   |

| 2.2.2.4 Examples                   | 2-10   |

| 2.2.3 Error Indications            | . 2-11 |

| 2.2.4 Test Examples                | 2.13   |

### SECTION 3 INSTRUCTION TESTS

| 3.1 | PRELIMINARY PROCEDURES      | 3-5 |

|-----|-----------------------------|-----|

| 3.2 | EXECUTING INSTRUCTION TESTS | 3.6 |

| 3.3 | ERROR INDICATIONS           | 3.7 |

| 3.4 | TEST VALIDATION EXAMPLES    | 3.9 |

### SECTION 4 MEMORY TEST PROGRAM

| 4.1   | INITIAL CONDITION SELECTION        | 4-1 |

|-------|------------------------------------|-----|

| 4.2   | EXECUTING THE MEMORY TEST PROGRAMS | 4-2 |

| 4.2.1 | Part 1                             | 4·2 |

| 4.2.2 | Part 2                             | 4.2 |

| 4.3   | ERROR INDICATIONS                  | 4.3 |

| 4.4   | TEST VALIDATION EXAMPLES           | 4.5 |

### SECTION 5 TELETYPE TEST PROGRAM

| 5.1 | INITIAL CONDITION SELECTION | 5-2 |

|-----|-----------------------------|-----|

| 5.2 | EXECUTING THE TESTS         | 5.2 |

| 5.3 | ERROR INDICATIONS           | 5-4 |

| 5.4 | TEST VALIDATION EXAMPLES    | 5.5 |

# SECTION 6 POWER-FAILURE/RESTART TEST

| 6.1 | INITIAL CONDITION SELECTION     | 6.2 |

|-----|---------------------------------|-----|

| 6.2 | EXECUTING THE PF/R TEST PROGRAM | 6.2 |

| 6.3 | ERROR INDICATIONS               | 6.3 |

| 6.4 | TEST VALIDATION EXAMPLES        | 6-4 |

# SECTION 7 PRIORITY-INTERRUPT-MODULE TEST

| 7.1 | INITIAL CONDITION SELECTION    | . 7.2 |

|-----|--------------------------------|-------|

| 7.2 | EXECUTING THE PIM TEST PROGRAM | 7.2   |

| 7.3 | ERROR INDICATIONS              | 7.4   |

| 7.4 | TEST VALIDATION EXAMPLES       | 7.4   |

.

# SECTION 8 REAL-TIME CLOCK TEST PROGRAM

| 8.1 FUNCTIONAL CAPABILITIES                   | 8-1 |

|-----------------------------------------------|-----|

| 8.2 HARDWARE SUMMARY                          | 8∙2 |

| 8.2.1 Major Modules and Performance           | 8.2 |

| 8.2.1.1 Free-Running Counter (V70, 620/f)     | 8-2 |

| 8.2.1.2 Variable Interval Interrupt           | 8.2 |

| (V70, 620/f)                                  |     |

| . 8.2.1.3 Interval Interrupt (620/i, 620/L)   |     |

| 8.2.1.4 Memory-Overflow Interrupt (All CPU's) | 8∙3 |

| 8.2.2 Configurations                          | 8-3 |

| 8.3 SOFTWARE DESIGN SUMMARY                   | 8.3 |

| 8.3.1 I/O Instruction and                     | 8-3 |

| Interrupt Test                                |     |

| 8.3.2 Interrupt Timing Test                   | 8.3 |

| 8.4 USER FACILITIES                           |     |

| 8.4.1 Interval Timer                          | 8.3 |

| 8.4.1.1 Interval Timer Accuracy               | 8-3 |

| 8.4.2 Elapsed Time Counters                   | 8-3 |

| 8.5 LOADING PROCEDURE                         | -   |

| 8.6 OPERATING INSTRUCTIONS                    |     |

| 8.6.1 Initial Condition Selection             | 8-4 |

| 8.6.2 Mode of Operation                       | 8-4 |

| 8.6.2.1 I/O Instruction and Interrupt Test    | 8.4 |

| 8.6.2.2 Input of Hardware Parameters          | 8-4 |

| 8.6.2.3 Interrupt Timing Test Inputs          | 8-5 |

| 8.6.2.4 Interrupt Timing Test Execution       | 8.5 |

| 8.7 SUMARY OF TELETYPE/PRINTER                | 8.6 |

| OUTPUT STATEMENTS                             |     |

| 8.8 SUMMARY OF TELETYPE                       | 8.6 |

| INPUT STATEMENTS                              |     |

| 8.9 ERROR INDICATIONS                         | 8.6 |

| 8.10 ERROR HALT DESCRIPTIONS                  | 8.7 |

# SECTION 9

# 620/f AND V70 MEMORY-PROTECTION TEST PROGRAM

| 9.1 PROGRAM DESIGN SUMMARY               | . 9.1 |

|------------------------------------------|-------|

| 9.1.1 Mask-Register Test                 | 9-1   |

| 9.1.2 Instruction Interrupt Address Test | .9-1  |

| 9.2 620/f-V70 MEMORY-PROTECTION          | . 9.2 |

| DIFFERENCES                              |       |

| 9.3 SYSTEM CONFIGURATION                 | .9-2  |

| 9.4 PRELIMINARY PROCEDURES               |       |

| 9.5 OPERATING THE MEMORY-PROTECTION      | 9.2   |

| TEST PROGRAM                             |       |

| 9.5.1 Mode of Operation                  | 9.2   |

| 9.6 ERROR INDICATIONS                    | 9.3   |

| 9.6.1 Mask-Register Test                 | 9.3   |

| 9.6.2 Instruction Interrupt Address Test | 9.3   |

| 9.7 TEST VALIDATION EXAMPLES             | 9.7   |

### SECTION 10 BUFFERED-1/O-CONTROLLER TEST PROGRAM

| 10.1 | PRELIMINARY PROCEDURES          | 10-2   |

|------|---------------------------------|--------|

|      | EXECUTING THE BIOC TEST PROGRAM |        |

| 10.3 | ERROR INDICATIONS               | . 10-3 |

| 10.4 | TEST VALIDATION EXAMPLES        | 10.4   |

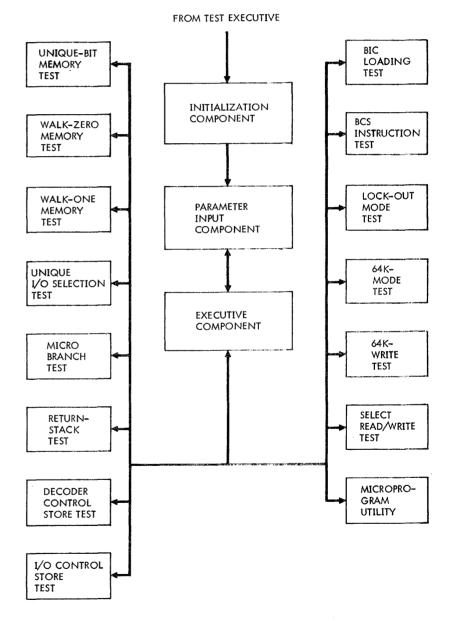

### SECTION 11 WRITABLE CONTROL STORE TEST PROGRAM

| 11.1 TEST PROGRAM ORGANIZATION       |      |

|--------------------------------------|------|

| 11.1.1 Unique-Bit Memory Test        |      |

| 11.1.2 Walk-Zero Memory Test         | 11.2 |

| 11.1.3 Walk-One Memory Test          | 11.2 |

| 11.1.4 Unique I/O Selection Test     |      |

| 11.1.5 Micro-Branch Test             |      |

| 11.1.6 Return-Stack Test             |      |

| 11.1.7 Decoder Control Store Test    |      |

| 11.1.8 I/O Control Store Test        | 11.2 |

| 11.1.9 BIC Loading Test              | 11-2 |

| 11.1.10 BCS Instruction Test         | 11-3 |

| 11.1.11 Lockout-Mode Test            |      |

| 11.1.12 64K-Mode Test                |      |

| 11.1.13 64K-Write Test               | 11-3 |

| 11.1.14 Read/Write Selection Test    | 11.3 |

| 11.1.15 Microprogram Utility         | 11-3 |

| 11.2 TEST IDENTIFICATION             | 11.3 |

| 11.3 PROGRAM LOADING                 |      |

| 11.4 SENSE SWITCHES                  | 11-4 |

| 11.5 TELETYPE MODE                   | 11-4 |

| 11.5.1 TTY Input Editing             |      |

| 11.5.2 Determining the Configuration |      |

| 11.5.3 Control Stores to be Tested   |      |

| 11.5.4 Tests to be Performed         | 11.5 |

| 11.5.5 Test-Sequence Execution       |      |

| 11.5.6 Error Message Formats         |      |

| 11.5.7 Summary of TTY Requests       |      |

| 11.5.8 Microprogram Utility          |      |

| 11.6 CONTROL-PANEL INDICATORS        |      |

| 11.7 DESCRIPTION OF ERROR CODES      |      |

| 11.8 TTY MESSAGE EXAMPLES            |      |

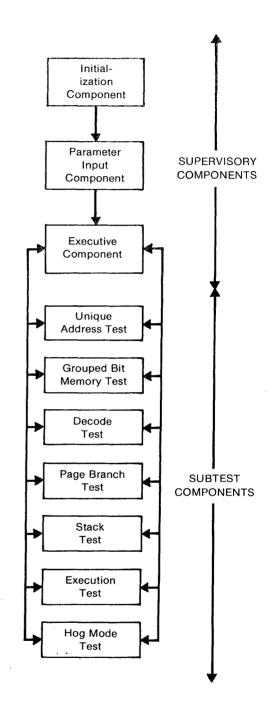

# SECTION 12 V77-400 WRITABLE CONTROL STORE TEST PROGRAM

| 12.1 TEST PROGRAM ORGANIZATION 12-1        |

|--------------------------------------------|

| 12.1.1 Supervising Components 12-1         |

| 12.1.2 Subtest Components 12-1             |

| 12.2 PROGRAM LOADING 12-2                  |

| 12.3 SENSE SWITCHES 12-2                   |

| 12.4 OPERATING PROCEDURES 12-3             |

| 12.4.1 Configuration Determination 12-3    |

| 12.4.2 Tests to be Performed 12-4          |

| 12.4.3 Execution of the Test Sequence 12-4 |

| 12.5 ERROR MESSAGE FORMATS 12-4            |

| 12.5.1 Unique Address Test 12-4            |

| 12.5.2 Grouped Bit Memory Test 12-5        |

| 12.5.3 Decode Test 12-5                    |

| 12.5.4 Page Branch Test                    |

| 12.5.5 Stack Test                          |

| 12.5.6 Execution Test                      |

| 12.5.7 Hog Mode Test 12-5                  |

| 12.6 UTILITY FUNCTIONS                     |

| 12.6.1 Changing Memory Pattern 6 12-6      |

| 12.6.2 Returning to MAINTAIN III Executive |

| 12.6.3 Examining/Changing WCS Contents     |

|                                            |

# SECTION 13 CACHE MEMORY TEST PROGRAM

| 13.1 HARDWARE SUMMARY                              |

|----------------------------------------------------|

| 13.2 TEST PROGRAM ORGANIZATION                     |

| 13.3 DESCRIPTIONS OF CACHE DISABLED SUBTESTS       |

| 13.3.1 Go-No-Go Test                               |

| 13.3.2 Write/Read Word Tests (with Cache Disabled) |

| 13.3.3 Write/Read Byte Test (with Cache Disabled)  |

| 13.3.4 Unique Address Test 1 (with Cache Disabled) |

| 13.3.5 Unique Address Test 2 (with Cache Disabled) |

| 13.4 DESCRIPTIONS OF CACHE ENABLED SUBTESTS        |

| 13.4.1 Read Word Hit                               |

| 13.4.2 Read Word Miss                              |

| 13.4.3 Write Word Hit                              |

| 13.4.4 Write Word Miss                             |

| 13.4.5 Write Bytes                                 |

| 13.4.6 Tag Comparison Test                         |

| 13.4.7 Least-Recently-Used Logic Test              |

| 13.4.8 Data RAM Test                               |

| 13.4.9 LRU RAM Test                                |

| 13.4.10 Tag RAM Test                               |

| 13.4.11 Valid RAM Test                             |

| 13.4.12 Data Loop Test                             |

| 13.4.13 Go-No-Go Test                              |

| 13.4.14 Control Logic Test                         |

| 13.5 OPERATING PROCEDURES                          |

| 13.6 SUMMARY OF TEST PARAMETER REQUESTS            |

| 13.7 ERROR MESSAGE FORMATS                         |

| 13.8 ERROR CODES                                   |

Contents 4

# SECTION 14 MEGAMAP PROGRAM

| 14.1 DESCRIPTIONS OF MEGAMAP COMPONENTS                      | 14-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14.1.1 Miscellaneous Register Test                           | 14-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.1.2 Map Register Test                                     | 14-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.1.3 Executive States Access and Map Select Test           | 14-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.1.4 Memory Test                                           | 14-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.1.5 Memory Protect Test                                   | 14-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.1.6 Map Utility Routines                                  | 14-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.2 HARDWARE SUMMARY                                        | 14-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.3 OPERATING PROCEDURES                                    | 14-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.3.1 Map Type Selection                                    | 14-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.3.2 Memory Configuration Selection                        | 14-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.3.3 Map Test Sequence Selection                           | 14-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.3.4 Memory Test Component Selection                       | 14-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.3.5 Cycle Count Selection and Program Termination         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14.4 MAP UTILITY ROUTINES OPERATION                          | 14-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5 ERROR INDICATIONS                                       | 14-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.1 Input Directive Errors                                | 14-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.2 Miscellaneous Register Test Errors                    | 14-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.3 Map Register Test Errors                              | 14-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.4 Executive States Access and Map Selection Test Errors | 14-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.5 Memory Test Errors                                    | 14-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.6 Memory Protect Test Errors                            | 14-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.7 General Considerations                                | 14-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.8 MEMORY PARITY ERRORS                                  | 14-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.5.8.1 Memory Parity Interrupts                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14.5.8.2 V77-600 ERRCC Error.                                | 14-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14.6 LOADING AND EXECUTION OF MAINTAIN III                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PROGRAMS IN A MEGAMAP SYSTEM                                 | 14-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14.7 MEMORY PROTECTION ERROR DESCRIPTIONS                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14.8 4K MEMORY MODULES IN TERMS OF OCTAL ADDRESSES           | 14-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -                                                            | 14.1.1       Miscellaneous Register Test.         14.1.2       Map Register Test.         14.1.3       Executive States Access and Map Select Test.         14.1.4       Memory Test.         14.1.5       Memory Protect Test.         14.1.6       Map Utility Routines.         14.1.6       Map Utility Routines.         14.2       HARDWARE SUMMARY         14.3       OPERATING PROCEDURES         14.3.1       Map Type Selection         14.3.2       Memory Configuration Selection.         14.3.3       Map Test Sequence Selection.         14.3.4       Memory Test Component Selection.         14.3.5       Cycle Count Selection and Program Termination.         14.4       MAP UTILITY ROUTINES OPERATION.         14.5       ERROR INDICATIONS         14.5.1       Input Directive Errors.         14.5.2       Miscellaneous Register Test Errors.         14.5.4       Executive States Access and Map Selection Test Errors.         14.5.5       Memory Protect Test Errors.         14.5.6       Memory Protect Test Errors.         14.5.7       General Considerations.         14.5.8       MEMORY PARITY ERRORS.         14.5.8.1       Memory Parity Interrupts         14.5.8.2 |

# SECTION 15 V77-800 MICRODIAGNOSTIC TEST PROGRAM

| 15.1 HARDWARE REQUIREMENTS               |

|------------------------------------------|

|                                          |

| 15.2 DESCRIPTION OF TEST COMPONENTS 15-1 |

| 15.2.1 Supervisor                        |

| 15.2.1.1 Program Entry                   |

| 15.2.1.2 Initialization                  |

| 15.2.1.3 Test Load and Execution         |

| 15.2.1.4 Test Restart                    |

| 15.2.1.5 Error Data Display 15-2         |

| 15.2.1.6 WCS Dump 15-2                   |

| 15.2.1.7 Microinstruction Alteration     |

| 15.2.2 Test                              |

| 15.3 OPERATING PROCEDURES 15-3           |

| 15.3.1 Program Start 15-4                |

| 15.3.2 Program Execution                 |

| 15.3.3 Program Continuation              |

| 15.3.4 Utility Routines 15-5             |

| 15.3.4.1 WCS Dump 15-5                   |

| 15.3.4.2 Input To WCS 15-5               |

| 15.4 ERROR MESSAGES 15-5                 |

| 15.4.1 Input Errors 15-5                 |

| 15.4.2 Invalid Test Data 15-6            |

| 15.4.3 Unexpected Interrupts 15-6        |

| 15.4.4 Unexplained Interrupts 15-6       |

| 15.4.5 Test Recovery 15-6                |

|                                          |

# SECTION 16 V77-800 CACHE MEMORY TEST PROGRAM

### SECTION 17 V77-800 MAP/MEMORY TEST PROGRAM

| 17.1 HARDWARE REQUIREMENTS                                   |

|--------------------------------------------------------------|

| 17.2 DESCRIPTION OF TEST COMPONENTS 17-1                     |

| 17.2.1 Test Monitor                                          |

| 17.2.2 Utility Routines 17-1                                 |

| 17.2.3 Map Test                                              |

| 17.2.3.1 Static Register Subtest                             |

| 17.2.3.2 Map RAM Subtest 17-2                                |

| 17.2.3.3 Executive Mode State and User Key Selection Subtest |

| 17.2.3.4 Executive Key Subtest                               |

| 17.2.3.5 Extended Indexing Subtest                           |

| 17.2.3.6 64K Mode Subtest 17-3                               |

| 17.2.3.7 Memory Protection Subtest                           |

| 17.2.4 Memory Test                                           |

| 17.3 OPERATING PROCEDURES 17-5                               |

| 17.3.1 Test Monitor Selection 17-6                           |

| 17.3.2 Map Test Selection                                    |

| 17.3.3 Memory Test Selection 17-8                            |

| 17.3.4 Cycle Count Selection                                 |

| 17.4 ERROR MESSAGES 17-9                                     |

| 17.4.1 Global                                                |

| 17.4.2 Static Register                                       |

| 17.4.3 Map RAM                                               |

| 17.4.4 Executive Mode State and User Key Selection           |

| 17.4.5 Executive Key                                         |

| 17.4.6 Extended Indexing 17-10                               |

| 17.4.7 64K Mode                                              |

| 17.4.8 Memory Protection                                     |

| 17.4.9 Memory                                                |

|                                                              |

### SECTION 18 V77-800 WRITABLE CONTROL STORE TEST PROGRAM

| 18.1 HARDWARE REQUIREMENTS                |      |

|-------------------------------------------|------|

| 18.2 DESCRIPTION OF TEST COMPONENTS       |      |

| 18.2.1 Unique Address Test                |      |

| 18.2.2 Grouped Bit Memory Test            |      |

| 18.2.3 Execution Test                     |      |

| 18.2.4 Burn-in Test                       |      |

| 18.2.5 Utility Routines                   |      |

| 18.3 OPERATING PROCEDURES                 |      |

| 18.3.1 Test Initialization                |      |

| 18.3.2 Test Selection                     | 18-3 |

| 18.3.3 Address Parameter                  |      |

| 18.3.4 Cycle Parameter                    |      |

| 18.3.5 Utility Routines                   | 18-4 |

| 18.3.5.1 Examining/Changing WCS Contents  |      |

| 18.3.5.2 Dump WCS Memory                  |      |

| 18.3.5.3 Initialize WCS Memory            |      |

| 18.3.5.4 Change User-Defined Pattern      |      |

| 18.3.5.5 Run Microprogram in WCS          |      |

| 18.3.5.6 Save WCS Memory                  |      |

| 18.3.5.7 Write Saved WCS Data             |      |

| 18.3.5.8 Return to MAINTAIN III Executive |      |

| 18.4 ERROR MESSAGES                       |      |

| 18.4.1 Unique Address Test                |      |

| 18.4.2 Grouped Bit Memory Test            |      |

| 18.4.3 Execution Test                     |      |

### SECTION 19 V77-800 FLOATING-POINT PROCESSOR TEST PROGRAM

| 19.1 HARDWARE REQUIREMENTS          | . 19-1 |

|-------------------------------------|--------|

| 19.2 DESCRIPTION OF TEST COMPONENTS | . 19-1 |

| 19.3 OPERATING PROCEDURE            | . 19-2 |

| 19.3.1 Program Start                | . 19-2 |

| 19.3.2 WCS Loading                  | . 19-2 |

| 19.3.3 Cycle Selection              | . 19-3 |

| 19.3.4 Test Termination             |        |

| 19.4 ERROR MESSAGES                 | . 19-3 |

# APPENDIX A CONTROL PANEL OPERATION

# LIST OF ILLUSTRATIONS

| Figure 1-1.  | MAINTAIN III System Block Diagram                       | 1.1     |

|--------------|---------------------------------------------------------|---------|

| Figure 11-1. | Test Program Flow Diagram                               | 11-1    |

| Figure 11-2. | Printout for a Successfully Run Test Program            | 11-11   |

| Figure 11-3. | An Error Message for I/O Control Store Test             | 11-12   |

| Figure 11-4. | Error Messages for a Non-Existing WCS Page              | 11.12   |

| Figure 11-5. | Error Messages for Test F                               | . 11-13 |

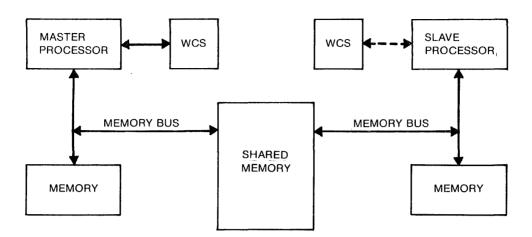

| Figure 12-1. | V77-400 Writable Control Store Test Program System Flow | 12-3    |

| Figure 12-2. | Bit Patterns for Grouped Bit Memory Test                | 12-2    |

| Figure 12-3. | Configuration for the Hog Mode Test                     | 12-4    |

| Figure 13-1  | Cache System Flow of Control                            | . 13-2  |

# LIST OF TABLES

| Table 2-1. Preliminary Instructions Test Summary         2-2        | 1 |

|---------------------------------------------------------------------|---|

| Table 2-2. Test Executive Utility Routines                          | 2 |

| Table 2-3. Standard Test Data Items                                 | 2 |

| Table 2-4. Test Executive Standard Data Routines 2-2                | 2 |

| Table 2-5 Magnetic-Tape Bootstrap Routine                           |   |

| (F3093-0x, F3062-00, 0870-99, and 0870-35 Tape Units)               | 1 |

| Table 2-6. Magnetic Tape Bootstrap Routine                          | 4 |

| Table 2-7.         Teletype Paper-Tape Bootstrap Routine            | 5 |

| Table 2-8. High-Speed Paper-Tape Bootstrap Routine                  | 5 |

| Table 2-9. Disk Bootstrap Routine                                   |   |

| (F3094-0x and F3096-0x RMD)2.6                                      | 6 |

| Table 2-10. Disk Bootstrap Routine (70-7606, F3094-0x, F3310-xx and |   |

| F3096-0x RMD's)                                                     | 7 |

| Table 2-11. Card Bootstrap Routine                                  |   |

| Table 2-12. Test Executive Utility Routine Commands                 | 9 |

| Table 2-13. Preliminary Instructions Test Error Codes 2-12          | 2 |

| Table 5.1 (ACOII) Chandand Chanadara                                | , |

| Table 5-1. (ASCII) Standard Characters       5-1                    |   |

| Table 6-1. Typical PF/R Service Routine         6-1                 | 1 |

| Table 7-1. PIM Input/Output Instructions                            | L |

| Table 7-2. Typical PIM Service Routine                              | 1 |

| Table 10-1. BIOC Input/Output Instructions                          | 1 |

| Table 10-2. Typical BIOC Service Routine                            | 2 |

| Table 11-1. Test Identifications                                    | 4 |

| Table 11-2. SENSE Switch Settings                                   | 4 |

| Table 11-3. Decoder Control Store Test Cases                        |   |

| Table 12-1. V77-400 Writable Control Store Decode Test Functions    |   |

# **LIST OF TABLES** (continued)

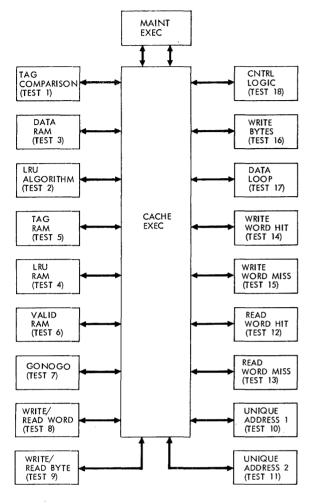

| Table 13-1.  | Subtests of the Cache Test Program         | 1 <b>3-2</b> |

|--------------|--------------------------------------------|--------------|

| Table 13-2a. | Cache Preliminary Test                     | 13-4         |

| Table 13-2b. | Cache Byte Test                            | 13-4         |

| Table 13-3.  | Tag Compare Tests                          | 13-5         |

| Table 13-4.  | LRU Algorithm Test Procedures              | 13-6         |

| Table 13-5.  | Data RAM Write Complement-After-Read Test  | 13-7         |

| Table 13-6.  | LRU RAM Write-Complement-After-Read Test   | 13-9         |

| Table 13-7.  | Tag RAM Write-Complement-After-Read Test   | 13-10        |

| Table 13-7c. | Physical Addresses for Tag RAM Test        | 13-10        |

| Table 13-8.  | Valid RAM Write-Complement-After-Read Test | 13-11        |

| Table 14-1.  | Memory Protection Errors                   | 14-10        |

| Table 14-2.  | Decimal Representation                     | 14-14        |

| Table 15-1.  | Microinstruction Tests                     |              |

| Table 16-1.  | Error Codes                                | 16-6         |

| Table 17-1.  | Operational Error Listing                  | 17-11        |

| Table 19-1.  | FPP Instructions                           | 19-1         |

| Table 19-2.  | Error Messages                             | 19-4         |

| Table 19-3.  | Processor Status Word                      |              |

| Table 19-4.  | Floating-Point Status Word                 | 19-4         |

# SECTION 1 SYSTEM OVERVIEW

The V70/620 MAINTAIN III Test Program System is a system approach to testing and maintaining Sperry Univac 70 and 620-series computers, internal options, and peripherals. MAINTAIN III provides an effective and uniform interface between the computer and the user.

The test programs in this manual cover only the computers and internal options. Refer to the Bibliography for a list of Software Performance Specifications (SPS) covering peripheral test programs that operate in the MAINTAIN III Test Program System.

The test programs are to be used in conjunction with the maintenance manuals for the system, which include theory of operation, installation, and maintenance information.

The MAINTAIN III system programs are designed to verify correct system operation, including internal instructions, memory, internal computer options, and peripherals and their controllers. Malfunctions can be isolated to a specific area of the system and corrected.

### **1.1 STRUCTURE**

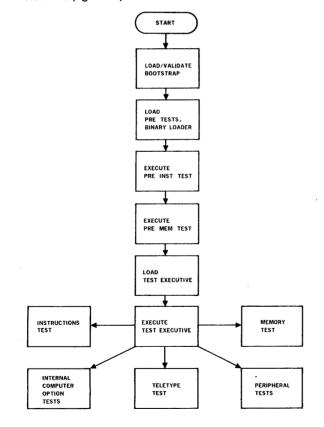

The MAINTAIN III system consists of the following elements (figure 1-1):

NOTE: The Test Executive operates with only one test program in memory at a time. **VTII-3185**

Figure 1-1. MAINTAIN III System Block Diagram

- a. Test executive program which includes preliminary instruction and memory tests, binary loader, and test executive

- b. Instructions test program

- c. Memory test program

- d. Teletype (TTY) test program

- e. Internal computer option test programs

- f. Peripheral test programs

The test executive program:

- a. Loads test program

- b. Accepts control directives and parameters from the user

- c. Executes test programs

- d. Contains a utility package, consisting of aids for debugging, program maintenance, and hardware troubleshooting

- e. Includes standard test program subroutines, i.e., TTY input/ output, time delay, memory size determination, SENSE switch option, etc.

The preliminary instructions test portion of the executive test program validates basic CPU operation, the preliminary memory test checks basic functions of the first 8K memory module, and the binary loader reads binary data and stores it in memory.

The memory test program verifies correct operation of memory. It is applicable to 16-bit systems with from 8,192 to 32,768-word memories.

The instructions test program tests and verifies execution of internal, I/O, and optional instructions.

The TTY test program verifies correct operation of the Sperry Univac-modified 33/35 ASR TTY unit.

The internal computer option test programs individually test each option to ensure correct operation.

The peripheral test programs verify correct operation of associated system peripherals (i.e., line printer, disc, paper tape system, etc.) and their controllers.

### **1.2 MAINTENANCE CONCEPTS**

MAINTAIN III minimizes maintenance time for the V70/ 620-series computers. The programs can be executed when the computer is off-line and not transferring data or performing control functions.

#### SYSTEM OVERVIEW

MAINTAIN III test programs are normally on punched paper tape; other media, such as object card decks or magnetic tape are available. The programs exercise the computer, internal options, and peripherals and their controllers with sequences of instructions. If an instruction is improperly executed, the sequence is halted and an error message is output to indicate the failing instruction or operation. The user can then repeat, continue, or halt the program until the fault is isolated and corrected.

To correct hardware malfunctions: