# PRIORITY INTERRUPT MODULE OPERATION AND SERVICE MANUAL

UP-8630

98 A 9902 428

FEBRUARY 1978

The statements in this publication are not intended to create any warranty, express or implied. Equipment specifications and performance characteristics stated herein may be changed at any time without notice. Address comments regarding this document to Sperry Univac, Mini-Computer Operations, Publications Department, 2722 Michelson Drive, P.O. Box C-19504, Irvine, California, 92713.

© 1978 SPERRY RAND CORPORATION

#### CHANGE RECORD

| Page<br>Number | Issue<br>Date | Change Description                |

|----------------|---------------|-----------------------------------|

| Various        | 2/78          | Deleted all references to Varian. |

|                |               | ÷                                 |

|                |               | •                                 |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               |                                   |

|                |               | -                                 |

|                |               | ·                                 |

|                |               |                                   |

|                |               |                                   |

### Change Procedure:

When changes occur to this manual, updated pages are issued to replace the obsolete pages. On each updated page, a vertical line is drawn in the margin to flag each change and a letter is added to the page number. When the manual is revised and completely reprinted, the vertical line and page-number letter are removed.

### LIST OF EFFECTIVE PAGES

| Page Number | Change in Effect  |

|-------------|-------------------|

| A11         | Complete revision |

|             |                   |

|             |                   |

|             |                   |

|             |                   |

|             |                   |

|             |                   |

|             |                   |

|             |                   |

|             | ·                 |

|             |                   |

|             |                   |

|             |                   |

|             |                   |

|             |                   |

| %A0731-000B |                   |

## TABLE OF CONTENTS

### SECTION 1 GENERAL DESCRIPTION

### SECTION 2 INSTALLATION

| 2.1 INSPECTION                       | 2.1 |

|--------------------------------------|-----|

| 2.2 PHYSICAL DESCRIPTION             | 2.1 |

| 2.3 PIM INTERRUPT LINES              | 2-1 |

| 2.4 DEVICE ADDRESS ASSIGNMENT        | 2-1 |

| 2.5 INTERCONNECTION                  | 2-1 |

|                                      |     |

| SECTION 3 OPERATION                  |     |

| 3.1 I/O INSTRUCTIONS                 |     |

| 3.2 PROGRAMMING CONSIDERATIONS       | 3.1 |

| 3.3 UNINTERRUPTABLE INSTRUCTIONS AND |     |

| CONDITIONS                           |     |

| 3.4 PROGRAM EXAMPLE                  | 3-2 |

|                                      |     |

| SECTION 4 THEORY OF OPERATION        |     |

| 4.1 GENERAL                          | 4-1 |

| 4.1 GENERAL                          | 4-1 |

| 4.1 GENERAL                          | 4·1 |

| 4.1 GENERAL                          |     |

### SECTION 6 MNEMONICS

## LIST OF ILLUSTRATIONS

| Figure | 2.1. | PIM Board (Component Side)                               | 2-1   |

|--------|------|----------------------------------------------------------|-------|

| Figure | 2.2  | Device Address Connections                               | 2.2   |

| Figure | 4-1. | PIM Functional Block Diagram                             | 4-1   |

|        |      | Timing for Reception and Servicing of a Single Interrupt |       |

|        |      | LIST OF TABLES                                           |       |

| Table  | 1.1. | PIM Specifications                                       | 1 · 1 |

| Table  | 2.1. | Pin Assignments for Interrupt Lines                      | 2.1   |

| Table  | 3.1. | I/O Instructions                                         | 3.1   |

| Table  | 3.2  | Program Example                                          | 3.2   |

## **SECTION 1 GENERAL DESCRIPTION**

The Priority Interrupt Module is an I/O option available with 70 series and 620 computer systems. This manual is divided into six sections:

- Features and specifications

- Installation and interconnection

- Operation

- Theory of Operation

- Maintenance

- Mnemonics list

Documents such as logic diagrams, schematics, and parts lists are supplied in a system documentation package. This package is assembled when the equipment is shipped, and reflects the configuration of a specific system.

The following list contains the part numbers of other manuals

| document number is the revision number 0 through 9): |              |

|------------------------------------------------------|--------------|

| V70 Series Architecture Reference                    | 98A 9906 00X |

| 141011001                   |              |

|-----------------------------|--------------|

| V70 Series Processor Manual | 98A 9906 02X |

| V70 Series Option Board     | 98A 9906 05X |

98A 9906 40X V77-600 Computer System Description V77-400 Computer System Description 98A 9906 41X V77-200 Computer System Description 98A 9906 42X V77-400 Processor Operation and Service 98A 9906 43X Manual V77-200 Processor Manual 98A 9906 50X V77-800 Processor Manual 98A 9906 61X

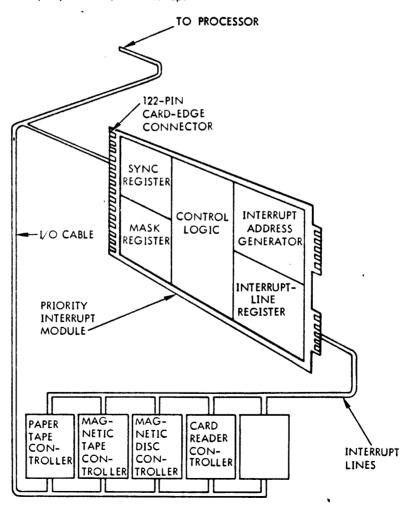

The priority interrupt module (PIM) provides for the orderly servicing of peripheral-initiated interrupts of a program in progress. It does so by:

- a. Establishing up to eight levels of interrupt priority for selected peripheral controllers.

- b. Storing interrupt requests originated by associated peripheral controllers and placing the requests on the I/O bus in the order of the established priority.

In effect, the PIM organizes a "priority-within-a-priority" system. Peripheral controllers that cannot normally initiate an interrupt because of their inability to generate memory addresses can do so when connected to the PIM. PIMcontrolled priority assignments are prewired at the factory to user specifications.

Table 1-1 lists the PIM specifications.

#### Table 1-1. PIM Specifications

#### **Parameter** Description Contains line synchronization, and mask reg-Organization isters; an interrupt address generator; priority and control logic; and line drivers, and receivers Establishes and implements eight levels of in-Control Capability terrupt priority (user-assigned) for system peripheral controllers. I/O Capability Five external control and three transfer instructions Standard Device Address 040 through 043 Interrupt Addresses First PIM: 0100 through 0117 Second and succeeding PIMs: 0120 through 0177

#### Table 1-1 PIM Specifications (continued)

System Priority Assignment

Determined by location in the system priority

chain (user-selected)

Logic levels (internal)

High = +2.4 to +5.0 V dc

Low = 0 to + 0.4 V dc

Logic levels (I/O bus)

High = +2.8 to +3.6V dc

Low = 0 to +0.5 V dc

Size

Contained on one 7-3/4-by-12-inch (19.7 x 30.3 cm)

printed-circuit board.

Power

5V dc at 0.45A

**Operating Environment**

0 to 50 degrees C, 0 to 90 percent relative

humidity without condensation.

# SECTION 2 INSTALLATION

#### 2.1 INSPECTION

The PIM has been packed and inspected to ensure its arrival in good working order. To prevent damage, take care during unpacking and handling. Check the shipping list to ensure that all equipment has been received. Immediately after unpacking, inspect the equipment for shipping damage. If damage exists:

- a. Notify the transportation company.

- b. Notify Sperry Univac.

- c. Save all packing material.

#### 2.2 PHYSICAL DESCRIPTION

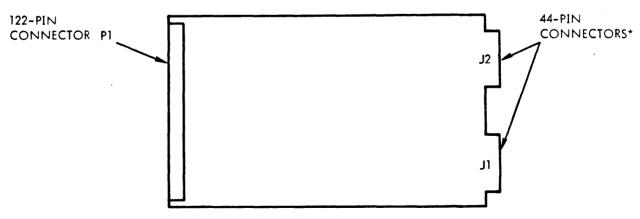

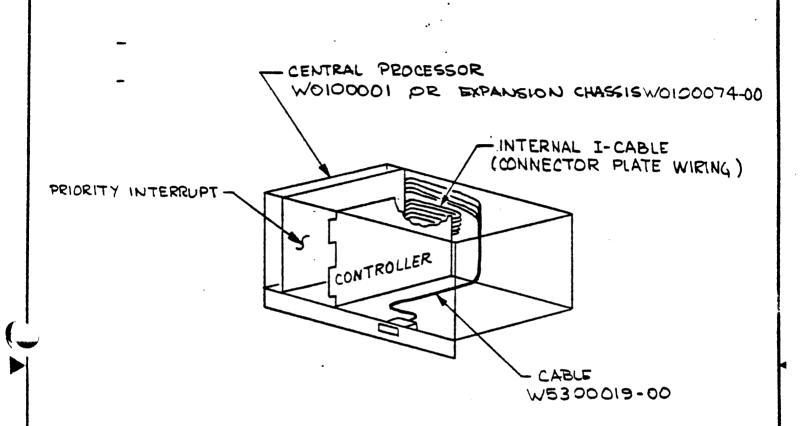

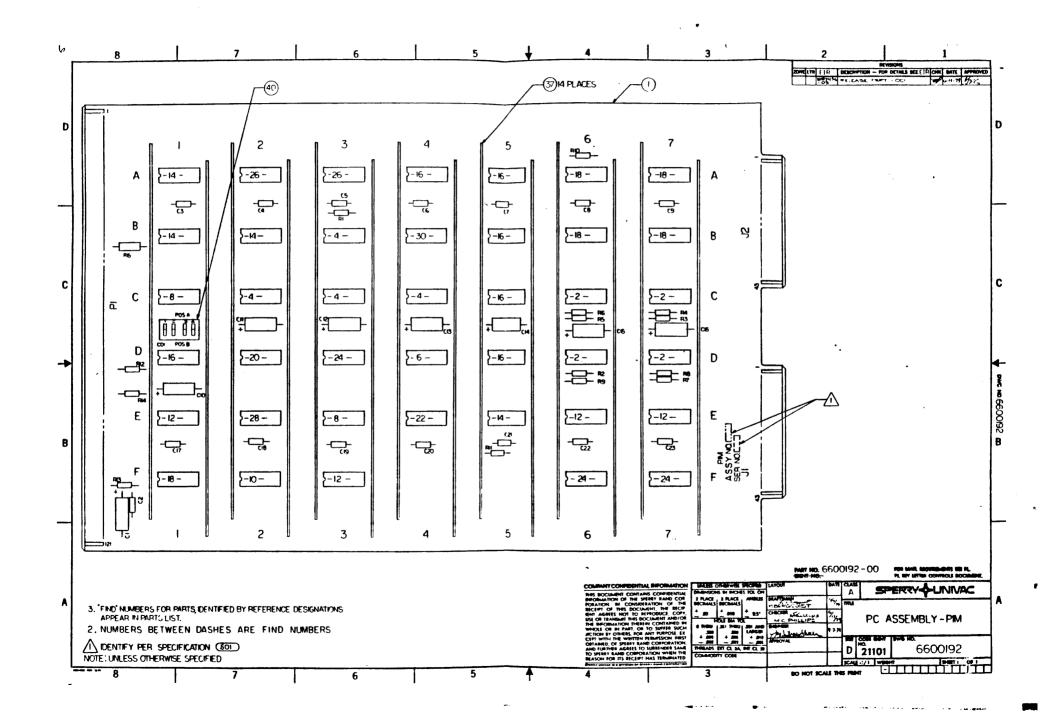

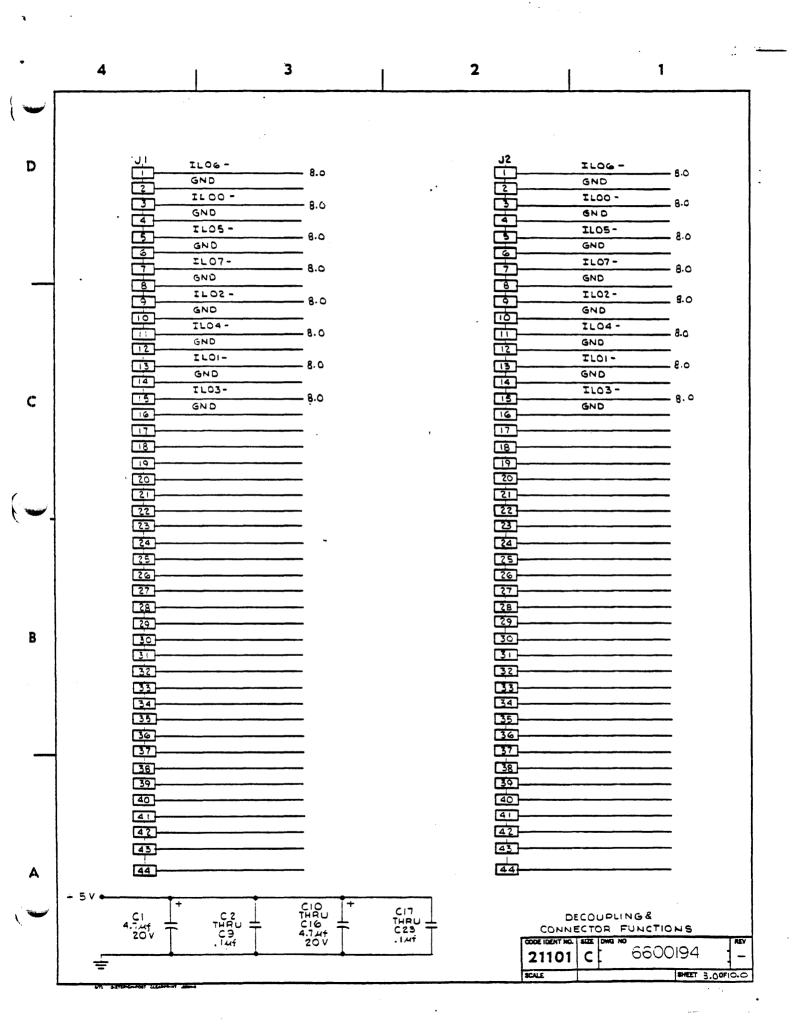

The PIM circuits are contained on a single printed-circuit (PC) board (p/n 44P0683). As illustrated in figure 2-1, the board contains three connectors P1, J1, and J2. Connectors J1 and J2 each contain eight interrupt lines (IL00-through IL07-) that can be connected to selected peripheral controllers. Connector P1 also contains the same eight interrupt lines as well as all I/O bus control signals for the PIM.

#### 2.3 PIM INTERRUPT LINES

The PIM has eight interrupt lines that enable up to eight peripheral controllers to be connected in the desired order of priority. The interrupt lines are designated IL00-through IL07-, where IL00- has the highest priority and IL07- the lowest. For controllers that are installed in the same chassis as the PIM, the interrupt lines are connected at the computer backplane connector that mates with P1 of the PIM board. For controllers in a different chassis, the

interrupt lines are contained in either an I/O expansion cable that connects to P1 of the PIM (via computer backplane) or in an interrupt cable that connects to J1 or J2 of the PIM. Pin assignments for the interrupt lines are listed in table 2-1.

Table 2-1. Pin Assignments for Interrupt Lines

| Interrupt |     |    |    |       |     |    |    |

|-----------|-----|----|----|-------|-----|----|----|

| Lines     | P1  | J1 | J2 | Lines | ·P1 | J1 | J2 |

| IL00-     | 108 | 3  | 3  | IL04- | 102 | 11 | 11 |

| IL01-     | 114 | 13 | 13 | 1L05- | 88  | 5  | 5  |

| IL02-     | 104 | 9  | 9  | IL06- | 112 | 1  | 1  |

| ILO3-     | 110 | 15 | 15 | 1L07- | 86  | 7  | 7  |

#### 2.4 DEVICE ADDRESS ASSIGNMENT

The device address for each PIM is implemented with jumper wires installed on the computer backplane connector that mates with P1 of the PIM board (figure 2-2). Device addresses 040 through 043 are reserved for PIM. Normally 040 is assigned to the first PIM, 041 to the second, 042 to the third, and 043 to the fourth. Address 044 affects all PIMs simultaneously and is used to enable or disable all PIMs.

#### 2.5 INTERCONNECTION

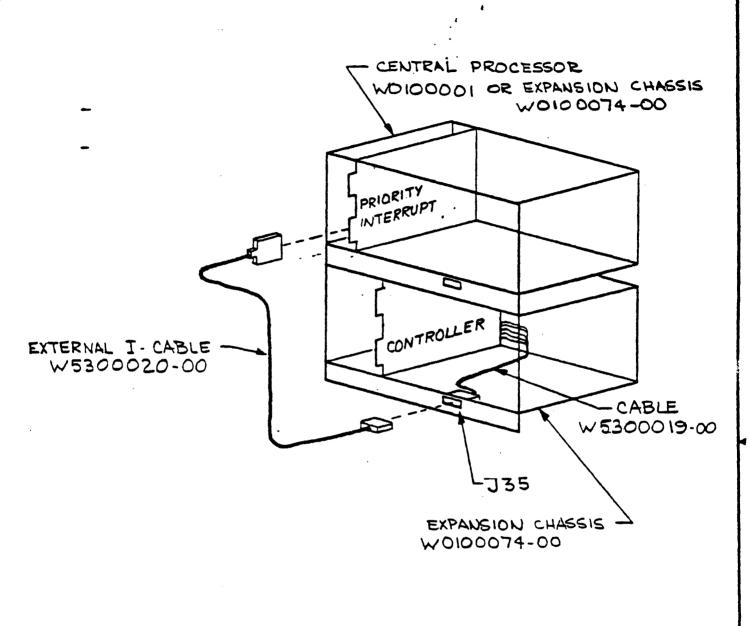

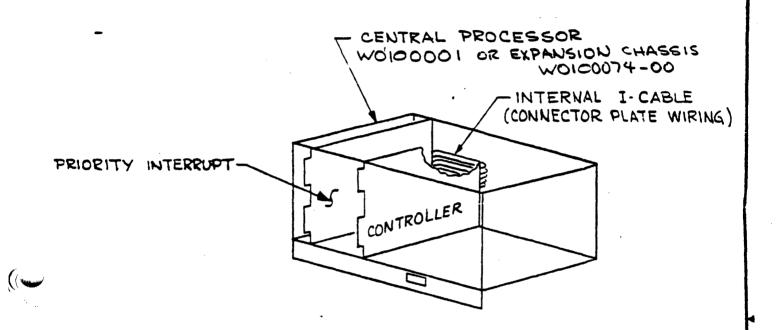

In the V70 series systems, the PIM is installed in a designated slot of an I/O chassis. Refer to the appropriate system reference manual for further installation information.

\* CONNECTORS J1 AND J2 ARE PARALLEL WIRED

VTII-1792

Figure 2-1. PIM Board (Component Side)

The PIM can be installed in designated slots of the main-frame and expansion chassis for 620/L systems. Further installation information for these computer systems, can be found in the 620/L Maintenance Manual (document number 98 A 9905 15x).

The PIM can be installed in the 77-400/200 mainframe or expansion chassis "S" slot connector plane. Further

information for these computer systems can be found in the 77-400 and 77-200 System Reference Manuals and in the 77-400/200 Configuration Guide.

The pin assignments for the connectors on the PIM board are provided in logic diagram 91D0016.

VT11-2023

Figure 2-2. Device Address Connections

# SECTION 3 OPERATION

The PIM has no operating controls or indicators. It operates under program control.

#### 3.1 I/O INSTRUCTIONS

The PIM responds to the five external control and three data transfer instructions listed in table 3-1.

loops. Two NOP instructions are required after an external control (EXC) instruction.

For computer systems containing the memory protection (MP) option in addition to the PIM, the MP is disabled everytime an interrupt is serviced. Therefore at the end of the PIM service program, the MP must be enabled again.

Table 3-1. I/O Instructions

| Mnemonic         | Program<br>Code | Functional Description                            |

|------------------|-----------------|---------------------------------------------------|

| External Control |                 | •                                                 |

| EXC 014*         | 10014*          | Clear interrupt registers.                        |

| EXC 024          | 10024           | Enable PIM.                                       |

| EXC 0244         | 100244          | Enable all PIMs in system.                        |

| EXC 034          | 10034           | Clear interrupt registers and enable PIM.         |

| EXC 044          | 10044           | Disable PIM.                                      |

| EXC 0444         | 100444          | Disable all PIMs in system.                       |

| EXC 054          | 10054           | Clear interrupt registers and disable PIM.        |

| Data Transfer    |                 |                                                   |

| OME 04           | 10304           | Transfer contents of memory to mask register.     |

| OAR 04           | 10314           | Transfer contents of A register to mask register. |

| OBR 04           | 10324           | Transfer contents of B register to mask register. |

<sup>\*</sup> represents the last octal digit of the device address.

#### 3.2 PROGRAMMING CONSIDERATIONS

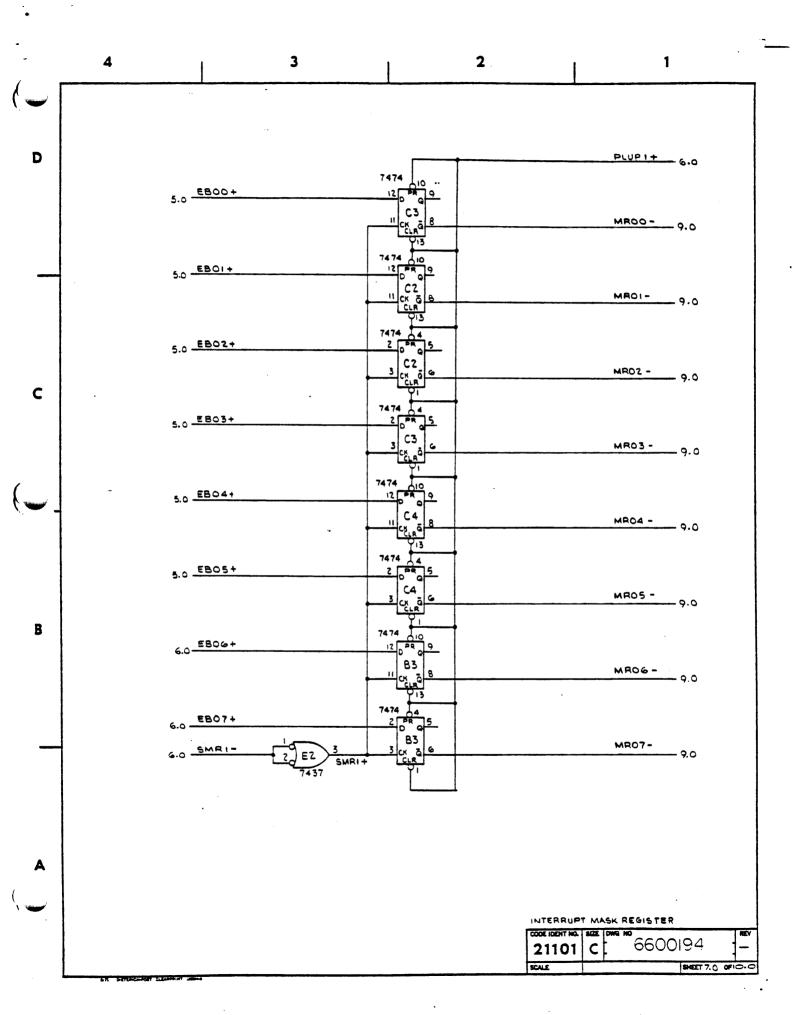

When preparing a PIM program, clear the interrupt registers to establish initial conditions. To mask peripheral controllers, write a mask word in the program. The eight least significant bits of the mask word correspond to the eight priority interrupt lines. Setting bit 0 inhibits the highest priority line, setting bit 1 inhibits the second-highest priority line, etc. The mask register must be loaded by the program after any power-up sequence, including the power-up cycle of the power failure/restart (PF/R) feature. System reset does not clear the PIM mask register.

When program loops contain only uninterruptable instructions, interrupts cannot occur. Thus, when recognition of an interrupt is imperative (such as with the PF/R), at least one no-operation (NOP) instruction must be added to such

# 3.3 UNINTERRUPTABLE INSTRUCTIONS AND CONDITIONS

An interrupt can be detected only during the last cycle of an instruction execution. In V70 systems using the memory protection feature, interrupts can be detected immediately following all instructions except:

- a. Halt (HLT) instructions

- b. Any external control (EXC) I/O instruction

- Any execution instruction. If the condition is met, interrupts are inhibited between executions of an

execution instruction and the instruction at the execution address. If the condition is not met,

interrupts are inhibited between executions of an execution instruction and the instruction following in sequence.

d. Any instruction executed in the step mode.

In 70 series systems without the memory protection feature, detection of an interrupt is inhibited during the following types of instructions:

- a. Halt (HLT) instructions

- b. All shift instructions

- c. All I/O instructions

- d. All double-word instructions

- e. All multiplication or division instructions

- f. Any instruction executed in the step mode

In all 620/L systems, detection of an interrupt is inhibited during the following types of instructions and conditions:

- a. Halt (HLT) instructions

- b. All jump, jump and mark, or execution instructions when the jump condition is met. (When the jump condition is not met these instructions are interruptable).

- c. All I/O instructions

- d. All shift or rotation instructions

- e. All multiplication or division instructions

- f. During the processor cycle immediately following an external control (EXC) I/O instruction.

- g. During the processor cycle immediately following a shift, rotation, multiplication, or division instruction during which a trap occurred (DMA operation).

- h. During the first instruction executed after entering run mode if that instruction is a single-word instruction.

- i. During a manual step operation

- j. During a halt condition

Refer to the 77-400 and 77-200 processor manuals for the uninterruptable instructions and conditions for those computer systems.

#### 3.4 PROGRAM EXAMPLE

Table 3-2 shows a typical program using the PIM. In this program, 256 descending binary frames are transferred to the high-speed paper tape punch. Memory locations 01000 to 01023 are used in the program as are computer mnemonic codes with corresponding machine language codes.

Table 3-2. Program Example

| Machi    | ne Code     |           | Source     | Code     |                        |

|----------|-------------|-----------|------------|----------|------------------------|

| Location | Instruction | Label     | Mnemonic   | Operand  | Description            |

| 001000   |             | STRT      | .ORG       | .01000 - |                        |

| 001000   | 011011      |           | .LDA       | ,MASK    | FETCH INTERRUPT MASK   |

| 001001   | 103140      |           | .OAR       | .040     | AND STORE IN REGISTER  |

| 001002   | 006010      |           | .LDAI      | .0377    | INITIALIZE OUTPUT DATA |

| 001003   | 000377      |           |            |          |                        |

| 001004   | 103137      |           | .OAR       | .037     | PRIME INTERRUPT MODULE |

| 001005   | 100240      |           | .EXC       | .0240    | ENABLE PIM             |

| 001006   | 005000      |           | .NOP       |          |                        |

| 001007   | 001000      |           | JMP        | * 1      | DELAY FOR INTERRUPTS   |

| 001010   | 001006      |           |            |          |                        |

| 001011   | 000376      | MASK      | .DATA      | .0376    | •                      |

| ¥        |             |           | PROCESSIN  |          |                        |

| 001012   | 000000      | INTR      | .ENTR      |          |                        |

| 001013   | 005311      | ******    | .DAR       | •        | DECR OUTPUT DATA       |

| 001014   | 103137      |           | OAR        | .037     | OUTPUT DATA TO PUNCH   |

| 001015   | 100240      |           | .EXC       | .0240    | RE-ENABLE PIM          |

| 001016   | 001010      |           | .JAZ       | .* +4    | 712 C777 OZE 7 777     |

| 001017   | 001022      |           | .5         |          |                        |

| 001020   | 001000      |           | JMP*       | INTR     | EXIT                   |

| 001021   | 101012      |           | ,3,4,,     |          | EAT!                   |

| 001022   | 100440      |           | .EXC       | .0440    | CLEAR PIM              |

| 001023   | 000000      |           | HLT        |          | END OF PROGRAM         |

| 00.020   | 000000      | INTERRUPT | ADDRESS    | •        | END, OF THOUNAM        |

| 000100   |             |           | .ORG       | .0100    |                        |

| 000100   | 002000      |           | JMPM       | INTR     |                        |

| 000101   | 001012      |           | ,31411 141 | ,,,,,,,, | •                      |

| 300101   | 000000      |           | .END       |          |                        |

|          | 00000       |           | ,LITO      | •        |                        |

# SECTION 4 THEORY OF OPERATION

#### 4.1 GENERAL

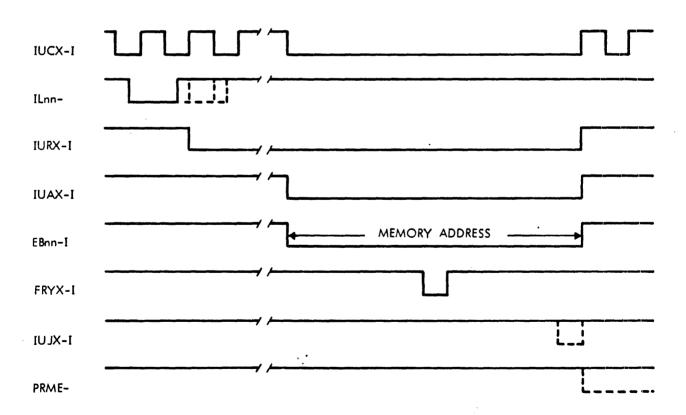

Communication between the PIM and the processor is similar to that of any peripheral controller except that the PIM can request a program interrupt. When the computer acknowledges the interrupt, the PIM specifies the memory location of the instruction to be executed.

The PIM scans the interrupt lines with every cycle of the interrupt clock (IUCX-I). If signals are detected on more than one line, the highest-priority signal is acknowledged. The remaining interrupt requests are stored in the PIM interrupt-line register until acknowledged. The PIM has an eight-bit mask register that selectively inhibits interrupt requests from the interrupt-line register. When a given flipflop of the mask register is set, corresponding interrupt requests from the interrupt-line register are inhibited. When the mask register flip-flop is reset, the interrupt

request is not inhibited. The mask register is unaffected by system reset and must be loaded under program control using data-transfer instructions.

Acknowledgment of an interrupt by the processor causes execution of the instruction located at the memory address specified by the PIM. Any instruction can be executed except an I/O type. An interrupt is thus serviced in one instruction period.

#### 4.2 FUNCTIONAL DESCRIPTION

The following subsections describe the five functional circuits of the PIM (figure 4-1). Refer to the timing waveforms of figure 4-2 and the PIM logic diagram.

VTII-1794 A

Figure 4-1. PIM Functional Block Diagram

#### 4.2.1 Control Logic

The control logic circuit directs and sequences the response of the PIM to external control, data transfer, and interrupt operations. When a computer program interrupt is requested, the processor requests the PIM to place the interrupt address on the I/O bus. If the PIM has system priority, the address line drivers are enabled. The PIM interrupt-request signal will remain active until all interrupts stored (but not inhibited) by the PIM have been acknowledged, or until PIM priority is lost.

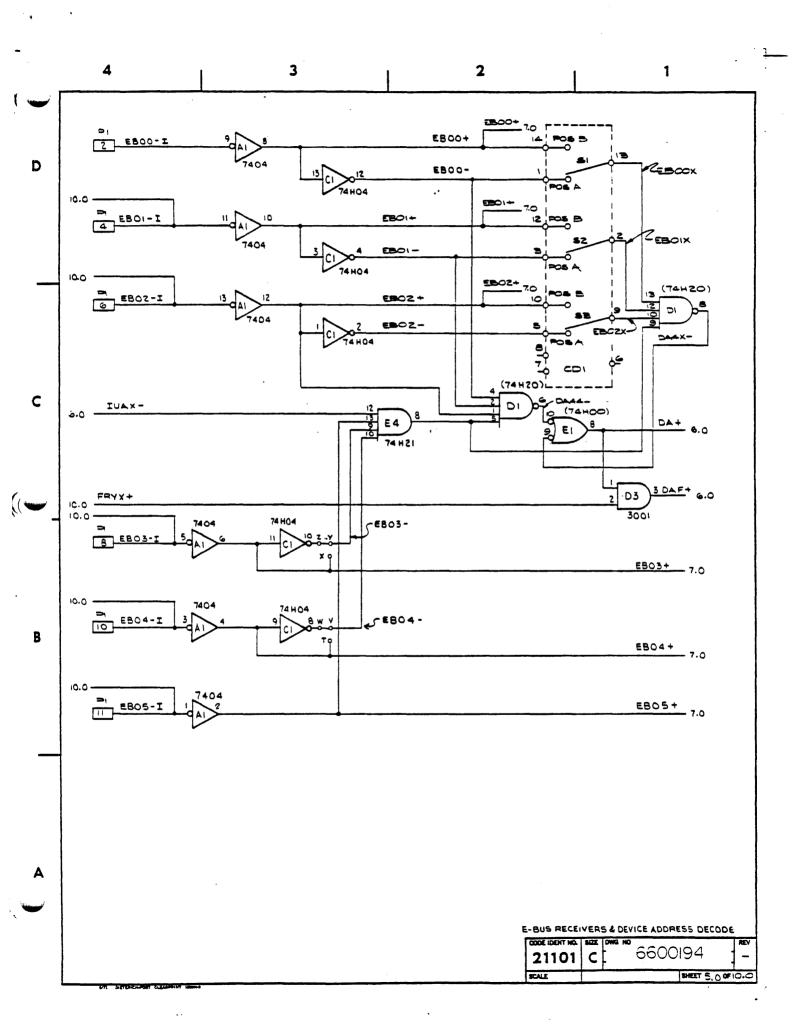

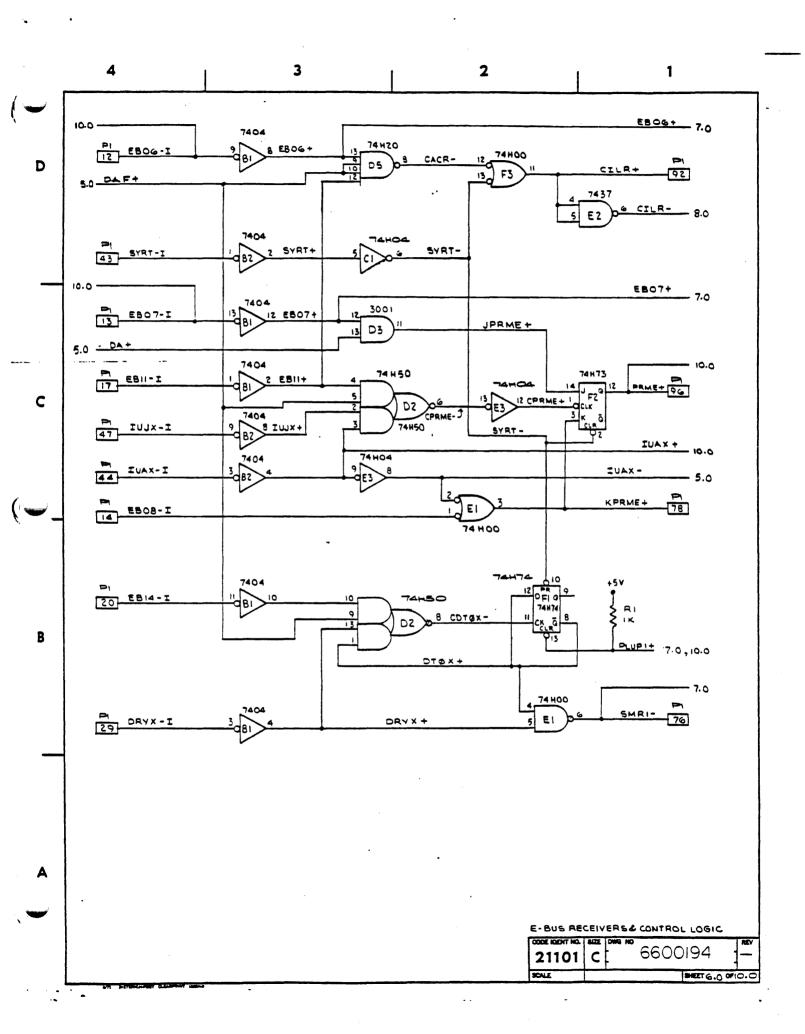

The control logic circuit consists of flip-flops PRME, DTOX, IURM and associated gates. During the execution of an output data transfer command, signals FRYX and DA set DTOX. DTOX + high and DRYX + generate SMR1- low, which transfers the mask word from the I/O bus to the mask register. At the end of the transfer, DRYX + resets flip-flop DTOX. DA, in conjunction with FRYX +, indicates that the central processor is communicating with the PIM.

External control commands for the PIM are indicated by EXCX + low. EB06 + , EB07 + , and EB08 + are combined

with EXCX+ to actuate the five external control commands.

Flip-flop PRME provides master enable/disable for the entire PIM. When PRME is reset, computer program interrupts cannot be requested by the PIM; however, the PIM continues to receive and store interrupts from external devices. When PRME+ is high, flip-flop IURM is set by INR1+ high, one IUCX-1 clock period after an interrupt is clocked into the sync register. IURM+ and PRME+ high plus PRMX-1 low generate IURX-1 low, requesting an interrupt.

When a computer program interrupt is requested by the PIM, the processor responds with signal IUAX-I low. This signal requests that PIM place the interrupt instruction address on the I/O bus.

If the PIM has system priority, the address line drivers are enabled as long as IUAX-I is low. When IUAX-I goes low, IUCX-I is held low. Interrupt conditions are therefore held static during the time that IUAX-I is low. Flip-flop IURM is cleared when all interrupts received by the PIM have been acknowledged by the central processor.

VT11-347B

Figure 4-2. Timing for Reception and Servicing of a Single Interrupt

#### 4.2.2 Interrupt Address Generator

The interrupt address generator consists of coding logic that generates the binary number of the interrupt line requesting the interrupt. A pair of memory locations is reserved for each interrupt line. The interrupt addresses are normally in memory locations 0100 through 0117. However, the 16 interrupt addresses can be placed anywhere within the first 128 memory locations except 040 through 047, and may be placed at other addresses by special request.

The interrupt address generator consists of three gates that use line priority signals to generate signals AOXX+, A1XX+, and A2XX+. These signals constitute three bits of the address code for the interrupt line to be serviced. They are placed on the I/O bus by IAEX+ low. The least-significant bit of the address code is always low, resulting in an even address. This bit is supplied by the processor when the second word of a double-word interrupt instruction is accessed.

Signal IAEX + low is generated by signals PRMX-I and IUAX-I low and FF set signal PRME + and IURM + high. These four signals indicate, respectively, that: the PIM has priority; the PIM interrupt has been acknowledged; the PIM is activated; and interrupt awaits on one of the interrupt lines.

#### 4.2.3 Interrupt-Line Register

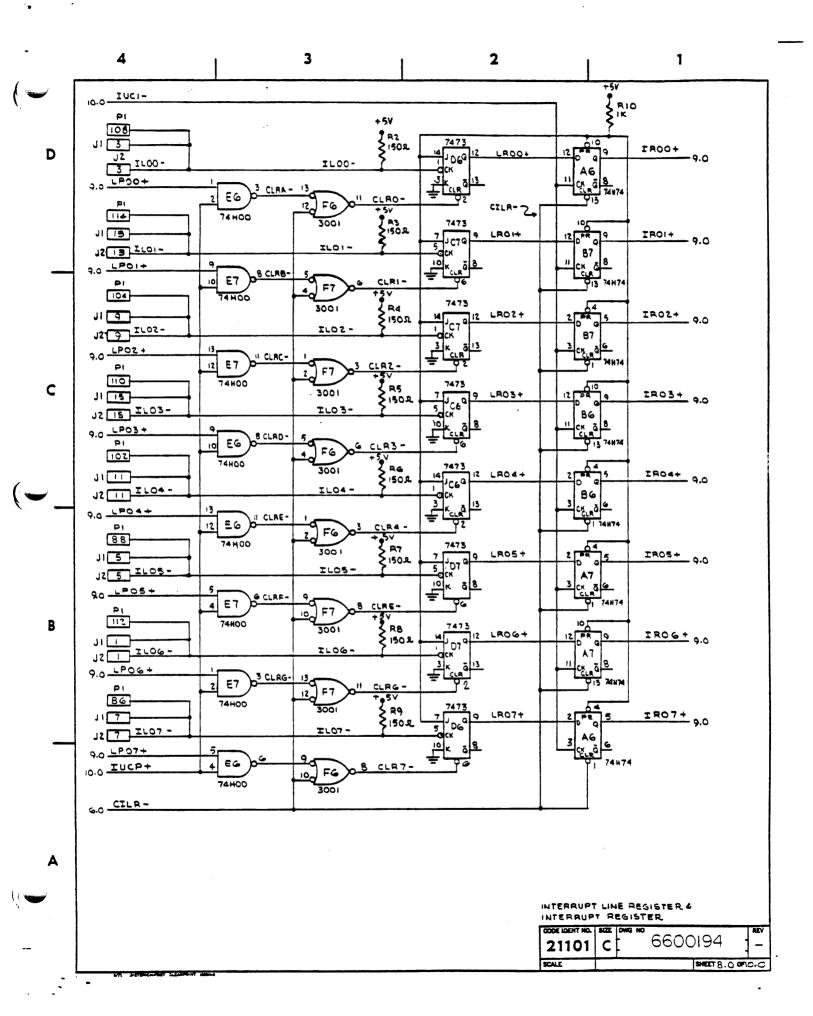

The interrupt-line register consists of eight flip-flops that asynchronously accept interrupt inputs. An interrupt is stored in the register until the interrupt is serviced or until the entire register is cleared by command.

The interrupt-line register consists of flip-flops LR00 through LR07. An interrupt is generated when an interrupt line signal, ILnn-, goes low. IL00- through IL07- are each connected to the clock input of an interrupt-line register flip-flop. ILnn- may remain low for any period of time greater than 0.2 microseconds; a constant low does not produce repetitive interrupts. If the interrupt is serviced, the flip-flop is reset by IUCP+ and a line priority signal,

LPnn+. Although IUCP+ is sent to all register flip-flops, only the flip-flop that was serviced is reset.

#### 4.2.4 Sync Register and Line Priority

The sync register consists of eight flip-flops. At each interrupt clock period, the outputs of the interrupt-line register are clocked into the sync register. The sync register, therefore, samples the status of the eight interrupt lines synchronously with the computer interrupt clock. The sync register outputs activate the priority logic used to generate the interrupt address.

If two or more interrupts occur simultaneously, the line with the highest priority is given precedence and all other lines are temporarily inhibited. An interrupt line can request a computer program interrupt only if the line has not been inhibited and a higher-priority line is not active.

The sync register consists of flip-flops IR00 through IR07. IUC1- clocks the contents of the interrupt-line register into the sync register. The outputs of the sync register are fed into a network of gates that determine the priority of each interrupt line signal. The line priority circuit generates signal INR1+, which enables the generation of signal IURX-I. In addition, LP00+ through LP07+ determine the interrupt address and the interrupt-line register flip-flop to be reset after servicing its interrupt. IL00- has the highest priority, and signal IL07- has the lowest.

#### 4.2.5 Mask Register

The mask register inhibits interrupt requests from selected interrupt lines to be disarmed while other lines are permitted to cause a program interrupt. The eight flip-flops of the mask register inhibit corresponding interrupt requests from the interrupt-line register. The mask register must be loaded under program control to establish which interrupts are to be inhibits.

EB00+ through EB07+ are loaded into the mask register when a particular interrupt is to be masked (inhibited). SMR1+ clocks this mask word into the register. The register outputs are fed into the line priority circuit. If one or more interrupts are inhibited by the mask register, the highest-priority unmasked interrupt is serviced.

# SECTION 5 MAINTENANCE

Maintenance personnel should be familiar with the contents of this manual before attempting PIM troubleshooting. The MAINTAIN III test program system (Test Programs Manual, 98 A 9952 07x) contains a PIM test program used to test various phases of PIM operation. Further diagnosis can then be made by referring to this manual.

#### **5.1 TEST EQUIPMENT**

The following test equipment and tools are recommeded for maintenance:

- a. Oscilloscope, Tektronix type 547 with dual-trace plug-in unit, or equivalent.

- b. Multimeter, Triplett type 630 or equivalent.

- c. Soldering iron, 39-watt pencil type.

#### 5.2 CIRCUIT-BOARD REPAIR

If it has been determined that circuit-board repair is required, it is recommended that the Sperry Univac customer service department be contacted so that a new circuit board can be installed in the user's system and the faulty one returned to the factory for repairs. However, if the user decides to perform his own repairs, caution should be used so that the circuit board is not permanently damaged. Approved repair procedures should be followed such as the ones described in document IPC-R-700A prepared by the Institute of Printed Circuits.

# SECTION 6 MNEMONICS

| Mnemonics | Description ··                                                                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------|

| AnXX      | Address code of device with priority interrupt.                                                                     |

| CACR      | Clear ac register. Generates signal CILR on receipt of signal EXCX.                                                 |

| CILR      | Clear line register. Clears the line and sync registers.                                                            |

| DA        | Decoded device address.                                                                                             |

| DRYX      | Data ready pulse that resets flip-flop DTOX; enables signal SMR1.                                                   |

| DTOX      | Data transfer out flip-flop. Stores the occurrence of an output command from the processor.                         |

| EBnn-I    | Address or function code bit from I/O bus.                                                                          |

| EXCX      | Enables initialization of PIM upon external control command.                                                        |

| FRYX      | Function ready pulse that sets flip flop DTOX.                                                                      |

| IAEX      | Interrupt address enable. Gates address of interrupt line onto I/O bus.                                             |

| lLnn      | Interrupt line from peripheral controller.                                                                          |

| INRn      | Interrupt request. Indicates a request from one or more interrupt lines.                                            |

| IRnn      | Sync register outputs. Stores the status of the line register in synchronism with the interrupt clock signal.       |

| IUAX      | Interrupt acknowledgment. Enables servicing of PIM interrupts.                                                      |

| IUCP      | Interrupt completion resets line register flip-flop after interrupt is serviced.                                    |

| IUCX      | Interrupt clock. Provides timing for servicing of PIM interrupt request.                                            |

| IUCI      | Interrupt clock inverted. Clocks contents of line register into sync register.                                      |

| IUDX      | Interrupt detection. Sets flip-flop IURM.                                                                           |

| IUJX      | Interrupt jump. Inhibits the PIM after a jump and mark command.                                                     |

| IURM      | Interrupt request memory flip flop. Stores a request for an interrupt from an interrupt line.                       |

| IURX-I    | Interrupt request. Sent to the processor to request signal IUAX-I.                                                  |

| KPRME     | K-input to PRME                                                                                                     |

| LPii      | Line priority signals. Indicates the eight PIM priorities.                                                          |

| LRnn      | Line register flip-flop outputs. Stores request for an interrupt from a device connected to an interrupt line.      |

| PRME      | PIM enabling flip-flop. Stores the activation of the PIM.                                                           |

| PRMX      | Priority input. Gives priority to PIM.                                                                              |

| PRNX      | Priority output. Passes priority to next in line after interrupts are serviced.                                     |

| SMR1      | Clocks mask word into mask register.                                                                                |

| SYRT      | System reset. Clears flip-flops DTOX and PRME and generates signal CILR when control-panel reset switch is pressed. |

|           |                                                                                                                     |

S.O.454618 Rev.00

Maintenance Documentation Set

F-3024-01

Priority Interrupt Module

### F3024-01

010094-001 Priority Interrupt Module

66P0192 Priority Interrupt Module

66D0192 Priority Interrupt Module

66A0194 Logic Diagram

9809902-428 Manual-Priority Interrupt Module

| _ | n | - |

|---|---|---|

| n |   | 1 |

|   |   |   |

UD1-1517 REV 2 75

| SPERRY   | Y UNIVA              |                  | SAD |          | PARTS L         |             | MFG. CODE ISSUE DATE CONTROL CA TYPE COMM. CODE ST. DOC NO SHEEL PL | RE'     | - 1      |       |

|----------|----------------------|------------------|-----|----------|-----------------|-------------|---------------------------------------------------------------------|---------|----------|-------|

| PRIOR    | ITY INTER            | RUF              | 7   | nPT      | ION, EXP        | ANSI        | ON AC DOC RANGE THRU ISSUE PI                                       | C RE    | - 1      |       |

| FIND NO. | QUANTITY<br>REQUIRED | U/M              | 5   |          | PART OR IDENT N | O<br>L DASH | NOMENCLATURE OR DESCRIPTION                                         |         | S<br>P   | C H C |

| 204      | ` !                  | 1                |     |          | W-87464         | -02         | PL REV D, PIC REV D, RANGE 00 + 03 EIR RELEASED 02/07/8             | 0       | $\top$   |       |

| 203      |                      |                  |     |          | W=87474         | -22         | PL REV C, PIC REV B, RANGE 00 - 03 EIR RELEASED 10/15/7             |         |          |       |

| ***      |                      | ***              |     | . * *    |                 | .           | **************************************                              |         |          |       |

| 501      | İ                    | X                |     |          |                 | i           | PART IDENTIFICATION PART IDENTIFICATION                             |         | A        |       |

| Sna      |                      | x                |     |          |                 | 1 1         | TEST SPECIFICATION PRIORITY INTERRUPT MODULE                        |         | •        |       |

| 803      |                      | x                |     |          |                 |             | DESIGN SPECIFICATION PRIORITY INTERRUPT MODULE                      |         | A        |       |

| ***      | *****                |                  |     | * * *    |                 | : 1         | +620 I EXPANSION + VARIABLE DATA = 00**********                     | *       | *        |       |

| 2        | 1                    | FA               |     |          |                 |             | PC ASSEMBLY-PIM. (4400683-000)                                      |         | A        | •     |

| 51       | 1                    | FA               |     | W        |                 | :           | CABLE ASSY -PRIGRITY INTERRUPT INTERNAL                             | 1       | A        |       |

| 6        | 1                    | EA               |     | W        |                 |             | CABLE - PRIDRITY INTEGRUPT, EXTERNAL                                |         | A        |       |

| A        | 18                   | FA               |     | W        | 5800002         | 1           |                                                                     |         | A        |       |

| 11       | 4                    | FA               |     | M        | 2104402         | -61         | SCREW, TRUSS HEAD 4.40 REPLACED BY 2100062                          |         | A        |       |

| 12       | 4                    | FA               |     | W        | 2204400         | -01         | WASHER-FLAT, NO.4 .250 OD, 125 ID, 028 THK                          | ı       | A        |       |

| 13       | 4                    | FA               |     | 1        |                 |             | WASHER, LOCK, INT TOOTH                                             |         | A        |       |

| 14       | 4                    | FA               |     | l        |                 | 1           | NUT, HEXAGON, LARGE PATTERN #4-40                                   |         | <u> </u> |       |

| ***      | *****                |                  |     | 1.       |                 |             | **************************************                              | *       | *        |       |

| 2        | 1                    | FA               |     |          |                 | . 1         | PC ASSEMBLY-PIM (4400683-000)                                       |         | A .      | *     |

| ***      | ******               |                  |     | **       |                 | i           | **************************************                              | *       | *        |       |

| 3        | 1                    | FA               |     | W        | 4400022         | -00         | PC ASSEMBLY PRIORITY INTERRUPT DM124                                |         | A        |       |

| 5        | 1                    | F                | \   | W        | 5300019         | -00         | CARLE ASSY -PRIGRITY INTERRUPT INTERNAL                             |         | A        |       |

| 7        | 1                    | FA               | 1   | W        | 5300060         | -00         | CABLE ASSY -PRIGRITY INTERRUPT EXTERNAL                             |         | A        |       |

| Ą        | 36                   | FA               | \   | W        |                 |             | CONTACT 22-26 AWG, .036103 INS DIA                                  |         | A        |       |

| 11       | A                    | FA               |     | W        | 2104402         | -61         | SCREW, TRUSS HEAD 424 REPLACED BY 2100062                           |         | 4        |       |

| 12       | 8                    | FA               |     | W        | 2204400         | -01         | WASHER-FLAT, NO.4 .250 OD, .125 ID, .028 THK                        |         | A        |       |

| 13       | 8                    | FA               |     | W        | 2204401         | -02         | WASHER, LOCK, INT TOOTH                                             |         | A        |       |

| .14      | 8                    | FA               |     | W        | 2304400         | -01         | NUT, HEXAGON, LARGE PATTERN #4-40                                   |         | A        |       |

|          |                      | mre <sub>o</sub> |     | <u> </u> |                 | <u> </u>    | <u> </u>                                                            | $\perp$ | $\perp$  |       |

| TITLE                         | UNIVAC IS A DIVISION OF SPEHRY RAND CO | J W 02/U7/80 W777            | TYPE COMM. CODE ST A PL DOC NO SHEET REV.  M PL W 010094 2 D |

|-------------------------------|----------------------------------------|------------------------------|--------------------------------------------------------------|

|                               | ERRIIPT OPTION, EXPAN                  | IUN                          | EA 9 SIZE A D                                                |

| FIND NO. QUANTITY<br>REQUIRED | DOCUMENT NO. DA                        | H                            | OMENCLATURE OR DESCRIPTION                                   |

| 24 1                          | 1 1 1                                  |                              | CT   MALE 8 1 FEMALE JACKSCREWS   A                          |

| 24 26                         | 1, 1 1.                                | 2 PIN - CONNECTOR            | 20 AWG WIRE SIZE MAX                                         |

| **** *********<br> <br>  3  1 | -                                      | PC ASSEMBLY                  | PRICETTY INTERRUPT DM124                                     |

| 5 1                           | 1 1 1 1                                | O CABLE ASSY -PRIGRITY THER  | i i                                                          |

| 11 4                          | 1 1 1                                  | 1 SCREW, TRUSS HEAD 4.4      |                                                              |

| 12 4                          | 1 1 1                                  | 1 WASHER-FLAT, NO.4          | l i                                                          |

| 13 4                          | 1 1 1                                  | 2 WASHER, LOCK, INT TOOTH    |                                                              |

| 1 4                           | 1 1 1 !                                | 1 NUT, HEXAGON, LARGE PATTER | N #4=40                                                      |

| 23 1                          |                                        |                              | ET T MALE & 1 FEMALE JACKSCREWS A                            |

| 54 26                         | 1 1 1 1                                | 2 PIN - CONNECTOR            | ⇒0 AWG WIRE SIZE MAX                                         |

| UD1-1517 REV. 2-75            | DIPLICATE                              |                              | SHEET 2 OF 2                                                 |

auv

|         |     |               | REVISIONS                                                 |    |         |

|---------|-----|---------------|-----------------------------------------------------------|----|---------|

|         | REV | EIR CODE      | DESCRIPTIONS                                              | DR | APPD    |

| 74      | Û   | we7474<br>-22 | RELEASE TO API                                            | РВ | 12-5-79 |

| Z01000% | Ω   | W87464<br>-02 | REVISED PEREIR, UPDATED FORMAT, DOC.<br>NO. WAS OIA 0094. | B  |         |

PART NO. WO100094-00THRU-03

FOR MATL REQUIREMENTS SEE PL PL REV LETTER CONTROLS DOCUMENT.

| NEXT | ASSEMBLY    |         | MODEL NO.                                                                         | S                         | PEIZZY      | <b>\</b> C |  |

|------|-------------|---------|-----------------------------------------------------------------------------------|---------------------------|-------------|------------|--|

| DR   | MUMEMTHALES | 3/21/Gr | CODE 21101                                                                        | TITLE                     |             |            |  |

| ÇHK  | AB B        | 3/25/68 | IDENT NO.                                                                         | PRIORITY INTERRUPT OPTION |             |            |  |

| SGN  | JB          | =125/ce | THIS DOCUMENT MAY CONTAIN PROPRIETARY INFORMATION AND SUCH INFORMATION MAY NOT BE | 620                       | I EXPANSION |            |  |

| ENGR | D. MARTIN   | 41-168  | DISCLOSED TO OTHERS FOR ANY PURPOSE OR USED TO PRODUCE                            | SIZE                      | DWG NO.     | RE∨        |  |

| APPD | D.MARTIN    | 1/2/68  | THE ARTICLE OR SUBJECT, WITH-<br>OUT PERMISSION FROM SPERRY                       | A                         | ₩010 0094   | D          |  |

| APPD | R.PEPPER    | 4/2/68  | UNIVAC .                                                                          | SHEET                     | 1 OF 9      | <b></b>    |  |

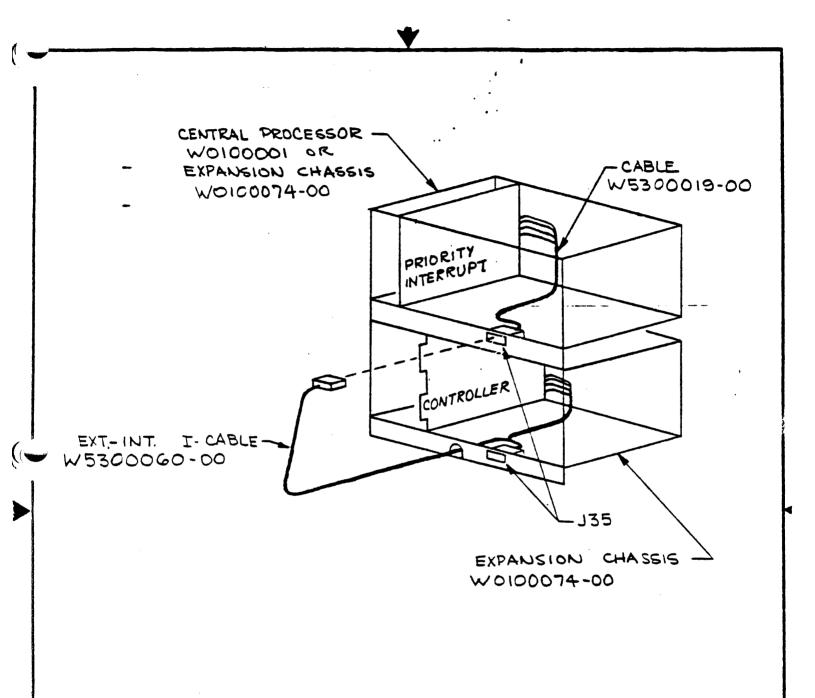

#### NOTES:

- This drawing provides the Priority Interrupt Option for the 6201 Expansion Unit. The assemblies mount in either the central processor (W0100001) or the expansion chassis (W0100074) or both

- 2. Parts List, W0100094

- Install parts per W0100074 (Also see sheets 3, 4, 5, & 6 of this drawing),

- 4 For wiring information see sheet 7.

- 5 Unterminated wires of cables are trimmed to length at installation and terminal (W580002-00) are attached.

- If the Priority Interrupt Option is to be shipped for customer installation, package it in a suitable container and identify the container with the following information:

Part No W0100094 - (Applicable Dash No and Rev Ltr )

- 7 Wiring changes per W9500003 CHG AB must be incorporated to enable this option to function

- 8 Test per W9800114

- 9 Design Spec W9800191

0

CODE IDENT NO. SIZE

21101 A W0100094 D

SCALE NONE SHEET 3 OF 9

CODE IDENT NO. SIZE

21101 A WOLOOO94

SCALE NONE

SHEE

SHEET 4 OF 9

REV

CODE IDENT NO. SIZE

21101 A WOLOOG H D

SCALE NONE SHEET 5 OF 9

SCALE NONE

CODE IDENT NO. SIZE

WOLOOO94

SHEET 6 OF 9

THE FOLLOWING FUNCTIONS WILL APPEAR AT THE CONNECTORS AS SHOWN:

|            | <u> </u>  |           |

|------------|-----------|-----------|

| FUNCTION   | CARD EDGE |           |

| 1 0.461.04 | CONNECTOR | CONNECTOR |

| IL00-      | 3         | Ά         |

| R          | 4         | В         |

| ILOI-      | 13        | C         |

| R          | 14        | D         |

| IL02-      | 9         | Ē         |

| R          | 10        | Ŧ         |

| IL03-      | ī         | #         |

| R          | 16        | J         |

| TL04-      | 11        | K         |

| R          | 12        | L         |

| IL05-      | 5         | M         |

| R          | 6.        | N         |

| IL06-      | 1         | P         |

| R          | 2         | · R       |

| IL07-      | 7         | S         |

| R          | 8         | T         |

| SPARE      | 17        | U         |

| SPARE      | 18        | V         |

| 21101          |      | W010009 | SHEET 7 OF | 0 0 |

|----------------|------|---------|------------|-----|

| CODE IDENT NO. | SIZE | 100000  |            | REV |

# DEVICE ADDRESS TABLE FOR THE NEW PIM (6600102)

| TO SELECT | LOCATION | 7 CDI    |            |

|-----------|----------|----------|------------|

| ADDRESS   | 53       | 52       | <b>S</b> 1 |

| 40        | A        | Α        | Α.         |

| 41        | A        | A        | Ø          |

| 42        | A        | <b>5</b> | <u> </u>   |

| 45        | Α        | B        | <b>(</b> ) |

### NOTES:

- 1. MAKE NO CONNECTION TO PIN 63 FOR DEVICE ADDRESSING.

- 2. TO INSTALL A NEW PMWAADOGBSORGOODIGE IN PLACE OF AN OLD STYLE PIM (W4400172), PEMOVE ENTIRE WIRE WRAP STRING (IF ANY) BETWEEN PIN 63 AND ANY OF THE FOLLOWING PINS: 66,69 AND 72.

| CODE<br>IDENT NO. | W0100094  | D   |

|-------------------|-----------|-----|

| 21101             | SH C OF G | REV |

## DEVICE ADDRESS WIRING TABLE FOR PIM(W4400172) (SHOWN FOR REFERENCE)

| i                 | ADD W/W          | JUMPER            | FROM PI            |                                           |

|-------------------|------------------|-------------------|--------------------|-------------------------------------------|

| DEVICE<br>ADDRESS | PIN 64<br>TO PIN | PIN PIN<br>TO PIN | P107<br>707<br>707 | PI DI |

| 40                | 66               | 69                | 72                 |                                           |

| 41                | 65               | 69                | 72                 | 66                                        |

| 42                | 66               | 68.               | 72                 | 69                                        |

| 43                | 65               | 68                | 72                 | 66,69                                     |

| 44                | 66               | 69                | 71                 | 72                                        |

| 45                | 65.              | 69                | . 71               | 66,72                                     |

| 46                | 66               | 48                | 71                 | 69,72                                     |

| 47                | 65               | <b>6</b> 8        | 71                 | 66,69,72                                  |

DEVICE ADDRESS WIRING TABLE FOR PIMIWA400683) SHOWN FOR REFERENCE

| <u> </u>  | <del>*************************************</del> | <u> </u> | M FOR REFE |

|-----------|--------------------------------------------------|----------|------------|

| TO SELECT | イリロ~                                             | W JUMPES | r from Pi  |

| DEVICE    | PIN 64                                           | PIN 67   | P1270      |

| ADDRESS   | TO PIN                                           | TOPIN    | TOPIU      |

| 40        | 66                                               | 69       | 72         |

| 41        | .J                                               | 69       | 72         |

| 42        | 60                                               | 68       | 72         |

| 43        | 65                                               | 68       | 72         |

| 44        | 66                                               | 69       | 71         |

| 45        | <b>4</b> 5                                       | 69       | 7.(        |

| 46        | 66                                               | 68       | 71         |

| 47        | 65                                               | 68       | 71         |

|           |                                                  |          |            |

CODE IDENT NO. 21101 W0100094 D SH 9 OF 9 REV

|       | SPERRY UN            |       | PARTS LIST DIVISION OF SPERRY RAND CORP | W 09/27/79 W777 AP A PL BOC NO 6600192 1          | •        |

|-------|----------------------|-------|-----------------------------------------|---------------------------------------------------|----------|

| C AS  | SEMBLY-P1            | M     | (440                                    | 0683-000)  A EA DOC RANGE THRU ISSUE PIC          | RE V     |

| ND NO | QUANTITY<br>REQUIRED | U/M 2 | PART OR IDENT NO DOCUMENT NO.   DASH    | NOMENCLATURE OR DESCRIPTION                       | S<br>P   |

| 00    |                      |       | W-87436 -01                             |                                                   | ,        |

| 1     | 1                    | EA    | 6600193 -00                             | **************************************            | / * A    |

| 2     | 4                    | EA    | W 4900002 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC               |          |

| 4     | 41                   | EA    | W 4900012 -00                           | INTEGRATED CIRCUIT PLASTIC OR CERAMIC             | A        |

| 6     | 1                    | EA    | W 4900022 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC               | A        |

| 8     | 5                    | EA    | W 4900023 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC OR CERAMIC    | A        |

| 10    | 1                    | EA    | W 4900036 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC               | A        |

| 1 2   | 4                    | EA    | W 4900039 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC               | <b>A</b> |

| 14    | 4                    | EA    | W 4900040 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC               | A        |

| 6     | 6                    | EA    | W 4900056 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC               | A        |

| 8     | 5                    | EA    | W 4900082 -01                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC OR CERAMIC    | A        |

| 5 0 į | 1                    | EA    | W 4900093 -01                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC               | A        |

| ? 2¦  | 1                    | EA    | W 4900094 -01                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC OR CERAMIC    | A        |

| 24    | 3                    | EA    | W 4900104 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC OR CERAMIC    | A        |

| 6     | 2                    | EA    | W 4900128 -01                           | INTEGRATED CIRCUIT 14 DIL PLASTIC OR CERAMIC SEL  | A        |

| 8     | 1                    | EA    | W 4900138 -00                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC OR CERAMIC    | A        |

| 5 O   | 1                    | EA    | W 4900554 -01                           | INTEGRATED CIRCUIT 14 DIL - PLASTIC OR CERAMIC    | A        |

| 32    | 6                    | EA    | W 6502500 102                           | RESISTOR, FIXED COMP, 1/4W, 5%1000 OHMS           | A        |

|       |                      |       | REF DES 1                               | R1 R10 THRU R14                                   |          |

| 33    | 8                    | EA    | W 6502500 151                           | RESISTOR, FIXED COMP, 1/4H, 5x150 OHMS            | A        |

| !     | İ                    |       | REF DES 1                               | R2 THRU R9                                        |          |

| 4     | 1                    | EA    | W 6505000 151                           | RESISTOR, FIXED, CARBON .5W 5% 150 OHMS           | A        |

|       | !                    |       | REF DES 1                               | R15                                               |          |

| 5     | 15                   | EA    | 6630012 -11                             | CAPACITUR, FIXED, CERAMIC .100 MF,50VDC,+80%,-20% | A        |

| 1     | İ                    |       | REF DES 1                               | C2 THRU C9 C17 THRU C23                           |          |

|          |                      |          |           |                            |             | 74                     |            |        |                      |             |                 |        |          |       |      |    |

|----------|----------------------|----------|-----------|----------------------------|-------------|------------------------|------------|--------|----------------------|-------------|-----------------|--------|----------|-------|------|----|

| SPERR    | Y <b>\</b> UNIVA     | C´       |           | PARTS LIST                 | MFG CODE    | 155UE DATE<br>09/27/79 | CONTROL CA | AP     | COMM. CODE ST        | PL          | DOC NO          | 600192 | SHEET    | PL R  | REV  |    |

|          | SPERRY UN            | IIVAC IS | A DIV     | ISION OF SPERHY RAND CORP. |             |                        |            | U/M    |                      |             |                 | 000172 |          | PIC F |      | L  |

| PC AS    | SEMBLY-P             | T M      |           | 1440                       | 0683-000)   |                        | A          | 1      | 1                    | DOC<br>SIZE | RANGE           | THRU   | 15501    | 1     | RE V |    |

|          |                      | -        | 3.1       | PART OR IDENT NO           |             |                        | "          |        |                      |             |                 |        | <u> </u> |       | -    | -  |

| FIND NO  | QUANTITY<br>REQUIRED | U/M      | 1         | DOCUMENT NO   DASH         |             |                        | NO!        | WENCIA | ATURE OR DESCRIPTION |             |                 |        |          |       | P    | HG |

| 36       | 8                    | EA       |           | W 7100200 475              | CAPACITOR,  | TANTALUM               | 204 10     | X .    | 4.7 MF               | ı           |                 |        |          |       | Δ    | *  |

|          |                      |          |           | REF DES 1                  | Ci          |                        | C10        | 1      | THRU C16             |             |                 |        |          | :     |      | *  |

| 37       | 14                   | EA       |           | W 5300194 -00              | BUS, POWER  | DISTRIBU               | NOIT       |        | 8 SPACE              |             |                 |        |          |       | A    | •  |

| 40       | 1                    | EA       |           | W 7800114 -00              | SWITCH, DIP | AND SWITE              | H COVE     | 2      | SWITCH, DIP          | FOR         | ROCKER          | ,      |          |       | A    | *  |

| FOI      | į                    | X        | İ         | 6600194 -00                | LOGIC DIAG  | RAM-PIM                |            |        |                      | 1           |                 |        | ;        |       | A    | •  |

| \$01     |                      | X        |           | SW01163 -00                | MARKING SPI | EC                     |            |        | PART IDENT           | IFIC        | ATION           |        |          |       | A    | •  |

|          | 1                    |          |           | 1                          |             |                        |            |        |                      |             |                 |        |          |       |      |    |

|          |                      |          |           |                            |             | •                      |            |        |                      |             |                 |        |          |       |      | 1  |

|          |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | į  |

| 1. !     |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | İ  |

|          |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | ĺ  |

|          |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | 1  |

| <b> </b> |                      |          |           |                            |             |                        |            | -      |                      |             |                 | :      |          |       |      | l  |

|          |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      |    |

|          |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | l  |

| 1        | į                    |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | ĺ  |

|          |                      |          |           | i                          |             |                        |            |        |                      |             |                 |        |          |       |      | l  |

|          | İ                    |          |           | į                          |             |                        |            |        |                      |             |                 |        |          |       |      |    |

|          |                      |          |           | į                          |             |                        |            |        |                      |             |                 |        |          |       |      |    |

|          |                      |          |           | į                          |             |                        |            |        |                      |             |                 |        |          |       |      | l  |

|          |                      |          |           | į                          |             |                        |            |        |                      |             |                 |        |          |       |      | İ  |

|          | İ                    |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      |    |

|          | į                    |          |           | į                          |             |                        |            |        |                      |             |                 |        |          |       |      | Į  |

|          | į                    |          |           | i                          |             |                        |            |        |                      |             |                 |        |          |       |      | l  |

|          | į                    |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | ĺ  |

|          |                      |          |           | į                          |             |                        |            |        |                      |             |                 | •      |          |       |      | İ  |

|          |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | İ  |

| 1.       |                      |          |           |                            |             |                        |            |        |                      |             |                 |        |          |       |      | l  |

|          |                      |          |           |                            |             |                        |            |        | ı                    | i           |                 |        |          |       |      |    |

|          |                      | .N7/h    | <u></u> _ | IDI TEATE                  |             | <b>X</b>               | <u> </u>   |        |                      |             | SHEE            | 7 2 0  | F        | 5     | II   |    |

|          |                      |          |           |                            |             |                        |            |        |                      |             | ~ · · · · · · · |        | •        | _     |      |    |

D

C

B

#### NOTES: (UNLESS OTHERWISE SPECIFIED)

I. ALL RESISTORS ARE 1/4 W. 5%

|          | REVISIONS |             |       |         |        |     |         |          |  |  |  |  |

|----------|-----------|-------------|-------|---------|--------|-----|---------|----------|--|--|--|--|

| ZONE LTR | EI        | DESCRIPTION | - FOR | DETAILS | SEETIR | CHK | DATE    | APPROVED |  |  |  |  |

| 1-       | W87456    | RELEASE     | -     | 7 "25   |        | 70  | 6-11-74 | 13/10    |  |  |  |  |

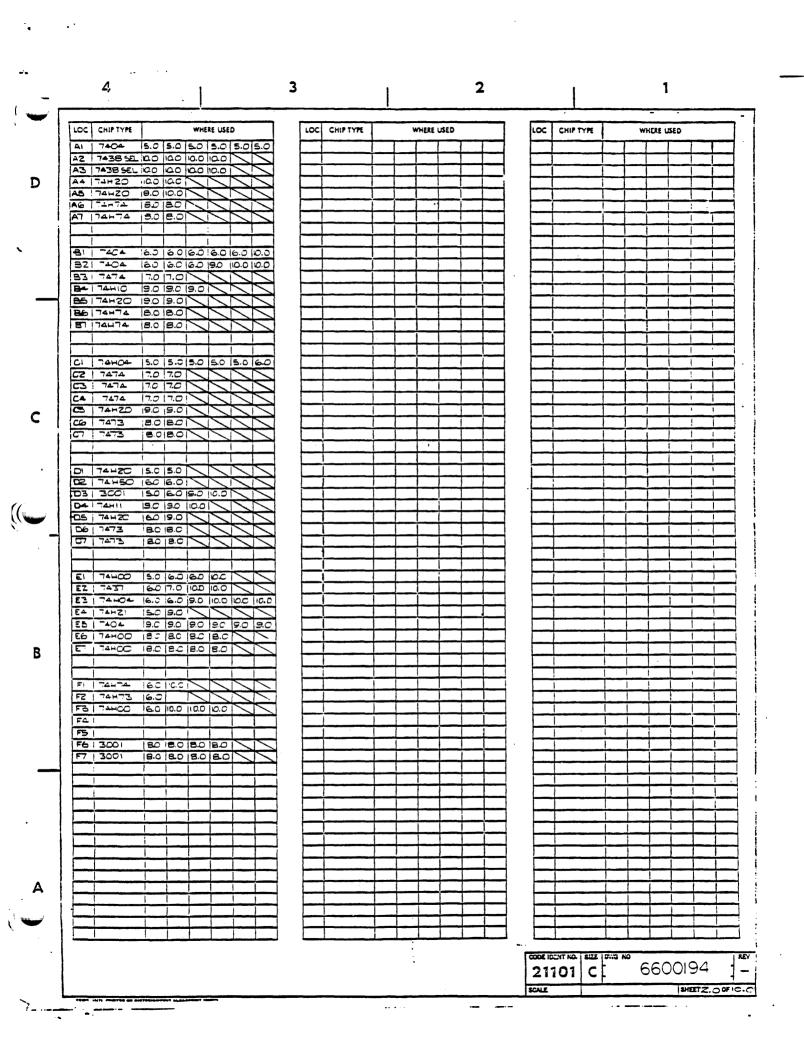

#### TABLE OF CONTENTS

| DESCRIPTION                                  | SHEET       |

|----------------------------------------------|-------------|

| cover, table of contents                     | 1.0         |

| I.C. LOCATION CHART                          | 2.0         |

| DECOUPLING, CONNECTOR FUNCTION               | 3.0 44.0    |

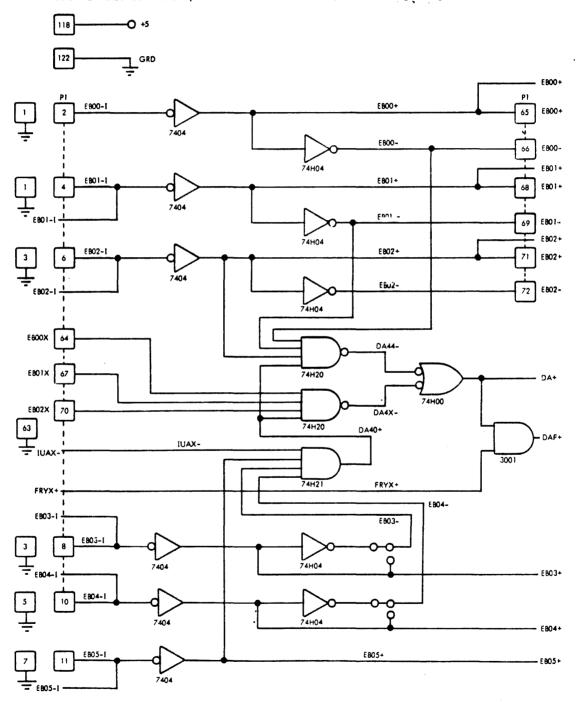

| E- BUS RECEIVERS & DEVICE ADDRESS DECODE     | 5.0         |

| E- BUS RECEIVERS & CONTROL LOGIC             | 6.0         |

| INTERRUPT MASK REGISTER                      | 7.0 '       |

| INTERRUPT LINE REGISTER & INTERRUPT REGISTER | <b>6</b> .0 |

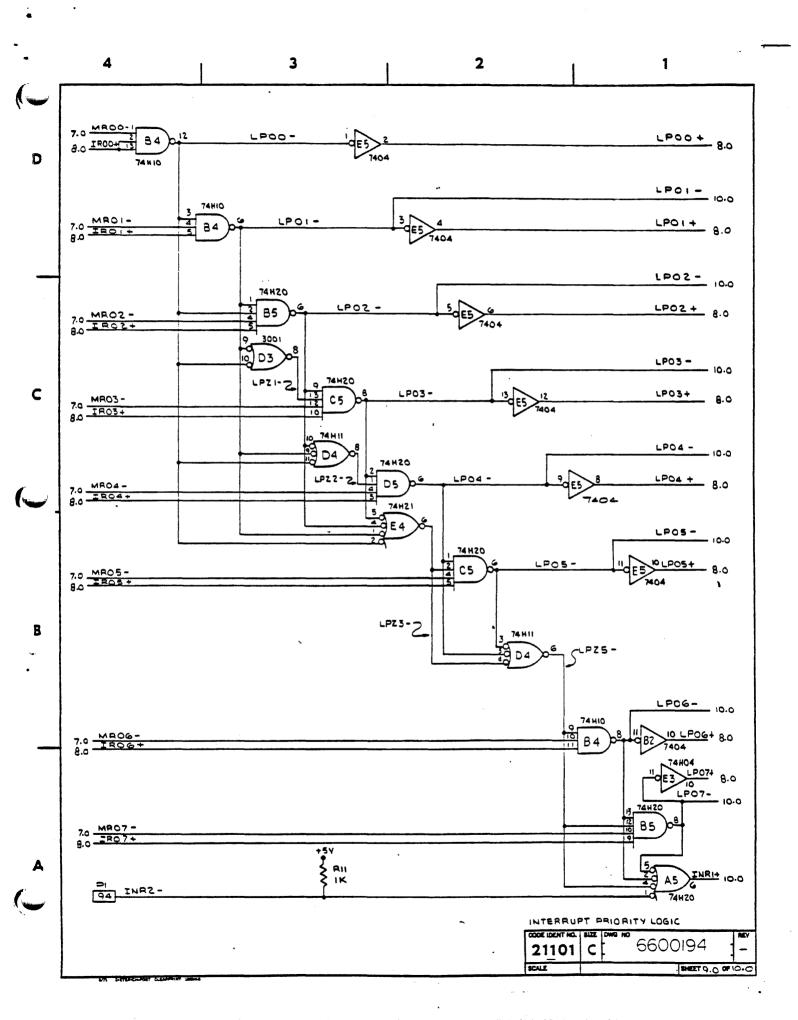

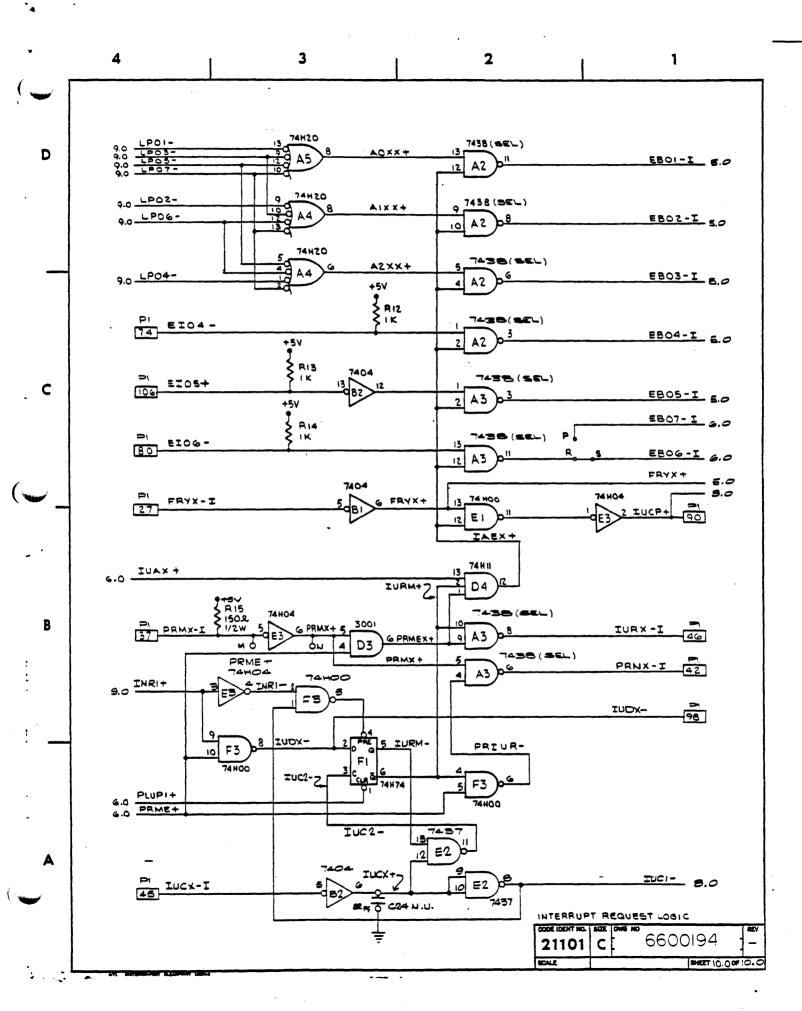

| INTERRUPT PRICRITY LOGIC                     | 9.0         |

| INTERRUPT REGUEST LOGIC                      | 10.0        |

|         | REFERENCE DESIGNATIONS |        |

|---------|------------------------|--------|

| HIGHEST | NOT USED               |        |

| J 2     |                        |        |

| ə١      |                        |        |

| R 15    |                        |        |

| C74     |                        |        |

|         |                        | $\neg$ |

|         |                        |        |

COMPANY CONFIDENTIAL INFORMATION

THIS DOCUMENT CONTAINS CONFIDENTIAL

INFORMATION OF THE SPERRY RAND CORPORATION. IN CONSIDERATION OF THE

RECEIPT OF THIS DOCUMENT. THE RECIPIENT AGREES NOT TO REPRODUCE. COPY,

USE OR TRANSMIT THIS DOCUMENT AND/OR

THE INFORMATION THEREIN CONTAINED IN

WHOLE OR IN PART. OR TO SUFFER SUCH

ACTION BY OTHERS, FOR ANY PURPOSE, EX.

CEPT WITH THE WRITTEN PERMISSION. FIRST

OBTAINED: OF SPERRY RAND CORPORATION.

AND FURTHER AGREES TO SURRENDER SAME

TO SPERRY RAND CORPORATION WHEN THE

REASON FOR ITS RECEIPT HAS TERMINATED.

WERRY UNIVAC. IE & DIVISION OF MERRY RAND COMPORATION.

|       | ASSEMBLY NO. 6600192-00 IDENT NO. 6600194-00    |               |       |       |                    |                 |     |

|-------|-------------------------------------------------|---------------|-------|-------|--------------------|-----------------|-----|

| ₹⊦    | SHEET                                           | LAYOUT D.     | ATE   | CLAS  | \$ =               | PERRY           | •   |

| 0     | REV   1 1 !   1   1   1   1   1   1   1   1     |               |       | Α     |                    | - CITCE TO LONG | •   |

| 8     | SHEET                                           | DRAFTSMAN     | 20/   | TITLE | <del></del>        |                 |     |

| 压     | REV                                             |               |       |       |                    | 1.C D 4.14 D114 |     |

| آم آ  | SHEET                                           | CHECKER       | 11/4  | L.    | LOGIC DIAGRAM-PIM. |                 |     |

| t     |                                                 | NI C PHILLIPS | 474   | į     |                    |                 |     |

| .∠ Ł  |                                                 | ENGINEER      | -7-79 |       |                    |                 |     |

| ्र° [ | SHEET 11.0 (2013-214-215-21-2017-216-219-010-01 |               | ٠,    |       |                    |                 |     |

| -     | REV     -   -   -   -   -                       | APPROVAL      |       | SIZE  | CODE IDENT         |                 | REV |

| ſ     | SHEET INDEX                                     |               |       | C     | 21101              | 6600194         | -   |

| - {   |                                                 |               |       | _     | 21101              | <u> </u>        |     |

| - 1   | SHEET: O OF:                                    |               |       |       | FIC.O              |                 |     |

|           | 4               | ] 3             | }         | 1      | 2                | ł          |             | 1                   |

|-----------|-----------------|-----------------|-----------|--------|------------------|------------|-------------|---------------------|

| ( [       | PI GND          |                 | PI        | PRNX-I |                  | PI         |             |                     |

|           | EB00-T          |                 | 42        | SYRT-I | - 10. 0          | 84         | GND         | -                   |

| į         | [3]             | <del></del> 5.0 | 43        | LUAX-I | <b> 6.</b> 0     | 85         |             |                     |

| D         | 3 GND<br>EBOI-I |                 | 44        | IUCX-I | <b>— 6.</b> 0    | 86         | IL07-       | — B.o               |

|           | 4               | 5.0, 10.0       | 45        |        | - 10.0           | 87         | <del></del> |                     |

|           | 3               |                 | 46        | IURX-I | _ 10.0           | 88         | ILO5-       | 8.0                 |

|           | <u> </u>        | 5.0,10.0        | 47        | IUJX-I | _ 6.0            | <u>\$9</u> | GND         |                     |

|           |                 |                 | 48        |        | <del>-</del> .   | 90         | IUCP+       | 10-0                |

|           | 8 E803-I        | 5.0,10.0        | 49        |        | <del></del>      | 91         | GND         |                     |

|           | 9 GND           |                 | 50        |        |                  | 92         | CILR+       | 60                  |

| -         | 10 EB04-I       | 5.0,10.0        | 51        | GND    | _                | 93         | GND         |                     |

|           | EBOS-I          | 5.0,10.0        | 52        |        |                  | 94         | INR2 -      | 9.0                 |

|           | EBOG-I          | 6.0,10.0        | 53        | GND    |                  | 95         | GND         |                     |

|           | 13 EB07-I       | 6.0,10.0        | 54        |        |                  | 96         | PRMET       | -6.0,10.0           |

| _         | EB08-1          | 6.0,10.0        | 55        |        | _                | 97         | GND         |                     |

| C         | 15              | ·               | 56        |        | -                | 98         | IUD×-       | 10.0                |

| į         | 16              |                 | 57        |        |                  | 99         | GND         |                     |

|           | EBH-I           | <b>6.</b> 0     | 58        |        |                  | 100        |             |                     |

|           | 18              |                 | 59        |        |                  | 101        | GND         |                     |

|           | 19              |                 | 60        |        | _                | 102        | IL04-       |                     |

|           | EB14 - I        | 6.0             | [60]      |        | _                | 103        | GND         | <del>- 8.0</del>    |

|           | 1               | 6.0             | •         |        |                  | 1          | ILOS-       |                     |

|           | 21 GND          |                 | (3)       | GND    |                  | 104        | GND         | 8.0                 |

| -         | 22              | <del></del>     | 63        |        | <del></del>      | 105        | E105+       |                     |

|           | 23 GND          | <del></del>     | 64        |        |                  | 106        | GND         | -10.0               |

|           | 24              | _               | 65        | - M    | <del>_</del>     | 107        | IF00-       | _                   |

| В         | 25 GND          |                 | 66        |        |                  | 108        | GND         | 8.0                 |

| 1         | Z6 ERVX-T       |                 | 67        |        |                  | 109        | ILO3-       |                     |

| į         | [27]            |                 | 68        |        | _                | 110        | GND         | 8.0                 |

|           | 28              | <del></del>     | 69        |        | <del>-</del>     |            | IL06-       | _                   |

|           | 29              | G.O             | 70        |        |                  | 112        | GND         | — s.c               |

|           |                 |                 | 71        |        | _                | 113        | FLOI-       |                     |

|           | 31 GND          |                 | 72        |        |                  | 114        |             | -8.0                |

|           | 32              |                 | 73        | E104 - | <del></del>      | 115        |             |                     |

|           | 33              |                 | 74        | 5104 - | - 10.0           | 116        |             |                     |

|           | 34 GND          | <del></del>     | 75        | 5MR1 - | -                | 117        | +57         |                     |

|           | 35              | <del></del>     | 76        | 3MK1 - | -6.0,7.0         | 118        | . 51        | -                   |

| A         | 36 GND          | <del></del>     | 77        | 498ME: | _                | 119        |             | -                   |

|           | 37 PAMA-1       | 10.0            | 78        | CPRME+ | <b> 6.0</b>      | 120        | +5∨         |                     |

|           | GND             |                 | 79        | EIOG - | _                | 121        | <del></del> | -                   |

| <b>\_</b> | 39              |                 | 180       |        | <del></del> 10.0 | 122        | GND         | CONNECTOR FUNCTIONS |

|           | GND GND         | <del></del>     | 82        |        | <del></del>      | 21101      | C MIG NO    | 00194               |

|           | 4               | *****           | <u>B3</u> |        |                  | SCALE      |             | SHEET 4.0 0F10.0    |