# TELECOMMUNICATION CONTROLLERS

## Models:

TCB-1 DLP 64 DLP 128

### PREFACE

This document is the Standard Maintenance (STD) Manual for the TCB-1, DLP 64, and DLP 128 TC Controllers. It is organized in accordance with the approved STD outline established at the Field/Home Office Publications meetings conducted on September 14th and 15th, 1982. The scope of this manual reflects the type of maintenance philosophy selected for this product.

The purpose of this manual is to provide the Wang-trained Customer Engineer (CE) with instructions to operate and diagnose faults of the TCB-1, DLP 64, and DLP 128 TC Controllers. It will be updated on a regular schedule.

### Third Edition, February (1984)

This edition of this STD manual obsoletes document(s) no. 729-0887 and 729-0887-A. The material in this document may only be used for the purpose stated in the Preface. Updates and/or changes to this document will be published as a Publication Update Bulletin (PUB) or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing Wang equipment. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

©Copyright WANG Labs., Inc. 1982, 1983, 1984

### TABLE OF CONTENTS

| CHAPTER                                                                                     | 1 INTRODUCTION                                                                                                                                                                                                                                                                                       | PAGE                                                                           |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4                                                                    | Introduction                                                                                                                                                                                                                                                                                         | 1-1<br>1-1<br>1-2<br>1-3                                                       |

| CHAPTER                                                                                     | 2 THEORY OF OPERATION                                                                                                                                                                                                                                                                                |                                                                                |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.3<br>2.3.1<br>2.4<br>2.4.1.1<br>2.4.1.1 | Introduction Processor Section Processor Section Overview. Character and Master Monitor. Maskable Interrupt Sequence. Non-Maskable Interrupt Sequence. Data Link Section Data link Section Overview. Memory Control Section Memory Control Section Overview. TCB-1 Memory DLP 64/128 Memory          | 2-1<br>2-2<br>2-4<br>2-6<br>2-7<br>2-8<br>2-10<br>2-12<br>2-14<br>2-17<br>2-17 |

| CHAPTER                                                                                     | 3 OPERATION                                                                                                                                                                                                                                                                                          |                                                                                |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.3<br>3.4<br>3.5       | Introduction TC Controller Software Support 3270 Software Emulation Asynchronous Operation Bisynchronous Operation Remote Wangnet (WSN). SNA Teletex OIS 3270 Emulation Front Panel LED Indicators. Remote Wangnet Front Panel LED Indicators Teletex Front Panel LED Indicators Interface Standards | 3-1<br>3-2<br>3-3<br>3-3<br>3-4<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11    |

| CHAPTER                                                                                     | 4 INSTALLATION                                                                                                                                                                                                                                                                                       |                                                                                |

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                       | Introduction Unpacking and Inspection Switch Settings OIS Switch Bank SWl Switch Settings OIS Switch Bank SW2 Switch Settings VS Leased Line Modem Operation Switch Settings for VS Null Modem Operation                                                                                             | 4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-4                                  |

|                                                                                                                                                        | ,                                                                               | PAGE                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 4.4<br>4.4.1<br>4.4.2<br>4.4.2.1<br>4.4.2.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.5.1<br>4.4.5.2<br>4.4.5.3<br>4.4.5.4<br>4.4.6                            | Installation Requirements (140/145 Class Masters)  Top Cover Removal            | 4-6<br>4-7<br>4-7<br>4-8<br>4-9<br>4-13<br>4-14<br>4-14<br>4-16<br>4-19                      |

| 4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.3.1<br>4.5.3.2<br>4.5.4<br>4.5.5<br>4.5.6<br>4.5.6<br>4.5.7<br>4.5.7.1<br>4.5.7.2<br>4.5.7.3<br>4.5.7.4<br>4.5.8 | Installation Requirements (105/115/125A/130A) Masters                           | 4-22<br>4-25<br>4-25<br>4-27<br>4-27<br>4-27<br>4-32<br>4-34<br>4-34<br>4-34<br>4-36<br>4-36 |

| 4.6<br>4.6.1<br>4.6.2<br>4.6.2.1<br>4.6.2.2<br>4.6.2.3<br>4.6.2.4<br>4.6.2.5<br>4.6.2.6                                                                | Installation Requirements (OIS 40/50 Masters)                                   | 4-39<br>4-41<br>4-41<br>4-41<br>4-43<br>4-44                                                 |

| 4.7<br>4.7.1<br>4.7.2<br>4.7.3.<br>4.7.3.1<br>4.7.3.2                                                                                                  | Installation Requirements (TCP) Telecommunications Processor  Top Cover Removal | 4-51<br>4-51<br>4-52<br>4-52                                                                 |

|                                                       |                                                                                                                                                                                                                                                                                               | PAGE                                   |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4.7.3.4<br>4.7.3.5<br>4.8<br>4.9                      | X.21 Interface Cable Installation  TC Rear Panel Installation  TC Controller PCB Installation  Master Power-On Procedure  Interconnection With Modems/ACU  Optional Cables                                                                                                                    | 4-55<br>4-56<br>4-59<br>4-59           |

| CHAPTER 5                                             | PREVENTIVE AND CORRECTIVE MAINTENANCE                                                                                                                                                                                                                                                         |                                        |

| 5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4 | Preventive Maintenance  Corrective Maintenance  Troubleshooting Check List  Power-Up Diagnostics  TCB-1 Power-Up Diagnostics  TCB-1 Loopback Test Procedure Requirements.  DLP 64/128 Power-Up Diagnostics  DLP 64/128 Loopback Test Requirements.  EIA Interface Test Set and Breakout Boxes | 5-1<br>5-3<br>5-3<br>5-6<br>5-7<br>5-9 |

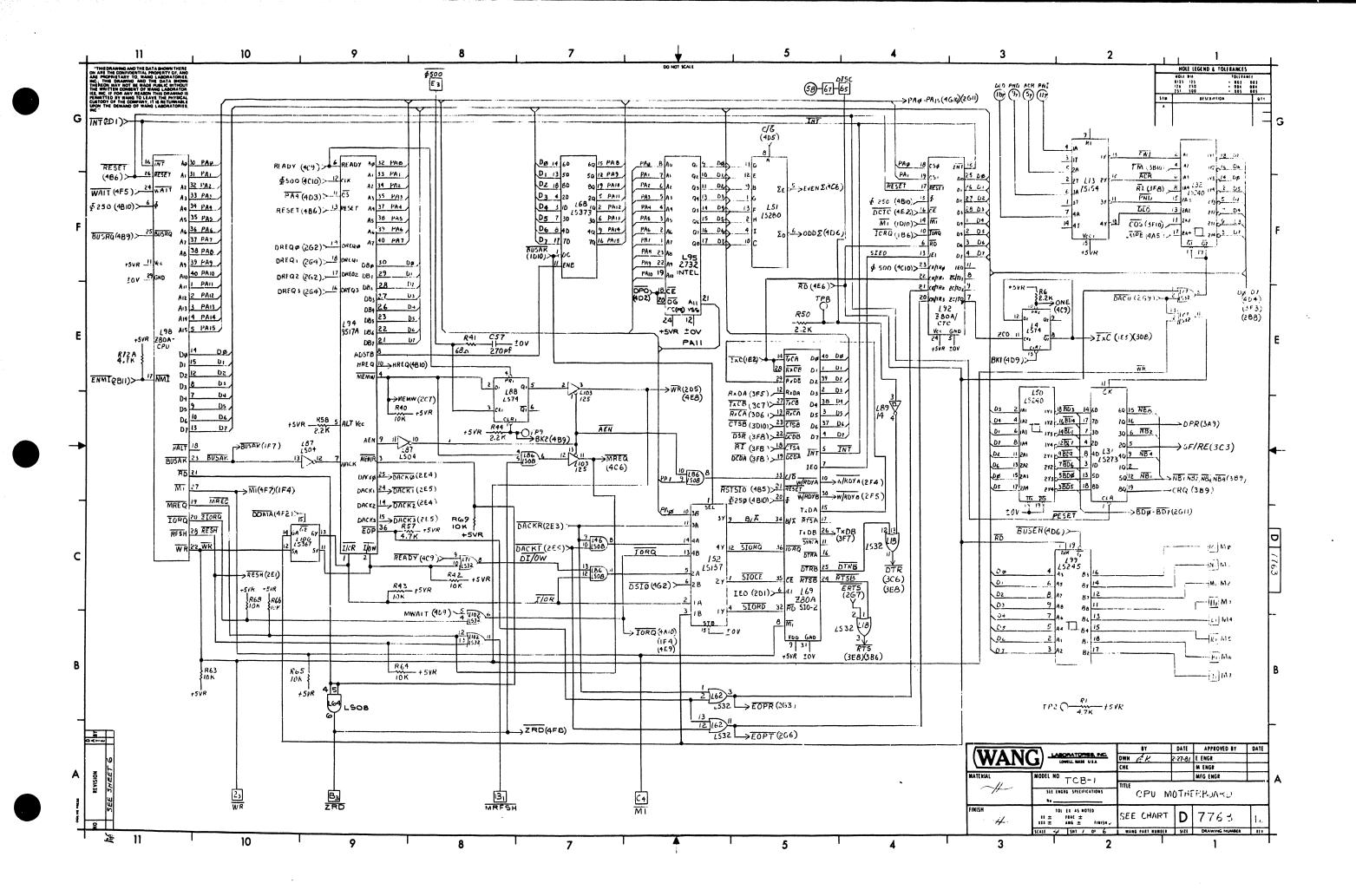

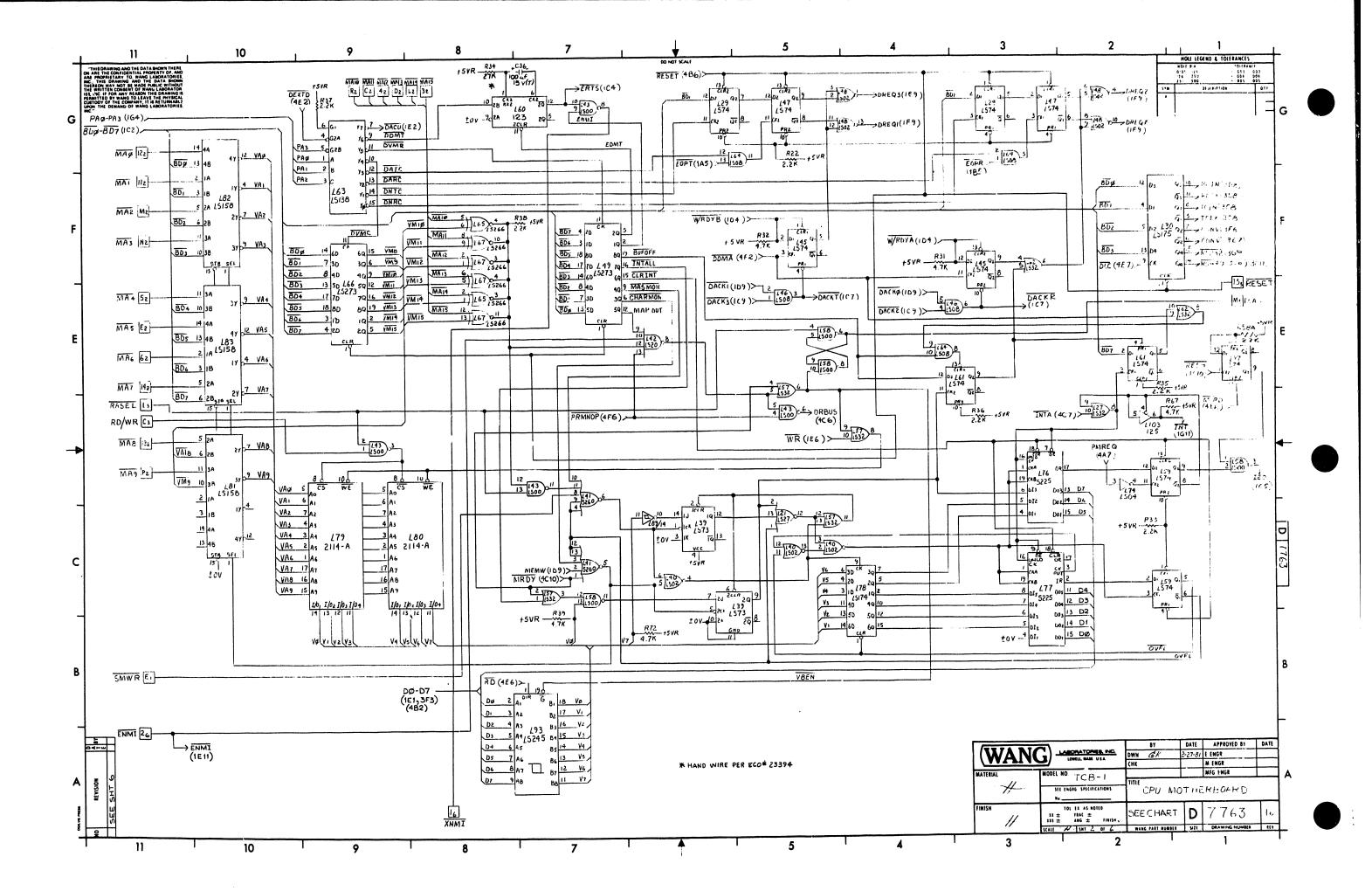

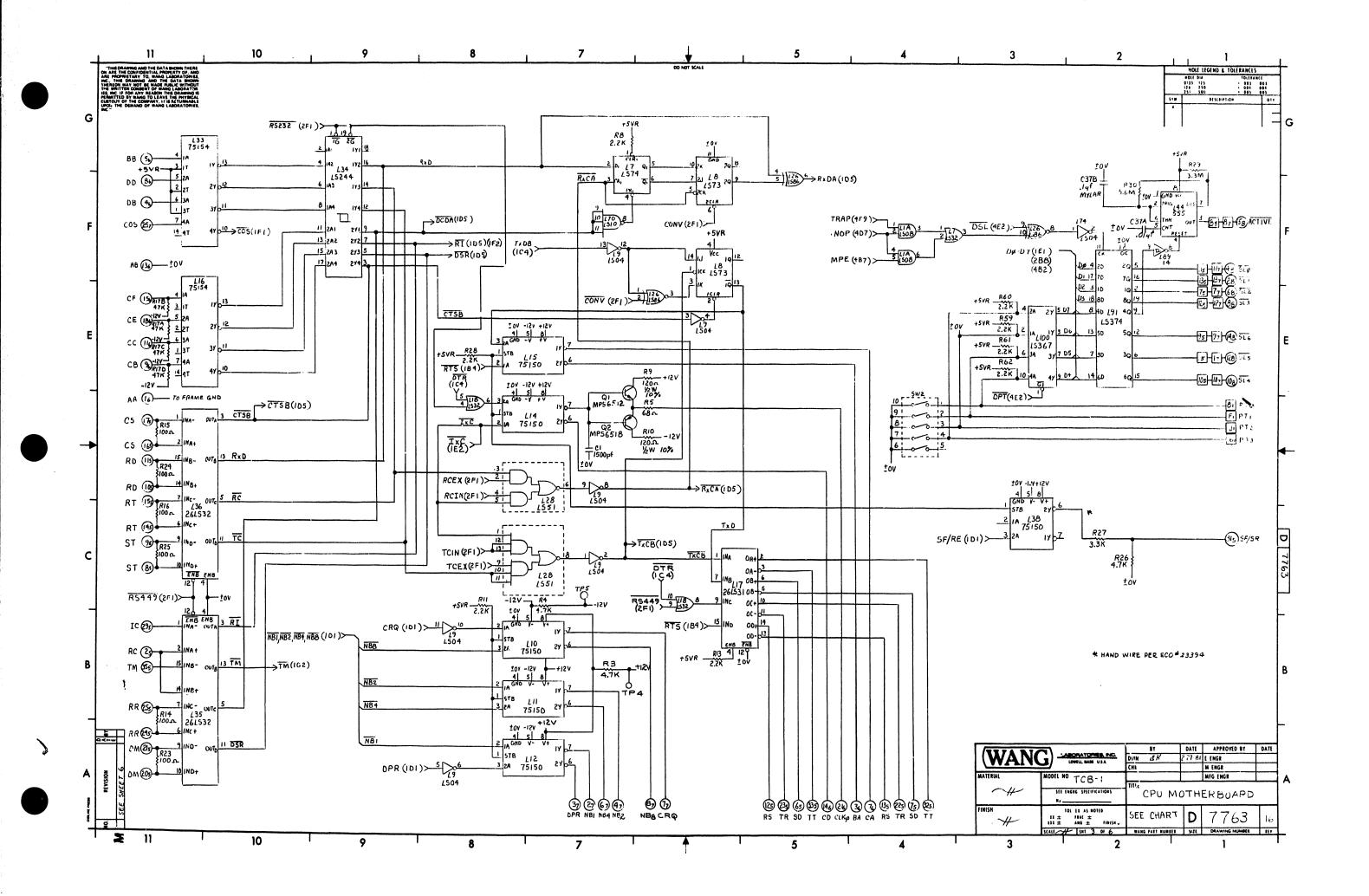

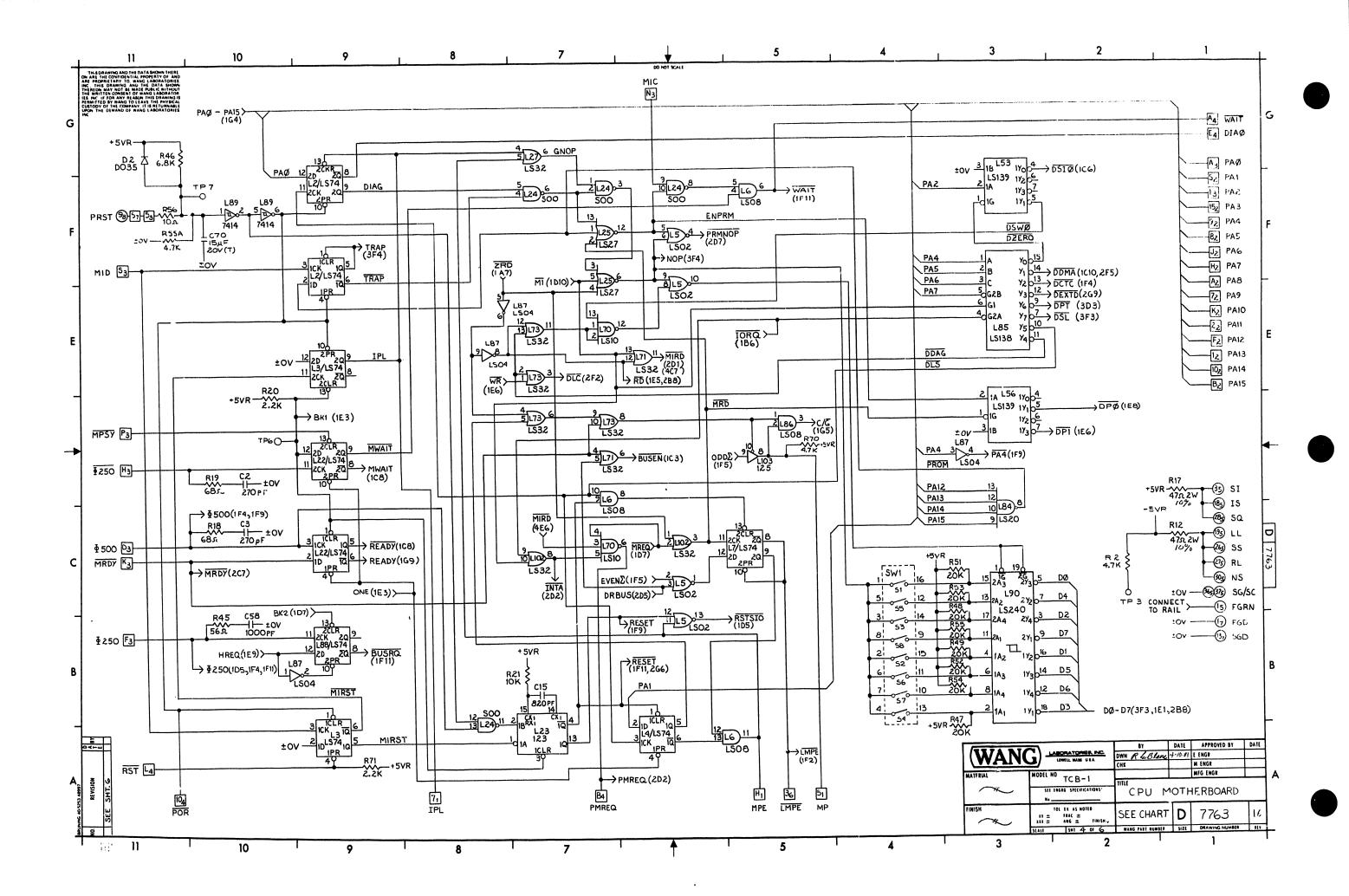

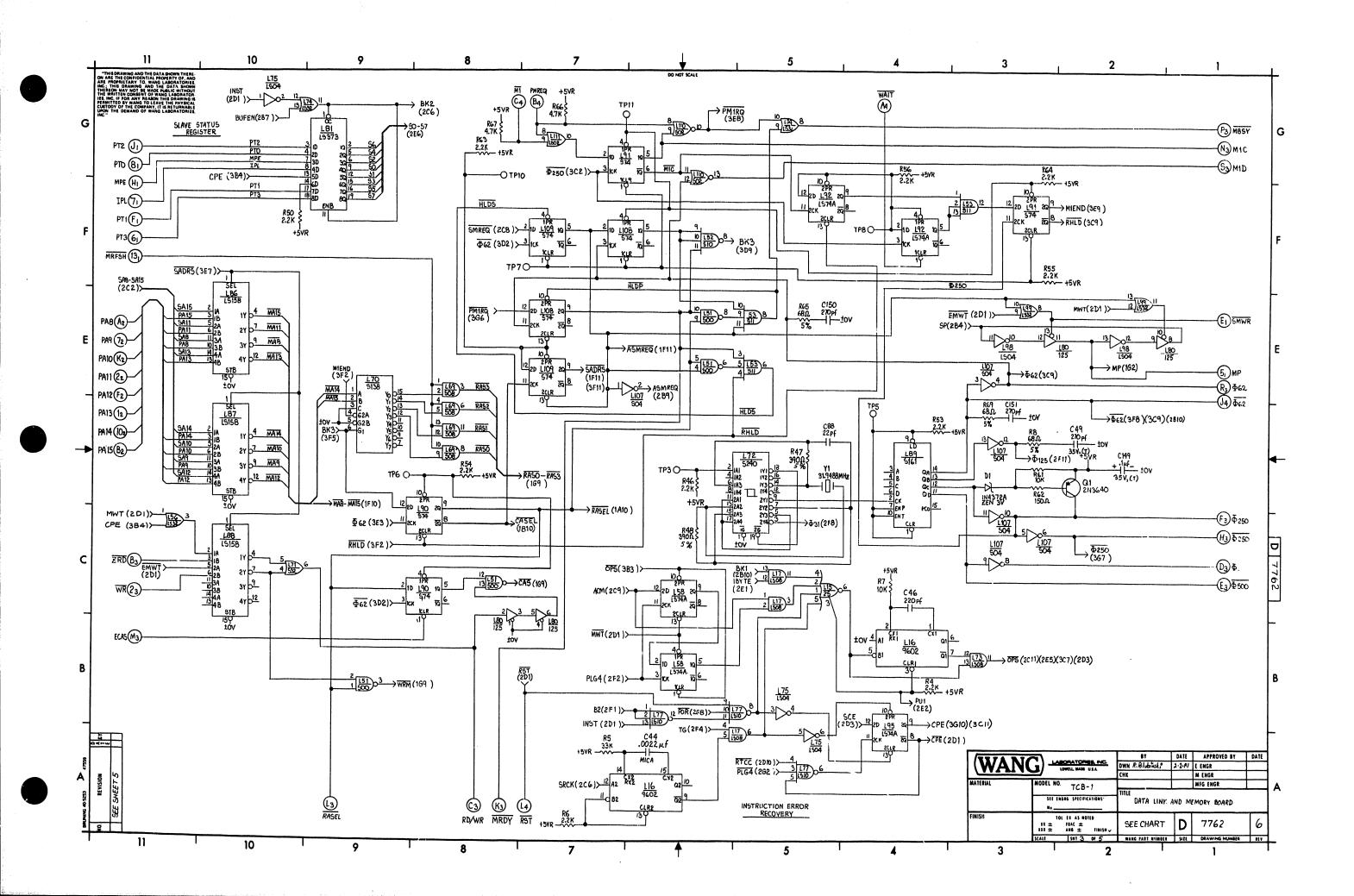

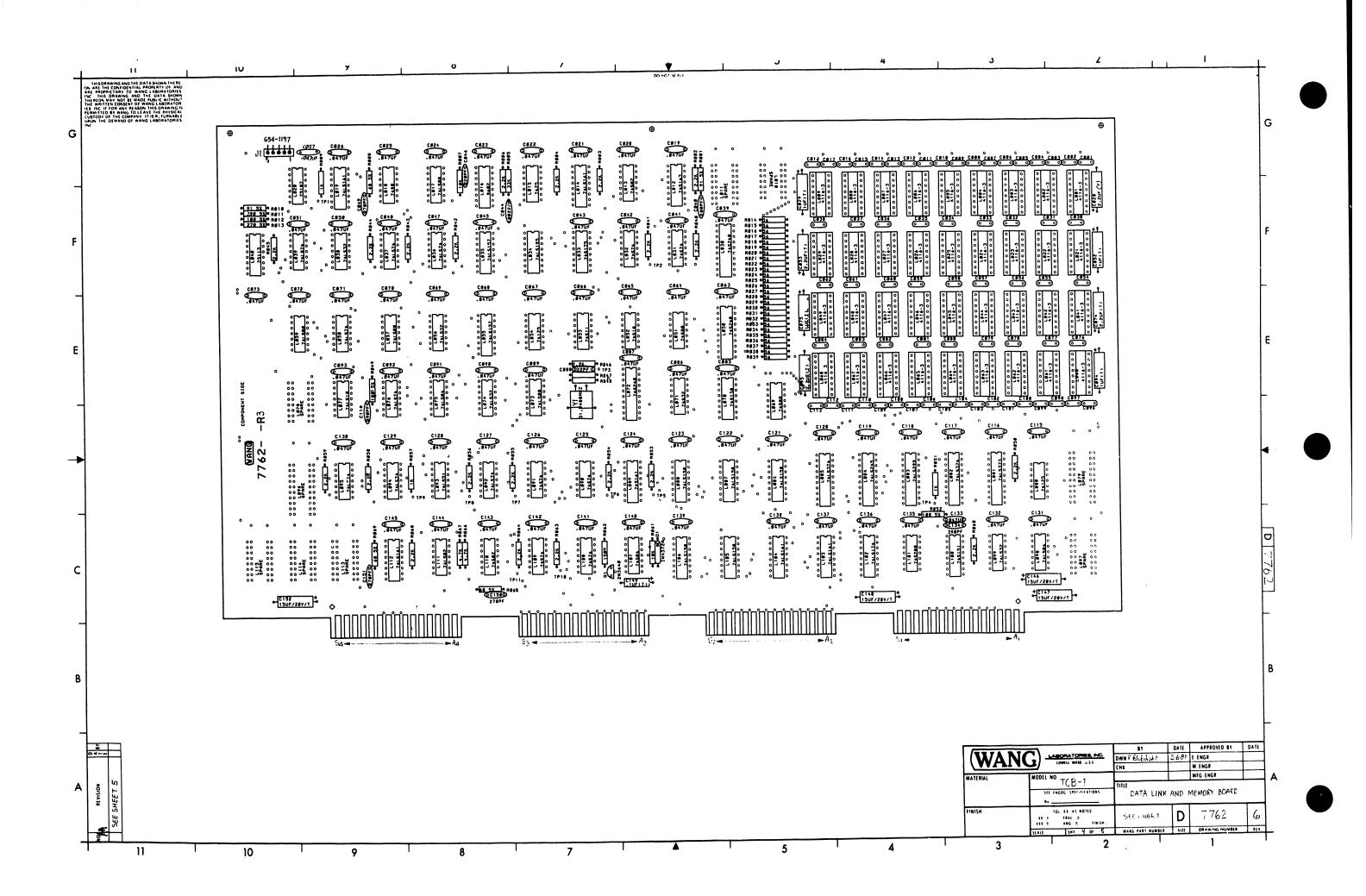

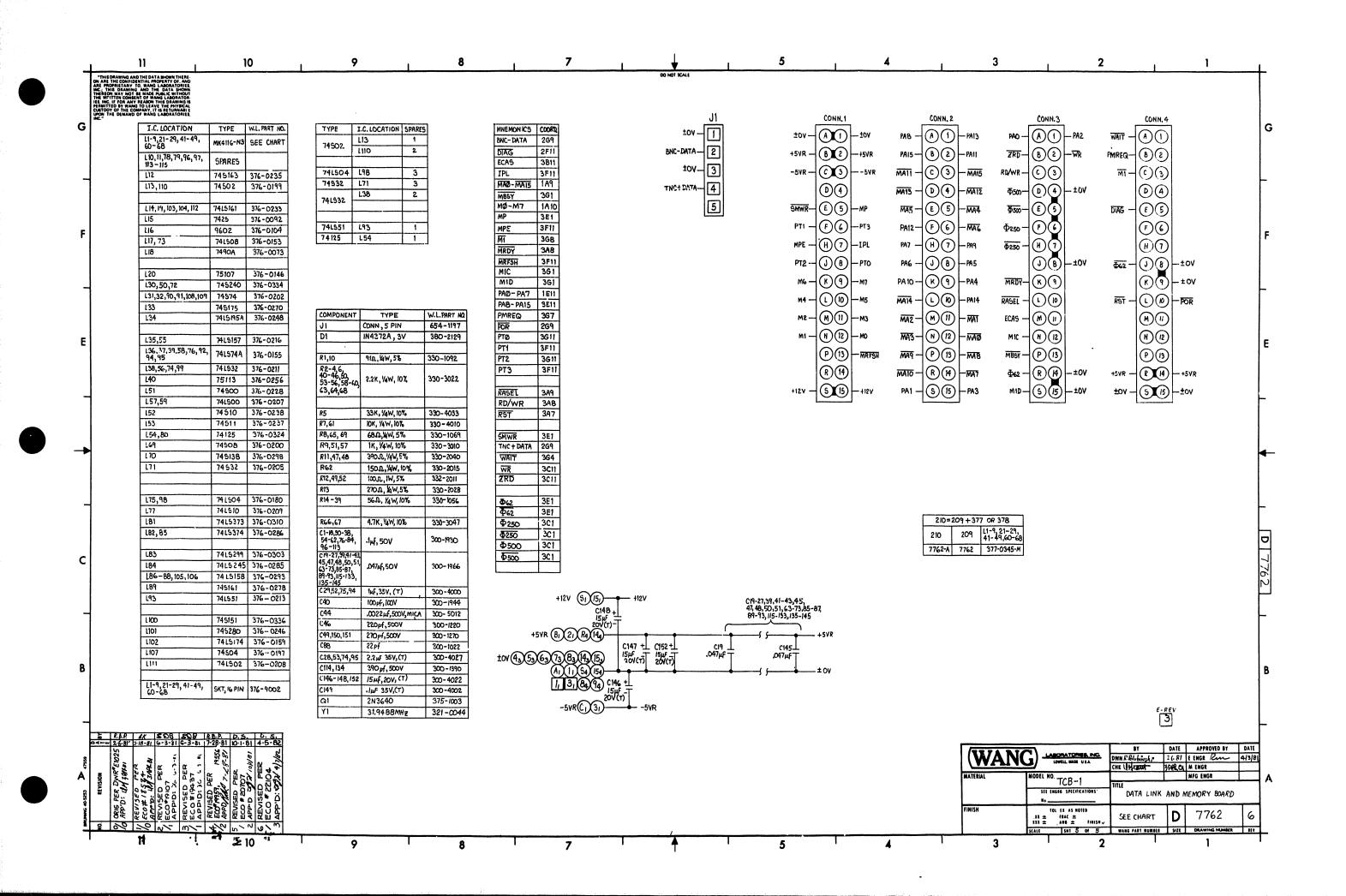

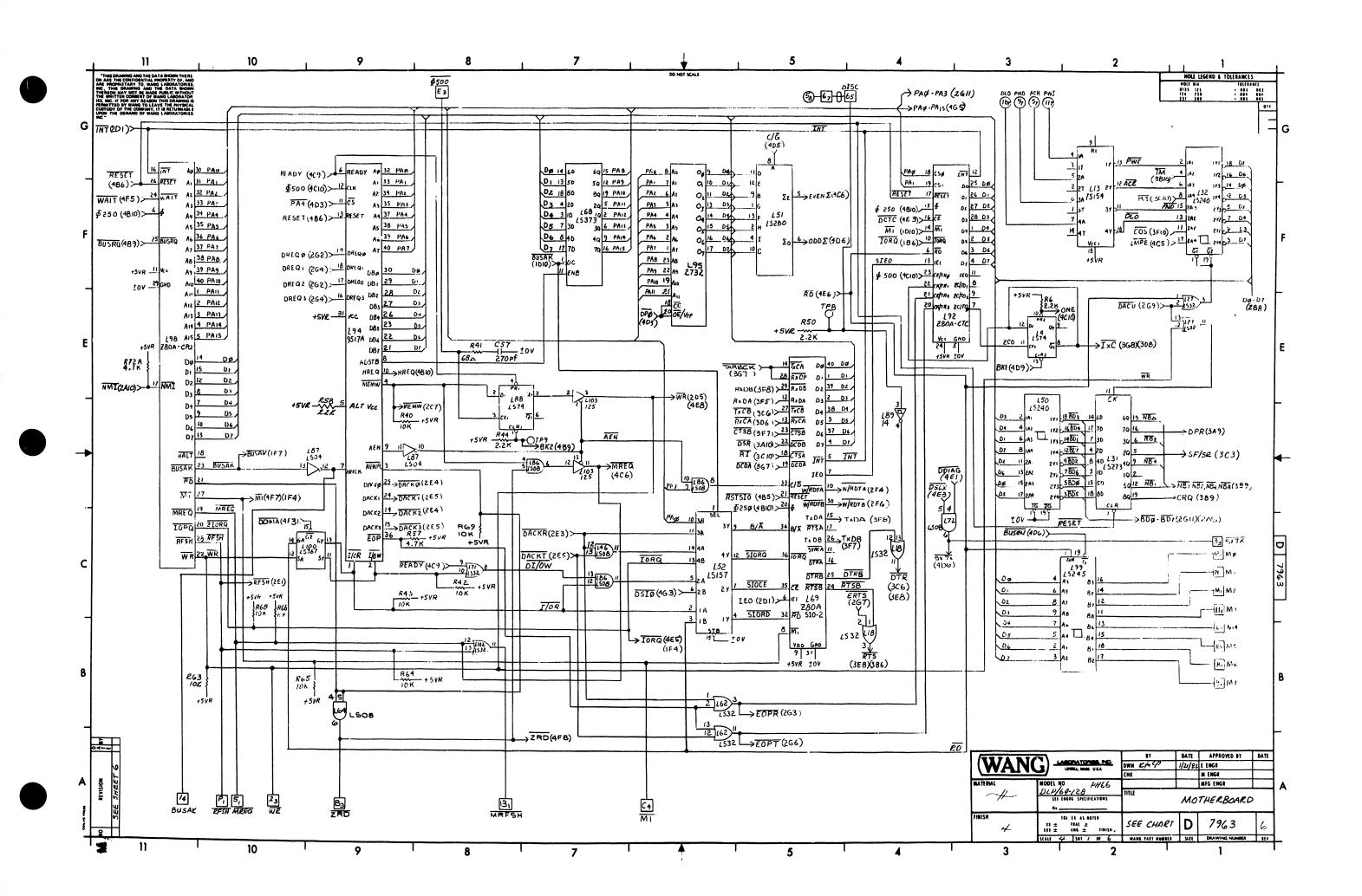

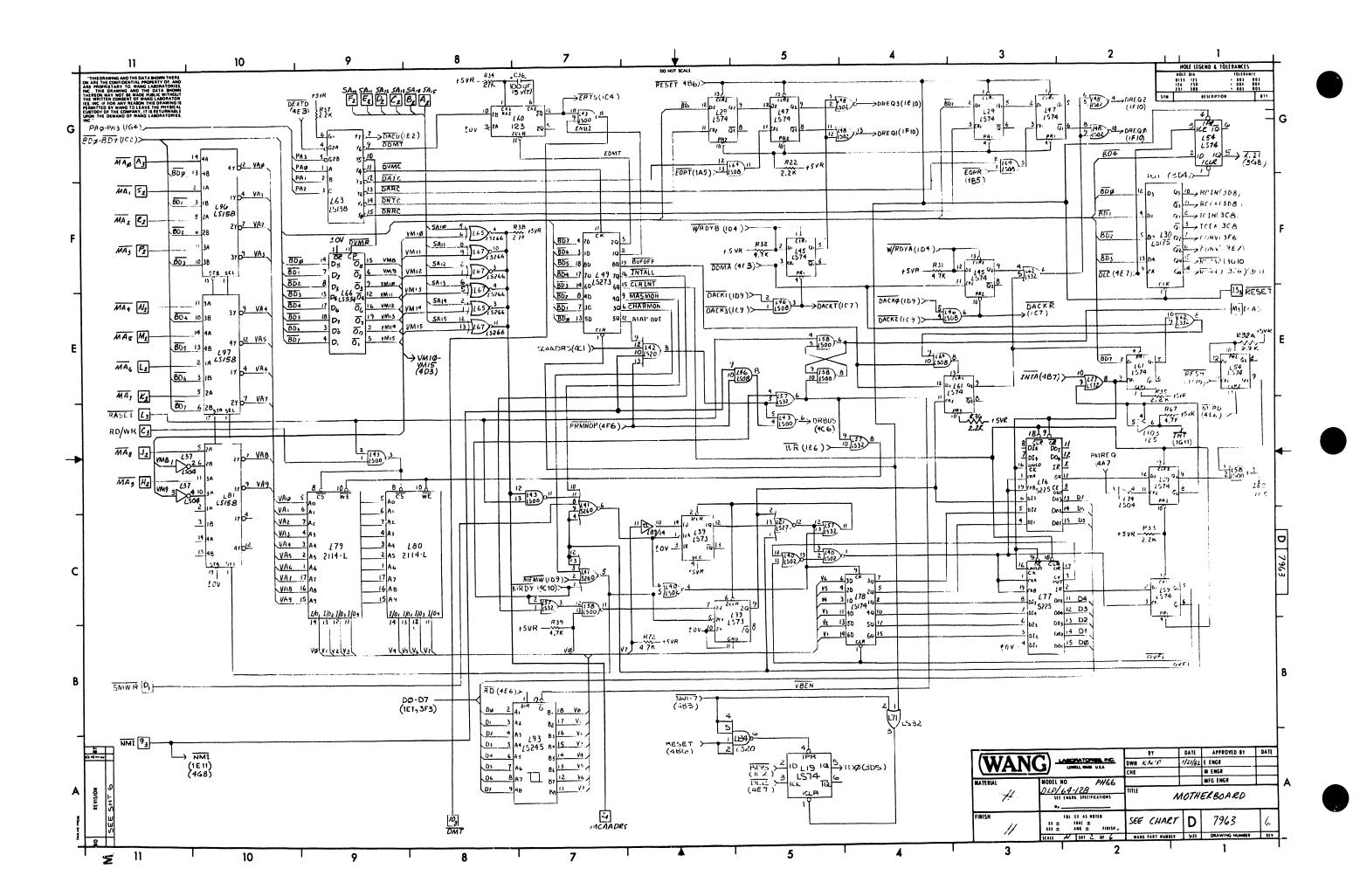

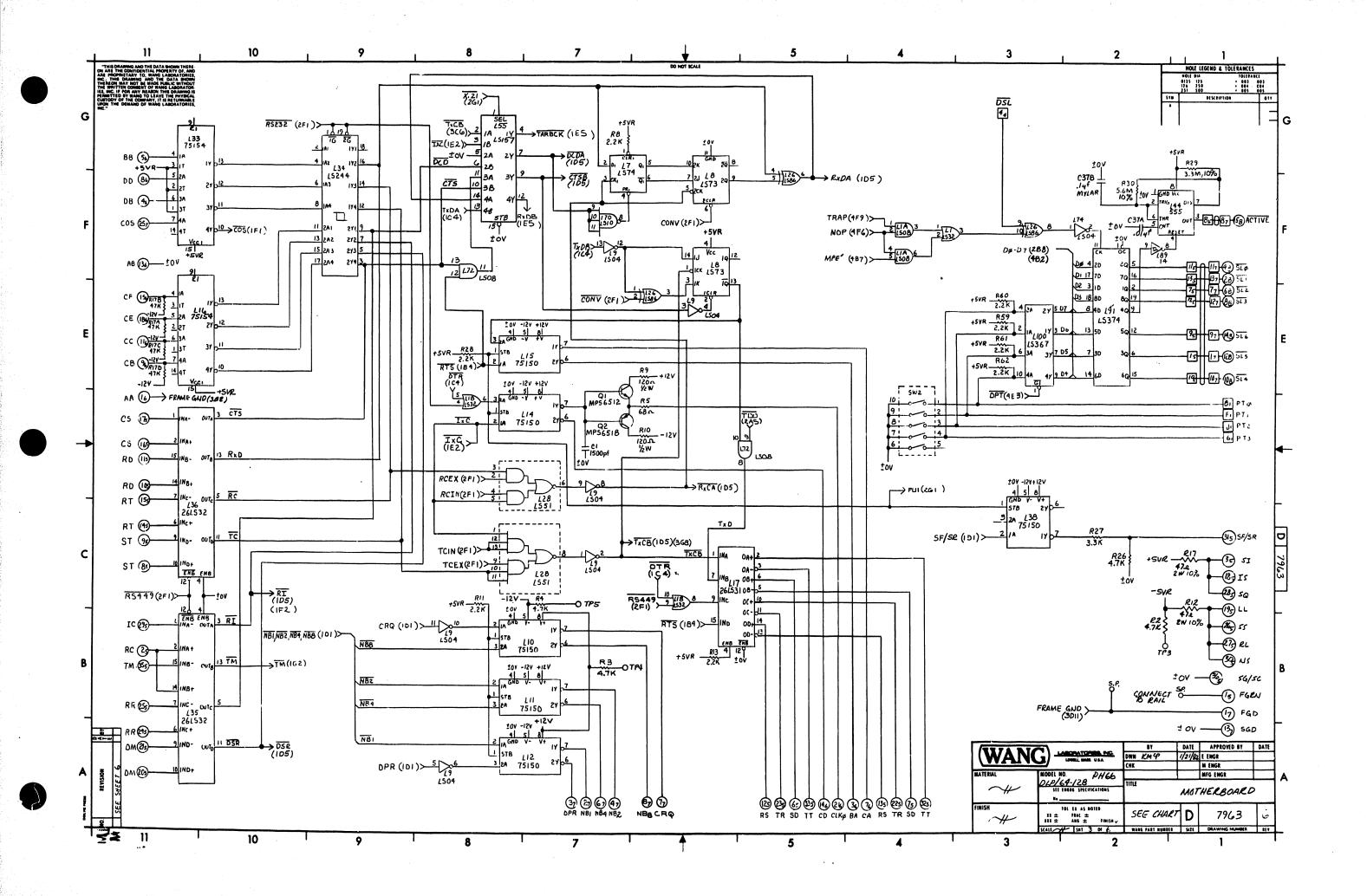

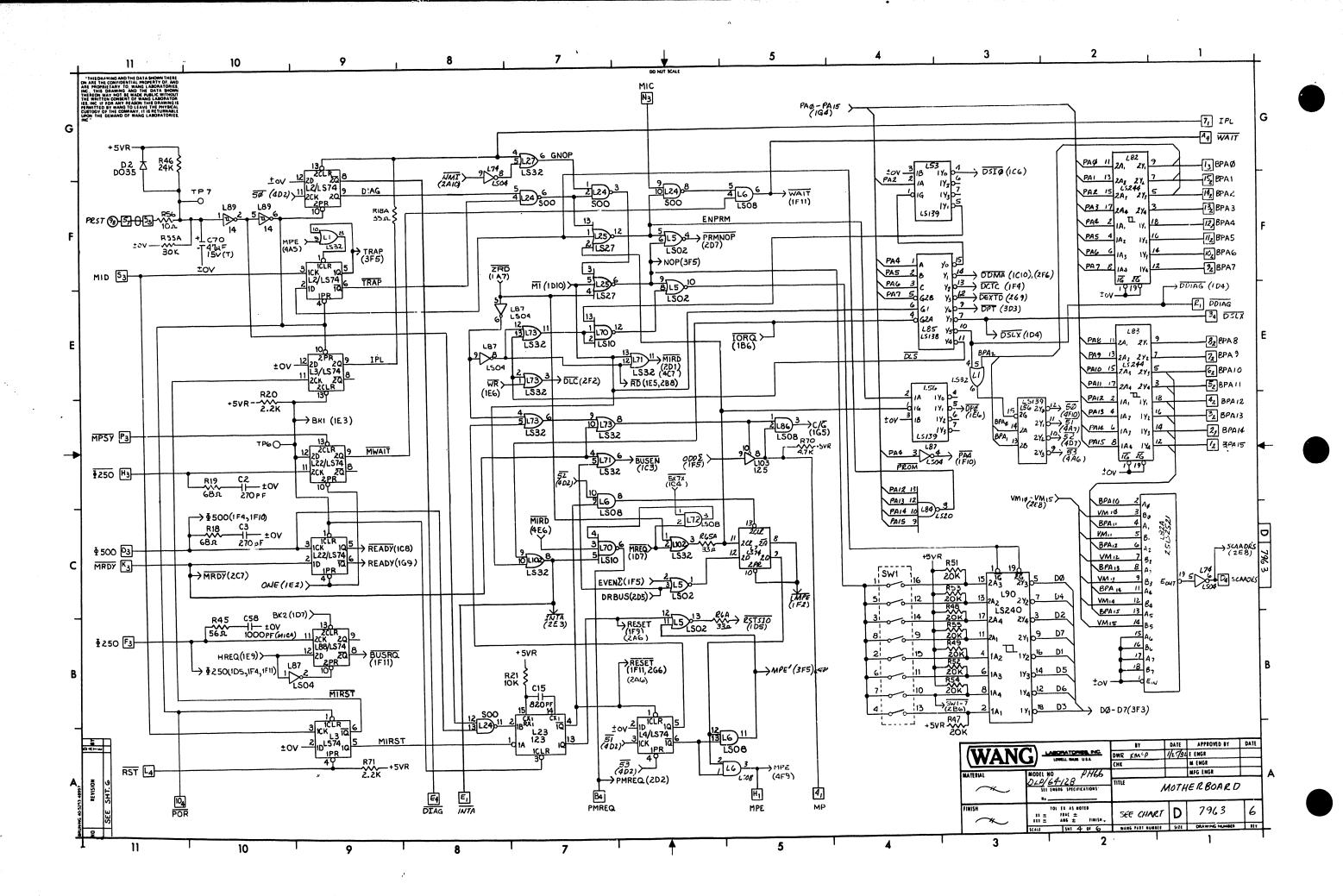

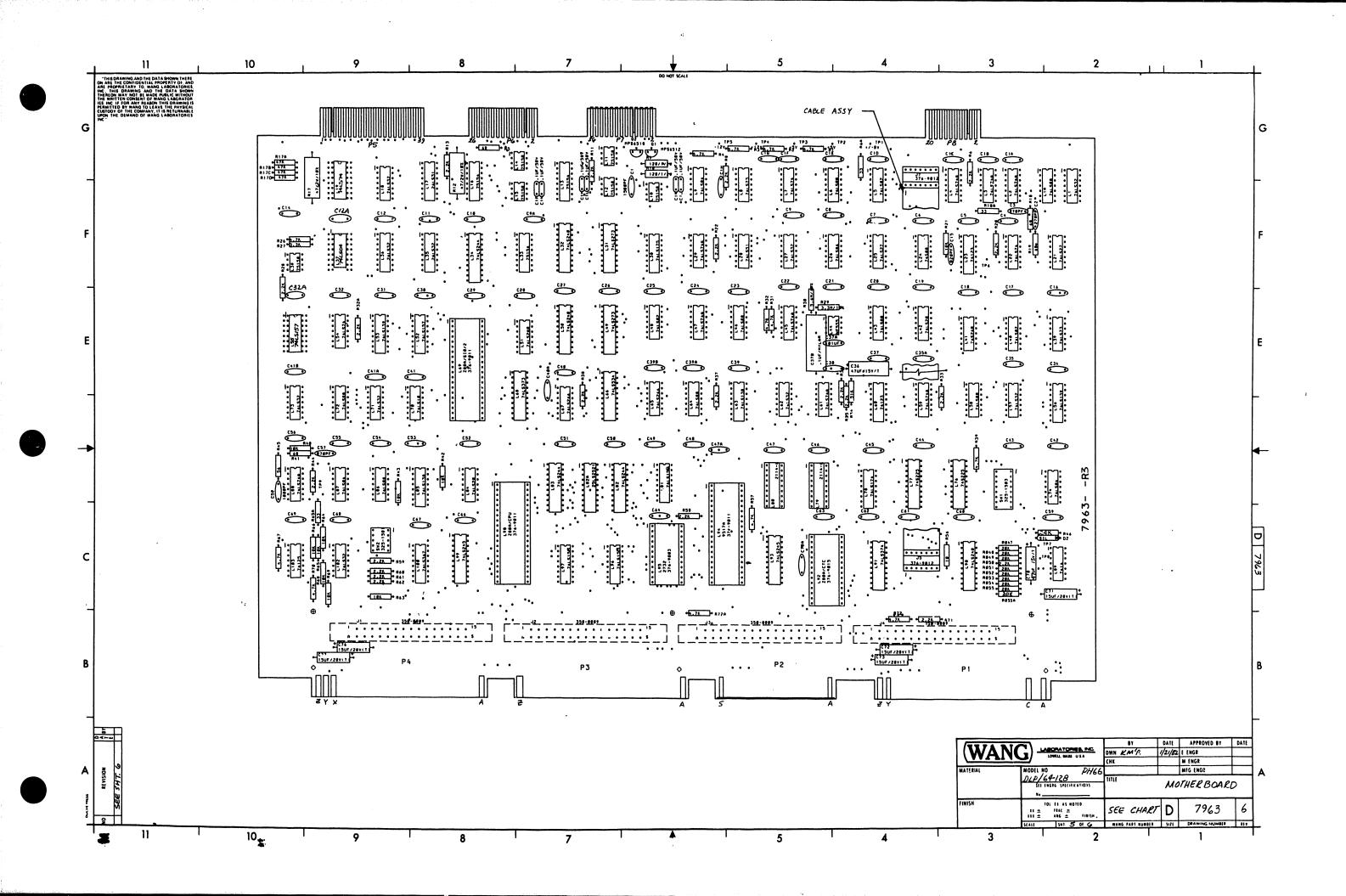

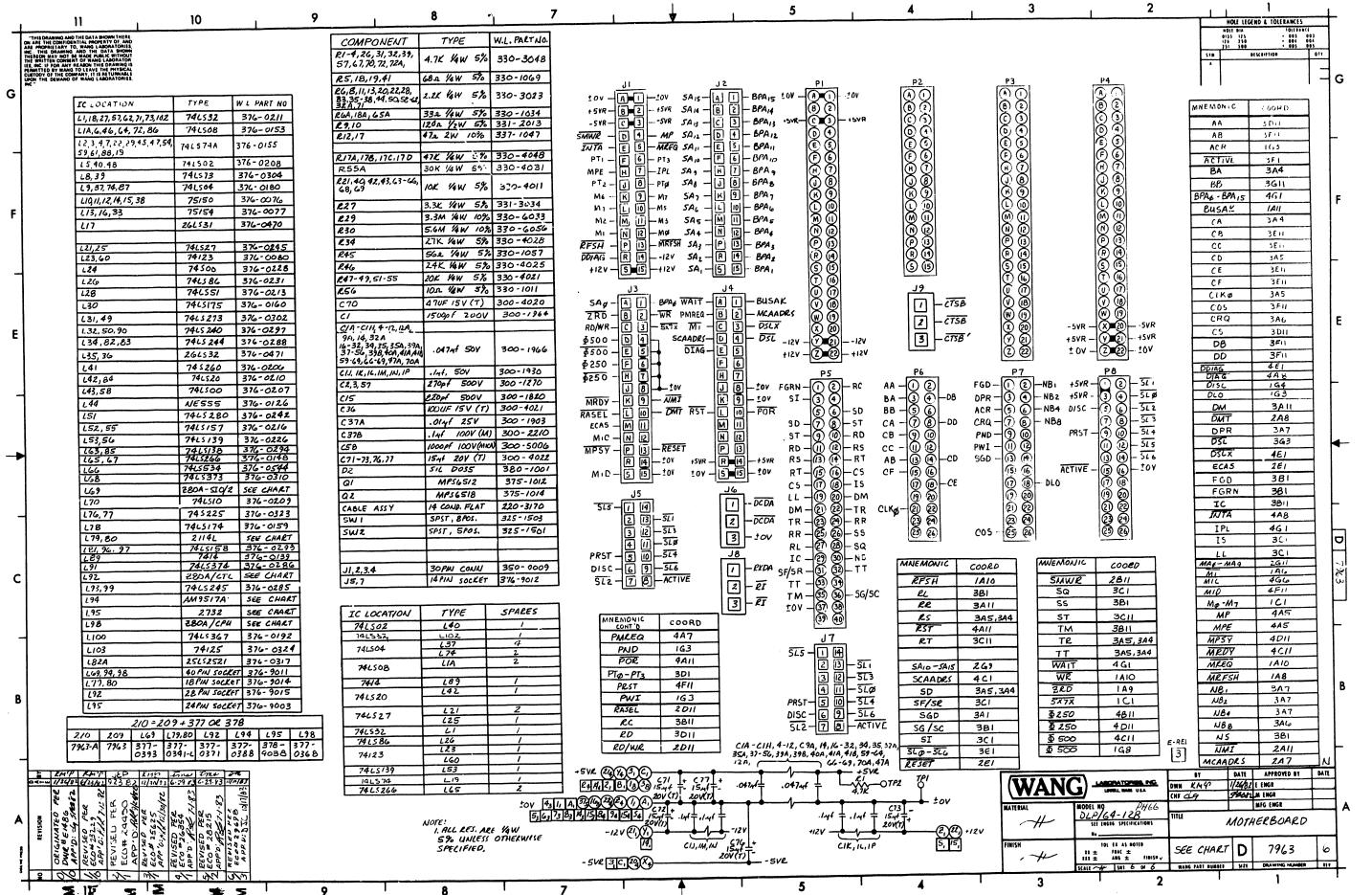

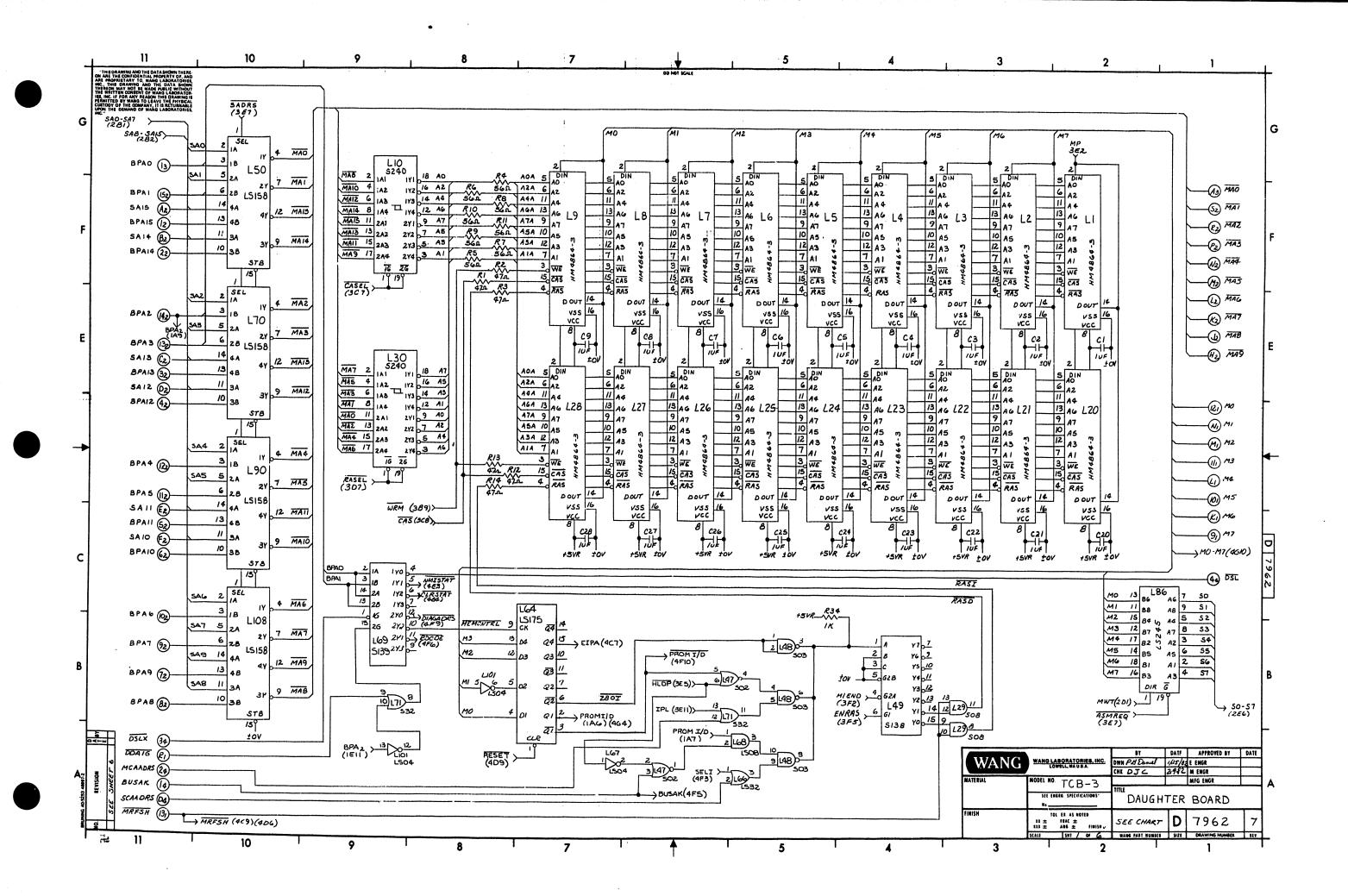

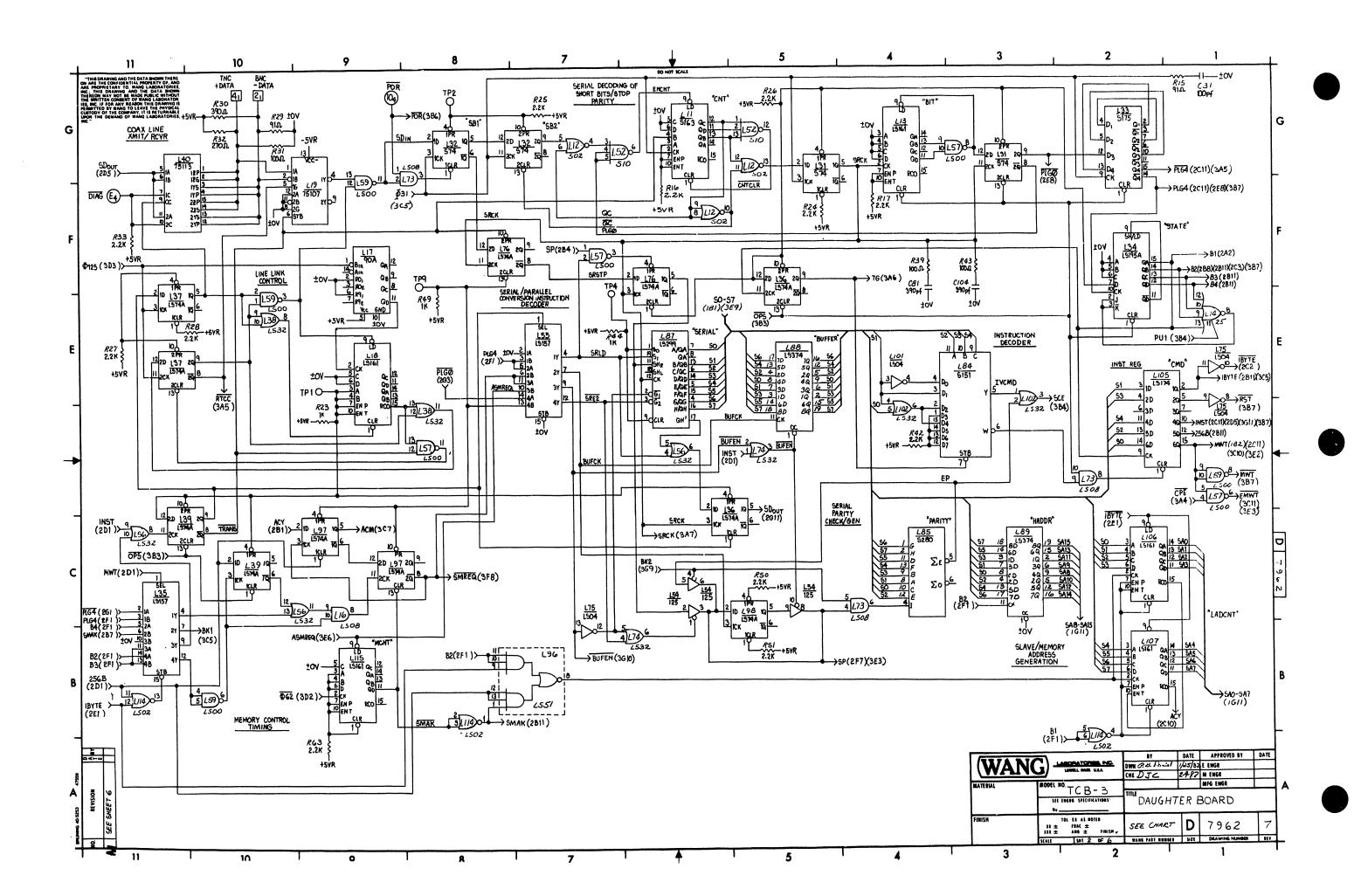

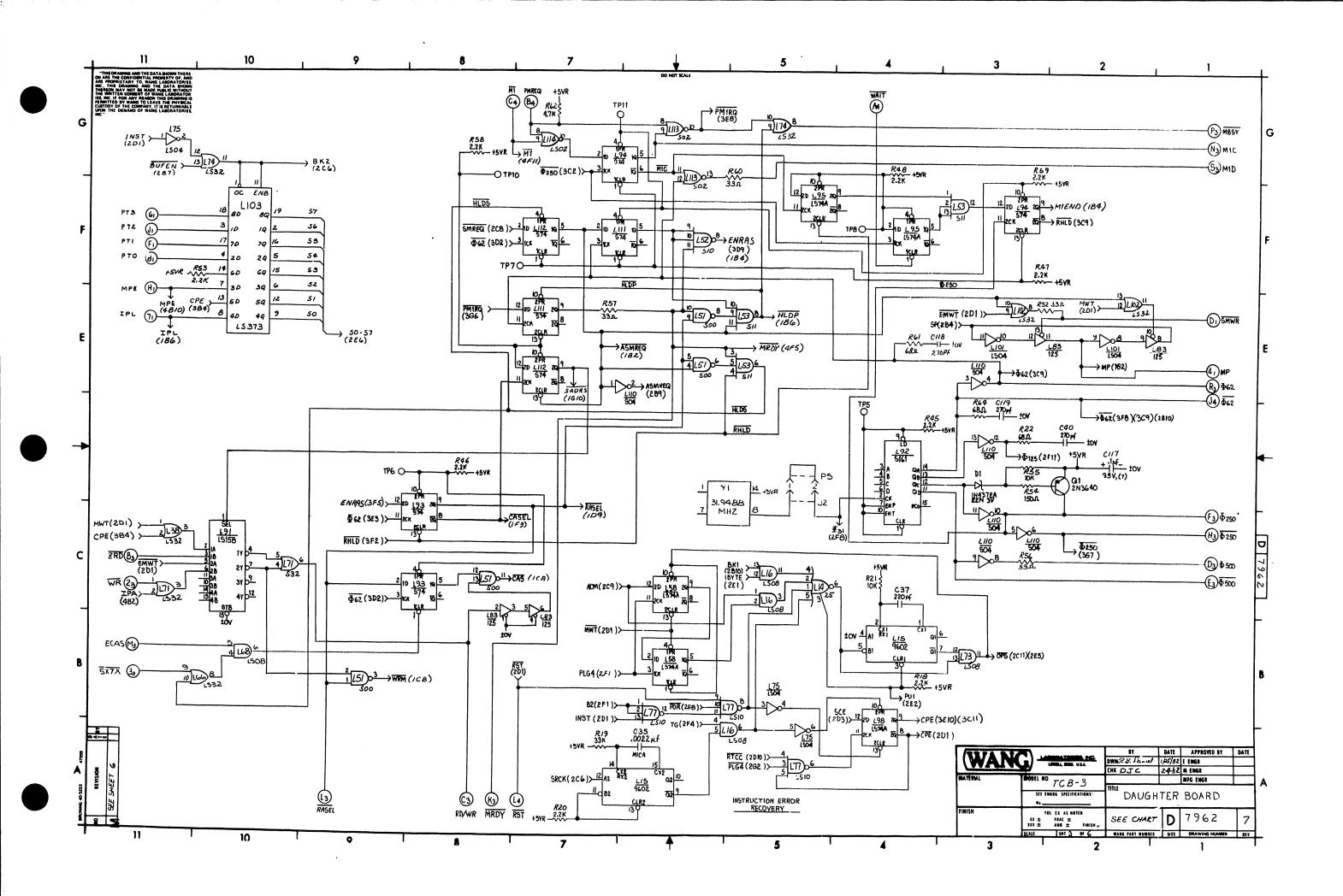

| CHAPTER 6                                             | SCHEMATICS                                                                                                                                                                                                                                                                                    |                                        |

| 6.1                                                   | Schematics                                                                                                                                                                                                                                                                                    | 6-1                                    |

| CHAPTER 7                                             | ILLUSTRATED PARTS BREAKDOWN                                                                                                                                                                                                                                                                   |                                        |

| 7.1                                                   | Parts List Breakdown                                                                                                                                                                                                                                                                          | 7-1                                    |

| CHAPTER 8                                             | TROUBLESHOOTING                                                                                                                                                                                                                                                                               |                                        |

| 8.1                                                   | Troubleshooting Flowcharts                                                                                                                                                                                                                                                                    | 8-1                                    |

| APPENDIX A                                            | A                                                                                                                                                                                                                                                                                             |                                        |

| X.21 Inter                                            | 2-C Interface rface terface terface                                                                                                                                                                                                                                                           | A-3<br>A-7                             |

### ILLUSTRATIONS

| FIGURE | TITLE                                                                                        |      |

|--------|----------------------------------------------------------------------------------------------|------|

| 2-1    | Functional Block Diagram                                                                     | 2-1  |

| 2-2    | Processor Section Block Diagram                                                              | 2-5  |

| 2-3    | Data Link Section Block Diagram                                                              | 2-11 |

| 2-4    | TCB-1 Memory Control Section                                                                 | 2-14 |

| 2-5    | DLP 64/128 Memory Control Section                                                            | 2-15 |

| 2-6    | RAM Chip Layout                                                                              | 2-16 |

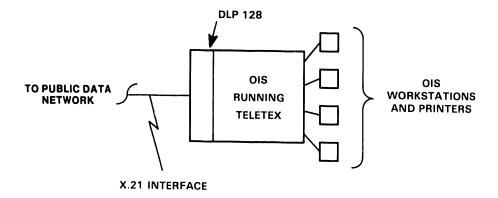

| 3-1    | 3270 Emulation Operation                                                                     | 3-2  |

| 3-2    | Asynchronous/Bisynchronous Operation                                                         | 3-3  |

| 3-3    | Remote Wangnet (WSN) Point-to-Point                                                          | 3-4  |

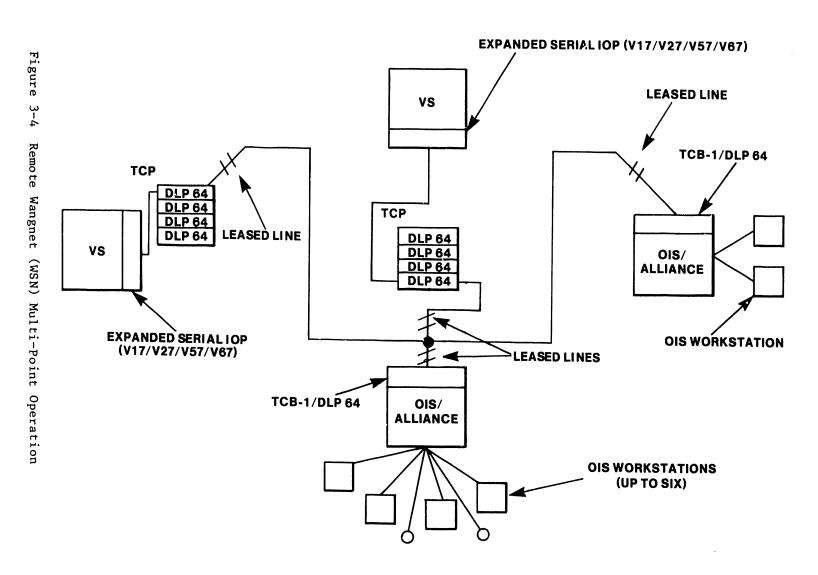

| 3-4    | Remote Wangnet (WSN) Multi-Point Operation                                                   | 3-5  |

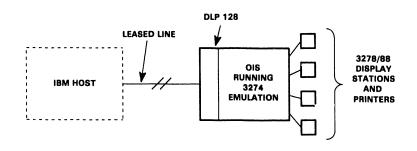

| 3-5    | SNA 3274/3777 Emulation                                                                      | 3-6  |

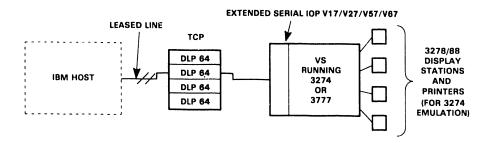

| 3-6    | Teletex Operation                                                                            | 3-7  |

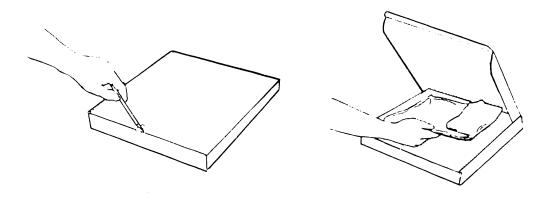

| 4-1    | Unpacking the TC Controller                                                                  | 4-1  |

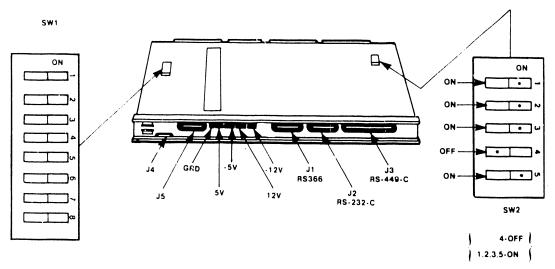

| 4-2    | Line Address and Device Address Switch<br>Settings                                           | 4-2  |

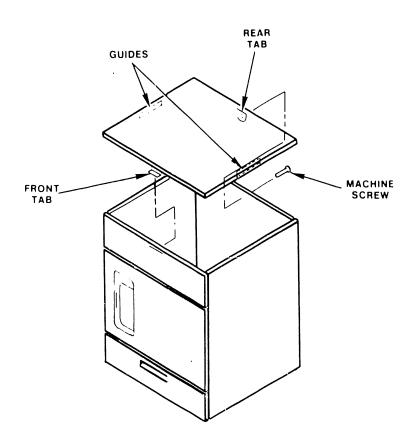

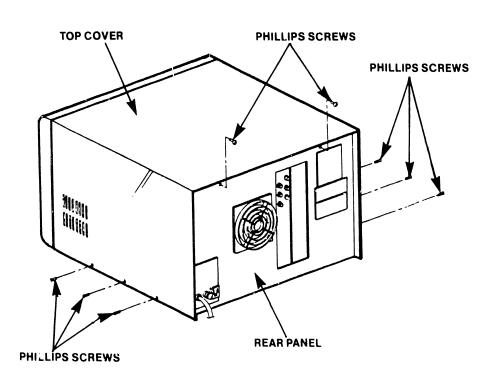

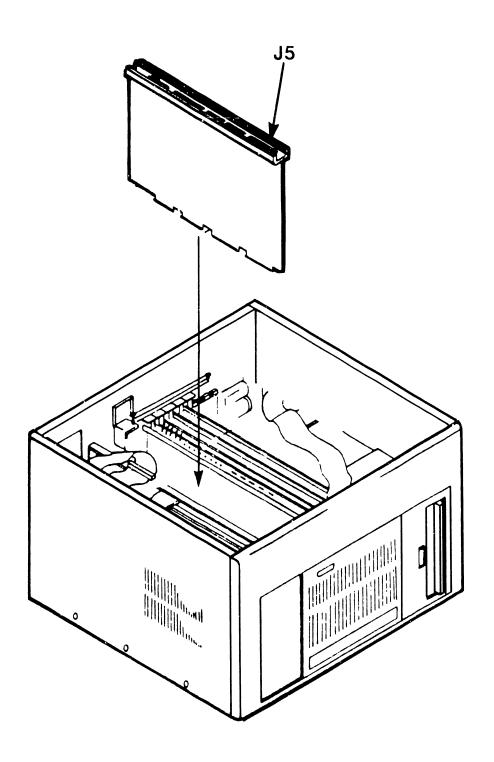

| 4-3    | Top Cover Removal/Installation                                                               | 4-6  |

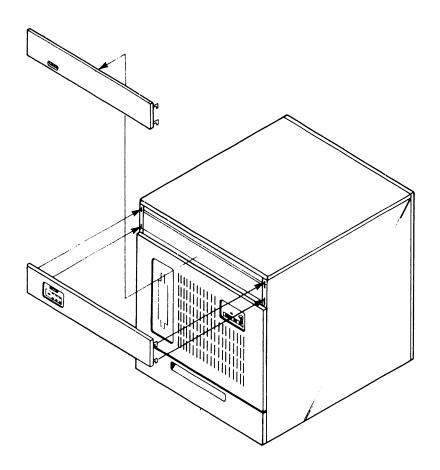

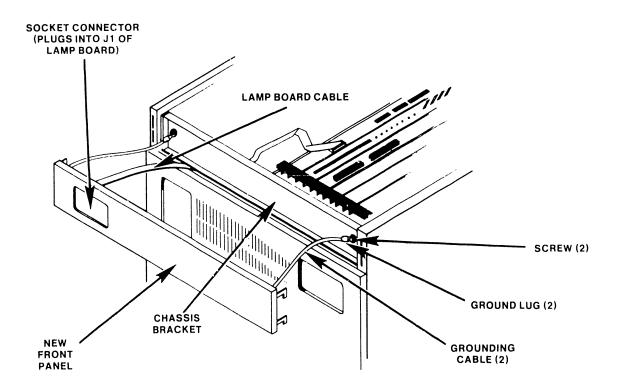

| 4-4    | Upper Front Panel Removal/Installation                                                       | 4-7  |

| 4-5    | New OIS 140/145 Front Panel Installation                                                     | 4-8  |

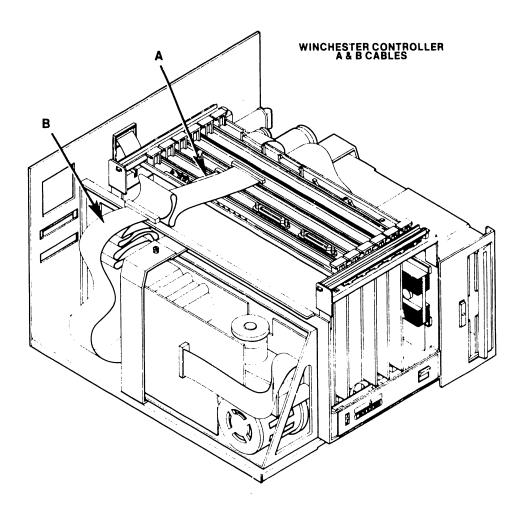

| 4-6    | TC Controller Installation (140/145 Masters)                                                 | 4-10 |

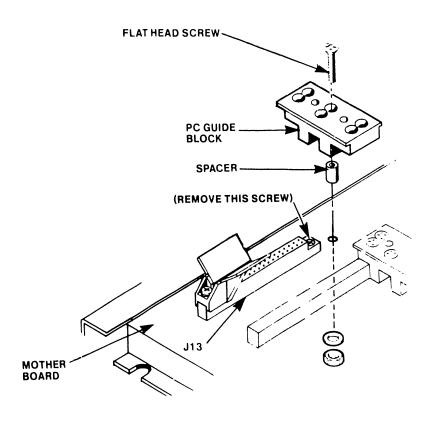

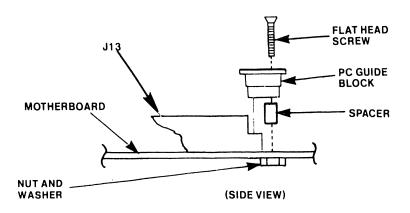

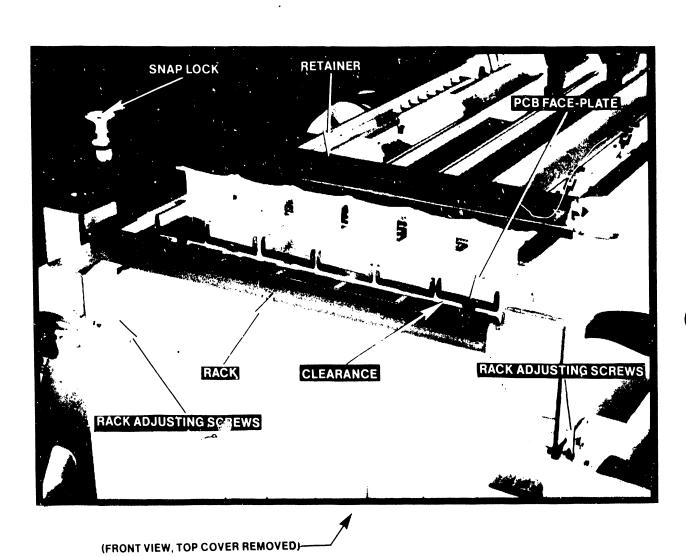

| 4-7    | PC Guide Block Installation (140/145 Masters)                                                | 4-12 |

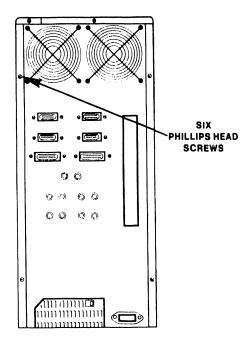

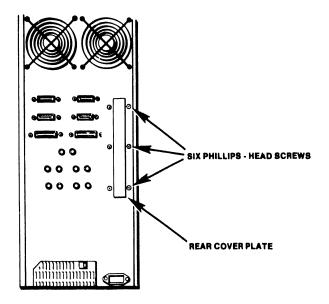

| 4-8    | Rear Cover Plate Removal/TC Rear Panel<br>Installation (140/145)                             | 4-15 |

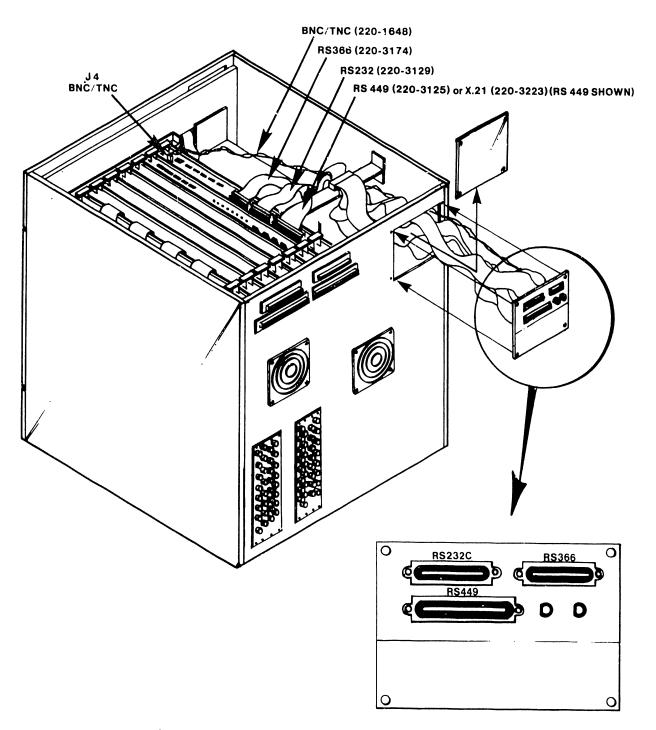

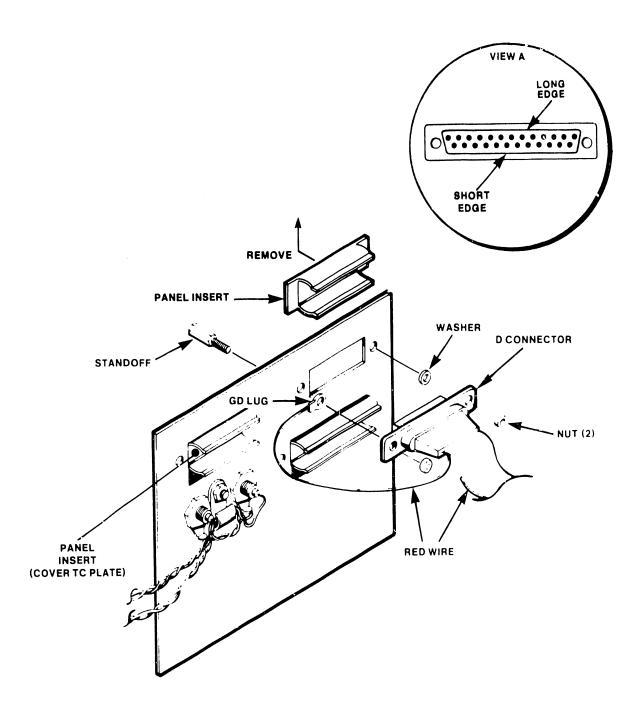

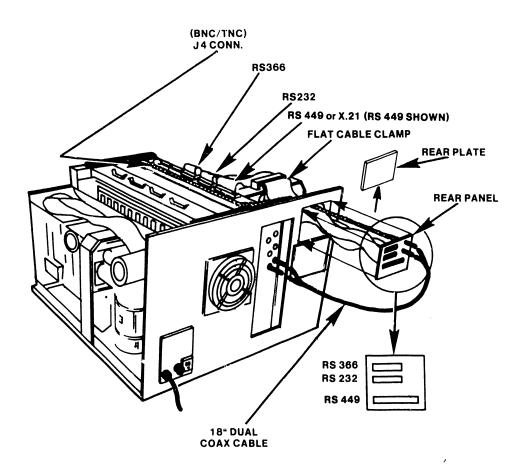

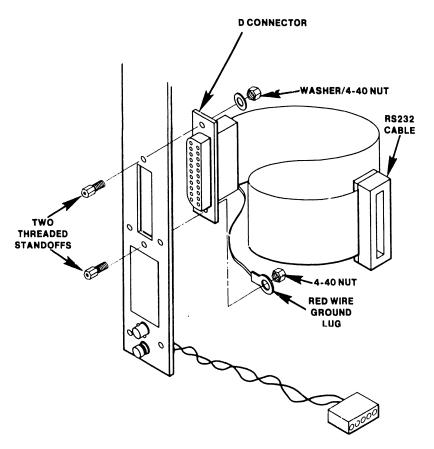

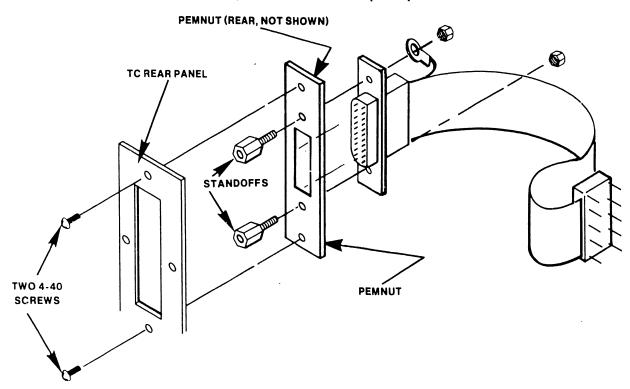

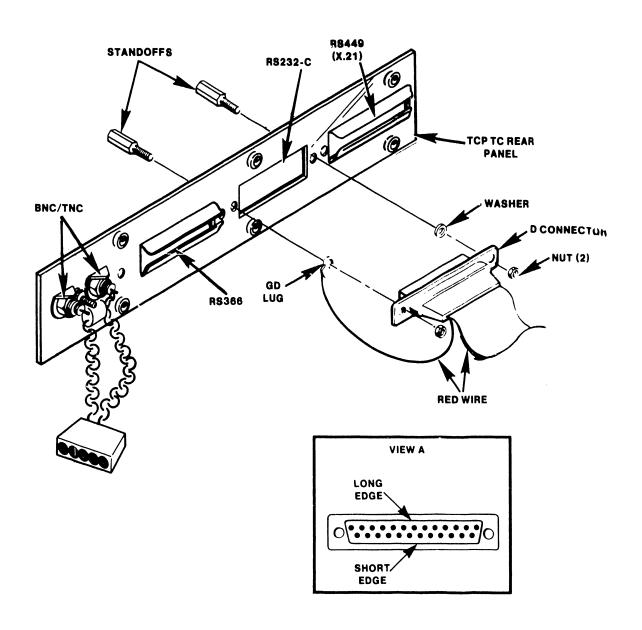

| 4-9    | RS-232 C or RS-366 Interface Cable Installation (Installed from inner side of TC rear panel) | 4-17 |

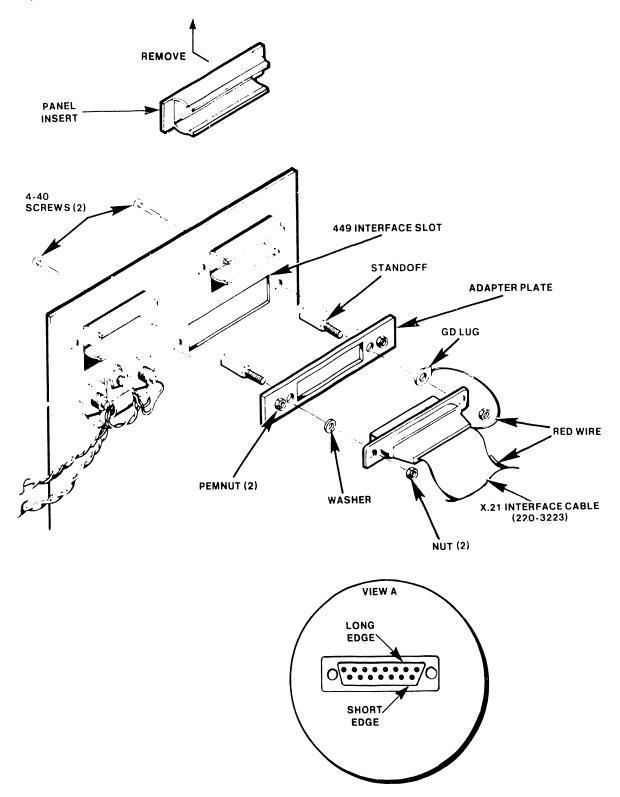

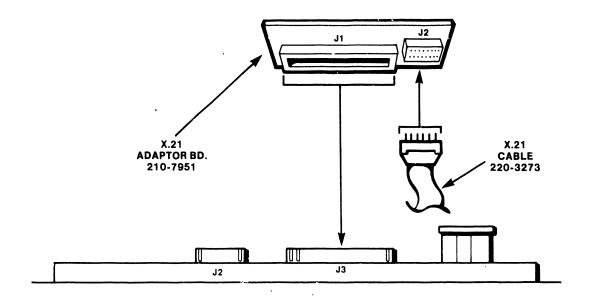

| 4-10   | X.21 Cable Installation (Internal side)                                                      | 4-18 |

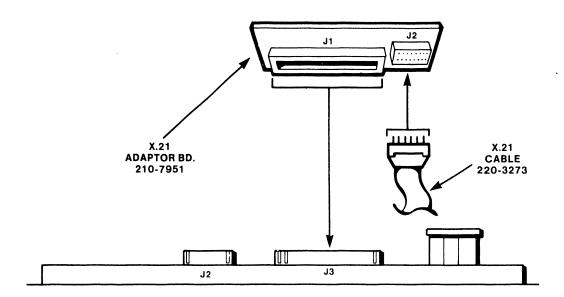

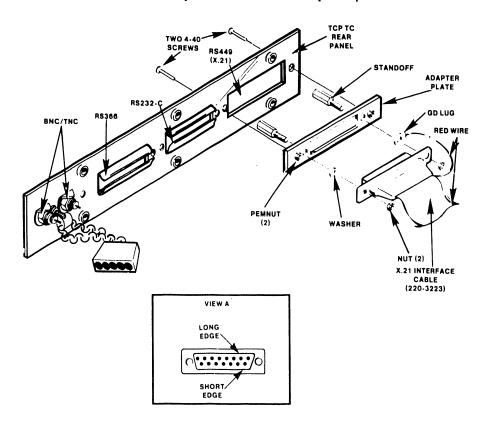

| 4-11   | X.21 Interface Adaptor Board Installation                                                    | 4-20 |

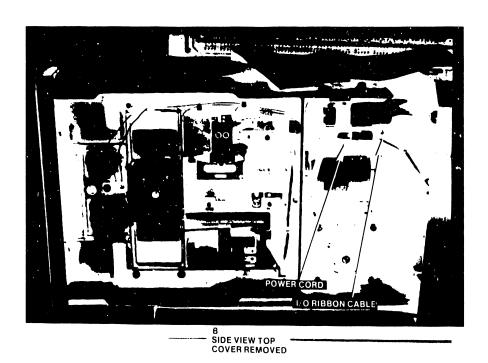

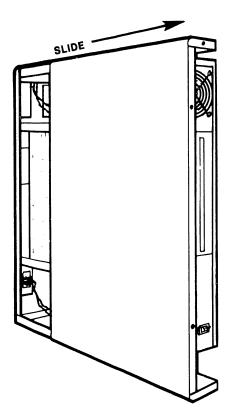

| 4-12   | OIS 105/115/125A/130A Top Cover Removal/Installation                                         | 4-23 |

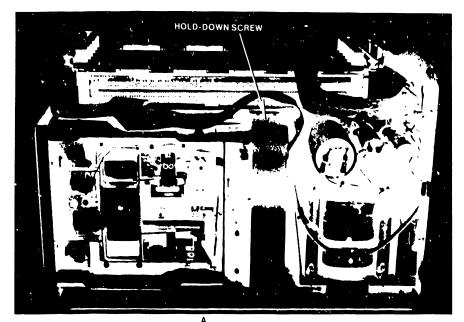

| 4-13   | Removing/Installing the Diskette Drive                                                       | 4-24 |

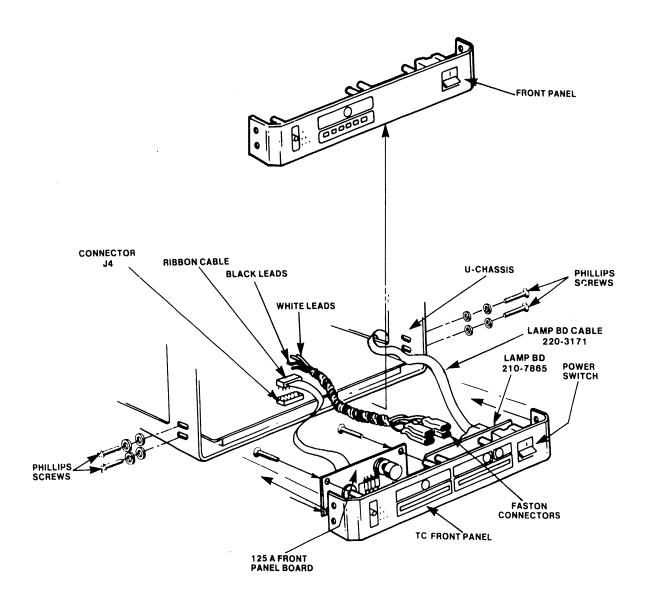

| 4-14   | Front Panel Removal/Installation                                                             | 4-26 |

| 4-15   | Ribbon Cable Connections                                                                     | 4-28 |

| 4-16   | PCB Removal/Installation (105/115/125A/130A) Masters                                         | 4-30 |

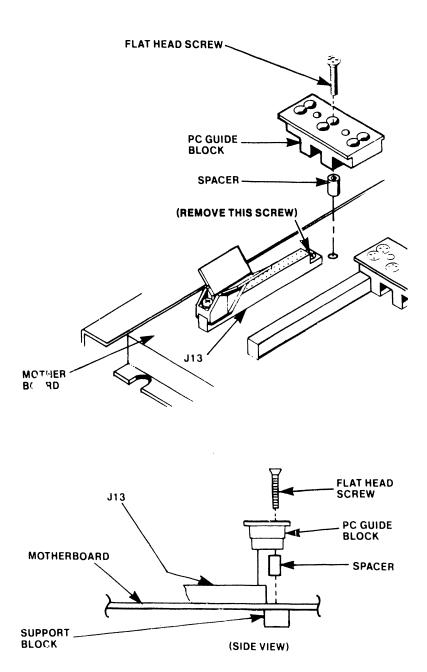

| 4-17   | PC Guide Block Installation<br>(105/115/125A/130A) Only                                      | 4-31 |

| 4-18   | TC Controller Installation into 105/115/125A/130A Masters                                    | 4-33 |

| 4-19   | Rear Cover Plate Removal                                                                     | 4-35 |

| 4-20   | 40/50 Master Rear Panel Removal                                                              | 4-40 |

| 4-21   | Side Cover Removal                                                                           | 4-40 |

| 4-22   | Rear Cover Plate Removal                                                                     | 4-42 |

| 4-23   | RS-232 C or RS-366 Interface Cable Installation (Installed from inner side of TC Rear Panel) | 4-42 |

| 4-24   | X.21 Interface Cable Installation                                                            | 4-43 |

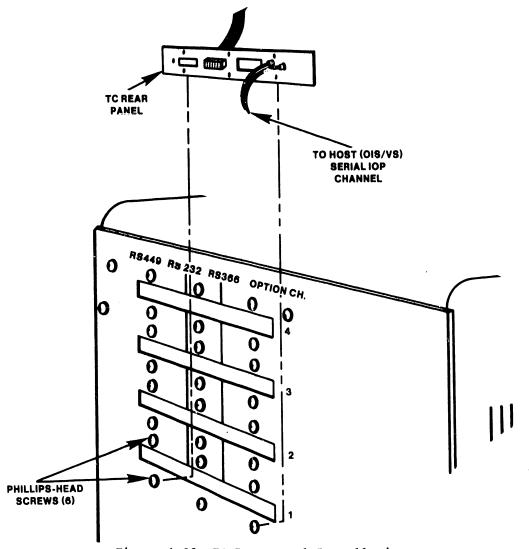

| 4-25   | TC Rear Panel Installation                                                                   | 4-44 |

| FIGURE | TITLE                                                 |      |  |

|--------|-------------------------------------------------------|------|--|

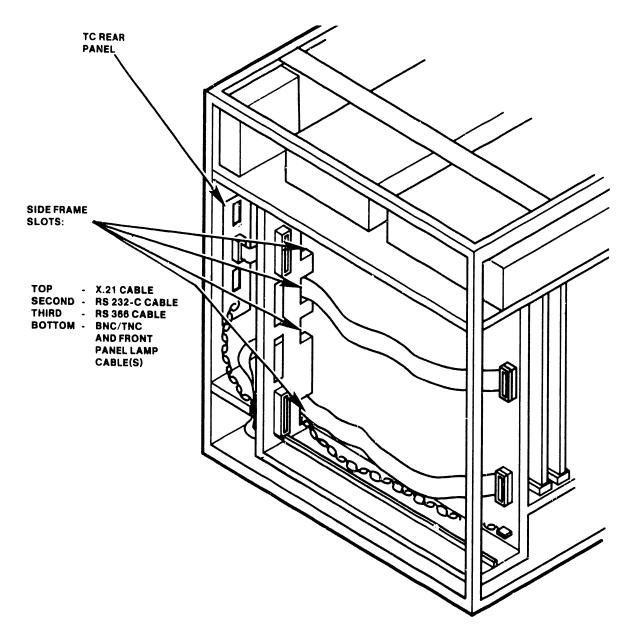

| 4-26   | Side Frame Slots                                      | 4-45 |  |

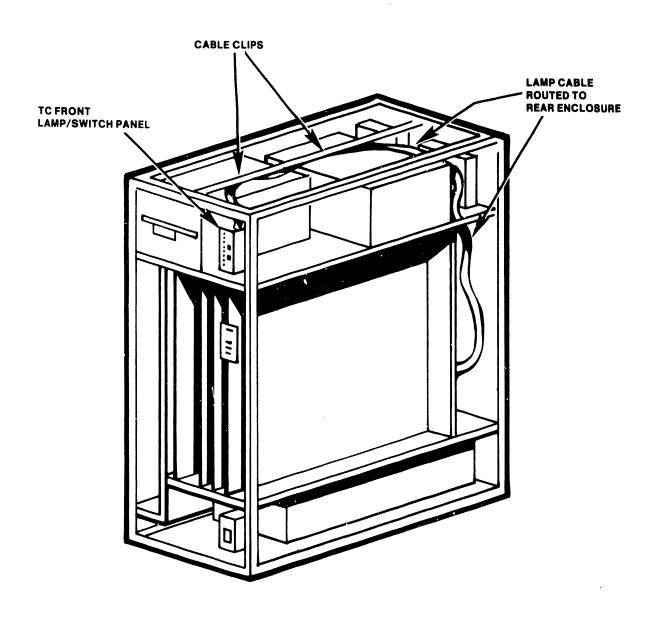

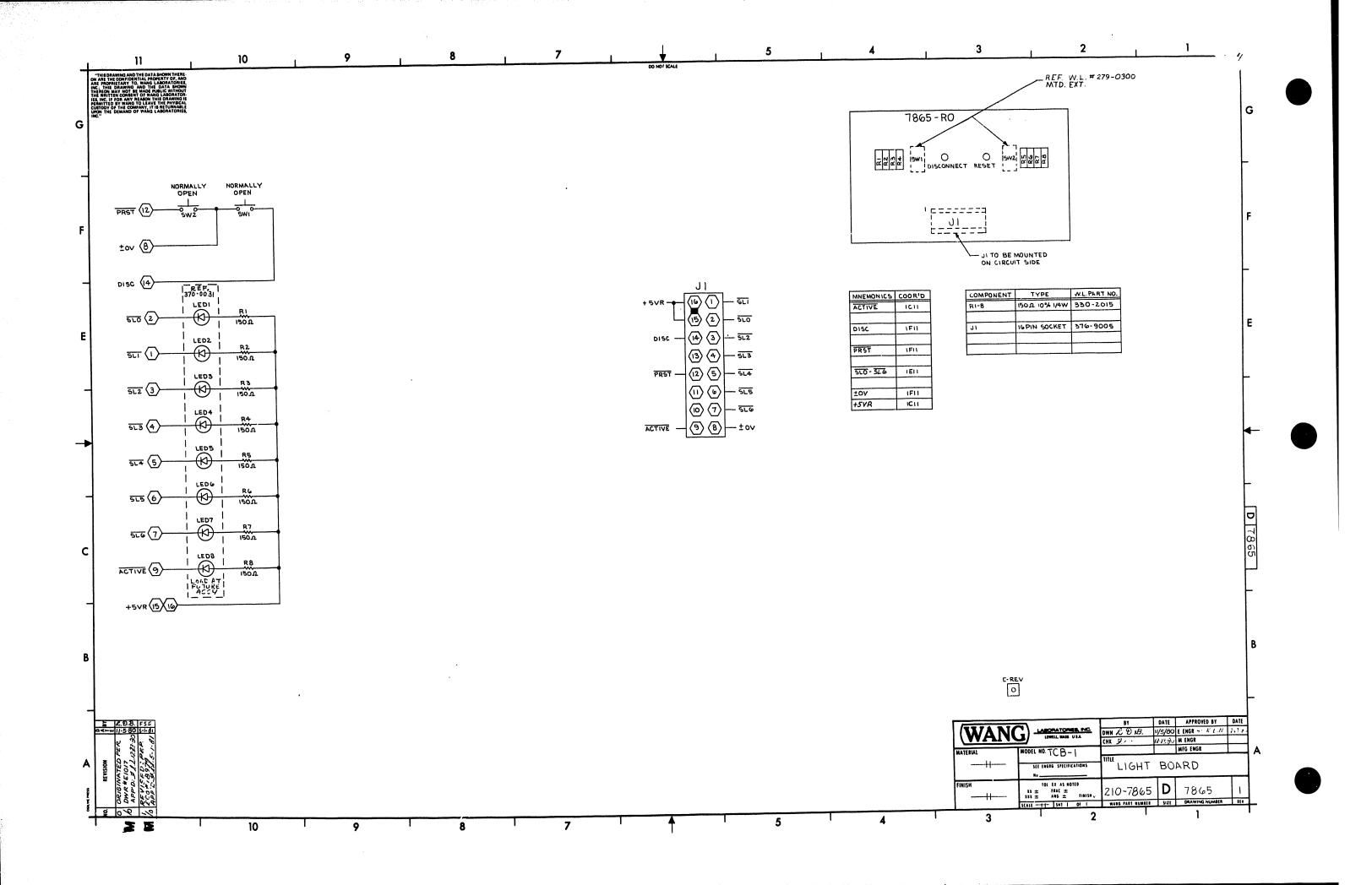

| 4-27   | TC Front Lamp/Switch Panel Installation Cable Routing |      |  |

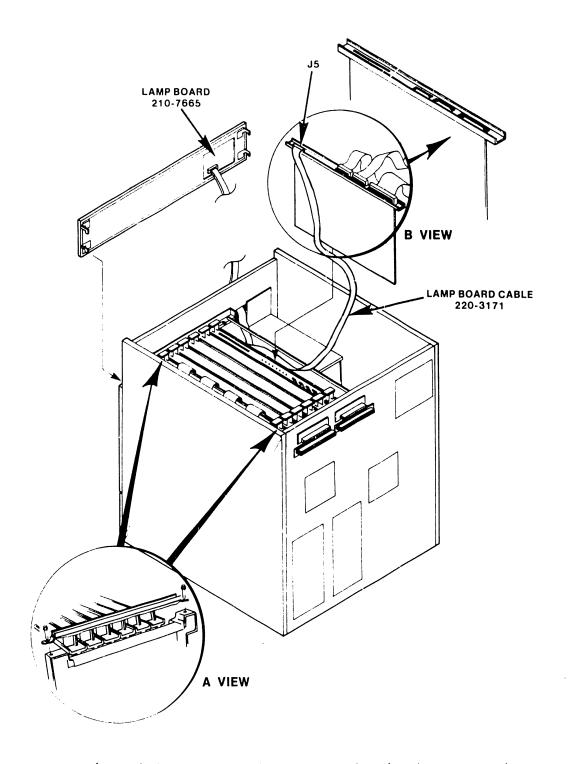

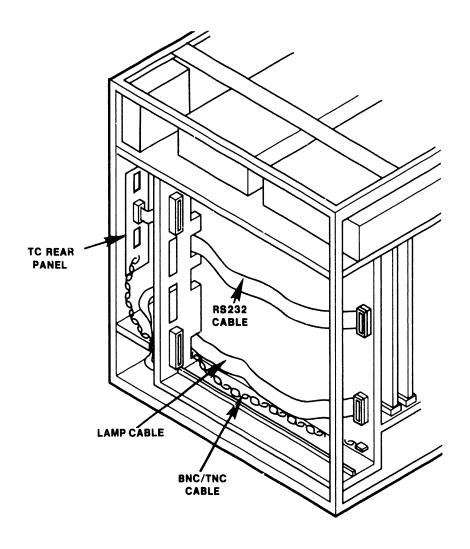

| 4-28   | TC Lamp Board Cable Routing (bottom side              | 4-48 |  |

|        | frame slot)                                           | 4-29 |  |

|        | TC Controller PCB Installation                        | 4-49 |  |

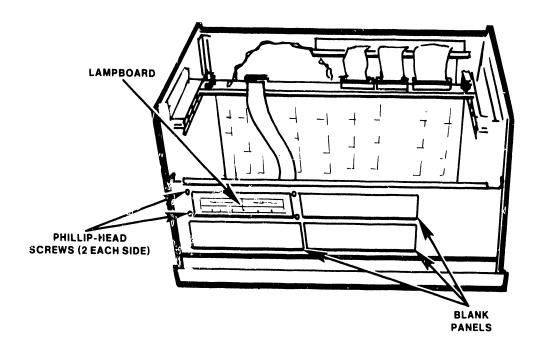

| 4-30   | Lamp Board Installation                               | 4-51 |  |

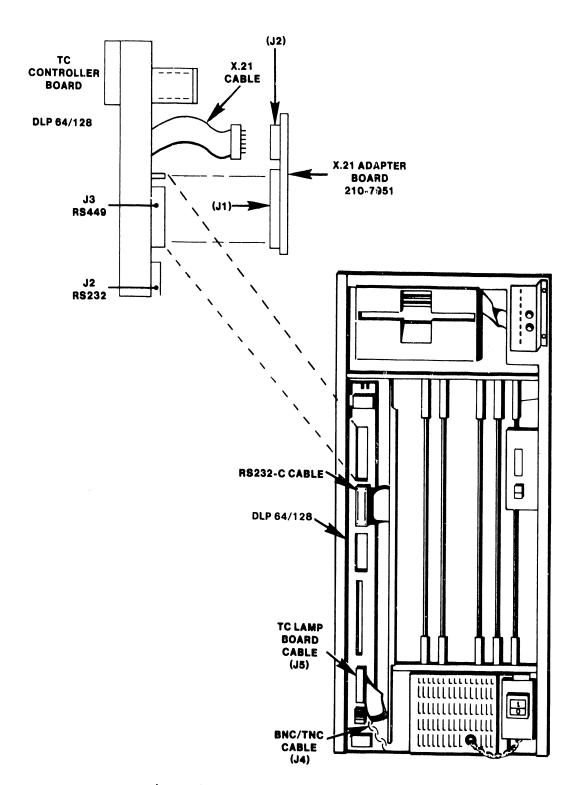

| 4-31   | RS-232 C or RS-366 Interface Cable<br>Installation    | 4-53 |  |

| 4-32   | X.21 Interface Cable Installation                     | 4-54 |  |

| 4-33   | TC Rear Panel Installation                            | 4-55 |  |

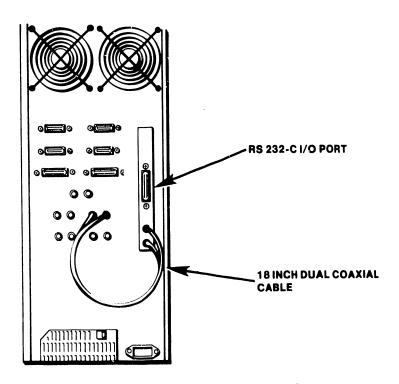

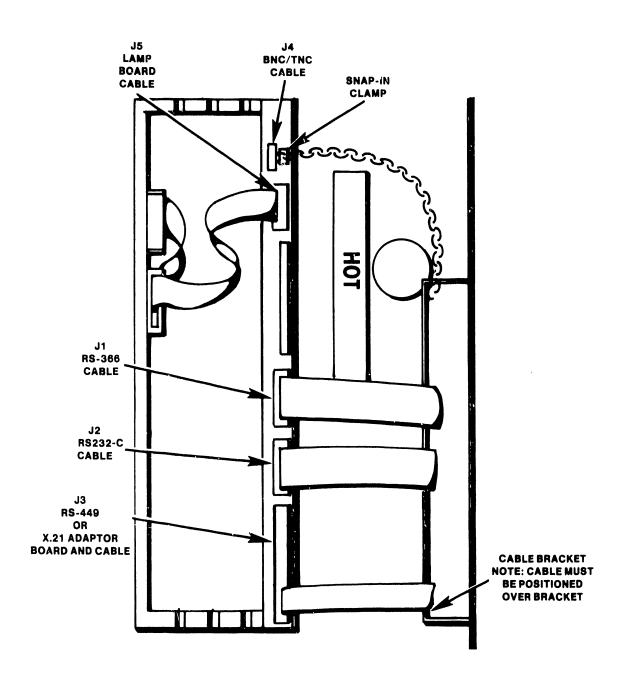

| 4-34   | Interface Cable Connection                            | 4-57 |  |

| 4-35   | X.21 Interface Adaptor Board Installation             | 4-58 |  |

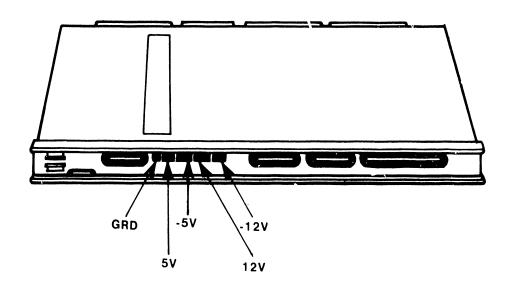

| 5-1    | Voltage Test Points                                   | 5-2  |  |

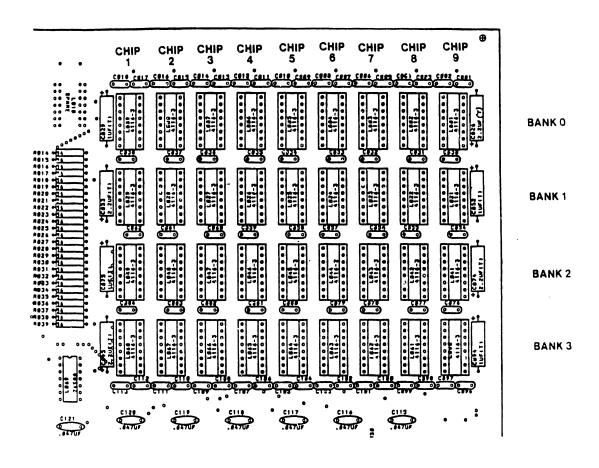

| 5-2    | Memory Chip Layout                                    | 5-5  |  |

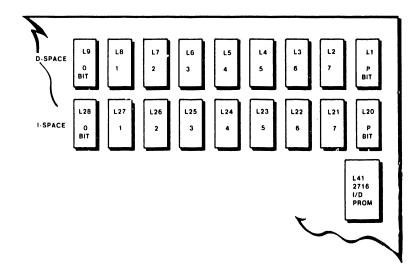

| 5-3    | I and D Space RAM                                     | 5-8  |  |

### TABLES

| TABLE | TITLE                                        | PAGE |  |

|-------|----------------------------------------------|------|--|

| 1-1   | OIS/VS TCB-1, DLP 64/128-                    | 1-2  |  |

|       | Communication Requirements                   |      |  |

| 1-2   | Related Wang Documentation                   | 1-3  |  |

| 2-1   | Control Bit Format                           | 2-6  |  |

| 2-2   | Data Link Commands                           | 2-12 |  |

| 3-1   | OIS 3270 Front Panel LEDS                    | 3-8  |  |

| 3-2   | Remote Wangnet (WSN) LED Status Indicators   | 3-9  |  |

| 3-3   | Teletex Front Panel LED Indicators           | 3-10 |  |

| 4-1   | Switch Bank SWl Switch Settings              |      |  |

|       | (First TC Controller)                        | 4-3  |  |

| 4-2   | SWl Switch Settings (Second TC Controller)   | 4-3  |  |

| 4-3   | Switch Bank SWl Switch Settings (Leased-Line | 4-3  |  |

|       | Modem Operation)                             | 4-4  |  |

|       | Null Modem Switch Settings                   | 4-4  |  |

| 4-5   | PC Guide Block Installation                  | 4-9  |  |

| 4-6   | PC Guide Block Installation                  | 4-29 |  |

| 5-1   | TCB-1 LED Status Description                 | 5-3  |  |

| 5-2   | TCB-1 Loopback Test Switch Settings          | 5-6  |  |

| 5-3   | DLP 64/128-LED Status Description            | 5-7  |  |

| 5-4   | Memory Chip Detect                           | 5-8  |  |

| 5-5   | DLP 64/128 Loopback Test Switch              | 5-9  |  |

|       | Settings                                     |      |  |

### TC CONTROLLER CONVENTIONS

In the chapters that follow reference will be made to the use and implementation of the TCB-1, and in the case of this manual, the DLP 64, and DLP 128 TC Controllers. These TC controllers, specifically the DLP 64 and DLP 128, have been documented and referred to in the following manner:

OIS and Alliance Systems

```

TCB-1 as - TC-SC-1, TC-SC-2, TC-AC-2, or 6554-1A through 6554-4A. DLP 64 as - TCB-3 64K, or OIS-TC. DLP 128 as - TCB-3, OIS-TC1.

```

VS Systems

```

TCB-1 as - 6554-1 through 6554-4.

DLP 64 as - TCB-3 64K, or VS-TC.

DLP 128 as - TCB-3, or VS-TC1.

```

In ordering this controller the TCB-3 "convention" or "nomenclature," is used by Logistics in filling field order requirements. This manual will refer to these controllers as a DLP 64 (TCB-3 64K), and as a DLP 128 (TCB-3). Refer to Chapter 4, for reference to part numbers.

# CHAPTER INTRO-DUCTION

# CHAPTER 1 INTRODUCTION

### 1.1 INTRODUCTION

The scope of this manual concerns the TCB-1, DLP 64 (TCB-3 64K), and DLP 128 (TCB-3) TC Controllers, and is intended to enable field personnel to complete the maintenance tasks described below, and to understand what TC controller indications to look for during normal operation, as well as indications relating to fault conditions. This will enable fault isolation, and the action to take to service the fault. Maintenance procedures concern the following areas:

Unpack, set switches and install in OIS and VS Systems. Refer to diagnostic and loopback test requirements. Run diagnostics.

Define error indications if diagnostics fail.

Service fault.

Chapter Two provides a block-level description and a functional overview of the TCB-1, DLP 64, and DLP 128 Controllers.

### 1.2 SYSTEM DESCRIPTION

The TCB-1, DLP 64, and DLP 128, are a motherboard/daughterboard arranged telecommunications controllers. They are designed for use on all Z80A-CPU-based OIS and VS Systems. The TC Controllers are installed and made operational in OIS 40/50, 105/115/125A/130A, and 140/145 Masters, and in the Telecommunications Processor (TCP). One TC Controller may be used on OIS 40/50, 105/115/125A/130A Systems, while 140/145 Systems may be configured with two. Up to four TC controllers may be used in each TCP.

The TCB-1, DLP 64 and DLP 128, Controllers contain interface connectors that are connected, by cable, to an I/O port on the rear of the OIS master or TCP. This cable interface from the controller to the I/O port, enables physical connection of one of four interfaces to a modem or null modem. These controllers support RS-232-C, RS-366, RS-449, and X.21 interfaces. The interfaces that are supported and installed, depends on the software emulation that the system is using. Refer to Chapter Four, Installation Requirements, for the above mentioned systems for more detail.

The TCB-1, DLP 64 and DLP 128 Controllers, support communications software that allows emulation of protocols, the type employed depending on the hardware and software requirements. Typically, emulator software allows a VS System through a TCP, or OIS Master to communicate with other VS or OIS Masters, as well as non-Wang systems. The present available emulation environment supported, and the required communications hardware (TCB-1, DLP 64 and DLP 128), are defined in Table 1-1.

The TCB-1 and DLP 64 contain 64K bytes of memory, while the DLP 128, an enhanced version of the DLP 64 contains 128K bytes of memory. The DLP 64 functionally replaces the TCB-1. The DLP 128, due to increased memory capacity, contains additional circuitry for memory selection.

### 1.3 COMMUNICATION REQUIREMENTS

Table 1-1 specifies communication requirements of an OIS Master and TCP.

Table 1-1 OIS/TCP TCB-1, DLP 64/128 Communication Requirements

|                       |                               | OIS 40/50 | Other Z-80 based OIS<br>and Alliance Systems | VS 25/45-100    |

|-----------------------|-------------------------------|-----------|----------------------------------------------|-----------------|

| W<br>A<br>N<br>G      | WSN Multi-Point<br>Primary*   | N/A       | N/A                                          | TCB-1<br>DLP-64 |

| N<br>E                | WSN Multi-Point<br>Secondary* | DLP-64    | TCB-1<br>DLP-64                              | TCB-1<br>DLP-64 |

| TW                    | WSN Point-to-<br>Point*       | DLP-64    | TCB-1<br>DLP-64                              | TCB-1<br>DLP-64 |

| O<br>R<br>K           | IDS                           | N/A       | N/A                                          | DLP-64          |

| I<br>N<br>G           | X.25                          | DLP-128   | DLP-128                                      | DLP-128         |

| S                     | 3274 SNA/SDLC                 | DLP-128   | DLP-128                                      | DLP-64          |

| A                     | 3777 SNA/SDLC                 | N/A       | N/A                                          | DLP-64          |

| B<br>I<br>S<br>Y      | 2780/3780<br>WPS Enhanced     | DLP-64    | DLP-64                                       | N/A             |

| N<br>C                | 3271 BSC                      | DLP-64    | TCB-1<br>DLP-64                              | N/A             |

| A<br>S<br>Y<br>N<br>C | Async TIY                     | DLP-64    | DLP-64                                       | N/A             |

|                       | Teletex                       |           | DLP 128                                      | N/A             |

<sup>\*</sup> Wang Systems Networking (WSN) formerly Remote Wangnet.

### 1.4 RELATED WANG DOCUMENTATION

Table 1-2 Related Wang Documentation

|                                                                     |                    | (                                                                                                                                                             |

|---------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Document                                                            | Reorder No.        | Description                                                                                                                                                   |

| Telecommunications<br>Processor (TCP) Product<br>Maintenance Manual | 729-1043           | Provides installation procedures, data set test descriptions and describes characteristics of Interfaces.                                                     |

| OIS 3270 Emulation User<br>Guide                                    | 700-6980           | Provides a detailed description of all 3270 Emulation procedures.                                                                                             |

| Network User's Guide to<br>File Transfer and Remote<br>Log-on       | 800-1316-RU-<br>02 | Provides procedures that will enable interaction of VS and OIS Systems. File transfers, remote log-on and document transfer procedures are discussed.         |

| Network Configuration and<br>Operations Guide                       | 800-1317-RO-<br>02 | Provides procedures to edit network edit network configuration files and assign names, services and addresses to VS and OIS systems implemented in a network. |

| Alliance Batch Communication Interfaces                             | 700-7149           | Provides information concerning Users Guide batch TC operation using Alliance software.                                                                       |

# CHAPTER THEORY OF OPERA-TION

## CHAPTER 2 THEORY OF OPERATION

### 2.1 INTRODUCTION

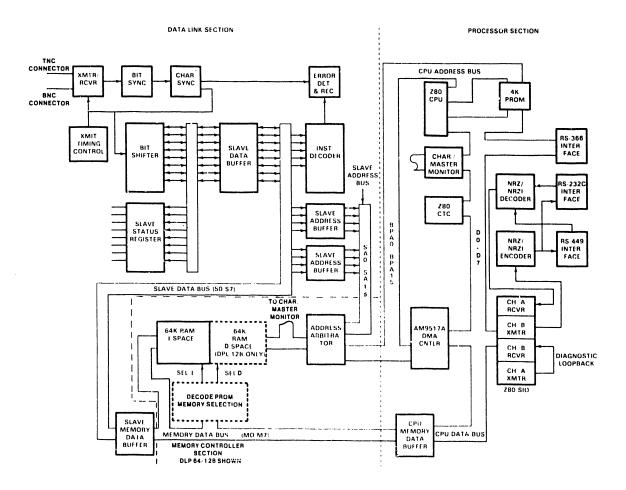

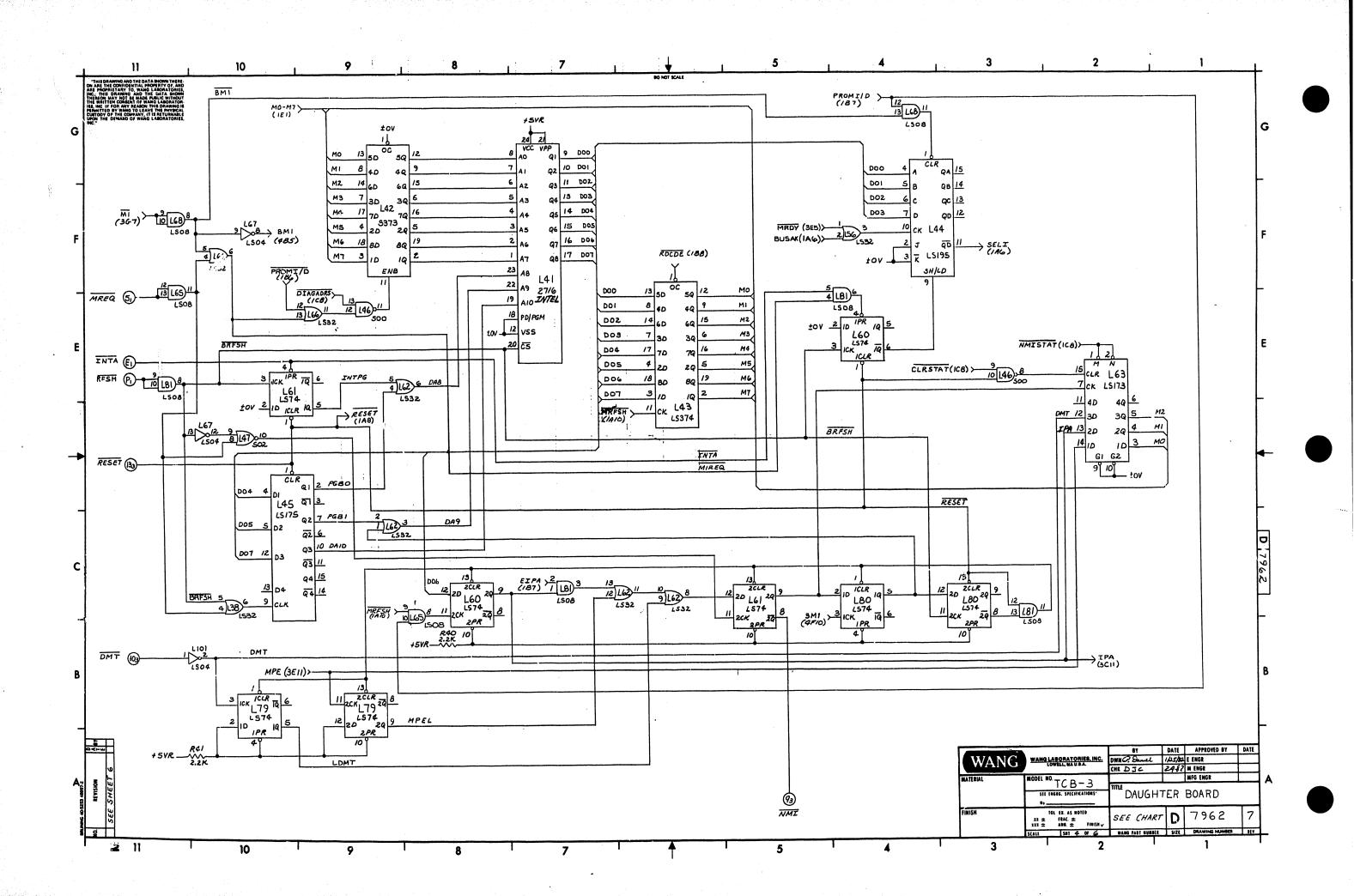

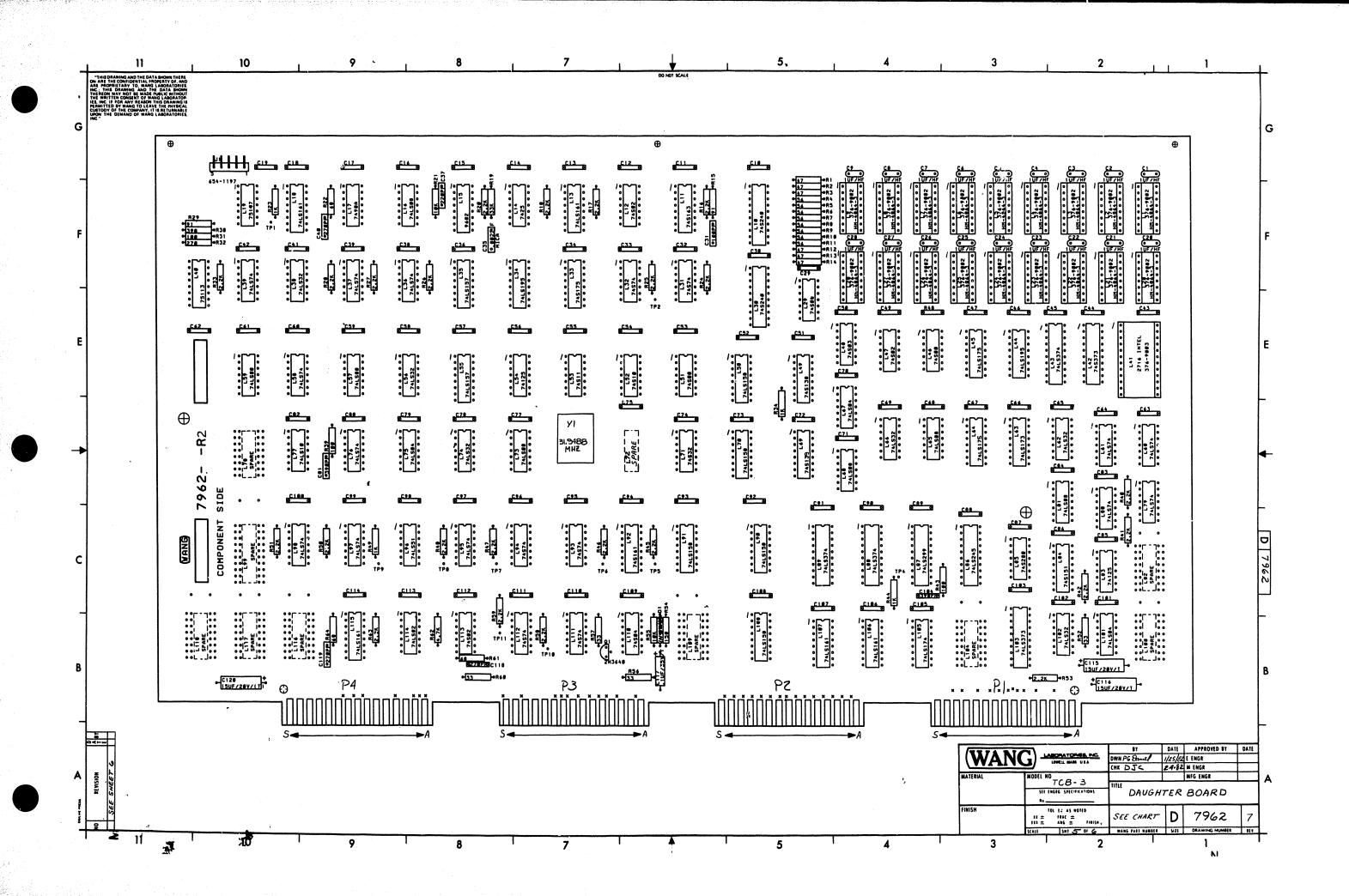

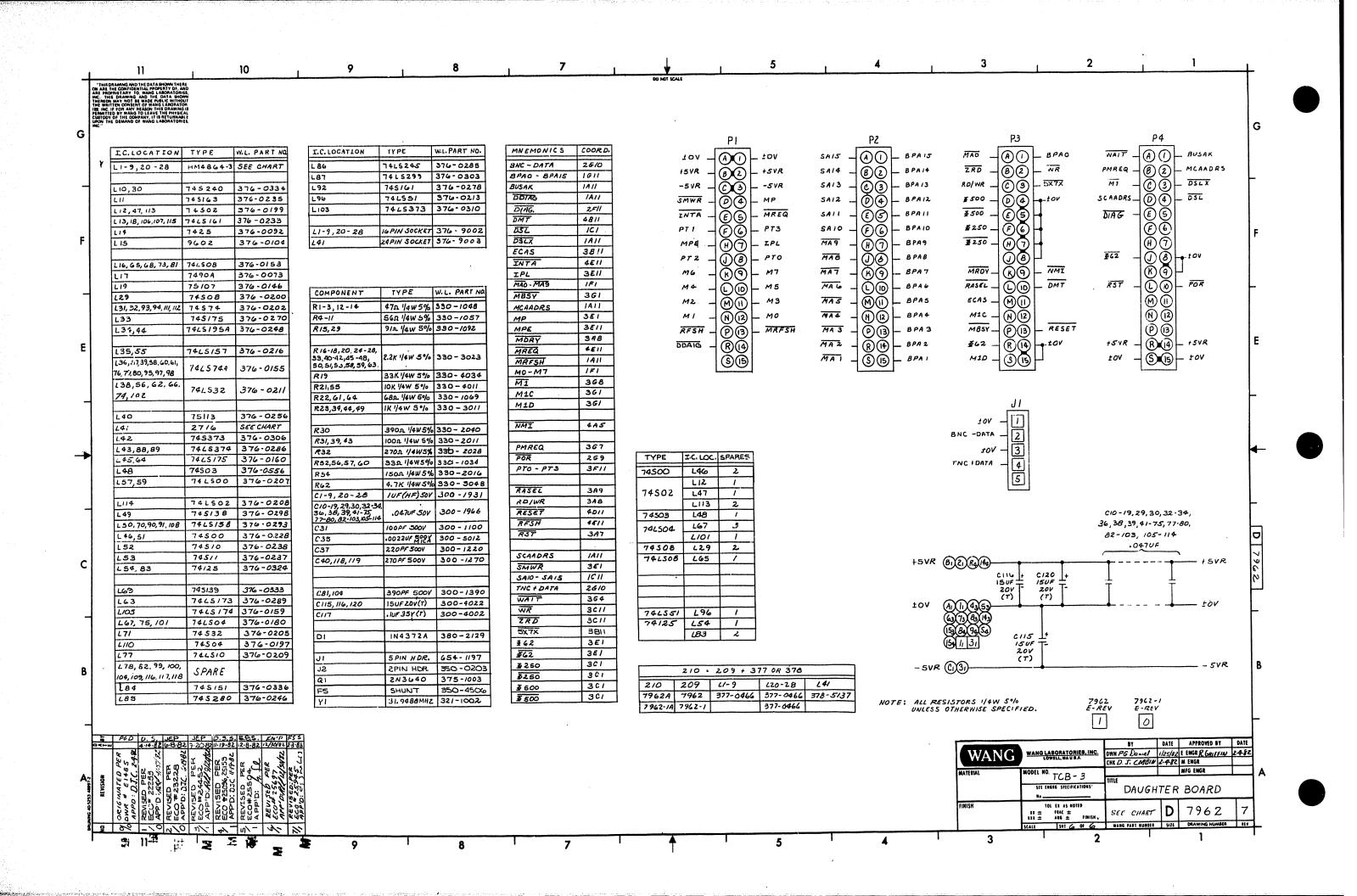

The TCB-1 and DLP 64/128 Controllers are comprised of a motherboard which contains the Processor Section, a daughterboard which contains the Data Link Section, and the Memory Controller Section.

The Processor Section contains circuitry to enable DMA data transfers through the appropriate interface, and to generate vectored interrupts for special characters. The Data Link Section contains circuitry that interfaces the OIS Master/TCP or VS-TCP, through dual coaxial cable as a slave data link. The Memory Controller Section coordinates TC controller memory access between the processor and the data link section. The following paragraphs describe the controllers. Characteristics that are unique to a controller(s) will be identified.

Figure 2-1 Functional Block Diagram

### 2.2 PROCESSOR SECTION

The Processor section comprises the following components:

Z80A-CPU

Z80A-CTC

Z80A-SIO/2

AM 9517A DMA Controller

Character/Master Monitor

PROM Memory

RS-232C Interface

RS-449 Interface

RS-366 Interface

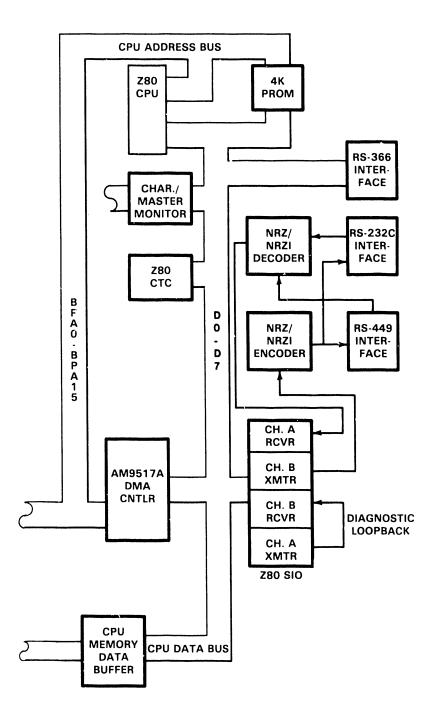

$\overline{280}$ A-CPU - The Z80A-CPU is the main control and processing element of the TC controller. It operates on a 250 ns clock cycle (4 MHz) and shares a common data bus with the DMA controller and the Z80A-Serial Input Output Controller (SIO/2). The Z80A-CPU resides at location L98.

Z80A-Counter Timer - The Z80A-Counter Timer Chip (CTC), provides timing and counting functions for the TC controller. The CTC is divided into four channels, with channel 0 providing baud rate clock, channel 1 providing software event timing, and channels 2 and 3 alerting the CPU of DMA completion. The Z80A-CTC resides at location L92.

Z80A-Serial Input/Output Controller - The Z80A-Serial Input/Output Controller (SIO/2), converts 8 bit parallel data into one of several serial formats and vice versa. Both synchronous and asynchronous operation, and both character and bit-oriented protocols are supported.

In addition the Z80A-SIO/2, performs character and line buffering, line control and status monitoring, and error protection and detection. The Z80A-SIO/2 consists of two channels, channel A and channel B. Normally the channel A receiver and the channel B transmitter are used for all transmit and receive operations. This allows full duplex operation if required. When running internal diagnostic loopback tests, the channel A transmitter and channel B receiver are used. The SIO/2 resides at location L69.

AM 9517A DMA Controller - The DMA Controller allows high speed data transfers between the Z80-SIO/2 and D space RAM memory. It is controlled by the Z80A-CPU and will support speeds up to 880 Kbps with minimal system overhead. The DMA controller is a four channel device, supporting both SIO/2 transmitters as one two-channel pair, and both SIO/2 receivers as the other two-channel pair. The DMA controller resides at location L94.

This combined with the use of a "next" and "current" channel register for each channel pair, and the Z80A-CTC providing interrupt signaling, insures quick handling of SIO/DMA requests.

<u>Character/Master Monitor</u> - The Character/Master Monitor, provides supervisory services for the TC controllers, by alerting the Z80A-CPU when a specific memory write occurs. Its circuits consist of various components, but are located from L76 to L83.

The character portion of the monitor "watches", for program specified DMA characters deposited in memory, which act as lookup addresses for the 256 byte vector table. The master portion uses data link memory addresses for the same purpose. The retrieved byte from the vector table allows for generation of one of 256 different interrupts, few of which are used at this time. The circuitry responsible for addressing vector memory include multiplexers (L96, L97, and L81). Circuitry associated with character and master monitor supervisory services include:

The Monitor Control Register (L49)

The Monitor Base Register (L66)

Vector Memory (L79, L80)

The monitor control register contains eight bits that control the mode of monitor operation, refer to Paragraph 2.2.2, for more detail.

The monitor base register contains eight bits, six of which form the starting address of the Master Slave Communication Area (MSCA).

Vector memory comprises two 1K-by-4 bit static RAM chips arranged as 1K eight bits. Vector memory contains the interrupt vectors used when program specified characters are deposited, and addresses are written in memory.

PROM Memory - PROM memory is used for TC controller power-up diagnostics. It resides at location L95. The PROM memory consists of 4K worth of extensive power-up diagnostics that will even point to a specific defective RAM chip. It consumes 4K worth of overall memory addressing space.

RS-232C Interface - The RS-232C Interface circuits provide the necessary interface to connect to the standard 25 pin EIA modem connection on the back of the TC controller - equipped OIS Master or TCP. Most of the RS-232C Interface circuits reside at locations L14, L15, L16, L33, and L34.

RS-449 Interface - The RS-449 Interface circuits provide the necessary interface to connect to the 37 pin EIA modem connection on the back of the TC controller - equipped OIS Master or TCP. Most of the RS-449 interface circuits reside at locations L17, L18, L35, and L36. The interface circuitry of the RS-449 interface, supports and is used to implement the X.21 interface. The RS-449 interface is not widely used. Notice that the RS-232C and RS-449 signals may be encoded in NRZ or NRZI format and that either format is receivable.

RS-366 Interface - The RS-366 Interface circuits provide the necessary interface to connect to the 25 pin EIA connection on the back of the TC controller-equipped OIS Msster or TCP. Most of the RS-366 Interface circuits reside at locations L10 - L13. This interface is used to connect to an Automatic Calling Unit for automatic switched network call establishment for communications.

### 2.2.1 Processor Section Overview

The Z80A-CPU, is the main processing element of the TC controller. The Z80A-CPU controls via software, all functions of the TC controller. Software control, allows the CPU to initialize and program the DMA controller, the SIO/2, CTC, and character/master monitors for all operations.

On a read operation from a telecommunications line, data is input to the motherboard from an interface port (RS-232-C, RS 449/X.21). This data is clocked into the SIO/2 channel A receive port at the baud rate specified by the CTC (channel zero). The SIO/2 converts the serial data to eight bit parallel data. Conversely, during a transmit operation, eight bit parallel data is converted to serial data via the SIO/2 channel B function. This data is transmitted at the specified baud rate to an interface port.

Transfer of eight bit parallel data from/to channel A or channel B of the SIO/2 is accomplished via SIO/2 signals (W/RDYA) or (W/RDYB), which are used to form DMA requests.

Once a DMA request is granted, the DMA controller gains control of the memory address bus and places the low order address on the processor address bus (PAO-PA7), while the high order address (PA8-PA15), are sourced from the DMA data lines (DO-D7). The DMA controller generates a memory request, and transfer of eight bits of data then proceeds directly to/from the SIO/2 and memory. DMA channels 0 and 2, support data input from the SIO/2 receiver and are called the receiver pair. DMA channels 1 and 3, support data output to the SIO/2 transmitter and are referred to as the transmit pair.

When a DMA end of process (EOP) is signalled for a particular channel pair (transmit or receive), the next channel register is copied to the current channel register effectively switching to the next inactive or available DMA channel of that pair. In addition, the CTC will signal an interrupt for that pair (CTC channel 2 = DMA receiver pair; channel 3 = DMA transmit pair).

If the character monitor is enabled during a DMA write to memory (SIO/2 receive function), the characters being deposited are "watched" as explained in Paragraph 2.2.2.

### PROCESSOR SECTION

Figure 2-2 Processor Section Block Diagram

### 2.2.2 Character and Master Monitor

The Character and Master Monitors provide supervisory services for the TCB-1, DLP 64 and DLP 128 controllers. These monitors alert the Z80A-CPU if a specific memory write occurs. Both monitors may be enabled simultaneously.

The Character Monitor, which is enabled by the CHARMON signal, "watches" characters deposited in memory by the DMA controller. Thus, the character monitor can interrupt the Z80A-CPU when specific characters (control, format) are deposited. The Z80A-CPU can then perform an immediate action such as disabling the receiver CRC or switching buffers.

The Master Monitor, enabled by the MASMON signal, "watches" the data link memory write accesses, and can interrupt the Z80A-CPU whenever a OIS master or VS, accesses the master/slave communication area (MSCA) of controller memory. This interrupt may be used to queue another request, awaken a sleeping task, etc.

The Character and Master monitor circuits include the monitor control register, the monitor base register, vector memory, the monitor FIFO, and multiplexer chips and associated circuitry.

The monitor control register, contains eight control, bits six of which determine the mode of monitor operation. The two remaining bits control the deadman timer (Refer to the non-maskable interrupt sequence for more detail relating to the deadman timer). The contents of the monitor control register are under CPU/software control. The control bits have the following format:

Table 2-1 Control Bit Format

| Data Bit | Control Bit<br>Reference | Function                                                                    |

|----------|--------------------------|-----------------------------------------------------------------------------|

| DO       | MAPOUT                   | Remove vector memory from processor memory space.                           |

| D1       | CHARMON                  | Enable the character monitor function.                                      |

| D2       | MASMON                   | Enables the master monitor function.                                        |

| D3       | CLRINT                   | Clears all pending interrupts by clearing monitor FIFO.                     |

| D4       | INTALL                   | Forces vector memory bit VO=0, which generate interrupt for all characters. |

| D5       | BUFOFF                   | Disables buffering by the SIO/2 DMA controller pair.                        |

| D6       | DNMI                     | Disables DNMI non-maskable interrupt sequence.                              |

| D7       | DDMT                     | Disables Deadman timer.                                                     |

The monitor base register contains eight bits. Six of the bits (VM10-VM15) form the starting address of the 1K byte master slave communication area (MSCA). These bits are set by the master monitor and compared against the most significant six bits of the data link memory address (SA10-SA15). This comparison takes place during data link write operations to memory, to determine if the MSCA is being accessed. The remaining two bits (VM8-VM9), are used by the Character Monitor to select one-of-four 256 byte recognition tables of vector memory.

Addressing of vector memory is accomplished via multiplexers. This circuitry selects either memory address lines MAO-MA9 (in Master Monitor mode) or data lines BDO-BD7 and base register bits VM8, VM9 (in Character mode) to become the vector memory addresses.

Vector memory comprises two 1K by 4 bit static RAMS arranged as 1K eight bit bytes. Vector memory bits are referred to as VO-V7. If VO=O of a given byte is set, then the location is activated as being a potential character vector. V7=O activates a byte as being a master vector. Thus, a single vector memory location may be activated for both Character and Master Vectoring (VO and V7=O). When a location of vector memory is read it is transferred to the monitor FIFO. Circuitry associated with this transfer, will indicate which monitor (character or master) caused the vector address and will set V7 (1 or O) accordingly. VO however, is loaded into the FIFO as O, to assure that all interrupt service routine - program counters are aligned on halfword boundaries.

Up to 16 vectors may be held in the FIFO awaiting Z80A-CPU acknowledgement. In the event of a FIFO overflow, either a hex 00 or hex 80 vector will be deposited in the FIFO to indicate which monitor was the last to overflow. Refer to paragraph 2.2.3 for further discussion of vector (maskable), interrupt sequence.

### 2.2.3 Maskable Interrupt Sequence

The vector information contained in vector memory determines which memory events should generate interrupts. If an interrupt is enabled by the Z80A-CPU, the monitor FIFO will present the interrupt request, (generated via the character or master monitor, storing the vector in the monitor FIFO), and pass the interrupt vector to the Z80A-CPU during the time that interrupt acknowledge (INTA) is enabled low.

The Z80A-CPU will read the vector (placed on data lines D0-D7 by the FIFO) and merge it into its I Register (the vector byte becomes the low order address in the I register, whereas the high order byte already resides there). The CPU stores the program counter (PC) on the stack, then outputs the contents of its I register (containing both low and high order bytes) on the address bus to access the vector address table in memory. The contents of the location in the vector address table specified by the I register is then read by the CPU, placed in the PC, and used to access the interrupt service routine.

Once the interrupt service routine is completed, the old program counter is pulled from the stack and restored in the PC. Control is then passed to the interrupted program.

On DLP 128's, all interrupt sequences are steered to D space memory. When a maskable interrupt occurs, the acknowledge (MI/IORQ or INTA) signals, select page 1 of the decode PROM. All 256 locations of page 1 contain the same code which force the access to D space. See Paragraph 2.4, Memory Control Section, for more information on D space selection.

### 2.2.4 Non-Maskable Interrupt Sequence

For the TCB-1, DLP 64 and DLP 128, Non-Maskable Interrupts (NMI) may be caused by Memory Parity Errors (MPE) or a Deadman Timer (DMT) timeout. On a DLP 128, an additional source of a NMI is an Illegal PROM Address (IPA). Non-maskable interrupts of the DMT or IPA variety may be enabled or disabled via I/O commands (refer to Paragraph 2.2.2, Table 2-1, for reference to I/O commands enabled by data bits D6 and D7).

NMI's on DLP 128's force memory access to D-space. See Paragraph 2.4 for more detail regarding D space selection.

Whenever data is accessed from memory, the 8 data bits along with the memory parity bit are compared to determine that correct parity has been maintained. If an even number of 'one' bits are detected, then a MPE is generated. MPE's on a TCB-1 cause the TCB-1 to perform NOPs. This does not occur on a DLP 64 or a DLP 128.

The deadman timer prevents the communications line from "hanging up" in the event of a software or hardware failure. The deadman timer functions through I/O instructions.

Once enabled the deadman timer is reset by the system software at least every 0.5 seconds to prevent it from timing out. This timeout will produce a non-maskable interrupt.

Two control bits DNMI and DDMT enable or disable the timer functions and are linked with the monitor control register bits. The following conditions enable or disable the timer:

| DNMI = 1 | - | The Z80A-CPU will not be interrupted regardless of                                                                                       |

|----------|---|------------------------------------------------------------------------------------------------------------------------------------------|

|          |   | the state of the timer.                                                                                                                  |

| DNMI = 0 | - | The Z80A-CPU will be unconditionally interrupted                                                                                         |

|          |   | when the timer expires via a NMI. DNMI should only be set to one, disabling the NMI, before the DDMT is set to 1 - to disable the timer. |

| DDMT = 0 | - | Setting DDMT to zero will start the timer function                                                                                       |

DDMT = 0 - Setting DDMT to zero will start the timer function.

DDMT = 1 - Stops the timer function.

On DLP 128's an Illegal PROM Address (IPA), will cause generation of a non-maskable interrupt. An IPA will occur if the second opcode of a dual opcode instruction is invalid or incorrect. A special code, Hex 40, is read out of the PROM and generates the (IPA).

DLP 64 and DLP 128 Controllers, have a second status register independent of the status register normally examined by a master OIS or VS system. This second status register is provided to allow the TC controller software to determine which NMI condition (MPE, DMT, IPA) produced the interrupt. The error condition is loaded into the status register at the time of NMI generation. The error handling routine may then examine the status register by executing an IN '71' (generates NMISTAT). A CLRSTAT command (Out '72') clears the register.

### 2.3 DATA LINK SECTION

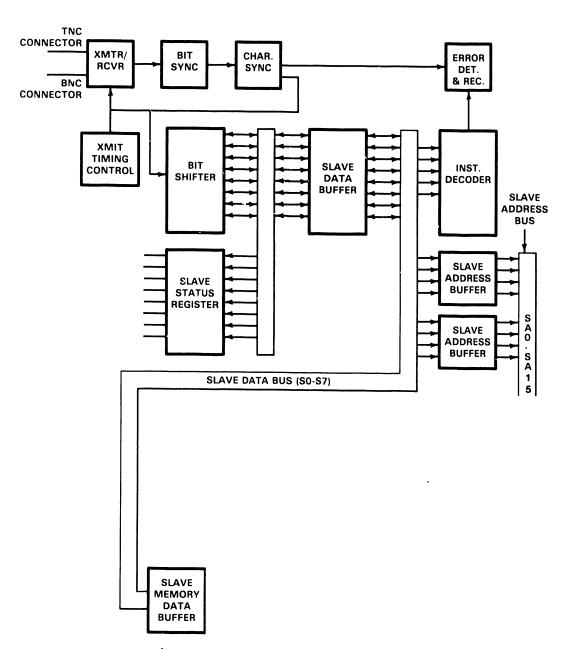

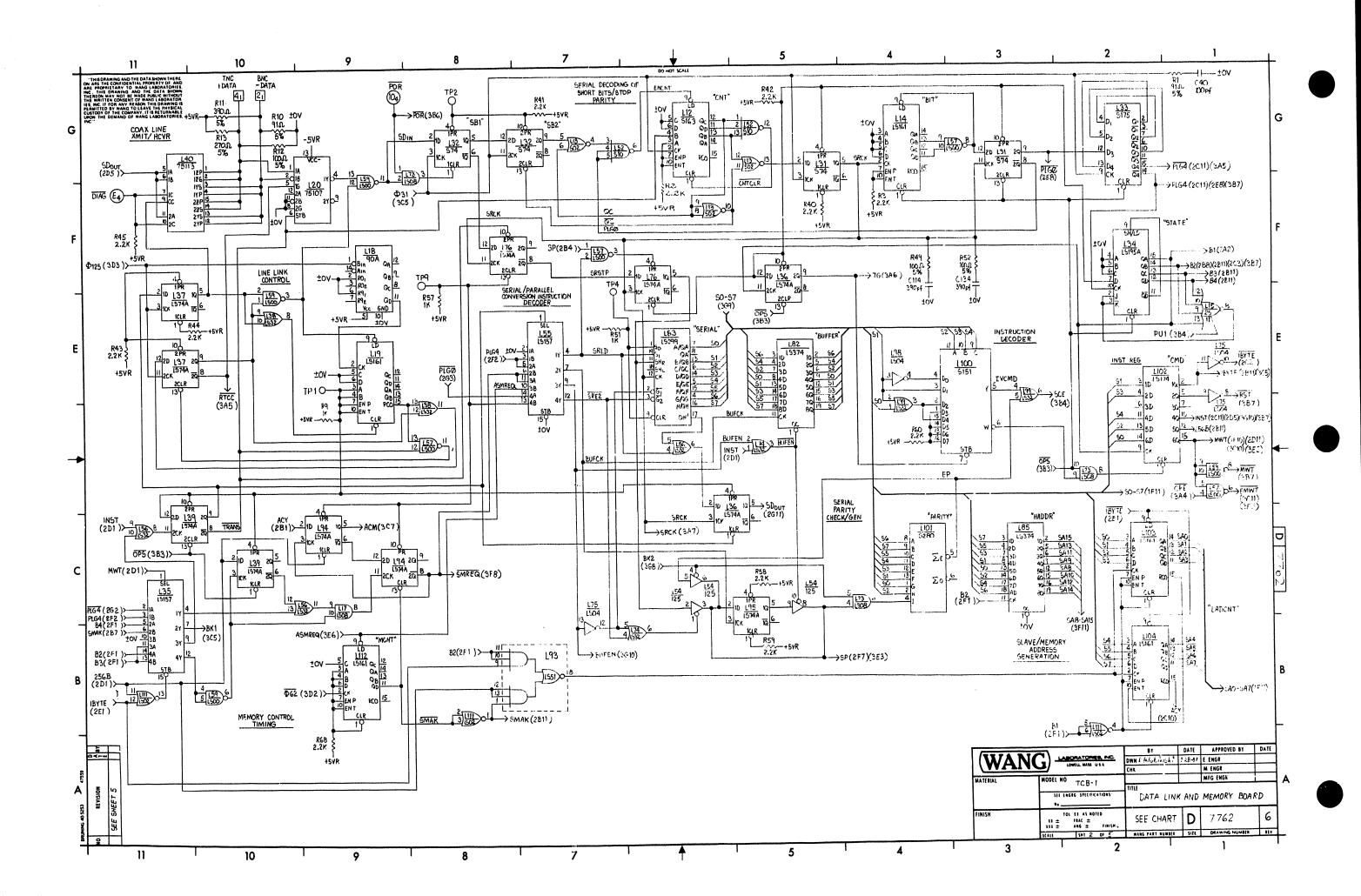

The Data Link section, located on the daughterboard, comprises circuitry for instruction decoding, address selection, and error recovery and detection. The following paragraphs provide a block-level description of the 928 Data Link Section.

Receiver/Transmitter - The receiver/transmitter circuits, are responsible for the reception and transmission of data and control information between the TC controller and the OIS or VS master. This channel operates in a half duplex balanced mode, utilizing a high speed (4.275 Mbps) start/stop line discipline. This circuitry resides at location L19 and L40 on a DLP 64/128; L20 and L40 on a TCB-1.

Transmit Timing Control - The transmit timing control circuits, insure that data and control information sent to the master maintain the correct line discipline. This circuitry resides at location L17, L18, and L37 on a DLP 64/128; L18, L19, and L37 on a TCB-1.

Bit Synchronization - The bit synchronization circuits, synchronize the received bit stream bit by bit, insuring that the TC controller and the master are in synchronization. In addition to synchronizing, these circuits also "strip" the start, parity, and stop bits from the eleven bit transmitted character leaving only the eight bit data or control word. This circuitry resides at location L32, L11, L31, and L13 on a DLP 64/128; L32, L12, L31, and L14 on a TCB-1.

Character Synchronization - The character synchronization circuitry, synchronize the received data or control bit stream character by character, insuring that the controller and the master are in character synchronization. This circuitry resides at location L33 and L34.

Bit Shifter - The bit shifter, is responsible for converting the received serial bit stream into a parallel eight-bit bus and vice versa during transmit operations. This circuitry resides at location L87, L88 on a DLP 64/128; L83 and L82 on a TCB-1.

<u>Instruction Decoder</u> - The instruction decoder, is responsible for sampling the slave data bus information to validate a command or control words that may be present in the first byte of receive data. This circuitry will also decode the data or command word as a 1 byte or 256 byte read/write operation or a control command (restart, status). It also supplies input to the error detection and recovery section when illegal commands or control words are found. This circuitry resides at location L84 and L105 on a DLP 64/128; L100 and L101 on a TCB-1.

Error Detection/Recovery - The error detection/recovery circuits, are responsible for detecting character errors at the character synchronization or instruction decoder sections, and indicating these by setting the CPE (channel parity error) input to the slave status register. These circuits also contain logic to initialize error recovery by use of OPS (Operation Start) which restarts the slave data link channel. This circuitry resides at location L15, L58, L98 on a DLP 64/128; L16, L58, and L95 on a TCB-1.

Slave Status Register - The slave status register maintains a status of three slave conditions and the slaves device type. It maintains status of whether the slave is running (IPL), whether the slave is experiencing a memory parity error (MPE), or whether the slave is experiencing a data error in the form of a channel parity error (CPE). It resides at location L103 on a DLP 64/128; L81 on a TCB-1.

### **DATA LINK SECTION**

Figure 2-3 Data Link Block Diagram

### 2.3.1 Data Link Section Overview

The 928 Data Link Section consists of circuitry associated with interfacing an OIS Master/TCP or VS TCP, with slave data links. This is accomplished by transmitting and receiving control and data information, via a dual coaxial cable link, to and from the master associated with that TC controller.

The data link channel operates in a half-duplex mode utilizing a 4.275 Mb/s asynchronous line discipline. The line format consists of a start bit, eight data bits, a parity bit, and a stop bit. The 928 Data Link, under control of the master, can respond to two control commands and four memory access commands as described in Table 2-2.

Table 2-2 Data Link Commands

| Command   | Result                                                                                                                                                                                           |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Restart   | The Restart command instructs the 928 Data Link to Reset the processor; clear the IPL, memory parity error (MPE) lines and exit diagnostic mode.                                                 |  |  |

| Status    | The Status command instructs the 928 Data Link to transmit the 928 Data Link and processor status, channel parity error (CPE), IPL, and memory parity error).                                    |  |  |

| Read 1    | The Read 1 command instructs the 928 Data Link to transmit one byte to the master, from the specified TC controller memory address.                                                              |  |  |

| Write 1   | The Write 1 command instructs the 928 Data Link to receive one byte from the master and deposit it at the specified TC controller memory address.                                                |  |  |

| Read 256  | The Read 256 command instructs the 928 Data Link to transmit 256 bytes of data to the master starting at the specified 256 byte aligned address from the specified TC controller memory address. |  |  |

| Write 256 | The Write 256 command instructs the 928 Data Link to receive 256 bytes of data from the master and deposit it at the specified 256 byte aligned TC controller memory address.                    |  |  |

Control and data information transmitted by the master is received on the TC controller daughterboard, via dual coaxial cable, where the serial data stream is clocked into receiver circuitry. This data is then clocked into bit synchronization circuitry where it is checked for a valid start bit. This circuit checks for a valid start bit by sampling the serial data two times - 32ns apart to ensure that noise does not corrupt detection of the start bit.

Once the start bit is detected, the data from the master is counted and synchronized via the synchronization circuitry which also strips the start, stop and parity bits leaving eight data bits. Character synchronization is provided by character synchronization circuitry to ensure that character data is synchronized to the master. Data and control information that is sent to the master is controlled by transmit timing control circuitry that "turns the line around", disabling the receiver and enabling the transmitter.

After the data is counted and synchronized it is converted from serial to parallel via a bit shifter, and then sampled by instruction decoder circuitry (data selector/multiplexers) that decodes the data to determine if the data bits (first byte) constitute a valid instruction. If a command is invalid, an error will be flagged by the instruction error recovery circuitry and relayed to the status register.

At the same time that the data or control word (first byte) is decoded to determine if the instruction is valid, it is parallel loaded into a parity generator/checker and checked for valid parity. If a parity error is detected a channel parity error (CPE) will be routed to the instruction recovery circuit. Recovery circuitry will in turn relay this parity error to the status register. Refer to Paragraph 2.2.4, for more information relating to the non-maskable interrupt sequence.

A valid command or control word is clocked into the instruction decoder where the command or control word is decoded as a restart command, status command or a read or write (1 byte or 256 byte) command as described in Table 2-2.

After the instruction is decoded, the necessary timing for a slave memory request is generated via the memory timing control circuitry.

To process the instruction, i.e. a 256 byte write, the memory address has to be specified. This occurs upon receiving the second byte (high order address) and third byte (low order address) from the master. The high order address (byte two) is loaded into the slave high order register at B2 time. The slave low order register is loaded with the low order address (third byte) only if the instruction has been decoded as a one byte transfer (read or write). For a 256 byte transfer the slave low order register remains cleared (X '00') thereby forcing all 256 byte transfers to a 256 byte boundary.

The slave memory address (high and low registers) is buffered onto the memory address bus and clocked into the memory selection logic. A memory write or read is then performed depending on the original slave instruction.

If the master monitor has been enabled and the memory address selected is in the master/slave communication area (as it normally is), and the command is a memory write, then a vectored interrupt will be generated by the Master Monitor. Refer to Paragraph 2.2.2, for further information regarding the master monitor.

### 2.4 MEMORY CONTROL SECTION

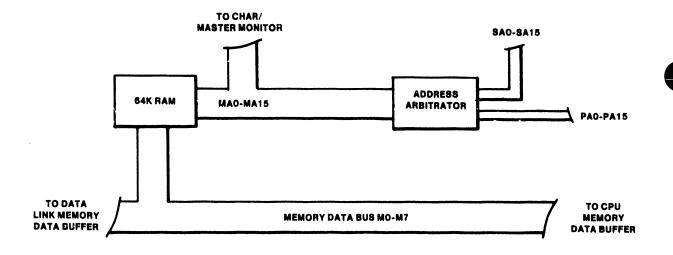

The Memory Control Section, located on the daughterboard, monitors requests from the Data Link Section and the Processor Section on a round robin basis. Memory requests are either granted by a READY notification or pended by a WAIT notification, thus allowing processor and 928 data link access interleaving.

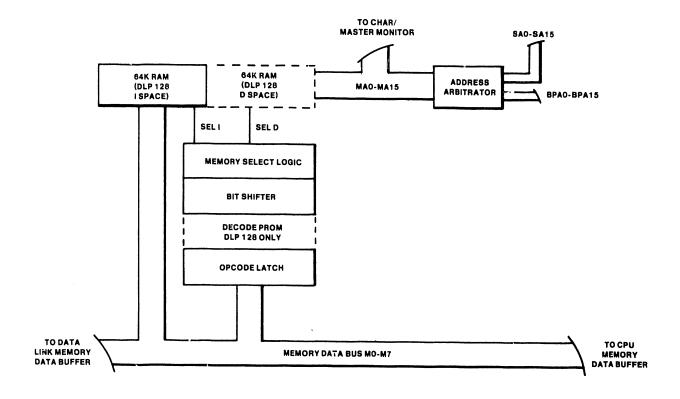

The Memory Control Section (see Figures 2-4 and 2-5), for all TC controllers comprise an address arbitrator and memory. Additional memory control circuitry for the DLP 64 and DLP 128, comprises an opcode latch, bit shifter, memory select logic, and opcode decode PROM (DLP 128 only).

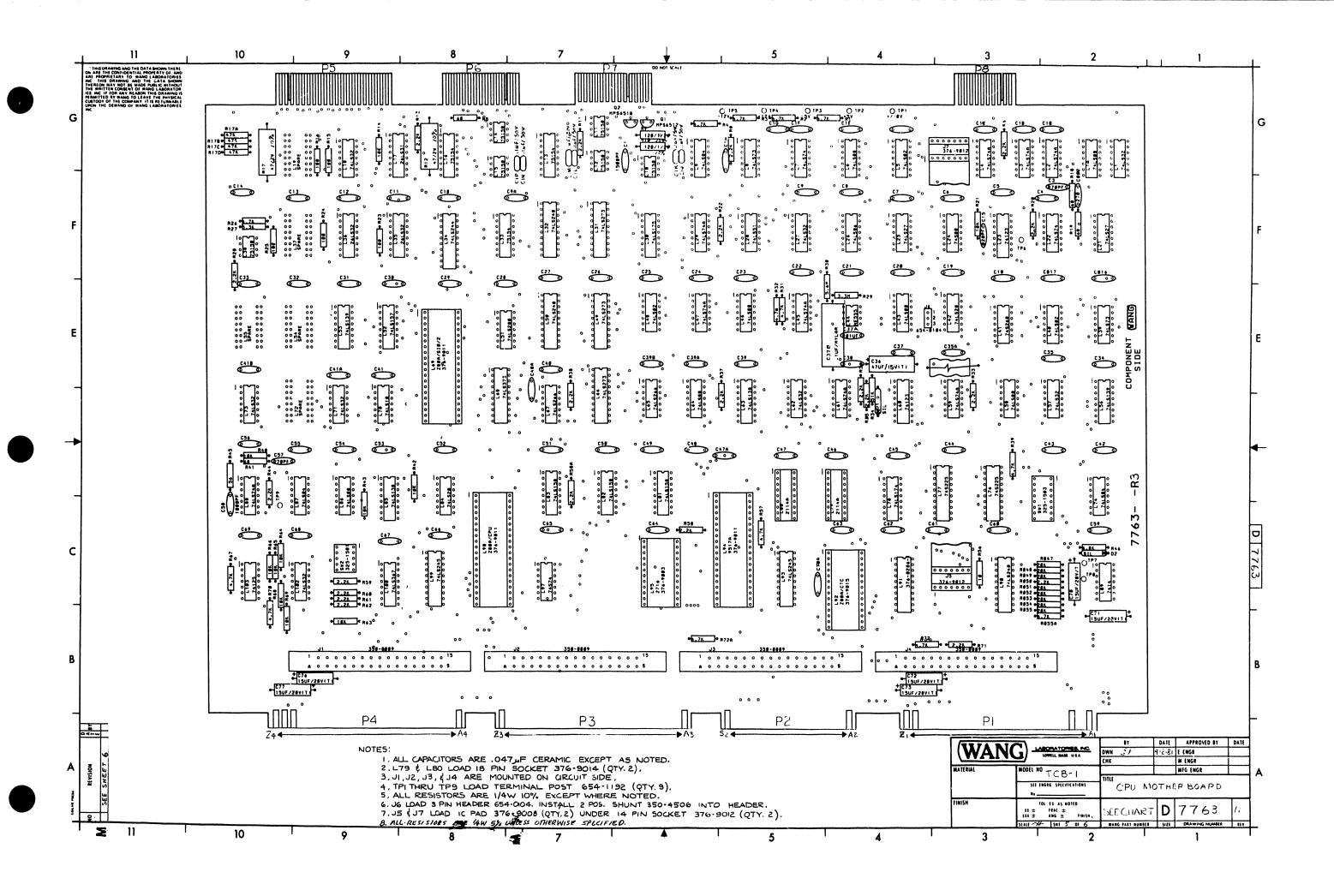

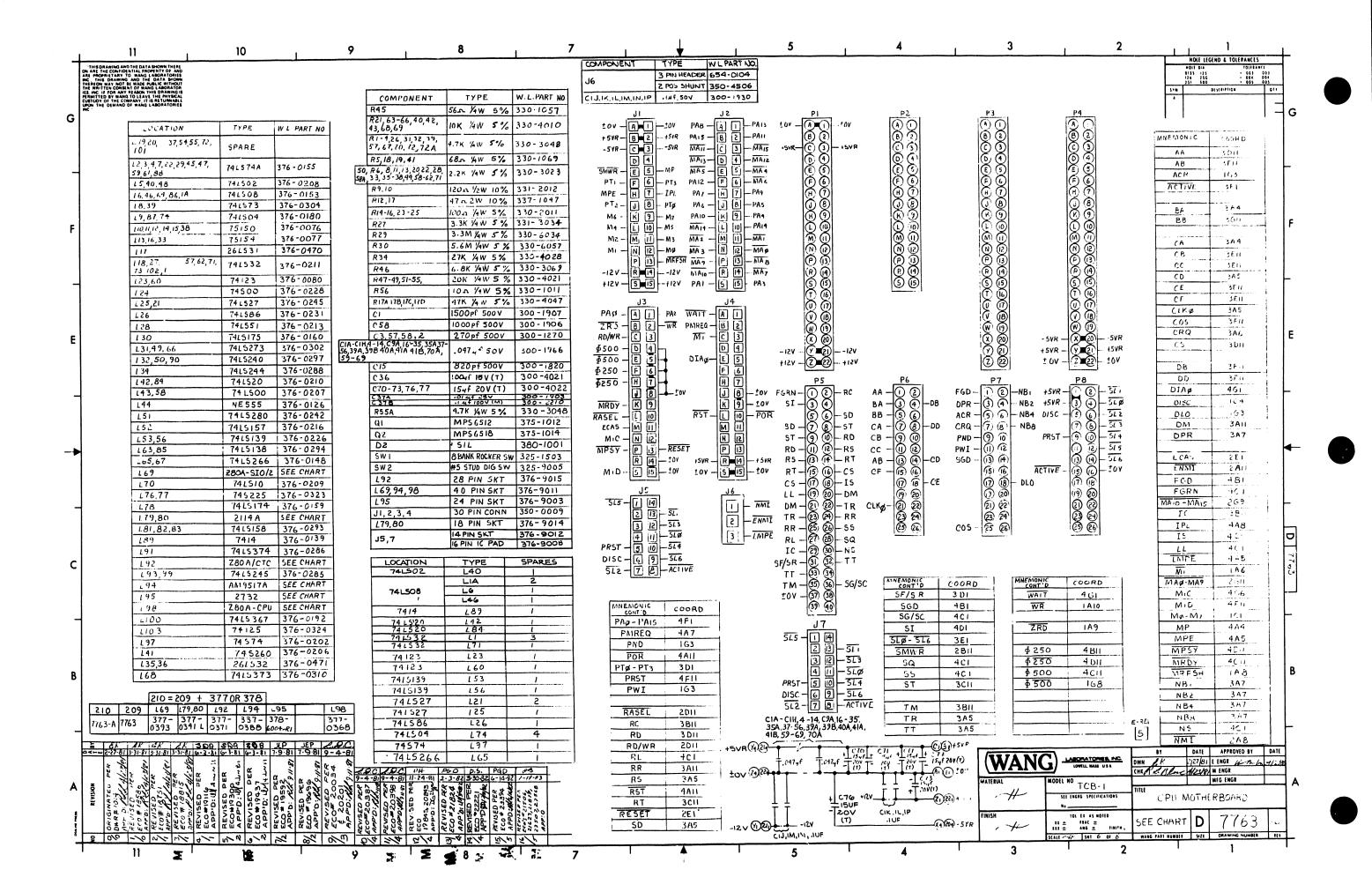

Figure 2-4 TCB-1 Memory Control Section

Figure 2-5 DLP 64/128 Memory Control Section

Address Arbitrator - The address arbitrator consisting of 4 multiplexor chips, selectively gates processor or data link address lines as inputs to row and column memory address latches. These chips reside at locations L50, L70, L90, L108 on a DLP 64 or DLP/128; L86, L87, L105, L106 on a TCB-1.

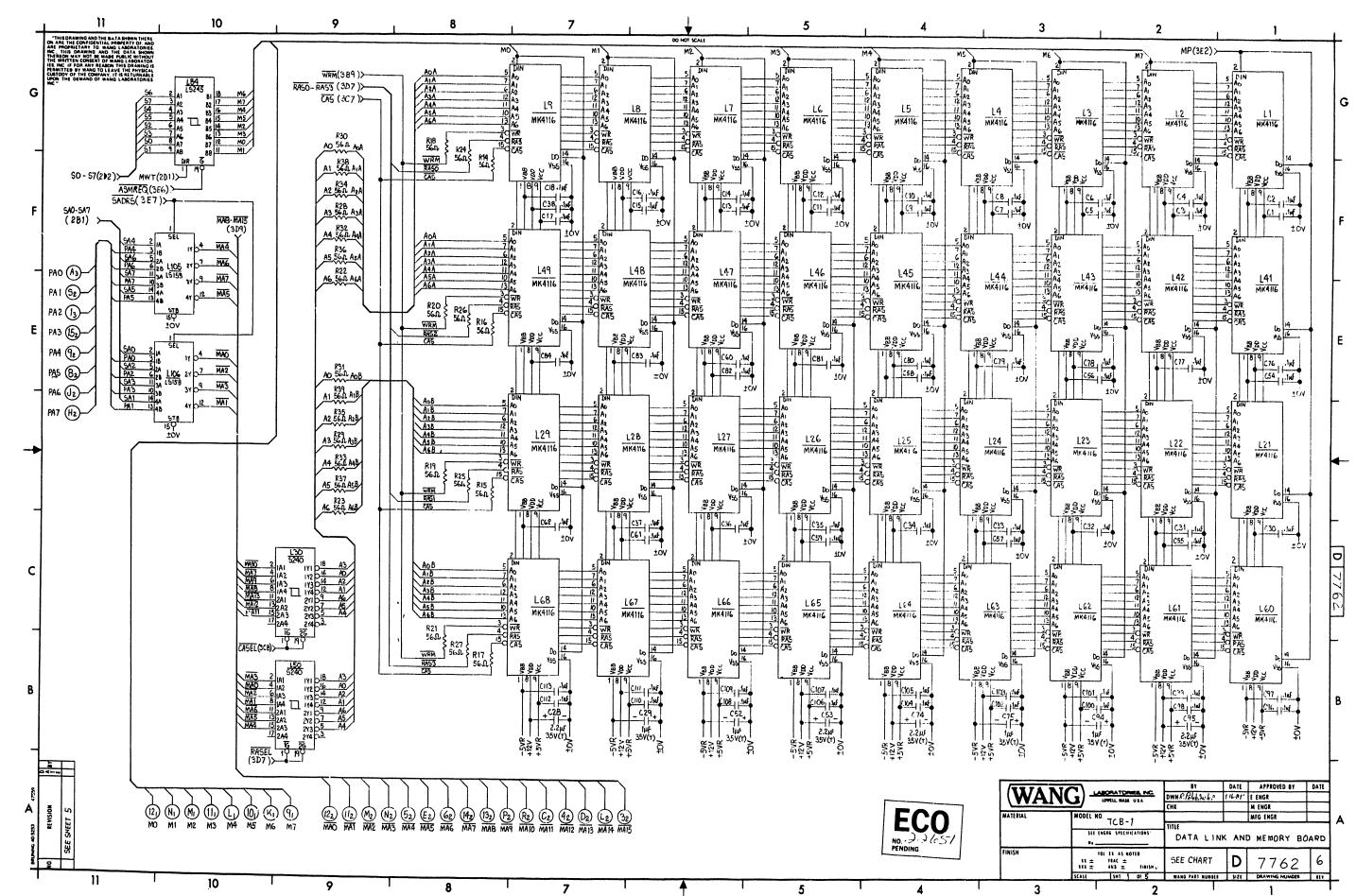

Memory - The memory of the TC controller contains all the controller operating software as well as buffers for communication data being transferred between a master OIS or VS system and the communication line. The memory is organized as 8 bit data bytes, with each byte having its own parity bit. Depending on the controller, the memory is either 64K or 128K bytes wide (see Figure 2-6). The TCB-1 uses 16K X 1 Dynamic RAMS to obtain the overall size requirement, whereas the DLP 64 and DLP 128, use 64K X 1 chips. Note that on the DLP 128, 128K is arranged in two 64K blocks referred to as I-Space and D-Space memory.

| TCB-1 (64K)                            | DLP 64 (64K) | DLP 128 (128K)                |

|----------------------------------------|--------------|-------------------------------|

| L1-L9<br>L21-L29<br>L41-L49<br>L60-L68 | L20-L28      | I-Space D-Space L20-L28 L1-L9 |

Figure 2-6 RAM Chip Layout

Opcode Latch (DLP 64/128 only) - This 8 bit D-type latch (L42), is loaded with an instruction opcode at the end of a Z80A-CPU opcode fetch cycle (M1). Its contents (opcode) are used to address the I/D PROM.

Bit Shifter (DLP 64/128 only) - The bit shifter, is a 4 bit shift register used to steer memory selection logic to either I-Space or D-Space. It is loaded at the end of a CPU Ml cycle with the low order 4 bits read from the I/D PROM. Each subsequent memory request shifts bits out (from the QD bar) providing a steering mechanism for the memory selection logic. The bit shifter resides at location (L44).

Memory Selection Logic (DLP 64/128 only) - The memory selection logic is responsible for generation of memory row address strobe pulses. One of two pulses may be generated - RASI or RASD which respectively select I-space or D-space for memory access. Major portions of this circuitry reside at locations L64, L47, L48, L66-L68 and L49.

Decode PROM (DLP 128 only) - The decode PROM is a 2K X 8 PROM contained on the daughterboard. The decode PROM is divided into eight pages with each page consisting of 256 bytes. Address election within a page is provided by the output of an opcode latch (L42). Decode PROM page selection is accomplished via PROM address lines A8-A10, which are outputs of a D-type latch (L45).

The decode PROM outputs a code that is used as follows. Bits zero to three of this code is routed to the bit shifter for use as a steering mechanism for I space and D space memory accesses. Bits four, five and seven are routed to L45 and contain code for changing the page accessed in decode PROM. Accessing another page in decode PROM would be typical of an instruction that requires two opcode fetches. Bit six is tested by the hardware to determine if an illegal PROM address (IPA), has been accessed. The decode PROM code is used for generation of maskable and non-maskable interrupts, dual M1 cycle instructions, etc. Decode PROM resides at location (L41).

The codes contained in the decode PROM are derived by examining each Z80A instruction and deciding where the next operation after the opcode fetch is to take place (I space or D space).

### 2.4.1 Memory Control Section Overview

Controller memory access is granted on a priority basis. The 928 Data Link section has the highest priority while the CPU and DMA respectively have the next lower priorities. Memory address arbitration is controlled by the signal SADRS which, by its state (0 or 1) selects either data link memory addresses (SAO-SA15), or processor (CPU/RAM) memory addresses (PAO - PA15), to be gated to the memory address lines MAO - MA15. These (MAO - MA15) lines in turn are used to form row (RAS) and column (CAS) addresses.

### 2.4.1.1 TCB-1 Memory

TCB-1 memory is laid out as 4 banks with each bank having 9 16K X 1 DRAMS (MO - M7, MP). Bank selection is provided by decoding address lines MA14 and MA15. Address lines MAO - MA13 form row and column addresses.

### 2.4.1.2 DLP 64/128 Memory

The DLP 64 and DLP 128 contain 64K bytes and 128K bytes of memory respectively. Each use 64K X 1 DRAMs, to meet their respective size allocations. The DLP 128 memory is arranged in two 64K blocks referred to as I-space (instructions), and D-space (data).

The DLP 64 and DLP 128, have added memory control circuitry not available on the TCB-1. On the DLP 64 this circuitry is not used. This is due to communication software, designed for the TCB-1 and carried over for use on DLP 64-based systems, not having the added instructions required to exercise the added DLP hardware. there we, the remainder of this discussion will relate to the DLP 128, with DLP 64 exceptions noted as required.

I space contains the software instruction code for the DLP 128, as well as the lk Master/Slave Communication area address ('0000'-'03FF'). D space contains variables, pointers, tables, and the stack. D space addresses ('0000'-03FF"), (the MSCA equivalent) cannot be accessed.

DLP 128 memory selection logic can operate in three software selectable modes:

| 1. | I Mode | All memory operations access I space. The DLP 64/128, will default to I mode after any reset (the DLP 64 remains in I mode due to |

|----|--------|-----------------------------------------------------------------------------------------------------------------------------------|

|    |        |                                                                                                                                   |

|    |        | lack of software necessary to change the mode.                                                                                    |

- 2. D Mode All memory operations access D space.

- 3. I/D Mode

Both I space and D space are utilized.

Control circuitry selects the appropriate memory selection circuitry for each selection.

When I/D mode is selected, the opcode latch, along with certain memory selection circuitry is enabled. At the start of a Z80A-CPU instruction fetch (Ml cycle), I space selection is forced by the memory selection circuitry. The opcode is read from memory by the Z80A-CPU and simultaneously applied to the input of the opcode latch. The opcode is loaded into the latch at the end of the Ml request, and provides an address to page 0 of the decode PROM.

At the end of the M1 cycle, the four low order bits of the PROM, output a code that is loaded into a bit shifter. Each subsequent memory request shifts a bit out of the register providing a steering mechanism for the memory selection logic. Every time a '0' is shifted out, D space is enabled (RAS D generation). If a '1' is shifted out, I space is enabled (RAS I generation).

If the instruction requires two opcode fetches the PROM code addressed by the first opcode is used to change the selected PROM page. The new PROM page address is formed via the output of the D type latch.

The second opcode is fetched and addresses the new PROM page which then outputs the appropriate code to the 4-bit - parallel shift register. This sets up selection of I or D space memory as explained above.

Not all 256 Hex combinations (00-FF) are valid for the second opcode. If the second opcode is invalid a special code (Hex 40), is read out of the PROM and generates an illegal PROM address (IPA). This error along with a memory parity error and a deadman timer error will generate a non - maskable interrupt NMI. Refer to Paragraph 2.2.4, for more information relating to the non-maskable interrupt sequence.

# CHAPTER OPERA-TION

## Chapter 3 OPERATING INFORMATION

### 3.1 INTRODUCTION

Chapter 3, provides detail relating to the operation and functional use of the TCB-1, DLP 64 and DLP 128 TC Controllers.

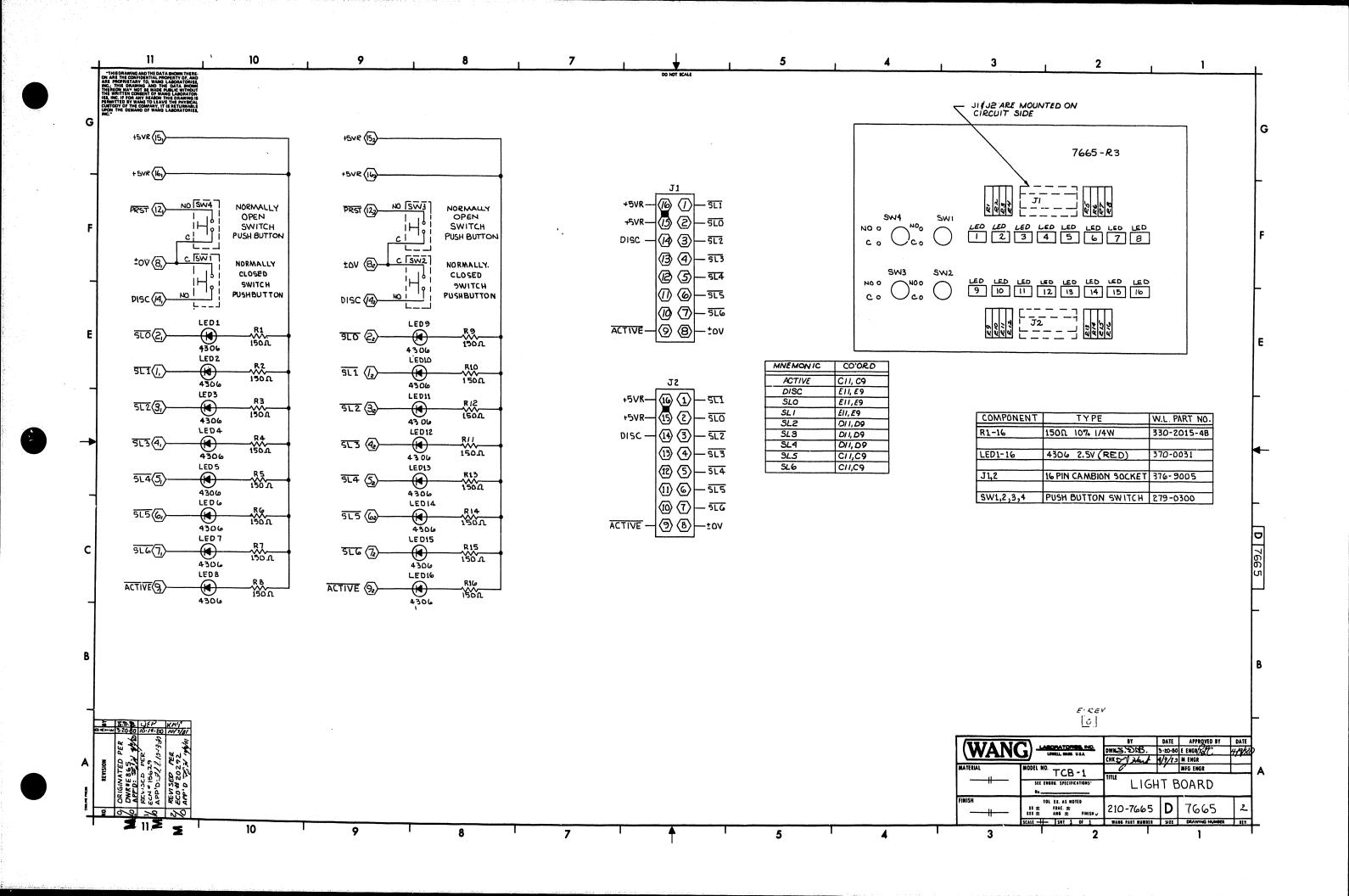

When equipped with a TC Controller, the OIS Master/TCP or VS TCP, requires a new front panel and a rear panel interface connector - the type depending on the interface(s) supported. The front panel LEDS enable monitoring of the interface signals that provide status information during normal operation. Refer to Paragraphs 3.3, 3.4 and 3.5, for more detail regarding front panel LED status indicators.

### 3.2 TC CONTROLLER SOFTWARE SUPPORT

The following paragraphs describe the software packages supported by the TCB-1, DLP 64 and DLP 128 Controllers. Typical system configurations and the required protocol support are also provided. See Table 1-2, for reference to documentation that provides more detailed information regarding protocol use and installation.

The TCB-1

Remote Wangnet (Wang Systems Networking) on OIS, Alliance, and VS Systems; 3270 on OIS and Alliance Systems.

The DLP 64

Remote Wangnet (WSN) on OIS, Alliance and VS Systems; 3270 on OIS and Alliance Systems; SNA on VS Systems.

The DLP 128

SNA on OIS and Alliance Systems; Teletex on OIS, Alliance and VS Systems.

### 3.2.1 3270 Emulation

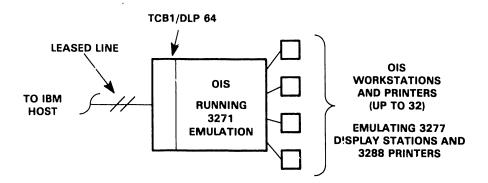

When configured to operate with a TCB-l or DLP 64 TC Controller running 3270 Emulation Software, an OIS master appears (emulates) to a host to be a remotely located 3271 Control Unit while OIS workstations emulate the 3277 Display Station and 3288 Printer. In this configuration the host controls the emulated control unit which in turn controls the emulated devices. A BISYNC polling protocol is employed and intended for use over a multi-point leased line which supports up to 32 control units. Each control unit may support up to 32 devices.

Figure 3-1 3270 Emulation Operation

### 3.2.2 Asynchronous Operation

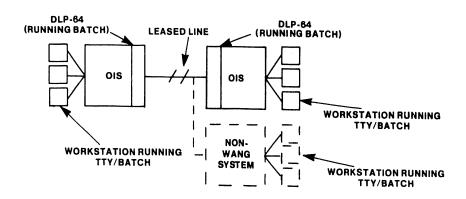

When equipped with communication software that emulates Teletype (TTY), an OIS System can send a document to, or receive a document from, another OIS or a non-Wang system that supports the same protocol, in a leased-line or dial-up-line environment. TTY emulation software also provides a limited batch capabilty by allowing an entire document to be sent and received by a Wang or non-Wang Systems.

Since asynchronous protocols are traditionally interactive in nature, emulation software operates in the foreground through a workstation that is dedicated to sending and receiving information while the communications activity is in process. When communication occurs through a system based TC controller (DLP-64), the activity take place in the background allowing workstations to perform other functions.

Figure 3-2 Asynchronous/Bisynchronous Operation

### 3.2.3 Bisynchronous Operation

Communication between two OIS Systems, and with non-Wang Systems, is supported by software that emulates IBM 2780 and 3780 Bisynchronous protocols. The Wang WPS program, is intended for batch communication between two OIS-Systems that support IBM 2780 or 3780, in a point-to-point, half-duplex, bisynchronous environment via a leased or dial-up network. WPS enables transfer of files and libraries between two OIS Systems.

Batch 2780/3780 Emulation Software, allows for batch communications with non-Wang Systems. Batch emulation software supports point-to-point, half-duplex, Bisynchronous communication over leased, or switched (dial-up) networks. Emulation Software allows VS data files or libraries, to be transmitted to other systems and workstations that support 2780 or 3780 protocols. Batch emulation software may operate in foreground mode through a workstation that is dedicated to sending and receiving information while the communications activity is in process. When communication occurs through a system based TC controller (DLP-64), the activity take place in the background allowing workstations to perform other functions (Figure 3-2).

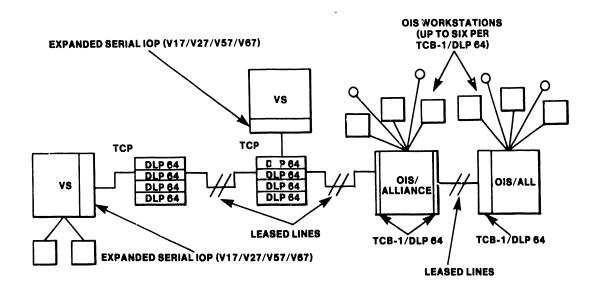

# 3.2.4 Remote Wangnet (WSN)

Using Remote Wangnet (WSN) software a VS System host is currently capable of sending a document or file to, or receiving a document or file from, a remotely located OIS System and an OIS Workstation is capable of remotely logging on to the VS host in a dedicated or leased line environment (point to point or multi-point) as shown in Figures 3-3 and 3-4. Present releases include VS to VS, OIS to OIS configurations. The TCB-1 or DLP 64, operating with Remote Wangnet (WSN) enables the VS System host to send and receive a document or file to and from several OIS Systems (Nodes) concurrently to provide paths for file transfer and log-on services for each.

Figure 3-3 Remote Wangnet (WSN) Point-to-Point

# 3.2.5 SNA

When an OIS or VS (system master) is operating with 3274 emulation software, an OIS based DLP 128 Controller or a DLP 64 Controller housed in a TCP, will provide users with interactive access to applications run from an IBM host. Emulation software will support both physical and virtual workstations as well as multiple printers. The emulation runs as an SNA multiple logical unit supporting concurrent data streams to and from the host. By implementing Synchronous Data Link Control (SDLC) line protocol, system master logical devices will communicate at speeds up to 9600 bits per second. Emulation software (3274), communicates in half-duplex mode with a host computer that supports 3274 Cluster Controllers, with up to 32 terminals or printers (3278 Display Stations and 3288 Printers).

When operating with 3777 Emulation software a VS master can access an IBM hosts batch processing capability operating in the SNA format employing SDLC line protocol. The system master SNA emulator can communicate in half-duplex mode with an IBM host over multi-point lines using IBM compatible EBCDIC transmission code. The 3777 emulator, supports up to six concurrent data streams to and from host logical units.

OR

Figure 3-5 SNA 3274/3777 Emulation

# 3.2.6 Teletex

Teletex service employs a standard specified by the CCITT as a high speed replacement for Telex. The Teletex service as implemented allows a document to be created and printed locally and then printed with full error checking to any other Teletex terminal.

### NOTE

When installing Teletex software the workstation date and time option and TCP modification are required.

The OIS Teletex terminal facility will provide any Wang user with the capability of exchanging correspondence (Teletex document) with other Teletex (Wang or Vendor System) via public data networks.

Figure 3-6 Teletex Operation

# 3.3 OIS 3270 EMULATION FRONT PANEL LED INDICATORS

During normal operation the eight TC front panel LEDS indicate the presence of interface signals. The eighth LED is a D.C. power indicator. The following table describes the LED indicators of an OIS System when running 3270 Emulation Software.

Table 3-1 OIS 3270 Front Panels LEDS

| LED Indication           | Description                                                                                                                                                                    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l-Receive Data           | Rapidly flashing LED indicates transitions between ones and zeroes representing serially encoded characters received by data communications equipment (DCE) from a remote DTE. |

| 2-Transmit Data          | Rapidly flashing LED indicates transitions between ones and zeroes representing serially encoded characters generated by the data terminal equipment (DTE).                    |

| 3-Clear to Send          | LED on indication generated by the DCE to indicate whether or not the data set is transmit enabled.                                                                            |

| 4-Request to Send        | LED on indication generated by the data terminal to condition the local DCE for data transmission.                                                                             |

| 5-Data Carrier Detect    | LED on indication generated by the DCE indicating that data transmission from the remote data set to the DTE is enabled.                                                       |

| 6-Data Terminal Detected | LED on indication generated by the DTE used to control switching of the DCE to the communication channel.                                                                      |

| 7Data Set Ready          | LED on indication generated by DCE indicates that the DCE is capable of transmitting and receiving data signals.                                                               |

| 8-Power Indicator        | On during normal operation.                                                                                                                                                    |

# 3.4 REMOTE WANGNET (WSN) FRONT PANEL LED INDICATORS

The following paragraphs provide reference to the status of LED indicators used to monitor interface signals when running Remote Wangnet Emulation Software. On an OIS, interface signals are monitored from the TC front panel or the TCP front panel. On a VS, interface signals are monitored from the TCP front panel LED's. LED's four and five on OIS Systems differ in Table 3-2.

Table 3-2 Remote Wangnet (WSN) LED Status Indicators

| LED Indication                                    | Description                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-System Activity                                 | In normal operation LED #1 will blink several times per second to indicate that microcode has been loaded; and in the absence of other lights, the system is waiting for a line to come up. If the LED is flashing slowly, it indicates that a large amount of message traffic is being processed and that the message traffic requires compression. |

| 2-Received Valid Data                             | This LED indicates that a message frame was received without a CRC error. Each time a message is received, the LED will invert its state. That is, if the LED is on, it will then turn off when a subsequent message is received.                                                                                                                    |

| 3-Transmitter Active                              | When asserted this LED indicates that the transmitter is currently in the process of transmitting a frame on the line. The off state indicates that the transmitter is not active.                                                                                                                                                                   |

| 4-Data Carrier Signal Detected (VS Systems, TCP)  | This LED is asserted when a remote (secondary) system is actively transmitting transmit data.                                                                                                                                                                                                                                                        |

| 4-Data Carrier Signal Detected (OIS Systems, TCP) | This LED asserts to indicate that both the local and primary modems are capable of transmitting and receiving data. If modems are not in use and the LED asserts, then it is an indication that the VS Primary software is operating.                                                                                                                |

| 5-Virtual Circuit Active                          | This LED indicates that at least one virtual circuit has been established. As an example, it may indicate that a user has logged on or attempted to log onto the VS, or that a batch file manager is active. This LED may also indicate that a workstation is using a TC controller prior to it being IPL'ed as part of the control functions menu.  |

| Remote Wangnet | (WSN) | LED | Status | Indicators | (cont,d) |

|----------------|-------|-----|--------|------------|----------|

|----------------|-------|-----|--------|------------|----------|

| 6-Activity to OIS/VS                 | This LED asserts when the TC controller is in the process of talking to the local host.                                                               |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-TC Controller Refusing New Traffic | This LED asserts when the controller has more traffic that it can handle. Additional messages will be refused.                                        |

| 8-Diagnostic Mode                    | This LED when asserted indicates normal operation of the TC controller. If blinking the controller is in diagnostic mode.                             |

| TC Controller Idle                   | A single light rotating on the TCB-l from left to right, indicates that the controller is idle and may be loaded by the control menu and initialized. |

# 3.5 TELETEX FRONT PANEL LED INDICATORS

The following table provides reference to the status of LED indicators used to monitor interface signals when running Teletex Terminal Facility Software. On an OIS, interface signals are monitored from the TC front panel or a TCP front panel. On a VS, interface signals are monitored from the TCP front panel LEDs.

Table 3-3 Teletex Front Panel LED Indicators

| LED Indication          | Description                                                                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| l-Document Received     | When on this LED indicates that a document was received or partly received (at least six sectors worth). LED stays on until the log file is purged. |