# Wang LOCI

Service Manual

WANG LABORATORIES, INC.

TEWKSBURY, MASS. 01876 • TEL: 617-851-7311 • TWX: 710-343-6769

# **FOREWORD**

This manual will be revised periodically for the purpose of providing accurate, up-to-date information to all field personnel and LOCI users.

Meanwhile, when new information is not of such volume as to require a complete revision of the manual, change pages will be distributed for easy insertion to keep the manual updated at all times pending the publication of the revised manual.

# **CONTENTS**

| Ι.       | Introduction                        | 1  |  |  |  |

|----------|-------------------------------------|----|--|--|--|

|          | A. Scope                            | 1  |  |  |  |

|          | B. LOCI Configurations              | 1  |  |  |  |

|          | C. Possible Combinations            | 1  |  |  |  |

| II.      | Command Definitions                 | 2  |  |  |  |

| III.     | Circuit Card Descriptions           | 7  |  |  |  |

|          | A. General, Technical, and Physical | 7  |  |  |  |

|          | 1401A Card                          | 9  |  |  |  |

|          | 1402A Card                          |    |  |  |  |

|          | 1403A Card                          |    |  |  |  |

|          | 1404A Card                          |    |  |  |  |

|          | 1405A Card                          |    |  |  |  |

|          | 1407A Card                          |    |  |  |  |

|          | 1408A Card                          |    |  |  |  |

|          | 1410 A Card                         | 2  |  |  |  |

|          | 1411A Card                          |    |  |  |  |

|          | 1412A Card                          |    |  |  |  |

|          | 1501A Card                          |    |  |  |  |

|          | 5123A, 5129A Cards                  |    |  |  |  |

| IV.      | CU-3/CU-4 Circuit Description       |    |  |  |  |

|          | A. Output Multiplex                 |    |  |  |  |

|          | B. Format Logic                     |    |  |  |  |

|          | C. Format Timing                    |    |  |  |  |

|          | D. Teletype Interface               |    |  |  |  |

|          | E. Code Matrix                      | 4- |  |  |  |

|          | F. Reader Control                   | 41 |  |  |  |

| V.       | Packing and Shipping                | 42 |  |  |  |

| VI.      | Problems                            | 43 |  |  |  |

| VII.     | Conclusion                          | 45 |  |  |  |

| Appendix |                                     |    |  |  |  |

|          | Signal Source and Disposition       | 47 |  |  |  |

# I. INTRODUCTION

#### A. SCOPE

This manual is intended for use by those who have had experience in and some exposure to electronic computer technology. Specifically, its purpose is to aid repair personnel in LOCI malfunction isolation and/or correction and, in some cases, to provide enough information to enable the service man to correct the problem.

The manual contains general and technical description of the componentry, electronic and mechanical, of the LOCI. The information presented, together with discussion of some of the more common malfunctions, is deemed adequate to provide the LOCI user with the necessary knowledge to effect a solution for any problem.

Information contained in this manual shall not be construed by the user, however, as authorization to modify the design of the LOCI.

#### **B. LOCI CONFIGURATIONS**

**LOCI-1** - No longer in production; it was the basic unit, having no storage or programming capabilities.

**LOCI-2** - Now the basic unit; it has storage capability, as well as 80 steps of program capacity (one reader).

**LOCI-2a** - The basic LOCI-2, with 16 storage registers and 80 steps of program capacity (one reader).

LOCI-2s - The LOCI-2, without program option or storage capacity.

**LOCI-2S2** - The LOCI-2, without program option, but with 2 storage registers.

LOCI-2S4 - The LOCI-2, without program option, but with 4 storage registers.

#### C. POSSIBLE COMBINATIONS

The following suffix letters indicate possible combinations with the basic LOCI, each suffix representing optional peripheral equipment which can be added to the basic unit.

(a) A second card reader option, possible with LOCI-2 or LOCI-2a.

NOTE: The following options are available only with the LOCI-2a.

- (b) Teletype Model 33 Input/Output Writer.

- (c) Presin Printer.

- (d) Teletype and Control Unit 3 (CU-3).

| LOCI Command                  | LOCI Key       | LOCI Code | Definition                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clear Error                   | CLEAR<br>ERROR | (01)      | This command is given to clear or turn off the error indicator light, which becomes illuminated when the contents of the log register exceeds the limits. The log-register limits are -41.999 999999 to 41.999 999999.                                                                                                                                  |

| Clear W-Register              | CLEAR W        | (02)      | This command is given to clear the work, or display, register. When this command is executed, the LOCI will display zeros. It also returns the Memory Selection (MS) Counter to zero.                                                                                                                                                                   |

| Clear Accumulator             | CLEAR A        | (03)      | This command is given to clear the contents of the A-register only.                                                                                                                                                                                                                                                                                     |

| Square Root                   | √——            | (04)      | This command is a mathematical operation which calculates the square root of the W-register and adds that root to the L-register.                                                                                                                                                                                                                       |

|                               |                |           | $L+\frac{1}{2}log_{e}(W) \longrightarrow L$                                                                                                                                                                                                                                                                                                             |

| Reciprocal of the square root | 1/√            | (05)      | When this command is given, the LOCI takes the contents of the W-register, calculates the reciprocal of the square root, and adds the log of the reciprocal of that root to the L-register.                                                                                                                                                             |

|                               |                |           | $L^{-1/2}log_{\Theta}(W) \longrightarrow L$                                                                                                                                                                                                                                                                                                             |

| Square                        |                | (06)      | This command takes the contents of the W-register, calculates the square, then adds twice the log of the square in the L-register.                                                                                                                                                                                                                      |

|                               |                |           | $L+2log_{e}(W) \longrightarrow L$                                                                                                                                                                                                                                                                                                                       |

| Reciprocal of the square      | 1/ 🗌           | (07)      | When this command is given, the LOCI takes the contents of the W-register and calculates the reciprocal of the square, then adds the log of that reciprocal to the L-register.                                                                                                                                                                          |

|                               |                |           | $L-2log_{\Theta}(W) \longrightarrow L$                                                                                                                                                                                                                                                                                                                  |

| Memory Selection<br>Counter   | STEP<br>MSC    | (10)      | This is a command which selects or designates which group of storage registers is active. Each group has four registers and each group assumes an MS value which corresponds to the value of the first register in that group. MS values are 0, 4, 8, and 12. The quantity of storage registers is dependent on the type of LOCI used in the operation. |

| LOCI Command     | LOCI Key                                       | LOCI Code                                                                    | Definition                                                                                                                                                                                                                                                                |

|------------------|------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write            | WRITE                                          | (11)                                                                         | The WRITE command obtains a printout of what is displayed on the W-register. Printouts can be obtained from connected Teletype machines, which can produce both a punched tape and/or a regular paper printout to command the Presin Printer to print.                    |

| Multiplication   | X                                              | (12)                                                                         | This command multiplies the content of the W-register by the contents of the L-register. At the completion, the product will be in logarithmic form in the L-register. In fact, the $\times$ operation adds the log of W to L. L+log <sub>e</sub> (W) $\longrightarrow$ L |

| Addition         | +                                              | (13)                                                                         | This operation adds the contents of the W-register to the contents of the A-register. At completion, the sum, or total, is in the A-register.                                                                                                                             |

|                  |                                                |                                                                              | A+W> A                                                                                                                                                                                                                                                                    |

| Anti-log         | ANTI<br>LOG                                    | (14)                                                                         | This command takes the anti-log of the contents of the log register and displays the answer in the log form. At completion of the command, the L-register is cleared.                                                                                                     |

| Subtraction      | -                                              | (15)                                                                         | This command subtracts the contents of the W-register from the contents of the A-register.                                                                                                                                                                                |

| Decimal Point    | •                                              | (16)                                                                         | This command places a decimal point in the LOCI at the appropriate place. It can be used only once on each display. The decimal point is entered in the W-register only.                                                                                                  |

| Division         | 0                                              | (17)                                                                         | This command divides the contents of the log register by the contents of the W-register.                                                                                                                                                                                  |

| Numbers 0 thru 9 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | (20)<br>(21)<br>(22)<br>(23)<br>(24)<br>(25)<br>(26)<br>(27)<br>(28)<br>(29) | Each of these commands enters a digit into the W-register in succession, starting with the high-order number, or left-hand side of the display.                                                                                                                           |

|                                                   | 00111111       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------|----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCI Command                                      | LOCI Key       | LOCI Code    | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Run                                               | RUN            | (32)         | This operation is directly dependent on the Mode Selection Switch, which has three positions, STEP, AUTO, and MNL. When the switch is in any one of these positions, there are other dependents which must be considered. The switch advances the program by 1 step in STEP mode, continues the program which might have been stopped intentionally in the AUTO mode, and executes the command manually when indicated by toggle switches in MANL mode. |

| Sign ±                                            | CHANGE<br>SIGN | (33)         | This command changes the sign of the contents of the W-register only. It will not affect the contents of the register per se.                                                                                                                                                                                                                                                                                                                           |

| Input MX<br>Output MX                             |                | (34)<br>(35) | These are special option commands used with peripheral equipment.                                                                                                                                                                                                                                                                                                                                                                                       |

| Prime                                             | PRIME          | (36)         | This operation clears the W, A, and L registers and the Memory Selection Counter. It puts zeros into the three registers, and gives a zero value to the MSC.                                                                                                                                                                                                                                                                                            |

| Stop                                              |                | (37)         | This command stops the program. When it is given, the calculating halts, as does any equipment (Teletype, etc.) connected to the LOCI.                                                                                                                                                                                                                                                                                                                  |

| Work Register to<br>Program Counter (PC<br>W → PC | )              | (40)         | This command alters the value of the PC. It takes the first two digits regardless of the position of the decimal point in the W-register and places the number into the PC. This command gives freedom of movement within the program. (The PC is a light indicator which indicates the location of the command to be executed on the program.)                                                                                                         |

| $W \longrightarrow XPC$                           |                | (41)         | This command is similar to the W                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Work Register to Decrement Counter (DC) W DC      |                | (42)         | This command puts the first two digits of the W-register into the DC if the decimal point is in the second position. If there is only one decimal point position, only one digit enters the DC. The functions of the DC are to control the number of iterations which has been predetermined, or to count the number of times a sequence has been performed.                                                                                            |

| LOCI Command                                                | LOCI Key | LOCI Code | Definition                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $DC \longrightarrow W$                                      |          | (43)      | This command is the converse of W $\longrightarrow$ DC, and takes the contents of the DC and puts it in the W-register. This option does not destroy the contents in the DC.                                                                                                                                                                                        |

| Work Register to<br>Accumulator Register<br>W → A           |          | (44)      | This command enters the contents of the W-register into the A-register. It does not destroy the contents of W.                                                                                                                                                                                                                                                      |

| Accumulator Register to Work Register A $\longrightarrow$ W |          | (45)      | This command is the converse of W $\longrightarrow$ A, and it will not destroy the contents of A.                                                                                                                                                                                                                                                                   |

| Work Register to<br>Log Register<br>W → L                   |          | (46)      | This command puts the log of the contents of W into L. It will not destroy the contents of W. However, if the contents of W are 100, the Error Indicator will light, indicating that the limits of L have been exceeded. If W 10.00000, W will be re-aligned to the xx. xxxxxxxxxe format.                                                                          |

| Log Register to Work Register L                             |          | (47)      | This command puts the contents of $\  \  \  \  $ into $\  \  \  $ w, and clears the contents of $\  \  \  \  $ after the operation.                                                                                                                                                                                                                                 |

| Store PC, DC, then W → PC                                   |          | (64)      | This command causes the following events:  PC → PCS (PC Storage)  DC → DCS (DC Storage)  W → PC  Information previously stored in PCS and DCS will be destroyed when this command is executed, and the contents of PC and DC will be put into the PCS and DCS registers. The DC register will remain the same, and the PC register will now have the contents of W. |

| Recall PC and DC                                            |          | (65)      | This command exchanges the contents of the PC and PCS, and puts the contents of DCS into the DC.  PCS $\stackrel{\longleftarrow}{\longrightarrow}$ PC DCS $\stackrel{\longleftarrow}{\longrightarrow}$ DC                                                                                                                                                           |

| Decrement                                                   |          | (66)      | This command reduces the contents of the DC by one.                                                                                                                                                                                                                                                                                                                 |

|                                                                                                             | 00111            | 1017 11 10 1 |                                                                                                                                                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------|------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LOCI Command                                                                                                | LOCI Key L       | OCI Code     | Definition                                                                                                                                                                                        |  |  |

| The following test commands are program tools to maneuver within the program when certain conditions exist: |                  |              |                                                                                                                                                                                                   |  |  |

| Test Error:                                                                                                 |                  | (67)         | If there is no overload of any register, this command advances the PC by four counts. If an overload exists, it advances the PC by one count. There is no effect on the contents of any register. |  |  |

| Test DC = 0                                                                                                 |                  | (70)         | If DC is zero, this command advances the PC by four counts. If DC is not zero, it advances the PC by one count. There is no effect on the contents of any register.                               |  |  |

| Test A = 0                                                                                                  |                  | (71)         | If A is zero, the command advances the PC by four counts. If A is not zero, it advances the PC by one count. There is no effect on the contents of any register.                                  |  |  |

| Test W = 0                                                                                                  |                  | (72)         | If W is zero, this command advances PC by four counts. If W is not zero, it advances PC by one count. There is no effect on the contents of any register.                                         |  |  |

| Test W for - sign                                                                                           |                  | (73)         | If W is negative, the command advances the PC by four counts. If W is not negative, it advances the PC by one count. There is no effect on the contents of any register.                          |  |  |

| Test L for - exponent                                                                                       | t                | (74)         | If the contents of L are negative, the command advances PC by four counts. If L is not negative, it advances PC by one count. There is no effect on the contents of any register.                 |  |  |

| The following commands are used with some of the optional equipment available, namely, the Teletype:        |                  |              |                                                                                                                                                                                                   |  |  |

| Carriage Return                                                                                             | CAR'GE<br>RETURN | (75)         | This command can make the Teletype carriage return, and also make it skip to a new line if needed.                                                                                                |  |  |

| Read                                                                                                        | READ             | (76)         | This command obtains information from the Teletype machine reader, which supplies the LOCI with an input from a paper tape.                                                                       |  |  |

| Read                                                                                                        | READ             | (77)         | This command obtains information from a second tape reader which supplies the LOCI with an input from a paper tape.                                                                               |  |  |

# III. CIRCUIT CARD DESCRIPTIONS

The LOCI (LOgarithmic Computing Instrument) is an electronic computing machine containing a number of printed cards. Each LOCI contains from 8 to 11 cards, depending upon the machine model. Each card is described herein in detail.

# A. GENERAL, TECHNICAL, AND PHYSICAL

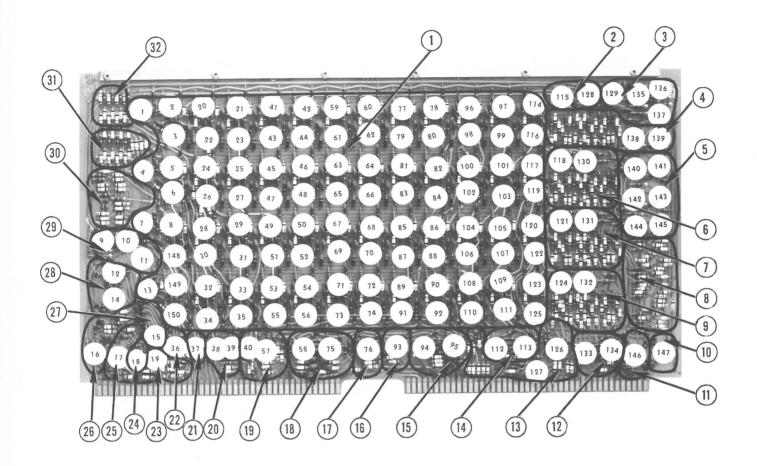

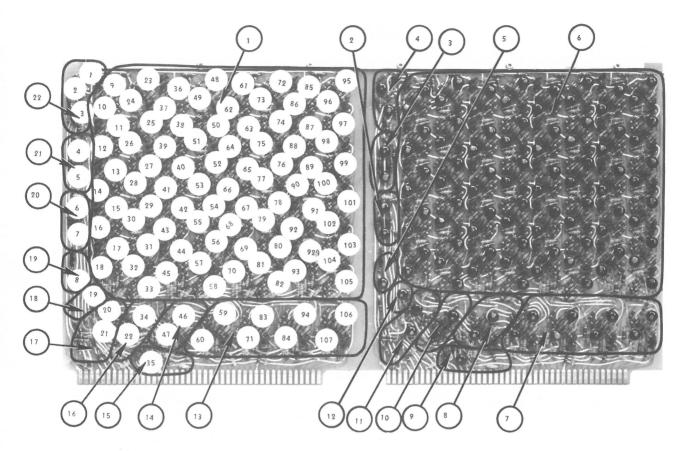

The descriptions on the following pages are accompanied by illustrations of the numbered cards which are to assist the user and the technician to locate specific circuitry.

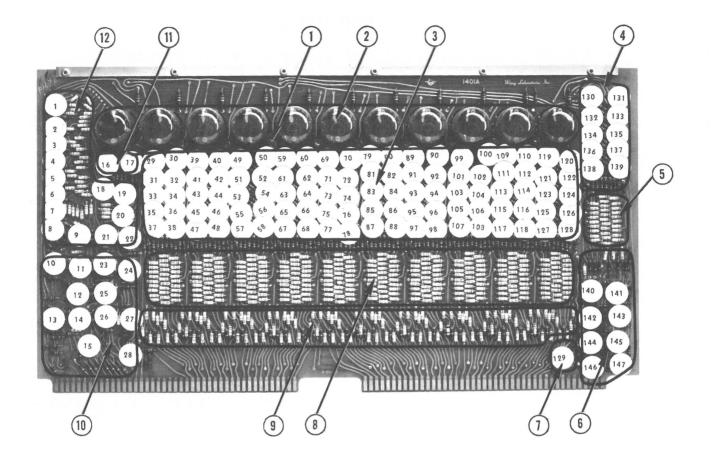

- 1. Decimal Point Position (Neon Bulb)

- 2. Readout Tubes

- 3. Transistor Drives for Readout Tubes

- 4. Blanking Circuit

- 5. Blanking Circuit Decoder Network

- 6. ER Counter Circuit

- 7. Input Driver to Blanking Circuit

- 8. Decoding Circuit for Readout Tubes

- 9. Control Circuits for Data Traveling between cards

- 10. DCN Counter Circuits

- 11. Sign Circuits (SN)

- 12. Decimal Point Positioning Circuits

Note 1:

(Number on the Transistor corresponding with the digit controlled by that transistor. Each of the ten circuits are the same)

This card contains 11 readout\* tubes. The first card is for the sign (plus or minus); the others are for each of the 10 digits in the W-register.

There are 10 neon bulbs for positioning the decimal point. The card also contains associated decoding for displaying the sign, 10 digits, and a decimal point of the W-register. In addition, it contains the W-register decimal-point counter and a digital counter for processing the logarithmic operations.

The diagram of this card shows the locations of the various circuits. The 11 readout tubes are located across the top of the card, and directly below each readout tube is a series of transistors (either Type 35224 or Type S16393), which are used to drive the tubes.

Below the transistor drivers are the germanium diodes which, with the transistors, comprise the decoding circuits of the readout tubes.

At the bottom of the card, and centered, is a series of germanium diodes and resistors comprising the control circuits for the data traveling between cards.

In the lower right-hand corner of this card is the Entry Memory (EM) register counter circuit, which consists of four (4) flip-flop circuits. The ER counter indicates which digit is to be entered. It also is used to process either number-to-log or log-to-number functions. The ER is a binary coded decimal (BCD) counter, next to which is the transistor circuitry for entry to the card of the input-blanking signal.

The decimal-point position drivers and decoding circuits are located in the top left-hand corner of the card. The Work-Register (W) decimal counter (DCN) circuit is located in the lower left-hand corner. This circuit consists of four (4) flip-flop circuits.

<sup>\*</sup>These tubes heretofore had been called NIXIE tubes, but since NIXIE is a trade name of a component no longer used at Wang Laboratories the name has been changed in this manual to "readout" tubes to describe their function more closely.

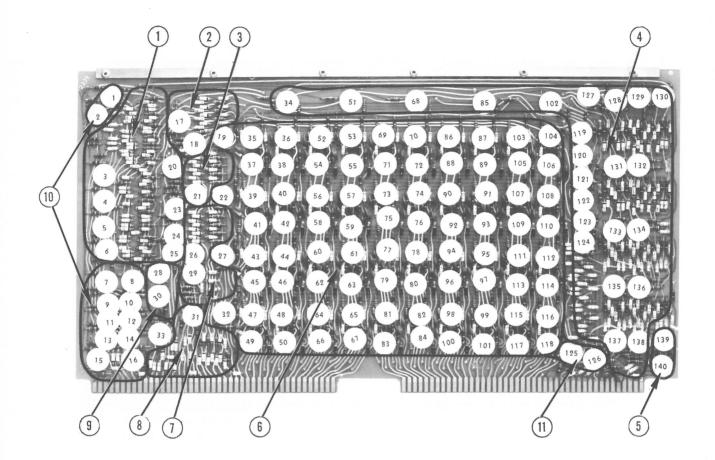

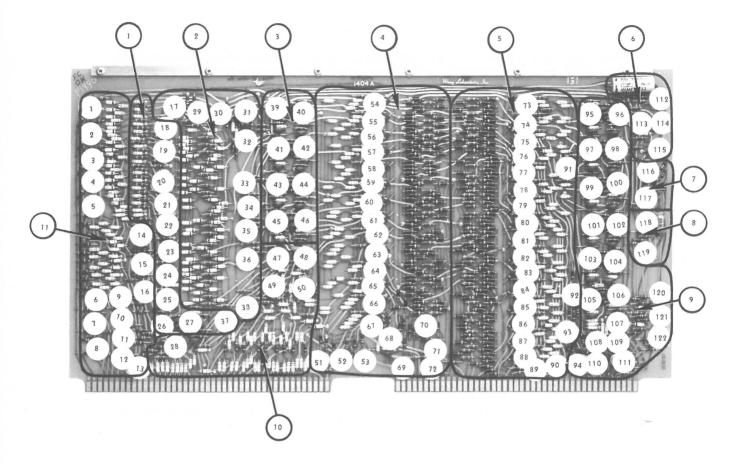

- 1. Number Register Adder Result circuit.

- 2. Number Register Result circuit. (ms, s19, nld, cai, ent, sm, ld.)

- 3. Control Circuit for the command A-W.

- 4. Binary Adder circuits.

- Control circuit for one of the Anti-Log Function signals (CC).

- 6. Circuitry for the ten digits of the Work Register (NR).

- 7., 8. Control circuits for the following signals:

- a) Decoder for the log process output

- b) Memory Select

- c) Decrement Counter.

- 9. Shift Pulse Signal Circuit.

- 10. Adder input control signal.

- 11. Control to Accumulator Register. Stepping. (ASR)

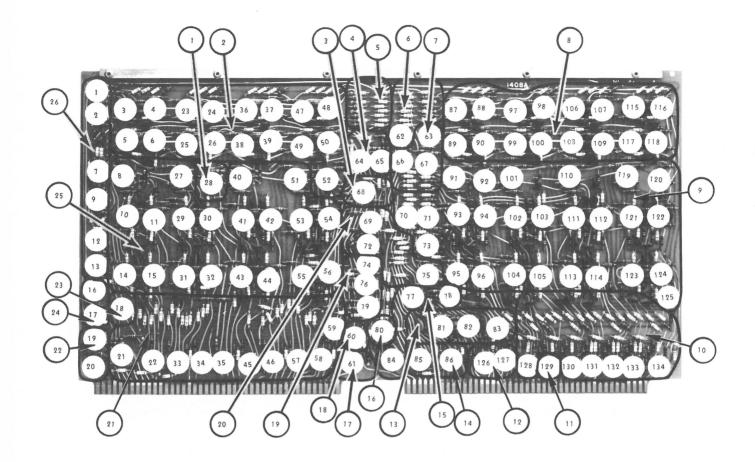

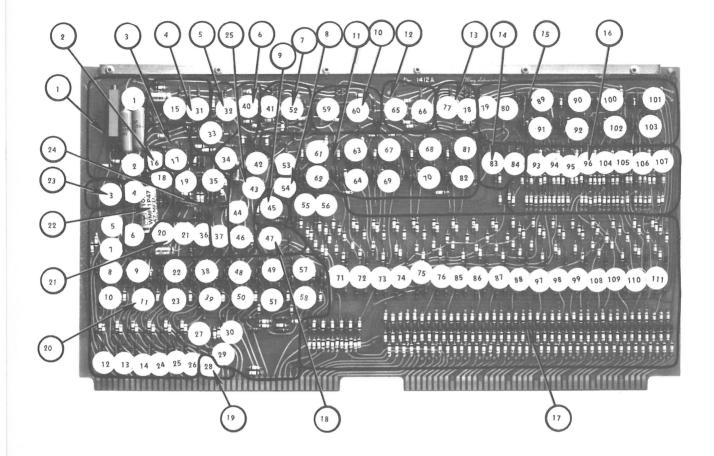

This card contains the 10 digits of the W-register, plus the binary adder used in addition, subtraction, and processing of numbers during log and anti-log operations. It performs the steps for anti-log generation and also the carry-gate process for carry-over of digits.

The diagram indicates the location of the various circuits on this card, in the center of which are 80 transistors and the componentry to form the 10-digit W-register storage units.

Directly to the left of these units are four transistors which comprise the input for the W-register storage.

The four transistors across the top center of the card and all transistors, with the exception of two on the right-hand side, form the Binary Adder circuit. The two transistors in the lower-right center are the DC level control of the 9's complement circuit, between the W-register and the W-register Adder and its indicator.

In the lower right-hand corner are two transistors which are part of a flip-flop network. When this network is OFF, it indicates that the W-register is over.9999999999.

The two transistors in the upper left-hand corner and the 11 transistors in the lower left-hand corner form the driver and decoding circuits for the Adder input signal. There are nine transistors which are located on the left-hand center of the card, which form the driver and decoding circuits for the Adder output signal. At the lower left-center are two transistors which form the number W-register shift-pulse circuit.

On the right-hand center are six transistors, of which four are used to drive the following signals: two drive the CAI, ENT, SM, and LD signals; the other two drive the MS, S19, and NLP 13 signals (refer to signal definitions).

- Circuitry for the storage of the log register information (Bin 1, 2, 4, 8)

- 2. Circuit for the log register shift pulse (LR)

- 3. Log Register Adder result circuit

- 4. Binary 8 (9's complement input circuit)

- 5. Binary 2, 4 and 8 Adder output

- 6. Binary 4 (9's complement input circuit)

- 7. Binary 2 (9's complement input circuit)

- 8. Log Register mixer circuit

- 9. Binary 1 (9's complement input circuit)

- 10. Binary 1 carry circuit

- 11. Gate circuit for the carrier memory of the log register

- 12. Carrier memory of the log register circuit (C1)

- 13. Blocking signal when error has accumulated circuit (LDE)

- 14. Same as thirteen (LDE)

- Memory of number sign of the log register circuit (LSN)

- 16. Control gate for (#15) (LSN)

- 17. Control gate for (#18) (SN)

- 18. Memory of the sign of the work register (SN)

- 19. Main reset of the log register circuit (LRS)

- 20. Circuit which indicates zero in the log register (LR0)

- 21. Circuit indicating a number 1 or greater at the end of an anti-log operation (MS)

- 22. Circuit controlled by memory select used to shift a 1 into the Work Register under certain conditions (MSP)

- 23.)

24. Control circuits for \*\*S\*\* signals  $(S_1, S_2, S_{16})$ 25.

- 26. Control gate for the error signal (ERR)

- 27. Pulse generator circuit (LTP)

- 28. Circuit for the error signal (ERR)

- 29. Circuit indicating positive or negative log (ML)

- 30. Decoder circuit for log and anti-log process (PA)

- 31. Control circuit for the W-L command (LD)

- 32. Control circuit for the Log Register Adder results and log and anti-log process (PA)

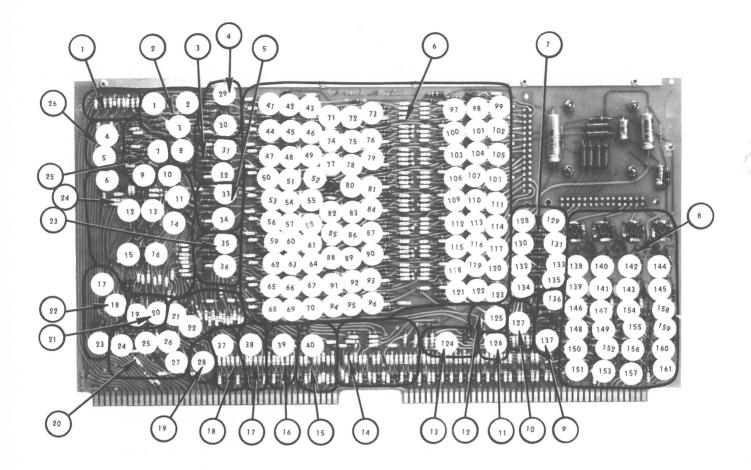

This card consists of 12 digits of log information, with a fixed decimal point of two places. It also contains a Binary Adder used to add and subtract log constants generated by the log generator. The card also contains the following miscellaneous circuits:

- a) The sign of the W-register,

- b) The error-light circuits,c) The sign of the real numbers in the L-register, and

- d) Shift pulse, S<sub>1</sub>, S<sub>2</sub>, S<sub>16</sub> (refer to signal definitions).

The center of the 1403A card contains 96 transistors which, with associated components, make up 48 flip-flop networks, 12 each for Binary 1, Binary 2, Binary 4, and Binary 8.

In the upper right-hand corner are the circuits for the L-register shift pulse containing two of the transistors. The other four transistors are for the L-register adder results, one each for Binary 1, 2, 4, and 8.

Directly below these six transistors are 14 transistors, in groups of two. Four of these groups, with the associated components, form the Binary 1, 2, 3, and 8 circuitry for the 9's complement inputs. The other three groups are part of the Binary 2, 4, and 8 adder-output circuits.

Below the adder-output circuits are the components which form the L-register minus circuits.

The transistors in the lower right-hand corner are part of the Binary 1 carry circuit. Along the bottom of the card, moving from right to left, the second transistor is a part of the circuit which forms the gate for the carrier memory for the L-register adder. The next two transistors form the circuits for this carrier memory.

The next four transistors, of which two form a flip-flop network, are part of the circuit which serves as a blocking signal when an error has accumulated.

On the lower right center, there are three transistors which are part of the memory of the number sign of the L-register circuit. To the left of these are three transistors which are part of the memory of the sign of the W-register. Included in this circuitry is a flip-flop network.

Continuing to the right, the next two transistors are a part of the main reset of the Lregister circuits. The next two are part of the circuit which performs function of giving the DC-level indicating zero in the L-register.

The next two are part of the memory-select circuit and the functions it performs. This gives a DC level, indicating that the number is greater than .999999999 at the end of an anti-log operation. There also is a pulse, controlled by the memory select, which shifts a "1" into the W-register at the end of an anti-log operation, if the number is greater than .9999999999.

Of the next four transistors, one is for control of a 20-30 microsecond pulse, generated by the turning ON of the L-register transfer. The other three are S<sub>1</sub>, S<sub>2</sub>, and S<sub>16</sub> signals, and their functions are as follows:

- a) S<sub>1</sub> generates a pulse which steps the ER counter during the entrance of numbers.

- b)  $S_2$  generates a pulse which shifts the W-register during entrance of numbers. c)  $S_{16}$  generates a pulse which shifts in the number of zeros left in the DCN, if

- the log was negative at the beginning of an anti-log.

The three transistors on the left-hand side, from bottom to top, are the error drivers and a flip-flop network. The next two are used in the circuit that gives the DC level, indicating a positive or a negative log.

Directly above these transistors is a group of components forming part of the pulse amplifier (PA) reset decoder circuit which is the master control flip-flop for log and anti-log processing. Above this circuit is the circuitry for control of the W-register to L-register transfer. In the upper left-hand corner is the circuitry for the L-register and the PA control.

- 1. Timing control circuit for the entrance of numbers.

- 2. Timing control circuit for the binary numbers.

- 3. Log process (normally zero pulse) circuit. (CP)

- 4. Circuit for the decoded output of the log process. (NLP's 0-13)  $\,$

- 5. Circuit for the decoding of the 16 step clock. (TD's 0-15)

- 6. Control circuit for a keyboard command and function pulse.

- 7. Circuit for the clock control signal.

- 8. Control circuit for a function pulse.

- 9. Circuitry for the two main timing pulse.

- 10. Control circuit for the log process (normally zero pulse) circuit.

- 11. Control circuit for control of the output of the LR's 9 complement signal.

This card contains the 16-step, main timing counter and associated timing pulses which control the entire LOCI. This card also contains the 14-step programmer and the log generator used in all log operations.

Along the left-hand side of the card are 16 transistors which comprise the circuitry for the L-register 9's complement. To the right of these complement circuits are two columns of transistors and their associated circuits, which are the decoding circuits for the following signals:  $EN_{1}$ ,  $EN_{2}$ ,  $EN_{4}$ , and  $EN_{8}$ , all of which originate on the 1405A card.

To the right of this circuitry, there are 13 transistors forming part of the log-process step (LPS), which is a pulse to step the log-process control.

In the center of the card is a column of 14 transistors and eight more in a cluster at the bottom of the column. These 22 transistors form the circuitry which provides the decoded output of the log process.

To the right of this circuit a column of 16 transistors (five to the right of the column) forms the circuitry for decoding the 16-step clock used in each cycle of operation.

The next two columns and the three at the lower right-hand edge comprise the main timing-pulse circuits. They contain six flip-flop networks.

The four transistors in the top right-hand corner and the two just below the center on the right-hand edge form part of the circuitry for providing a signal to the keyboard.

There are two transistors just above the center of the right hand edge, and these are part of the clock control circuits.

- 1. Gate control for the entrance of number. (ENT)

- 2. Circuit used to put zero's into the Work Register Adder. (NB)

- 3. Control circuit for the clock. (KC)

- 4. Control for the back space signal. (BS)

- Circuit controlling the summing of the Work Register and the Accumulator Register. (SM)

- Control circuit for aligning the decimal point between the Accumulator Register and the Work Register. (AD)

- 7. Pulse generator circuit (input is a DC level) (LND)

- 8. Circuitry controlling the transfer of the Log Register to the Work Register. (LT)

- 9. Circuit for memory of the negative log. (LND, ML)

- Circuit for the carrier memory for the Work Register. (C1)

- 11. Circuit which controls the number to log or the log to number transfer. (LN)

- 12 Memory of negative log. (DM)

- 13. Circuit for controlling Work Register to Accumulator Register transfer. (LD)

- 14. Control circuit for the log and anti-log process. (NLD)

- 15. Circuit for the reset signal generated by RT. (RS)

- Circuit that is set when the first number after an operation is entered into the LOCI. (RT)

- 17. Control circuits for Log and anti-log process. (DA)

- 18. Program reset circuit.

- 19. Nine's complement of number Register output control circuit. (NR)

- 20. Control circuit for functions from the Program.

- 21. Control circuit to blank the decimal light. (DCN)

- 22. Circuit to move decimal point to the left. (FM)

- 23, 24. Circuit for entrance of number control of log Generation and of add and subtract process. (EN1,2)

- 25. Control circuit for the number Register. (NR)

- 26, 27, 28. Same as #23. (EN2,4,8)

- 29. Same as #25. (NR)

- Shift pulse circuit for the Log, Accumulator and the Number Register. (ACR, C, NR)

- 31. Control circuits for various signals coming from storage. (DCA AND DCN SET GATES)

- 32. Control circuit indicating a nine's complement signal between the Work Register and the Adder.

- 33. Control circuit for the main reset of the Log Register.

- 34. Circuit for the Accumulator Register reset. (ARS)

- 35. Circuit which moves the decimal point right.

- 36. Circuitry for the carrier memory of the Work Register. (C1)

- 37. Circuit for the memory of the Ro Gate. (R0)

- 38. Control circuit for a er shift pulse. (ER)

- 39. Control circuit for signals from storage to the decimal counter. (DCN)

- 40. Circuit to move decimal point to the right. (FP)

- 41. Pulse generator circuit. (not used)

- 42. Control circuits for S<sup>S</sup> signals. (S<sup>S</sup>)

- 43. Control circuit for a decoded output of the Log Process. (NCP2)

- 44. Control circuit for memory of the decimal point. (DP)

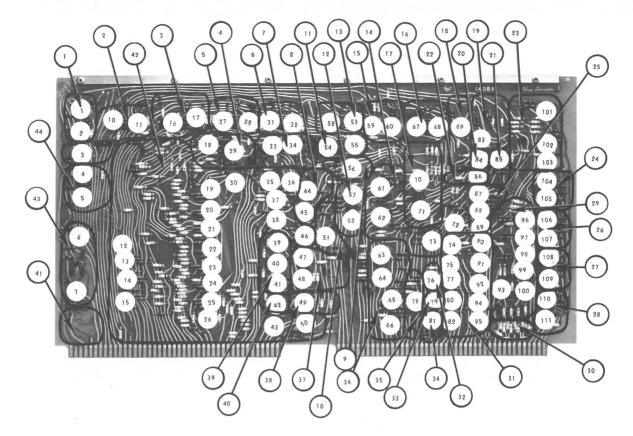

This card consists principally of miscellaneous circuits used throughout the entire LOCI. The majority of the circuits comprise shift pulses to control the A-, W-, and L-registers.

Because of the complexity of the circuits, the transistors have been numbered and these numbers coincide with the numbers on the diagram. A breakdown of the card circuitry follows:

**Transistors 1 and 2 —** These are part of the circuitry for the main gate-control flip-flop, for entrance of numbers.

**Transistor 3** — This is part of the circuit which combines diode output of the L-register with output of a flip-flop, indicating number-to-log operation when OFF and log-to-number operation when ON.

**Transistors 4 and 5 —** These are part of the flip-flop network in a memory circuit used to enter the decimal point.

Transistors 6, 7, 8, and 9 - These are normally ON pulse generators.

**Transistors 10 and 11 —** These are part of a flip-flop network used to put zeros into the input of the W-register adder during the log operation.

**Transistors 12 through 15, 19 through 26, 30, 35 through 38, 43, 46, and 50** — These transistors, and the associated components, form controls for some of the signals leaving the card.

**Transistors 16 and 17** — These are part of the flip-flop network which controls the clock.

**Transistors 18 and 29 —** These are part of the flip-flop network used to control the back-space signal. (This circuit is not used on all LOCI models.)

$Transistors 31 \ and 32 - These are part of the flip-flop network used to align the decimal point between the A- and W-registers.$

**Transistors 39, 40, and 41 —** These are a part of a control circuit for the blank decimal lights.

**Transistor 42 —** This is part of the circuit which moves the decimal point to the right.

**Transistors 44 and 45** — These are part of the flip-flop network used to control the transfer of the L-register to the W-register.

**Transistors 47 and 48** — These are part of the flip-flop network used to control the signal from the W-register adder input, indicating a number of "5," or greater.

**Transistor 49** — This is a part of a control circuit for the shift pulse to the W-register.

Transistor 51 - This is the control gate for the carrier memory of the W-register adder.

**Transistors 52 and 53** — These are part of the flip-flop network used to control the W-register to L-register transfer.

**Transistors 54 and 55** — These are part of a flip-flop network used to indicate number-to-log operation when OFF and log-to-number operation when ON.

**Transistor 56** – This is a control for the memory of the negative log.

**Transistors 57 and 58** — These are part of a flip-flop network used to control the memory signal of the negative log.

**Transistors 59 and 60 —** These are part of a control circuit for a reset signal generated by Transistors 67 and 68.

**Transistors 61, 62, and 73** — These are drivers and controls for the master control flip-flop for log and anti-log processing.

**Transistors 70 and 71 —** These are the master control and flip-flop for log and anti-log processing.

**Transistors 63, 64, and 76** — These are part of a flip-flop and control circuit for the carrier memory for the W-register adder.

**Transistors 67 and 68** — These are part of a flip-flop network, set when the first number after a previous operation is entered into the LOCI.

**Transistor 69** — This controls a signal used to reset the programmer.

Transistor 78 - This is a control which moves the decimal point to the right.

Transistor 79 - This is a control for the pulse used for resetting the W-register.

**Transistor 81** — This is the reset control for the A-register.

**Transistors 83 and 84** — These provide direct-current level control of the 9's complement circuit between the W-register and the W-register adder.

Transistor 85 - This provides control to blank the decimal lights.

**Transistor 86** — This is part of the control circuit that moves the decimal point to the left.

**Transistors 72, 87, and 89** — These are part of the control circuit for the number-register reset and the decimal-counter reset.

Transistors 74, 75, 77, 80, 82, 90, 91, 92, 94, and 95 — These act as controls for various signals coming from the storage cards 1407A or 1410A, used to set the Work Register decimal counter.

**Transistors 96 and 97** — These are used for the control of the entrance of numbers, control of log generation, and control of the adding and subtracting processes.

**Transistors 93, 98, 99, and 100** — These form the control circuit for the number-register adder input.

**Transistors 101 through 111** — These form the circuitry (including the flip-flops) of entrance of numbers, control of log generation, and control of the add and subtract processes.

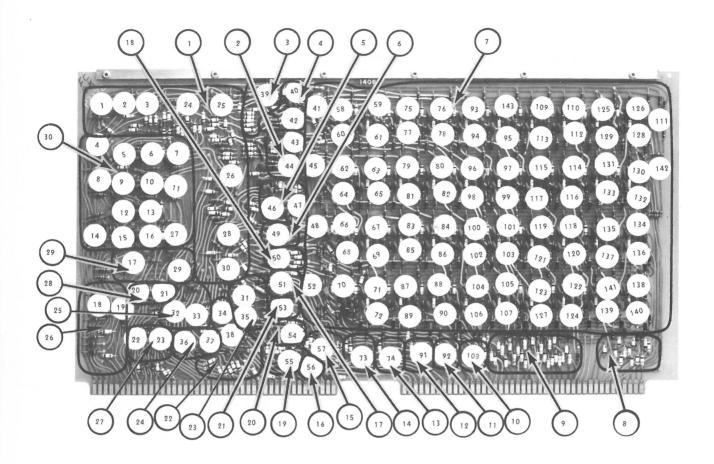

- Circuit for the Accumulator decimal point counter. (DCN)

- 2. Control circuit for the A→W command. (ACD)

- 3 and 4. Control circuit for clearing leading insignificant digits in the accumulator Register. (ACS)

- 5. Control circuit indicating positive or negative number in the Accumulator Register. (ACN)

- 6. Circuit for one of the "S" signals.

- 7. Circuit that contains entry information of the Accumulator Register.

- 8. A Decoding circuit for the "S" signals.

- 10 through 15. Circuits for the "S" signals. (\$18, 19, 21, 22, 28, 29, 31, 34, 36)

- 16. Driver circuits for the Accumulator Register signal. (ACR)

- 17 and 18. Same as #10.

- 19. A control circuit for the decimal point. (DCN)

- 20. Circuitry for the Accumulator Register Reset. (ARS)

- 21. Same as #10.

- 22. Same as #16.

- 23. One of the circuits of the sixteen step clock. (TD2)

- 24. Circuit that indicates the DCN is two or greater. (DCS)

- 25. Same as #20.

- 26. Accumulator decimal point circuits. (DCA)

- 27. Work Register decimal point circuits. (DCN)

- 28, 29. Same as #16.

- 30. Same as #26. (DCA)

This card contains the entire A-register, including 10 digits, a decimal point, and a sign. The card also has a comparator circuit used to align the floating decimal point during addition or subtraction, and it develops most of the control pulses in addition and subtraction processes.

The related schematic of the card indicates the location of some of the circuitry on the board. The right side of the card contains 80 transistors which form 40 flip-flop networks, and 6 transistors which are control drivers for the flip-flops. These 86 transistors and associated components form the binary storage circuits.

Across the bottom right-hand half of the card are six transistors which form six of the "S" signal circuits.

To the right of these are some of the decoding circuits for the binary storage. The upper left-hand portion of the card contains five transistors in a row. The first four, together with three down the left center, are part of the decimal-point counter circuit. The fifth is a part of the CAI signal circuit.

There is a group of seven transistors, of which three form part of the ACS signal circuit. Two are part of the ACD signal circuit, and two are used with the binary circuits.

The next two transistors under the ACD circuit form part of the A-register circuits.

Next are four transistors which form part of the "S" signal circuits.

Near the left-hand edge, in the center of the card, is a group of 14 transistors which form part of the DCA (Decimal Counter for the Accumulator) register circuitry.

There are 16 transistors positioned in the lower left-hand corner, five of which form part of the A-register circuit, two each for the  $DCA_0$ ,  $DCN_0$ , DCS, TD2, and ARS signals, and one for the DCN signal.

- 1. A complete storage register.

- 2. Control circuit for the store register. (CA1)

- 3. Circuit that indicates information is being transferred. (CP)

- 4. Shift pulse circuit for the ACR or N.R. signal.

- 5. Same as #2.

- 6. Same as #1.

- 7. Decimal point inputs (DCA or DCN) circuits.

- 8. Control circuit for the sign (ACN or SN).

- Control circuit for one of the decoded sixteen step clock signals. (TD3)

- 10. Circuit indicating information is leaving the Decrement counter when it is on. (CA)

- 11. Same as #8.

- 12. Control circuit for the transfer of signals to or from the Program counter. (CP)  $\,$

- 13. Same as #7.

- 14. Same as #8.

- 15. Same as #9.

- 16. Same as #10.

- 17. Same as #11.

- 18. Same as #12.

- 19. Same as #5. 20. Same as #2.

- 21. Same as #3.

- 22. Same as #4.

This card is used principally for storage. It has two complete transistor storage registers, each containing 10 digits, decimal point, and sign. The card also has four control circuits used by the programming features in the card.

The card is divided into two sections, with the circuitry identical in each section. The three flip-flop networks on each side are the only circuits not used for storage.

The three transistors located in the upper left-hand corner are part of the circuitry which provides a shift pulse for the A-register, or the number register. The two directly below these are part of a flip-flop network which is in the circuit that controls the information being transferred into, or out of, the program counter.

Continuing down the left-hand side, the next three are part of a flip-flop network and a driver in the circuitry which indicates that information is coming into the decrement counter, the program counter, or into storage.

The two transistors in the lower left-hand corner are part of a control circuit for the sign. There are six flip-flop networks across the bottom of the card; the first in the circuitry indicating that information is going out of the decrement counter, or storage, when it is ON, and the next is part of the circuitry which indicates positive or negative numbers in the A-register.

Under this flip-flop, there is one control transistor for the decoding of the 16-step clock used in each cycle of operation.

The next four flip-flop networks are all part of the control of signals from storage to set the A-register, or the W-register.

There are 80 transistors making up 40 flip-flops for PC, PCS, DC, and DCS.

The circuitry on the right is the same except that the sixth and seventh transistors from the top and right-hand edge are part of a flip-flop which controls the signal for the store operation.

- 1. Spare.

- 2. Program counter stepping circuit. (PCS)

- 3. Gate control of the number Register. (DCNS)

- 4. Stepping control circuit for the Program counter. (PCS)

- 5. Decoding circuit for the Program counter.

- 6. Circuit indicating Data is being received by the Decrement counter, Program counter or storage.

- 7. Part of #2.

- 8. Circuit that indicates DCN is greater than #2. (DCS)

- 9. Decrement counter circuits. (DC)

- Control circuits for signals from the Keyboard. (LDET) (CRT) (NRT) (ACRT) (DCT)

- 11. Control circuit for the Decrement Counter. (DC)

- 12. Function set and reset.

- 13. Control circuit for Program code stepping if one of the six decision making tests is true. (PCP)

- 14. Pulse Generator circuit. (AFP)

- 15. Pulse Generator circuit. (triggered by the run Key) (RE)

- 16. Control signal circuit for the Program Counter.

- 17. One of the Decoding circuits for the sixteen step clock.

- 18. Stepping pulse of the Program counter.

- 19. Number Register shift pulse circuit. (NRSHIFT)

- 20. Circuit which indicates when information is being parallel shifted into or out of the Decrement counter. (CDC)

- 21. Control circuits for various signals coming from the Keyboard.

- 22. Circuit controlling the restore operation. (RST)

- 23. Spare.

- 24. Part of the Program counter stepping circuit. (PCS)

- 25. Circuitry of the Program counter.

- 26. Circuit controlling the stepping of the P.C. counter. (DCF)

This card is principally concerned with the 160-step program counter, the 100-step decrement counter, and their associated storages. The card also contains the decision-making circuits for looping and jumping.

From the upper left-hand corner and coming down the side of the card, the first six transistors are part of the circuitry which includes a flip-flop to control the stepping of the program counter. The remaining two in this group are a flip-flop which is used to control the restore operation. Across the bottom left of the card are 10 transistors which are drivers for signals coming from the keyboard.

All other transistors, with the exception of two (which are spares), are part of the program counter, or program-counter storage circuits. In the center of the card are two transistors, of which one is the control indicating that information is flowing out of the decrement counter, or storage, when it is ON; and the other is for the gate control of the number register switch input from the decrement counter. Below this are three transistors which include a flip-flop network. This circuit is used to indicate that information is being parallel-shifted into, or out of, the decrement counter.

Continuing down the side of the card, the next three transistors are part of the circuitry which controls the W-register shift pulse. On the right-hand side are two transistors and these, together with one at the bottom of the card, control a delayed pulse generated by the RUN key.

In the lower right-hand corner, from right to left, there is a row of 11 transistors, of which the first five are control drivers for signals from the keyboard. The next one is part of the decrement-counter circuits; the next is a control driver for the signals coming from the keyboard. The next two are part of the function-reset circuits; and the last two are a control for the 30-microsecond pulse which gates on the input decoder.

Directly above this circuit, there are three transistors which control the programcounter stepping, if one of the six decision-making tests is true. The remainder of the transistors and circuitry are part of the decrement counter and the decrementcounter storage circuits.

- 1. Output circuit for signals going to the 1501. (DCN)

- 2. Control circuit for the memory select counter. (T2)

- 3. Circuit for the  $\overline{8}$  control of the core storage.

- 4, 5. Control circuit that selects the storage. (CS2, C33)

- 6. Components and circuitry of the memory core.

- 7. Memory core drivers circuits.

- 8. Circuits of the sensing amplifier.

- 9. Sensing amplifier gate reset circuit.

- Set circuit for the positive or negative indication in the Accumulator Register. (ACN)

- 11. Control circuit for the signals from storage to set the Accumulator decimal counter. (DCA)

- 12. Control circuit for setting the memory of the sign of the Work Register. (SN)  $\,$

- 13. Control circuit for signal from storage to set the Work Register decimal counter. (DCN)

- 14. DCN and DCA Decoding circuits.

- Control circuit for the Work Register decimal counter. (DCN)

- Control circuit for the Accumulator Register decimal counter. (DCA)

- 17. Control circuit for the Work Register counter. (NR)

- 18. Control circuit for the Accumulator Register counter.

- 19. Same as #17. (NR)

- 20. Control circuits for the store operations and indication information. (TD)

- 21. Control circuit for the decimal point in the Accumulator and Number Register.

- 22. Control circuit for one of the memory timing pulses. (T2)

- 23. Circuit  $\overline{4}$  control of the core storage selection of the Decrement counter, Program counter or storage when on.

- 24. Circuit indication information going out or coming in to the Decrement counter, Program counter or storage when on. (CA1, CA)

- 25. Shift pulse circuit for the Accumulator and the Number Register.

- 26. Control circuit for the storage selection signals. (CS3, CS4, RS2)

This card consists of 16 complete core storage units. It also contains four control circuits which are used by the programming features of the 1408A card.

In the top center of the 1410 A card are 83 transistors and associated components which make up the circuitry of the memory core.

In the lower right-hand section are 24 transistors and associated circuitry of the sensing amplifier.

To the left of the sensing amplifier, and to the right of the memory core, are 8 transistors which are the memory core drivers. Below these drivers are three transistors of which two are part of the circuit for the gate reset for the sensing amplifier. The remaining transistor is the set control for indicating positive or negative numbers in the A-register.

To the left of the set control for the sign memory of the W-register are two transistors which control signals from the storages to set the accumulator decimal counter.

The next four transistors along the bottom of the card are control gates for the A-register and number register.

The next one to the left is a control driver for the combined switch inputs to the W-register.

To the left of the memory core circuits are four flip-flop networks which are core storage selection networks.

In the top left center and the lower left corner are four and three transistors, respectively, which are in the circuitry that controls one of two main timing pulses. To the left of these are eight transistors which are part of the control circuits for the following signals: data coming into the card to indicate that information is being transferred into, or out of, the program counter; and the signal which controls the store operation.

Directly above these eight transistors are eight more which include three flip-flop networks forming part of the control circuits for the signal for the master control flip-flop of the 16 storage registers; and a second signal for the flip-flop indicating information is coming into the decrement counter, program counter, or storage. The third signal is a flip-flop indicating that information is going out of the decrement counter, or storage, when it is ON. Directly above these are two transistors which are control drivers for the A-register shift pulse and the number-register shift pulse.

- 1. Pulse generator control circuit used for reset. (RXP)

- 2. Control circuit for an Interrupt Pulse from an external source. (INT)

- 3. Control circuit for control of the input multiplexier. (MMC)

- 4. Control circuit for a pulse generated by the write key.

- Load Register for various signals of the Number Register.

- 6. Control circuit for a pulse generated by the carriage return key. (PCB)

- 7. Same as #5.

- 8. Control circuit for a pulse generated to set the channel of the output multiplexier. (QMS)

- 9. Control circuit for a pulse generated to set the channel of the input multiplexier. (IMS)

- 10. Circuit for the operation code input signal.

- 11. Strobo pulse circuits.

- 12. Same as #1. (RXP)

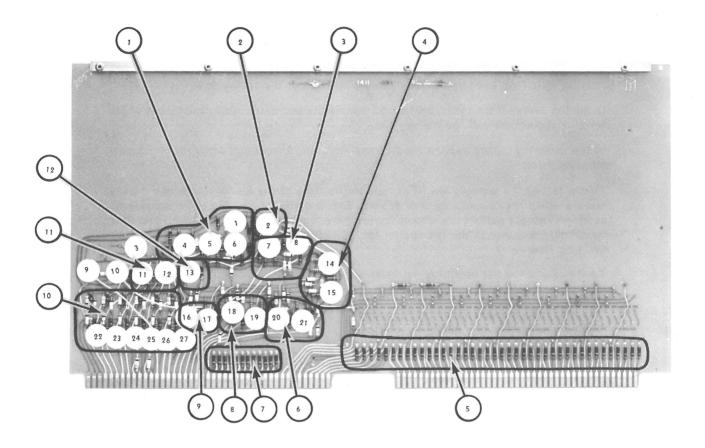

The 1411A card has all of the circuits concerned with the input-output interface. It has the least amount of circuitry of any of the cards and is used as an optional equipment card in the regular LOCI.

The circuitry is confined to the lower portion. Across the lower left-hand side are current-controlling circuits for the signals from the 1401A card.

In the lower right-hand corner are six transistors which control the signals coming from some of the peripheral equipment and going to the operation-code, flip-flop networks on the 1501 card.

Continuing across the bottom are eight transistors which are grouped two to a circuit. One circuit, commanded from the 1501 card, is used as a control pulse for the output multiplier. The other three are controls for the signals to the printer which is part of the optional equipment. It is, in fact, a pulse generator which is connected only when a Beckman-type printer is used.

The remaining transistors, which are in the upper left section of the circuitry, are control circuits for the input multiplier.

- 1. Control circuitry for the Teletype card. (TMC)

- 2. Circuit for the read start control of the Teletype. (RDS)

- 3. Controlling operations of the Reader in the Teletype.

- 4. Oscillator circuit for the Teletype card. (OSC)

- Circuit that controls the number of digits to be printed out, signal coming from the Teletype digit control switch. (NDP)

- 6. Control circuit for the pulse generated by the write key and the carriage return. (CR)

- 7. Master control circuit, circuit for the Teletype card. (TIME)

- 8, 9. Control circuit for the signal generated by the carriage return key. (PCB)

- 10. Print memory control circuit. (PMC)

- 11. Circuit for the Program stepper. (PS)

- 12. Control circuit for sign and decimal point in the printout. (PSN)

- 13. Control circuit for one of the Teletype stepping pulses. (TSD11)

- 14. Same as #13. (TSD9)

- 15. Same as #13. (TS)

- 16, 17. Circuit for the decoded output of the counter that selects digits to be serialized by the Teletype card. (PSD, PSN, PSD'S 0-13)

- 18. Control circuit for the pulse generated by the Write key. (PCA)

- Control circuit for the Reader start control of the Teletype. (RDS)

- 20. Control circuit for the operation code input.

- 21, 22, 23. Pulse generator circuits. (100MS) (3MS)

- 24. Controlling operations of the READER in the Teletype. (RF)

- 25. Same as #2. (30MS)

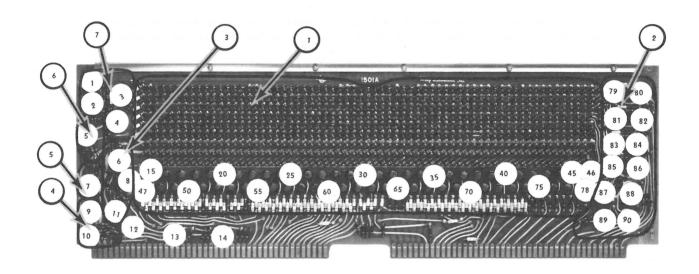

The 1412A card contains all necessary circuits to transmit data and to receive instructions from a Teletype Model 33ASR. This card is a special option card.

The lower right-hand half of the card contains the circuitry for the 18 transistors controlling the decoded output of the counter, which selects the digit to be serialized by the Teletype card.

Above these, on the right-hand side, are eight transistors and associated circuitry of the control circuits for the decoded output which selects the digits to be serialized by the Teletype card.

In the upper right corner are eight transistors which are part of four flip-flop networks. These networks are all part of the Teletype switching circuitry.

To the left of the switching circuit are two transistors which are control drivers for the Teletype switch decoding circuit. There are two transistors to the left of this circuit for controlling the number in the program stepper.

To the left is a flip-flop network which is part of the print-memory control circuit. To the left and below the print memory are 11 transistors which include five flip-flops which are part of the circuitry that controls the program stepper.

On the lower left-hand side, the bottom transistor is for the Reader START control of the Teletype.

The 25 transistors located on the lower left-hand side of the card are part of the program code-control signals. This circuitry has seven flip-flop networks.

Above these seven networks are 12 transistors which form part of three pulse generator circuits. To the right of these are three transistors, of which two are for the control of the pulses generated by the Write key, and the other is for control of the pulses generated by the Carriage Return key.

The three transistors above the pulse-generating circuitry, which include a flip-flop network, are for control of the Reader in the Teletype.

The upper left-hand corner has the circuitry for the control of the master control flipflop in the Teletype card.

To the right, across the top, are the flip-flops for the oscillator 9.09 milliseconds for the Teletype card. Directly under this oscillator circuit is the circuit for the Reader START control of the Teletype.

To the right are the two transistors which control the number of digits to be printed out, the signal for which comes from the Teletype digit-control switch.

Continuing to the right are two transistors which are drivers for a signal controlled by a signal from the program memory control, and which is going to the Teletype.

- 1. Input decoder circuit.

- 2. Circuit for the control of signals from the Reader output.

- 3. Pulse generator circuit that gates on the input decoder. (AFP)

- 4. Prime signal from the Keyboard. (LAMP)

- 5. Function reset circuits.

- 6. Function pulse circuits.

- 7. Function set circuits.

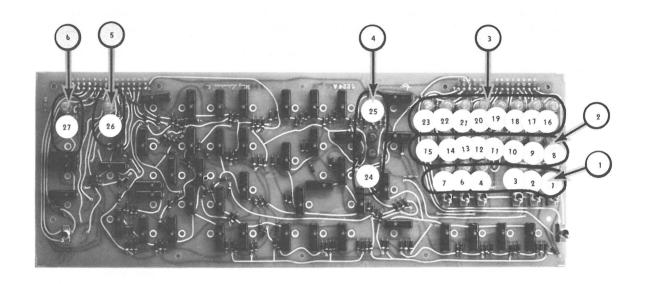

#### 1501A Card

This card is the means of communication between certain external sources (such as the Keyboard, Card Reader, or Teletype) and the arithmetic processing and storage unit.

The card receives a six-bit octal code; it also has the storage facilities of the octal code, and it decodes this information and distributes it to the proper data and control points in the LOCI to initiate the indicated operation. A decoded electrical signal is generated for each operation. This card also receives the prime machine pulse from the keyboard, and the function controls, resets, and various decoder signals.

On the right-hand edge of the card are six flip-flops to receive the octal operation code from the card reader.

Across the center of the card is the input decoder circuit. On the top left are six transistors which are part of the control circuit for the functions Set and Reset.

The two transistors in the lower left-hand corner control the prime signal from the keyboard. To the right of these are three transistors which are part of the 30-microsecond pulse circuit for gating on the input decoder.

#### 5224A CARD

- 1. Operation code indicator circuit.

- 2. Program code indicator circuit. (PC1, PC2, PC4, PC8, PC10, PC20, PC40, PC80)

- 3. Decrement counter indicator circuit. (DC1, DC2, DC4, DC8, DC10, DC20, DC40, DC80)

- 4. Memory select indicator circuit. (CS1, CS0)

- 5. Response indicator circuit.

- 6. Error indicator circuit. (err)

#### 5224A Card

This is the keyboard card. It has all of the indicator lamps, and performs all manual operations.

The 46 microswitches located throughout this card set the operation code flip-flops on the 1501 card by pulling through the proper diodes. The eight toggle switches perform basically the same functions as the microswitches.

There are 26 indicator lamps, and each has a transistor which acts as a driver. The break-down of indicators and drivers is as follows:

- 8 Decrement counter

- 8 Program counter

- 6 Program code

- 2 Memory select

- 1 Response signal

- 1 Error signal

### 5123A & 5129A CARDS

- 1. Output circuitry.

- 2. Control drivers for the output of the Reader.

- 3. Input circuitry.

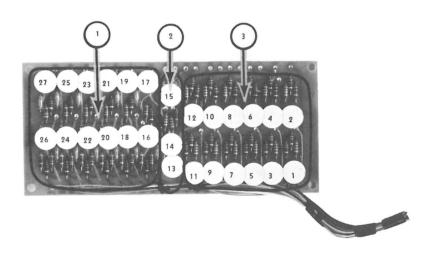

### 5123A, 5129A Cards

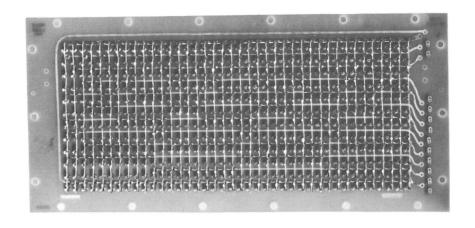

These two cards contain all of the electronic circuitry of the card reader. The card reader controls various signals used in the operation-code circuitry.

Looking at the 5129A card with the attached wires at the top right are two rows of six transistors each. These are drivers for the signals leaving the card reader. In the center of the card are three transistors: two are for the control of the output drivers; the third is a gate control for a second card reader output.

On the left of the card are two rows of six transistors each. These, and their associated components, are the control drivers for the signals coming into the card reader.

The 5123A card contains resistors and diodes only. These are used to control the signals passing through the program card.

# IV. LOCI CU-3/CU-4 CIRCUIT DESCRIPTION

#### A. OUTPUT MULTIPLEX (Drawing 5485-10)

The output multiplex circuit accepts parallel output data from the LOCI W-register and distributes it to one of the three output channels. This circuit consists of an output multiplex (OM) switch, a buffer storage register, and assorted control circuits.

The three outputs of the OM switch (CD22) are designated  $OM_0$  for tape leader,  $OM_1$  for the format register, and  $OM_2$  for the teletype. The switch is loaded by execution of LOCI Command 35, provided the sign of W is negative. This causes a negative level ( $M_Z$ ) at J2, Pin 48, which acts through Gate D17 and pulse Generators D18 to Reset CD22 first, after which the channel number is set in by transferring the most significant digit of W into CD22 by acting through gated Drivers D21. Outputs of the OM switch control distribution of Write commands to the appropriate channel by acting on Gates D23.

Execution of Command 35, with W positive, acts on pulse Generators D19F to prime the CU-3.

Execution of LOCI Write and CR commands act through Gates D17 and pulse Generators D19 and D20 to generate control pulses for the teletype interface and timing circuits. Flip-Flop D-16 inhibits further outputs from the LOCI until typing is complete. LOCI output commands are acknowledged at J2, Pin 49 through diode Gates C24.

The output storage buffer is a serial shift register loaded in parallel from the LOCI upon receipt of a Write command. Shift register modules are AB22, AB24, CD27. Loading is through gated Drivers A23, B23, A25, B25, A27, C26, and D26. Following each Write operation, the shift register is cleared by a burst of clock pulses acting through gated pulse Generator D25 and Inverters C6M and D15S.

#### B. FORMAT LOGIC (Drawing 5485-11)

The format logic circuit controls the transfer of data from the output buffer-shift register to the teletype unit.

The format register is a three-digit storage register containing the control word governing output format. This register, consisting of Modules AB20 and BC15, is loaded from the four most significant digits of W by execution of a Write command, provided that the OM has been set to  $OM_1$ .

Prior to each typing operation, the contents of AB20, which correspond to the desired number of characters before the decimal point, are transferred into binary Counters B18 by Pulse SFC acting on gated Drivers B19. Simultaneously, the decimal point locator digit from J2 Pins 41, 42, 43, and 44 is loaded into Counters B17 through A17. Each of these counters had previously been reset by the Transfer pulse acting through A15H.

The actual writing sequence begins with the appearance of AFT pulses at A16KM. These pulses cause B17 and B18 to count up from their preset values. When B17 reaches a count of 10, it acts through B16NM, A16S, and A15K to prevent further counting, and through A16P and C19E to enable shift pulses for the storage-shift register. Simi-

larly, when B18 reaches 10 it stops counting and acts on Flip-Flop C20M and pulse Generator C14P to produce the Start Write Data pulse. Either B17 or B18 may be first to reach 10, depending on the format control word.

The occurrence of the decimal point in the writing sequence, as determined by the format timing circuit (Drawing 5485-12) causes the EDR pulse, which acts on Flip-Flop C20JE, to enable  $\overline{AFT}$  pulses at A18K through C19N and C18K. This counter, which was previously reset by the Transfer pulse, then counts up until it equals the digit in Register AB20, which equals the number of desired characters after the decimal point. Comparison is accomplished by A19. Coincidence acts through C12E and C13F to produce the End Data pulse at C13H.

Counter C17 keeps track of the number of words per line. It is compared to the reference digit by C16. Coincidence acts through C18E to provide automatic carriage return.

#### C. FORMAT TIMING (Drawing 5485-12)

The format timing circuit controls the sequencing of sign, data, and decimal-point information to the Teletype unit. It also provides for insertion of Run and  $\pm$  codes on the output tape, as well as the automatic carriage-return and line-feed commands.

Receipt of the Type signal from the output multiplex circuit acts on Flip-Flop D3EJ to enable D25J and allow clock pulses at D25K to appear at D2H. These pass through to D6P, causing high speed  $\overline{AFT}$  pulses at D6R. Occurrence of the Start Write Data pulse at P24R acts on Flip-Flop D3 to disable D25J and enable D25N. This causes all subsequent  $\overline{AFT}$  pulses to be derived from, and thus synchronized to, the teletype loop clock through D1H and D25N.