# PRELIMINARY User's Guide

# WD1007A-WAH/2

February 17, 1988

#### USER'S GUIDE

#### WD1007A-WAH/WA2 WINCHESTER/FLOPPY DISK CONTROLLER

#### 1.0 DESCRIPTION AND DOCUMENT SCOPE

The WD1007A-WA2 and the WD1007A-WAH are single board Winchester Disk Controllers designed to interface two ESDI compatible disk drives to the IBM PC/AT or compatible host computer. The WD1007A-WA2 supports two 5-1/4 inch floppy disk drives; the WD1007A-WAH is a hard disk only version of the controller.

The ESDI drives used with this controller generally have two modes of operation, soft sector and hard sector. At this time, the WD1007A-WA2 offers only the hard sector mode of operation.

When integrating a hard disk drive into the AT environment, a drive type table must be selected that represents the physical characteristics of the drive being used. This information consists of the number of cylinders, heads and sectors per track. It is often difficult to match the drive and the table exactly. Most system BIOS'and/or Operating Systems support only the older MFM/ST-506 drives that used 17 sectors per track. The ESDI disk drive typically has 34 sectors per track when operating in the hard sector mode.

The WD1007A controllers have an optional BIOS ROM that provides drive parameter tables, low-level formatting routines, and surface analysis routines. While low-level formatting of the drive can be accomplished by several means, Western Digital recommends that you use the low-level format routine present in the WD1007A BIOS. If your controller does not have the BIOS option, obtain Western Digital's WDFMT 2.10 formatting utility.

This document describes installation in the IBM Personal Computer AT. If you have an AT compatible, you should refer to your system manuals or contact your dealer for information concerning installation of the WD1007A-WA2. The user should refer to the 1007A Application Notes and Data Sheet for a more thorough explanation of the board functions.

#### 2.0 HARDWARE INSTALLATION INSTRUCTIONS

This section briefly describes installation of the WD1007A-WA2. If you wish to install the disk drive internally, it is best to locate the controller in the closest available expansion slot relative to the drive.

#### CAUTION

Handle the controller board by the ends of the board. Some of the chips are static sensitive and damage may occur if the board is incorrectly handled.

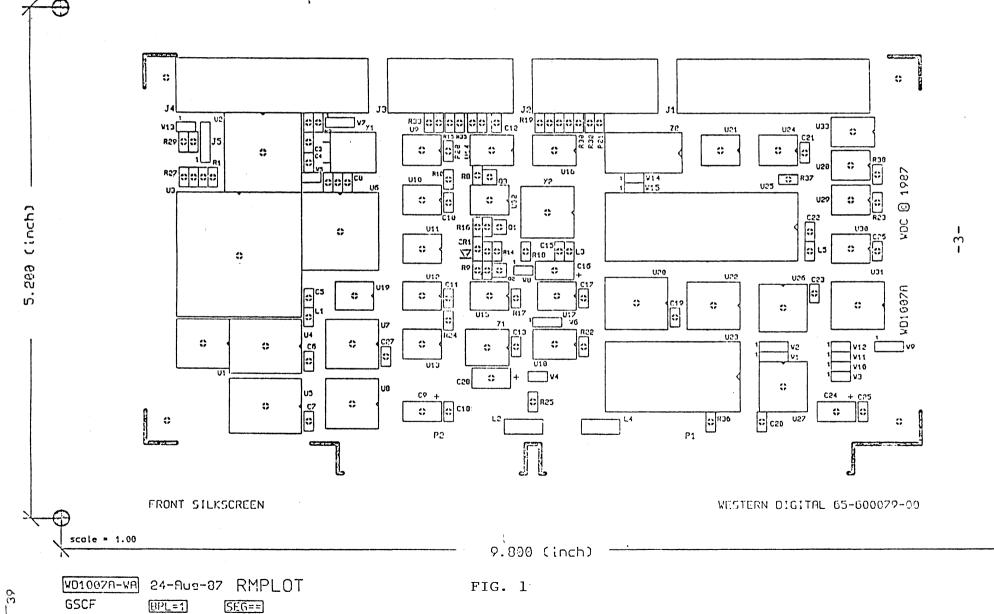

> Verify the controller jumper settings. Modification of the standard 1. factor settings on the controller is rarely necessary. Modify the jumpers only under the direction of a qualified individual; i.e., your dealer. Figure 1 illustrates the jumper locations. Table 1 lists the jumper default settings for the WD1007A-WA2 and the WD1007A-WAH. Table 2 provides the various address select ranges and corresponding jumper Refer to WD1007A-WA2/WAH Data Sheet and Application Notes for settings. a more complete description of the jumper functions and options. The WD1007A-WAH can be used as a field replacement board for existing WD1005-WAH boards without reformatting the hard disk drive. The WD1005-WAH firmware does not recognize the Set Unformatted Bytes Per Second command, and the user must set jumper/switches on the drive to the desired sectors per track. Substituting the WD1007A-WAH board and installing a jumper at W8 precludes the use of "Set Unformatted Bytes/Sector" command. When in the WD1007A-WA2 mode (no jumper on W8), the ESDI drive is forced to 35 sectors per track by the Set Unformatted Bytes Per Sector command. The interleave ratio is 1:1.

2. Remove or disable any other floppy controller in your system, if you are installing the WD1007A-WA2.

3. Verify termination of the last hard disk drive. Verify proper setting of drive select switches on the drive, if necessary. Do NOT use the drive's radial select option. Refer to the drive owner's manual for information about proper drive termination and select switches.

4. Remove the blank expansion slot bracket. Put the bracket away and save it for possible future use. The bracket screw will be used to hold the controller board in place.

5. Connect the 34-pin control cable to J1 connector. Keyed connectors prevent reversal of the cables.

6. Connect the control cable to the hard disk drive(s).

7. Attach a 20-pin data cable to J2 connector (for Drive 0).

8. Attach a 20-pin data cable to J3 connector (for Drive 1).

9. Connect the cable(s) to the proper hard disk drive(s).

10. Attach the 34-pin daisy-chain cable to J4 connector.

11. Connect the cable to the floppy drive(s).

12. Attach Winchester activity LED connector to J5.

13. Install the controller board into the expansion slot. Insure that the board is seated properly by pressing down on both ends of the board. Secure the board with the bracket screw.

-2-

# HD1007A-HA2 JUMPERS CONFIGURATION TABLES

TABLE I

| BIOS ADDRESS RANGES                                                         | JUMPER                           | SETTINGS                         |                                                    |

|-----------------------------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------------------------|

|                                                                             | K1                               | W2                               | W3                                                 |

| C2000 - C3FFF<br>CA000 - CBFFF<br>CC000 - CDFFF<br>CE000 - CFFFF<br>DISABLE | 2 - 3<br>2 - 3<br>1 - 2<br>1 - 2 | 2 - 3<br>1 - 2<br>2 - 3<br>1 - 2 | JUMPED<br>JUMPED<br>JUMPED<br>JUMPED<br>NON JUMPED |

#### TABLE II

| FLOPPY CONTROLLER | W4         | W13 IN ETCH |

|-------------------|------------|-------------|

| ENABLE            | NON JUMPED | UNCUT       |

| DISABLE           | JUMPED     | CUT         |

|                   |            |             |

# TABLE III

| DRIVE TYPE INPUT       | W5         |

|------------------------|------------|

| 2 SPEEDS SPINDLE MOTOR | JUMPED     |

| SINGLE SPEED           | NON JUMPED |

#### TABLE IV

| FLOPPY ADDRESS RANGES | WS    |

|-----------------------|-------|

| 37X                   | 1 - 2 |

| 3FX                   | 2 - 3 |

# TABLE V

| HIGH DENSITY SELECTION | W7    |

|------------------------|-------|

| 5.25", 1.2M            | 1 - 2 |

| 3.5", 1.44M            | 1 - 2 |

# TABLE VI

| WD1005 MODE |      | JUMPED     |

|-------------|------|------------|

| WD1007 MODE | - W8 | NON JUMPED |

#### TABLE VII

| CHASSIS GROUND & DIGITAL GROUND | W9 1  |

|---------------------------------|-------|

| CONNECTED                       | 2 - 3 |

|                                 | 1 - 2 |

WD1005 Mode - The controller sends 'Unformatted bytes/sector' from drive

WD1007 Mode - The controller sends 'Set Unformatted bytes/sector' command to

the drive.

| WD1007A-WA2                                                                                                                                                                                                                         | WD100TA-WAH                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| DEFAULT SETTING                                                                                                                                                                                                                     | Default_setting                                                                                                                                 |

| - W1 2 - 3<br>- W2 2 - 3<br>- W2 2 - 3<br>- W3 JUMPED<br>- W4 NON JUMPED<br>- W5 2 - 3<br>- W7 1 - 2<br>- W8 NON JUMPED<br>W9 NON JUMPED<br>- W10 NON JUMPED<br>- W10 NON JUMPED<br>- W11 JUMPED<br>- W12 NON JUMPED<br>- W13 UNCUT | 41 2 - 3<br>42 2 - 3<br>43 NON JUMPED<br>43 NON JUMPED<br>40 NON JUMPED<br>410 NON JUMPED<br>411 NON JUMPED<br>412 NON JUMPED<br>414 NON JUMPED |

#### TABLE VIII

| DIGITAL INPUT REG MODE | W10        |

|------------------------|------------|

| LATCHED                | JUMPED     |

| NON LATCHED            | NON JUMPED |

## TABLE IX

| DISKCHANGE INPUT   | W11        |

|--------------------|------------|

| WITH FDC OPTION    | JUMPED     |

| WITHOUT FDC OPTION | Non Jumped |

| TABLE X                                  |                      |

|------------------------------------------|----------------------|

| PRIMARY/SECONDARY<br>HARD DISK ADDRESSES | - W12                |

| 1FX<br>17X                               | NON JUMPED<br>JUMPED |

| TABLE XI           |                      |

|--------------------|----------------------|

| SECTOR TRANSLATION | W14                  |

| ENABLE<br>DISABLE  | NON JUMPED<br>JUMPED |

| TABLE XII          |                      |

| ECC SELECTION | W15        |

|---------------|------------|

| 7 BYTES       | JUMPED     |

| 4 BYTES       | NON JUMPED |

#### 3.0 OPERATION

The WD1007A controller can be installed into any 16 bit slot in the IBM PC/AT or compatible host computer. By referring to the jumper option, the controller can be configured for the desired mode of operation. Be sure that the drive configuration is set properly to support the hard sector mode. Connecting cables for the ESDI hard disk are the same as those used on the ST506 interface disks. Also, device ID jumpers are implemented on the ESDI device just as with ST506 drives. In order to use an ESDI drive in a given system, a three step process has to be followed:

1) Low level format: done through WDFMT, third party software, or 1007A BIOS;

2) Active drive partitioning: done using MSDOS 3.3 (using FDISK) or other operating systems that allow partitioning (such as SCO XENIX).

3) High level format: done through the operating system using the normal 'Format C: (or D:)/S' command.

There are two different BIOS' that can play a role in the use of the WD1007A with the ESDI drive: the system BIOS and the 1007A BIOS. If one wishes to avoid using the 1007A BIOS (and just use the system BIOS), the exact physical drive parameters for the drive in question must be present in the system BIOS tables.

In terms of maximum flexibility and adaptability with different drives, Western Digital recommends the use of the WD1007A BIOS.

#### 4.0 USING YOUR SYSTEM BIOS TO CONFIGURE YOUR DRIVE

The system BIOS refers to the BIOS that is controlling the computer (e.g. Phoenix, IBM-AT, Faraday). If the appropriate drive parameter tables are present, the system BIOS can be used, along with the operating system (MSDOS, SCO Xenix) to partition and high level format a given drive.

1. To determine if a system BIOS has the physical drive parameters required for your ESDI drive, use the appropriate set-up diskette for your system to see if the appropriate number of heads, number of cylinders and number of sectors/track are listed. If they are not listed, the system BIOS probably does not have the required parameter tables and one needs to use other means (such as WDFMT or the WD1007A BIOS) to low level format.

2. Another way of examining the system parameter tables to determine if the drive is listed in the BIOS is through the DOS Debug Utility:

a. Although some systems locate drive parameters in other locations, the standard location in the AT BIOS is F000:E401. The proper command at the DEBUG prompt (-) is as follows:

df000:e401 <CR>

This corresponds to drive type 1 and will display 8 lines of data from the BIOS ROM. By entering another "d" at the DEBUG prompt, another 8 lines of data will be displayed, corresponding to drive type 2, etc. This procedure is continued until all drive parameter information for all drive types is displayed. If the particular drive parameters are encountered in this process, it means the drive is recognized by the system BIOS.

Each parameter table has 16 bytes of data. Data from the BIOS ROM is displayed in hex, least signifcant byte first. This data breaks down as follows:

| Bytes 1&2   | Number of cylinders                |

|-------------|------------------------------------|

| Byte 3      | Number of heads                    |

| Bytes 4&5   | Not Used                           |

| Bytes 6&7   | Write Pre-Compensation cylinder    |

| Byte 8      | Not Used                           |

| Byte 9      | Control Byte (= 08H for > 8 heads) |

| Byte 10-12  | Not Used                           |

| Bytes 13&14 | Landing Zone3                      |

| Byte 15     | Sectors Per Track                  |

| Byte 16     | Not Used                           |

|             |                                    |

3. There is also a way of using the DOS DEBUG utility to confirm the parameters for the current drive selected. This is done through the INT 41 (located at d0:104) and the INT 46 (located at d0:118) handlers. INT 41 corresponds to the address of the current selected parameters for drive) and INT 46 corresponds to the address of the current selected parameters for drive 1.

a. If you desire to see the current selected parameters for drive 0, the proper command at the DEBUG prompt (-) is:

#### d0:104

The first four bytes displayed correspond to the offset (2 bytes) and segment 6 (2 bytes) of the location where the selected parameters are, e.g., if after the above d0:104 the result is:

30 IF 00 C8 AB 73 . . . <=> Location C800:1F30 [ ] [ ] Offset Segment

The current selected parameters are located at address C800:1F30. By typing DC800:1F30 at the DEBUG prompt, 16 bytes will be displayed (as explained above) describing the selected drive parameters.

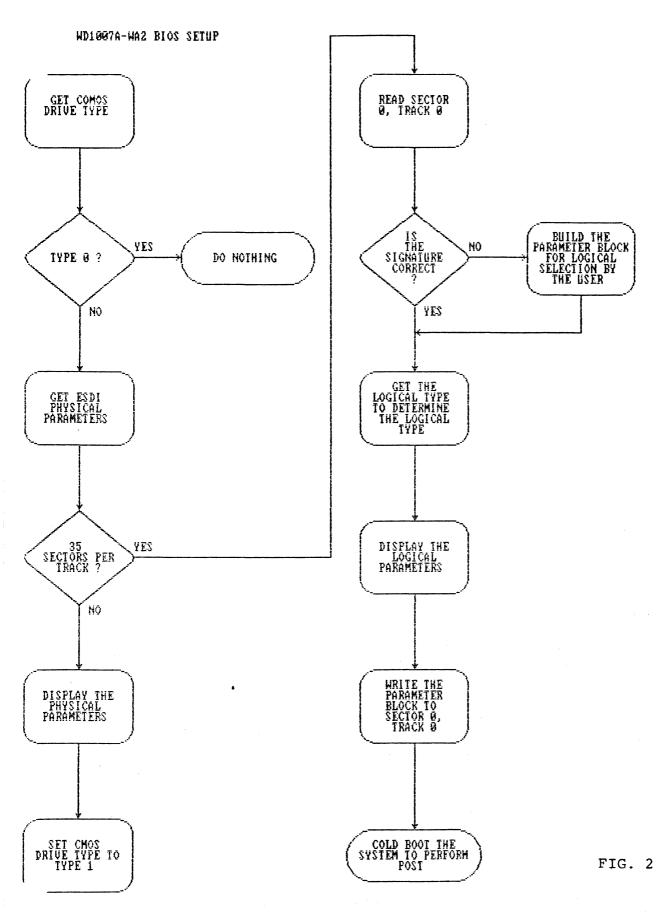

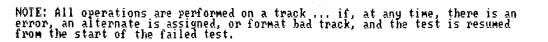

Please see Figure 2 for the illustration of the above.

C800:1F80 C800:1F90 0800:1FA0 0800:1FB0 CCC0: 1FC0 CS00:1FD0 00 00 00 00 00 00 00 00-00 00 00 00 00 00 00 00 C800:1FE0 00 00 00 00 00 00 00 00-00 00 00 00 00 00 00 00 00

-d0:104 30 1F 00 C8-65 F0 00 F0 00 28 00 C0 0000:0100 Q...e....'.. 0000:0110 84 60 00 F0 84 60 00 F0-01 E4 00 F0 84 60 00 F0 . . 84 60 00 F0 84 60 00 F0-84 60 00 F0 84 0000:0120 -60 00 FO 40 00 FO 0000:0130 84 50 00 F0 84 50 00 F0-84 50 00 F0 84 . . . . . . . . . . . . . . . . 0000:0140 40 00 F0 84 40 00 F0-84 60 00 F0 84 60 00 F0 34 34 50 00 F0 84 50 00 F0-84 50 00 F0 84 50 00 F0 0000:0150 84 60 00 F0 84 60 00 F0-84 60 00 F0 84 60 00 F0 0000:0160 0000:0170 84 60 00 F0 84 60 00 F0-84 60 00 F0 84 60 00 F0 00 00 00 00 000:0180 . . . . -dc800:1f00 0800:1F00 57 45 53 54 45 52 4E 20-44 49 47 49 54 41 4C -24 WESTERN DIGIT 19 CB00:1F10 . . . . . . . . . . . . . . . . . . 03 09 00 00 FF FF 00-C0 00 00 00 00 00 23 00 CE00:1F20 ·C8 . . . . . . . . . . . . . <del>. .</del>. 03 09 00 00 FF FF 00-08 00 00 00 C8 03 22 00 C200:1F30 08 C8 03 10 00 00 FF FF 00-08 00 00 00 C8 03 11 00 C800:1F40 . . . . . . . . . . . . . . . . . . C200:1F50 25 01 10 00 00 FF FF 00-08 00 00 00 25 01 3F 00 CS00:1F60 37 769............ C800:1F70 . . . . . . . . . . . . . . . . . . .

(): \>debug

----

•-----

---\_ ----------------------d

C800:1FF0

FIG. 2

-7-

4. If, in using the above methods you verify that the system BIOS does contain the physical parameter tables for your drives, you need to use WDFMT to low level format the drive, FDISK (MSDOS 3.3) to partition it and finally the 'FORMAT C:(D:)/S' to high level format.

SEE FIGURE 2 FOR AN ILLUSTRATION OF THE ABOVE METHODS OF DETERMINING IF THE PHYSICAL DRIVE PARAMETERS ARE LOCATED IN THE SYSTEM BIOS.

#### 5.0 USING THE 1007A BIOS

1. Before using the BIOS, make sure the proper address range is selected on W1 and W2. Confirm that the BIOS is enabled (jumper on W3).

2. Enter the BIOS routine through the DOS DEBUG utility. Execute the DEBUG utility and at the program prompt "-", type:

G=C800:5 <CR>

Depending upon the settings of W1 and W2, this causes the system to execute program code stored at location 5 in ROM. The BIOS then tries to read the parameter tables from the drive and store them in the shadow RAM. If the drive has not been formatted the BIOS will return a message of "drive not initialized". The user will see the following on the screen:

\*\*\* Western Digital 1007A-WA2 Initialization Utilities, Rev. 1.0\*\*\* PRESENT DRIVE SETUP ... + or - to change, <ENTER> for selection

DRIVE 0 CYLINDERS XXX HEADS XX PRECOMP CYLINDER XXX SPT XX DRIVE 1 CYLINDERS XXX HEADS XX PRECOMP CYLINDER XXX SPT XX

| Change Drive Types | > 1 |

|--------------------|-----|

| Low Level Format   | > 2 |

| Surface Analysis   | > 3 |

| Verify Drive       | > 4 |

| Enter Defect List  | > 5 |

| Exit and Reboot    | > 6 |

Enter Choice (1-6) -->

3. All functions can be executed by simply entering the number for the desired routine. The BIOS will execute that routine and then prompt the user to press a key to return to the main menu. Note that all changes made while in the BIOS will only be finalized after a proper exit through function 6 - otherwise some features might not be valid including drive type selected.

#### A. Drive type routine

The drive types can be changed by using the "+" and "-" keys. Assuming that all the ESDI drives in question are specified at 34 SPT, there are four possible choices that can be implemented for a drive:

A.1 No drive present. The BIOS will automatically select a drive type 0 if there is no drive present. The user will get the message "\*\*\* NONE SELECTED OR NO DRIVE PRESENT ! \*\*\*" next to the drive number.

A.2 A selection with 17 SPT. This feature should be used when the drive is being used in a system that does not recognize drives with SPT values other than 17 SPT. Although the low level format will still be at 35 SPT, logical parameter tables will be created reflecting 17 SPT (with translation enabled). See section on Translations for more details.

**A.3** A selection with 34 SPT. This feature should be used, if the system being used recognizes the standard 34 SPT drive.

A.4 A selection with 63 SPT. This feature should be implemented only when the drive in question is specified as having greater than 1024 cylinders. Translation should always be enabled when such a condition exists. What this feature does is to allow full use of all the cylinders of the drive (even though most AT BIOS' only recognize 1024 cylinders as a maximum) through a translation scheme that uses 63 SPT.

#### B. Low Level Format Routine

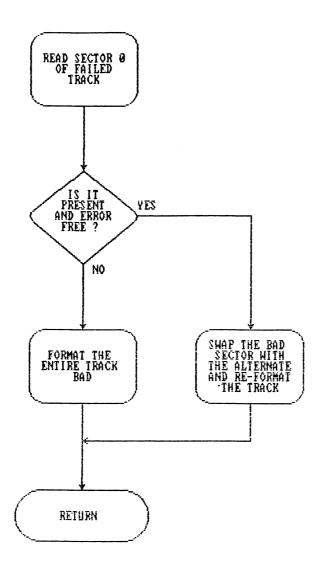

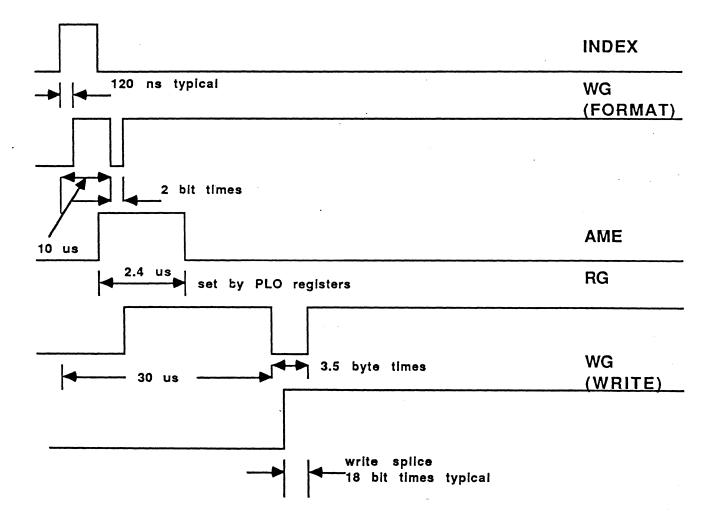

Formatting routines are present to do the low-level initialization of the disk surface. The drive is formatted at 35 sectors/track (SPT). Transparent to the user, the format routine formats with a sector skew and also formats a spare sector on each track. This sector is used by the surface analysis routines to provide the ability to reallocate a bad sector on a track. It is also used to store the parameter information generated by the BIOS. This information is written to the spare sector on cylinder 0, head 0. The sector skew, which is fixed at two, allows the controller to maintain a one to one interleave across all head boundaries. Sector Skewing is a method of formatting in which the sector numbers are rotated in the interleave table for each track.

#### C. Enter defect list routine

This routine allows the user to enter the list of 'bad tracks' as listed by the drive manufacterer on the drive.

#### D. Surface analysis routine

A surface analysis routine is available that identifies bad tracks on the drive and in the event that there is only one sector bad on the track (and it is NOT sector zero), assigns the alternate sector (sector 35) in the place of the bad one. This 'saves' the track from being marked bad by the controller.

If one had entered a list of the 'bad tracks' at the begining of this routine, after the surface analysis, all the tracks marked bad will now be error free (within the constrictions of the above paragraph).

#### E. Verify drive routine.

The verify routine will identify all the 'bad tracks' on the drive and list them by head and cylinder number. Use the FDISK and FORMAT utilities to prepare

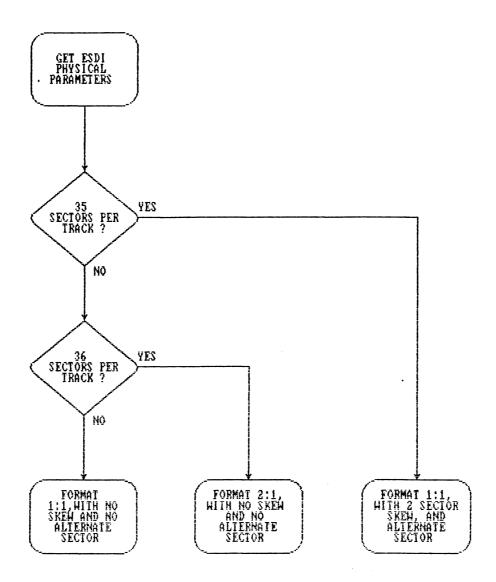

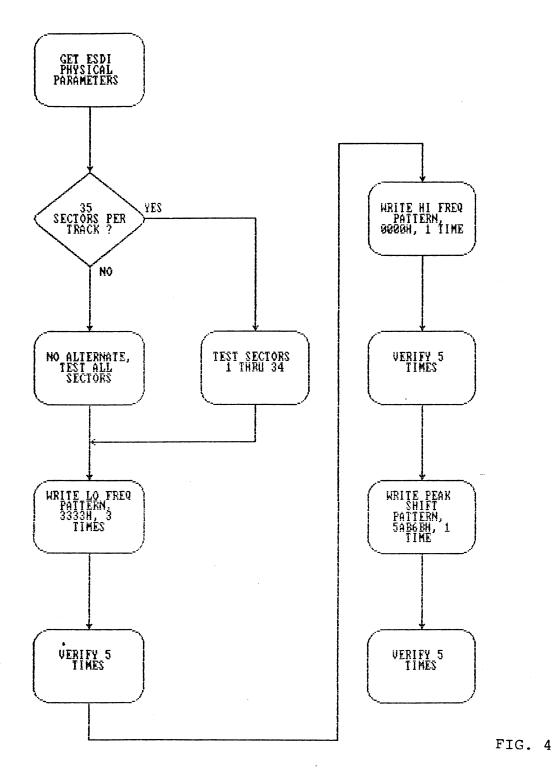

4. 1005 mode as opposed to the 1007 mode: If it is desired to format a drive at a value other than 35 SPT the board should be configured to be in the 1005-WAH mode (Jumper W8). In this mode the the controller will format the drive at this value as long as the drive is configured to reflect this SPT value. The WD1007A BIOS will read the drive parameters off the drive in this mode and will allow a low level format at the read values with no skew, no alternate sector, and a 1:1 interleave. The only exception to this is if the drive is configured to be at 36 SPT; for this mode, a 2:1 interleave has to be used.

5. If one is using a 5 MB/S ESDI drive the 1007A translation feature should be disabled (jumper W14). This type of ESDI drive is always configured at 17 SPT.

SEE FIGURES 3-7 FOR AN ILLUSTRATION OF THE VARIOUS BIOS FUNCTIONS.

#### 6.0 WDFMT

Western Digital provides a low-level format utility that will allow the user to prepare the drive for use by the system. The program includes routines for low-level formatting, disk verify, surface analysis and bad track entry. When using the 1007A board one should use an interleave of 1, a skew on 2 and format at 35 SPT with an alternate sector. See the explanations for these features provided below. WDFMT 2.10 presents the following display: % # Western Divital WD1007A-WA2 Initialization Utilities, Pav. 1.0 \* \*

FREEENT ERIVE SETUP ... + en - to CHANGE, (ENTER) for SELECTION

DRIVE O CYLINDERS 968 HEADS 9 SPT 35 - ### Drive NOT initialized ! ### DRIVE 1 - ### NOME SELECTED or NO ERIVE PRESENT ! ###

Change Prive Types ---> 1 Low Level Format ----> 2 Curface Analysis ----> 3 Verify Prive ----> 4 Enter Defect List ----> 5 Exit and Reboot ----> 6 Enter Choice (1-6) ---> 2 ... FEPMAT

Files will be LOST ... are you sure ? (Y/D) y Enter drive (0/1) 0 FORMATTING ... bead 8 - cylinder 967 FORMAT SUCCESSFUL ... Use DOS "FDISK" AND "FOFMAT".

Hit any key to return to Menu ...

· · · · ·

ABOVE ARE THE PHYSICAL PARAMETERS OF A CDC WREN III. WE HAVE JUST PERFORMED A LOW LEVEL FORMAT WITH 1:1 INTERLEAVE, SKEW CF 2 SECTORS PER TRACK AND WITH AMPERNATE SECTOR.

\* \* \* Western Digital WD1007A-WA2 Initialization Utilities, Rev. 1.0 \* \*

PRESENT DRIVE SETUP ... + or - to CHANGE, <ENTER> for SELECTION

DRIVE 0 \*\*\* NONE SELECTED or NO DRIVE PRESENT ! \*\*\*

TYPE + AS MANY TIMES AS YOU LIKE, UNTIL YOU HAVE THE LOGICAL TABLE YOU WANT, THEN TYPE ENTER.

FIG. 3

-11-

\* \* \* Mestern Digital WD1007A-WA2 Initialization Utilities, Pev. 1.0 \* \*

PRESENT DRIVE SETUP ... \* or - to CHANGE, KENTER> for SELECTION

ERIVE 0 CYLINDERS 748 HEADS 14 SPT 17

ABOVE IS THE 17 SECTOR TABLE TO BE USED WITH EAPLIER OPERATING SYSTEMS THAT ALWAYS EXPECT 17 SECTORS PER IPACH.

\* \* Western Digital WD1007A-WA2 Initialization Utilities, Rev. 1.0 7 \*

PRESENT DRIVE SETUP ... + or - to CHANGE, <ENTER> for SELECTION

DRIVE 0 CYLINDERS 293 MEADS 16 SPT 63

ABOVE IS THE 63 SECTOR TABLE TO BE USED IF YOUR DRIVE HAS MORE THAN 1024 CYLINDERS AND YOUR SYSTEM BIOS CANNOT HANDLE THAT MANY CYLINDERS.

FIG. 4

an go a co

\* \* \* Mestern Digital WD1007A-WA2 Initialization Utilities, Rev. 1.0  $\pm$  \*

PRESENT DRIVE SETUP ...  $\leftarrow$  or - to CHANGE. <ENTER> for SELECTION

DRIVE O CYLINDERS 968 HEADS 9 SPT 34

ABOVE IS THE 34 SECTOR TABLE WHICH PROVIDES AN ALTERNATE SHOLDT PER TRACK, WHICH IS USED BY THIS UTILITY IN THE EVENT OF A BAD SECTOR.

WE WILL USE THIS ONE ... TYPE ENTER.

\* \* \* Western Digital WD1007A-WA2 Initialization Utilities, Rev. 1.0 & \*

PRESENT DRIVE SETUP ... + or - to CHANGE, KENTER> for SELECTION

DRIVE 0 CYLINDERS 968 HEADS 9 SPT 34 DRIVE 1 \*\*\* NONE SELECTED or NO DRIVE PRESENT 1 \*\*\*

Change Drive Types ---> 1 Low Level Format ----> 2 Surface Analysis ----> 3 Verify Drive ----> 4 Enter Defect List ---> 5 Exit and Reboot ----> 6

Enter Choice (1-6) ---->

AT THE MENU NOW, LET'S DO A VERIFY ... TYPE 4.

## FIG. 5

\* \* \* Western Digital WD1007A-WA2 Initialization Utilities, Sev. 1.0 \* \* PRESENT ERIVE SETUR ... + on - to CHANGE, KENTERS for SELECTION. URIVE O CYLINDERS 968 HEADS 9 SPT 34 DRIVE 1 FAR NONE SELECTED of NO DRIVE PRESENT ! APR Chance Drive Types ---> 1 Low Level Format -----> 2 Surface Analysis -----> 3 Verify Drive -----> 4 Enter Defect List ----> 5 Exit and Reboot ----> 6 Enter Choice (1-6) ----> 4 ... VERIEY Enter Crive (0/1) 0 TESTING .... head 8 PAD TRACK cylinder 37 TESTING .... head i cylinder 43 - PAD TPRCK TESTING .... head 2 cylinder 380 PAD TRACK TESTING .... head 8 cylinder 967 Hit any key to return to Menu ...

YOU WILL NOTICE THAT WE FOUND 3 BAD SECTORS.

WE WILL NOW DO A SURFACE AMALYSIS ... TYPE 3 AT THE MENU.

FIG. 6

-14-

3 8 9 Western Digital WD1007A-WA2 Initialization Utilities, Rev. 1.0 8 8 PRESENT DRIVE SETUP ... + or - to CHANGE, <ENTER> for SELECTION DRIVE O CYLINDERS 968 HEADS 9 SPT 34 DRIVE 1 \*\*\* NONE SELECTED or NO DRIVE PRESENT ! \*\*\* Change Crive Types ---> 1 Low Level Format ----> 2 Eurface Analysis ----> 3 Verify Drive -----> 4 Enter Defect List ----> 5 . Exit and Reboot ----> 6 Enter Choice (1-6) ----> 3 ... SUFFACE AMALYSIS Files will be LOST ... and you sure ? (Y/N) y Enter drive (0/1) 0 Enter manufacturer's DEFECT list . ( <ENTER> to end ) HEAD 8 BYTE COUNT AFTER INDEX 8054 CYLINDER 37 ALTERMATE ASSISHE CYLINDER 43 HEAD 1 BYTE COUNT AFTER INDEX 19245 ALTERNATE ASSIGN CYLINDER 380 HEAD 2 BYTE COUNT AFTER INDEX 9293 ALTERNATE ASSIGNE CYLINDER HEAD BYTE COUNT AFTER INDEX TESTING .... head 8 cylinder 136 ALTERNATE ASSIGNED TESTING .... cylinder 315 head 4

te la plane a site d'al d

WE ENTERED THE 3 BAD SPOTS LISTED ON THE DRIVE AND THE SURFACE ANALYSIS FOUND ONE MORE AND ASSIGNED AN ALTERNATE. IF WE DID A VERIFY NOW, WE WOULD HAVE AN ERROR FREE DRIVE.

-15-

> \*\*\* Western Digital Corporation \*\*\* AT Disk Format Utility Rev. 2.10 Current drive parameters are: Drive (0/1): 0 Cylinders : 615 Heads : 4 Sectors 17 : Interleave 3 : Precomp : 306 Skew 0 : Alt Sector No :

#### ENTER MENU CHOICE

Format disk CAUTION this will destroy all data on drive! Verify disk Bad sector entry Surface test CAUTION this will destroy all data on drive! Quit

#### A. Sector Skewing

Sector Skewing is a method of formatting a drive in which sector numbers are rotated in the interleave table each time a new head on a cylinder is formatted. For example, using a 2 sector skew, the first sector after index on head 0 will be identified as sector 1. The sector identified as sector 1 on head 1 will be the third physical sector from index.

Sector Skew formatting is available with version 2.10 of WDFMT.

Example: Ten sectors per track with a skew of 2 and interleave of 1

| <u>Head</u> | # |    |   | Se | <u>cto</u> | <u>r #</u> | <u>'s</u> |   |   |    |

|-------------|---|----|---|----|------------|------------|-----------|---|---|----|

|             |   |    |   |    |            |            |           |   |   |    |

| 0           | 1 | 2  | 3 | 4  | 5          | 6          | 7         | 8 | 9 | 10 |

| 1           | 9 | 10 | 1 | 2  | 3          | 4          | 5         | 6 | 7 | 8  |

| 2           | 7 | 8  | 9 | 10 | 1          | 2          | 3         | 4 | 5 | 6  |

This formatting procedure allows the controller to maintain the 1:1 interleave when reading across the head boundary. This becomes critical when the number of sectors per track increases and the time allowed for overhead functions to be completed decreases as with ESDI applications. Because of controller firmware overhead, the controller will not be able to read the ID Field of the first sector on the next head. By changing the sector numbers, the controller can do the needed tasks and be ready to

> read the sector marked as number 1. The minimum sector skew factor for proper performance of the WD1007A has been determined to be 2. Different skew factors may be needed to optimize performance for different applications.

#### B. Sector Spare

Another option available in WDFMT Version 2.10 is the ability to format a spare sector on the track. This spare sector is given the ID of zero, making it invisible to the AT compatible System BIOS, which expects sector numbers starting at 1. This sector is always formatted as the last physical sector on the track.

The surface analysis portion of WDFMT will use that spare sector if an error is encountered with any sector on the given track. The program will reformat the track, numbering the bad sector as zero and shifting the following sectors one to the right. If more than one sector is found to be bad on the track, the entire track is marked as bad when reformatted.

This feature is useful since many system BIOS ROMS that support ESDI drives have a sector per track parameter of 34. By using the spare sector option, the drive will look like it has only 34 sectors. The spare sector can be used for the above mentioned bad sector reassignment, or it can be used to store custom data by providing software drivers to use the hidden sector.

# PRELIMINARY Data Sheet

# WD1007A-WAH/2

February 17, 1988

#### WD1007A-WAH/WA2 WINCHESTER/FLOPPY DISK CONTROLLER

#### FEATURES

- o PC-AT compatible Winchester and floppy disk controller

- o ESDI Drive Interface

- o Utilizes maximum storage capacity of ESDI drives

- Controls up to two fixed disk drives and two floppy disk drives (5.25 or 3.5 inch)

- o 84-pin Buffer Management and Control (AMAC) gate array

- o Optional BIOS ROM

- o Supports 1:1 interleave

- o Data transfer rate of 10 Mbits per second

- o Supports NRZ disk data format

- o Two 8192 x 8 RAMs for look-ahead read caching to reduce disk access time and increase data throughput

- o Software selectable 56-bit ECC

- o Multiple sector read/write commands

#### DESCRIPTION

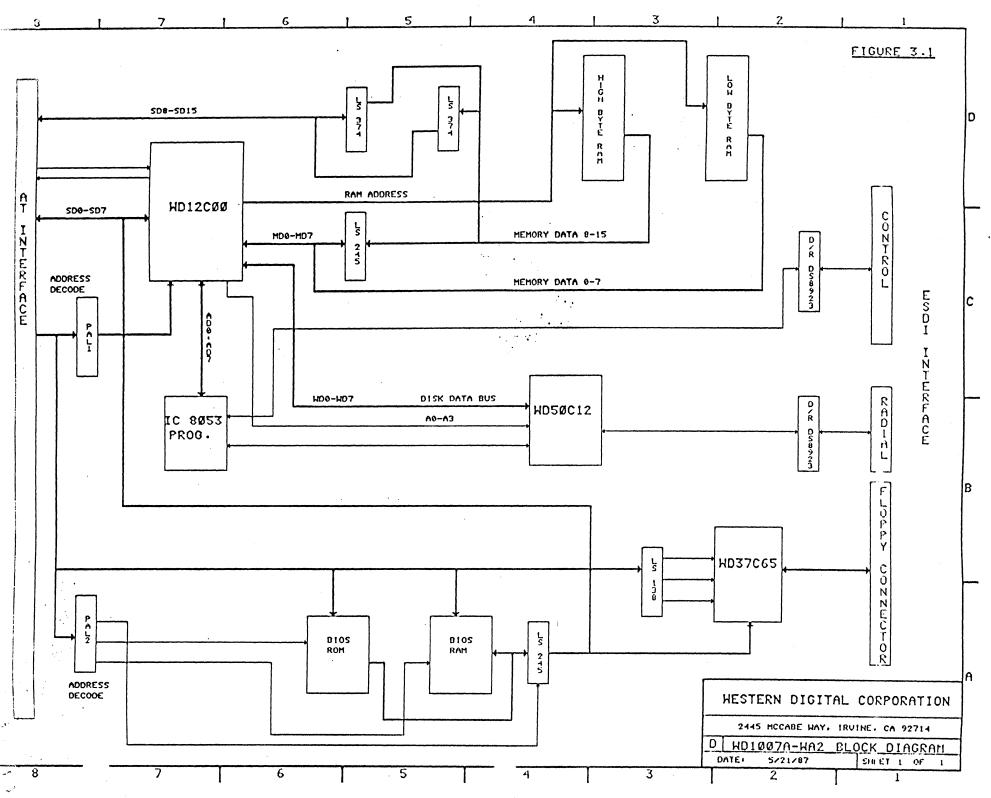

The WD1007A-WA2 Winchester/Floppy Disk Controller (WFDC) module interfaces two ESDI-compatible fixed disk drives and two 5-1/4 inch floppy disk drives to the PC-AT computer I/O Channel bus structure. An optional BIOS ROM provides parameter tables, lowlevel formatting and surface analysis routines to fully integrate ESDI drive capabilities into the system.

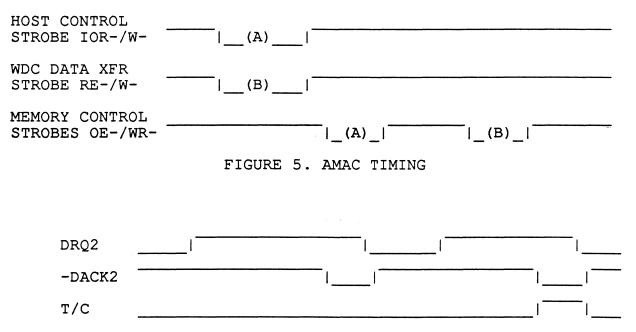

The fixed disk section of the module includes the WD50C12 Winchester Disk Controller, the WD1018 Buffer Manager/Control Processor, sector buffer RAM and associated control logic. The WD37C65 Floppy Disk Controller (FDC) implements the optional floppy disk control section. The WD12C00A (AMAC) gate array also provides buffering and control. The AMAC reduces module logic and supports a 1:1 interleave format.

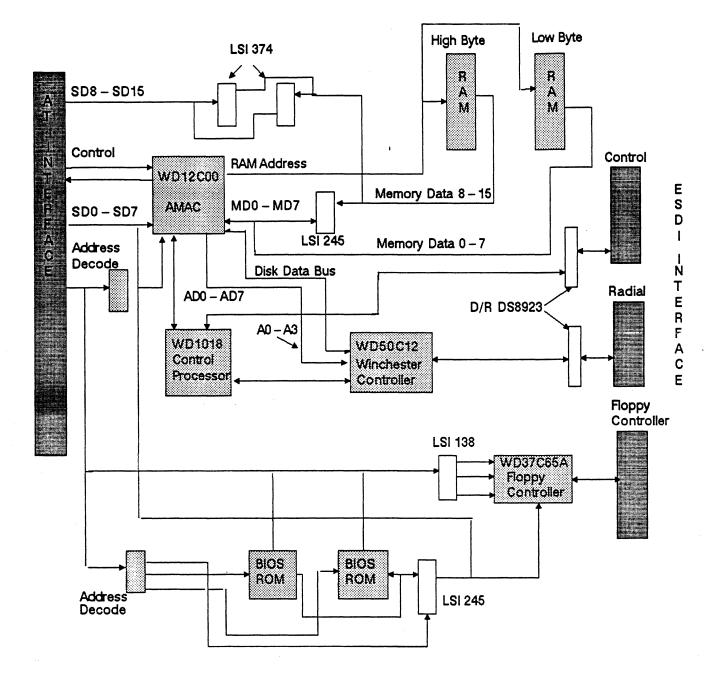

#### BLOCK DIAGRAM

A description of the functional blocks of the WD1007A-WA2 Winchester/Floppy Disk Controller (WFDC) appears below. Refer to the block diagram in Figure 1.

#### WD50C12 Winchester Disk Controller

The WD50C12 Winchester Disk Controller (WDC) is an advanced VLSI device that controls and coordinates the activity of the hard disk drive. The WDC supports 1:1 interleave and data transfer rates up to 10 Mbits per second. It utilizes the maximum storage capacity of ESDI drives by translating physical parameters into logical parameters for those operating systems which do not

PRELIMINARY DRAFT

recognize more than 17 sectors per track or more than 1048 cylinders per drive. (See Translation in the Appendix for an explanation of this feature). The WDC offers software selectable 56-bit ECC and supports the NRZ data format.

FIGURE 1. WD1007A-WA2 BLOCK DIAGRAM

PRELIMINARY DRAFT

#### WD1018 Buffer Manager/Control Processor

The WD1018 Buffer Manager/Control Processor is an eight-bit microcontroller that operates with the WD50C12 and the AMAC logic array to facilitate processing of disk commands. It provides sector data buffer management, helps in error recovery procedures and performs module diagnostics. The processor chip includes internal RAM and ROM memory.

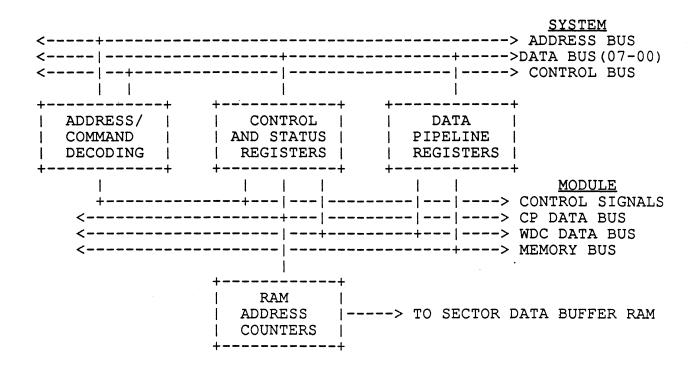

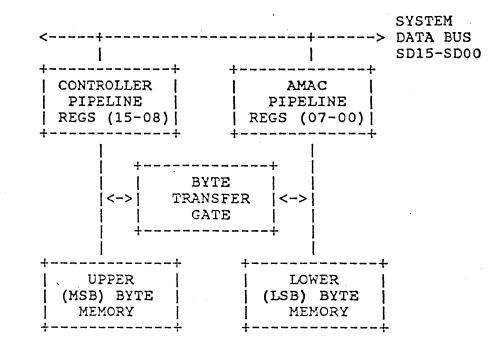

#### WD12C00A-JU22 Logic Array (AMAC)

The primary function of the AMAC logic is to provide host address and command decoding, task file control and data buffering. The VLSI logic array replaces the standard WD1014 support device and several SSI/MSI components. This simplifies the logic and lowers power consumption. The AMAC logic includes the data and address registers, memory read/write control, and WD50C12 task file image registers. It interfaces to both the system and module (local) bus structures. (See Figure 2. AMAC Block Diagram)

#### RAM Data Buffer

Two  $8192 \times 8$  static RAM memories buffer the sector data between the drive(s) and the PC-AT system bus. They also buffer Error Correction Code (ECC) information between the WD50C12 disk controller and the WD1018 control processor. The sector buffers and the above control components provide a 1:1 sector interleave format for optimal system performance.

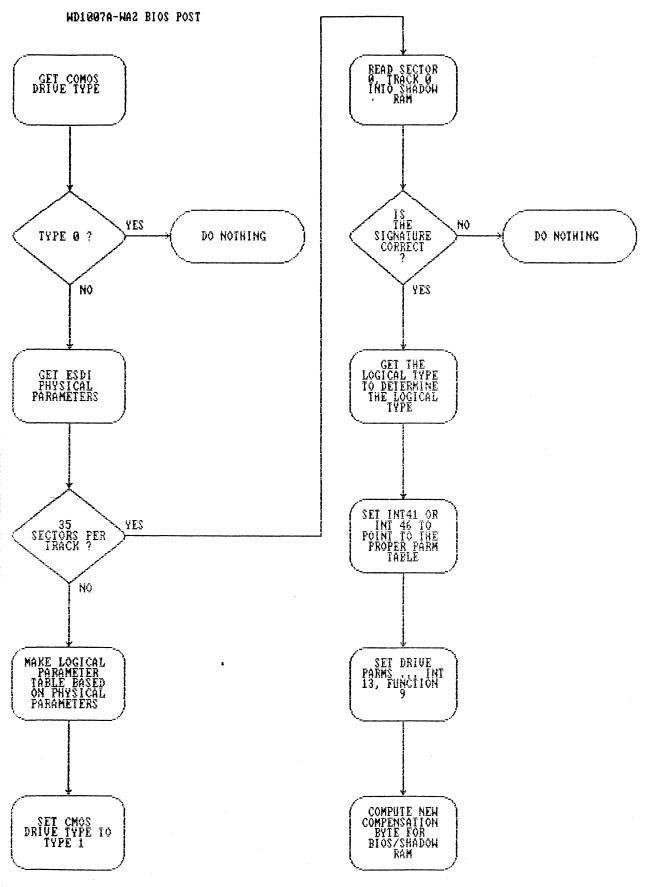

#### WD37C65 Floppy Disk Controller (FDC)

The optional WD37C65 Floppy Disk Controller (FDC) is a standard VLSI device that supports both single and double density diskette formats and provides data and control interfaces for the host and the floppy drive. The units major features include:

- o Multiple sector and track read/write commands

- o Host DMA and programmed I/O data transfers

- o High performance digital data separation

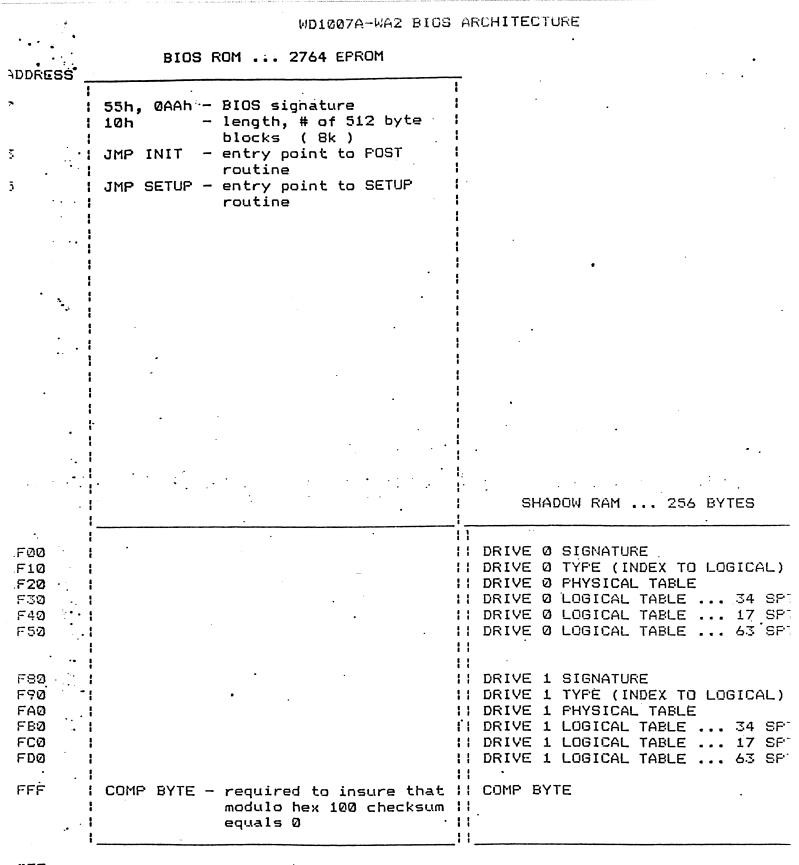

#### BIOS (P) ROM/RAM Option

Controller circuitry accommodates a programmed BIOS device for special applications. One unique feature of this BIOS option is its shadow RAM. The static RAM (which shares with the BIOS (P)ROM the last 256 upper address bytes of BIOS's 8 Kbyte address range) contains the Winchester drive's parameters. This shadow-RAM feature allows the WFDC to interface with all types of ESDI drives without modifying the system BIOS. Option jumpers

PRELIMINARY DRAFT

allow the device to be mapped at 1 of 4 address ranges. For more information, refer to the jumper configuration tables on page 13 and to the Appendix.

FIGURE 2. AMAC BLOCK DIAGRAM

PRELIMINARY DRAFT

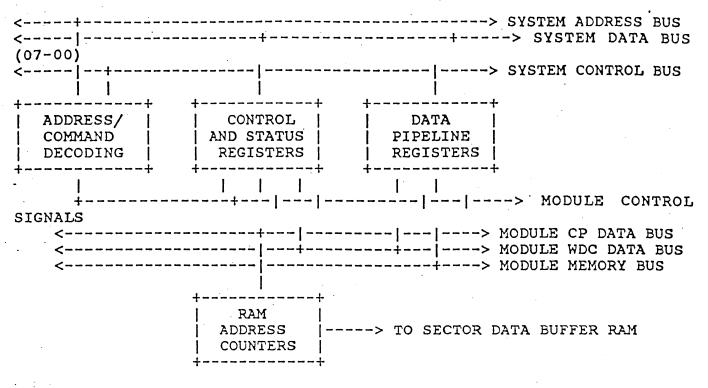

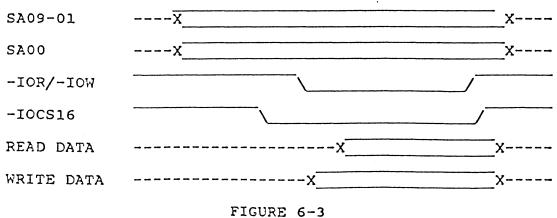

#### INTERFACE DESCRIPTION - HARDWARE

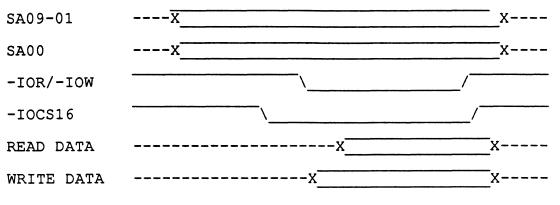

#### System Bus Interface

The WFDC interfaces with the system bus address to transmit data and I/O control signals. All fixed disk read/write data transfers are 16-bits wide and utilize the host I/O transfer protocol. Floppy disk data, fixed disk control, floppy disk control, and status transfers are 8 bits wide and use the lower data byte (SD07-00) only. The register address map of the WFDC module is fixed (at a primary or secondary range) as are the bus interrupt requests and the Floppy DMA channel assignment.

Tables 1 and 2 below provides the pin descriptions for the P1 and P2 system bus connectors.

| TABLE 1.        | SYSTEM INTERFA | CE CONNECTORS (P1) - PIN DESCRIPTION                                                                                                                   |

|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin             | Signal         | Description                                                                                                                                            |

| A02-A09         | SD07-SD00      | System Data Bus. Transfers 16-bit fixed disk data, 8-bit floppy data and 8-bit module control and status information.                                  |

| A11             | AEN            | Address Enable. Indicates a valid I/O<br>address is on the system bus. The AMAC<br>decode logic uses this term to qualify<br>the I/O address decoding. |

| A12-A31         | SA19-SA00      | System Address Bus. Selects the WFDC I/O addresses and BIOS ROM addresses.                                                                             |

| B01,B10,<br>B31 | GND            | Ground                                                                                                                                                 |

| B02             | RST            | Reset                                                                                                                                                  |

| B03,B29         | VCC            |                                                                                                                                                        |

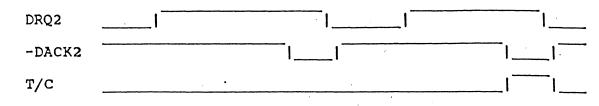

| B06             | DRQ2           | DMA Request Level 2. When a data byte<br>is ready for transfer to or from the<br>host memory, the WD37C65 floppy<br>controller generates this signal.  |

| в09             | VDC            | +12 Volts                                                                                                                                              |

| B11             | -SMEMW         | System Memory Write. Input strobe<br>used to write drive parameters in the<br>Shadow RAM.                                                              |

| B12             | -SMEMR         | System Memory Read. Enables BIOS ROM and shadow RAM.                                                                                                   |

PRELIMINARY DRAFT

- B13 -IOW I/O Write. Asserted by the system processor during bus 'write' cycles. The WFDC uses this strobe and the decoded bus address to input both data and command information.

- B14 -IOR I/O Read. Asserted by the system processor during bus 'read' cycles. The WFDC uses the signal (along with the system address bus decoding or DMA ACK signal) to enable system I/O reads of both data and command information.

- B22 IRQ6 Interrupt Request Level 6. Floppy controller interrupt request to the system processor indicating that the WD37C65 has completed the execution phase of a command or that the selected 'drive ready' line has changed state. Reading the result phase status or issuing a 'Sense Interrupt Status' command will clear the IRQ6.

- B26 -DACK2 DMA Acknowledge Level 2. Indicates the completion of a data byte transfer. The DMA controller provides bus control and system memory address.

- B27 T/C DMA Terminal Count. The WD37C65 terminates the data transfer sequence for read, write or scan commands when the DMA controller issues this signal.

- B28 BALE Bus Address Latch Enable. Input control signal used to initiate a data transfer on the system bus. The WFDC uses this input to generate the I/O transfer control signal and to enable control signals for high-order data bytes.

| TABLE 2. | SYSTEM INTERFA | CE CONNECTORS (P2) - PIN DESCRIPTION                                                                                  |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------------|

| Pin      | Signal         | Description                                                                                                           |

| C18-C11  | SD15-SD08      | System Data Bus. Transfers 16-bit fixed disk data, 8-bit floppy data and 8-bit module control and status information. |

PRELIMINARY DRAFT

| D02 | -I/OCS16 | I/O Control Signal 16. Indicates 16-bit<br>data transfer mode. The WFDC asserts<br>this signal for all hard disk data<br>transfers.                                                                                                                  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D07 | IRQ14    | Interrupt Request Level 14. Output to<br>the processor from the fixed disk<br>control requesting a data block transfer<br>or indicating command completion. The<br>level clears on a subsequent fixed disk<br>command to the WFDC or a system reset. |

| D16 | VCC      |                                                                                                                                                                                                                                                      |

| D18 | GND      | Ground                                                                                                                                                                                                                                               |

# Winchester Drive Interface

The WFDC module interfaces to the fixed disk drives via one 34pin control cable (J1) and two 20-pin data cables (J2,J3) in conformance with ESDI signal definitions. The WFDC module does not furnish drive power. Signal descriptions appear in Tables 3 and 4.

| Pin                                                       | Signal  | Description                                                                                                                             |

|-----------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1,3,5,7,<br>9,11,13,15,<br>17,19,21,23,<br>25,27,29,31,33 | GND     | Ground - Pin 15 keys the connector.                                                                                                     |

| 2,4,<br>18,14                                             | HS3-/0- | Head Select. Binary-coded select<br>signals allows selection of drives<br>with up to 16 read/write heads.                               |

| 6                                                         | WRG-    | Write Gate. Enables the selected<br>drive to accept write data. A<br>write fault condition or a module<br>reset will clear this signal. |

| 8                                                         | CSD-    | Configuration/Status Data. Data<br>from the selected drive in response<br>to controller command.                                        |

| 10                                                        | TXACK-  | Transfer Acknowledge. Handshake<br>response from selected drive<br>acknowledging the controller's<br>transfer request. The drive then   |

TABLE 3. FIXED DISK DRIVE CONTROL CONNECTOR (J1)

PRELIMINARY DRAFT

accepts command/data or returns configuration/status information.

- ATN- Attention. Control signal from the selected drive that indicates the drive has a faulty condition or a change of status. This signal is active also during drive power-up sequence.

- SCT- Sector Pulse (or Address Mark Found). Sector clock from the selected drive. Used for hard sectored format to mark the beginning of each sector. Used for soft sectored format to flag detection of an address mark.

- INDEX- Index. Positioning signal from the drive that occurs once per drive revolution. Used by the WDC for track formatting and command timeout.

- DRDY- Drive Ready. Control signal from the drive indicating the drive's motor is up to speed and that the I/O control signals are valid.

- TXREQ- Transfer Request. This control signal sets for command/data information transfers to the drive or for configuration/status information transfers from the drive.

- DS0- Drive Select. WFDC selects only DS1- Drive 0 or 1.

RG- Read gate. Enables the selected drive to send read data. Controls the drive VCO and data recovery circuit.

CMDDAT- Command Data. Sixteen-bit serial data plus parity sent to the selected drive. Data contains instructions for drive execution, i.e., recalibrate, seek, request status.

PRELIMINARY DRAFT

12

16

20

22

24

26

28

32

34

| TABLE 4. FIXED DISK DATA CONNECTORS (J2, J3) |                            |                                                                                                                                                                                                                                                                        |  |  |  |  |

|----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin                                          | Signal                     | Description                                                                                                                                                                                                                                                            |  |  |  |  |

| 1                                            | DSLTD 0,1-                 | Drive Selected. Status signal from<br>the drive informing the controller<br>of the selection status after it<br>has asserted a drive selection<br>signal.                                                                                                              |  |  |  |  |

| 3                                            | CMDCPLT 0,1-               | Command Completed. Status signal from each drive indicating comple-tion of any command.                                                                                                                                                                                |  |  |  |  |

| 4                                            | AME 0,1-                   | Address Mark Enable. Control<br>output to each drive used to write<br>address mark onto the disk or<br>search for address mark.                                                                                                                                        |  |  |  |  |

| 5,6,15,16,19                                 | GND                        | Ground                                                                                                                                                                                                                                                                 |  |  |  |  |

| 7<br>8                                       | WCLOCK 0,1+<br>WCLOCK 0,1- | Write Data Clock. Differen-<br>tial signal for synchronizing<br>write data operations. Derived<br>from reference clock.                                                                                                                                                |  |  |  |  |

| 10<br>11                                     | RCLK 0,1+<br>RCLK 0,1-     | Read/reference clock. Differen-<br>tial signal from the drive used to<br>determine data transfer rate. The<br>drive's data recovery circuits<br>supply the read clock during read<br>data transfers. At all other times<br>the drive furnishes the reference<br>clock. |  |  |  |  |

| 13<br>14                                     | WDATA 0,1+<br>WDATA 0,1-   | Differential write data to be written to each drive.                                                                                                                                                                                                                   |  |  |  |  |

| 17<br>18                                     | RDATA 0,1+<br>RDATA 0,1-   | Differential read data input from each drive.                                                                                                                                                                                                                          |  |  |  |  |

# Floppy Drive Interface

The controller interfaces to the floppy drives via one 34-pin data and control cable (J4) per the 5 1/4" PC-AT standard. Table 5 below provides the pin descriptions.

PRELIMINARY DRAFT

| TABLE 5. FLOPPY DISK DRIVE INTERFACE (J4)             |                |                                                                                                                                                                                                      |  |  |  |

|-------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                                                   | Signal         | Description                                                                                                                                                                                          |  |  |  |

| 1,3,5,7,9,11,13,<br>15,17,19,21,23,<br>25,27,29,31,33 | GND            | Ground - Pin 5 keys the connector.                                                                                                                                                                   |  |  |  |

| 2                                                     | DRATESLCT      | Dual Rate Select. Selects<br>either 360 rpm or 300 rpm for<br>dual-speed drives.                                                                                                                     |  |  |  |

| 8                                                     | IDX-           | Floppy Index Pulse. Position-<br>ing signal used by the FDC to<br>indicate the beginning of a<br>disk track.                                                                                         |  |  |  |

| 10<br>16                                              | M01-<br>M02-   | Floppy drive motor enable.                                                                                                                                                                           |  |  |  |

| 12<br>14                                              | FDS2-<br>FDS1- | Floppy Drive Select 1 and 2.<br>Select signals from the FDC<br>operations register. A system<br>master reset or a software<br>reset will inactivate these<br>signals.                                |  |  |  |

| 18                                                    | DIRC-          | Direction Control. Determines<br>the head 'step' direction of a<br>selected drive during<br>controller seek operations.<br>When asserted (low), the step<br>direction is toward the inner<br>tracks. |  |  |  |

| 20                                                    | STEP-          | Step. Step pulses to the<br>selected drive from the FDC.<br>FDC's Specify command<br>controls the rate.                                                                                              |  |  |  |

| 22                                                    | FWD-           | Floppy write (MFM or FM).<br>Data input to selected drive.                                                                                                                                           |  |  |  |

| 24                                                    | FWE-           | Floppy Write Enable. Enable<br>signal from FDC to selected<br>head.                                                                                                                                  |  |  |  |

| 26                                                    | TRK0-          | Floppy Track 0. During seek<br>operations, the selected<br>drive issues a positioning<br>flag to indicate head position<br>over the outermost track.                                                 |  |  |  |

PRELIMINARY DRAFT

| 28 | FWP-  | Floppy Write Protect. Write<br>protect status from selected<br>drive.                             |

|----|-------|---------------------------------------------------------------------------------------------------|

| 30 | FRDD- | Floppy read data. Output from selected drive.                                                     |

| 32 | FHS-  | Floppy Head Select. Head<br>select signal to the<br>active drive. A low signal<br>selects Head 1. |

| 34 | DCHG- | Diskette change status. Used<br>for host control of diagnostic<br>information.                    |

PRELIMINARY DRAFT

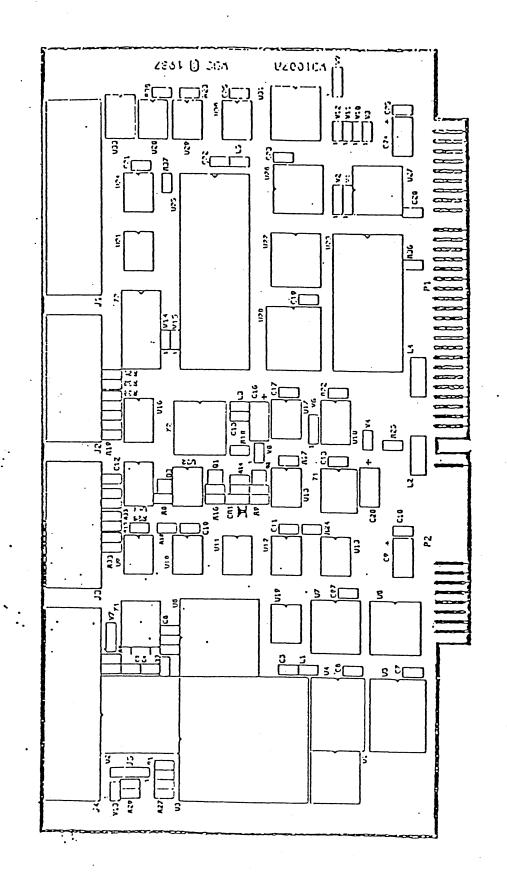

# FIGURE 3. CONTROLLER MODULE LAYOUT

PRELIMINARY DRAFT Page 12

Figure 3 illustrates the general module jumper placement and approximate connector locations. The module dimensions are 13.12 by 4.2 inches and a mounting bracket is included. Jumper configurations for the WFDC module appear in Table 6.

#### WFDC Configuration

Table 6 below lists the default settings for the WD1007A-WA2 which supports two 5-1/4 inch drives. The WD1007A-WAH is a hard disk only version of the controller.

#### TABLE 6. JUMPER DEFAULT SETTINGS

| Jumper Function                                                                                                                                                   | WD10                                               | 07A-WA2                                                                          | WD10                                        | )7A-WAH                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------|

| BIOS Address Select<br>BIOS Address Select<br>BIOS Shadow RAM Enable<br>Floppy Enable<br>Dual Spindle Speed Enable<br>Floppy Address Select<br>Floppy Drive Type  | W1<br>W2<br>W3<br>W4<br>W5<br>W6<br>W7             | 2-3<br>2-3<br>Jumper<br>No Jumper<br>No Jumper<br>2-3<br>1-2                     | พ1<br>พ2<br>พ3                              | 2-3<br>2-3<br>Jumper                                                       |

| 5WAH Mode Select<br>Chassis ground<br>Digital Input Register<br>Diskette Change Enable<br>Secondary Address Select<br>In Etch<br>Translate Override<br>ECC Length | W8<br>W9<br>W10<br>W11<br>W12<br>W13<br>W14<br>W15 | No Jumper<br>No Jumper<br>Jumper<br>No Jumper<br>Uncut<br>No Jumper<br>No Jumper | W8<br>W9<br>W10<br>W11<br>W12<br>W14<br>W15 | No Jumper<br>No Jumper<br>No Jumper<br>No Jumper<br>No Jumper<br>No Jumper |

#### Address Select Jumpers

Jumper connections W1-W2 select the BIOS ROM/RAM memory addresses. The default address range (C8000 - C9FFF) is factory set. Jumper connection W3 enables the ROM/RAM BIOS when it is jumpered.

Jumper connecton W6 selects the floppy drive's address ranges. The default range is 3FX.

The module's primary hard disk address range is (1F0-1F7 and 3F6-3F7). To select the secondary hard disk address range (170-177 and 376-377), jumper the W12 connector.

| BIOS ADDRESS RANGES                                              | JUMPER SE<br>W1 W2                                   | TTINGS<br>W3         |

|------------------------------------------------------------------|------------------------------------------------------|----------------------|

| C8000 - 09FFF<br>CA000 - CBFFF<br>CC000 - CDFFF<br>CE000 - CFFFF | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 2 Jumper<br>3 Jumper |

| FLOPPY ADDRESS RANGES                                            | w6                                                   |                      |

| 37X<br>3FX                                                       | 1 - 2<br>2 - 3                                       |                      |

| PRIMARY/SECONDARY<br>HARD DISK ADDRESSES                         | w12                                                  |                      |

| 1FX<br>17X                                                       | No Jumper<br>Jumper                                  |                      |

#### TABLE 7. ADDRESS SELECT JUMPERS

#### Diagnostic Register Latch Control

When installed, jumper connection W10 enables the diagnostic Digital Input Register for operation in the latched mode; i.e., the register outputs latch when the register is accessed. The jumper is normally not used.

#### WD1018 Mode Control

Jumper connections W8, W14, W15 provide three external mode selects to the control processor.

#### **W8**

<u>No Jumper</u> - This is the normal WD1007A-WAH/WA2 mode. The firmware forces a 10 Mhz ESDI drive to 35 sectors per track when using the Set Unformatted Bytes per Sector command. This mode supports a 1:1 interleave.

<u>Jumper</u> - This is the WD1005-WAH mode. It allows the 1007A-WAH to be used as a replacement board for existing WD1005-WAH boards without reformatting the drive. It provides 36 sectors per track, a 2:1 interleave, and use of the Set Unformatted Bytes per Second command. This eliminates the need to set the drive's jumpers and switches for the desired number of sectors per track.

#### W14

Because some of the older operating systems can only recognize 17 sectors per track or a maximum of 1048 cylinders per drive, the

PRELIMINARY DRAFT

WD1007A-WA2 provides a translation scheme so that ESDI hard disk drives can be fully utilized in the PC/AT environment.

<u>No Jumper</u> - The translation mode provides two types of physical to logical translation. See Translation, page 39 for explanation.

<u>Jumper</u> - Physical to logical translation by the firmware is disabled.

#### W15

The purpose of this jumper is to support either four or seven bytes of syndrome during Read or Write Long commands. Four bytes of ECC is the default mode. Installing the jumper provides seven bytes of ECC.

#### Floppy Drive and Data Rate Selection Control

Jumper connection W5 selects either single speed or dual speed drive type. A jumper is not normally installed causing selection to default to a single speed drive and 125 nanoseconds precompensation.

The WD1007A-WA2 supports 5 1/4 inch, 1.2 Megabyte or 360 Kbyte floppy disk drives. W7 (1 - 2) must be jumpered to select the 1.2 Megabyte drive option.

Jumper connectors W4 and W13 enable the floppy drive controller.

| FLOPPY CONTROLLER | W4        | W13 IN ETCH |

|-------------------|-----------|-------------|

| ENABLE            | No Jumper | Uncut       |

| DISABLE           | Jumper    | Cut         |

Jumper W11 is the disk change input signal, and must be jumpered if floppy drives are installed.

#### Mounting Bracket Jumper

Jumper connection W9 allows grounding of the module mounting bracket to chassis or logic ground. The jumper is not normally used.

W9

| Chassis | ground | connected    | 2 | - | 3 |  |

|---------|--------|--------------|---|---|---|--|

| Digital | ground | disconnected | 1 | - | 2 |  |

PRELIMINARY DRAFT

### INTERFACE DESCRIPTION - SOFTWARE

## Register Address Map

Table 8 summarizes the WFDC I/O Register Address Map and includes the WD50C12 task file area, the WD37C65 registers and the module auxiliary support registers. It lists the primary address first with the secondary address shown within parentheses.

| +                                                                                                                                                                                                |                                                                                                 |                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS (HEX)                                                                                                                                                                                    | REGISTER                                                                                        | FUNCTION                                                                                                                                                                                                                                                                                  |

| 1F0 (170) RW<br>  1F1 (171) WO<br>  1F1 (171) RO<br>  1F2 (172) RW<br>  1F3 (173) RW<br>  1F3 (173) RW<br>  1F4 (174) RW<br>  1F5 (175) RW<br>  1F6 (176) RW<br>  1F7 (177) WO<br>  1F7 (177) RO | HDDTR<br>HDPLO<br>HDERR<br>HDSCT<br>HDSSN<br>HDCLL<br>HDCLH<br>HDCLH<br>HDSDH<br>HDCMD<br>HDSTT | Hard Disk Data Register (16 bits)  <br>Gap, ID PLO and Data PLO Lengths  <br>Error Register  <br>Sector Count  <br>Starting Sector Number  <br>Cylinder Number - Low Byte  <br>Cylinder Number - High Byte  <br>Sector Size, Drive/Head Select  <br>Command Register  <br>Status Register |

| 3F2 (372) WO<br>3F4 (374) RO<br>3F5 (375) RW<br>3F6 (376) WO<br>3F6 (376) RO<br>3F7 (377) WO<br>3F7 (377) RO                                                                                     | FDDOR<br>FDMSR<br>FDDTR<br>HDFDR<br>HDASR<br>FDFCR<br>HDDIR                                     | Floppy Digital Operations Register  <br>Floppy Main Status Reg (WD37C65)  <br>Floppy Data Registers (WD37C65)  <br>Fixed Disk (Control) Register  <br>Alternate Status Register  <br>Floppy Control Register  <br>Digital Input Register                                                  |

TABLE 8. REGISTER ADDRESS MAP

#### Task File Registers

Table 9 summarizes the fixed disk Task File Registers (addresses 1F1/171 through 1F7/177) and their bit assignments with respect to the system processor's lower-byte bus terms (SD07-00).

Host access to these registers is always via the register image contained within the AMAC. The WD1018 control processor has access to both the AMAC and WD50C12 register set.

| REGISTER     |   | 7   | 1 | 6    |     | 5    | 1   | 4    | 1   | 3     | I  | 2    | 1   | 1     | ۱  | 0   |

|--------------|---|-----|---|------|-----|------|-----|------|-----|-------|----|------|-----|-------|----|-----|

| HDPLO        |   |     | ( | GAP, | ID  | PL   | 5 Z | AND  | DA  | TA PI | 20 | LENG | GTH | IS    |    |     |

| HDERR        |   | BBD |   | ECC  |     | 0    |     | INF  |     | 0     |    | ACD  |     | TK0   |    | DNF |

| <b>ĻDSCT</b> |   |     |   |      | NU  | MBEI | R ( | OF S | EC: | ORS   |    |      |     |       |    |     |

| HDSSN        |   |     |   | ST   | ART | ING  | SI  | ECTO | R 1 | IUMBI | ER |      |     |       |    |     |

| HDCLL        | I |     |   | C    | YLI | NDE  | R I | NUMB | ER  | LSB   |    |      |     |       |    |     |

| HDCLH        |   | 0   |   | 0    |     | 0    |     | 0    |     | 0     |    | CYL  | N   | JMBEI | 21 | MSB |

| HDSDH        |   | 1   |   | S    | ЕСТ | OR   |     | DN   |     | HS3   |    | HS2  |     | HS1   |    | HS0 |

| HDCMD        |   |     |   |      |     |      | C   | OMMA | ND  |       |    |      |     |       |    |     |

| HDSTT        |   | BSY |   | RDY  |     | WFT  |     | SKC  |     | DRQ   |    | CRD  |     | CIP   |    | ERR |

|              |   |     |   |      |     |      |     |      |     |       |    |      |     |       |    |     |

TABLE 9. TASK FILE REGISTERS

#### WFDC Control and Status Registers

Hard Disk Alternate Status Register (HDASR) 3F6/376 (RO)

This register lies within the AMAC array and provides fixed disk status to the system processor. The register contains a 'real time' section (bits 7, 6, 3 and 1) and a 'register' section set by the control processor at sector transfer time (bits 5, 4, 2 and 0).

PRELIMINARY DRAFT

TABLE 10. ALTERNATE STATUS REGISTER

| +- |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| 1  | 7 | I | 6 | 1 | 5 | 1 | 4 | I | 3 | 1 | 2 | 1 | 1 | 1 | 0   |

|    |   | • |   | • |   | • |   | • |   |   |   | • |   | - |     |

| 1  |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ERR |

|    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

where: BSY = Controller Busy Flag RDY = Ready from selected drive WFT = Write Fault Flag from WD1018 SKC = Seek Complete Flag from WD1018 DRQ = Data Transfer Request Flag CRD = Corrected Data Flag from WD1018 IDX = Index Pulse from selected drive ERR = Error Flag from WD1018

The Alternate Status Register reflects the same status as the WD50C12 Status Register, except for bit position 1 which holds the drive index signal instead of the Command in Progress (CIP) flag. The index bit does not latch and thus follows the drive control signal (approximately a 200 microsecond pulse every 16.7 milliseconds).

The Write Fault bit sets for all the ESDI error conditions. The host processor detects a drive's error by issuing the Initiate ESDI command to read the drive's status.

The host processor can interrogate the register at any time without interfering with other control functions. The host status input at this address will not clear the fixed disk interrupt.

Hard Disk Diagnostic Input Register (HDDIR) 3F7/377 (RO)

The fixed disk Diagnostic Input Register reflects the current state of the floppy diskette change flag and the fixed disk Drive Select, Head Select and Drive Write gate signals (complimented form). When the floppy disk option is not installed, bit 7 remains tri-state.

PRELIMINARY DRAFT

TABLE 11. WFDC DIAGNOSTIC INPUT REGISTER

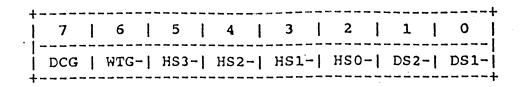

| -  | 7  | l | 6   | I | 5    | I | 4   | I | 3   | I  | 2   | Ι | 1   | I | 0   |  |

|----|----|---|-----|---|------|---|-----|---|-----|----|-----|---|-----|---|-----|--|

| DC | CG | 1 | WTG | - | HS3- | - | HS2 | - | HS1 | -1 | HS0 | - | DS2 | - | DS1 |  |

where: DCG = Diskette Change flag WTG- = Write Gate on HS3-/0- = Drive Head Select (binary) DS2-/1- = Drive Select

The WD1018 generates the head select signals which are not transparent as in previous Western Digital Winchester disk controllers. Before the HDASR can be read correctly, the WD1018 requires a "wake-up" in order to update the head select signals.

Hard Disk Auxiliary Control Register (HDFDR) 3F6/376 (WO)

AMAC's Hard Disk Auxiliary Control Register provides programmable controller reset. It also provides enable/disable control of the fixed disk priority interrupt.

TABLE 12. AUXILIARY CONTROL REGISTER

| +- |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   | -+ |

|----|---|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|----|

| 1  | 7 | 1 | 6 | 1 | 5 |   | 4 | 1 | 3 |   | 2   | 1 | 1 | 1 | 0 | 1  |

| •  |   | • |   | • |   | - |   | • |   | • |     |   |   | • |   | •  |

| •  |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   | •  |

| •  |   |   |   | • |   |   |   |   |   |   | RST | • |   | • |   |    |

| +- |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   | -+ |

where: RST = Program controlled (master) reset IDS = Data Transfer Interrupt Disable

NOTE: The software controlled reset bit (RST) will reset the fixed disk logic for as long as the bit is 'on'. RST must be turned on (for a minimum of 10.0 microseconds), then off, to complete the reset function.

The Interrupt Disable control bit does not clear the interrupt level of the disabled state. A pending interrupt will occur when it is re-enabled. A system Master Reset will disable the interrupt.

#### Fixed Disk Data Registers

The controller reserves the system's I/O address 1F0/170(H) for programmed transfers of input/output data for the fixed disk. All data transactions on the system bus between the controller and the system processor use a 16-bit word. The controller and AMAC array provide read and write data 'pipeline' registers in order for the sector data memory to function as a dual-port memory. These registers (along with the host's upper byte

PRELIMINARY DRAFT

equivalent) allow the WFDC module to perform concurrent host and WDC memory accesses necessary for multi-sector 1:1 interleaving. The AMAC arbitrates simultaneous host and WDC requests and gates the appropriate address counter to external memory.

Table 13 below illustrates the fixed disk data format.

TABLE 13. FIXED DISK (WORD) DATA FORMAT

| + |        |   |      |     |   |      |     |   |   |      |     |   |      |     |        |  |

|---|--------|---|------|-----|---|------|-----|---|---|------|-----|---|------|-----|--------|--|

| • |        |   |      |     |   |      |     |   |   |      |     |   |      |     |        |  |

| 1 | ID     |   | WORD | 000 |   | WORD | 000 |   | 1 | WORD | 255 |   | WORD | 255 | CHECK  |  |

|   |        |   |      |     |   |      |     | • | • |      |     | • |      |     | • •    |  |

|   | FIELDS |   | LS   | в   |   | MS   | SB  |   |   | -LS  | SB  |   | MS   | SB  | FIELDS |  |

| : |        | • |      |     | • |      |     | • | • |      |     | • |      |     |        |  |

| + |        |   |      |     | - |      |     |   |   |      |     |   |      |     |        |  |

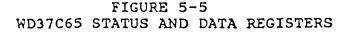

#### WD37C65 Floppy Disk Controller Status/Data Registers

Table 14 summarizes FDC's status and data read/write registers and bit assignments with respect to the system's lower-byte data bus. The main status register (FDMSR) contains the controller's primary status and may be accessed at any time. It indicates drive busy status and facilitates host/controller data transfers. The data register (FDDTR) is actually a register stack that is written during the WD37C65 command phase and read during the result phase.

TABLE 14. WD37C65 STATUS AND DATA REGISTERS

| REGISTER |   | 7   |   | 6   | 1 | 5   |     | 4   |     | 3   |     | 2 | 1 | 1   |  | 0   |

|----------|---|-----|---|-----|---|-----|-----|-----|-----|-----|-----|---|---|-----|--|-----|

| FDMSR    |   | RQM | 1 | DIO | 1 | EXM |     | СВ  |     | 0   |     | 0 |   | D1B |  | DOB |

| FDDTR    | 1 |     |   |     |   | RE  | EAI | )/W | RIT | E D | ATA |   |   |     |  |     |

where: RQM = Transfer Request To/From Host DIO = Transfer Direction, `1' is from WD37C65 to Host EXM = Not DMA Transfer Mode during command execution phase CB = Read or Write Command in Progress (Busy) D1B = Drive B in Seek Mode (Busy) D0B = Drive A in Seek Mode (Busy)

Data Read/Write Register Stack

Tables 15 and 16 illustrate the write stack registers and the read stack registers, respectively.

The stack is accessed at the FDDTR register address 3F5 (375).

PRELIMINARY DRAFT

#### TABLE 15. WD37C65 WRITE STACK REGISTER

| +                                         |          |              |          |              |     |      |      |      |     |      |           |                     | `<br> |      |    |       |

|-------------------------------------------|----------|--------------|----------|--------------|-----|------|------|------|-----|------|-----------|---------------------|-------|------|----|-------|

| WD37C65<br>  REGISTER                     | l        |              |          |              |     | E    | BIT  | ASS  | IGN | IMEN | T         |                     |       |      |    |       |

| MNEMONIC                                  |          | 7            |          | 6            |     | 5    |      | 4    |     | 3    |           | 2                   |       | 1    |    | 0     |

| CMD                                       |          | MT           |          | MF           |     | SK   |      |      |     |      | CMI       | o co                | DE    |      |    |       |

| SEL                                       | 1        | 0            |          | 0            | 1   | 0    |      | 0    |     | 0    |           | HS                  |       | 0    |    | US0   |

| C                                         |          | 0            |          |              |     |      | 0    | CYLI | NDE | ER N | IUME      | BER                 |       |      |    |       |

| Н                                         |          | 0            |          | 0            |     | 0    |      | 0    |     | 0    |           | 0                   |       | 0    |    | HA    |

| R                                         |          | 0            |          | 0            | 1   | 0    |      | 0    |     |      | SI        | ЕСТО                | R N   | NUMB | ER |       |

| N                                         | 1        | 0            |          | 0            |     | 0    |      | 0    |     | 0    |           | 0                   |       | 1    |    | 0     |

| EOT                                       |          | 0            |          | 0            |     | 0    |      | 0    |     | TRA  | CK        | FIN                 | AL    | SEC  | TO | R #   |

| GPL                                       |          |              |          |              | E   | ORM  | 1AT  | GAP  | LI  | ENGT | н         |                     |       |      |    |       |

| DTL                                       |          | 1            |          | 1            |     | 1    |      | 1    |     | 1    |           | 1                   |       | 1    |    | 1     |

| SC                                        |          | 0            |          | 0            |     | 0    |      | 0    |     | SEC  | TOF       | RS P                | ER    | CYL  | IN | DER   |

| D                                         |          |              |          | ()           | FOE | RMAT | C) [ | ATA  | F   | LLE  | R I       | BYTE                |       |      |    |       |

| STP                                       |          | 0            |          | 0            |     | 0    |      | 0    |     | 0    |           | 0                   |       | STP  |    | STP   |

| SHT                                       |          | STE          | P        | RATE         | T   | [ME  | (SF  | RT)  |     | HEA  |           | JNLO                | AD    | TIM  | E  | (HUT) |

| HLD                                       |          |              |          |              | HI  | EAD  | LOF  | AD T | IM  | E (H | LT)       | )                   |       |      |    | ND    |

| NCN                                       |          | 0            |          |              |     |      | NEV  | V CY |     | NDEF | NU        | JMBE                | R<br> |      |    |       |

| MT = Mult<br>SK = Skip                    |          |              |          |              |     | ss N | 1ar) | ¢    |     | -    | = U1      | FM D<br>hit<br>elec | (Di   | rive |    |       |

| HS = Head $STP = 1 =$ $= 2 =$ $ND = Non-$ | Sc<br>Sc | an C<br>an C | om<br>om | pare<br>pare | A   | lter |      |      |     | ctor | = He<br>s | ead                 |       |      | S  | 1     |

Note: The MT, MF and SK command bits set to zero for those commands which do not define them. The FDC digital operations register (FDDOR) selects the drive. The unit select bit (USO) is shown for reference only. The HD bit selects the head. The head address bit (HA) identifies the sector.

PRELIMINARY DRAFT

|                 | WD37C6                                                           | •               |              |    |                                |                                                 |                                                            | BI                                                                                | T P                                                      | os                                              | ITIO                                                            | N                   |                                             |                                  |                                                                      |                                                                                                                    |                                                              |