# WD1007A-WAH/WA2 WINCHESTER/FLOPPY DISK CONTROLLER

# FEATURES

- IBM\* PC-AT\* compatible Winchester and floppy disk controller

- ESDI Drive Interface

- Utilizes maximum storage capacity of ESDI drives

- Controls two fixed disk drives and two floppy disk drives (5.25 or 3.5 inch)

- 84-pin Buffer Management and Control (AMAC) gate array

- Optional BIOS ROM

- · Supports 1:1 interleave

- · Data transfer rate of 10 Mbits per second

- · Supports NRZ disk data format

- Two 8192 x 8 RAMs for look-ahead read caching to reduce disk access time and increase data throughput

- · Software selectable 56-bit ECC

- · Multiple sector read/write commands

# DESCRIPTION

The WD1007A-WA2 Winchester/Floppy Disk Controller (WFDC) module interfaces two ESDIcompatible fixed disk drives and two floppy disk drives (5.25 or 3.5 inch) to the PC-AT computer I/O Channel bus structure. An optional BIOS ROM provides parameter tables, low-level formatting and surface analysis routines to fully integrate ESDI drive capabilities into the system.

The fixed disk section of the module includes the WD50C12 Winchester Disk Controller, the WD1018 Buffer Manager/Control Processor, sector buffer RAM and associated control logic. The WD37C65A Floppy Disk Controller (FDC) implements the optional floppy disk control section. The WD12C00A (AMAC) gate array also provides buffering and control. The AMAC reduces module logic and supports a 1:1 interleave format.

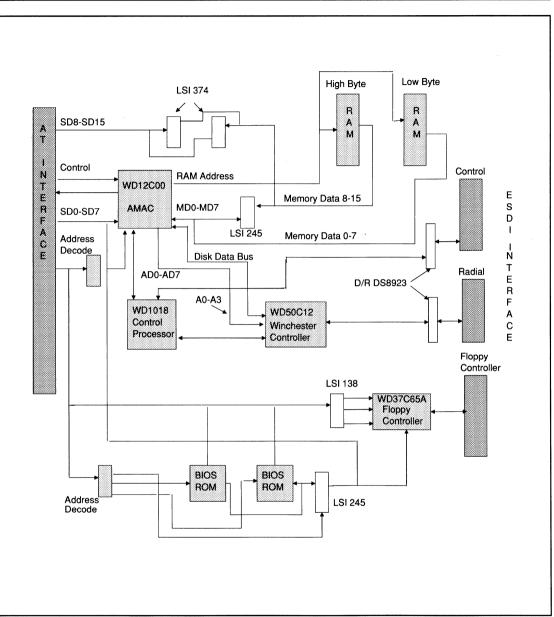

A description of the functional blocks of the WD1007A-WA2 Winchester/Floppy Disk Controller (WFDC) appears below. Refer to the block diagram in Figure 1.

## WD50C12 Winchester Disk Controller

The WD50C12 Winchester Disk Controller (WDC) is an advanced VLSI device that controls and coordinates the activity of the hard disk drive. The WDC supports 1:1 interleave and data transfer rates up to 10 Mbits per second. It utilizes the maximum storage capacity of ESDI drives by translating physical parameters into logical parameters for those operating systems which do not recognize more than 17 sectors per track or more than 1048 cylinders per drive. (See Translation in the Appendix for an explanation of this feature). The WDC offers software selectable 56-bit ECC and supports the NRZ data format.

#### WD1018 Buffer Manager/Control Processor

The WD1018 Buffer Manager/Control Processor is an eight-bit microcontroller that operates with the WD50C12 and the AMAC logic array to facilitate processing of disk commands. It provides sector data buffer management, helps in error recovery procedures and performs module diagnostics. The processor chip includes internal RAM and ROM memory.

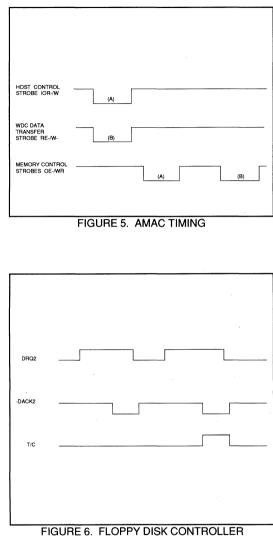

## WD12C00A-JU22 Logic Array (AMAC)

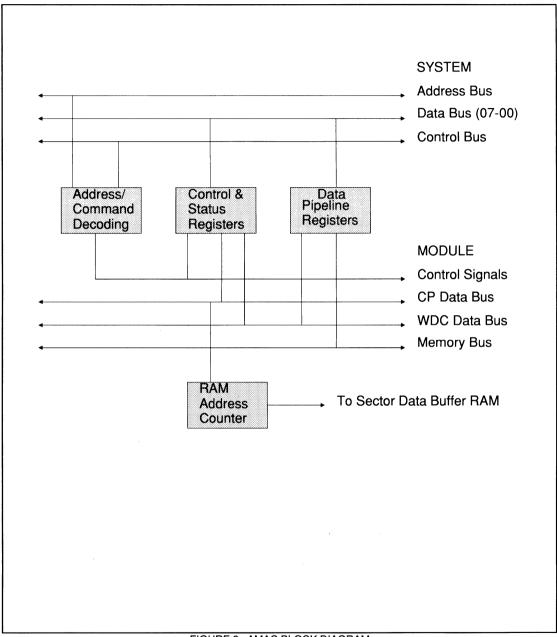

The primary function of the AMAC logic is to provide host address and command decoding, task file control and data buffering. The VLSI logic array replaces the standard WD1014 support device and several SSI/MSI components. This simplifies the logic and lowers power consumption. The AMAC logic includes the data and address registers, memory read/write control, and WD50C12 task file image registers. It interfaces to both the system and module (local) bus structures. (See Figure 2. AMAC Block Diagram)

\* IBM and AT are registered trademarks of International Business Machines.

# WESTERN DIGITAL

#### **RAM Data Buffer**

Two 8192 x 8 static RAM memories buffer the sector data between the drive(s) and the PC-AT system bus. They also buffer Error Correction Code (ECC) information between the WD50C12 disk controller and the WD1018 control processor. The sector buffers and the above control components provide a 1:1 sector interleave format for optimal system performance.

#### WD37C65A Floppy Disk Controller (FDC)

The optional WD37C65A Floppy Disk Controller (FDC) is a standard VLSI device that supports both single and double density diskette formats and provides data and control interfaces for the host and the floppy drive. The units major features include:

- Multiple sector and track read/write commands

- Host DMA and programmed I/O data transfers

- High performance digital data separation

#### BIOS (P)ROM/RAM Option

Controller circuitry accommodates a programmed BIOS device for special applications. One unique feature of this BIOS option is its shadow RAM. The static RAM (which shares with the BIOS (P)ROM the last 256 upper address bytes of the BIOS's 8 Kbyte address range) contains the Winchester drive's parameters. This shadow RAM feature allows the WFDC to interface with all types of ESDI drives without modifying the system BIOS. Option jumpers allow the device to be mapped at one of four address ranges. For more information, refer to the jumper configuration tables on page 10 through 13.

FIGURE 1. WD1007A-WA2 BLOCK DIAGRAM

# FIGURE 2. AMAC BLOCK DIAGRAM

# **INTERFACE DESCRIPTION - HARDWARE**

#### **System Bus Interface**

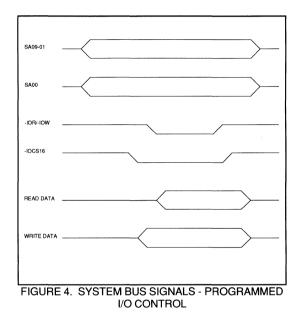

The WFDC interfaces with the system bus address to transmit data and I/O control signals. All fixed disk read/write data transfers are 16-bits wide and utilize the host I/O transfer protocol. Floppy disk data, fixed disk control, floppy disk control, and status transfers are 8 bits wide and use the lower data byte (SD07-00) only. The register address map of the WFDC module is fixed (at a primary or secondary range) as are the bus interrupt requests and the Floppy DMA channel assignment.

Tables 1 and 2 below provides the pin descriptions for the P1 and P2 system bus connectors.

| PIN                                                    | MNEMONIC  | SIGNAL NAME            | I/O | FUNCTION                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------|-----------|------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1,A10,B4,<br>B5,B7-<br>B9,B15-<br>B21,B23-<br>B25,B30 | NC        | Not Connected          |     |                                                                                                                                                                                                                                                                                                               |

| A02-A09                                                | SD07-SD00 | System Data Bus        | I/O | Transfers 16-bit fixed disk data, 8-bit floppy data and 8-bit module control and status information.                                                                                                                                                                                                          |

| A11                                                    | AEN       | Address Enable         | Ι   | Indicates a valid I/O address is on the system bus.<br>The AMAC decode logic uses this term to qualify the<br>I/O address decoding.                                                                                                                                                                           |

| A12-A31                                                | SA19-SA00 | System Address<br>Bus  | I   | Selects the WFDC I/O addresses and BIOS ROM addresses.                                                                                                                                                                                                                                                        |

| B01,B10,B31                                            | GND       | Ground                 |     |                                                                                                                                                                                                                                                                                                               |

| B02                                                    | RST       | Reset                  | I   | Input module reset used to initialize the WD50C12,<br>WD1018 and WD37C65A; clear the interrupt levels;<br>and deselect the hard disk drives. When Reset<br>clears, the WD1018 will automatically execute on-<br>board diagnostic tests and load the test result status<br>into the Fixed Disk Error Register. |

| B03,B29                                                | VCC       |                        |     |                                                                                                                                                                                                                                                                                                               |

| B06                                                    | DRQ2      | DMA Request<br>Level 2 | 0   | When a data byte is ready for transfer to or from the host memory, the WD37C65A floppy controller generates this signal.                                                                                                                                                                                      |

| B11                                                    | -SMEMW    | System Memory<br>Write | I   | Input strobe used to write drive parameters in the Shadow RAM.                                                                                                                                                                                                                                                |

| B12                                                    | -SMEMR    | System Memory<br>Read  | 1   | Enables BIOS ROM and shadow RAM.                                                                                                                                                                                                                                                                              |

#### TABLE 1. SYSTEM INTERFACE CONNECTOR (P1)

| PIN | MNEMONIC | SIGNAL NAME                    | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                 |

|-----|----------|--------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B13 | -IOW     | I/O Write                      | I   | Asserted by the system processor during bus 'write' cycles. The WFDC uses this strobe and the decoded bus address to input both data and command information.                                                                                                                                                            |

| B14 | -IOR     | I/O Read.                      | I   | Asserted by the system processor during bus 'read' cycles. The WFDC uses the signal (along with the system address bus decoding or DMA ACK signal) to enable system I/O reads of both data and command information.                                                                                                      |

| B22 | IRQ6     | Interrupt Request<br>Level 6.  | 0   | Floppy controller interrupt request to the system<br>processor indicating that the WD37C65A has com-<br>pleted the execution phase of a command or that the<br>selected 'drive ready' line has changed state. Read-<br>ing the result phase status or issuing a Sense Inter-<br>rupt Status command will clear the IRQ6. |

| B26 | -DACK2   | DMA<br>Acknowledge<br>Level 2. | I   | Indicates the completion of a data byte transfer. The DMA controller provides bus control and system memory address.                                                                                                                                                                                                     |

| B27 | T/C      | DMA Terminal<br>Count          | I   | The WD37C65A terminates the data transfer se-<br>guence for read, write or scan commands when the<br>DMA controller issues this signal.                                                                                                                                                                                  |

| B28 | BALE     | Bus Address<br>Latch Enable.   | 1   | Input control signal used to initiate a data transfer on<br>the system bus. The WFDC uses this input to<br>generate the I/O transfer control signal and to enable<br>control signals for high-order data bytes.                                                                                                          |

# TABLE 1. SYSTEM INTERFACE CONNECTOR (P1) Continued

# TABLE 2. SYSTEM INTERFACE CONNECTORS (P2)

| PIN                                | MNEMONIC  | SIGNAL NAME                   | I/O | FUNCTION                                                                                                                                                                                                       |

|------------------------------------|-----------|-------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1-C10,D1,<br>D3-D6,<br>D8-D15,D17 | NC        | Not Connected                 |     |                                                                                                                                                                                                                |

| C18-C11                            | SD15-SD08 | System Data Bus               | I/O | Transfers 16-bit fixed disk data, 8-bit floppy data and 8-bit module control and status information.                                                                                                           |

| D02                                | -I/OCS16  | I/O Control Signal<br>16      | 0   | Indicates 16-bit data transfer mode. The WFDC as-<br>serts this signal for all hard disk data transfers.                                                                                                       |

| D07                                | IRQ14     | Interrupt Request<br>Level 14 | 0   | Output to the processor from the fixed disk control requesting a data block transfer or indicating com-<br>mand completion. The level clears on a subsequent fixed disk command to the WFDC or a system reset. |

| D16                                | VCC       |                               |     |                                                                                                                                                                                                                |

| D18                                | GND       | Ground                        |     |                                                                                                                                                                                                                |

#### Winchester Drive Interface

The WFDC module interfaces to the fixed disk drives via one 34-pin control cable (J1) and two 20-pin data cables (J2,J3) in conformance with ESDI signal definitions. The WFDC module does not furnish drive power. Signal descriptions appear in Tables 3 and 4.

|  | TABLE 3 | FIXED DISK | DRIVE ( | CONTROL | CONNECTOR (J1) |  |

|--|---------|------------|---------|---------|----------------|--|

|--|---------|------------|---------|---------|----------------|--|

| PIN                                                       | MNEMONIC   | SIGNAL NAME                                | I/O | FUNCTION                                                                                                                                                                              |

|-----------------------------------------------------------|------------|--------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,3,5,7,9,11,<br>13,15,17,19,<br>21,23,25,27,<br>29,31,33 | GND        | Ground                                     |     | Pin 15 keys the connector.                                                                                                                                                            |

| 2,4,18,14                                                 | HS3-/0-    | Head Select                                | 0   | Binary-coded select signals allows selection of drives with up to 16 read/write heads.                                                                                                |

| 6                                                         | WRG-       | Write Gate                                 | 0   | Enables the selected drive to accept write data. A write fault condition or a module reset will clear this signal.                                                                    |

| 8                                                         | CSD-       | Configuration/<br>Status Data.             | I   | Data from the selected drive in response to controller command.                                                                                                                       |

| 10                                                        | TXACK-     | Transfer<br>Acknowledge.                   | I   | Handshake response from selected drive acknow-<br>ledging the controller's transfer request. The drive<br>then accepts command/data or returns configura-<br>tion/status information. |

| 12                                                        | ATN-       | Attention                                  | Ι   | Control signal from the selected drive that indicates<br>the drive has a faulty condition or a change of status.<br>This signal is active also during drive power-up se-<br>quence.   |

| 16                                                        | SCT-       | Sector Pulse (or<br>Address Mark<br>Found) | I   | Sector clock from the selected drive. Used for hard sectored format to mark the beginning of each sector. Used for soft-sectored format to flag detection of an address mark.         |

| 20                                                        | INDEX-     | Index                                      | I   | Positioning signal from the drive that occurs once per drive revolution. Used by the WDC for track format-ting and command timeout.                                                   |

| 22                                                        | DRDY-      | Drive Ready                                | I   | Control signal from the drive indicating the drive's motor is up to speed and that the I/O control signals are valid.                                                                 |

| 24                                                        | TXREQ-     | Transfer Request                           | 0   | This control signal sets for command/data informa-<br>tion transfers to the drive or for configuration/status<br>information transfers from the drive.                                |

| 26,28                                                     | DS0-, DS1- | Drive Select                               | 0   | WFDC selects only Drive 0 or 1.                                                                                                                                                       |

| 32                                                        | RG-        | Read Gate                                  | 0   | Enables the selected drive to send read data. Con-<br>trols the drive VCO and data recovery circuit.                                                                                  |

| 34                                                        | CMDDAT-    | Command Data                               | 0   | Sixteen-bit serial data plus parity sent to the selected drive. Data contains instructions for drive execution, i.e., recalibrate, seek, request status.                              |

| PIN              | MNEMONIC                   | SIGNAL NAME             | I/O | FUNCTION                                                                                                                                                                                                                              |

|------------------|----------------------------|-------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9,20             | NU                         | Not Used                |     |                                                                                                                                                                                                                                       |

| 1                | DSLTD 0,1-                 | Drive Selected          | I   | Status signal from the drive informing the controller<br>of the selection status after it has asserted a drive<br>selection signal.                                                                                                   |

| 3                | CMDCPLT 0,1-               | Command<br>Completed    | I   | Status signal from each drive indicating completion of any command.                                                                                                                                                                   |

| 4                | AME 0,1-                   | Address Mark<br>Enable  | 0   | Control output to each drive used to write address mark onto the disk or search for address mark.                                                                                                                                     |

| 5,6,15,16,<br>19 | GND                        | Ground                  |     |                                                                                                                                                                                                                                       |

| 7,8              | WCLOCK 0,1+<br>WCLOCK 0,1- | Write Data Clock        | I   | Differential signal for synchronizing write data opera-<br>tions. Derived from reference clock.                                                                                                                                       |

| 10,11            | RCLK 0,1+<br>RCLK 0,1-     | Read/Reference<br>Clock | I   | Differential signal from the drive used to determine<br>data transfer rate. The drive's data recovery circuits<br>supply the read clock during read data transfers. At<br>all other times the drive furnishes the reference<br>clock. |

| 13,14            | WDATA 0,1+<br>WDATA 0,1-   | Write Data              | I   | Differential write data to be written to each drive.                                                                                                                                                                                  |

| 17,18            | RDATA 0,1+<br>RDATA 0,1-   | Read Data               | I   | Differential read data input from each drive.                                                                                                                                                                                         |

# TABLE 4. FIXED DISK DATA CONNECTORS (J2, J3)

# **Floppy Drive Interface**

The controller interfaces to the floppy drives via one 34-pin data and control cable (J4) per the 5.25 inch PC-AT standard. Table 5 below provides the pin descriptions.

| PIN                                                       | MNEMONIC    | SIGNAL NAME                     | I/O | FUNCTION                                                                                                                       |

|-----------------------------------------------------------|-------------|---------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| 1,3,5,7,9,11,<br>13,15,17,19,<br>21,23,25,27,<br>29,31,33 | GND         | Ground                          |     | Pin 5 keys the connector.                                                                                                      |

| 4,6                                                       | NC          | Not Connected                   |     |                                                                                                                                |

| 2                                                         | DRATESLCT   | Dual Rate Select                | 0   | Selects either 360 rpm or 300 rpm for dual-speed drives.                                                                       |

| 8                                                         | IDX-        | Floppy Index<br>Pulse           | I   | Positioning signal used by the FDC to indicate the beginning of a disk track.                                                  |

| 10                                                        | MO1-, M02-  | Floppy Drive<br>Motor Enable    | 0   | Signal from the Digital Output Register to enable either drive.                                                                |

| 14,12                                                     | FDS2-,FDS1- | Floppy Drive<br>Select 1 and 2. | 0   | Select signals from the FDC operations register. A system master reset or a software reset will inac-<br>tivate these signals. |

TABLE 5. FLOPPY DISK DRIVE INTERFACE (J4)

| PIN  | MNEMONIC | SIGNAL NAME                 | I/O | FUNCTION                                                                                                                                                        |

|------|----------|-----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| . 18 | DIRC-    | Direction Control           | 0   | Determines the head 'step' direction of a selected drive during controller seek operations. When asserted (low), the step direction is toward the inner tracks. |

| 20   | STEP-    | Step                        | 0   | Step pulses to the selected drive from the FDC. FDC's Specify command controls the rate.                                                                        |

| 22   | FWD-     | Floppy Write<br>(MFM or FM) | 0   | Data input to selected drive.                                                                                                                                   |

| 24   | FWE-     | Floppy Write<br>Enable 0    | 0   | Enable signal from FDC to selected head.                                                                                                                        |

| 26   | TRK0-    | Floppy Track 0              | I   | During seek operations, the selected drive issues a positioning flag to indicate head position over the outermost track.                                        |

| 28   | FWP-     | Floppy Write<br>Protect     | I   | Write protect status from selected drive.                                                                                                                       |

| 30   | FRDD-    | Floppy Read Data            | I   | Output from selected drive.                                                                                                                                     |

| 32   | FHS-     | Floppy Head<br>Select       | 0   | Head select signal to the active drive. A low signal selects Head 1.                                                                                            |

| 34   | DCHG-    | Diskette Change<br>Status   | I   | Used for host control of diagnostic information.                                                                                                                |

# TABLE 5. FLOPPY DISK DRIVE INTERFACE (J4) Continued

# **WFDC Configuration**

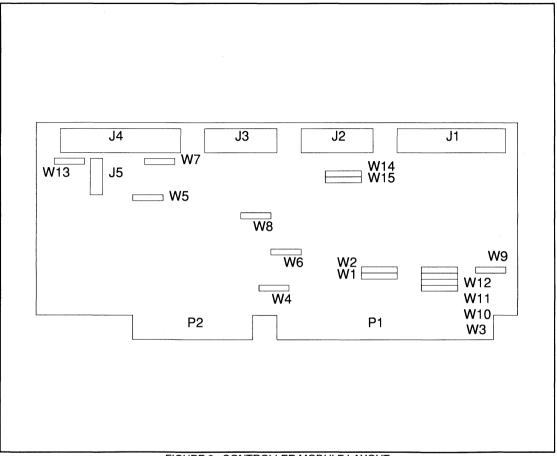

FIGURE 3. CONTROLLER MODULE LAYOUT

Figure 3 illustrates the general module jumper placement and approximate connector locations. The module dimensions are 13.12 by 4.2 inches

and a mounting bracket is included. Jumper configurations for the WFDC module appear in Table 6. Table 6 below lists the default settings for the WD1007A-WA2 which supports two 5.25 or 3.5 inch drives. The WD1007A-WAH is a hard disk only version of the controller.

| WD100      | 07A-WA2                                                                               | WD100                                                                                                                                                                                                                                                                             | 7A-WAH                                                                                                                            |

|------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| W1         | 2-3                                                                                   | W1                                                                                                                                                                                                                                                                                | 2-3                                                                                                                               |

| W2         | 2-3                                                                                   | W2                                                                                                                                                                                                                                                                                | 2-3                                                                                                                               |

| WЗ         | Jumper                                                                                | W3                                                                                                                                                                                                                                                                                | Jumper                                                                                                                            |

| W4         | No Jumper                                                                             |                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| W5         | No Jumper                                                                             |                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| W6         | 2-3                                                                                   |                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| <b>W</b> 7 | 1-2                                                                                   |                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| W8         | No Jumper                                                                             | W8                                                                                                                                                                                                                                                                                | No Jumper                                                                                                                         |

| W9         | No Jumper                                                                             | W9                                                                                                                                                                                                                                                                                | No Jumper                                                                                                                         |

| W10        | No Jumper                                                                             | W10                                                                                                                                                                                                                                                                               | No Jumper                                                                                                                         |

| W11        | Jumper                                                                                | W11                                                                                                                                                                                                                                                                               | No Jumper                                                                                                                         |

| W12        | No Jumper                                                                             | W12                                                                                                                                                                                                                                                                               | No Jumper                                                                                                                         |

| W13        | Uncut                                                                                 |                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| W14        | No Jumper                                                                             | W14                                                                                                                                                                                                                                                                               | No Jumper                                                                                                                         |

| W15        | No Jumper                                                                             | W15                                                                                                                                                                                                                                                                               | No Jumper                                                                                                                         |

|            | W1<br>W2<br>W3<br>W4<br>W5<br>W6<br>W7<br>W8<br>W9<br>W10<br>W11<br>W12<br>W13<br>W14 | <ul> <li>W2 2-3</li> <li>W3 Jumper</li> <li>W4 No Jumper</li> <li>W5 No Jumper</li> <li>W5 2-3</li> <li>W7 1-2</li> <li>W8 No Jumper</li> <li>W9 No Jumper</li> <li>W10 No Jumper</li> <li>W11 Jumper</li> <li>W12 No Jumper</li> <li>W13 Uncut</li> <li>W14 No Jumper</li> </ul> | W12-3W1W22-3W2W3JumperW3W4No JumperW3W5No JumperVW62-3V7W71-2V8W9No JumperW9W10No JumperW10W11JumperW11W12No JumperW12W13UncutV14 |

## TABLE 6. JUMPER DEFAULT SETTINGS

#### Address Select Jumpers

Table 7, Address Select Jumpers, lists the various jumper configurations for address selections for both the hard drive and the floppy drive. Jumper connections W1-W2 select the BIOS ROM/RAM memory addresses. The default address range (C8000 - C9FFF) is factory set. Jumper connection W3 enables the ROM/RAM BIOS when it is jumpered.

Jumper connection W6 selects the floppy drive's address ranges. The default range is 3FX.

The module's primary hard disk address range is (1F0-1F7 and 3F6-3F7). To select the secondary hard disk address range (170-177 and 376-377), jumper the W12 connector.

| TABLE 7. ADDRESS SELECT JUMPERS          |           |         |        |

|------------------------------------------|-----------|---------|--------|

| BIOS ADDRESS RANGES                      | JUMPER SE | ETTINGS |        |

|                                          | W1        | W2      | W3     |

| C8000 - 09FFF                            | 2 - 3     | 2 - 3   | Jumper |

| CA000 - CBFFF                            | 2 - 3     | 1 - 2   | Jumper |

| CC000 - CDFFF                            | 1 - 2     | 2 - 3   | Jumper |

| CE000 - CFFFF                            | 1 - 2     | 1 - 2   | Jumper |

| FLOPPY ADDRESS RANGES                    | W6        |         |        |

| 37X                                      | 1 - 2     |         |        |

| 3FX                                      | 2 - 3     |         |        |

| PRIMARY/SECONDARY HARD<br>DISK ADDRESSES | W12       |         |        |

| 1FX                                      | No Jumper |         |        |

| 17X                                      | Jumper    |         |        |

## Diagnostic Register Latch Control

When installed, jumper connection W10 enables the diagnostic Digital Input Register for operation in the latched mode; i.e., the register outputs latch when the register is accessed. The jumper is normally not used.

#### WD1018 Mode Control

Jumper connections W8, W14, W15 provide three external mode selects to the control processor.

#### W8 Jumper Connection

*W8 (No Jumper)* - This is the normal WD1007A-WAH/WA2 mode. The firmware forces a 10 Mhz ESDI drive to 35 sectors per track when using the Set Unformatted Bytes per Sector command. It is not necessary to set the drive's jumpers and switches for the desired number of sectors per track. This mode supports a 1:1 interleave.

*W8 (Jumper)* - This mode allows the 1007A-WAH to be used as a replacement board for existing WD1005-WAH boards without reformatting the drive. The controller reads the Unformatted Bytes per Sector from the drive. Consult the WD1007A-WAH/WA2 User's Guide for more information.

## W14 Jumper Connection

Because some of the older operating systems can only recognize 17 sectors per track or a maximum of 1048 cylinders per drive, the WD1007A-WA2 provides a translation scheme so that ESDI hard disk drives can be fully utilized in the PC/AT environment.

*W14 (No Jumper)* - The translation mode provides two types of physical to logical translation. See Translation, page 30 for explanation.

*W14 (Jumper)* - Physical to logical translation by the firmware is disabled.

#### W15 Jumper Connection

The purpose of this jumper is to support either four or seven bytes of syndrome during Read or Write Long commands. Four bytes of ECC is the default mode. Installing the jumper provides seven bytes of ECC.

W15 (No Jumper) - 4 Bytes ECC

W15 (Jumper) - 7 Bytes ECC

#### Floppy Drive and Data Rate Selection Control

#### W5 Jumper Connection

Jumper connection W5 selects either a single speed or a dual speed drive. A jumper is not normally installed, causing selection to default to a single speed drive and 125 nanoseconds precompensation.

*W5 (No Jumper)* - Single Speed *W5 (Jumper)* - Dual Speed

#### W7 Jumper Connection

The WD1007A-WA2 supports 5.25 and 3.5 inch floppy disk drives. Install jumper at W7 (1 - 2).

#### W4 and W13 Jumper Connections

Jumper connectors W4 and W13 enable the floppy drive controller.

|         | <u>W4</u> | W13 IN ETCH |

|---------|-----------|-------------|

| ENABLE  | No Jumper | Uncut       |

| DISABLE | Jumper    | Cut         |

#### W11 Jumper Connection

Jumper W11 is the disk change input signal, and must be jumpered if floppy drives are installed.

# **Mounting Bracket Jumper**

Jumper connection W9 allows grounding of the module mounting bracket to chassis or logic ground. The jumper is not normally used.

W9

| Chassis ground connected    | 2-3 |

|-----------------------------|-----|

| Digital ground disconnected | 1-2 |

# **INTERFACE DESCRIPTION - SOFTWARE**

#### **Register Address Map**

\$

.

Table 8 summarizes the WFDC I/O Register Address Map and includes the WD50C12 task file area, the WD37C65A registers and the module auxiliary support registers. It lists the primary address first with the secondary address shown within parentheses.

## TABLE 8. REGISTER ADDRESS MAP

| ADDRESS (HEX) | REGISTER | FUNCTION                               |

|---------------|----------|----------------------------------------|

| 1F0 (170) RW  | HDDTR    | Hard Disk Data Register (16 bits)      |

| 1F1 (171) WO  | HDPLO    | Gap, ID PLO and Data PLO Lengths       |

| 1F1 (171) RO  | HDERR    | Error Register                         |

| 1F2 (172) RW  | HDSCT    | Sector Count                           |

| 1F3 (173) RW  | HDSSN    | Starting Sector Number                 |

| 1F4 (174) RW  | HDCLL    | Cylinder Number - Low Byte             |

| 1F5 (175) RW  | HDCLH    | Cylinder Number - High Byte            |

| 1F6 (176) RW  | HDSDH    | Sector Size, Drive/Head Select         |

| 1F7 (177) WO  | HDCMD    | Command Register                       |

| 1F7 (177) RO  | HDSTT    | Status Register                        |

| 3F2 (372) WO  | FDDOR    | Floppy Digital Operations Register     |

| 3F4 (374) RO  | FDMSR    | Floppy Main Status Register (WD37C65A) |

| 3F5 (375) RW  | FDDTR    | Floppy Data Registers (WD37C65A)       |

| 3F6 (376) WO  | HDFDR    | Fixed Disk (Control) Register          |

| 3F6 (376) RO  | HDASR    | Alternate Status Register              |

| 3F7 (377) WO  | FDFCR    | Floppy Control Register                |

| 3F7 (377) RO  | HDDIR    | Digital Input Register                 |

|               |          |                                        |

## **Task File Registers**

Table 9 summarizes the fixed disk Task File Registers (addresses 1F1/171 through 1F7/177) and their bit assignments with respect to the system processor's lower-byte bus terms (SD07-00).

Host access to these registers is always via the register image contained within the AMAC. The WD1018 control processor has access to both the AMAC and WD50C12 register set.

|                   |           |             |          | Bit Posit | ions     |        |         |        |

|-------------------|-----------|-------------|----------|-----------|----------|--------|---------|--------|

| REGISTER          | 7         | 6           | 5        | 4         | 3        | 2      | 1       | 0      |

| HDPLO             |           | GAP         | ID PLO A | ND DATA   | PLO LENO | ATHS   |         |        |

| HDERR             | BBD       | ECC         | 0        | INF       | 0        | ACD    | TK0     | DNF    |

| HDSCT             |           |             | NUMB     | ER OF SE  | CTORS    |        |         |        |

| HDSSN             |           |             | STARTIN  | G SECTOR  |          | ł      |         |        |

| HDCLL             |           |             | CYLINE   | DER NUME  | BER LSB  |        |         |        |

| HDCLH             | 0         | 0           | 0        | 0         | 0        | CYLIND | ER NUMB | ER MSB |

| HDSDH             | 1         | SECTOR      |          | DN        | HS3      | HS2    | HS1     | HS0    |

| HDCMD             |           | (           | COMMAN   | D         |          |        |         |        |

| HDSTT             | BSY       | RDY         | WFT      | SKC       | DRQ      | CRD    | CIP     | ERR    |

| Note : Bit 7 is t | he most s | significant | bit.     |           |          |        |         |        |

# TABLE 9. TASK FILE REGISTERS

#### WFDC Control and Status Registers

Hard Disk Alternate Status Register (HDASR) 3F6/376 (RO)

This register lies within the AMAC array and provides fixed disk status to the system processor. The register contains a 'real time' section (bits 7, 6, 3 and 1) and a 'register' section set by the control processor at sector transfer time (bits 5, 4, 2 and 0).

|       |     |     | Bit Po | sitions |     |     |     |

|-------|-----|-----|--------|---------|-----|-----|-----|

| 7     | 6   | 5   | 4      | 3       | 2   | 1   | 0   |

| BSY   | RDY | WFT | SKC    | DRQ     | CRD | IDX | ERR |

| where | •   |     |        |         |     |     |     |

BSY = Controller Busy Flag

RDY = Ready from selected drive

WFT = Write Fault Flag from WD1018

SKC = Seek Complete Flag from WD1018

DRQ = Data Transfer Request Flag

CRD = Corrected Data Flag from WD1018

IDX = Index Pulse from selected drive

ERR = Error Flag from WD1018

The Alternate Status Register reflects the same status as the WD50C12 Status Register, except for bit position 1 which holds the drive index signal instead of the Command in Progress (ČIP) flag. The index bit does not latch and thus follows the drive control signal (approximately a 200 microsecond pulse every 16.7 milliseconds).

The Write Fault bit sets for all the ESDI error conditions. The host processor detects a drive's error by issuing the Initiate ESDI command to read the drive's status.

The host processor can interrogate the register at any time without interfering with other control functions. The host status input at this address will not clear the fixed disk interrupt.

# Hard Disk Diagnostic Input Register (HDDIR) 3F7/377 (RO)

The fixed disk Diagnostic Input Register reflects the current state of the floppy diskette change flag and the fixed disk Drive Select, Head Select and Drive Write gate signals (complimented form). When the floppy disk option is not installed, bit 7 remains tri-state.

|     |      |      | Bit Po | sitions |      |      |      |

|-----|------|------|--------|---------|------|------|------|

| 7   | 6    | 5    | 4      | 3       | 2    | 1    | 0    |

| DCG | WTG- | HS3- | HS2-   | HS1-    | HS0- | DS2- | DS1- |

where:

DCG = Diskette Change flag

WTG- = Write Gate on

HS3-/0- = Drive Head Select (binary)

DS2-/1- = Drive Select

The WD1018 generates the head select signals which are not transparent as in previous Western Digital Winchester disk controllers. Before the HDASR can be read correctly, the WD1018 requires a "wake-up" in order to update the head select signals.

# Hard Disk Auxiliary Control Register (HDFDR) 3F6/376 (WO)

AMAC's Hard Disk Auxiliary Control Register provides programmable controller reset. It also provides enable/disable control of the fixed disk priority interrupt.

|   |   |   | DILFO | SILIONS | 5   |     |   |

|---|---|---|-------|---------|-----|-----|---|

| 7 | 6 | 5 | 4     | 3       | 2   | 1   | 0 |

| 0 | 0 | 0 | 0     | 0       | RST | IDS | 0 |

where:

RST = Program controlled (master) reset

IDS = Data Transfer Interrupt Disable

NOTE: The software controlled reset bit (RST) will reset the fixed disk logic for as long as the bit is 'on'. RST must be turned on (for a minimum of 10.0 microseconds), then off, to complete the reset function.

The Interrupt Disable control bit does not clear the interrupt level of the disabled state. A pending interrupt will occur when it is re-enabled. A system Master Reset will disable the interrupt.

#### **Fixed Disk Data Registers**

The controller reserves the system's I/O address 1F0/170(H) for programmed transfers of input/output data for the fixed disk. All data transactions on the system bus between the controller and the system processor use a 16-bit word. The controller and AMAC array provide read and write data 'pipeline' registers in order for the sector data memory to function as a dual-port memory. These registers (along with the host's upper byte equivalent) allow the WFDC module to perform concurrent host and WDC memory accesses necessary for multi-sector 1:1 interleaving. The AMAC arbitrates simultaneous host and WDC requests and gates the appropriate address counter to external memory.

## WD37C65A Floppy Disk Controller Status/Data Registers

The charts below summarize FDC's status and data read/write registers and bit assignments with respect to the system's lower-byte data bus. The main status register (FDMSR) contains the controller's primary status and may be accessed at any time. It indicates drive busy status and facilitates host/controller data transfers. The data register (FDDTR) is actually a register stack that is written during the WD37C65A command phase and read during the result phase.

|     |     | FD  | ISR R  | egister | Bits |     |     |

|-----|-----|-----|--------|---------|------|-----|-----|

| 7   | 6   | 5   | 4      | 3       | 2    | 1   | 0   |

| RQM | DIO | EXM | СВ     | 0       | 0    | D1B | D0B |

|     |     |     |        |         |      |     |     |

|     |     | FDI | DTR Re | egister | Bits |     |     |

| 7   | 6   | 5   | 4      | 3       | 2    | 1   | 0   |

|     |     |     | READ/  | WRITE   | DATA | Ą   |     |

where:

RQM = Transfer Request To/From Host

DIO = Transfer Direction, '1' is from WD37C65A to Host

EXM = Not DMA Transfer Mode during command execution phase

CB = Read or Write Command in Progress (Busy)

D1B = Drive B in Seek Mode (Busy)

D0B = Drive A in Seek Mode (Busy)

#### **Data Read/Write Register Stack**

Tables 10 and 11 illustrate the write stack registers and the read stack registers, respectively. The stack is accessed at the FDDTR register address 3F5 (375).

|          |        |           |          | Bit Posi                                                | tions     |                        |        |         |

|----------|--------|-----------|----------|---------------------------------------------------------|-----------|------------------------|--------|---------|

| MNEMONIC | 7      | 6         | 5        | 4                                                       | 3         | 2                      | 1      | 0       |

| CMD      | MT     | MF        | SK       | an de la face de la contra de la contra de la contra de | (         | CMD COD                | E      |         |

| SEL      | 0      | 0         | 0        | 0                                                       | 0         | HS                     | 0      | US0     |

| С        | 0      |           | CYL      | INDER NU                                                | IMBER     |                        |        |         |

| Н        | 0      | 0         | 0        | 0                                                       | 0         | 0                      | 0      | НА      |

| R        | 0      | 0         | 0        | 0                                                       | SEC       | TOR NUM                | BER    |         |

| N        | 0      | 0         | 0        | 0                                                       | 0         | 0                      | 1      | 0       |

| EOT      | 0      | 0         | 0        | 0                                                       | TRACK     | FINAL SE               | CTOR # |         |

| GPL      |        | FORM      | AT GAP L | ENGTH                                                   |           | - to - to - to - o - A |        | ******* |

| DTL      | 1      | 1         | 1        | 1                                                       | 1         | 1                      | 1      | 1       |

| SC       | 0      | 0         | 0        | 0                                                       | SECTOR    | RS PER CI              | LINDER |         |

| D        |        |           | (FORMAT  | ) DATA FI                                               | LLER BYTE | <u>-</u>               |        |         |

| STP      | 0      | 0         | 0        | 0                                                       | 0         | 0                      | STP    | STP     |

| SHT      | STEP I | RATE TIME | E (SRT)  | HEAD L                                                  | JNLOAD TI | ME (HUT)               |        | A       |

| HLD      | HEAD   | LOAD TIM  | E (HLT)  | <u>41)</u>                                              |           |                        |        | ND      |

| NCN      | 0      |           | NEW C    | YLINDER                                                 | NUMBER    |                        |        |         |

## TABLE 10. WD37C65A WRITE STACK REGISTER

MT = Multi-track Mode

- MF = MFM Data Mode

- SK = Skip Deleted Address Mark

- US0 = Unit (Drive) Select B

- HS = Head Select 1

- HA = Head Address 1

- STP = 1 = Scan Compare Contiguous Sectors;

- 2 = Scan Compare Alternate Sectors

- ND = Non-DMA Transfer Mode

Note: The MT, MF and SK command bits set to zero for those commands which do not define them. The FDC digital operations register (FDDOR) selects the drive. The unit select bit (US0) is shown for reference only. The HD bit selects the head. The head address bit (HA) identifies the sector.

# TABLE 11. WD37C65A READ STACK REGISTER

|          |       |         |          | Bit Posit | ions |         |     |       |

|----------|-------|---------|----------|-----------|------|---------|-----|-------|

| MNEMONIC | 7     | 6       | 5        | 4         | 3    | 2       | 1   | 0     |

| ST0      |       | IC      | SE       | EC        | NR   | HS      | 0   | US0   |

| ST1      | EN    | 0       | DE       | OR        | 0    | ND      | NW  | MA    |

| ST2      | 0     | СМ      | DD       | WC        | SH   | SN      | BC  | MD    |

| ST3      | FT(0) | WP      | RY(1)    | ТО        | WP   | HS      | US1 | US0   |

| С        | 0     | CYLI    | NDER NUM | IBER      |      |         |     |       |

| Н        | 0     | 0       | 0        | 0         | 0    | 0       | 0   | HA    |

| R        | 0     | 0       | 0        | 0         | SEC  | TOR NUM | BER |       |

| N        | 0     | 0       | 0        | 0         | 0    | 0       |     | BYTES |

| PCN      | 0     | PRESENT | CYLINDEF |           | 3    |         |     |       |

#### Where:

IC = Interrupt Code = 0 = Normal Command Termination

- = 1 = Abnormal (Error) Command Termination

- = 2 = Invalid Command

- = 3 = Abnormal (Drive Ready Change) Termination

- SE = Seek End

- EC = Equipment Check

- NR = Drive Not Ready

- HS = Current Head Address

- US0 = Unit Select B

- EN = End of Cylinder

- DE = Data Error

- OR = Overrun Error

- ND = No Data Transferred

- NW = No Write

MA = Missing Address Mark CM = Control Mark Found DD = Data Field Error WC = Wrong Cylinder SH = Scan Equal Hit SN = Scan Not Hit BC = Bad Cylinder MD = Missing Data Mark FT = Drive Fault WP = Drive Fault WP = Drive Ready T0 = Track 0 Flag TS = Drive Two Sided HD = Drive Head Address US1/0 = Drive Select Code = 0 Drive A, = 1 =

Drive B

Status Register 3 (ST3) contains the status of the selected drive while status registers 0, 1 and 2 contain information on the controller status and command execution. Registers C, H, R and N contain sector identification information following command execution. Register PCN indicates the current cylinder number (head position) following the Sense Interrupt Status command.

# **Floppy Auxiliary Control Registers**

Operations Register (FDDOR) 3F2/372 (WO)

The Operations Register selects the floppy drive, provides drive motor control, enables or disables the floppy interrupt and DMA functions, and provides a WD37C65A software reset command.

|     |     |     | Bit Po: | sitions |     |     |     |

|-----|-----|-----|---------|---------|-----|-----|-----|

| 7   | 6   | 5   | 4       | 3       | 2   | 1   |     |

| RSV | RSV | MBE | MAE     | IDE     | RST | RSV | DSB |

RSV = Reserved

MBE = Drive B Motor Enable

MAE = Drive A Motor Enable

IDE = Interrupt and DMA Enable

RST = Floppy Section Reset

DSB = Drive B Select

To enable the floppy section operation, RST and IDE must be set.

#### Floppy Control Register (FDFCR) 3F7/377 (WO)

The Floppy Control Register selects one of four standard read/write data rates as shown below. The 250 Kbps rate is the default state following any reset.

|   |   |   | Bit Po | sitions |   |   |   |

|---|---|---|--------|---------|---|---|---|

| 7 | 6 | 5 | 4      | 3       | 2 | 1 | 0 |

| 0 | 0 | 0 | 0      | 0       | 0 | 0 | 0 |

FR1/FR0 = 00 = 500 Kbps (MFM)

= 01 = 300 Kbps (MFM)

= 10 = 250 Kbps (MFM)

= 11 = 125 Kbps (FM)

# SPECIFICATIONS

#### Power Requirements +5 VDC

#### **Environmental Requirements**

Temperature Operating Non-operating Humidity Operating Non-operating Shock and Vibration Shock Vibration

# Altitude Operating Non-operating

| Data Transfer Format |

|----------------------|

| Data Rate            |

| Sector format        |

| Drives supported     |

| Heads supported      |

| Cylinders supported  |

## **Error Correction Specifications:**

Method Degree Forward polynomial

Reciprocal polynomial

Record length (r) Correction span (b) Single burst detection span With b = 11Double burst detection span With b = 11Non-detection probability Miscorrection probability +/- 5.0% 1.200 amperes

10<sup>°</sup> to 50<sup>°</sup> Celsius -40<sup>°</sup> to 60<sup>°</sup> Celsius

8% to 85% non-condensing 5% to 95% non-condensing

35G/20MS square wave maximum 1G/0-600 Hz, dwell not to exceed 30 seconds at any resonance

0 to 3000 meters maximum 0 to 5000 meters maximum

#### **Fixed Disk Specifications**

| NRZ                                                      |

|----------------------------------------------------------|

| 10 MBits per second                                      |

| 512 bytes/sector, 35 sectors/track, hard-sectored format |

| 2 maximum                                                |

| 16 maximum                                               |

| 2048 maximum                                             |

| Polynomial division                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $X_{08}^{56} + X_{22}^{50} + X_{08}^{50} + X_{04}^{43} + X_{04}^{41} + X_{04}^{34} + X_{04}^{30} + X_{04}^{26} + X_{04}^{24} + X_{04}^{26} + $ |

| $X_{04}^{56} + X_{48}^{48} + X_{32}^{32} + X_{30}^{30} + X_{26}^{26} + X_{22}^{22} + X_{15}^{15} + X_{13}^{13} + X_{14}^{06} + $ |

| 519 X 8 bits maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| r = 519 X 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 32 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| r = 519 X 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |