# Appendix A.

# Daybreak Display Controller Chip

¥

# Daybreak Display Controller Chip

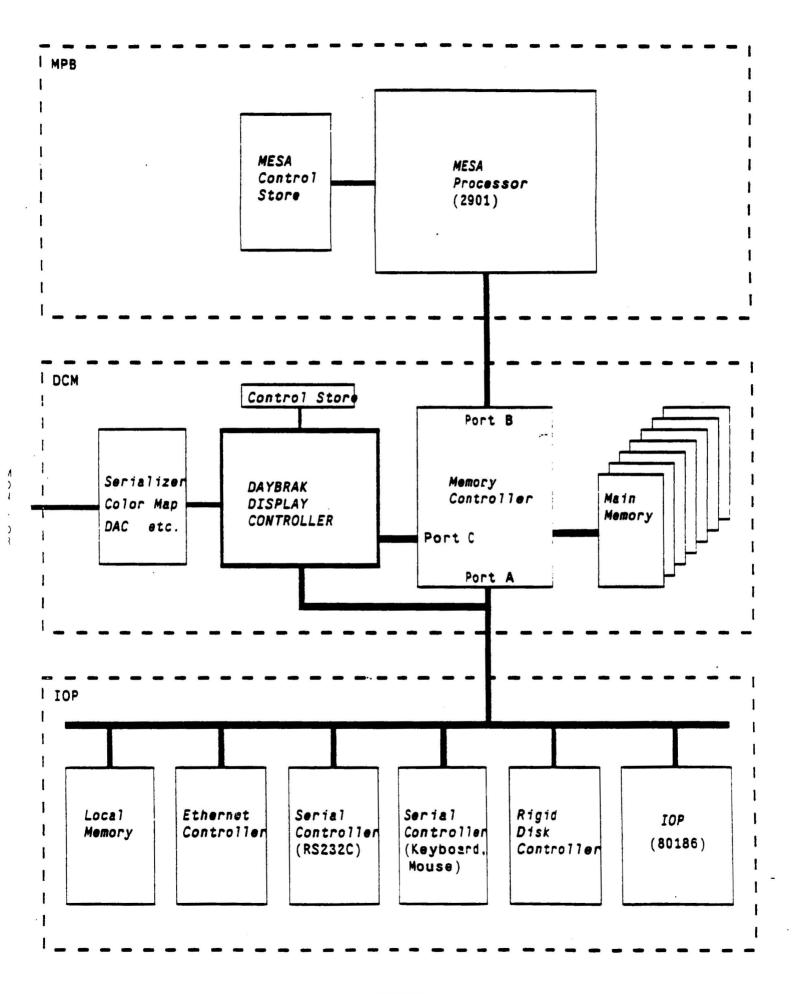

The Daybreak Display Controller (DDC) is a CMOS LSI chip designed for use in the Daybreak system. Appendix A reprints information about the chip, including:

- Software differences between DCM gate array display controller and DCM/DDC standard cell display controller

- Chip functional and timing specification

DCM board schematics with DDC are contained in Appendix B (printed separately).

# **Software Differences**

This section is reprinted verbatim from a memo titled "DCM/DDC soft. differences," dated 6-Dec-85.

Software differences between DCM (gate array display cntrl) and DCM/DDC (standard cell display contrl):

REV C: added lines 10 and 11

- Contents of horizontal and vertical control stores (proms) are different. This means DCM and DCM/DDC control stores are not interchangeable. A new Xerox part# number is being specified for DCM/DDC CS proms.

- 2. Contents of DCM/DDC horizontal and vertical control stores can be read by diagnostic routines. Contents of DCM control stores cannot be read.

- 3. Contents of DCM/DDC cursor buffer can be read by diagnostic routines. Contents of DCM cursor buffer cannot be read.

- 3. Gate array displays border registers in the following sequence: low, high, low, etc., whereas standard cell displays them high, low, high, etc.

Fix, switch programmed values of border registers.

| 4. | Cursor line number low:  | DCM;<br>DCM/DDC; | 6 bits wide (LSB)<br>8 bits wide (LSB) |

|----|--------------------------|------------------|----------------------------------------|

| 5. | Cursor line number high: | DCM;<br>DCM/DDC: | 4 bits wide (MSB)<br>2 bits wide (MSB) |

6. Cursor offset register of DCM/DDC contains a control bit (bit 7) called NCURSOR. A "0" in this bit enables the cursor while a "1" will disable cursor from display; default value is zero. DCM does not implement this function.

-

4

A - 1

- 7. A "0" written to bit 1 (video enable bit) of DCM/DDC display control register (EC80) does not disable cursor on the screen. In order to completely blank out display monitor, two steps are required: disable video enable bit and NCURSOR bit. DCM video enable bit completely enable/disables data to screen.

- 8. DCM: video disabled, no vertical interrupts DCM/DDC: video disabled, vertical interrupts still enabled. Solution: Display handler disregards vertical interrupts whenever video disabled.

- Display size/controller type status port ECCC bit 1 DCM: always "1" DCM/DDC: always "0"

- 10. Standard cell DCC does not support cursor and data mixing function "F." I believe this mixing function is never used, but if it is, there are other ways to implement it (e.g., use function "C.")

- 11. Standard cell DCC does not support reading of status information.

#### Miscellaneous

1. All address decoding of registers, control stores, and cursor buffers are same between DCM and DCM/DDC.

4

# Appendix A.

# **DDC Chip Functional & Timing Specification**

.

#### DDC CHIP

#### L INTRODUCTION

The Daybreak Display Controller (DDC) is a CMOS LSI chip designed for use in the Daybreak System. It is based on the Xerox CMOS-III Technology, and is intended to be used in both the 15 inch and the 19 inch black and white display system, running at a maximum clock frequency of 16 MHZ (64 MHZ pixel rate). It has a total of 88 input and output pins (including power and ground pin), and is currently housed in a 119 pin ceramic pin-grid package. It implements both the cursor and the border functions. A total of 16 cursor mixing functions are provided. It can handle a maximum of 2048 pixels (including horizontal sync) in the X dimension and a maximum of 1024 lines (including the vertical sync) in the Y dimension for the display. It can work in either interlaced mode or noninterlaced mode.

The DDC has 2 clock inputs, MC and RAWCLK, and they are asynchronous to each other. MC is 4 times slower than the dot-rate of the monitor and can go as high as 16 MHZ. Rawclk is designed for 16 MHZ. The chip is not guaranteed to work with MC greater than 14.2 MHZ and Rawclk slower than 16 MHZ - 5% in the worst case of memory performance.

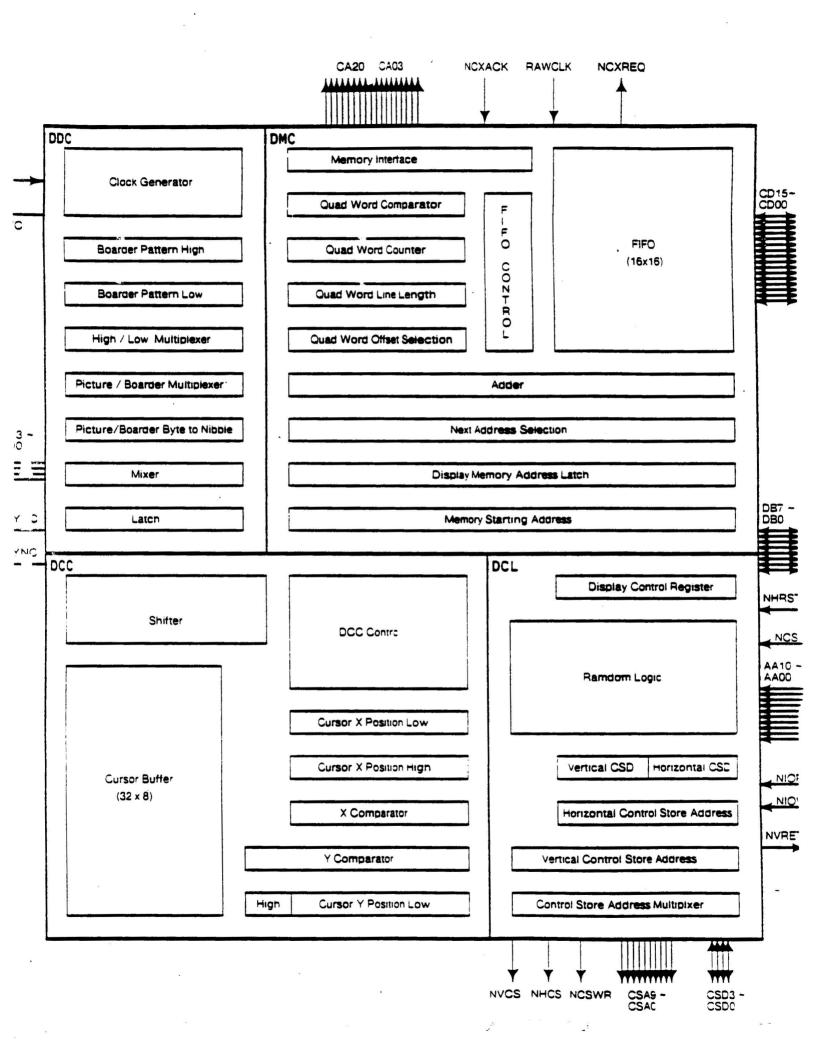

# IL. THE INTERFACE PORTS

The DDC chip is designed to be used in an environment as depicted in Fig. 1.0. It consists of 4 separate I/O ports: 1) The System Interface Port, 2) The Control Store Port, 3) The Memory Controller Interface Port, 4) The Display Monitor Port. Figure 1.1 shows the corresponding interface ports of the chip.

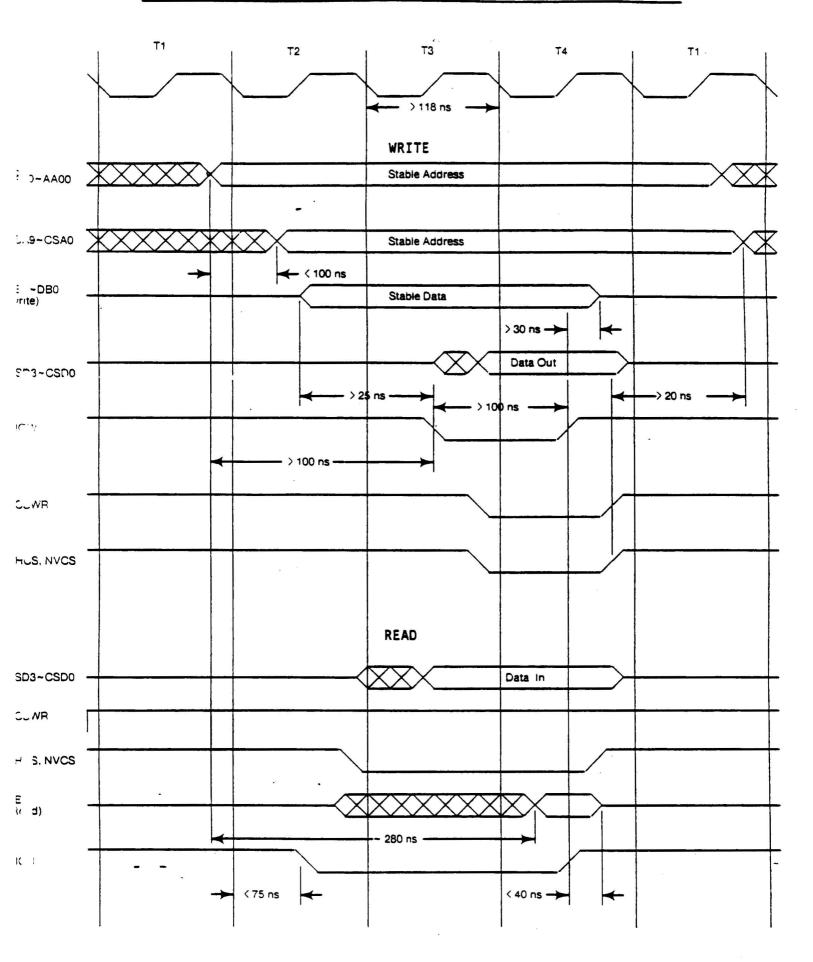

### 2.1 THE SYSTEM INTERFACE PORT

This is a bi-directional asynchronous port to mainly interface with the 8086 system bus. Through the 8086 system bus, all necessary chip configurations can be programmed, such as: the bitmap start address, number of quadwords per Scan line, border information, cursor patterns and location, interlaced or noninterlaced, scan line length, bit map starting location, border pattern etc. The control store for DDC is also downloaded via this port.

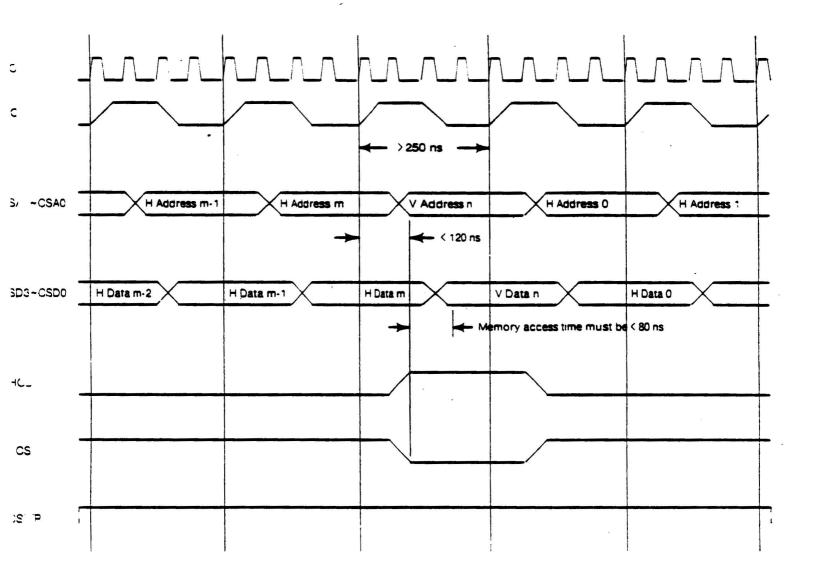

Fig. 2.0 shows the 8086 system bus read/write timing into the chip, while Fig. 2.1 shows the direct read/write timing thru the chip to the control store memory.

#### 2.2 THE CONTROL STORE PORT

This port interfaces with the local control store memory. Decoded addresses and data thru the 8086 system bus are transfered via this port and are written into the control store memory asynochronously with respect to the MC clock. Ten unidirectional address lines CSA $\emptyset$  to 9, four bidirectional data bus CSD $\emptyset$  to 3 together with the 3 control lines, namely NVCS (vertical control store memory select), NHCS (horizontal control store memory select) and the NCSWR (control store write enable) constitute this port. The Direct read/write timing from the system bus via this port is as shown in Figure 2.1. During the normal operation, the control store program is read into the chip via this port to be executed.

The timing for reading the control store during normal operations is shown in Fig. 2.2. The read of the control store is synchronous with the internal word clock (WC) of the DDC chip. WC is generated by MC divided by 4.

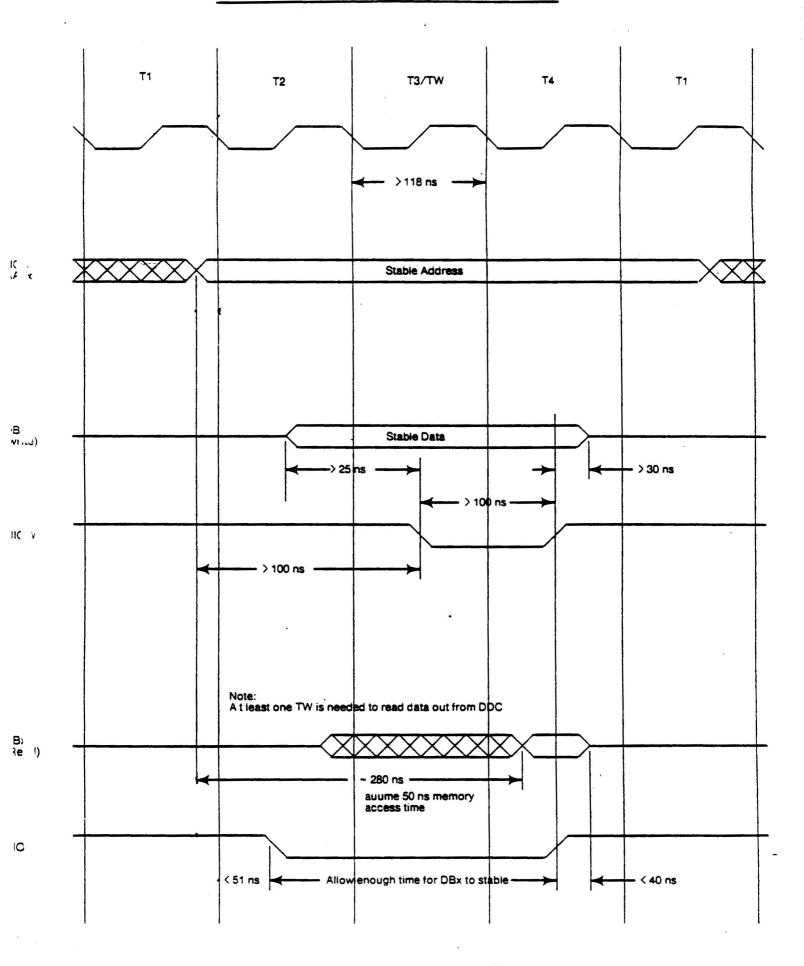

### 2.3 THE MEMORY INTERFACE PORT

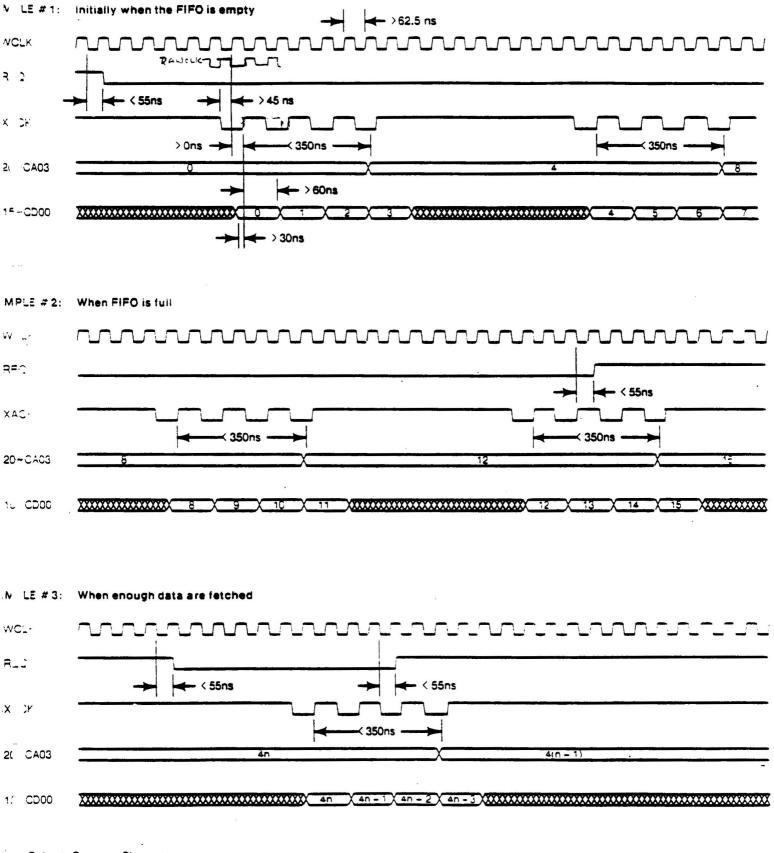

This port interfaces solely with the memory controller to obtain the bit map data to be displayed. The DDC chip requests the bit-map data by lowering it's request signal (NCREQ) and at the same time sends out the corresponding address to the memory controller.

The memory controller, in response, sends back 4 consecutive acknowledge signals (NCXACK) along with 4 data words each 16 bits wide. The DDC uses the rising edge of NCXACK to strobe in the data. All signals in this port are synchronized to RAWCLK.

The timing for this port is shown in Figure 2.3.

#### 2.4 THE DISPLAY MONITOR PORT

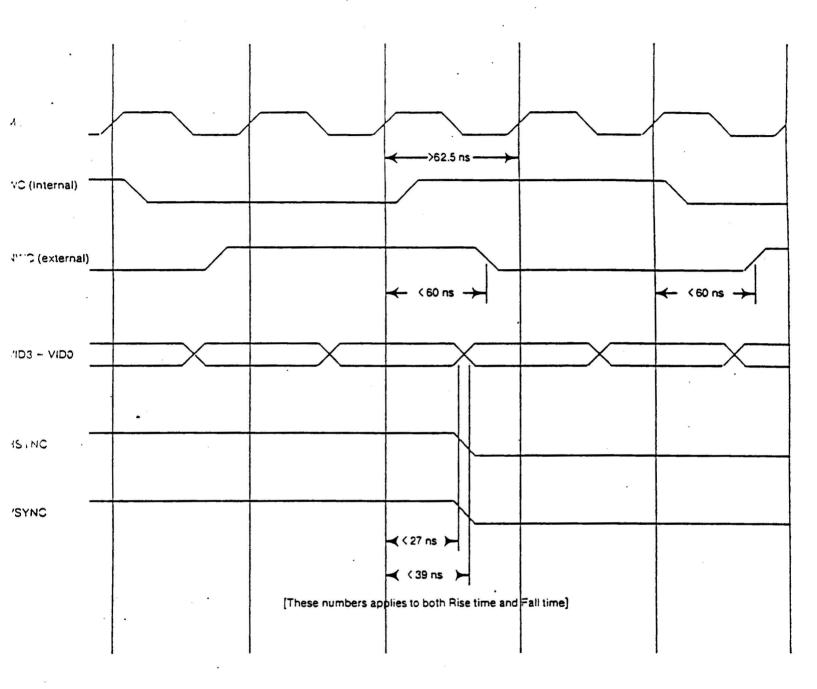

This port is a unidirectional interface between the DDC and the Display Monitor. Four video data output bits along with the vertical sync and the horizontal sync pulse are sent out at the rising edge of the MC clock to the Display Monitor. The maximum Output rate of the video data is at 16 MHZ per nibble, which translates to 64 MHZ pixel clock rate. Figure 2.4 shows the DDC video output timing. The video data is serialized externally to the chip, with the video data bit VID3 as the first and the VIDØ as the last video data to be sent to the monitor for display.

#### III. FUNCTIONAL PIN DEFINITIONS

Fig. 3.0 shows the pin assignment and both top and bottom view of the Daybreak Display controller (DDC) chip. The DDC chip is currently housed in a 119 pin ceramic pin-grid package. There are a total of 88 pins used, out of which thirty-six are input pins (including power and ground pins), forty are output pins and the rest are Bidirectional I/O pins.

#### 3.1 CLOCK/RESET PINS

#### 3.1.1 MC (CLOCK INPUT)

The MC clock pin receives an external input clock of 25% duty cycle (25% high, 75% low)  $T^2L$  signal and converts it into CMOS Level within the chip to be used by the internal logic. It also generates two divide down internal clock signals, namely BC (divided by 2) and WC (divided by 4) used by the internal chip logic.

# 3.1.2 NWC (CLOCK OUTPUT)

Inverted version of the internal clock signal WC (MC divided by four). Its main function is for testing the chip.

## 3.1.3 RAWCLK (CLOCK INPUT)

This clock signal is only used by the FIFO section in the DDC chip. The request signal NCXREQ and the address generated to the memory controller are in sync to this clock signal.

#### 3.1.4.NHRST (INPUT - LOW TRUE RESET SIGNAL)

This signal will reset the "video" bit in the Display Control Register inside the DDC chip to zero, which blanks out all the video data output to the display monitor. It will at the same time disable the NCREQ signal from requesting any bit-map data from the memory controller. However, the DDC chip will still be fetching the control store data at a random fashion before the control store is properly initialized. The NHRST signal has no effect in resetting any internal data latches to a known state, nor will it tri-state any I/O signals of the DDC chip.

.

#### 3.2 SYSTEM INTERFACE PORT PINS

## 3.2.1 NCS (INPUT - ACTIVE LOW CHIP SELECT)

A low on this pin enables I/O read/write communication between the DDC chip and the external system processor.

# 3.2.2 AAØØ THROUGH AA10 (INPUT ADDRESS PINS 0 TO 10)

These eleven pins point to either internal DDC registers or to external control store RAM.

## 3.2.3 NIOW (INPUT - ACTIVE LOW WRITE STROKE)

The system processor envokes the write strobe in conjunction with the chip select and address to deliver data to the internal location or to the external control store memory specified by the address.

#### 3.2.4 NIOR (INPUT - ACTIVE LOW READ STROKE)

The system processor envokes the read strobe in conjunction with the chip select and address to access the internal cursor RAM contents or the control store memory contents. (other Internal Registers are not readable)

# 3.2.5 NVRET (OUTPUT - ACTIVE LOW VERTICAL RETRACE LINE)

This signal is the inverted version of the EOF (End of Field). Low for one scan line period.

## 3.2.6 DBØ THROUGH DB7 (BI-DIRECTIONAL - DATA PIN ØTO 7)

The data pins are used to provide the data for I/O transfers to and from the DDC chip. It is also used in conjuction with the Control Store Port of the DDC chip via its CSDØ:3 data bus for I/O transfer to and from the external control store memory.

### 3.3. THE CONTROL STORE PORT PINS

### 3.3.1 NVCS (OUTPUT - ACTIVE LOW VERTICAL CONTROL STORE MEMORY SELECT)

A Low on this pin enables I/O read/write communication between the DDC chip and the vertical control store memory.

# 3.3.2 NHCS (OUTPUT - ACTIVE LOW HORIZONTAL CONTROL STORE MEMORY SELECT)

A Low on this pin enables I/O read/write communication between the DDC chip and the horizontal control store memory.

#### 3.3.3 CSAØ THRU CSA9 (OUTPUT ADDRESS PIN Ø TO 9)

These ten pins address the Control Store memory.

#### 3.3.4 NCSWR (OUTPUT - LOW WRITE AND HIGH READ)

A Low on the signal will enable the write operation to the control store memory, while a high will read out the content of the control store memory. The signal stays high during normal operation.

#### 3.3.5 CSDØ THRU CSD3 (BI-DIRECTION - DATA PIN Ø TO 3)

The data pins are the datapath for transfers between the DDC chip and the control store memory.

#### 3.4 THE MEMORY INTERFACE PORT PINS

#### 3.4.1 NCXREQ (OUTPUT - LOW TRUE REQUEST PIN)

A low on this signal indicates the DDC chip is requesting bit-map data from the external memory controller.

# 3.4.2 NCXACK (INPUT - LOW TRUE ACKNOWLEDGE PIN)

A high to low transition on this pin indicates that the bitmap data request by the DDC chip is accepted, and the bitmap data is valid on the data bus. The DDC chip uses the rising edge of this signal to latch in the data on the data bus.

#### 3.4.3 CA#3 THRU CA20 (OUTPUT - ADDRESS PIN 3 TO 20)

These eighteen address pins, generated by the DDC chip point to the current location of bitmap data. (The first address of a 4 word group)

#### 3.4.4. CD40 THRU CD15 (INPUT - DATA PIN ¢ TO 15)

These sixteen data pins are used to provide the bit-map data from the memory controller to the DDC chip.

.

### 3.5 THE DISPLAY MONITOR PORT PINS

# 3.5.1 VSYNC (OUTPUT SIGNAL)

This is the vertical sync pulse sent from the DDC chip to the display monitor. It is synchronized with the MC clock signal and is sent out at the rising edge of the MC clock.

# 3.5.2 HSYNC (OUTPUT SIGNAL)

This is the horizontal sync pulse sent from the DDC chip to the display monitor. It is synchronized and sent out at the rising edge of the MC clock.

### 3.5.3 VID THRU VID3 (OUTPUT - DATA PIN 0 TO 3)

These four output data pins carry the video display data from the DDC chip to the display monitor. It is synchronized and sent out at the rising edge of the MC clock.

#### 3.6 VDD AND GND (INPUT PINS)

There is only one VDD and one ground pin for the DDC chip. VDD supplies 5 volts to the chip.

### IV. SOFTWARE PROCEDURES AND PROGRAMMING

## 4.0 DESCRIPTION OF THE DDC CONTROL WORD ADDRESS AND FORMAT

Fig. 4.0 shows the DDC's relative control word address and format. It also includes a table showing the mixing function between the cursor and the bit-map data.

### 4.0.1 VERTICAL CONTROL STORE

The Vertical Control Store defines the characteristic of the scan lines to be displayed. Each control word in the vertical control store defines a whole scan line. It has a maximum capacity of up to 1024 vertical control word. The address for the vertical control store is E800 to EBFF. The 5 MSB's of the 20 bit address line coming from the system bus are decoded externally as NCS comes into the DDC chip. The remaining 11 address lines come directly to the DDC chip. (It is assumed that throughout the remaining of the writing). As illustrated in Fig 4.0, only the lower nibble of the data byte constitute the control word. The definition of the Vertical Control word is as follows:

t

# BITØ - VSYNC: a l in this bit will generate a line length of vertical sync.

- BIT1 VBLANK: a 1 in this bit will blank the whole line

- BIT2 VPIC: a l in this bit defines a picture line while a  $\emptyset$  defines the whole line as border.

- BIT3 EOF: a l in this bit generates the END OF FIELD signal, and causes a retace to the beginning of the next scanning field.

EOF indicates it is the last control word of a field (either even or odd)

#### 4.0.2 HORIZONTAL CONTROL STORE

The horizontal control store defines a region in a scan line. Each horizontal control word in the horizontal control store defines a 16 bit region in a scan line. Current DDC chip design has a maximum capacity of up to 128 horizontal control words, and controls up to 128 words or 2048 pixels in a scan line. The address for the horizontal control store is ECØØ to EC7F. In a similar manner to the vertical control store, only the lower nibble of the data byte constitutes the control word.

The definition of the horizontal control word is as follows:

| BITO - HSYNC:  | a 1 in this bit will generate a 16 -<br>pixel wide (4 MC clock period)<br>horizontal sync within a scan line. |

|----------------|---------------------------------------------------------------------------------------------------------------|

| BIT1 - HBLANK: | a l in this bit will blank out a 16 -<br>pixel wide region within a scan<br>line.                             |

| BIT2 - HPIC:   | a l in this bit will define a picture<br>word within a scan line, while a<br>Ødefine a border word.           |

| BIT3 - VCLK:   | a 1 in this bit will generate a vertical clock pulse (4 MC Period)                                            |

|                | There should be a total of exactly<br>3 VCLK's programmed in the<br>horizontal control store. Labeled         |

VCLK #2, VCLK #3 and VCLK

1

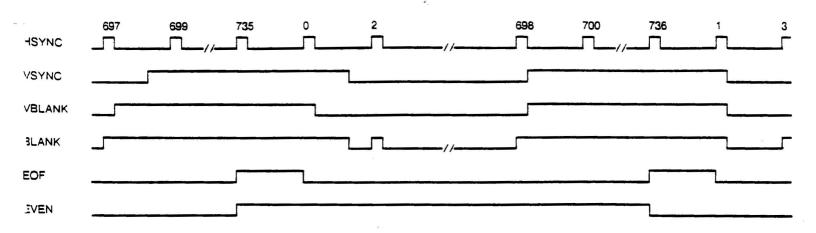

#1. See Fig. 4.1 and Fig. 4.2 for the programming example of horizontal control store.

VCLK #2 and VCLK #3 define the transition edge of the VSYNC signal, while VCLK #1 defines the last control word of the horizontal control store. VCLK #1 also signals a vertical control store fetch in the next cycle. The VCLK's should never be programmed in consecutive words. (In the gate array version VCLK#1 is the second last control word instead of the last control word)

# 4.0.3 DISPLAY CONTROL REGISTER

The address for the Display Control register inside the DDC is EC80. It is a 8-bit Register. The representation of its corresponding functions are as follows:

| BITØ - NINTL: | A 1 in this bit sets the display is<br>in non-interlace mode, and a Øsets<br>it in interlace mode.                                                                                                                                                                                                                                                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT1 - VIDEO: | A 1 in this bit enables the display,<br>while a $\emptyset$ will blank out the<br>display. During the reset time<br>(i.e. NHRST = LOW), this bit is<br>reset to zero, and the display<br>monitor is blanked out. It is<br>important to set this bit back to 1<br>to enable the video display before<br>proceeding on with the normal<br>operation. |

| BIT2 -        | UNUSED                                                                                                                                                                                                                                                                                                                                             |

| BIT3 - DPIC:  | A 1 in this bit is the normal mode while a $\emptyset$ forces the display to be an all border pattern.                                                                                                                                                                                                                                             |

BIT4-7 - BFØ:BF3 These 4 bits define the mixing function between the cursor and the bit map data. See Fig. 4.Ø for the corresponding mixing function.

#### 4.0.4 BORDER PATTERN LOW REGISTER

This 8 bit register defines the low border pattern. The address for writing into this register inside the DDC chip is EC81. The display for the whole screen is arranged in such a way that 2 lines of border pattern high alternates with 2 lines of border pattern low, with the border pattern high at the top of the screen.

## 4.0.5 BORDER PATTERN HIGH REGISTER

This 8 bit register defines the high border pattern. The address for this internal register is EC82.

#### 4.0.6 CURSOR X HIGH REGISTER

This 8 bit register holds the cursor's location in the Xdimension. The address of this internal register is EC83.

#### 4.0.7 CURSOR X LOW REGISTER

The lower nibble (bit 3 to bit  $\emptyset$ ) of this register holds the cursor's bit-OFFSET Position from the location specifed by the cursor X High Register. For example, if bit3: $\emptyset$  = 1111, it specifies that the cursor's location will be shifted right 15 bit in the X-dimension from the location specify by the address in the cursor X High Register.

Bit 7 of this Register also contains a control BIT called NCURSOR. A  $\emptyset$  in this bit enables the cursor while a 1 will disable the cursor from display. The address for this internal register is EC84.

#### 4.0.8 CURSOR Y LOW REGISTER

This register holds the Lower 8 bits of the cursor's location in the Y-dimension. The address for this internal register is EC85.

#### 4.0.9 CURSOR Y HIGH REGISTER

This register holds the 2 high bits of the cursor's location in the Y-dimension. Together with the lower 8 bits in the cursor Y Low Register, it forms the entire 10 bit address of the cursor's location in the Y-dimension. The address for this internal register is EC86.

1.

1

#### 4.0.10 QUADWORDS PER LINE REGISTER

Bit 5 to bit  $\emptyset$  of this Register holds the number of quadwords per scan line. This is used for different size display screens. The address for this internal register is EC88.

#### 4.0.11 BIT MAP START ADDRESS LOW REGISTER

This internal register holds the low byte of the Bit Map data's starting address. The address for this internal register is EC89.

#### 4.0.12 BIT MAP START ADDRESS HIGH REGISTER

This internal register holds the high byte of the bit map data's starting address. The address for this internal register is EC8A.

#### 4.0.13 CURSOR BUFFER

This cursor buffer is 32 bytes deep in the DDC chip. The writing in of the cursor pattern is specified in the Intel byte format. See Fig. 4.3 for the format. The address for the cursor buffer is from ED00 to ED1F.

#### 4.0.14 SOFTWARE RESET

The software reset will reset the chip and align the display to the beginning of the first scan line. The address for the software reset is ED6Ø to ED7F.

#### 4.1 DATA FORMAT FOR MEMORY DATA AND CURSOR DATA

Fig 4.3 shows both the memory bit-map data and the cursor data format. They are both specified in the Intel format.

#### 4.2 PROGRAMMING THE CONTROL STORE

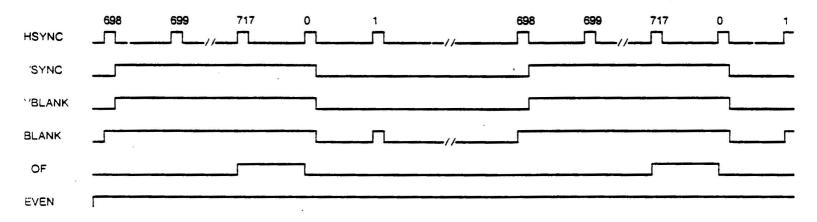

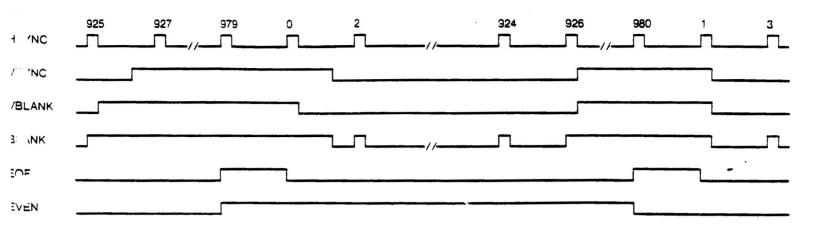

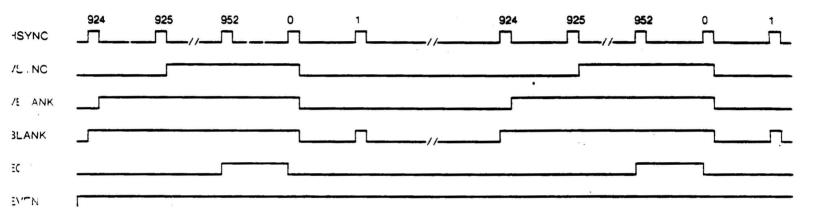

Fig. 4.1 and Fig 4.2 show two programming examples of the Control Store. One is for the 15 inch black and white display and the other is for the 19 inch B/W display. Notice in the horizontal control store, as mentioned before, there are exactly three VCLKs programmed, and that the VCLK 41 defines the last control word of the horizontal control store. For the vertical control store, EOF defines the last control word in both the interlace and the non-interlace cases. Each count in the horizontal control store represents a duration of 4 MC clock period. The HSYNC, for instance, in the horizontal control which represents a 40 MC clock period.

All pins are  $T^{2}L$  compatible with the exception of MC input.

VIL = 0.8v VIH = 2VVOL = 0.4v VOH = 2.4V

MC Input:

VIL = 0.8V VIH = 4.0V

All output and I/O pins with the exception of HSYNC, VSYNC and VIDØ:3 can sink 3MA @ 0.4V and source 0.2MA @ 2.4V. The output signals HSYNC, VSYNC and VIDØ:3 can sink 2MA @ 0.4V and source 200uA @ 2.4V.

All input capacitance CI = 18pf.

All output and I/O pins with the exception of HSYNC, VSYNC and VID $\emptyset$ :3 output pins can drive 40pf of external output capacitance.

HSYNC, VSYNC and VIDØ:3 output pins can drive 12pf of external output capacitance.

FIGURE 1.0

# SYSTEM INTERFACE PORT TIMING REQUIREMENT

# DIRECT READ/WRITE OF CONTROL STORE THROUGH SYSTEM INTERFACE PORT

FIGURE 2.1

.

# DDC MEMORY INTERFACE TIMING

Refresh Cycle are Shown here

\*

Aaximum rise time or Fall time is 12 ns Rise time is mesured from 0.8V to 2.0V fall time is mesured from 2.0V to 0.8V

# DISPLAY CONTROLLER PIN ASSIGNMENT

-----

2.44

| PIN #             | SIGNAL NAME                                                              | TYPE        | PIN #                                 | SIGNAL NAME       | TYPE                                              | PIN #          | SIGNAL NAME             | TYPE                     | PIN #                          |                           | TYPE     |

|-------------------|--------------------------------------------------------------------------|-------------|---------------------------------------|-------------------|---------------------------------------------------|----------------|-------------------------|--------------------------|--------------------------------|---------------------------|----------|

|                   |                                                                          |             | 31                                    |                   |                                                   | 61             |                         |                          | 91                             |                           |          |

| 2                 |                                                                          |             | 32<br>33                              |                   | ·                                                 | 62<br>63       |                         |                          | 92<br>93                       |                           |          |

|                   |                                                                          |             | 34                                    |                   |                                                   | 64             |                         |                          | 94                             |                           |          |

| 5                 | NCXACK                                                                   |             | 35                                    | NWC               | 0                                                 | 65             | CSD2                    | 1/0                      | 95                             | DB2                       | 1/0      |

| <u>ج</u>          | RAWCLK                                                                   |             | 36<br>37                              | MC<br>HSYNC       | 0                                                 | 66<br>67       | CSD1<br>CSD0            | 1/0                      | 96<br>97                       | DB3<br>DB4                | 1/0      |

| 8                 | CA03                                                                     | 00          | 38                                    | VSYNC             | 0                                                 | 68             | NVRET                   | 0                        | 98                             | 085                       | 1/0      |

| ٩                 | CA04                                                                     | 0           | 39                                    | VIDO              | 0                                                 | 69             | NIOR                    | I                        | 99                             | DB6                       | 1/0      |

| 0                 | CA05                                                                     | 0           | 40                                    | VID1              | 0                                                 | 70             | NIOW                    | ł                        | 100                            | D87                       | 1/0      |

|                   | CA06<br>CA07                                                             | 0           | 41                                    | VID2              | 0                                                 | 71             | AAOO                    |                          | 101                            | CD 15                     |          |

| 12<br>3           | CA07<br>CA08                                                             | 0 0         | 42<br>43                              | VID3<br>NCSWR     | 0 0                                               | 72<br>73       | AA01<br>AA02            | 1                        | 102<br>103                     | CD14<br>CD13              |          |

| 14                | CAO9                                                                     | 0           | 44                                    | NVCS              | 0                                                 | 74             | AAO3                    | T                        | 104                            | CD12                      |          |

| 15                | VDD                                                                      | 1           | 45                                    | NHCS              | 0                                                 | 75             | AAQ4                    | L                        | 105                            | CD11                      |          |

| 6<br>.7           | CA10                                                                     | 0           | 46<br>47                              | CSA9              | 0                                                 | 76             | GND                     |                          | 106                            | CD10                      |          |

| 18                | CA11<br>CA12                                                             | 0 0         | 4/<br>48                              | CSA8<br>CSA7      | 0 0                                               | 77<br>78       | AA05<br>AA06            |                          | 107<br>108                     | CD09<br>CD08              |          |

| Э                 | CA13                                                                     | 0           | 49                                    | CSA6              | 0                                                 | 79             | AA07                    | 1                        | 109                            | CD07                      |          |

| C                 | CA14                                                                     | 0           | 50                                    | CSA5              | 0                                                 | 80             | AAOS                    | I                        | 110                            | CD06                      | 11       |

| 21<br>2           | CA15<br>CA16                                                             | 0 0         | 51<br>52                              | CSA4<br>CSA3      | 0 0                                               | 81<br>82       | AA09<br>AA10            |                          | 111                            | CD05<br>CD64              |          |

| 3                 | CA18<br>CA17                                                             | 0           | 52                                    | CSA2              | 0                                                 | 83             | NCS                     |                          | 112                            | CD03                      |          |

| 24                | CA18                                                                     | 0           | 54                                    | CSA1              | 0                                                 | 84             | NHRST                   | i                        | 114                            | CD02                      |          |

| - 3               | CA19                                                                     | 0           | 55                                    | CSAO              | 0                                                 | 85             | DB0 ·                   | 1/0                      | 115                            | CD01                      | 1 1      |

| э<br>27           | CA20                                                                     | 0           | 56<br>57                              | CSD3              | 1/0                                               | 86<br>87       | DB1                     | 1/0                      | 116                            | CD00                      |          |

| 27                |                                                                          |             | 58                                    |                   |                                                   | 88             |                         |                          | 118                            |                           |          |

| 3                 |                                                                          |             | 59                                    |                   |                                                   | 89             |                         |                          | 119                            |                           |          |

| 30                |                                                                          |             | 60                                    |                   |                                                   | 90             |                         |                          | key                            |                           |          |

| (3)               | 4) (35) (38) (40)                                                        | (43) (4     | 4) (47) (                             | 50) (52) (55) (58 | 61                                                | 61)            | 58) (55) (52) (50       | (47)                     | 4 (43)                         | (40) (38) (35) (          | 34 3.    |

| 28) (2            | <pre>XXXX</pre>                                                          |             | 6 48 (                                | 51) (54) (56) (55 |                                                   | 64             | <b>59</b> (56) (54) (51 |                          | 46) (42)                       | <b>39 35 32</b>           | 29 22    |

|                   | <pre>XXXXX</pre>                                                         | $\simeq$    | $\langle \boldsymbol{\times} \rangle$ |                   | $\sim$                                            | $\Xi$          |                         | $(\simeq)$               | $\simeq$                       | žžžž                      | $\simeq$ |

|                   | $\langle \mathbf{x} \mathbf{x} \mathbf{y} \mathbf{y} \mathbf{y} \rangle$ | ) (41) (4   | 5) (49) (                             | 53)(57)(60)(66    | $\langle \boldsymbol{\boldsymbol{\Xi}}  $         | Ĭ              |                         | 3) (49) (                | 45) (41)                       |                           | 25) (25) |

| 27) (2<br>(2.) (2 | 4) (27)                                                                  |             |                                       | (63) (66          | 5) (68)                                           | (68) (         | <b>66</b> ) (63)        |                          |                                | (27) (                    | 24 (22)  |

| (2.) (2           | 1)(23)                                                                   |             |                                       | (67) (69          |                                                   | 70)            | <b>69</b> (67)          |                          |                                | (23)                      | 27) 22)  |

| $\widetilde{1}$   | < ×                                                                      |             |                                       | (71)              |                                                   | $\sim$         | 72 71                   |                          |                                | (19)                      | 18       |

|                   | $\leq \geq$                                                              |             |                                       |                   |                                                   | Ĭ              | ž ž                     |                          |                                | $\simeq$                  | $\simeq$ |

| 14                | 6) (15)                                                                  | BOTTO       | M VIEW                                | (75) (76          | 5) (74)                                           | 74             | 76 (75)                 | TOP                      | VIEW                           | (15) (                    | 16 (14)  |

| $\overline{1}$    | 2)(11)                                                                   |             |                                       | (79) (78          |                                                   | $\overline{7}$ | 78 (79)                 |                          |                                | (11)                      | 2 (13)   |

| 10)(9             | $\tilde{\mathbf{D}}$                                                     |             |                                       | (83) (8           |                                                   | (80)           | 81)(83)                 |                          |                                | $\widetilde{\mathcal{T}}$ | 9 (10)   |

| $\sim$            | $\leq \geq$                                                              |             |                                       | × ×               | $\langle \boldsymbol{\boldsymbol{\succ}} \rangle$ | X              | ž ž                     |                          |                                | $\simeq$                  | $\simeq$ |

| 8 (6              | )(3)                                                                     |             |                                       | (87) (84          | •) (82)                                           | (82) (         | 84 (87)                 |                          | Variation of the second second | (3)                       | 6)(8)    |

| 5)(2              | ) key (17) (13                                                           | ) (00) (0   | 5 (01)                                | 97 93 90 8        | 5) (85)                                           | 85) (          | 86 99 93 9              | 7 (01)                   | 105 (09)                       | (13) (17) key (           | 2)5      |

| - (11             | 9) (16) (14) (11                                                         | ) (08) (0   | x) (02) (                             | 99) (96) (92) (85 |                                                   | Ă              | 89 (92) (96) (96        | 9 (02)                   | 06 (08)                        |                           | 119 4    |

| トン                | < × × × ×                                                                | $\simeq$    | $\leq \geq 1$                         | ××××              | $\langle \boldsymbol{\boldsymbol{\Xi}}  $         | Ĭ              |                         | $\langle \simeq \rangle$ | $\cong$                        | ××××                      | $\simeq$ |

| <u>い</u> (1)      | 8 (15) (12) (10                                                          | ) (107) (10 | ×) (03) (                             | 00 (98) (95) (9   | 4) (91)                                           | (91) (         | 94 (95) (98) (10        | 0 (03) (                 | 104 (107                       | (10) (12) (15) (          | 118 (1)  |

|                   |                                                                          |             |                                       |                   |                                                   |                |                         |                          |                                |                           |          |

J

-

.

1.000

# DDC CONTROL WORDS ADDRESS AND FORMAT

|                        |     |             | bit 7   |      |      |           |            |         |             | bit 0 |

|------------------------|-----|-------------|---------|------|------|-----------|------------|---------|-------------|-------|

| tical Control Store    | R/W | E800 ~ EBFF |         |      |      |           | EOF        | VPIC    | VBLANK      | VSYNC |

| rizontal Control Store | R/W | EC00 ~ EC7F |         |      |      |           | VCLK       | HPIC    | HBLANK      | HSYNC |

| Luy Control Register   | w   | EC80        | BF3     | BF2  | BF1  | BFO       | DPIC       |         | VIDEO       | NINTL |

| τ r Pattern Low        | w   | EC81        |         |      |      | Border Pa | ittern Low |         |             |       |

| τ r Pattern High       | w   | EC82        |         |      |      | Border Pa | ttern High |         |             |       |

| ఞా X High              | w   | EC83        |         |      |      | Curso     | r X High   |         |             |       |

| sor X Low              | w   | EC84        | NCURSOR |      |      |           |            | Cu      | insor X Low |       |

| rsor Y Low             | w   | EC85        |         | · ·  |      | Curso     | r Y Low    |         |             |       |

| 's⊎≓Y High             | w   | EC86        |         |      | .u   | -         |            | -       | Cursor      | YLOW  |

| ar rords Per Line      | w   | EC88        |         |      |      | · · · ·   | Quadwords  | PerLine |             | :     |

|                        |     |             |         |      |      |           |            |         |             |       |

| n. ) Start Address Lov | v W | EC89        | CA12    | CA11 | CA10 | CAO9      | CAOS       | CA07    | CA06        | CA05  |

| n – Start Addreas Hig  | h W | EC8A        | CA20    | CA19 | CA18 | CA17      | CA16       | CA15    | CA14        | CA13  |

| sor Buffer             | R/W | ED00 - ED1F |         |      |      | Curs      | or Byte    |         |             |       |

#### ware Reset

ED60 - ED7F

3 ~ 3F0 Mixing Function

= End Of Field

./ K Blank Word

C

1 = Picture Word

0 = Border Word

/h :

Horizontal Sync

JRSOR

1 = Disable Cursor

0 = Enable Cursor

T

1 = Non-Interlace

0 = Interlace

.A..K

Blank Line

.K Vertical Clock

El Enable Bitmap display

C 1 = Picture Line 0 = Border Line

'N Vertical Sync

| N      | lixing Fu                                                         | unction                                                                                                                                                                                                                              |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESULT | BG                                                                | F                                                                                                                                                                                                                                    | RESULT                                                                                                                                                                                | BG                                                                                                                                                                                                                                                                                                                                                                           | F                                                                                                                                                                                                                                                                                                                                                                                            | BF3 - BFO                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0      | 1                                                                 | 8                                                                                                                                                                                                                                    | v · c                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                            | BG                                                                                                                                                                                                                                                                                                                                                                                           | Cursor Background                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| v·c    | 0                                                                 | 9                                                                                                                                                                                                                                    | v⊞c                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                            | v                                                                                                                                                                                                                                                                                                                                                                                            | Bitmap                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| v·c    | 1                                                                 | A                                                                                                                                                                                                                                    | с                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                            | С                                                                                                                                                                                                                                                                                                                                                                                            | Cursor                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| r      | 0                                                                 | в                                                                                                                                                                                                                                    | v + c                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                                                                                                                                                                                                                                            | AND                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| v • c  | 0                                                                 | c                                                                                                                                                                                                                                    | v                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                            | +                                                                                                                                                                                                                                                                                                                                                                                            | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C'     | 1                                                                 | D                                                                                                                                                                                                                                    | v + c                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                            | ŧ                                                                                                                                                                                                                                                                                                                                                                                            | Exclusive OR                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| v ⊞c   | 0                                                                 | E                                                                                                                                                                                                                                    | v + c                                                                                                                                                                                 | o                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| v + c  | 1                                                                 | F                                                                                                                                                                                                                                    | 1                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | RESULT<br>0<br>✓ • C<br>✓ • C<br>✓ • C<br>✓ • C<br>✓ • C<br>✓ • C | RESULT     BG       0     1       V     •       V     •       V     •       V     •       C'     0       V     •       C'     1       V     •       C'     1       V     •       C'     0       C'     1       V     •       C     0 | RESULT     BG     F       0     1     8       V • C     0     9       V • C     1     A       V • C     0     B       V • C'     0     C       C     1     D       V • C'     0     E | RESULT       BG       F       RESULT         0       1       8 $\vee \cdot C$ $\vee \cdot C$ 0       9 $\vee  \boxdot$ $\vee \cdot C$ 1       A       C $\vee \cdot C$ 0       B $\vee + C$ $\vee \cdot C^{\prime}$ 0       C $\vee$ $\vee \cdot C^{\prime}$ 0       C $\vee$ $\vee \cdot C^{\prime}$ 0       C $\vee$ $\vee \cdot C^{\prime}$ 0       E $\vee + C^{\prime}$ | RESULT       BG       F       RESULT       BG         0       1       8 $\vee \cdot C$ 1 $\vee \cdot C$ 0       9 $\vee \cdot E$ 0 $\vee \cdot C$ 1       A       C       0 $\vee \cdot C$ 1       B $\vee \cdot C$ 0 $\vee \cdot C$ 0       B $\vee \cdot C$ 0 $\vee \cdot C'$ 0       C $\vee \cdot C$ 0 $\vee \cdot C'$ 0       C $\vee \cdot C$ 1 $\vee \cdot C'$ 0       E $\vee + C$ 1 | RESULT       BG       F       RESULT       BG       F         0       1       8 $\vee \cdot C$ 1       BG $\vee \cdot C$ 0       9 $\vee \cdot C$ 1       BG $\vee \cdot C$ 1       A       C       0       V $\vee \cdot C$ 1       A       C       0       C $\vee \cdot C$ 0       B $\vee + C$ 0       + $\vee \cdot C'$ 0       C $\vee \cdot C$ 0       + $\vee \cdot C'$ 1       D $\vee + C'$ 1       E $\vee + C$ 0       E $\vee + C$ 0       - |

# 15 INCH DISPLAY WITH INTERLACE

# 15 INCH DISPLAY WITHOUT INTERLACE

# FXAMPLE:

#### orizontal Control Store

| Address<br>(D) | Code<br>(H) | Count<br>(D) | Comment                  |

|----------------|-------------|--------------|--------------------------|

| 0~8            | 3           | 9            | HSync, HBlank            |

| )              | в           | 1            | HSync, HBlank, VClk # 2  |

| 10-11          | 0           | 2            | Border                   |

| 12~43          | 4           | 32           | Picture                  |

| 4              | С           | 1            | Picture, VClk # 3        |

| .5~63          | 4           | 19           | Picture                  |

| 64~65          | 0           | 2            | Border                   |

| 6~67           | 2           | 2            | HBlank, Border           |

| 8              | A           | 1            | HBlank, Border, VCLK # 1 |

### Vertical Control Store

| Address | Code | Count | Comment            |

|---------|------|-------|--------------------|

| (D)     | (H)  | (D)   |                    |

| 0~31    | 0    | 32    | Top Border         |

| 32~664  | 4    | 633   | Bit Map            |

| 665~696 | 0    | 32    | Bottom Border      |

| 697~734 | 3    | 38    | Vsync, VBlank      |

| 735~736 | в    | 2     | Vsync, VBlank, EOF |

| Non-Inter      | ace         |              | 00<br>. 00        |

|----------------|-------------|--------------|-------------------|

| Address<br>(D) | Code<br>(H) | Count<br>(D) | Comment           |

| 0-31           | 0           | 32           | Top Border        |

| 32-665         | 4           | 634          | Bit Map           |

| 666~697        | 0           | 32           | Bottom Border     |

| 698~716        | 3           | 19           | Vsync, VBlank     |

| 717            | в           | 1            | Vsync, VBlank, EC |

4

-

# 19 INCH DISPLAY WITH INTERLACE

# 19 INCH DISPLAY WITHOUT INTERLACE

# U (MPLE:

### ic. izontal Control Store

| A <b>tress</b><br>(ک | Code<br>(H) | Count<br>(D) | Comment                 |

|----------------------|-------------|--------------|-------------------------|

| 0 14                 | 3           | 15           | HSync, HBlank           |

| 1                    | в           | 1            | HSync, HBlank, VClk # 2 |

| 16~17                | 0           | 2            | Border                  |

| 19-64                | 4           | 47           | Picture                 |

| 6                    | С           | 1            | Picture, VClk #3        |

| 66~89                | 4           | 24           | Picture                 |

| 90~91                | 0           | 2            | Border                  |

| 9                    | 2           | 1            | HBlank, Border          |

| ن9                   | A           | 1            | HBlank, Border, VCLK#1  |

## Vertical Control Store

| interlace        |             |              |                    |

|------------------|-------------|--------------|--------------------|

| Address<br>· (D) | Code<br>(H) | Count<br>(D) | Comment            |

| 0~31             | 0           | 32           | Top.Border         |

| 32~892           | 4           | 861          | Bit Map            |

| 893~924          | 0           | 32           | Bottom Border      |

| 925~978          | 3           | 54           | Vsync, VBlank      |

| 979-980          | в           | 2            | Vsvnc, VBlank, EOF |

| Non-Interlace  |             |              |                    |  |  |  |  |

|----------------|-------------|--------------|--------------------|--|--|--|--|

| Address<br>(D) | Code<br>(H) | Count<br>(D) | Comment            |  |  |  |  |

| 0-31           | 0           | 32           | Top Border         |  |  |  |  |

| 32~891         | 4           | 860          | Bit Map            |  |  |  |  |

| 892~923        | 0           | 32           | Bottom Border      |  |  |  |  |

| 924            | 2           | 1            | VBlank. Border     |  |  |  |  |

| 925~951        | 3           | 27           | Vsync, VBiank      |  |  |  |  |

| 952            | В           | 1            | Vsync, VBlank, EOF |  |  |  |  |