÷.

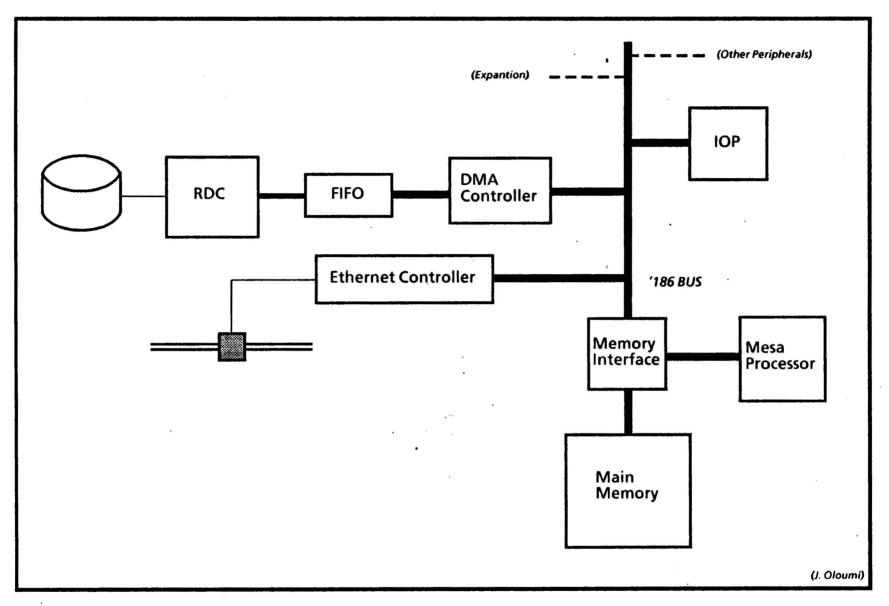

Dove Block Diagram

# **DMA Features:**

- Programmable by IOP (Starting Address, Word Count, CR Register and Start DMA)

- . Can transfer up to 256 words (of 16 bits) at a time

- Provides 24 bits of Address to the Main Memory

- Data transfer at '186 memory cycle rate

- End-of-transfer always interrupts IOP

### - What is being "DMAed"?

Pages of data (256 words/page = mesa page)

- IOCBs

#### - Limitations of DMA

Treats everything as DATA to be DMAed between FIFO and Main Memory (process data and IOCB).

#### - Programming the DMA

- -Word Count

- Statrting Address (24 bits)

- Transfer Direction

- StartDMA

- Other (2942, etc.)

- Have the Programmer's Notes handy

#### - Control and Status Registers

- Reset-on-read Status Register

- Control Register

- Interfacing '186 bus: (Playing '186 role for Main Memory, S' Lines)

- DMA Controller is a Bus Master

- DMA Controller acts as an 80186 for the Main Memory during DMA transfer,

- And acts as an IOP peripheral other times (available for programming and/or inquiries).

- Bus Arbiter under program control grants or removes Bus Masters according to a priority scheme. Arbiter signals DMA Controller to leave '186 bus by dropping DMA's Hold Acknowledge line (HLDA).

#### - DMA's response to Special situations:

- FIFO not responding (out of bound condition based on direction) : Drops HLD and waits for FIFO available before raises HLD again.

- Ethernet intervention:

Drops HLD and waits for one more T cycle before raising HLD (Bus Arbiter will delay granting the bus until the higher priority user relinquishes the bus).

PromStatesRevP.DMA 23 May 84 16:40:02 PD1

\_

.

|             | l rorloop | Waitforfff0<br>FlF0Available | Endowa | SendlutReq | De lay | DropHLD<br>TrlsfTLO | 1wAndWait<br>14Normai<br>14AndEOXfer<br>14AndEutOfBnd<br>14AndEtherH1d | 13     | IZState | <b>I</b> 1State | IsState | WaitforHLDA<br>CotHLDA | SendillD .<br>{ rror1 | InitialWait | C OFI                                     | Notes:<br>1 DRead'& DWrite' have been combined into one signal and inverted. BWrite/DRead'goes bigh beginning 17 and stays kigh<br>2 Based on the state of Elf00AtOfBound' during 13, decision is made to put the status on the bus beginning 14 for the ne<br>3 Another signal (Elf0Prefetah) added to pre fetch the Elf0 during Elf0 to MEM transfer. |

|-------------|-----------|------------------------------|--------|------------|--------|---------------------|------------------------------------------------------------------------|--------|---------|-----------------|---------|------------------------|-----------------------|-------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (<br>(<br>( | ×         | ××                           | ×      | ×          | ×      | ××                  | ****                                                                   | ×      | X       | ×               | ×       | ××                     | ××                    | ×           | Unused<br>bit                             | ite" ha<br>state i<br>at (Eff                                                                                                                                                                                                                                                                                                                           |

|             | x         | ××                           | ×      | ×          | ×      | - 0                 | • × × - ×                                                              | ×      | ×       | ×               | x       | - 0                    | ××                    | ×           | D i sk<br>HL DA                           | ve been<br>of EU00<br>OPrefet                                                                                                                                                                                                                                                                                                                           |

|             | ×         | ××                           | ×      | <b>×</b>   | ×      | ××                  | 0                                                                      | ×      | ×       | ×               | ×       | ××                     | ××                    | ×           | 5ync<br>ARDY                              | combined<br>attifBoun<br>ch) adde                                                                                                                                                                                                                                                                                                                       |

|             | ×         | - 0                          | ×      | ×          | ×      | × ×                 | * 0 × 1 ×                                                              | ×      | ×       | ×               | ×       | * *                    | ××                    | ×           | 0.8.                                      | d to pro                                                                                                                                                                                                                                                                                                                                                |

|             | ×         | ××                           | ×      | ×          | ×,     | ××                  |                                                                        | ×      | ×       | ×               | ×       | * *                    | o -                   | ×           | Lad01<br>Xfer                             | re signa<br>19 13, de<br>Fetch 1                                                                                                                                                                                                                                                                                                                        |

|             | 0 1101    | 0 1100<br>0 1100             | 0 1011 | 0 1010     | 0 1001 | 0 1000<br>0 1000    | 0 0111<br>0 0111<br>0 01111<br>0 01111<br>0 01111                      | 0 0110 | 1010 0  | 0 0100          | 0 0011  | 0 0010                 | 0 0001<br>0 0001      | 0 0000      | State<br>Number                           | L and im<br>sciston<br>he THO                                                                                                                                                                                                                                                                                                                           |

|             | -         | ••                           | -      | -          | -      |                     |                                                                        | -      | -       | -               | -       | • •                    |                       |             |                                           | verted.<br>is made<br>during                                                                                                                                                                                                                                                                                                                            |

|             | 0         |                              | -      | -          | -      |                     |                                                                        | -      | -       | -               | -       |                        | 0 -                   | -           | l rror<br>Trap'                           | BWrite <i>r</i> D<br>to put t<br>FIIO to                                                                                                                                                                                                                                                                                                                |

|             | -         | 90                           | e      | -          | o      | 00                  |                                                                        | 0      | 0       | •               | 0       | • •                    | - 0                   | 8           | let.                                      | Road go<br>he Statu<br>MUM Lian                                                                                                                                                                                                                                                                                                                         |

|             | -         |                              | -      | -          | -      |                     |                                                                        | -      | °,      | 9               | 0       |                        |                       | -           | st ines                                   | es bigh_i<br>s on the<br>sfer.                                                                                                                                                                                                                                                                                                                          |

|             | -         |                              | -      | -          | -      | <b></b>             |                                                                        | -      | 1       | : •             | -       | '                      | ~ ~                   | -           | Sate ADDr'7<br>Slines' Data               | bus beg                                                                                                                                                                                                                                                                                                                                                 |

|             | 8         | 0 0                          | 0      | -          | o      |                     |                                                                        | -      | -       | -               | •-      | - 0                    | 00                    | 0           | DMA<br>Active                             | t 12 and<br>inning to                                                                                                                                                                                                                                                                                                                                   |

|             | c         |                              | •      | 0          | . •    | 00                  | 0000-                                                                  | -      | -       | -               | 0       | c 🤉                    | 0 0                   | 0           | DWF1L9<br>DRead                           | stays b<br>I for the                                                                                                                                                                                                                                                                                                                                    |

|             | 0         | 00                           | 0      | 0          | 3      | 60                  |                                                                        | -      | -       | -               | -       |                        | 0 1                   | 0           | e ni sk                                   | igh antir the<br>e mext cycle.                                                                                                                                                                                                                                                                                                                          |

|             | o         | с с                          | 0      | 0          | 0      | 00                  | 000-0                                                                  | Ð      | 0       | -               |         |                        | <b>e</b> e            | 0           | 1110<br>1110                              | untif the end of fa<br>ext cycle.                                                                                                                                                                                                                                                                                                                       |

|             | 000       | 000                          | 000    | 000        | 000    | 000                 | 000<br>000<br>000                                                      | 000    | 000     | 000             | 000     | 900<br>000             | 000<br>000            | 000         | FIIO Unused<br>Pr <sup>ed</sup> itch Data | 1 01 13                                                                                                                                                                                                                                                                                                                                                 |

|             | 0 1101    | 0 1100<br>0 0001             | 0 0000 | 0 1011     | 0 0001 | 0 1001              | 0 0111<br>0 1010<br>0 1000<br>0 1000                                   | 0 0111 | 0 0110  | 0 0101          | 0 0100  | 0 0010                 | 0 0010<br>0 1101      | 0 1160      | Next<br>State                             |                                                                                                                                                                                                                                                                                                                                                         |

.

PromStatesRevP.DHA

23 May 84 16:40:02 PD1

•

.

.

.

۰.

٠

## A Transfer Scenario (Mem-FIFO)

IOP:

- Programs the DMA (not necessarily in this order):

CR register, Word Count (2's complement), Starting Address (24 bits)

- Sets the direction bit to 1

- Issues AllowRDC

- Issues StartDMA

### ĎMA:

- Checks if FIFO is available for transfer

- Sends Hold request (HLD) and waits for HLDA

- Once HLDA received, transfers one word per memory cycle:

Moves S' lines active (memory Read)

Puts 24 bits address on the bus (AD15-00 and AA23-16) during T1 state

Waits till data from Memory stable on the bus (delays for ARDY)

Data written into destination (FIFO) by T4 state

- Decrements the Word Count (increments the 2's complement)

- Increments the address (24 bits)

- Transfers another word (during the next T1 through T4)

- If HLDA drops, DMA drops HLD, delays for one cycle, sends Hold request again

- When FIFO unavailable, DMA drops HLD, waits for FIFO available, then sends HLD

- DMA continues to transfer until End-of-Transfer

- At End-of-Transfer, sends Interrupt to IOP and go back to ready state (InitialWait).

#### IOP:

- Once interrupted will check if it is End-of-Transfer or due to error.

- If IOP is interrupted while DMA, it should issue AllowRDC again (to Arbiter)

- IOP will have the control for the next DMA transfer.

## A Transfer Scenario (FIFO-Mem)

IOP:

- Programs the DMA (not necessarily in this order):

CR register, Word Count (2's complement), Starting Address (24 bits)

- Sets the direction bit to 0

- Issues AllowRDC

- Issues StartDMA

#### DMA:

- Checks if FIFO is available for transfer

- Sends Hold request (HLD) and waits for HLDA

- Once HLDA received, transfers one word per memory cycle:

Moves S' lines active (memory Write)

Puts 24 bits address on the bus (AD15-00 and AA23-16) during T1 state

Pre-Fetches data from FIFO (during last T4 & present T1)

Puts data on the '186 bus during T2 and T3 (Plus any Tw's caused by ARDY) Data written into destination (Main Memory) by T4 state

- Decrements the Word Count (increments the 2's complement)

- Increments the address (24 bits)

- Transfers another word (during the next T1 through T4)

- If HLDA drops, DMA then drops HLD, delays for one cycle, sends Hold request again

- When FIFO unavailable, DMA drops HLD, waits for FIFO available, then sends HLD

- DMA continues to transfer until End-of-Transfer

- At End-of-Transfer, sends Interrupt to IOP and go back to ready state (InitialWait).

#### **IOP:**

- Once interrupted will check if it is End-of-Transfer or due to error.

- If IOP is interrupted while DMA, it should issue AllowRDC again (to Arbiter)

- IOP will have the control for the next DMA transfer.

# **FIFO Features:**

- 512 words long (made of 512X9 components)

- Bidirectional access (memory-to-disk & disk-to-memory)

- Programable direction control

- Simultaneously and asynchronously accessible by DMA and RDC

- Full, Empty and Half Full indication