# Debugger Interface TABLE OF CONTENTS

| 10.1. Hardware                                           | 10-1 |

|----------------------------------------------------------|------|

| 10.1.1 Interface Connector                               | 10-3 |

| 10.1.2 Programmable Peripheral Interface                 | 10-4 |

| 10.1.3 Line Drivers                                      | 10-4 |

| 10.1.4 Line Receivers                                    | 10-5 |

| 10.2. Theory of Operations                               | 10-5 |

| 10.2.1 Sending and Receiving Data                        | 10-5 |

| 10.2.2 Handshaking                                       | 10-6 |

| 10.3. Programmer Interface                               | 10-7 |

| 10.3.1 Addressing the Debugger Interface                 | 10-7 |

| 10.3.2 Programming the PPI                               | 10-7 |

| 10.3.2.1 Operational descriptions and configurations     | 10-7 |

| 10.3.2.2 Initialization                                  | 10-7 |

| 10.3.2.3 Sending a byte                                  | 10-8 |

| 10.3.2.4 Receiving a byte                                | 10-8 |

| 10.3.2.5 Sending boot (Reset) signal to debuggee machine | 10-8 |

| 10.3.2.6 Sending an NMI signal                           | 10-9 |

| 10.3.3 Timing                                            | 10-9 |

# 10.

The debugger interface (also called Song Board) provides a parallel communication link between the Dove workstation and a debugger machine (Dandelion). This board replaces the previous debugger board.

The main component of the debugger interface is an Intel 8255A-5, programmable peripheral interface. This component handles both handshakings and interrupts and can be directly accessed by the IOP.

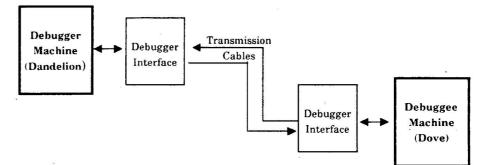

Figure 10.1 illustrates a typical debugging system. A debugger interface is attatched to the debugger machine and the debuggee machine. Transmission cables transmit data between the two boards.

#### Figure 10.1. Debugger boards in a typical debugging system

# 10.1 Hardware

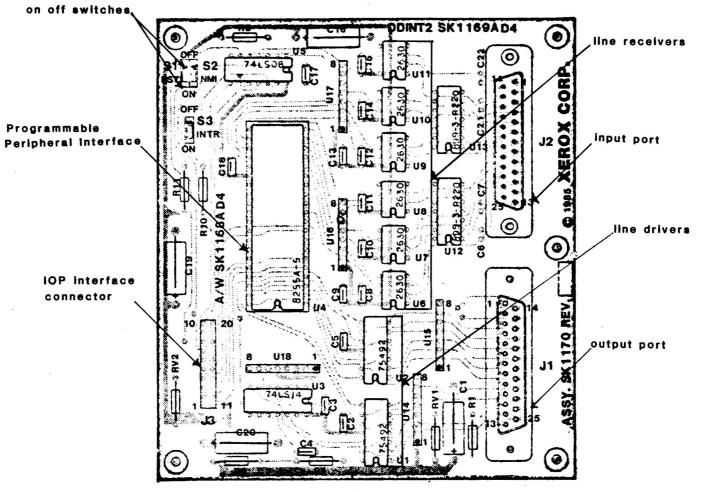

The debugger interface PWBA is housed in a  $4\frac{3}{4}$ -inch x  $5\frac{1}{2}$ -inch x 1inch metal case and contains the programmable peripheral interface, line drivers, and line receivers. The total power consumption is about 250 mA. Figure 10.2 illustrates the debugger interface PWB assembly.

Figure 10.2 Debugger interface PWB assembly

<u>10 - 2</u>

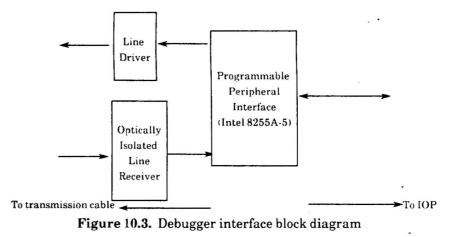

All components on the debugger interface are off-the-shelf components and are socketed for easy servicing. Figure 10.3 illustrates the hardware, broken down into three functional groups: programmable peripheral interface, line drivers, and line receivers. For full schematics, refer to Appendix D.

<sup>10.1.1</sup> Interface Connector

Table 10.1 lists and describes the signals of the of 20-pin connector chip that connects the debugger interface and the IOP.

| Signal        | Туре   | Function                                                                                                                                                       |

|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPRD'         | Input  | A low on this input pin enables the debugger interface to send the data or status information to the IOP on the data bus.                                      |

| IPWR'         | Input  | A low on this input pin enables the IOP to write data or control words to the debugger interface.                                                              |

| IPSEL'        | Input  | A low on this input pin enables the communication between the debugger interface and the IOP.                                                                  |

| IPA1 and IPA0 | Input  | These input signals address the ports (A, B, and C) or the control register.                                                                                   |

| RESET         | Input  | A high on this input pin causes the debugger interface to be reset<br>During reset, the control word is cleared and all of the ports are set to<br>input mode. |

| InINTR        | Output | An active high signal indicates a byte was received.                                                                                                           |

| IPReset'      | Output | An active low signal resets (boot) IOP. This signal should be disabled in debugger side using the switch located on the debugger box.                          |

| OutINTR       | Output | An active high signal indicates that the output port is empty and ready to accept another byte from the IOP.                                                   |

| NMI'          | Output | An active low signal sends an NMI to the IOP.                                                                                                                  |

| IPD7-0        | I/O    | Lines 7-0 are data buses on the debugger interface. These lines carry data between the debugger interface and the IOP.                                         |

| Table 10.1. 2 | 0-Pin | Connector | Descrip | otion |

|---------------|-------|-----------|---------|-------|

|---------------|-------|-----------|---------|-------|

Debugger Interface

### 10.1.2 Programmable Peripheral Interface

The programmable peripheral interface (PPI), is an Intel 8255A-5. Figure 10.4 illustrates the 40-pin interface chip and also lists the pins and signals.

|                                                                                                                                                      |                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                          | . *                                                                                                      |                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA3<br>PA2<br>PA1<br>PA0<br>RD'<br>CS'<br>GND<br>A1<br>A0<br>PC7<br>PC6<br>PC7<br>PC6<br>PC5<br>PC4<br>PC0<br>PC1<br>PC2<br>PC3<br>PB0<br>PB1<br>PB2 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>8255A-5<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | PA4         40       PA5         39       PA6         38       PA7         37       WR'         36       RESET         35       D0         34       D1         33       D2         34       D1         30       D5         29       D6         28       D7         27       VCC         26       PB7         25       PB6         24       PB5         23       PB4         22       PB3 | Pin Name<br>D7-D0<br>RESET<br>CS'<br>RD'<br>WR'<br>A0, A1<br>PA7-PA0<br>PB7-PB0<br>PC7-PC0<br>VCC<br>GND | Pin Signal<br>DATA BUS (BI-DIRECTIONAL)<br>RESET INPUT<br>CHIP SELECT<br>READ INPUT<br>WRITE INPUT<br>PORT ADDRESS<br>PORT A (BIT)<br>PORT B (BIT)<br>PORT C (BIT)<br>+ 5 VOLTS<br>0 VOLTS |

|                                                                                                                                                      |                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                          | *See Intel data<br>component                                                                             | book for a detailed description of this                                                                                                                                                    |

Figure 10.4. PPI pins and signals

10 - 4

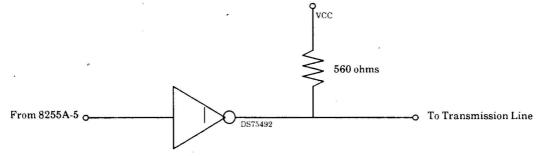

The cable between two debugger interfaces is recommended but not required to be at most 10 feet. In order to drive this cable, opencollector Hex LED drivers, DS75492, are used as transmission line drivers. The output of the drivers is individually pulled up with 560 ohm resistors. Figure 10.5 illustrates the line driver circuits.

**Debugger Interface**

# **10.1.4 Line Receivers**

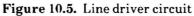

To eliminate ground loops between the debugger machine and the debuggee machine, the opto-isolator, HPCL2630, is used as the line receiver. The characteristics of this device depend on the input voltage, input current, and pull-up resistor.

The values of the resistors used with line drivers and receivers are carefully balanced for proper and reliable operations. Figure 10.6 illustrates the line receiver circuits.

# **10.2 Theory of Operations**

The debugger interface performs two major tasks: sending a byte and receiving a byte. This section describes both of these tasks and the steps that must take place before either action can occur. Refer to Intel's 1984 Micropressor Handbook Volume II for further information on modes.

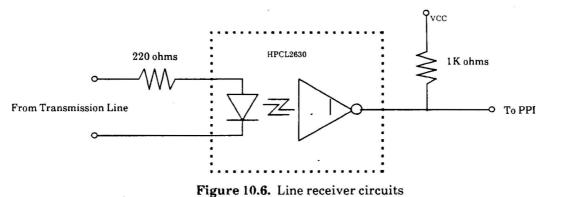

#### 10.2.1 Sending and Receiving Data

Figure 10.7 illustrates how data is sent from the debuggee to the debugger.

Debugger Interface

- 1. Machine A writes a byte of data to the output port of the PPI attached to machine A.

- 2. This byte is transmitted through the line drivers and received by the line receivers.

- 3. The data is obtained by the PPI attached to machine B by handshaking.

- 4. Machine B retrieves the byte by reading from the PPI input port.

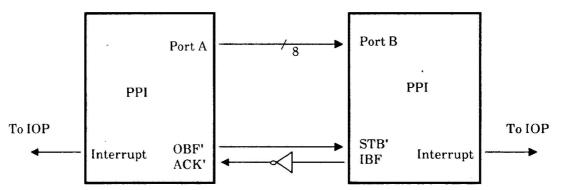

#### 10.2.2 Handshaking

Port A of the PPI is programmed as a mode 1 output port, and port B is programmed as a mode 1 input port. Both ports use handshaking for data transmissions. In mode 1, handshaking is done by PPI port C, internally. Figure 10.8 illustrates the connection between the input port of one debugger interface and the output port of the other debugger interface. The line drivers and receivers are omitted. Table 10.2 lists the steps involved in the handshaking procedure.

| Table 1 | 0.2. Har | dshakir | ng Proced | ure |

|---------|----------|---------|-----------|-----|

|---------|----------|---------|-----------|-----|

| Output Port                                                      | Input Port                          |

|------------------------------------------------------------------|-------------------------------------|

| - IOP writes a byte to Port A -<br>1. Lower OBF'                 |                                     |

| PPI turns off the Interrupt (LOW)                                |                                     |

|                                                                  | 2. Detect LOW in STB'               |

|                                                                  | 3. Port B latches the byte into the |

|                                                                  | buffer                              |

|                                                                  | 4. Raise IBF                        |

|                                                                  | Notify IOP by an interrupt (HIGH).  |

| 5. Detect Low in ACK'                                            |                                     |

| 6. Raise OBF'                                                    |                                     |

| Notify IOP by an interrupt (HIGH)                                |                                     |

| nenne sen 🗸 sona na an 🖉 sonastanensä 122 il 🖬 il foldeni 201928 | - IOP reads the byte from Port B -  |

|                                                                  | PPI turns off the Interrupt (LOW)   |

**Debugger Interface**

10 - 6

# **10.3 Programmer Interface**

Improper programming of the debugger interface may result in damage to the circuits on the board. The following sections describe information necessary to program the debugger interface.

# 10.3.1 Addressing the Debugger Interface

The debugger interface uses four address spaces. Table 10.3 lists the I/O address spaces in the IOP.

| Address       | RD' | WR' | CS' | Input Operation (Read)   |  |

|---------------|-----|-----|-----|--------------------------|--|

| 70H           | 0   | 1   | 0   | Port A X Data Bus        |  |

| 72H           | 0   | 1   | 0   | Port B X Data Bus        |  |

| 74H           | 0   | 1   | 0   | Port C X Data Bus        |  |

|               |     |     |     | Output Operation (Write) |  |

| 70H           | 1   | 0   | 0   | Data Bus X Port A        |  |

| 72H           | 1   | 0   | 0   | Data Bus X Port B        |  |

| 74H           | 1   | 0   | 0   | Data Bus X Port C        |  |

| 76H           | 1   | 0   | 0   | Da'ta Bus X Control      |  |

| 0 12 12 YOF 0 |     |     |     | Disable Function         |  |

|               | X   | X   | 1   | Data Bus X 3-State       |  |

| 76H           | 0   | 1   | 0   | Illegal Condition        |  |

|               | 1   | 1   | 0   | Data Bus X 3-State       |  |

Table 10.3. Basic Operations of the Debugger Interface (PPI)

#### 10.3.2 Programming the PPI

The Programmable Peripheral Interface must be programmed in the following way for correct operations to occur.

| 10.3.2.1.<br>Operational<br>Descriptions and<br>Configurations | Table 10.4 lists the debugger interface configurations.                                                                                                                               |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.3.2.2.<br>Initialization                                    | While the PPI is being reset, the control register is cleared and all ports are set to input mode. To configure the PPI as the debugger interface, the following steps are necessary. |

|                                                                | <ol> <li>Configure the ports to the following modes:</li> </ol>                                                                                                                       |

|                                                                | Port A to mode 1 output port<br>Port B to mode 1 input port<br>Port C, bits 4 and 5, to output port<br>Data, A6H, should be written into the control register, 76H.                   |

|                                                                | 2. Set the interrupts.                                                                                                                                                                |

|                                                                | Set the input interrupt: Data, 05H, should be written into the                                                                                                                        |

control register, 76H.

**Debugger Interface**

10 - 7

| Port | Pin #                                                | I/O                                           | Use                                                                                                                               |

|------|------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| A    | PA7<br>PA6<br>PA5<br>PA4<br>PA3<br>PA2<br>PA1<br>PA0 | OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT<br>OUT | Output<br>Port                                                                                                                    |

| В    | PB7<br>PB6<br>PB5<br>PB4<br>PB3<br>PB2<br>PB1<br>PB0 | IN<br>IN<br>IN<br>IN<br>IN<br>IN<br>IN        | Input<br>Port                                                                                                                     |

| С    | PC7<br>PC6<br>PC5<br>PC4<br>PC3<br>PC2<br>PC1<br>PC0 | OUT<br>IN<br>OUT<br>OUT<br>IN<br>OUT<br>OUT   | OBF <sub>A</sub> '<br>ACK <sub>A</sub><br>I/O<br>INTR <sub>A</sub><br>STB <sub>B</sub> '<br>IBF <sub>B</sub><br>INTR <sub>B</sub> |

Set the output interrupt: Data, 0DH, should be written into the control register, 74H.

Table 10.4. Configuration of the Intel 8255A-5 in the debugger interface

#### Signal Key

| OBFA'        | = Output buffer full'                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------|

| ACKA'        | = Acknowledge input                                                                                                      |

| I/O<br>INTRA | <ul> <li>Input/Output</li> <li>Interrupt acknowledge. This signal is<br/>reset by the falling edge of Write'.</li> </ul> |

| STBB'        | = Strobe input                                                                                                           |

| IBFB'        | = Input buffer full                                                                                                      |

| INTRB        | = Interrupt Acknowledge. This signal is reset by the falling edge of Read'.                                              |

# 10.3.2.3.

Sending a Byte

First, check the status of the output port, Port A, by reading Port C. A high in bit 3 of Port C indicates that the output port is empty and ready to send the next byte. Write the byte to Port A.

#### 10.3.2.4.

**Receiving a Byte**

Check the status of the input port, Port B, by reading Port C. A high in bit 0 of Port C indicates that the input port is full and ready to be read.

# 10.3.2.5.

### Sending Boot (Reset) Signal to Debuggee

Machine

In order to boot the debuggee machine, bit 4 of port C in the debugger side must be toggled.

- 1. Set bit 4 of port C: Write data, 09H, to control register C, 76H.

- 2. Wait for about 50 ms.

- 3. Reset bit 4 of port C: Write data, 08H, to control register C, 76H.

| 10.3.2.6.<br>Sending an<br>NMI Signal | In order to send NMI, bit 5 of port C must be toggled.               |

|---------------------------------------|----------------------------------------------------------------------|

|                                       | 1. Set bit 5 of port C: Write data, 0BH, to control register, 76H.   |

|                                       | 2. Reset bit 5 of port C: Write data, 0AH, to control register, 76H. |

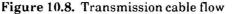

| 10.3.3 Timing                         |                                                                      |

Table 10.5 lists the timing characteristics for a read and a write. Figure 10.9 illustrates the timing for a read, write, and a read-write.

|              |        | _                                     | PPI |     |      |

|--------------|--------|---------------------------------------|-----|-----|------|

|              | Symbol | Parameter                             | Min | Max | Unit |

| Read         | ιAR    | Address is stable before a Read       | 0   |     | ns   |

|              | tRA    | Address is stable after a Read occurs | 0   |     | ns   |

|              | tRR    | Read pulse width                      | 300 |     | ns   |

| •            | tRD    | Data is valid from Read               |     | 200 | ns   |

|              | tDF    | Data floats after Read                | 10  | 100 | ns   |

|              | tAW    | Address is stable before a Write      | 0   |     |      |

|              | tWA    | Address is stable after a Write       | 20  |     |      |

| <u>Write</u> | tWW    | Write pulse width                     | 300 |     |      |

|              | tDW    | Data valid to Write                   | 100 |     |      |

|              | tWD    | Data valid after Write                | 30  |     | ns   |

| Read/Write   | tRV    | Time between Reads and/or Writes      | 850 |     | ns   |

Table 10.5. Timing Characteristics

Dove IOP Board

**Read/Write**

**Debugger Interface**

<u>10 - 10</u>