# **XVME-653/658**

Single-Slot VMEbus Intel Pentium<sup>®</sup>/AMD-K6<sup>®</sup>-2 Processor Module

P/N 74653-001B

| Revision | Description     | Date |

|----------|-----------------|------|

| Α        | Manual Released | 2/98 |

| В        | Revision        | 6/99 |

#### Trademark Information

Brand or product names are trademarks or registered trademarks of their respective owners. Pentium is a registered trademark and MMX is a trademark of Intel Corporation. Windows and Windows NT are registered trademarks of Microsoft Corp. in the US and in other countries.

### **Copyright Information**

This document is copyrighted by Xycom Automation, Incorporated (Xycom Automation) and shall not be reproduced or copied without expressed written authorization from Xycom Automation.

The information contained within this document is subject to change without notice. Xycom Automation does not guarantee the accuracy of the information.

Xycom Automation, Inc. 750 North Maple Road Saline, MI 48176–1292 734-429-4971 (phone) 734-429-1010 (fax)

#### WARNING

This is a Class A product. In a domestic environment this product may cause radio interference, in which case the user may be required to take adequate measures.

\_\_\_\_\_

European Union Directive 89/336/EEC requires that this apparatus comply with relevant ITE EMC standards. EMC compliance demands that this apparatus is installed within a VME enclosure designed to contain electromagnetic radiation and which will provide protection for the apparatus with regard to electromagnetic immunity. This enclosure must be fully shielded. An example of such an enclosure is a Schroff 7U EMC-RFI VME System chassis, which includes a front cover to complete the enclosure.

The connection of non-shielded equipment interface cables to this equipment will invalidate European Economic Area (EEA) EMC compliance and may result in electromagnetic interference and/or susceptibility levels that are in violation of regulations which apply to the legal operation of this device. It is the responsibility of the system integrator and/or user to apply the following directions, as well as those in the user manual, which relate to installation and configuration:

All interface cables should be shielded, both inside and outside of the VME enclosure. Braid/foil type shields are recommended for serial, parallel, and SCSI interface cables. Whereas external mouse cables are not generally shielded, an internal mouse interface cable must either be shielded or looped (1 turn) through a ferrite bead at the enclosure point of exit (bulkhead connector). External cable connectors must be metal with metal backshells and provide 360-degree protection about the interface wires. The cable shield must be terminated directly to the metal connector shell; shield ground drain wires alone are not adequate. VME panel mount connectors that provide interface to external cables (e.g., RS-232, SCSI, keyboard, mouse, etc.) must have metal housings and provide direct connection to the metal VME chassis. Connector ground drain wires are not adequate.

# **Table of Contents**

| Chapter 1 – Introduction                          | 1-1 |

|---------------------------------------------------|-----|

| Module Features                                   | 1-1 |

| Architecture                                      |     |

| CPU Chip                                          |     |

| Ethernet Controller                               |     |

| PCI Local Bus Interface                           | 1-2 |

| Video Controller                                  |     |

| Fast IDE controller and Floppy Drive Controller   |     |

| VMEbus Interface                                  |     |

| Card Expansion Options                            | 1-3 |

| Onboard Memory                                    |     |

| DRAM Memory                                       | 1-3 |

| Secondary Cache                                   | 1-4 |

| Flash BIOS                                        |     |

| ROM Site                                          | 1-4 |

| Nonvolatile SRAM                                  | 1-4 |

| DiskOnChip                                        | 1-4 |

| Universal Serial Bus Port                         | 1-4 |

| Serial and Parallel Ports                         | 1-4 |

| Mouse Port                                        | 1-4 |

| Keyboard Interface                                | 1-5 |

| Hard and Floppy Drives                            | 1-5 |

| Watchdog Timer                                    | 1-5 |

| Operational Description                           | 1-6 |

| Environmental Specifications                      | 1-7 |

| Hardware Specifications                           | 1-7 |

| System Configuration and Expansion Options Tables | 1-8 |

| Chapter 2 – Installation                          | 2-1 |

| Jumper Settings                                   | 2-2 |

| CPU Configuration                                 |     |

| CPU Core Voltage                                  |     |

| CPU Voltage Plane Configuration                   |     |

|                                                   | 2-3 |

| Memory                                            | 2-3 |

| Switch Settings                                   |     |

| Registers                                         |     |

| Register 218h – Abort/Clear CMOS Port             |     |

| Register 219h – LED/BIOS Port                     |     |

| Register 233h – Watchdog Timer Port               |     |

| Register 234h – NVRAM and DiskOnChip Port         |     |

| Connectors                                        | 2-7 |

| Serial Port Connectors                       | 2-7             |

|----------------------------------------------|-----------------|

| Parallel Port Connector                      | 2-7             |

| USB Port Connector                           | 2-8             |

| VGA Connector                                | 2-8             |

| Keyboard Port Connector                      | 2-8             |

| Auxiliary Connector                          | 2-9             |

| VMEbus Connectors                            | 2-10            |

| P1 Connector                                 | 2-10            |

| P2 Connector                                 | 2-11            |

| Interboard Connector 1 (P4)                  | 2-12            |

| Interboard Connector 2 (P3)                  | 2-13            |

| Installing the XVME-653/658 into a Backplane |                 |

| Enabling the PCI Ethernet Controller         |                 |

| Loading the Ethernet Driver                  |                 |

| Pinouts for the RJ-45 10/100 BaseT Connector |                 |

| Using a DiskOnChip                           | 2-17            |

| Chapter 3 – BIOS Setup Menus                 | 2.4             |

|                                              |                 |

| Getting to the BIOS Setup Menus              |                 |

| Moving through the Menus                     |                 |

| BIOS Main Setup Menu                         |                 |

| IDE Adapter 0 Master and Slave Submenus      |                 |

| Memory Cache Submenu                         |                 |

| Memory Shadow Submenu                        |                 |

| Boot Sequence Submenu                        |                 |

| Numlock Submenu                              |                 |

| Advanced Menu                                |                 |

| Integrated Peripherals Submenu               |                 |

| 32-Pin ROM Site Submenu                      |                 |

| Advanced Chipset Control Submenu             |                 |

| Security Menu.                               |                 |

| VMEbus Setup Menu                            |                 |

| System Controller Submenu                    |                 |

| Master Interface Submenu                     |                 |

| Slave Interface Submenus                     |                 |

| Exit MenuBIOS Compatibility                  |                 |

| BIOS Companionity                            |                 |

| Chapter 4 – Programming                      | 4-1             |

| Memory Map                                   | $\it \Delta$ _1 |

| I/O Map                                      |                 |

| IRQ Map                                      |                 |

| VME Interface                                |                 |

| System Resources                             |                 |

| VMEbus Master Interface                      |                 |

| VMEbus Slave Interface                       |                 |

| VMEbus Interrupt Handling                    |                 |

| VMEbus Interrupt Generation                  |                 |

| VMEhus Reset Ontions                         |                 |

| PCI BIOS Functions                          | 4-6  |

|---------------------------------------------|------|

| Calling Conventions                         | 4-7  |

| 16-Bit Interface                            | 4-7  |

| 32-Bit Interface                            | 4-7  |

| PCI BIOS Function Calls                     | 4-8  |

| Locating the Universe Chip                  | 4-8  |

| Read Configuration Byte                     | 4-9  |

| Read Configuration Word                     | 4-9  |

| Read Configuration Dword                    | 4-10 |

| Write Configuration Byte                    | 4-10 |

| Write Configuration Word                    | 4-11 |

| Write Configuration Dword                   |      |

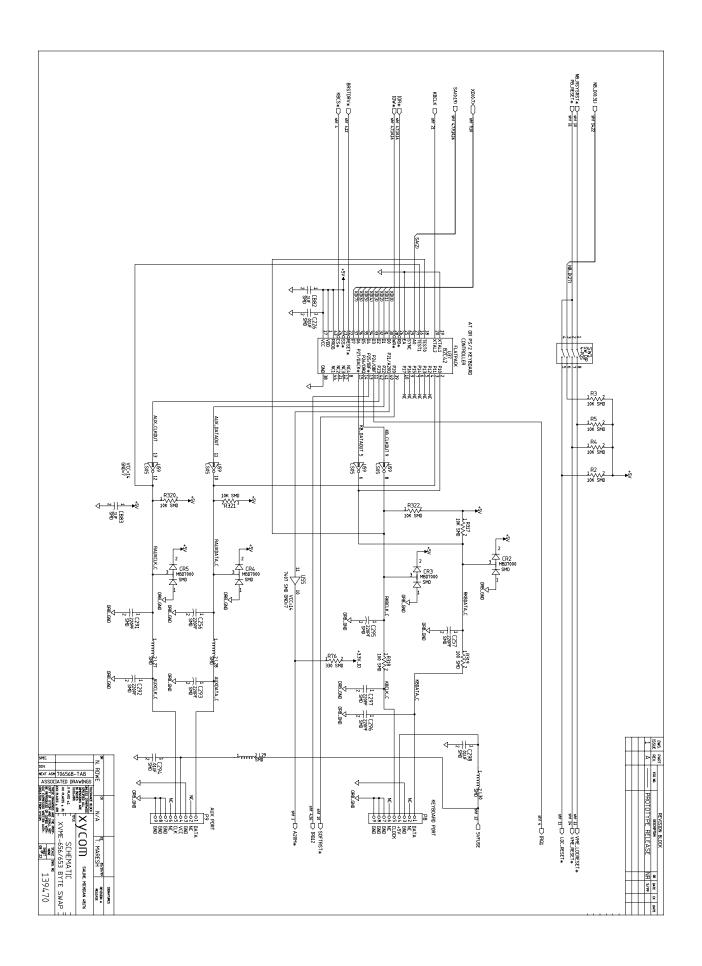

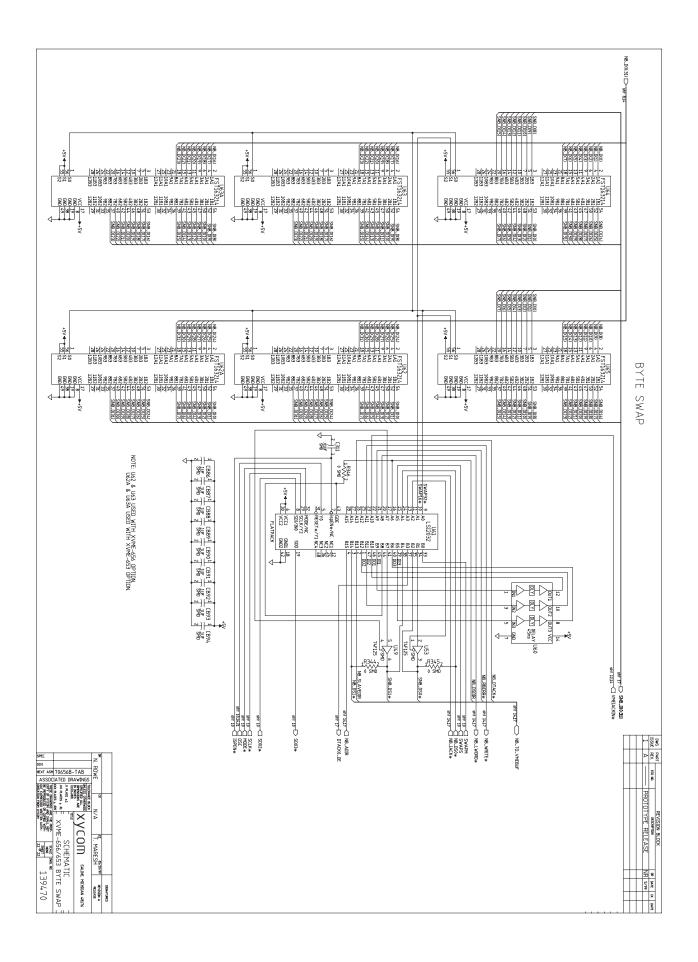

| Software-Selectable Byte-Swapping Hardware  |      |

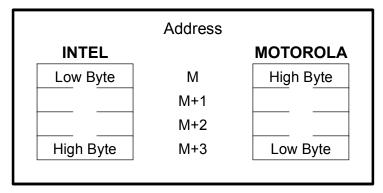

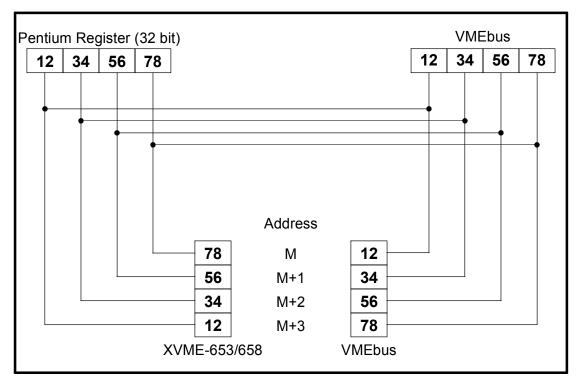

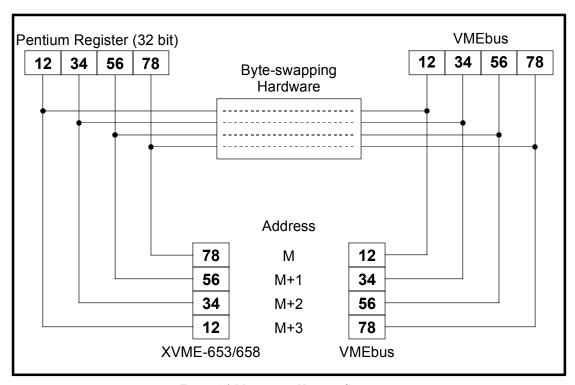

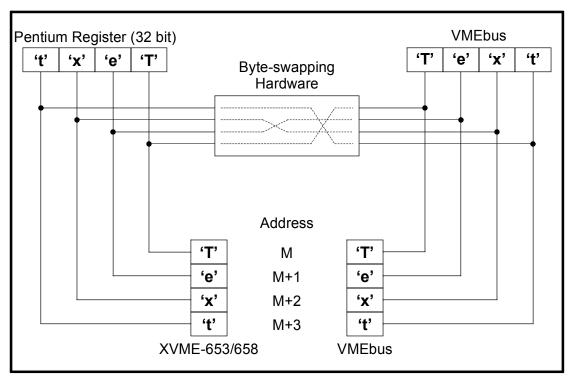

| Byte-Ordering Schemes                       |      |

| Numeric Consistency                         | 4-14 |

| Address Consistency                         | 4-15 |

| Chapter 5 – XVME-973/1 Drive Adapter Module | 5-1  |

| Connectors                                  | 5-2  |

| P1 Connector                                |      |

| P2 Connector                                |      |

| P3 Connector                                |      |

| P4 Connector                                | 5-5  |

| P5 Connector                                |      |

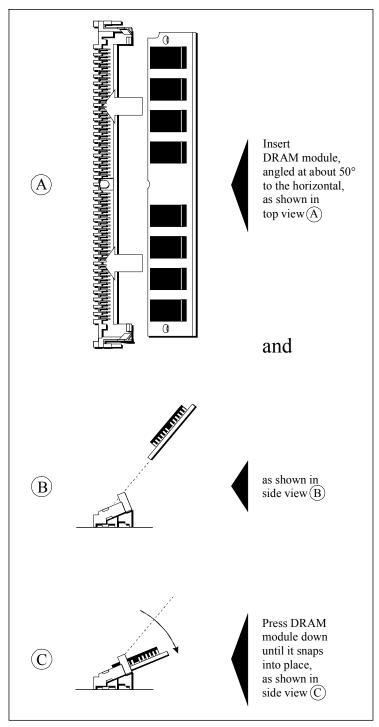

| Appendix A – DRAM Installation              | A-1  |

| Appendix B – Drawings                       | B-1  |

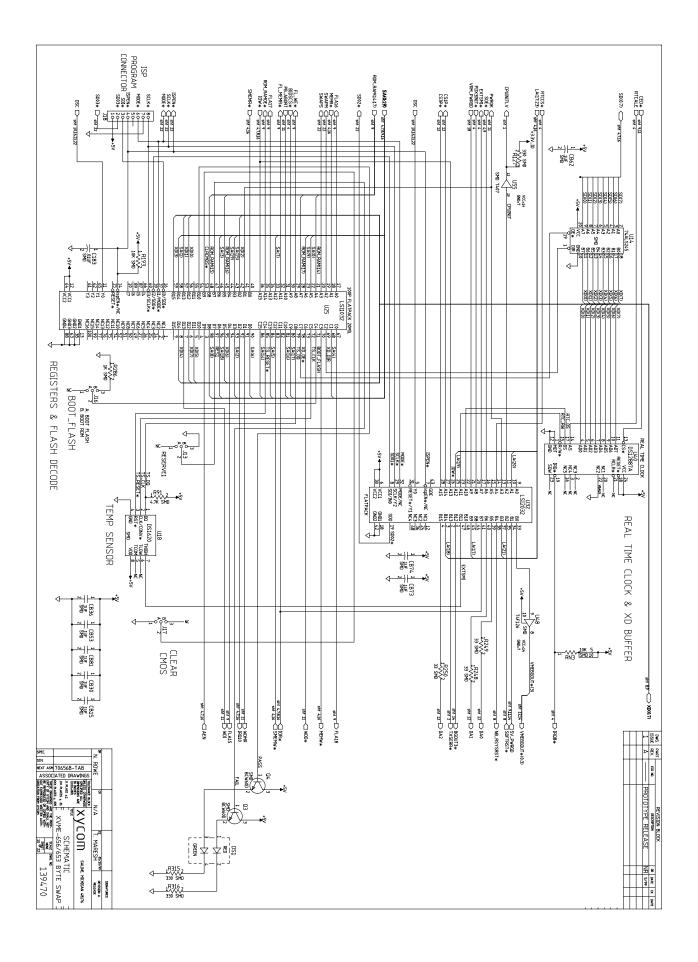

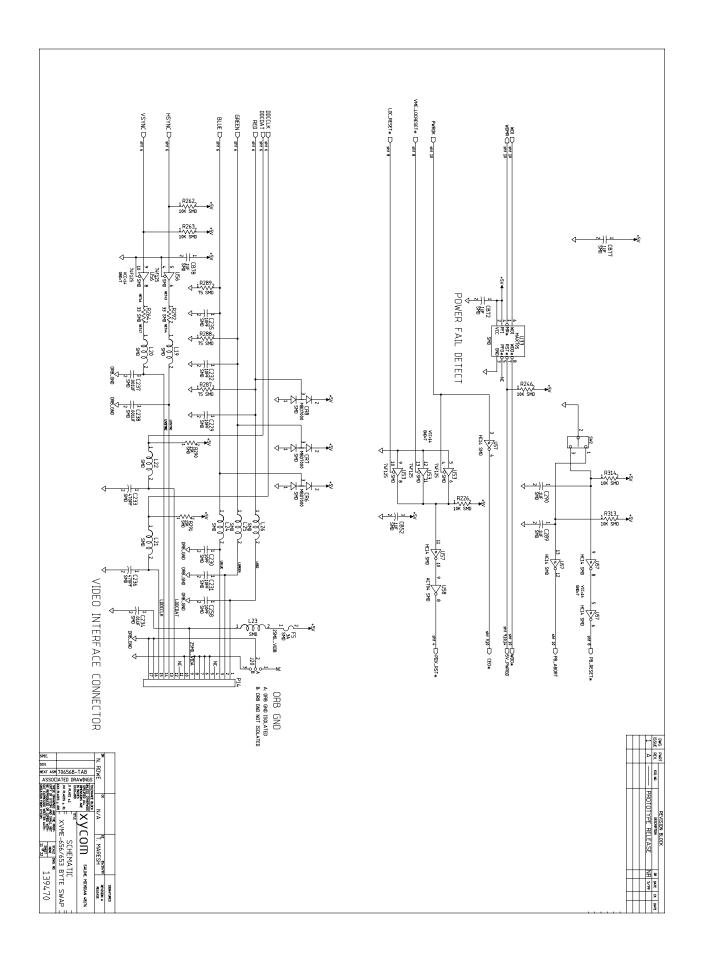

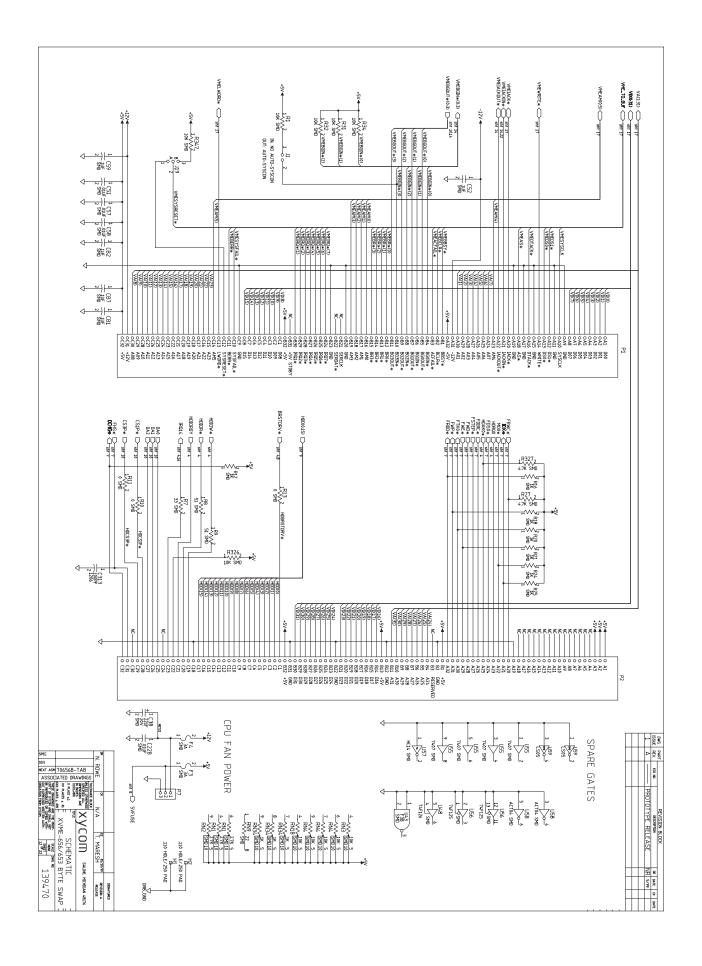

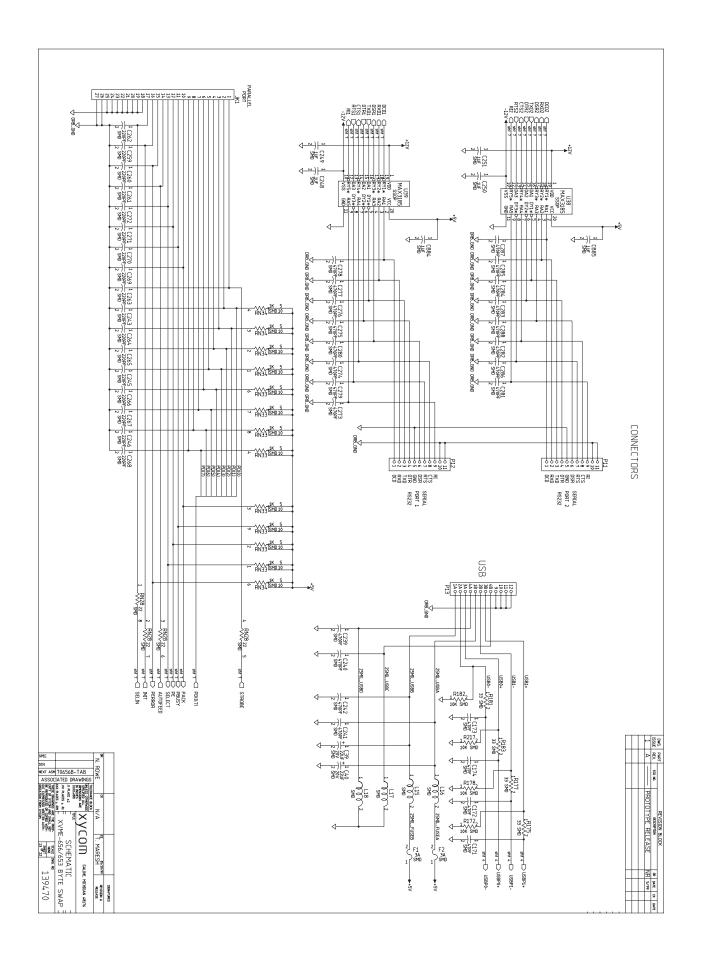

| Annandiy C — Schamatic                      | C-1  |

# **Chapter 1 – Introduction**

The XVME-653 VMEbus Pentium<sup>®</sup> MMX<sup>TM</sup> PC-compatible VMEbus processor module and the XVME-658 VMEbus AMD-K6<sup>®</sup>-2 PC-compatible VMEbus processor module are designed to combine the high performance and ruggedized packaging of the VMEbus with the broad application software base of the IBM PC standard. These modules integrate the latest processor and chipset technology.

At the core of the XVME-653 is an Intel® 233 MHz Pentium CPU with MMX technology. This generation of Pentium processors features enhanced multimedia instructions, larger level 1 caches, and a 10 to 20 percent performance increase over standard Pentium processors.

At the core of the XVME-658 is an AMD 333 MHz K6-2 CPU with 3DNOW!<sup>TM</sup> Technology. 3DNOW!<sup>TM</sup> Technology is the first innovation to the x86 processor architecture that significantly enhances floating-point-intensive three-dimensional (3D) graphics performance. The AMD-K6-2 system can provide performance comparable to the many of the Pentium II systems on the market today.

### **Module Features**

The XVME-653 and the XVME-658 offer the following features:

- 233 MHz Intel Pentium MMX CPU (XVME-653)

- 333 MHz AMD-K6-2 CPU with 3DNOW! Technology (XVME-658)

- Up to 256 MB fast-page or EDO DRAM in 72-pin SIMM sites, with ECC or parity

- 512 KB of synchronous level 2 pipeline cache

- High-performance PCI local bus SVGA controller with 2 MB of VRAM

- PCI Enhanced IDE controller with DMA

- 10/100 Mbit PCI Ethernet controller with front RJ-45 connector

- 32-pin site for *DiskOnChip* or battery-backed SRAM

- PCI-to-VMEbus interface with DMA

- Two high-speed 16550-compatible serial ports

- One Universal Serial Bus (USB) port

- EPP or ECP configurable parallel port

- PS/2-style keyboard and mouse ports

- Configurable hardware byte-swapping logic (XVME-658 and XVME-653/31x)

- Expansion options for PC/104, PMC, ISA, and PCI cards

### **Architecture**

This section describes the XVME-653/658 processor modules' architecture.

## **CPU Chip**

The XVME-653 supports the Intel 233 MHz Pentium MMX processor. The MMX processor features new instructions to improve multimedia performance. A dynamic branch prediction unit, improved internal pipelines, and separate 16 KB data and instruction caches further enhance performance.

The XVME-658 supports the AMD 333 MHz K6-2 processor with 3DNOW! Technology. The AMD 333 MHz K6-2 processor incorporates the MMX instruction set as well as the new 3DNOW! Technology instruction set which can increase the speed of floating-point-intensive operations and 3D graphics. In addition, a 64 KB L1 cache, four x86 instructions decoders, a large branch prediction table, and six integer-execution units further enhance performance.

### **Ethernet Controller**

The XVME-653/658 contains a state-of-the-art Intel 82558 10/100 BaseTX Ethernet controller with a 32-bit PCI bus mastering interface to support 100 Mbits per second bus transfers. The RJ-45 connector on the module's front panel provides autosensing for 10BaseT and 100BaseTX connections.

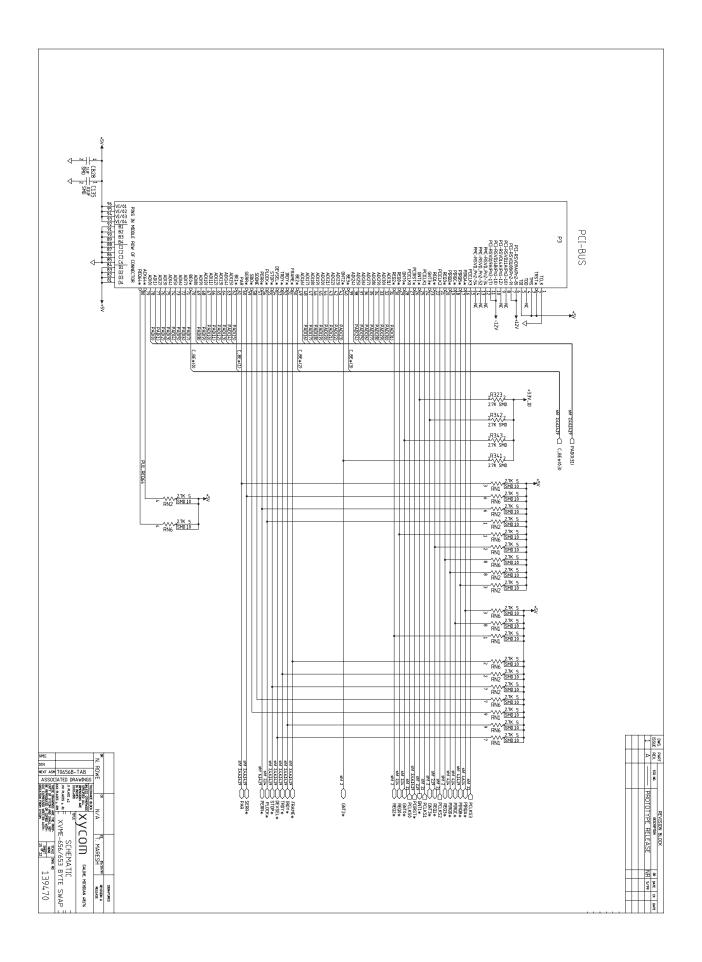

### **PCI Local Bus Interface**

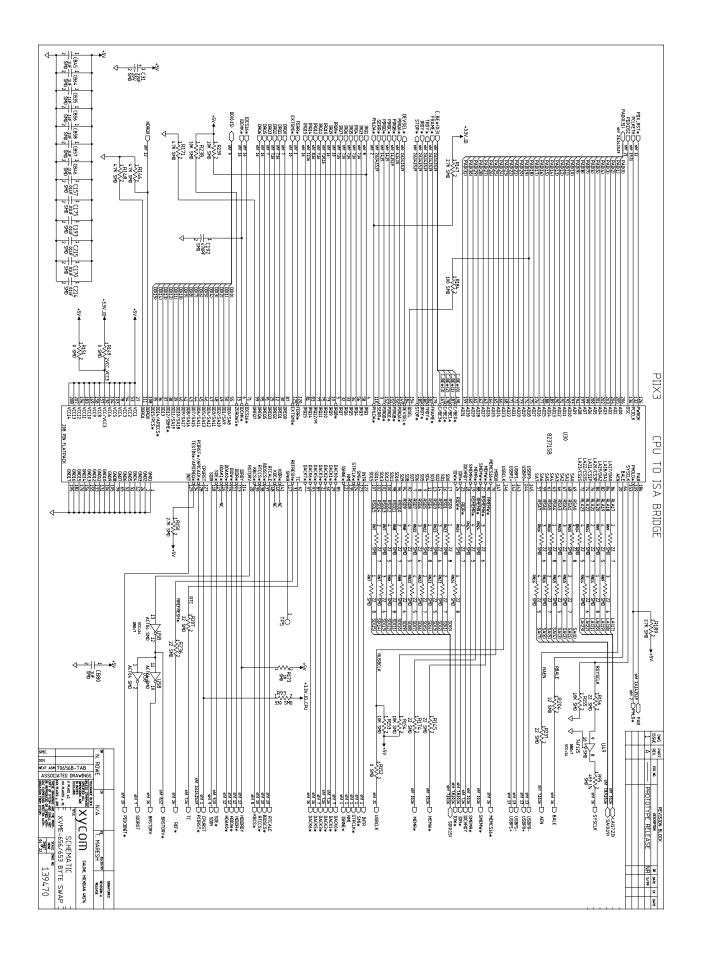

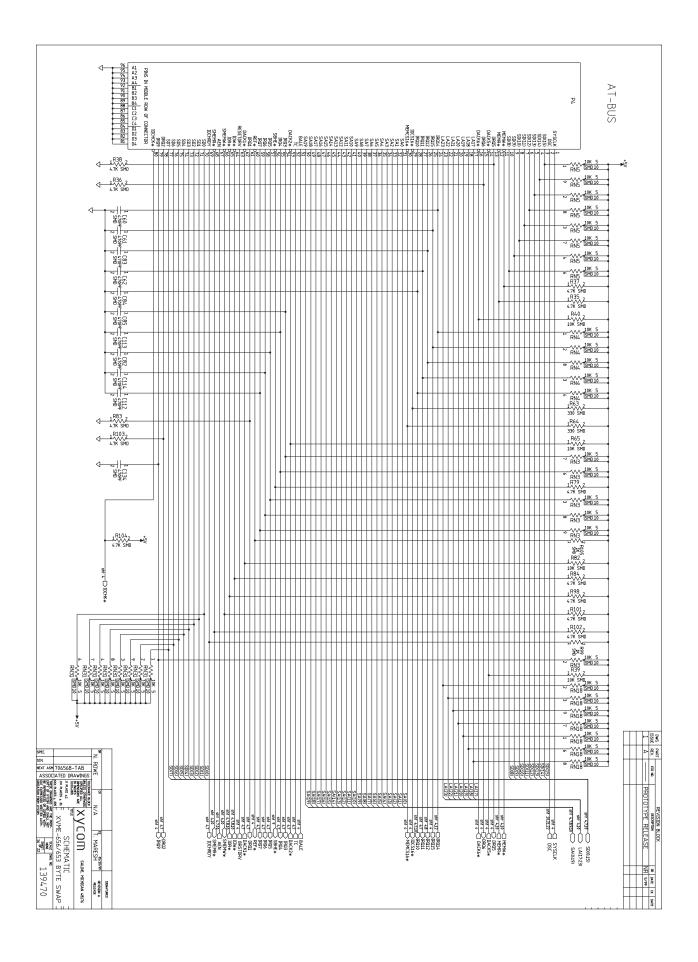

The PCI-to-ISA bridge device provides an accelerated PCI-to-ISA interface that includes a high-performance enhanced IDE controller, PCI and ISA master/slave interfaces, enhanced DMA functions, and a plug-and-play port for onboard devices. The bridge device also provides many common I/O functions found in ISA-based PC systems, including a seven channel DMA controller, two 82C59 interrupt controllers, an 8254 timer/counter, and control logic for NMI generation.

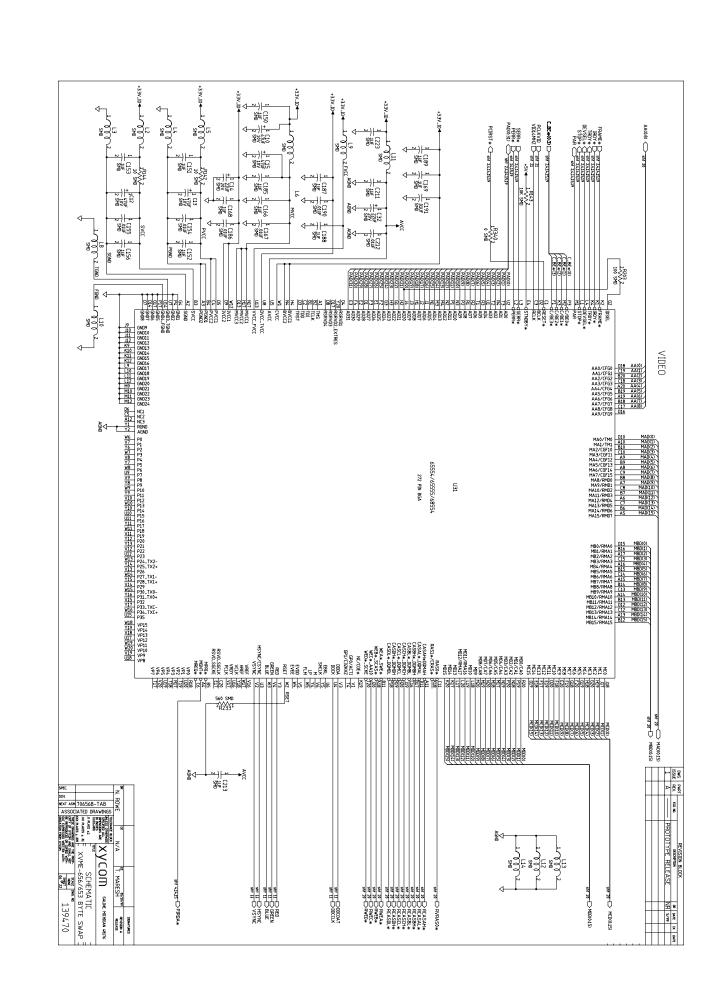

#### Video Controller

The PCI bus video controller features a 64-bit graphics engine, with 24-bit RAMDAC for true color support. It has 2 MB of VRAM and supports resolutions up to 1280 x 1024 with 256K colors.

### **Fast IDE controller and Floppy Drive Controller**

The enhanced IDE controller supports programmed I/O (PIO) and bus mastering DMA with transfer rates to 22 MB/second. The controller contains an 8 x 32 bit buffer for bus master IDE PCI burst transfers, and will support up to two IDE devices. This controller can also handle a single optional floppy drive device. If present, this floppy drive will be designated Drive A.

### Caution

The IDE controller supports enhanced PIO modes, which reduce the cycle times for 16-bit data transfers to the hard drive. Check with your drive manual to see if the drive you are using supports these modes. The higher the PIO mode, the shorter the cycle time. As the IDE cable length increases, this reduced cycle time can lead to erratic operation. As a result, it is in your best interest to keep the IDE cable as short as possible.

The PIO modes are selected in the BIOS setup (see p. 3-4). The Autoconfig will attempt to classify the connected drive if the drive supports the auto ID command. If you experience problems, change the **Transfer Mode:** to *Standard*.

### Caution

The total cable length must not exceed 18 inches. Also, if two drives are connected, they must be no more than six inches apart.

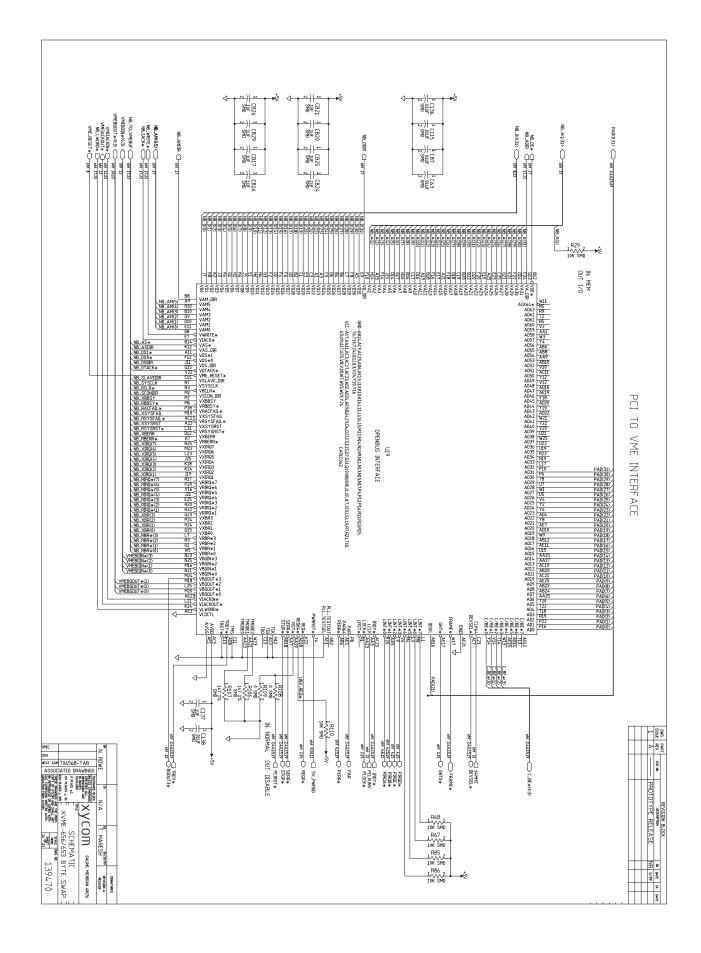

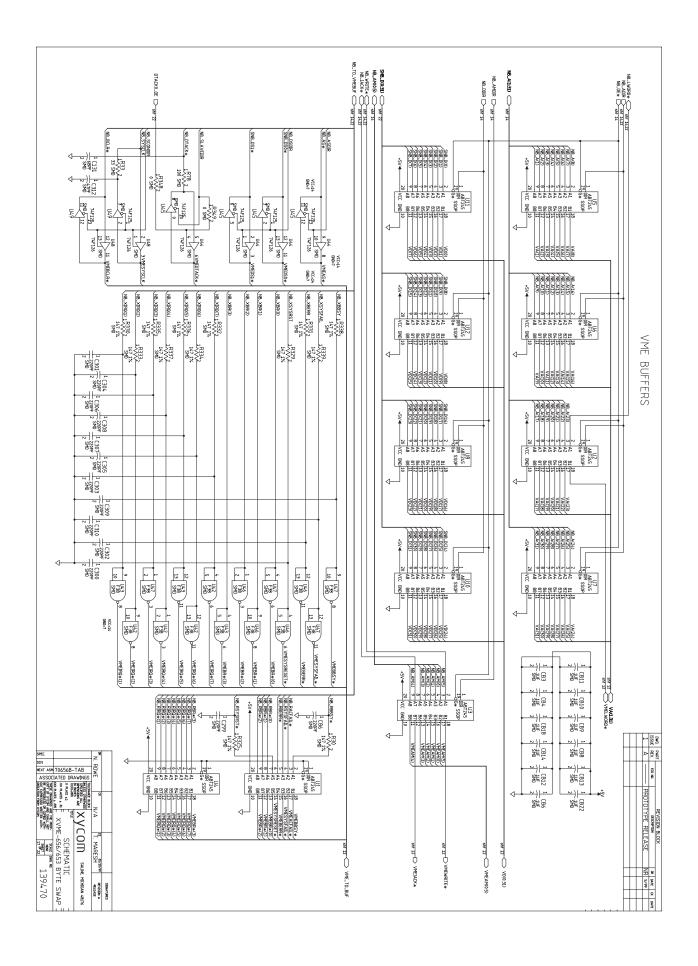

### VMEbus Interface

The XVME-653/658 uses the PCI local bus to interface to the VMEbus. The VMEbus interface supports full DMA to and from the VMEbus, integral FIFOs for posted writes, block mode transfers, and read-modify-write operations. The interface contains one master and four slave images that can be programmed in a variety of modes to allow the VMEbus to be mapped into the XVME-653/658 local memory. This makes it easy to configure VMEbus resources in protected and real mode programs. The XVME-658 and the XVME-653/31x modules also incorporate onboard hardware byte-swapping (see Table 1-1).

## **Card Expansion Options**

The XVME-653/658 supports optional PMC (PCI Mezzanine Card), PC/104, short ISA, or PCI expansion using XVME-976 expansion modules. The XVME-976/201 provides one PCI Mezzanine Card (PMC) site and one 16-bit PC/104 site. The XVME-976/202 provides one 16-bit short ISA expansion site. The XVME-976/203 provides two PMC sites. The XVME-976/204 provides two 16-bit PC/104 sites. The XVME-976/205 provides one PCI card expansion site. All XVME-976 modules are designed to plug directly into the XVME-653/658 using the 80-pin interboard connectors.

## **Onboard Memory**

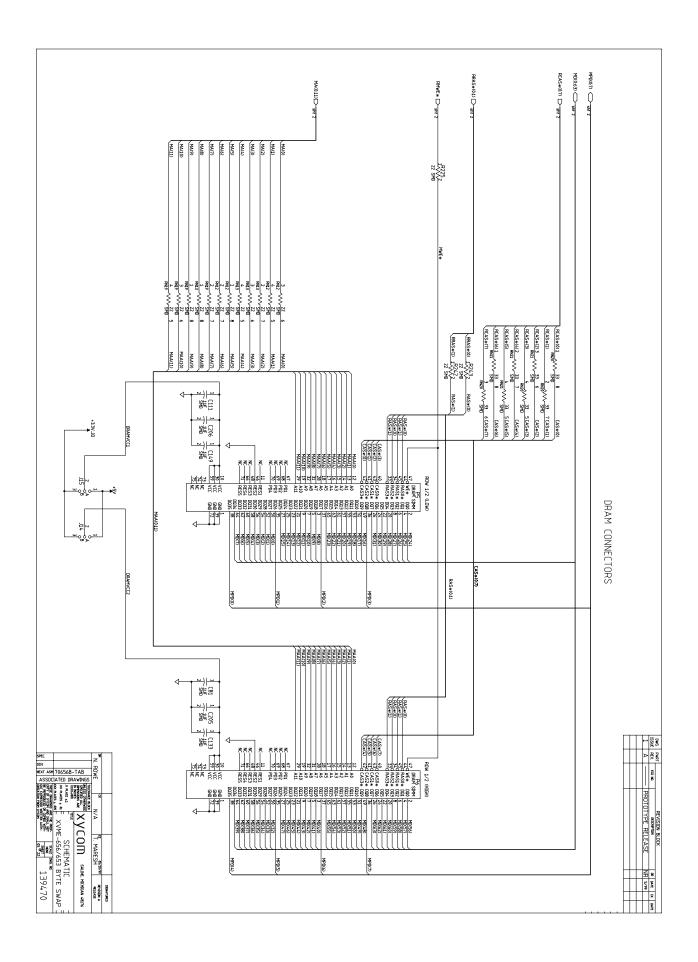

### **DRAM Memory**

The XVME-653/658 has two 72-pin SIMM memory sites, providing up to 256 MB of DRAM. The memory sites can be populated with standard fast page mode memory or enhanced data out memory (EDO). EDO memory is designed to improve DRAM read performance. Using EDO memory improves the back-to-back burst timing to 5-2-2-2 from the 5-3-3-3 of standard memory. The XVME-653/658 also supports error checking

and correction (ECC) or parity checking DRAM memory. Approved DRAM suppliers are listed in Appendix A.

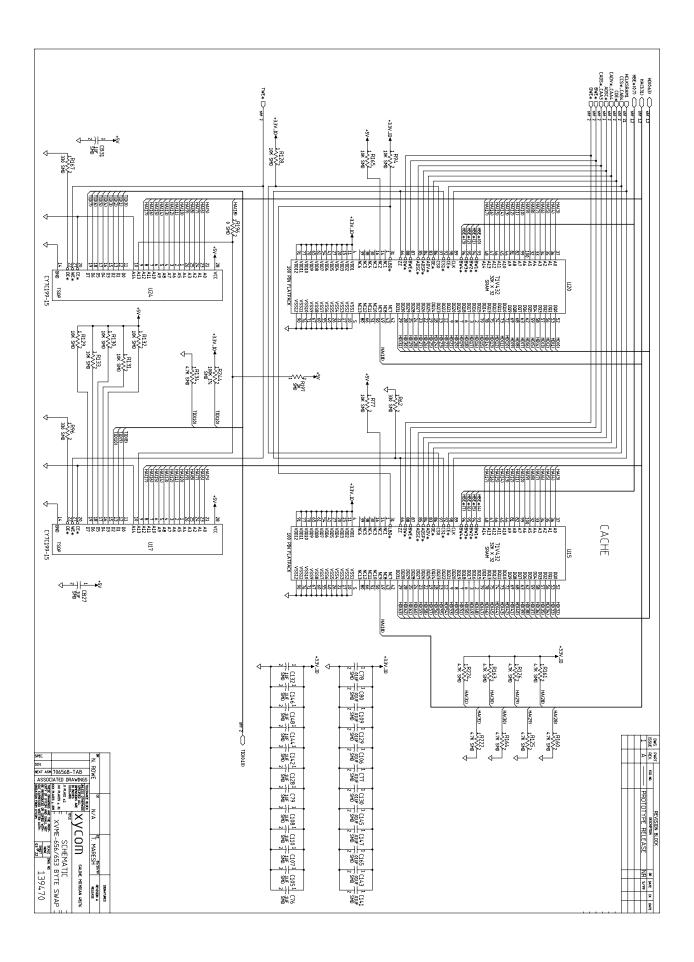

### **Secondary Cache**

The XVME-653/658 comes equipped with 512 KB synchronous level 2 pipeline burst cache.

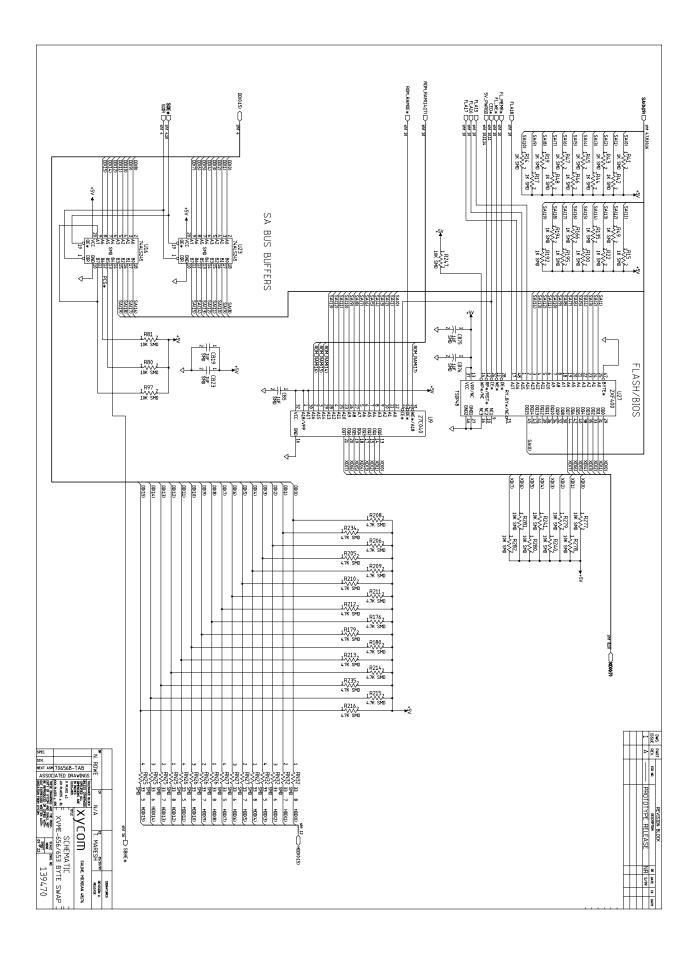

#### Flash BIOS

The XVME-653/658 system BIOS is contained in a 512 KB flash device to facilitate system BIOS updates. You can program and enable additional areas of the flash device to provide optional ROM support. You should contact Xycom Automation for more information on flashing option ROMs and video ROMs into the BIOS image.

### **ROM Site**

This 32-pin onboard site supports nonvolatile SRAM and *DiskOnChip*.

#### Nonvolatile SRAM

The board supports 32K x 8 and 128K x 8 nonvolatile SRAM memory sizes. Packaged in a standard 32-pin DIP format, the SRAM contains a built-in battery and battery backup. Battery life is seven years minimum in absence of V<sub>CC</sub>.

### DiskOnChip

The *DiskOnChip* is a single-chip flash disk in a standard 32-pin DIP format. It requires an 8 KB window to view as an extension BIOS. During boot up, the *DiskOnChip* loads its software in the PC memory and installs itself as an additional drive. See Table 1-2 for *DiskOnChip* size options.

### **Universal Serial Bus Port**

The XVME-653/658 incorporates a Universal Serial Bus (USB) port that is compatible with USB devices. The port terminates in a standard two-pin connector.

#### Serial and Parallel Ports

PC peripherals include two high-speed 16550-compatible serial ports and an ECP or EPP configurable parallel port.

#### **Mouse Port**

The XVME-653/658 includes a PS/2-compatible mouse port.

### **Keyboard Interface**

The keyboard interface uses a PS/2-style connector on the front panel. The +5 V is protected with a polyswitch. This device will open up if the +5 V is shorted to GND. Once the shorting condition is removed, the polyswitch will allow current flow to resume.

## **Hard and Floppy Drives**

The XVME-653/658 IDE hard drive and floppy drive signals are routed through the P2 connector, providing a simplified method of connecting external floppy and hard drives. The XVME-653/658 will support only one floppy drive.

When used with the XVME-977 mass storage module, the hard and floppy drives do not need to be located next to the processor. Using the supplied six-inch ribbon cable (which connects the XVME boards' J2 VME backplane connectors), the XVME-977 can be installed up to six slots away from the XVME-653/658 on the VME backplane. This allows greater flexibility in configuring the VMEbus card cage.

For applications that require mass storage outside the VMEbus chassis, the XVME-973/1 drive adapter module plugs onto the VMEbus J2 connector. This module provides industry standard connections for IDE and floppy signals. One floppy drive can be connected to the XVME-973/1. This drive may be 2.88 MB, 1.44 MB, 1.2 MB, or 360 KB in size. For more information on the XVME-973/1, refer to Chapter 5.

### Caution

The total cable length must not exceed 18 inches. If two drives are connected, they must be no more than six inches apart.

## **Watchdog Timer**

The XVME-653/658 incorporates a watchdog timer. When enabled, the timer can either generate an interrupt or a master reset, depending on how you configure the watchdog timer port. The timer input needs to be toggled within 1.6 seconds to prevent timeout.

# **Operational Description**

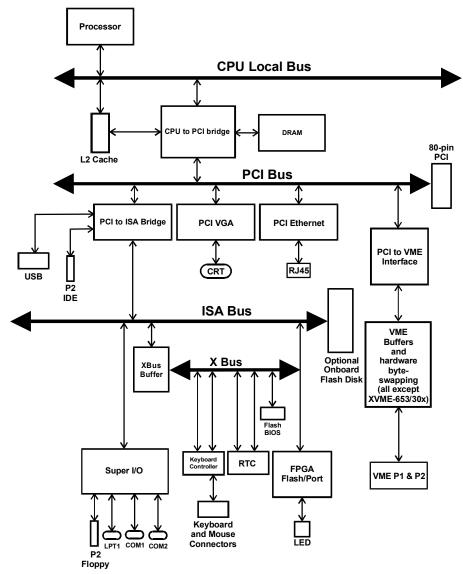

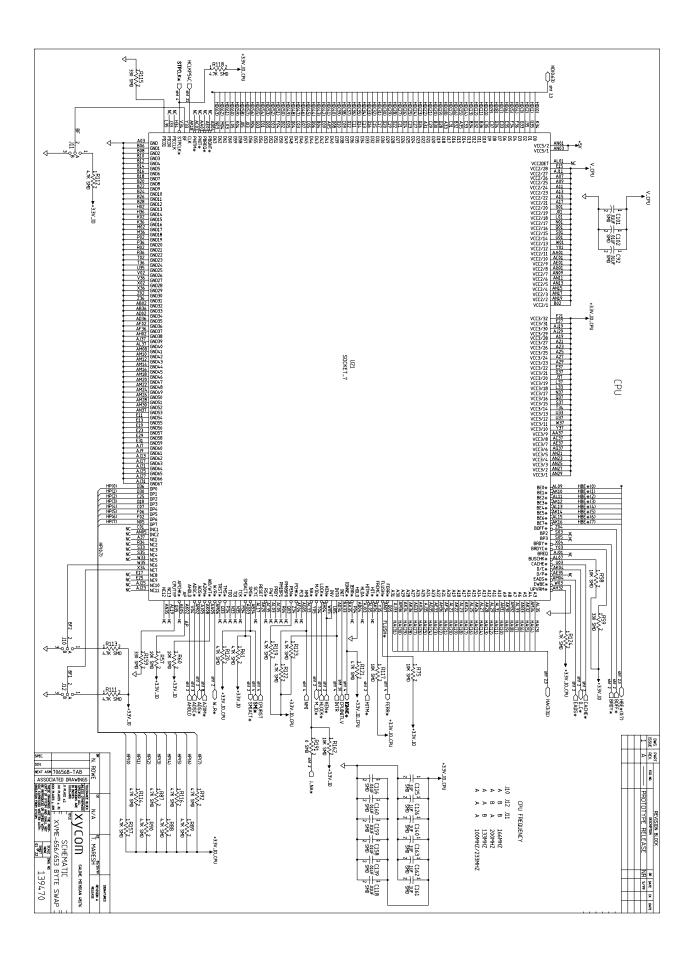

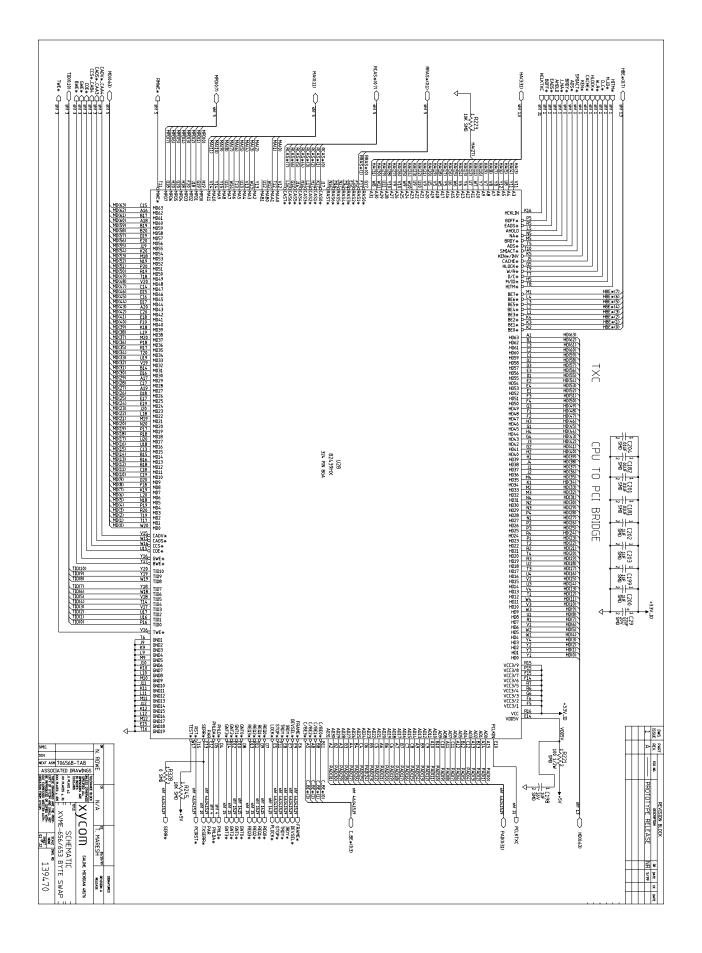

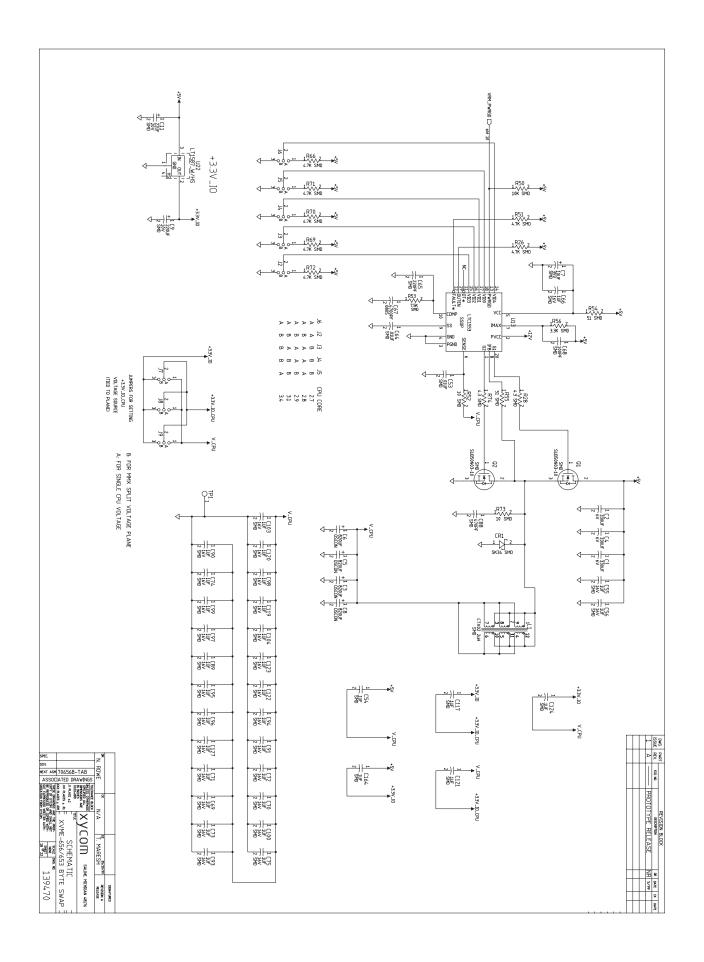

Figure 1-1 is the block diagram for the XVME-653/658.

Figure 1-1 XVME-653/658 Block Diagram

# **Environmental Specifications**

| Characteristic                                                                                        | Specification                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature: Operating (100 cfm airflow) XVME-653 (Intel 233 MHz Pentium) XVME-658 (AMD 333 MHz K6-2) | 0 to 50°C (32 to 122°F)<br>0 to 45°C (32 to 113°F)                                                                                                           |

| Nonoperating                                                                                          | -45 to 85°C (-49 to 185°F)                                                                                                                                   |

| Vibration: Frequency Operating Nonoperating                                                           | 5 to 2000 Hz 0.015" (0.38 mm) peak-to-peak displacement 2.5 G (maximum) acceleration 0.030" (0.76 mm) peak-to-peak displacement 5.0 G (maximum) acceleration |

| Shock: Operating Nonoperating                                                                         | 30 G peak acceleration, 11 msec duration 50 G peak acceleration, 11 msec duration                                                                            |

| Humidity                                                                                              | 20% to 80% RH, noncondensing                                                                                                                                 |

# **Hardware Specifications**

| Characteristic                                                          | Specification                                                             |  |  |  |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|

| Power Specifications:<br>+12V<br>-12V                                   | 75 mA maximum<br>24 mA maximum                                            |  |  |  |

| +5V:<br>XVME-653 (Intel 233 MHz Pentium)<br>XVME-658 (AMD 333 MHz K6-2) | 10.59 A (maximum); 5.87 A (typical)<br>10.59 A (maximum); 6.5 A (typical) |  |  |  |

| CPU speed: XVME-653<br>XVME-658                                         | 233 MHz<br>333 MHz                                                        |  |  |  |

| Cache                                                                   | 512 KB pipeline burst cache                                               |  |  |  |

| Ethernet controller                                                     | Intel 82558 10/100 BaseTX Fast Ethernet; RJ-45                            |  |  |  |

| PCI Super VGA Graphics Controller                                       | 1280 x 1024 maximum resolution, 256 colors; 2 MB VRAM                     |  |  |  |

| Serial Ports                                                            | RS-232C, 16550 compatible (2)<br>USB (1)                                  |  |  |  |

| Parallel Interface                                                      | EPP/ECP compatible (1)                                                    |  |  |  |

| Onboard memory                                                          | Fast-page or EDO DRAM, ECC or parity, up to 256 MB                        |  |  |  |

| Regulatory Compliance                                                   | European Union<br>Electromagnetic Compatibility - 89/336/EEC              |  |  |  |

#### **VMEbus Compliance**

Complies with VMEbus Specification ANSI/VITA 1–1994 A32/A24/A16:D64/D32/D16/D08(EO) DTB Master A32/A24/A16:D64/D32/D16/D08(EO) DTB Slave R(0-3) Bus Requester Interrupter I(1)-I(7) DYN IH(1)-IH(7) Interrupt Handler SYSCLK and SYSRESET Driver

PRI, SGL, RRS Arbiter RWD, ROR bus release

Form Factor: Double-height, single-width 233 mm x 160 mm (9.2" x 6.3")

# **System Configuration and Expansion Options Tables**

Your XVME-653/658 can be ordered in a variety of configurations and expanded as well. The following tables show these options.

Table 1-1 XVME-653/658 CPU and DRAM Configurations and Byte-Swapping Hardware

| Intel 2            | XVME-653<br>233 MHz Pentium ( | CPU    | AMI          | XVME-658<br>D 333 MHz K6-2 CF | าบ     |

|--------------------|-------------------------------|--------|--------------|-------------------------------|--------|

| Ordering<br>Number | Byte-Swapping Hardware?       | DRAM   |              | Byte-Swapping Hardware?       | DRAM   |

| XVME-653/310       | Yes                           | None   | XVME-658/310 | Yes                           | None   |

| XVME-653/313       | Yes                           | 32 MB  | XVME-658/313 | Yes                           | 32 MB  |

| XVME-653/314       | Yes                           | 64 MB  | XVME-658/314 | Yes                           | 64 MB  |

| XVME-653/315       | Yes                           | 128 MB | XVME-658/315 | Yes                           | 128 MB |

| XVME-653/316       | Yes                           | 256 MB | XVME-658/316 | Yes                           | 256 MB |

| XVME-653/300       | No                            | None   |              |                               |        |

| XVME-653/303       | No                            | 32 MB  |              |                               |        |

| XVME-653/304       | No                            | 64 MB  |              |                               |        |

| XVME-653/305       | No                            | 128 MB |              |                               |        |

| XVME-653/306       | No                            | 256 MB |              |                               |        |

The ordering number is broken into two parts. The model number is the 653 or 658. The tab number is the three digits after the slash. For the XVME-653/658, the tab number indicates the presence of byte-swapping hardware (the second digit is a one if the unit has byte-swapping hardware, otherwise it is a zero) and the amount of DRAM memory (the third digit). DRAM options are explained more fully in Appendix A.

There are also several expansion options for the XVME-653/658.

Table 1-2 XVME-653/658 Expansion Options

| Ordering<br>Number | Description                              |  |  |  |

|--------------------|------------------------------------------|--|--|--|

| XVME-973/1         | Drive Adapter Module for external drives |  |  |  |

| XVME-976/201       | PMC and PC/104 Expansion Module          |  |  |  |

| XVME-976/202       | 16-bit short ISA Expansion Module        |  |  |  |

| XVME-976/203       | Dual PMC Expansion Module                |  |  |  |

| XVME-976/204       | Dual PC/104 Expansion Module             |  |  |  |

| XVME-976/205       | PCI Carrier Module                       |  |  |  |

| XVME-977           | Single-slot Mass Storage Module          |  |  |  |

| XVME-992/8         | 8 MB DiskOnChip                          |  |  |  |

| XVME-992/24        | 24 MB DiskOnChip                         |  |  |  |

| XVME-992/40        | 40 MB DiskOnChip                         |  |  |  |

| XVME-992/72        | 72 MB DiskOnChip                         |  |  |  |

| XVME-992/144       | 144 MB DiskOnChip                        |  |  |  |

The XVME-976 expansion modules and the XVME-977 module are described in their own manuals. The XVME-973/1 is described in Chapter 5.

# **Chapter 2 – Installation**

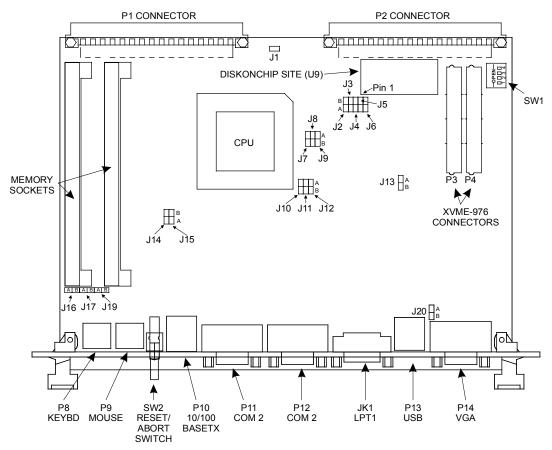

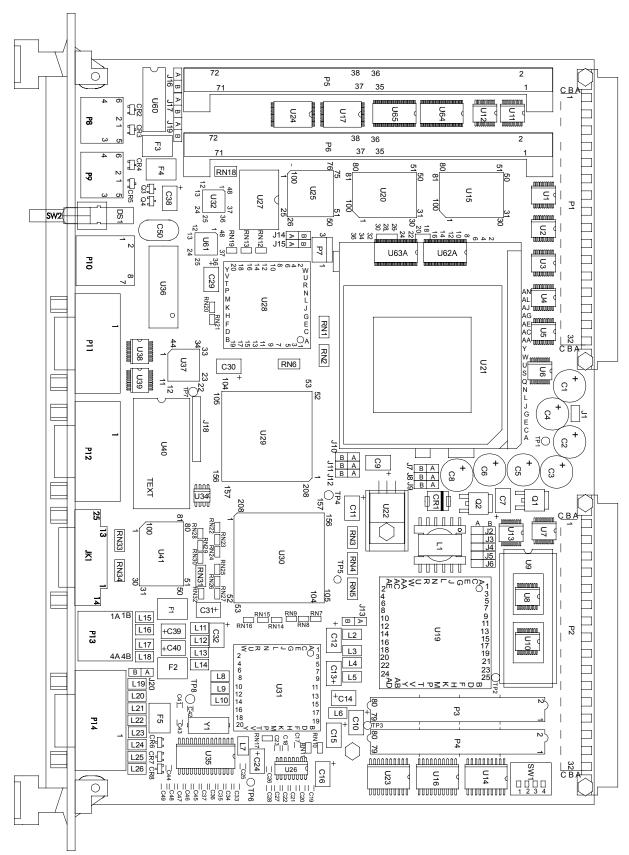

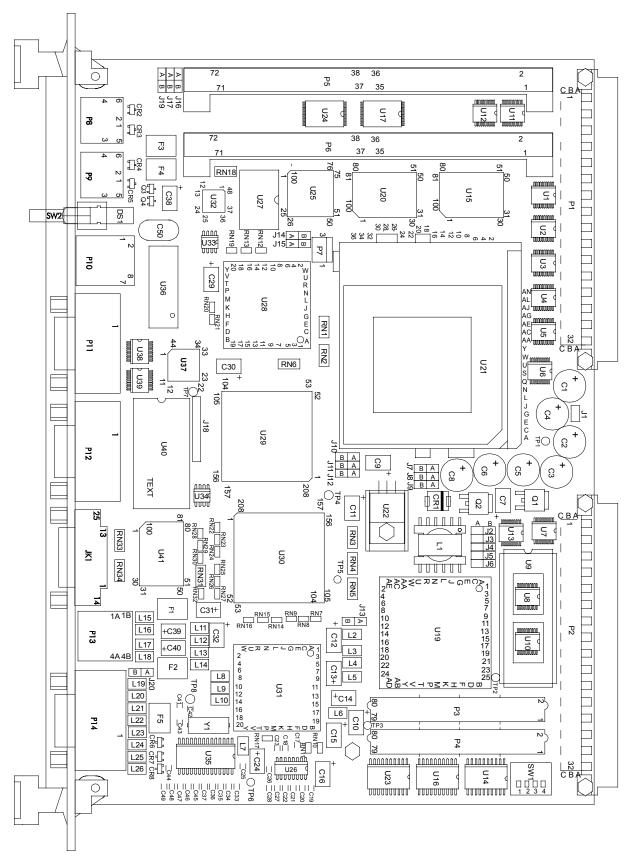

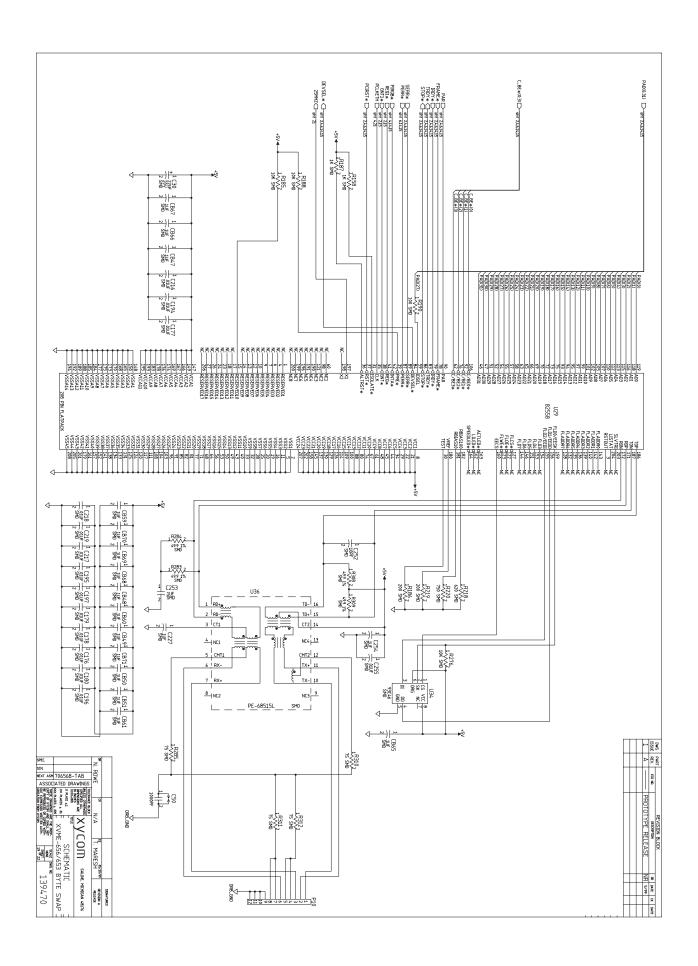

This chapter provides information on configuring the XVME-653/658 modules. It also provides information on installing the XVME-653/658 into a backplane and enabling the Ethernet controller. Figure 2-1 and Figure 2-2 illustrate the jumper, switch, and connector locations on the XVME-653/658. Note that the version of the XVME-653 module without the byte-swapping hardware has three jumpers in slightly different positions.

Figure 2-1 XVME-653/658 Jumper, Switch, and Connector Locations

Figure 2-2 J16, J17, and J19 Jumper Locations for XVME-653/30x (no byte-swapping hardware)

# **Jumper Settings**

The following tables list the XVME-653/658 jumpers, their default positions (either checked or labeled by module number), and their functions. Jumper locations are shown in Figure 2-1 and Figure 2-2.

Jumper **Position Function** J1 In Disables system resource function Enables system resource function Out √ J13 A √ Reserve 1 В J16 A √ Boot from Flash Boot from ROM В Α Clear CMOS memory J17 Normal CMOS memory в√ Α√ J19 Reserve 2 В J20 Α Reserve 3

Table 2-1 General Jumper Settings

## **CPU Configuration**

в√

Table 2-2 CPU Configuration Jumper Settings

| Module/Speed     | J2 | J3 | J4 | J5 | J6 | J7 | J8 | J9 | J10 | J11 | J12 |

|------------------|----|----|----|----|----|----|----|----|-----|-----|-----|

| XVME-653/233 MHz | В  | Α  | Α  | Α  | Α  | В  | В  | В  | Α   | Α   | Α   |

| XVME-658/333 MHz | Α  | Α  | В  | Α  | Α  | В  | В  | В  | В   | Α   | В   |

## **CPU Core Voltage**

Table 2-3 CPU Core Voltage Jumper Settings

| CPU Core Voltage         | J2 | J3 | J4 | J5 | J6 |

|--------------------------|----|----|----|----|----|

| 2.2 V (XVME-658/333 MHz) | Α  | Α  | В  | Α  | Α  |

| 2.8 V (XVME-653/233 MHz) | В  | Α  | Α  | Α  | Α  |

## **CPU Voltage Plane Configuration**

Table 2-4 CPU Voltage Plane Configuration Jumper Settings

| CPU Configuration                     |   | J8 | J9 |

|---------------------------------------|---|----|----|

| Single Voltage Plane                  | Α | Α  | Α  |

| Split Voltage Planes (XVME-653/658) √ | В | В  | В  |

# **Processor Speed**

Table 2-5 Processor Speed Jumper Settings

| Processor Speed         | J10 | J11 | J12 |

|-------------------------|-----|-----|-----|

| 3/2x (XVME-653/233 MHz) | Α   | Α   | Α   |

| 5x (XVME-658/333 MHz)   | В   | Α   | В   |

# Memory

Table 2-6 Memory Voltage Jumper Settings

| Memory         | J14 | J15 |

|----------------|-----|-----|

| 5.0 V <b>√</b> | Α   | Α   |

| 3.3 V          | В   | В   |

# **Switch Settings**

The XVME-653/658 has one four-pole switch (SW1). This switch controls the system response to the front panel **Reset** switch (SW2). Table 2-7 shows the switch settings required to reset on the XVME-653/658 CPU, to reset only the VME backplane, or to reset both. The switch 3 is reserved and should always be closed. The XVME-653/658 is shipped with all four switches in the closed position (which causes SW2 to reset both the XVME-653/658 and the VME backplane). Both switches are shown on Figure 2-1.

For the front panel reset The four-pole switch switch (SW2) is to do this: (SW1) settings must be: 2 No Resets Closed Open Open Reset the VME backplane only\* Open Closed Open Reset the XVME-653/658 CPU only\*\* Closed Open Closed Reset both the VME backplane and the Closed Closed Closed XVME-653/658 CPU (default setting)

Table 2-7 Four-Pole Switch (SW1) Settings

### \*Caution

Resetting only the VME backplane will reset the Universe chip.

### \*\*Caution

If you have an older XVME-653 which has a Tundra Universe chip instead of a Tundra Universe II chip (U19), you do not have the ability to reset the CPU only. The option to reset both the CPU and the VME backplane still works normally.

You can tell a Universe from a Universe II by looking at the model number on the top of the chip. The Universe has CA91C042-33CE and the Universe II has CA91C142-33CE.

## Registers

The XVME-653/658 contains four I/O port registers: 218h, 219h, 233h, and 234h.

## Register 218h - Abort/Clear CMOS Port

This register controls the abort toggle switch and allows you to read the CMOS clear jumper (J17).

Bit R/W Result Signal 0 **RESERVED** Reserved 1 **RESERVED** Reserved **RESERVED** Reserved 2 3 **RESERVED** Reserved 4 ABORT\_STS 1 = Abort toggle switch caused interrupt R 0 = Clear and disable abort R/W 5 ABORT\_CLR 1 = Enable abort 6 **RESERVED** Reads jumper J13 R **CLRCMOS** 0 = Clear CMOS R 1 = CMOS okay

Table 2-8 Abort/Clear CMOS Port Register Settings

## Register 219h - LED/BIOS Port

This register controls the following LEDs and signals.

| Bit | LED/Signal       | Result                                                                          | R/W |

|-----|------------------|---------------------------------------------------------------------------------|-----|

| 0   | FAULT            | 0 = Fault LED on<br>1 = Fault LED off                                           | R/W |

| 1   | PASS             | 0 = PASS LED off<br>1 = PASS LED on                                             | R/W |

| 2   | FLB_A18_EN       | 1 = Flash write enabled and A18 is controllable                                 | R/W |

| 3*  | FLB_A18/reserve2 | Reads jumper J19 when FLB_A18_EN = 0 Flash BIOS address A18 when FLB_A18_EN = 1 | R/W |

| 4   | RESERVED         | Reserved                                                                        |     |

| 5   | BIOS_D0          | 1 = Enable UPPER on board BIOS area @D0000                                      | R/W |

| 6   | RESERVED         | Reserved                                                                        |     |

| 7   | RESERVED         | Reserved                                                                        |     |

Table 2-9 LED/BIOS Port Register Settings

### \*Note

A18, along with control ROM/RAM 15-17 are to be used to page the Flash when FLB A18 EN is asserted.

## Register 233h - Watchdog Timer Port

This register controls watchdog timer operation.

Table 2-10 Watchdog Timer Port Register Settings

| Bit | Signal    | Result                                |

|-----|-----------|---------------------------------------|

| 0   | RESERVED  | Reserved                              |

| 1   | RESERVED  | Reserved                              |

| 2   | RESERVED  | Reserved                              |

| 3   | RESERVED  | Reserved                              |

| 4   | WDOG_EN   | Enables the watchdog timer            |

| 5   | MRESET_EN | Timeout generates reset when asserted |

| 6   | WDOG_STS  | Watchdog timer status bit             |

| 7   | WDOG_CLR  | Clears the watchdog timer             |

## Register 234h - NVRAM and DiskOnChip Port

This register controls access to either the NVRAM or the *DiskOnChip* (DOC) component. Bits 7 and 8 also control the byte swapping on XVME-653/658 modules that are equipped with byte-swapping hardware. In XVME-653/30x modules without byte-swapping hardware, bits 7 and 8 are RESERVED.

Table 2-11 NVRAM and DiskOnChip Port Register Settings

| Bit | Signal            | Result                                                                                                              |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------|

| 0   | Control ROM/RAM15 | ROM address 15 - page control bit                                                                                   |

| 1   | Control ROM/RAM16 | ROM address 16 - page control bit                                                                                   |

| 2   | Control ROM/RAM17 | ROM address 17 - page control bit                                                                                   |

| 3   | DOC enable        | Enables DOC mode                                                                                                    |

| 4   | Range select 0    |                                                                                                                     |

| 5   | Range select 1    |                                                                                                                     |

| 6   | SWAPS             | 1 = No swapping (data invariant) occurs during Slave cycles (This byte can only be set for byte-swapping modules.)  |

| 7   | SWAPM             | 1 = No swapping (data invariant) occurs during Master cycles (This byte can only be set for byte-swapping modules.) |

The following ranges are defined by bits 4 and 5 in register 234h.

Table 2-12 Register 234h Defined Ranges

| Range Select Bits | Range       |

|-------------------|-------------|

| 00                | No range    |

| 01                | CC000-CFFFF |

| 10                | D0000-D7FFF |

| 11                | D8000-DFFFF |

## **Connectors**

This section provides the pinouts for the XVME-653/658 connectors. Refer to the EMC warning at the beginning of this manual before attaching cables.

## **Serial Port Connectors**

Table 2-13 Serial Port Connector Pinout

| COM1 |        |  |

|------|--------|--|

| Pin  | Signal |  |

| 1    | DCD1   |  |

| 2    | RXD1   |  |

| 3    | TXD1   |  |

| 4    | DTR1   |  |

| 5    | GND    |  |

| 6    | DSR1   |  |

| 7    | RTS1   |  |

| 8    | CTS1   |  |

| 9    | RI1    |  |

| COM2   |  |  |

|--------|--|--|

| Signal |  |  |

| DCD2   |  |  |

| RXD2   |  |  |

| TXD2   |  |  |

| DTR2   |  |  |

| GND    |  |  |

| DSR2   |  |  |

| RTS2   |  |  |

| CTS2   |  |  |

| RI2    |  |  |

|        |  |  |

### **Parallel Port Connector**

Table 2-14 Parallel Port Connector Pinout

| Pin | Signal | Pin | Signal   |

|-----|--------|-----|----------|

| 1   | STROBE | 14  | AUTOFEED |

| 2   | PDOUT0 | 15  | PERROR   |

| 3   | PDOUT1 | 16  | INIT     |

| 4   | PDOUT2 | 17  | SELIN    |

| 5   | PDOUT3 | 18  | GND      |

| 6   | PDOUT4 | 19  | GND      |

| 7   | PDOUT5 | 20  | GND      |

| 8   | PDOUT6 | 21  | GND      |

| 9   | PDOUT7 | 22  | GND      |

| 10  | PACK   | 23  | GND      |

| 11  | PBUSY  | 24  | GND      |

| 12  | PE     | 25  | GND      |

| 13  | SELECT |     |          |

### **USB Port Connector**

Table 2-15 USB Port Connector Pinout

| Pin | Signal |

|-----|--------|

| 1A  | +5V    |

| 2A  | USBP0- |

| 3A  | USBP0+ |

| 4A  | GND    |

| 1B  | +5V    |

| 2B  | USBP1- |

| 3B  | USBP1+ |

| 4B  | GND    |

## **VGA** Connector

Table 2-16 VGA Connector Pinout

| Pin | Signal     |

|-----|------------|

| 1   | RED        |

| 2   | GREEN      |

| 3   | BLUE       |

| 4   | NC         |

| 5   | GND        |

| 6   | GND        |

| 7   | GND        |

| 8   | GND        |

| 9   | 25MIL_VIDA |

| 10  | GND        |

| 11  | NC         |

| 12  | LDDCDAT    |

| 13  | HYSNC      |

| 14  | VSYNC      |

| 15  | LDDCCLK    |

# **Keyboard Port Connector**

Table 2-17 Keyboard Port Connector Pinout

| Pin | Signal |  |

|-----|--------|--|

| 1   | DATA   |  |

| 2   | NC     |  |

| 3   | GND    |  |

| 4   | +5V    |  |

| 5   | CLK    |  |

| 6   | NC     |  |

# **Auxiliary Connector**

The auxiliary port accepts a PS/2-compatible mouse, track ball, etc.

Table 2-18 Auxiliary Port Connector Pinout

| Pin | Signal |  |

|-----|--------|--|

| 1   | DATA   |  |

| 2   | NC     |  |

| 3   | GND    |  |

| 4   | VCC    |  |

| 5   | CLK    |  |

| 6   | NC     |  |

# **VMEbus Connectors**

P1 and P2 are the VMEbus connectors.

### **P1 Connector**

Table 2-19 P1 Connector Pinout

| Pin | Α        | В       | С         |

|-----|----------|---------|-----------|

| 1   | D00      | BBSY*   | D08       |

| 2   | D01      | BCLR*   | D09       |

| 3   | D02      | ACFAIL* | D10       |

| 4   | D03      | BG0IN*  | D11       |

| 5   | D04      | BG0OUT* | D12       |

| 6   | D05      | BG1IN*  | D13       |

| 7   | D06      | BG1OUT* | D14       |

| 8   | D07      | BG2IN*  | D15       |

| 9   | GND      | BG2OUT* | GND       |

| 10  | SYSCLK   | BG3IN*  | SYSFAIL*  |

| 11  | GND      | BG3OUT* | BERR*     |

| 12  | DS1*     | BR0*    | SYSRESET* |

| 13  | DS0*     | BR1*    | LWORD*    |

| 14  | WRITE*   | BR2*    | AM5       |

| 15  | GND      | BR3*    | A23       |

| 16  | DTACK*   | AM0     | A22       |

| 17  | GND      | AM1     | A21       |

| 18  | AS*      | AM2     | A20       |

| 19  | GND      | AM3     | A19       |

| 20  | IACK*    | GND     | A18       |

| 21  | IACKIN*  | NC      | A17       |

| 22  | IACKOUT* | NC      | A16       |

| 23  | AM4      | GND     | A15       |

| 24  | A07      | IRQ7*   | A14       |

| 25  | A06      | IRQ6*   | A13       |

| 26  | A05      | IRQ5*   | A12       |

| 27  | A04      | IRQ4*   | A11       |

| 28  | A03      | IRQ3*   | A10       |

| 29  | A02      | IRQ2*   | A09       |

| 30  | A01      | IRQ1*   | A08       |

| 31  | -12V     | NC      | +12V      |

| 32  | +5V      | +5V     | +5V       |

## **P2 Connector**

Table 2-20 P2 Connector Pinout

| Pin | Α       | В    | С                |

|-----|---------|------|------------------|

| 1   | +5V     | +5V  | HDBRSTDRV*       |

| 2   | +5V     | GND  | HDD0             |

| 3   | +5V     | RES  | HDD1             |

| 4   | RES     | VA24 | HDD2             |

| 5   | RES     | VA25 | HDD3             |

| 6   | RES     | VA26 | HDD4             |

| 7   | RES     | VA27 | HDD5             |

| 8   | RES     | VA28 | HDD6             |

| 9   | RES     | VA29 | HDD7             |

| 10  | RES     | VA30 | HDD8             |

| 11  | RES     | VA31 | HDD9             |

| 12  | RES     | GND  | HDD10            |

| 13  | RES     | +5V  | HDD11            |

| 14  | RES     | VD16 | HDD12            |

| 15  | RES     | VD17 | HDD13            |

| 16  | RES     | VD18 | HDD14            |

| 17  | RES     | VD19 | HDD15            |

| 18  | RES     | VD20 | GND              |

| 19  | GND     | VD21 | HDIOW*           |

| 20  | FRWC*   | VD22 | HDIOR*           |

| 21  | IDX*    | VD23 | HDIORDY          |

| 22  | MO0*    | GND  | +5V (10K pullup) |

| 23  | HDRQ0   | VD24 | IRQ14            |

| 24  | FDS0*   | VD25 | RES              |

| 25  | HDACK0* | VD26 | DA0              |

| 26  | FDIRC*  | VD27 | DA1              |

| 27  | FSTEP*  | VD28 | DA2              |

| 28  | FWD*    | VD29 | CS1P*            |

| 29  | FWE*    | VD30 | CS3P*            |

| 30  | FTK0*   | VD31 | RES              |

| 31  | FWP*    | GND  | FHS*             |

| 32  | FRDD*   | +5V  | DCHG*            |

# Interboard Connector 1 (P4)

Table 2-21 Interboard Connector 1 Pinout

| Pin | Signal   | Pin | Signal   |

|-----|----------|-----|----------|

| 1   | SYSCLK   | 41  | SA10     |

| 2   | OSC      | 42  | SA11     |

| 3   | SD(15)   | 43  | SA12     |

| 4   | SD(14)   | 44  | SA13     |

| 5   | SD(13)   | 45  | SA14     |

| 6   | SD(12)   | 46  | SA15     |

| 7   | SD(11)   | 47  | SA16     |

| 8   | SD(10)   | 48  | SA17     |

| 9   | SD(9)    | 49  | SA18     |

| 10  | SD(8)    | 50  | SA19     |

| 11  | MEMW*    | 51  | BALE     |

| 12  | MEMR*    | 52  | TC       |

| 13  | DRQ5     | 53  | DACK2*   |

| 14  | DACK5*   | 54  | IRQ3     |

| 15  | DRQ6     | 55  | IRQ4     |

| 16  | DACK6*   | 56  | SBHE*    |

| 17  | LA17     | 57  | IRQ5     |

| 18  | LA18     | 58  | IRQ6     |

| 19  | LA19     | 59  | IRQ7     |

| 20  | LA20     | 60  | REF*     |

| 21  | LA21     | 61  | DRQ1     |

| 22  | LA22     | 62  | DACK1*   |

| 23  | LA23     | 63  | RESETDRV |

| 24  | IRQ14    | 64  | IOW*     |

| 25  | IRQ15    | 65  | IOR*     |

| 26  | IRQ12    | 66  | SMEMW*   |

| 27  | IRQ11    | 67  | AEN      |

| 28  | IRQ10    | 68  | SMEMR*   |

| 29  | IOCS16*  | 69  | IOCHRDY  |

| 30  | MEMCS16* | 70  | SD0      |

| 31  | SA0      | 71  | SD1      |

| 32  | SA1      | 72  | SD2      |

| 33  | SA2      | 73  | SD3      |

| 34  | SA3      | 74  | SD4      |

| 35  | SA4      | 75  | SD5      |

| 36  | SA5      | 76  | SD6      |

| 37  | SA6      | 77  | SD7      |

| 38  | SA7      | 78  | DRQ2     |

| 39  | SA8      | 79  | IRQ9     |

| 40  | SA9      | 80  | IOCHCK*  |

# Interboard Connector 2 (P3)

This connector provides power through the center pins.

Table 2-22 Interboard Connector 2 Pinout

| Pin | Signal               | Pin | Signal  |

|-----|----------------------|-----|---------|

| 1   | TCLK                 | 41  | AD23    |

| 2   | TRST*                | 42  | AD22    |

| 3   | TMS                  | 43  | AD21    |

| 4   | TDO                  | 44  | AD20    |

| 5   | TDI                  | 45  | AD19    |

| 6   | PCI-RSVD9A (Pn2-8)   | 46  | AD18    |

| 7   | PCI-RSVD10B (Pn2-9)  | 47  | AD17    |

| 8   | PCI-RSVD11A (Pn2-10) | 48  | AD16    |

| 9   | PCI-RSVD14A (Pn1-12) | 49  | BE2*    |

| 10  | PCI-RSVD14B (Pn1-10) | 50  | FRAME*  |

| 11  | PCI-RSVD19A (Pn2-17) | 51  | IRDY*   |

| 12  | PMC-RSVD_Pn2-34      | 52  | TRDY*   |

| 13  | PMC-RSVD_Pn2-52      | 53  | DEVSEL* |

| 14  | PMC-RSVD_Pn2-54      | 54  | STOP*   |

| 15  | PCICLK3              | 55  | PLOCK*  |

| 16  | PIRQA*               | 56  | PERR*   |

| 17  | PIRQB*               | 57  | SDONE   |

| 18  | PIRQC*               | 58  | SBO*    |

| 19  | PIRQD*               | 59  | SERR*   |

| 20  | REQ3*                | 60  | PAR     |

| 21  | PCICLK2              | 61  | BE1*    |

| 22  | REQ1*                | 62  | AD15    |

| 23  | GNT3*                | 63  | AD14    |

| 24  | PCICLK1              | 64  | AD13    |

| 25  | GNT1*                | 65  | AD12    |

| 26  | PCIRST*              | 66  | AD11    |

| 27  | PCICLK0              | 67  | AD10    |

| 28  | GNT0*                | 68  | AD9     |

| 29  | REQ0*                | 69  | AD8     |

| 30  | REQ2*                | 70  | BE0*    |

| 31  | AD31                 | 71  | AD7     |

| 32  | AD30                 | 72  | AD6     |

| 33  | AD29                 | 73  | AD5     |

| 34  | AD28                 | 74  | AD4     |

| 35  | AD27                 | 75  | AD3     |

| 36  | AD26                 | 76  | AD2     |

| 37  | AD25                 | 77  | AD1     |

| 38  | AD24                 | 78  | AD0     |

| 39  | BE3*                 | 79  | ACK64*  |

| 40  | GNT2*                | 80  | REQ64*  |

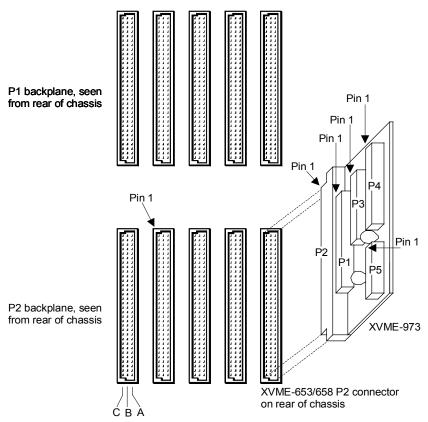

## Installing the XVME-653/658 into a Backplane

This section provides the information necessary to install the XVME-653/658 into the VMEbus backplane. The XVME-653/658 is a double-high, single board VMEbus module that occupies one VMEbus slot.

#### **Note**

Xycom Automation XVME modules are designed to comply with all physical and electrical VMEbus backplane specifications.

### Caution

Do not install the XVME-653/658 on a VMEbus system without a P2 backplane.

### Warning

Never install or remove any boards before turning off the power to the bus and all related external power supplies.

- 1. Disconnect all power supplies to the backplane and the card cage. Disconnect the power cable.

- 2. Make sure backplane connectors P1 and P2 are available.

- 3. Verify that all jumper settings are correct.

- 4. Verify that the card cage slot is clear and accessible.

- 5. Install the XVME-653/658 in the card cage by centering the unit on the plastic guides in the slots (P1 connector facing up). Push the board slowly toward the rear of the chassis until the P1 and P2 connectors engage. The board should slide freely in the plastic guides.

### Caution

Do not use excessive force or pressure to engage the connectors. If the boards do not properly connect with the backplane, remove the module and inspect all connectors and guide slots for damage or obstructions.

- 6. Secure the module to the chassis by tightening the machine screws at the top and bottom of the board.

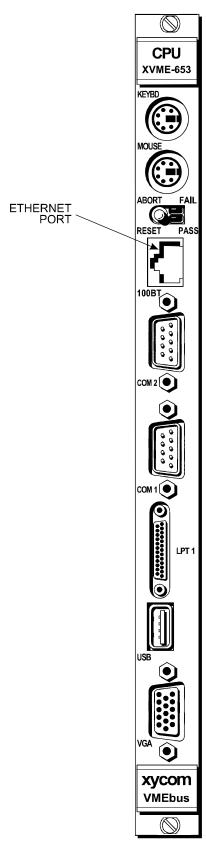

- 7. Connect all remaining peripherals by attaching each interface cable into the appropriate connector on the front of the XVME-653/658 board as shown in Table 2-23.

- 8. Turn on power to the VMEbus card cage.

Table 2-23 Front Panel Connector Labels

| Connector       | Label        |

|-----------------|--------------|

| Keyboard        | KEYBD        |

| Mouse           | MOUSE        |

| Ethernet cable  | 100BT        |

| Serial devices  | COM 1, COM 2 |

| Parallel device | LPT1         |

| USB cable       | USB          |

| Display cable   | VGA          |

### Note

The floppy drive and hard drive are either cabled across P2 to the XVME-977 disk unit, or they are connected to the XVME-973/1 board. Refer to Chapter 5 for more information on the XVME-973/1.

Figure 2-3 illustrates the XVME-653/658 front panel, to help you locate connectors.

Figure 2-3 XVME-653/658 Front Panel

# **Enabling the PCI Ethernet Controller**

The XVME-653/658 incorporates a high-performance 32-bit PCI bus mastering Ethernet controller.

### **Loading the Ethernet Driver**

To enable the Ethernet controller, you must load the applicable Ethernet driver for your operating system. Refer to the READMEFIRST.TXT file on the Intel 558 Ethernet Drivers disk for installation instructions. For best results, always use the supplied drivers.

### Pinouts for the RJ-45 10/100 BaseT Connector

| Pin | Signal |  |

|-----|--------|--|

| 1   | TX+    |  |

| 2   | TX-    |  |

| 3   | RX+    |  |

| 4   | GND    |  |

| 5   | GND    |  |

| 6   | RX-    |  |

| 7   | GND    |  |

| 8   | GND    |  |

Table 2-24 RJ-45 10/100 BaseT Connector Pinout

# Using a DiskOnChip

The *DiskOnChip* device is a self-contained solid-state disk drive that is packaged in a 32-pin device. It can be plugged into the onboard SRAM/Flash socket.

Perform the following steps to configure the XVME-653/658 to use a *DiskOnChip*:

- 1. Plug the *DiskOnChip* into socket U9 on the CPU module. Be sure the direction is correct (pin 1 of the *DiskOnChip* is aligned with pin 1 of the socket).

- 2. Turn on the system and enter the BIOS setup menus. (See Chapter 3 for information on accessing the BIOS setup menus.)

- 3. Select the Advanced menu option from the BIOS Setup main screen.

- 4. Select the Integrated peripherals option.

- 5. Select the 32-pin ROM site option.

- 6. Set the 32-pin ROM site type to DiskOnChip.

- 7. Set the 32-pin ROM site address to the desired value.

- 8. Exit the BIOS setup menus and reboot the system.

If the *DiskOnChip* is the only drive in the system, it will appear as the first disk (drive C: in DOS). If there are other drives in the system, the *DiskOnChip* will appear by default as the last drive, unless it is programmed as the first drive.

If you want the *DiskOnChip* to be bootable, copy the operating system files into it using the standard DOS command (for example *sys d*).

The *DiskOnChip* works with MS-DOS, Windows 3.11, and Windows NT. To fit a version of Windows NT onto the *DiskOnChip* (72 MB minimum), reduce the size of the Windows NT space requirement with a utility such as VenturCom *Component Integrator*<sup>TM</sup>. If you use another operating system, please visit the M-Systems web site at <a href="https://www.m-sys.com">www.m-sys.com</a> or contact Xycom Automation Application Engineering at 734-429-4971.

# **Chapter 3 – BIOS Setup Menus**

The XVME-653/658 customized BIOS is designed to surpass the functionality provided for normal PCs. This custom BIOS allows you to access the value-added features on the XVME-653/658 module without interfacing to the hardware directly.

# **Getting to the BIOS Setup Menus**

If the setup prompt is disabled on your system (the default setting) press F2 repeatedly after the memory tests and before your system loads the operating system in order to access the main menu.

If the setup prompt is enabled on your system, the BIOS displays the following message: *Press F2 to enter Setup*. Once this message appears, press F2 to access the main menu.

The BIOS Main Setup Menu is shown on the next page.

# Moving through the Menus

General instructions for navigating through the screens are described below:

| Key                                      | Result                                               |  |  |

|------------------------------------------|------------------------------------------------------|--|--|

| F1 or ALT-H                              | Accesses the general Help window                     |  |  |

| ESC                                      | Exits the menu                                       |  |  |

| $\leftarrow$ or $\rightarrow$ arrow keys | Selects a different menu                             |  |  |

| ↑ or ↓ arrow keys                        | Moves the cursor up or down                          |  |  |

| TAB or SHIFT-TAB                         | Cycles the cursor up or down                         |  |  |

| HOME or END                              | Moves the cursor to the top or bottom of the window  |  |  |

| PGUP or PGDN                             | Moves the cursor to the next or previous page        |  |  |

| F5 or -                                  | Selects the previous value for the field             |  |  |

| F6 or + or SPACE                         | Selects the next value for the field                 |  |  |

| F9                                       | Loads the default configuration values for the menu  |  |  |

| F10                                      | Loads the previous configuration values for the menu |  |  |

| ENTER                                    | Executes the Command or Selects a → Submenu          |  |  |

To select an item, use the arrow keys to move the cursor to the field you want. Then use the TAB, SHIFT-TAB, or ENTER keys to select a subfield, if any. Then use the + and – keys or the F5 and F6 keys to select a value for that field. The **Save Changes** commands in the **Exit Menu** save the values currently displayed in all the menus.

To display a submenu, use the arrow keys to move the cursor to the submenu you want. Then press ENTER. A triangle bullet ( • ) indicates a submenu.

# **BIOS Main Setup Menu**

| Main Advan             | ced Security   | VMEbus | Exit                                 |

|------------------------|----------------|--------|--------------------------------------|

|                        |                |        | Item Specific Help                   |

| System Time:           | [16:19:20]     |        |                                      |

| System Date:           | [03/02/95]     |        |                                      |

| Diskette A:            | [1.44 MB, 3½"] |        | If the line item you are viewing     |

| ▶ IDE Adapter 0 Master | (C: 260 Mb)    |        | has specific help, it will be listed |

| ▶ IDE Adapter 0 Slave  | (D:105 Mb)     |        | here.                                |

| IDE Adapter 1 Master   | (None)         |        |                                      |

| IDE Adapter 1 Slave    | (None)         |        |                                      |

| Video System:          | [EGA/VGA]      |        |                                      |

| Memory Cache           |                |        |                                      |

| ▶ Memory Shadow        |                |        |                                      |

| • Boot sequence:       | [A: then C:]   |        |                                      |

| Numlock:               | [Auto]         |        |                                      |

|                        |                |        |                                      |

| System Memory:         | 640 KB         |        |                                      |

| Extended Memory:       | 63 MB          |        |                                      |

|                        |                |        |                                      |

$\longleftrightarrow$  Select Menu Enter Select  $\blacktriangleright$  Submenu F10 Previous Values

Figure 3-1 Main Setup Menu

### **Note**

IDE Adapter 1 (the secondary IDE controller) is not available to the XVME-653/658.

ESC Exit

Table 3-1 Main Setup Menu Options

| Option                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Time (HH/MM/SS)   | Sets the real-time clock for hour, minute, and seconds. The hour is calculated according to the 24 hour military clock (i.e., 00:00:00 through 23:59:59). Use TAB to move right and SHIFT-TAB to move left. The ENTER key may be used to move from one field to the next. The numeric keys, 0-9, are used to change the field values. The F6 and the + keys may also be used to increment the values, while the F5 and the – keys may be used to decrement them. It is not necessary to enter the seconds or type zeros in front of numbers. |

| System Date (MM:DD:YYYY) | Sets the real-time clock for the month, day, and year. Use TAB to move right and SHIFT-TAB to move left. The ENTER key may be used to move from one field to the next. The numeric keys, 0-9, are used to change the field values. The F6 and the + keys may also be used to increment the values, while the F5 and the – keys may be used to decrement them. It is not necessary to type zeros in front of numbers.                                                                                                                         |

| Diskette A or B          | Selects the floppy disk drive installed in your system. The XVME-653/658 can only support one floppy drive (Drive A).                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Video System             | Selects the default video device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| System Memory            | Displays the amount of conventional memory detected during bootup. This field is not user configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Extended Memory          | Displays the amount of extended memory detected during bootup. This field is not user configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# **IDE Adapter 0 Master and Slave Submenus**

The IDE Adapter 0 Master and Slave submenus are used to configure IDE hard drive information. If only one drive is attached to the IDE adapter, then only the parameters in the Master Submenu need to be entered. If two drives are connected, both Master and Slave Submenu parameters will need to be entered. The Master and Slave Submenus contain the same information.

| PhoenixBIOS Setup-Copyright 1985-95 Phoenix Technologies Ltd. |                        |                                      |  |

|---------------------------------------------------------------|------------------------|--------------------------------------|--|

| Main                                                          |                        |                                      |  |

| IDE Adapter 0                                                 | Master (C: 850 Mb)     | Item Specific Help                   |  |

| Autotype Fixed Disk:                                          | [Press Enter]          |                                      |  |

| Type:                                                         | [User] 850 Mb          |                                      |  |

| Cylinders:                                                    | [1647]                 | If the line item you are viewing     |  |

| Heads:                                                        | [ 16]                  | has specific help, it will be listed |  |

| Sectors/Track:                                                | [ 63]                  | here.                                |  |

| Write Precomp:                                                | [None]                 |                                      |  |

|                                                               |                        |                                      |  |

| Multi-Sector Transfers:                                       | [8 Sectors]            |                                      |  |

| LBA Mode Control:                                             | [Enabled]              |                                      |  |

| 32 Bit I/O:                                                   | [Disabled]             |                                      |  |

| Transfer Mode:                                                | [Standard]             |                                      |  |

|                                                               |                        |                                      |  |

| F1 Help $\uparrow\downarrow$ Select                           | Item -/+ Change Values | F9 Setup Defaults                    |  |

Figure 3-2 IDE Adapter Submenu

Enter Select ▶ Submenu

F10 Previous Values

$\longleftrightarrow$  Select Menu

ESC Exit

Table 3-2 IDE Adapter Submenu Options

| Option                 | Description                                                                                                                                                                                                                                                                                      |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Autotype Fixed Disk    | Reads the hard disk parameters from the drive if you press ENTER. It then sets the Type field to User and lets you edit the other fields. Do not attempt to manually set the disk drive parameters unless instructed to do so by Xycom Application Engineering.                                  |

| Туре                   | Options include 1 to 39, User, or Auto. The 1 to 39 option fills in all remaining fields with values for predefined disk type. User prompts you to fill in remaining fields. Auto autotypes at each boot, displays settings in setup menus, and does not allow you to edit the remaining fields. |

| Cylinders              | Indicates the number of cylinders on the hard drive. This information is automatically entered if the Autotype Fixed Disk option is set.                                                                                                                                                         |

| Heads                  | Indicates the number of read/write heads on the hard drive. This information is automatically entered if the Autotype Fixed Disk option is set.                                                                                                                                                  |

| Sectors/Track          | Indicates the number of sectors per track on the hard drive. This information is automatically entered if the Autotype Fixed Disk option is set.                                                                                                                                                 |

| Write Precomp          | This value is not used or required by IDE hard drives.                                                                                                                                                                                                                                           |

| Multi-Sector Transfers | Sets the number of sectors per block. Options are <i>Auto</i> , 2, 4, 8, or 16 sectors. <i>Auto</i> sets the number of sectors per block to the highest number supported by the drive.                                                                                                           |

| LBA Mode Control       | Enables Logical Block Access. The default ( <i>Disabled</i> ) should work with most hard drives.                                                                                                                                                                                                 |

| 32 Bit I/O             | Enables 32-bit communication between CPU and IDE interface.                                                                                                                                                                                                                                      |

| Transfer Mode          | Selects the method for transferring the data between the hard disk and system memory. Available options are determined by the drive type and cable length.                                                                                                                                       |

## **Memory Cache Submenu**

Enabling cache increases CPU performance by holding data most recently accessed in a special high-speed static RAM area called cache. The XVME-653/658 provides two levels of cache memory; level one is internal to the CPU (see **CPU Chip** on p. 1-2), and level two (external cache) is 512 KB of high-speed cache memory.

| PhoenixBIOS Se                | tup-Copyright 1985-95 Phoenix Techn | nologies Ltd.                        |  |  |

|-------------------------------|-------------------------------------|--------------------------------------|--|--|

| Main                          |                                     |                                      |  |  |

| Memory Cache Item Specific He |                                     |                                      |  |  |

| External Cache:               | [Enabled]                           |                                      |  |  |

| Cache System BIOS area:       | [Enabled]                           |                                      |  |  |

| Cache Video BIOS area:        | [Enabled]                           | If the line item you are viewing     |  |  |

|                               |                                     | has specific help, it will be listed |  |  |

| Cache Memory Region           |                                     | here.                                |  |  |

| CC00-CFFF:                    | [Disabled]                          |                                      |  |  |

| D000-D3FF:                    | [Disabled]                          |                                      |  |  |

| D400-D7FF:                    | [Disabled]                          |                                      |  |  |

| D800-DBFF                     | [Disabled]                          |                                      |  |  |

| DC00-DFFF:                    | [Disabled]                          |                                      |  |  |

|                               |                                     |                                      |  |  |

|                               |                                     |                                      |  |  |

|                               |                                     | l                                    |  |  |

F1 Help  $\uparrow\downarrow$  Select Item -/+ Change Values F9 Setup Defaults ESC Exit  $\longleftrightarrow$  Select Menu Enter Select  $\blacktriangleright$  Submenu F10 Previous Values

Figure 3-3 Memory Cache Submenu

Table 3-3 Memory Cache Submenu Options

| Option                 | Description                                                                                                                                                                                                                                           |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External Cache         | Controls the state of external cache memory. The system BIOS automatically disables external cache if it is not installed. The default is <i>Enabled</i> .                                                                                            |

| Cache System BIOS Area | Allows the system BIOS memory area to be cached if <i>Enabled</i> . Enabling also increases system performance. The default is <i>Enabled</i> .                                                                                                       |

| Cache Video BIOS Area  | Allows the video BIOS memory area to be cached if <i>Enabled</i> . Enabling also increases system performance. The default is <i>Enabled</i> .                                                                                                        |

| Cache Memory Region    | Caches the corresponding memory when <i>Enabled</i> . Memory in this area is usually extended BIOS or AT-bus memory. Enabling cache may increase system performance, depending on how the extended BIOS is accessed. The default is <i>Disabled</i> . |

# **Memory Shadow Submenu**

The summary screen displays the amount of shadow memory in use. Shadow memory is used to copy system and/or video BIOS into RAM to improve performance. The XVME-653/658 displays the number of KB allocated to Shadow RAM on the summary screen. The System Shadow field, which is not editable, is for reference only.

The XVME-653/658 is shipped with both the system BIOS and video BIOS shadowed.

| PhoenixBIOS Setup-Copyright 1985-95 Phoenix Technologies Ltd. |                                      |                        |                                                                             |  |  |

|---------------------------------------------------------------|--------------------------------------|------------------------|-----------------------------------------------------------------------------|--|--|

| Main                                                          |                                      |                        |                                                                             |  |  |

|                                                               | Memory Shadow                        |                        | Item Specific Help                                                          |  |  |

| System Shadow: Video Shadow: Regions with Legacy              | Enabled<br>Enabled<br>Expansion Roms |                        | If the line item you are viewing has specific help, it will be listed here. |  |  |

| F1 Help ↑↓                                                    | Select Item                          | -/+ Change Values      | F9 Setup Defaults                                                           |  |  |

| ESC Exit $\longleftrightarrow$                                | Select Menu                          | Enter Select ▶ Submenu | F10 Previous Values                                                         |  |  |

Figure 3-4 Memory Shadow Submenu

Table 3-4 Memory Shadow Submenu Options

| Option                             | Description                                                 |

|------------------------------------|-------------------------------------------------------------|

| System Shadow                      | Permanently Enabled.                                        |

| Video Shadow                       | Permanently Enabled.                                        |

| Regions with Legacy Expansion ROMs | Regions are listed below the header if detected by the BIOS |

# **Boot Sequence Submenu**

This menu allows the boot sequence to be configured.

| Phoer           | nixBIOS Setup-Copyright 1985-95 Pho | penix Technologies Ltd.              |

|-----------------|-------------------------------------|--------------------------------------|

| Main            |                                     |                                      |

|                 | Boot Sequence                       | Item Specific Help                   |

|                 |                                     |                                      |

| Previous Boot:  | [Disabled]                          |                                      |

| Boot sequence:  | [A: then C:]                        |                                      |

| SETUP Prompt:   | [Disabled]                          | If the line item you are viewing     |

| POST Errors:    | [Enabled]                           | has specific help, it will be listed |

| Floppy check:   | [Disabled]                          | here.                                |

| Summary screen: | [Enabled]                           |                                      |