SECTION 1: SPECIFICATIONS

#### 1.0 GENERAL

The DCE is a multifunction VME bus interface board that consists of two separate controllers. One controller is a standard 712. The other controller is a Xylogics Model 732 Disk Controller that couples two floppy disk drives and one QIC02 tape drive to VMEbusl systems.

# 1.1 USING THIS MANUAL

This manual describes the 732 floppy/QIC02 controller. Section 2 describes how to install and test the 732; Section 3 describes the 732 registers; Section 4 describes the IOPBs; and Section 5 describes the 732 commands. Section 6 describes error processing; Section 7 is a programming tutorial; Section 8 explains the 732's special functions; Section 9 describes the 732 theory of operation; and Section 10 includes maintenance aides.

# 1.1.1 Abbreviations

This manual uses the following mnemonics:

| AIO<br>AIOP<br>AIOR<br>AM<br>ASR<br>AUD<br>BHT<br>CHEN<br>CHEN<br>CMPL<br>CRIO<br>CRBS<br>CTYP<br>DFLT | Add New IOPB<br>AIO Pending<br>AIO Response Time<br>Address Modifier<br>Automatic Seek Retry<br>Auto-update<br>Black Hole Transfer<br>Chain Enable<br>Command Complete<br>Clear Remove IOPB<br>Clear Register Busy<br>Controller Type<br>Drive Fault |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFLT<br>DMA<br>DRDY                                                                                    | Drive Fault<br>Direct Memory Access<br>Drive Ready                                                                                                                                                                                                   |

|                                                                                                        |                                                                                                                                                                                                                                                      |

1. VMEbus is a trademark of the VMEbus International Trade Association.

Rev. A. February 11, 1987

1.1.1 Abbreviations (continued)

| EDT    | Enable DMA Timeout                         |

|--------|--------------------------------------------|

| ERRS   | Error Summary                              |

| FERR   | Fatal Error                                |

| FIFO   | First In/First Out Disk Data Buffer        |

| Н      | Notation For Numerical Values Expressed in |

|        | Hexadecimal                                |

| ICS    | IOPB Checksum                              |

| IEC    | Interrupt At End Of Chain                  |

| IOPB   | Input/Output Parameter Block               |

| MBS    | Megabytes Per Second                       |

| MMA    | Maintenance Mode Active                    |

| MM     | Maintenance Mode                           |

| NPRM   | Non-privileged Register Mode               |

| ovs    | Overlap Seek Enable                        |

| PNUM   | Prom Number                                |

| PRIO   |                                            |

| PSEL   |                                            |

| RBS    |                                            |

| REGCEL | Register Read/Write and Interrupt          |

| RIO    | Remove IOPB                                |

| RMM    |                                            |

| ROR    |                                            |

| SGM    | Scatter/Gather Mode                        |

|        | Seek Error                                 |

| TDT    | Throttle Dead Time                         |

|        | Throttle                                   |

| TMOD   | Transfer Mode                              |

| VMEDMA | Direct Memory Access Controller Chip       |

| WRPT   | Write-protect                              |

# 1.2 DESIGN RELIABILITY

Xylogics implements the following features to minimize the likelihood of product failure:

- o Design for worst case voltage and temperature.

- o Extensive evaluation testing.

- o Low parts count through extensive use of custom LSI.

- o Buffer parity for continuous error checking.

- 1.2 DESIGN RELIABILITY (continued)

- o Low-stress design on all components.

- o All components burned-in.

- o One card; resides in backplane or expansion chassis.

- Controller is power-cycled under thermal stress during test.

- 1.3 PHYSICAL

- PACKAGING -- The 732 completely resides on part one printed circuit board.

- DIMENSIONS -- The DCE is a Honeywell special size board.

CONNECTORS -- All connectors are on the edge of the board facing out.

# 1.4 ENVIRONMENTAL

The 732 environmental requirements are 0 - 55xC, with a maximum relative humidity of 90% (without condensation). Air flow across the board must maintain a maximum temperature differential of 7xC to prevent hot spots.

#### 1.5 ELECTRICAL

POWER -- The 732 uses ? amperes at +5 volts DC (VDC).

TOLERANCE -- Voltage must be within plus or minus five percent (4.75 to 5.25).

GROUNDING -- Common earth ground must be established between the disk drives and the CPU chassis, backplane, and expansion cabinets.

# Rev. A. February 11, 1987

# 1.6 SYSTEM RELATED SPECIFICATIONS

DATA BUFFERING -- The 732 has a FIFO buffer that is 8k-bytes long and incorporates parity error detection. Data can be put into one end of the FIFO and simultaneously removed at the other end; there are no delays associated with filling and emptying the buffer.

FORMAT -- The 732 Format command formats a specified number of tracks. Standard interleaving is 1:1.

STATUS LEDs -- The 732 implements two status LEDs. L1 (BSY) indicates the controller is active; L2 (ERR) indicates the on-board diagnostics did not complete successfully, or a fatal error occurred.

SCATTER/GATHER -- The 732 supports Scatter/Gather on Read and Write commands. The controller can gather data from various memory locations and transfer it to the buffer for use in a Write command; it can scatter the data out from the disk drive to the appropriate memory locations with a Read command. To execute a scatter/gather, software issues a normal Read or Write command along with a DMA list that contains a memory address and the number of words to transfer to/from that location. The smallest granularity of scatter/gather is a 16-bit word.

MULTIPLE IOPBS -- The 732 can store up to 15 IOPB's for processing, but only one will be active at any instant in time. Both the DMA data transfer and the drive activity must be completed before the next IOPB is started.

ERROR DETECTION -- The 732 supports a 16-bit data CRC on the floppy drives. The QIC02 tape drive formatter has its own error correction system.

BLACK HOLE TRANSFERS -- The 732 may transfer all the DMA data into the same bus address without incrementing the address at each DMA.

SOFTWARE SUPPORT -- Sample software driver supplied for use in UNIX2 (5.0) based systems (source included).

Rev. A2. June 17, 1987

#### 1.7 DISK DRIVE RELATED SPECIFICATIONS

PHYSICAL DRIVE INTERFACE -- The 732 supports the high density floppy disk drive.

INTERFACE DATA RATE AND STANDARD INTERLEAVE FACTOR -- The 732 supports a maximum disk data rate of 500 kilo bit per second (MBS). The 732 supports this data rate at a 1:1 interleave factor.

NUMBER OF DISK DRIVES -- The 732 supports up to two floppy disk drives.

DISK SECTOR FORMAT -- The 732 sector format includes a header field separated from a data field by a splice area.

HEADER FORMAT -- The header format is the industry standard 5.25" floppy format as generated by the WD37C65 controller chip.

CABLING -- The 732 uses standard 34 pin flat ribbon cable. The maximum length of each cable is 3 meters (9.8 feet).

#### 1.8 QIC02 TAPE DRIVE RALATED SPECIFICATIONS

TAPE INTERFACE -- QIC02 formatted interface

TAPE DATA TRANSFER RATE -- The 732 supports tape drive data trasfer rates of up to 1 Megabyte per second. Typical QIC02 tape drives average data rates are 85 Kilo bytes per second.

NUMBER OF TAPE DRIVES -- Only one tape drive is supported. It is addressed as unit 4 and selects drive number 1.

INSTRUCTION SET -- The QIC02 standard instruction set is supported.

HARDWARE INTERFACE -- The standard QICO2 interface will be used except that all the receivers that are normally terminated with 150 to +5 will be terminated with 330 to +5 volts and 470 to 0 volts.

5

2. UNIX is a trademark of AT&T.

Rev. A. February 11, 1987

1.9 VMEbus RELATED SPECIFICATIONS

VME COMPLIANCE NUMBER -- IEEE P1014/D1.0.

TRANSFER MODE -- Direct Memory Access (DMA).

DMA THROTTLE CONTROL -- Each time the 732 becomes bus master, it executes DMA transfers to or from the buffer up to the max throttle limit or the number of bytes/spaces available in the buffer.

DMA DATA TRANSFER RATE -- The 732 transfers data at a rate of up to 10 MBS; this rate requires Longword mode transfers and system memory that responds within 200 nanoseconds.

DMA DEAD TIME -- The 732 supports a programmable throttle dead time between throttle bursts. This prevents the 732 from taking over the bus and allows time for other DMA devices to access the bus.

DATA TRANSFER LIMIT -- Data transfer length, from 1 to 65,535 sectors with a single IOPB.

BUS COMPATIBILITY -- The 732 is compatible with the standard VMEbus.

ADDRESSING CAPABILITY -- The 732 supports Master A32, and Slave Al6, as per the VMEbus Specification Manual. As a slave, the 732 responds to Address Modifiers 29H and 2DH.

DATA WIDTH -- The 732 supports D16 and D32 as per the VMEbus Specification Manual. The 732 transfers one byte, one word, or a byte and a word, until the transfer aligns with a word or longword boundary.

RELEASE ON REQUEST -- The 732 releases the bus at the request of other peripheral devices.

RELEASE WHEN DONE -- The 732 releases the bus after each bus access.

BUS REQUEST LEVELS -- The 732 supports four bus request levels.

EARLY RELEASE OF BUS BUSY/ -- The 732 does not support early release of Bus Busy/.

1.9 VMEbus RELATED SPECIFICATIONS (Continued)

INTERRUPT PRIORITY -- Software programmable interrupt level and vector.

CONTROLLER I/O PARAMETER BLOCK (IOPB) LENGTH -- 30 bytes.

CONTROLLER REGISTERS -- Seven 8-bit I/O Registers; byte or word addressable. Only eight bits respond during word access.

DIAGNOSTIC SUPPORT -- Comprehensive set of stand-alone diagnostics written in 'C' are available.

#### 1.10 SOFTWARE RELATED SPECIFICATIONS

SOFTWARE INTERFACE -- The 732 supports a high level software interface that allows host software to use the same method to add IOPBs to a chain while the controller is busy or while it is free.

1.10.1 Software Interface

The software interface includes seven byte-wide registers. Four of these bytes comprise the VME Address Register, the fifth byte is the Address Modifier Register, and the sixth byte is the Control and Status Register (CSR). The CSR includes two bits that are very important to IOPB processing: Add IOPB (AIO) and Remove IOPB (RIO). The last byte is the Fatal Error Register; the 732 returns the fatal error codes in this register.

The IOPB is a block of command and status information; it includes the disk address, the bus address, and the type of operation to be performed. The software driver sets up the IOPB in user memory, sends the IOPB address to the VME Address Registers, and sets AIO. After the 732 receives the IOPB address it resets AIO. The 732 then performs the IOPB function and, upon completion or error, updates the IOPB status and sets RIO. The VME Address Registers point to the complete IOPB; the software driver reads the address and then resets RIO.

Software may add IOPBs to the queue, providing AIO is reset, by writing the IOPB address to the address registers and setting AIO (regardless of the 732's busy status).

- 1.11 PROGRAMMABLE FEATURES

- o Software Controlled Interrupt or Polled Operations.

- o Software Programmable DMA Parameters.

- Software Programmable Drive Size Parameters (Including Sector Size).

- Software Programmable Sector Interleaving --Standard 1:1.

- o Software Controlled Register Response.

- o Software Controlled Transfer Retry/Correction.

- o Software Programmable Hard or Soft Sector Mode.

1.12 COMPONENT SPECIFICATION

All components used on the 732 will be approved by Honeywell.

No 74S or 74AS parts will be used except for the 74AS286's FIFO parity generator/checker.

SECTION 2: INSTALLING AND TESTING THE 732

2.0 GENERAL

This secion describes how to unpack, configure, install, and test your 732 controller.

2.1 UNPACKING AND INSPECTION

2.1.1 Inspect the Shipping Carton

Inspect the carton for possible shipping damage. If you determine there is damage, do not unpack the unit. Notify Xylogics and the freight carrier immediately.

If no damage is visible, carefully unpack the 732. Save the carton and other packing material for possible later use.

2.1.2 Contents

The 732 is a single printed circuit board. Optional items include a manual and/or software on a floppy diskette, or + inch magnetic tape.

If any items are missing or damaged, please contact Xylogics at one of the following telephone numbers.

United States: (617) 272-8140 United Kingdom (Milton Keynes): 0044-908-569444

2.1.3 Handling Precautions

Observing proper handling precautions minimizes the risk of damaging the 732 with electrostatic discharge. When transporting the 732, use an antistatic bag, antistatic bin, or the original shipping carton and packing material. Personnel handling the 732 should observe proper grounding methods including, but not limited to, wrist bands, heel straps, and antistatic mats.

Rev. Al. February 11, 1987

# 2.1.4 Inspect the 732

Inspect the 732 for socketed parts that may have loosened during shipment. Assure that all parts are firmly seated in their sockets. If any parts must be reinserted, observe proper orientation.

# 2.2CONFIGURING THE 732

You can configure the 732 with several jumper options. The following subsections describe these options.

•

FIGURE 2-1. 732 - COMPONENT LOCATION

Rev. A. February 11, 1987

# 2.2.1 Base Address Selection

Jumper block JA controls the base address. Table 2-1 shows how to set the jumpers for commonly used base addresses. Inserting a jumper makes the 732 respond to a 0 on that address line; removing a jumper makes the 732 respond to a 1. Connect the jumper between similar pin numbers on each block. (The 732 uses bits 1 through 3 to determine which register is being accessed.) The 732 is an Al6 Slave, and responds to address modifier 02DH, and optionally 029H.

> \* These two pins are test points, not address jumpers FIGURE 2-2. BASE ADDRESS JUMPER BLOCK

| Screen Label>                             | F      | E | D | С | B | A                | 9      | 8      | 7 | 6 | 5                | 4 |

|-------------------------------------------|--------|---|---|---|---|------------------|--------|--------|---|---|------------------|---|

| Address:<br>EEA0*<br>EE40<br>0800<br>0100 | 0<br>I | 0 | - | Ī | 0 | 0<br>0<br>I<br>I | 0<br>I | I<br>I | I | I | O<br>I<br>I<br>I | _ |

0 = Out; I = In;

\* Standard Factory Configurantion

TABLE 2-1. BASE ADDRESS SELECTION

### 2.2.2 Bus Request and Bus Grant Lines

The 732 uses the Bus Request and Bus Grant lines to become bus master. In VMEbus arbitration, there are four Bus Request/Grant levels: 0 through 3. The 732 drives one Bus Request line according to the jumper scheme you choose. The arbiter drives the four Bus Grant In lines: BG0IN\* through BG3IN\*. If the 732 receives a Bus Grant, and is not requesting the bus, it passes the grant by driving the appropriate Bus Grant Out line: BG00UT\* through BG30UT\*.

Rev. A. February 11, 1987 11

2.2.2 Bus Request and Bus Grant Lines (continued)

Select a request level by jumpering one Bus Request (BRO\* through BR3\*), one Bus Grant In, and one Bus Grant Out line to match the selected request level. Jumper the remaining Bus Grant In/Out lines so that the incoming signal passes through the board (i.e., jumper BGxIN\* to BGxOUT\*, where x represents the remaining grant levels).

For example, Figure 2-3 shows the jumpering scheme for level 0 (Figure 2-3A shows the jumper blocks as they actually appear on the board; 2-3B is labeled for this example): jumper JBl to JB5; then jumper JCl to JC5, and JDl to JD5. Jumper the remaining Grant levels from JC6 to JD2, JC7 to JD3, and JC8 to JD4. Factory configuration: Bus Request Level 3.

#### NOTE

Some VME processors only support Bus Request Level 3.

FIGURE 2-3. JUMPERING BUS REQUEST AND BUS GRANT LEVELS

2.2.3 Parallel Arbitration If you are using the 732 in parallel arbitration, and the Bus Grant Out lines must be isolated from the next slot's Bus Grant In Lines, remove all jumpers between JC 5-8 and JD 1-4 (See Figure 2-3B).

2.3SELF TEST DISABLE

When jumper JE 3-4 is installed, the 732 does not execute the Self Test on power-up.

2.4 PROMS AND PALS

LOCATION PART NUMBER TYPE

TABLE 2-2. PROM / PAL PART NUMBER AND LOCATION

2.5 LIGHT EMITTING DIODES

The 732 has two light emitting diodes (LEDs). L1 (BSY) is the Busy LED (it is located closest to the printed circuit board). L2 (ERR) is the Error LED (it straddles L1).

2.6 BOARD LABELS / REVISION CONTROL

All Xylogics controllers use various revision control labels. This information is important when discussing configuration issues with us. Please familiarize yourself with your board revision levels before contacting us.

732-001-01 | | | Product\_\_\_\_| | | Configuration\_\_\_\_| |\_\_\_\_Revision Level

FIGURE 2-4. SAMPLE PART NUMBER

Rev. A. February 11, 1987

### 2.7 PREPARING THE COMPUTER SYSTEM FOR INSTALLATION

The backplane of your system must provide a VMEbus slot for the 732. The slot must be capable of handling a bus master, and the power source must handle the power consumption of the entire system, including the 732.

#### 2.7.1 Backplane Jumpers

Remove any jumpers that short, or cause the Interrupt Acknowledge (IACK IN/OUT) and DMA Grants (BG 0-3 IN/OUT) to bypass the slot in which you are installing the 732.

#### 2.7.2 Card Cage Slot

The card cage must have a slot at the proper DMA priority available for the 732. The 732 uses DMA to transfer data and IOPBs. Placement of the 732 in the DMA priority chain may be critical. The amount of bus bandwidth it uses will be high at times; this may affect other boards in the system. Likewise, other boards may not allow enough time for the 732 to DMA enough data to keep up with the disk; consider this when choosing a slot. If the 732 does not get a high enough priority, then its DMA falls behind what the disk requires, and it has to wait until the next revolution before continuing the transfer. If the 732 priority is high, it gets enough DMA time, but other boards having insufficient buffers may starve from lack of DMA time. The priorities must be balanced for your system to work properly.

#### 2.7.3 Power Considerations

The 732 affects the power consumption of the entire computer system. The 732 uses +5 volts (4.75 to 5.25 volts) at ?? amps. Be sure the power supplies can handle the entire power load. Readjust the voltages AFTER plugging in the 732. A power supply that is just adequate may cause intermittent and unusual problems due to noise generated by occasionally going into overcurrent protection.

#### 2.8 PREPARING THE DRIVES FOR INSTALLATION

Follow the manufacturer's instructions for unpacking and inspecting the drives.

#### Rev. Al. February 11, 1987 14

2.9 INSTALL AND CABLE THE 732

2.9.1 Install the 732

Place the 732 into the computer card cage; make sure it is firmly seated. Be careful not to dislodge any socketed ICs. Situate the disk drive and connect it to its power source.

2.9.2 Cable the Subsystem

2.9.2.1 Connect the Floppy Cable.

Install the floppy cable, observing "pin 1" markings on both ends. This cable connects to the 34-pin connector on the 732, and to the cable connector on the drive. Use the "in" connector on the drive if there are two 34-pin connectors marked "in" and "out". The other connector should have a terminator, or the terminator should be built into the drive. (Only cable one disk drive for the initial system check. You can connect additional disk drives later.)

2.9.2.2 Connect The Tape Cable

Install a tape cable (50-pin cable) from the tape cable port on the 732 to the appropriate connector on the tape drive.

2.9.2.3 Mechanical Restraint

Make sure the floppy and tape cables are mechanically restrained at both ends to prevent them from accidentally disconnecting. Using "pull tabs" on the cables greatly reduces connector damage.

2.9.2.4 Disk Drive Grounds

Install a ground braid wire between the ground terminal on the disk drive(s) and the computer system ground.

# 2.10 INITIAL TESTS

This section relies upon your familiarity with your computer system's monitor and dignostics.

### 2.10.1 Power-up and Self Test

The 732 initiates a self test upon power-up. The Error LED (L2) lights for a moment, and then goes off. If L2 remains on, and the Fatal Error Register indicates an IRAM Checksum error, then you need to load good parameters into the IRAM. Otherwise, if L2 remains on, the board is not functioning properly (the Fatal Error Register may indicate the nature of the problem). Contact Xylogics for further assistance.

#### NOTE

Check the power supply voltage to ensure it is within limits (4.75 to 5.25 volts).

#### 2.10.2 Drive Ready

Spin the drive up and wait for it to become ready. Issue a Read Drive Parameters IOPB. The Drive Status byte indicates the drive status at execution time. If DRDY is not set, recheck the drive cable connections and try again. If you are still unable to get the proper status, check the +5V supply on the bus. If the problem persists, check the disk drive for functionality with an off-line tester.

#### 2.11 DIAGNOSTICS

When you run your diagnostics:

- Format the disk with either a diagnostic or format program.

- Run a full pass of your diagnostic (or determine that the system is working properly.

- o Cable and test any additional drives.

### 2.12 CABLING MULTIPLE FLOPPY DRIVES

If you are using multiple drives, make sure the cables are properly connected; observe the "pin 1" markings on both the cables and the drives.

#### Rev. A. February 11, 1987 16

# 2.12.1 Terminator

Remove the terminator from the drive currently connected to the controller. Install the terminator in the last drive in the chain.

2.12.2 Unit Select - Floppy

If you are daisy-chaining drives, assign each drive a unique Unit Select number. The 732 accesses drives with Unit Numbers 1 and 2 for the floppy.

2.12.3 Unit Select - Tape

The 732 only accesses drive 1.

SECTION 3: THE 732 REGISTERS

### 3.0 GENERAL

The 732 programming interface is based on the use of seven, one-byte long, I/O registers. The bus address jumpers define the base address of the register set. Table 3-1 lists the registers along with the address offset from the base address. The 732 responds to either bytes or 16-bit words; when it responds to words, only 8 bits are valid.

The registers have one function when read, and another when written. The following subsections detail their definitions.

REGISTER

#### OFFSET

1

3

5 7

9

В

D

IOPB ADDRESS BYTE 0 (Least Significant Byte) IOPB ADDRESS BYTE 1 IOPB ADDRESS BYTE 2 IOPB ADDRESS BYTE 3 (Most Significant Byte) IOPB ADDRESS MODIFIER CONTROL AND STATUS REGISTER FATAL ERROR REGISTER

TABLE 3-1. REGISTER OFFSETS

#### 3.1 IOPB ADDRESS REGISTERS

The first four registers define the 32-bit address of an IOPB or IOPB chain. When these registers are written, the 732 interprets it as the address of the IOPB or IOPB chain to be executed. When read, and Remove IOPB (RIO) is set, the registers point to the IOPB or IOPB chain completed by the 732.

The protocol for reading and writing this address register is defined by the use of the Add IOPB (AIO) and Remove IOPB (RIO) bits in the Control and Status Register (See Section 3.3).

# 3.2 IOPB ADDRESS MODIFIER REGISTER

This register defines the IOPB address modifier. (Address modifiers are used for many purposes, such as memory mapping, privilege levels, and addressing range. Please consult the VMEbus

Rev. A. February 11, 1987 18

#### 3.2 IOPB ADDRESS MODIFIER REGISTER (continued)

Specification Manual for more information on using address modifiers.) This register also specifies whether an IOPB has priority over the current set of IOPBs in the 732 command queue. Section 3.3 defines the protocol for reading and writing this register.

|       |  |      |  | F     | R | [ OF | RI? | ГҮ  | I | OPI | 3 I | REC | SIS | STI | ER |   |   |

|-------|--|------|--|-------|---|------|-----|-----|---|-----|-----|-----|-----|-----|----|---|---|

|       |  | 7    |  | 6     | 1 | 5    | 1   | 4   |   | 3   |     | 2   | 1   | 1   |    | 0 | 1 |

|       |  | ]    |  |       |   |      |     |     |   |     |     | ļ   | _   |     |    | ! |   |

| ED    |  | <br> |  | <br>_ |   | 1    |     | 1   |   | 1   |     |     |     | 1   |    |   |   |

| IFIER |  |      |  |       | - | _1_  |     | _1_ |   | _1_ |     | _ _ | -   | _1_ |    | _ |   |

BIT MNEMONIC DESCRIPTION

- 7-6 RESERVED.

- 5-0 AM ADDRESS MODIFIER Most systems use the standard AM code of 3D. See the VMEbus Specification Manual.

# 3.3 CONTROL AND STATUS REGISTER

When written, this register provides the host with control of the 732 operation; when read, it provides the host with 732 status information. Section 3.3.1 defines the bits in this register when written; Section 3.3.2 defines the bits when read.

# 3.3.1 Control Register (Write)

|                                                                                                           |   |   | СС | DN? | rr( | CL | R | EGI | [S' | ΓEF | ર | (Write) |  |   |   |   |  |  |  |

|-----------------------------------------------------------------------------------------------------------|---|---|----|-----|-----|----|---|-----|-----|-----|---|---------|--|---|---|---|--|--|--|

|                                                                                                           | 1 | 7 | 1  | 6   |     | 5  |   | 4   | 1   | 3   | 1 | 2       |  | 1 | 1 | 0 |  |  |  |

| RESERVED<br>ENABLE MAINTENANCE MODE<br>RESERVED<br>CONTROLLER RESET<br>ADD IOPB<br>CLEAR RIO<br>CLEAR RBS |   |   |    |     |     |    |   |     |     |     |   |         |  |   |   |   |  |  |  |

Rev. A. February 11, 1987

3.3.1 Control Register (Write) (continued)

- BIT MNEMONIC DESCRIPTION

- 7-6 RESERVED.

- 5 MM ENABLE MAINTENANCE MODE - Setting MM and AIO places the 732 in Maintenance mode. This mode supports a different Register protocol and is used as a diagnostic tool. Section 8 outlines the Maintenance mode.

- 4 RESERVED.

- 3 CRST CONTROLLER RESET - This bit signals the 732 microprocessor to perform a "soft" reset; it deselects (releases dual port) all the drives, stops the DMA and Disk Sequencers (potentially during sector transfers), and cancels any IOPBs in the queue. When the Controller Reset completes, the 732 resets the CSR to zero. CRST does not initiate a Power-up Self Test.

#### NOTE

A Controller Reset takes up to one second to complete.

2 AIO ADD IOPB - The host sets AIO to indicate that the 732 should execute the IOPB (chain) at the address pointed to by the IOPB Address and Address Modifier Registers. Essentially. AIO commands the 732 to begin executing a new IOPB (chain). As soon as the host asserts this bit, the 732 asserts the AIO Pending (AIOP) bit in the Status Register; this indicates that the 732 has received the AIO, signal but has not yet processed the address of the new chain. AIOP is negated in the Status Register after the 732 internally stores the new (chain) address. The 732 can store up to 47 IOPB addresses in this manner. Reasserting AIO if AIOP is asserted in the Status Register violates the Register protocol.

Rev. A. February 11, 1987

3.3.1. Control Register (Write) (continued)

- DESCRIPTION BIT MNEMONIC

- 1 CRIO CLEAR RIO - The host sets CRIO to clear RIO in the Status Register. Typically, the host sets CRIO after it reads the address of a completed IOPB chain from the IOPB Address and Modifier Regiaters. Clearing RIO enables the 732 to update the IOPB Address and Modifier Registers with the address and address modifier of a newly completed IOPB Clearing RIO if it is not asserted in chain. the Status Register violates the Register protocol.

- 0 CRBS CLEAR RBS - The host sets the Clear Register Busy (CRBS) bit to clear the RBS bit in the Status Register. Clearing RBS effectively releases the registers for use by another host (See Section 8.8.2). (CRBS is only relevant in a multiprocessor environment.)

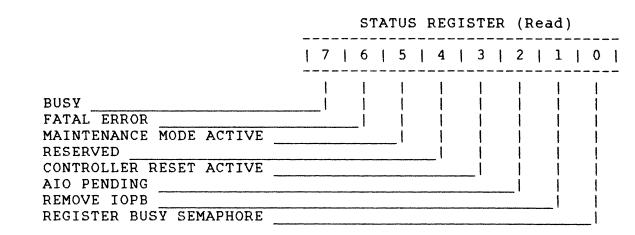

- 3.3.2 Status Register (Read)

#### BIT MNEMONIC DESCRIPTION

7 BUSY BUSY - The 732 is executing IOPBs. The 732 sets BUSY when it clears AIOP to acknowledge the first IOPB address; it clears BUSY after completing all the IOPBs with no new ones pending (within 500 microseconds of the host clearing RIO on the last (IOPB). This bit is redefined when the 732 is in Maintenance mode (see Section 8.6).

Rev. A. February 11, 1987 21

- 3.3.2 Status Register (Read) (continued)

- BIT MNEMONIC DESCRIPTION

FERR FATAL ERROR - The 732 detected a fatal hardware error. A Controller Reset clears this bit. The 732 asserts FERR under the following conditions:

- Maintenance Mode Test Failure;

- (2) Power-up Self Test Failure;

- (3) IOPB Checksum Miscompare;

- (4) IOPB DMA Fatal;

- (5) IOPB Address Alignment Error;

- (6) Firmware Error;

- (7) Illegal Maintenance Mode Test Number

- (8) ACFAIL Asserted.

- 5 MMA MAINTENANCE MODE ACTIVE When set, the 732 is in Maintenance mode (See Section 8.6).

- 4 RESERVED.

6

- 3 RSTA CONTROLLER RESET ACTIVE The host set Controller Reset in the Control Register and the 732 is currently resetting itself.

- 2 AIOP AIO PENDING When set, AIO has been set in the Control Register, but the 732 has not acknowledged its receipt. When clear, AIO may be set again.

After the host reads the address and modifier, it must clear RIO by writing Clear RIO (CRIO) in the Control Register.

- 1 RIO REMOVE IOPB The 732 sets RIO after completing an IOPB, or a chain of IOPBs, and placing the address in the IOPB Address and Address Modifier Registers.

- 0 RBS REGISTER BUSY SEMAPHORE RBS provides a means of allowing multiple hosts to share access to the 732 registers without simultaneous access (See Section 8.8.2). (RBS is only relevant in a multiprocessor environment.)

# 3.4 FATAL ERROR REGISTER

If a fatal error occurs, the 732 returns the appropriate Completion Code in this register. Table 3-2 lists the fatal error codes; Section 6.5 describes them.

| EO    | IRAM Checksum Failure                         |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| El    | IRAM Self Test Failure                        |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E2    | EPROM Checksum Failure                        |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E 3   | Maintenance Test 3 Failure (Floppy Chip)      |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E4    | Maintenance Test 4 Failure (QIC-02 Interface) |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E5    | Maintenance Test 5 Failure (VMEDMA Registers) |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E6    | Maintenance Test 6 Failure (REGCEL Chip)      |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E7    | Maintenance Test 7 Failure (Buffer Parity)    |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E8    | Maintenance Test 8 Failure (Disk FIFO)        |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E9-EF | Reserved                                      |  |  |  |  |  |  |  |  |  |  |  |  |  |

| ΕO    | IOPB Checksum Miscompare                      |  |  |  |  |  |  |  |  |  |  |  |  |  |

| Fl    | IOPB DMA Fatal                                |  |  |  |  |  |  |  |  |  |  |  |  |  |

| F2    | IOPB Address Alignment Error                  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| F3    | Firmware Error                                |  |  |  |  |  |  |  |  |  |  |  |  |  |

| F5    | Illegal Maintenance Mode Test Number          |  |  |  |  |  |  |  |  |  |  |  |  |  |

TABLE 3-2. FATAL ERROR CODES

Rev. A2. June 17, 1987

# SECTION 4: IOPB DESCRIPTION

# 4.0 GENERAL

The Input/Output Parameter Block (IOPB) passes messages between the 732 and host software: software passes the type of transfer, disk address, data address, and count to the 732; the 732 returns the transfer status and possibly the ending addresses upon command completion. This section begins with the standard IOPB for most data transfer commands and follows with variations of the IOPB.

# 4.1 STANDARD IOPB

The 732 uses the standard floppy IOPB for data transfer commands and some general purpose commands, when a floppy unit number is selected. It uses the standard tape IOPB when the tape unit number is selected

4.1.1 IOPB Byte 0 (Command)

|     |              | 7   6   5   4   3   2   1   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | DONE<br>CHAI | N ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BIT | MNEMON       | IC DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7   | ERRS         | ERROR SUMMARY - ERRS is only valid if DONE is<br>set. When set, a hard or soft error occurred<br>during IOPB processing. When clear, the 732<br>successfully completed the IOPB.                                                                                                                                                                                                                                                                                                                 |

| 6   | DONE         | DONE - When set, the IOPB is complete; if<br>chained, software may remove the IOPB from<br>the chain. Software must relink the chain in<br>the same order as before, and cannot move<br>IOPBs in memory.                                                                                                                                                                                                                                                                                         |

| 5   | CHEN         | CHAIN ENABLE - When set, the Next IOPB<br>Address Modifier and Next IOPB Address point<br>to the next chained IOPB. When clear, this<br>IOPB is not chained to another IOPB. If CHEN<br>and IEC are set, the 732 returns the whole<br>chain with one RIO; if CHEN is set and IEC is<br>clear, the 732 returns one IOPB at a time.                                                                                                                                                                |

| 4   | SGM          | SCATTER/GATHER MODE - When set, the IOPB is<br>either a scatter (read) or a gather (write)<br>transfer; a linked list describes the number<br>of 16-bit words and to what address the 732<br>transfers each section of the data. The link<br>address modifier and the link address specify<br>the link list location. When clear, this<br>IOPB specifies the data transfer address; the<br>data is transferred to/from contiguous<br>memory. SGM is only valid for standard Reads<br>and Writes. |

| 3-0 | COMM         | COMMAND - See Table 4-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# 4.1.2 IOPB Byte 1 (Status Byte 1)

After the 732 executes the IOPB, it sets DONE and posts a Completion Code in this byte. (Completion Codes are only valid if DONE is set.) A code of 0x indicates a successful completion; any other value indicates an error occurred (See Section 6).

4.1.3.1 IOPB Byte 2 (Status Byte 2) for FLOPPY DISK

IOPB Byte 2 is the Disk Status byte; it is only valid if DONE is set.

|     |         |                                                          | _ |   |    |    |     |    |     |    |     |     | _   |    |  |   |   |   |  |

|-----|---------|----------------------------------------------------------|---|---|----|----|-----|----|-----|----|-----|-----|-----|----|--|---|---|---|--|

|     |         |                                                          | 1 | 7 | 1  | 6  | 1   | 5  | 1   | 4  |     | 3   |     | 2  |  | 1 | 1 | 0 |  |

|     | RESERV  | VED<br>VED<br>TION HIGH                                  |   |   |    |    |     |    |     |    |     |     |     |    |  |   |   |   |  |

|     | DRIVE   | READY                                                    |   |   |    |    |     |    |     | i  |     |     |     |    |  |   |   | _ |  |

| BIT | MNEMONI | C DESCRIPTION                                            |   |   |    |    |     |    |     |    |     |     |     |    |  |   |   |   |  |

| 7   |         | RESERVED.                                                |   |   |    |    |     |    |     |    |     |     |     |    |  |   |   |   |  |

| 6   |         | RESERVED.                                                |   |   |    |    |     |    |     |    |     |     |     |    |  |   |   |   |  |

| 5-4 |         | RESERVED.                                                |   |   |    |    |     |    |     |    |     |     |     |    |  |   |   |   |  |

| 3   | ATTN    | ATTENTION HIGH - The<br>drive reports an err             |   |   | se | ts | ; A | ΥТ | 'n  | wh | ner | n t | :he | ÷  |  |   |   |   |  |

| 2   |         | RESERVED.                                                |   |   |    |    |     |    |     |    |     |     |     |    |  |   |   |   |  |

| 1   | CMPL    | COMMAND COMPLETE - T<br>currently selected d<br>command. |   |   |    |    |     |    |     |    |     |     |     |    |  |   |   |   |  |

| 0   | DRDY    | DRIVE READY - The 73<br>drive selected is re             |   |   | S  | DR | DY  | w  | 'nε | en | tł  | ıe  | la  | st |  |   |   |   |  |

4.1.3.2 IOPB Byte 2 (QICO2 status 0) for TAPE

BIT MNEMONIC DESCRIPTION 7 STO SET - if any other bit in byte 0 is set. If bit 7 is set Exception may be set. 6 CNI CARTRIDGE NOT IN - Exception set if cartridge removed, and (1) drive selected by select drive with Lock Cartridge command; (2) motion command is issued; or (3) tape moved previously from BOT. 5 DFF DEVICE FAULT FLAG - No longer unselected drive (USL) bit. DFF sets Exception. Must be followed by a Read Status sequence to (Read Extended Status III clear Exception. contains information in Byte 25 to determine cause of fault.) DFF set when formatter detects 540 condition which prohibits further command execution. 1. No tape motion (jammed cartridge). 2. Failure to recognize or exit area between BOT/load point, or early warning/EOT. 3. No tach pulses. 4. Failure to complete command function in specified internal time. For example: not completing rewind once formatter initiates command. DFF indicates an unrecoverable 540 or cartridge error to user. 4 WRP WRITE PROTECTED CARTRIDGE - Set if cartridge write protect mechanism on safe. Remains set if any Write or Erase command is issued when cartridge is write protected. 3 EOM END OF MEDIA - Set when early warning hole detected on last track in write mode. Remains set while tape is at logical end of Not reset by Read Status. When set, media. Exception is set.

Rev. A. February 11, 1987 27

- 4.1.3.2. IOPB Byte 2 (QICO2 Status 0) for TAPE (continued)

- BIT MNEMONIC DESCRIPTION

- 2 UDE UNRECOVERABLE DATA ERROR Set for unrecoverable data error during read or write operation. If set, Exception is set. Reset by Read Status.

- 1 BNL BAD BLOCK NOT LOCATED Set to indicate drive not able to locate correct block on tape. If set, Exception is set. When set with (UDE), drive transfers filler data block or data from a different block to keep correct total block count. BNL reset by Read Status.

- 0 FMD FILEMARK DETECTED Set when filemark block is read. Exception set and FMD reset by Read Status.

- 4.1.4.1. IOPB Byte 3 (Status Byte 3) for FLOPPY DISK

IOPB Byte 3 is reserved. It reflects the 732's internal status and may be a non-zero value.

- 4.1.4.2. IOPB Byte 3 (QICO2 Status 1) for TAPE

- BIT MNEMONIC DESCRIPTION

- 7 STI SET If any other bit in Byte 1 is set. If set, Exception may be set.

- 6 ILL ILLEGAL COMMAND Exceptions and Bit 6 set under these conditions:

- 1. On line not asserted when read or write type command attempted or in process.

- 2. Non-implemented command is issued.

- 3. Non-read type command issued without proper termination of read sequence.

- Non-write type command issued without proper termination of write sequence. ILL reset by Read Status.

- 5 NDT NO DATA DETECTED Set when drive determines no data is recorded on one tape. If set, Exception is set. NTD reset by Read Status.

- 4.1.4.2. IOPB Byte 3 (QICO2 Status 1) for TAPE

- BIT MNEMONIC DESCRIPTION

- 4 MBD MARGINAL BLOCK DETECTED Set at detection of marginal data block. Enhanced track offset read recovery uses MBD to alert host if q4mil or q8-mil offset required to read recorded cartridge. Exception set only if Exception and filemark read status are indicated. A set MBD indicates track position offset, when filemark was read. This status indicates to host a marginally recorded cartridge. Host may determine to write append tape, or recover data and rewrite cartridge.

- 3 BOM BEGINNING OF MEDIUM Bit set when drive is logically at BOT, Track 0. If set, Exception is set. Bit not reset by Read Status, but reset when tape moved away from logical BOT.

- 2 BPE BUS PARITY ERROR Bit set when drive detects odd parity error on bus during data transfer to drive. If set, Exception is set. Odd parity is an odd number of active bits on bus. Parity is enabled by W8, W9, W10 jumper configuration on 540 formatter. Only data checked for parity.

- ERM END OF RECORDED MEDIA Bit set when drive detects end of recorded media, or following a Seek End of Data command. If set, Exception is set.

- 0 POR POWER ON/RESET OCCURRED SET Bit set following power on to drive or a reset from host. If set, Exception is set. Bit reset by a Read Status.

4.1.5 IOPB Byte 4 (Subfunction)

IOPB Byte 4 is the Subfunction byte. Subfunction Codes follow a convention that indicates whether the code is generic to all VME controllers, generic to a group of controllers (i.e., disk, tape, etc.), or specific to a particular controller (See Table 4-1).

Rev. A. February 11, 1987 29

4.1.5 IOPB Byte 4 (Subfunction) (continued)

The 732 combines standard Command Codes with Subfunction Codes to execute commands. The IOPB Command Code and Subfunction Code fields define the required operation. Table 4-2 lists the 732 Command and Subfunction Codes.

SUBFUNCTION CODES

CLASS

| 00-1F | Generic To All |

|-------|----------------|

| 20-3F | Generic Tape   |

| 40-5F | 772-Specific   |

| 60-7F | Reserved       |

| 80-9F | Generic Disk   |

| A0-AF | 751-Specific   |

| B0-BF | 712-Specific   |

| CO-FF | Reserved       |

TABLE 4-1. SUBFUNCTION CODE CLASSES

| CODE | COMMAND | SUB EN | J DESCRIPTION |

|------|---------|--------|---------------|

| 0000 |         | 000 11 |               |

- 0 NOP 00 No Operation

- 1 WRITE 00 Normal Write

- 2 00 Normal Read READ

- SEEK (FLOPPY) 00 Report Current Address 01 Seek and Report Current Address

- 3 SEEK (TAPE) 21 Space record reverse 40 File Mark Search Forward 42 Mult. File Mark Search Forward DRIVE RESET (FLOPPY) 00 Drive Reset (With RTZ)

- DRIVE RESET (TAPE) 00 Drive Reset 21 Rewind 22 Offline 24 Retension

#### TABLE 4-2. 732 COMMAND/SUBFUNCTION CODES

Rev. A2. June 17, 1987

3

4

4

4.1.5. IOPB Byte 4 (Subfunction) (continued)

CODE COMMAND SUB FN DESCRIPTION

5 WRITE PARAMETERS 00 Write Controller Prmtrs. 80 Write Drive Parameters 6 READ PARAMETERS 00 Read Controller Prmtrs. 40 Read QIC02 Status 80 Read Floppy Drive Parameters 7 EXTENDED WRITE 81 Write Track Format (FLOPPY) 7 EXTENDED WRITE (TAPE) 20 Write File Mark 21 Erase 8 EXTENDED READ 81 Verify Data - not implemented 83 Read Full Track

9 DIAGNOSTICS 00 Self Test

A-F RESERVED

TABLE 4-2. 732 COMMAND/SUBFUNCTION CODES (continued)

4.1.6 IOPB Byte 5 (Unit)

|                               | 1 | 7 | 1 | 6 | 1 | 5 | 1 | 4 | 1 | 3 | 1 | 2 | 1 | 1 | 1 | 0 | 1 |

|-------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| SKIP DELETED DATA<br>RESERVED |   | _ |   |   |   |   |   |   |   | 1 |   |   |   |   |   | 1 |   |

| BLACK HOLE TRANSFER           |   |   |   |   |   |   |   | _ |   | 1 |   | 1 |   | 1 |   | 1 |   |

| BYTE SWAP                     |   |   |   |   |   |   |   |   |   |   |   | 1 |   |   |   | 1 |   |

| UNIT NUMBER                   |   |   |   |   |   |   |   |   |   |   |   | 1 |   | 1 |   | 1 |   |

BIT MNEMONIC DESCRIPTION

7 SK SKIP DATA FIELD - When set in Read Command. If deleted data mark detected, and go on to next sector. When clear in read command, if (floppy only)a DDM is detected, data is transferred from that sector, and command stops with an error.

Rev. A. February 11, 1987

- 4.1.6 IOPB Byte 5 (Unit) (continued)

- BIT MNEMONIC DESCRIPTION

- 7-5 RESERVED.

.

- 4 BHT BLACK HOLE TRANSFER When set, the 712 does not increment the bus address during a data transfer; IOPB transfers occur normally. When clear, the 732 does increment the bus address.

- 3 BS BYTE SWAP Each word transfer

- 2-0 UNIT UNIT NUMBER This value specifies the Unit Number of the attached drive to which the transfer is directed.

UNIT SELECTION

| LOGICAL UNIT | BIT | BIT | BIT | DRIVE         |

|--------------|-----|-----|-----|---------------|

| 0            | 0   | 0   | 0   | Floppy Unit l |

| 1            | 0   | 0   | 1   | Floppy Unit 2 |

| 2,3          | 0   | 1   | Х   | Reserved      |

| 4            | 1   | 0   | 0   | Tape Unit l   |

| 5            | 1   | 0   | 1   | Reserved      |

| 6,7          | 1   | 1   | Х   | Reserved      |

4.1.7 IOPB Byte 6 (Interrupt Level)

| 7   6   5   4   3   2   1   0     LINK LIST LENGTH     _   _   _   _   _         INTERBUPT LEVEL |  |          |     |   |     |   |     |   |   |   |   |   |   |   |   |   |   |   |

|--------------------------------------------------------------------------------------------------|--|----------|-----|---|-----|---|-----|---|---|---|---|---|---|---|---|---|---|---|

|                                                                                                  |  | 1        | 7   | ł | 6   | ۱ | 5   | I | 4 | ۱ | 3 | ۱ | 2 | I | 1 | ۱ | 0 | I |

|                                                                                                  |  | <br>•••• | _ _ |   | _ _ |   | _ _ |   |   |   | _ |   |   | 4 |   | - | ! |   |

### BIT MNEMONIC DESCRIPTION

7-3 LLL LINK LIST LENGTH - Bits 7-3 specify the length, in elements, of a linked list for Scatter/Gather commands. Each element refers to an 8-byte block in the linked list. See Table 8-2.

Rev. A. February 11, 1987 32

4.1.7 IOPB Byte 6 (Interrupt Level) (continued)

- BIT MNEMONIC DESCRIPTION

- 2-0 INTL INTERRUPT LEVEL The 732 uses these bits as the VMEbus hardware interrupt level when it completes the IOPB. The 732 will not interrupt if bits 0 through 2 are clear.

NOTE

Depending on the command, Bytes 6 through 13 have different definitions (See Sections 4.2 through 4.4).

4.1.8 IOPB Byte 7 (Interrupt Vector)

IOPB Byte 7 determines the interrupt vector that the 732 uses upon command completion. This byte is not valid if the interrupt level is zero.

4.1.9 IOPB Bytes 8 and 9 (count)

Byte 8 is the Count High; Byte 9 is the Count Low. The bytes specify the number of disk sectors or tape blocks to be transferred in a data transfer IOPB.

The disk format command uses this count to specify the number of tracks to format.

The tape Multiple File Mark Search command uses this count to specify the number of contiguous file marks to be found.

If an error occurs, these bytes indicate the residual count, i.e. the number of sectors or blocks not transferred. A count of 0 is illegal, and the IOPB returns a completion code 013H.

4.1.10 IOPB Bytes A-D

These Bytes are used differently for floppy disk data transfer commands, tape data transfer commands and parameter commands. See section 4.2 and 4.3 for usage in parameter commands.

4.1.11 IOPB Bytes A-D for Floppy Disk

4.1.11.1 IOPB Byte A

This byte is reserved for floppy data transfer commands.

Rev. A. February 11, 1987

4.1.11.2 IOPB Byte B (Cylinder)

This byte specifies the starting cylinder address for a data transfer.

4.1.11.3 IOPB Byte C (Head)

This byte specifies the starting head address for a data transfer. Only heads 0 and 1 are valid.

4.1.11.4 IOPB Byte D (Sector)

This byte specifies the starting head address for a data transfer. The controller adds 1 to the logical sector number before addressing the drive, unless the SZV bit is set.

4.1.12 IOPB Bytes A-D for QIC02 Tape

4.1.12.1 IOPB Bytes A and B

These bytes contain the Re-write count for a write operation if a QIC02 error occurred, or if the drive status is read.

4.1.12.2 IOPB Bytes C and D

These bytes contain the Re-read count for a read operation if a QIC02 error occurred, or if the drive status is read.

4.1.13 IOPB Byte E (Data or Link Address Modifier)

|                             | ۱ | 7   | ١ | 6 | I | 5 | ۱ | 4 | I | 3 | 1 | 2 | ۱ | 1 | 1 | 0 | I |

|-----------------------------|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| RESERVED                    |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| DATA OR LINK ADDRESS MODIFI | E | R T |   | _ |   | 1 |   | 1 |   | 1 |   | 1 |   | I |   | 1 |   |

BIT DESCRIPTION

7-6 RESERVED.

5-0 DATA OR LINK ADDRESS MODIFIER - If SGM is set, bits 5 through 0 specify the Link List Address Modifier; if SGM is clear, this field specifies the Data Address Modifier. The 732 uses these modifiers to complete the address.

4.1.14 IOPB Byte F (Next IOPB Address Modifier)

|                            | I | 7     | ł | 6 | I | 5   | I | 4   | ۱ | 3   | ł | 2   | I | 1   | ۱ | 0 | I |

|----------------------------|---|-------|---|---|---|-----|---|-----|---|-----|---|-----|---|-----|---|---|---|

|                            |   |       |   |   |   |     |   |     | - | 1   |   |     |   |     |   |   |   |

| RESERVED                   |   | _   _ |   |   |   |     |   |     |   |     |   |     |   |     |   |   |   |

| NEXT IOPB ADDRESS MODIFIER |   |       |   |   |   | _ _ |   | _ _ |   | _1_ |   | _1_ |   | _1_ |   | _ |   |

- BIT MNEMONIC DESCRIPTION

- 7-6 RESERVED.

- 5-0 NEXT IOPB ADDRESS MODIFIER The Next IOPB address Modifier, along with the Next IOPB Address, point to the next IOPB in the chain.

4.1.15 IOPB Bytes 10 through 13 (DMA Data Address)

IOPB Byte 10 is DMA Data Address High; Byte 13 is DMA Data Address Low. These bytes comprise the data or link list address pointers. The 732 uses these bytes with the data or link list address modifier to point to the data or linked list address. If SGM is set, this address points to the linked list; if SGM is clear, this address points to the data address.

4.1.16 IOPB Bytes 14 through 17 (Next IOPB Address)

IOPB Byte 14 is Next IOPB Address High; Byte 17 is Next IOPB Address Low. These bytes comprise the Next IOPB Address pointers. The 732 uses these bytes with the Next IOPB Address modifier to point to the next IOPB in the chain (if CHEN is set in Byte 0).

4.1.17 IOPB Bytes 18 and 19 (IOPB Checksum)

Byte 18 is IOPB Checksum High; Byte 19 is IOPB Checksum Low. The 732 calculates the checksum by adding the IOPB bytes. See Section 8.15.

### 4.2 CONTROLLER PARAMETERS IOPB

This IOPB sets and reads various controller parameters. The 732 uses the standard IOPB, but redefines bits in Bytes 8, 9, A, B, C, and E.

| Rev. A. February 11, 1987 35 | Rev. | Α. | February | 11, | 1987 | 35 |

|------------------------------|------|----|----------|-----|------|----|

|------------------------------|------|----|----------|-----|------|----|

CONTROLLER PARAMETERS

4.2.1IOPB Byte 8 (Controller Parameters A)

|                           |     |        |   |                   |   |   |   |   |   |   |   |   |   |    |   |   | - |

|---------------------------|-----|--------|---|-------------------|---|---|---|---|---|---|---|---|---|----|---|---|---|

|                           | I   | 7      | ١ | 6                 | I | 5 | ۱ | 4 | ۱ | 3 | ł | 2 | ۱ | 1  | I | 0 | I |

| AUTO-UPDATE               |     |        |   |                   |   |   |   |   |   |   |   |   |   |    |   |   |   |

| RESERVED                  |     |        |   | I                 |   | 1 |   | 1 |   | Ì |   | Ì |   | Ì  |   | 1 |   |

| IOPB CHECKSUM             |     |        |   |                   |   |   |   | Ì |   | 1 |   | Ì |   | Ì  |   | Ì |   |

| ENABLE DMA TIMEOUT        |     |        |   |                   |   |   |   |   |   | Ì |   | Ì |   | İ  |   | Ì |   |

| NON-PRIVILEGED REGISTER M | ODE |        |   | <b>*****</b> **** |   |   |   |   |   |   |   | İ |   | Ì  |   | Ì |   |

| AIO RESPONSE TIME         |     | ****** |   |                   |   |   |   |   |   |   |   |   |   | 1. |   | Ì |   |

#### BIT MNEMONIC DESCRIPTION

7 AUD AUTO-UPDATE - When set, the 732 updates the IOPB to the transfer's correct ending parameters; it updates the disk address, the sector count, and the data address after completing the transfer or detecting an error. When clear, the 732 only updates the IOPB if an error occurs. The values are then set up so that host software can tell the 732 to continue (the values should point to the sector in error, the correct remaining sector count, and proper data address).

Rev. A. February 11, 1987 36

- 4.2.1 IOPB Byte 8 (Controller Parameters A) (Continued)

- BIT MNEMONIC DESCRIPTION

- 6-5 RESERVED

- 4 ICS IOPB CHECKSUM When set, the 732 reads the IOPB, compares the checksum it generated during the read with the checksum the software driver appended to the IOPB. The 732 also updates the Checksum bytes in any IOPB if AUD is set. Clearing ICS disables this feature. See Section 8.15.

#### NOTE

Since this feature adds 50 microseconds to each transfer, it affects the 732's performance.

- 3 EDT ENABLE DMA TIMEOUT When set, the 732 enables a DMA bus error timer. When clear, the 732 relies on the VMEbus transfer timer.

- 2 NPRM NON-PRIVILEGED REGISTER MODE When set, the 732 responds to address modifiers 2DH and 29H. When clear, the 732 only responds to 2DH. (See the VMEbus Specification Manual for more information on address modifiers.)

- 1-0 AIOR AIO RESPONSE TIME These bits respond to the four values that indicate the maximum AIO response time. This is the time from setting AIO to the time the 732 clears it. The shorter the response time, the greater the 732 overhead.

| VALUE | TIME |    |          |          |

|-------|------|----|----------|----------|

| 00    | 100  | us | (Factory | Default) |

| 01    | 75   | us |          |          |

| 02    | 62   | us |          |          |

| 03    | 50   | us |          |          |

TABLE 4-3. AIO RESPONSE TIMES

Rev. A. February 11, 1987

4.2.2 IOPB Byte 9 (Controller Parameters B)

|                                | _ |     |   |    |   |   |   |   |   |        |  |         |   |   |   |   |  |

|--------------------------------|---|-----|---|----|---|---|---|---|---|--------|--|---------|---|---|---|---|--|

|                                |   | 7   | 1 | 6  | 1 | 5 | 1 | 4 | 1 | 3      |  | 2       | 1 | 1 | 1 | 0 |  |

| THROTTLE DEAD TIME<br>RESERVED |   | _1_ |   | _1 |   |   |   |   |   | 1      |  |         |   |   |   |   |  |

| RELEASE ON REQUEST<br>RESERVED |   |     |   |    |   |   |   | _ |   | <br> _ |  | <br>_ _ |   |   |   |   |  |

- BIT MNEMONIC DESCRIPTION

- 7-6 TDT THROTTLE DEAD TIME TDT selects one of four minimum time periods that determines the time the 732 remains off the bus between throttle bursts (See Section 8.12).

- 5 RESERVED.

- 4 ROR RELEASE ON REQUEST When set, the 732 releases the bus at the request of other bus masters; otherwise, it continues with the next throttle burst. The 732 monitors the bus request lines and releases bus busy only if another bus request is pending. It completes its specified throttle burst before releasing the bus due to a pending request. When clear, the 732 releases the bus at the end of each throttle burst and rearbitrates if more data transfers are pending.

- 3-0 RESERVED.

- 4.2.3 IOPB Byte A (Controller Parameters C)

|                           |   |   |   |   |   |   |   |   |   | - |   |   | - |   |   |   | - |

|---------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|                           | 1 | 7 | I | 6 | ١ | 5 | ١ | 4 | ١ | 3 | 1 | 2 | ۱ | 1 | ١ | 0 | 1 |

| RESERVED                  |   |   |   |   |   |   |   |   |   |   |   |   |   | 1 |   |   |   |

| INTERRUPT AT END OF CHAIN |   |   |   | · |   | Ì |   | Ì |   | Ì |   | İ |   | Ì |   | Ì |   |

| AUTOMATIC SEEK RETRY      |   |   |   |   |   | - |   | Ì |   | Ì |   | I |   | Ì |   | 1 |   |

| RESERVED                  |   |   |   |   |   |   |   |   |   | 1 |   | 1 |   | Ì |   | 1 |   |

38

- BIT MNEMONIC DESCRIPTION

- 7-6 RESERVED

Rev. A. February 11, 1987

4.2.3. IOPB Byte A (Controller Parameters C) (Continued)

- BIT MNEMONIC DESCRIPTION

- 5 IEC INTERRUPT AT END OF CHAIN When set, the 732 returns all IOPB chains with one RIO and one interrupt; it does not relink or unlink IOPBS. The RIO address of a completed chain is the address of the first IOPB in the chain. The 732 also uses the interrupt level and vector of the first IOPB in the chain. Clearing IEC disables this feature. (Do not set or clear IEC while the 732 is processing an IOPB chain.)

- 4 ASR AUTOMATIC SEEK RETRY When set, the 732 resets the drive, seeks to the commanded cylinder and retries the transfer on Seek and Header Error/Cylinder errors.

- 3-0 RESERVED.

4.2.4 IOPB Byte B (Controller Parameters D)

Bits 0 through 7 are the Throttle (THRO) bits. The throttle is the maximum number of transfers allowed each time the 732 becomes bus master. The throttle value determines the maximum DMA burst length for both data and IOPB DMA transfers. Each bit position represents a binary weight, allowing a throttle from 1 to 256.

| VALUE      | WEIGHT          |

|------------|-----------------|

| 0          | 256             |

| 1          | 1               |

| 2          | 2               |

| 3          | 3               |

| :          | :               |

| 255        | 255             |

| TABLE 4-4. | THROTTLE VALUES |

4.2.5 IOPB Byte C (Release Level)

The 732 returns its release level on a Read Controller Parameters command.

Rev. A. February 11, 1987 39

#### 4.2.6 IOPB Byte E (Controller Type)

IOPB Byte E is the Controller Type byte. Xylogics assigns each VME controller a unique controller type code.

| CONTROLLER | CODE ( | н)                          |

|------------|--------|-----------------------------|

| 712        | 12     | (ESDI Disk Controller)      |

| 732        | 32     | (Floppy & QIC02 Controller) |

| 751        | 51     | (SMD/SMD-E Controller)      |

| 772        | 72     | (Pertec Tape Controller)    |

#### TABLE 4-5. CONTROLLER TYPE CODES

4.2.7 IOPB Bytes 10 and 11 (EPROM Part Number)

The 732 returns a portion of the EPROM part number on a Read Controller Parameters command. The 4 nibbles in these 2 bytes refer to the part number's last 4 digits. For example, if the part number is 180-002-151, Byte 10 holds 21H and Byte 11 holds 51H.

4.2.8 IOPB Byte 12 (Revision)

This byte contains the revision level of the EPROM plugged into the board (0=Unreleased Prototype, 1=A, 2=B, etc.).

4.2.9 IOPB Byte 13 (Subrevision)

This byte contains the subrevision level of the EPROM plugged into the board. Any value other than zero indicates that the microcode is an unreleased version available for testing purposes (0=Released, 1=1, 2=2, etc.).

# 4.3 DRIVE PARAMETERS IOPB (Floppy only) DRIVE PARAMETERS

## 4.3.1. IOPB Byte 5 (Unit)

•

|                               | 1      | 7   | ۱ | 6 | 1 | 5   | ۱ | 4 | ۱ | 3 | ۱ | 2   | 1 | 1 | ۱ | 0 | ۱ |

|-------------------------------|--------|-----|---|---|---|-----|---|---|---|---|---|-----|---|---|---|---|---|

| RESERVED<br>SECTOR ZERO VALID |        | _ _ |   | _ |   |     |   |   |   |   |   |     |   |   |   |   |   |

| RESERVED                      | ****** |     |   |   |   | _ ! |   |   |   | _ |   | _ _ |   | _ |   | 1 |   |

•

Rev. A. February 11, 1987 41

- 4.3.1 IOPB Byte 5 (Unit) (continued)

- BIT MNEMONIC DESCRIPTION

- 7-6 RESERVED.

- 5 SZV SECTOR ZERO VALID If set, the first sector on the media sector is 0. If clear, the first sector on the media is sector 1 (normal mode).

- 4-1 RESERVED.

- 0 UNIT UNIT If set command applies to Drive 2, if clear command applies to Drive 1.

- 4.3.1 IOPB Byte 6 (Drive Parameters)

|                 | 1 | 7  | ١ | 6 | 1 | 5 | ١ | 4   | 1 | 3 | ł | 2 | 1 | 1 | 1 | 0 |  |

|-----------------|---|----|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|--|

| DOUBLE STEP     |   | _1 |   |   |   |   |   |     |   |   |   |   |   |   |   |   |  |

| MULTI TRACK     |   |    |   |   |   | _ |   | 1   |   | 1 |   | 1 |   | ! |   | 1 |  |

| PRECOMP         |   |    |   |   |   |   |   | _ ! |   | 1 |   |   |   |   |   | 1 |  |

| INTERRUPT LEVEL |   |    |   |   |   |   |   |     |   | ' |   | i |   | i |   | i |  |

- BIT MNEMONIC DESCRIPTION

- 7 DSTP DOUBLE STEP When the seek distance from the present cylinder to the required cylinder is doubled, and that number of step pulses is issued to the drive. It allows a 48TPI disk to be read on a 96TPI drive.

- 6 MFM When set the media is read and written in MFM mode. When clear, FM encoding is used.

- 5 MT MULTI TRACK When set, if the max head is 1, i.e. the drive has 2 heads, large transfers spiral from the last sector on head 0 to the first sector on head 1 through to the last sector on head 1 to the first sector of the next cylinder of head 0.

- 4.3.1 IOPB Byte 6 (Drive Parameters) (continued)

- BIT MNEMONIC DESCRIPTION

- 4 PCMP PRECOMPENSATION When set all MFM data is precompensated by gl25ns, regardless of cylinder. When clear, MFM data written to cylinders less than 28 are precompensated by 187ns.

- 3 SPD SPEED When set dual spindle speed drives are run at 300 revs/minute. When clear, the drive runs at 360 revs/minute.

- 2-0 INTL INTERRUPT LEVEL

4.3.2 IOPB Byte 8 (Head Load Time)

Byte 8 is the Head Load Time in milliseconds, values 2-254ms. Recommended value for the TOSHIBA ND-08DE is 36ms.

4.3.3 IOPB Bytes 9 and A (Gap 3 length)

4.3.3.1IOPB Byte 9 specifies the length of GAP 3 used in Read and Write operations.

4.3.3.2IOPB Byte A specifies the length of GAP 3 used in Format operations.

4.3.3.3Recommended values of GAP 3 for 5," drives (from NEC fPD765A manual).

| MFM | MODULATION | SECTOR SIZE | N | R&W<br>GPL | FORMAT<br>GPL |

|-----|------------|-------------|---|------------|---------------|

| 0   | FM         | 128         | 0 | 07         | 09            |

| 0   | FM         | 256         | 1 | 10         | 19            |

| 0   | FM         | 512         | 2 | 18         | 30            |

| 0   | FM         | 1024        | 3 | 46         | 87            |

| 1   | MFM        | 256         | 1 | 0A         | 0C            |

| 1   | MFM        | 512         | 2 | 20         | 32            |

| 1   | MFM        | 1024        | 3 | 2A         | 50            |

| 1   | MFM        | 2048        | 4 | 80         | FO            |

|     |            |             |   |            |               |

#### 4.3.4 IOPB Byte B (Max Cylinder)

IOPB Byte B specifies the maximum cylinder number to be accessed on the selected drive. For an 80 cylinder drive the value will be 79 = 4F hex.

Rev. A2. June 17, 1987 43

4.3.5.IOPB Byte C (Sector Size and Max Head)

Bits 7-4 specify the number of bytes per sector, they represent the variable 'n' recorded in the media header.

n bytes per sector 0001 256 0010 512 0011 1024

Bits 3-1 are reserved and must be set to 0. Bit 0 if set, specifies a drive with two heads. If clear, the drive has only one head or only head 0 will be used on the media.

4.3.6. IOPB Byte D (Max Sector)

IOPB Byte D specifies the drive's maximum sector value. This value is 0 based. For example, on a drive with 8 sectors, the maximum sector is specified as 7. All starting sector numbers for data transfers are specified in the range 0-7. If the SZV bit is set, data transfer is started from the sector with that value on its header. If the SZV bit is clear, one is added to the sector number in the IOPB, and the data transfer is started from that sector, as there is no sector 0 on the media.

4.3.7. IOPB Byte E (Timing)

4.3.7.1. Head Unload Time

Bits 7-4 specify the time to delay before unloading the heads after a data transfer operation has completed. The value is increments of 16ms from 1=16ms to F=240ms. The user may select any value, short times give minimum head wear, but longer access time for a follow-on command which must start with a head load.

4.3.7.2. Step Rate

Bits 0-3 specify the 2's complement of the interval in milliseconds between stepping pulses sent to the drive. 0=16ms, F=1ms. Recommended value for the TOSHIBA ND-08DE drive is 3ms, value D hex.

Rev. A2. June 17, 1987

SECTION 5: COMMANDS

#### 5.0 GENERAL

Each disk command begins a new page. An IOPB diagram follows each command description. The diagrams are highlighted to indicate which bytes the 732 requires for command execution, and which bytes return after execution.

Each 732 IOPB is 26-bytes long. All commands use Bytes 0 through 19H. Reserving all 26 bytes maintains IOPB integrity.

5.0.1 Setting Up the Command

Each IOPB diagram indicates the bytes or fields that must be set for each operation. Certain parameters are essential; others are optional. All commands require the Command, Unit, and Interrupt Level fields to contain valid information. (This is also true for the Interrupt Vector field if the Interrupt Level is not zero.)

5.0.2 Completing the Command

After the 732 completes the command, it updates IOPB Bytes 0 through 3 with ERRS, DONE, a Completion Code, and an internal status. The 732 only updates the entire IOPB if Auto-update (AUD) is enabled, an error occurs, or if Read Parameters, Report Current Address or Read Status commands are executed. If AUD is set, and no errors occur, the 732 sets DONE, posts a Completion Code of zero in Byte 1, and disk drive status information in Byte 2; for any command that DMAs data to/from memory, the 732 updates the data address to point to the last address plus one of the transfer. See Table 5-1.

STATUS ACTION

AUD Clear/No Error732 updates Bytes 0-3 with ERRS, DONE, Occurs Completion Code, and internal status

AUD Set/No Error Occurs732 updates entire IOPB

AUD Clear/Error Occurs732 updates the entire IOPB

AUD Clear/A Read Params732 updates the entire IOPB Report Current Address or Read Status Command is Executed

TABLE 5-1. 732 COMMAND COMPLETION

Rev. A. February 11, 1987

## 5.1 NO OPERATION

The No Operation (NOP) command is a diagnostic tool. The 732 reads the IOPB and marks it complete.

.

NOP

#### 5.2 WRITE DATA

The 732, after reading and decoding the IOPB, positions the disk drive heads at the target cylinder; it then reads in the data from the host (indicated by the IOPB) and writes the data contiguously to the disk's sequential sectors.

Write Data has two IOPB formats: Normal and Scatter/Gather. A Normal IOPB specifies one contiguous block of host memory to write to the disk. A Gather Write IOPB specifies up to 32 different blocks of host memory to be placed in contiguous sectors on the disk (See Section 8.11).

If the BS bit is set in IOPB Byte 5, the high and low byte in each word are swapped.

#### WRITE DATATAPE

#### 5.3 READ DATA

The 732, after reading and decoding the IOPB, positions the disk drive heads at the target cylinder, then reads the disk data indicated by the IOPB, and writes the data in host memory.

Read Data has two IOPB formats: Normal and Scatter/Gather. A Normal IOPB specifies one contiguous block of host memory that is used when placing the data from the disk. A Scatter Read IOPB specifies up to 32 different blocks of host memory where the disk data will be placed (See Section 8.11).

If the BS bit in IOPB byte 5 is set, the high and low byte in each word are swapped. See Section 4.1.6 for handling of deleted data dependant on the SK bit.

#### READ DATATAPE

5.4 REPORT CURRENT ADDRESS (Floppy only)

The 732 selects the disk drive, reads the first good header field, and returns the address to the host via the IOPB; it updates the IOPB regardless of AUD's status.

**REPORT CURRENT ADDRESS**

#### Rev. A. February 11, 1987

5.5 SEEK AND REPORT CURRENT ADDRESS (Floppy only)

The 732 issues a seek to the selected disk drive for the target cylinder. After the drive completes the seek, the 732 reads the first good header field it encounters and reports it to the host via the completed IOPB. The 732 updates the IOPB regardless of AUD's status.

SEEK AND REPORT CURRENT ADDRESS

5.6 POSITION (Tape only)

The position commands move tape forward and reverse over records or files, without transferring data. The 732 uses the count field to set up the number of file marks to search for.

POSITION

#### Rev. A. February 11, 1987

- 5.6.1. Position Subfunction Codes

- CODE DESCRIPTION

- 21 SPACE RECORD REVERSE Spaces reverse one record. Each command places the tape head in the interrecord gap that separates records from one another (see figure 5-1). If the 732 detects a tape mark, tape motion ceases and the controller reports a File Mark Detected On Bead error. The 732 aborts this command if it encounters a BOT marker (Reverse into BOT error).

- 40 FILE MARK SEARCH FORWARD Searches forward the number of file marks specified in the count field. Each count placed the tape heads in the interrecord gap just after the file mark in questions. If this command is issued, and there are no file marks on the tape, the 772 searched until it detects EOT.

- 42 MULTIPLE FILE MARK SEARCH FORWARD Searches forward for a specified number of consecutive file marks. This is especially useful for positioning the tape heads at the logical end of tape (usually indicated by several consecutive file marks). This command follows the same completion rules as File Mark Search Forward.

#### FIGURE 5-1. TYPICAL TAPE FORMAT

#### 5.7 DRIVE RESET

5.7.1. Floppy Disk

The 732 issues commands to the disk drive to reset. First it issues a fault clear, and then a recalibrates (return to zero). The IOPB is complete when the recalibrate completes or times out on drives that are ready. The 732 does not wait for the recalibrate to complete on drives that are not ready.

5.7.2.Tape

The 732 issues a drive reset to the QICO2 interface.

DRIVE RESET TAPE

- 5.7.3 Drive Reset Subfunction Codes

- CODE DESCRIPTION

- 00 DRIVE RESET Resets the tape drive by pulsing the reset line. Use this command if a tape runaway condition occurs. Always consider the tape position unknown following a Drive Reset.

- 21 REWIND Moves the tape at high speed in the reverse direction until the BOT marker is detected. The tape drive should indicate it is at BOT or load point. The Rewind command completes immediately, although the tape is still rewinding. To verify the tape drive has completed rewinding, software must issue a Read Drive Status command. The following conditions should be true: BOT set, REW clear, and DRRDY set. (Caution: even if REW is clear, the drive may not be ready [DRRDY clear].)

- 22 OFFLINE Removes the online signal from the QIC-02 interface, causing the drive to write a file mark if the previous command was a write, and to initialise a rewind command. All other commands leave the drive online.

- 24 RETENSION Issues a command to the QICO2 drive to go to the end of tape and rewind to the beginning of medium.

#### 5.8 WRITE CONTROLLER PARAMETERS

This command initializes the 732 with its operational parameters. No default parameters are assumed, but once loaded, the parameters remain stored in the 732 volatile memory until the controller is powered down. Section 4.2 defines how to change the parameters for individual applications; Section 6.6 explains the IRAM checksum.

WRITE CONTROLLER PARAMETERS

### 5.9 WRITE DRIVE PARAMETERS (Floppy only)

This command informs the 732 of the disk drive's physical characteristics. No default values are assumed, but once loaded, the parameters remain stored in the 732 volatile memory until the controller is powered down. See Section 4.3.

The disk address bytes OB-OD specify the maximum cylinder, head and sector on the media.

#### WRITE DRIVE PARAMETERS

#### 5.10 READ CONTROLLER PARAMETERS

The 732 returns the current 732 operational parameters to the host via the IOPB; it verifies the IRAM checksum before completing the transfer regardless of AUD's status. See Section 4.2.

READ CONTROLLER PARAMETERS

5.11 READ DRIVE PARAMETERS (Floppy only)

The 732 returns the disk drive's physical characteristics to the host via the IOPB. The 732 verifies the IRAM checksum before completing the transfer; it updates the IOPB regardless of AUD's status. See Section 4.3.

READ DRIVE PARAMETERS

#### 5.12 READ STATUS BYTES (Tape only)

The 732 reads the QICO2 drive interface's status bytes. It returns drive-specific status and diagnostic information in the IOPB. Consult your drive manufacturer's manual for the definitions for read status 0. This command is always sent to the drive by the controller if an exception occurs. READ STATUS

#### 5.11 WRITE TRACK FORMAT (Floppy only)