# GR 2515 COMPUTER-AIDED TEST SYSTEM SERVICE MANUAL

Publication 2515-0101

Revision 1, Original December 1984

## **REVISION PAGE**

September 1984

PRELIMINARY issued.

December 1984

Revision 1, Original issued.

#### **FOREWORD**

The material in this manual is for informational purposes only and is subject to change without notice. GenRad assumes no responsibility for any errors or for consequential damages that may result from the use or misinterpretations of any procedure in this publication.

# **GenRad**

We warrant that this product is free from defects in material and workmanship and, when properly used, will perform in accordance with applicable GenRad specifications. If within 90 days after original shipment it is found not to meet this standard, it will be repaired or, at the option of GenRad, replaced at no charge when returned to a GenRad service facility. Changes in the product not approved by GenRad shall void this warranty. GenRad shall not be liable for any indirect, special, or consequential damages, even if notice has been given of the possibility of such damages.

THIS WARRANTY IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

GenRad policy is to maintain product repair capability for a period of five years after original shipment and to make this capability available at the then prevailing schedule of charges.

#### **SERVICE POLICY**

After ninety (90) days following original installation, the product will be repaired at our then prevailing schedule of charges.

Your local GenRad office or representative will assist you in all matters relating to product maintenance, such as calibration, repair, replacement parts and service contracts. Field servicing of GenRad system products can be accomplished by any of the following methods:

- By GenRad on a contract specifying a fixed price per period.

- By GenRad on a per call basis with no contract, or

- By the customer, after purchase of spares and service training from GenRad.

July 1980

# CONTENTS

| Paragra                                          |                                                                                                                     | Page                                                |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|                                                  | SECTION I<br>INTRODUCTION                                                                                           |                                                     |

| 1.1                                              | SCOPE AND ORGANIZATION                                                                                              | 1-1                                                 |

| 1.2                                              | GENRAD FIELD SERVICE                                                                                                | 1-1                                                 |

| 1.3                                              | EQUIPMENT RETURN                                                                                                    | 1-2                                                 |

| 1.4                                              | SPECIFICATIONS                                                                                                      | 1-3                                                 |

|                                                  | SECTION II<br>INSTALLATION                                                                                          |                                                     |

| 2.1                                              | INSTALLATION POLICY                                                                                                 | 2-1                                                 |

| 2.2                                              | SWITCHING POWER                                                                                                     | 2-1                                                 |

| 2.3                                              | CRT INSTALLATION                                                                                                    | 2-2                                                 |

| 2.4<br>2.4.1                                     | POWER SUPPLY INSTALLATION Power Fail Option                                                                         | 2-2<br>2-3                                          |

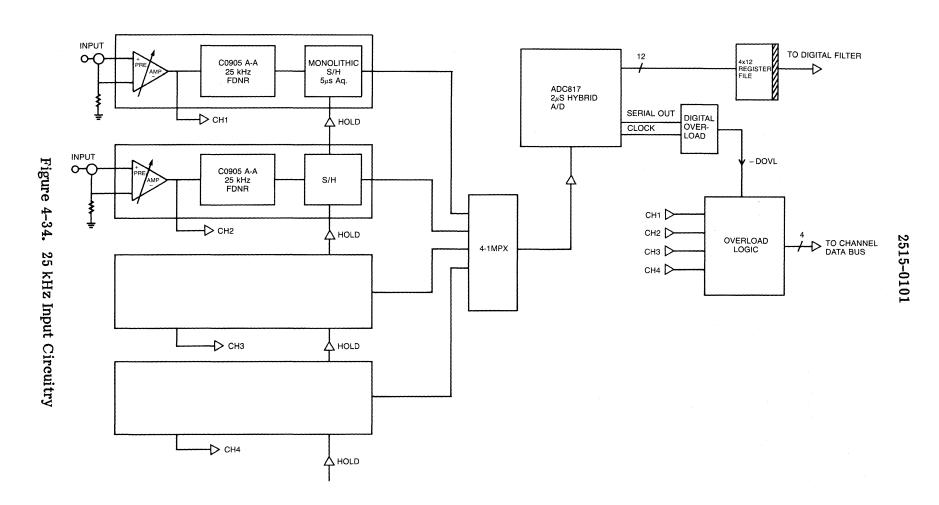

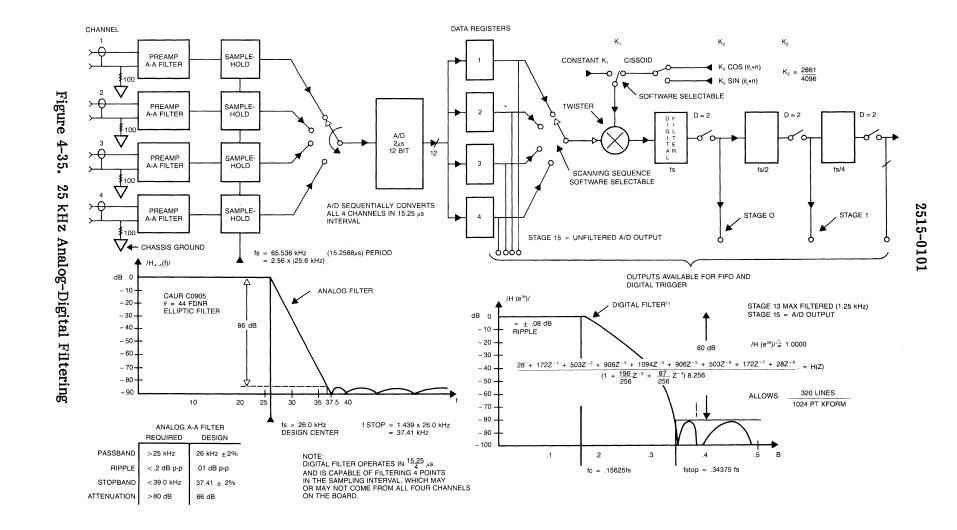

|                                                  | Utility Board<br>Channel Control Board<br>25 kHz Channel Board                                                      | 2-3 2-4 2-4 2-6 2-6 2-6 2-7 2-7 2-7 2-7 2-7 2-7 2-7 |

|                                                  | SECTION III<br>MECHANICAL AND DISASSEI                                                                              | MBLY                                                |

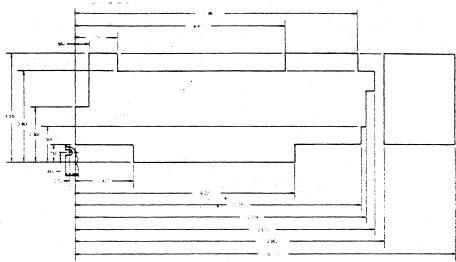

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5 | PHYSICAL DESCRIPTION Chassis Sub-Assembly Power Supply and Line Filter Drive Interconnect Fan and Cooling Backplane | 3-2<br>3-2<br>3-4<br>3-4<br>3-4                     |

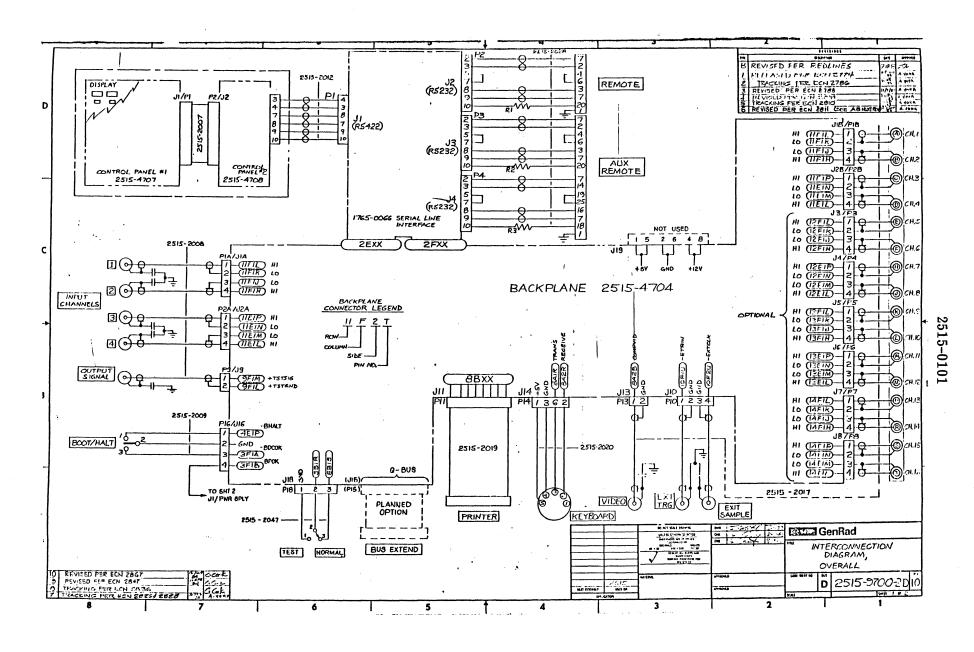

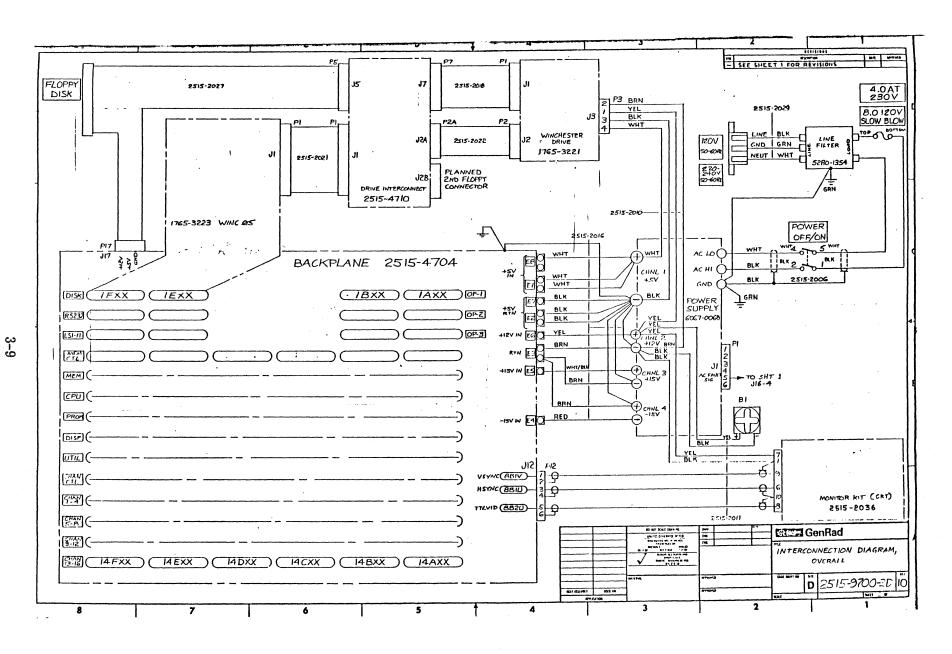

| 3.2                                              | INTERCONNECTIONS                                                                                                    | 3-6                                                 |

| 4.7.2       Memory State Sequencing Circuit       4-36         4.7.3       Microprocessor Hold Logic       4-38         4.7.4       AI Selection, Microprocessor Data Bus Buffer Circuit       4-40         4.7.5       Address Register Circuit       4-41         4.7.6       Temporary Address Register Circuit       4-43         4.7.7       Address Register Incrementer       4-43         4.7.8       Q-Bus Slave and Interrupt Control Circuit       4-44         4.7.9       Memory Data Register       4-47         4.7.10       Q-Bus Memory Mapper       4-47         4.7.11       Q-Bus Transceivers and Address Latches       4-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Paragraph                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                    | Page                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| ### THEORY OF OPERATION  4.1 OVERALL FUNCTIONAL DESCRIPTION  4.2 BUS STRUCTURE  4.2.1 2501 Microprocessor Bus  4.2.2 Microinstruction Bus  4.7  4.2.3 LSI-11 Q-Bus  4.8  4.2.4 Pseudo-Unibus  4.2.5 Analog FIFO Control Bus  4.11  4.2.6 Channel Bus  4-11  4.3 FRONT PANEL PCB ASSEMBLY  4.3.1 Control Panel Boards 1 and 2  4.4  4.5 WINCHESTER/FLOPPY INTERFACE BOARD  4.5 WINCHESTER/FLOPPY INTERFACE BOARD  4.6 LSI-11/23 PROCESSOR BOARD  4.7 MEMORY CONTROLLER BOARD  4.7 MEMORY CONTROLLER BOARD  4.7 MEMORY CONTROLLER BOARD  4.7 Memory State Sequencing Circuit  4.7.1 Source/Destination Decoding  4.7.2 Memory State Sequencing Circuit  4.7.3 Microprocessor Hold Logic  4.7.4 AI Selection, Microprocessor Data Bus Buffer Circuit  4.7.5 Address Register Circuit  4.7.6 Temporary Address Register Circuit  4.7.7 Address Register Incrementer  4.7.8 Q-Bus Slave and Interrupt Control Circuit  4.7.9 Memory Data Register  4.7.10 Q-Bus Memory Mapper  4.7.11 Q-Bus Transceivers and Address Latches                                                                                                                                                                | 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5                                                                   | Top Cover, Removal Bottom Cover, Removal Winchester WINC05, Removal Power Supply, Removal CRT, Removal                                                                                                                                                                                                                                                                             | 3-10<br>3-10<br>3-10<br>3-11<br>3-11                                                 |

| 4.2       BUS STRUCTURE       4-3         4.2.1       2501 Microprocessor Bus       4-3         4.2.2       Microinstruction Bus       4-7         4.2.3       LSI-11 Q-Bus       4-8         4.2.4       Pseudo-Unibus       4-10         4.2.5       Analog FIFO Control Bus       4-11         4.2.6       Channel Bus       4-11         4.3       FRONT PANEL PCB ASSEMBLY       4-14         4.3.1       Control Panel Boards 1 and 2       4-14         4.4       SERIAL LINE INTERFACE BOARD       4-24         4.5       WINCHESTER/FLOPPY INTERFACE BOARD       4-25         4.6       LSI-11/23 PROCESSOR BOARD       4-26         4.7       MEMORY CONTROLLER BOARD       4-27         4.7.1       Source/Destination Decoding       4-33         4.7.2       Memory State Sequencing Circuit       4-36         4.7.3       Microprocessor Hold Logic       4-38         4.7.4       AI Selection, Microprocessor Data Bus Buffer Circuit       4-41         4.7.5       Address Register Circuit       4-43         4.7.6       Temporary Address Register Circuit       4-43         4.7.7       Address Register Incrementer       4-43         4.7.8                  |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                      |

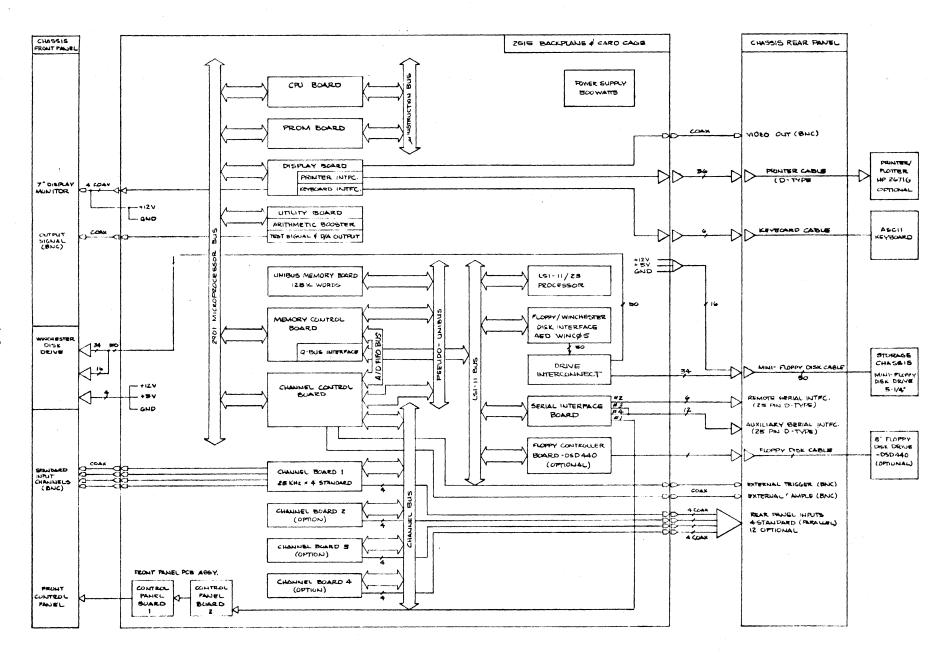

| 4.2.1       2501 Microprocessor Bus       4-3         4.2.2       Microinstruction Bus       4-7         4.2.3       LSI-11 Q-Bus       4-8         4.2.4       Pseudo-Unibus       4-10         4.2.5       Analog FIFO Control Bus       4-11         4.2.6       Channel Bus       4-11         4.3       FRONT PANEL PCB ASSEMBLY       4-14         4.3.1       Control Panel Boards 1 and 2       4-14         4.4       SERIAL LINE INTERFACE BOARD       4-24         4.5       WINCHESTER/FLOPPY INTERFACE BOARD       4-25         4.6       LSI-11/23 PROCESSOR BOARD       4-26         4.7       MEMORY CONTROLLER BOARD       4-26         4.7.1       Source/Destination Decoding       4-33         4.7.2       Memory State Sequencing Circuit       4-36         4.7.3       Microprocessor Hold Logic       4-36         4.7.4       AI Selection, Microprocessor Data Bus Buffer Circuit       4-43         4.7.5       Address Register Circuit       4-41         4.7.6       Temporary Address Register Circuit       4-43         4.7.7       Address Register Incrementer       4-43         4.7.8       Q-Bus Slave and Interrupt Control Circuit       4-47 | 4.1                                                                                                         | OVERALL FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     | 4-1                                                                                  |

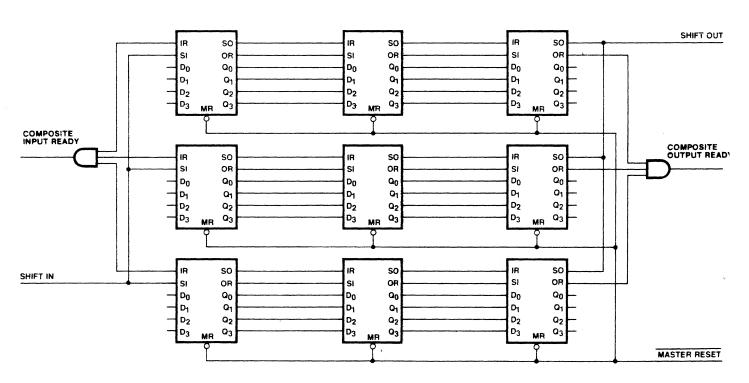

| 4.3.1       Control Panel Boards 1 and 2       4-14         4.4       SERIAL LINE INTERFACE BOARD       4-24         4.5       WINCHESTER/FLOPPY INTERFACE BOARD       4-25         4.6       LSI-11/23 PROCESSOR BOARD       4-26         4.7       MEMORY CONTROLLER BOARD       4-27         4.7.1       Source/Destination Decoding       4-33         4.7.2       Memory State Sequencing Circuit       4-36         4.7.3       Microprocessor Hold Logic       4-36         4.7.4       AI Selection, Microprocessor Data Bus Buffer Circuit       4-40         4.7.5       Address Register Circuit       4-41         4.7.6       Temporary Address Register Circuit       4-43         4.7.7       Address Register Incrementer       4-43         4.7.8       Q-Bus Slave and Interrupt Control Circuit       4-44         4.7.9       Memory Data Register       4-47         4.7.10       Q-Bus Memory Mapper       4-47         4.7.11       Q-Bus Transceivers and Address Latches       4-50                                                                                                                                                                           | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                                                   | 2501 Microprocessor Bus Microinstruction Bus LSI-11 Q-Bus Pseudo-Unibus Analog FIFO Control Bus                                                                                                                                                                                                                                                                                    | 4-3<br>4-7<br>4-8<br>4-10<br>4-11                                                    |

| 4.5 WINCHESTER/FLOPPY INTERFACE BOARD  4.6 LSI-11/23 PROCESSOR BOARD  4.7 MEMORY CONTROLLER BOARD  4.7.1 Source/Destination Decoding  4.7.2 Memory State Sequencing Circuit  4.7.3 Microprocessor Hold Logic  4.7.4 AI Selection, Microprocessor Data Bus Buffer Circuit  4.7.5 Address Register Circuit  4.7.6 Temporary Address Register Circuit  4.7.7 Address Register Incrementer  4.7.8 Q-Bus Slave and Interrupt Control Circuit  4.7.9 Memory Data Register  4.7.10 Q-Bus Memory Mapper  4.7.11 Q-Bus Transceivers and Address Latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                      |

| 4.6 LSI-11/23 PROCESSOR BOARD  4.7 MEMORY CONTROLLER BOARD  4.7.1 Source/Destination Decoding  4.7.2 Memory State Sequencing Circuit  4.7.3 Microprocessor Hold Logic  4.7.4 AI Selection, Microprocessor Data Bus Buffer Circuit  4.7.5 Address Register Circuit  4.7.6 Temporary Address Register Circuit  4.7.7 Address Register Incrementer  4.7.8 Q-Bus Slave and Interrupt Control Circuit  4.7.9 Memory Data Register  4.7.10 Q-Bus Memory Mapper  4.7.11 Q-Bus Transceivers and Address Latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4                                                                                                         | SERIAL LINE INTERFACE BOARD                                                                                                                                                                                                                                                                                                                                                        | 4-24                                                                                 |

| 4.7 MEMORY CONTROLLER BOARD 4.7.1 Source/Destination Decoding 4.7.2 Memory State Sequencing Circuit 4.7.3 Microprocessor Hold Logic 4.7.4 AI Selection, Microprocessor Data Bus Buffer Circuit 4.7.5 Address Register Circuit 4.7.6 Temporary Address Register Circuit 4.7.7 Address Register Incrementer 4.7.8 Q-Bus Slave and Interrupt Control Circuit 4.7.9 Memory Data Register 4.7.10 Q-Bus Memory Mapper 4.7.11 Q-Bus Transceivers and Address Latches 4-20 4-27 4-27 4-28 4-29 4-29 4-29 4-20 4-20 4-21 4-21 4-21 4-21 4-22 4-21 4-21 4-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.5                                                                                                         | WINCHESTER/FLOPPY INTERFACE BOARD                                                                                                                                                                                                                                                                                                                                                  | 4-25                                                                                 |

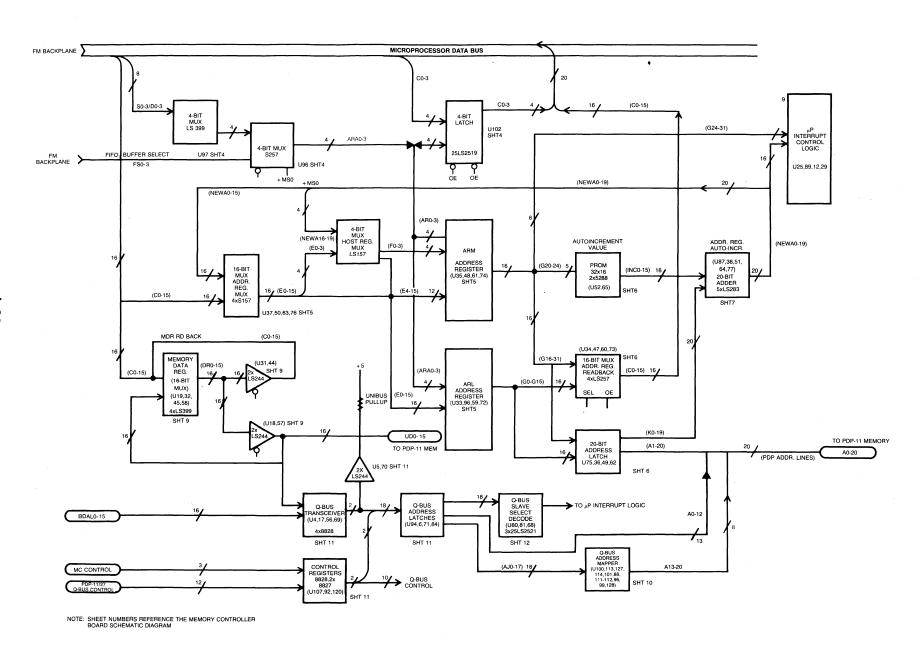

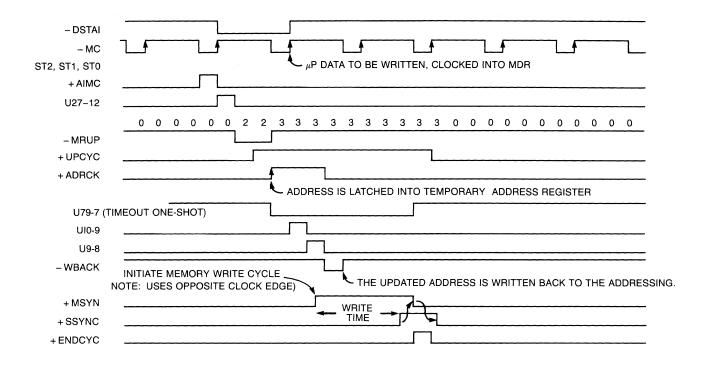

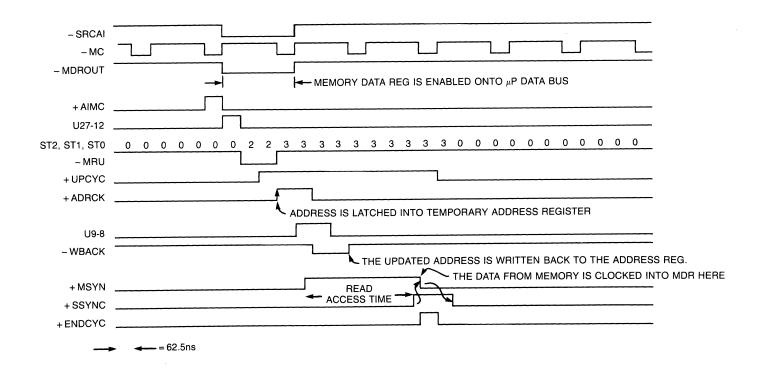

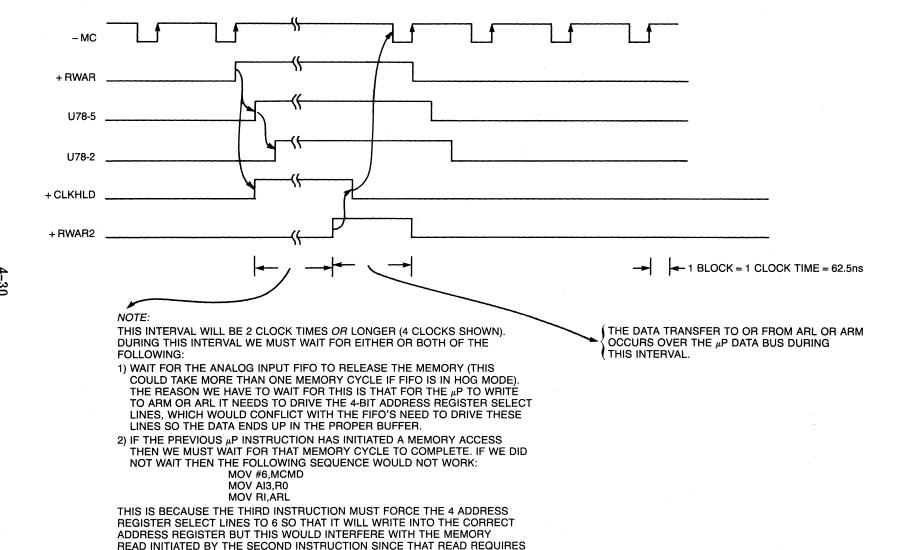

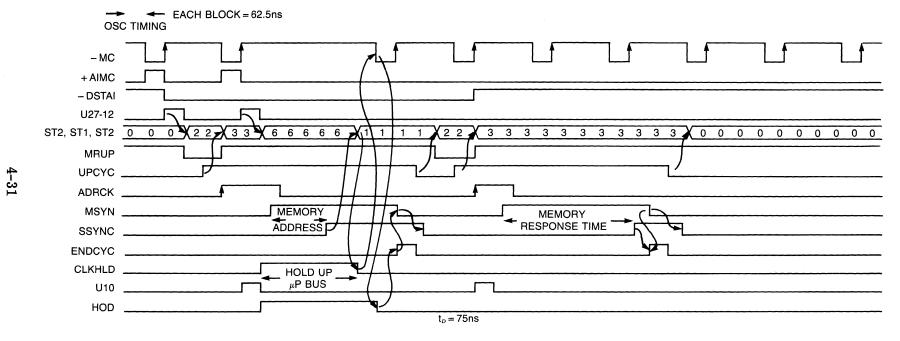

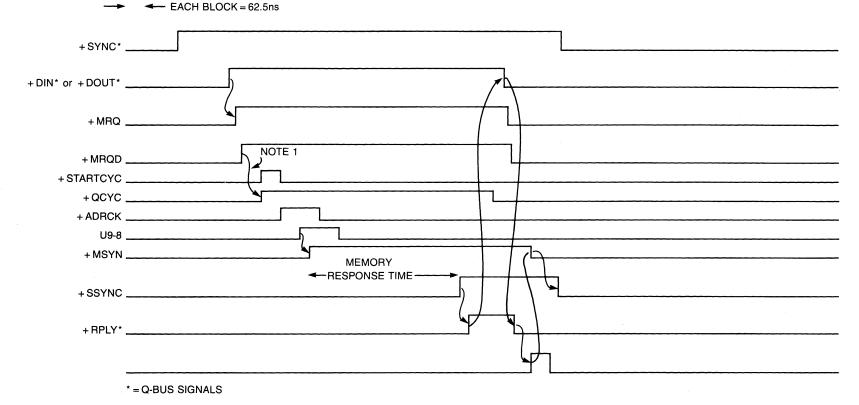

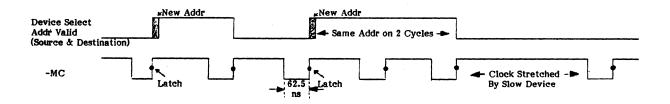

| 4.7.1       Source/Destination Decoding       4-33         4.7.2       Memory State Sequencing Circuit       4-36         4.7.3       Microprocessor Hold Logic       4-38         4.7.4       AI Selection, Microprocessor Data Bus Buffer Circuit       4-40         4.7.5       Address Register Circuit       4-41         4.7.6       Temporary Address Register Circuit       4-43         4.7.7       Address Register Incrementer       4-43         4.7.8       Q-Bus Slave and Interrupt Control Circuit       4-44         4.7.9       Memory Data Register       4-47         4.7.10       Q-Bus Memory Mapper       4-47         4.7.11       Q-Bus Transceivers and Address Latches       4-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.6                                                                                                         | LSI-11/23 PROCESSOR BOARD                                                                                                                                                                                                                                                                                                                                                          | 4-26                                                                                 |

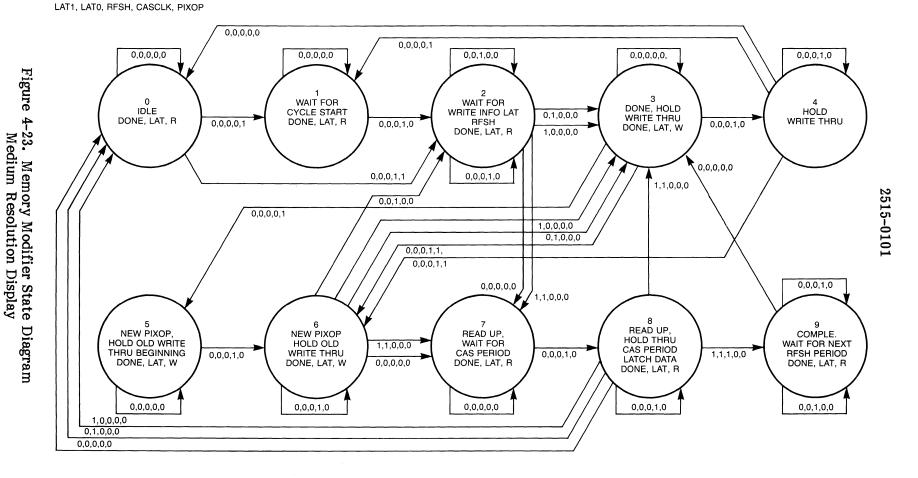

| 4.7.12 Q-Bus Address Decode 4.7.13 Microprocessor Interrupt Logic 4-52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6<br>4.7.7<br>4.7.8<br>4.7.9<br>4.7.10<br>4.7.11<br>4.7.12 | Source/Destination Decoding Memory State Sequencing Circuit Microprocessor Hold Logic AI Selection, Microprocessor Data Bus Buffer Circuit Address Register Circuit Temporary Address Register Circuit Address Register Incrementer Q-Bus Slave and Interrupt Control Circuit Memory Data Register Q-Bus Memory Mapper Q-Bus Transceivers and Address Latches Q-Bus Address Decode | 4-33<br>4-36<br>4-38<br>4-40<br>4-41<br>4-43<br>4-44<br>4-47<br>4-47<br>4-50<br>4-51 |

| 4.7.13 Microprocessor interrupt Logic 4–52 4.8 UNIBUS MEMORY BOARD 4–55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                      |

| Paragraph                                                |                                                                                                                                                                                      | Page                                                         |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

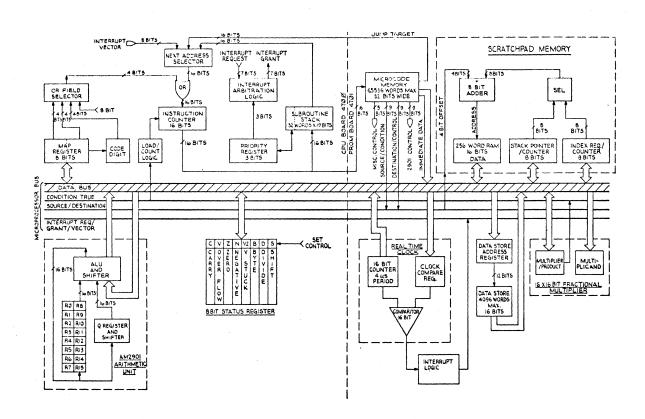

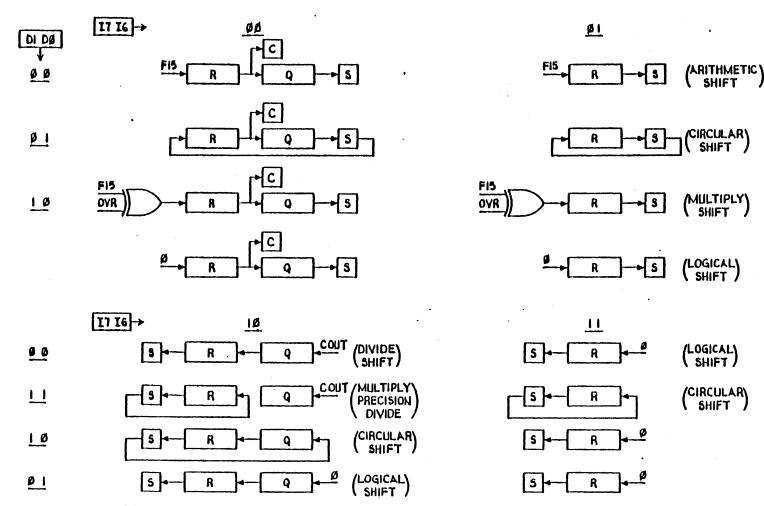

| 4.9<br>4.9.1<br>4.9.2<br>4.9.3<br>4.9.4                  | CPU BOARD Bus Line Electrical Characteristics Microprocessor Basic Instruction Formats Interrupts and System Priority Level Microprocessor Registers                                 | 4-56<br>4-57<br>4-57<br>4-66<br>4-67                         |

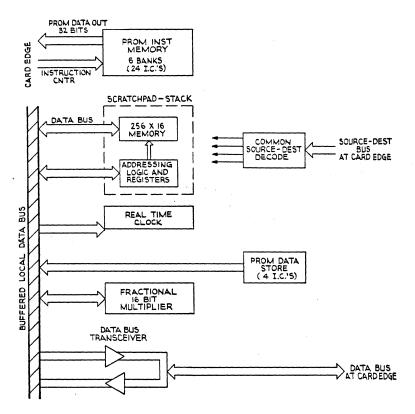

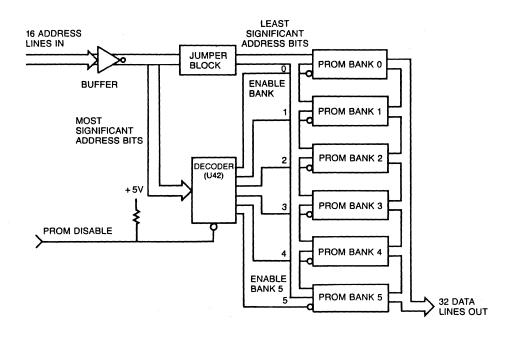

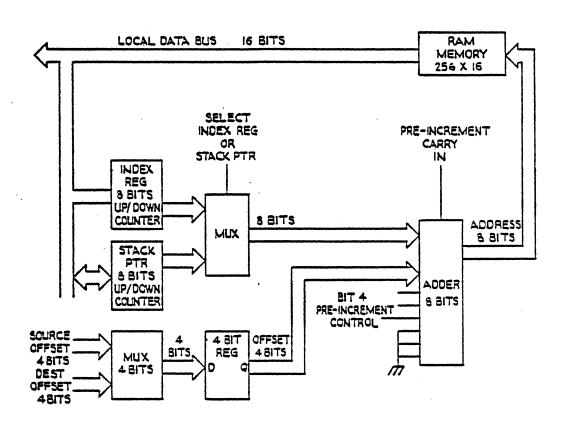

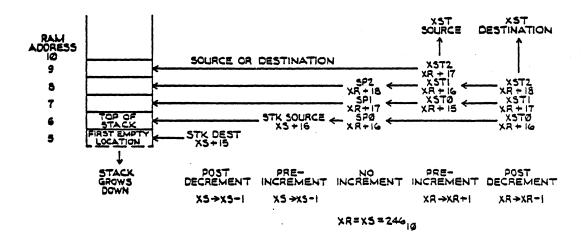

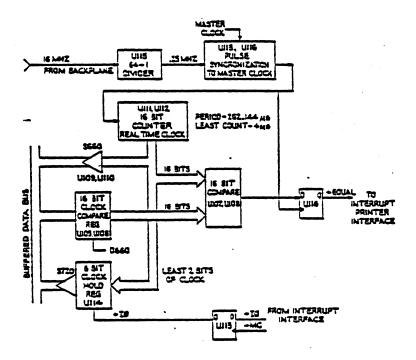

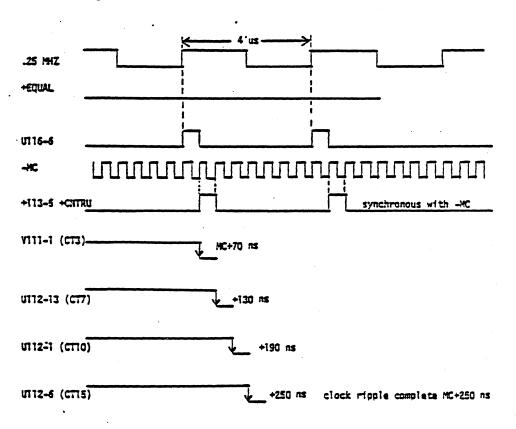

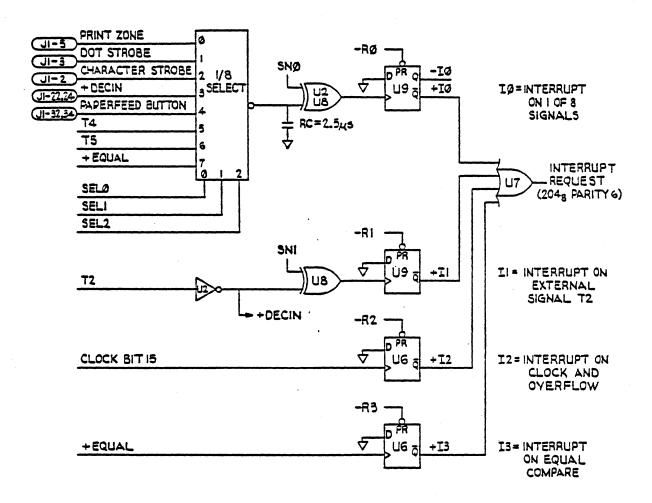

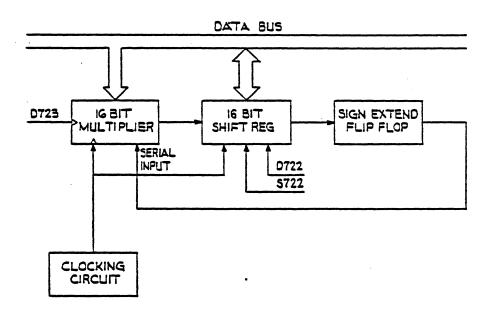

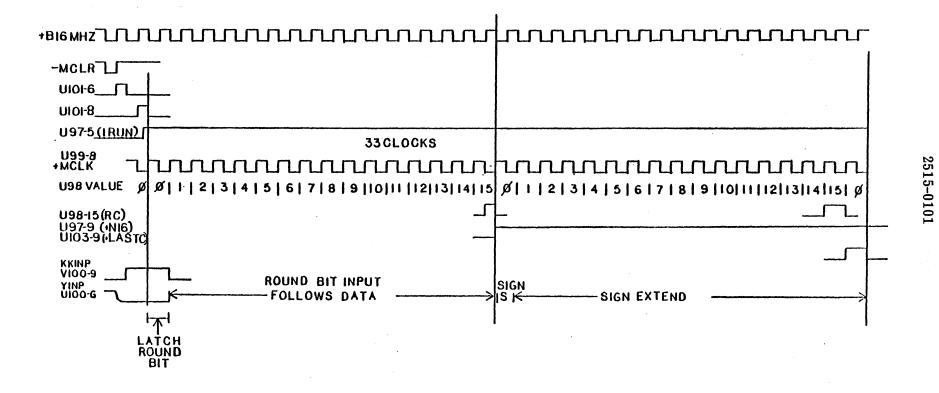

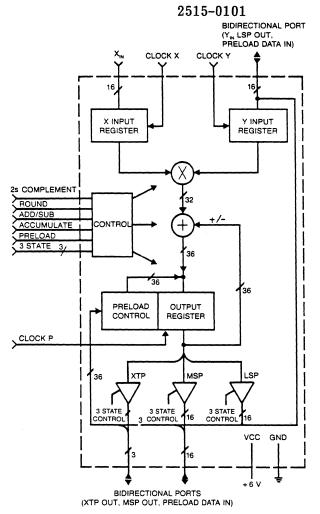

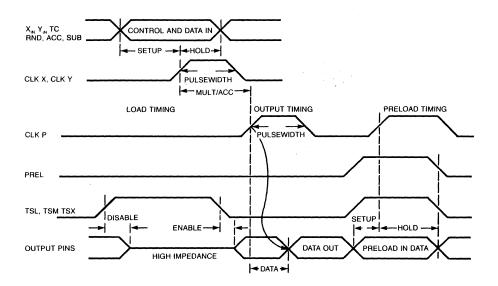

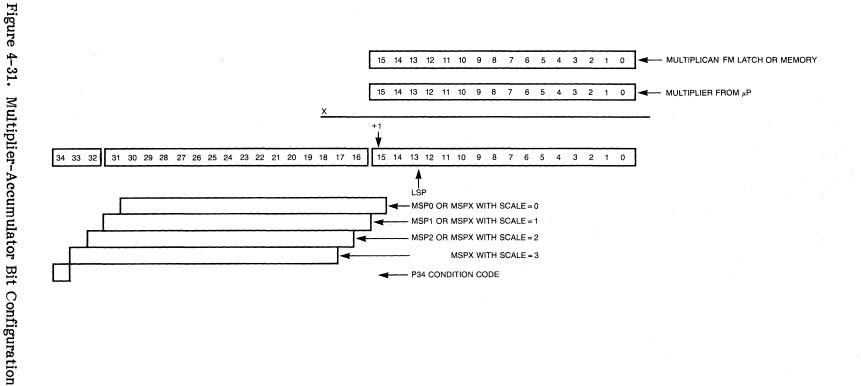

| 4.10.2<br>4.10.3<br>4.10.4                               | PROM BOARD Program Instruction Memory Stack Scratchpad Memory Real Time Clock Interrupt Interface Fractional Multiplier                                                              | 4-73<br>4-73<br>4-75<br>4-79<br>4-81<br>4-83                 |

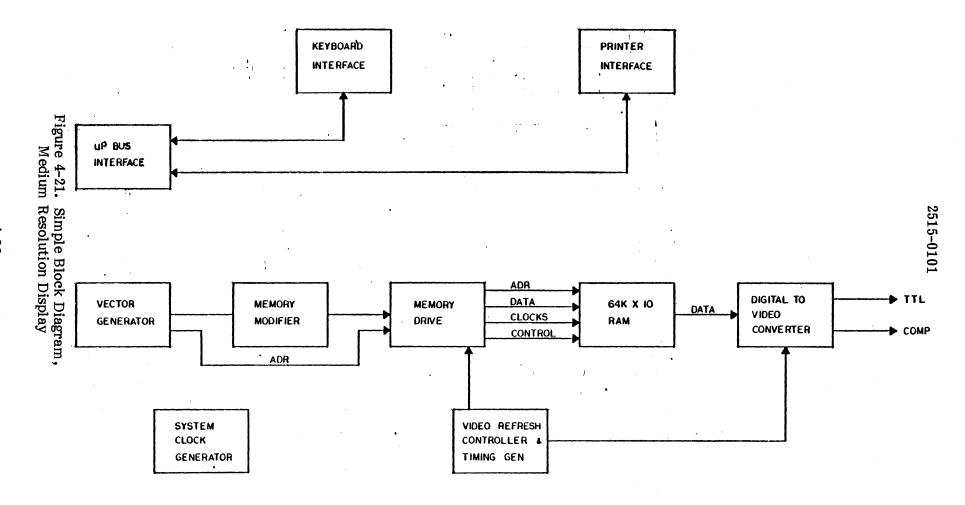

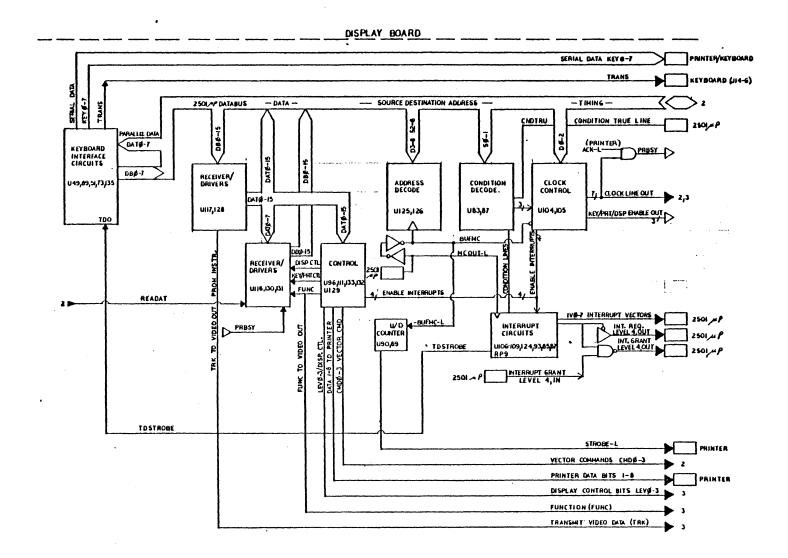

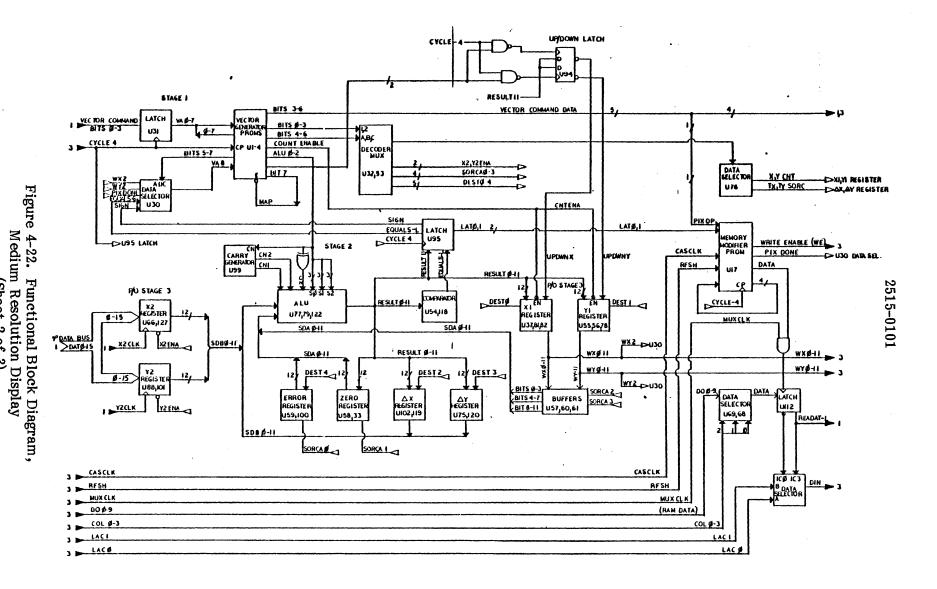

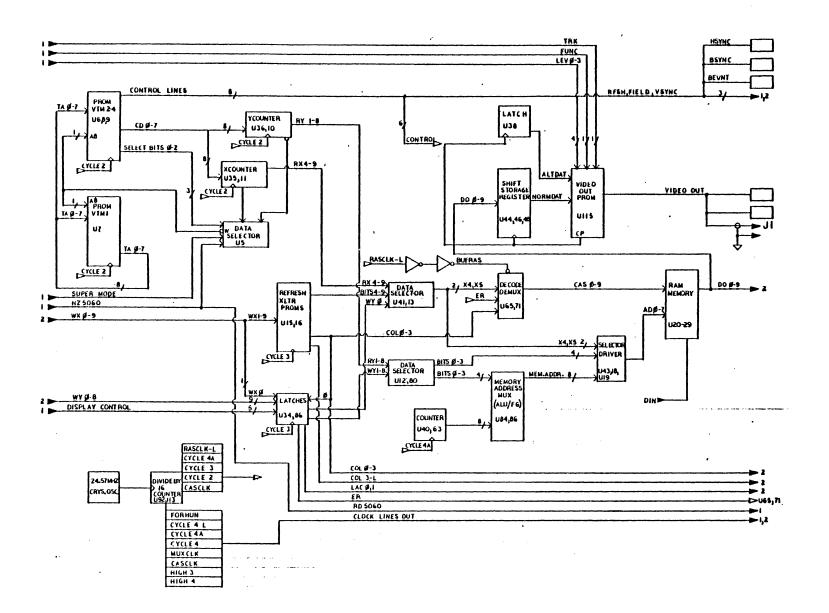

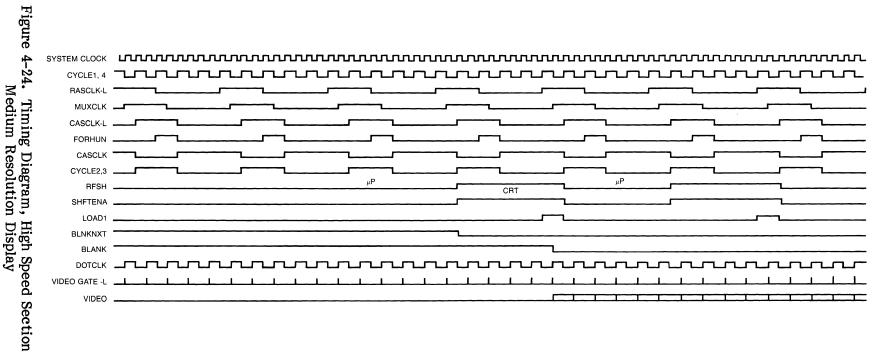

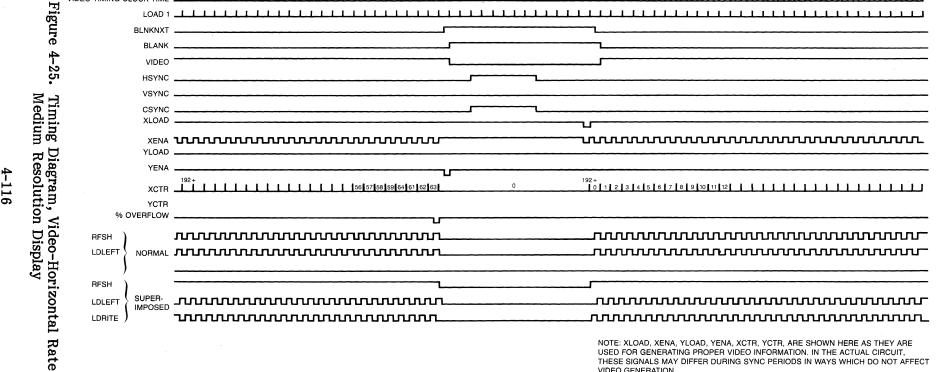

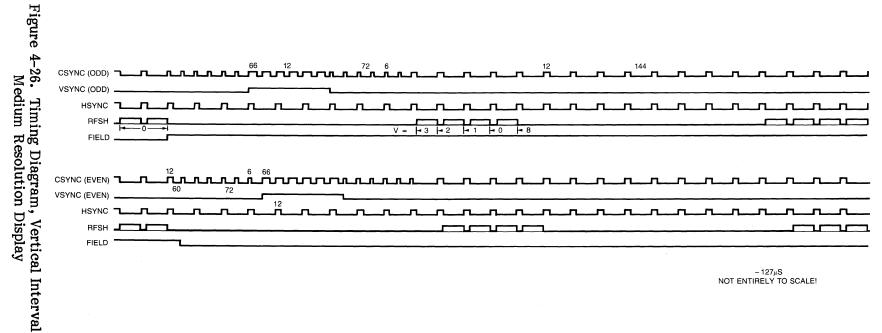

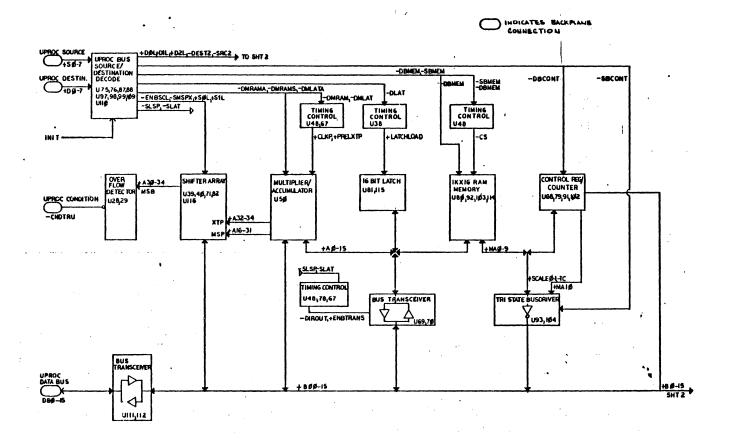

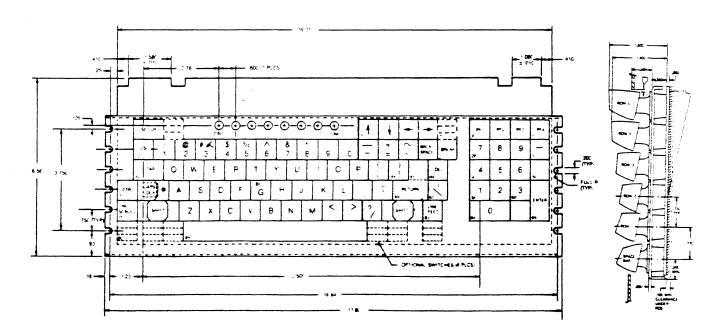

| 4.11.2<br>4.11.3<br>4.11.4<br>4.11.5<br>4.11.6<br>4.11.7 | MEDIUM RESOLUTION DISPLAY Keyboard Interface Printer Interface Interrupt Logic Address Decode Source/Destination Registers Condition - True Vector Generator Video Output and Timing | 4-85<br>4-85<br>4-91<br>4-92<br>4-94<br>4-95<br>4-10<br>4-11 |

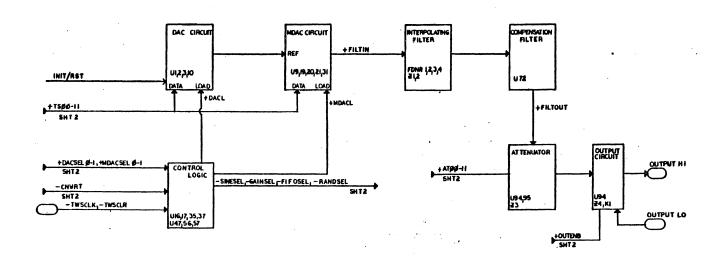

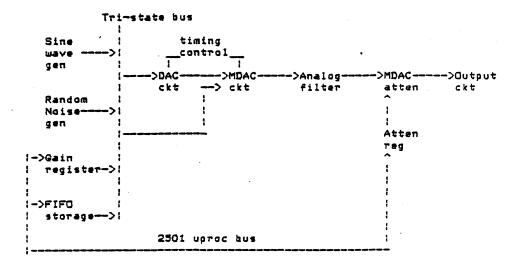

|                                                          | UTILITY BOARD Initialize and Master Clock Booster Section Test Signal Generator                                                                                                      | 4-11<br>4-11<br>4-11<br>4-13                                 |

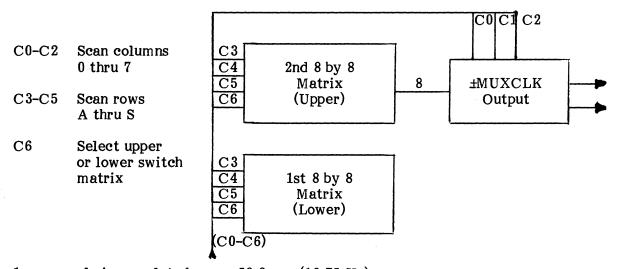

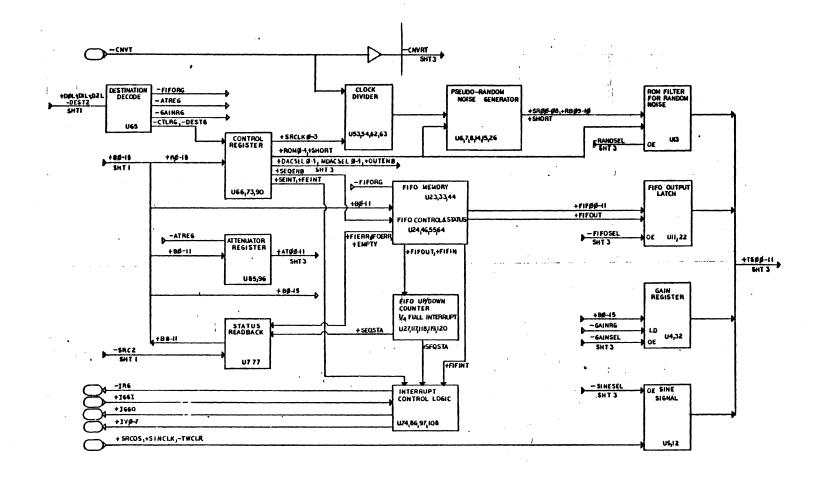

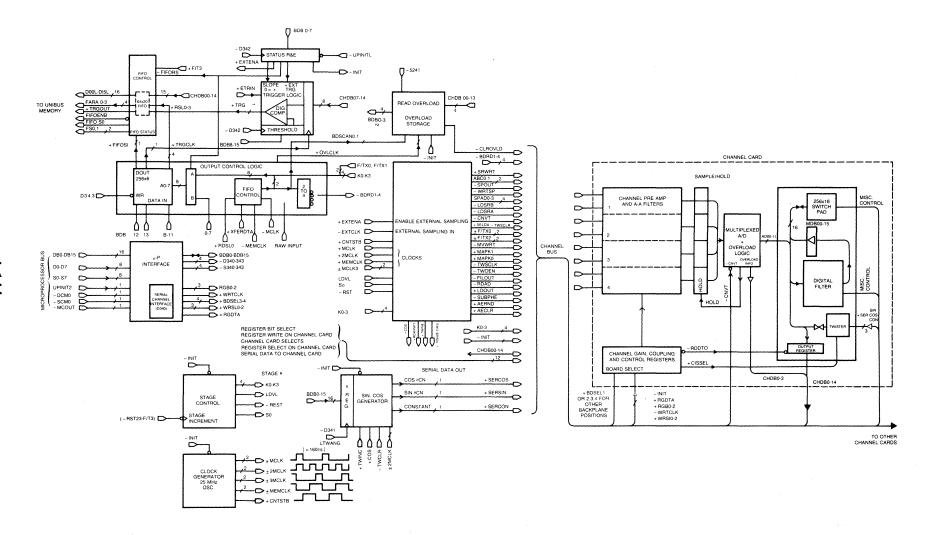

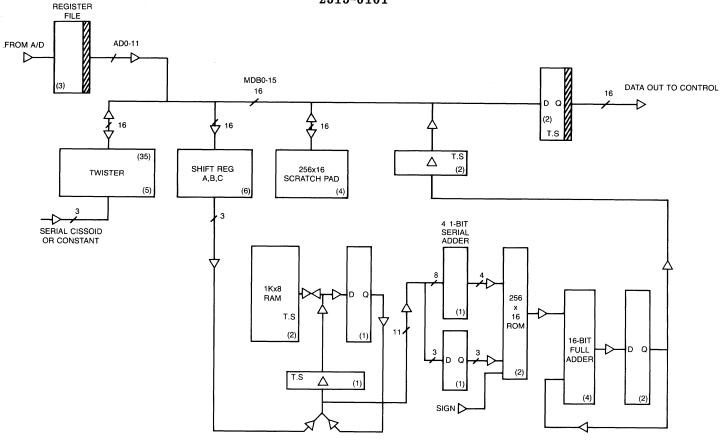

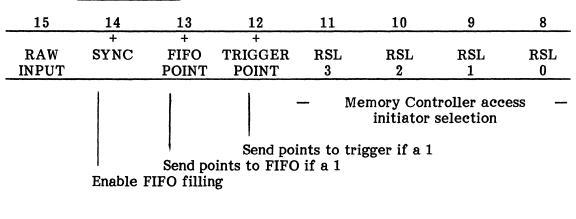

| 4.13.1<br>4.13.2<br>4.13.3<br>4.13.4<br>4.13.5           | Channel Board Signal Processing Sequence<br>Channel Board Digital Processing                                                                                                         | 4-14<br>4-14<br>4-14<br>4-14<br>4-15                         |

|                                                          | SECTION V<br>DIAGNOSTICS                                                                                                                                                             |                                                              |

| 5.1                                                      | INTRODUCTION                                                                                                                                                                         | 5-1                                                          |

| 5.2                                                      | REQUIRED TEST EQUIPMENT                                                                                                                                                              | 5-1                                                          |

| 5.3                                                      | SOFTWARE REQUIRED                                                                                                                                                                    | 5-2                                                          |

| 5.4<br>5.4.1<br>5.4.2                                    | MICROCODE DIAGNOSTICS All Fast Test Sequence User Selectable Test Program                                                                                                            | 5-2<br>5-2<br>5-4                                            |

| Paragra                                                                                                                      | <u>aph</u>                                                                                                                                                                                      | Pe                                                       | age                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 5.5<br>5.5.1<br>5.5.2<br>5.5.3                                                                                               | RT-11 BASED DIAGNOSTICS<br>Loading Instruction<br>Winchester and Floppy (WINFLP) Routines<br>Command Mode Menu                                                                                  | 5-<br>5-                                                 | ·12<br>·12<br>·12<br>·13                                                                     |

| 5.6<br>5.6.1<br>5.6.2<br>5.6.3                                                                                               | FRONT PANEL TEST<br>Loading and Running Instructions<br>Main Menu<br>Troubleshooting                                                                                                            | 5 <b>-</b><br>5-                                         | -58<br>-59<br>-59<br>-67                                                                     |

| 5.7<br>5.7.1<br>5.7.2                                                                                                        | FRONT-END DIAGNOSTIC<br>Loading and Running Instructions<br>Main Menu                                                                                                                           | 5-                                                       | -68<br>-68<br>-68                                                                            |

| 5.8.7<br>5.8.8<br>5.8.9<br>5.8.10<br>5.8.11                                                                                  |                                                                                                                                                                                                 | 5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5- | -81<br>-81<br>-82<br>-83<br>-83<br>-83<br>-85<br>-90<br>-90<br>-90<br>-92<br>-94<br>-96      |

| 5.9<br>5.9.1<br>5.9.2<br>5.9.3<br>5.9.4<br>5.9.5<br>5.9.6<br>5.9.7<br>5.9.8<br>5.9.9<br>5.9.10<br>5.9.11<br>5.9.12<br>5.9.13 | XXDP+ UPDATE PROGRAM DIR Command CLR Command LOAD Command DUMP Command XFR Command SAVE Command MOD Command CORE Command LOCORE Command HICORE Command DELETE Command ZERO Command BOOT Command | 5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5-<br>5- | -100<br>-100<br>-101<br>-101<br>-101<br>-102<br>-102<br>-103<br>-103<br>-103<br>-104<br>-104 |

| 5.9.15                                                                                                                       | REN Command                                                                                                                                                                                     | 5-                                                       | 105                                                                                          |

| 5.9.17 PIP Command       5         5.9.18 READ Command       5         5.9.19 TYPE Command       5         5.9.20 DO Command       5         5.9.21 ASG Command       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-105<br>5-105<br>5-106<br>5-106<br>5-106<br>5-107<br>5-107<br>5-107 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 5.9.18 READ Command       5         5.9.19 TYPE Command       5         5.9.20 DO Command       5         5.9.21 ASG Command       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-105<br>5-106<br>5-106<br>5-106<br>5-107<br>5-107                   |

| 5.9.19 TYPE Command 5.9.20 DO Command 5.9.21 ASG Command 5.9.21 ASG Command 5.9.21 ASG Command 5.9.21 SG Command 5.9.21 | 5-106<br>5-106<br>5-106<br>5-106<br>5-107<br>5-107                   |

| 5.9.20 DO Command 5.9.21 ASG Command 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-106<br>5-106<br>5-106<br>5-107<br>5-107                            |

| 5.9.21 ASG Command 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-106<br>5-106<br>5-107<br>5-107<br>5-107                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-106<br>5-107<br>5-107<br>5-107                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5–107<br>5–107<br>5–107                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5–107<br>5–107                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-107                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| 5.9.25 UPD2 Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-108                                                                |

| 5.10 XTECO - TEXT EDITOR 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-108                                                                |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-110                                                                |

| 5.10.3 XTECO Edit Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-112                                                                |

| 5.10.4 Buffer Pointer Positioning Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-112                                                                |

| 5.10.5 Editing Command String Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-113                                                                |

| 5.10.6 Command Arguments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-113                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-114                                                                |

| 5.10.8 Deletion Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-114                                                                |

| 5.10.9 Insertion Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-114                                                                |