(part of pkg. 062-7124-02)

# The **1240/1241** Logic Analyzer

SERVICE MANUAL, VOL. I

PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

#### **WARNING**

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO. REFER TO OPERATORS SAFETY SUMMARY AND SERVICE SAFETY SUMMARY PRIOR TO PERFORMING ANY SERVICE.

Copyright © 1985, 1987, Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U. S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

# MANUAL REVISION STATUS

PRODUCT: 1240/1241 LOGIC ANALYZER SERVICE MANUAL VOL. I

This manual supports the following versions of this product: All

| REV DATE | DESCRIPTION                                                                                                                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JUL 1985 | First Printing                                                                                                                                                                                           |

| SEP 1985 | Revised Printing: Pagesix, xv, xxi, 2-3, 4-60, 4-65, 4-66, 4-67, 4-69, 4-70, 4-74, 4-75, 5-90, 5-91, 5-92, 5-93, 5-94, 5-95, 5-96, 5-97, 5-98, 5-99, 5-100, 8-209, 8-261. Add Pages5-101, 5-102 & 5-103. |

| MAR 1986 | Revised Printing: Pagesviii, 2-8, 8-262 & 8-266.                                                                                                                                                         |

| JUL 1986 | Revised Printing: Page7-8.                                                                                                                                                                               |

| SEP 1986 | Revised Printing: Page2-6.                                                                                                                                                                               |

| FEB 1987 | Revised Printing: Pages5-5, 7-3, 7-5, 7-6, 7-7 & 7-8. Add Page7-9.                                                                                                                                       |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                          |

| 1        |                                                                                                                                                                                                          |

#### **PREFACE**

The 062-7124-02 manuals package consists of the 1240/1241 Service Manual (volumes 1 and 2) and various addenda. The 1241 Service Manual Addendum, included in the two-volume set, provides additional support for the 1241 Logic Analyzer. Each manual and addendum in the set has its own part number starting with the prefix 070. Manual part numbers are located on the manual title page.

The 1240/1241 Service Manual provides information that allows service technicians to check, troubleshoot, repair, and maintain the 1240 and 1241 Logic Analyzers. When servicing a 1241 Logic Analyzer, use both volumes of the service manual and the 1241 Service Manual Addendum to find complete troubleshooting information. For detailed operating instructions, refer to the 1240/1241 Operator's Manual.

This manual is designed for use by a qualified service technician having moderate experience with digital circuitry. Familiarity with both TTL and ECL logic families is assumed. Familiarity with and the ability to operate standard test instruments used on digital circuitry, such as an oscilloscope or logic analyzer, is also assumed.

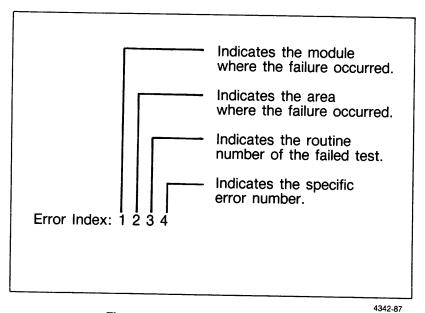

Troubleshooting of the 1240 and 1241 Logic Analyzers is based on the internal diagnostics. The diagnostics produce an on-screen error index message that allows the service technician to quickly identify instrument failure. This manual translates these error indexes into a list of probable causes for instrument failure and lists recommended repair actions.

This manual is divided into 12 sections, found in two volumes. Each section is preceded by a tabbed page for quick reference. Other reference aids included:

- Manual Table of Contents refer to the Table of Contents at the beginning of the manual for a breakdown of sections.

- Section Table of Contents refer to the Table of Contents at the beginning of each section for a detailed breakdown of section contents.

- Diagnostic Page-Bleed Tabs refer to the Troubleshooting and Repair section for page-edge bleed tabs that indicate, by their vertical page position, which module's diagnostic information is currently being accessed.

#### WHAT THIS MANUAL CONTAINS

#### **VOLUME 1**

**Section 1 – GENERAL INFORMATION.** Provides a basic description of the logic analyzers and an overview of the instrument controls and indicators. It also describes the operating and diagnostic menu layouts.

**Section 2 – SPECIFICATIONS.** Lists electrical, mechanical, and environmental specifications of the logic analyzer.

**Section 3 – OPERATING INFORMATION.** Describes the logic analyzer's power requirements, and lists the probe, pack, and I/O connections. Refer to the *1240/1241 Operator's Manual* for complete operating instructions.

- **Section 4 THEORY OF OPERATION.** Illustrates basic operation by introducing logical function blocks and by showing their relationship to the instrument modules. Also, this section describes the system architecture and the difference between the 1240D1 and 1240D2 acquisition cards.

- **Section 5 VERIFICATION AND ADJUSTMENT PROCEDURES.** Contains functional check procedures, adjustment procedures, and performance verification procedures.

- **Section 6 DISASSEMBLY AND INSTALLATION PROCEDURES.** Describes disassembly and reassembly procedures for instrument pieces.

- **Section 7 MAINTENANCE.** Contains information necessary to maintain the logic analyzers, including general precautions and preventive and corrective maintenance items.

- **Section 8 TROUBLESHOOTING AND REPAIR.** Contains information on the diagnostic tests. The diagnostic test descriptions, associated error indexes, and probable failure causes and solutions are grouped by module name with page-bleed tabs. Also provided are recommended repair practices for parts of the instrument not tested by diagnostics.

#### **VOLUME 2**

- Section 9 REPLACEABLE ELECTRICAL PARTS. Contains a list (including Tektronix part numbers) of all replaceable electrical parts in the logic analyzers.

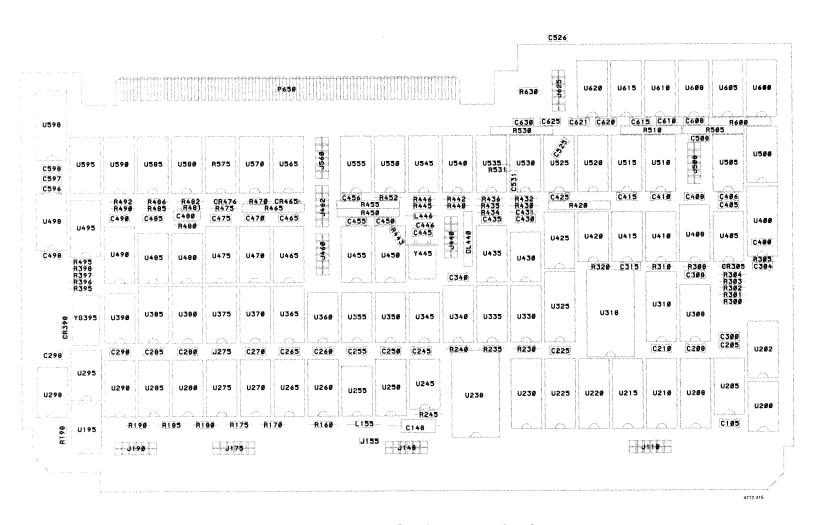

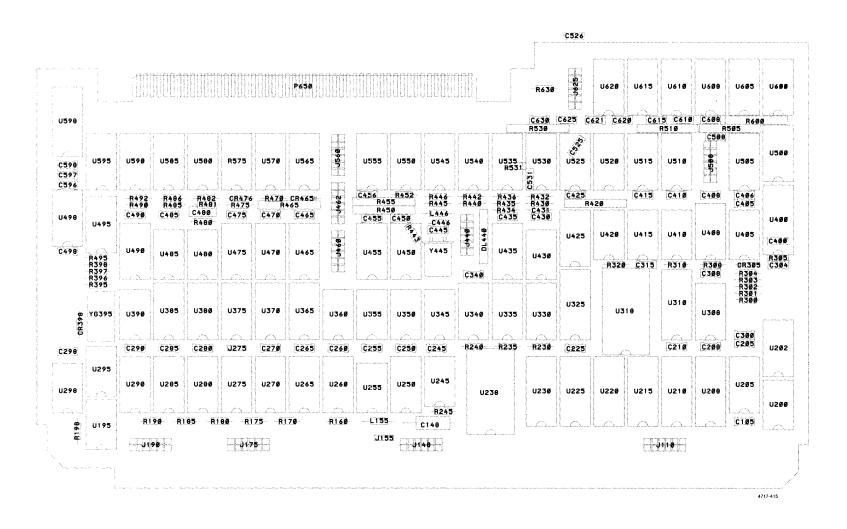

- **Section 10 SCHEMATIC DIAGRAMS.** Contains schematics as well as board and component locator diagrams and tables. The schematic diamond numbers refer to instrument theory discussions located in the *Theory of Operation* section.

- **Section 11 REPLACEABLE MECHANICAL PARTS.** Contains a list (including Tektronix part numbers) of all replaceable mechanical parts in the logic analyzers and provides illustrations to show the location of each of these parts.

- **Section 12 GLOSSARY.** Provides an alphabetical list of signal names and their corresponding descriptions.

# **TABLE OF CONTENTS**

|                      |                                        | Page             |

|----------------------|----------------------------------------|------------------|

| TABLE OF LIST OF ILI | CONTENTS                               | ii<br>XiX        |

|                      | ABLES A'S SAFETY SUMMARY AFETY SUMMARY | XX<br>XX i<br>XX |

| Section 1            | GENERAL INFORMATION                    |                  |

|                      | INTRODUCTION                           | 1-1              |

|                      | 1240 INSTRUMENT RECONFIGURATION        | 1-1              |

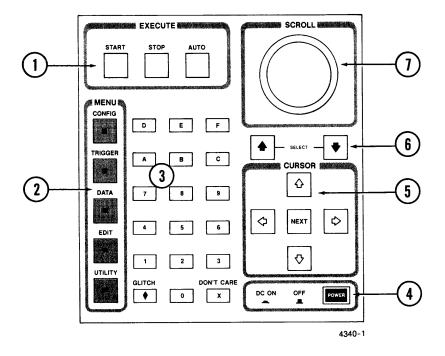

|                      | Execute Keys                           | 1-2<br>1-2       |

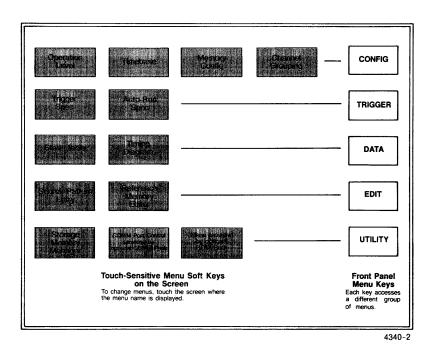

|                      | Menu Keys                              | 1-3              |

|                      | Data Entry Keys                        | 1-3              |

|                      | Power Switch                           | 1-3              |

|                      | Cursor Control Keys                    | 1-3<br>1-3       |

|                      | Scroll Knob                            | 1-4              |

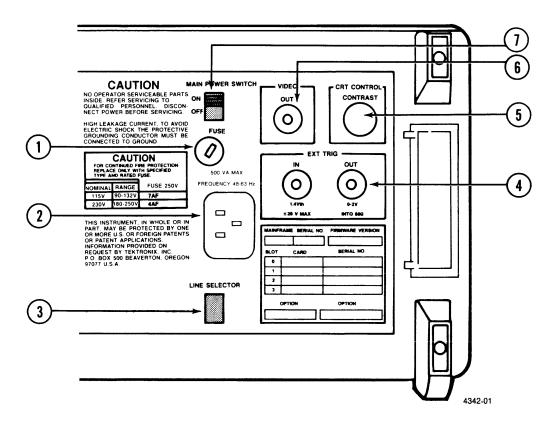

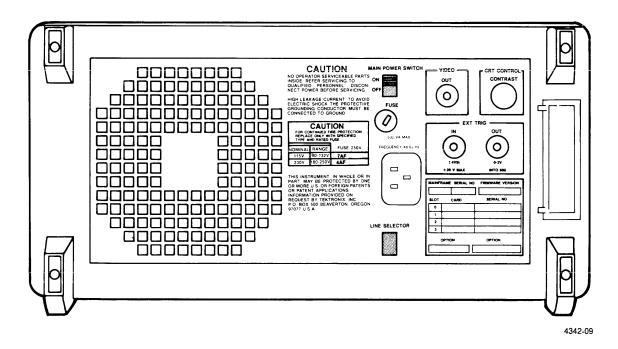

|                      | REAR PANEL DESCRIPTION                 | 1-4              |

|                      | Fuse                                   | 1-4              |

|                      | AC Power ConnectorLine Selector        | 1-5<br>1-5       |

|                      | Ext Trig (In/Out)                      | 1-5              |

|                      | CRT Control (Contrast)                 | 1-5              |

|                      | Video (Out)                            | 1-5              |

|                      | Main Power Switch                      | 1-5<br>1-6       |

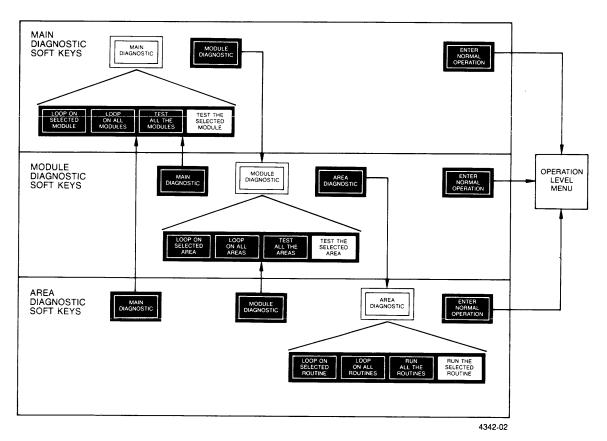

|                      | DIAGNOSTIC MENU OVERVIEW               | 1-6              |

|                      | Main Diagnostic Menu                   | 1-8              |

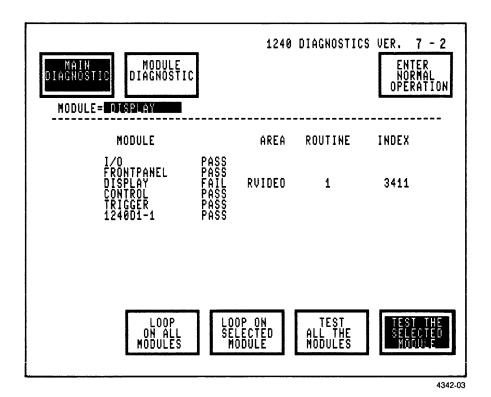

|                      | Module Diagnostic Menu                 | 1-9              |

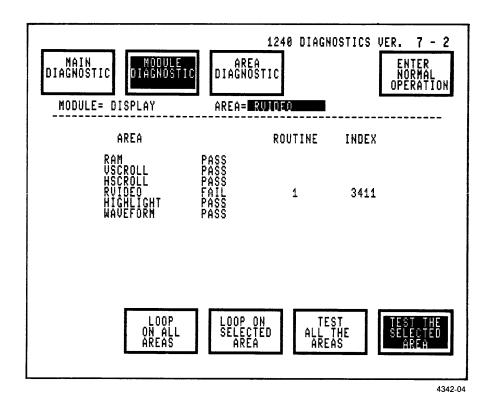

|                      | Area Diagnostic Menu                   | 1-1(             |

| Section 2            | SPECIFICATIONS                         |                  |

|                      | INTRODUCTION                           | 2-1<br>2-1       |

| Section 3            | OPERATING INFORMATION                  |                  |

|                      | POWER REQUIREMENTS                     | 3-1              |

|                      | POWER CORDS                            | 3-2              |

|                      | FUSES                                  | 3-3              |

|                      | POWER-UP DIAGNOSTICS                   | 3-3<br>3-3       |

|                      | ACQUISITION BOARDS                     | 3-6              |

|           | ACQUISITION PROBES                      |

|-----------|-----------------------------------------|

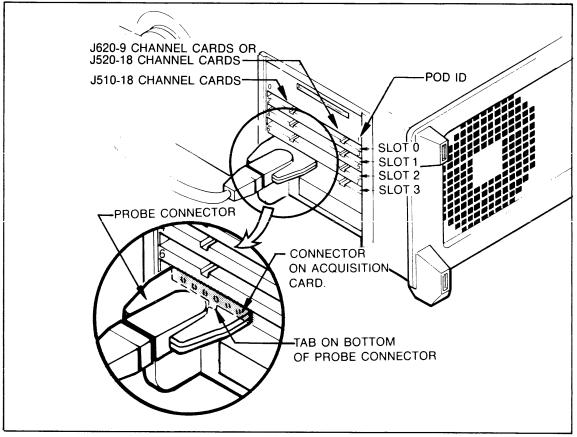

|           | Connection                              |

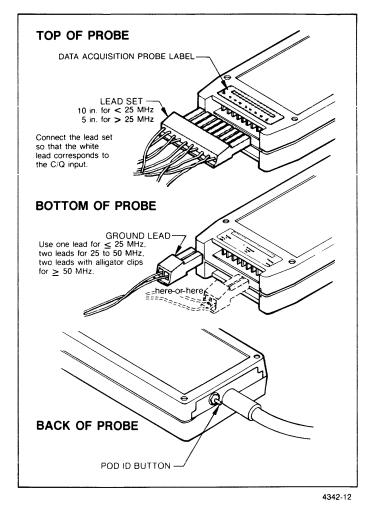

|           | Pod ID                                  |

|           | Lead Set                                |

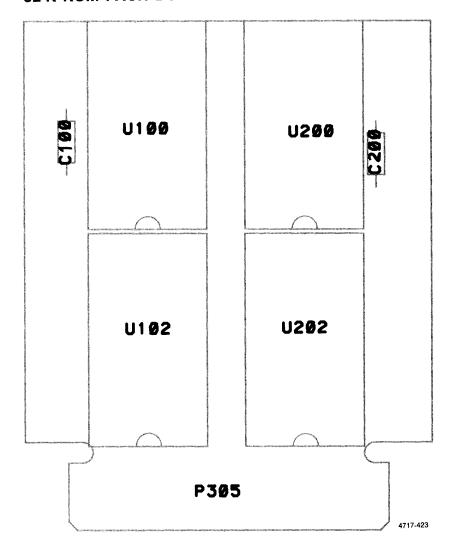

|           | ROM, RAM, AND COMM PACKS                |

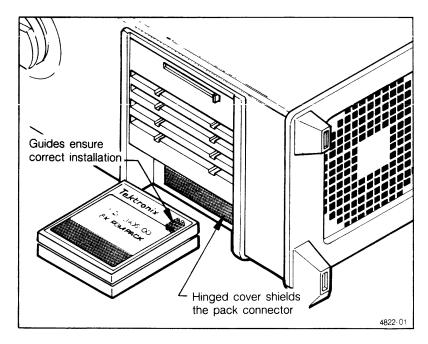

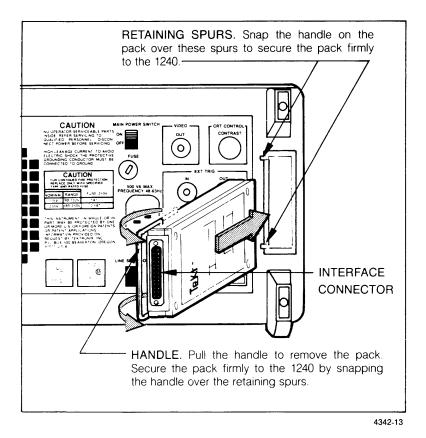

|           | Overview                                |

|           | Pack Installation                       |

|           | ROM/RAM Pack Initialization             |

|           | TEST PATTERN GENERATOR                  |

|           | REMOTE DIAGNOSTICS                      |

|           | TEMOTE DIAGNOSTICS                      |

| Section 4 | THEORY OF OPERATION                     |

|           | SECTION OVERVIEW                        |

|           | LOGIC CONVENTIONS                       |

|           | GENERAL SYSTEM DESCRIPTION              |

|           | Overview                                |

|           | Mainframe                               |

|           | Power Supply                            |

|           | • • •                                   |

|           |                                         |

|           | Display Monitor                         |

|           | LED/Phototransistor Boards and Keyboard |

|           | I/O Processor                           |

|           | Control Processor                       |

|           | ROM AND RAM Packs                       |

|           | COMM Packs                              |

|           | 9-Channel Acquisition Board             |

|           | 18-Channel Acquisition Board            |

|           | Trigger Board                           |

|           | Trigger Generation                      |

|           | Data Storage Control                    |

|           | DETAILED SYSTEM DESCRIPTION             |

|           | Overview                                |

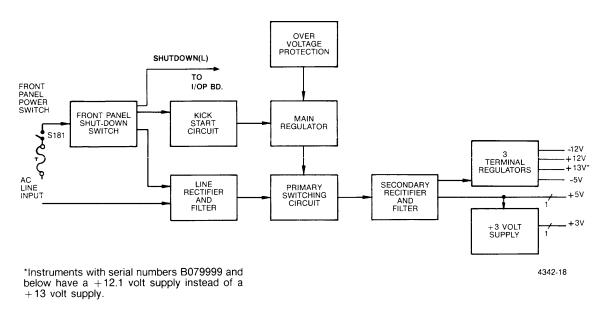

|           | 670-7534-06 POWER SUPPLY THEORY         |

|           | Line Filter And Rectifier (5)           |

|           | Front Panel Shutdown Switch 5           |

|           | Kick Start Circuitry 5                  |

|           | Main Regulator 5                        |

|           | Primary Switching Circuit 5             |

|           | Over-Voltage Protection 5               |

|           | Secondary Rectifier And Filter (5)      |

|           | 3-Terminal Regulators 5                 |

|           | +3 Volt Supply (5)                      |

|           | 670-7534-05 POWER SUPPLY THEORY         |

|           | Line Filter And Rectifier 5a            |

|           | Front Panel Shutdown Switch (5a)        |

|           | Kick Start Circuitry (5a).              |

|           |                                         |

|           | Main Regulator (5a)                     |

|           | POWER SUPPLY BOARD THEORY               |

|                                                                    | Page |

|--------------------------------------------------------------------|------|

| Overview                                                           | 4-11 |

| Primary Switching Circuit 5a                                       | 4-12 |

| Over-Voltage Protection (5a)                                       | 4-12 |

| Secondary Rectifier And Filter (5a)                                | 4-12 |

| 3-Terminal Regulators (5a)                                         | 4-13 |

| +3 Volt Supply (5a)                                                | 4-13 |

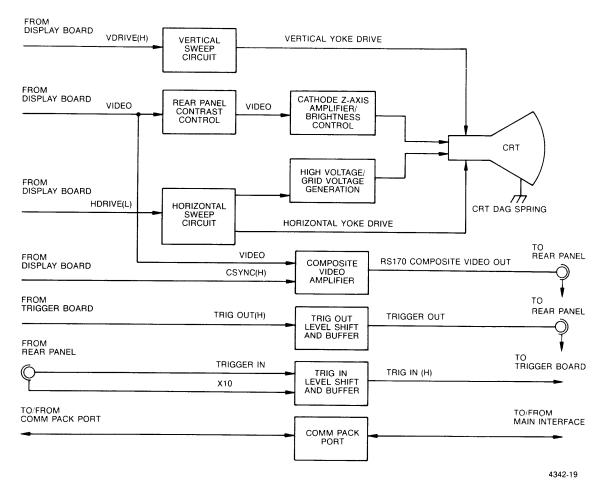

| +3 Volt Supply (5a)  CRT DRIVE BOARD THEORY                        | 4-14 |

| Overview                                                           | 4-14 |

| Vertical Sweep Circuit 4                                           | 4-14 |

| Horizontal Sweep Circuitry 4                                       | 4-15 |

| High Voltage/Grid Voltage Generation 4                             | 4-16 |

| Cathode Z-Axis Amplifier/Brightness Control 4                      | 4-16 |

| Composite Video Amplifier 3,                                       | 4-16 |

| Trig In Level Shift And Buffer 3                                   | 4-16 |

| Trig Out Level Shift And Buffer 3                                  | 4-16 |

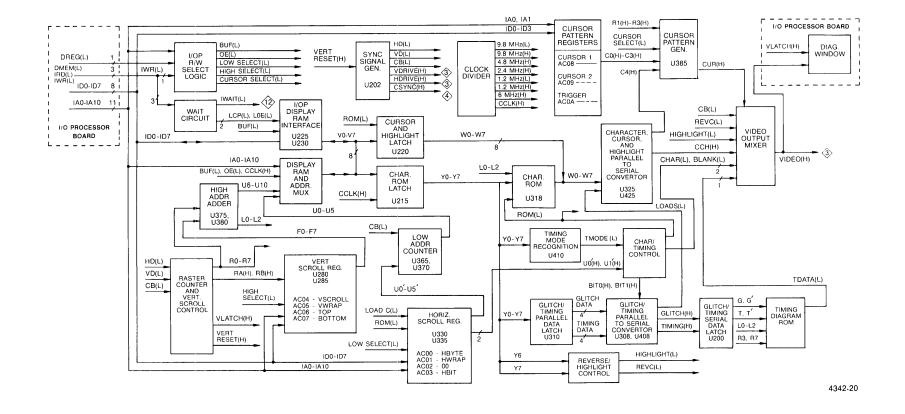

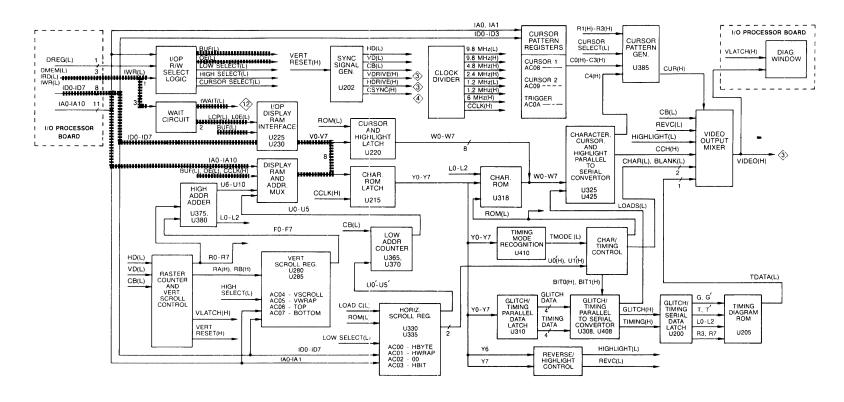

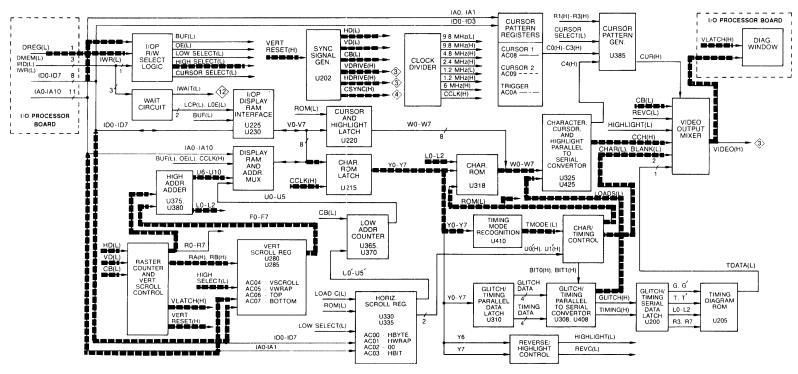

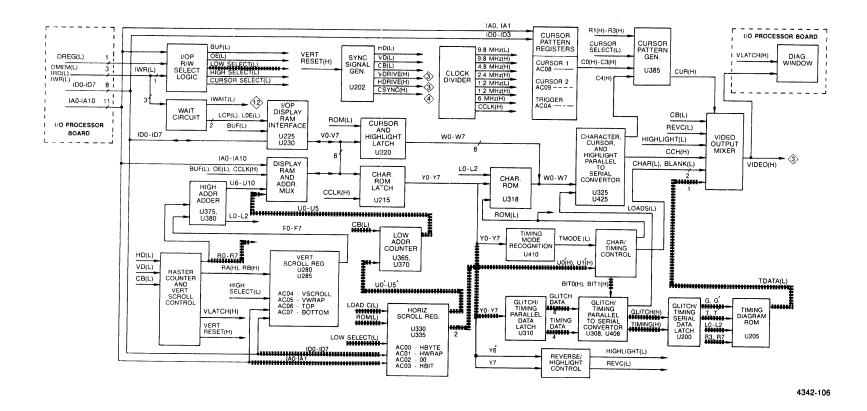

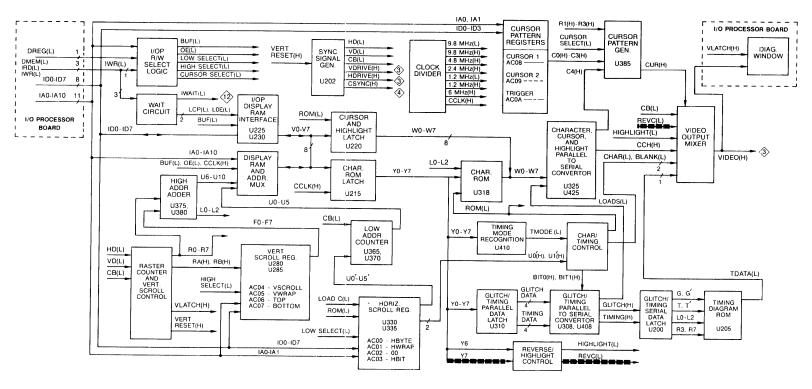

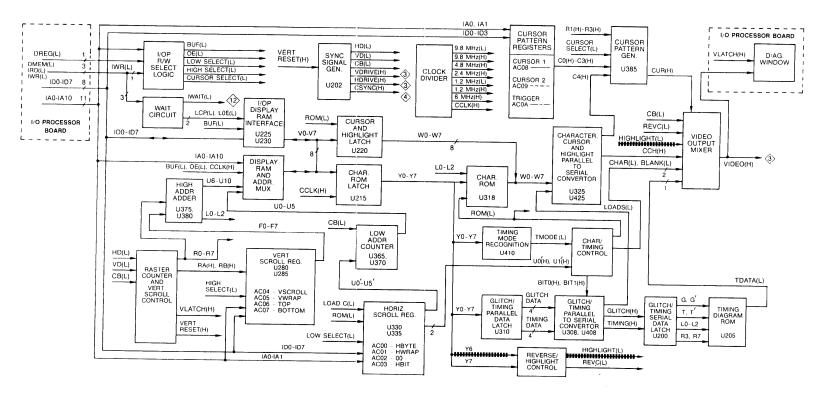

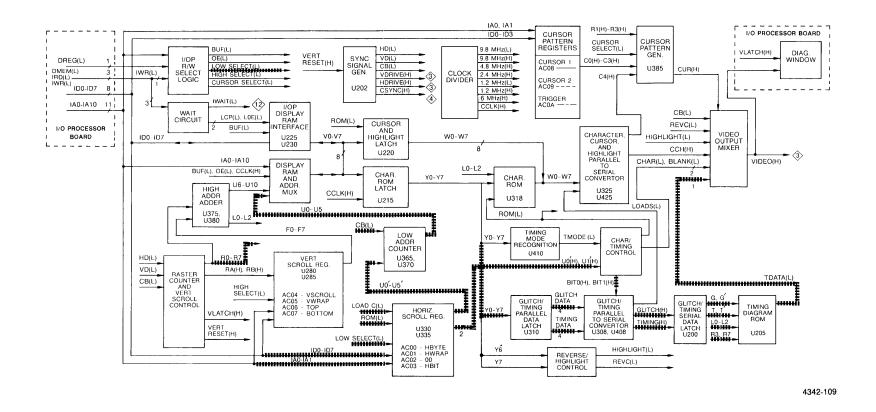

| DISPLAY BOARD THEORY                                               | 4-18 |

| Overview                                                           | 4-18 |

| CIRCUITRY FOR BASIC DISPLAY OPERATIONS                             | 4-19 |

| Clock Divider (17)                                                 | 4-19 |

| I/OP R/W Select Logic (25)                                         | 4-19 |

| Wait Circuit (17)                                                  | 4-19 |

| I/OP-Display RAM Interface (17)                                    | 4-19 |

| Sync Signal Generation (16)                                        | 4-19 |

| Raster Counter And Vertical Scrolling Control (15)                 | 4-19 |

| High Address Adder (15)                                            | 4-20 |

| Low Address Counter (15)                                           | 4-21 |

| Display RAM And Address Multiplexing (15)                          | 4-21 |

| Character ROM And Latch (16)                                       | 4-22 |

| Character, Cursor, And Highlight Parallel-To-Serial Convertor (16) | 4-22 |

| Character/Timing Control I (16)                                    | 4-22 |

| Reverse/Highlight Control (16)                                     | 4-22 |

| Video Output Mixer (17)                                            | 4-23 |

| CIRCUITRY FOR VERTICAL SCROLLING OPERATIONS                        | 4-23 |

| Overview                                                           | 4-23 |

| Vertical Scrolling Registers (15)                                  | 4-23 |

| CIRCUITRY FOR HORIZONTAL SCROLLING OPERATIONS                      | 4-23 |

| Overview                                                           | 4-23 |

| Horizontal Scrolling Registers 15                                  | 4-23 |

| Character/Timing Control II (16)                                   | 4-24 |

| Highlight And Cursor Latch (16)                                    | 4-24 |

| Glitch/Timing Parallel-To-Serial Convertor (16)                    | 4-24 |

| Timing Diagram ROM And Latch (17)                                  | 4-24 |

| Cursor Pattern Generator And Registers (16)                        | 4-24 |

| LED1, LED2, PT1, PT2 BOARDS THEORY `                               | 4-26 |

| Soft Key LED/Phototransistor Matrix (1)                            | 4-26 |

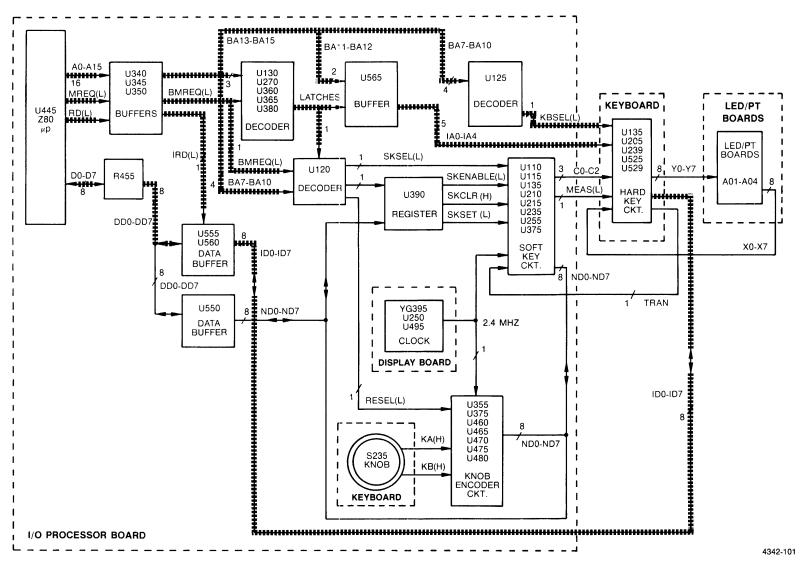

| KEYBOARD THEORY                                                    | 4-26 |

| Hard Keys (2)                                                      | 4-26 |

| Keyboard Readback (2)                                              | 4-26 |

| Menu Key LEDs <2>                                                  | 4-26 |

| Soft Key LED Selection                                             | 4-26 |

|                                                        | Р         |

|--------------------------------------------------------|-----------|

| Phototransistor 60 Hz Filters And Multiplexing 2       | . 4       |

| Front Panel Knob <2>                                   | . 4       |

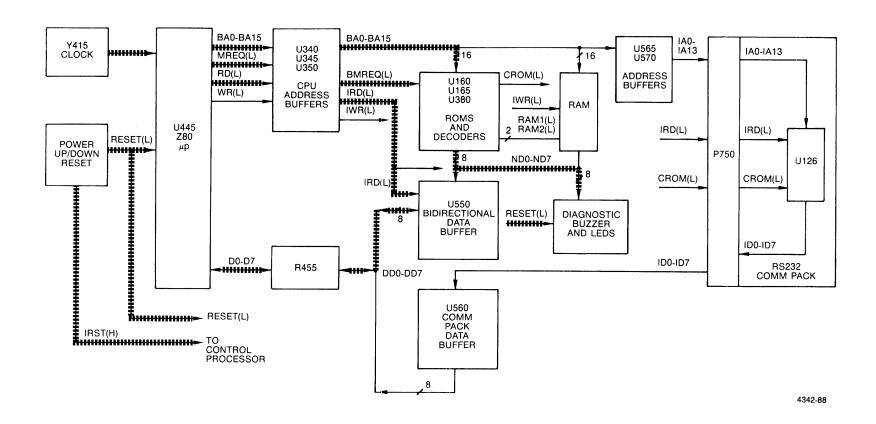

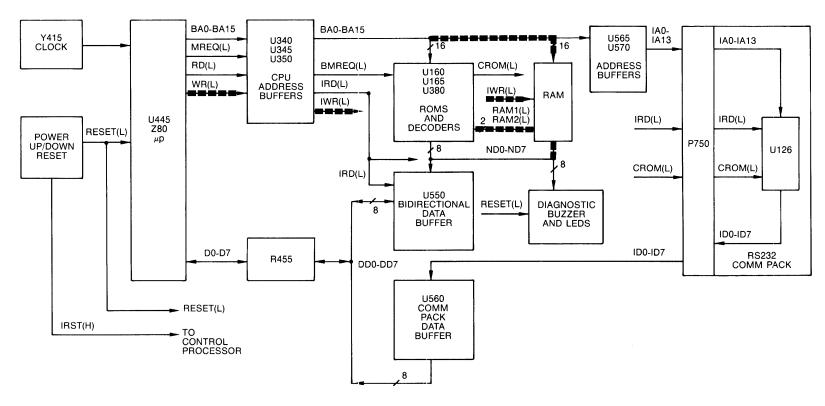

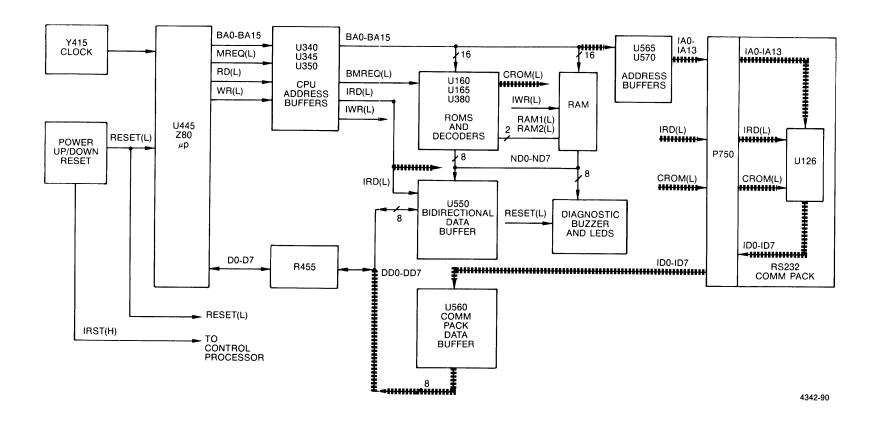

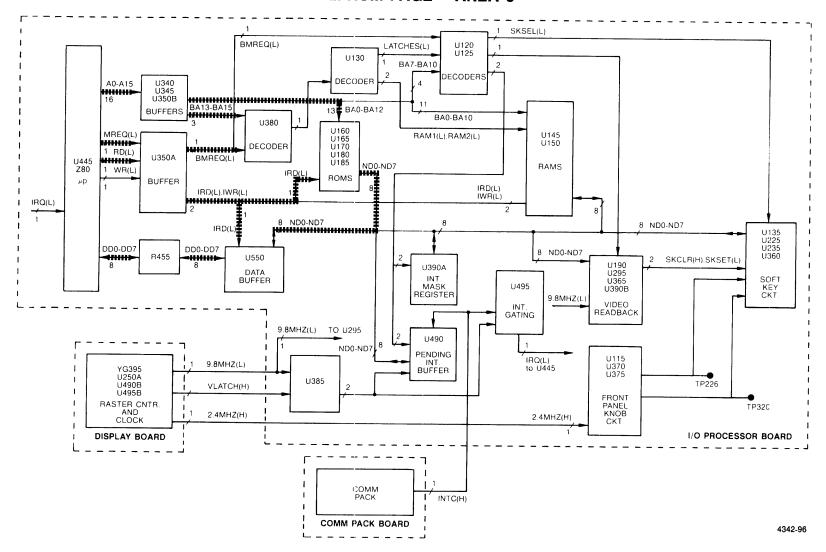

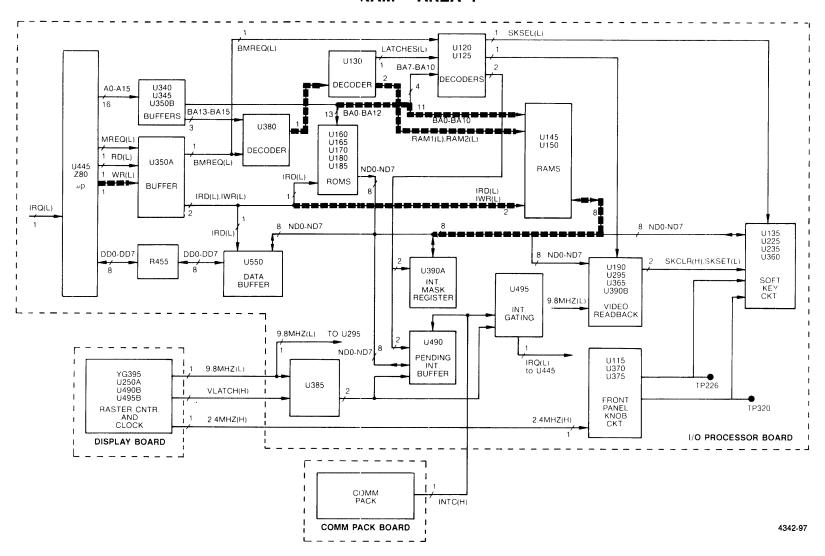

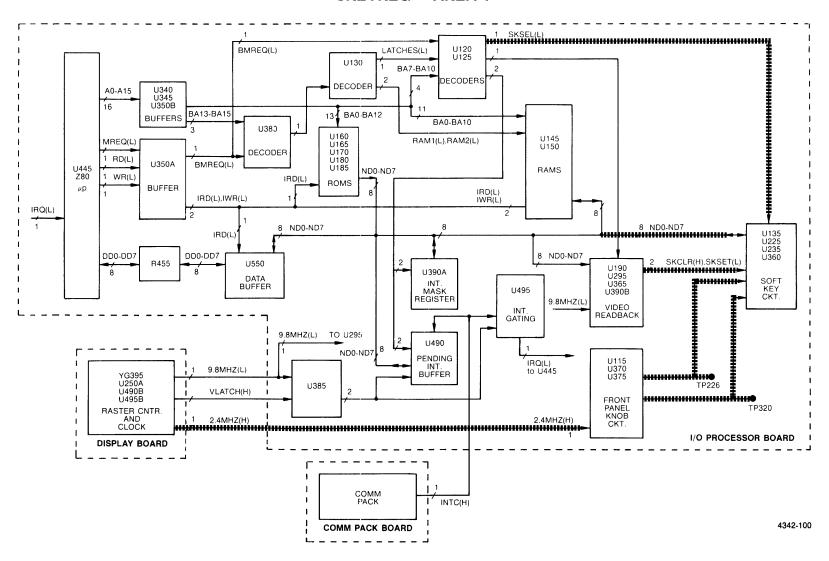

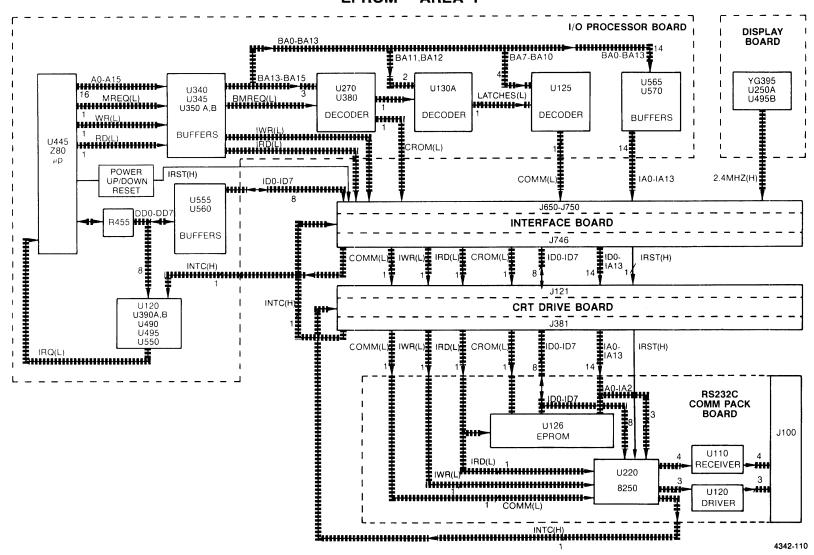

| I/O PROCESSOR BOĂRD THEORY                             | . 4       |

| Overview                                               | . 4       |

| CPU Clock (12)                                         | . 4       |

| Power Up/Down Reset (12)                               | . 4       |

| Z80 CPU And Buffers (12)                               |           |

| Address Bus                                            | . 4       |

| Data Bus                                               | . 4       |

| M1(L)                                                  |           |

| RD(L)                                                  |           |

| WR(L)                                                  |           |

| MREQ(L)                                                | . 4       |

| WAIT(L)                                                |           |

| IRQ(L)                                                 |           |

| RESET(L)                                               |           |

| Wait Circuit 12                                        |           |

| Decode Circuitry 12                                    | . 4       |

| ROMs (12).                                             | . 4       |

| RAM (2)                                                | . 4       |

|                                                        |           |

| Front Panel, COMM Pack, And Display Address Buffers 12 |           |

| Front Panel, COMM Pack, And Display Data Buffers 12    | . 4       |

| Bidirectional Data Buffer (13)                         | . 4       |

| CONP-I/OP Communication Circuitry (13)                 | . 4       |

| Interrupt Mask Register (13)                           | . 4       |

| Interrupt Gating (13)                                  | . 4       |

| Pending Interrupt Buffer (13)                          |           |

| Buzzer And Diagnostic LEDs 13                          | . 4       |

| Video Readback (Diagnostic Window) (13)                |           |

| Soft Key Circuitry 14                                  | . 4       |

| Front Panel Knob Circuitry (14)                        | . 4       |

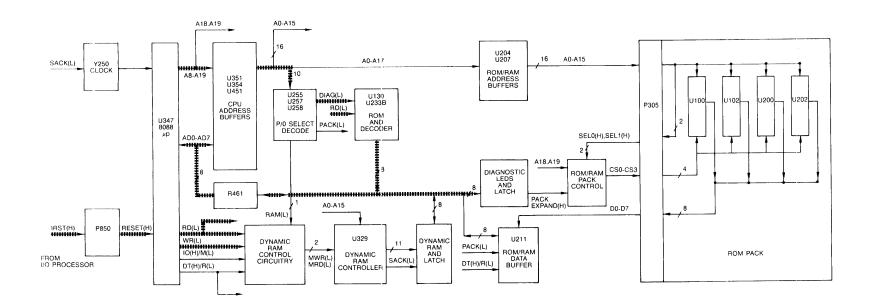

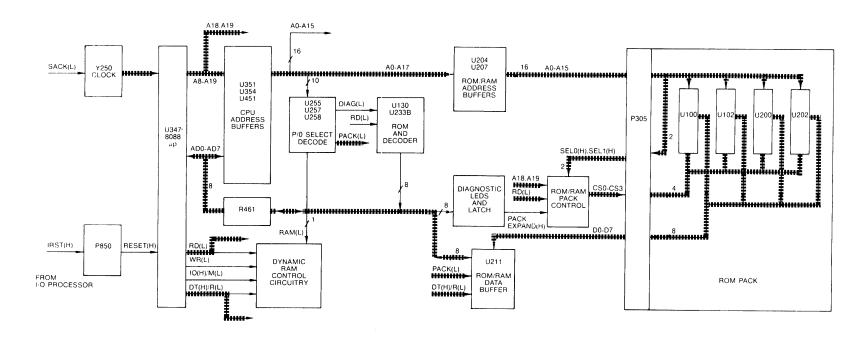

| ONTROL PROCESSOR BOARD THEORY                          |           |

| Overview                                               |           |

| 8088 CPU Clock (9)                                     |           |

| AD0-AD7 Address Bus                                    |           |

| A8-A15 Address Bus                                     | . 4       |

| ALE(H)                                                 | . 4       |

| DEN(L)                                                 | . 4       |

| DT(H)/R(L)                                             |           |

| INTR(L)                                                |           |

| IO(H)/M(L)                                             |           |

| RD(L)                                                  |           |

| READY(H)                                               |           |

| RESET(H)                                               |           |

| WR(L)                                                  |           |

| CPU Address/Data Buffers (9)                           | . 4.      |

| Select Decode 9                                        | 4.        |

| BOMs And BOM Decoder 40                                | , 4.<br>1 |

| ROMs And ROM Decoder 40                                |           |

|                                                     | Page |

|-----------------------------------------------------|------|

| Dynamic RAMs, Controller, And Latch (1)             | 4-41 |

| Instrument Addressing And Control (9)               | 4-42 |

| Instrument Data Buffer (9)                          | 4-43 |

| ROM/RAM Address Buffers (9)                         | 4-43 |

| ROM/RAM Data Buffer 🕎                               | 4-43 |

| ROM/RAM Pack Control 10                             | 4-43 |

| Nonvolatile Memory (1)                              | 4-44 |

| Battery Backup 🕦                                    | 4-44 |

| Diagnostic LEDs And Latch (1)                       | 4-44 |

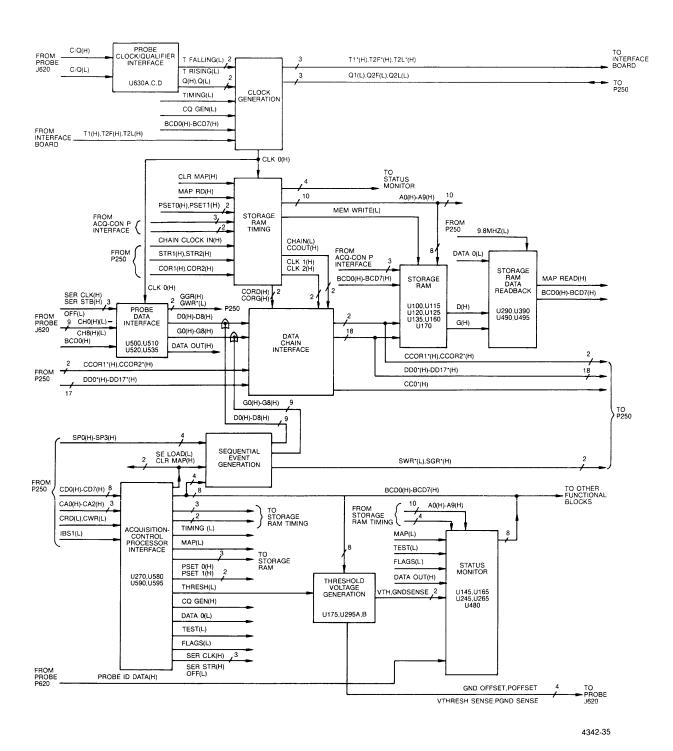

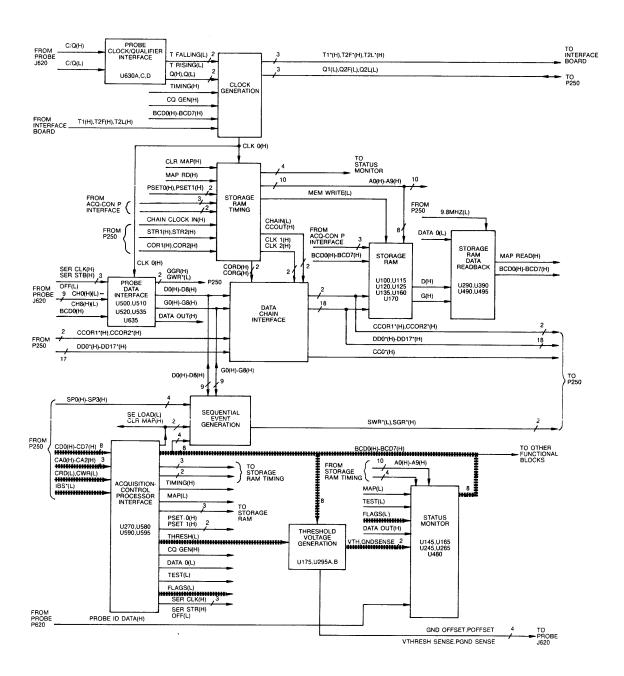

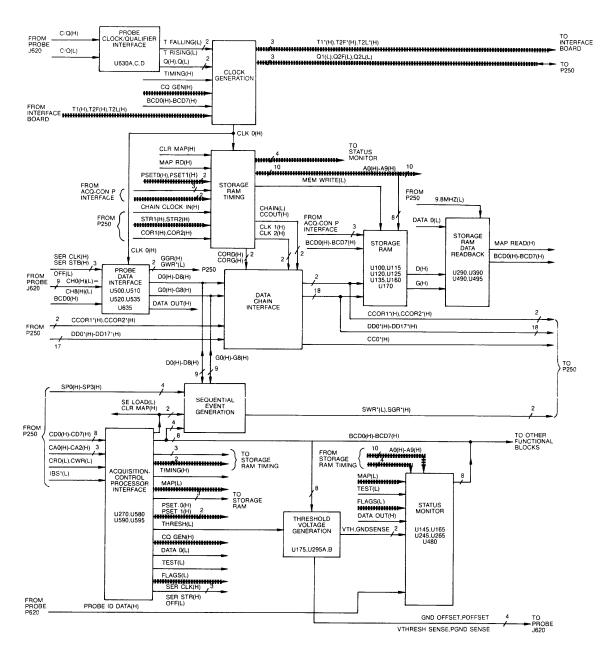

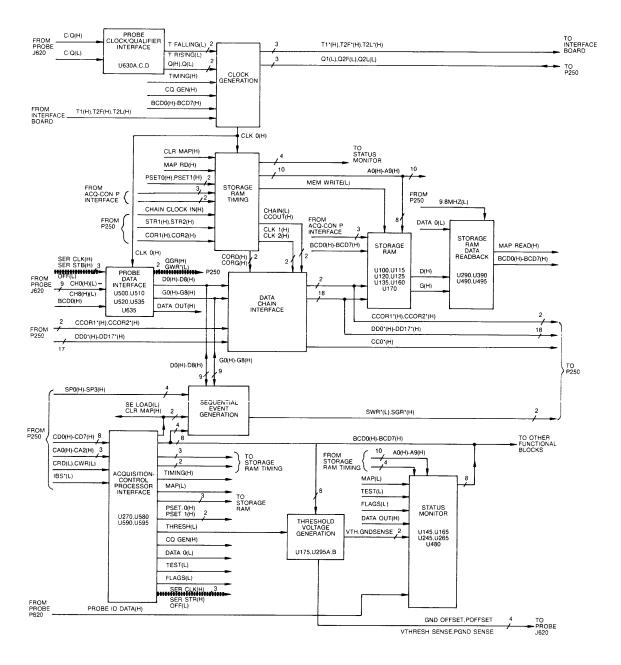

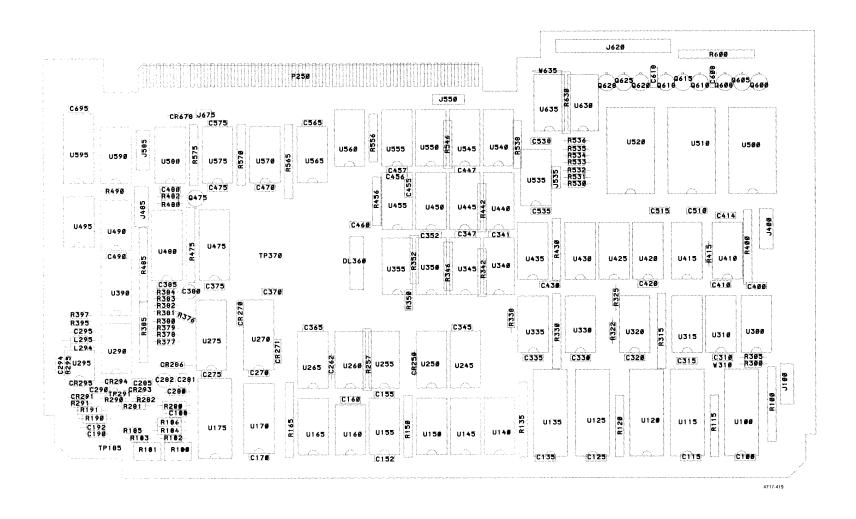

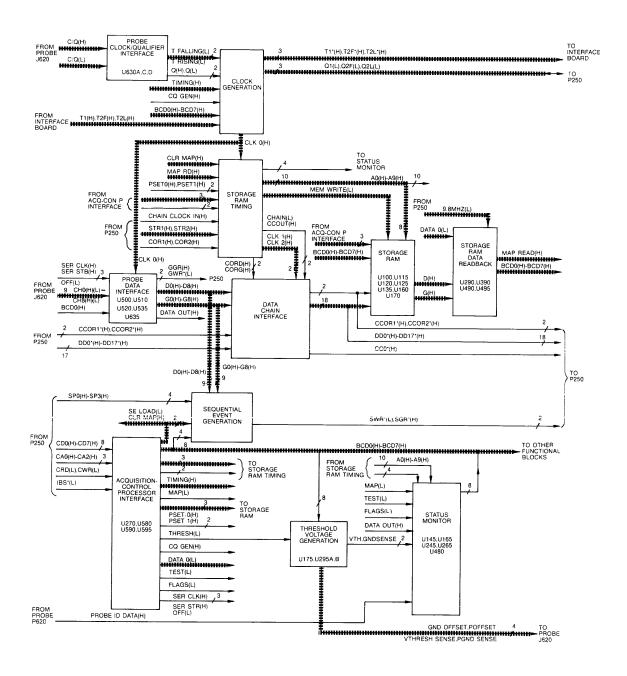

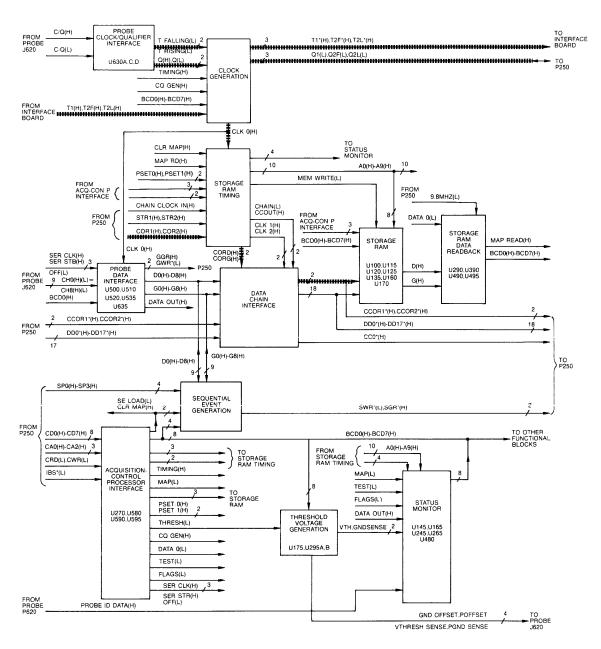

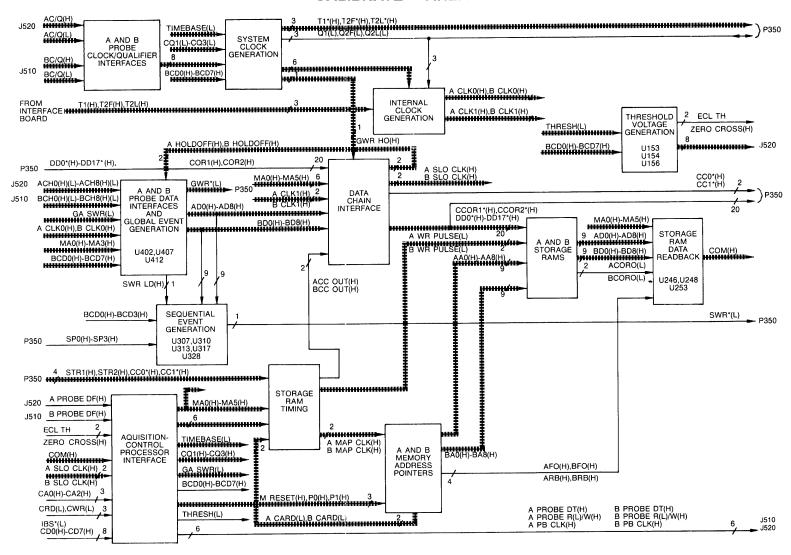

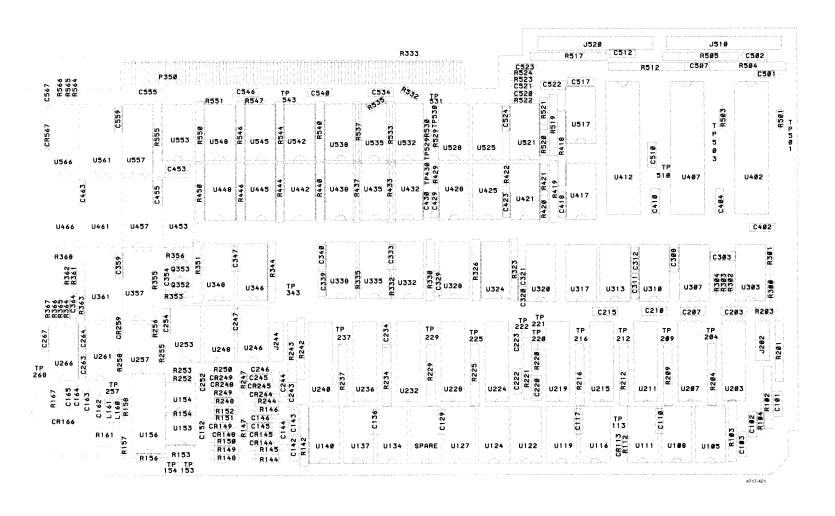

| 9-CHANNEL ACQUISITION THEORY                        | 4-46 |

| Overview                                            | 4-46 |

| Acquisition-Control Processor Interface 29          | 4-46 |

| Probe Clock/Qualifier Interface 🕸                   | 4-47 |

| Clock Generation (31)                               | 4-47 |

| Storage RAM Timing 🚯                                | 4-47 |

| Probe Data Interface 28                             | 4-49 |

| Sequential Event Generation 🕸                       | 4-49 |

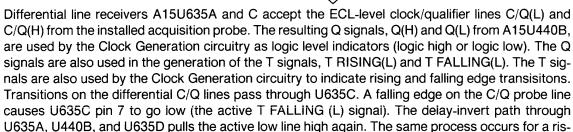

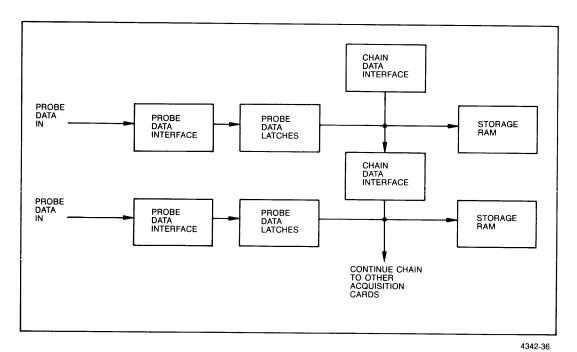

| Data Chain Interface ③                              | 4-49 |

| Storage RAMs 🚳                                      | 4-50 |

| Storage RAM Data Readback 🕸                         | 4-51 |

| Status Monitor 😥                                    | 4-51 |

| Threshold Voltage Generation 28                     | 4-51 |

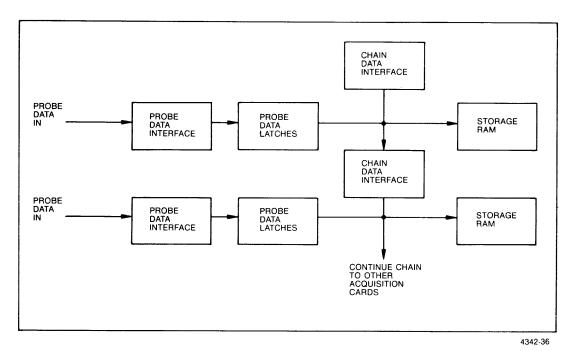

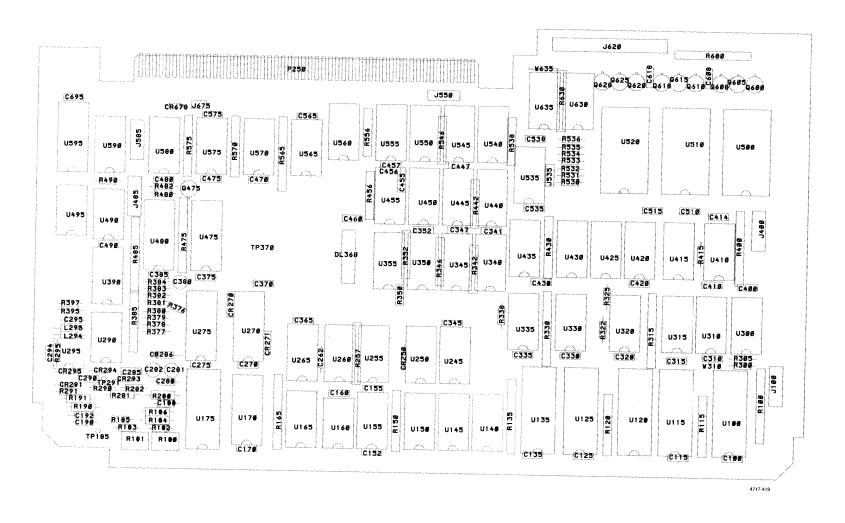

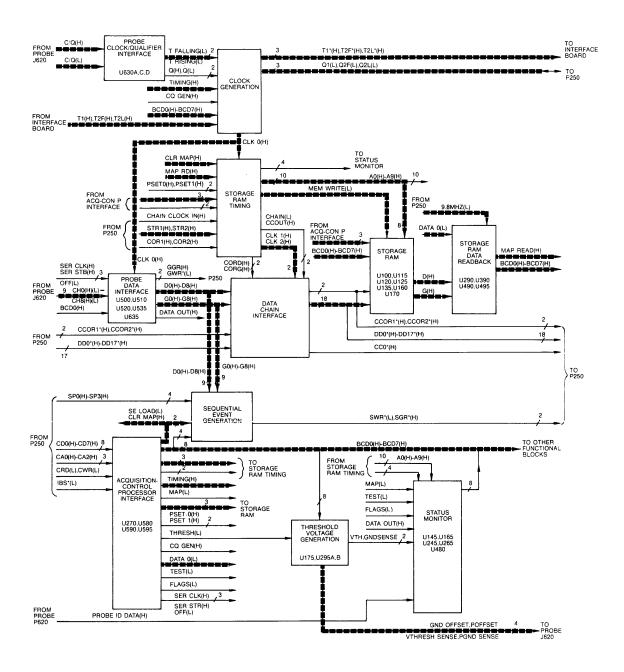

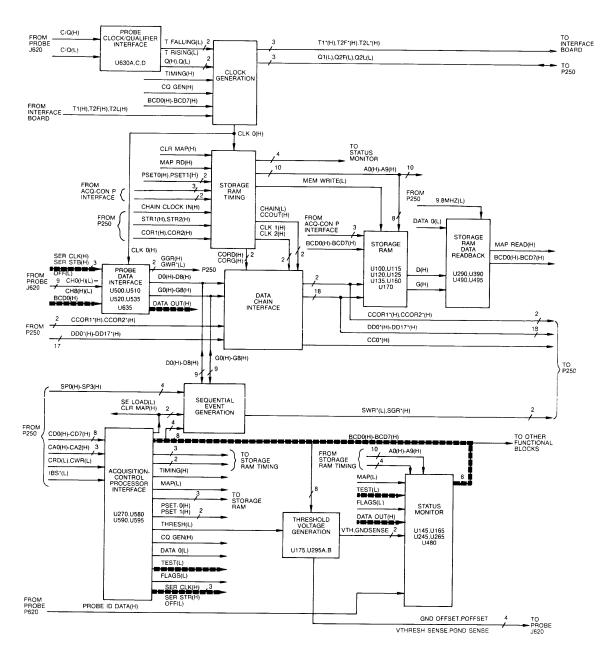

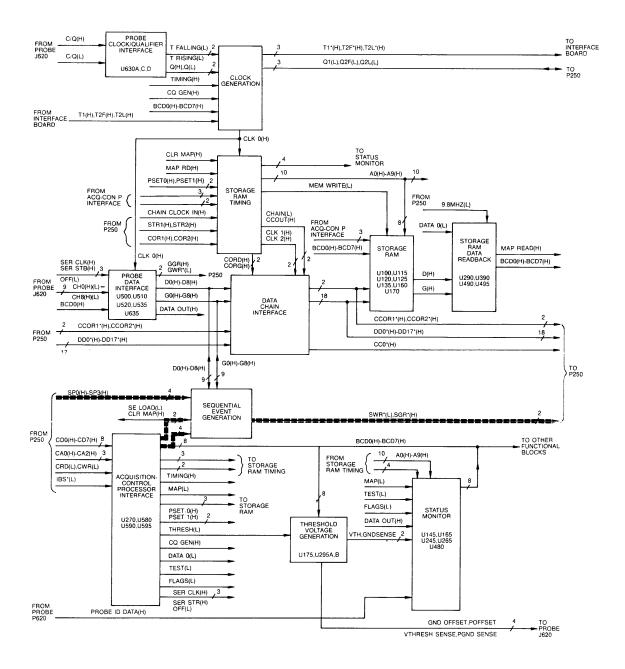

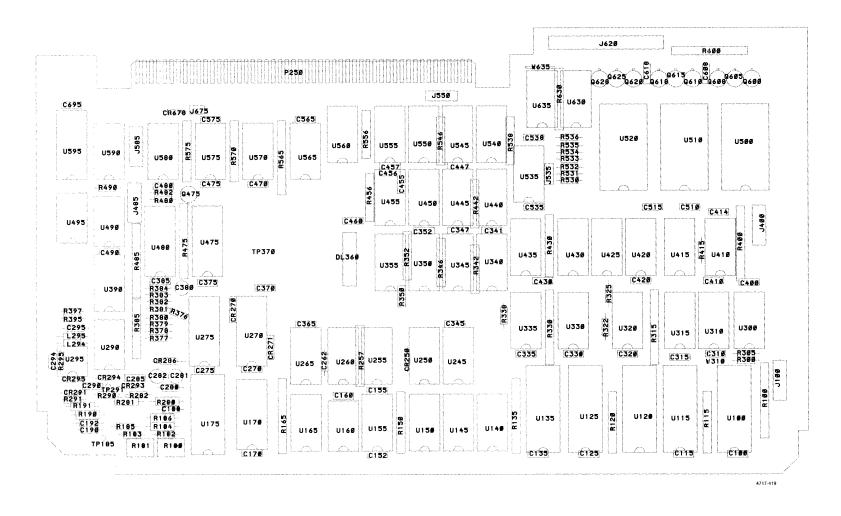

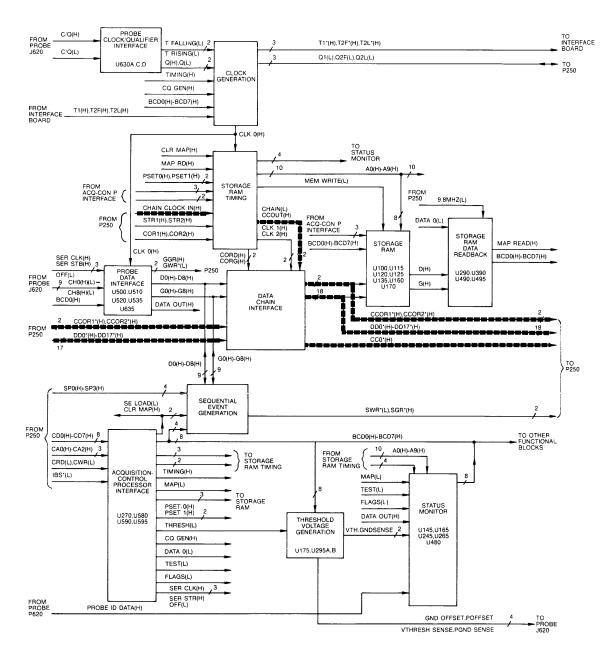

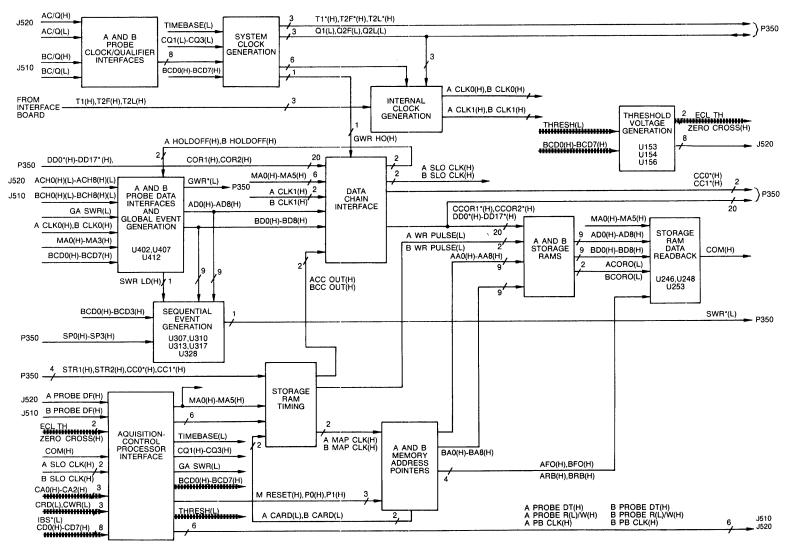

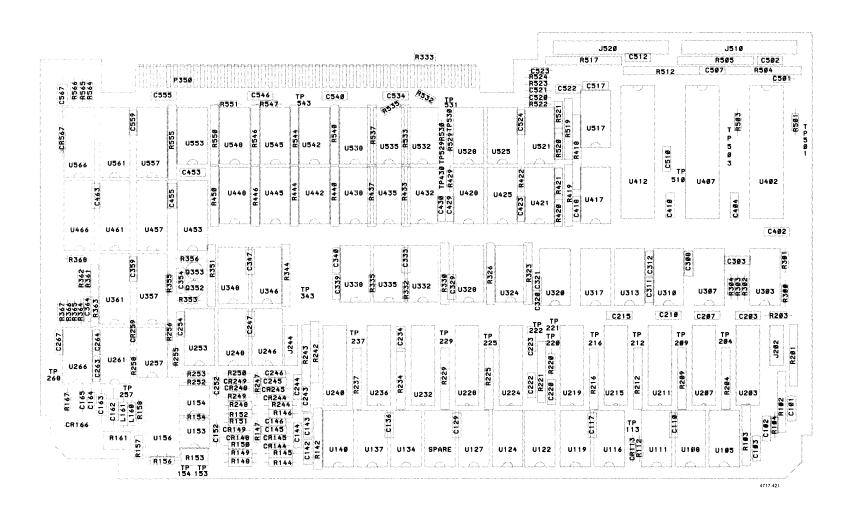

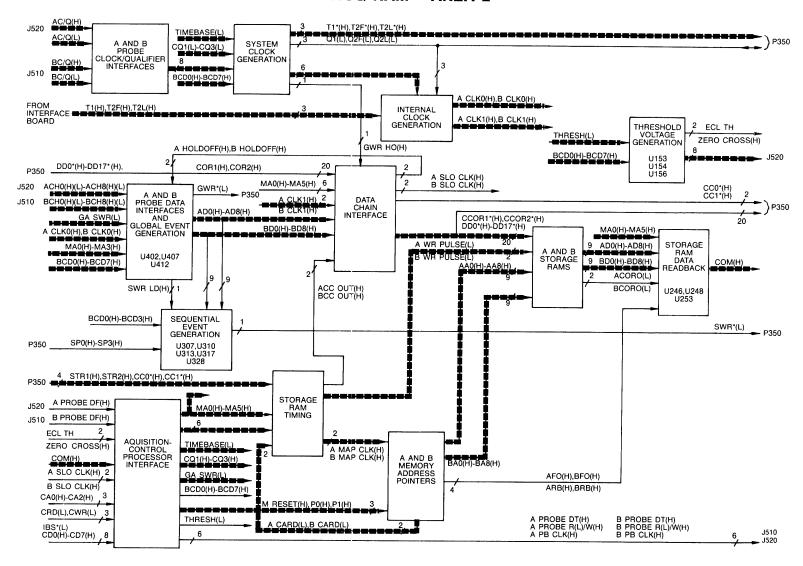

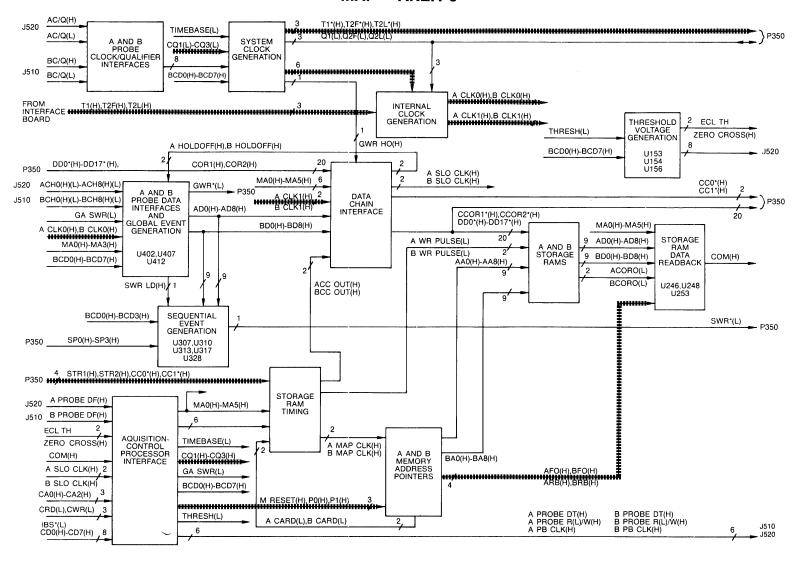

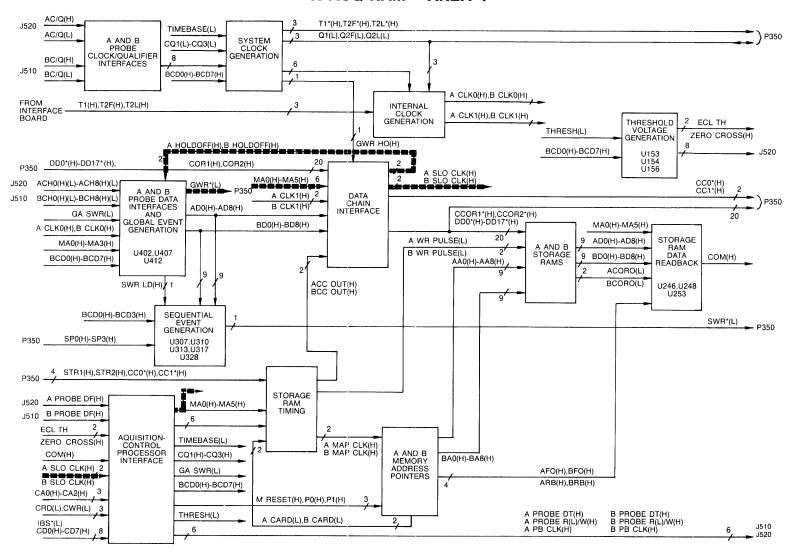

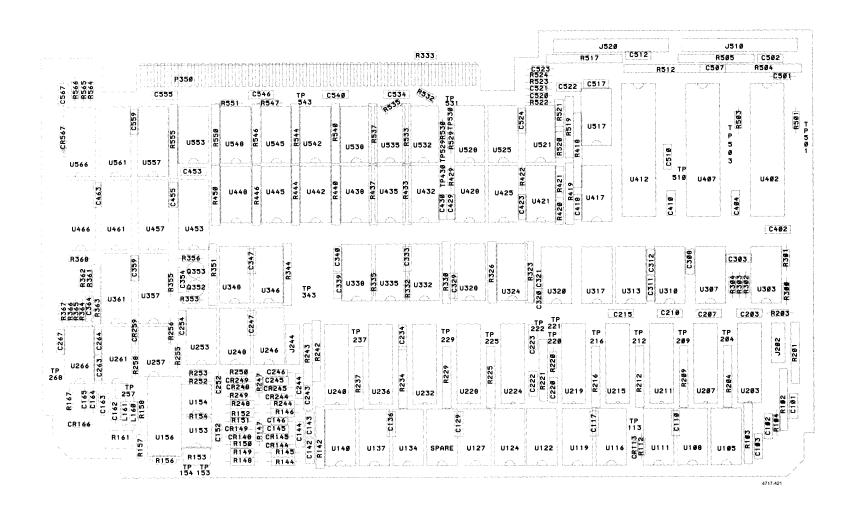

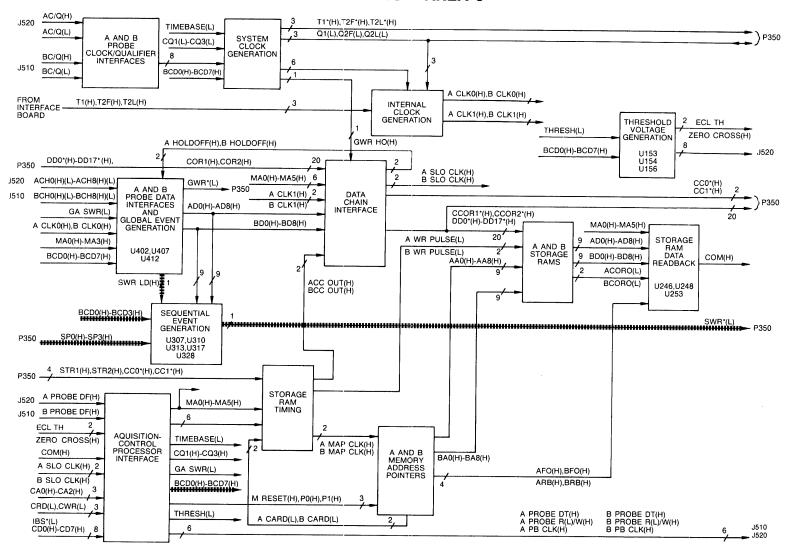

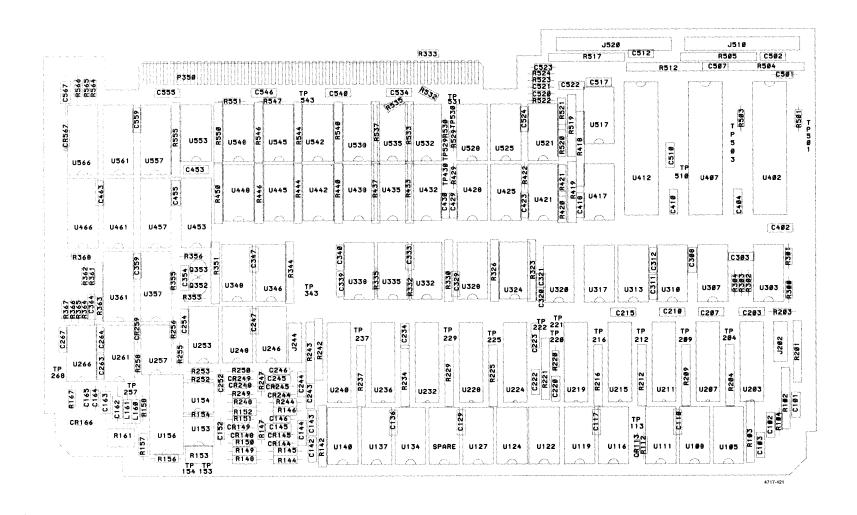

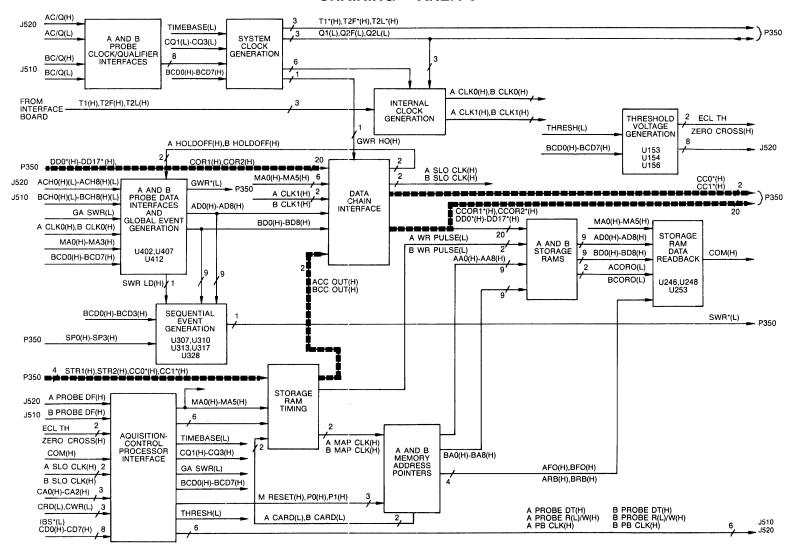

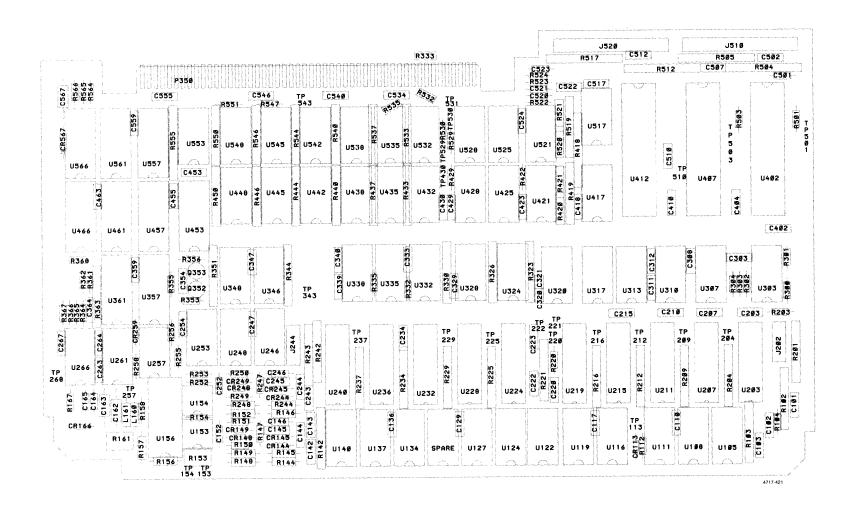

| 18-CHANNEL ACQUISITION THEORY                       | 4-53 |

| Overview                                            | 4-53 |

| Acquisition-Control Processor Interface 🔞           | 4-53 |

| Probe Clock/Qualifier Interface 35                  | 4-54 |

| System Clock Generation 35                          | 4-54 |

| Internal Clock Generation (35)                      | 4-55 |

| Storage RAM Timing 🚳                                | 4-55 |

| Probe Data Interface And Global Event Generation 32 | 4-55 |

| Data Chain Interface 33                             | 4-56 |

| Memory Address Pointer 34                           | 4-56 |

| Storage RAMs 34                                     | 4-57 |

| Storage RAM Data Readback 34                        | 4-57 |

| Sequential Event Generation (33)                    | 4-57 |

| Threshold Voltage Generation 35                     | 4-57 |

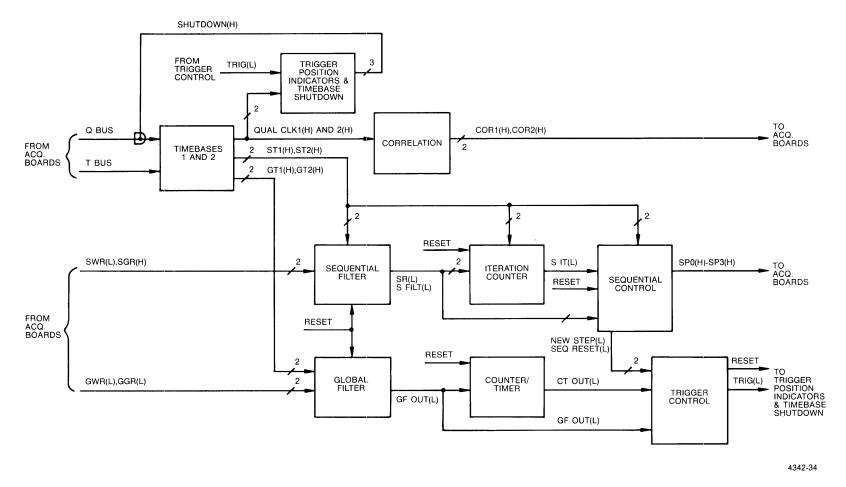

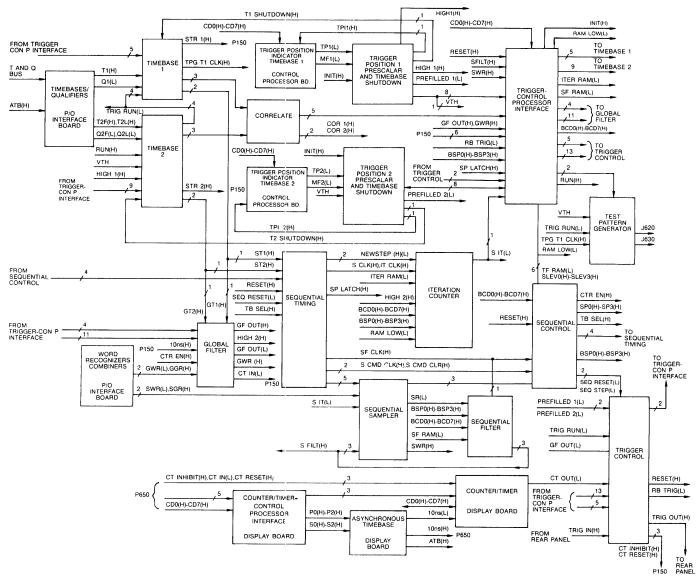

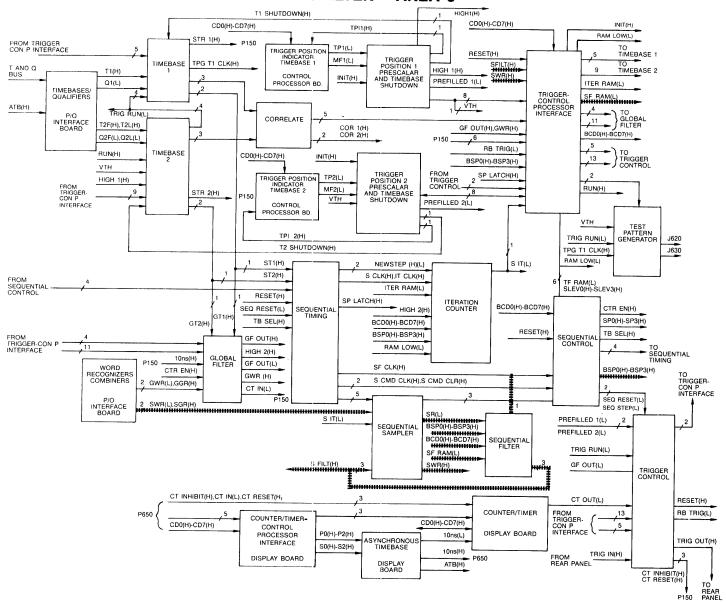

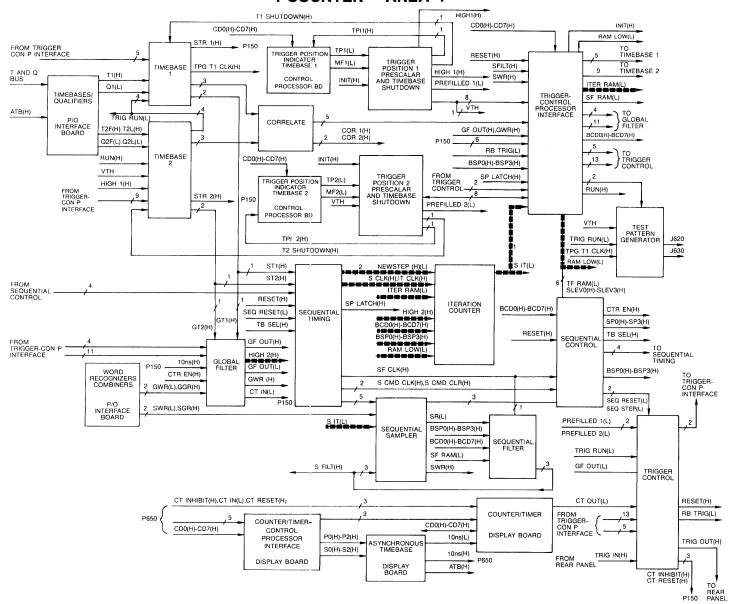

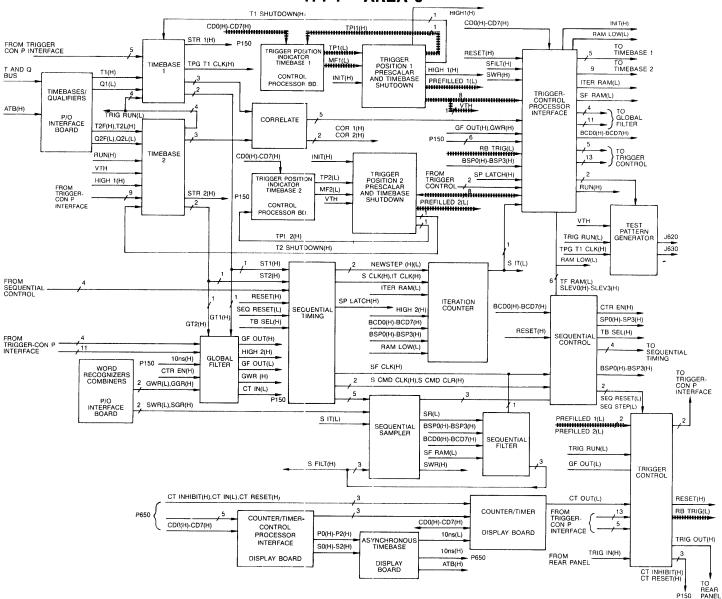

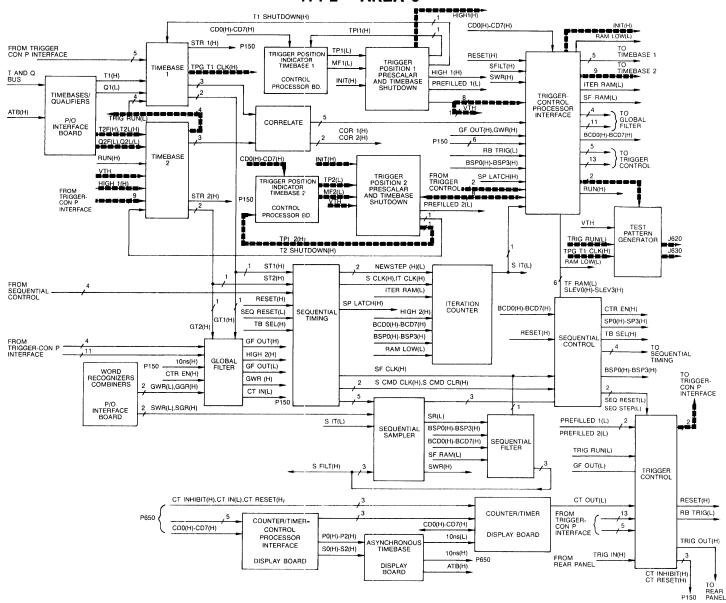

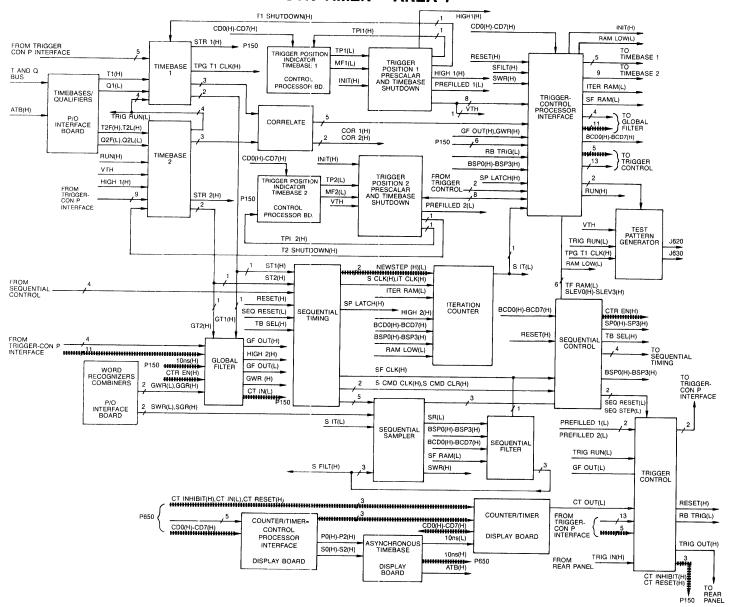

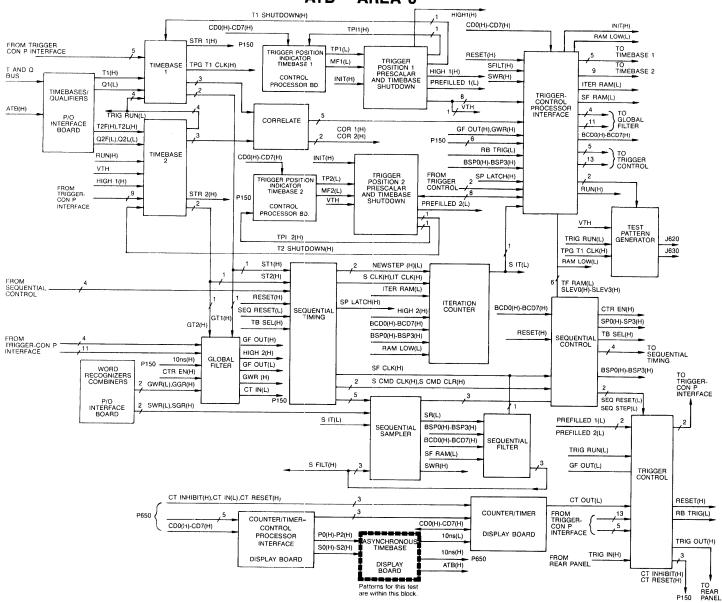

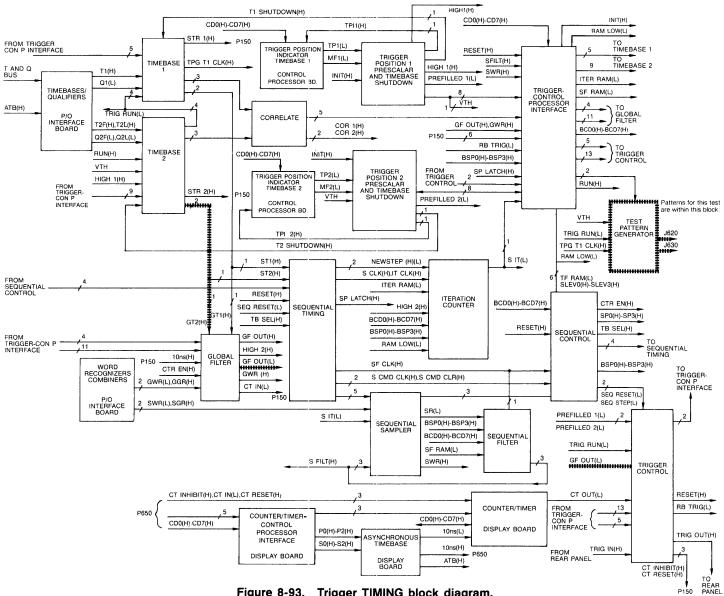

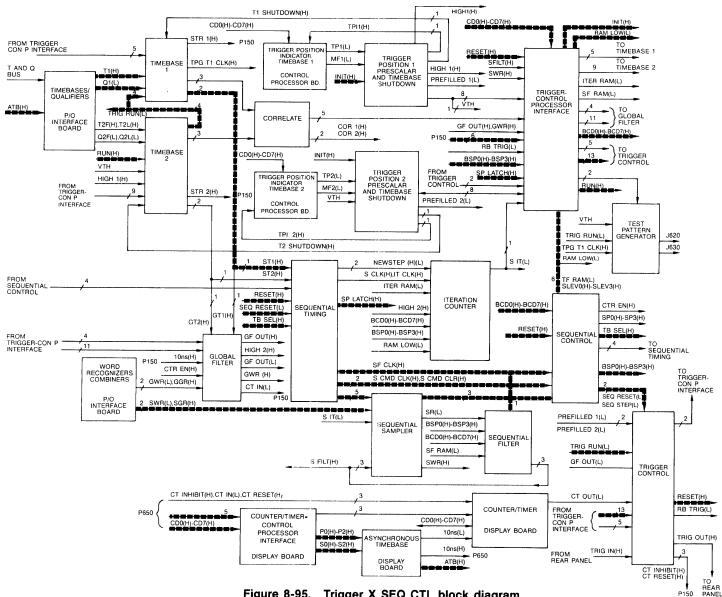

| TRIGGER BOARD THEORY                                | 4-59 |

| Overview                                            | 4-59 |

| Trigger Generation                                  | 4-59 |

| Sequential Event Timing 😥                           | 4-59 |

| Sequential Control 23                               | 4-61 |

| Sequential Filter 24                                | 4-62 |

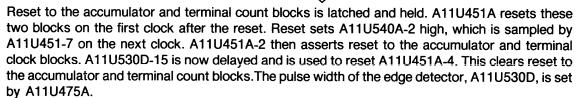

| Iteration Counter 24                                | 4-63 |

| Global Filter 25                                    | 4-63 |

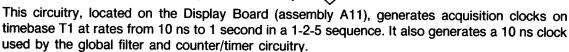

| Counter/Timer 18                                    | 4-65 |

| Trigger Control (25)                                | 4-68 |

|           | Data Storage Control                                      |

|-----------|-----------------------------------------------------------|

|           | Trigger Position Indicator Timebases 1 And 2 11           |

|           | Shutdowns ② ② ②                                           |

|           | Timebases 1 And 2 20 21                                   |

|           | Correlate Circuit 22                                      |

|           | Supplemental Circuit Blocks                               |

|           | Trigger-Processor Interface 26                            |

|           | Asynchronous Timebase                                     |

|           | Test Pattern Generator                                    |

| Section 5 | VERIFICATION AND ADJUSTMENT PROCEDURES                    |

|           | INTRODUCTION                                              |

|           | USING THE 1240 EXTENDER BOARDS                            |

|           | OPERATING THE 1240 IN THE SERVICE POSITION                |

|           | Proper Cooling Of The 1240                                |

|           | Timing Limitations                                        |

|           | CONSTRUCTING AN ACQUISITION THRESHOLD FIXTURE             |

|           | FUNCTIONAL CHECK PROCEDURES                               |

|           | Introduction                                              |

|           | 1 Internal Diagnostic Check Procedure                     |

|           | 2 Front Panel Functional Check                            |

|           | 3 Soft Key Functional Check                               |

|           | 4 RS-232 Comm Pack Functional Check Procedure             |

|           | 5 GPIB Comm Pack Functional Check Procedure               |

|           | PERFORMANCE VERIFICATION PROCEDURES                       |

|           | Introduction                                              |

|           | Part 1: Supply And TPG Performance Checks                 |

|           | Procedure 1: Power Supply Performance Check               |

|           | Procedure 2: Display High Voltage Performance Check       |

|           | Procedures 3A-E: Test Pattern Generator Performance Check |

|           | Part 2: Functionality Checks                              |

|           | Procedure 1: Trigger Functionality Check                  |

|           | Procedure 2: Acquisition Functionality Check              |

|           | Procedure 4: External Trigger Functionality Check         |

|           | Procedure 5: Glitch Detection Functionality Check         |

|           | Part 3: Acquisition And System Performance Checks         |

|           | Verification Setup Illustrations                          |

|           | Acquisition Performance Checks                            |

|           | Procedures 1A, B, & C: Timebase Generation                |

|           | Procedures 2A & B: Synchronous Operation                  |

|           | Procedures 3A, B, & C: Asynchronous Operation             |

|           | Procedure 4: Probe Threshold                              |

|           | System Performance Checks                                 |

|           | Procedures 1A - F: Global Event                           |

|           | Procedures 2A - D: Sequential Event                       |

|           | Procedure 3: Reset                                        |

viii

|           |                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|           |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

|           | Procedure 4: Counter/Timer                                                                                                                                                                                                                                                                                                                                                        | 5-65                                                                                    |

|           | Procedure 5: T2 Demux Control                                                                                                                                                                                                                                                                                                                                                     | 5-69                                                                                    |

|           | Procedure 6: Two Timebase Correlation                                                                                                                                                                                                                                                                                                                                             | 5-71                                                                                    |

|           | ADJUSTMENT PROCEDURES                                                                                                                                                                                                                                                                                                                                                             | 5-76                                                                                    |

|           | Introduction                                                                                                                                                                                                                                                                                                                                                                      | 5-76                                                                                    |

|           | Purpose                                                                                                                                                                                                                                                                                                                                                                           | 5-76                                                                                    |

|           | Limits And Tolerances                                                                                                                                                                                                                                                                                                                                                             | 5-76                                                                                    |

|           | Equipment Required                                                                                                                                                                                                                                                                                                                                                                | 5-76                                                                                    |

|           | Equipment Alternatives                                                                                                                                                                                                                                                                                                                                                            | 5-76                                                                                    |

|           | Adjustment Interval                                                                                                                                                                                                                                                                                                                                                               | 5-76                                                                                    |

|           | Test Sequence                                                                                                                                                                                                                                                                                                                                                                     | 5-77                                                                                    |

|           | Pre-Adjustment Procedure                                                                                                                                                                                                                                                                                                                                                          | 5-77                                                                                    |

|           | 1A. CRT: Alignment Adjust                                                                                                                                                                                                                                                                                                                                                         | 5-79                                                                                    |

|           | 1B. CRT: Soft Key Sensitivity Adjust                                                                                                                                                                                                                                                                                                                                              | 5-81                                                                                    |

|           | 2. 1240D1 Acquisition Card: Threshold Adjust                                                                                                                                                                                                                                                                                                                                      | 5-84                                                                                    |

|           | 3. 1240D2 Acquisition Card: Threshold Adjust                                                                                                                                                                                                                                                                                                                                      | 5-85                                                                                    |

|           | 4A. Trigger Board: Test Pattern Generator Adjust                                                                                                                                                                                                                                                                                                                                  | 5-87                                                                                    |

|           | 4B. Trigger Board: Timebase 1 Adjust                                                                                                                                                                                                                                                                                                                                              | 5-90                                                                                    |

|           | 4C. Trigger Board: Timebase 2 Adjust                                                                                                                                                                                                                                                                                                                                              | 5-96                                                                                    |

|           | 4D. Trigger Board: Sequential Timing Adjust                                                                                                                                                                                                                                                                                                                                       | 5-99                                                                                    |

|           | 5. Display Board: Counter/Timer Adjust                                                                                                                                                                                                                                                                                                                                            | 5-100                                                                                   |

|           | 6. CRT Drive Board: External Trigger Adjust                                                                                                                                                                                                                                                                                                                                       | 5-103                                                                                   |

|           | 0. Ott blive board. External ringger Adjust                                                                                                                                                                                                                                                                                                                                       | 3-100                                                                                   |

|           |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| Section 6 | DISASSEMBLY AND INSTALL ATION PROCEDURES                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

| Section 6 | DISASSEMBLY AND INSTALLATION PROCEDURES                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| Section 6 |                                                                                                                                                                                                                                                                                                                                                                                   | 6-1                                                                                     |

| Section 6 | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                          | 6-1<br>6-1                                                                              |

| Section 6 | OVERVIEW  GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS                                                                                                                                                                                                                                                                                                                            | -                                                                                       |

| Section 6 | OVERVIEW                                                                                                                                                                                                                                                                                                                                                                          | 6-1<br>6-2                                                                              |

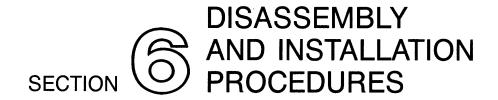

| Section 6 | OVERVIEW  GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS  TOOLS REQUIRED  PROCEDURE #1: CABINET                                                                                                                                                                                                                                                                                     | 6-1<br>6-2<br>6-2                                                                       |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly                                                                                                                                                                                                                                                                            | 6-1<br>6-2<br>6-2<br>6-2                                                                |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints                                                                                                                                                                                                                                                         | 6-1<br>6-2<br>6-2<br>6-2<br>6-2                                                         |

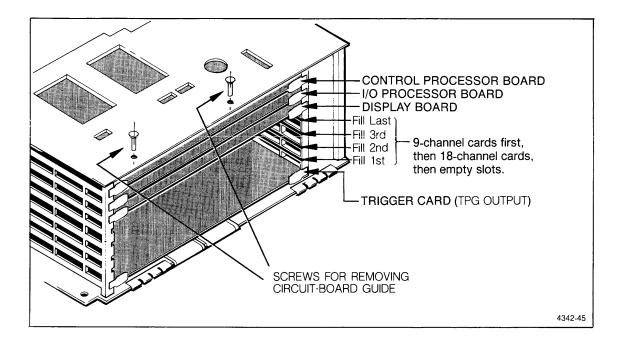

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL                                                                                                                                                                                                                                | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2                                                  |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly                                                                                                                                                                                                                    | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2                                           |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL                                                                                                                                                                                       | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3                                    |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly                                                                                                                                                                           | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3                             |

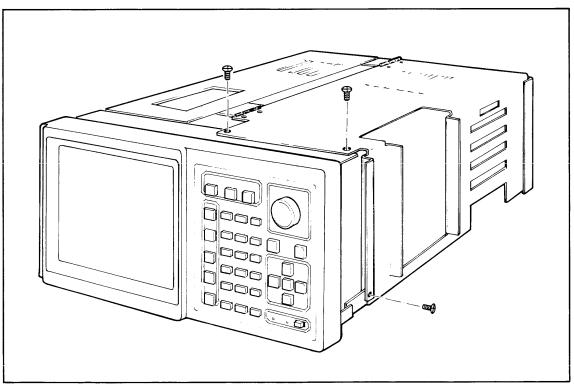

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL                                                                                                                                               | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4                      |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly                                                                                                                                   | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4                      |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints                                                                                                                | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4                      |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints PROCEDURE #5: FRONT PANEL                                                                                      | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4<br>6-4               |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints PROCEDURE #5: FRONT PANEL Disassembly                                                                          | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4<br>6-5<br>6-5        |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints PROCEDURE #5: FRONT PANEL Disassembly Installation Hints                                                       | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4<br>6-5<br>6-5        |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints PROCEDURE #5: FRONT PANEL Disassembly Installation Hints PROCEDURE #6: KEYBOARD                                | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4<br>6-5<br>6-5<br>6-5 |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints PROCEDURE #5: FRONT PANEL Disassembly Installation Hints PROCEDURE #6: KEYBOARD Disassembly Disassembly        | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4<br>6-5<br>6-6<br>6-6 |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints PROCEDURE #5: FRONT PANEL Disassembly Installation Hints PROCEDURE #6: KEYBOARD Disassembly Installation Hints | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4<br>6-5<br>6-6<br>6-6 |

| Section 6 | OVERVIEW GENERAL DISASSEMBLY/INSTALLATION PRECAUTIONS TOOLS REQUIRED PROCEDURE #1: CABINET Disassembly Installation Hints PROCEDURE #2: REAR PANEL Disassembly PROCEDURE #3: CARD CAGE ROLL Disassembly PROCEDURE #4: BOARD REMOVAL Disassembly Installation Hints PROCEDURE #5: FRONT PANEL Disassembly Installation Hints PROCEDURE #6: KEYBOARD Disassembly Disassembly        | 6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-4<br>6-4<br>6-5<br>6-6<br>6-6 |

REV SEPT 1985

|           |                                                            | Page         |

|-----------|------------------------------------------------------------|--------------|

|           | PROCEDURE #8: CRT DRIVE BOARD REMOVAL                      | 6-6          |

|           | Disassembly                                                | 6-6          |

|           | Installation Hints                                         | 6-7          |

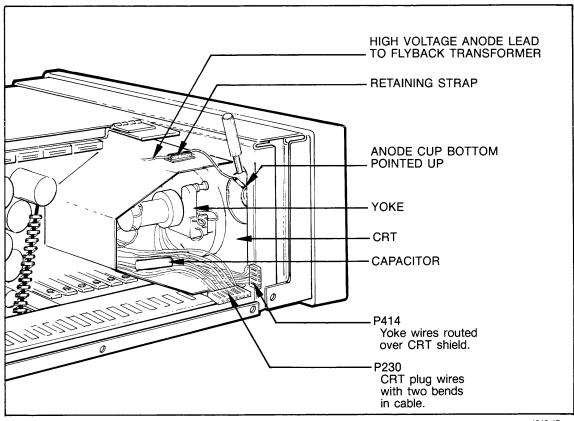

|           | PROCEDURE #9: CRT REMOVAL                                  | 6-8          |

|           | Disassembly                                                | 6-8          |

|           | Installation HintsPROCEDURE #10: POWER SUPPLY BOARD        | 6-8          |

|           | Disassembly                                                | 6-10<br>6-10 |

|           | Installation Hints                                         | 6-10         |

|           | PROCEDURE #11: INTERFACE BOARD                             | 6-11         |

|           | Disassembly                                                | 6-11         |

|           | Installation Hints                                         | 6-12         |

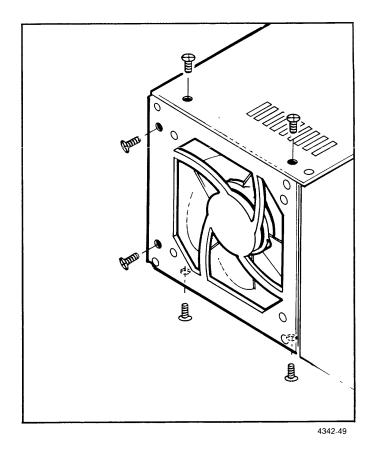

|           | PROCEDURE #12: FAN REMOVAL                                 | 6-12         |

|           | Disassembly                                                | 6-12         |

| Coation 7 | RA INTENANOE                                               |              |

| Section 7 | MAINTENANCE                                                |              |

|           | TOOLS REQUIRED FOR MAINTENANCE                             | 7-1          |

|           | MAINTENANCE PRECAUTIONS                                    | 7-2          |

|           | Soldering                                                  | 7-2          |

|           | Light-Emitting Diodes (LEDs)                               | 7-2          |

|           | Static Precautions                                         | 7-2          |

|           | PREVENTIVE MAINTENANCE                                     | 7-3          |

|           | Exterior Cleaning                                          | 7-3          |

|           | Interior Cleaning                                          | 7-4          |

|           | Cleaning Guidelines                                        | 7-4          |

|           | Inspection                                                 | 7-5          |

|           | CORRECTIVE MAINTENANCE                                     | 7-5          |

|           | Obtaining Replacements Electrical And Mechanical Parts     | 7-5          |

|           | Acquisition Boards And Probes                              | 7-5<br>7-6   |

|           | Replaceable As Assemblies                                  | 7-6<br>7-6   |

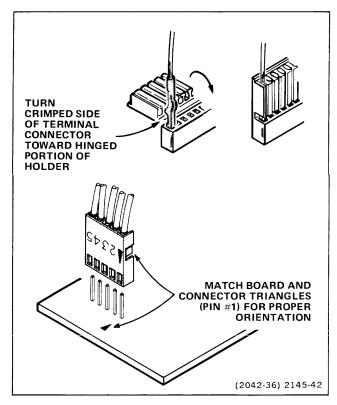

|           | Repairing Multi-Conductor Connectors                       | 7-6          |

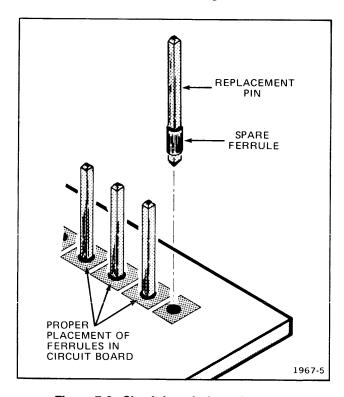

|           | Circuit Board Pin Replacement                              | 7-7          |

|           | Battery Replacement For The Control Processor and RAM Pack | 7-8          |

|           | Power Supply Jumper Change                                 | 7-8          |

|           |                                                            |              |

| Section 8 | TROUBLESHOOTING AND REPAIR                                 |              |

|           | OVERVIEW                                                   | 8-1          |

|           | TROUBLESHOOTING EQUIPMENT                                  | 8-2          |

|           | USING THE 1240 EXTENDER BOARDS                             | 8-2          |

|           | REPLACING DEFECTIVE PARTS                                  | 8-2          |

|           | LIST OF ASSEMBLIES                                         | 8-2          |

|           | TROUBLESHOOTING PRECAUTIONS                                | 8-3          |

|           | Discharging The CRT                                        | 8-3          |

|           | Static Discharge Damage (Special Handling Required)        | 8-3          |

|                                                     | Page         |

|-----------------------------------------------------|--------------|

| Operating The 1240 With The Cabinet Removed         | 8-4          |

| 1240 TROUBLESHOOTING WITHOUT ERROR INDEXES          | 8-5          |

| Damage Resulting From Incorrect Board Installation  | 8-5          |

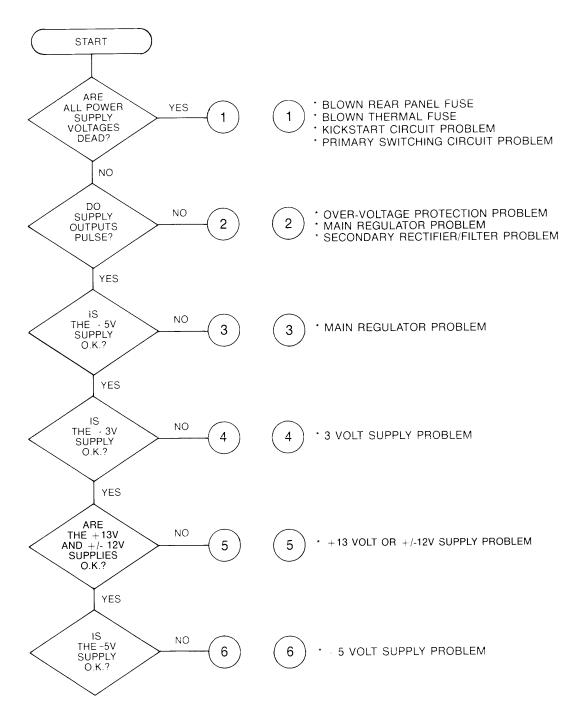

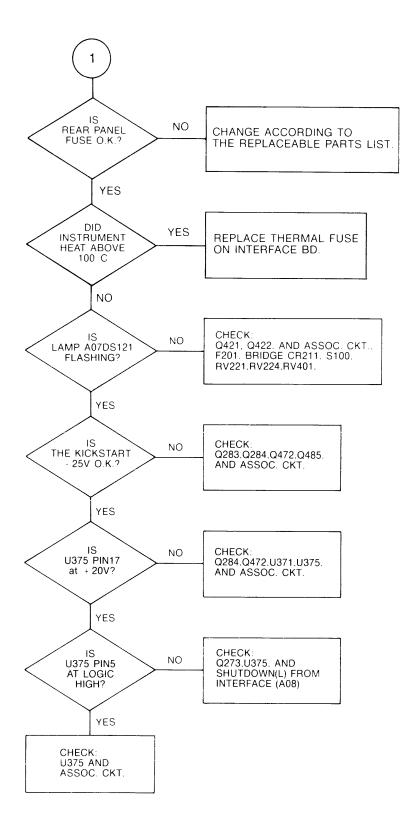

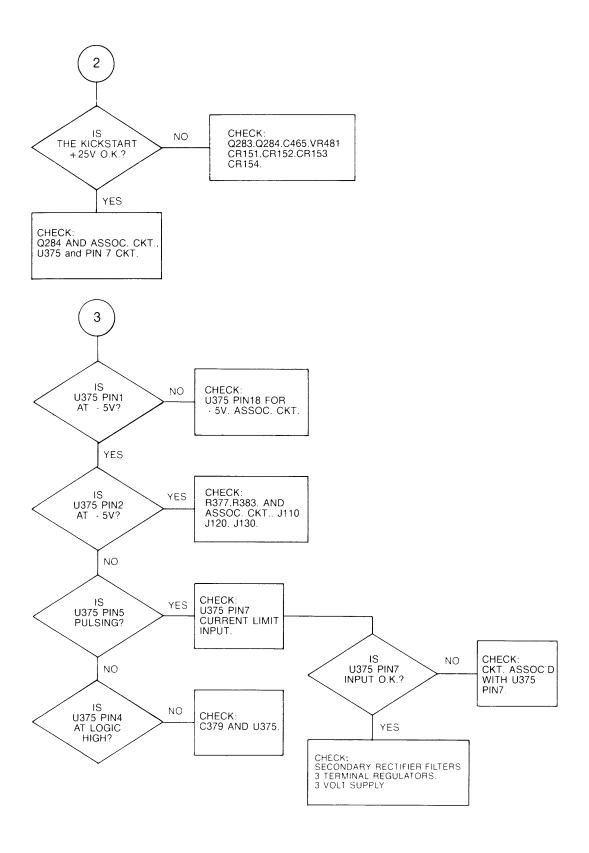

| Power Supply Troubleshooting                        | 8-6          |

| 1240 Thermal Fuse                                   | 8-6          |

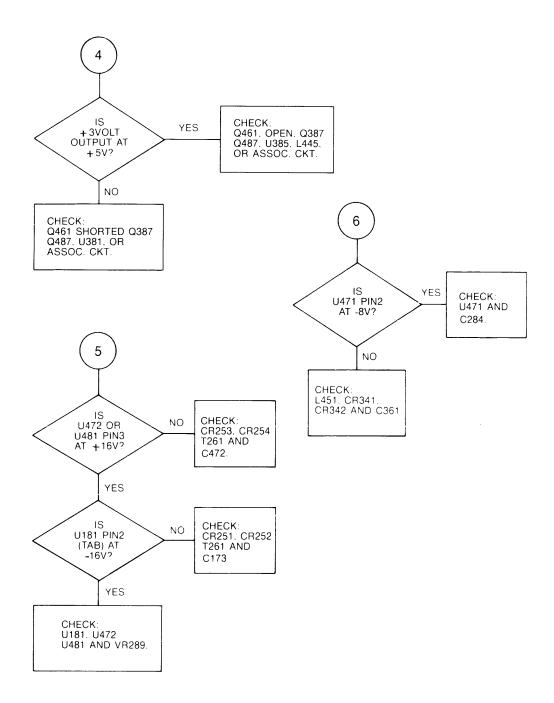

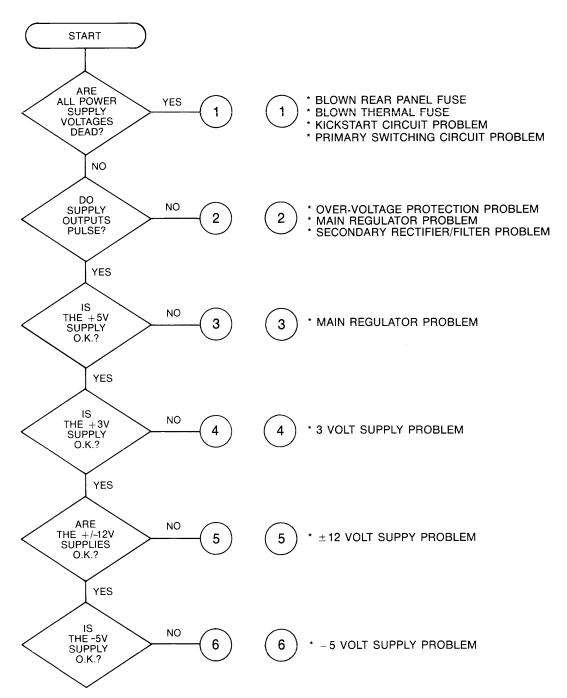

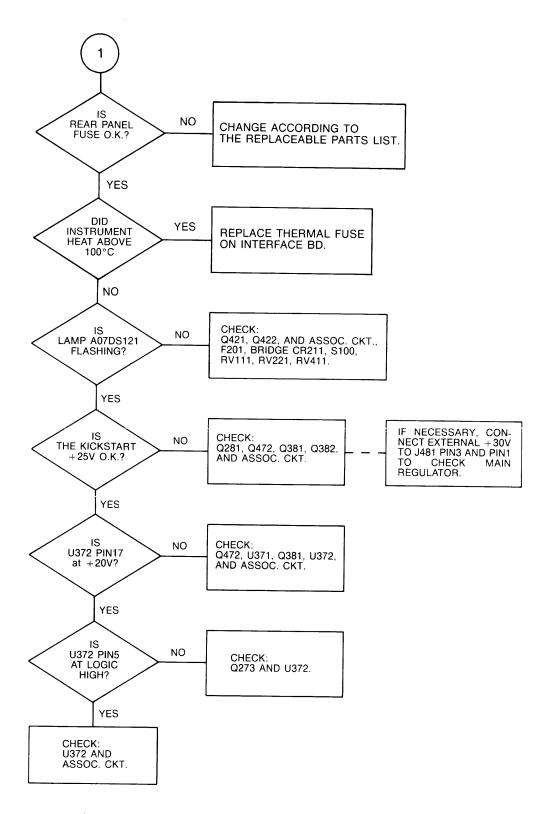

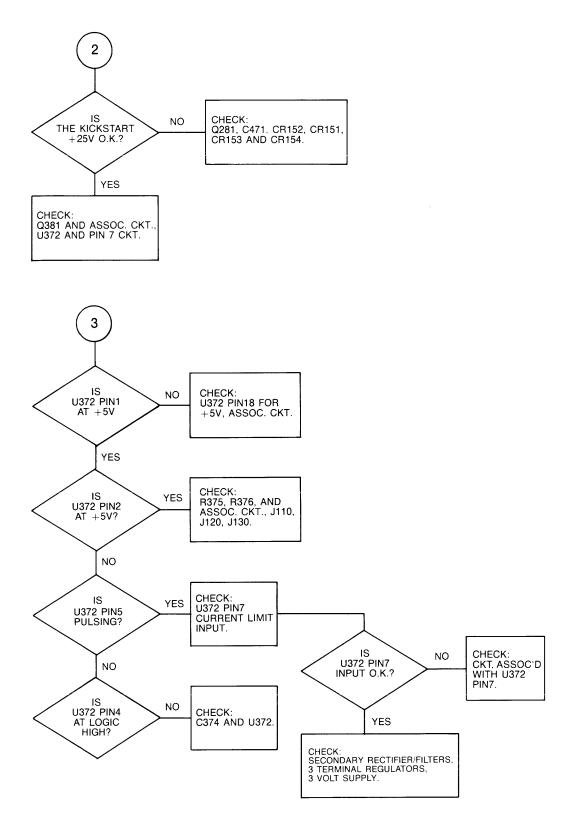

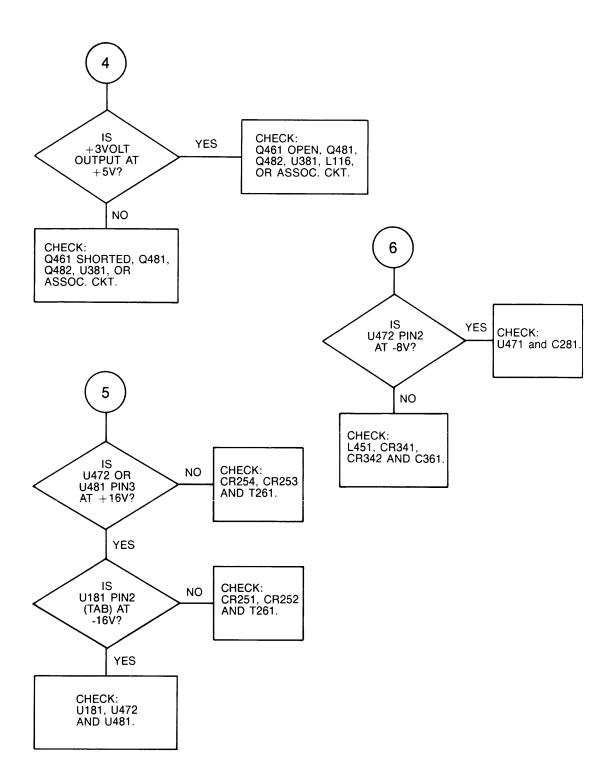

| 1240 Power Supply Troubleshooting Trees             | 8-6          |

| 670-7534-06 Power Supply Troubleshooting Trees      | 8-6a         |

| 670-7534-05 Power Supply Troubleshooting Trees      | 8-7          |

| CRT Drive Board Troubleshooting Waveforms           | 8-11         |

| Soft Key Troubleshooting                            | 8-15         |

| Keyboard Failures                                   | 8-19         |

| Processor LEDs                                      | 8-19         |

| Kernel Signature Analysis                           | 8-19         |

| I/O Processor Kernel Troubleshooting                | 8-20         |

| Control Processor Kernel Troubleshooting            | 8-20         |

| TROUBLESHOOTING USING DIAGNOSTICS ERROR INFORMATION | 8-25         |

| Diagnostics Overview                                | 8-25         |

| Error Index Overview                                | 8-26         |

| Troubleshooting An Example Failure                  | 8-27         |

| COMM Pack Failures                                  | 8-28         |

| ROM Or RAM Pack Failures                            | 8-28         |

| Acquisition Probe Failures                          | 8-28         |

| Troubleshooting Intermittent Failures               | 8-29         |

| Remote Diagnostics                                  | 8-29         |

| 1240 Manual Tests                                   | 8-29         |

| Troubleshooting Page Layout                         | 8-31         |

| I/O PROCESSOR KERNEL LED ERROR INDEXES              | 8-33<br>8-34 |

| Power-Up And ROM - Stage 0                          | 8-40         |

| COMM Pack - Stage 2                                 | 8-44         |

| CONTROL PROCESSOR KERNEL LED ERROR INDEXES          | 8-47         |

| Power-Up And ROM - Stage 0                          | 8-48         |

| RAM - Stage 1                                       | 8-54         |

| ROM Pack - Stage 2                                  | 8-60         |

| 1XXX I/O PROCESSOR ERROR INDEXES                    | 8-67         |

| 11XX-EPROM COMP, AREA 1                             | 8-68         |

| 12XX-EPROM CSUM, AREA 2                             | 8-72         |

| 13XX-EPROM PAGE, AREA 3                             | 8-76         |

| 14XX-RAM, AREA 4                                    | 8-82         |

| 15XX-INTERRUPT, AREA 5                              | 8-86         |

| 16XX-DWINDOW, AREA 6                                | 8-92         |

| 17XX-SKEYREG, AREA 7                                | 8-96         |

| 2XXX FRONTPANEL ERROR INDEXES                       | 8-101        |

| 21XX-HARD KEYS, AREA 1                              | 8-102        |

| 22XX-SOFT KEYS, AREA 2                              | 8-108        |

| 23XX-KNOB. AREA 3                                   | 8-114        |

|                                           | Page    |

|-------------------------------------------|---------|

| 3XXX DISPLAY ERROR INDEXES                | 8-119   |

| 31XX-RAM, AREA 1                          | _       |

| 32XX-VERTICAL SCROLLING, AREA 2           |         |

| 33XX-HORIZONTAL SCROLLING, AREA 3         | 8-130   |

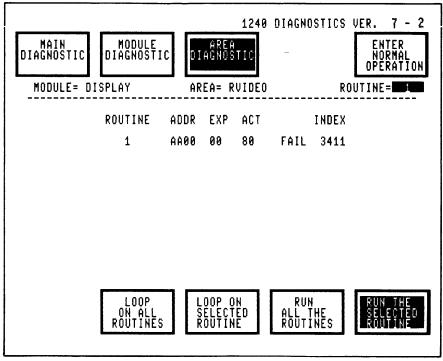

| 34XX-REVERSE VIDEO, AREA 4                |         |

| 35XX-HIGHLIGHTING, AREA 5                 |         |

| 36XX-WAVEFORM (GENERATION), AREA 6        |         |

| 4XXX COMM PACK ERROR INDEXES              |         |

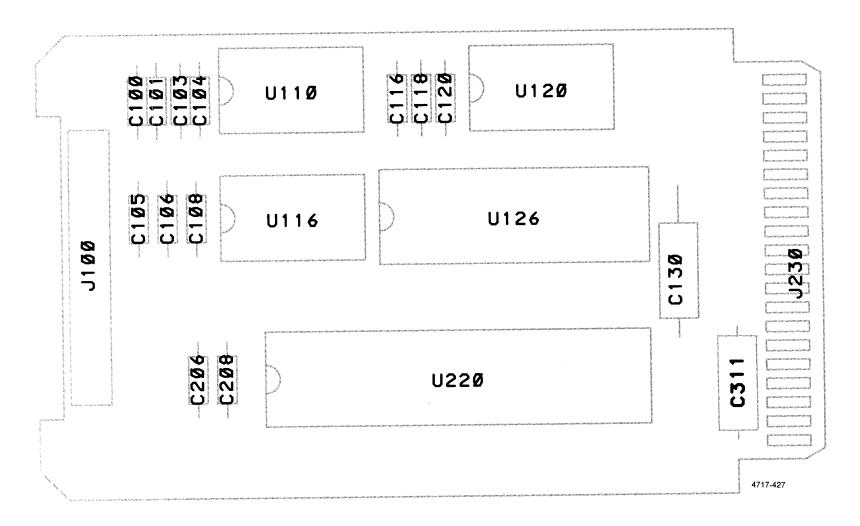

| 41XX-RS232 COMM Pack EPROM, AREA 1        |         |

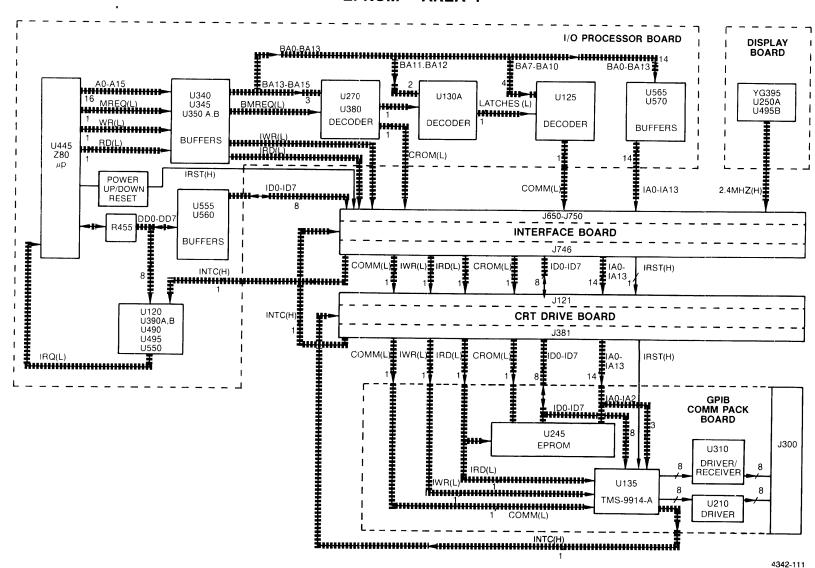

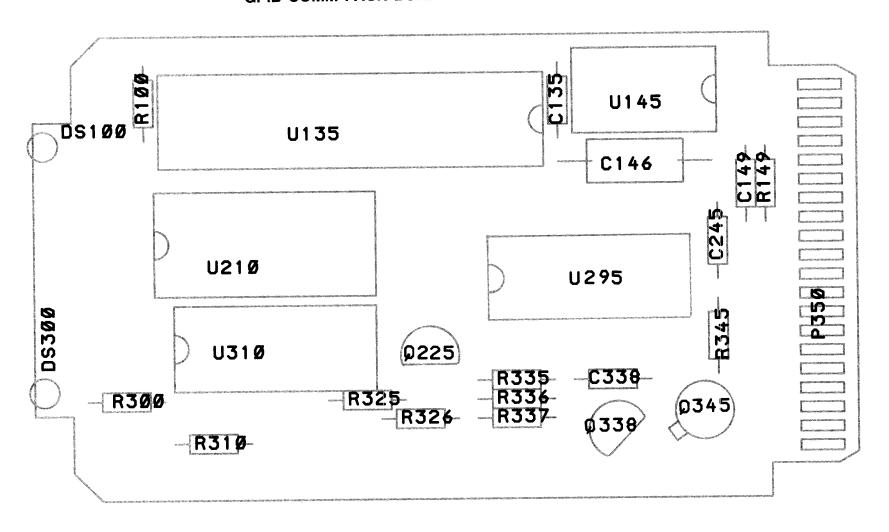

| 41XX-GPIB COMM Pack EPROM, AREA 1         |         |

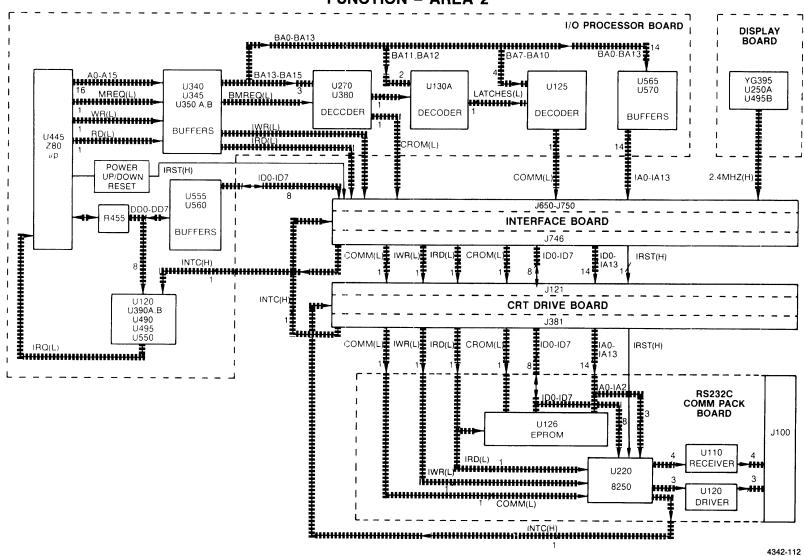

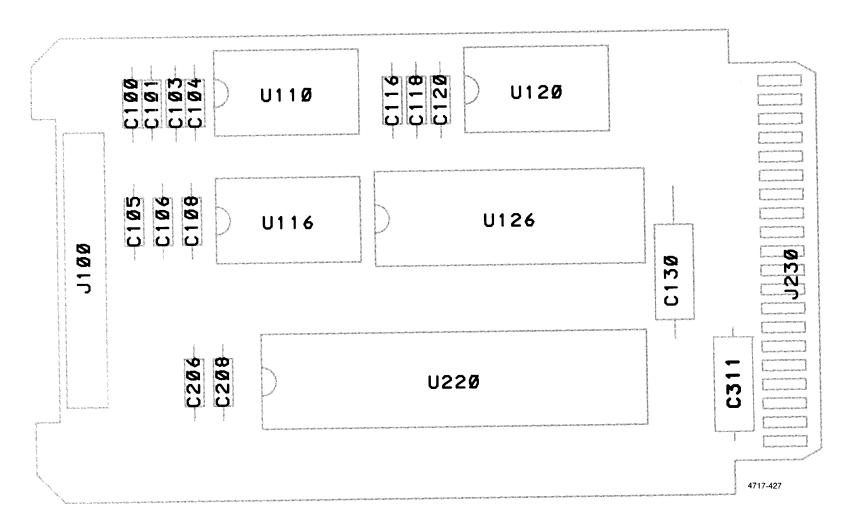

| 42XX-RS232 COMM Pack FUNCTION, AREA 2     |         |

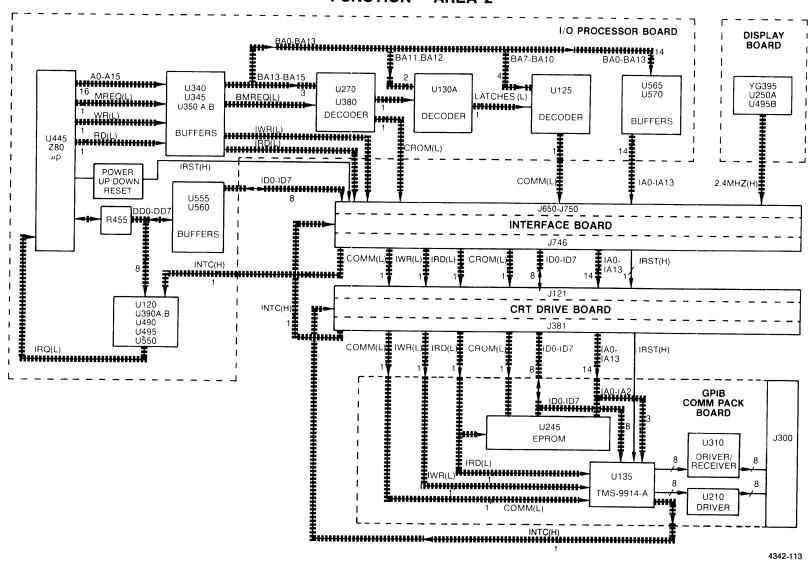

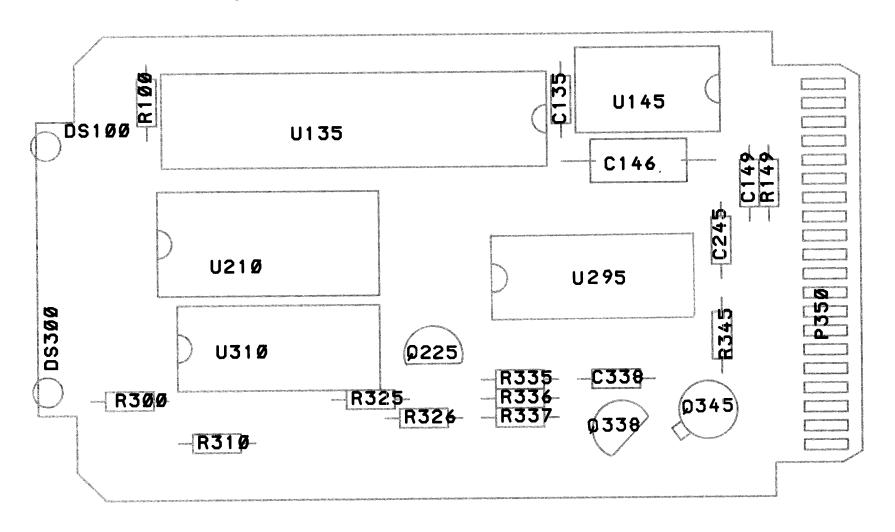

| 42XX-GPIB COMM Pack FUNCTION, AREA 2      |         |

| RS232 COMM Pack Manual Test               |         |

| 5XXX CONTROL PROCESSOR ERROR INDEXES      |         |

| 51XX-EPROM COMP, AREA 1                   |         |

| 52XX-EPROM CSUM, AREA 2                   |         |

| 53XX-EPROM PAGE, AREA 3                   |         |

| 54XX-RAM, AREA 4                          |         |

| 55XX-NONVOLATILE MEMORY, AREA 5           | 8-196   |

| 6XXX TRIGGER ERROR INDEXES                |         |

| 61XX-SEQ CTRL, AREA 1                     |         |

| 62XX-GLOBAL FILTER, AREA 2                |         |

| 63XX-SEQ FILTER, AREA 3                   |         |

| 64XX-I COUNTER, AREA 4                    |         |

| 65XX-TPI 1,AREA 5                         |         |

| 66XX-TPI 2, AREA 6                        |         |

| 67XX-CTR/TIMER, AREA 7                    | 0-240   |

|                                           |         |

| 68XX-ATB, AREA 8                          |         |

| 69XX-TIMING, AREA 9                       |         |

| 6AXX-X SEQ CTL, AREA A                    | . 8-288 |

|                                           |         |

| 71XX-THRESHOLD, AREA 1                    |         |

| 72XX-ACQ RAM, AREA 2                      |         |

| 73XX-MAP, AREA 3                          |         |

| 74XX-FEH, AREA 4                          |         |

| 75XX-GWR/GGR, AREA 5                      |         |

| 76XX-SWR/SGR, AREA 6                      |         |

| 77XX-X ACQ RAM, AREA 7                    |         |

| 78XX-CHAINING, AREA 8                     |         |

| 79XX-TIMING, AREA 9                       |         |

| 1240D1 CAL ACQ9 Manual Test               |         |

| 8XXX 18-CHANNEL ACQUISITION ERROR INDEXES |         |

| 81XX-THRESHOLD, AREA 1                    |         |

| 82XX-ACQ RAM, AREA 2                      |         |

| 83XX-MAP, AREA 3                          |         |

| 84XX-X ACQ RAM, AREA 4                    | 8-400   |

|                                    | Page  |

|------------------------------------|-------|

| 85XX-WORD REC, AREA 5              | 8-410 |

| 86XX-CHAINING, AREA 6              | 8-430 |

| 87XX-CALIBRATE, AREA 7             | 8-440 |

| 88XX-TIMING, AREA 8                | 8-446 |

| 1240D2 CAL ACQ18 Manual Test       | 8-462 |

| 9XXX ROM OR RAM PACK ERROR INDEXES | 8-465 |

| 91XX-EPROM COMP, AREA 1            | 8-466 |

| 92XX-EPROM CSUM, AREA 2            | 8-470 |

| 93XX-EPROM PAGE, AREA 3            | 8-474 |

| AXXX RAMPACK ERROR INDEXES         | 8-479 |

| A1XX-RAM, AREA 1                   | 8-480 |

#### **VOLUME 2:**

| •       | _ |      |        |       |          |         |

|---------|---|------|--------|-------|----------|---------|

| Section | 9 | REPL | ACEABL | .E EL | _ECTRICA | L PARTS |

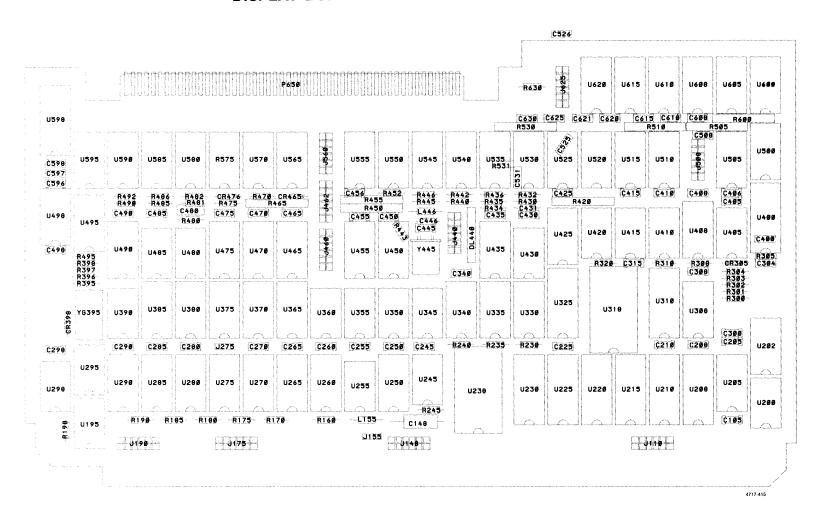

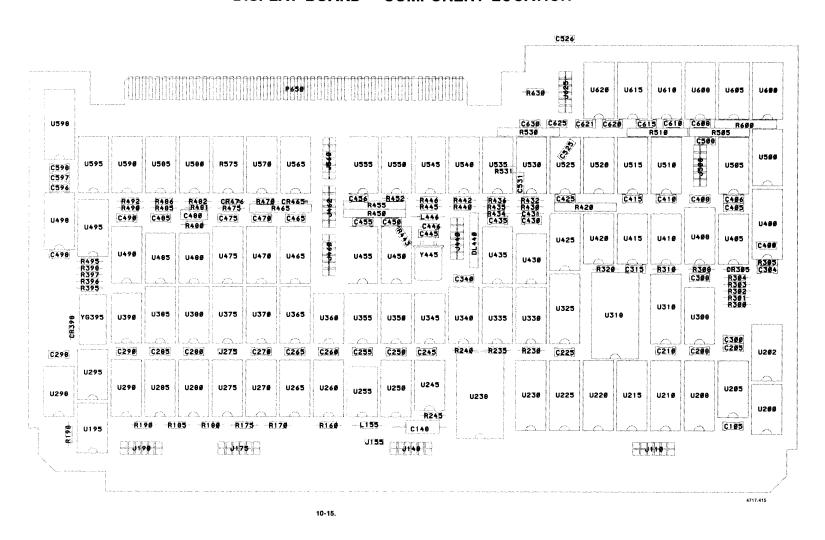

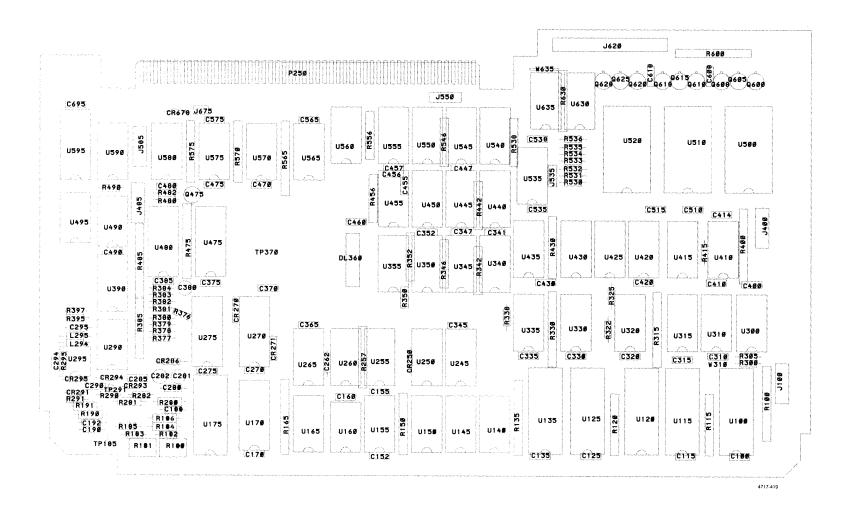

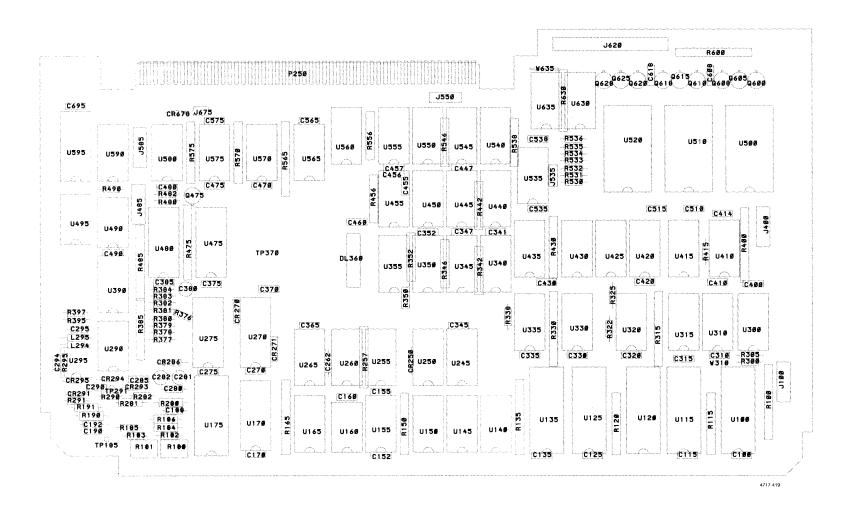

Section 10 DIAGRAMS

Section 11 REPLACEABLE MECHANICAL PARTS

Section 12 GLOSSARY

# LIST OF ILLUSTRATIONS

| Figure       |                                                                     | Page         |

|--------------|---------------------------------------------------------------------|--------------|

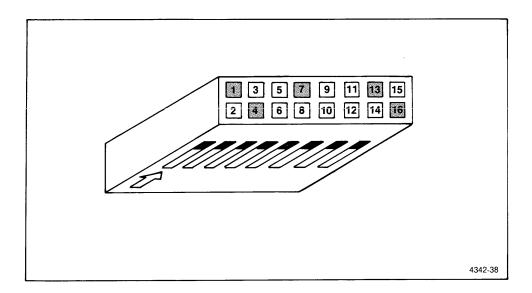

| 1-1          | 1240 keyboard layout                                                | 1-2          |

| 1-2<br>1-3   | 1240 rear panel layout                                              | 1-4          |

| . 0          | MENU key                                                            | 1-6          |

| 1-4          | Diagnostics menu overview showing the link between diagnostic menus | 1-7          |

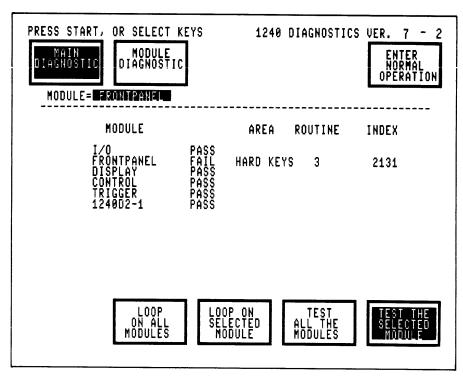

| 1-5          | Main Diagnostic menu                                                | 1-8          |

| 1-6          | Module Diagnostic menu                                              | 1-9          |

| 1-7          | Area Diagnostic menu                                                | 1-10         |

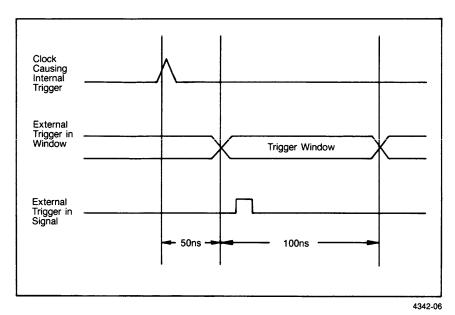

| 2-1          | External Trigger in acceptance window                               | 2-5          |

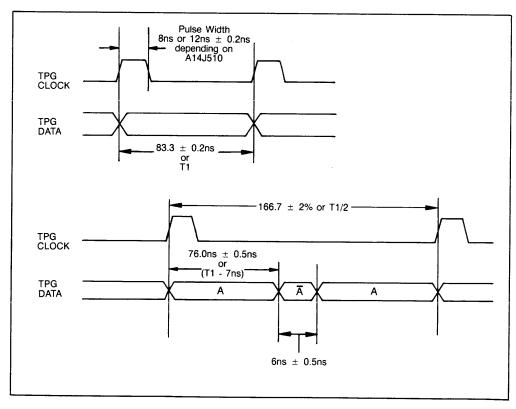

| 2-2          | TPG clock and data outputs                                          | 2-5          |

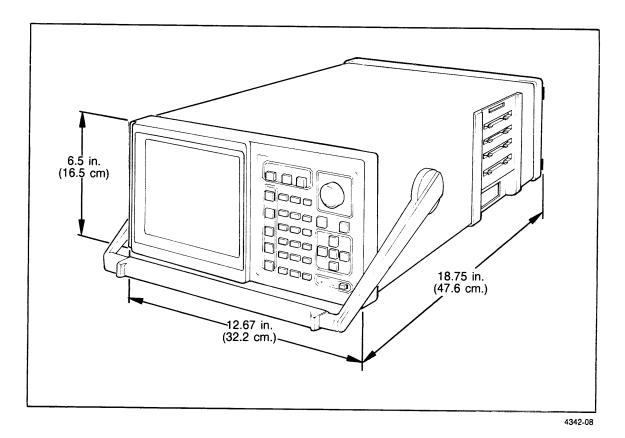

| 2-3          | 1240 dimensions                                                     | 2-14         |

| 3-1          | 1240 rear panel                                                     | 3-1          |

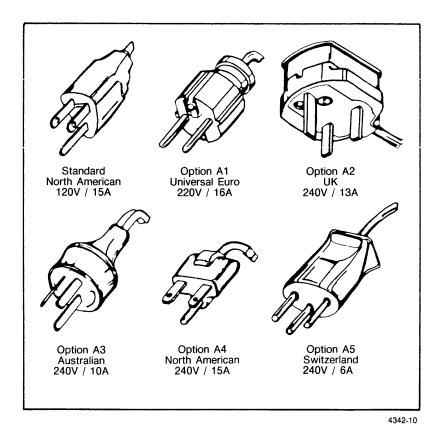

| 3-2          | Optional 1240 power cords                                           | 3-2          |

| 3-3          | 1240 right side panel showing acquisition probe connection          | 3-6          |

| 3-4<br>3-5   | P6460 Data Acquisition Probe                                        | 3-8          |

| 3-5<br>3-6   | ROM or RAM pack door location                                       | 3-10         |

| 3-7          | COMM pack door location                                             | 3-11<br>3-12 |

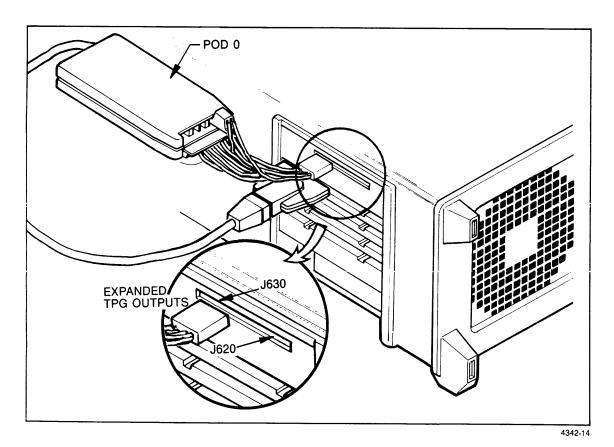

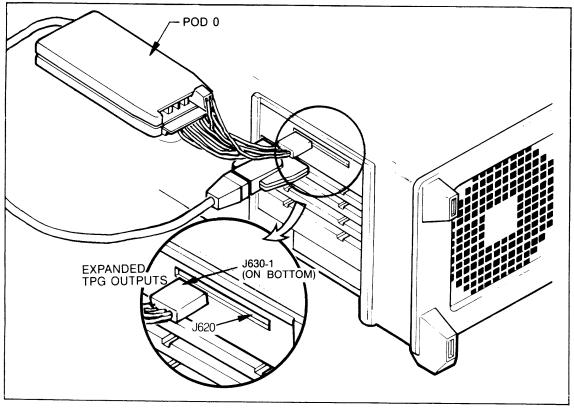

| 0-7          | Tra output connections                                              | 3-12         |

| 4-1          | 1240 system block diagram                                           | 4-2          |

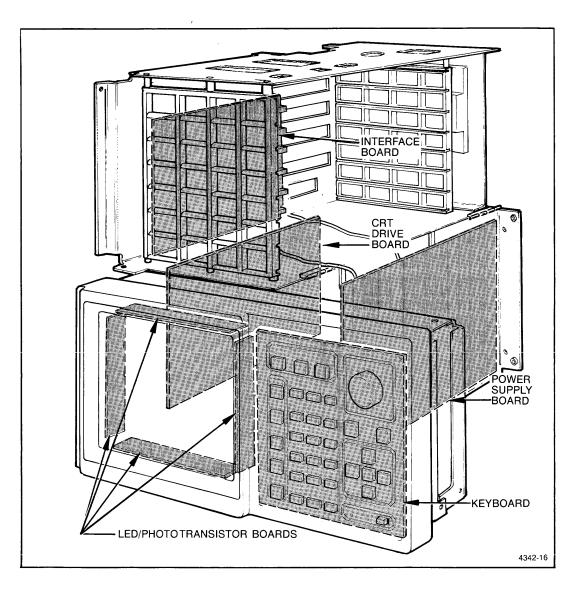

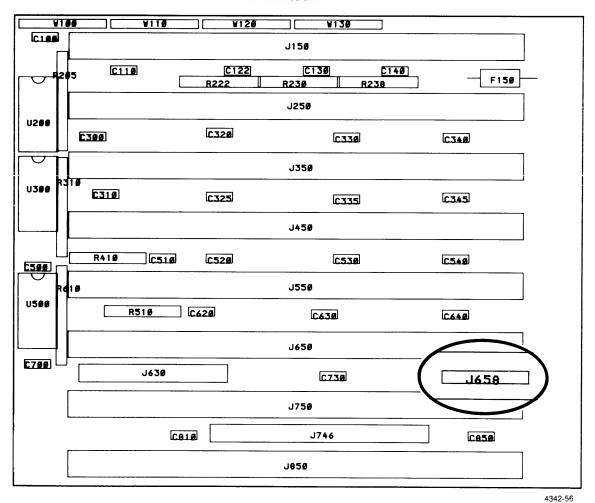

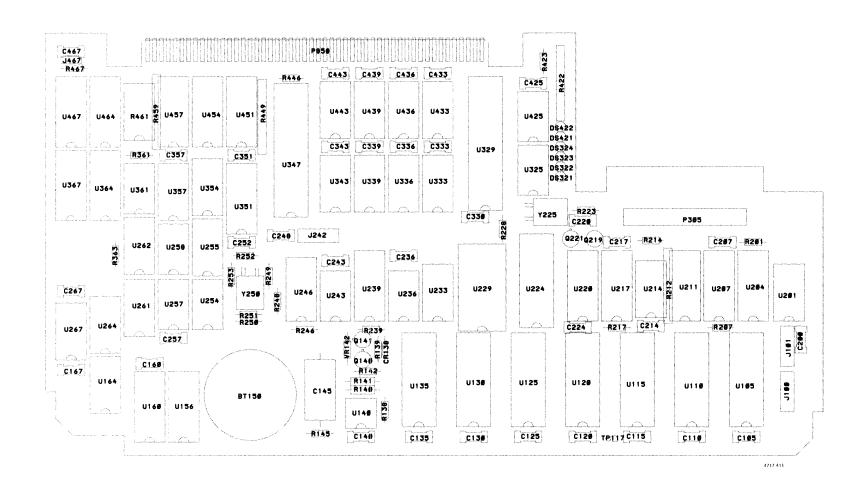

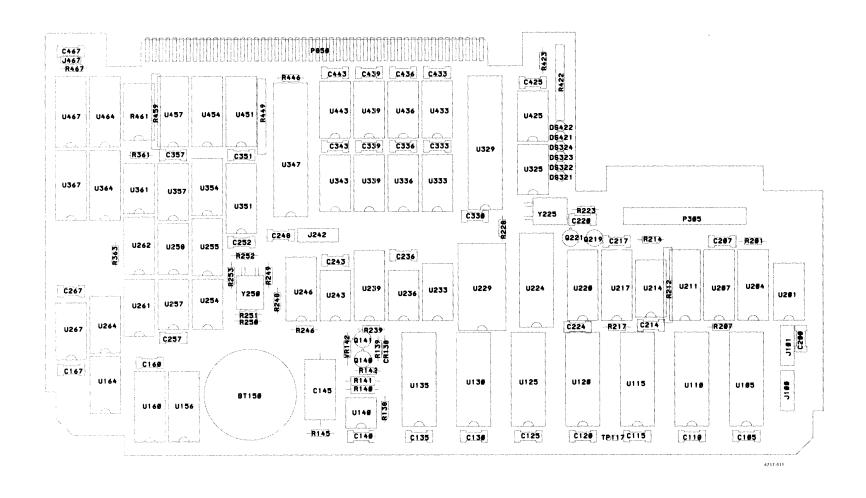

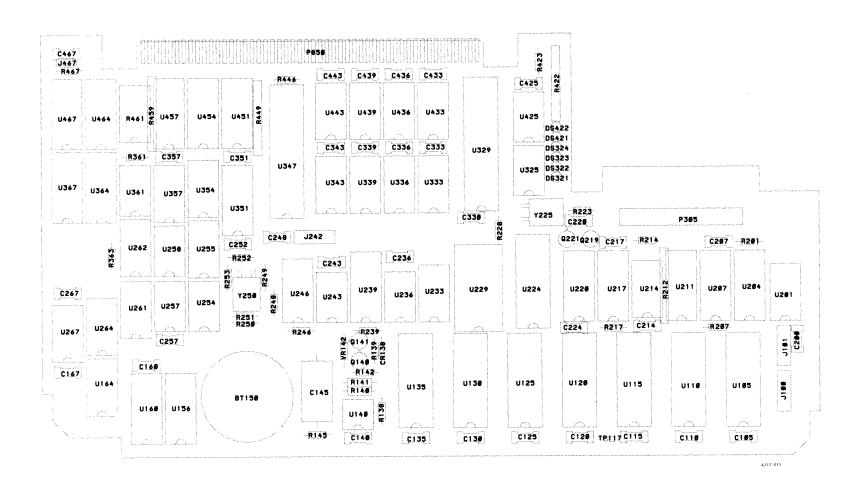

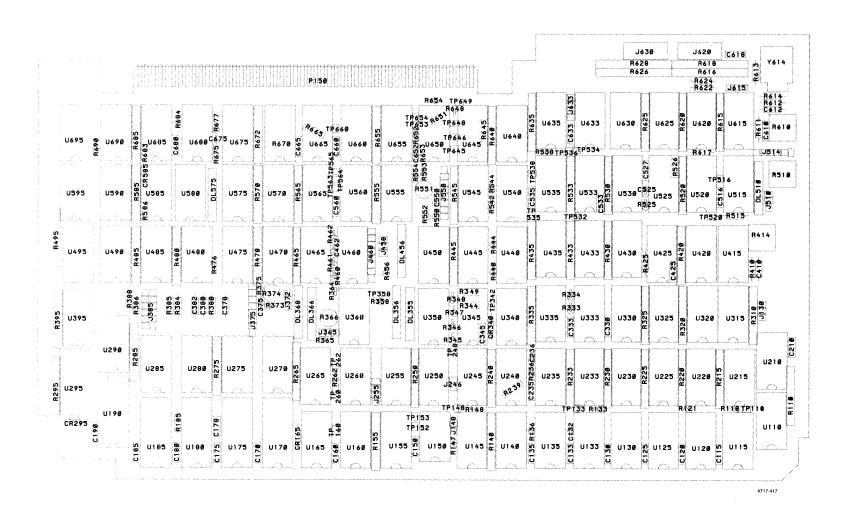

| 4-2          | 1240 mainframe board locations                                      | 4-3          |

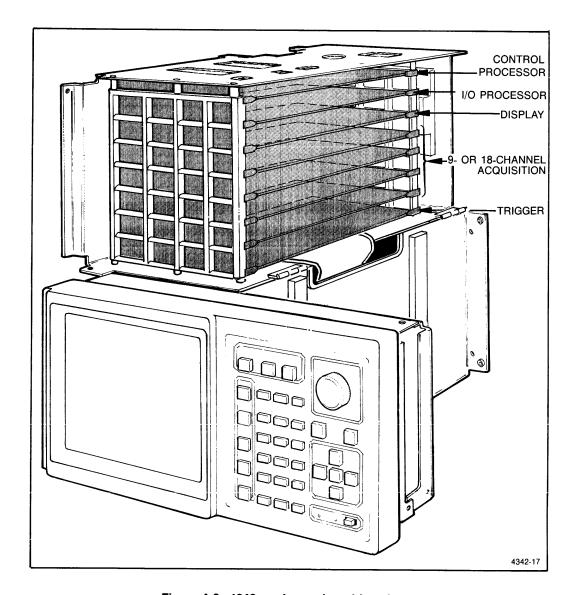

| 4-3          | 1240 card-cage board locations                                      | 4-4          |

| 4-4<br>4-5   | Simplified trigger block diagram                                    | 4-9          |

| 4-5<br>4-6   | Power Supply Board functional block diagram                         | 4-11         |

| 4-0          | CRT Drive Board functional block diagram                            | 4-14         |

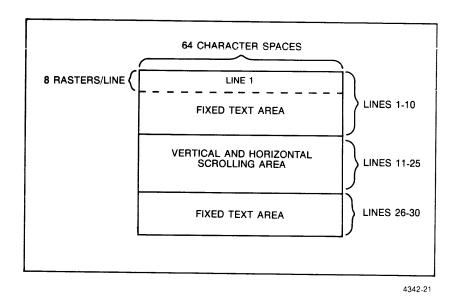

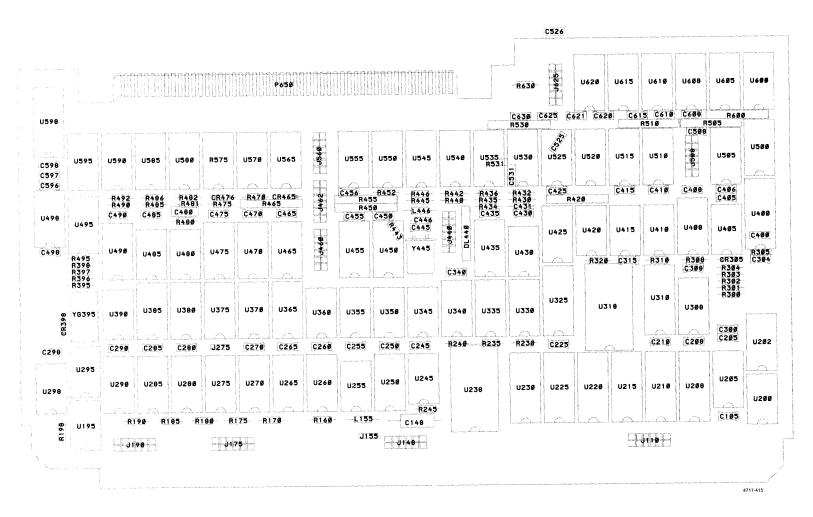

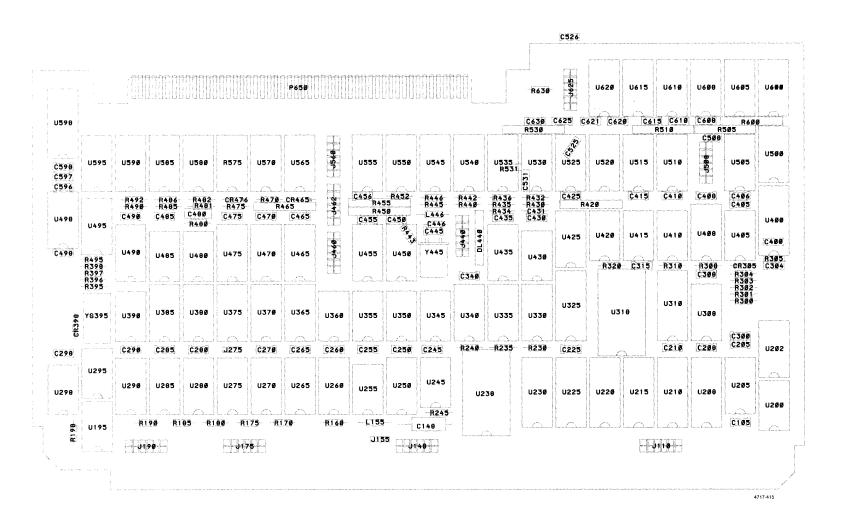

| 4-8          | 1240 display screen                                                 | 4-17<br>4-18 |

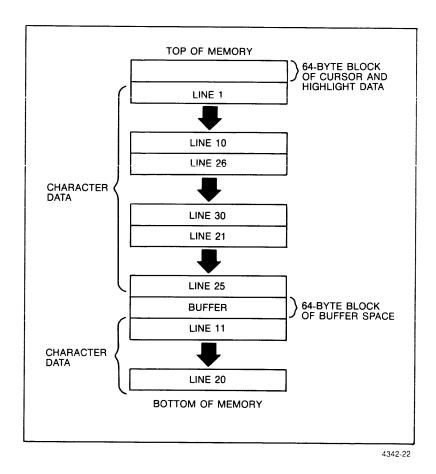

| 4-9          | Display RAM memory map                                              | 4-10         |

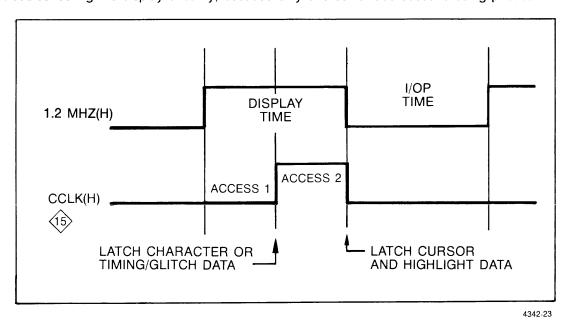

| 4-10         | Display memory access times                                         | 4-21         |

| 4-11         | LED/PT and Keyboard functional block diagram                        | 4-25         |

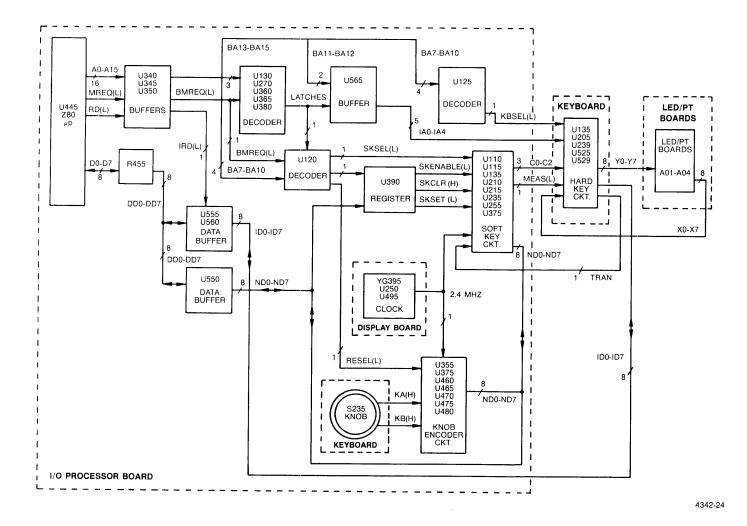

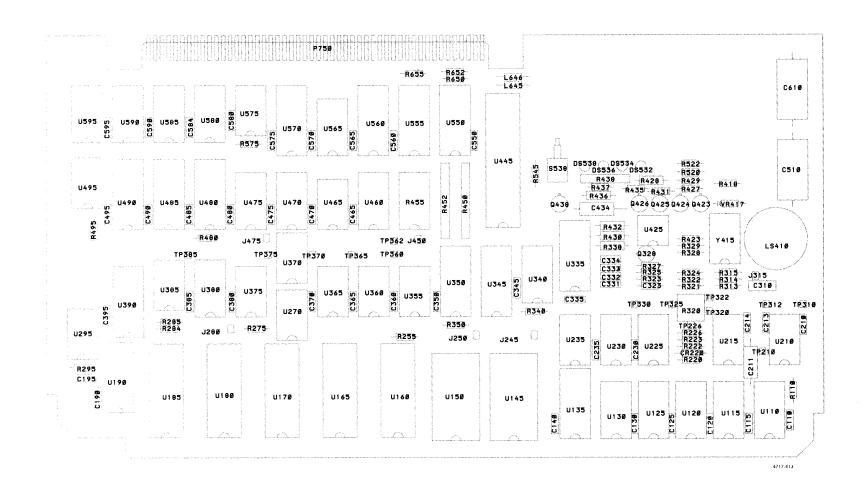

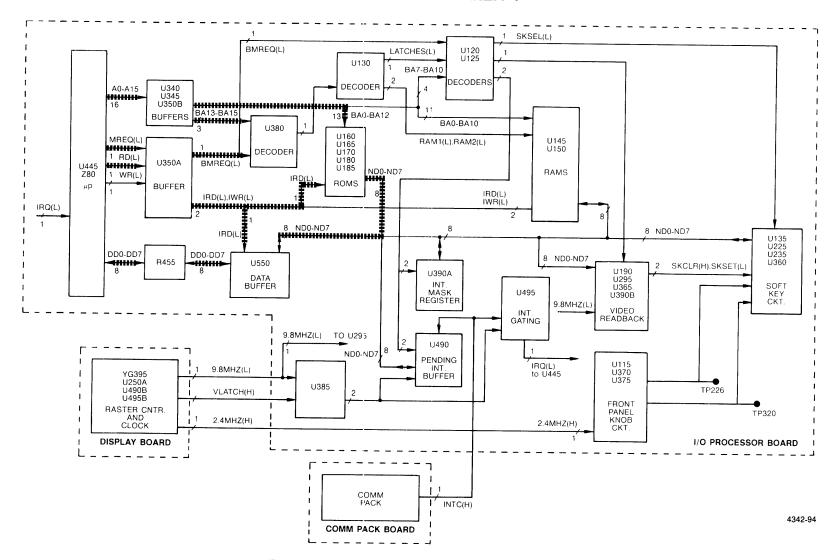

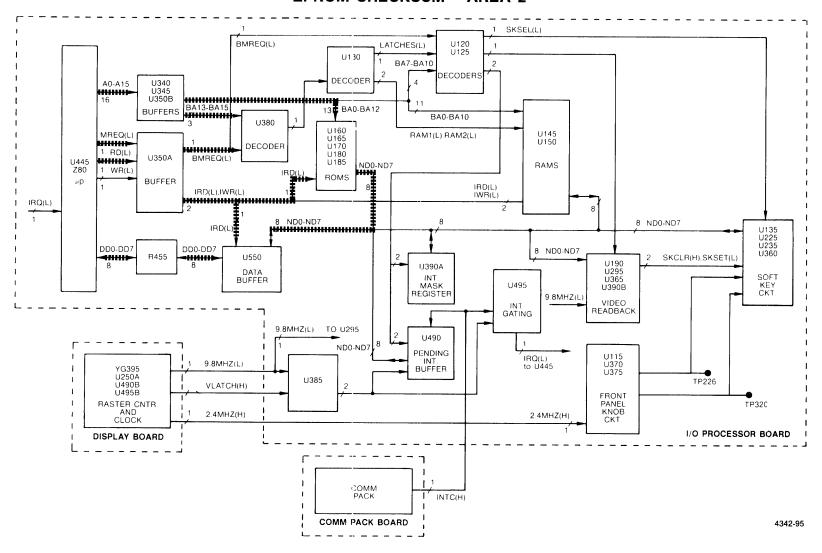

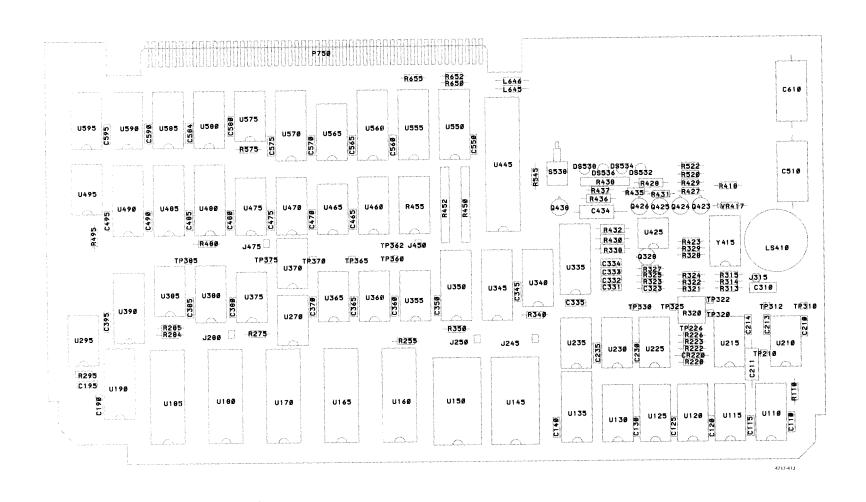

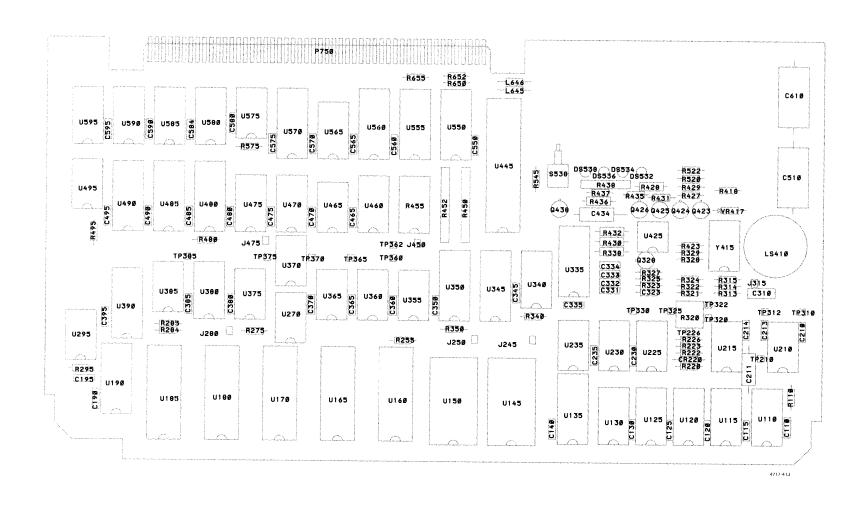

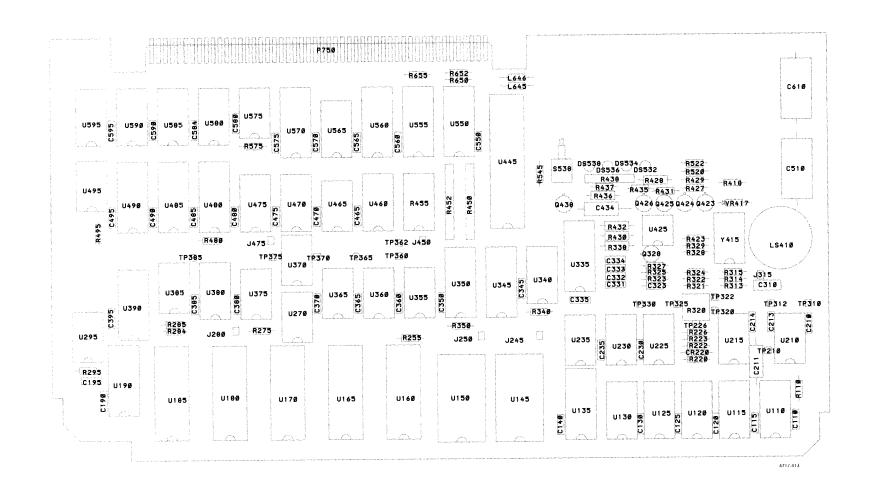

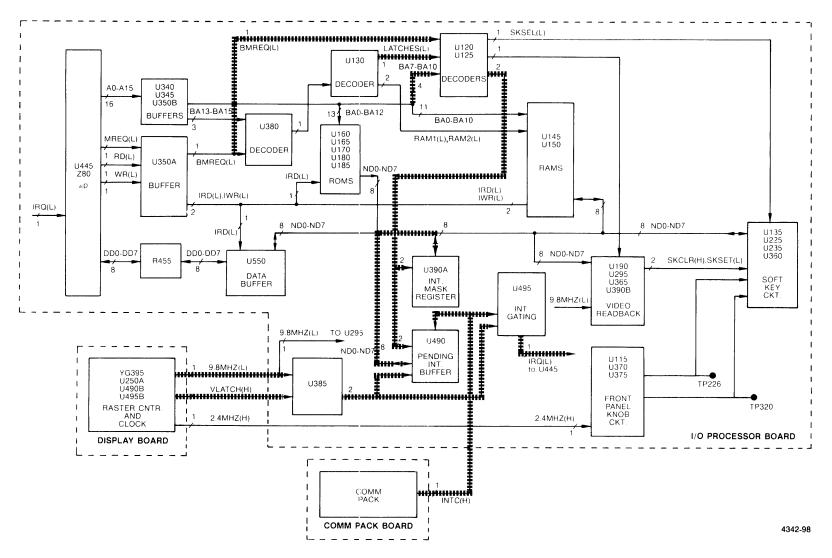

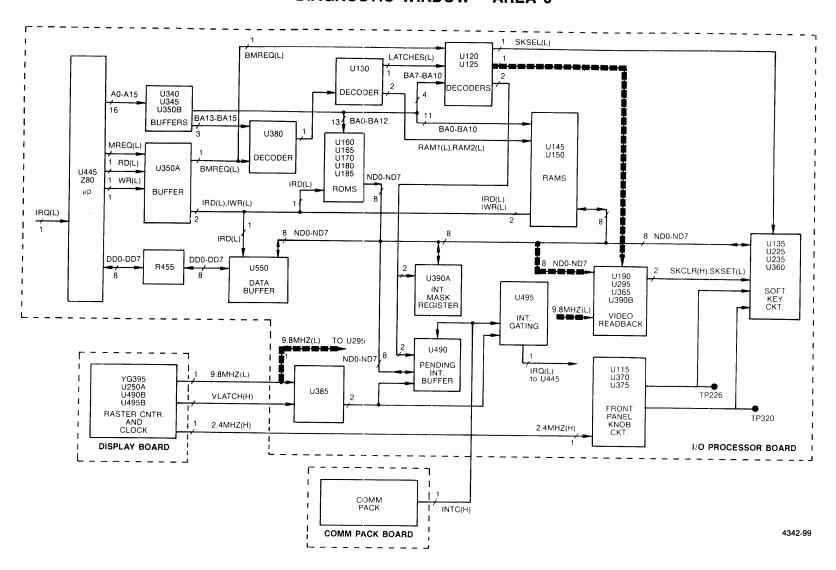

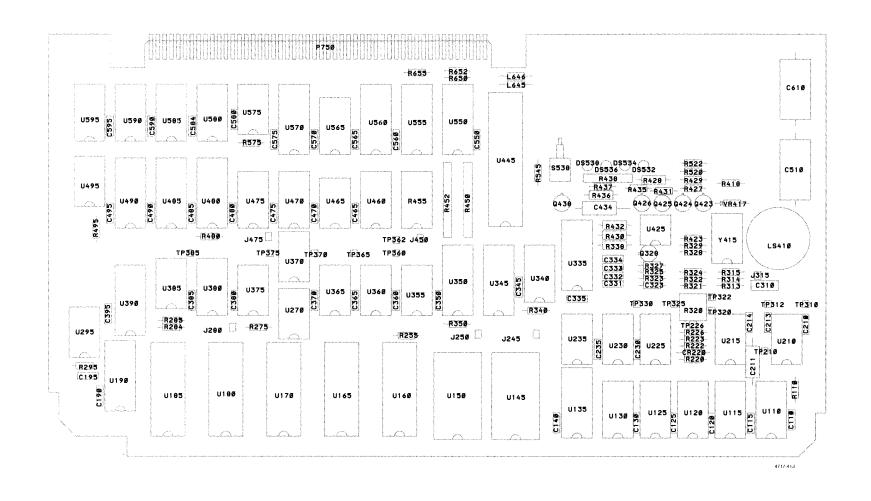

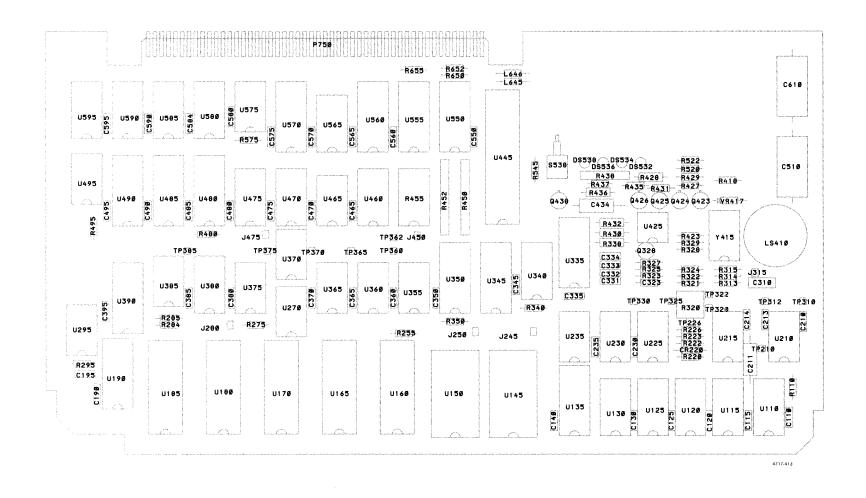

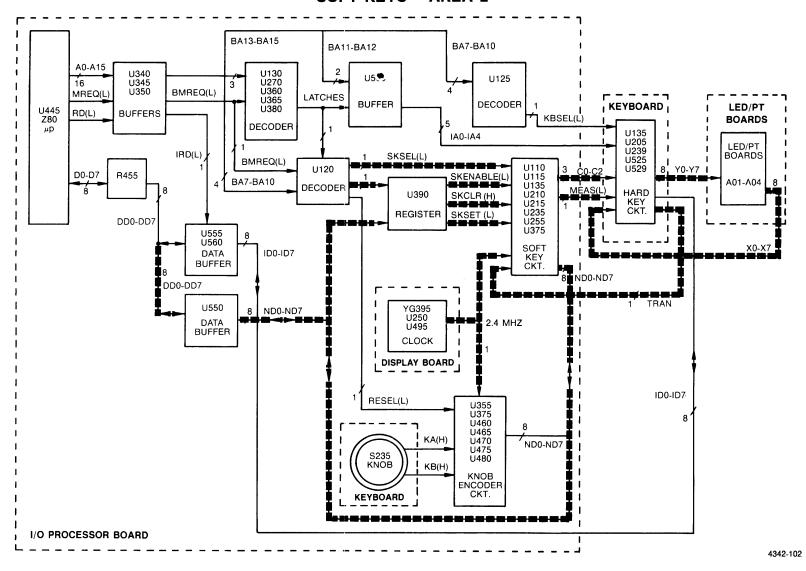

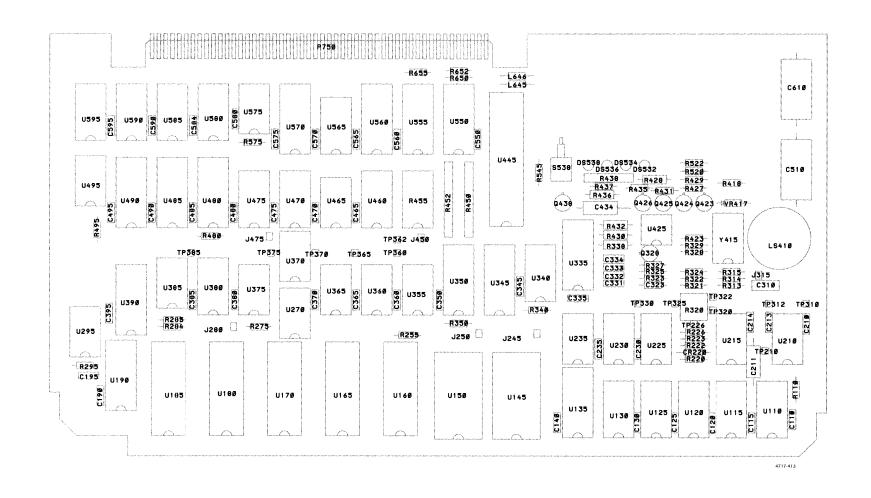

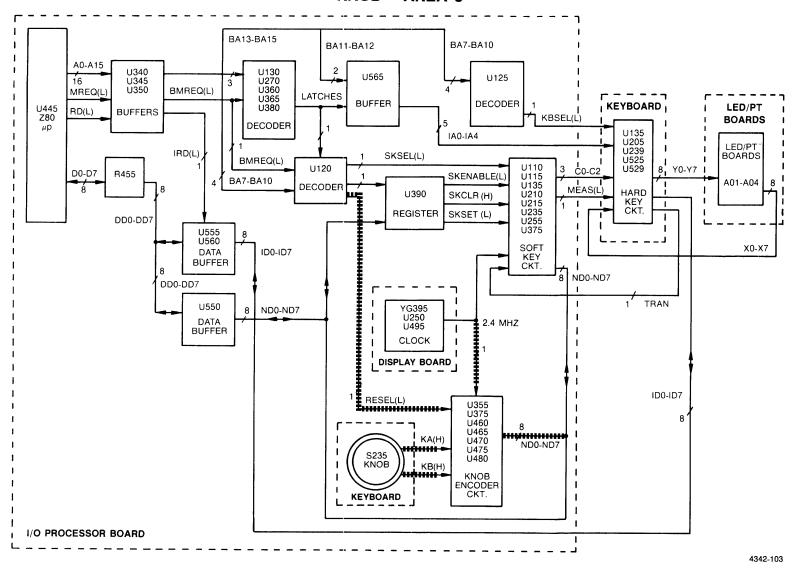

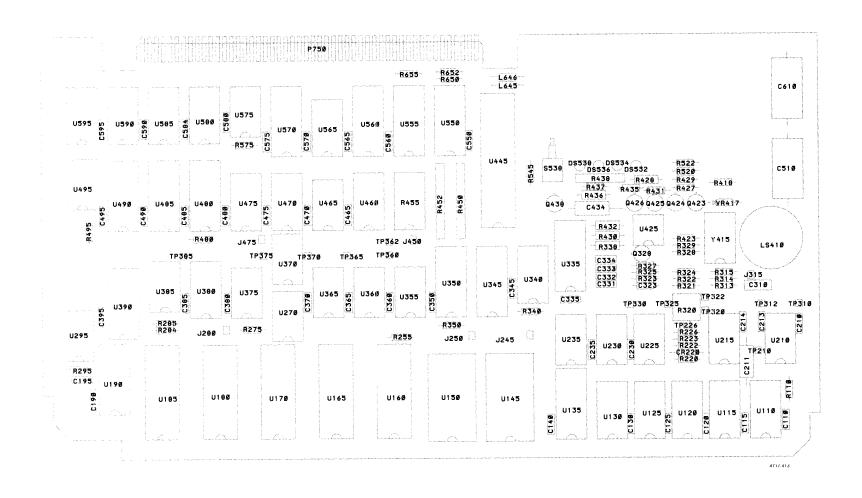

| 4-12         | I/O Processor Board functional block diagram                        | 4-28         |

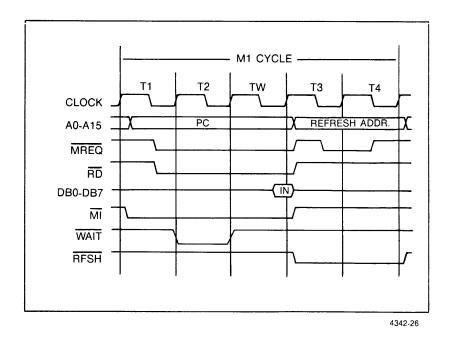

| 4-13         | Instruction opcode fetch with wait states                           | 4-30         |

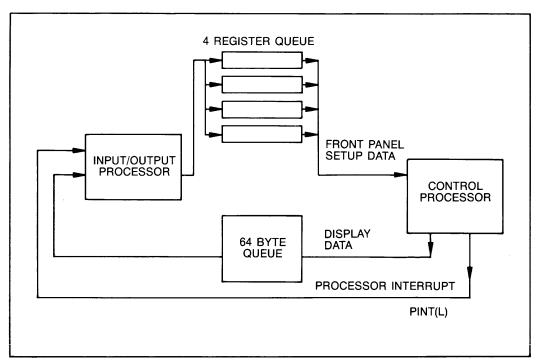

| 4-14         | Inter-processor communication path                                  | 4-33         |

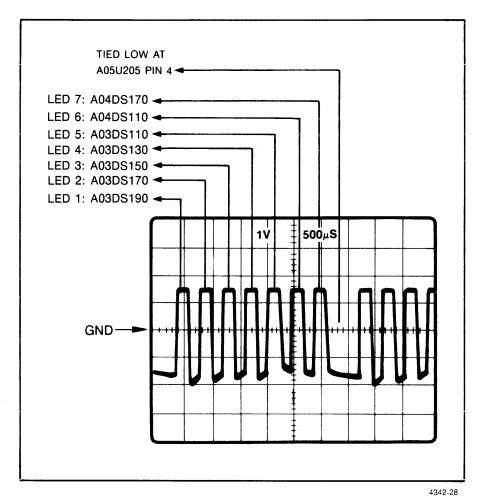

| 4-15         | Data pulses corresponding to soft key boxes                         | 4-36         |

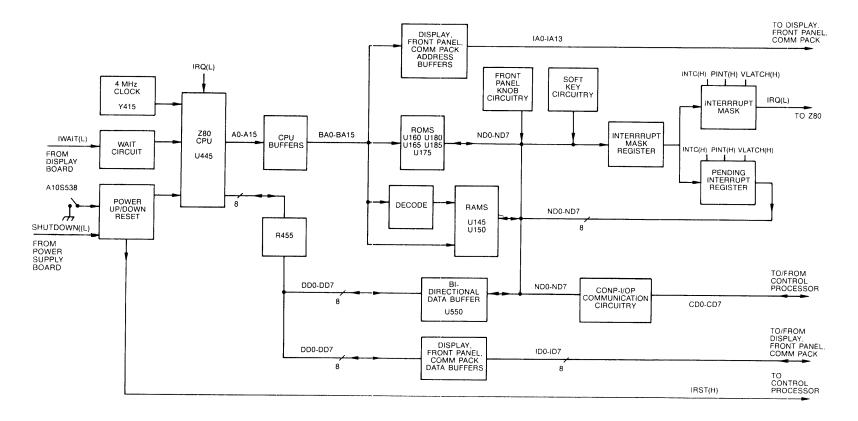

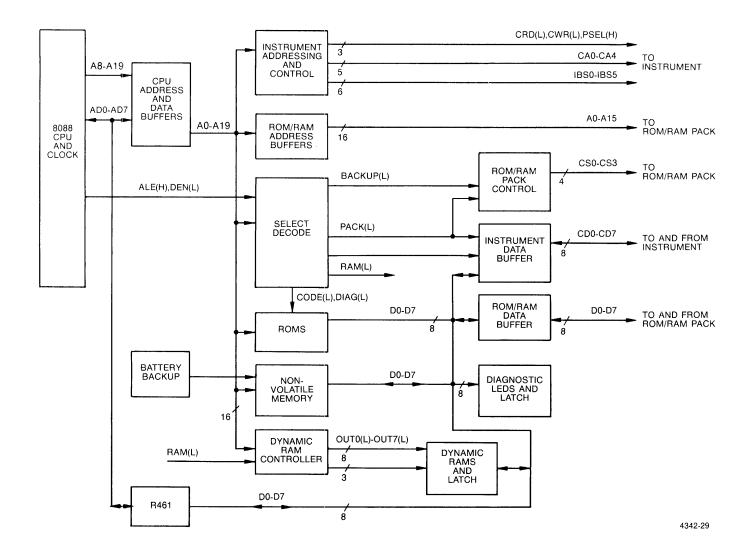

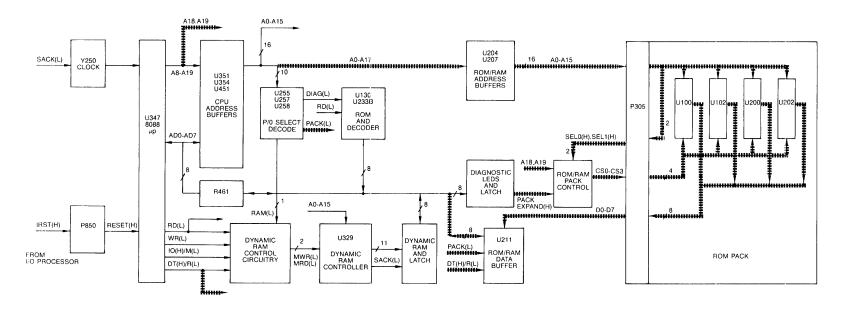

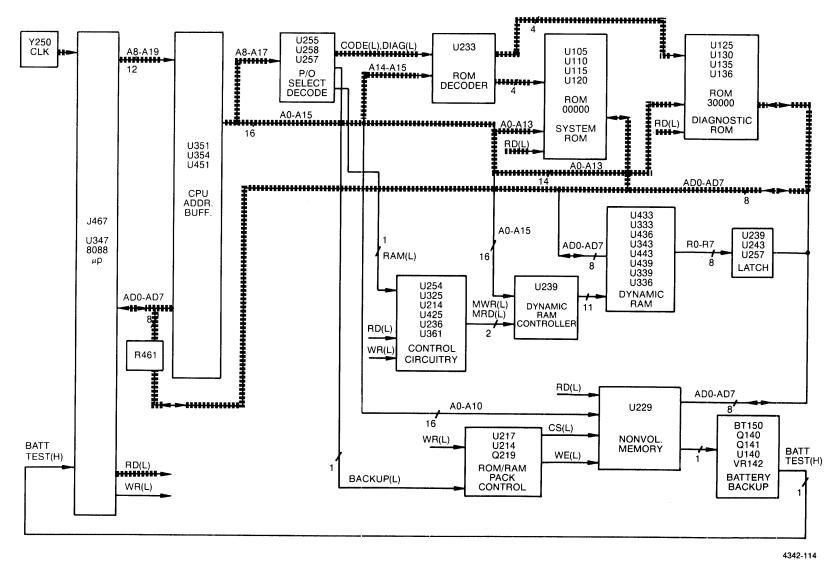

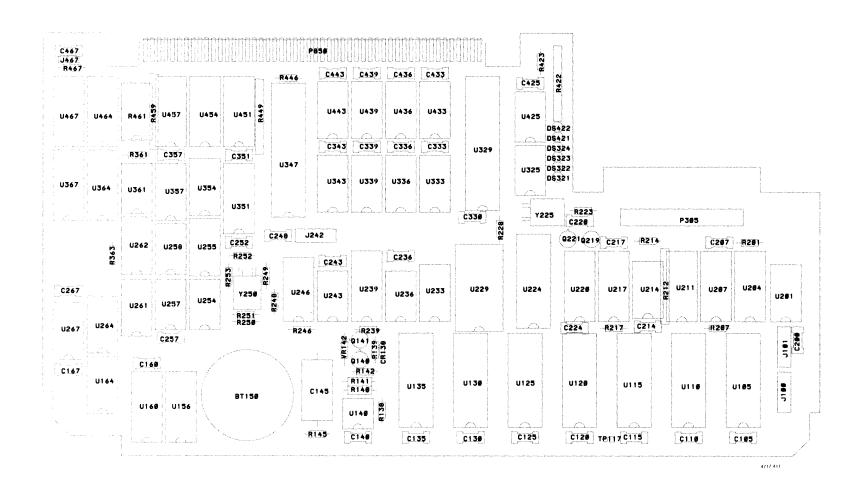

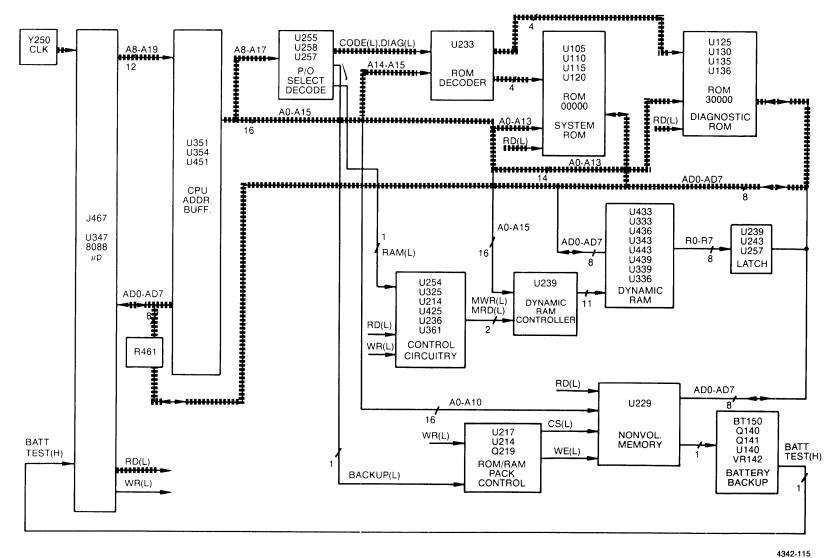

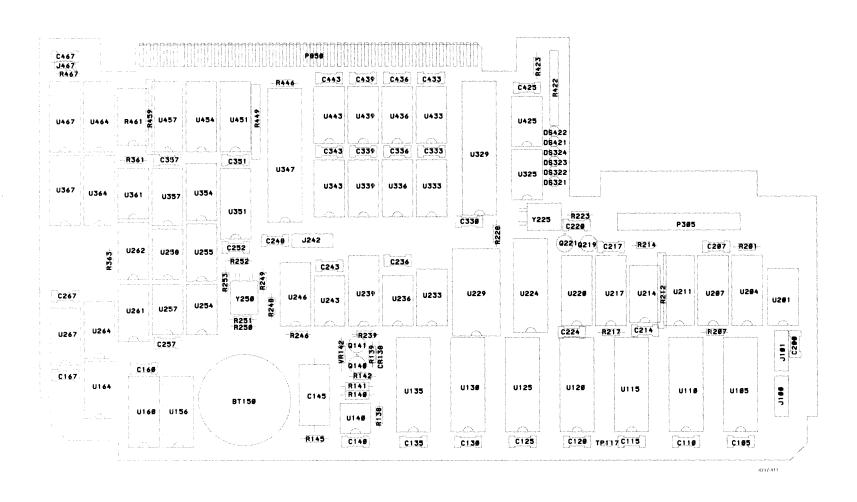

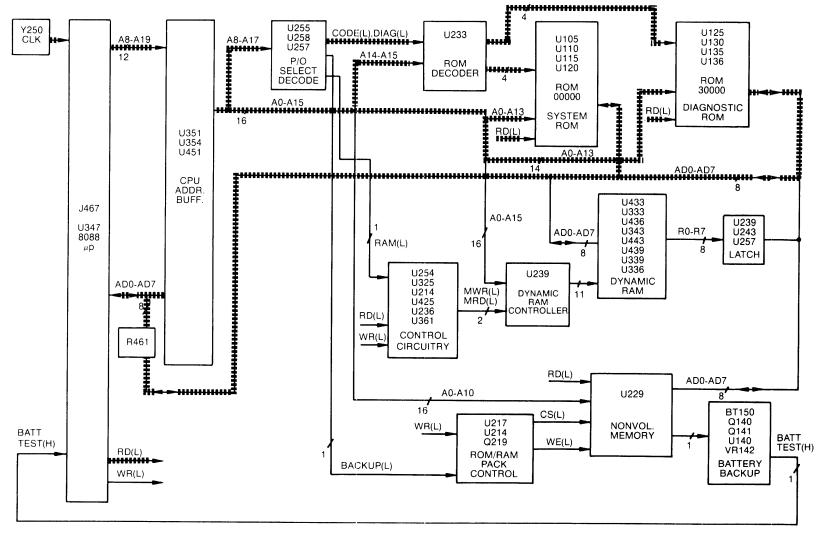

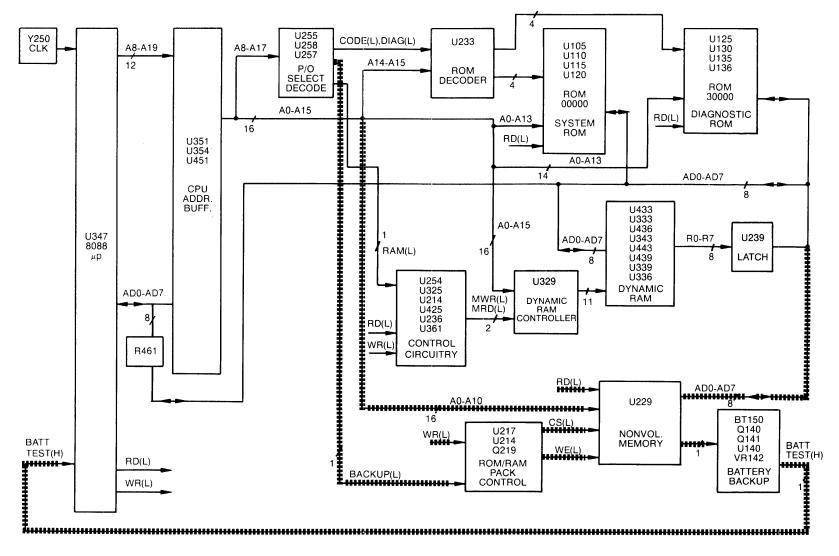

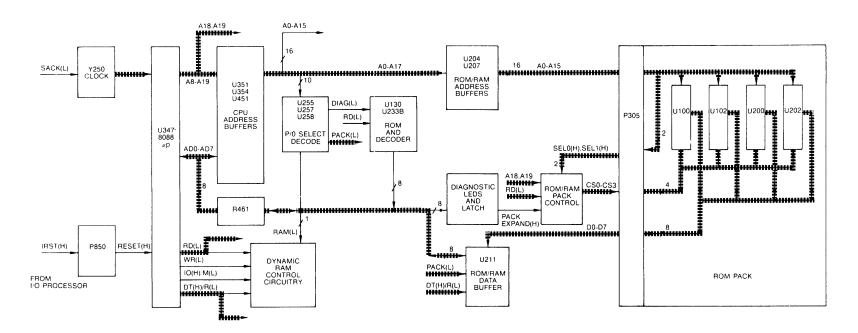

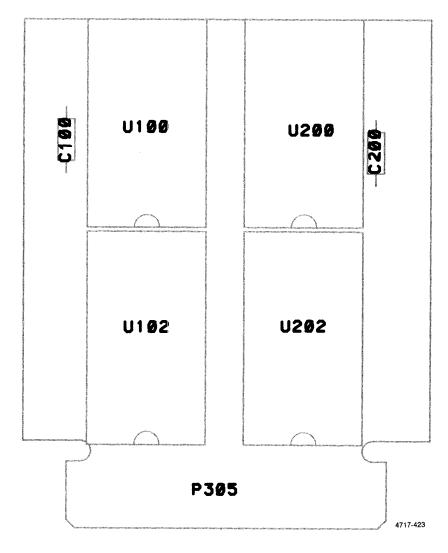

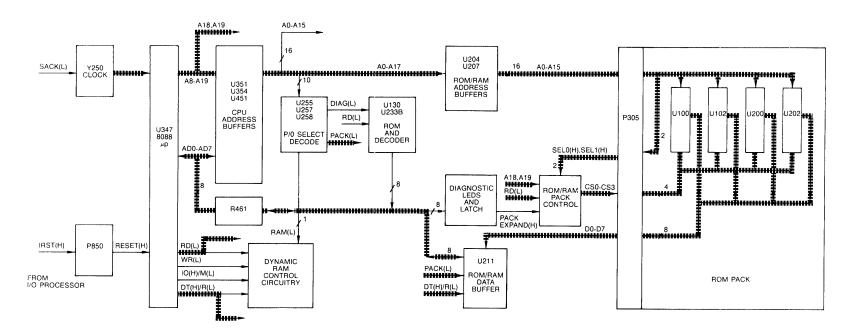

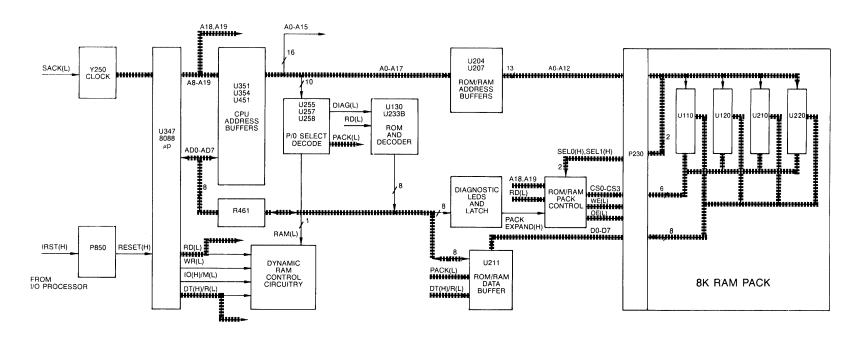

| 4-16         | Control Processor Board functional block diagram                    | 4-37         |

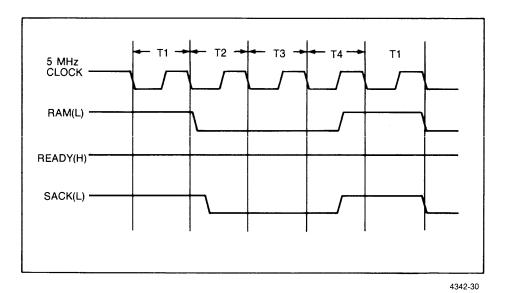

| 4-17<br>4-18 | READY signal not causing a wait state                               | 4-39         |

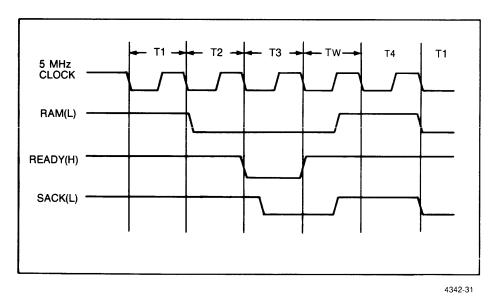

| 4-18<br>4-19 | READY signal causing one extra wait state                           | 4-39         |

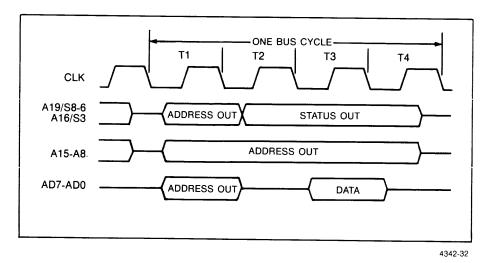

|              | Bus cycle with multiplexed address/data on AD bus                   | 4-40         |

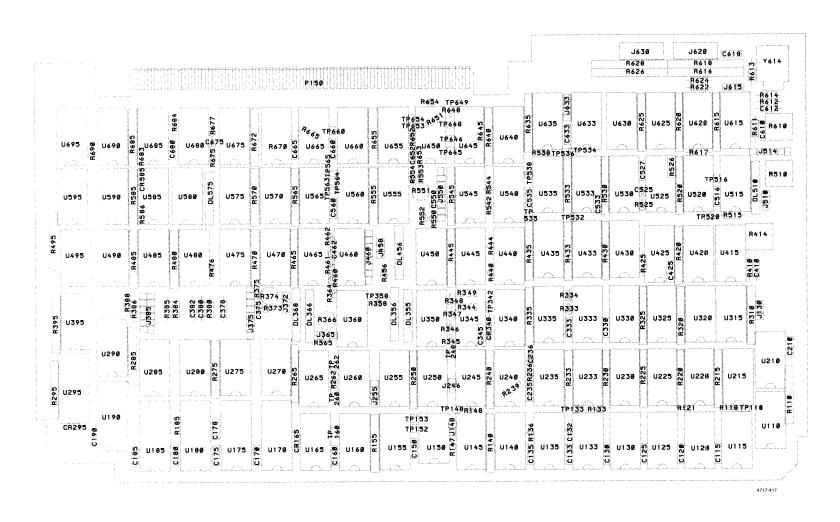

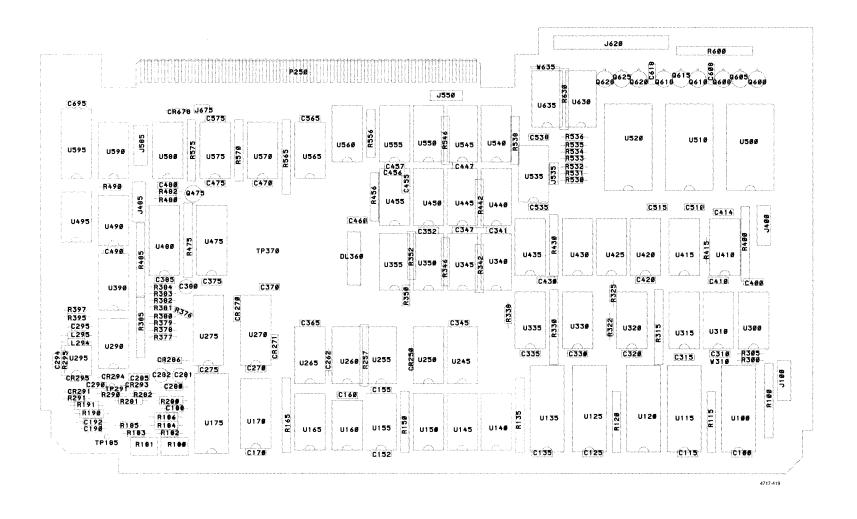

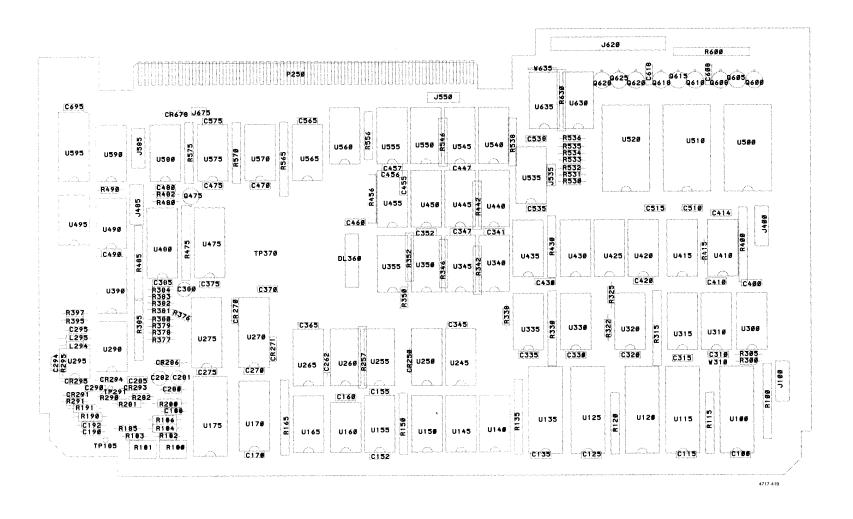

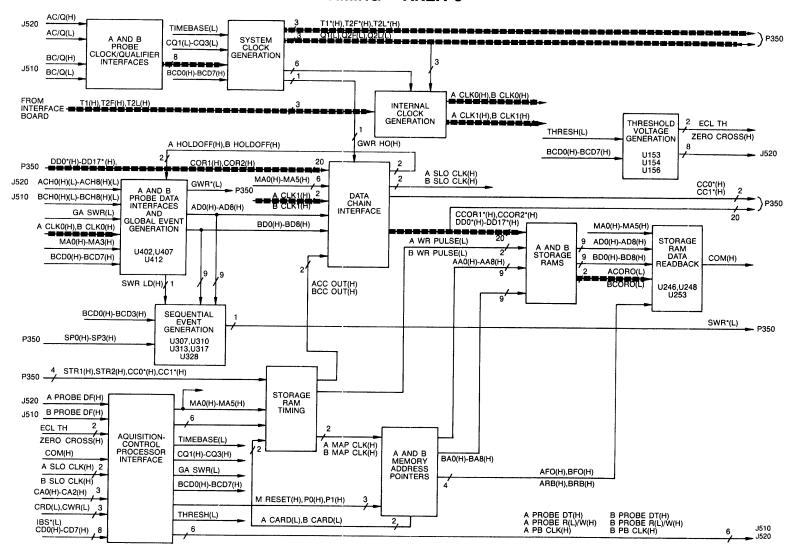

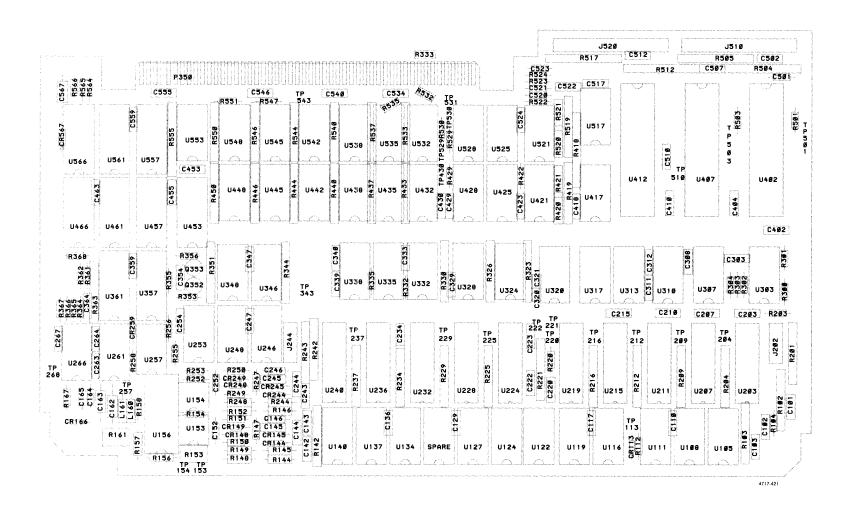

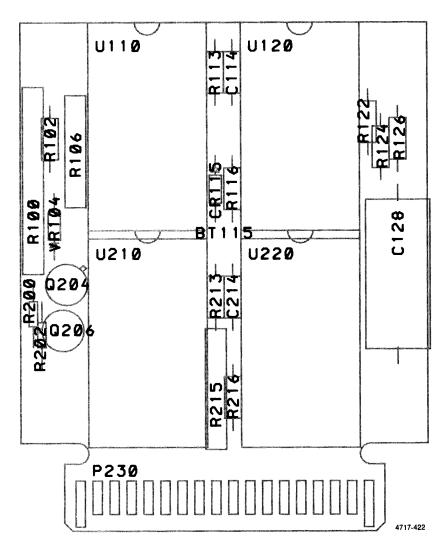

|              | 9-Channel Acquisition Board functional block diagram                | 4-42         |

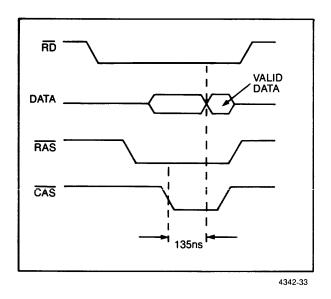

|              | Data chain interface                                                | 4-45<br>4-50 |

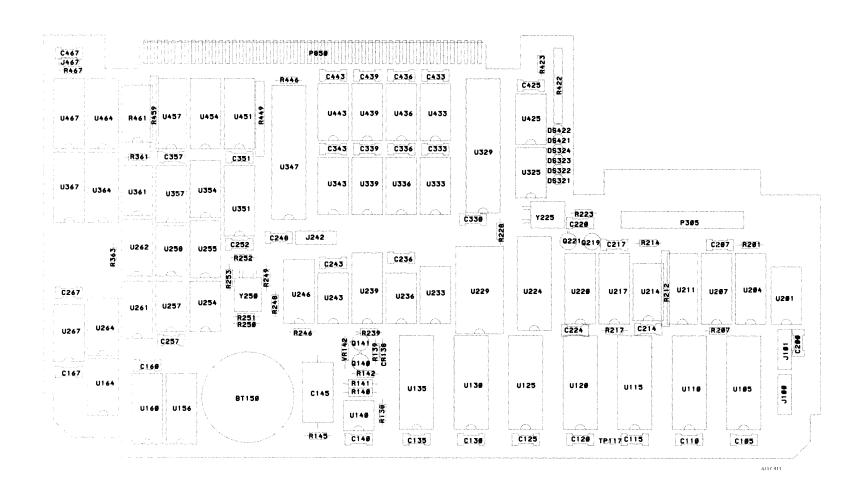

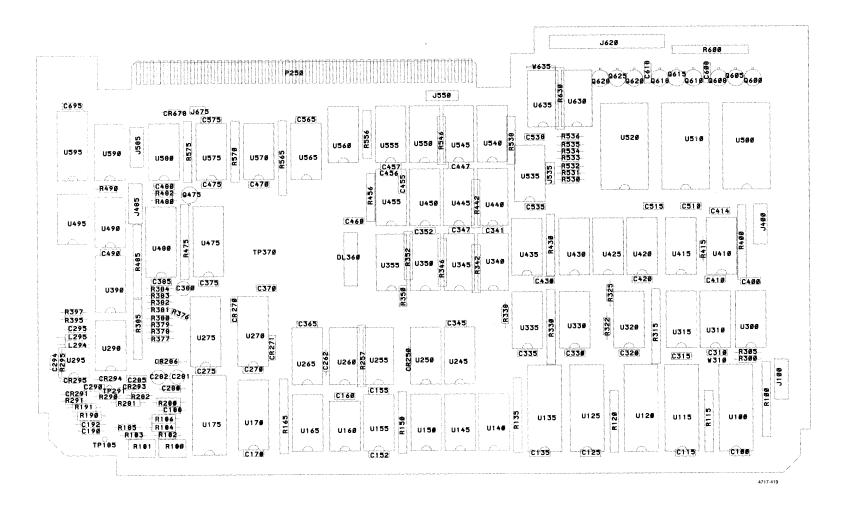

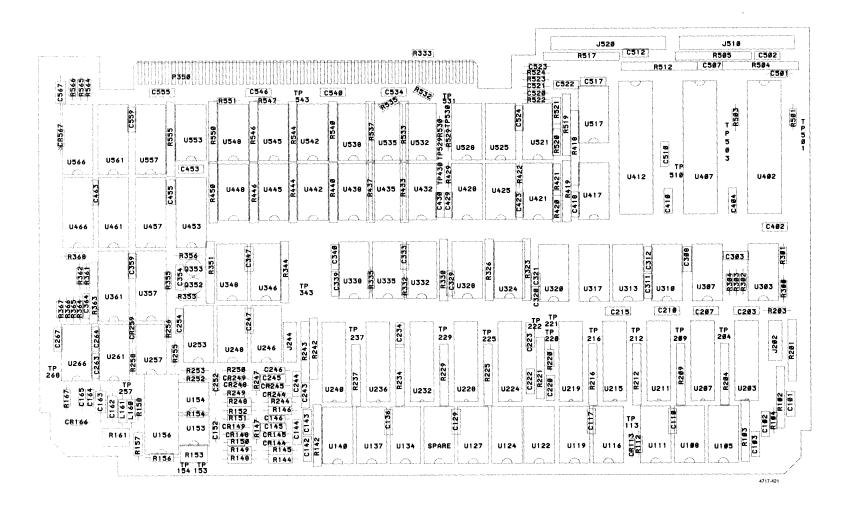

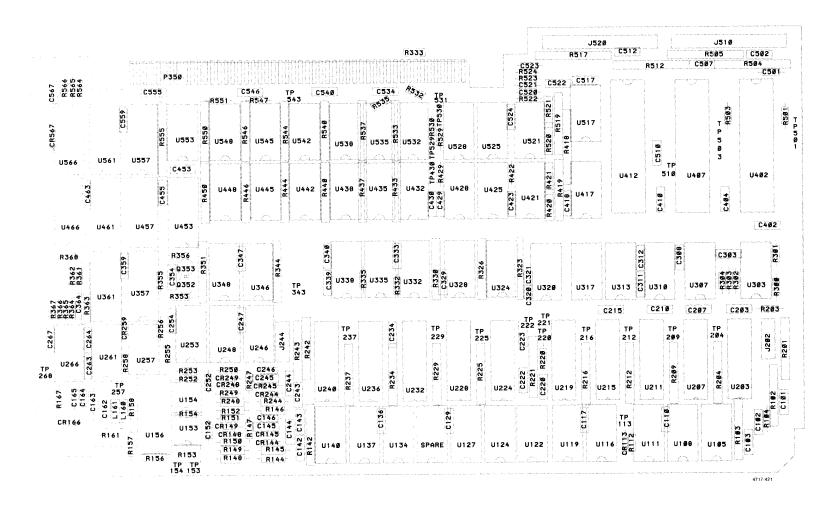

|              | 18-Channel Acquisition Board functional block diagram               | 4-50         |

| 4-24         | Data chain interface                                                | 4-56         |

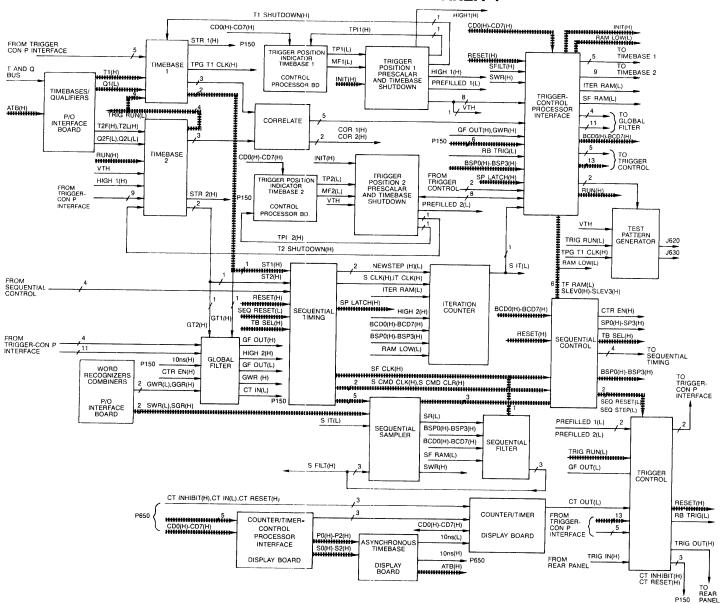

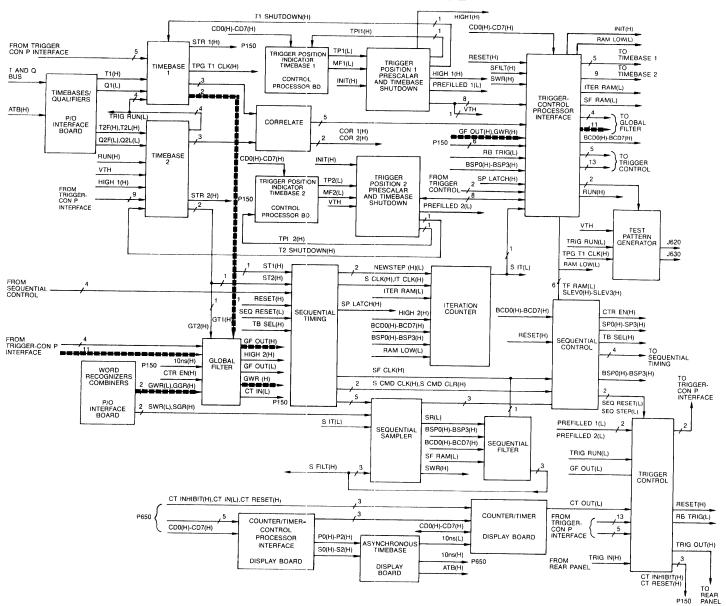

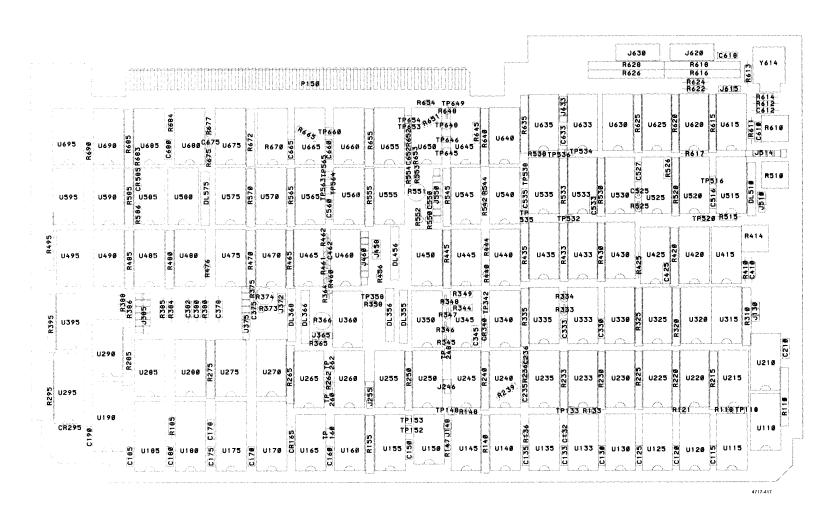

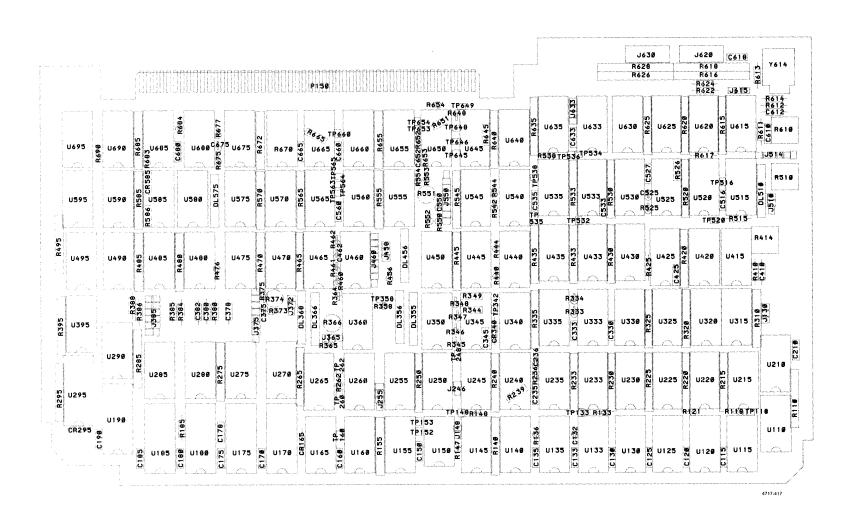

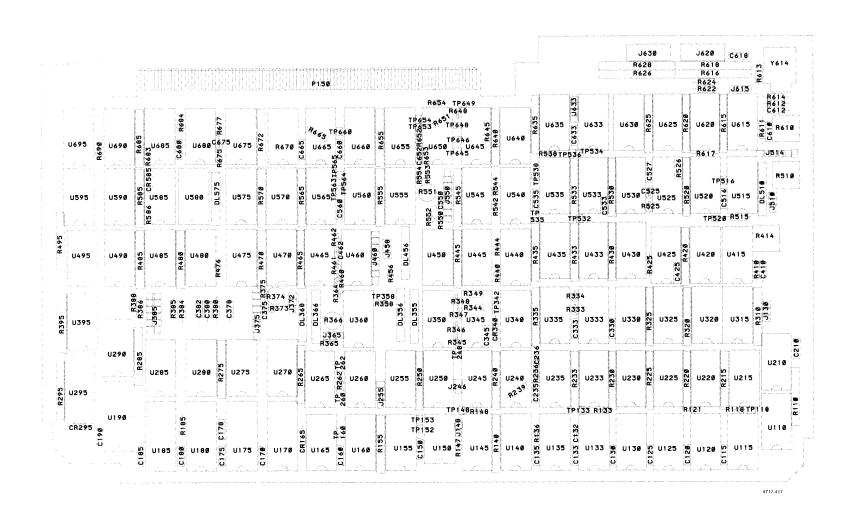

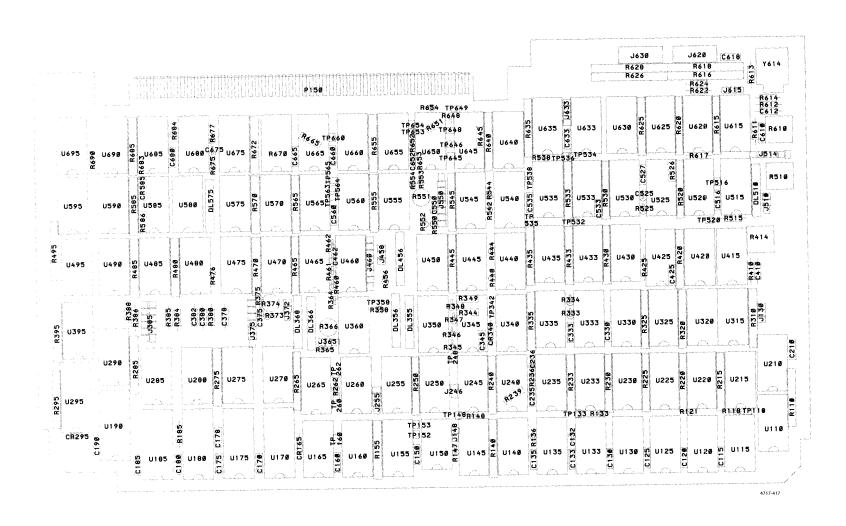

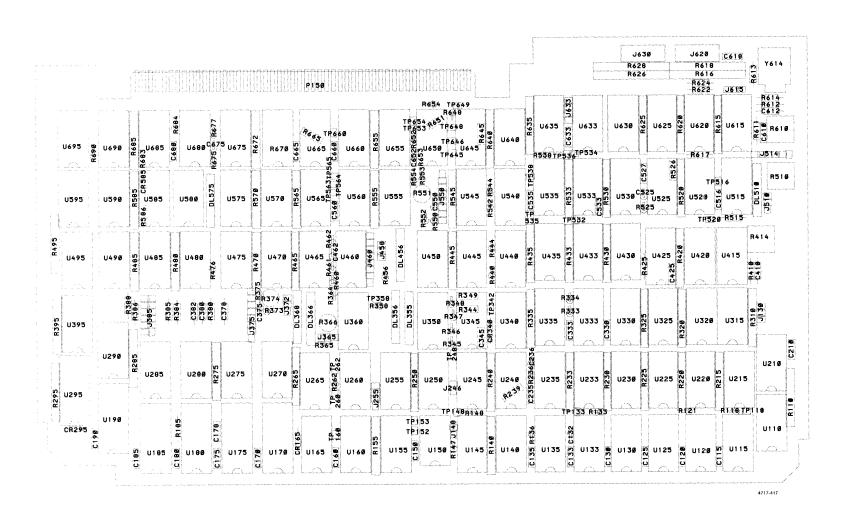

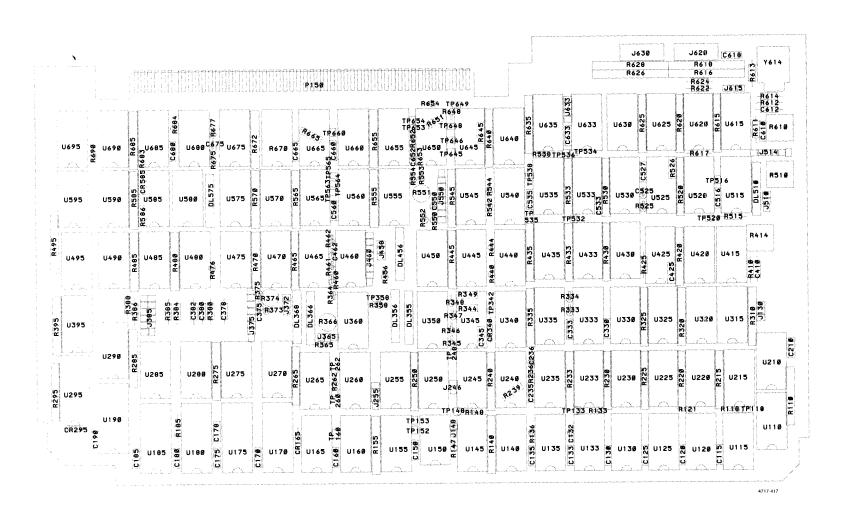

| 4-25         | Trigger Board functional block diagram                              | 4-58         |

| Figure |                                                                               | Page  |

|--------|-------------------------------------------------------------------------------|-------|

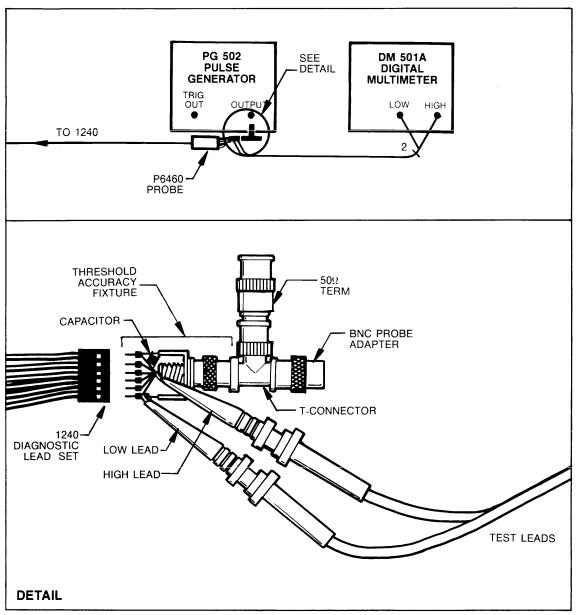

| 5-1    | Acquisition threshold adjust fixture                                          | 5-5   |

| 5-2    | Typical diagnostic power-up display                                           | 5-6   |

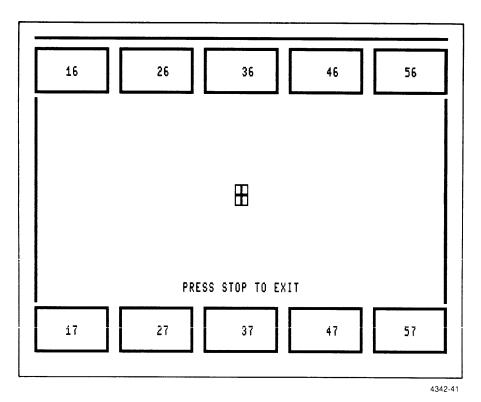

| 5-3    | Front panel keyboard manual test display                                      | 5-7   |

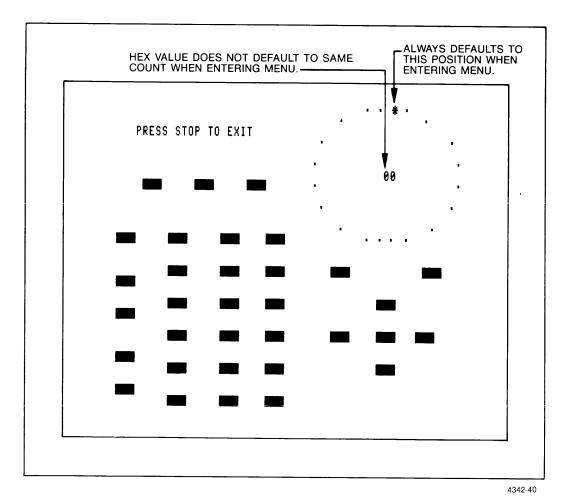

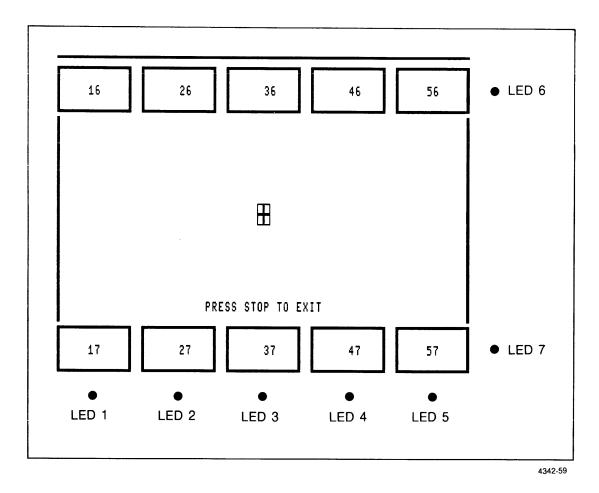

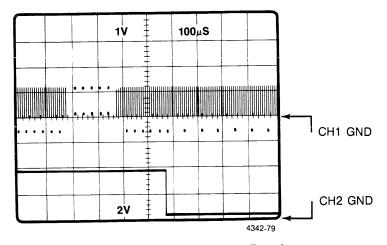

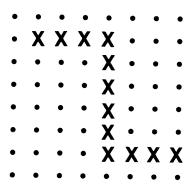

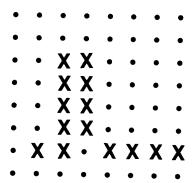

| 5-4    | Soft key adjustment pattern                                                   | 5-8   |

| 5-5    | Expanded view of the Interface Board shows power supply measurment pins       | 5-11  |

| 5-6    | Glitch detection functionality check results                                  | 5-20  |

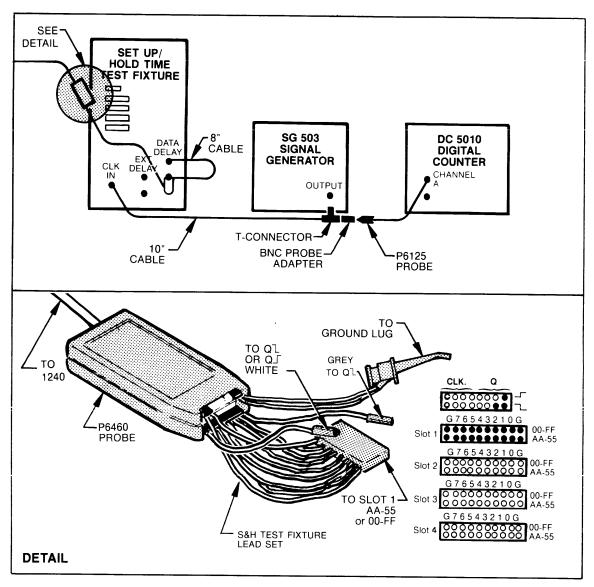

| 5-7    | Verification setup A                                                          | 5-22  |

| 5-8    | Verification setup B                                                          | 5-23  |

| 5-9    | Verification setup C                                                          | 5-24  |

| 5-10   | Verification setup D                                                          | 5-25  |

| 5-11   | Verification setup E                                                          | 5-26  |

| 5-12   | Expanded view of the Interface Board shows power supply measurement pins      | 5-78  |

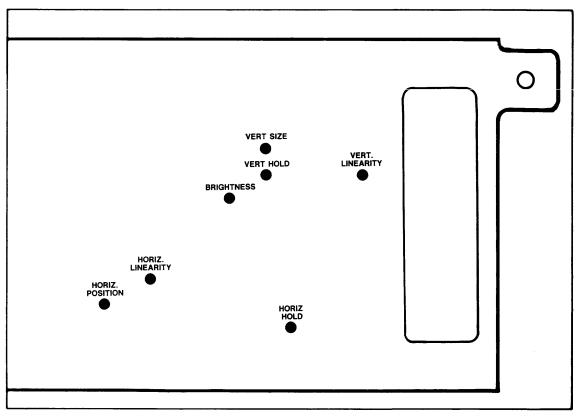

| 5-13   | 1240 side showing CRT Drive Board adjustment holes                            | 5-79  |

| 5-14   | Expanded view of the I/O Processor Board shows components used in Soft Key    |       |

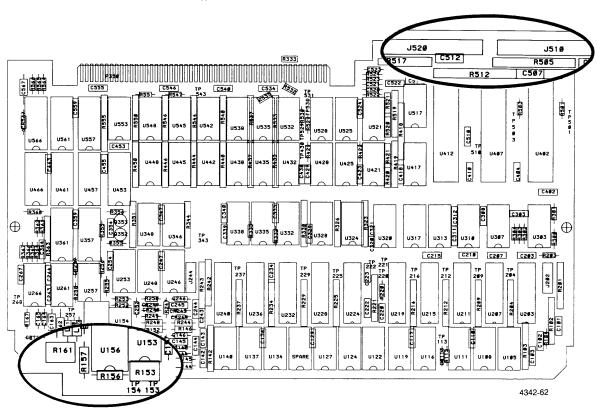

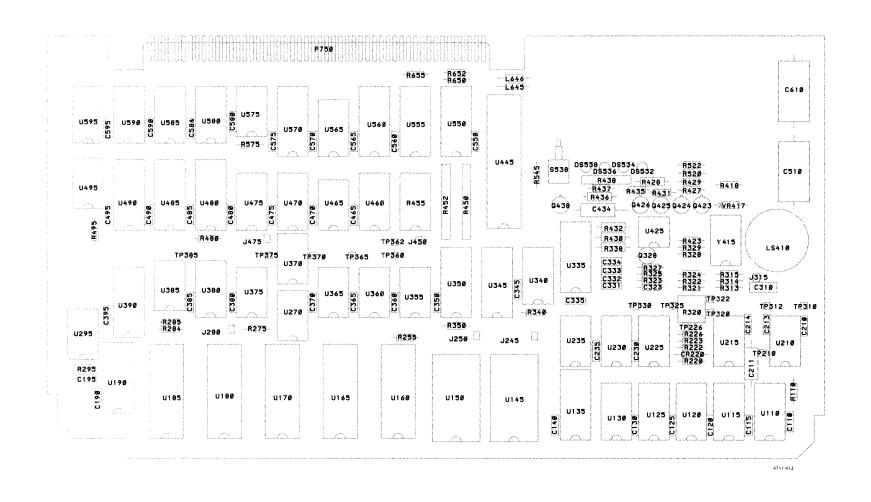

|        | Sensitivity Adjust                                                            | 5-81  |

| 5-15   | Soft key adjustment pattern showing screen boxes and corresponding LED pairs  | 5-82  |

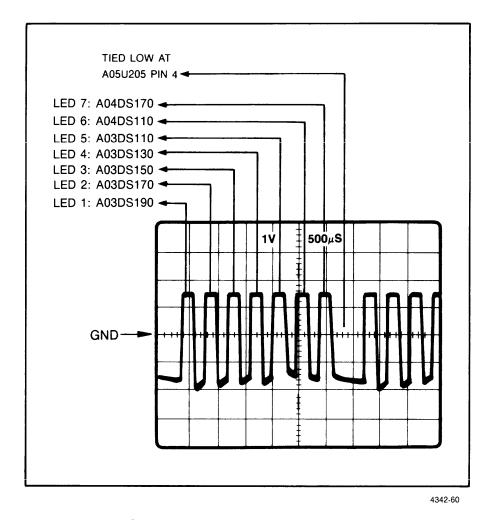

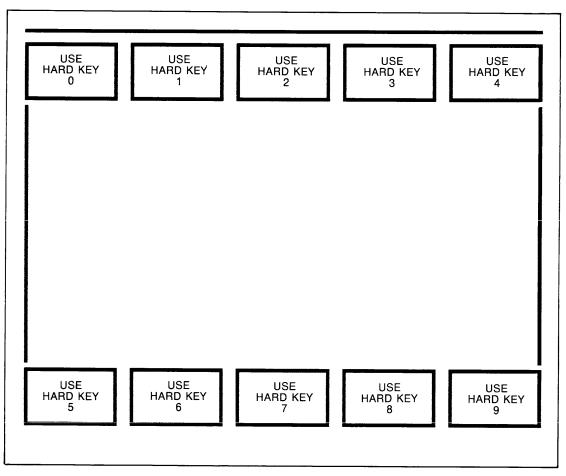

| 5-16   | Soft key adjustment pulses and corresponding LEDs                             | 5-83  |

| 5-17   | Expanded view of the 1240D1 9-Channel Acquisition Board shows components      |       |

|        | used in the Threshold Adjust                                                  | 5-84  |

| 5-18   | Expanded view of the 1240D2 18-Channel Acquisition Board shows components     |       |

|        | used in the Threshold Adjust                                                  | 5-85  |

| 5-19   | Expanded view of the Trigger Board shows components used in the TPG Adjust .  | 5-87  |

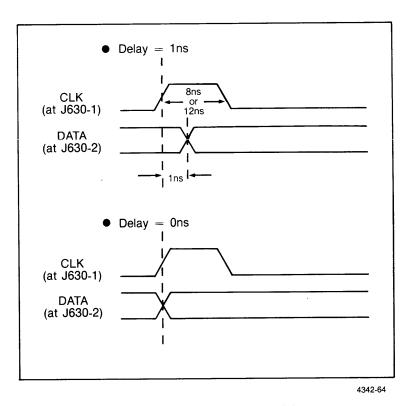

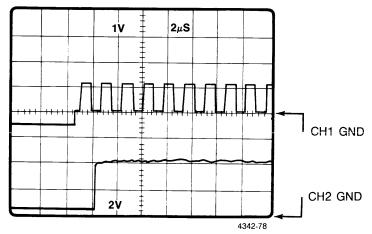

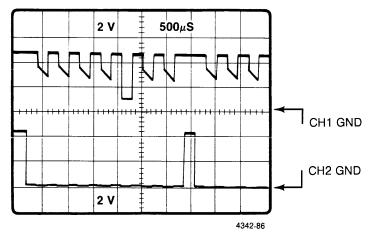

| 5-20   | TPG clock and data delays                                                     | 5-89  |

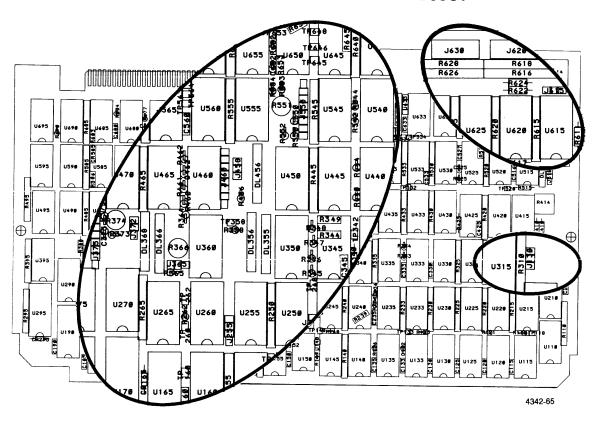

| 5-21   | Expanded view of the Trigger Board shows components used in Timebase 1 Adjust | 5-90  |

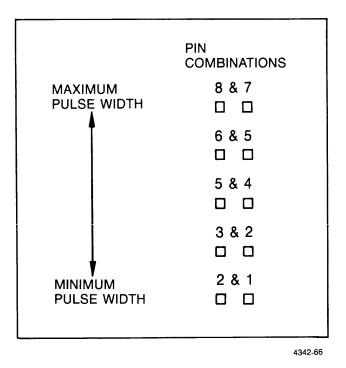

| 5-22   | Pin combinations for Timebase 1 adjust                                        | 5-93  |

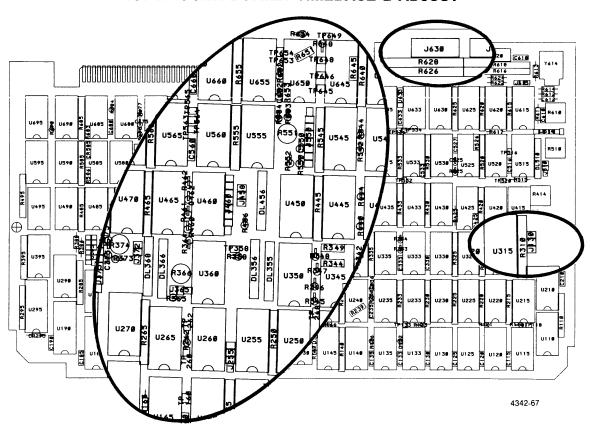

| 5-23   | Expanded view of the Trigger Board shows components used in Timebase 2        |       |

|        | Adjust                                                                        | 5-96  |

| 5-24   | Expanded view of the Trigger Board shows components used in Sequential Timing |       |

|        | Adjust                                                                        | 5-99  |

| 5-25   | Expanded view of the Display Board shows components used in Counter/Timer     |       |

|        | Adjust                                                                        | 5-100 |

| 5-26   | Expanded view of the CRT Drive Board shows components used in External        |       |

|        | Trigger Adjust                                                                | 5-103 |

|        |                                                                               |       |

| 6-1    | Location of screws for card cage roll                                         | 6-3   |

| 6-2    | 1240 card-cage board assignments                                              | 6-5   |

| 6-3    | Location of screws for CRT Board bracket removal                              | 6-7   |

| 6-4    | Discharging a CRT using a flat-blade screwdriver                              | 6-9   |

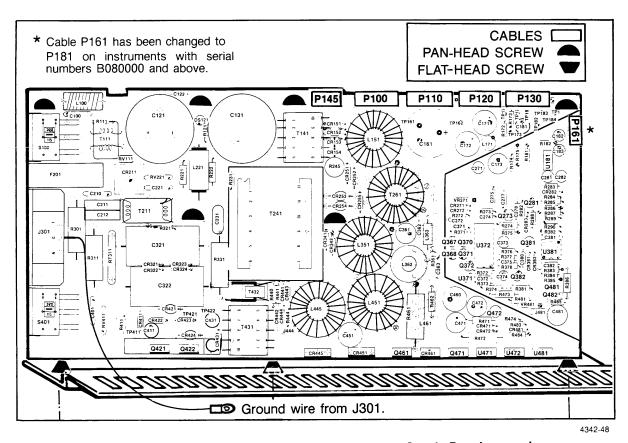

| 6-5    | Location of screws and cables for Power Supply Board removal                  | 6-11  |

| 6-6    | Location of screws for fan removal                                            | 6-13  |

|        |                                                                               |       |

| 7-1    | Multi-conductor terminal connectors                                           | 7-6   |

| 7-2    | Circuit board pin replacement                                                 | 7-7   |

REV SEPT 1985

| Figure |                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------|------|

| 8-1    | 1240 power supply troubleshooting tree                                               | 8-7  |

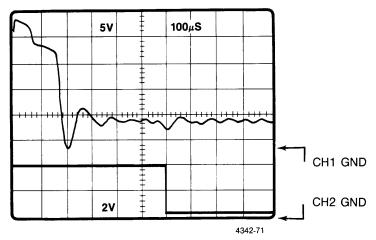

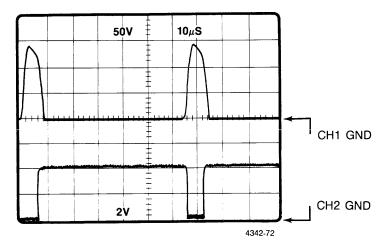

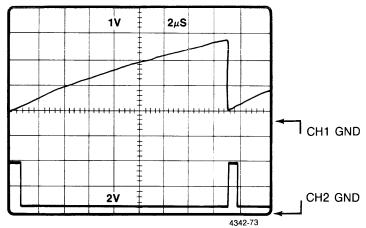

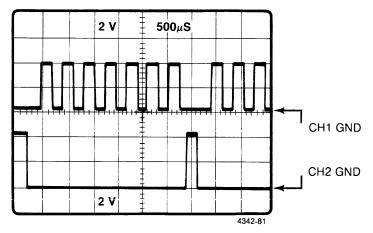

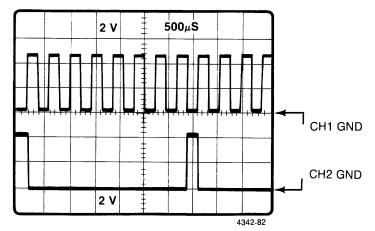

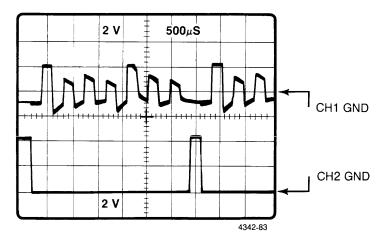

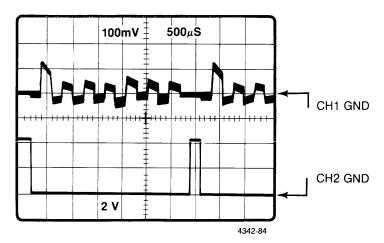

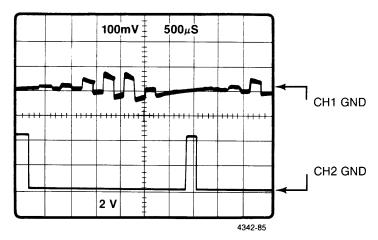

| 8-2    | A06TP414 vertical sweep out; A06TP111 VDRIVE(H)                                      | 8-11 |

| 8-3    | A06TP452 horizontal flyback; A06TP521 HDRIVE(L)                                      | 8-11 |

| 8-4    | A06U311-9 vertical oscillator; A06TP111                                              | 8-12 |

| 8-5    | A06U534-7 horizontal oscillator; A06TP521 HDRIVE(L)                                  | 8-12 |

| 8-6    | A06TP210 cathode Z-axis amplifier with Display Board A11J155 in TEST position;       | 0    |

|        | A06TP521 HDRIVE(L)                                                                   | 8-12 |