## M2331K/M2333K MICRO-DISK DRIVES

### **CE MANUAL**

| Edition     Date published     Revised contents       01     Jan., 1985 |     |                | REVISION RECORD                                                                                                                                                                        |  |

|-------------------------------------------------------------------------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                         | n l | Date published | Revised contents                                                                                                                                                                       |  |

|                                                                         |     | Jan., 1985     |                                                                                                                                                                                        |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                | 동물 위상 방법 가격 등 것을 통한 것을 가지 않는 것이다. 동안에 많은 것은 것<br>같은 것은 것 같은 것은 것은 것은 것을 것을 것을 것을 것을 것을 것이다. 것은 것은 것은 것을                                            |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                | 에는 사람이 있는 것이 있는 것이 있는 것이 있는 것이 가지 않는 것이 있다.<br>같이 있는 것이 있는 것이 동물을 것이 같이 있는 것이 있는 것이 같이 많이 많이 많이 있다.                                                                                    |  |

|                                                                         |     |                |                                                                                                                                                                                        |  |

|                                                                         |     |                | 사람은 가장 가장에 관한 것이 같은 것이 같이 가지 않는 것이 같이 있다. 것이 가지 않는 것이 있는 것이 같이 있다.<br>같이 같은 것이 같은 것이 같은 것이 같이 있는 것이 같이 많이 많이 많이 많이 많이 있다. 것이 같이 있는 것이 같이 있다. 것이 같이 있는 것이 같이 있는 것이 없다. 것이 있는 것이 없는 것이 있 |  |

| 승규는 방법 방법은 가장 감독을 다 가지 않는 것이 것을 알 것 같아요. 강성 것이 많을 것 같아.                 |     |                |                                                                                                                                                                                        |  |

| 승규는 동안에 가장에 가장 같은 것이 같이 가장 사람을 가 많다. 것 같아요. 것 같아요. 같아.                  |     |                |                                                                                                                                                                                        |  |

| Specification No.: B03P-4760-0111A                                      |     |                |                                                                                                                                                                                        |  |

The contents of this manual is subject to change without prior notice.

i

All Rights Reserved, Copyright © 1985 FUJITSU LIMITED

B03P-4760-0111A...01

and has not MCCS1K/MCCCH midro

Comments concerning this manual to one of the following addresses:

FUJITSU LIMITED International Marketing Marunouchi 1-6-1, Chiyoda-ku, Tokyo 100 JAPAN

TEL:

03-216-3211

FAX:

03-216-3211

TLX:

J22833

Cable:

"FUJITSULIMITED LIMITED"

-30 FUJITSU AMERICA INC. 3055 Orchard Drive, San Jose, California 95134-2017, U.S.A. 98

TEL:

408-988-8100

FAX:

408-945-1318

TLX:

230-176207

TWX:

910-338-2193

÷. FUJITSU EUROPE LIMITED 54 Jermyn Street, London SW1Y 6NQ, ENGLAND TEL: 1-408-0043 FAX: 1-629-9826 TLX: 263871 FT ERP G FUJITSU ELECTRONIK GmbH Sonnen Straße 29, D-8000 München 2, F.R. GERMANY TEL: 89-592891 ~ 4 FAX: 89-592895 TLX: 41-5213994 FUJITSU NORDIC AB Kungsgaton 44, 111 35 Stockholm, SWEDEN TEL: 8-231125 FAX: 8-106865 TLX: 54-13411 FUJITSU ITALIA S.p.A. Via Lazzaroni, 4, 20124 Milano, ITALIA TEL: 2-607-3601 FAX: 2-688-6637 TLX: 350142 FJITLY I FUJITSU AUSTRALIA LIMITED 41 McLaren Street, North Sydney, N.S.W. 2060, AUSTRALIA TEL: 2-922-1822 FAX: 2-922-2653 TLX: 71-25233

B03P-4760-0117A...01

. D.

مي<sup>ت</sup>

01

$\sim 11^{\circ}$

1.1.1.28

ii

### Preface

This manual explains how to operate, handle, and maintain the M2331K/M2333K microdisk drives.

The information is provided in 10 sections:

| SECTION 1<br>SECTION 2<br>SECTION 3<br>SECTION 4<br>SECTION 5<br>SECTION 6<br>SECTION 7<br>SECTION 8<br>SECTION 9<br>SECTION 9<br>SECTION 10 | GENERAL DESCRIPTION<br>OPERATION<br>INSTALLATION<br>THEORY OF OPERATION<br>TROUBLESHOOTING GUIDE<br>MAINTENANCE<br>SPARE PARTS LIST<br>IC DETAIL<br>PARTS LIST<br>SCHEMATICS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                              | 7 <b>94</b> -25<br>                                                                                                                                                          | Mini Construction<br>Inclusion<br>Inclusion<br>States<br>Landon 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                              | : #N2 +<br>:                                                                                                                                                                 | т.<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>годи<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>година<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>годи<br>19<br>соди<br>19<br>годи<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>соди<br>19<br>с<br>19<br>соди<br>19<br>с<br>10<br>со<br>10<br>со<br>10<br>со<br>10<br>со<br>10<br>со<br>10<br>с<br>со<br>с<br>со |

|                                                                                                                                              |                                                                                                                                                                              | Fujitsu Ltd.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                              | B03P-4760-9111A3601                                                                                                                                                          | <b>iii</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### **Table of Contents**

|       | GENERAL DESCRIPTION                 | Page |

|-------|-------------------------------------|------|

| 1.    | GENERAL DESCRIPTION                 | 1-1  |

| 1.1   | GENERAL DESCRIPTION                 | 1-1  |

| 1.1.1 | General Description                 |      |

| 1.1.2 | Features                            |      |

| 1.2   | SPECIFICATIONS                      |      |

| 1.2.1 | Unit Specifications                 |      |

| 1.2.2 | Physical Specifications             |      |

| 1.2.3 | Power Requirements                  |      |

| 1.2.4 | Data Recording Specifications       |      |

| 1.2.5 | Reliability                         |      |

| 1.2.6 | Data Integrity                      |      |

| 1.3   | CONFIGURATION                       |      |

| 1.3.1 | Fundamental Unit Configuration      |      |

| 1.3.2 | Options                             |      |

| 2.    | OPERATION                           | 2-1  |

| 2.1   | GENERAL DESCRIPTION                 |      |

| 2.2   | POWERING UP/DOWN                    |      |

| 2.3   | CONTROL AND INDICATORS              |      |

| 2.3.1 | Operator Panel (option)             |      |

| 2.3.2 | PCB Assembly                        |      |

| 2.4   | Dual Channel PCB Assembly (Option)  |      |

| 2.5   | POWER SUPPLY                        | 2-6  |

| 2.5.1 | Main Line Switch                    |      |

| 2.5.2 | Indicators (LEDs)                   | 2-6  |

| 2.5.3 | Device Alarm                        | 2-6  |

| 3.    | INSTALLATION                        | 2.1  |

| 3.1   | GENERAL DESCRIPTION                 | 3-1  |

| 3.2   | UNPACKING                           |      |

| 3.3   | VISUAL INSPECTION                   | 3-1  |

| 3.4   | INSTALLATION                        |      |

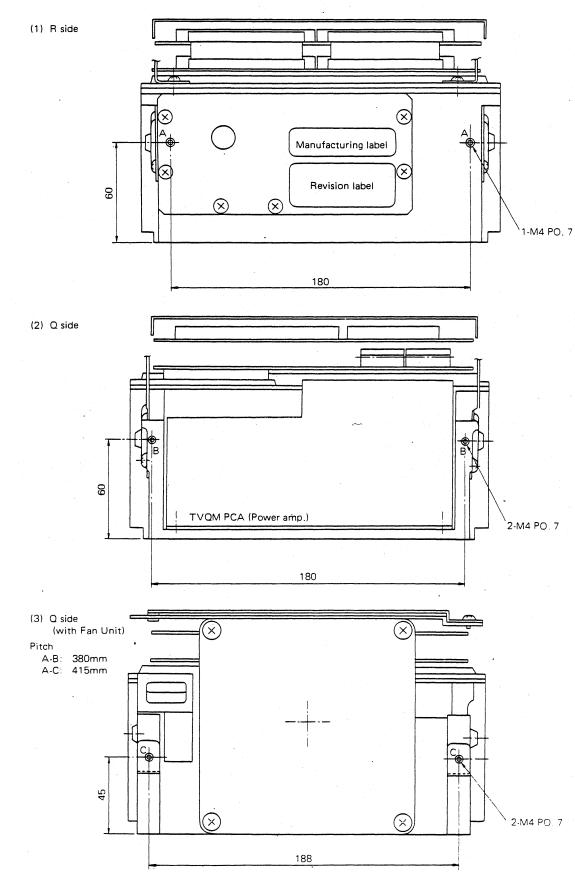

| 3.4.1 | Mounting Dimensions                 |      |

| 3.4.2 | Service Area                        |      |

| 3.4.3 | Securing the Unit                   |      |

| 3.4.4 | Cooling*                            |      |

| 3.5   | MOUNTING OF OPTIONS                 |      |

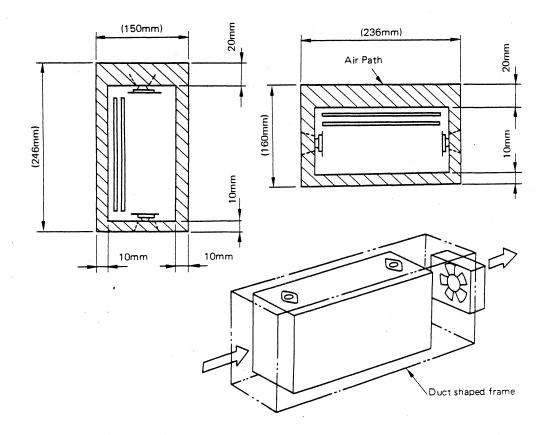

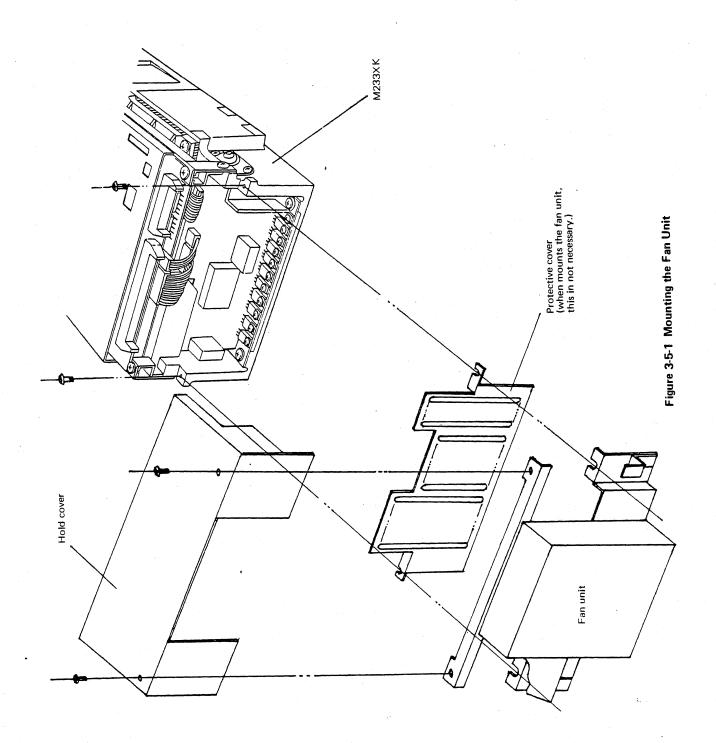

| 3.5.1 | Mounting the fan unit               | 3-12 |

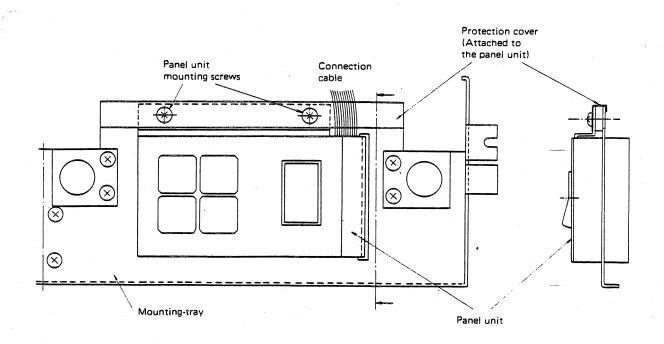

| 3.5.2 | Mounting the Panel Unit             |      |

| 3.5.3 | Installation Mounting Tray          | 3-15 |

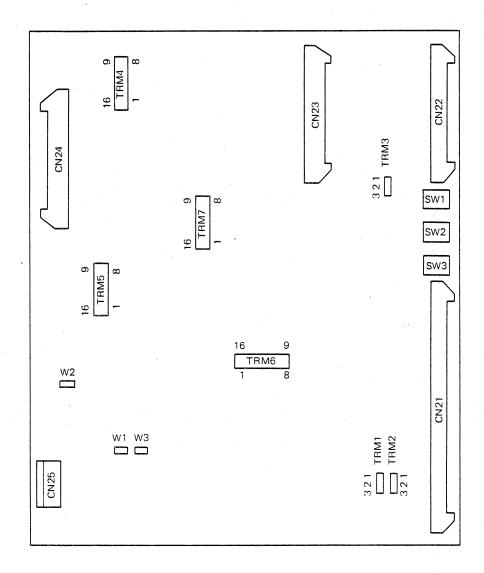

| 3.5.4 | Mounting the Dual Channel Option    |      |

| 3.6   | CABLING                             | 3-30 |

| 3.6.1 | Connectors On Unit Side             |      |

| 3.6.2 | Power Cable Connection              | 3-30 |

| 3.6.3 | Interface Cabling                   | 3-32 |

| 3.6.4 | System Grounding                    |      |

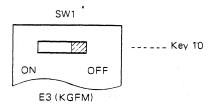

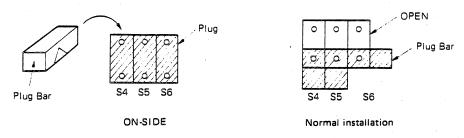

| 3.7   | MODE SELECT SETTING                 | 3-36 |

| 3.7.1 | Disk Addressing                     |      |

| 3.7.2 | Tag 4/5 Enable                      |      |

| 3.7.3 | File Protect                        |      |

| 3.7.4 | Device Type (optional)              |      |

| 3.7.5 | ON-Side Switch (for vertical mount) |      |

| 3.7.6 | Sector Counting                     | 3-40 |

Ì

B03P-4760-0111A...01

| 3.8<br>3.9 | SHIPPING<br>STORAGE AND REPACKING         | 3-42<br>3-42 |

|------------|-------------------------------------------|--------------|

| 4.<br>4.1  |                                           | 4-1<br>4-1   |

| 4.2        | MECHANICAL ASSEMBLIES                     | 4-1          |

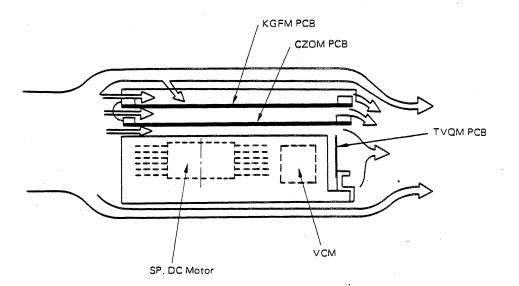

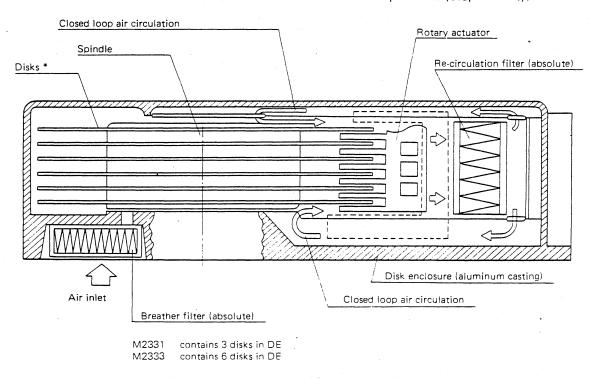

| 4.2.1      | Disk Enclosure                            | 4-1          |

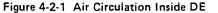

| 4.2.2      | Air Circulation in DE                     | 4-1          |

| 4.2.3      | Spindle Drive Motor                       |              |

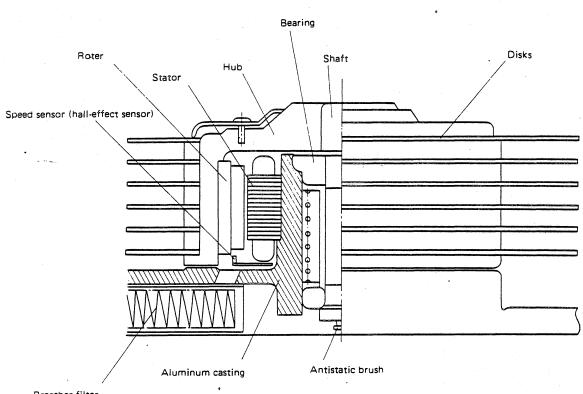

|            | Actuator Arm Assembly                     | 4-2          |

| 4.3        | MAGNETIC HEADS AND RECORDING MEDIA        |              |

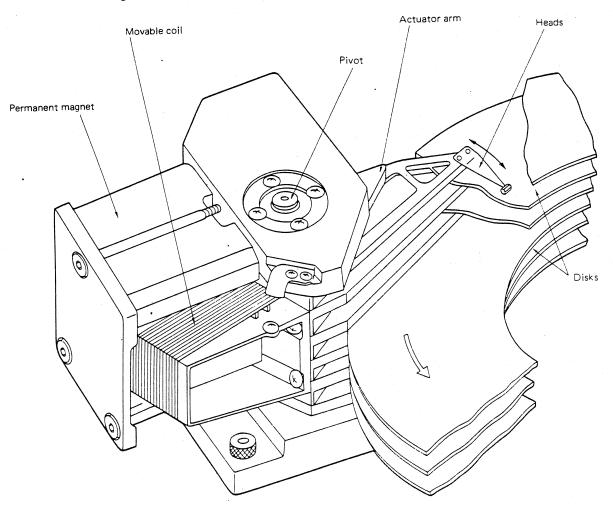

| 4.3.1 S    | Magnetic Heads                            | 4-4<br>1 E   |

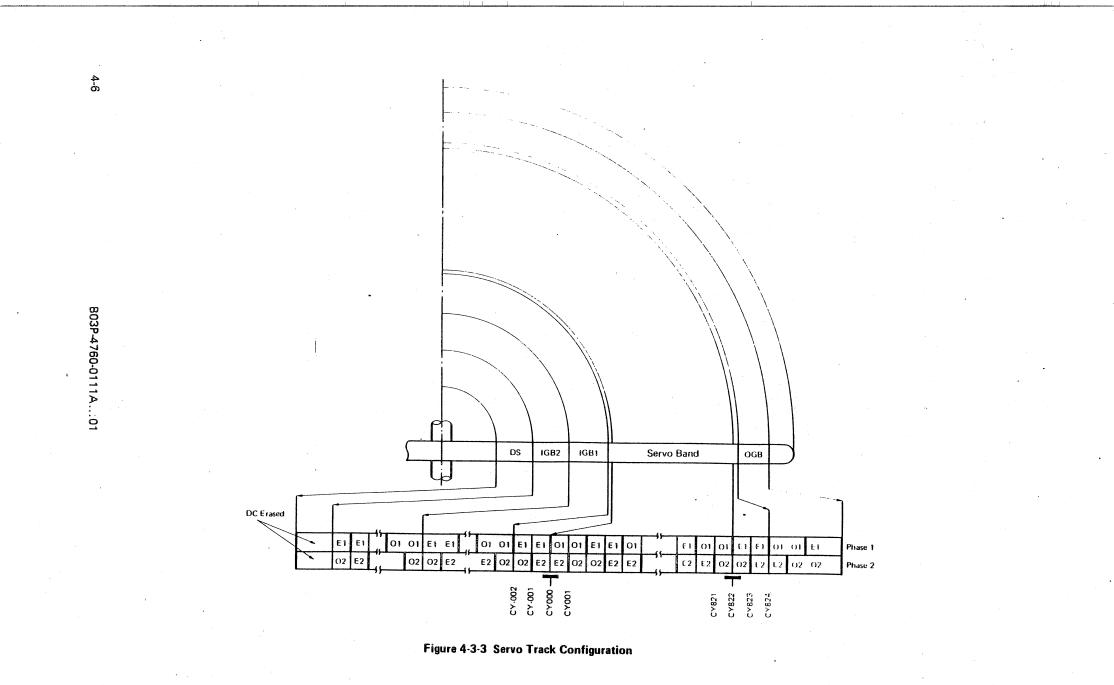

| 4.3.2      | Servo Track Format                        | 4-5          |

| 4.3.4      | Data Surface Format                       | 4-12         |

| 4.3.5      | Head and Surface Configuration            |              |

| 4.4        | FORMAT                                    |              |

| 4.4.1      | Description                               |              |

| 4.4.2      | Fixed Sector Format                       |              |

| 4.4.3      | Description of Format Parameters          |              |

| 4.5        | INTERFACE                                 |              |

| 4.5.1      | Introduction                              |              |

| 4.5.2      | Interface Cabling                         |              |

| 4.5.3      | Type and Name of Signal Lines             |              |

| 4.5.4      | Description of Signal Lines               | 4-19         |

| 4.5.5      | Timing                                    | 4-26         |

| 4.5.6      | Read/Write Timing                         |              |

| 4.5.7      | Interface Transmission                    |              |

| 4.5.8      | Connectors and Cables                     |              |

| 4.5.9      | Connector Pin Assignment                  |              |

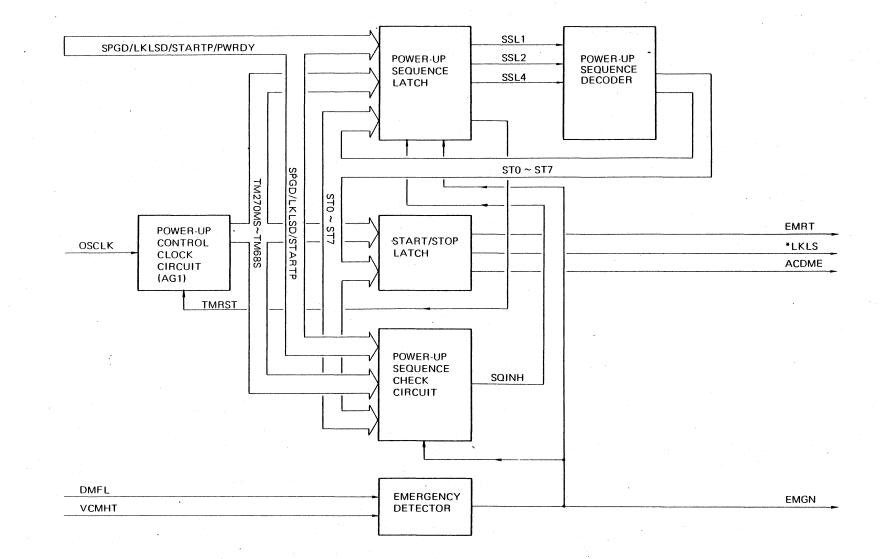

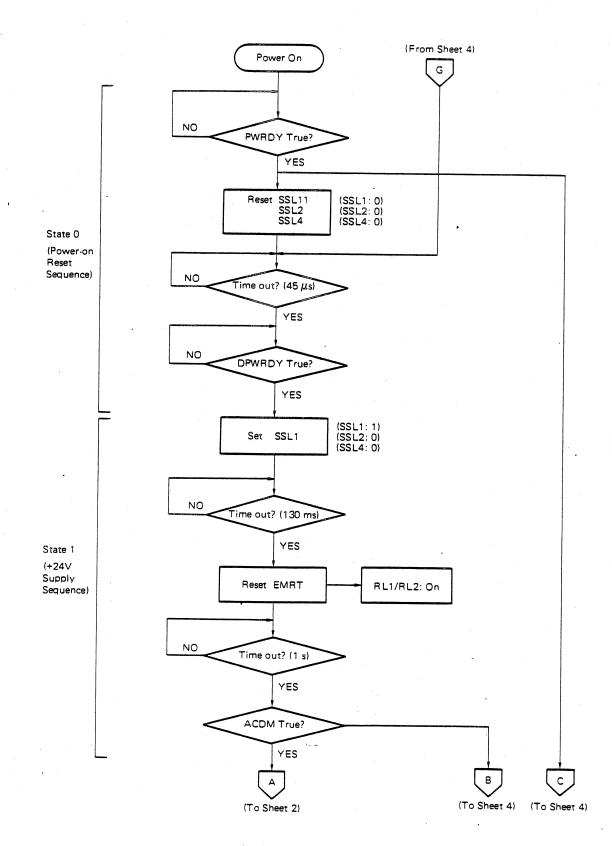

| 4.6        | ELECTRICAL CIRCUIT FUNCTION               |              |

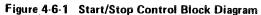

| 4.6.1      | Start/Stop Control                        |              |

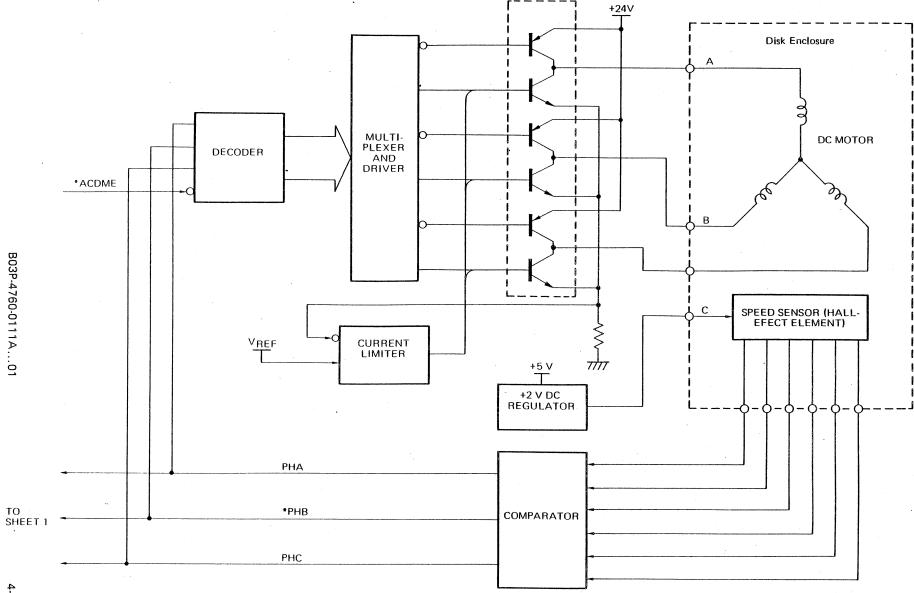

| 4.6.2      | DC Motor Control                          |              |

| 4.6.3      | Unit Selection                            |              |

| 4.6.5      | Servo Circuit Function                    |              |

| 4.6.6      | Index/Sector/Guard Band Generate Function | 4-00         |

| 4.6.7      | Head Selection                            |              |

| 4.6.8      | Read/Write Function                       |              |

| 4.6.9      | VFO                                       |              |

| 5.         | TROUBLESHOOTING GUIDE                     |              |

| 5.1        | INTRODUCTION                              |              |

| 5.2        | ERROR STATUS                              |              |

| 5.3        | FAULT ISOLATION LIST                      | 5.2          |

| 5.4        | TROUBLESHOOTING SYMBOL                    | 5-6          |

| 5.5        | TROUBLESHOOTING FLOW CHART                |              |

| 6.         | MAINTENANCE                               |              |

| 6.1        | INTRODUCTION                              |              |

| 6.2        | GENERAL PRECAUTIONS                       |              |

| 6.2.1      | Power On/Off                              |              |

| 6.2.2      | Parts Replacement                         |              |

| 6.2.3      | Dual Channel Switches                     |              |

| 6.2.4      | Other                                     | 6-1          |

| 6.3        | MAINTENANCE TOOLS AND EQUIPMENT           | 6-1          |

| 6.4        | PREVENTIVE MAINTENANCE                    | 6-1          |

| 6.5        | PCB ASSEMBLY REPLACEMENT                  | 6-1          |

}

B03P-4760-0111A ... 01

vi

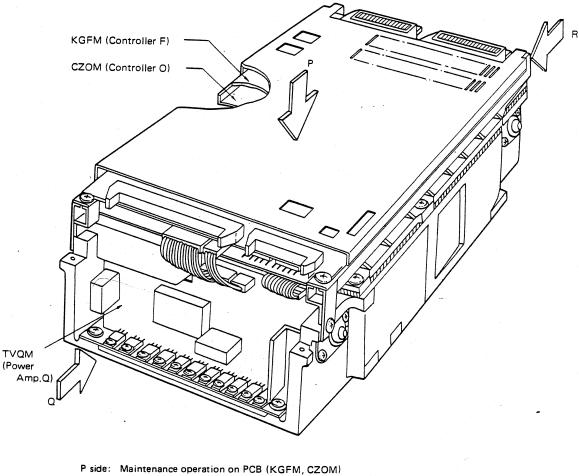

| 6.5.1 | PCB Assembly Arrangement                                  | . 6-1                                   |

|-------|-----------------------------------------------------------|-----------------------------------------|

| 6.5.2 | KGFM PCB Assembly Replacement Procedure                   | . 6-2                                   |

| 6.5.3 | CZOM PCB Assy, Replacement Procedure                      | 6-3                                     |

| 6.5.4 | TVQM PCB Assembly Replacement                             | 6-5                                     |

| 6.6   | PCB CHECK AND ADJUSTMENT                                  | . 6-6                                   |

| 6.6.1 | PCB CHECK AND ADJUSTMENT<br>Test Point Arrangement on PCB | . 6-6                                   |

| 6.6.2 | PCB Adjustment after PCB Replacement                      | . 6-20                                  |

| 6.6.3 | Electrical Measurement                                    | . 6-21                                  |

| 7.    | SPARE PARTS LIST                                          | 71                                      |

| 7.1   |                                                           | ·/-2.33                                 |

|       | SPARE PARTS LIST                                          | /•1                                     |

| 8.    | IC DETAILS                                                | 8-1                                     |

| 8.1   | INTRODUCTION                                              | . 8-1                                   |

| 8.2   | LOGIC CONVENTIONS AND SYMBOLOGY                           |                                         |

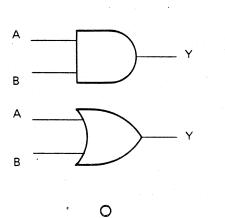

| 8.2.1 | TTL Logic                                                 | . 8-1                                   |

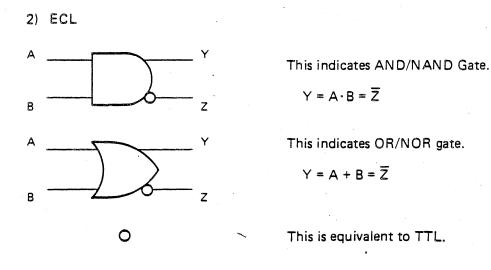

| 8.2.2 | ECL Logic                                                 | . 8-2                                   |

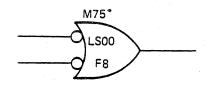

| 8.2.3 | Logic Symbology                                           | . 8-3                                   |

| 8.3   | INTERCHANGEABILITY GUIDE                                  |                                         |

| 8.3.1 | TTL IC Interchangeability                                 |                                         |

| 8.3.2 | ECL IC Interchangeability                                 | 8-6                                     |

| 8.3.3 | Linear IC Interchangeability                              | 8-6                                     |

| 8.3.4 | FUJITSU Proprietary IC                                    | . 8-6                                   |

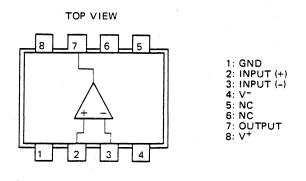

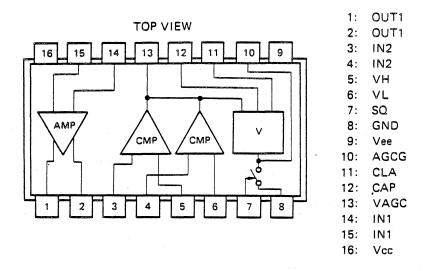

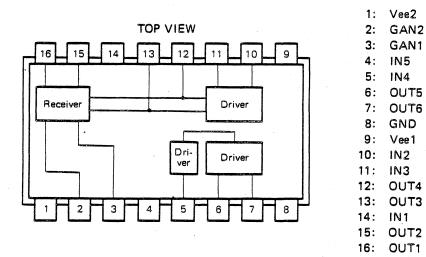

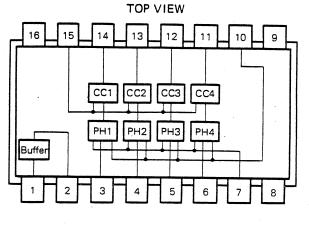

| 8.4   | FUJITSU PROPRIETARY IC DETAIL                             | 8-7                                     |

| 9.    | PARTS LIST                                                | 9-1                                     |

|       |                                                           | T t d A                                 |

|       |                                                           | 2 1 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 2 3 |

|       |                                                           |                                         |

|       | 이 것은                  | 10 B                                    |

|       |                                                           |                                         |

|       |                                                           |                                         |

)

• • •

• • •

t.

3. j.

## Illustrations

| FIGURE           |                                               | Page |

|------------------|-----------------------------------------------|------|

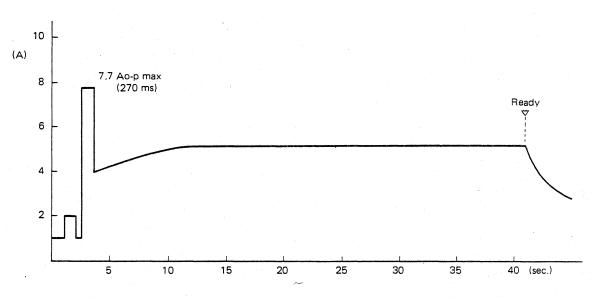

| 1-2-1            | +24V DC Load Current on Power Up Sequence     | 1-3  |

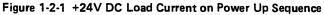

| 1-2-2            | Total +24V DC Load Current (Ready)            | 1-4  |

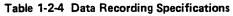

| 1-2-3            | Positioning Time Profile                      | 1-5  |

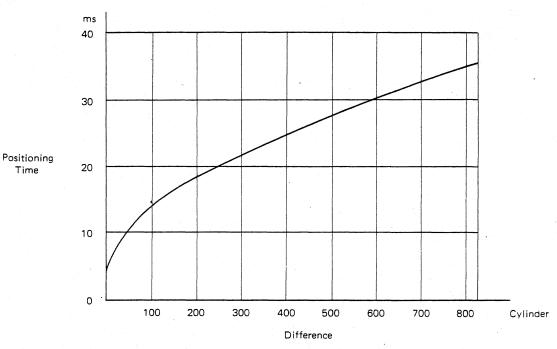

| 1-2-4            | Media Defect Format 1                         | 1-8  |

| 1-2-5            | Skip Displaced Format                         | 1-9  |

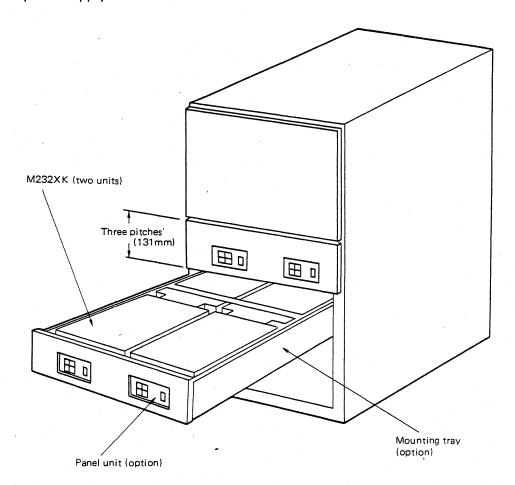

| 1-3-1            | Fundamental Configuration                     | 1-10 |

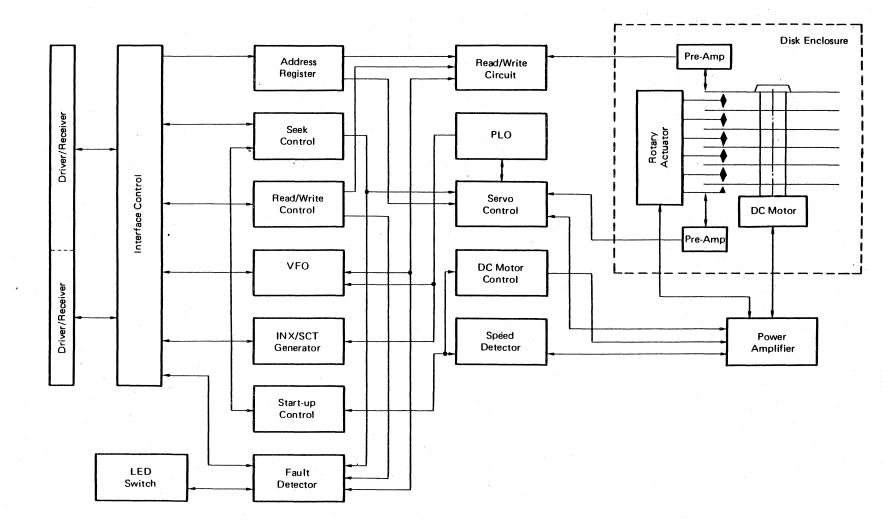

| 1-3-2            | Block Diagram                                 |      |

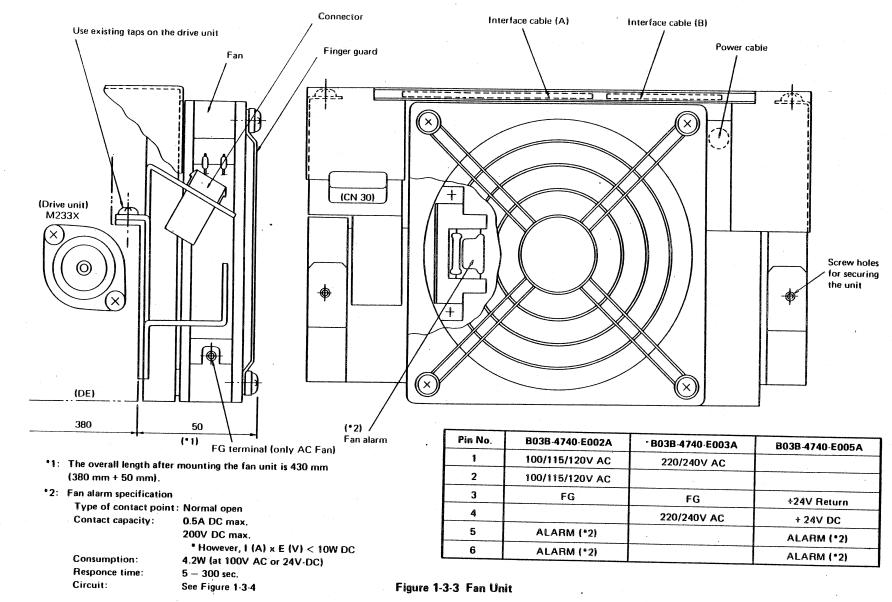

| 1-3-3            | Fan Unit                                      | 1-14 |

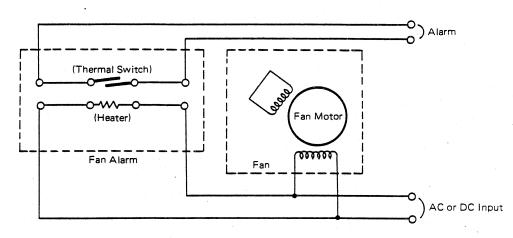

| 1-3-4            | Optional Fan Unit Alarm                       | 1-15 |

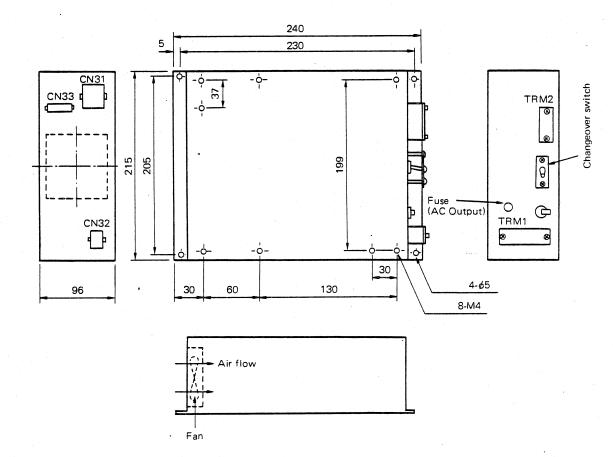

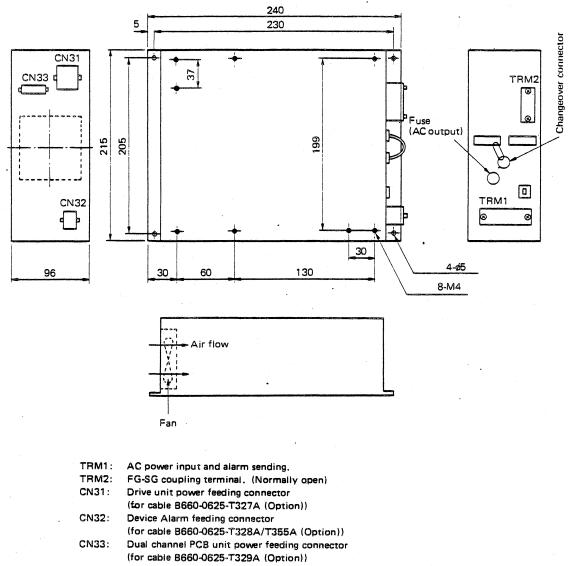

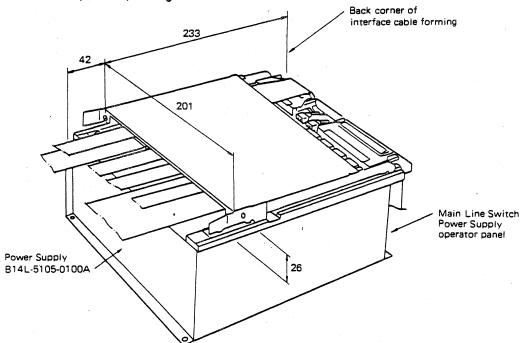

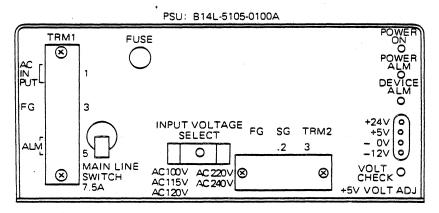

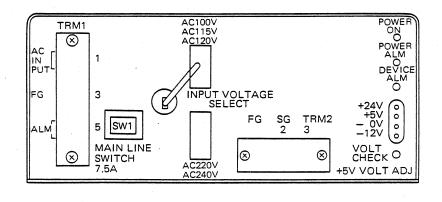

| 1-3-5 (a)        | Power Supply Unit: B14L-5105-0100A            | 1-15 |

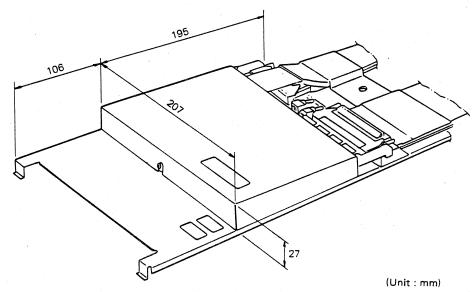

| 1-3-5 (b)        | Power Supply Unit: B14L-5105-0154A#A1         |      |

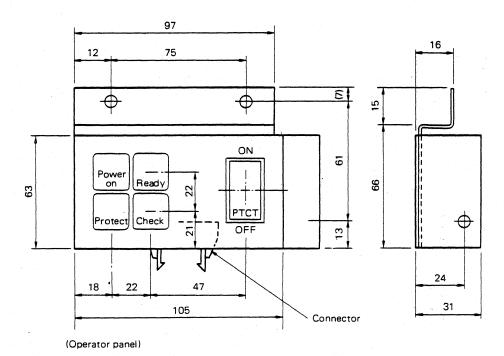

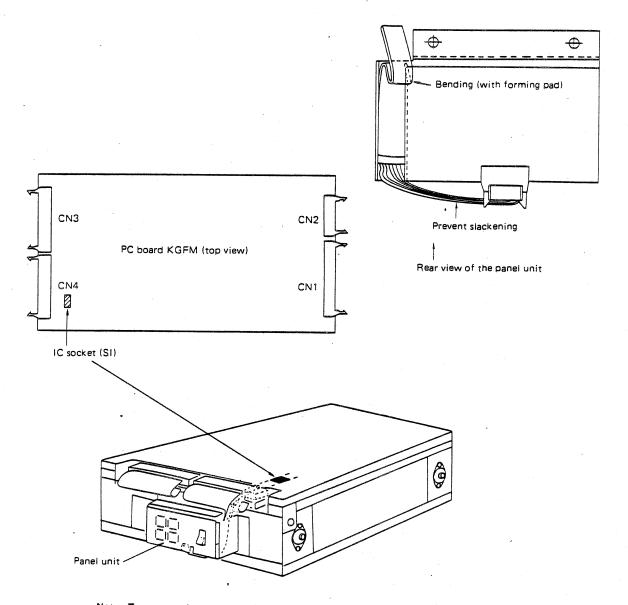

| 1-3-6            | Panel Unit                                    | 1-17 |

| 1-3-7            | Mounting Dimensions of Panel Unit             | 1-18 |

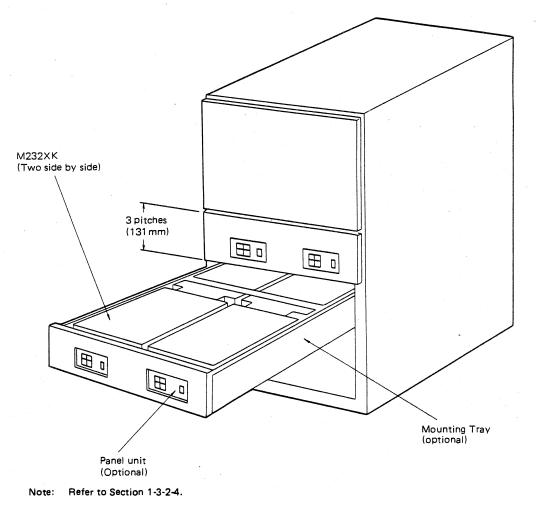

| 1-3-8            | 19" Rack Mount Installation                   | 1-19 |

| 1-3-9            | Mounting-Tray and Brackets                    | 1-20 |

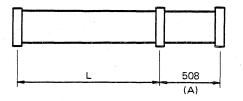

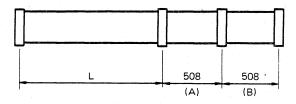

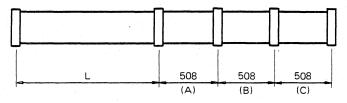

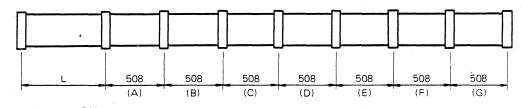

| 1-3-10           | A-Cables for Daisy-Chain                      | 1-21 |

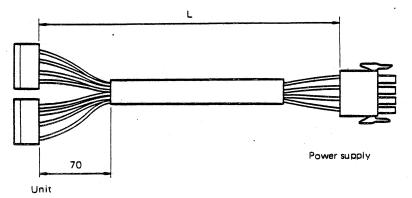

| 1-3-11           | Power Cable B660-0625-T327A                   | 1-22 |

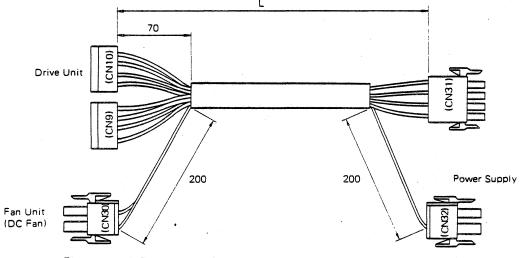

| 1-3-12           | Power Cable B660-1995-T041A                   | 1-22 |

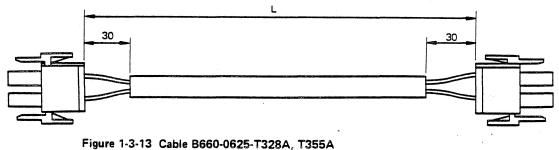

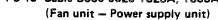

| 1-3-13           | Cable B660-0625-T328A, T355A                  |      |

|                  | (Fan unit – Power supply unit)                | 1-22 |

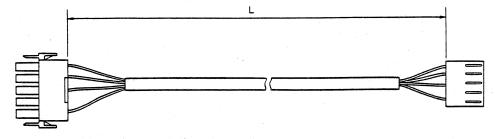

| 1-3-14           | Cable B660-0625-T329A                         |      |

|                  | (Dual Channel PCB assy. – Power supply unit)  | 1-23 |

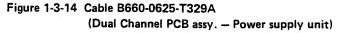

| 1-3-15           | Cable B660-1995-T003A                         |      |

|                  | (E501A Panel unit – Drive unit connecting)    | 1-23 |

| 1-3-16           | Dual Channel Option (E401A)                   | 1-24 |

| 1-3-17<br>1-3-18 | Dual Channel Option (E402A)                   | 1-25 |

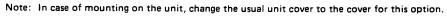

|                  | Dual Channel PCB Assembly Connector Location  |      |

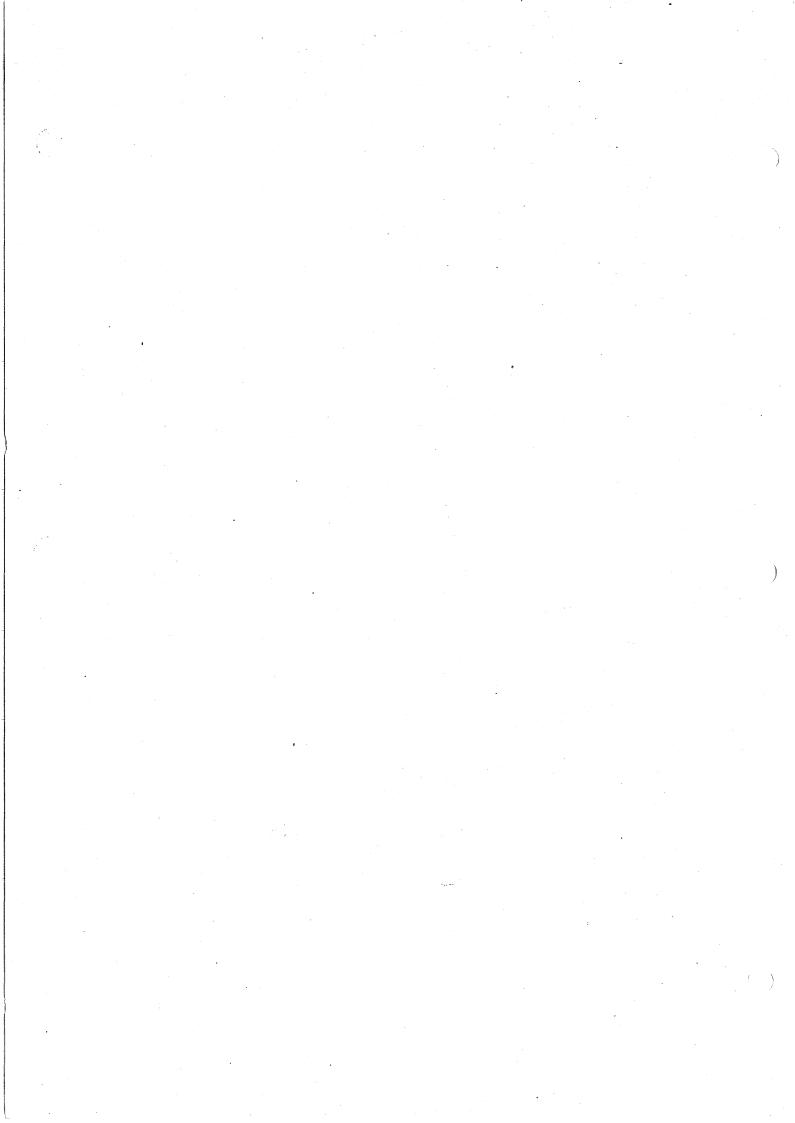

| 2-3-1            | Operator Panel (Optional)                     | 2-1  |

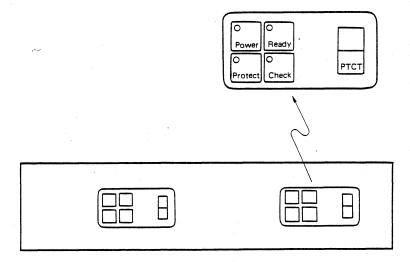

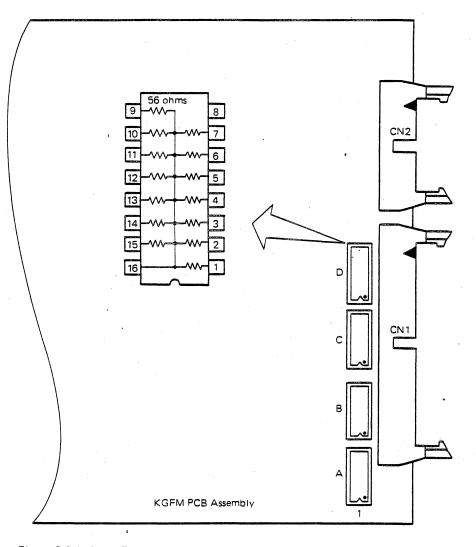

| 2-3-2            | Fault Display Location on KGFM PCB            | 2-2  |

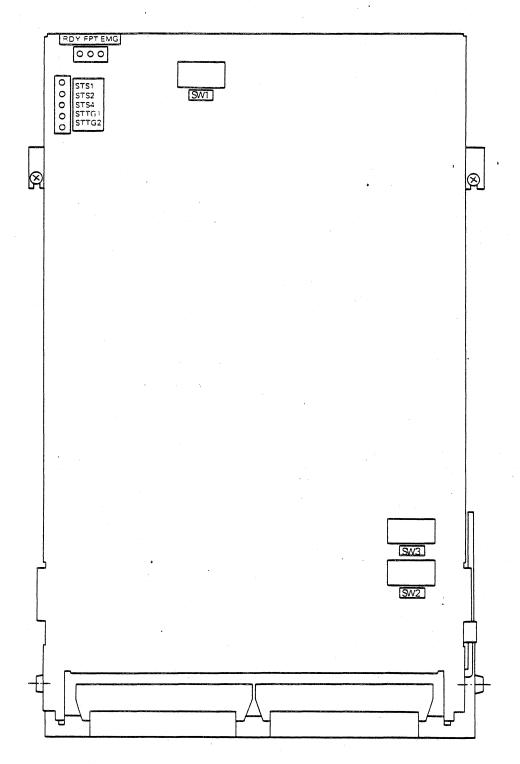

| 2-4-1            | Dual Channel PCB Assembly                     | 2-5  |

| 2-5-1            | Front View of Power Supply                    | 2-6  |

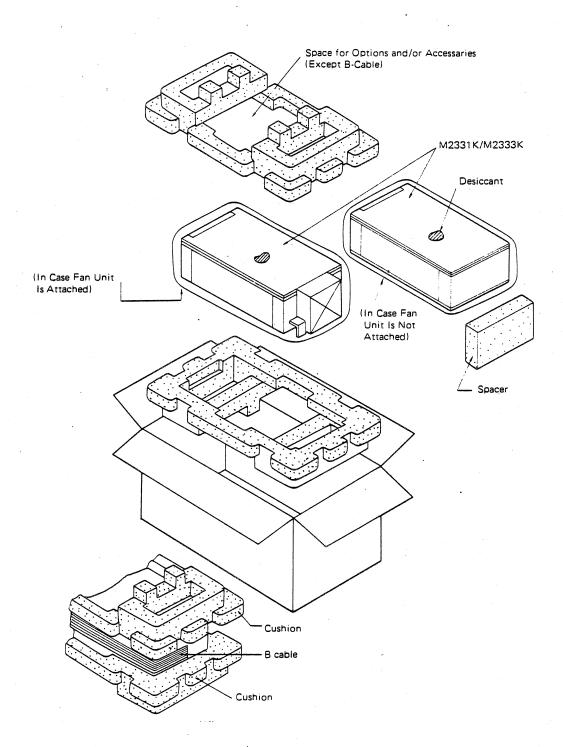

| 3-2-1            | External View of Carton                       | 3-2  |

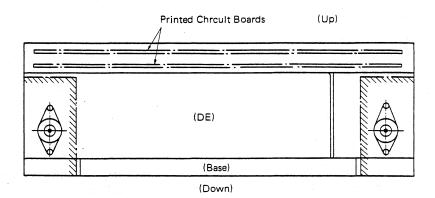

| 3-4-1            | Mounting direction                            | 3-3  |

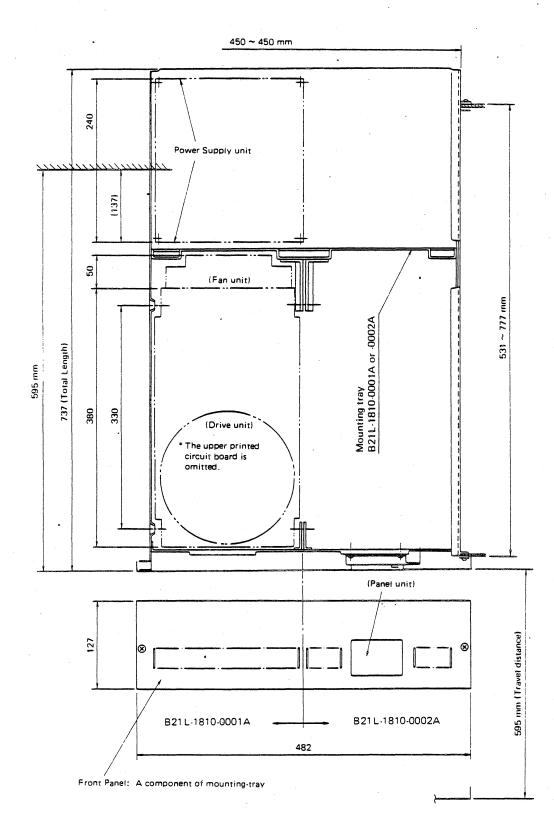

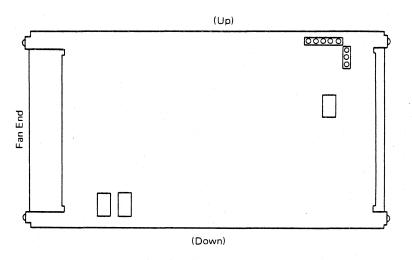

| 3-4-2            | Mounting Dimensions of the Unit               | 3-4  |

| 3-4-3            | Maintenance Access on the Unit                | 3-5  |

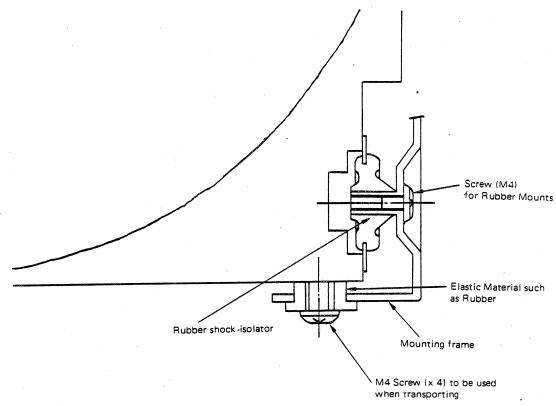

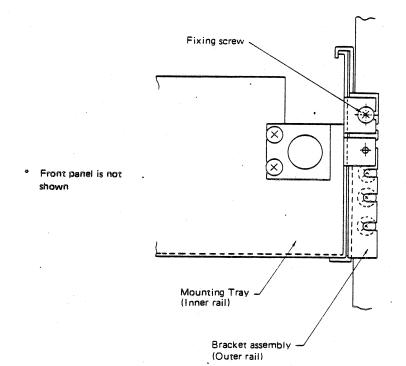

| 3-4-4            | Securing the Unit (Example 1)                 | 3-6  |

| 3-4-5            | Securing the Unit (Example 2)                 | 3-7  |

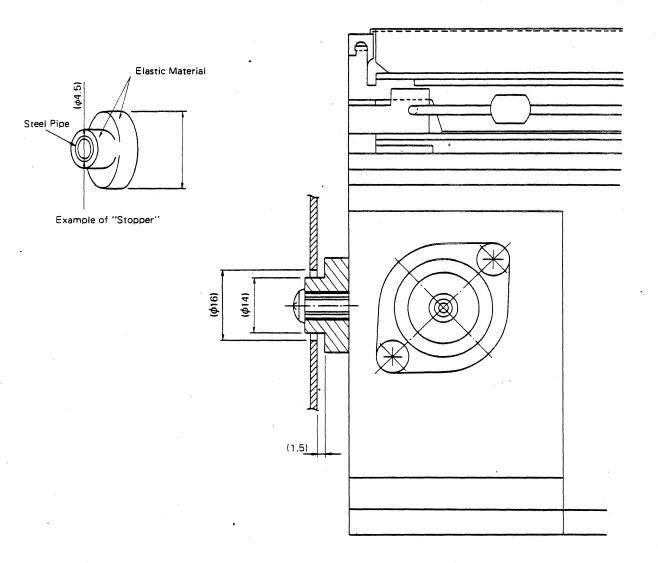

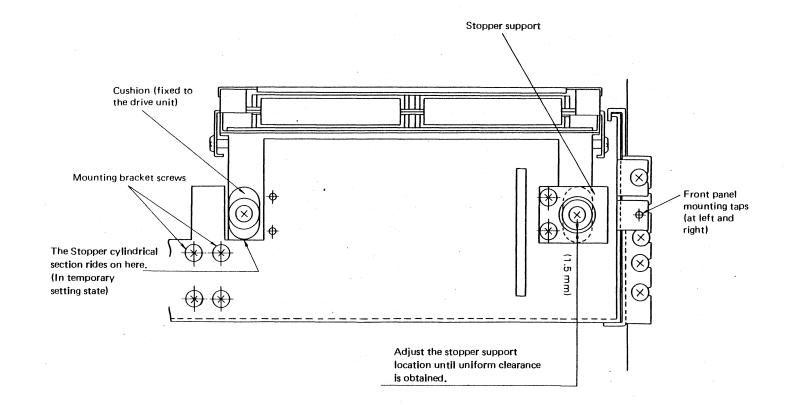

| 3-4-6            | Form of the Stopper                           | 3-8  |

| 3-4-7            | Dimensions of the Screw Holes                 | 3-9  |

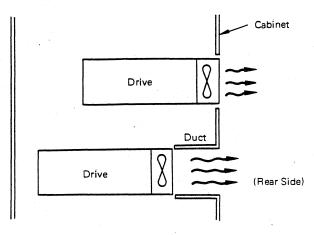

| 3-4-8            | Recommended Air Flow Posture                  | 3-10 |

| 3-4-9            | Examples of Installation Cooling              | 3-11 |

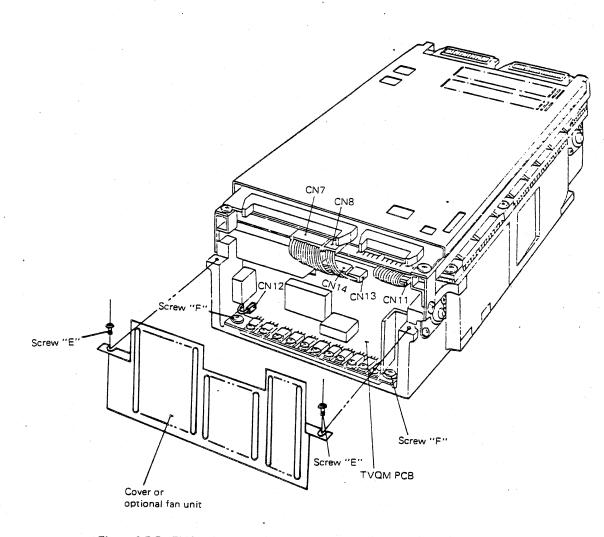

| 3-5-1            | Mounting the Fan Unit                         | 3-13 |

| 3-5-2            | Mounting the Panel Unit                       | 3-14 |

| 3-5-3<br>3-5-4   | Installation in the 19-inch Rack              |      |

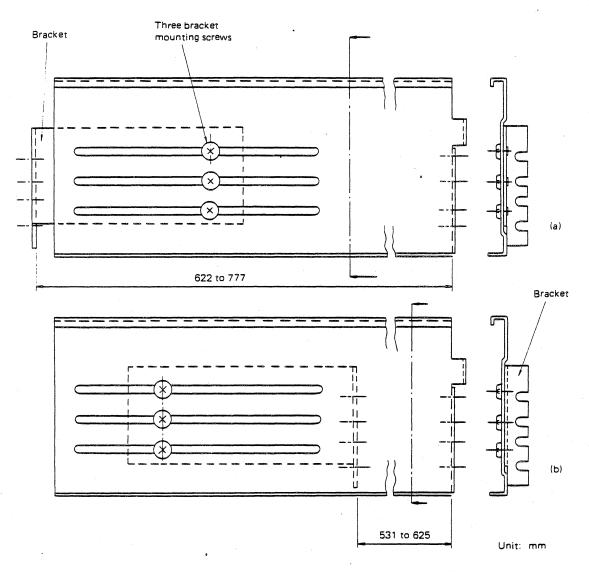

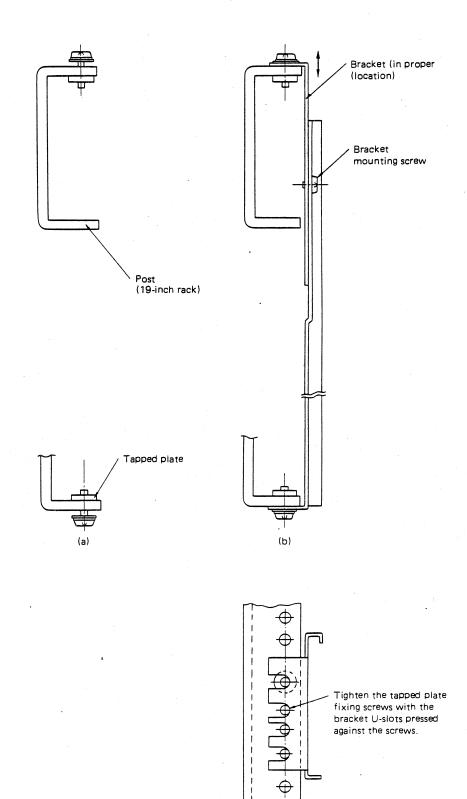

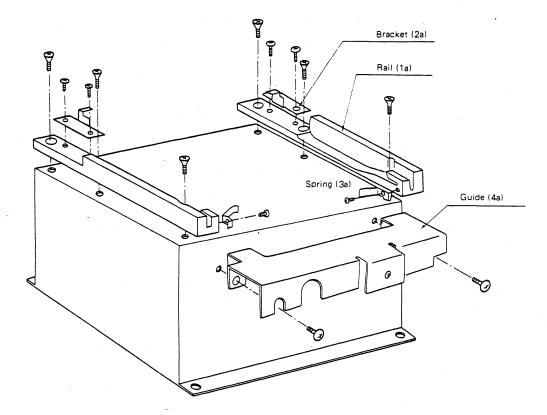

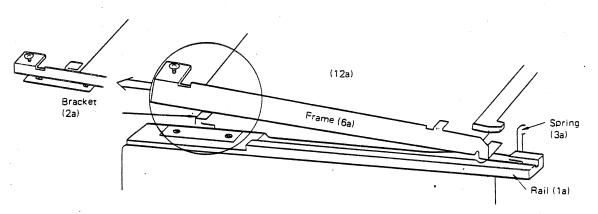

| 3-5-4<br>3-5-5   | Bracket Assembly                              | 3-16 |

| 3-5-5<br>3-5-6   | Bracket Assembly Mounting on the 19-inch Rack | 5-1/ |

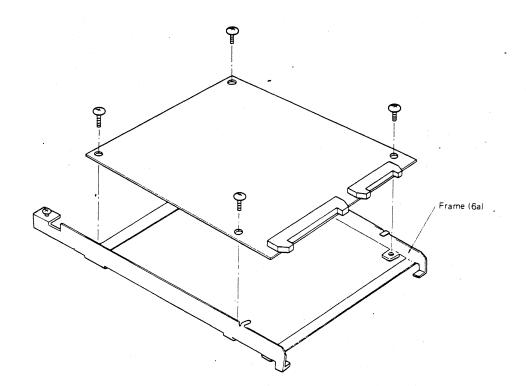

| 3-5-6<br>3-5-7   | Mounting Tray to the Outer Rails              | 3-18 |

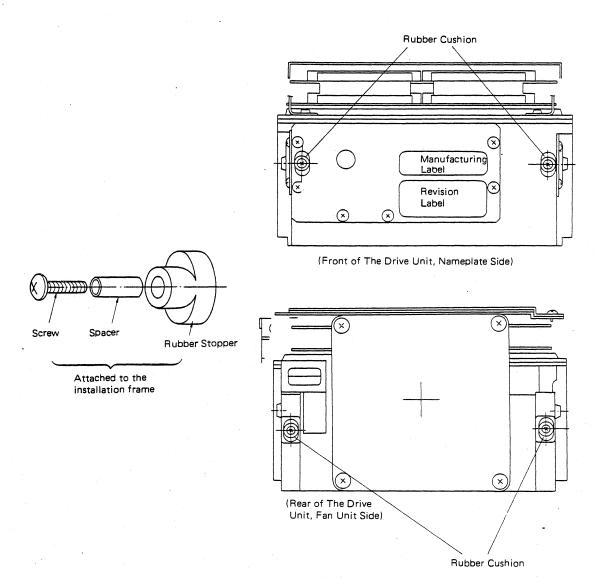

| 3-5-7            | Rubber Cushion Mounting                       |      |

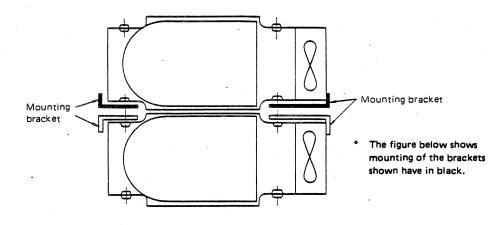

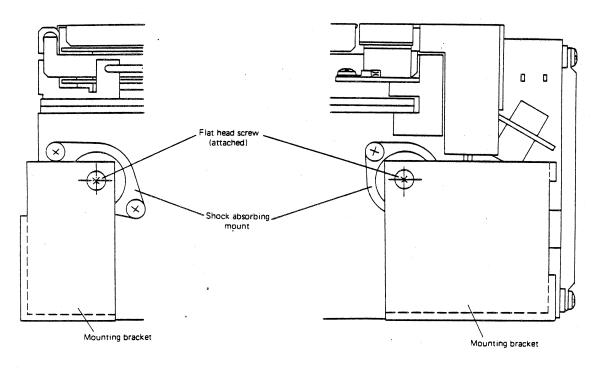

| 3-5-8            | Bracket Mounting                              |      |

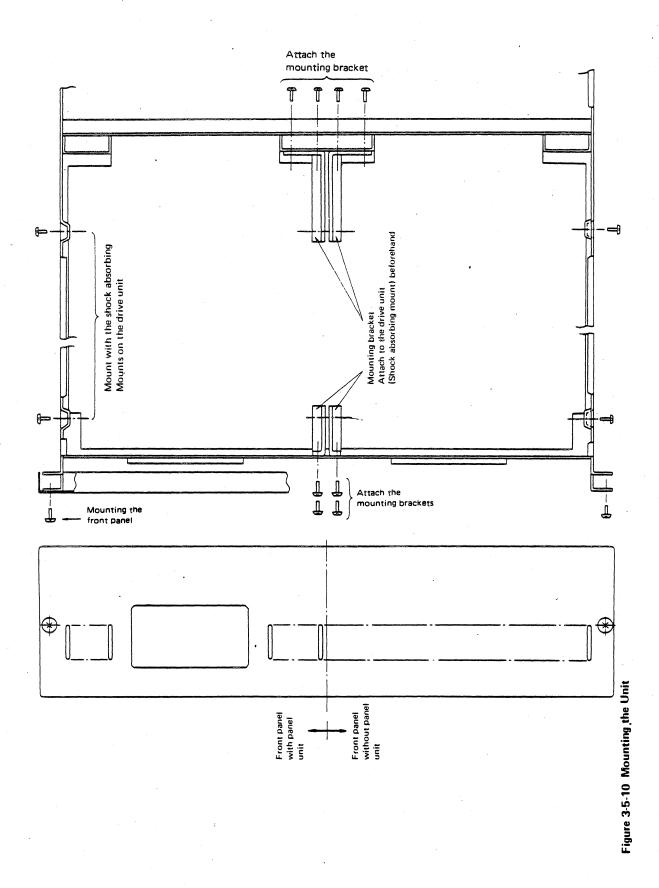

| 3-5-10           | Mounting the Unit                             |      |

|                  |                                               | コームム |

)

ix

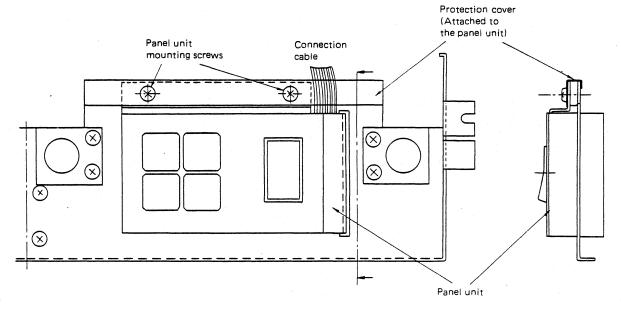

| 3-5-11 | Mounting the Panel Unit                      | 22  |

|--------|----------------------------------------------|-----|

|        |                                              |     |

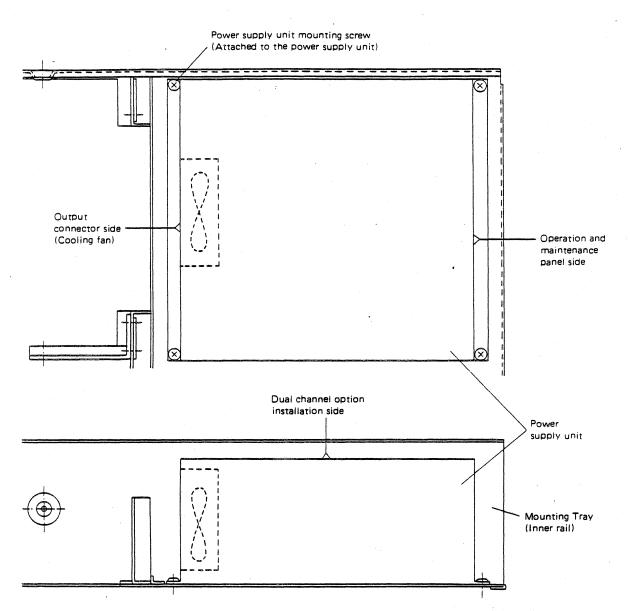

| 3-5-12 | Power Supply Unit Installation               |     |

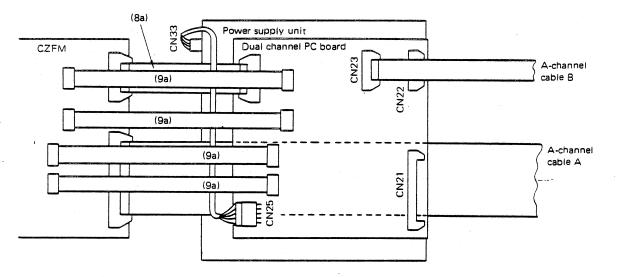

| 3-5-13 | Dual Channel Option Installation 1           | 25  |

| 3-5-14 | Dual Channel Option Installation 2           |     |

| 3-5-15 | Dual Channel Frame Mount                     |     |

|        |                                              |     |

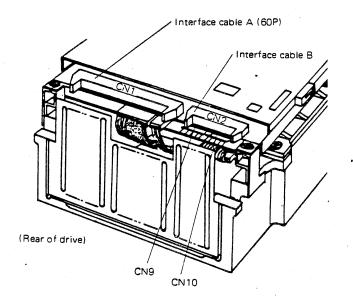

| 3-5-16 | Dual Channel Cabling                         |     |

| 3-5-17 | Dual Channel Top Cover Fixing                |     |

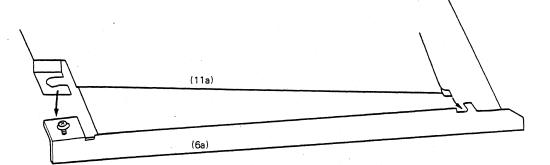

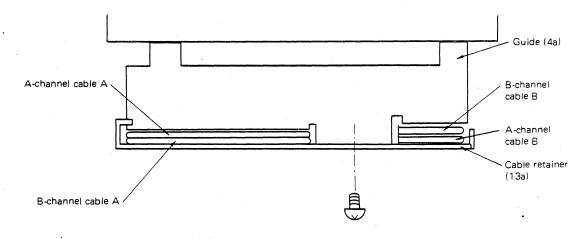

| 3-5-18 | Dual Channel Interface Cables Holding        | 27  |

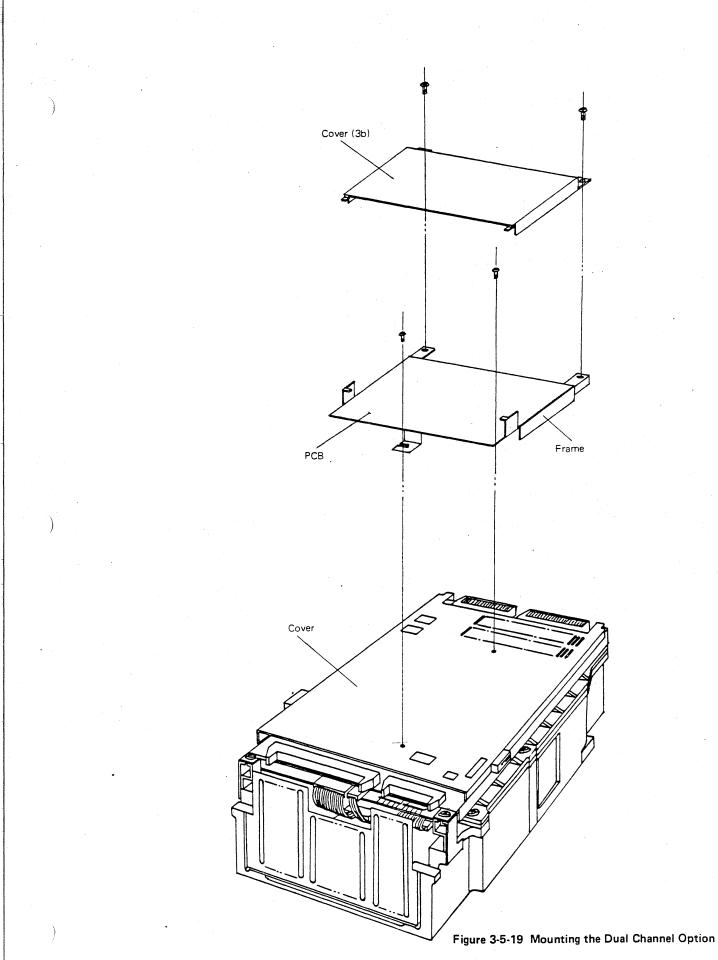

| 3-5-19 | Mounting the Dual Channel Option             | 29  |

| 3-6-1  | Mounting Positions of Connectors             |     |

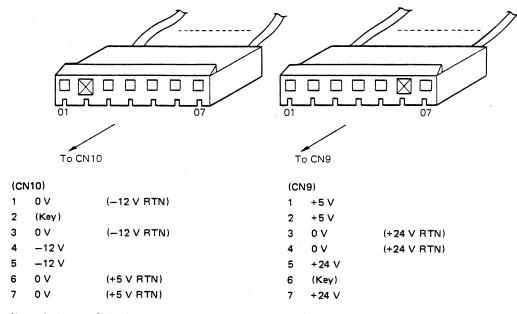

| 3-6-2  | Pin Assignment and Voltages                  |     |

|        |                                              |     |

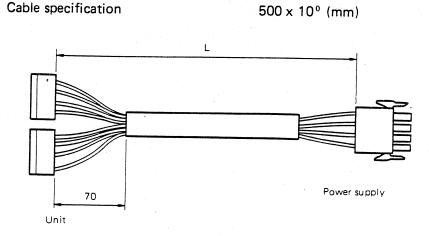

| 3-6-3  | Power Cable (Specification: B660-0625-T327A) |     |

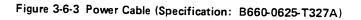

| 3-6-4  | System Interface Cabling                     |     |

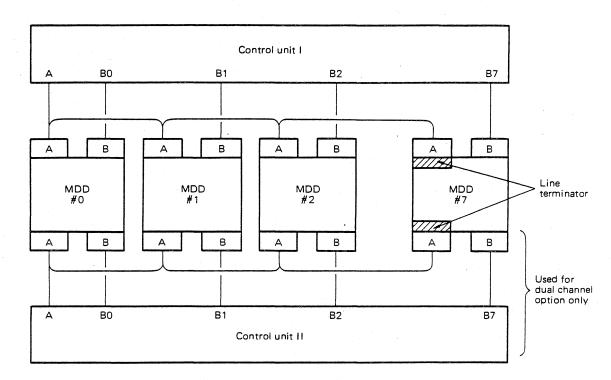

| 3-6-5  | Interface Cabling                            | 33  |

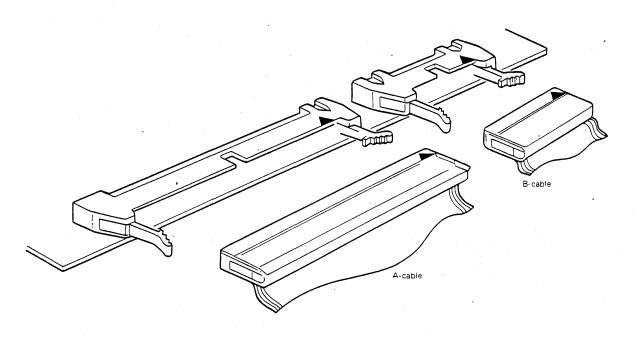

| 3-6-6  | Cable Termination                            | 34  |

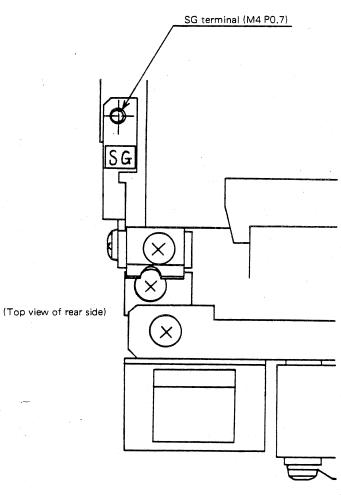

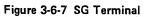

| 3-6-7  | SG Terminal                                  |     |

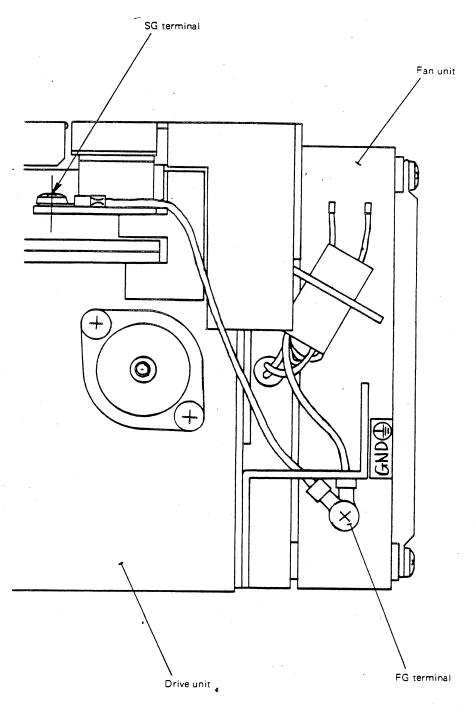

|        | FG/SG Connection                             |     |

| 3-6-8  |                                              |     |

| 3-7-1  | Mode Select Switch Location                  |     |

| 3-7-2  | Disk Addressing                              | 37  |

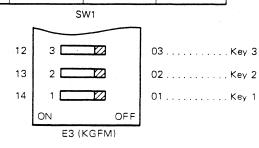

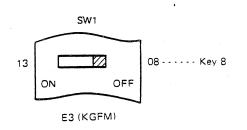

| 3-7-3  | Tag 4/5 Enable                               | 38  |

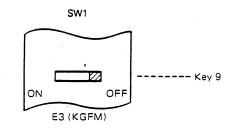

| 3.7.4  | File Protect                                 |     |

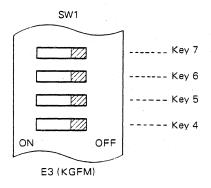

| 3-7-5  | Device Type                                  |     |

|        |                                              |     |

| 3-7-6  | On-Side                                      |     |

| 4-2-1  | Air Circulation Inside DE                    | 1   |

| 4-2-2  | Spindle Drive Motor                          |     |

| 4-2-3  | Actuator Arm Assembly                        |     |

|        |                                              |     |

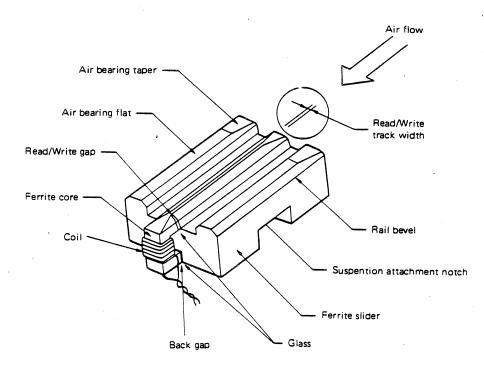

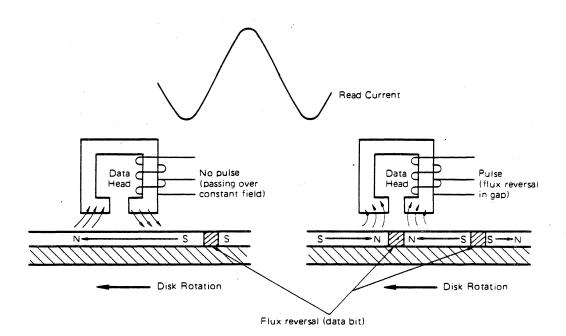

| 4-3-1  | Read/Write Head                              |     |

| 4-3-2  | Tapered Flat Slider                          |     |

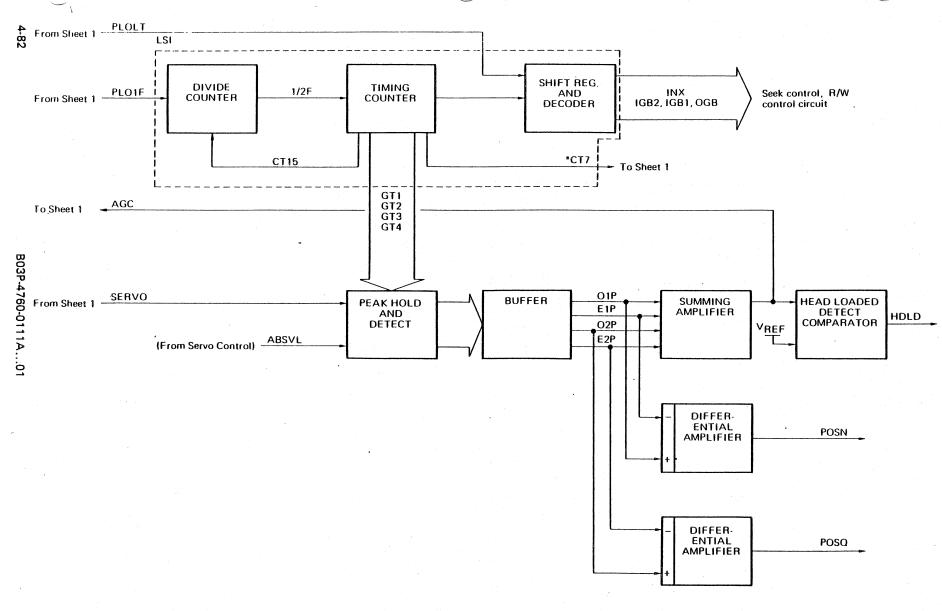

| 4-3-3  | Servo Track Configuration                    | 6   |

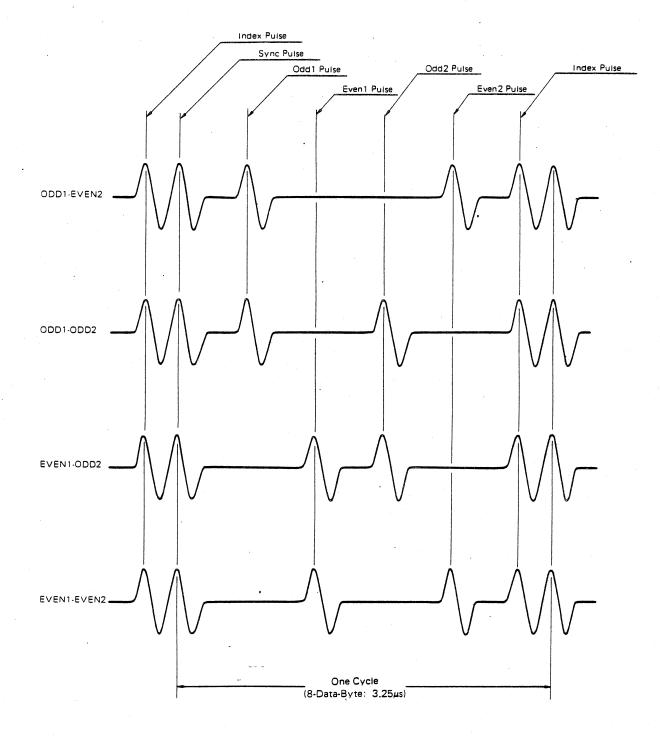

| 4-3-4  | Normal Bit Pattern                           | 8   |

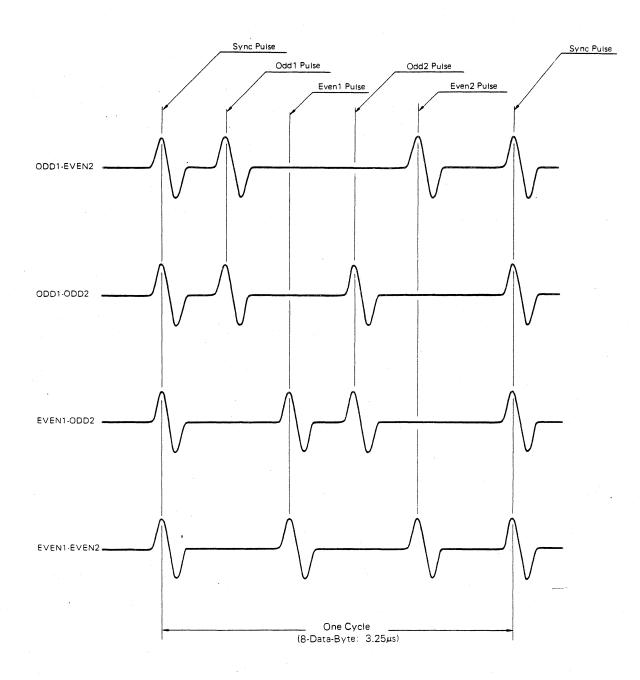

| 4-3-5  | Index Bit Pattern                            |     |

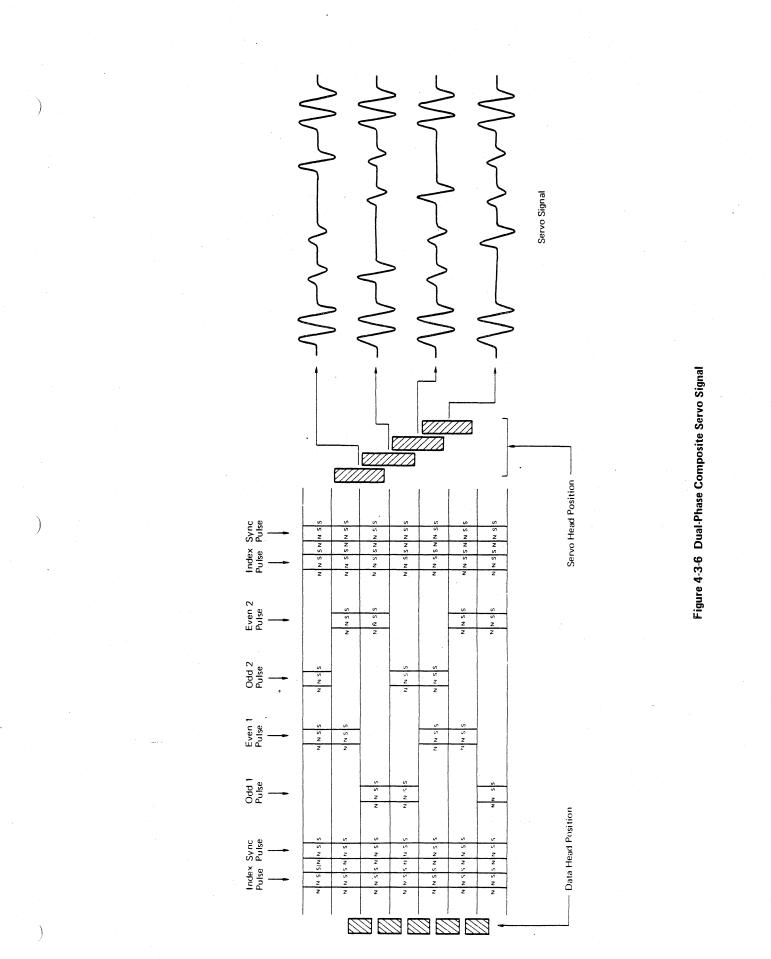

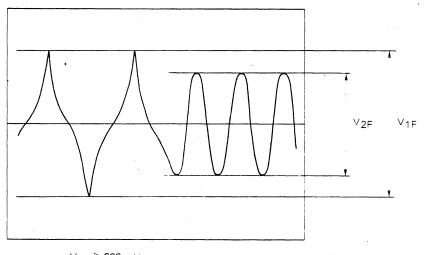

| 4-3-6  | Dual-Phase Composite Servo Signal            |     |

|        |                                              |     |

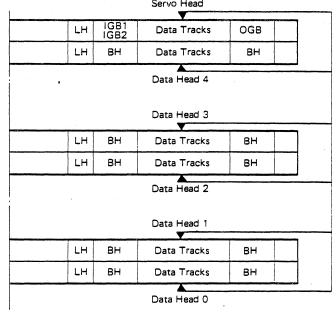

| 4-3-7  | M2331 Surface Configuration                  |     |

| 4-3-8  | M2333 Surface Configuration                  |     |

| 4-4-1  | Fixed Sector Format                          | 14  |

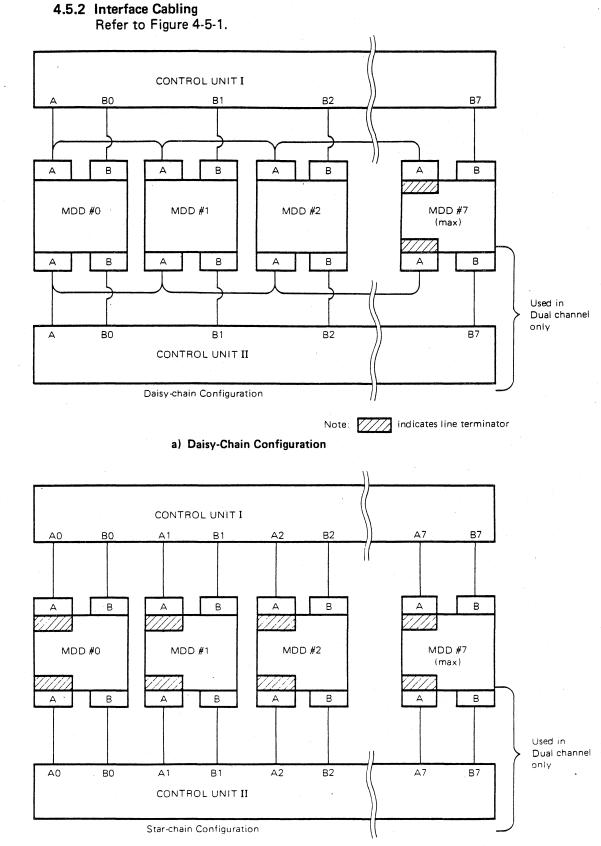

| 4-5-1  | Interface Cabling                            | 17  |

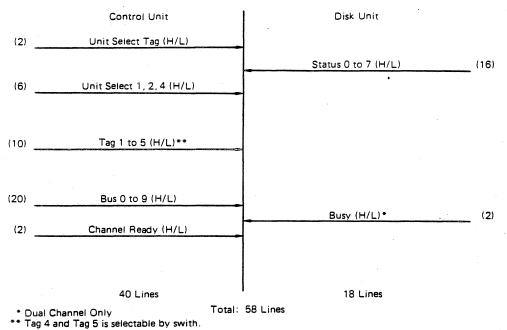

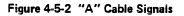

| 4-5-2  | "A" Cable Signals                            |     |

| 4-5-3  |                                              |     |

|        | "B" Cable Signals                            | 18  |

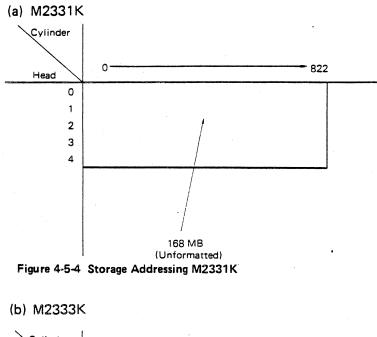

| 4-5-4  | Storage Addressing M2331K 4-                 |     |

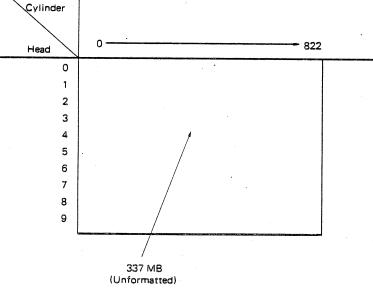

| 4-5-5  | Storage Addressing M2333K 4-:                | 20  |

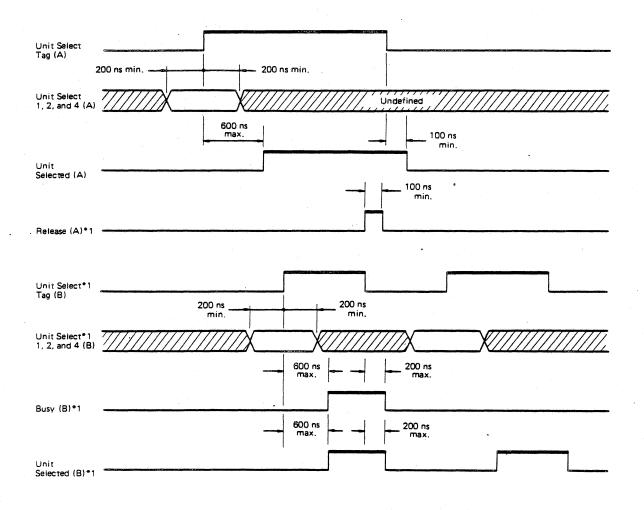

| 4-5-6  | Unit Select Timing                           | 26  |

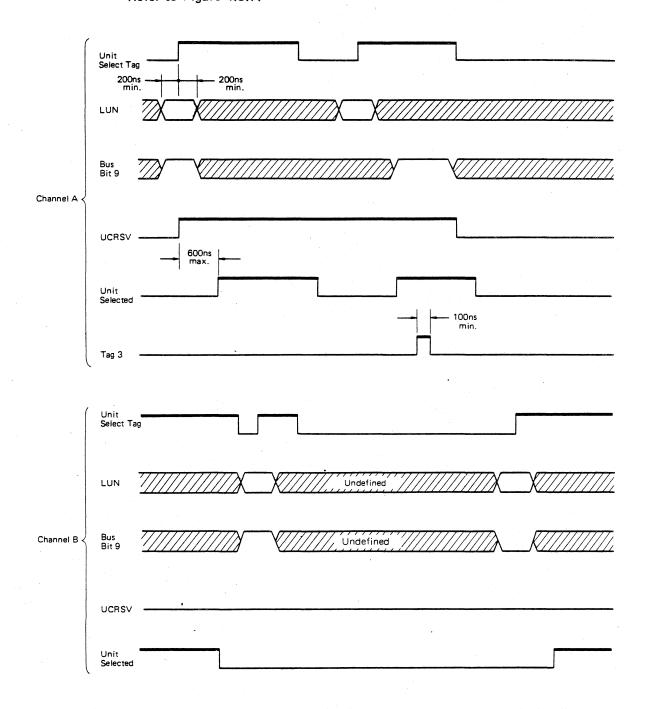

| 4-5-7  | Priority Select Timing                       |     |

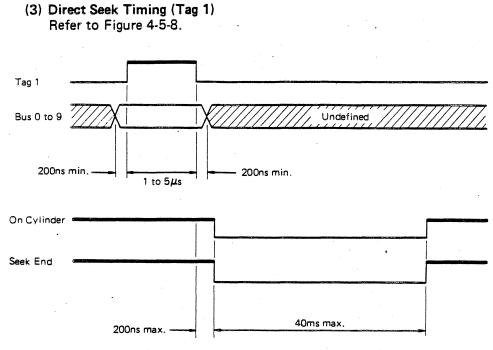

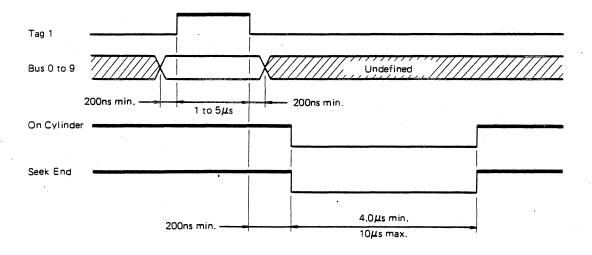

| 4-5-8  | Direct Seek Timing                           |     |

| 4-5-9  |                                              |     |

|        | Same Cylinder Address                        |     |

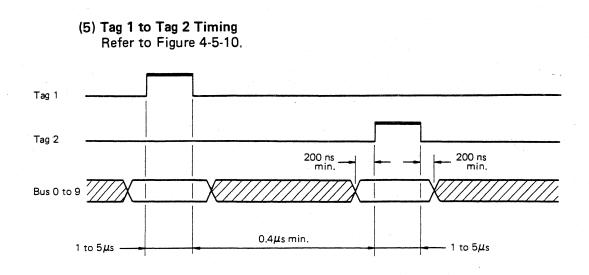

| 4-5-10 | Tag 1 to Tag 2 Timing         4-3            |     |

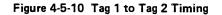

| 4-5-11 | Offset Plus/Minus Timing 4-                  |     |

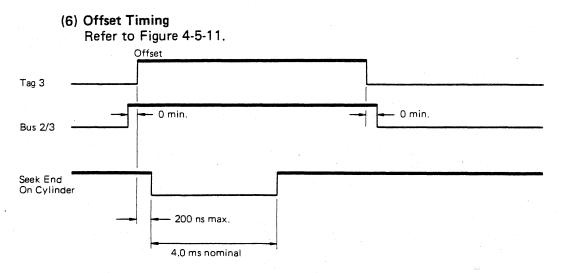

| 4-5-12 | Fault Clear Timing                           | 30  |

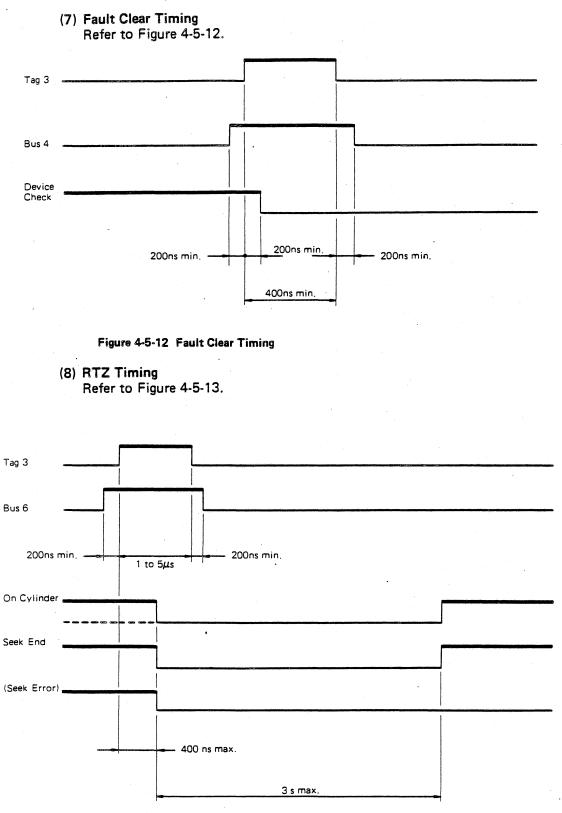

| 4-5-13 | RTZ Timing                                   |     |

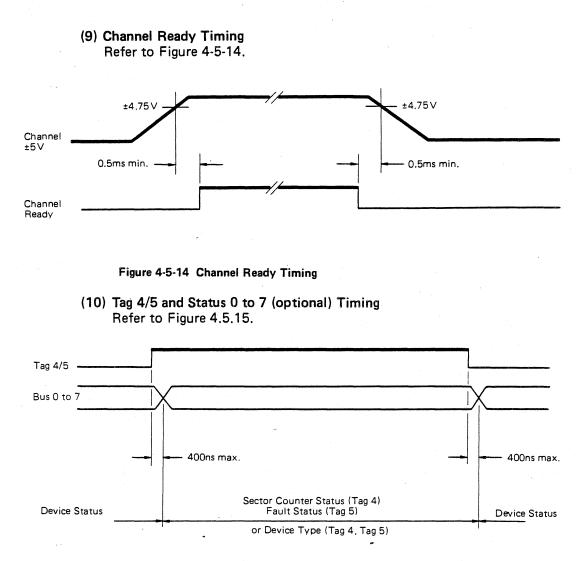

| 4-5-14 | Channel Ready Timing                         |     |

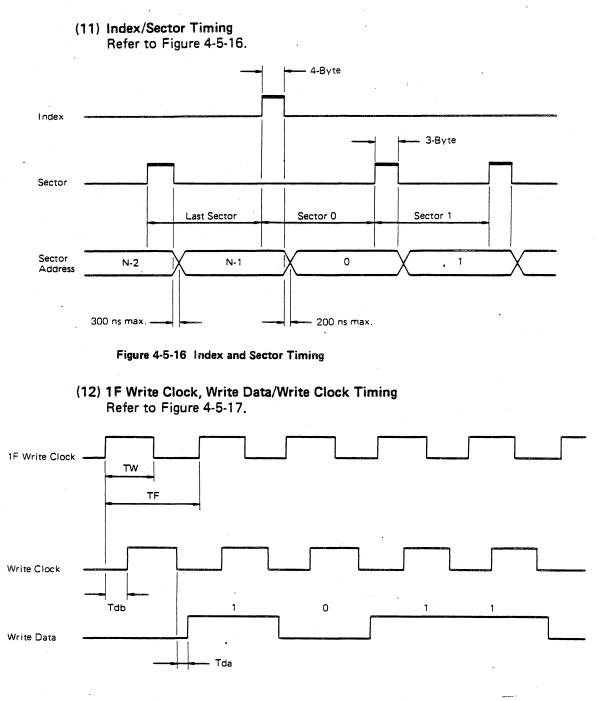

| 4-5-15 | Tag 4/5 Timing                               |     |

|        |                                              |     |

| 4-5-16 | Index and Sector Timing                      |     |

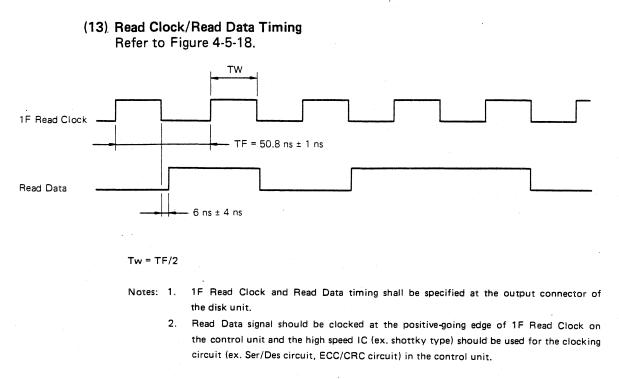

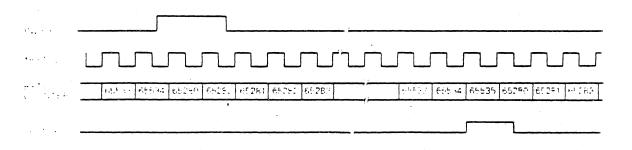

| 4-5-17 | Write Data and Write Clock Timing 4-         |     |

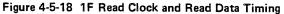

| 4-5-18 | 1F Read Clock and Read Data Timing4-         |     |

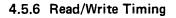

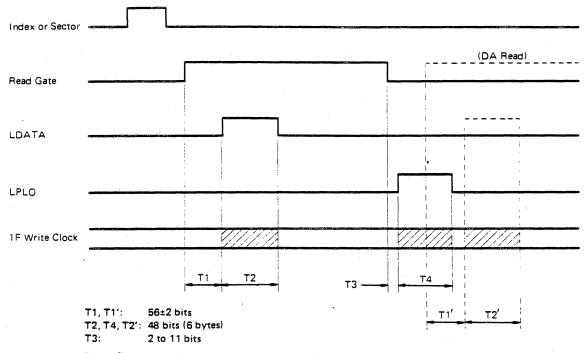

| 4-5-19 | Format Write Timing                          | 33  |

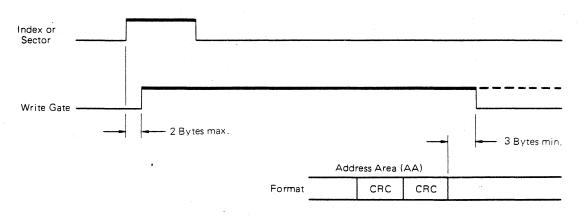

| 4-5-20 | Write DataTiming                             |     |

| 4-5-21 | Read DataTiming                              |     |

|        |                                              | UT. |

B03P-4760-0111A...01

x

|                 | 이 같은 것은                                                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------|

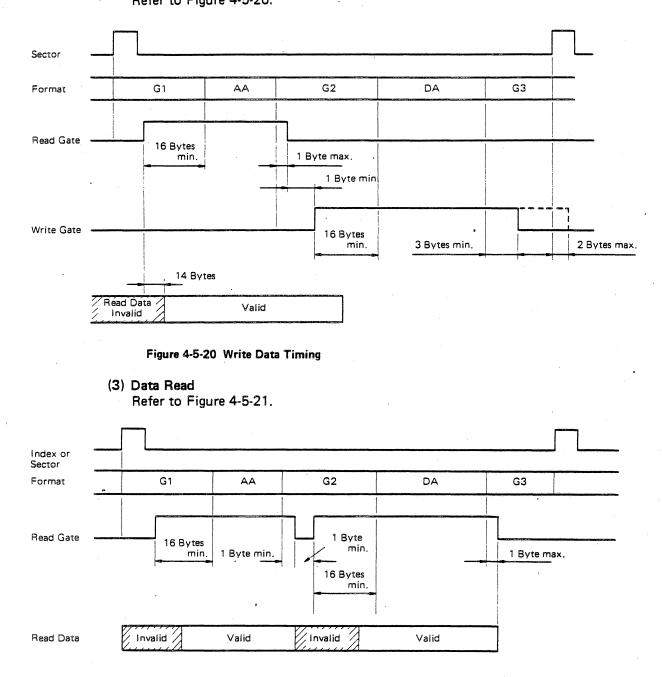

| 4-5-22          | Write-To-Read Recovery Time                                                                                       |

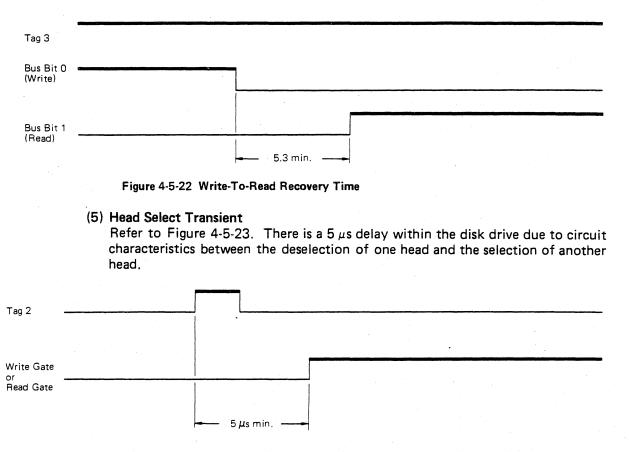

| 4-5-23          | Head Select Transient                                                                                             |

| 4-5-24          | 1F Write Clock in Reading 4-36                                                                                    |

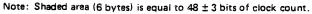

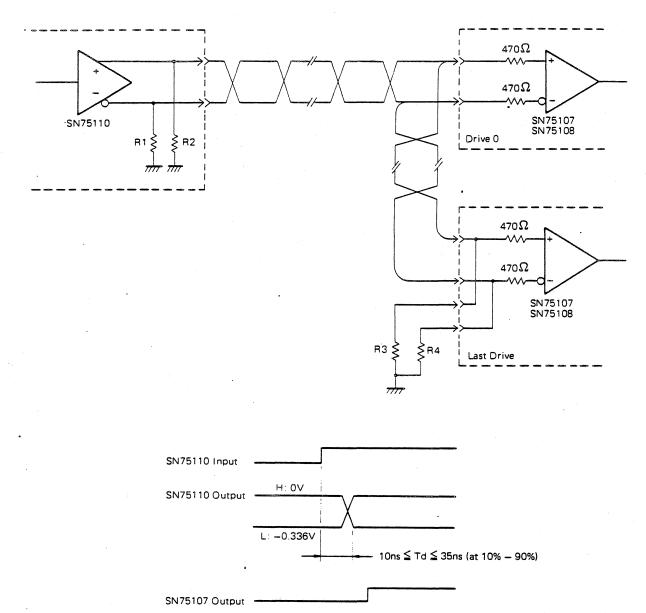

| 4-5-25          | Driver Logic Diagram (SN75110) 4-37                                                                               |

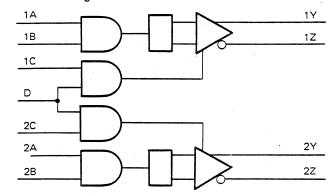

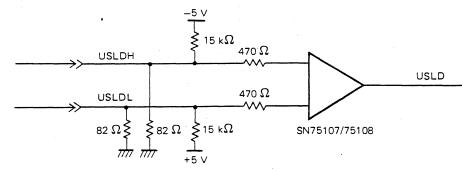

| 4-5-26          | Receiver Logic Diagram (SN75107/75108)                                                                            |

| 4-5-27          | Balanced Transmission of "A" Cable 4-38                                                                           |

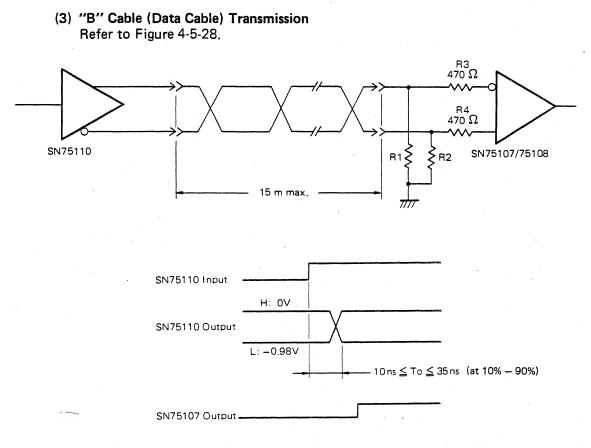

| 4-5-28          | Balanced Transmission "B" Cable                                                                                   |

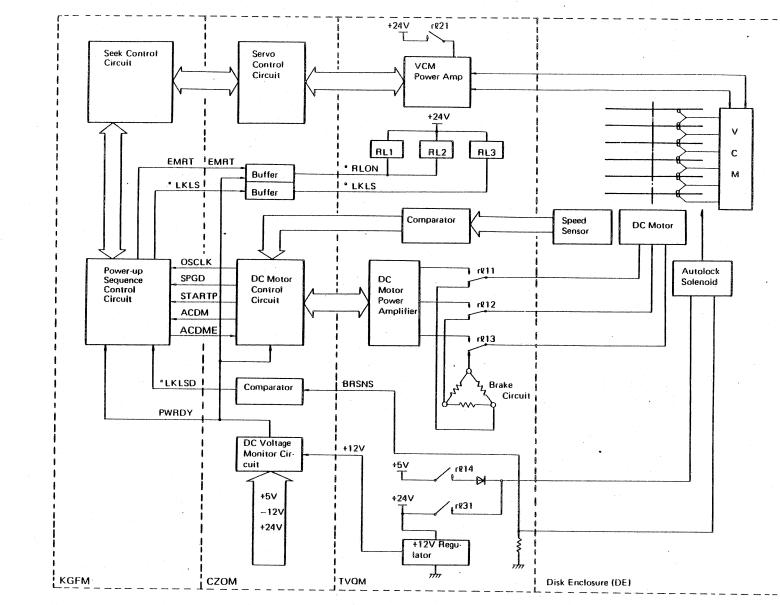

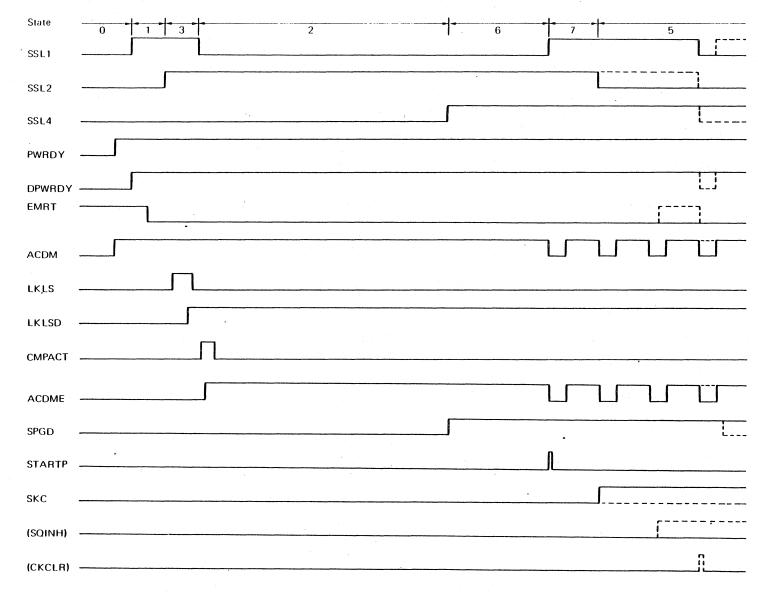

| 4-6-1           | Start/Stop Control Block Diagram                                                                                  |

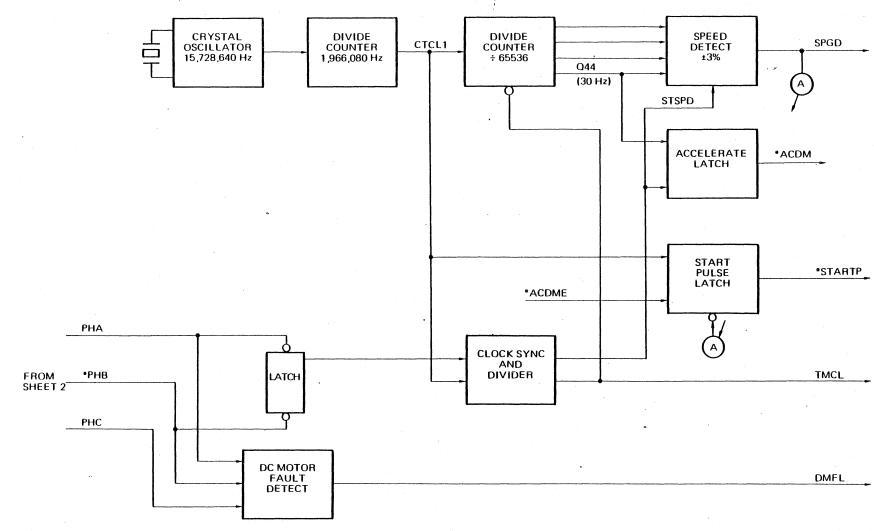

| 4-6-2           | Power-up Sequence Control Block Diagram                                                                           |

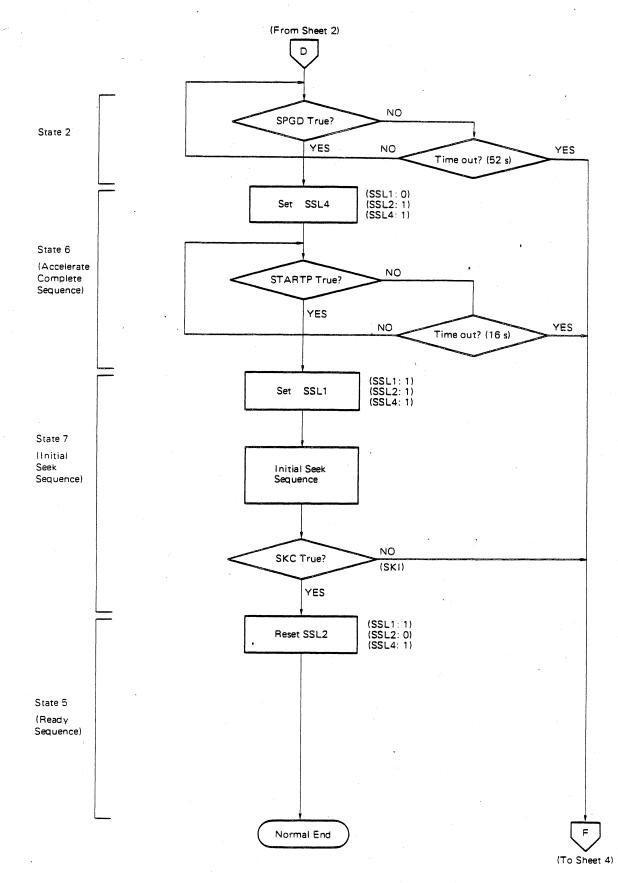

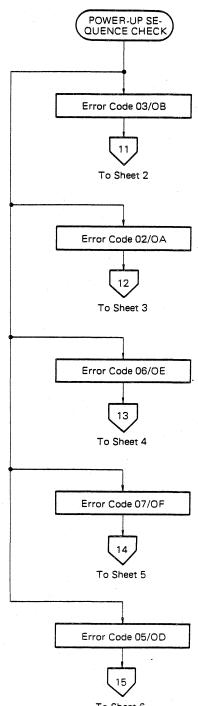

| 4-6-3           | Power-up Sequence Flow Chart (Sheet 1 of 4)                                                                       |

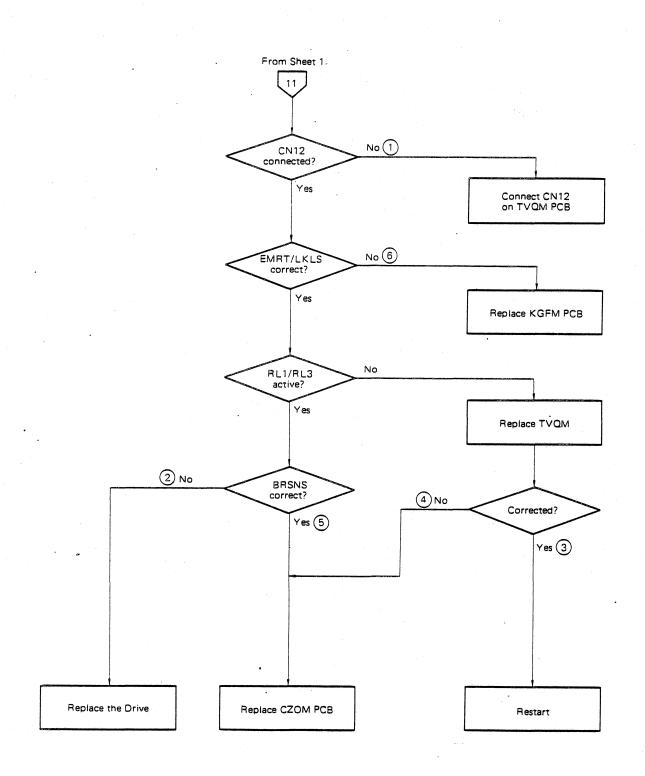

| 4-6-3           | Power-up Sequence Flow Chart (Sheet 2 of 4)                                                                       |

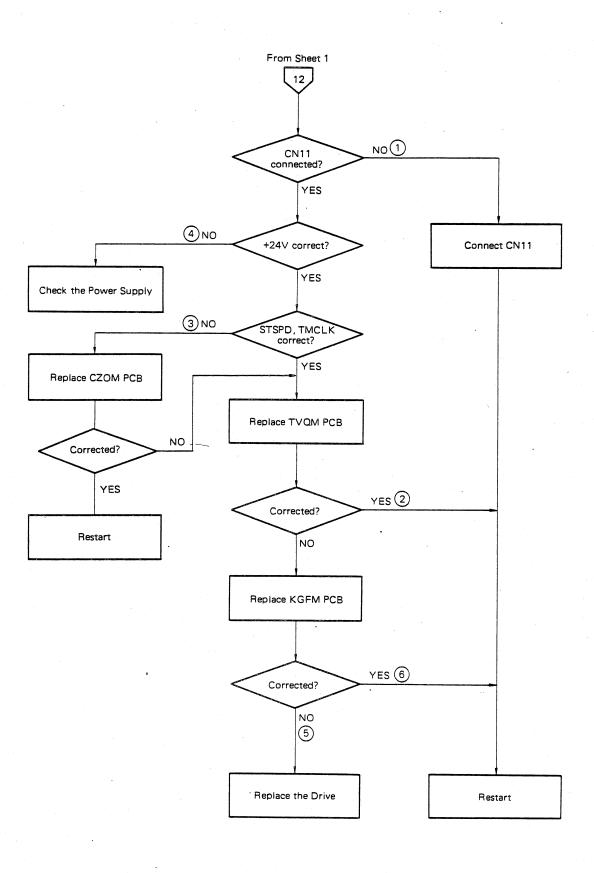

| 4-6-3           | Power-up Sequence Flow Chart (Sheet 3 of 4)                                                                       |

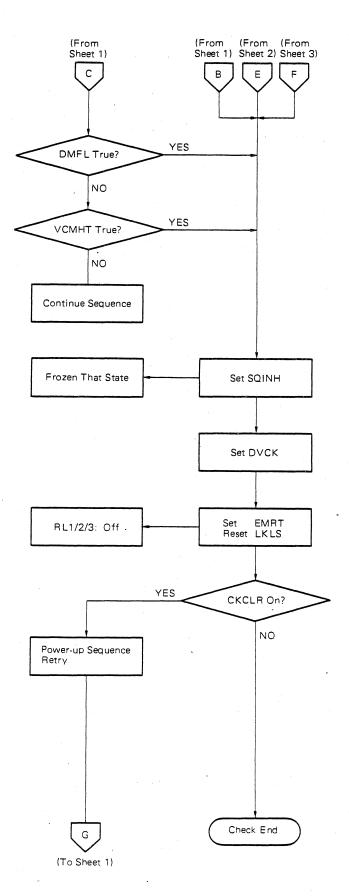

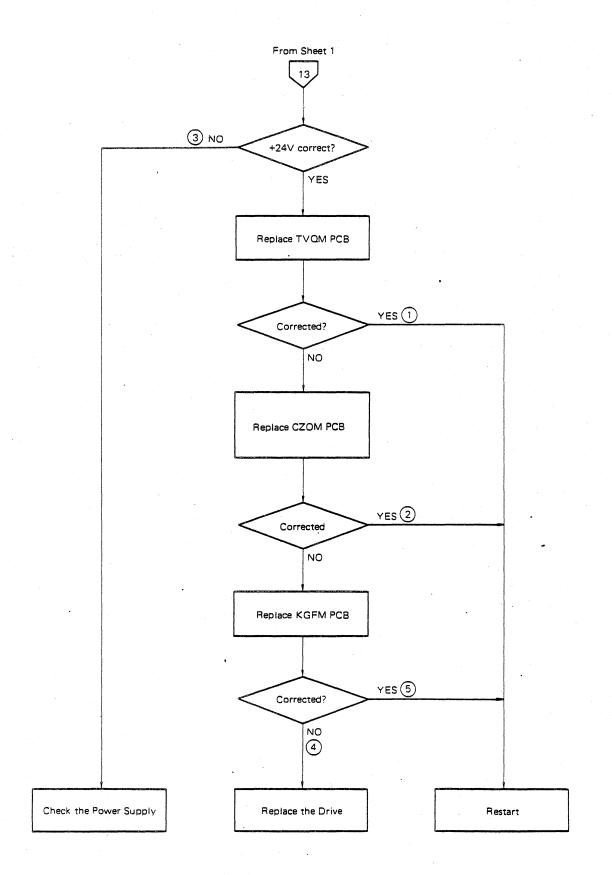

| 4-6-3           | Power-up Sequence Flow Chart (Sheet 4 of 4)                                                                       |

| 4-6-4           | Power-up Sequence Timing Chart                                                                                    |

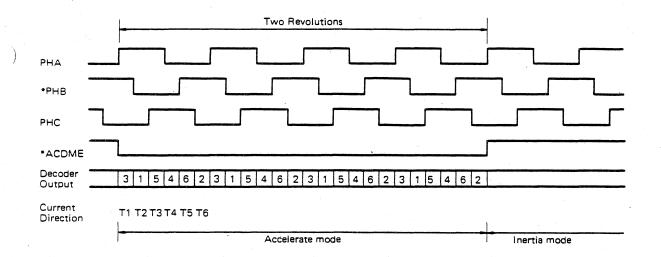

| 4-6-5           | DC Motor Control Block Diagram (Sheet 1 of 2)                                                                     |

| 4-6-5           | DC Motor Control Block Diagram (Sheet 2 of 2)                                                                     |

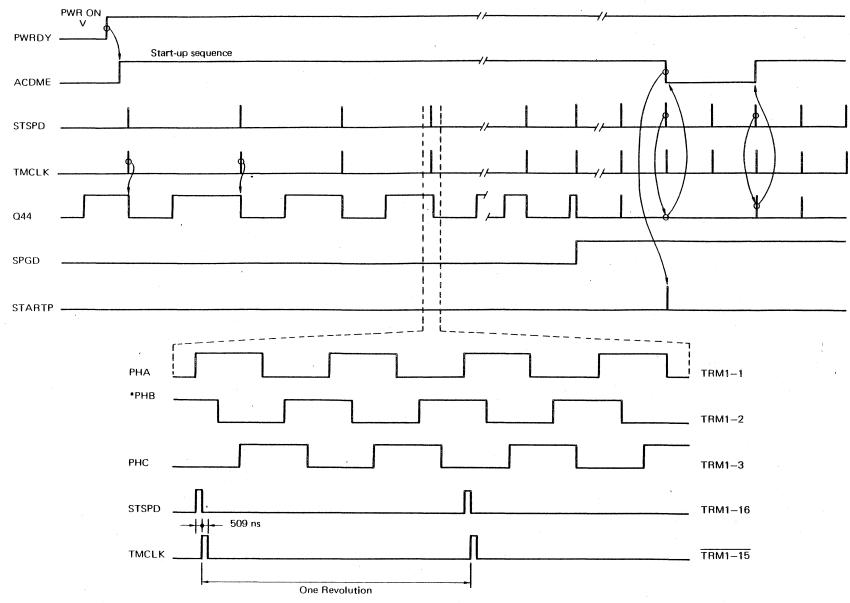

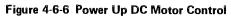

| 4-6-6           | Power Up DC Motor Control                                                                                         |

| 4-0-0           | DC Motor Accelerate/Inertia Mode Control                                                                          |

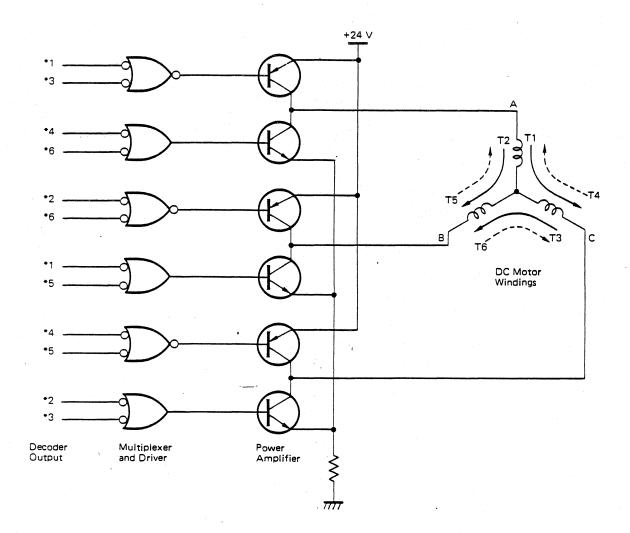

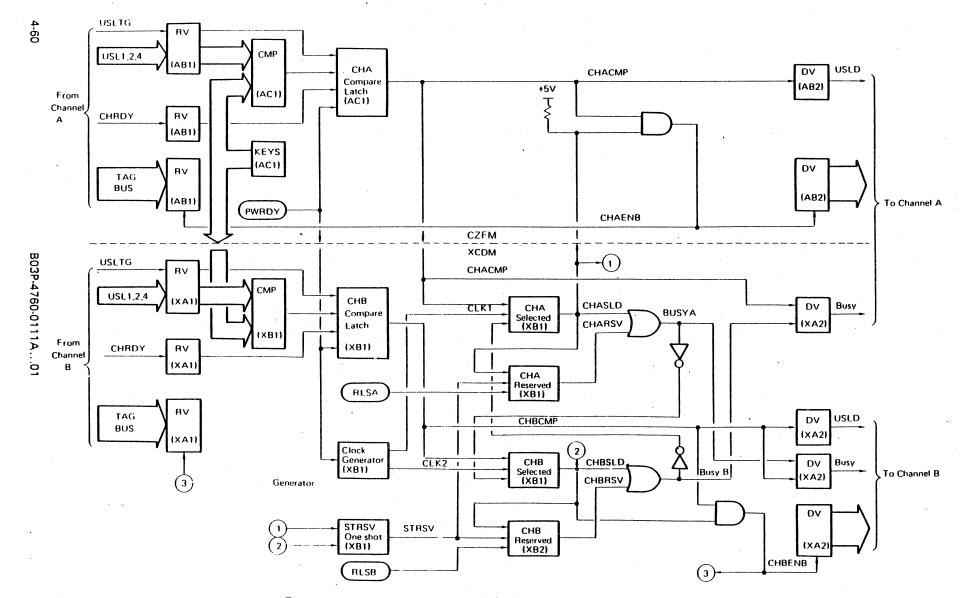

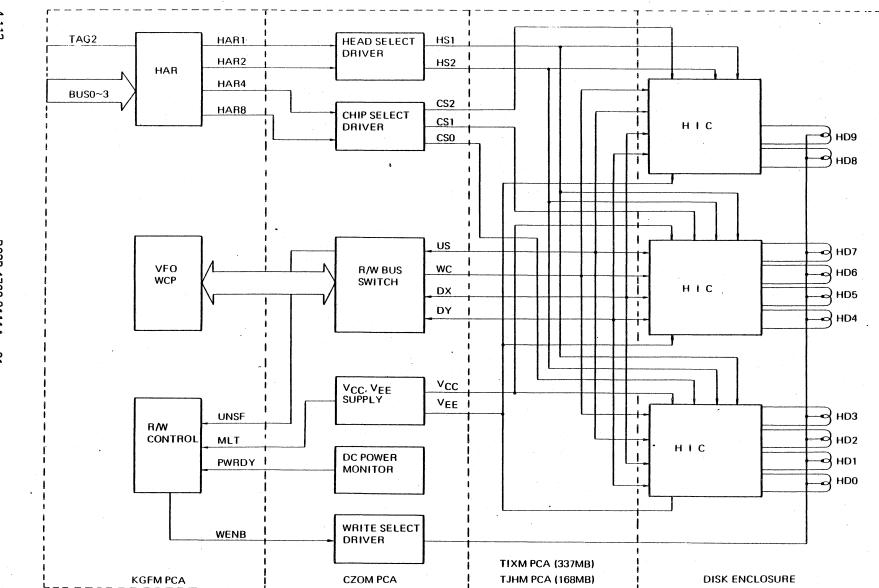

| 4-6-8           | Functional Block Diagram of Dual Channel                                                                          |

| 4-0-0           |                                                                                                                   |

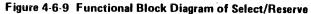

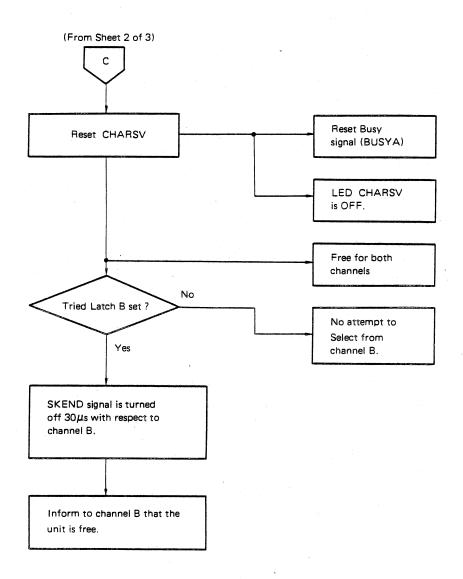

| 4-6-9<br>4-6-10 | Functional Block Diagram of Select/Reserve       4-60         Select/Reserve Flow Chart (Sheet 1 of 3)       4-61 |

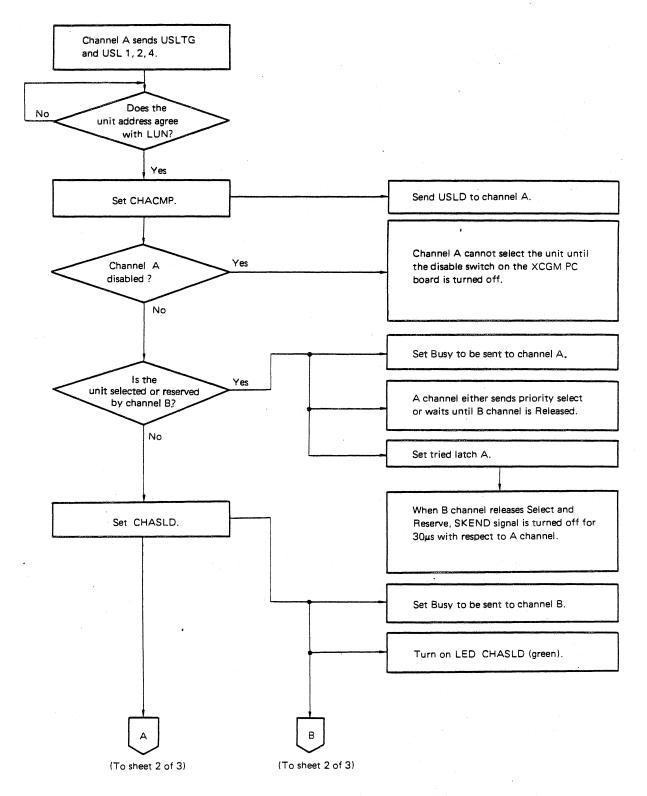

|                 |                                                                                                                   |

| 4-6-10          | Select/Reserve Flow Chart (Sheet 2 of 3)                                                                          |

| 4-6-10          | Select/Reserve Flow Chart (Sheet 3 of 3)                                                                          |

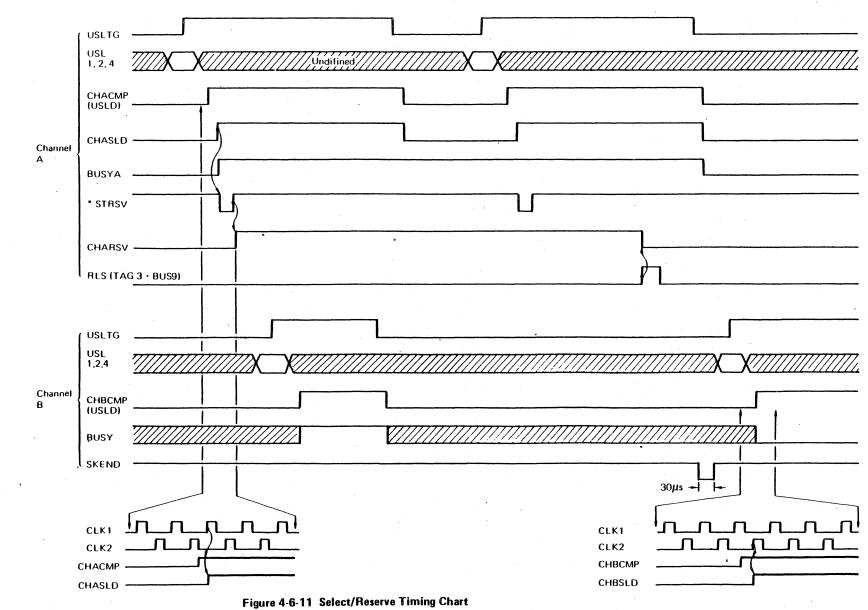

| 4-6-11          | Select/Reserve Timing Chart                                                                                       |

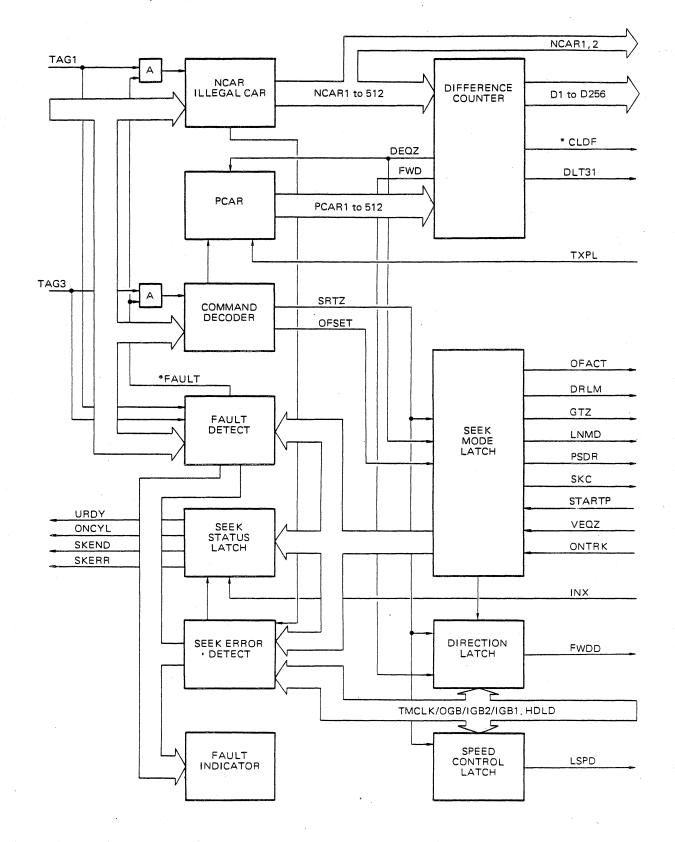

| 4-6-12          | Seek Control Logic Block Diagram                                                                                  |

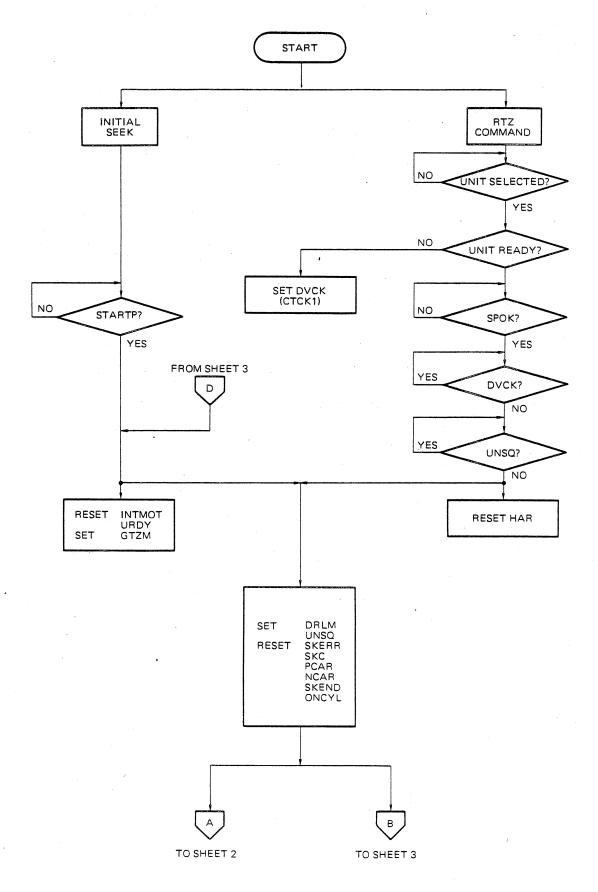

| 4-6-13          | Go To Zero Flow Chart (Sheet 1 of 3)                                                                              |

| 4-6-13          | Go To Zero Flow Chart (Sheet 2 of 3)                                                                              |

| 4-6-13          | Go To Zero Flow Chart (Sheet 3 of 3)                                                                              |

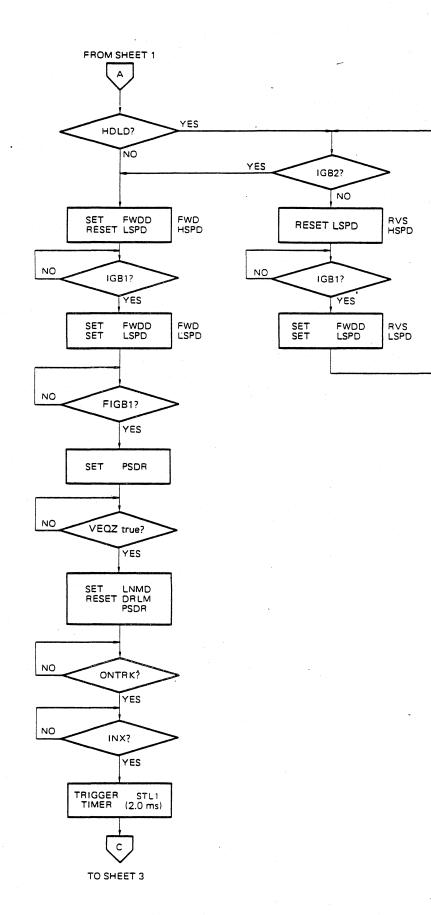

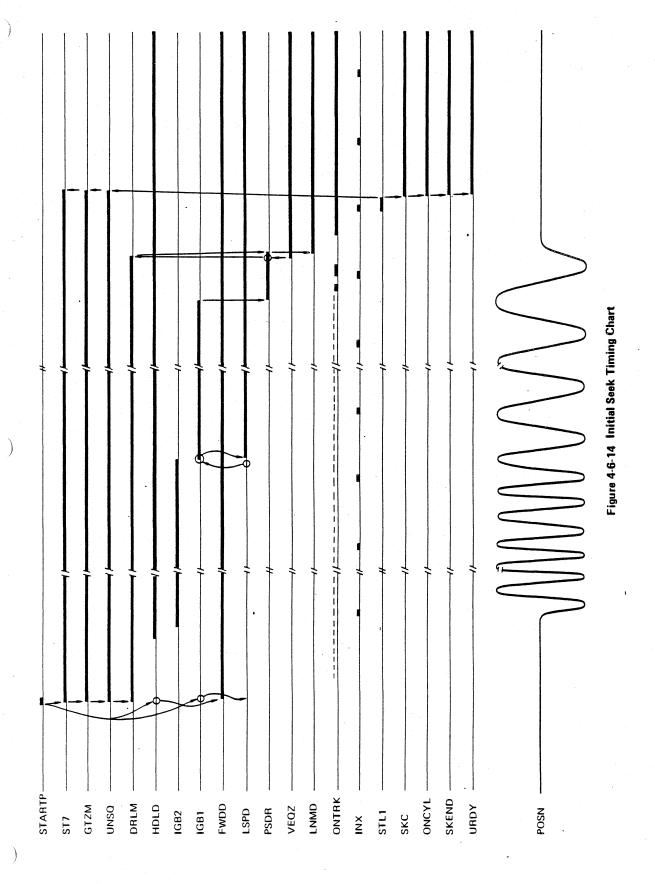

| 4-6-14          | Initial Seek Timing Chart                                                                                         |

| 4-6-15          | Return To Zero Timing Chart                                                                                       |

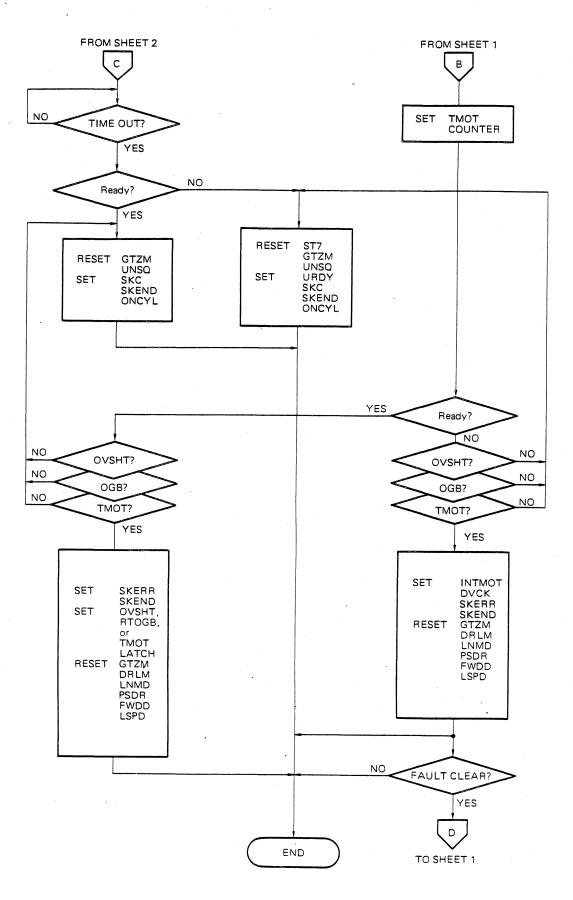

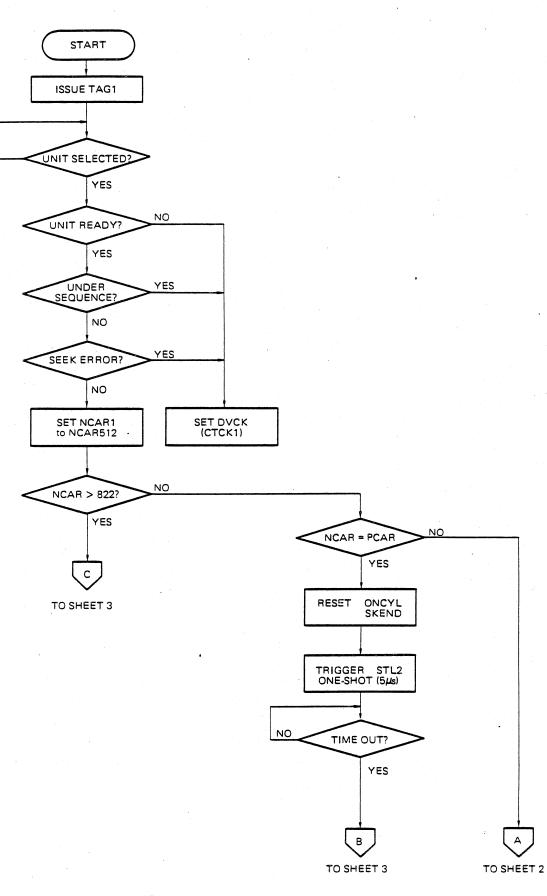

| 4-6-16          | Direct Seek Flow Chart (Sheet 1 of 3)                                                                             |

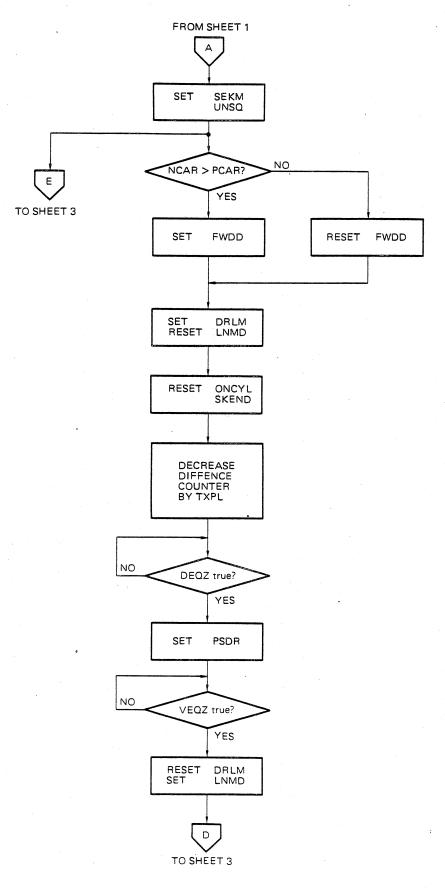

| 4-6-16          | Direct Seek Flow Chart (Sheet 2 of 3) 4-77                                                                        |

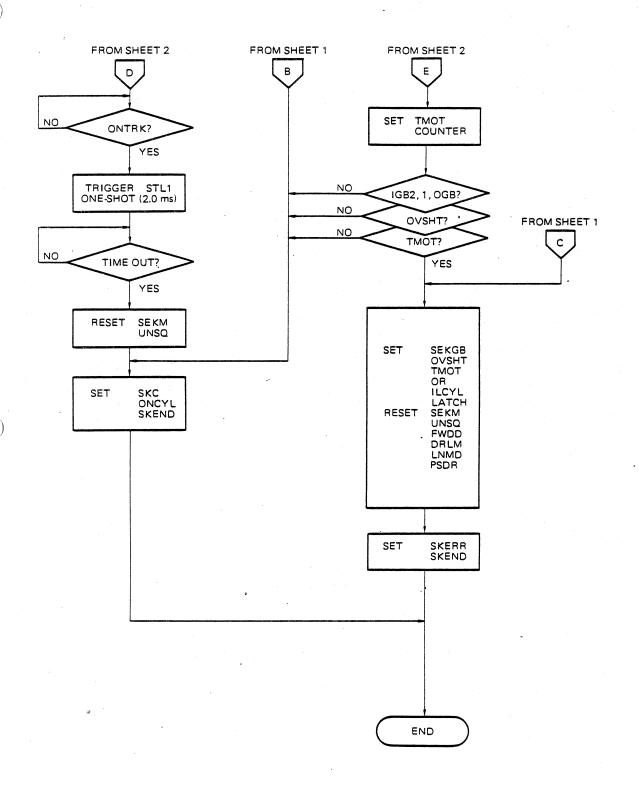

| 4-6-16          | Direct Seek Flow Chart (Sheet 3 of 3) 4-78                                                                        |

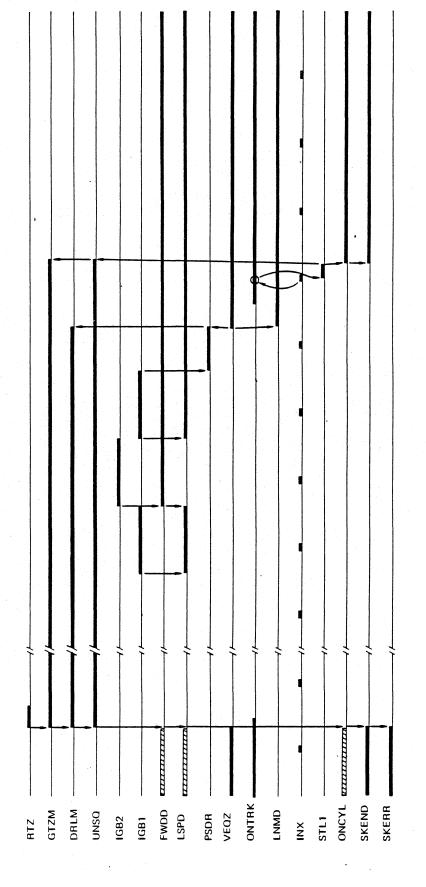

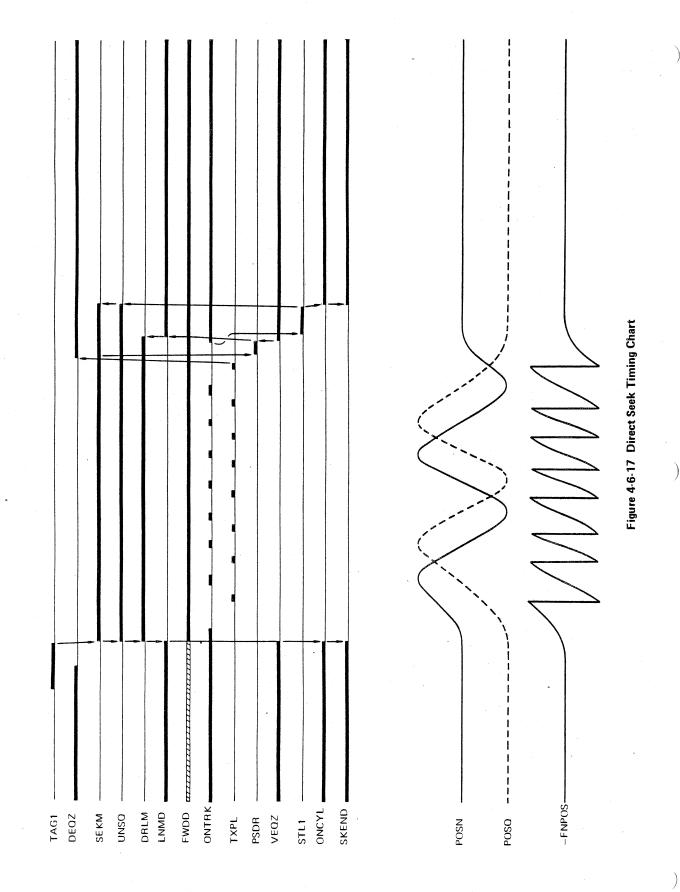

| 4-6-17          | Direct Seek Timing Chart 4-79                                                                                     |

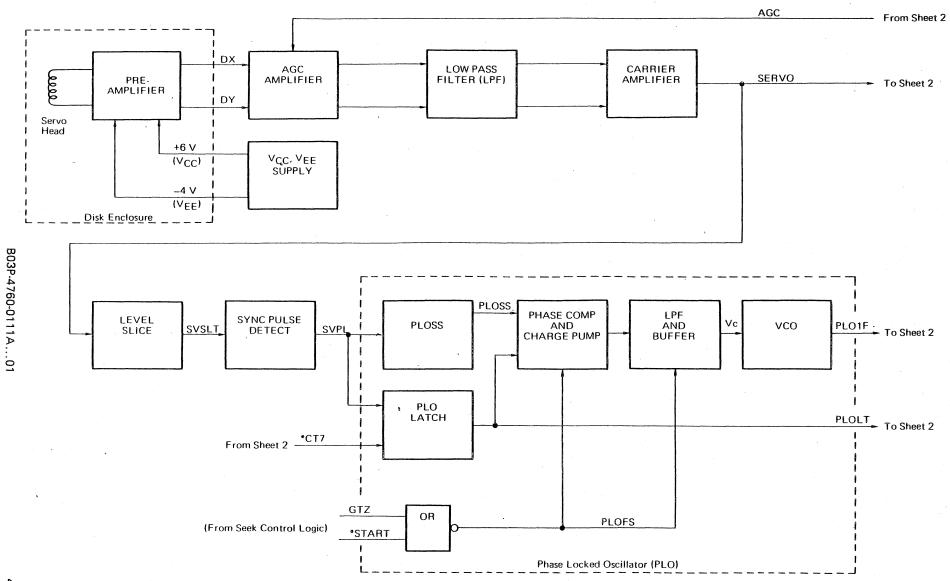

| 4-6-18          | Position Sensing Block Diagram (Sheet 1 of 2)                                                                     |

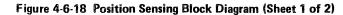

| 4-6-18          | Position Sensing Block Diagram (Sheet 2 of 2)                                                                     |

| 4-6-19          | PLO and Peak Hold Timing Chart 4-84                                                                               |

| 4-6-20          | Servo Signal to Position Signal Conversion                                                                        |

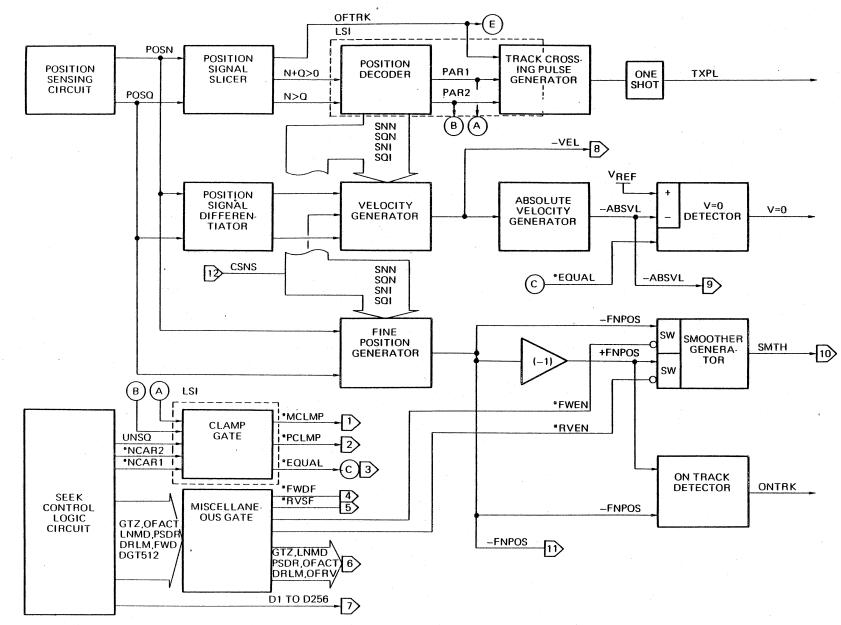

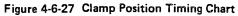

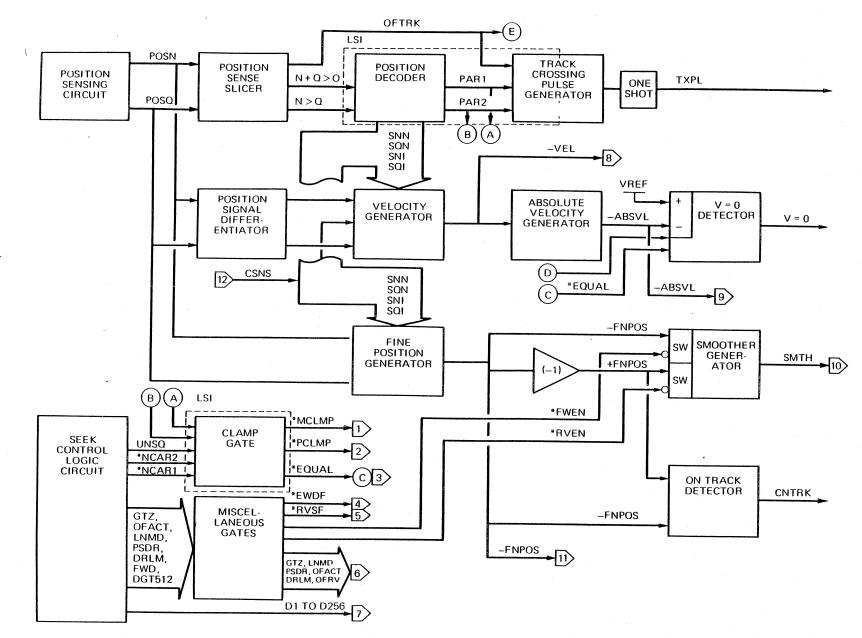

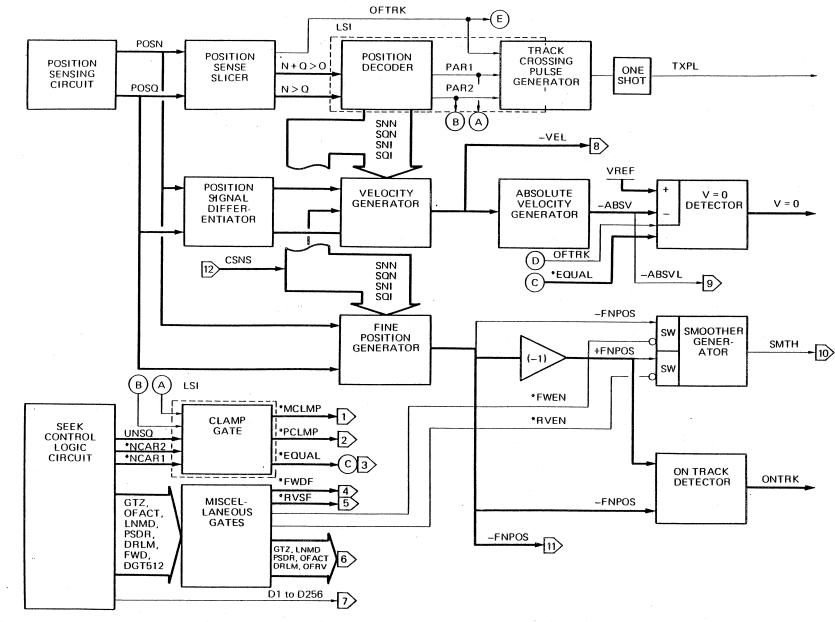

| 4-6-21          | Servo Control Block Diagram (Sheet 1 of 2)                                                                        |

| 4-6-21          | Servo Control Block Diagram (Sheet 2 of 2)                                                                        |

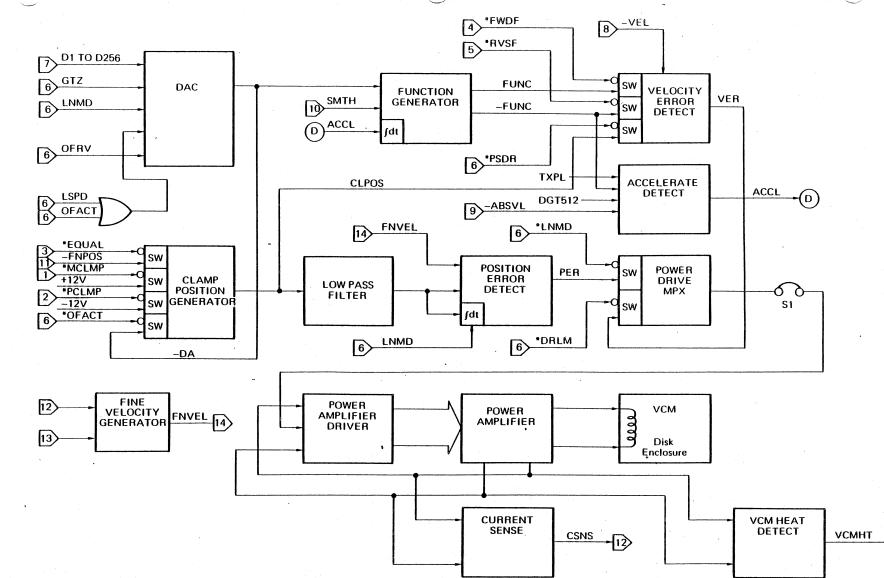

| 4-6-22          | Position Detect Timing Chart 4-89                                                                                 |

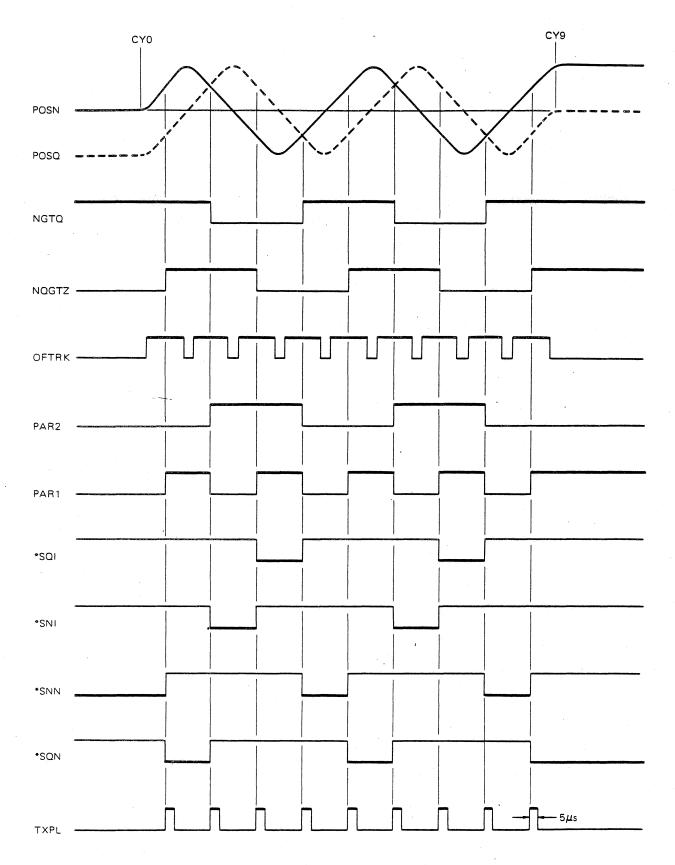

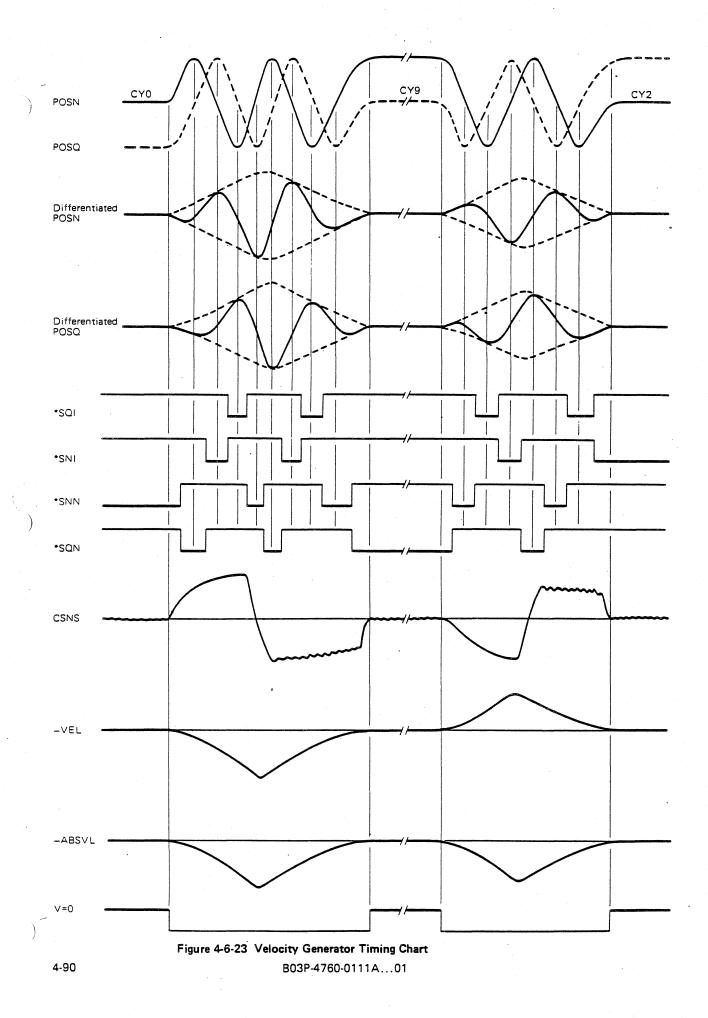

| 4-6-23          | Velocity Generator Timing Chart 4-90                                                                              |

| 4-6-24          | Fine Position Generator Timing Chart 4-92                                                                         |

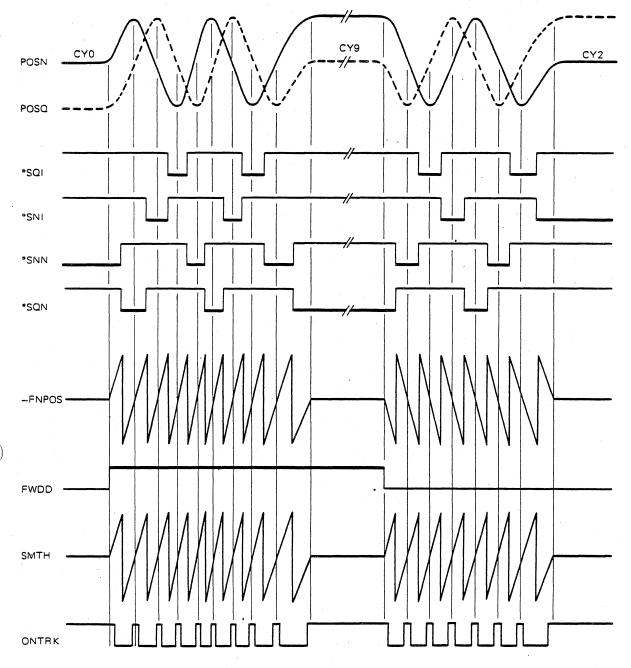

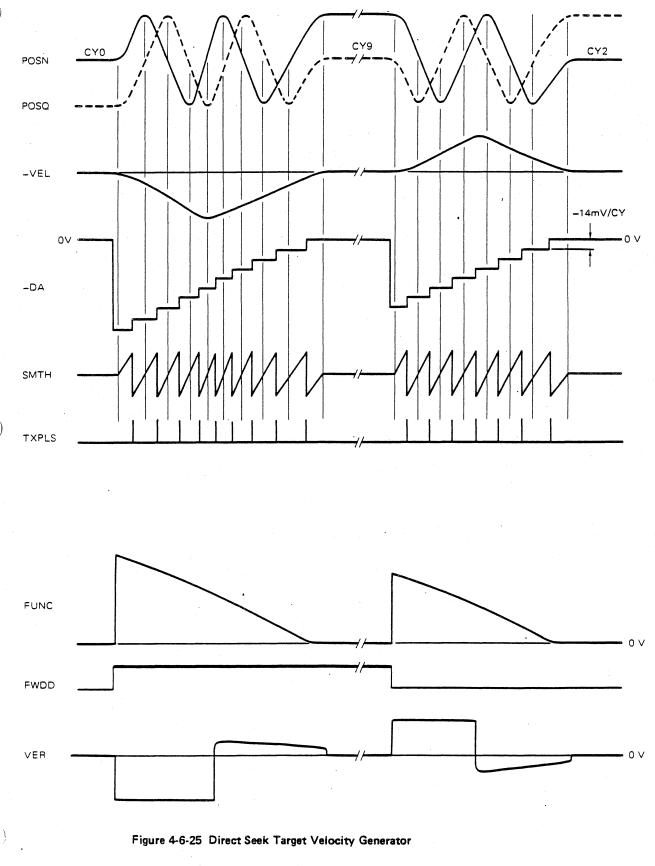

| 4-6-25          | Direct Seek Target Velocity Generator 4-94                                                                        |

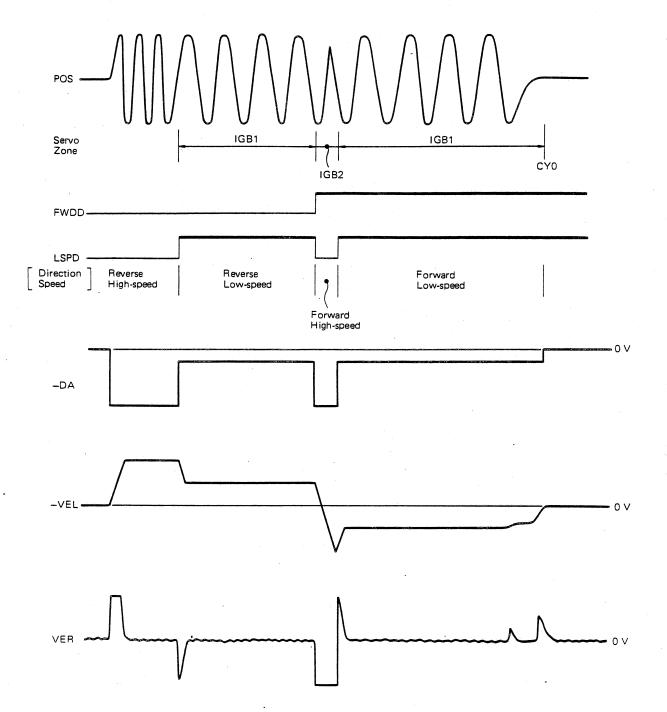

| 4-6-26          | GTZ Target Velocity Generator 4-95                                                                                |

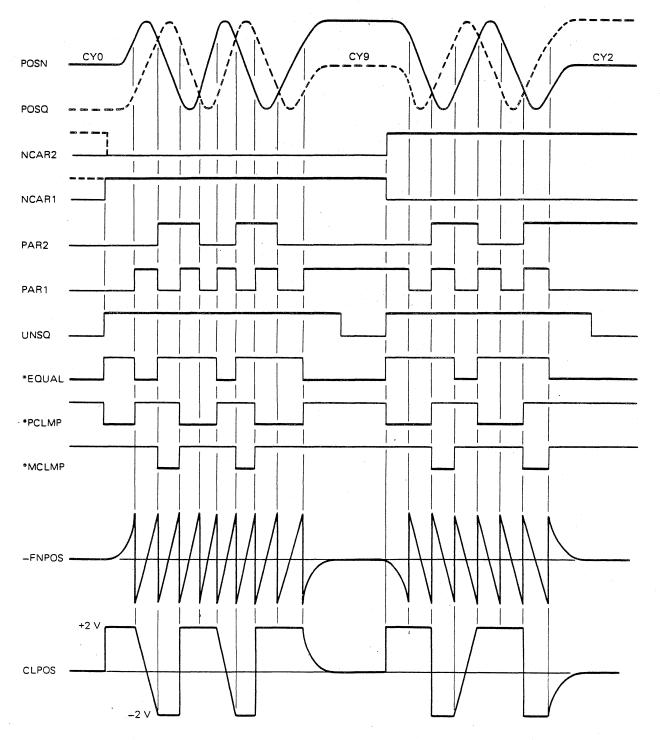

| 4-6-27          | Clamp Positon Timing Chart                                                                                        |

| 4-6-28          | Direct Seek Signal Flow (Sheet 1 of 2)                                                                            |

| 4-6-28          | Direct Seek Signal Flow (Sheet 2 of 2) 4-100                                                                      |

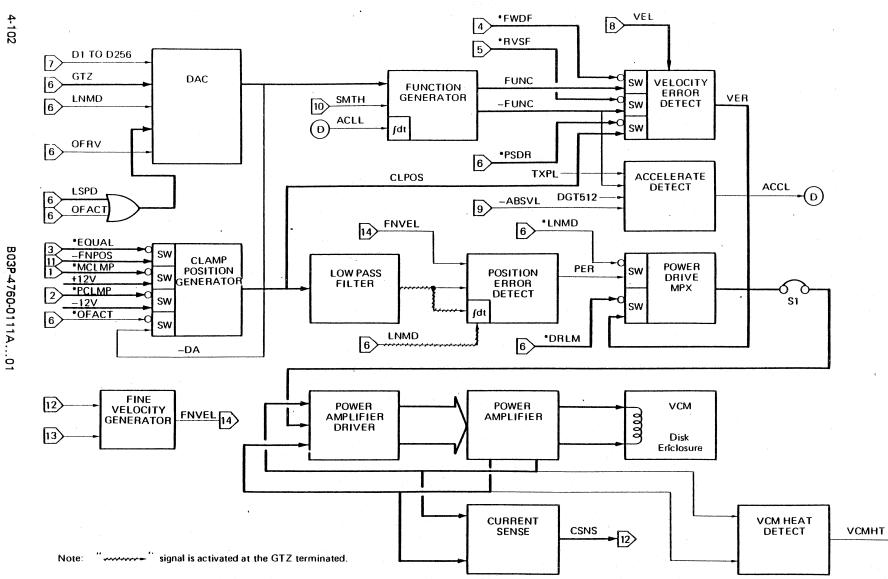

| 4-6-29          | GTZ Signal Flow (Sheet 1 of 2) 4-101                                                                              |

| 4-6-29          | GTZ Signal Flow (Sheet 2 of 2) 4-102                                                                              |

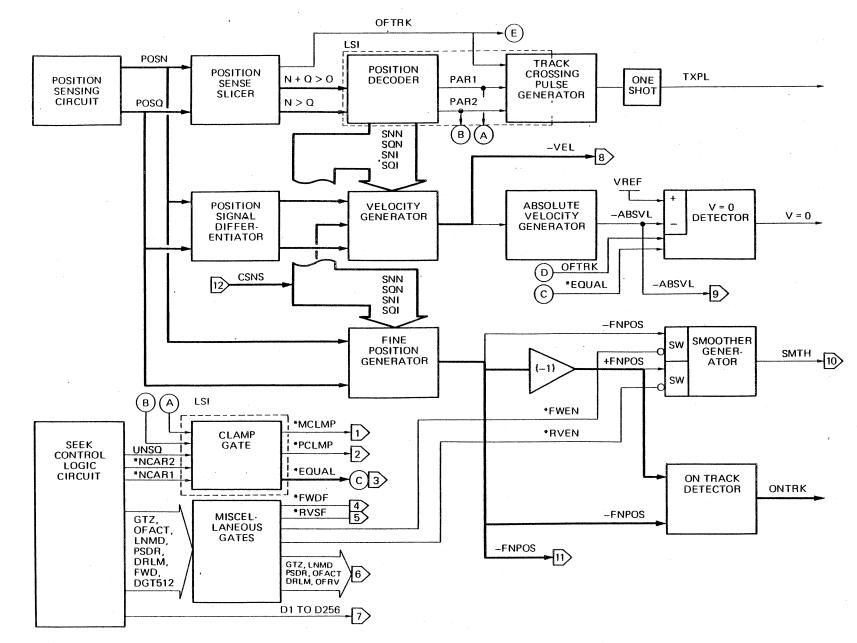

| 4-6-30          | Linear Mode Signal Flow (Sheet 1 of 2)                                                                            |

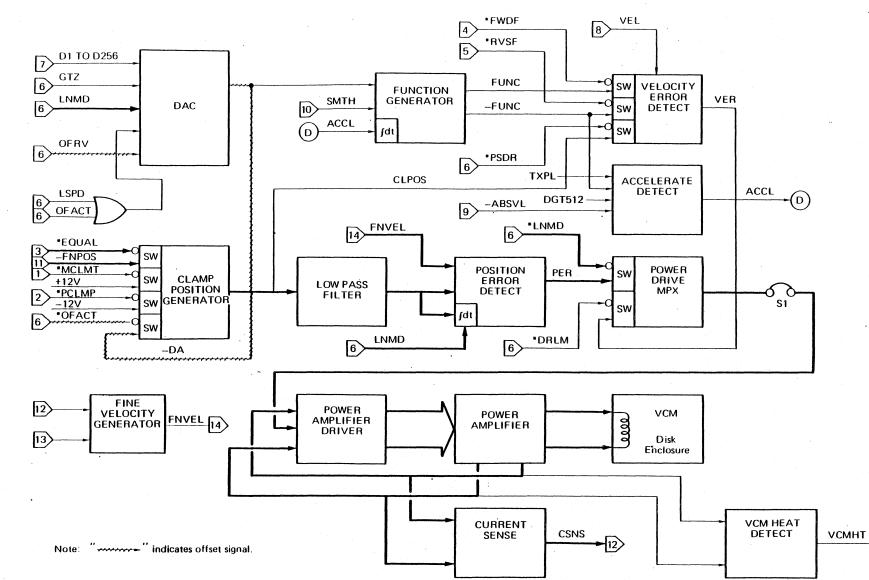

| 4-6-30          | Linear Mode Signal Flow (Sheet 2 of 2) 4-104                                                                      |

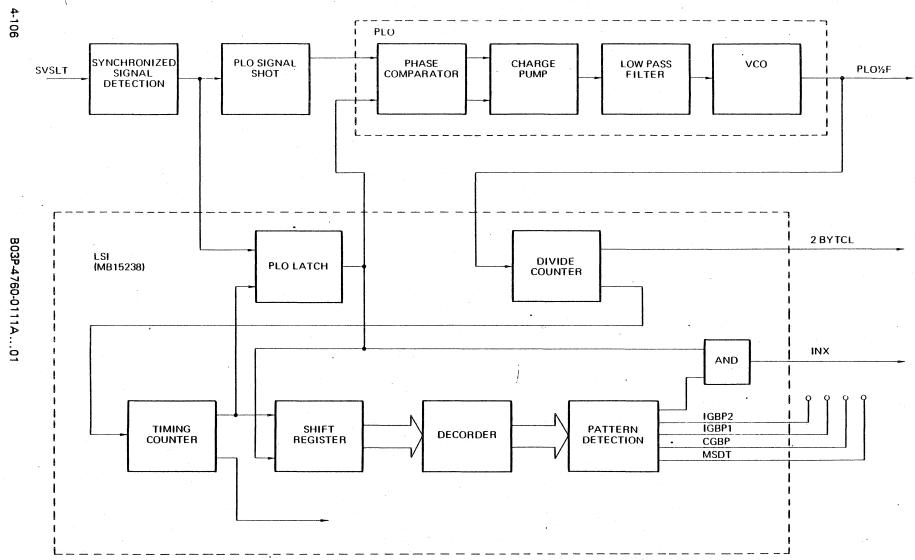

| 4-6-31          | Index/Guard Band Patterns Detect Block Diagram                                                                    |

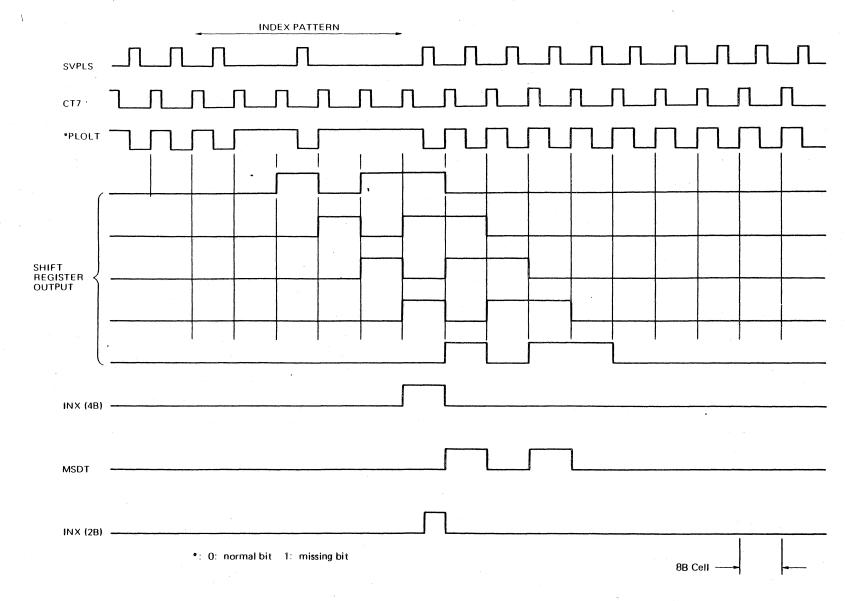

| 4-6-32          | Index Detect Timing Chart 4-107                                                                                   |

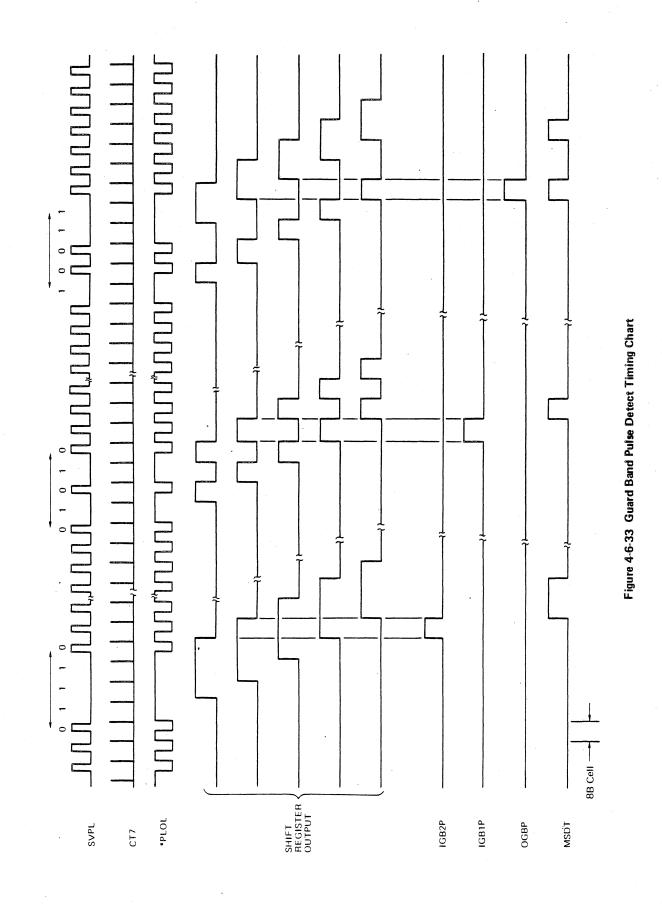

| 4-6-33          | Guard Band Pulse Detect Timing Chart                                                                              |

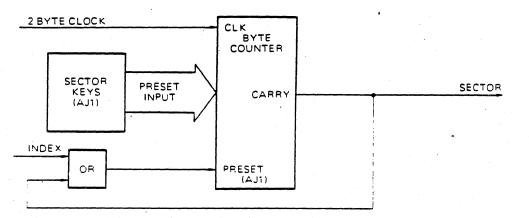

| 4-6-34          | Sector Generator Block Diagram                                                                                    |

|                 |                                                                                                                   |

|                 |                                                                                                                   |

xi

| 4-6-35     | Sector Generator Timing Chart                      |

|------------|----------------------------------------------------|

| 4-6-36     | Head Selection Block Diagram                       |

| 4-6-37     | Data Write                                         |

| <br>4-6-38 | Data Read                                          |

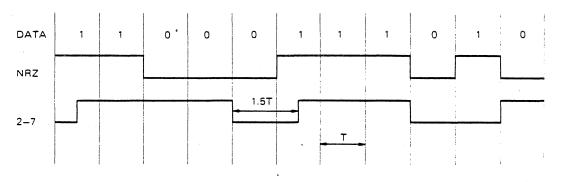

| 4-6-39     | 2-7 Coding                                         |

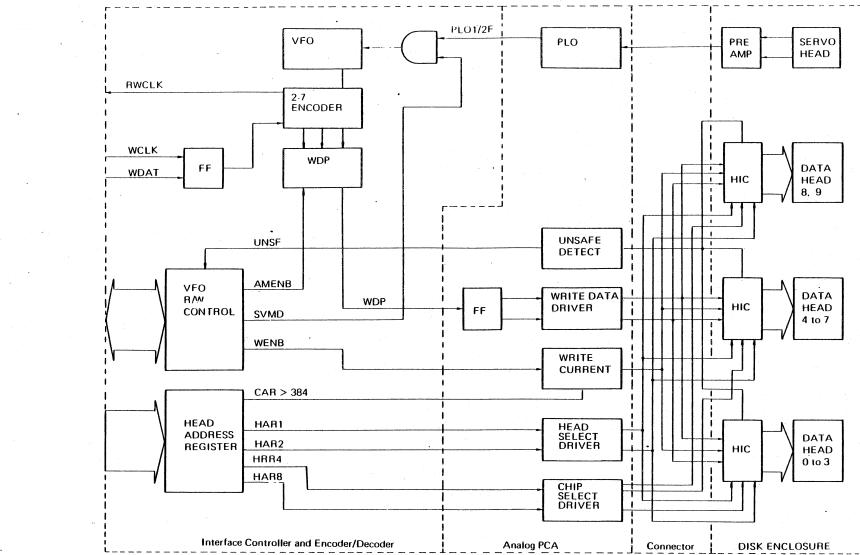

|            | Write Operation Block Diagram                      |

| 4-6-40     |                                                    |

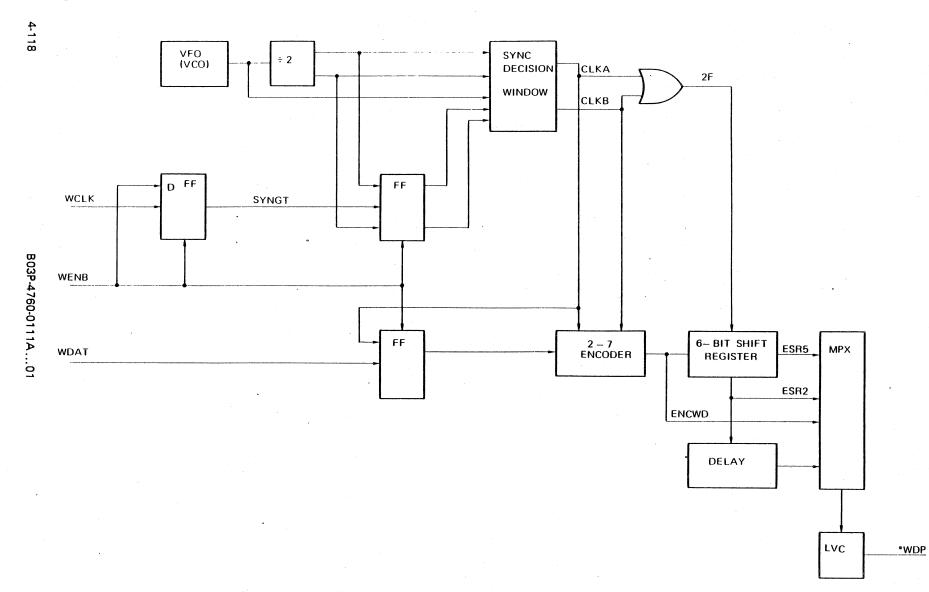

| 4-6-41     | 2-7 Coding and Write Compensation Block Diagram    |

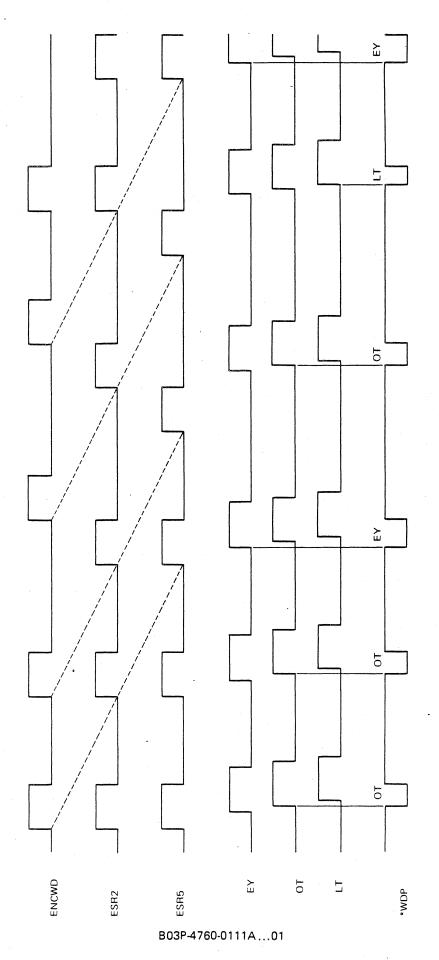

| 4-6-42     | Write Compensation Timing Chart 4-119              |

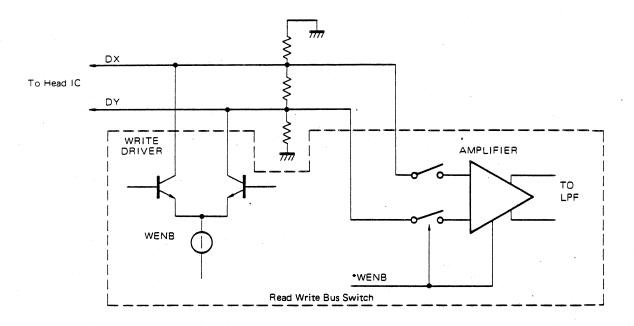

| 4-6-43     | Read Write Bus Switch 4-120                        |

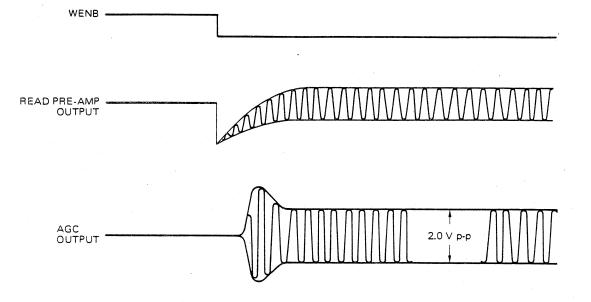

| 4-6-44     | AGC Squelch Function                               |

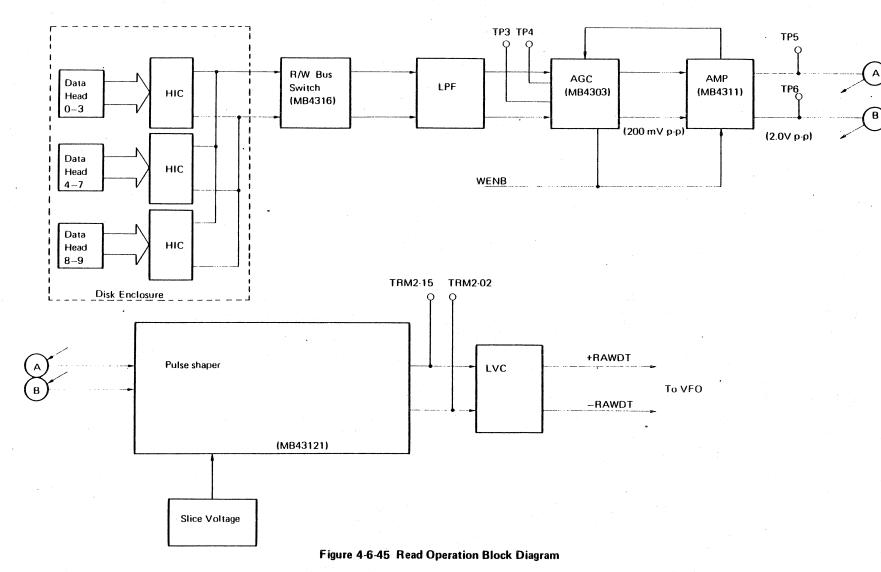

| 4-6-45     | Read Operation Block Diagram                       |

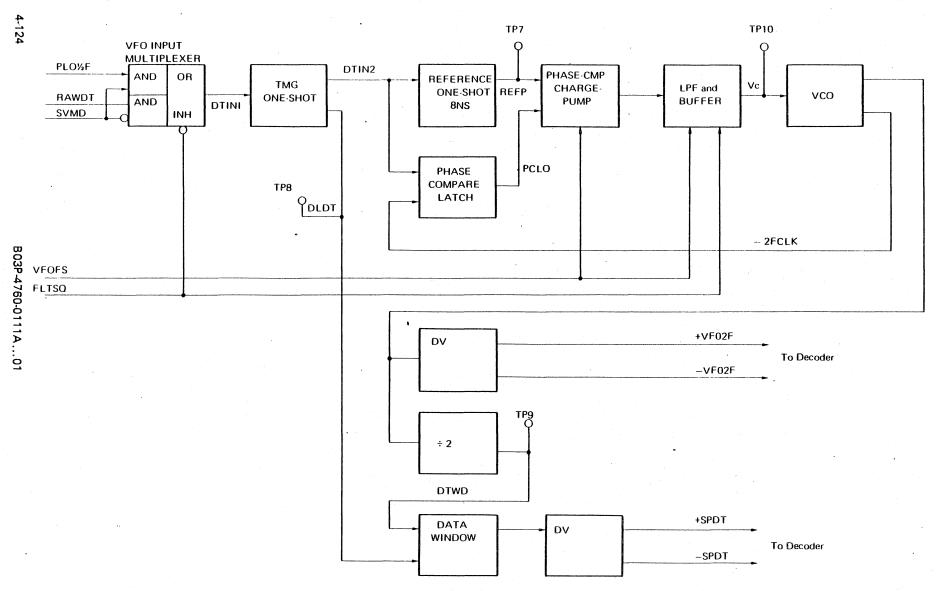

| 4-6-46     | VFO Block Diagram                                  |

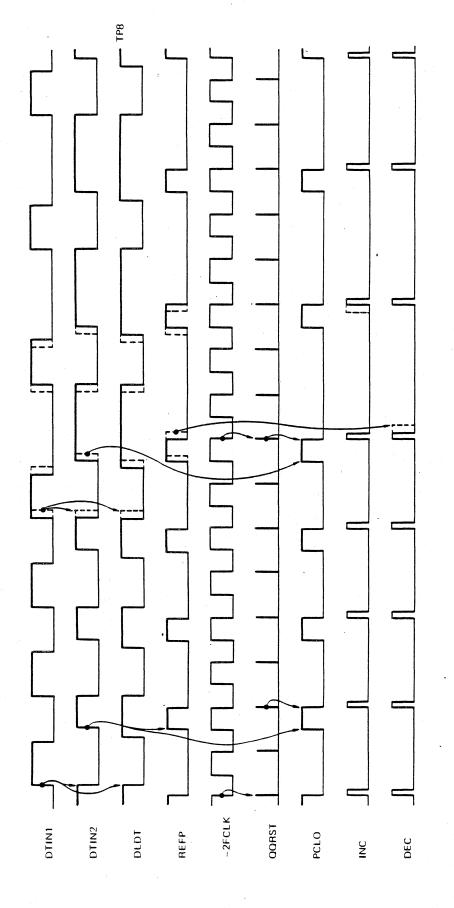

| 4-6-47     | VFO Timing Chart                                   |

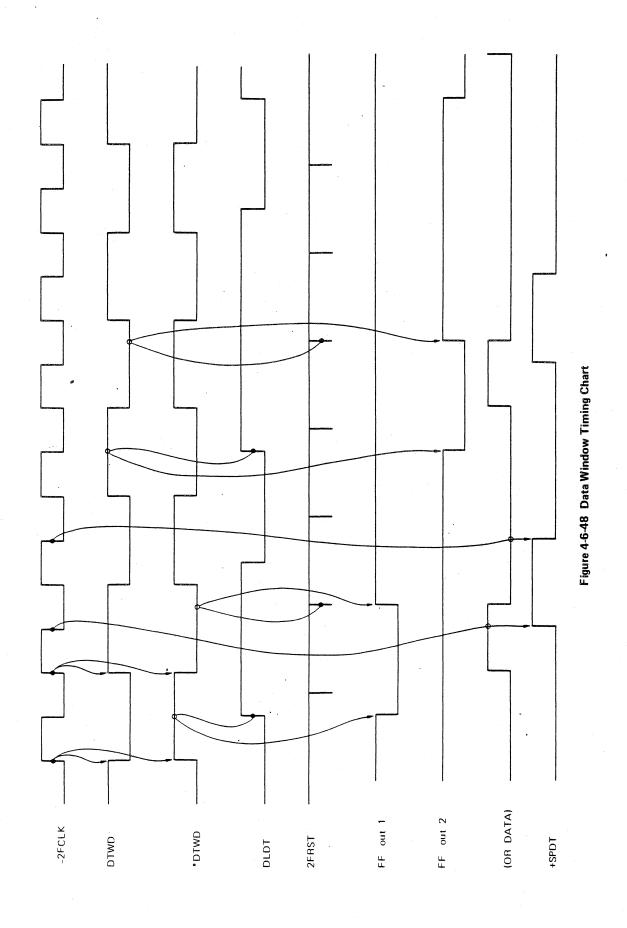

| 4-6-48     | Data Window Timing Chart                           |

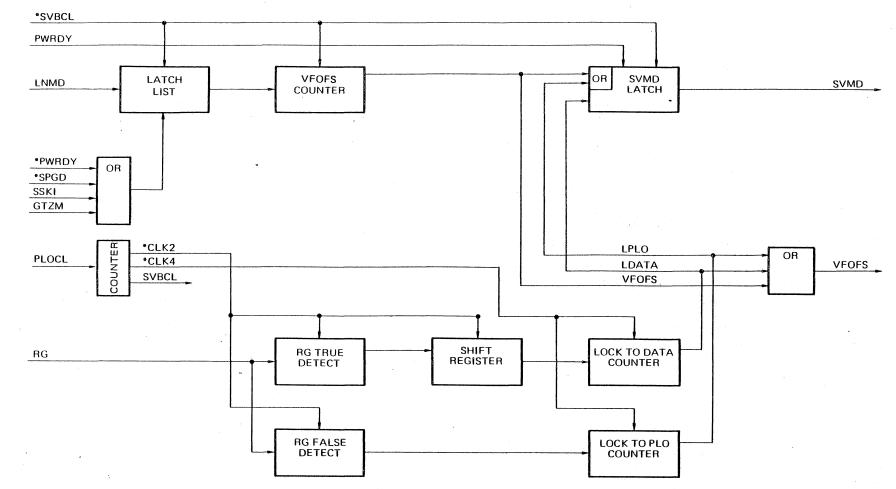

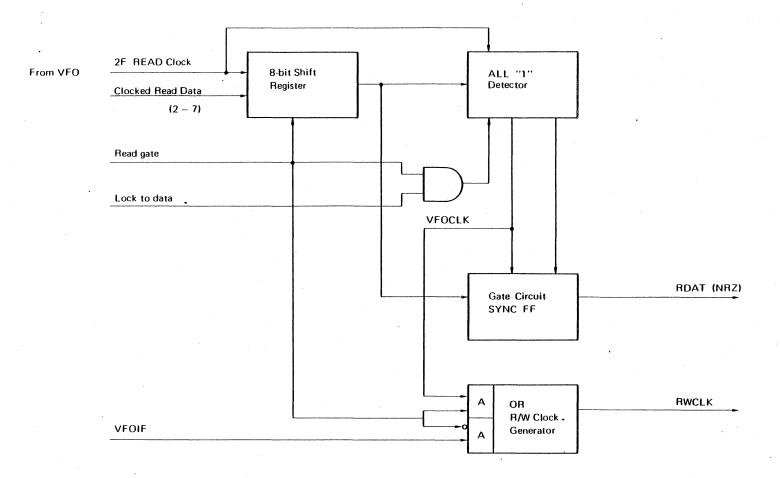

| 4-6-49     | VFO Control Logic Block Diagram                    |

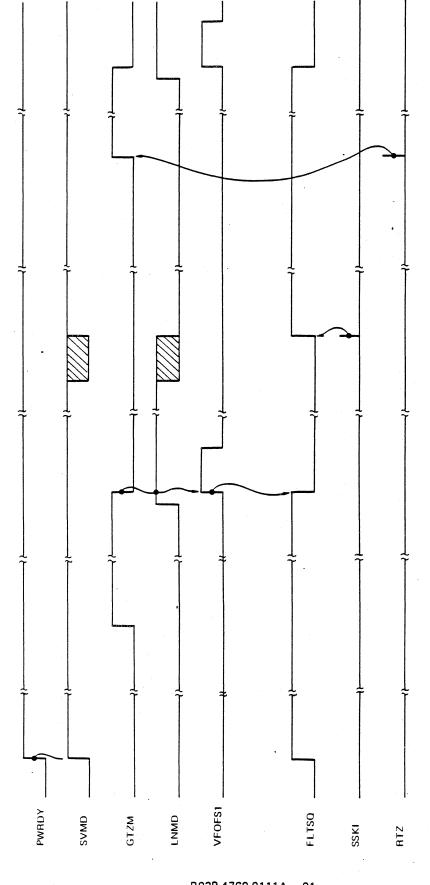

| 4-6-50     | Initial VFO Control Timing Chart                   |

| 4-6-51     |                                                    |

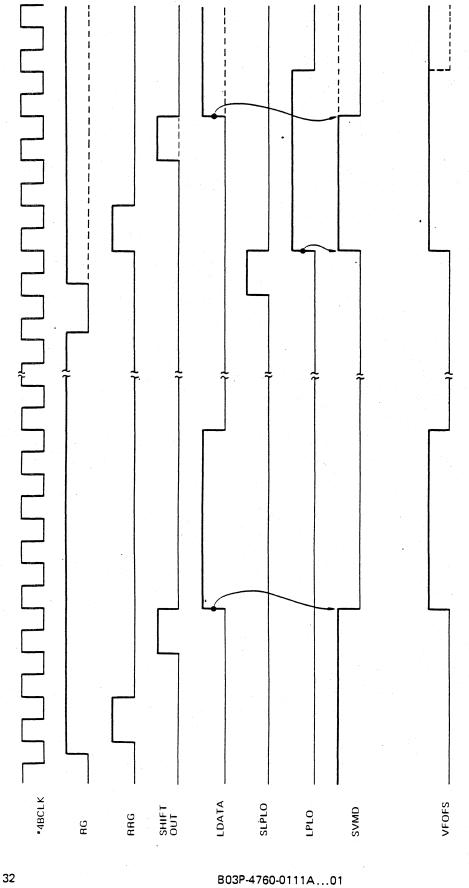

|            | VFO Control Timing Chart                           |

| 4-6-52     | 2-7 Decoder Block Diagram                          |

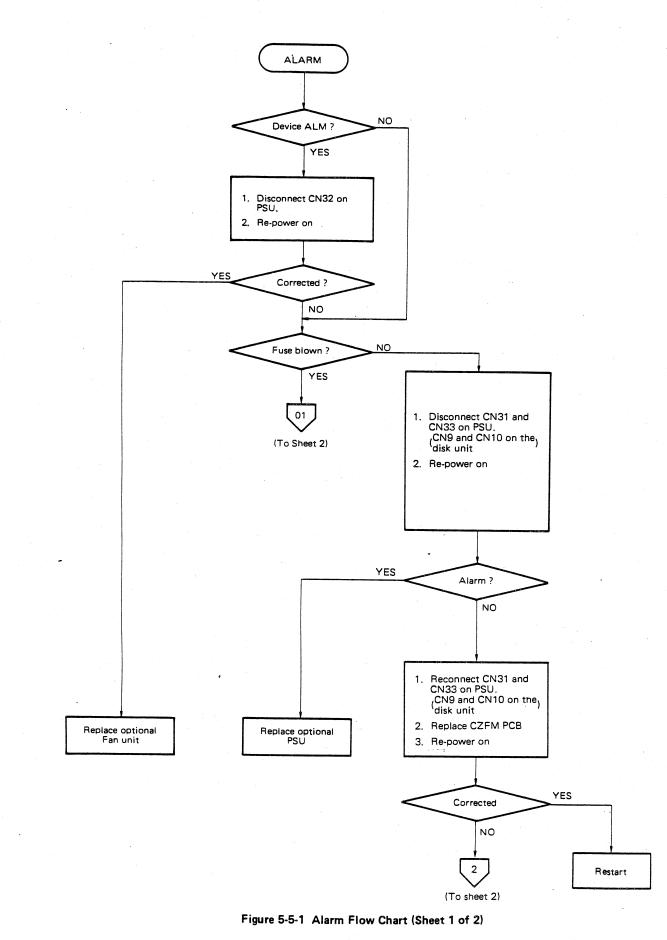

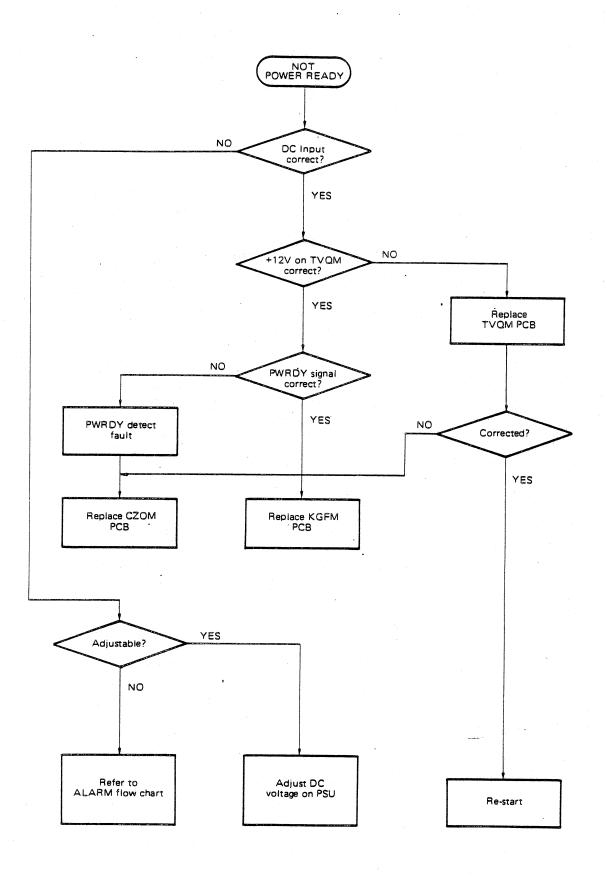

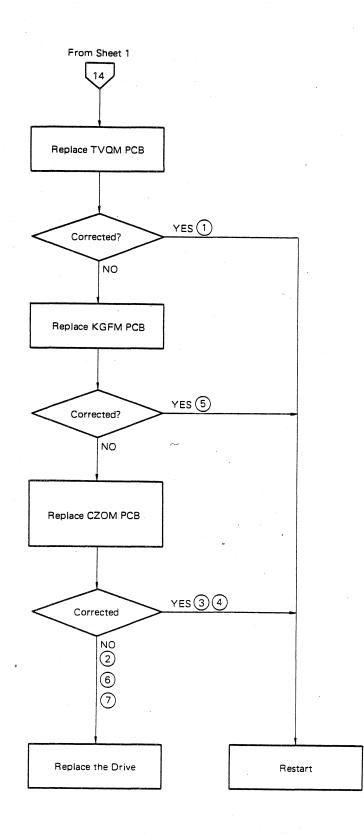

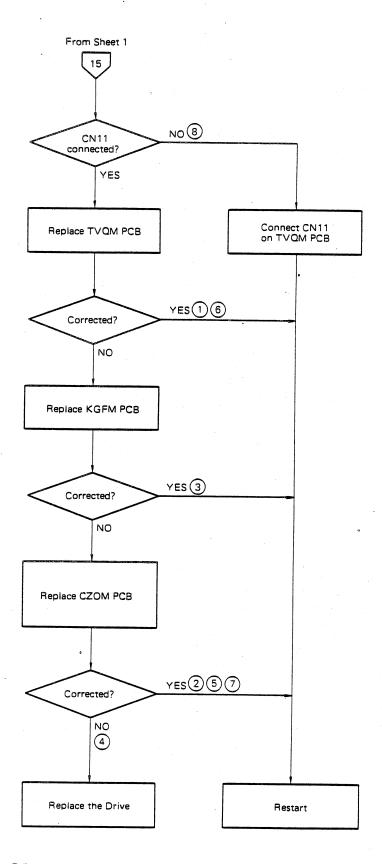

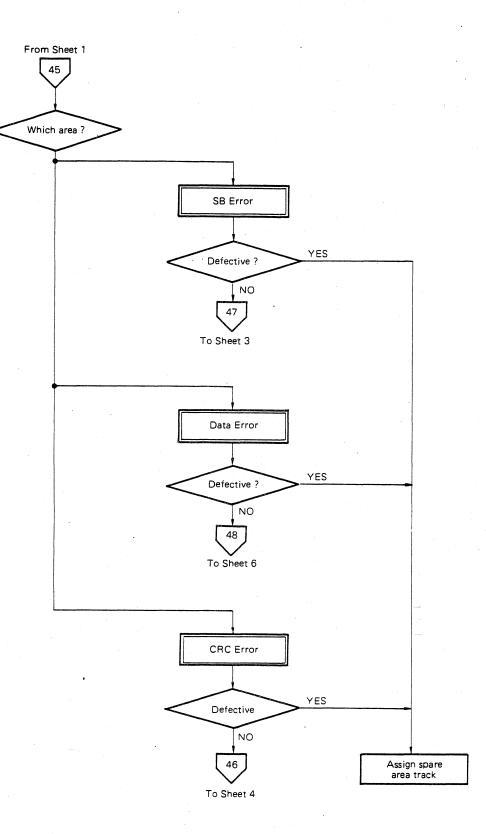

| 5-5-1      | Alarm Flow Chart (Sheet 1 of 2)                    |

| 5-5-1      | Alarm Flow Chart (Sheet 2 of 2)                    |

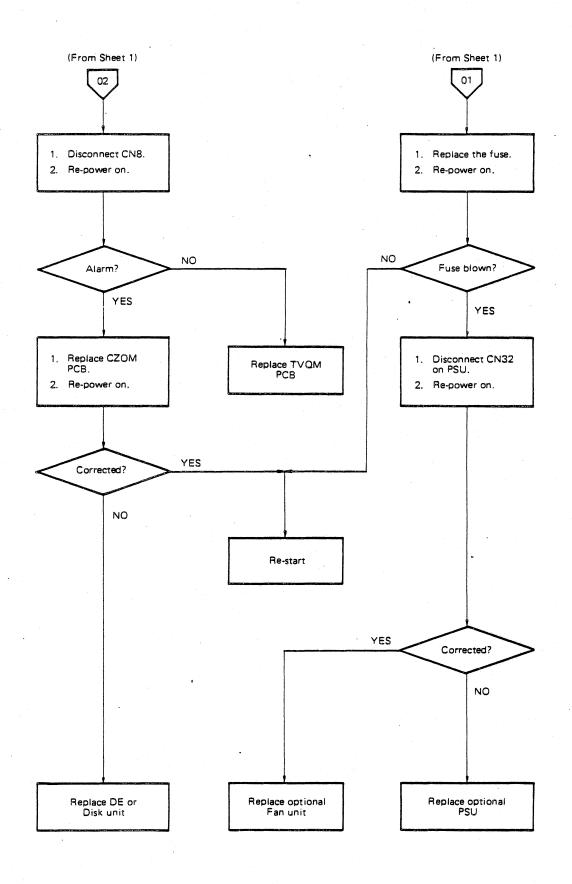

| 5-5-2      | Not Selected Flow Chart                            |

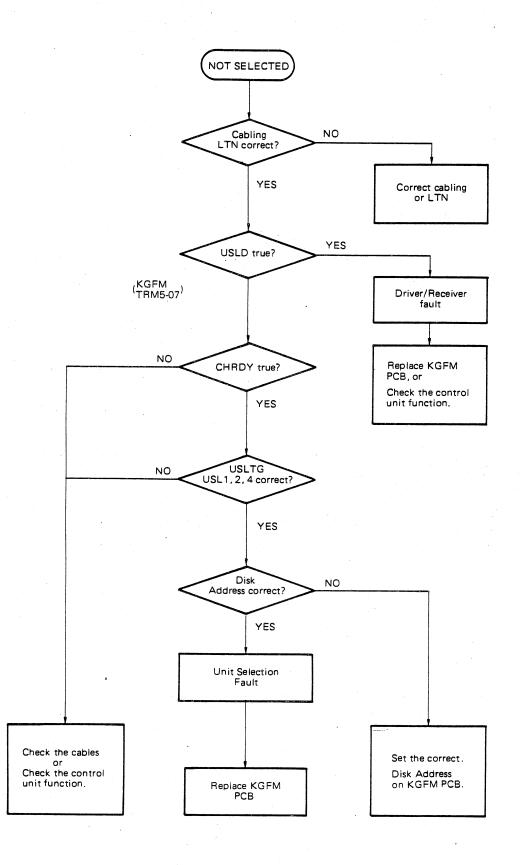

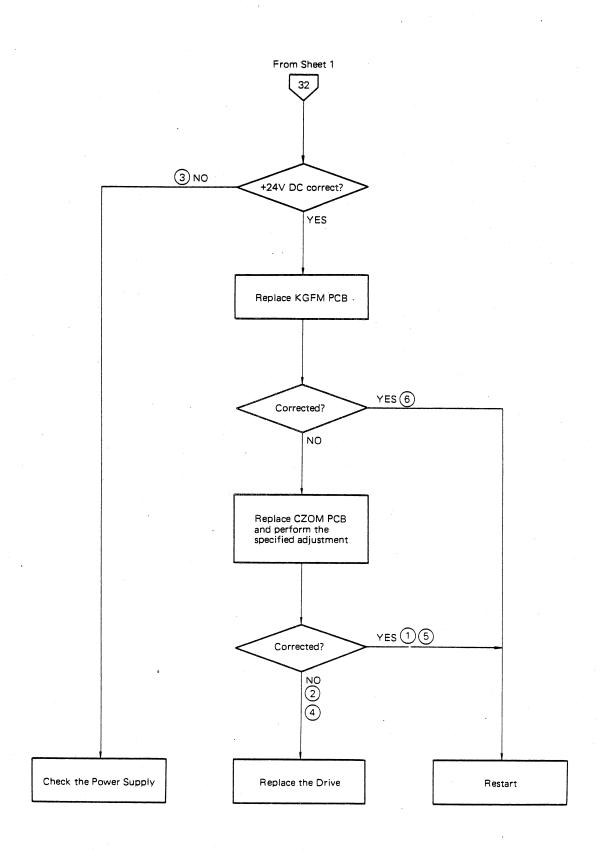

| 5-5-3      | Not Power Ready Flow Chart                         |

| 5-5-4      | Power-up Sequence Check Flow Chart (Sheet 1 of 6)  |

|            | Power-up Sequence Check Flow Chart (Sheet 2 of 6)  |

| 5-5-4      |                                                    |

| 5-5-4      | Power-up Sequence Check Flow Chart (Sheet 3 of 6)  |

| 5-5-4      | Power-up Sequence Check Flow Chart (Sheet 4 of 6)  |

| 5-5-4      | Power-up Sequence Check Flow Chart (Sheet 5 of 6)  |

| 5-5-4      | Power-up Sequence Check Flow Chart (Sheet 6 of 6)  |

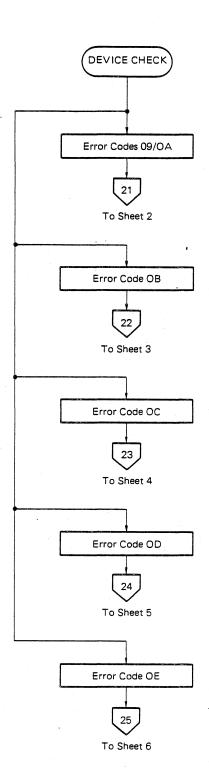

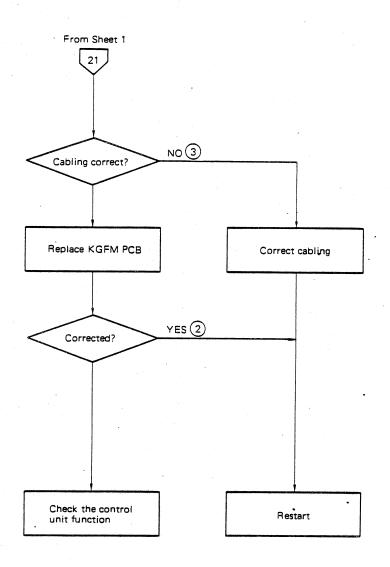

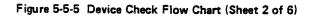

| 5-5-5      | Device Check Flow Chart (Sheet 1 of 6)             |

| 5-5-5      | Device Check Flow Chart (Sheet 2 of 6)             |

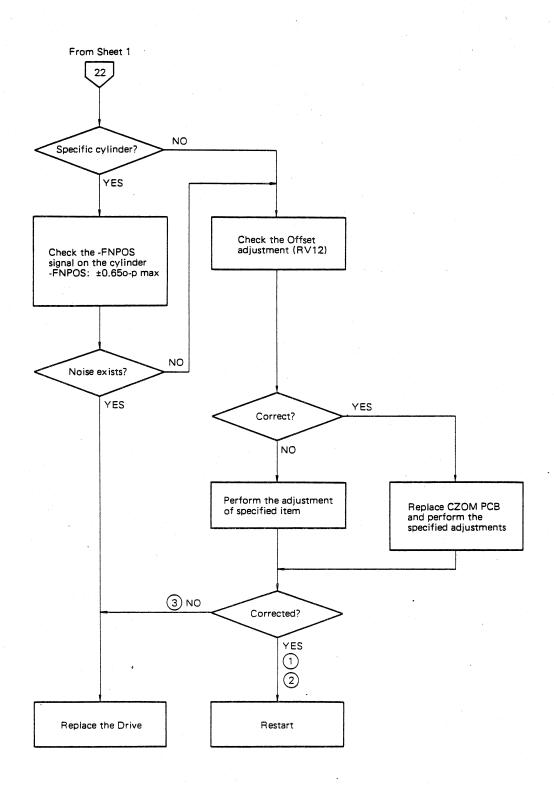

| 5-5-5      | Device Check Flow Chart (Sheet 3 of 6)             |

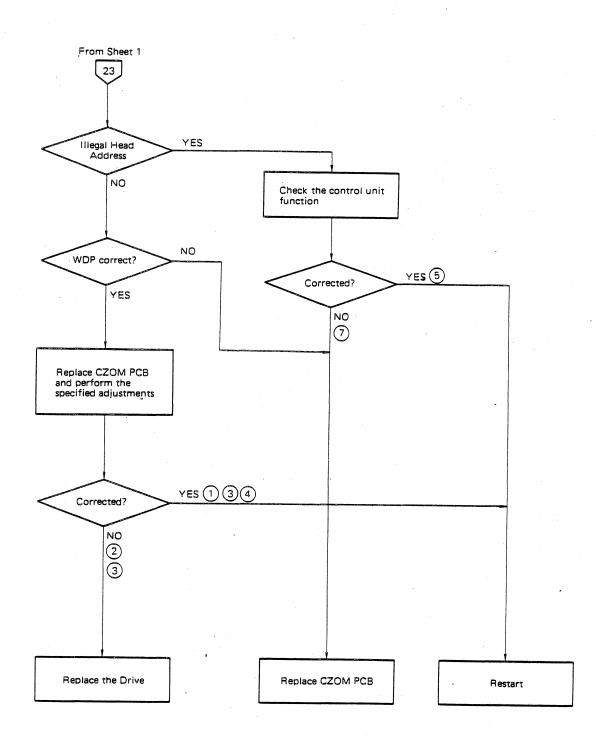

| 5-5-5      | Device Check Flow Chart (Sheet 4 of 6)             |

| 5-5-5      | Device Check Flow Chart (Sheet 5 of 6)             |

| 5-5-5      | Device Check Flow Chart (Sheet 6 of 6)             |

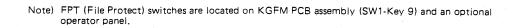

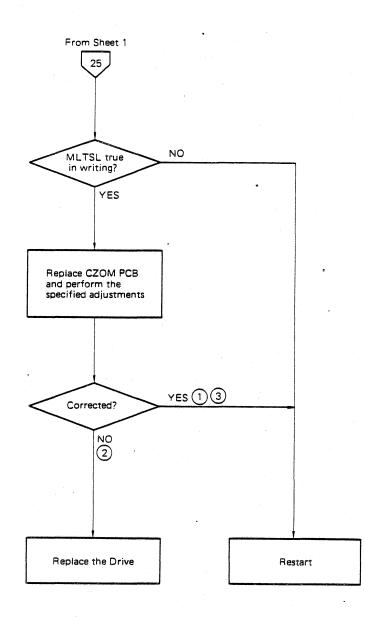

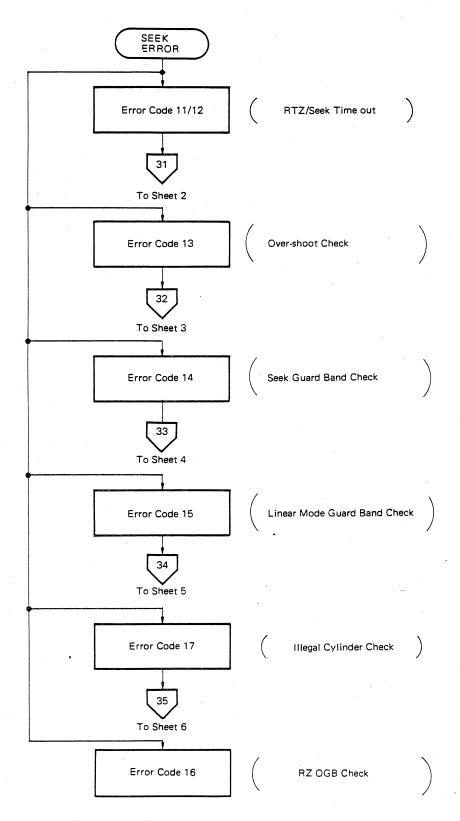

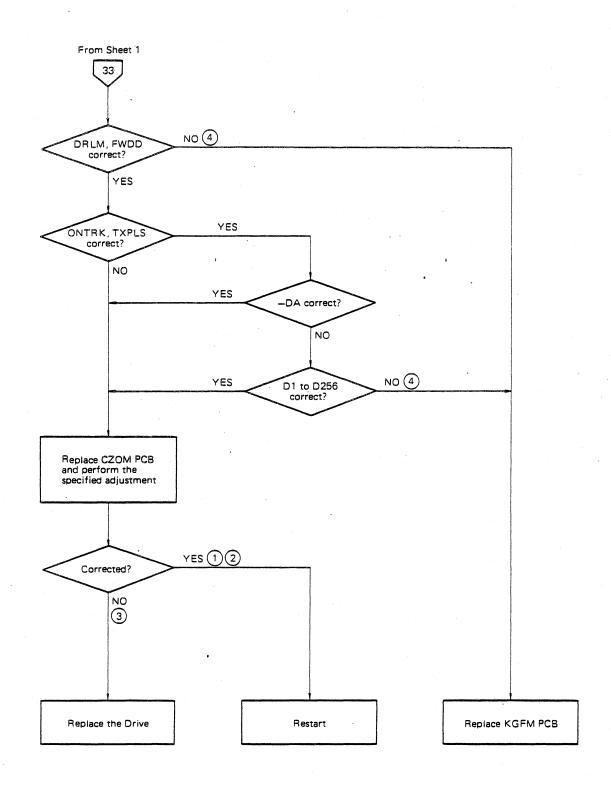

| 5-5-6      | Seek Error Flow Chart (Sheet 1 of 6)               |

|            |                                                    |

| 5-5-6      | Seek Error Flow Chart (Sheet 2 of 6 )              |

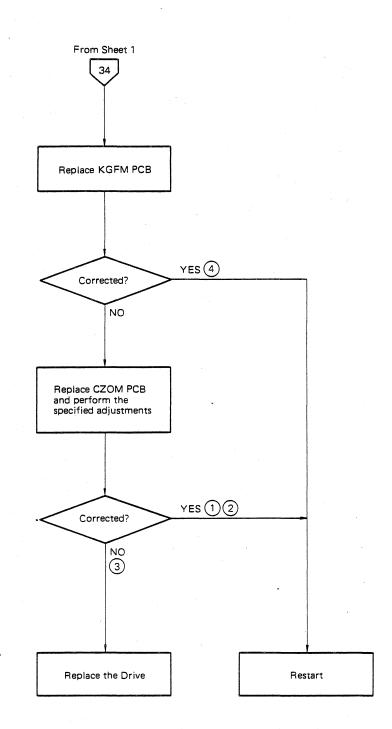

| 5-5-6      | Seek Error Flow Chart (Sheet 3 of 6 )              |

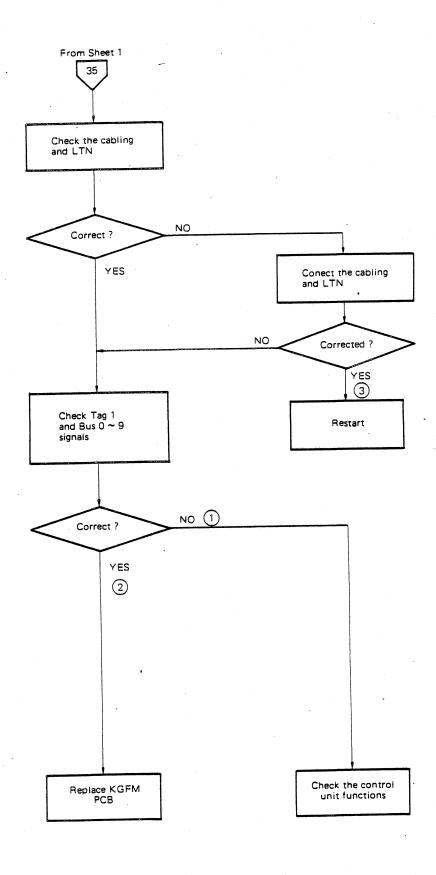

| 5-5-6      | Seek Error Flow Chart (Sheet 4 of 6) 5-26          |

| 5-5-6      | Seek Error Flow Chart (Sheet 5 of 6) 5-27          |

| 5-5-6      | Seek Error Flow Chart (Sheet 6 of 6) 5-28          |

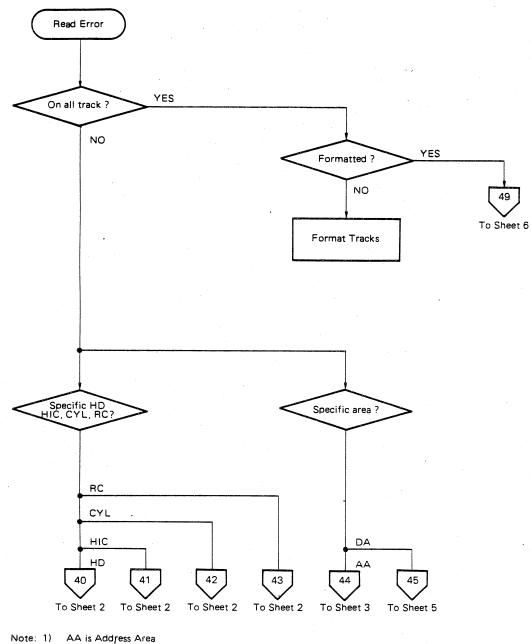

| 5-5-7      | Read Error Flow Chart (Sheet 1 of 6)               |

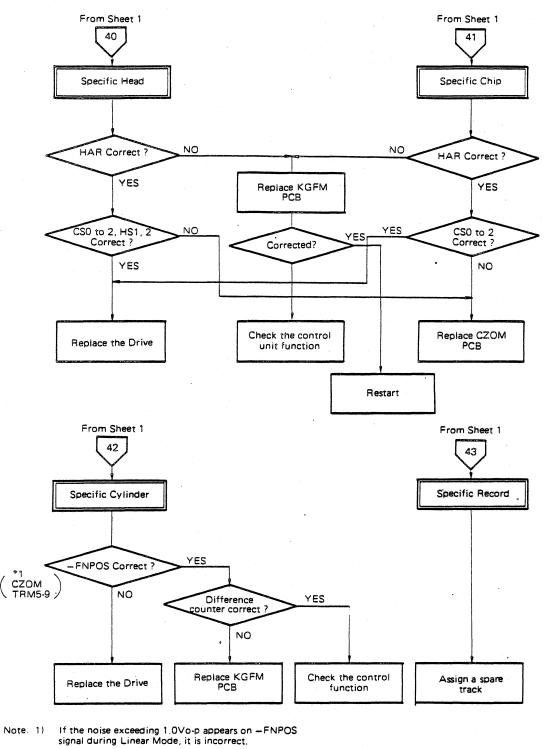

| 5-5-7      | Read Error Flow Chart (Sheet 2 of 6)               |

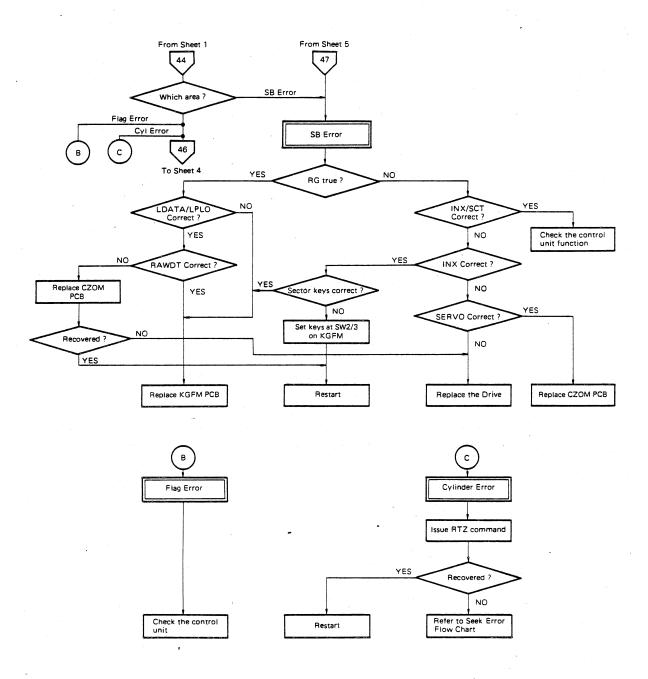

| 5-5-7      | Read Error Flow Chart (Sheet 3 of 6)               |

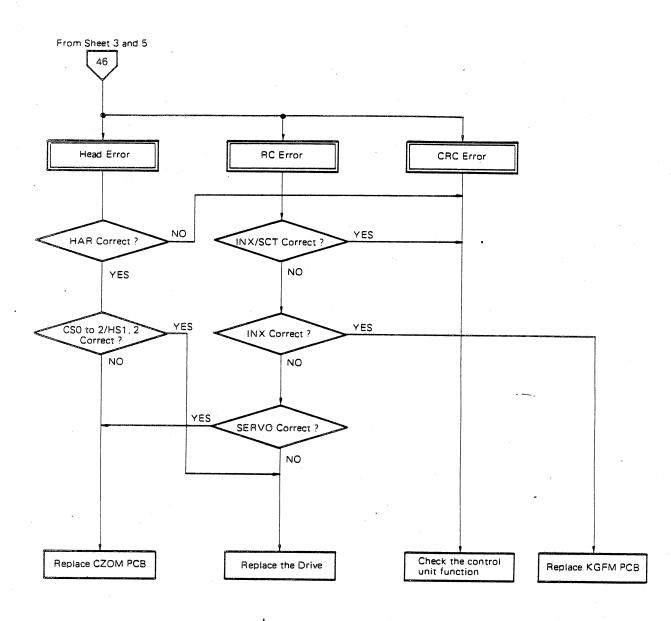

| 5-5-7      | Read Error Flow Chart (Sheet 4 of 6)               |

| 5-5-7      | Read Error Flow Chart (Sheet 5 of 6)               |

| 5-5-7      | Read Error Flow Chart (Sheet 6 of 6)               |

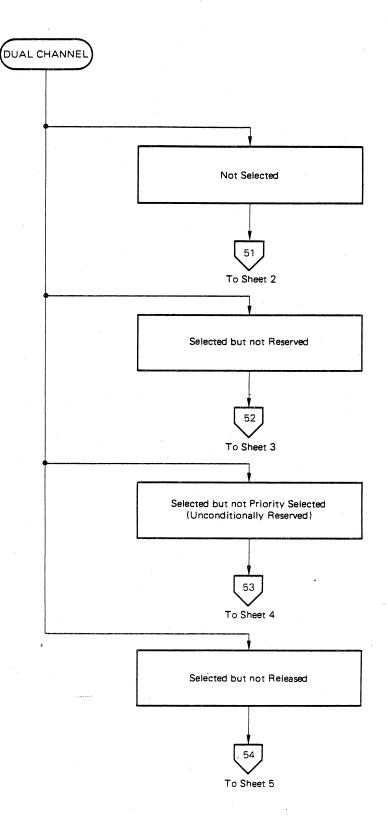

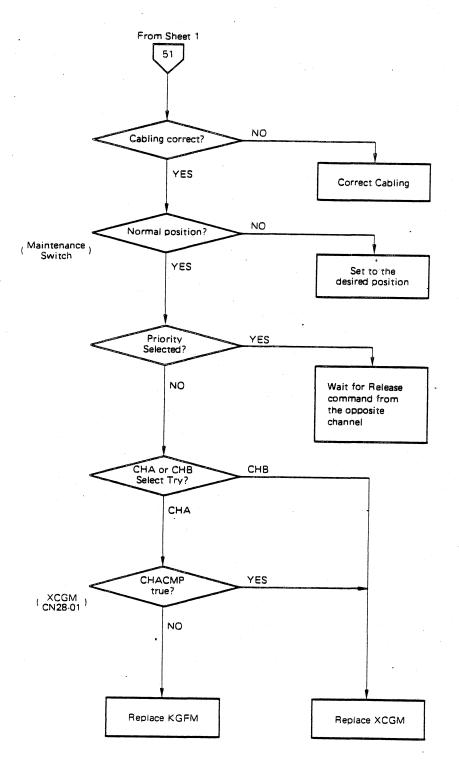

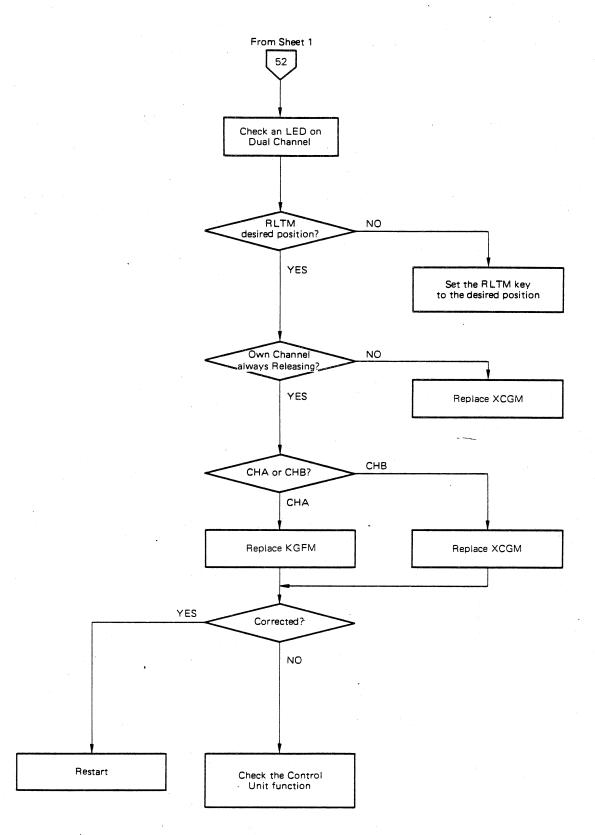

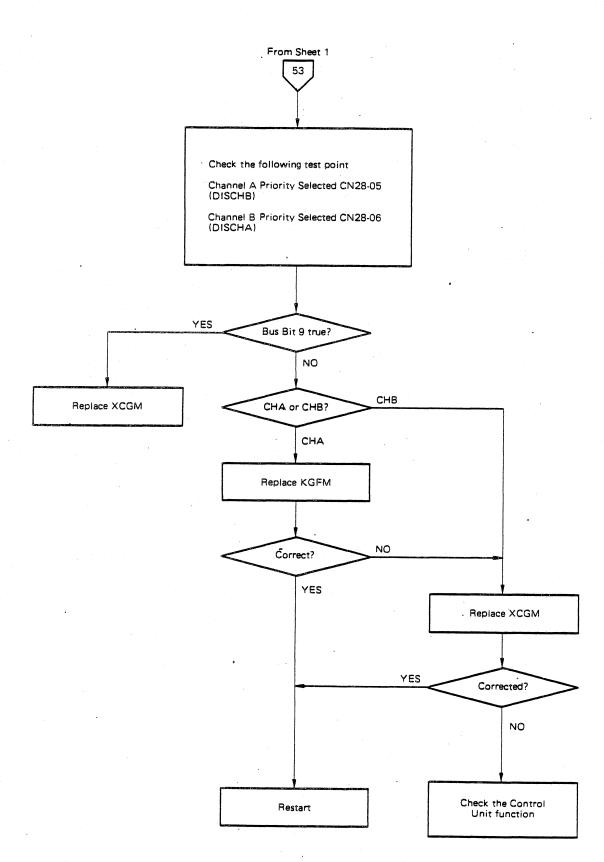

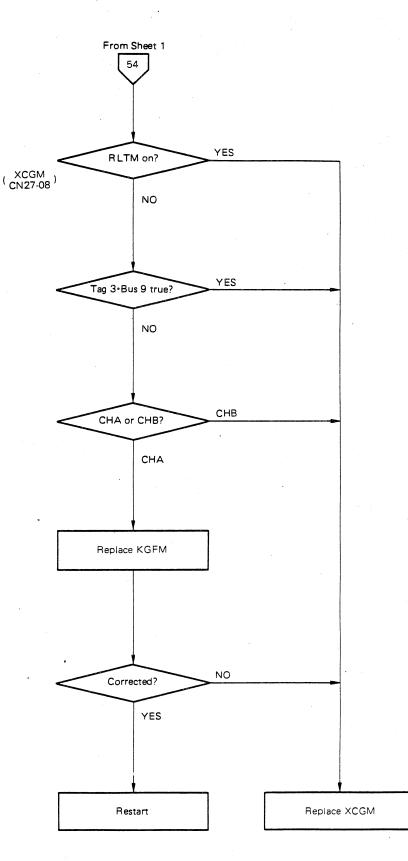

| 5-5-8      | Dual Channel Malfunction Flow Chart (Sheet 1 of 5) |

| 5-5-8      |                                                    |

|            | Dual Channel Malfunction Flow Chart (Sheet 2 of 5) |

| 5-5-8      | Dual Channel Malfunction Flow Chart (Sheet 3 of 5) |

| 5-5-8      | Dual Channel Malfunction Flow Chart (Sheet 4 of 5) |

| 5-5-8      | Dual Channel Malfunction Flow Chart (Sheet 5 of 5) |

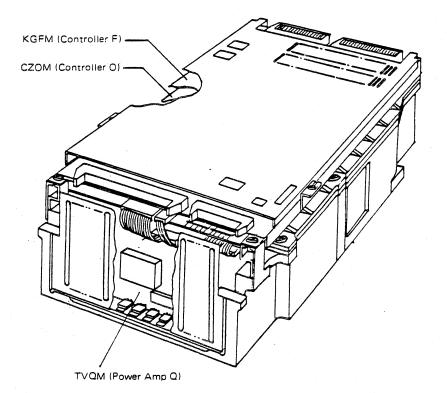

| 6-5-1      | PCB Assy. Arrangement                              |

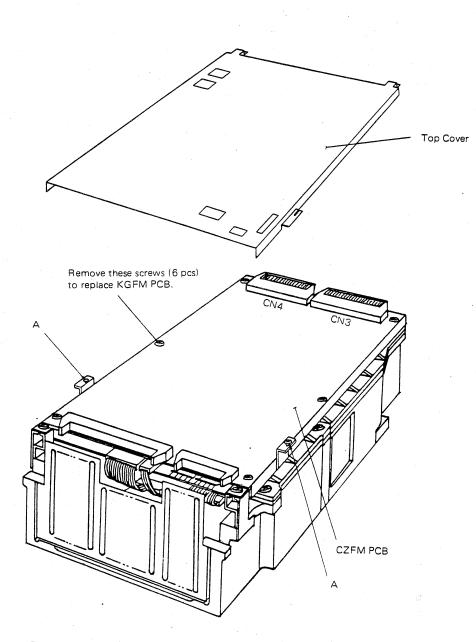

| 6-5-2      | KGFM PCB Assembly Replacement                      |

|            |                                                    |

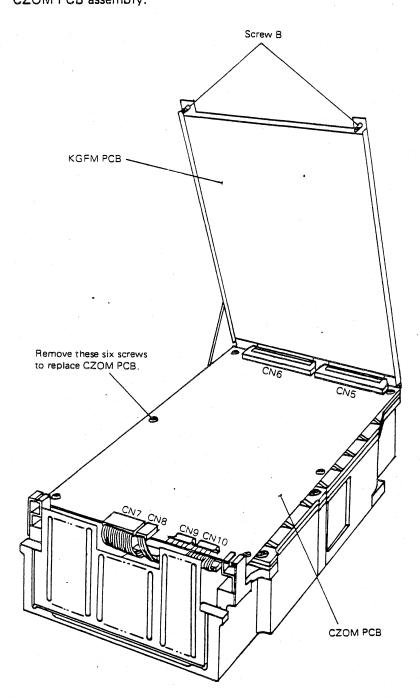

|            | CZOM PCB Replacement                               |

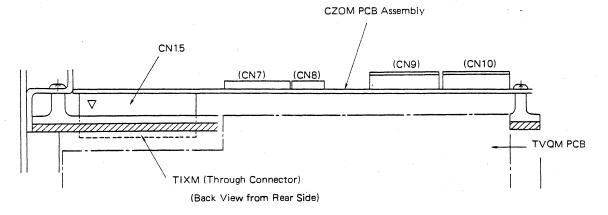

| 6-5-4      | TIXM Connection                                    |

| 6-5-5      | TVQM PCB Assembly Replacement                      |

|            |                                                    |

)

B03P-4760-0111A...01

xii

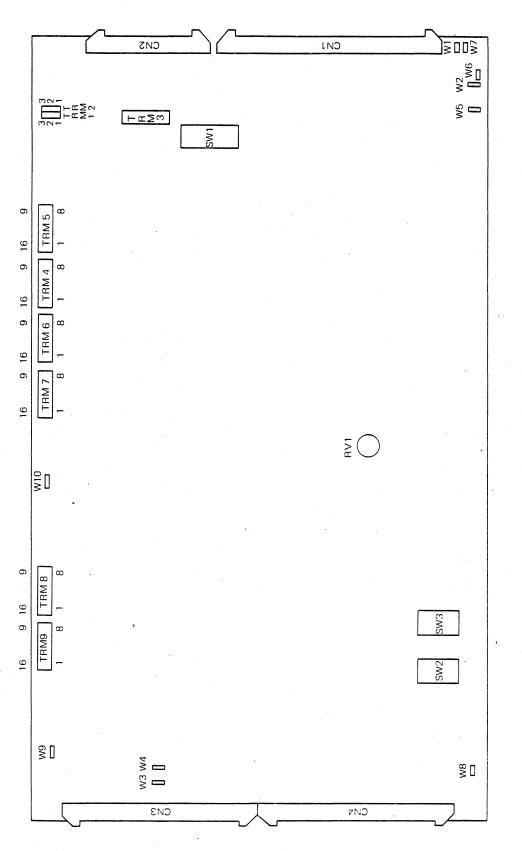

| 6-6-1      | KGFM PCB Assembly Test Points             |

|------------|-------------------------------------------|

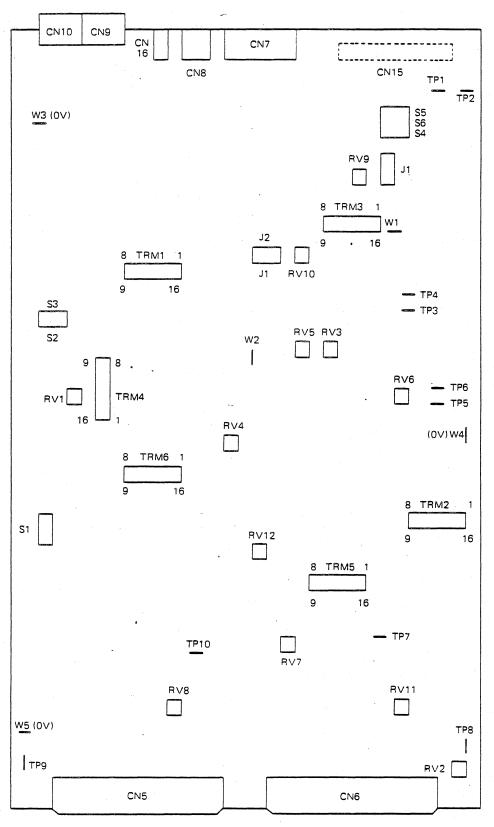

| 6-6-2      | CZOM PCB Assembly Test Points Arrangement |

| 6-6-3      | XCGM PCB Assembly Test Points             |

| 6-6-4      | Position Signal Gain Adjustment           |

| 6-6-5      | Positioning Time Adjustment               |

| 6-6-6      | Read Output Measurement 6-21              |

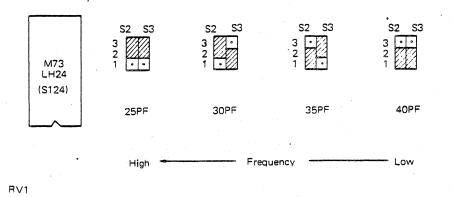

| 6-6-7      | PLO Free-run Frequency Adjustment         |

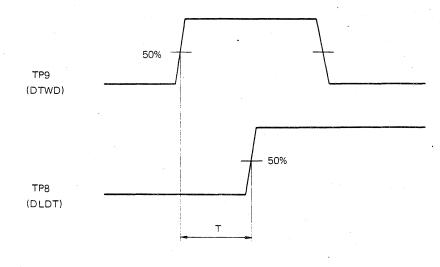

| 6-6-8      | Delayed Data One-shot Adjustment 6-23     |

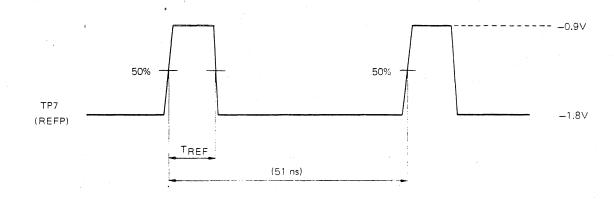

| 6-6-9      | Reference Pulse Adjustment 6-23           |

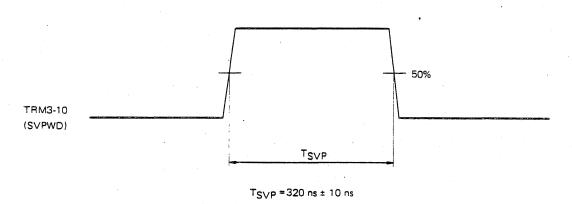

| 6-6-10     | Servo Pulse Window Adjustment             |

| 6-6-11     | PLO Single-shot Adjustment 6-23           |

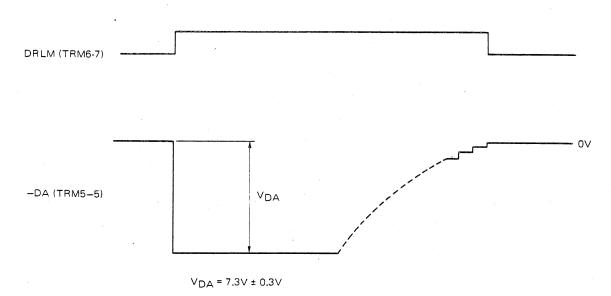

| 6-6-12     | DAC Output Adjustment                     |

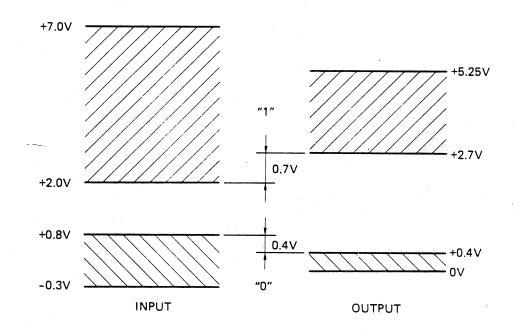

| 8-2-1      | Low Power Schottky IC Level               |

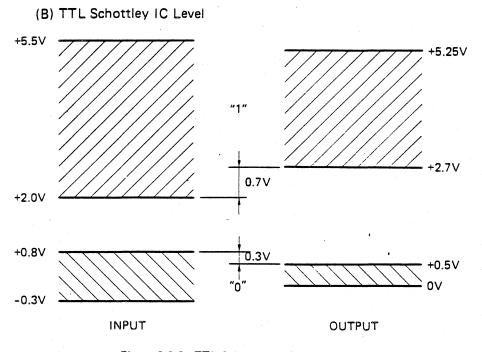

| 8-2-2      | TTL Schottky IC Level                     |

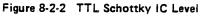

| 8-2-3      | ECL Logic Level                           |

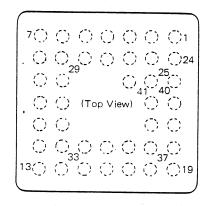

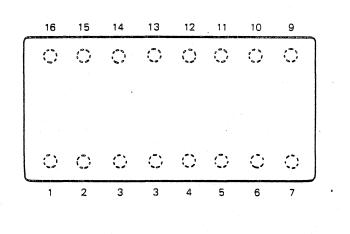

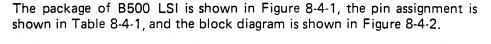

| 8-4-1      | B500 LSI Package                          |

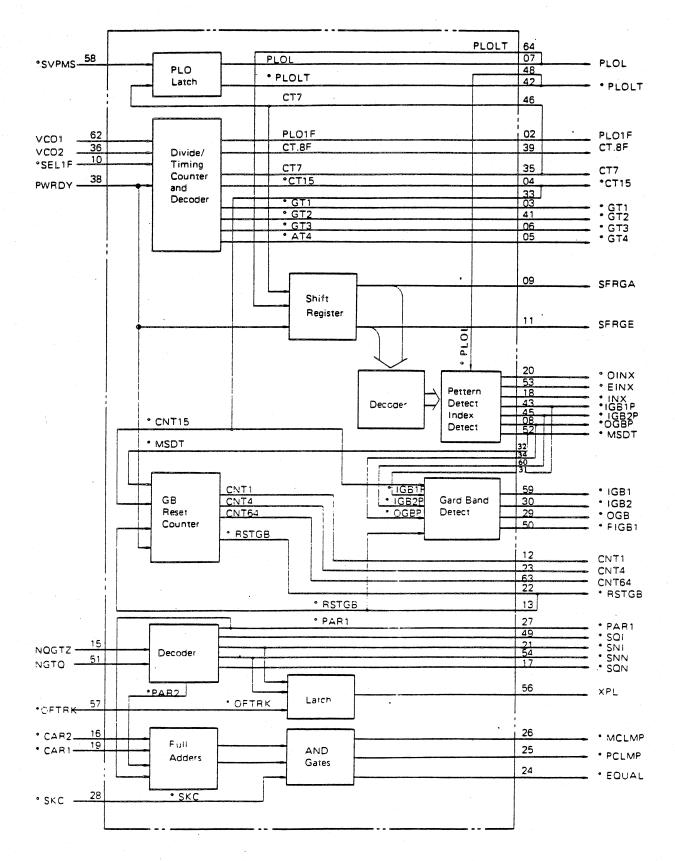

| 8-4-2      | MB15238C Block Diagram                    |

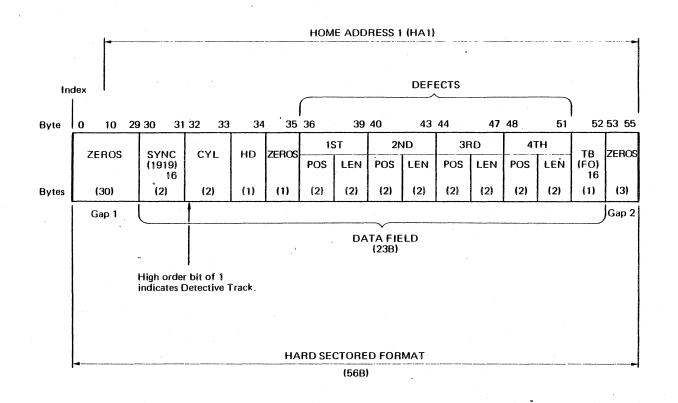

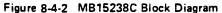

| 9-1        | M2331K/M2333K Micro Disk Drive            |

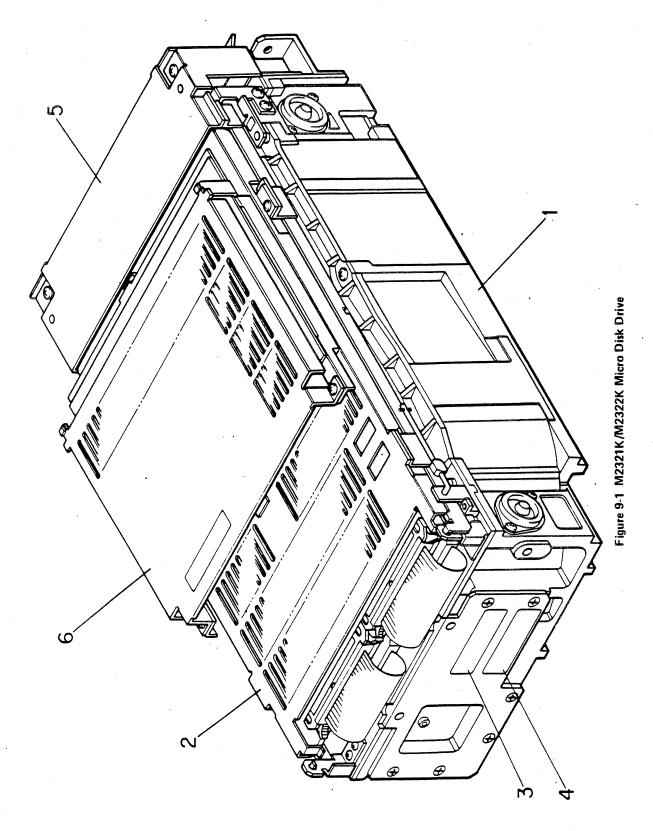

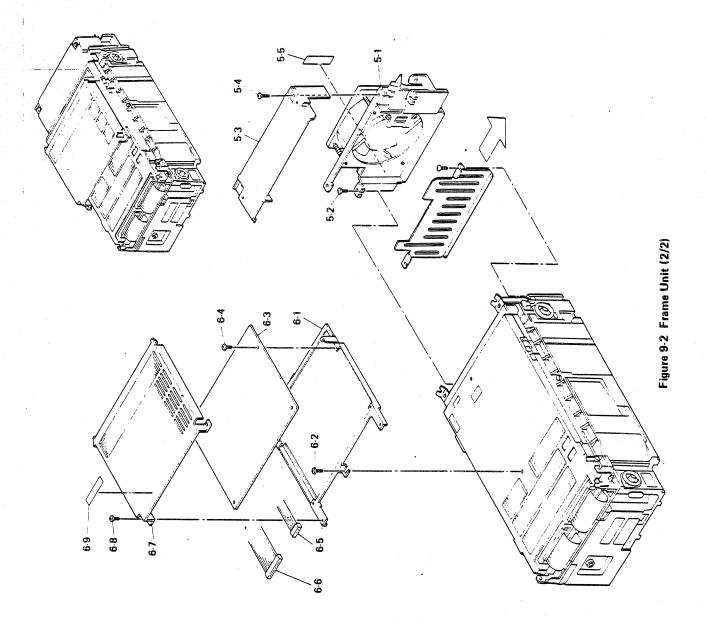

| 9-2        | Frame Unit (1/2)                          |

| 9-2<br>9-2 | Frame Unit (2/2)                          |

| J-2        | 11ame Umit (2/2/                          |

h

### **Tables**

| TABLE                                                                                                                      | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1-2-1<br>1-2-2<br>1-2-3<br>1-2-4<br>1-3-1                                                                                  | Basic Specifications1-2Physical Specifications1-2DC Power Requirement1-2Data Recording Specifications1-5Options1-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 1-3-2<br>1-3-3                                                                                                             | Specifications of fan units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| 2-3-1                                                                                                                      | Fault Indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| 3-4-1<br>3-7-1<br>3-7-2<br>3-7-3<br>3-7-4<br>3-7-5<br>3-7-6<br>3-7-7                                                       | Thermal Check Point3-10Disk Addressing3-37Tag 4/5 Enable3-38File Protect3-38Device Type3-39On-Side Switch3-39Sector Counting Keys3-40Commonly Used Sector Counting3-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| 4-3-1<br>4-5-1<br>4-5-2<br>4-5-3<br>4-5-4<br>4-5-5<br>4-5-6<br>4-5-6<br>4-5-7<br>4-5-8                                     | Index, IGB2, IGB1, and OGB Patterns4-12Tag/Bus Lines4-19Status Lines Determined by Tag 4/54-21Fault/Seek Error Status4-24Device Type Code4-24SN75110 Function Table4-37SN75107/75108 Function Table4-37"A" Cable Connectors4-40"B" Cable Connectors4-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |