Digital Equipment Corporation Maynard, Massachusetts

PDP-10 Maintenance Manual

# RP10 DISK PACK SYNCHRONIZER

Volume 1

DEC-10-H5EC-D (1)

# PDP-10 RP10 DISK PACK SYNCHRONIZER MAINTENANCE MANUAL VOLUME 1

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

1st Edition November 1969 2nd Printing May 1970 2nd Edition November 1970 3rd Edition August 1971

Copyright © 1969, 1970, 1971 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC FLIP CHIP DIGITAL PDP FOCAL COMPUTER LAB

# CONTENTS

# CHAPTER 1 GENERAL INFORMATION

| 1.1   | Introduction                  | 1-1 |

|-------|-------------------------------|-----|

| 1.2   | Specifications                | 1-1 |

| 1.2.1 | Physical                      | 1-1 |

| 1.2.2 | Environmental                 | 1-2 |

| 1.2.3 | Electrical                    | 1-2 |

| 1.2.4 | Performance                   | 1-3 |

| 1.3   | Interface Requirements        | 1-3 |

| 1.3.1 | RP10/RP01/02 Interface        | 1-3 |

| 1.3.2 | RP10/DF10 Interface           | 1-5 |

| 1.3.3 | RP10/I/O Interface            | 1-5 |

| 1.3.4 | Disk Pack/Disk Pack Interface | 1-6 |

| 1.4   | Equipment Supplied            | 1-8 |

| 1.5   | Reference Documents           | 1-8 |

| 1.6   | Glossary                      | 1-8 |

# CHAPTER 2 INSTALLATION

| 2.1   | General                         | 2-1 |

|-------|---------------------------------|-----|

| 2.2   | Unpacking                       | 2-1 |

| 2.2.1 | Special Handling                | 2-1 |

| 2.2.2 | Inspection                      | 2-1 |

| 2.2.3 | Power Requirements              | 2-1 |

| 2.3   | Installation Procedure          | 2-2 |

| 2.4   | Turn-On and Checkout Procedures | 2-4 |

# CHAPTER 3 OPERATION

| 3.1     | General                                                 | 3-1  |

|---------|---------------------------------------------------------|------|

| 3.2     | Controls and Indicators                                 | 3-1  |

| 3.3     | Operation                                               | 3-6  |

| 3.3.1   | Loading, Unloading, and Storage of RP01P/02P Disk Packs | 3-6  |

| 3.4     | Programming                                             | 3-7  |

| 3.4.1   | RP01/02 Disk Pack Characteristics                       | 3-7  |

| 3.4.2   | RP10 Programming                                        | 3-11 |

| 3.4.2.1 | DATAO Information                                       | 3-12 |

| 3.4.2.2 | DATAI Information                                       | 3-16 |

| 3.4.2.3 | CONO Information                                        | 3-17 |

| 3.4.2.4 | CONI Information                                        | 3-18 |

|         |                                                         |      |

# CONTENTS (Cont)

# CHAPTER 4 THEORY OF OPERATION

| 4.1     | General                              | 4-1  |

|---------|--------------------------------------|------|

| 4.2     | General Block Diagram Discussion     | 4-1  |

| 4.3     | Sequence of Operation                | 4-1  |

| 4.3.1   | Write Data or Read Data              | 4-2  |

| 4.3.2   | Write Headers and Data (Format)      | 4-4  |

| 4.3.3   | Local/Remote                         | 4-4  |

| 4.4     | RP10 Recording Technique             | 4-5  |

| 4.5     | RP01/02 Addressing Method            | 4-5  |

| 4.6     | RP10 Register Organization           | 4-6  |

| 4.7     | RP10 Registers                       | 4-6  |

| 4.7.1   | Assembly Register                    | 4-6  |

| 4.7.2   | Assembly Register Data Gate          | 4-7  |

| 4.7.3   | Condition Register                   | 4-10 |

| 4.7.4   | Data Address Register                | 4-13 |

| 4.7.5   | Longitudinal Parity Register         | 4-13 |

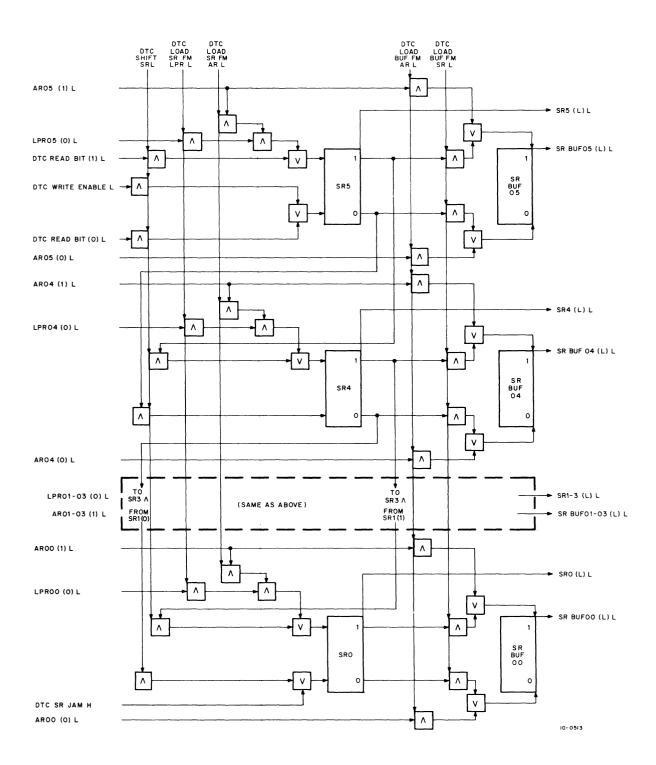

| 4.7.6   | Shift Register                       | 4-13 |

| 4.8     | RP10 Control Circuits                | 4-13 |

| 4.8.1   | Channel Control                      | 4-13 |

| 4.8.2   | Data Transfer Control                | 4-17 |

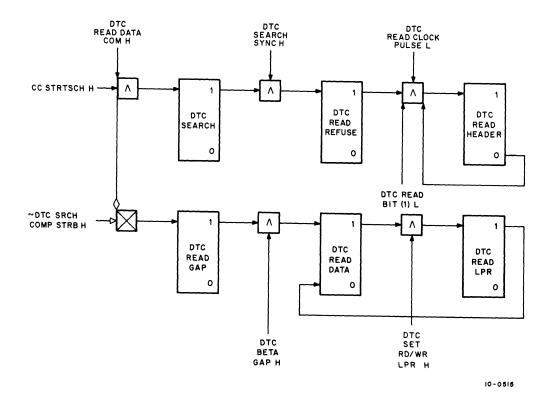

| 4.8.2.1 | Read Data                            | 4-17 |

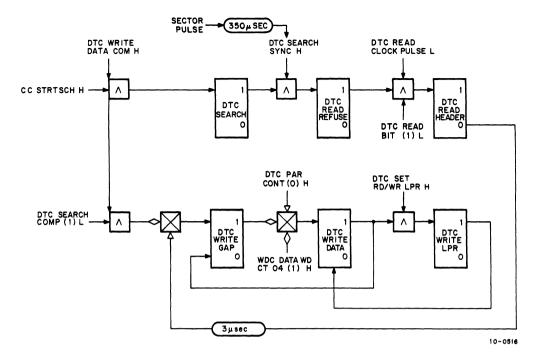

| 4.8.2.2 | Write Data                           | 4-19 |

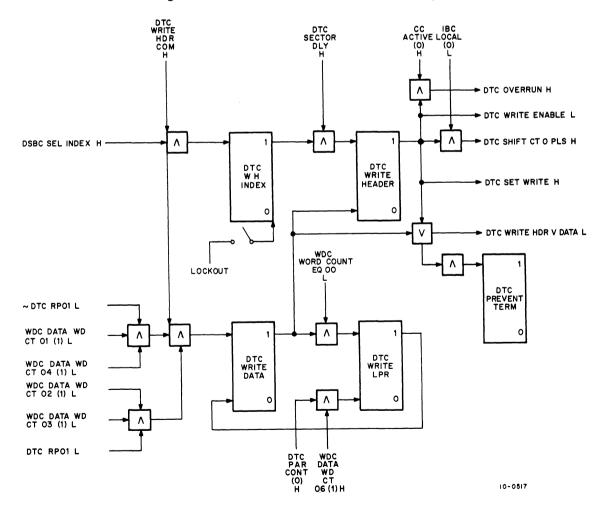

| 4.8.2.3 | Write Headers and Data               | 4-19 |

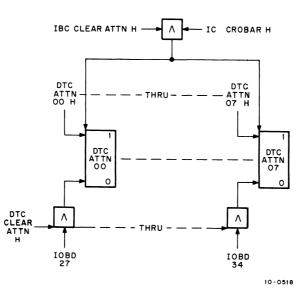

| 4.8.2.4 | Clear Attentions                     | 4-19 |

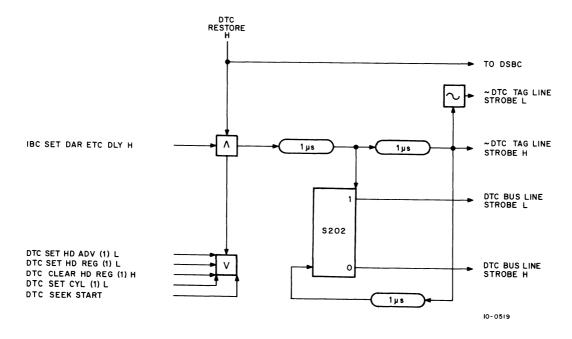

| 4.8.2.5 | Restore                              | 4-19 |

| 4.8.2.6 | Seek                                 | 4-22 |

| 4.8.3   | I/O Bus Control                      | 4-22 |

| 4.8.4   | RP10 Read Data Separator             | 4-23 |

| 4.9     | RP10 Counters                        | 4-28 |

| 4.9.1   | Sector Counters                      | 4-29 |

| 4.9.2   | Sector Counter Buffer                | 4-29 |

| 4.9.3   | Sector Counter Control Pulses        | 4-29 |

| 4.9.4   | Sector Counter Multiplexer           | 4-31 |

| 4.9.5   | Word Counters                        | 4-31 |

| 4.10    | RP10 Comparators                     | 4-34 |

| 4.10.1  | Header Compare and Designation Error | 4-34 |

| 4.11    | RP10 Data Flow                       | 4-34 |

| 4.11.1  | Starting                             | 4-34 |

| 4.11.2  | Recognizing Headers                  | 4-37 |

| 4.11.3  | Reading Data                         | 4-37 |

| 4.11.4  | Writing Data                         | 4-38 |

| 4.11.5  | Commanding the Drive                 | 4-38 |

| 4.11.6  | Reading Multiple Sectors             | 4-38 |

# **CONTENTS** (Cont)

| 4.11.7   | Loading Words      | 4-39 |

|----------|--------------------|------|

| 4.11.7.1 | Header Words       | 4-39 |

| 4.11.7.2 | Data Words         | 4-39 |

| 4.11.8   | Transferring Words | 4-39 |

| 4.11.8.1 | Write Header       | 4-39 |

| 4.11.8.2 | Write Data         | 4-39 |

| 4.11.9   | Writing Headers    | 4-39 |

| 4.11.10  | Generating Parity  | 4-39 |

| 4.11.11  | Terminating        | 4-40 |

# CHAPTER 5 MAINTENANCE

| 5.1     | Introduction                               | 5-1  |

|---------|--------------------------------------------|------|

| 5.2     | Preventive Maintenance                     | 5-1  |

| 5.2.1   | Preventive Maintenance Procedures          | 5-1  |

| 5.2.1.1 | Mechanical Checks                          | 5-1  |

| 5.2.1.2 | Test Equipment Required                    | 5-1  |

| 5.2.1.3 | Electrical Checks                          | 5-2  |

| 5.2.1.4 | Electronic Checks                          | 5-3  |

| 5.3     | Corrective Maintenance                     | 5-4  |

| 5.3.1   | General Corrective Procedures              | 5-4  |

| 5.3.2   | Diagnostic Testing                         | 5-5  |

| 5.3.2.1 | Vibration Tests                            | 5-5  |

| 5.3.3   | Adjustment Procedures                      | 5-5  |

| 5.3.3.1 | Read Data Separator Calibration            | 5-5  |

| 5.3.4   | General Troubleshooting Guides             | 5-9  |

| 5.3.4.1 | Disk Pack Compatibility                    | 5-9  |

| 5.3.4.2 | Proper Use of C.E. Packs                   | 5-9  |

| 5.3.4.3 | Search Errors                              | 5-10 |

| 5.3.4.4 | Parity Errors                              | 5-11 |

| 5.3.4.5 | Failure to Restore                         | 5-11 |

| 5.3.4.6 | Disk Pack Reliability Test Map Limitations | 5-11 |

| 5.3.4.7 | Cleaning                                   | 5-11 |

# CHAPTER 6 DRAWINGS

| 6.1 General | 6-1 |

|-------------|-----|

|-------------|-----|

# ILLUSTRATIONS

| Figure No | . Title                                                    | Art No. | Page |

|-----------|------------------------------------------------------------|---------|------|

| 1-1       | DEC Type RP10 Disk Pack Synchronizer                       |         | 1-1  |

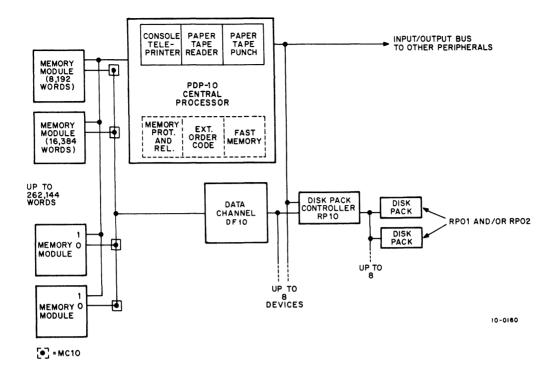

| 1-2       | Typical PDP-10 System with RP10 Disk Pack Synchronizer     | 10-0160 | 1-2  |

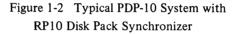

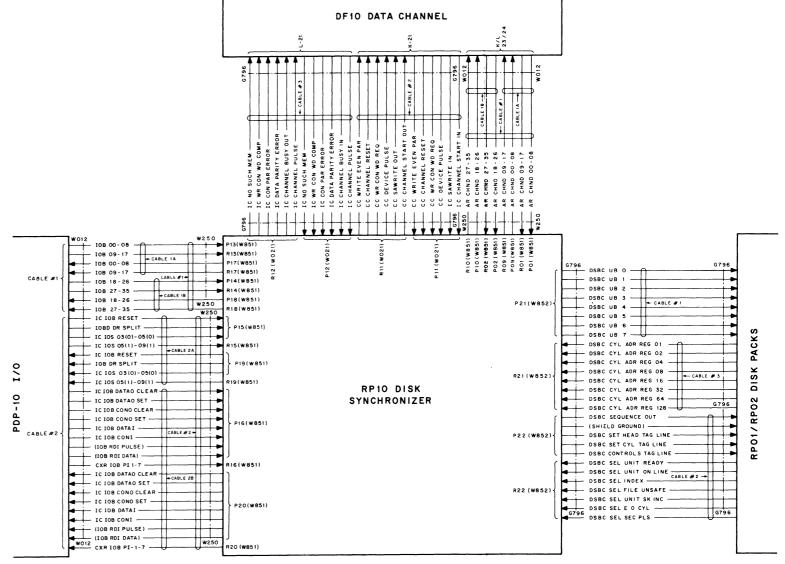

| 1-3       | RP10/DF10/RP01/RP02/I/O Interface                          | 10-0162 | 1-4  |

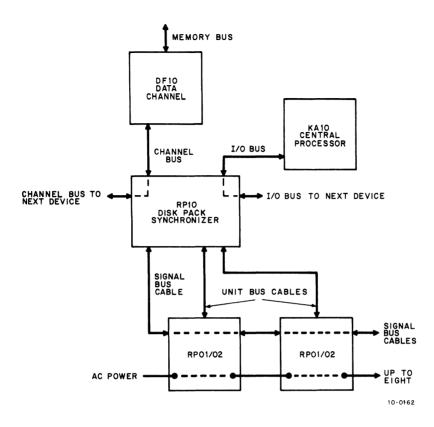

| 1-4       | RP10/RP01/02 Electrical Interface                          | 10-0163 | 1-4  |

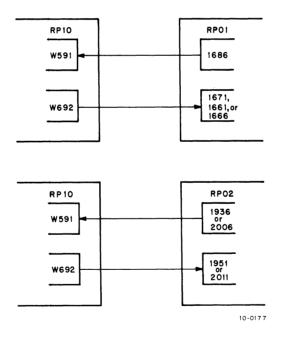

| 1-5       | RP10 Interface Wiring Diagram                              | 10-0177 | 1-6  |

| 1-6       | RP10 Cable Diagram                                         | 10-0161 | 1-7  |

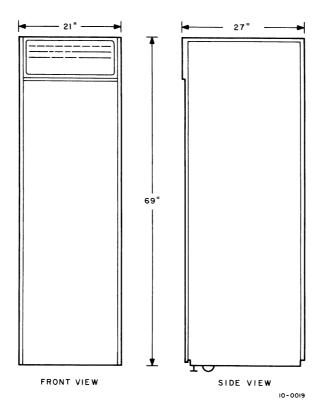

| 2-1       | RP10 Overall Dimensions                                    | 10-0019 | 2-4  |

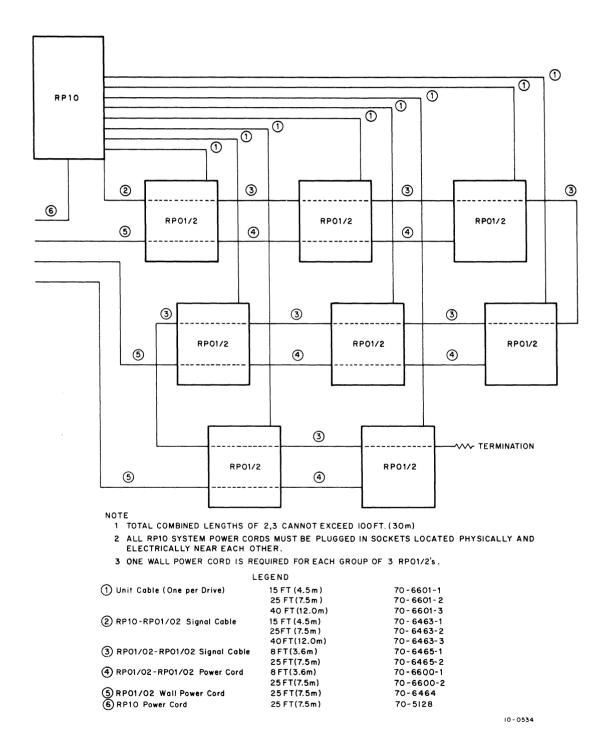

| 2-2       | RP10-RP01/RP02 Signal and Power Connections                | 10-0534 | 2-5  |

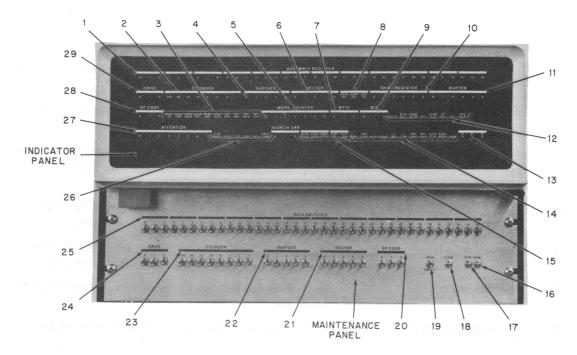

| 3-1       | RP10 Controls and Indicators                               |         | 3-1  |

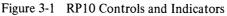

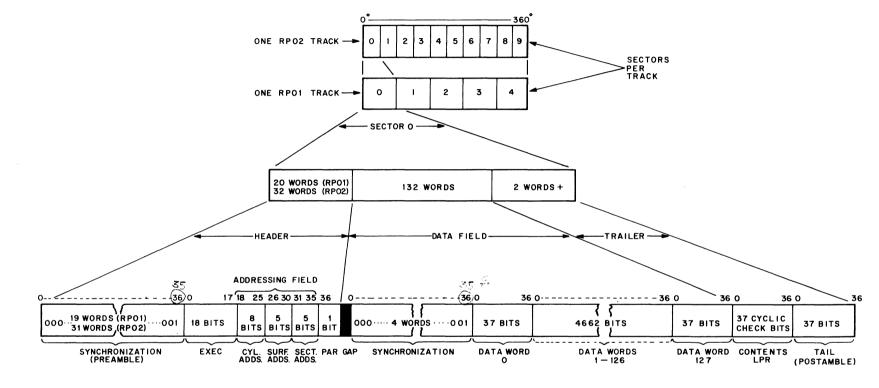

| 3-2       | RP01/RP02 Disk Pack Characteristics                        |         | 3-8  |

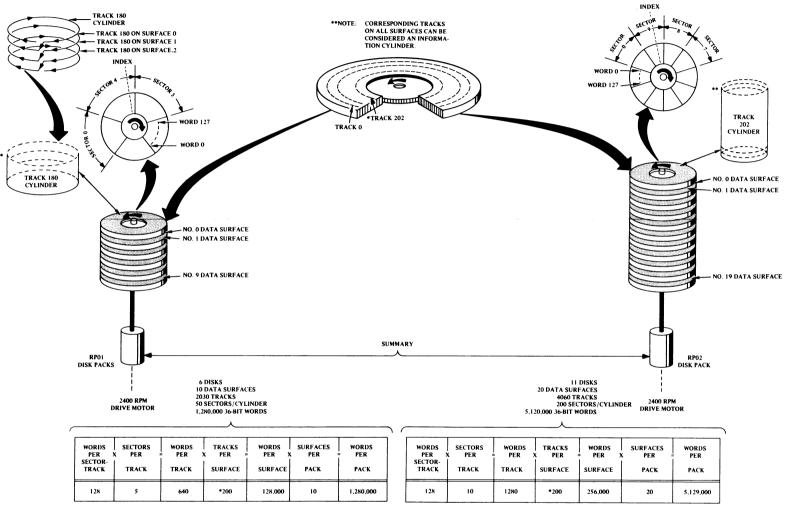

| 3-3       | RP10/RP01/RP02 Data Control Signals                        | 10-0165 | 3-9  |

| 3-4       | RP01/RP02 Data Format                                      | 10-0166 | 3-10 |

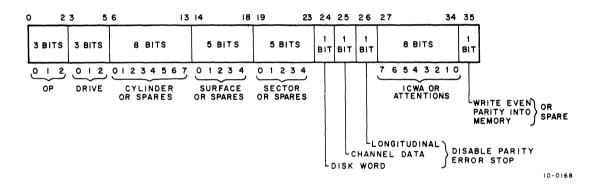

| 3-5       | DATAO Instruction Word Format                              | 10-0168 | 3-12 |

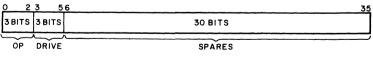

| 3-6       | Position Instruction Word                                  |         | 3-12 |

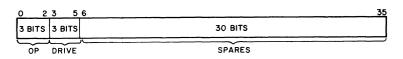

| 3-7       | Recalibrate Instruction Word                               | 10-0170 | 3-13 |

| 3-8       | Read Data Instruction Word                                 |         | 3-13 |

| 3-9       | Write Data Instruction Word                                |         | 3-14 |

| 3-10      | Write Header and Data Instruction Word                     |         | 3-15 |

| 3-11      | Clear Attentions Instruction Word                          |         | 3-15 |

| 3-12      | No Op Instruction Word                                     |         | 3-16 |

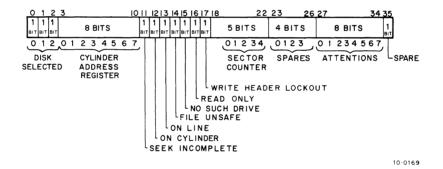

| 3-13      | DATAI Instruction Word Format                              | 10-0169 | 3-17 |

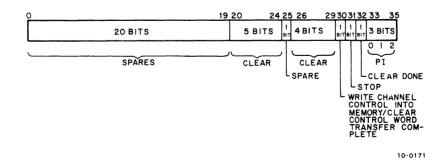

| 3-14      | CONO Instruction Word Format                               | 10-0171 | 3-17 |

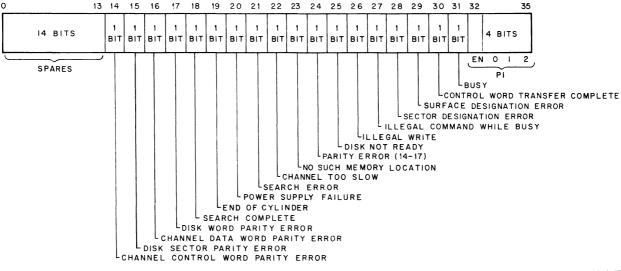

| 3-15      | CONI Instruction Word Format                               | 10-0167 | 3-19 |

| 4-1       | RP10 General Block Diagram                                 | 10-0159 | 4-2  |

| 4-2       | <b>RP10</b> Active and Inactive Functions                  | 10-0108 | 4-3  |

| 4-3       | RP10 Register Organization                                 | 10-0507 | 4-7  |

| 4-4       | RP10 Assembly Register Simplified Block Diagram            | 10-0508 | 4-9  |

| 4-5       | RP10 Assembly Register Data Gate, Simplified Block Diagram | 10-0509 | 4-10 |

| 4-6       | RP10 Condition Register, Block Diagram                     |         | 4-11 |

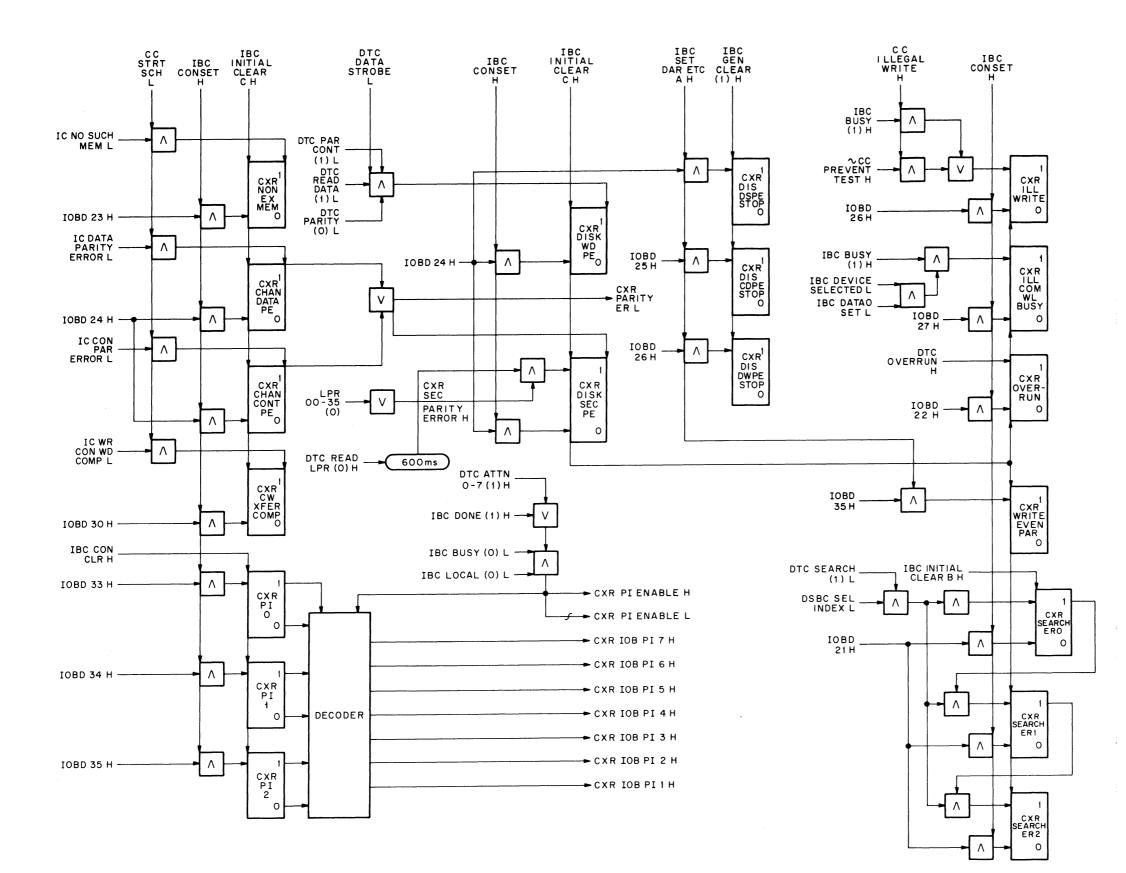

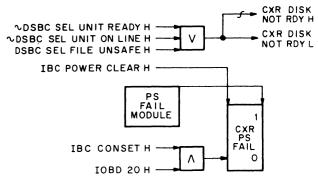

| 4-7       | RP10 Data Address Register, Block Diagram                  | 10-0511 | 4-14 |

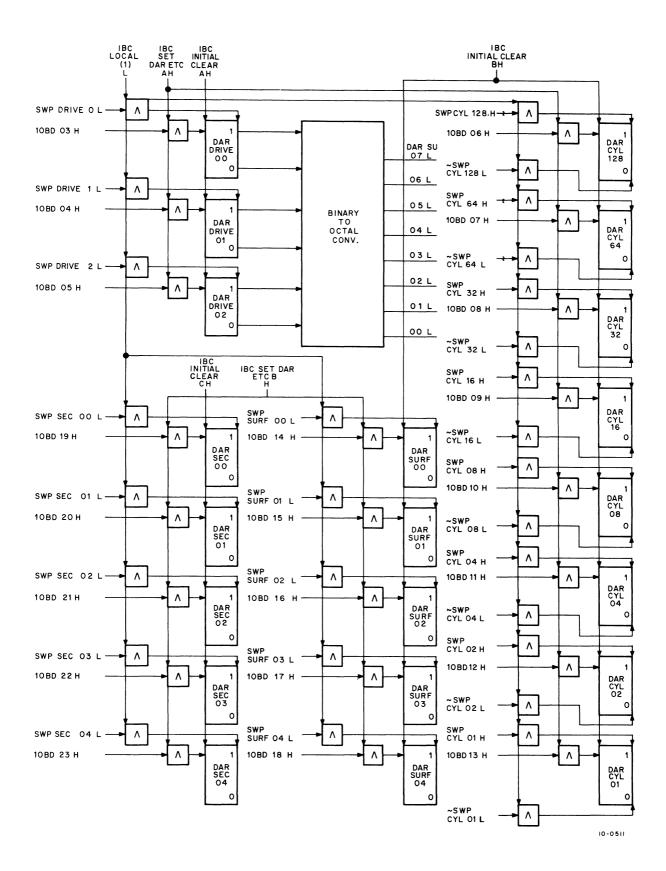

| 4-8       | RP10 Longitudinal Parity Register, Block Diagram           | 10-0512 | 4-15 |

| 4-9       | RP10 Shift Register, Block Diagram                         | 10-0513 | 4-16 |

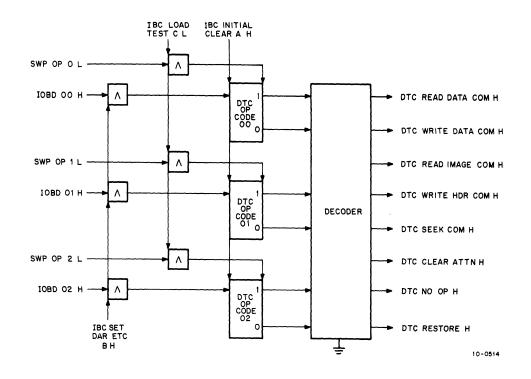

| 4-10      | DTC OP Decoding, Block Diagram                             | 10-0514 | 4-18 |

| 4-11      | DTC Read Data Command, Block Diagram                       | 10-0515 | 4-18 |

| 4-12      | DTC Write Data Command, Block Diagram                      | 10-0516 | 4-20 |

| 4-13      | DTC Write Headers and Data Command, Block Diagram          | 10-0517 | 4-20 |

| 4-14      | DTC Clear Attentions Command, Block Diagram                | 10-0518 | 4-21 |

| 4-15      | DTC Restore Command, Block Diagram                         | 10-0519 | 4-21 |

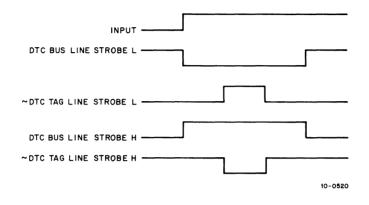

| 4-16      | Tag and Bus Line Strobe Waveforms                          | 10-0520 | 4-22 |

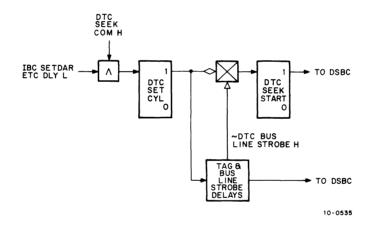

| 4-17      | DTC Seek Command, Block Diagram                            | 10-0535 | 4-22 |

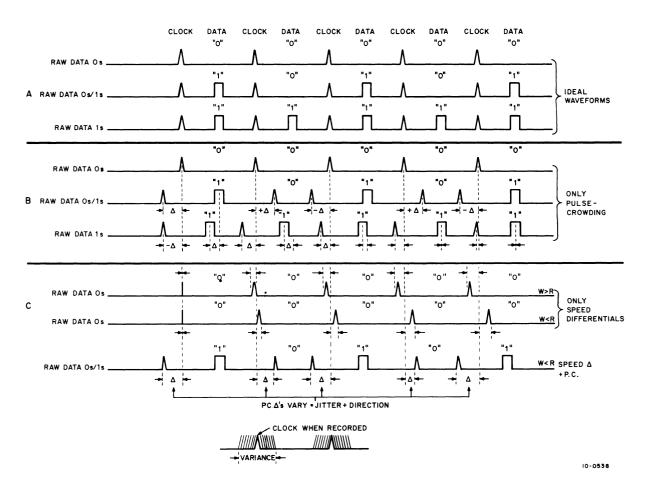

| 4-18      | Sources of Jitter in Disk Playback                         | 10-0538 | 4-24 |

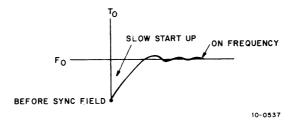

| 4-19      | VFO Startup Waveform                                       | 10-0537 | 4-25 |

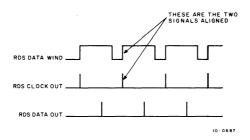

| 4-20      | RDS DATA WIND Waveform                                     | 10-0687 | 4-25 |

\* Denotes figures revised since the November 1970 printing.

# **ILLUSTRATIONS** (Cont)

| Figure N | lo. Title                                                    | Art No. | Page |

|----------|--------------------------------------------------------------|---------|------|

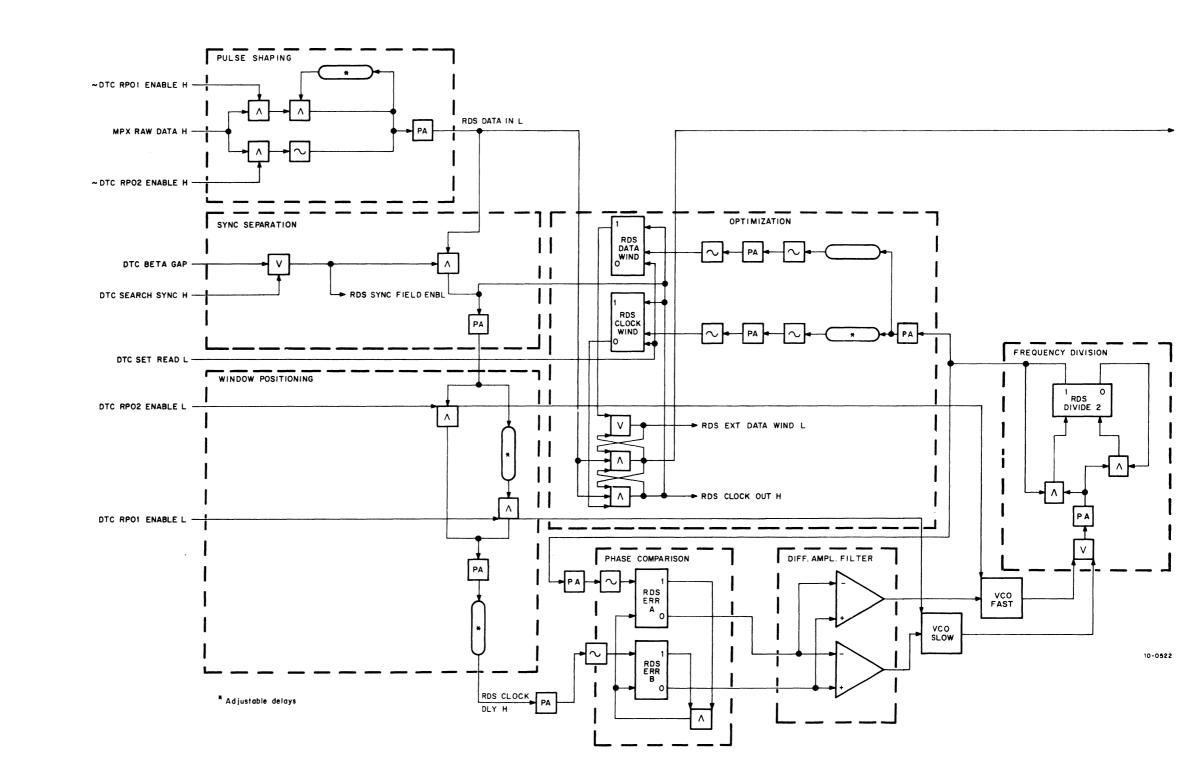

| * 4-21   | RP10 Read Data Separator, Block Diagram                      | 10-0522 | 4-27 |

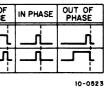

| 4-22     | RDS Error Flops Waveforms                                    | 10-0523 | 4-28 |

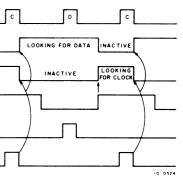

| * 4-23   | Optimum Window Generation Waveforms                          | 10-0524 | 4-28 |

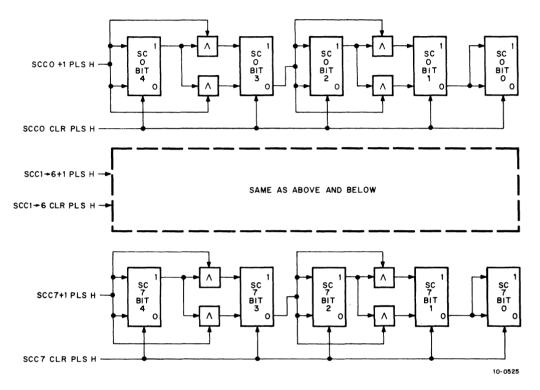

| 4-24     | RP10 Sector Counter, Block Diagram                           | 10-0525 | 4-29 |

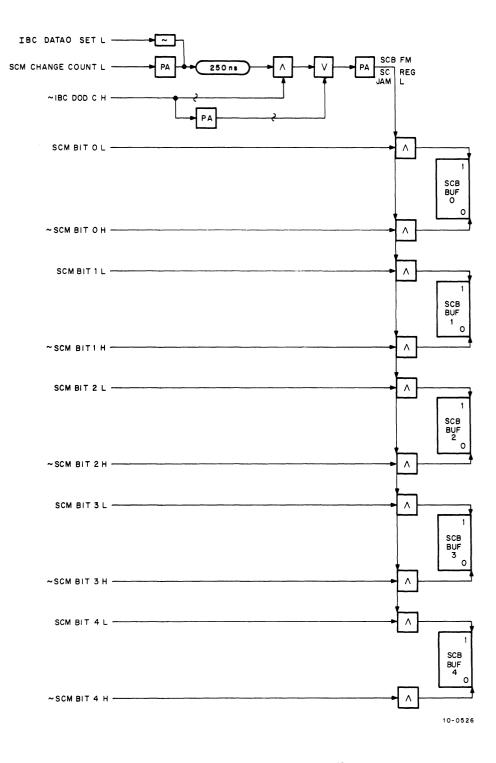

| * 4-25   | RP10 Sector Counter Buffer, Block Diagram                    | 10-0526 | 4-30 |

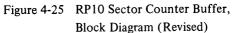

| 4-26     | RP10 Sector Counter Control Pulses, Simplified Block Diagram | 10-0527 | 4-31 |

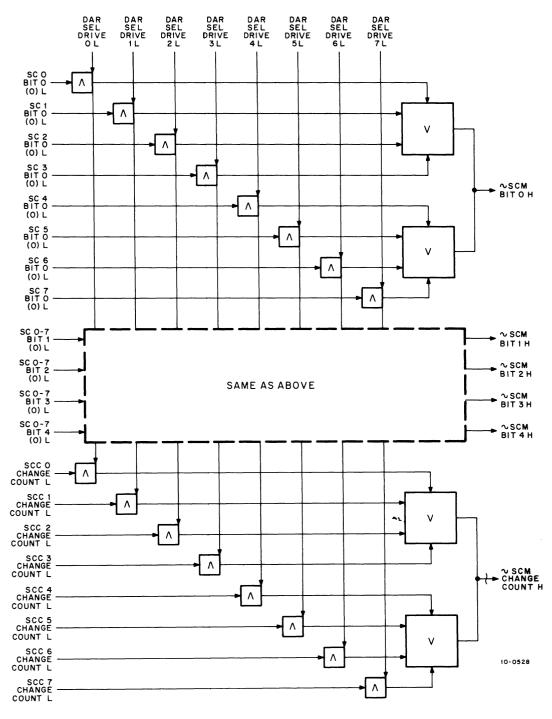

| 4-27     | RP10 Sector Counter Multiplexer, Block Diagram               | 10-0528 | 4-32 |

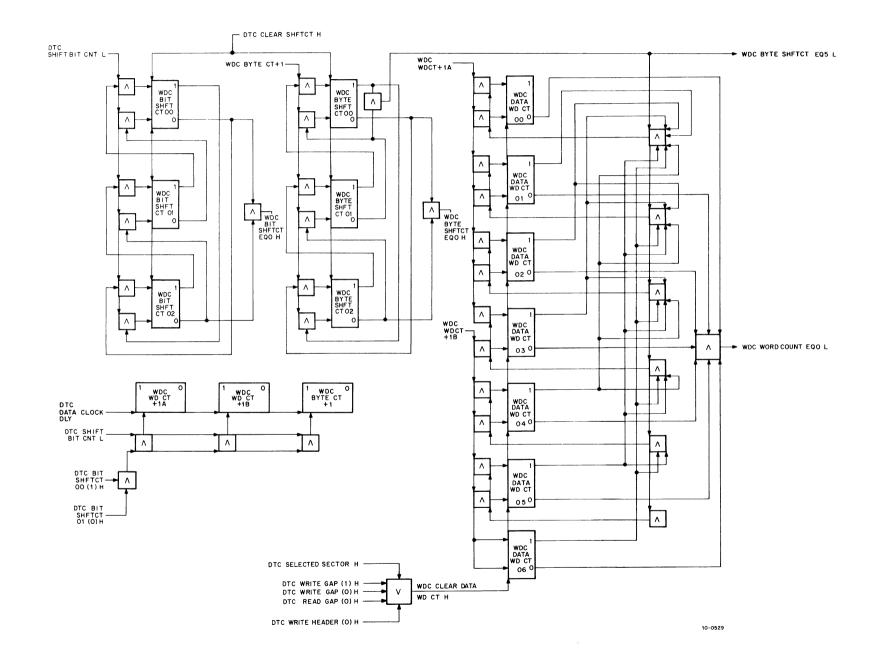

| * 4-28   | RP10 Word Counters Block Diagram                             | 10-0529 | 4-33 |

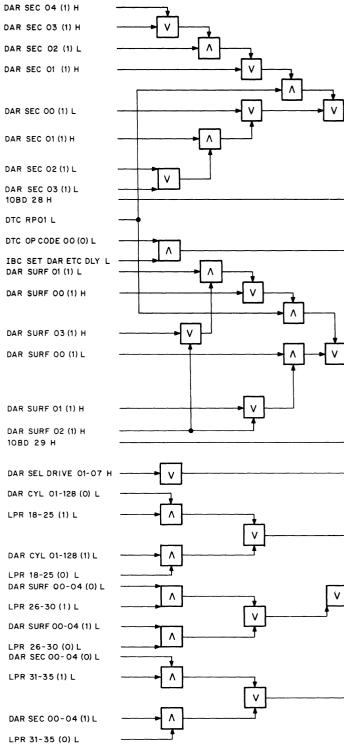

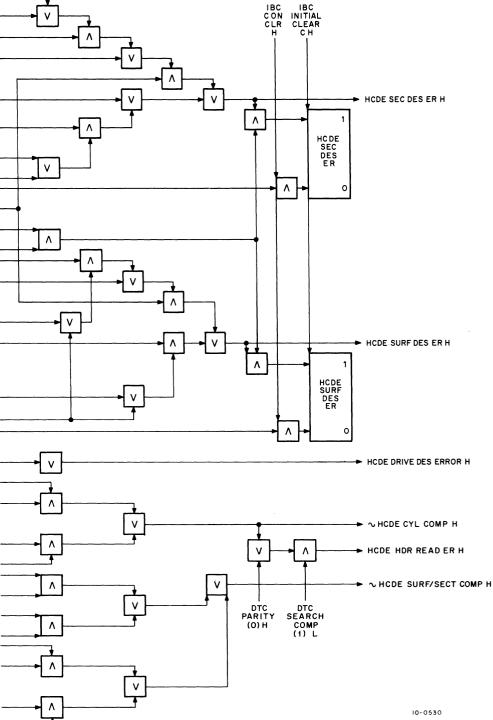

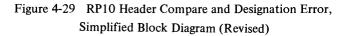

| * 4-29   | RP10 Header Compare and Designation Error,                   |         |      |

|          | Simplified Block Diagram                                     | 10-0530 | 4-35 |

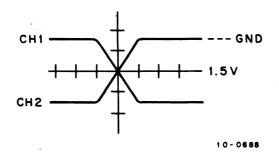

| **5-1    | RDS Waveform No. 1                                           | 10-0688 | 5-7  |

| **5-2    | RDS Waveform No. 2                                           | 10-0689 | 5-7  |

# TABLES

| Table I | No. Title                                                 | Page |

|---------|-----------------------------------------------------------|------|

| 1-1     | RP01/02 Features Compatible with RP10 Logic Configuration | 1-3  |

| 1-2     | RP10/RP01 and RP02 Interface Chart                        | 1-5  |

| 1-3     | RP10/DF10 Interface Chart                                 | 1-5  |

| 1-4     | RP10/I/O Interface Chart                                  | 1-6  |

| 1-5     | Equipment Supplied                                        | 1-8  |

| 2-1     | RP01/RP02 Power Requirements                              | 2-2  |

| 3-1     | RP10 Controls and Indicators                              | 3-2  |

| 4-1     | Data Transfer Control Commands                            | 4-36 |

| 5-1     | Test Equipment Required                                   | 5-2  |

| 5-2     | Power Supply Output Checks                                | 5-2  |

| 5-3     | Critical Delay Modules                                    | 5-3  |

| 5-4     | DF10 Voltage Margins                                      | 5-3  |

| 5-5     | RP10 Voltage Margins                                      | 5-4  |

| 6-1     | RP10 Engineering Drawings                                 | 6-1  |

|         |                                                           |      |

<sup>\*</sup>Denotes figures revised since the November 1970 printing. \*\*Denotes figures added since the November 1970 printing.

# Chapter 1 General Information

### 1.1 INTRODUCTION

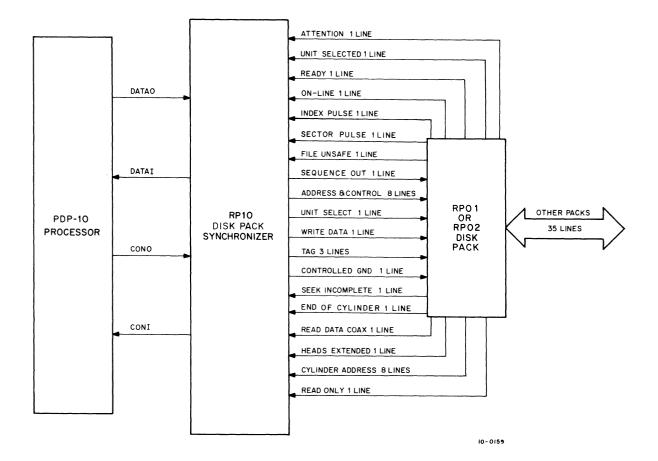

The RP10 Disk Pack Synchronizer, shown in Figure 1-1, provides the interface logic between the DF10 Data Channel and as many as eight of the DEC Type RP01 or RP02 Disk Pack Drives. The RP10 operates under control of the PDP-10 I/O Bus and, in turn, controls the RP01 or RP02 (see Figure 1-2). These units provide the PDP-10 computer with on-line auxiliary storage for between 1.28 and 40 million 36-bit words. Direct access to core memory is obtained through the DF10 Data Channel.

The RP10 is housed in a 19-in. cabinet containing eight module racks. Indicator and switch panels are located on the top front of the unit. These comprise monitoring and switch register facilities for data, address, and control. The unit contains the standard margin check voltage bracket, +10 and -15 Vdc power supplies and power control, and built-in cooling fans.

The RP10 is shipped complete and factory tested including all interconnecting cabling to the PDP-10 and the RP01/02 Disk Packs. Two types are available: the RP10-A for 60-Hz operation, and the RP10-B for 50-Hz operation.

## 1.2 SPECIFICATIONS

Physical, environmental, electrical, and performance specifications for the RP10 Disk Pack Synchronizer are given in the paragraphs that follow.

#### 1.2.1 Physical

#### Dimensions

| Width  | = | 21 in. |

|--------|---|--------|

| Height | = | 69 in. |

| Depth  | = | 27 in. |

| Weight | = | 390 lb |

#### Service Access Dimensions

Front = 36 in. Rear = 36 in.

Figure 1-1 DEC Type RP10 Disk Pack Synchronizer

# 1.2.2 Environmental

The RP10 operates under normal conditions of humidity, shock, and vibration.

#### **Recommended Ambient**

Operating Temperature =  $60^{\circ}$  to  $95^{\circ}$ F Storage Temperature =  $40^{\circ}$  to  $110^{\circ}$ F Humidity = 20% to 80% Relative Wet Bulb =  $78^{\circ}$ F (Max)

#### 1.2.3 Electrical

Power Requirement at Line Cord

115 Vac, 1-phase, 60 Hz @ 8.0A

Power/Heat Dissipation = 9000W/3000 Btu/Hr

Internal Power - From 4 self-contained Type 728 Power Supplies and one self-contained Type 844 Power Control.

+10 Vdc -15 Vdc

Unit Cable Lengths

50 ft (Max)

#### 1.2.4 Performance

#### Word Transfer Time

When synchronizing RP01 = 30  $\mu$ s When synchronizing RP02 = 15  $\mu$ s

#### **Positioning Time**

Track-to-track = 20 ms Average = 50 ms Maximum = 80 ms

#### Latency Time

Average = 12.5 ms Maximum = 25 ms

#### **1.3 INTERFACE REQUIREMENTS**

The RP10 Synchronizer is designed to interface with any of the RP01/02 Disk Pack options listed in Table 1-1. Figure 1-3 is the Interface Block Diagram for the system. A complete description of the RP01/02 is contained in the vendor manuals for the Disk Drives. These manuals are supplied with each piece of peripheral equipment.

| Logic Configuration                                                                                |                              |  |

|----------------------------------------------------------------------------------------------------|------------------------------|--|

| Feature                                                                                            | Variations                   |  |

| Input Voltage and Frequency 208/230 Vac<br>±10%, 60 Hz ±1/2 Hz<br>220/380 Vac<br>±10%, 50 Hz ±2 Hz |                              |  |

| NOTE<br>All drives in a given system must be driven by<br>the same voltage and the same frequency. |                              |  |

| Recording Density (bit cell<br>time)RP01 = 800 ns<br>RP02 = 400 ns                                 |                              |  |

| Number of Drives                                                                                   | RP01 = 1 - 8<br>RP02 = 1 - 8 |  |

| NOTE                                                                                               |                              |  |

| May be intermixed.                                                                                 |                              |  |

Table 1-1

RP01/02 Features Compatible with RP10

Logic Configuration

# 1.3.1 RP10/RP01/02 Interface

There are two cable assemblies through which the RP10 connects to the RP01 or RP02 Disk Pack (see Figures 1-4 and 1-5); these assemblies and their functions are listed in Table 1-2. The electrical specification of the RP10/RP01/02 interface is shown in Figure 1-4.

Figure 1-3 RP10/DF10/RP01/RP02/I/O Interface

Figure 1-4 RP10/RP01/02 Electrical Interface

| Between |         |                                                                                                                                                                                                                                                       |            |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| RP10    | RP01/02 | Function                                                                                                                                                                                                                                              | Cable Type |

| P/R-21  | J3      | Address and Control Bus Lines<br>Cylinder Address Bus Lines                                                                                                                                                                                           | G796-G796  |

| P/R-22  | J5      | Tag lines, Unit Select, Write Data,<br>+36 Vdc in, Controlled Ground,<br>'Attention', Unit Selected, Ready,<br>On-Line, Index Pulse, Sector Pulse,<br>File Unsafe, Seek Incomplete, End<br>of Cylinder, Read Data, Read Only,<br>Write Current Sense. | G796-G796  |

Table 1-2RP10/RP01 and RP02 Interface Chart

The RP10 feeds the Disk Pack with eight multifunction address and control bus lines, three tag lines, a unit select line, a write data line, sequence out, +5V to terminator, and controlled ground. The Disk Pack feeds the RP10 with 'attention', ready, on-line, index pulse, sector pulse, file unsafe, seek incomplete, end of cylinder, read data coax, eight cylinder address lines, read only, and selected unit sector pulse.

### 1.3.2 RP10/DF10 Interface

There are three cable assemblies through which the RP10 connects to the DF10 Data Channel (see Figures 1-5 and 1-6). These assemblies and their functions are listed in Table 1-3.

| Between |           | E                |            |

|---------|-----------|------------------|------------|

| RP10    | DF10      | Function         | Cable Type |

| P/R-1/2 | K/L-31/32 | Chan Cable No. 1 | W250-W012  |

| P/R-11  | K-21      | Chan Cable No. 2 | G796-G796  |

| P/R-12  | L-21      | Chan Cable No. 3 | G796-G796  |

|         |           |                  |            |

Table 1-3**RP10/DF10** Interface Chart

### 1.3.3 RP10/I/O Interface

There are two cable assemblies through which the RP10 connects to the PDP-10 I/O Bus (see Figures 1-5 and 1-6). These cable assemblies are listed in Table 1-4; the signals they carry are also included.

| Be                  | tween   |                                                                                                  |            |

|---------------------|---------|--------------------------------------------------------------------------------------------------|------------|

| RP10                | I/O Bus | Function                                                                                         | Cable Type |

| P/R-13/<br>14/17/18 | Cable 1 | IOB 00-35                                                                                        | W250-W012  |

| P/R-15/<br>16/19/20 | Cable 2 | IOB Reset, IOBD DR SPLIT, IC<br>IOS 03-09, DATAO, DATAI, CONO,<br>CONI, RD1PLS, RD1 DATA, PI 1-7 | W250-W012  |

Table 1-4RP10/I/O Interface Chart

# 1.3.4 Disk Pack/Disk Pack Interface

Two cable assemblies run serially between all Disk Pack Units. These cables carry sequence out plus all signal and control interconnections between the RP10 and the first Disk Pack. The sequence out from the RP10 is relayed to the next drive when this drive is up to speed and is drawing its running current (not more than 5A, RP01, or 7A, RP02).

Figure 1-5 RP10 Interface Wiring Diagram

10 - 0161

Figure 1-6 RP10 Cable Diagram

# 1.4 EQUIPMENT SUPPLIED

Table 1-5 lists the equipment supplied with the RP10 Disk Pack Synchronizer.

# Table 1-5 **Equipment Supplied**

| Quantity<br>Per<br>Equipment | Description         | Part Type No.   | Quantity<br>Per<br>Equipment | Description                       | Part Type No.                                         |

|------------------------------|---------------------|-----------------|------------------------------|-----------------------------------|-------------------------------------------------------|

| 1                            | Synchronizer        | RP10            | 1                            | Cable G796 to G796                | C-IA-7005469-13                                       |

| 2                            | Cables W250 to W012 | D-IA-7005459-12 | 1                            | Cable G796 to G796                | C-IA-7005469-6                                        |

| 5                            | Cables W250 to W012 | D-IA-7005459-24 | 1                            | Cable G796 to G796                | C-IA-7005469-7                                        |

| 2                            | Cables W250 to W012 | D-IA-7005459-15 | 1                            | Cable, Grounding                  |                                                       |

| 1                            | Cable W250 to W012  | D-IA-7005459-8  | 1 set                        | Spare Modules                     |                                                       |

| 2                            | Cables W250 to W012 | D-IA-7005459-11 | 1 set                        | Diagnostic Tapes                  | MAINDEC 10-D5OB<br>MAINDEC 10-D5MA<br>MAINDEC 10-D5NB |

| 2                            | Cables G796 to G796 | C-IA-7005469-10 | 1 ea.                        | Maintenance Manual<br>(2 volumes) | DEC-10-H5EB-D                                         |

| 1                            | Cable G796 to G796  | C-IA-7005469-2  | 1 set                        | Engineering Drawings              |                                                       |

### 1.5 REFERENCE DOCUMENTS

The following documents supplement the information contained in this manual:

PDP-10 System Reference Manual DF10 Data Channel Maintenance Manual PDP-10 Site Preparation Guide PDP-10 Interface Manual Vendor Manual for RP01/RP02 Disk Pack Drive

This material is available from the nearest DEC Field Office or from: Digital Equipment Corporation Direct Mail Department 146 Main Street Maynard, Massachusetts 01754

# 1.6 GLOSSARY

The abbreviations used throughout this manual are defined in Volume II of this manual.

# Chapter 2 Installation

### 2.1 GENERAL

This chapter contains information required for installation of the RP10 Disk Pack Synchronizer. The installation procedures are not complex because the RP10 is shipped complete and factory tested. When the equipment is received, all modules are in place and, all intra-bay cabling has been installed. The unit has been tested extensively while operating as part of a standard PDP-10 System. Turn-on and checkout procedures are included here-in to confirm operation of the equipment after it has been installed.

The equipment rack should be located as near as possible to the DF10 Data Channel, preferably next to the DF10 frame. Bolt the equipment rack to the main rack in four places using the hardware provided. Cable lengths and the location of the RP01/RP02 drives are the major factors governing placement of the RP10.

#### 2.2 UNPACKING

The following paragraphs describe the RP10 unpacking procedures.

#### 2.2.1 Special Handling

No special handling procedures are required for the RP10 beyond the normal care afforded any piece of scientific equipment of comparable size and weight. However, particular care should be exercised in the use of cranes or hoists to prevent damage to the unit.

#### 2.2.2 Inspection

On receipt of the equipment, inspect it for visible damage such as dents and abrasions that may have occurred in transit. Inspect the logic modules for foreign matter that may have lodged in them during shipment. Any damage should be reported immediately to both the Carrier and Digital Equipment Corporation. Check the contents of the carton with the shipping document and with Table 1-5 of this handbook. Immediately report any omissions or incorrect parts to Digital Equipment Corporation.

#### 2.2.3 Power Requirements

The RP10 is equipped with self-contained power supplies and power control. The +10 Vdc and -15 Vdc requirements of the unit are provided by four DEC Type 728 Power Supplies and a DEC Type 844 Power Control. Modifications for accommodating either 50- or 60-Hz operation are made within the basic unit. These are designated as RP10-A for 60-Hz and RP10-B for 50-Hz operation. Power is supplied from an 8A, 115 Vac, single-phase source. The RP01/02 Drives require a three-phase line. Power requirements per phase are listed in Table 2-1.

| Type of Drive | Number of Drives |     |        |

|---------------|------------------|-----|--------|

|               | 1-3              | 4-6 | 7 or 8 |

| RP01          | 8A               | 16A | 23A    |

| RP02          | 12A              | 24A | 36A    |

# Table 2-1**RP01/RP02** Power Requirements

#### NOTE

Three-phase power is required for from one through any number of drives. Each unit is a single-phase device but is connected on a phase rotation basis.

PDP-10 Systems operate from three-phase, Y-connected, 4-wire plus earth ground power mains. Standard voltages are  $115/200 \text{ Vac} \pm 10\%$ , 60 Hz  $\pm 1/2$  Hz and 230/400 Vac  $\pm 10\%$ , 50 Hz  $\pm 1/2$  Hz. Other common voltages can also be accommodated. A system earth ground connection must be supplied through the power cords in addition to the ground bus requirement.

The RP10 is supplied with terminal lugs, a 3-wire cord, and in North America, a 5-wire Hubbell #3521 male plug (mates with Hubbell #3520). One wall power cord is required for every RP01/02.

Terminal lugs are suitable for No. 10 to No. 18 AWG wire (0.04 to 0.12 in., 1 to 3 mm).

#### 2.3 INSTALLATION PROCEDURE

To install the RP10, proceed as follows:

| Step | Procedure                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Ensure that all power is removed from the PDP-10 System and from the RP01/02 Disk Packs.                                                      |

| 2    | Remove the shipping skid from the bottom of the rack and discard it.                                                                          |

| 3    | Remove the front and rear panel doors, and both side panels from the RP10.                                                                    |

|      | NOTE                                                                                                                                          |

|      | Overall dimensions are given in Figure 2-1.                                                                                                   |

| 4    | Set the rack in place next to the DF10 Data Channel and lower the floor pads on both units to prevent rolling.                                |

| 5    | Bolt the RP10 rack (in four places) to the DF10 rack already in place.                                                                        |

| 6    | Install the grounding cable to the bottom horizontal rack member. Tie the ground lead to the next grounded rack or to a system grounding bus. |

| 7    | Install separate grounds (No. 4 standard PDP-10 ground bus) from each drive to the RP10 (star ground system).                                 |

| 8    | Connect cables according to the site plan and cabling list supplied with each installation (see Figure 2-2).                                  |

| Step     | Procedure                                                                                                                                                                                                                                                            |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8 (Cont) | NOTE<br>Inspect all cable connectors for shipping and<br>handling damage; install them carefully and<br>securely. All power and signal cables should<br>be routed 1 ft apart, if possible. Power and<br>signal cables should cross at a 90° angle.                   |  |

| 9        | Locate the drives and level each to within 5°.                                                                                                                                                                                                                       |  |

| 10       | Connect the remote turn-on power cable from the lower REMOTE<br>CONTROL power outlet on the power control unit of the preceding<br>rack to the upper REMOTE CONTROL power receptacle of the<br>RP10.                                                                 |  |

| 11       | Connect the Margin Check Remote Control Cable from J1 of the preceding Power Connector Assembly Bracket to J2 of the same bracket on the RP10.                                                                                                                       |  |

|          | NOTE                                                                                                                                                                                                                                                                 |  |

|          | If the RP10 is the last unit in the Margin Check bus,<br>install the terminating plug in J1 of the RP10 Power<br>Connector Assembly Bracket.                                                                                                                         |  |

| 12       | Connect the RP10 power cable, already connected and secured to the Power Control Unit, to the system source of ac power.                                                                                                                                             |  |

| 13       | Install any 1/O bus termination plugs required (refer to DEC-10-HIFB-D, PDP-10 Interface Manual).                                                                                                                                                                    |  |

| 14       | Replace side panels and panel doors.                                                                                                                                                                                                                                 |  |

| 15       | On the drives, carefully remove tape from heads (installed for shipping purposes).                                                                                                                                                                                   |  |

| 16       | Inspect each head to ascertain that it is resting on the proper launching block.                                                                                                                                                                                     |  |

| 17       | Before attempting ON-LINE operation, Head and Servo Alignment must<br>be checked and, if necessary, adjusted with C.E. Packs and an OFF-LINE<br>Tester. See considerations in Paragraph 5.3.4. To load a disk pack on<br>the drive, refer to Paragraph 3.3.1.        |  |

| 18       | Using the OFF-LINE Tester perform the following steps on each drive as described in the Vendor Maintenance Manual:                                                                                                                                                   |  |

|          | <ol> <li>Adjust voltage and high/low voltage sense.</li> <li>Adjust positioner as described in Vendor Manual.</li> <li>Perform head alignment with C.E. Pack after completing<br/>a Thermal Equilibrium Procedure as described in Paragraph<br/>5.3.4.2d.</li> </ol> |  |

|          | NOTE                                                                                                                                                                                                                                                                 |  |

|          | When using the OFF-LINE Tester, do not have                                                                                                                                                                                                                          |  |

When using the OFF-LINE Tester, do not have either a cable or terminator block on 'signal out'.

Figure 2-1 RP10 Overall Dimensions

# 2.4 TURN-ON AND CHECKOUT PROCEDURES

When the RP10 has been installed, verify its operation by proceeding as follows:

| Step | Procedure                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------|

| 1    | Set all switches on switch panel to the down position. Make certain that all margin check switches are in the OFF position.  |

| 2    | Apply power to PDP-10 computer system and RP01/02 Disk Pack Drives.<br>The POWER indicator lamp should light.                |

| 3    | Set LOCAL/OFF/REMOTE switch on the DEC Type 844 Power Control panel to LOCAL position.                                       |

| 4    | Set PWR circuit breaker and the power switch located on Power Control panel to ON. The cooling fans should begin to operate. |

| 5    | Refer to the MAINDEC Diagnostic Routine and RP10 System Test<br>Procedure to conduct final checkout of RP10 Synchronizer.    |

|      | NOTE                                                                                                                         |

|      | Run diagnostics and reliability programs using scratch packs or maintenance packs. Scratch packs used for                    |

Run diagnostics and reliability programs using scratch packs or maintenance packs. Scratch packs used for reliability testing must be Mapped before they can be used with Monitor system because the entire surface is subject to writing by Reliability Test.

#### Procedure

Refer to Chapter 5 for any adjustments required during, or as a result of, this installation procedure. Adjustment procedures for the drives are contained in applicable Vendor Manuals.

Figure 2-2 RP10-RP01/RP02 Signal and Power Connections

# Chapter 3 Operation

# 3.1 GENERAL

Chapter 3 contains operating and programming information required to operate the RP10 Disk Pack Synchronizer. Also included in this chapter is an identification of the controls and indicators. A brief summary of RP01/02 characteristics is given as an introduction to RP10 programming considerations.

### 3.2 CONTROLS AND INDICATORS

The controls and indicators for the RP10 are located on the top front of the unit. The indicators are all located on one panel and the controls on another. The controls and indicators are shown in Figure 3-1 and defined in Table 3-1. Power controls and indicators are located behind the rear panel door on the Type 844 Power Control.

| Index No                  |                         |                                                                                                                                                                                        |

|---------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Index No.<br>(Figure 3-1) | Name                    | Function                                                                                                                                                                               |

| 1                         | ASSEMBLY REGISTER 00-35 | These thirty-six indicator lamps light when their<br>associated Assembly Register bit is set to 1. These<br>lamps indicate the contents of the Assembly Register<br>AR00-AR35.         |

|                           | Data Address Register   | These twenty-one indicator lamps light when their<br>associated Data Address Register bit is set to 1. These<br>lamps indicate the contents of the register as follows;                |

| 29                        | DRIVE                   | These three bits indicate which of eight possible disk drives has been selected.                                                                                                       |

| 2                         | CYLINDER                | These eight bits indicate which track cylinder on the selected drive has been selected.                                                                                                |

| 4                         | SURFACE                 | These five bits indicate which surface of the selected drive has been selected.                                                                                                        |

| 6                         | SECTOR                  | These five bits indicate which sector of the selected drive surface track has been selected.                                                                                           |

| 8                         | Designation Error       | These three indicator lamps indicate the data address<br>component in error. Tied to the Header comparator,<br>they indicate either DRIVE DE, SURF DE, or SEC DE<br>designation error. |

| 10                        | SHIFT REGISTER 0-5      | These six indicator lamps indicate the contents of the<br>Shift Register by lighting when their associated bit is<br>set to 1.                                                         |

| 11                        | BUFFER 0-5              | These six indicator lamps indicate the binary contents of the Shift Register Buffer.                                                                                                   |

|                           | Data Channel            | These thirteen indicator lamps indicate the command<br>being processed from the Data Transfer Control<br>assembly as follows;                                                          |

| 28                        | OP CODE 0-2             | Three bits, the binary combination of these bits indicates the operation to be performed.                                                                                              |

| 3                         | READ                    | Six bits indicate what is being read; IMAGE, LPR, DATA, GAP, HDR, or REF (a VFO sync area).                                                                                            |

| 3                         | WRITE                   | Four bits indicate what is being written (HDR, GAP, DATA, or LPR).                                                                                                                     |

| 5                         | WORD COUNTER            | These seven bits indicate the word count of data.                                                                                                                                      |

| 7                         | <b>BYTE 0-2</b>         | These three bits indicate the shift count of bytes.                                                                                                                                    |

| 9                         | BIT 0-2                 | These three bits indicate the bit count.                                                                                                                                               |

| 12                        | Status Bits             | These eight indicator lamps indicate the status of the following conditions;                                                                                                           |

Table 3-1RP10 Controls and Indicators

| Index No.<br>(Figure 3-1) | Name                 | Function                                                                                                                                                                                                                                                                                     |

|---------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12 (Cont)                 | ACTV                 | This bit indicates that the Synchronizer has asserted<br>CHAN START OUT and will have control of the<br>channel next, or has control of the channel.                                                                                                                                         |

|                           | ACTV BUF             | This bit indicates that the Synchronizer wants control of the channel.                                                                                                                                                                                                                       |

|                           | CHAN STTD            | This bit indicates that some device has control of the channel.                                                                                                                                                                                                                              |

|                           | INH                  | This bit indicates that the CC Inhibit flop is set.                                                                                                                                                                                                                                          |

|                           | CHAN PLS             | This bit indicates that a Channel Pulse has been received since the last Device Pulse was sent.                                                                                                                                                                                              |

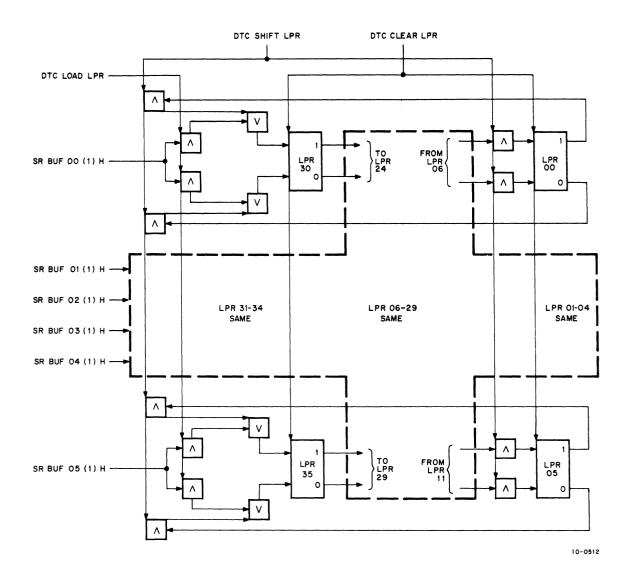

|                           | PS FAIL              | This bit indicates that the RP10 Power Supply outputs are out of tolerance.                                                                                                                                                                                                                  |

|                           | LCL                  | This bit indicates that the Synchronizer is in Local mode.                                                                                                                                                                                                                                   |

|                           | GEN CLR              | This bit indicates that the Synchronizer is idle.                                                                                                                                                                                                                                            |

| 27                        | ATTENTION 0-7        | These seven indicator lamps indicate that an interrupt<br>has been received from a drive, and that it has not been<br>serviced and cleared by a CLEAR ATTENTIONS op code.                                                                                                                    |

|                           | Parity Error         | These four indicator lamps indicate the parity compo-<br>nent in which an error has been detected, as follows;                                                                                                                                                                               |

| 26                        | DISK WDPE            | Parity Error in the Disk Word.                                                                                                                                                                                                                                                               |

|                           | DSPE                 | Parity Error in the Longitudinal Parity Word of a disk sector.                                                                                                                                                                                                                               |

|                           | CCPE                 | Parity Error in the Channel Control Word.                                                                                                                                                                                                                                                    |

|                           | CDPE                 | Parity Error in the Channel Data Word.                                                                                                                                                                                                                                                       |

| 26                        | SRCH                 | This bit indicates that a search operation is in progress.                                                                                                                                                                                                                                   |

| 26                        | SRCH COMP            | This bit indicates that the Synchronizer has found the first sector to be transferred in a read or write data command.                                                                                                                                                                       |

| 26                        | SEARCH ERR 0-2       | These three bits count the number of index pulses seen<br>while the search flop is on. If all bits are on, the con-<br>troller shuts down. After SRCH COMP is set, bit 2 will<br>be set, if a header (other than the first header in a mul-<br>tiple sector operation) was read incorrectly. |

| 15                        | Disabling Bit Status | These three bits indicate whether or not certain flags have been disabled as follows;                                                                                                                                                                                                        |

|                           | DSPE STOP            | This bit indicates that Disk Sector Parity Error will not stop read commands.                                                                                                                                                                                                                |

# Table 3-1 (Cont)RP10 Controls and Indicators

| Index No.<br>(Figure 3-1) | Name               | Function                                                                                                                                                                                                                                            |

|---------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 (Cont)                 | CDPE STOP          | This bit indicates that the Channel Data Word Parity<br>Error will not stop write commands.                                                                                                                                                         |

|                           | DWPE STOP          | This bit indicates that the Disk Word Parity Error will not stop read commands.                                                                                                                                                                     |

| 14                        | Status Bits        | These eleven bits indicate the status of the following conditions;                                                                                                                                                                                  |

|                           | PAR                | This bit indicates that the DTC Parity flop is set.                                                                                                                                                                                                 |

|                           | PAR CONT           | This bit indicates that the Parity Control flop is set.                                                                                                                                                                                             |

|                           | BUSY               | This bit indicates that the Synchronizer is busy exe-<br>cuting a data transfer command.                                                                                                                                                            |

|                           | DONE               | This bit indicates that the DONE flag has been raised<br>and the Synchronizer is no longer busy.                                                                                                                                                    |

|                           | ILL WR             | This bit indicates that a write command has been sup-<br>pressed because the READ-WRITE/READ ONLY<br>switch on the addressed drive is in the READ ONLY<br>position. Indicates a write operation was in process<br>when a sector pulse was received. |

|                           | ILL COM            | This bit indicates that a command to the Synchronizer during a data transfer has been suppressed.                                                                                                                                                   |

|                           | CWX COMP           | This bit indicates that transfer of the initial control word address is complete.                                                                                                                                                                   |

|                           | WR EVEN            | This bit indicates that even parity is being written into memory on all data words read from the disk.                                                                                                                                              |

|                           | OVERRUN            | This bit indicates that the channel did not send a channel pulse between two device pulses.                                                                                                                                                         |

|                           | DISK NRDY          | This bit indicates that the drive selected is either not ready, unsafe, or off line.                                                                                                                                                                |

|                           | NXM                | This bit indicates that the channel tried to access a non-<br>existent memory location.                                                                                                                                                             |

| 13                        | PI 0-2             | These three bits indicate the interrupt channel to which the unit has been assigned.                                                                                                                                                                |

| 25                        | DATA SWITCHES 0-35 | These thirty-six toggle switches permit toggling in any 36-bit data word to be written into disk-pack memory for testing purposes. Signals SWP DATA 00 through 35 are generated.                                                                    |

|                           | Data Address       | These twenty-one toggle switches permit toggling in any 21-bit disk-pack memory address into which the DATA SWITCHES word is to be written. These switches function as follows;                                                                     |

| Table 3-1 (Cont)                    |

|-------------------------------------|

| <b>RP10</b> Controls and Indicators |

| Index No.<br>(Figure 3-1) | Name                                      | Function                                                                                                                                                                                                  |

|---------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24                        | DRIVE 0, 1, 2                             | These three toggle switches determine which of eight<br>disk drives is selected by generating signals SWP DRIVE<br>0, 1, 2 in eight possible binary combinations.                                         |

| 23                        | CYLINDER                                  | These eight toggle switches determine which track-<br>cylinder on the selected drive is selected by generating<br>combinations of signals as follows;                                                     |

|                           | 128<br>64<br>32<br>16<br>8<br>4<br>2<br>1 | SWP CYL 128<br>SWP CYL 64<br>SWP CYL 32<br>SWP CYL 16<br>SWP CYL 8<br>SWP CYL 4<br>SWP CYL 2<br>SWP CYL 1                                                                                                 |

| 22                        | SURFACE 0-4                               | These five toggle switches determine which surface of<br>the selected drive and track-cylinder is selected. This<br>is accomplished by generating binary combinations of<br>signals SWP SURF 0-4.         |

| 21                        | SECTOR 0-4                                | These five toggle switches determine which sector of<br>the selected surface, track-cylinder, and drive is selected.<br>This is accomplished by generating binary combinations<br>of signals SWP SEC 0-4. |

| 20                        | OP CODE 0-2                               | These three toggle switches determine the operation to<br>be performed by the disk pack by generating binary<br>combinations of signals SWP OP 0-2.                                                       |

| 19                        | LOCAL/REMOTE                              | This toggle switch places the RP10 in Local mode or<br>Remote mode by generating the signal SWP LOCAL<br>SET when in the up position and SWP LOCAL CLR<br>when in the down position.                      |

| 18                        | CLEAR                                     | This pushbutton switch, when pressed, clears all registers<br>and stops the current operation by generating the signal<br>SWP CLEAR. Inoperative in Remote mode.                                          |

| 17                        | STOP                                      | This pushbutton switch, when pressed, stops data<br>transfer immediately by generating the signal<br>IBC STOP. Inoperative in Remote mode.                                                                |

| 16                        | START                                     | This pushbutton switch, when pressed, initiates an operation by generating SWP START. Inoperative in Remote mode.                                                                                         |

# Table 3-1 (Cont)RP10 Controls and Indicators

#### 3.3 OPERATION

The following paragraphs give a detailed description of the operation of the RP10 Disk Pack Synchronizer.

# 3.3.1 Loading, Unloading, and Storage of RP01P/02P Disk Packs

### NOTE

# The RP01/02 START/STOP switch should be left in the STOP position until an RP01/02 Disk Pack has been loaded and the cover has been closed.

To load a disk pack on the Disk Pack Drive, proceed as follows:

| Step | Procedure                                                                                                                                    |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | Make certain that power has been removed from the drive and/or the PDP-10.                                                                   |  |  |

| 2    | Holding the disk pack, enclosed in its plastic container, by the top handle; rotate the bottom cover latch and remove.                       |  |  |

|      | NOTE                                                                                                                                         |  |  |

|      | The disk pack will remain attached to top cover.                                                                                             |  |  |

| 3    | Raise the cover on the drive and lower the pack, with its cover attached, into<br>the well provided until the pack seats on its conical hub. |  |  |

| 4    | Rotate the top cover latch and disk assembly clockwise until the pack is proper-<br>ly seated and secure.                                    |  |  |

|      | CAUTION                                                                                                                                      |  |  |

|      | Do not overtighten the pack; snug fit is sufficient.                                                                                         |  |  |

| 5    | Once installed, rotate the top cover latch in the opposite direction and remove<br>the top plastic cover by lifting it out of the well.      |  |  |

| 6    | Return the top and bottom covers to live storage.                                                                                            |  |  |

| 7    | Close the lid on the drive and reapply power.                                                                                                |  |  |

To unload a disk pack from the Disk Pack Drive, proceed as follows:

| Step | Procedure                                                                                                              |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | Make certain that power has been removed from the drive and/or the PDP-10.                                             |  |  |  |

| 2    | Wait for the automatic breaks to stop the drive before raising the lid on the drive.                                   |  |  |  |

|      | NOTE                                                                                                                   |  |  |  |

|      | If the lid is opened when the drive is powered<br>up, power is automatically removed and braking<br>action is applied. |  |  |  |

| 3    | Remove the plastic top cover from its bottom cover and lower the top cover into the well over the disk pack.           |  |  |  |

| Step | Procedure                                                                                                                  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| 4    | Once top cover is seated, rotate the top cover latch counter-clockwise until a clicking sound occurs.                      |  |  |

| 5    | Rotate the latch in the opposite direction to loosen the pack from its hub.                                                |  |  |

| 6    | Holding the bottom cover ready, raise the cover and pack assembly out of its well and place it firmly on its bottom cover. |  |  |

| 7    | Rotate the bottom cover latch until it is snug; then, return the encased disk pack to live storage.                        |  |  |

| 8    | Close the cover on the disk pack drive and reapply power.                                                                  |  |  |

Store the RP01/02P Disk Pack in its plastic container in the same ambient conditions prevailing at the drive.

The maintenance panel is used to operate the RP10 in Local mode; the indicator panel monitors this operation. For general operation of the RP10, proceed as follows:

| Step | Procedure                                                                                                                         |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | Place the LOCAL/REMOTE switch on the maintenance panel in LOCAL position.                                                         |  |  |

| 2    | Set OP CODE switches for desired operation.                                                                                       |  |  |

| 3    | Set address desired in DRIVE, CYLINDER, SURFACE, and SECTOR switches.                                                             |  |  |

| 4    | To select data to be written, set the 36-bit DATA switches on the maintenance panel.                                              |  |  |

| 5    | Depress the START pushbutton. The Synchronizer will perform the selected operation, terminate, restart, and repeat the operation. |  |  |

| 6    | To discontinue operation, depress the STOP pushbutton. The Synchronizer will terminate at the conclusion of the operation.        |  |  |

|      | NOTE                                                                                                                              |  |  |

|      | For single-cycle operation, hold the STOP pushbutton while depressing START. Depressing CLEAR will clear                          |  |  |

# all registers and stop operation.

#### 3.4 PROGRAMMING

Programming of the RP10 is predicated on the requirements imposed by the RP01/02 Disk Packs; therefore, a brief summary of the file is given here as an introduction to programming techniques (see Figures 3-2 and 3-3).

#### 3.4.1 RP01/02 Disk Pack Characteristics

The total capacity of the RP01 Disk Pack is 46,125,440 bits, which is equivalent to 1,559,040 36-bit words; the total capacity of the RP02 Disk Pack is 205,793,280 bits, the equivalent of 5,716,480 36-bit words. In actual practice, however, the two outside surfaces on both Disk Packs are not used and, on all surfaces, tracks 200, 201, and 202 are reserved as spares. When these conditions are recognized, and when parity is added to each word, the relative characteristics are as depicted in the Summary portion of Figure 3-2. This yields a total data word capacity of 1,280,000 36-bit words for the RP01 and 5,120,000 36-bit words for the RP02.

\*NOTE: TRACKS 200,201, AND 202 ARE RESERVED FOR MAINTENANCE.

Figure 3-2 RP01/RP02 Disk Pack Characteristics

Each of the RP01 and RP02 Disk Packs contain 203 cylinders. Movable heads connected to a common positioning actuator access one cylinder at a time. Track-to-track, average, and maximum positioning times are 20, 50, and 80 ms, respectively. Rotation speed is 2400 rpm providing 12.5 ms average and 25 ms maximum latency times. Data is recorded by a double-frequency, nonreturn-to-zero technique. Data is formatted into 128-word sectors, individually addressable.

The RP01 has 10 read/write heads and the RP02 has 20. Recording frequencies are  $1.25 \times 10^6$  bits/sec for the RP01 and 2.5 x  $10^6$  bits/sec for the RP02. Each RP01 track contains five sectors and each RP02 track contains 10 sectors. Word transfer rates are 30 µs for the RP01 and 15 µs for the RP02.

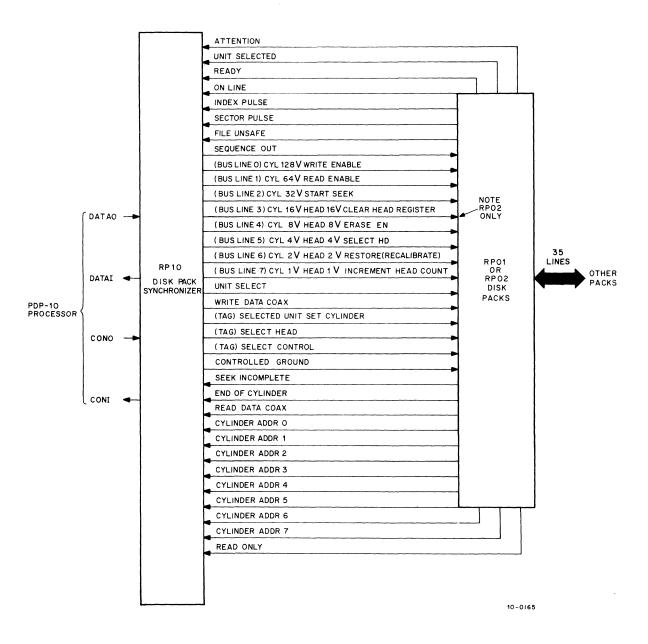

Figure 3-3 RP10/RP01/RP02 Data Control Signals

10-0166

Figure 3-4 RP01/RP02 Data Format

Data formats for information recorded on the disks are arranged as shown in Figure 3-4. These data formats consist of a twenty-word header field on the RP01 (thirty-two on RP02), a data field of 132 words, followed by a two-word trailer.

The first 18 words in the RP01 header field (30 words in RP02) consist of zeros to allow the read circuitry to synchronize with the data. The 19th (31st on RP02) word contains an octal one (000000000001). The last header field word comprises the addressing field.

The first three words in the data field function as a READ DISENABLE/WRITE ENABLE field. The next data field word is used for synchronization, and contains an octal one (00000000001). These words are followed by 128 36-bit words, each followed by its own 37th parity bit.

The first word in the trailer field contains the contents of the longitudinal parity register, and the last word (tail or postamble) contains a second LPR.

#### NOTE

When executing a Write Header command, the first 24 words in an RP01 or the first 36 words in an RP02 are written without parity. Therefore, both bits must be in data and the first bit of the word following the header is interpreted as the parity bit of the header when read back.

Addressing is effected by the 18-bit partitioned binary number, defined as word two in the header. The partitioning has been selected to provide sequential access to the entire memory with a minimum of positioning operations.

The Exec area (Figure 3-4) is determined by the executive program (monitor, operating system) and is ignored by the interface, except for parity checking.

The cylinder address, an unsigned binary number which functions as the track address (positioner), contains eight bits to describe the  $313_8$  tracks. The outer track cylinder is represented by  $000_8$ , and the inner track cylinder is represented by  $312_8$ .

The surface address, a five-bit, unsigned binary number, selects one of 10 disk surfaces for the RP01 (codes  $00_8$  to  $11_8$  are legal), and selects one of 20 disk surfaces for the RP02 (codes  $00_8$  to  $23_8$  are legal). Other codes are illegal (nonexistent).

The sector address, a five-bit, unsigned binary number, selects the proper sector on a track. One of five sectors is selected on the RP01 (codes  $00_8$  to  $04_8$  are legal), and one of 10 sectors on the RP02 ( $00_8$  to  $11_8$  are legal). Other codes are illegal (nonexistent).

In the RP01/02 there is one record per sector (see Figure 3-4). The sector mark defines the beginning of a record. All records are fixed length with a data field of 128 36-bit words plus parity. A header field associated with each record is used to identify the record and ensure that cylinder, surface, and sector selection is correct before writing or reading a record.

#### 3.4.2 RP10 Programming

The RP10 modes of operation are position (seek cylinder), recalibrate, read data, write data, write header and data, and clear attentions. Channel instructions must be placed in memory prior to initiating a data transfer in the synchronizer.

3.4.2.1 DATAO Information (see Figure 3-5) – A DATAO 250 instruction either performs a positioning operation or initiates a data transfer, if the synchronizer is not already busy. The RP10 is capable of executing the six instructions mentioned in the preceding paragraph. The instructions are described below (DATAO 254 is used if a second RP10 is installed in a PDP-10 System).

- a. Position Instruction (seek cylinder) The Position instruction word, shown in Figure 3-6, is divided into four fields:

- (1) Op Code: The Op Code is  $4_8$ .

- (2) Drive: The Drive field indicates the disk drive addressed. All codes are legal if the drives exist.

- (3) Cylinder: The Cylinder field specifies the cylinder sought. Codes 000<sub>8</sub> through 312<sub>8</sub> are legal. Others are nonexistent.

- (4) Bits 14-35: These bits are spares.

Execution of a position instruction requires 3 to 5  $\mu$ s of synchronizer time and 20 to 150 ms of drive time. Positioning is controlled by a difference count of the present address register and the cylinder address register that is loaded by this instruction. When a zero difference count (compare) is reached, the heads are positioned.

Figure 3-5 DATAO Instruction Word Format

| 0   | 2   | 3 5   | 6 | 13       | 1435     |

|-----|-----|-------|---|----------|----------|

| 3 B | ITS | 3 BIT | s | 8 BITS   | 2 2 BITS |

| 5   | )P  | DRIVE | - | CYLINDER | SPARES   |

Figure 3-6 Position Instruction Word

- b. Recalibrate Instruction the Recalibrate instruction word, shown in Figure 3-7, is divided into three fields:

- (1) Op Code: The Op Code is  $7_8$ .

- (2) Drive: The Drive field indicates the disk drive addressed. All codes are legal if the drives exist.

- (3) Bits 6-35: These bits are spares.

Execution of a recalibrate instruction moves the positioner to cylinder zero by force. Positioning is not controlled by the difference count from the current address register, which may be wrong.

- c. Read Data Instruction The Read Data instruction word, shown in Figure 3-8, is divided into ten fields:

- (1) Op Code: The Op Code is  $0_8$ .

- (2) Drive: The Drive field indicates the disk drive addressed. All codes are legal if the drives exist.

- (3) Cylinder: The Cylinder field specifies the cylinder on which the data to be read resides. Codes 000<sub>8</sub> through 312<sub>8</sub> are legal. Other cylinders are nonexistent.

#### NOTE

# The heads must have been previously positioned; this field is for verification only.

- (4) Surface: The Surface field indicates the recording surface on which the data to be read resides. Codes 00<sub>8</sub> through 11<sub>8</sub> are legal on RP01. Codes 00<sub>8</sub> through 23<sub>8</sub> are legal on RP02. All others are nonexistent.

- (5) Sector: The Sector field indicates the sector on which the data to be read resides. Codes  $00_8$  through  $04_8$  are legal on RP01. Codes  $00_8$  through  $11_8$  are legal on RP02. All others are nonexistent.

- (6) Bit 24: This bit is set to 1 to disable longitudinal parity error stop. If not disabled, the discovery of a longitudinal parity error stops data transmission and sets the longitudinal parity error bit.

- (7) Bit 25: This bit is a spare.

- (8) Bit 26: This bit is set to 1 to disable the disk word parity error stop. If not disabled, the discovery of a disk word parity error stops data transmission and sets the disk word parity error bit.

- (9) ICWA: The ICWA field specifies bits 27-34 of the Initial Control Word Address. All binary values above  $17_8$  are legal.

#### NOTE

#### The channel cannot access the fast registers.

(10) Bit 35: This bit, when set, causes the channel to write even parity into memory on all data words read from the disk.

The Read Data instruction causes data to be read until either the channel shuts down or the end of the cylinder is reached.

10-0170

Figure 3-7 Recalibrate Instruction Word

| ڡ   | _ 2  | 35     | 6        | 13 14 18 | 819 2  | 3242526 27           | ,      | 3435    |

|-----|------|--------|----------|----------|--------|----------------------|--------|---------|

| 3 6 | BITS | 3 BITS | 8 BITS   | 5 BITS   | 5 BITS | 1 1 1<br>BIT BIT BIT | 8 BITS | 1<br>вл |

| _   | ĴР   | DRIVE  | CYLINDER | SURFACE  | SECTOR |                      | ICWA   | ΞŢ,     |

Figure 3-8 Read Data Instruction Word

- d. Write Data Instruction The Write Data instruction word, shown in Figure 3-9, is divided into ten fields:

- (1) Op Code: The Op Code is  $1_8$ .

- (2) Drive: The Drive field indicates the disk drive addressed. All codes are legal if the drives exist.

- (3) Cylinder: The Cylinder field specifies the cylinder on which the data is to be written. Codes  $000_8$  through  $312_8$  are legal. Other cylinders are nonexistent.

#### NOTE

# The heads must have been previously positioned. This field is for verification only.

- (4) Surface: The Surface field indicates the recording surface on which the data is to be written. Codes  $00_8$  through  $11_8$  are legal on RP01. Codes  $00_8$  through  $23_8$  are legal on RP02. All others are nonexistent.

- (5) Sector: The Sector field indicates the sector on which data is to be written. Codes  $00_8$  through  $04_8$  are legal on RP01. Codes  $00_8$  through  $11_8$  are legal on RP02. All others are nonexistent.

- (6) Bit 24: This bit is a spare.

- (7) Bit 25: This bit is set to 1 to disable channel data word parity error stop. If not disabled, the discovery of a channel data word parity error stops data transmission and sets the channel data word parity error bit.

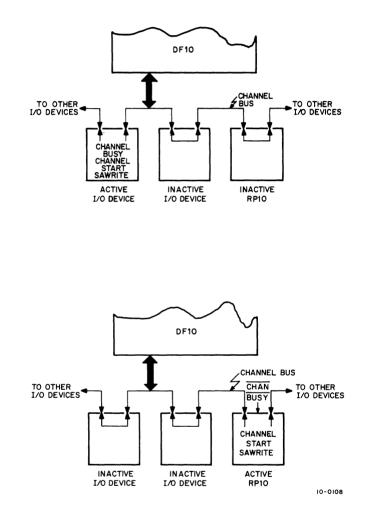

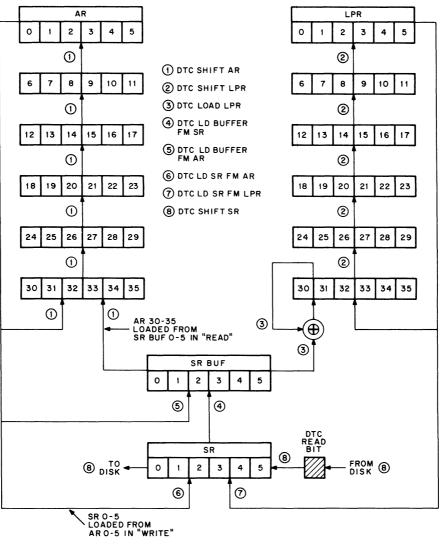

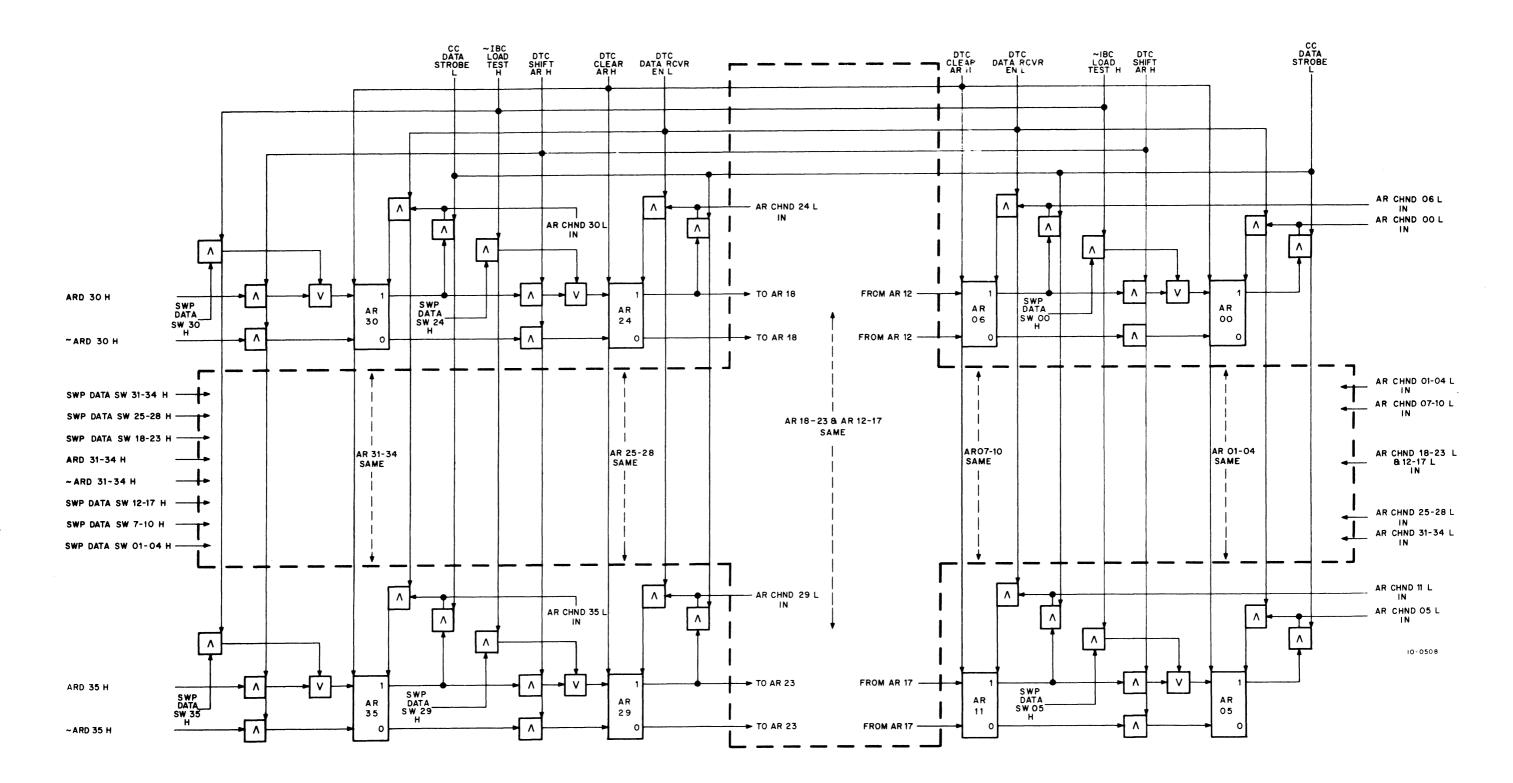

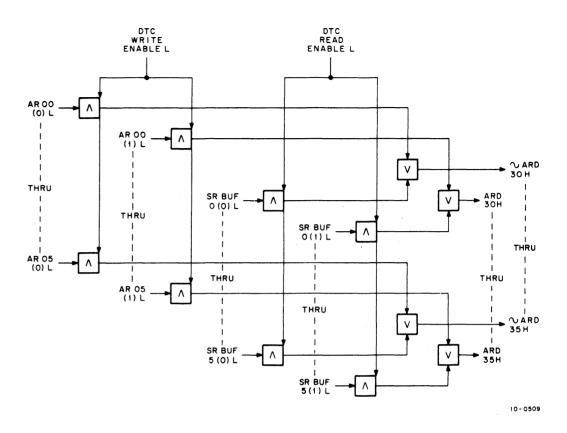

- (8) Bit 26: This bit is a spare.