# TM10 MAGNETIC TAPE CONTROL

DEC-10-I4AA-D

# TM10 MAGNETIC TAPE CONTROL MAINTENANCE MANUAL

DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

1st Printing September 1968 2nd Printing May 1969

# Copyright (C) 1968, 1969 by Digital Equipment Corporation

Instruction times, operating speeds and the like are included in this manual for reference only; they are not to be taken as specifications.

The following are registered trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| PDP          |

|--------------|

| FOCAL        |

| COMPUTER LAB |

|              |

# CONTENTS

Page

# CHAPTER 1 INTRODUCTION AND DESCRIPTION

| 1.1   | Purpose                  | 1-2 |

|-------|--------------------------|-----|

| 1.2   | 7–Track Tape Format      | 1-2 |

| 1.2.1 | Load Point and End Point | 1-4 |

| 1.3   | 9–Track Tape Format      | 1-4 |

| 1.3.1 | CRC Character            | 1-4 |

| 1.4   | Referenced Documents     | 1-5 |

# CHAPTER 2 OPERATION AND PROGRAMMING

| 2.1    | Command Bits                         | 2-4          |

|--------|--------------------------------------|--------------|

| 2.2    | Status Bits                          | 2-4          |

| 2.3    | Stop Bit                             | 2-6          |

| 2.4    | Tape Functions                       | 2-6          |

| 2.4.1  | NO-OP (0)                            | 2-6          |

| 2.4.2  | NO-OP (10)                           | 2-6          |

| 2.4.3  | Rewind (1)                           | 2-6          |

| 2.4.4  | Read (2)                             |              |

| 2.4.5  | Read Across Record Boundaries (12)   | 2-7          |

| 2.4.6  | Read/Compare (3)                     | 2-7          |

| 2.4.7  | RD/CMP Across Record Boundaries (13) | 2-7          |

| 2.4.8  | Write (4)                            | 2-7          |

| 2.4.9  | Write With Extended EOR GAP (14)     | 2-8          |

| 2.4.10 | Write End-of-File (5)                | 2-8          |

| 2.4.11 | Space Forward (6)                    | 2-8          |

| 2.4.12 | Space Forward To End-of-File (16)    | 2-8          |

| 2.4.13 | Space Reverse (7)                    | 2-9          |

| 2.4.14 | Space Reverse To End-of-File (17)    | 2-9          |

| 2.5    | Tape Functions (TM10B)               | 2-9          |

| 2.5.1  | NO-OP (0)                            | 2 <b>-</b> 9 |

| 2.5.2  | NO-OP (10)                           | 2-9          |

| 2.5.3  | Rewind (1)                           | 2-9          |

| 2.5.4  | Read (2)                             | 2-9          |

|        |                                      |              |

# CONTENTS (Cont)

Page

| 2.5.5  | Read Across Record Boundaries (12)   | 2-10 |

|--------|--------------------------------------|------|

| 2.5.6  | Read/Compare (3)                     | 2-10 |

| 2.5.7  | RD/CMP Across Record Boundaries (13) | 2-10 |

| 2.5.8  | Write (4)                            | 2-10 |

| 2.5.9  | Write With Extended EOR GAP (14)     | 2-11 |

| 2.5.10 | Write End-of-File (5)                | 2-11 |

| 2.5.11 | Space Forward (6)                    | 2-11 |

| 2.5.12 | Space Forward to End–of–File (16)    | 2-11 |

| 2.5.13 | Space Reverse (7)                    | 2-11 |

| 2.5.14 | Space Reverse to End-of-File (17)    | 2-12 |

| 2.6    | TM10A Command Timing                 | 2-12 |

| 2.7    | 9-Track Tape                         | 2-12 |

# CHAPTER 3 THEORY OF OPERATION

| 3.1    | DF10 Data Channel Description | 3-1  |

|--------|-------------------------------|------|

| 3.2    | NRZ Recording                 | 3-4  |

| 3.3    | System Description            | 3-6  |

| 3.3.1  | TM10A                         | 3-6  |

| 3.3.2  | TM10B                         | 3-8  |

| 3.4    | TM10A Initial Operation       | 3-10 |

| 3.5    | TM10B Initial Operation       | 3-10 |

| 3.6    | Inter-Record Gap Delay        | 3-13 |

| 3.7    | Write                         | 3-14 |

| 3.8    | Continued Operation           | 3-15 |

| 3.9    | Write End–of–File Mark        | 3-16 |

| 3.10   | Read                          | 3-16 |

| 3.11   | Read/Compare                  | 3-17 |

| 3.12   | Density Modes                 | 3-17 |

| 3.13   | Data Transfer                 | 3-18 |

| 3.13.1 | TM10A                         | 3-18 |

| 3.13.2 | тміов                         | 3-19 |

| 3.14   | Errors                        | 3-21 |

# CONTENTS (Cont)

| 3.14.1 | Data Late Errors                              | 3-21 |

|--------|-----------------------------------------------|------|

| 3.14.2 | Parity Error                                  | 3-21 |

| 3.14.3 | Read/Compare Error                            | 3-22 |

| 3.14.4 | Record Length Incorrect                       | 3-22 |

| 3.14.5 | Bad Tape Error                                | 3-22 |

| 3.15   | Illegal Commands                              | 3-22 |

| 3.16   | Space                                         | 3-22 |

| 3.17   | Space To End-of-File                          | 3-23 |

| 3.18   | Read or Read/Compare Across Record Boundaries | 3-23 |

| 3.19   | Read-In Mode                                  | 3-24 |

# CHAPTER 4 MAINTENANCE

| 4.1   | Preventive Maintenance    | 4-1 |

|-------|---------------------------|-----|

| 4.1.1 | Mechanical Checks         | 4-1 |

| 4.1.2 | Weekly Checks             | 4-2 |

| 4.1.3 | Monthly Checks            | 4-2 |

| 4.2   | Corrective Maintenance    | 4-3 |

| 4.2.1 | Preliminary Investigation | 4-3 |

| 4.2.2 | System Troubleshooting    | 4-3 |

| 4.2.3 | Signal Tracing            | 4-4 |

| 4.2.4 | Intermittent Failures     | 4-4 |

| 4.2.5 | Module Circuits           | 4-5 |

# CHAPTER 5 ENGINEERING DRAWINGS

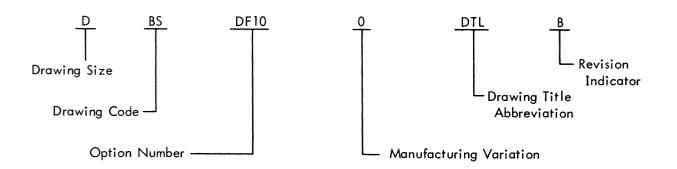

| 5.1 | Drawing Terminology      | 5-1          |

|-----|--------------------------|--------------|

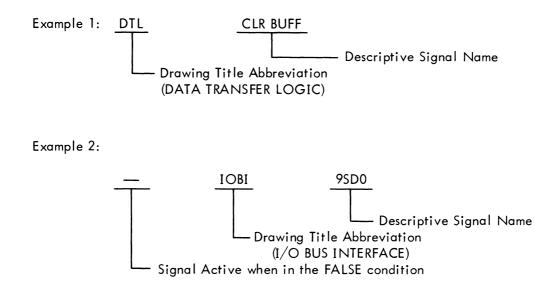

| 5.2 | Logic Symbols            | 5 <b>-</b> 2 |

| 5.3 | Logic Levels             | 5-2          |

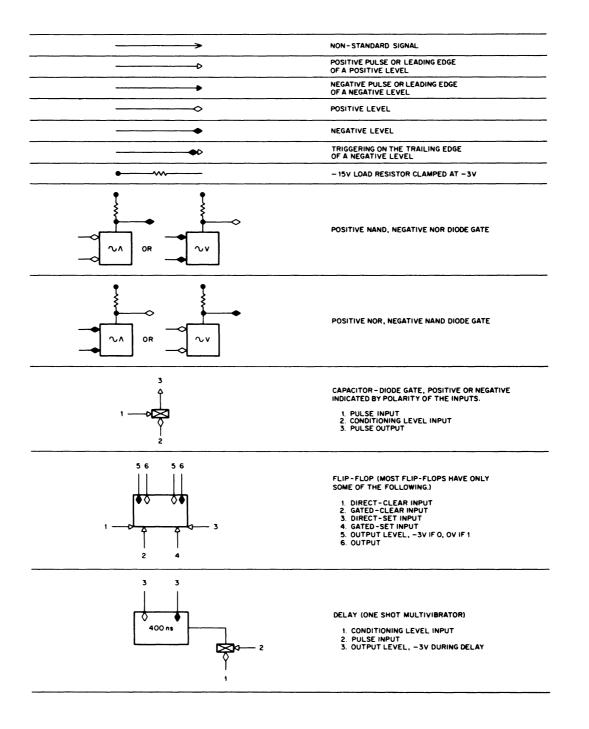

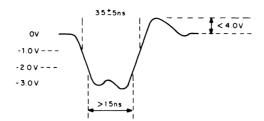

| 5.4 | FLIP-CHIP Pulses         | 5-4          |

| 5.5 | Engineering Drawing List | 5-5          |

# ILLUSTRATIONS

|     |                                   | Page |  |  |  |

|-----|-----------------------------------|------|--|--|--|

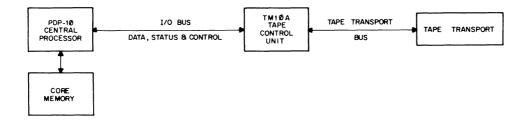

| 1-1 | TM10A Tape Control Configuration  | 1-1  |  |  |  |

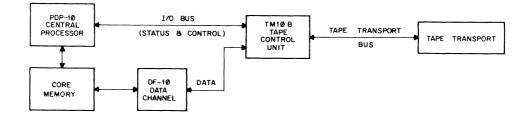

| 1-2 | TM10B Tape Control Configuration  | 1-1  |  |  |  |

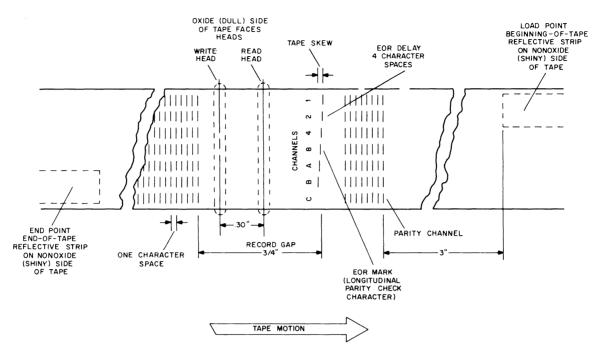

| 1-3 | 7–Track Tape Format               | 1-3  |  |  |  |

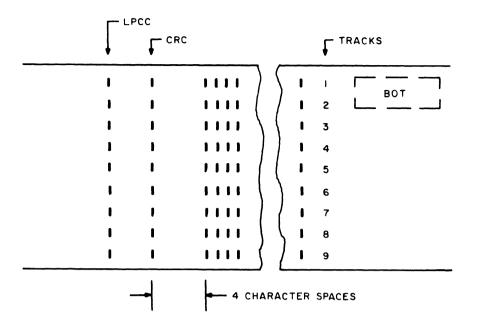

| 1-4 | 9–Track Tape Format               | 1-5  |  |  |  |

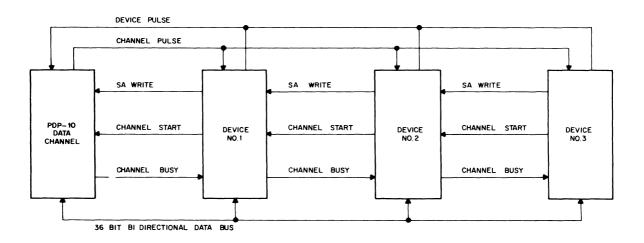

| 3-1 | Data Channel Interface            | 3-3  |  |  |  |

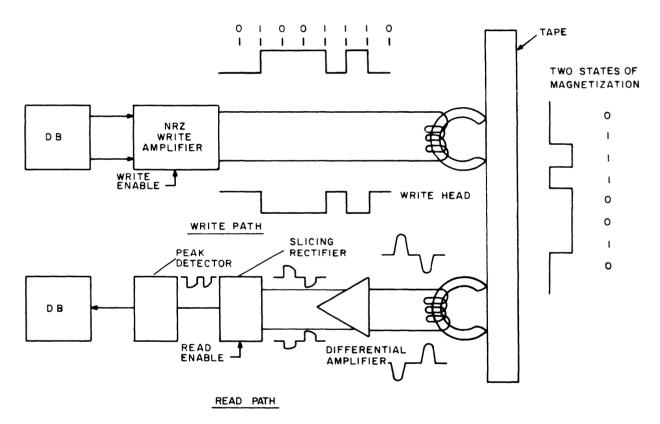

| 3-2 | Tape Write and Read Signal Flow   | 3-5  |  |  |  |

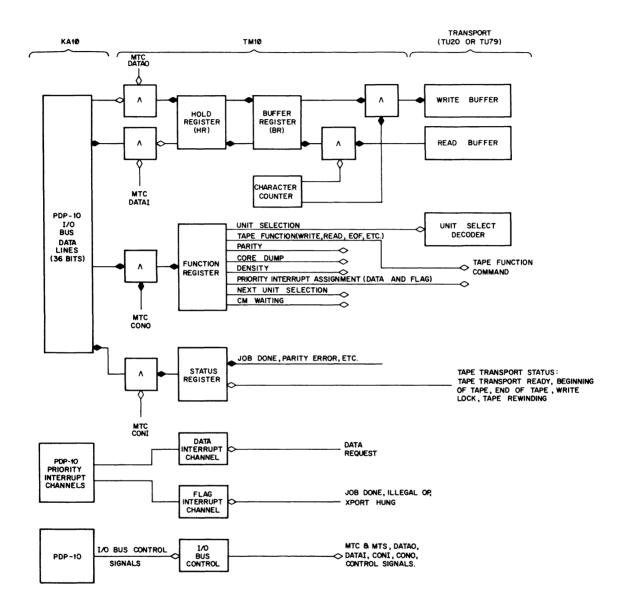

| 3-3 | TM10A Tape Control Block Diagram  | 3-7  |  |  |  |

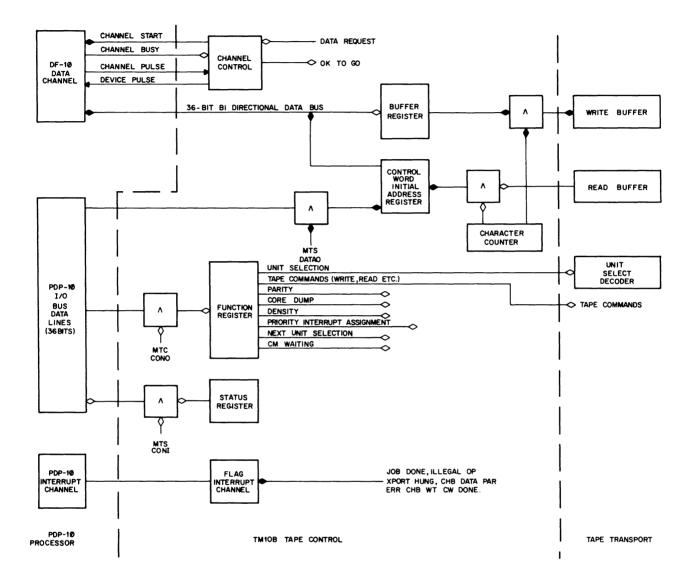

| 3-4 | TM10B Tape Control Block Diagram  |      |  |  |  |

| 5-1 | DEC Standard Logic Symbols        |      |  |  |  |

| 5-2 | R-Series and S-Series Pulses      | 5-4  |  |  |  |

| 5-3 | B-Series Pulse                    | 5-5  |  |  |  |

|     | TABLES                            |      |  |  |  |

| 2-1 | CONO/CONI 340 (MTC) Instructions  | 2-1  |  |  |  |

| 2-2 | TM10 Functions                    | 2-2  |  |  |  |

| 2-3 | Status Register (CONI 344 Format) | 2-3  |  |  |  |

| 4-1 | Diagnostic Programs               | 4-4  |  |  |  |

#### CHAPTER 1

## INTRODUCTION AND DESCRIPTION

The TM10A or TM10B Magnetic Tape Control Unit controls a magnetic tape transport conforming to the transport bus specification, such as DEC Model TU-20 or TU-79. Both transports are capable of operating either 7-track or 9-track head configurations.

The TM10A tape control unit (Figure 1-1) uses the PDP-10 I/O bus to transfer data between PDP-10 core memory and tape control. An executive program monitors the data flag interrupt for data requests (either read or write) and data is transferred under the control of the I/O instructions. The executive program monitors the data transfers to determine when to stop operation.

Figure 1-1 TM10A Tape Control Configuration

The TM10B (Figure 1–2) uses the DF10 Data Channel to transfer data between the TM10B and PDP-10 core memory. The computer program initializes the TM10B tape control and thereafter the tape control operates under control of the DF10 Data Channel to transfer data.

Figure 1-2 TM10B Tape Control Configuration

This manual, together with referenced documents, provides operation and maintenance information for both Model TM10A and Model TM10B Magnetic Tape Control Unit. The level of discussion assumes familiarity with the PDP-10 Programmed Data Processor, and a working knowledge of DEC logic symbology. For circuits and operations common to both models, no distinction is made between either the TM10A or TM10B. However, for those circuits and operations that differ, this manual makes a clear distinction in describing the individual operation of each model.

## 1.1 PURPOSE

The TM10 (A or B) functions in either 7-track or 800 bpi 9-track operation; either the 200, 556, or 800 bpi density mode is selectable in 7-track operation. It can operate in either binary (odd) or BCD (even) parity mode. For writing on tape, the 36-bit data words are transferred from core memory to the data buffer in the tape control logic. The buffer logic supplies the data to the tape transport write logic as six 7-bit (6-bit character plus parity bit) characters for 7-track operation (four 9-bit characters for a 9-track operation). For reading, the sequence is reversed, information is read from tape as 7-bit characters and is sent to the data buffer. When a complete 36-bit word has been assembled in the data buffer, a word transfer is initiated to transfer the data buffer word into core memory.

The operations that can be performed by the tape transport, under the control of the TM10 are as follows.

| REWIND        | The transport rewinds the tape to the load point and stops.                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITE         | N words are written on tape as specified by the program.                                                                                                                             |

| WRITE EOF     | An EOF (end-of-file) mark character is written on tape.                                                                                                                              |

| READ          | N words are read from tape as specified by the program.                                                                                                                              |

| READ/COMPARE  | N words are read from tape as specified by the program. After each complete word is read, it is compared to a word in memory producing a read-compare error when they don't compare. |

| SPACE FORWARD | The tape is spaced forward N records as specified by the program.<br>If EOT (end-of-tape) is encountered, the tape stops.                                                            |

| SPACE REVERSE | The tape is spaced in reverse for N records as specified by the program. If BOT (beginning-of-tape) is encountered, the tape stops.                                                  |

## 1.2 7-TRACK TAPE FORMAT

The 7-track system uses 1/2 in. tape with seven information channels; the format is shown in Figure 1-3. The left side of Figure 1-3 shows the tape in relation to the read and write heads. This tape is composed of a mylar base coated on one side with an iron oxide composition. The oxide, or dull side of the tape, faces the heads with the left edge toward the transport drive plate. The recording density is 200 cpi (characters per inch), 556 cpi, or 800 cpi. The method of recording is non-return-tozero (NRZ).

#### TAPE SHOWN WITH OXIDE SIDE DOWN

Figure 1-3 7-Track Tape Format

Although the tape has two basic states of remanent magnetization, the remanent magnetic state of the tape at a given position does not determine the value of the bit. A logical 1 is represented by a change of magnetization in either direction. A logical 0 is represented by a constant state of magnetization; therefore, writing a series of characters containing all 0s is equivalent to writing a section of blank tape. Each time a character is transferred into the tape transport write buffer, the NRZ writers produce an equivalent character on the tape. Because of the NRZ method of recording, however, a transfer into the write buffer is not a normal 1s transfer; instead, whenever a 1 bit is to be written in a given tape channel, the corresponding flip-flop is complemented to produce a change in the tape magnetization. When a 0 is written, the corresponding bit of the buffer remains in the initial stage, and there is no change in tape magnetization.

The structure and relative spacing of the individual tape characters are shown in the right portion of Figure 1-3. Each 36-bit computer word is divided into six 6-bit characters. However, the writers contain seven flip-flops corresponding to the seven tape channels; the seventh channel is a lateral parity channel. The parity of the character may be either odd (binary) or even (BCD) as specified by the program. In reading the tape, only 1s are detected.

The smallest unit of information that can be written on the tape is a record; since each computer word contains six 6-bit characters, a record contains  $N \ge 6$  data characters, where N is the number of words that the processor transfers.

After the last data character of the record is written, the tape travels slightly over four character spaces of blank tape (EOR gap), and then clears the write buffer to produce an end-of-record character, the EOR mark. The bit configuration of the EOR mark produced by clearing the write buffer leaves an even number of 1 bits in each of the seven channels of the tape. All bits of the write buffer start in the 0 state; to end in the 0 state, they must undergo an even number of transitions. For this reason, the EOR mark is referred to as the longitudinal parity-check character (LPCC). Besides detecting changes in magnetization through the read heads, the tape transport also includes a photo-electric system for sensing the beginning and end of the tape.

## 1.2.1 Load Point and End Point

The load and end points of the tape are marked by reflective strips mounted on the side of the tape away from the head (Figure 1-3). These strips are detected by photodiodes which sense light reflected from them. In writing on a rewound tape, a gap of about 3 in. is left from the load point before writing begins. When the load point is sensed during a fast rewind condition, the sensing device shuts off the high speed rewind. Before the tape movement stops, however, the load point will be passed and the forward tape motion will be enabled to advance the tape back to the load-point strip.

#### 1.3 9-TRACK TAPE FORMAT

The 9-track tape format shown in Figure 1-4 is similar to the 7-track format except that 9track format has 9 tracks, the CRC (cyclic redundancy check) character has been added, and operation is only in the 800 bpi mode.

The tape control assembles four 8-bit characters per 36-bit word for recording on tape. Each 8-bit character is recorded with a parity bit which can be either odd or even. The first character recorded contains the most significant bits of the PDP-10 36-bit word.

# 1.3.1 CRC Character

To write the CRC character, the TM10 control incorporates a 9-position register CRC1 through CRC9 with the following track assignments:

| Register Position | CR1 | CR2 | CR3 | CR4 | CR5 | CR6 | CR7 | CR8 | CR9 |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Track Number      | 4   | 7   | 6   | 5   | 3   | 9   | 1   | 8   | 2   |

Figure 1-4 9-Track Tape Format

To derive the CRC character, all data characters are exclusive ORed into the CRC register. Between character transfers, the CRC is shifted one position, CRC1 to CRC2, etc., and CRC9 to CRC1. If shifting causes a 1 in CRC1, then the bits shifted into CRC4, CRC5, CRC6, and CRC7 are inverted. After the last data character has been added (exclusive ORed), the CRC register is again shifted and, if CRC1 becomes 1, the CRC4, CRC5, CRC6, and CRC7 are inverted.

To write the CRC character on tape, all bit positions except CRC4 and CRC6 are inverted. An odd parity CRC character occurs if the number of data characters within the block is even, and an even parity CRC character occurs if the number of data characters within the block is odd. The CRC character may contain all 0 bits; in that case, the number of data characters was odd.

The LPCC character for 9-track format is the same as for the 7-track format.

#### 1.4 REFERENCED DOCUMENTS

The following documents contain information related to the TM10 Magnetic Tape Control

Unit.

| DEC-10-HMAA-D | PDP-10 Maintenance Manual, Volume I  |

|---------------|--------------------------------------|

| DEC-10-HGAA-D | PDP-10 Systems Reference Guide       |

| DEC-00-14AA-D | TU–20 Instruction Manual             |

| C105          | DEC Logic Handbook                   |

| DEC-10-18BA-D | DF10 Data Channel Instruction Manual |

# CHAPTER 2 OPERATION AND PROGRAMMING

This chapter describes the programming of both the TM10A and TM10B systems to satisfy any detailed programming requirements. Frequently, however, the programmer will not need the detailed procedures for programming the TM10A and TM10B described since the PDP-10 monitor provides call statements to the magnetic tape I/O driver subroutine that satisfy most of his requirements. The applicable PDP-10 document should be consulted for these procedures and call statements.

The TM10A operates under complete control of an executive program for all tape operations. The executive initiates an operation by issuing a CONO 340 (CONO MTC) instruction. The format of this instruction (see Table 2-1 and 2-2) specifies the parameters, the particular tape function, and starts the operation. Request for data transfer (either to or from core memory) is accomplished by use of the data interrupt channel. For example, during a write operation the DATA REQUEST flag is raised to signify that the tape control requires the next 36-bit word to be recorded. The flag generates a DATA interrupt and the executive responds to this interrupt by issuing a DATAO 340 instruction to transfer the 36-bit word to tape control via the I/O bus. Moreover, the executive monitors the number of data transfers to determine when to stop the write operation. It stops the operation by issuing a CONO 344 (CONO MTS) with bit 35 set to 1. The program monitors tape status (Table 2-3) by use of the CONI 344 (CONI MTS) instruction.

| Bit   | Name                       | Function                                                            |

|-------|----------------------------|---------------------------------------------------------------------|

| 15-17 | NEXT UNIT<br>NUMBER        | Specifies the next tape transport number selected for operation.    |

| 18-20 | UNIT<br>NUMBER             | Specifies the current tape transport number selected for operation. |

| 21    | PARITY                     | 1 = Odd; 0 = Even                                                   |

| 22    | CORE DUMP                  | 0 = 4 Bytes; $1 = 4 - 1/2$ Bytes                                    |

| 23-26 | FUNCTIONS                  | Tape functions (see Table 2-2 for encoded functions).               |

| 27    | NEXT UNIT<br>EN <b>A</b> B | When set, enables the NEXT UNIT flag to generate an interrupt.      |

Table 2–1 CONO/CONI 340 (MTC) Instructions

# Table 2–1 (Cont) CONO/CONI 340 (MTC) Instructions

| Bit    | Name      | Function                                                                |

|--------|-----------|-------------------------------------------------------------------------|

| 28, 29 | DENSITY   | 0 = 200 bpi; 1 = 556 bpi; 2 = 800 bpi; 3 = not used.                    |

| 30-32  | FLAG PIA  | Specifies the priority assigned to the flag priority interrupt channel. |

| 33-34  | DATA PIA* | Specifies the priority assigned to the data priority interrupt channel. |

\*Used only on the TM10A, always contains 1s in TM10B.

| Function | Octal Code | Description                                   |

|----------|------------|-----------------------------------------------|

| 0000     | 0          | No-op, clear interrupt flags                  |

| 1000     | 10         | No-op, interrupt when transport becomes idle. |

| 0001     | 1          | Rewind                                        |

| 0010     | 2          | Read                                          |

| 1010     | 12         | Read across record boundaries                 |

| 0011     | 3          | Read/Compare                                  |

| 1011     | 13         | Rd/Cmp across record boundaries               |

| 0100     | 4          | Write                                         |

| 1100     | 14         | Write with long EOR gap                       |

| 0101     | 5          | Write end-of-file                             |

| 0110     | 6          | Space forward one or more records             |

| 1110     | 16         | Space to end-of-file                          |

| 0111     | 7          | Space reverse one or more records             |

| 1111     | 17         | Space reverse to end-of-file                  |

# Table 2–2 TM10 Functions

| Bit   | Name                    | Interrupt                |

|-------|-------------------------|--------------------------|

|       |                         |                          |

| 11    | CW PAR ERR*             |                          |

| 12    | NO-EX MEM*              |                          |

| 13    | DATA PAR ERR*           | Flag Channel             |

| 14    | WT CW DONE*             | Flag Channel             |

| 15-17 | Character Counter       |                          |

| 18    | TRANSPORT HUNG          | Flag Channel             |

| 19    | REWINDING               |                          |

| 20    | BOT (beginning of tape) |                          |

| 21    | ILLEGAL OPERATION       | Flag Channel             |

| 22    | PARITY ERROR            |                          |

| 23    | EOF (end-of-file)       |                          |

| 24    | EOT (end-of-tape)       |                          |

| 25    | READ/COMPARE ERROR      |                          |

| 26    | RECORD LENGTH INCORRECT |                          |

| 27    | DATA LATE               |                          |

| 28    | BAD TAPE                |                          |

| 29    | JOB DONE                | Flag Channel             |

| 30    | TRANSPORT IDLE          |                          |

| 31    | CHANNEL ERROR *         |                          |

| 32    | WRITE LOCK              |                          |

| 33    | 7-CHANNEL TRANSPORT     |                          |

| 34    | NEXT UNIT               | Flag Channel, if enabled |

| 35    | DATA REQUEST            | Data Channel**           |

Table 2–3 Status Register (CONI 344 Format)

\*TM10B only \*\*TM10A only The TM10B uses the DF10 data channel facility to transfer data from PDP-10 core memory to the TM10B. An executive program must control the operation of both the DF10 Data Channel and the TM10B. (Refer to the DF10 Data Channel manual for program control of the data channel.) The executive program starts operation when it issues a CONO MTC instruction as it did for the TM10A. But first, the program must issue a DATAO 344 to transfer the initial control word address for the data channel to the TM10B where it is held until the TM10B gains access to the data channel.

## 2.1 COMMAND BITS

Bits transmitted via CONO MTC, have the meanings shown in Tables 2-1 and 2-2. The unit number bits select one of eight transports. The parity bit selects even or odd parity checking; 0 for even, 1 for odd (preferred parity is odd). The core dump bit should be used with 9-channel transports only. With the core dump bit = 1 and 9-channel tape, the TM10 writes out 36-bit words onto 9-channel tape by splitting the data up among five 8-bit bytes.

Function encoding is shown in Table 2–2. A detailed description of each function is provided in the following paragraphs.

The NEXT UNIT INTERRUPT ENABLE is used in conjunction with the no-op function to allow testing of the transport status bits. If the control is not free when a CONO MTC is given, there will be a delay until the current transport can be deselected and the new one selected. The next unit interrupt allows the program to examine the transport status bits at the earliest opportunity. Without the enable bit, the next interrupt will occur when the transport becomes ready (which may be long delayed, by a rewind for instance).

Any one of three bit densities may be selected, 200 bpi, 556 bpi, or 800 bpi. The encodings for these are 00, 01, and 10, respectively; with encoding 11 currently acting the same as 10, but reserved for future revisions. If 9-track tape is being used without the core dump bit, the program must select 800 bpi.

## 2.2 STATUS BITS

Table 2-3 shows status bits as sensed by the CONI instruction. Any of six status bits shown in Table 2-3 can cause a flag's channel interrupt. TRANSPORT HUNG means that the TM10 has waited for one second and the selected transport has not completed its operation or else has been switched offline during an operation.

ILLEGAL OP signifies that an improper command has been issued, such as write with the file protect ring out (write lock on). JOB DONE means that the TM10 has completed its command and is ready for a new command. The conditions under which JOB DONE is set are described separately

2-4

for each function. NEXT UNIT causes an interrupt only if the last command had the NEXT UNIT ENABLE bit a 1. NEXT UNIT means that the previous transport has been given a stop signal and the control is not tied up processing a command.

DATA REQUEST causes an interrupt on the data PI channel. This bit is turned off by a DATAO or DATAI MTC instruction, whichever is appropriate to the tape function.

The PARITY ERROR signifies incorrect parity, either lateral or longitudinal. Data that is written is read back and automatically checked for parity. EOF (end-of-file) means an end-of-file record was read from the tape. Both PARITY ERROR and EOF can be 1 during an operation, and yet be 0 at JOB DONE. In particular, if an end-of-file is read with odd parity, the PARITY ERROR bit will be on until the end of record when the control detects the end-of-file situation and turns off the PARITY ERROR bit. Also, when spacing reverse, if the Ingitudinal parity character and the last data byte of any record are both end-of-file characters, the EOF bit will come on until the next-to-last byte is read.

The READ/COMPARE ERROR bit means that the data read from the tape was not the same as the data sent out by a DATAO MTC, during a READ/COMPARE operation. If the READ/COMPARE ERROR bit becomes 1, there are no further data requests or other interrupts until the end-of-record.

RECORD LENGTH INCORRECT is valid only for a READ or READ/COMPARE operation. See the explanation of READ below for a description of this bit.

DATA LATE means that the program did not respond quickly enough to a data request and thus has lost data. During a read operation there are no further interrupts until the end-of-record. During a write operation, the last word is written a second time followed by an end-of-record.

BAD TAPE means data was seen in the end-of-record gap. This could indicate missed characters or noise in the end-of-record gap, either of which are to be blamed on faulty tape.

The following four bits are always 1 in the TM10A.

The CW PAR ERR flag means that the DF10 channel encountered a core memory parity error when fetching a control word. This bit does not cause an interrupt but comes on coincidently with JOB DONE.

The NON-EX MEM bit signifies that the DF10 channel encountered NON-EXISTENT memory on a core memory reference. This bit does not cause an interrupt but comes on coincidently with JOB DONE.

The DATA PAR ERR flag means that the DF10 channel encountered a core memory parity error when fetching a data word. This bit causes an interrupt on the flag channel. This bit is cleared by CONO 344, 20.

The WT CW DONE flag indicates that the DF10 channel has written the current control word into initial address +1 (as requested). This bit causes an interrupt. It is cleared by CONO 344, 10.

The OR of these four flags appears in bit 31 of the CONI 344 status word as CHANNEL ERROR. In the TM10A, CHANNEL ERROR is always 0.

In addition to the two bits to clear channel flags, the CONO 344 has the WRITE CONTROL WORD bit (CONO 344, 4). This bit forces the DF10 to write its current control word into memory, a process that may be delayed by up to 170 µs. (See WT CW DONE above.) For the TM10B, if CW PAR ERR or NON-EX MEM comes on, no further data transfers take place and the tape will stop at the end of whatever record is in progress. If DATA PAR ERR is on, the channel will attempt to complete its command list. To stop the function immediately and get a JOB DONE at the end of the current record, the program may issue CONO 344, 1.

#### 2.3 STOP BIT

The instruction CONO MTS, 1 sets a stop bit in the TM10. During a write operation, this bit indicates that the last word has been sent to the TM10. During a read or read/compare operation, this bit indicates that the program has finished with the current record and will not transfer any more words. During a spacing operation, this bit means stop at the end of the current record. This bit is operational in the TM10B but is used only in abnormal situations, such as data parity error.

## 2.4 TAPE FUNCTIONS (TM10A)

#### 2.4.1 NO-OP (0)

Clears all status bits except those associated with the transport and NEXT UNIT.

#### 2.4.2 NO-OP (10)

Loads a new current transport number and sets JOB DONE when the transport becomes ready. Note the NEXT UNIT ENABLE bit description.

# 2.4.3 REWIND (1)

Rewinds the selected transport. Sets JOB DONE as soon as the transport is up to speed. To interrupt at the end of a rewind, wait for JOB DONE and then use NO-OP (10).

# 2.4.4 READ (2)

Data is read in the forward direction only. The parity and density must be set the same as when the data was written. ILLEGAL OP is set if the transport is 9-channel and neither 800 bpi nor core dump mode is selected. The DATA REQUEST flag is raised whenever a 36-bit word is ready for the processor. JOB DONE is set at the end of record. If the program issues a CONO MTS, 1 after the last word in a record is read, the RECORD LENGTH INCORRECT flag stays off; this flag comes on if the record ends prematurely (the program never issues CONO MTS, 1; or does so late) or if another data word follows the CONO MTS, 1; in the latter case, the following words are ignored. DATA LATE is set when the control assembles a 36-bit word and the program has not done a DATAI for the previous 36-bit word. The average DATAI rate must equal the word rate from the tape transport. The maximum time between DATAI's assuming the most favorable possible timing, is 2-1/6 times the word rate for 7-channel tape, 2-1/5 for 9-channel core dump mode, and 2-1/4 for 9-channel compatible mode. If an end-of-file is encountered in READ mode, there are no DATA REQUESTS and the EOF flag will be set along with JOB DONE.

#### 2.4.5 READ ACROSS RECORD BOUNDARIES (12)

Like READ (2), except that JOB DONE is set only at the first end-of-record after an error, or at an end-of-file, or after CONO MTS, 1 is given, or if the number of characters in a record is not a multiple of six for 7-channel tape. Thus, a single BLKI can read in several records.

#### 2.4.6 READ/COMPARE (3)

Data is read from the tape by the control and the program sends data from core via DATAO. The two words are compared in the control and, if equal, the process continues with the next pair of words. If not equal, there are no further DATA REQUEST flags and the READ/COMPARE ERROR flag is set at the end of record. The first DATA REQUEST occurs when the tape begins to move.

For other flags, modes and timing considerations, see READ mode.

#### 2.4.7 RD/CMP ACROSS RECORD BOUNDARIES (13)

Like READ ACROSS RECORD BOUNDARIES (12), but compares.

#### 2.4.8 WRITE (4)

Data may be written in any of three densities (200 bpi, 556 bpi, or 800 bpi) on 7-channel transports, at 800 bpi in IBM-compatible format on 9-channel transports, or at any of three densities in core dump mode on 9-channel transports. Either even or odd parity may be selected. When selecting even parity, care must be taken to never write a character of all 0s on tape, since such a character will be ignored while reading. A WRITE command to a write-locked tape results in the ILLEGAL OP flag and no tape motion. To terminate a record, the program must follow the last DATAO with the CONO MTS, 1. There will be no further data requests; JOB DONE is set when the read-after-writing

circuit reads and checks the longitudinal parity. The BAD TAPE flag could be set at this time. If the CONO MTS, 1 is not given, the TM10A raises the DATA LATE flag, rewrites the last data word, and then writes an end-of-record and stops. The first DATA REQUEST occurs when the tape starts moving. Other timing considerations are the same as for READ mode.

#### 2.4.9 WRITE WITH EXTENDED EOR GAP (14)

Similar toWRITE (4) except that a 3-in. gap of blank tape (instead of 3/8 in.) is written prior to the start of the WRITE operation.

### 2.4.10 WRITE END OF FILE (5)

An end-of-file character and end-of-file gap are written on the tape. The parity is set automatically. The density must be set equal to that for the rest of the data on the tape (as must the CORE DUMP mode bit for 9-channel tape and densities other than 800 bpi.) The END-OF-FILE and JOB DONE flags are raised when the function is completed. ILLEGAL OP is raised and no tape motion results if the tape is write-locked. BAD TAPE nad PARITY ERROR can also be set indicating miswriting.

#### 2.4.11 SPACE FORWARD (6)

Any number of records may be spaced with a single SPACE FORWARD command. For each record, the TM10A raises the DATA REQUEST flag. The program should respond with a DATAO MTC, or BLKO (the data word itself is irrelevant). If the program does not respond (or responds late), the TM10A spaces one record and stops the tape. If the program responds, the TM10 spaces one record and raises the DATA REQUEST flag again. To space a second record, the program must give another DATAO MTC. If the program gives a CONO MTS, 1 the TM10 does not raise the DATA FLAG again and stops at the end of the current record. To summarize: the TM10A spaces one record for each DATAO from the program except that one record is spaced for 0 DATAOs. The TM10 stops spacing at an end-of-file, regardless of DATAOs. The TM10 also stops spacing at the first end of record following the EOT marker. JOB DONE is raised when the TM10 has finished spacing the last record.

The same density in which the tape was written must be selected. At lower density, the TM10 can miss an end-of-file mark. Parity is not relevant. CORE DUMP must be selected to allow a density of 200 bpi or 556 bpi on 9-channel tape. Other relevant flags are BAD TAPE and EOF.

#### 2.4.12 SPACE FORWARD TO END OF FILE (16)

Spaces any number of records and stops only for END-OF-FILE or EOT. The DATA REQUEST flag is never raised. Otherwise, this function is similar to SPACE FORWARD (6).

2-8

#### 2.4.13 SPACE REVERSE (7)

Spaces one or more records in reverse. The control of the number of records spaced is the same as for SPACE FORWARD (6). Regardless of the number of DATAOs given, the TM10 stops a SPACE REVERSE operation at an END-OF-FILE or at the BOT (beginning of tape, or loadpoint) marker. The EOT marker is ignored. ILLEGAL OP is raised if SPACE REVERSE is attempted and the tape is at the BOT at the start of the operation (no tape motion results). Otherwise, this function is similar to SPACE FORWARD (6).

## 2.4.14 SPACE REVERSE TO END-OF-FILE (17)

Spaces any number of records in reverse and stops only for END-OF-FILE or BOT. The DATA REQUEST flag is never raised. Otherwise, this function is similar to SPACE REVERSE (7).

# 2.5 TAPE FUNCTIONS (TM10B)

## 2.5.1 NO-OP (0)

Clears all status bits except those associated with the transport and NEXT UNIT.

# 2.5.2 NO-OP (10)

Loads a new current transport number and sets JOB DONE when the transport becomes ready or sets TRANSPORT HUNG after one second. Note the NEXT UNIT ENABLE bit description.

# 2.5.3 REWIND (1)

Rewinds the selected transport. Sets JOB DONE as soon as the transport is up to speed. To interrupt at the end of a rewind, wait for JOB DONE and then use NO-OP (10).

# 2.5.4 READ (2)

Data is read in the forward direction only. The WC register in the data channel specifies the number of words to read. The parity and density must be set the same as when the data was written. ILLEGAL OP is set if the transport is 9-channel and neither 800 bpi nor core dump mode is selected. JOB DONE is set at the end of record. Tape begins to move when the data channel is seized. If the data channel terminates operation after the last word in a record is read, the RECORD LENGTH IN-CORRECT flag stays off; this flag comes on if the record ends prematurely (data channel never terminates operation) or if another data word follows the data channel termination; in the latter case, the following words are ignored. DATA LATE is set when the control assembles a 36-bit word and the data channel has not transferred the previous 36-bit word.

#### 2.5.5 READ ACROSS RECORD BOUNDARIES (12)

Like READ (2), but JOB DONE is set only at the first end-of-record after an error, or at an end-of-file, or after the data channel terminates operation, or if the number of characters in a record is not a multiple of six for 7-channel tape.

## 2.5.6 READ/COMPARE (3)

Data is read from the tape by the control and the program sends data from core data channel. The WC register in the data channel specifies the number of words to read/compare. The two words are compared in the control and, if equal, the process continues with the next pair of words. If not equal, the READ/COMPARE ERROR flag is set at the end of record.

In READ/COMPARE mode (3 or 13), the data channel supplies the first data word before the TM10 is ready to receive it. Therefore, the first word of data from memory must be a 0. The second word from memory must match the first word from tape, and so on. The 0 word may be inserted conveniently into the data stream through use of the data channel's data-chaining facility. If the first word from memory is not 0, a READ/COMPARE ERROR always occurs.

For other flags, modes, and timing considerations, see READ mode.

#### 2.5.7 RD/CMP ACROSS RECORD BOUNDARIES (13)

Like READ ACROSS RECORD BOUNDARIES (12), but compares.

## 2.5.8 WRITE (4)

Data may be written in any of three densities (200 bpi, 556 bpi, or 800 bpi) on 7-channel transports, at 800 bpi in IBM-compatible format on 9-channel transports, or at any of three densities or in core mode on 9-channel transports. The WC register in the data channel specifies the number of words to write. Either even or odd parity may be selected. When selecting even parity, care must be taken never to write a character of all 0s on tape, since such a character will be ignored while reading. A WRITE command to a write-locked tape results in the ILLEGAL OP flag and no tape motion. To terminates a record, the data channel terminates CHANNEL BUSY. JOB DONE is set when the read-after-writing circuit reads and checks the longitudinal parity. The BAD TAPE flag could be set at this time.

#### 2.5.9 WRITE WITH EXTENDED EOR GAP (14)

Similar toWRITE (4) except that a 3-in. gap of blank tape (instead of 3/8 in.) is written prior to the start of the WRITE operation.

#### 2.5.10 WRITE END-OF-FILE (5)

An end-of-file character and end-of-file gap are written on the tape. The parity is set automatically. The data channel is not used for this operation. The density must be set the same as for the rest of the data on the tape (as must the CORE DUMP mode bit for 9-channel tape and densities other than 800 bpi.) The END-OF-FILE and JOB DONE flags are raised when the function is completed. ILLEGAL OP is raised and no tape motion results if the tape is write-locked. BAD TAPE and PARITY ERROR can also be set indicating miswriting.

#### 2.5.11 SPACE FORWARD (6)

For this operation, the data channel uses its WC register to count the number of records to space. When the specified number of records are spaced, the data channel terminates operation. However one record is spaced for a 0 WC. The TM10 stops spacing at an end-of-file, regardless of the WC and also at the first end of record following the EOT marker. JOB DONE is raised when the TM10 has finished spacing the last record.

The same density at which the tape was written must be selected. At lower density, the TM10 can miss an end-of-file mark. Parity is not relevant. CORE DUMP must be selected to allow 200 bpi or 556 bpi on 9-channel tape. Other relevant flags are BAD TAPE and EOF.

#### 2.5.12 SPACE FORWARD TO END-OF-FILE (16)

Spaces any number of records and stops only for END-OF-FILE or EOT. The data channel is not used for this operation. Otherwise, this function is similar to 6-SPACE FORWARD.

## 2.5.13 SPACE REVERSE (7)

Spaces one or more records in reverse. Control of the number of records spaced is the same as for SPACE FORWARD (6). Regardless of the records specified by the data channel, the TM10 stops a SPACE REVERSE operation at an EOF or at the BOT (beginning of tape, or loadpoint) marker. The EOT marker is ignored. ILLEGAL OP is raised if SPACE REVERSE is attempted and the tape is at the BOT at the start of the operation (no tape motion results). Otherwise, this function is similar to SPACE FORWARD (6).

# 2.5.14 SPACE REVERSE TO END-OF-FILE (17)

Spaces any number of records in reverse and stops only for EOF or BOT. The data channel is not used. Otherwise, this function is similar to SPACE REVERSE (7).

#### 2.6 TM10 COMMAND TIMING

At an end of record, the TM10A raises the JOB DONE flag before stopping the tape. If the program supplies a new command to the same transport requiring the same direction of motion as the previous command, the tape never stops moving provided the program does not take too long. The exact duration of "too long" depends on the stopping characteristics of the particular transport involved. If the program is slow, or if the direction of motion is different for the new command, the tape is automatically stopped and the command is held up until the transport becomes idle. If the new command is for a different transport number, the TM10 retains the old transport number until the appropriate time for giving the stop signal. Thus, CONI MTS will return the former unit number until that unit is stopped, whereupon the unit number is automatically changed to the new one. The TM10 then waits for the newly selected unit to become idle before starting it in motion. If this waiting period is more than 1s, the TRANSPORT HUNG flag is raised.

If a CONO MTC, is given before the JOB DONE flag comes on, the command in progress is aborted.

## 2.7 9-TRACK TAPE

Nine-track tape provides eight data channels and one parity bit across the width of the tape. To be IBM compatible, the program must select 800 bpi and odd parity. In this mode, four 8-bit bytes are written from each 36-bit word and 4 bits are ignored. The bytes are left justified packed as by the byte instructions. During reading, the rightmost 4 bits of the 36-bit words are loaded with the parity error bits corresponding, left to right, with the 4 data bytes.

Nine-track tape provides an error correcting feature whereby a suitable program can detect if errors are in one channel of the tape, or more than one channel. Once the bad channel is identified, the record can be reread and the bit in the bad channel will be complemented on every parity error. This feature is based on the cyclic redundancy character (CRC). During writing, a suitable CRC character is computed and automatically written on the tape in the end of record gap by the TM10. During reading, the CRC character from the tape is obtained by waiting for JOB DONE (and doing a CONO MTS, 2 in the TM10A only followed by a DATAI MTC, without waiting for the DATA REQUEST flag. See the Proposed American Standard for Recorded Magnetic Tape, <u>Communications of the ACM</u>, Volume 9, Number 4, April 1966, page 285, for further details. In order to facilitate the use of 9-channel tape for binary data applications (36-bit words) and to take advantage of the two extra channels, the TM10 has a CORE DUMP mode. In this mode the program may select any density. Thirty-six bit words are written in 5 bytes (as opposed to 6 on a 7-channel tape). The first four bytes are the four leftmost 8-bit bytes of the word. The fifth byte contains 0s in the left two bits and the rightmost six bits of the data word in the right six bits. During reading, the two bits that overlap in the above scheme are ORed together. The parity error bits are not obtainable in this mode. However, the CRC character is written correctly. The end-of-file character on 7-channel tape is 17 (octal) with a 0 parity bit. On 9-channel tape, the end-of-file is 023 with a 0 parity bit. In either case, the end-of-file is a 3-in. gap of erased tape followed by a single-character acter record. On 9-channel tape, the end-of-file record does not include a 0 CRC character.

# CHAPTER 3 THEORY OF OPERATION

This chapter provides a complete description of the theory of operation of the TM10A and TM10B Magnetic Tape Control Units. General and summary information of the data channel is presented first. This is followed by a detailed logic description of the circuits common to both the TM10A and TM10B; where the TM10A and TM10B differ is also fully discussed. The logic drawings referenced in this discussion are contained in Volume III of the PDP-10 Peripheral Device Engineering Drawing Set, DEC-10-I6CA-D, these logic drawings are referenced only by the last suffix. For example, logic drawing D-BS-TM10-0-CM1 is referenced as drawing CM1.

# 3.1 DF10 DATA CHANNEL DESCRIPTION

A complete description of the DF10 Data Channel is given in the DF10 Data Channel Instruction Manual. However, in order to understand the operation of the TM10B, it is necessary to understand how the DF10 communicates with the TM10B. Therefore, a brief description of the DF10 is given below.

This description is relevant for the TM10B and not for the TM10A. The MTS DATAO instruction is issued to provide an initial control word address. The control word address is held by the TM10B until it gains access to the data channel. When the TM10B gains access to the data channel, it sends the initial control word address to the data channel which stores this address in the control word address register. The data channel then fetches the control word normally consisting of WC (word count) and DA (data address). The WC and DA are stored in their respective data channel registers. The WC register specifies the 2's complement of the number of data words to transfer and the DA specifies the core memory location minus 1. DA is incremented by 1 prior to the first transfer. After a word transfer between core memory and the device communicating with the data channel, the WC is decremented and the DA is incremented. When the WC is reduced to 0, the number of words initially specified have been transferred. The control word address register is incremented and the next control word is fetched from core memory. If the control word contains all 0s, the end of communications is specified and the data channel terminates operation.

A number of devices can be connected to the data channel; however, the data channel communicates with only one at a time. To establish, maintain, and terminate communications, the following signals are exchanged between device and data channel.

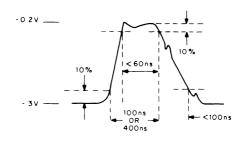

| DATA BUS                    | This incorporates 36 bidirectional data pulse lines. These signals are 100 ns negative going pulses swinging from ground to -3V.                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHANNEL PULSE               | This 100 ns negative going pulse is sent from the channel.<br>It accompanies the data pulses when the channel is sending<br>data to the device. It also signifies a readiness to receive<br>data when the device is trying to send data to memory.                                                                                                                                                                                                                                                                   |

| DEVICE PULSE                | The signal is similar in function to the channel pulse signal.<br>It accompanies the data when the device is sending, and<br>signifies readiness to receive when data flow is toward the<br>device.                                                                                                                                                                                                                                                                                                                  |

| CHANNEL START               | This is a level (-3V for true) which is sent from the device<br>to the channel. It will start the channel into operation<br>when asserted.                                                                                                                                                                                                                                                                                                                                                                           |

| SA WRITE                    | This signal controls the direction of data transfer. When<br>true, it signifies the device is writing some medium (reading<br>memory). The timing is the same as that for the CHANNEL<br>START.                                                                                                                                                                                                                                                                                                                      |

| CHANNEL BUSY                | This signal comes from the channel and is asserted (-3V)<br>sometime after CHANNEL START is asserted from the device.<br>The device must not put anything on the bus until this signal<br>is asserted. When this signal goes false after having been<br>true, the channel has terminated for one reason or another.<br>CHANNEL START and CHANNEL BUSY must all be false<br>for at least 400 ns prior to reassertion of CHANNEL START.                                                                                |

| WRITE CONTROL WORD REQUEST  | This negative 100 ns pulse from the device causes the chan-<br>nel to store the current contents of the data address register<br>and the control word address register into memory location<br>B + 1, where B (an even number) is the channel initial con-<br>trol word address. The contents of the control word address<br>register go into bit positions 0-17 and the contents of the<br>data address register into 18-35. Upon any channel termi-<br>nation, an automatic WRITE CONTROL WORD REQUEST is<br>made. |

| WRITE CONTROL WORD COMPLETE | This pulse from the channel signals the completion of the operation requested above. This pulse does not occur on the automatic transfer.                                                                                                                                                                                                                                                                                                                                                                            |

| NO SUCH MEMORY              | This pulse is sent from the channel as CHANNEL BUSY goes off and indicates that the memory addressed failed to re-spond.                                                                                                                                                                                                                                                                                                                                                                                             |

| CONTROL WORD PARITY ERROR   | If a control word is fetched from the memory by the channel<br>and this word has a parity error, CHANNEL BUSY is reset<br>and this pulse is sent to the device from the channel.                                                                                                                                                                                                                                                                                                                                     |

| DATA WORD PARITY ERROR      | This pulse accompanies the data and the CHANNEL PULSE<br>when a data word which was read from memory with a parity<br>error is sent to the device.                                                                                                                                                                                                                                                                                                                                                                   |

The I/O devices attached to a data channel are arranged as shown in Figure 3-1 (only the pertinent signals are shown). In order for a device to gain access to the data channel, it must generate a CHANNEL START and receive a CHANNEL BUSY. If a device is not actively engaged with the data channel, it relays the CHANNEL START and CHANNEL BUSY. A device that is relaying CHANNEL START is prevented from generating its own CHANNEL START. A device that is busy with the data channel does not relay CHANNEL BUSY.

Figure 3-1 Data Channel Interface

To further examine data channel communication, assume that devices 1 and 2 are not busy and device 3 initiates communication by asserting its CHANNEL START signal. CHANNEL START is applied to device 2 and since device 2 is not busy it relays the CHANNEL START. Similarly, device 1 relays CHANNEL START. The data channel acknowledges the CHANNEL START by asserting the CHANNEL BUSY. The data channel does not know which device requested access; the only thing it knows is that it received a CHANNEL START and it responds by asserting CHANNEL BUSY. Furthermore, the data channel responds only to stimulus of the control signals by transferring data to and from the data bus or starting or stopping operation. It is the responsibility of devices to determine which has access.

Since devices 1 and 2 are not busy, they relay the CHANNEL BUSY signal to device 3. Upon receipt of CHANNEL BUSY, device 3 has access to the data channel and can communicate via the data bus. A device requires two conditions to gain access to the data channel: the assertion of its own CHANNEL START and the receipt of CHANNEL BUSY.

To demonstrate this dual requirement, assume that device 2 is communicating with the data channel. It has asserted its CHANNEL START and received a CHANNEL BUSY. It does not relay CHANNEL BUSY to device 3. If now, device 3 attempts communications, it can assert at CHANNEL START since it is not relaying CHANNEL START. Since device 2 is already generating a CHANNEL START, it essentially ignores the CHANNEL START from device 3. The CHANNEL BUSY is not relayed to device 3; therefore, device 3 does not gain access to the data channel because of the two requirements: assertion of CHANNEL START and receipt of CHANNEL BUSY. Device 3 now must wait until device 2 has finished with the data channel.

Either device 2 or the data channel can terminate operation. The data channel terminates operation by removing CHANNEL BUSY and the device responds by negating CHANNEL START. After termination, device 3 is free to communicate; however, the data channel requires at least 400 ns time between the negation of CHANNEL BUSY and CHANNEL START and the assertion CHANNEL START. In this case, this requirement is imposed upon device 2 (or any other device that is generating or relaying CHANNEL START and receive the on-to-off transition of CHANNEL BUSY). When termination occurs, all devices must inhibit the generation or relaying of CHANNEL START for 400 ns.

#### 3.2 NRZ RECORDING

The actual technique of recording on magnetic tape is called the non-return-to-zero (NRZ) method. In this method, a reversal of the direction of magnetization in a channel represents a 1 bit, a lack of reversal represents a 0 bit. Writing is achieved by using a flip-flop to control the direction of magnetizing current in each channel write head; the group of flip-flops is called the write buffer. By applying the 1s lines to the complement inputs of the write-buffer, each channel reverses its flux only when a 1 bit is to be written for a character. Further, the write buffer accumulates the LPCC (longitudinal parity check character) to be written as an EOR character. When the write buffer is cleared at EOR time, the LPCC character is thus written automatically.

The NRZ recording method provides self-clocking during reading since a transition (or flux reversal) in any channel, signifying a 1 bit for that character in that channel, is used to strobe or sense all seven channels for that character. Ideally, all transitions for a single character would be sensed simultaneously by the 7-channel read head. In fact, tape skew makes these transitions (if more than one in a single character) nonsimultaneous on reading. There may be a difference in alignment of the read head with respect to the write head recording the tape (static skew). The tape alignment to the read head is apt to vary during tape travel (dynamic skew). To accommodate these timing variations between channels due to skewing, the first detected transition for a character initiates a delay before the character is strobed. This delay is selected to accept the maximum skewing produced at the linear tape transport speed with the designated tape density.

A simplified block diagram of the tape system write and read paths for a single channel is presented in Figure 3-2. The write path (WP) is shown at the top of the figure. The WRITE flip-flop in the write amplifier is complemented at each WP pulse if the data buffer for that particular character contains a 1. When gated by a WRITE ENABLE signal, the write amplifier drives one or the other of the two opposing directions at the write head. If the WRITE ENABLE level is not present, no current flows through the coil. Whenever a 1 is to be written on a tape, the WRITE flip-flop is complemented by the WP pulse. The transition of the WRITE flip-flop terminates the current in one direction and starts it in the other direction, changing the direction of the tape magnetization, and thus writing a 1 on tape. As long as the WRITE flip-flop remains in the same state, the current flows in the same direction, and 0s are written on the tape. The tape is then magnetized in the same direction over a series of character spaces.

Figure 3-2 Tape Write and Read Signal Flow

The read path is shown at the bottom of Figure 3-2. The tape reaches the read heads shortly after traversing the write head. As long as the direction of tape magnetization remains constant, no current flows through the read head coil. Each change in the direction of tape magnetization induces a current in the read head. The read current produced by two consecutive tape 1s is shown in the wave-form near the read head. These signals are applied to a differential read amplifier to provide ampli-

fication for different mode signals, but only fractional amplification for common mode signals. The output of the read amplifier is then sent through a slicing rectifier. The rectifier output pulse is of a single polarity although input pulses are of both polarities from the read amplifier. No slice output is generated, however, unless the input exceeds a designated voltage threshold level. A low-level noise input cannot generate an output pulse. Next, the slicing rectifier output is applied to a peak detector. The peak detector produces a logic pulse output at the peak of the input pulse.

#### 3.3 SYSTEM DESCRIPTION

#### 3.3.1 TM10A

A simplified block diagram of the TM10A is shown in Figure 3-3. Assuming a write operation, the program issues a CONO 340 I/O instruction. It is decoded by the I/O bus control circuits to generate the MTC CONO pulses that load the specified parameters (i.e., write, parity mode, density, etc.) into the command register. The appropriate motion commands are transferred to the selected tape transport. A short delay is implemented to provide the tape inter-record gap. During this delay, the DATA REQUEST signal enables the data interrupt channel to generate an interrupt. The executive program responds to the interrupt by issuing a DATAO 340 which loads the hold register (HR) The program cannot respond quickly enough to load the buffer register (BR) directly before recording (or reading) starts. Therefore, the hold register is provided to buffer the data between the PDP-10 and the buffer register. Whenever the buffer register is empty, the TM10A transfers the data word in the hold register to the buffer register and generates a DATA REQUEST to obtain the next word to be written.

After the inter-record gap delay and buffer register loading, the write operation begins. Assuming 7-track operation, the buffer register 36-bit word must be divided into six 6-bit characters for writing on tape. The character counter sequences the 6-bit character from the data buffer. As a 6-bit character is written from the high-order bits of the buffer register, the character counter is incremented to sequence the next low-order 6-bit character. After the six 6-bit characters from the data buffer are written, the DATA REQUEST is set to initiate another word transfer to the buffer register via the hold register.

Operation continues in this manner until the program determines that the desired number of words have been written, at which time the TM10A tape control is notified via a CONO MTS, 1 instruction. The LPCC character is written and write operation terminates. The tape continues in the forward motion until the read circuits detect the end-of-record passing under the read head. Tape motion ceases, the deceleration delay is initiated (time allotted for tape to stop), and the JOB DONE flag is set.

3-6

Figure 3-3 TM10A Tape Control Block Diagram

For the read operation, the initial programming sequence is similar to the one for the write operation. As 6-bit characters are read from tape, they are sequenced into the buffer by the character counter. When the buffer register is full the data is transferred to the HOLD register and the DATA REQUEST initiates a programmed transfer of the data into core memory. Operation continues until the read circuits detect the end-of-record.

As shown in Figure 3-3, the tape control status can be transferred to the PDP-10 by using the appropriately coded CONI instructions. Moreover, the JOB DONE flag and the error bits generate an interrupt separate from the DATA REQUEST interrupt.

# 3.3.2 TM10B

A simplified block diagram of the TM10B is shown in Figure 3-4. Assuming a write operation, the program issues a CONO 340 and a DATAO 344 instruction. The DATAO 344 is decoded by the I/O bus control circuits to generate MTS DATAO which loads the control word initial address register. The content of this register will be subsequently transferred to the DF10. The CONO 340 instruction is decoded to generate the MTC CONO pulses that load the specified parameters (write, read, parity mode, density, etc.) into the function register.

Before writing can begin, the TM10B must gain access to the data channel. Therefore, it makes a request by generating CHANNEL START. If data channel is not busy, it responds with CHAN-NEL BUSY. The TM10B sends the initial control word address to the data channel. The channel control circuits then generate the OK TO GO signal.

A short delay is implemented to provide the tape inter-record gap delay. The DEVICE PULSE requests the first 36-bit data word to be recorded. The data channel responds by loading the buffer register.

After the inter-record gap delay and buffer register loading, the write operation begins. Assuming 7-track operation, the buffer register 36-bit word must be divided into six 6-bit characters for writing on tape. The character counter sequences the 6-bit character from the data buffer. As a 6-bit character is written from the high-order bits of the data buffer, the character counter is incremented to sequence the next low-order 6-bit character. After the six 6-bit characters from the data buffer are written, the DEVICE PULSE initiates another word transfer to the buffer register via the data channel.

Operation continues in this manner until the data channel fetches a 0 control word signifying that the required data has been recorded. The data channel thus removes the CHANNEL BUSY signal to terminate operation. The LPCC character is written and write operation terminates. The tape

3-8

Figure 3-4 TM10B Tape Control Block Diagram

continues in the forward motion until the read circuits detect the end-of-record passing under the read head. Tape motion ceases, the deceleration delay is initiated (time allotted for tape to stop), and the JOB DONE flag is set.

For the read operation, the initial programming sequence is similar to write. As 6-bit characters are read from tape, they are sequenced into the buffer register by the character counter. When the buffer register is full, the DEVICE PULSE initiates a data channel transfer of the buffer register word into core memory. Operation continues until the read circuits detect the end-of-record.

## 3.4 TM10A INITIAL OPERATION

The MTC CONO instruction loads the parameters (tape function, density mode, unit number, priority interrupt channel numbers, etc.) into the command register as shown on drawing CM1 and CM2. The tape function register (CM FCN0-FCN3) is decoded to specify the operation. Since we are assuming initial operation, the content of CM NEXT UNIT (0-2) register (drawing CM2) is transferred to CM UNIT (0-2) register (drawing CM1). The TGO signal is false at this time. The CM UNIT register (via drawing TB) selects the desired tape drive.

The MTC CONO SET pulse also sets the CM WAITING flip-flop (drawing CM2). After a 1 µs delay, the CM UNIT OK flip-flop is set. If the selected tape unit is ready (signal TB TUR is true), the CM LEGAL TEST pulse is generated. This pulse tests the legal conditions (drawing ST). If any of the following illegal conditions are true, the ST ILLEGAL OP flip-flop is set.

- a. Writing on a protected tape (CM WRITING and TB WL are true).

- b. Write mode and tape is at end-of-tape (WRITING and TB EOT true).

- c. Space reverse and tape at beginning of tape (CM SP REV and TB BOT true).

- d. 9-channel operation and not 800 bpi density; and not core dump mode.

If the ST ILLEGAL OP flip-flop gets set, an interrupt is generated (drawing CM2), and the operation terminates. Assuming no illegal operation, the CM LEGAL TEST DONE signal generates CC OK TO GO which fires the CM MT GO pulse. (Note the jumper between H15 pins U and V which is present only on TM10A). The CM MT GO sets the TGO flip-flop (drawing T2) to start the operation as described in Section 3.6. The CM NO-OP DONE pulse (if present) sets the ST JOB DONE flip-flop.

#### 3.5 TM10B INITIAL OPERATION

Operation of the TM10B starts when the PDP-10 processor issues an MTS DATAO instruction to transfer the data channel initial control word initial address and an MTC CONO instruction to set up initial parameters. The MTS DATAO instruction loads the IA27-IA34 (initial address, drawing CC) register with the control word initial address. This will be subsequently transferred to the data channel. The MTC CONO instruction loads the parameters (tape function, density mode, unit number, priority interrupt channel number, etc.) into the command register as shown on drawing CM1 and CM2. The tape function register (CM FCN0 - FCN3) is decoded to specify the operation. Since we are assuming initial operation, the CM NEXT UNIT 0 - 2 register (drawing CM2) is transferred to CM UNIT 0-2 register (drawing CM1). The TGO signal is false at this time. The CM UNIT register (via drawing TB) selects the desired tape drive.

The MTC CONO SET pulse also sets the CM WAITING flip-flop (drawing CM2). After a 1 µs delay, the CM UNIT OK flip-flop is set. If the selected tape unit is ready (signal TB TUR is true), the CM LEGAL TEST pulse is generated. This pulse tests the legal conditions (drawing ST). If any of the following illegal conditions are true, the ST ILLEGAL OP flip-flop is set.

a. Writing on a protected tape (WRITING and TB WL are true).

b. The write mode specified and the tape is at end-of-tape (WRITING and TS EOT true).

c. A space reverse, specified and tape is at beginning of tape (CM SP REV and TB BOT true).

d. 9-channel operation and not 800 BPI density and not core dump mode.

If the ILLEGAL OP flip-flop gets set, an interrupt is generated (drawing CM1), and the operation terminates. Assuming no illegal operation, the CM LEGAL TEST DONE signal (drawing CM2) sets the CC CHN SYNC (drawing CC) to request access to the data channel. Note on drawing CM2 that the W990 module is removed for TM10B operation. Therefore, we must wait for the CC OK TO GO signal which signifies that the tape control has access to the data channel for those operations that require the data channel. For operations not requiring the data channel, the CC NEED CHANNEL signal (drawing CC) immediately generates CC OK TO GO.

With CC CHN SYNC set, the TM10B requests access to the data channel. The TM10B must now wait until it gains access to the data channel. If the data channel is busy with another device, the TM10B must wait until the data channel has completed its operation. For the ensuing description of channel control, it is assumed that the data channel is initially busy with another device.

The CC NEED CHANNEL (drawing CC) is true as previously described to request access to the data channel. The CC ACTIVE flip-flop, which signifies that the TM10 control has access to the data channel, is reset, since it is assumed that the data channel is busy with another device. The CHB CHANNEL START IN signal (drawing CHB) will be asserted and it asserts CHB CHANNEL START OUT. (Here we are assuming that the TM10B is between another device and the data channel.) Similarly, CHB CHANNEL BUSY IN is relayed as CHB CHANNEL BUSY OUT and CHB SA WRITE IN is relayed as CHB SA WRITE OUT.

The normal termination point of a data transfer is when the data channel fetches a 0 control word. It then terminates operation by removing the CHANNEL BUSY signal. The device that is busy recognizes the removal of CHANNEL BUSY as the key to stop operation and thus inhibits its CHANNEL START out. On the other hand, the device can terminate the operation for reasons such as parity errors, etc., by removing its CHANNEL START. The data channel responds by inhibiting CHANNEL BUSY. Regardless of which terminates, it requires the negation of both CHANNEL START IN and CHANNEL BUSY IN before the TM10B gains access to the data channel. When CHB CHANNEL BUSY IN, CC ACTIVE (0), and CHB CHANNEL START are true, the CC TERMINATE pulse is generated to set the CC INHIB (inhibit) flip-flop. Two hundred and fifty nanoseconds later CC TERMINATE DY clears the CC CHANNEL STARTED which in turn sets the CC ACTIVE flip-flop. Note that INHIB prevents ACTIVE from generating a CHANNEL START at this point. After another 250 ns, the CC RESET pulse is generated and resets the INHIB flip-flop. With CC INHIB reset and CC GRAB CHANNEL true, ACTIVE now generates a CHANNEL START which tells the data channel that the TM10B is ready to start operation, assuming no illegal status (ST ILLEGAL OP (0) true). CC GRAB CHANNEL is true due to CC CHN SYNC (1) being true. CHANNEL START also prevents any other device on the bus (closer to the data channel) from gaining access to the data channel in the same manner that the CHANNEL STARTED flipflop inhibits the TM10B (note that CHB CHANNEL START OUT holds CC CHANNEL STARTED in the set state).

The data channel responds to CHANNEL START by asserting CHANNEL BUSY. The receipt of CHANNEL BUSY by the TM10B is the acknowledgement that it has access to the data channel. The TM10B receives CHANNEL BUSY IN (CHB CHN BUSY IN, drawing CHB) but does not relay it. The CHB CHN BUSY IN signal ANDed with CC ACTIVE generates CC CHN SEIZED.

The CC CHAN SEIZED generates the CC DATA TO CHN pulses which transfer the content of BR to the channel bus (drawings CHND 1 and 2). This transfer sends the initial address data contained in BR 27 - BR 34 to the data channel. CC CHAN SEIZED now generates CC MT START and CC OK TO GO. The CC OK TO GO signal (drawing CM2) now generates CM MT GO which sets the T GO flipflop to start the operation as described in Sections 3.4 and 3.5. CM MT GO also generates the initial device pulse (CHB DEV PLS, drawing CHB) to inform the data channel that the tape control is ready to transfer data. Since the tape control has access to the data channel, the CM MT GO pulse clears CC CHN SYNC and CC WAIT DEL.

Operation now continues as explained in Section 3.6 with the inter-record delay, after which data is read from or recorded onto the tape. The subsequent data transfer between tape control and data channel is described in Section 3.13.

## 3.6 INTER-RECORD GAP DELAY

According to tape format, between each record there is an inter-record gap. Assuming that the tape is stopped, before reading or writing the tape must attain operating speed within the interrecord gap. To provide the inter-record gap, the tape control timing circuits incorporate a timing delay which is explained as follows: the TGO flip-flop (drawing T2) is set as previously described; the TGO signal performs the following functions.

a. Sets the T ACCEL (acceleration delay) flip-flop (drawing T1).

b. Generates the SET TAPE FCN pulse (drawing T2 which shuts the transport status off the bus and sends to the transport, the command direction, forward reverse, rewind, and write (drawing TB). The transport that receives the command sets the function into the tape transport register.

c. Generates the TB MOVE signal (drawing TB) to move the tape in the specified direction.