DX11-B system 360/370 channel to PDP-11 unibus interface maintenance manual

DX11-B system 360/370 channel to PDP-11 unibus interface maintenance manual

digital equipment corporation • maynard, massachusetts

1st Edition, August 1972 2nd Printing (Rev) March 1973 3rd Printing, July 1973

# Copyright © 1972, 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

CONTENTS

# CHAPTER 1 GENERAL DESCRIPTION

| 1.1   | Scope                  | 1-             |

|-------|------------------------|----------------|

| 1.2   | Introduction           | 1-             |

| 1.3   | System Description     | 1-             |

| 1.4   | Mechanical Description | 1-             |

| 1.5   | Specifications         | 1.             |

| 1.5.1 | Physical               | 1-<br>1-<br>1- |

| 1.5.2 | Environmental          | 1.             |

| 1.5.3 | Electrical             | 1.             |

| 1.5.4 | Performance            | 1.             |

| 1.6   | Engineering Drawings   | 1.             |

| 1.7   | Terminology            | 1.             |

# CHAPTER 2 INSTALLATION

| 2.1       | Scope                                           | 2-1  |

|-----------|-------------------------------------------------|------|

| 2.2       | Configuration Differences                       | 2-1  |

| 2.3       | Unpacking                                       | 2-1  |

| 2.4       | Inspection                                      | 2-2  |

| 2.5       | Space Requirements                              | 2-2  |

| 2.6       | Power and Cable Requirements                    | 2-2  |

| 2.7       | Installation Procedure and Checkout             | 2-4  |

| 2.8       | Customer Acceptance Procedure                   | 2-10 |

| 2.9       | IBM Control Unit and Device Address Jumper Card | 2-10 |

| 2.10      | NPR Timeout MONO (M306) Calibration Procedure   | 2-12 |

| 2.11      | DXTO Calibration Procedure                      | 2-12 |

| 2.12      | 2848/FRIEND Test Procedure                      | 2-14 |

| 2.13      | CTP/FRIEND System Test                          | 2-14 |

| 2.14      | Cautions and Warnings                           | 2-15 |

| 2.15      | Cable Check                                     | 2-16 |

| CHAPTER 3 | OPERATION                                       | •    |

| 3.1       | Scope                                           | 3-1  |

| 3.2       | Controls and Indicators                         | 3-1  |

| 3.3       | Special Operating Procedures                    | 3-8  |

| 3.3.1     | 2848 RESPONDER Operator's Guide                 | 3-8  |

| 3.3.2     | DMA4 Operator's Guide                           | 3-9  |

| 3.3.3     | DME Operator's Guide                            | 3-9  |

| 3.3.4     | FRIEND Operator's Guide                         | 3-11 |

|           |                                                 |      |

# CHAPTER 4 PROGRAMMING

| 4.1 | Scope                                    | 4-1 |

|-----|------------------------------------------|-----|

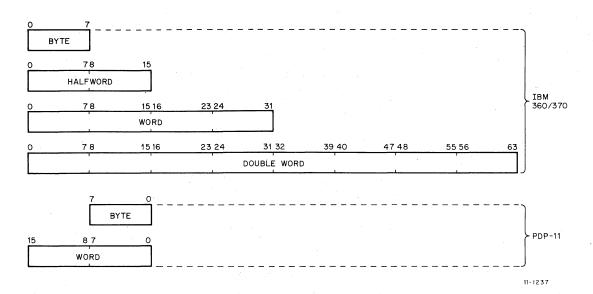

| 4.2 | IBM 360/370 and PDP-11 Format Comparison | 4-1 |

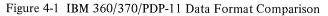

| 4.3 | IBM 360/370/DX11-B Communication         | 4-2 |

# CONTENTS (Cont)

|        |   |                                            | Page |

|--------|---|--------------------------------------------|------|

| 4.4    |   | DX11-B/PDP-11 Communication                | 4-2  |

| 4.5    |   | DX11-B Formats                             | 4-3  |

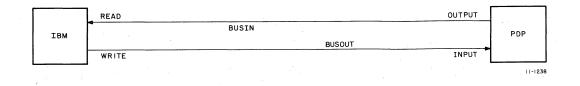

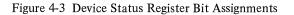

| 4.5.1  |   | Device Status Register (DXDS)              | 4-4  |

| 4.5.2  |   | Command and Address Register (DXCA)        | 4-6  |

| 4.5.3  |   | Control Unit Status Register (DXCS)        | 4-7  |

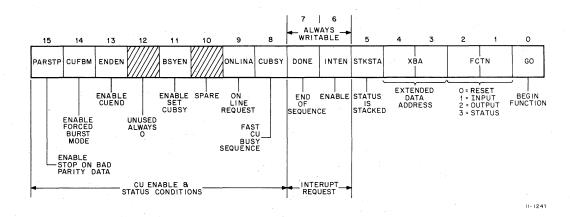

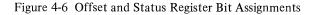

| 4.5.4  |   | Offset and Status Register (DXOS)          | 4-9  |

| 4.5.5  |   | Bus Address Register (DXBA)                | 4-10 |

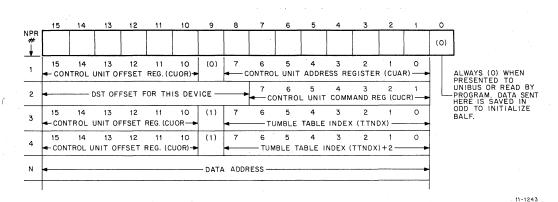

| 4.5.6  |   | Byte Count Register (DXBC)                 | 4-11 |

| 4.5.7  |   | Maintenance Out Register (DXMO)            | 4-11 |

| 4.5.8  |   | Maintenance In Register (DXMI)             | 4-13 |

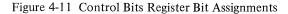

| 4.5.9  |   | Control Bits Register (DXCB)               | 4-14 |

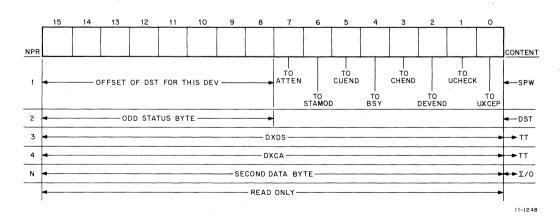

| 4.5.10 |   | Non-Processor Request Data Register (DXND) | 4-16 |

| 4.5.11 |   | Extra Signals Registers (DXES1 and DXES2)  | 4-17 |

| 4.5.12 |   | Maintenance Out Buffered Register (DXMOB)  | 4-18 |

| 4.6    |   | Programming Considerations                 | 4-18 |

| 4.6.1  |   | Hardware/Software Interlock                | 4-18 |

| 4.6.2  |   | Boundary Considerations                    | 4-19 |

| 4.6.3  |   | Interrupt Request                          | 4-19 |

| 4.6.4  |   | Data Transfer                              | 4-20 |

| 4.6.5  |   | Status Presentation                        | 4-20 |

| 4.6.6  |   | On-Line/Off-Line Control                   | 4-20 |

|        | 1 |                                            |      |

# CHAPTER 5 THEORY OF OPERATION

| 5.1     | Scope                                      | 5-1  |

|---------|--------------------------------------------|------|

| 5.2     | Functional Description                     | 5-1  |

| 5.3     | Block Diagram Discussion                   | 5-2  |

| 5.3.1   | IBM Interface Operation                    | 5-3  |

| 5.3.2   | IBM Control Operation                      | 5-11 |

| 5.3.3   | Unibus Interface Operation                 | 5-12 |

| 5.3.4   | PDP-11 Control Operation                   | 5-12 |

| 5.3.5   | Central Control Operation                  | 5-13 |

| 5.3.6   | Channel Simulator Operation                | 5-14 |

| 5.4     | Sequences of Operation                     | 5-14 |

| 5.4.1   | IBM Sequences                              | 5-15 |

| 5.4.1.1 | Selector Channel-Initiated Sequences (CHI) | 5-15 |

| 5.4.1.2 | Control Unit Initiated Sequences (CUI)     | 5-19 |

| 5.4.1.3 | Reset Sequences                            | 5-20 |

| 5.4.1.4 | Multiplexer Channel Differences            | 5-22 |

| 5.4.1.5 | IBM Sequence Summary                       | 5-24 |

| 5.4.2   | DX11-B Sequences                           | 5-27 |

| 5.4.2.1 | Register Organization                      | 5-27 |

| 5.4.2.2 | Flow Diagram Conventions                   | 5-29 |

| 5.4.2.3 | Design Flows                               | 5-30 |

iv

**CONTENTS** (Cont)

|           |                                                            | Page |

|-----------|------------------------------------------------------------|------|

| 5.5       | Circuit Descriptions                                       | 5-40 |

| 5.5.1     | DX11 Device Status Register (DXDS)                         | 5-40 |

| 5.5.2     | Control Unit Status Register (DXCS)                        | 5-41 |

| 5.5.3     | DX11 Bus Address Register (DXBA)                           | 5-41 |

| 5.5.4     | DX11 Byte Counter (DXBC)                                   | 5-42 |

| 5.5.5     | Control Unit Status Register (CUSR) Part of DXOS           | 5-42 |

| 5.5.6     | NPR Data Register (DXND)                                   | 5-43 |

| 5.5.7     | DX11 Control Bits Register (DXCB)                          | 5-43 |

| 5.5.8     | Control Lines Out Register (CONO) Part of DXMO             | 5-44 |

| 5.5.9     | Control Lines In Register (CONI) Part of DXMI              | 5-44 |

| 5.5.10    | IBM Bus-In Lines (BUSI) Part of DXMI                       | 5-45 |

| 5.5.11    | Tumble Table Index (TTNDX)                                 | 5-45 |

| 5.5.12    | Control Unit Address Register (CUAR), Part of DXCA         | 5-45 |

| 5.5.13    | Control Unit Command Register (CUCR), Part of DXCA         | 5-45 |

| 5.5.14    | Unibus Interface                                           | 5-46 |

| 5.5.15    | NPR and INT Control                                        | 5-46 |

| 5.5.16    | Data Bus Multiplexer                                       | 5-47 |

| 5.5.17    | Clock, Phase and Time State Generator                      | 5-47 |

| 5.5.18    | Maintenance Out Buffered Register (DXMOB)                  | 5-47 |

| 5.5.19    | General Controls                                           | 5-48 |

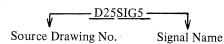

| 5.5.20    | Signals and Gates                                          | 5-48 |

| 5.5.21    | Parity and Address Compare                                 | 5-49 |

| 5.5.22    | IBM Interface                                              | 5-50 |

| 5.5.23    | Select Bypass and Power Fail                               | 5-50 |

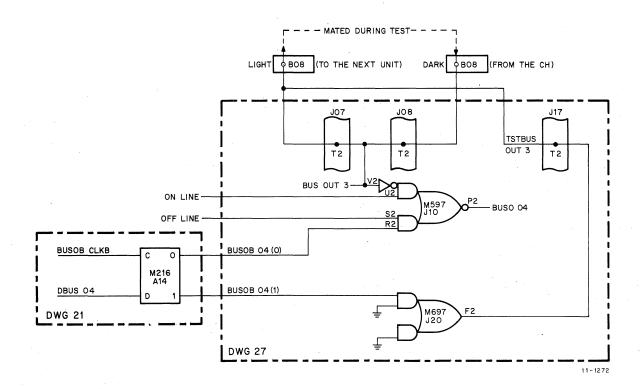

| 5.5.24    | "Bit Slice" and "Select" Loop Trace in Off-Line Cable Mode | 5-50 |

| 5.5.25    | EPO Panel Operation                                        | 5-52 |

| •         |                                                            |      |

| CHAPTER 6 | MAINTENANCE                                                |      |

| 6.1       | Introduction                                               | 6-1  |

| 6.2       | Preventive Maintenance                                     | 6-1  |

| 6.2.1     | Mechanical Checks                                          | 6-1  |

| 6.2.2     | Test Equipment Required                                    | 6-1  |

| 6.3       | Corrective Maintenance                                     | 6-2  |

| 6.3.1     | General Corrective Procedures                              | 6-2  |

| 6.3.2     | Diagnostic Testing                                         | 6-2  |

| 6.3.3     | Vibration Tests                                            | 6-3  |

|           |                                                            |      |

| CHAPTER 7 | ENGINEERING DRAWINGS                                       |      |

| 7.1       | General                                                    | 7-1  |

|           |                                                            |      |

v

APPENDIX A REFERENCE MATERIAL

A.1

# CONTENTS (Cont)

Page

# ILLUSTRATIONS

| Figure No.     | Title Title                                                | Page |

|----------------|------------------------------------------------------------|------|

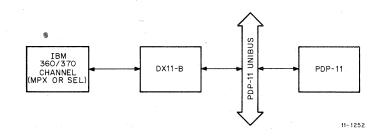

| ( <b>1</b> -1) | DX11-B, System 360/370 Channel to PDP-11 Unibus Interface  | 1-2  |

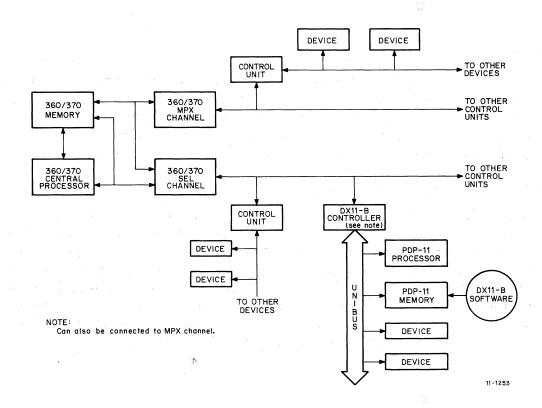

| 1-2            | Typical DX11-B System Block Diagram                        | 1-3  |

| 1-3            | DX11-B Functional Block Diagram                            | 1-4  |

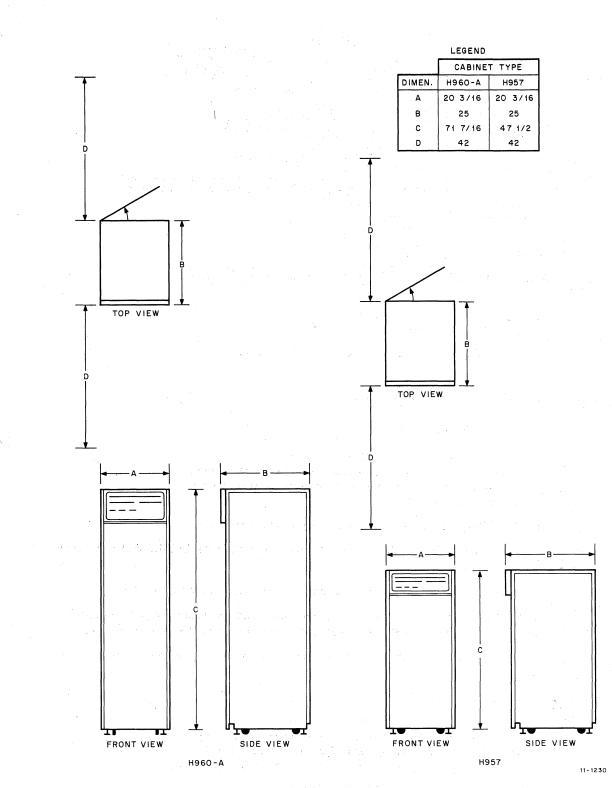

| 2-1            | Overall Dimensions                                         | 2-3  |

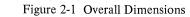

| 2-2 ,          | System Power and Cabling Diagram                           | 2-4  |

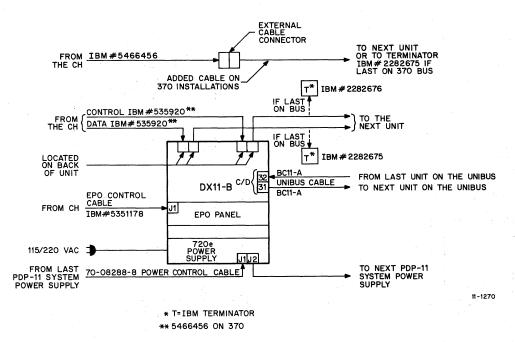

| 2-3            | Normal Cable Connections to Channel Bus if on End of Bus   | 2-5  |

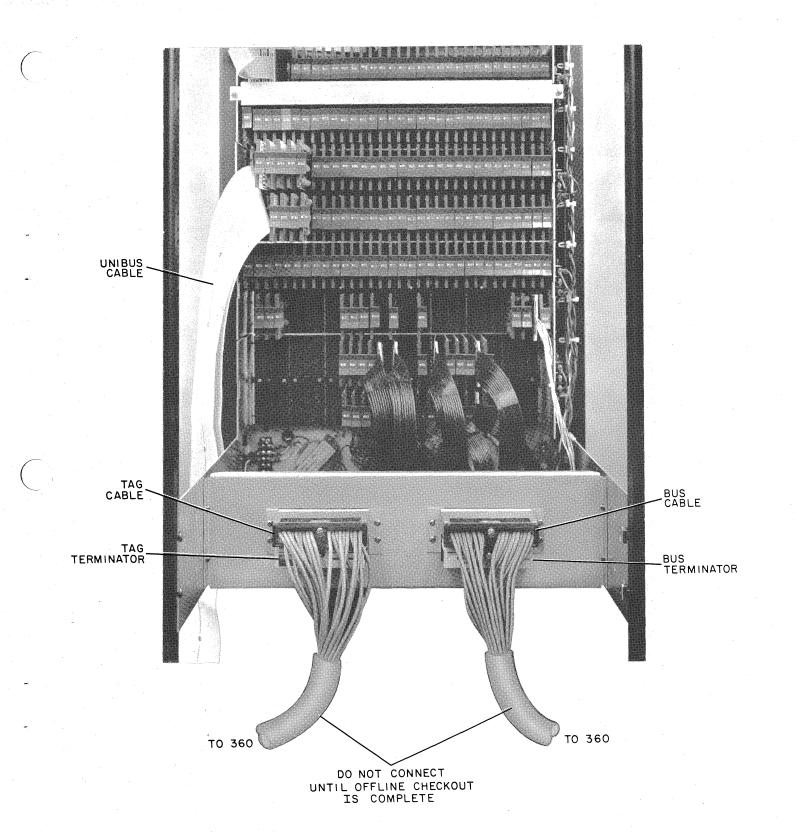

| 2-4            | Normal Cable Connections to Channel if Not on End of Bus   | 2-6  |

| 2-5            | Test Bus Cable Connections with IBM Cables in the Loop     | 2-8  |

| 2-6            | Test Bus Connections Without IBM Cables                    | 2-9  |

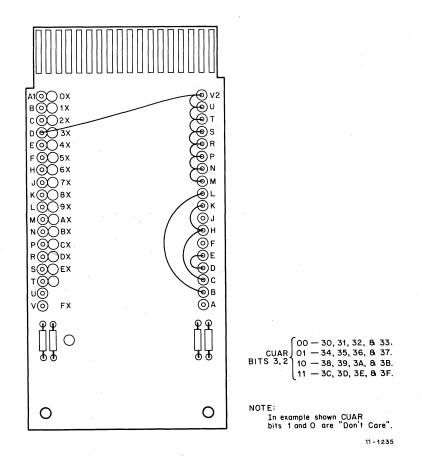

| 2-7            | M908B Module Before Wiring                                 | 2-11 |

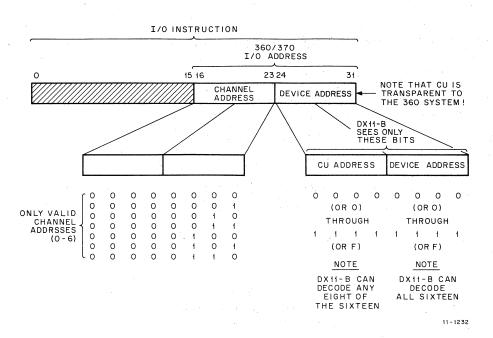

| 2-8            | I/O Address Format                                         | 2-11 |

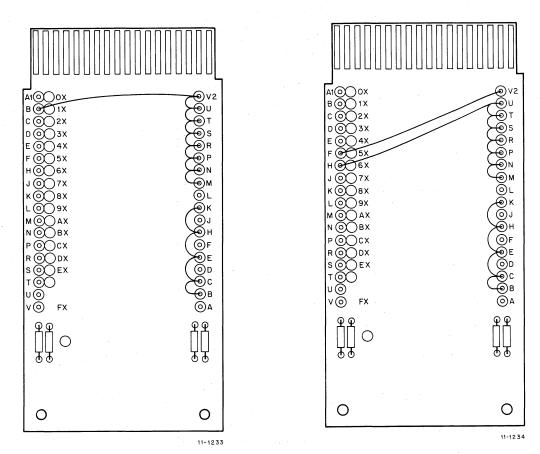

| 2-9            | Example of Wiring for 16 Devices 10 through 1F (1x)        | 2-12 |

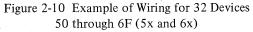

| 2-10           | Example of Wiring for 32 Devices 50 through 6F (5x and 6x) | 2-12 |

| 2-11           | Example of Wiring for Four Devices                         | 2-13 |

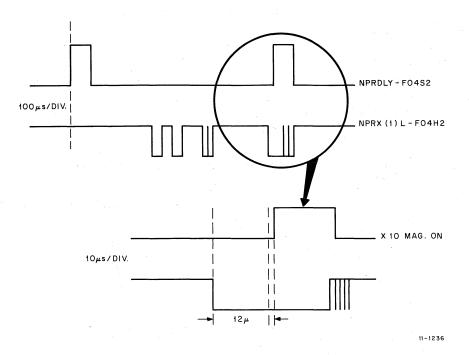

| 2-12           | NPR Timeout Mono Calibration Waveform                      | 2-13 |

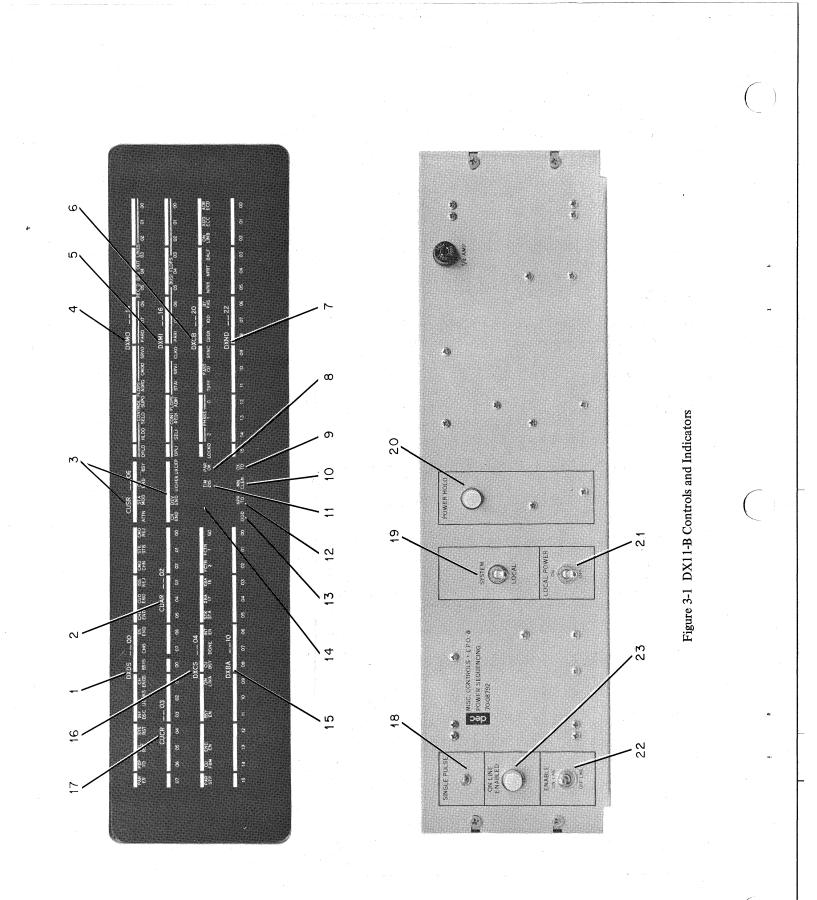

| 3-1            | DX11-B Controls and Indicators                             | 3-2  |

| 4-1            | IBM 360/370/PDP-11 Data Format Comparison                  | 4-1  |

| 4-2            | 360/PDP-11 Transfer Conventions                            | 4-3  |

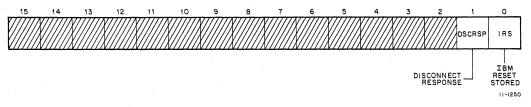

| 4-3            | Device Status Register Bit Assignments                     | 4-4  |

| 4-4            | Command and Address Register Bit Assignments               | 4-7  |

| 4-5            | Control Unit Status Register Bit Assignments               | 4-7  |

| 4-6            | Offset and Status Register Bit Assignments                 | 4-10 |

| 4-7            | Bus Address Register Bit Assignments                       | 4-11 |

| 4-8            | Byte Count Register Bit Assignments                        | 4-11 |

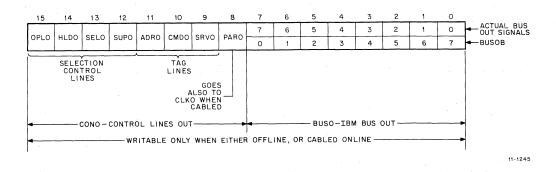

| 4-9            | Maintenance Out Register Bit Assignments                   | 4-12 |

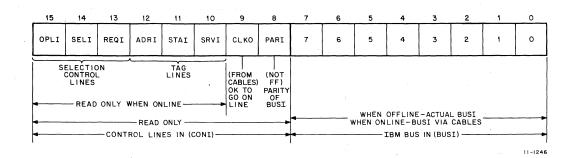

| 4-10           | Maintenance In Register Bit Assignments                    | 4-13 |

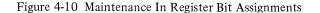

| 4-11           | Control Bits Register Bit Assignments                      | 4-14 |

| 4-12           | Non-Processor Request Data Register Bit Assignments        | 4-16 |

| 4-13           | Extra Signals Register DXES1 Bit Assignments               | 4-17 |

| 4-14           | Extra Signals Register DXES2 Bit Assignments               | 4-18 |

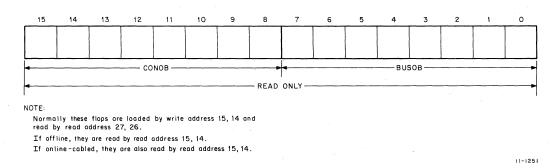

| 4-15           | Maintenance Out Buffered Register Bit Assignments          | 4-18 |

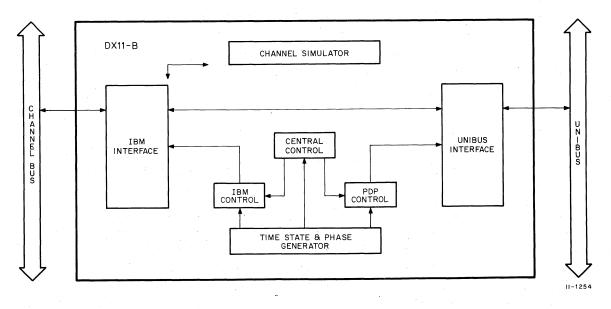

| 5-1            | DX11-B System, Functional Block Diagram                    | 5-1  |

| 5-2            | DX11-B System, Block Diagram                               | 5-2  |

| 5-3            | DX11-B, Block Diagram                                      | 5-3  |

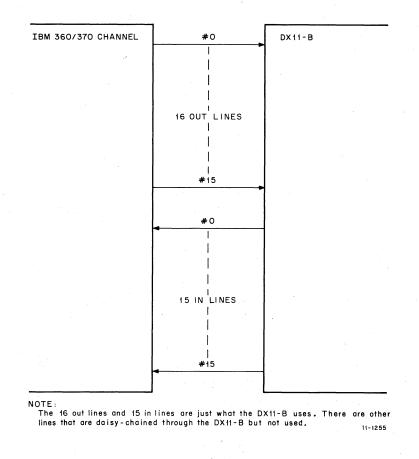

| 5-4            | Channel/DX11-B Interface                                   | 5-9  |

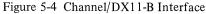

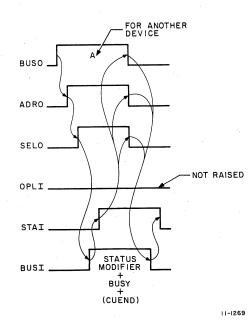

| 5-5            | Channel Selection Chain                                    | 5-11 |

vi

# **ILLUSTRATIONS (Cont)**

| Figure No. | Title                                                            | Page |

|------------|------------------------------------------------------------------|------|

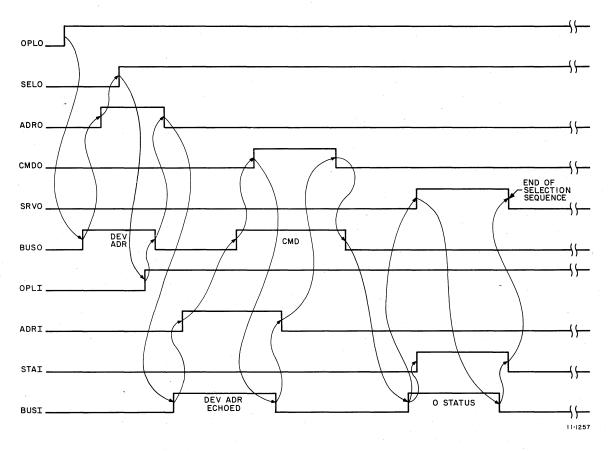

| 5-6        | Initial Selection Sequence (ISS) Selector Channel Initiated      | 5-16 |

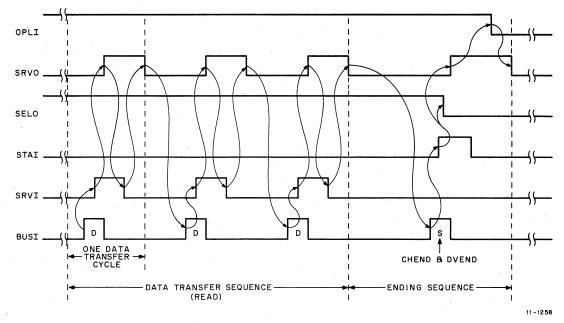

| 5-7a       | Data (Read) Transfer and Ending Sequences with Selector Channel  | 5-17 |

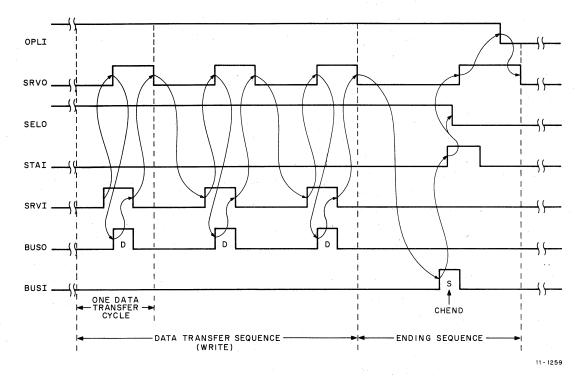

| 5-7b       | Data (Write) Transfer and Ending Sequences with Selector Channel | 5-17 |

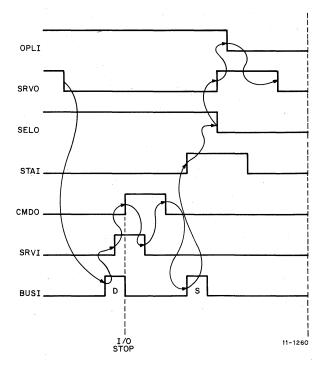

| 5-8        | I/O Stop Sequence on Selector Channel                            | 5-18 |

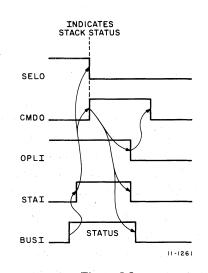

| 5-9        | Stack Status Sequence                                            | 5-19 |

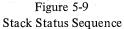

| 5-10       | CUI Sequence to Selector Channel                                 | 5-20 |

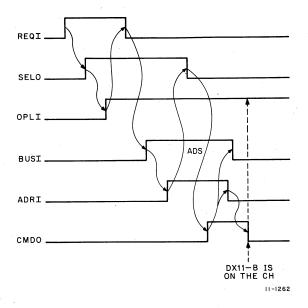

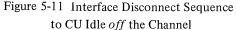

| 5-11       | Interface Disconnect Sequence to CU Idle off the Channel         | 5-20 |

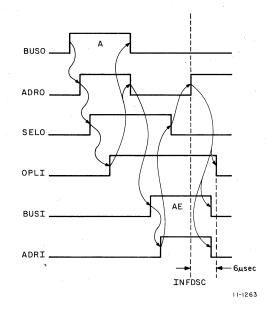

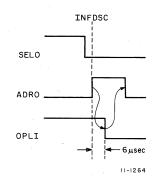

| 5-12       | Interface Disconnect Sequence to CU Idle on the Channel          | 5-21 |

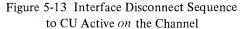

| 5-13       | Interface Disconnect Sequence to CU Active on the Channel        | 5-21 |

| 5-14       | ISS, Multiplexer Channel Initiated                               | 5-22 |

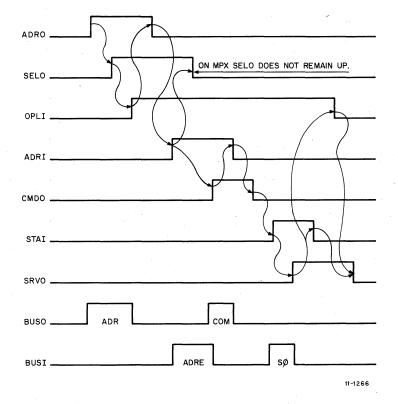

| 5-15       | CUIS and Data Transfer, Multiplexer Channel                      | 5-23 |

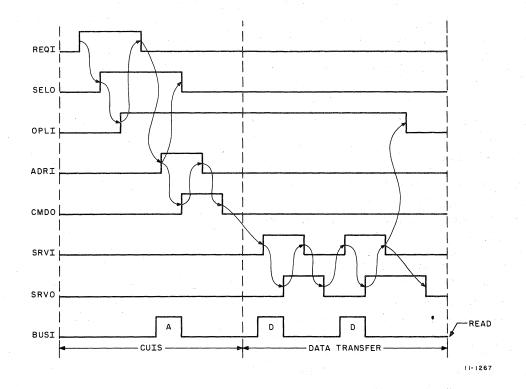

| 5-16       | CUIS and Status Transfer, Multiplexer Channel                    | 5-23 |

| 5-17       | Fast CU Busy Sequence, Multiplexer Channel                       | 5-24 |

| 5-18       | One Bit Slice Loop Trace                                         | 5-51 |

| 5-19       | Select-Out/Select-In Loop Trace                                  | 5-51 |

# TABLES

()

| Table No. | Title                                           | Page |

|-----------|-------------------------------------------------|------|

| 2-1       | DX11-B Option Designations                      | 2-1  |

| 2-2       | DX11-B List of Interconnecting Cables           | 2-2  |

| 3-1       | DX11-B Controls and Indicators                  | 3-1  |

| 4-1       | DX11-B Registers (Addressable as PDP-11 Memory) | 4-3  |

| 4-2       | DXDS Bit Assignments                            | 4-4  |

| 4-3       | DXCA Bit Assignments                            | 4-7  |

| 4-4       | DXCS Bit Assignments                            | 4-8  |

| 4-5       | DXOS Bit Assignments                            | 4-10 |

| 4-6       | DXMO CONO Bit Assignments                       | 4-12 |

| 4-7       | DXMI CONO Bit Assignments                       | 4-14 |

| 4-8       | DXCB Bit Assignments                            | 4-15 |

| 4-9       | DXES1 and DXES2 Bit Assignments                 | 4-17 |

| 5-1       | I/O Command Byte Formats                        | 5-8  |

| 5-2       | Channel/DX11-B Interface Lines                  | 5-10 |

| 6-1       | Test Equipment Required                         | 6-2  |

| 7-1       | DX11-B Engineering Drawings                     | 7-1  |

| A-1       | DX11-B Signal Glossary                          | A-1  |

| A-2       | Hex/Octal/EBCDIC Conversion Chart               | A-12 |

# FOREWORD

This manual provides the information necessary to maintain the DX11-B, System 360/370 Channel to PDP-11 Unibus Interface. Chapter 1 contains introductory information with brief specifications. For more information concerning performance characteristics, refer to the Engineering Specification, Spec No. KFS-DX11-B-31. Chapter 2 of this manual is concerned with the basic information needed to unpack and install the equipment, although specific reference should be made to the individual Customer Site Plan for the particular installation. Included are general programming procedures required in testing, following installation. Although Chapters 3 and 4 provide considerable information as to formats, programming considerations, etc., further reference should be made to the programming documentation.

This manual is primarily concerned with the operation of the DX11-B hardware and the ways in which it interacts with its specially designed software. Chapter 5, Theory of Operation, provides information about the 360/370 Channel operation as it bears on the interface with the DX11-B. Included are detailed discussions of the functional parts and the various sequences of operation. Some of the more obscure aspects of the hardware are also discussed.

This is not a basic manual, some prior knowledge of the IBM 360/370 is required, together with familiarity with the PDP-11 System, particularly with regards to the Unibus Interface. The following table lists related PDP-11 and IBM documents applicable to the DX11-B System.

| Title                                                                           | Number        | Coverage                                      |

|---------------------------------------------------------------------------------|---------------|-----------------------------------------------|

| PDP-11 Unibus Interface Manual,<br>2nd Edition                                  | DEC-11-HIAB-D | How to interface to the PDP-11 Unibus         |

| IBM System/360 and System/370<br>I/O Interface Channel to Control<br>Unit OEMI. | GA22-6974     | How to interface to an IBM 360/370<br>Channel |

| IBM System/360 Principles of Operation                                          | GA22-6821     | How the 360 works                             |

# CHAPTER 1 GENERAL DESCRIPTION

#### 1.1 SCOPE

This chapter describes a typical DX11-B System in the most general of terms. Included is a listing of its mechanical, electrical, environmental, and performance specifications.

### **1.2 INTRODUCTION**

The DX11-B, System 360/370 Channel to PDP-11 Unibus Interface, shown in Figure 1-1, is a data and status transfer controller that provides communication between an I/O channel of a System 360 or System 370 IBM Computer and software within a Digital Equipment Corporation PDP-11 Computer. The system is "table-driven" for convenience and efficiency. When installed, the DX11-B responds automatically to any 360/370 I/O command or status interrogation that is directed to its assigned addresses. It will conduct data transfers (upon PDP-11 program initiation) between the 360/370 Channel and the Unibus, automatically transferring data between the DX11-B buffers and the Unibus locations; participating in data transfers on the 360/370 Channel, and stopping the transfer when the prescribed number of bytes have been transferred. Additionally, the DX11-B communicates with the PDP-11 processor which, in turn, controls the status indications provided to the 360/370 Channel, sets up the DX11-B to execute the commands transmitted by the channel, and provides communication between other devices on the Unibus and the address space used by the DX11-B.

#### **1.3 SYSTEM DESCRIPTION**

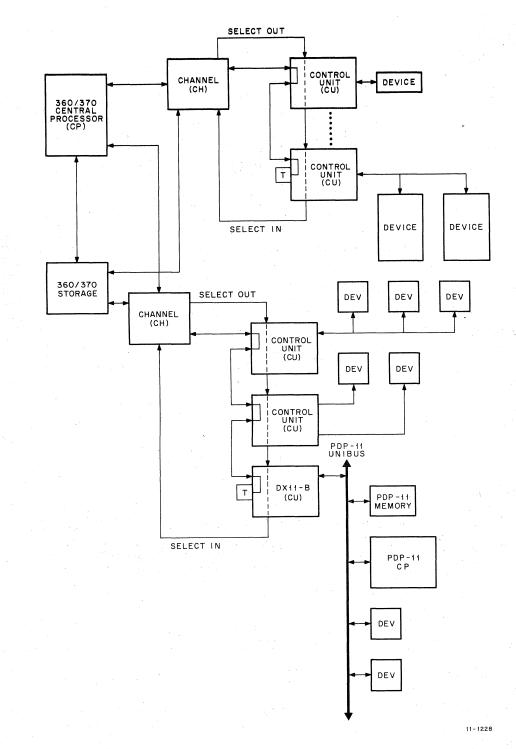

As shown in Figure 1-2, the typical system that is attached to an IBM processor consists of a channel (CH), the control units (CU) attached to the channel, and the devices attached to each controller. Several channels can operate with one processor. The DX11-B operates as a control unit, routing data from devices that store data in different formats to a channel that provides selection and timing control.

The DX11-B is used to perform some of the functions of a controller. However, much of the functional operation of the controller, such as determining the status of the devices, initiating transfers, and detecting errors, is performed by a PDP-11 programmed processor that is interposed between the DX11-B and the devices with which it operates. In addition, the DX11-B, under control of the PDP-11 processor, can appear to the channel to operate with several different types of devices.

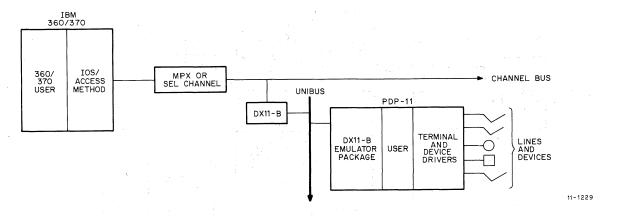

As shown in Figure 1-3, from a functional standpoint, the DX11-B can be considered to be two interfaces: a standard hardware interface to the IBM 360/370 and a standardized software interface (within the PDP-11) to device emulator programs and application programs. The basic package can be programmed to emulate most standard IBM control units with up to 128 devices attached. The emulation only requires the addition of software to the basic package. As a result, the PDP-11 based equipment can be substituted directly for a 360/370 device or devices, with no reprogramming of the 360/370 required. Although hardware and software are described

separately in this manual, because of the interactive characteristics between hardware and software in the DX11-B, they are, in reality, inseparable and *must* be considered as one device in order to gain a complete understanding of the operation of this equipment.

The outstanding features of the DX11-B are:

- Operates on either multiplexer, block multiplexer, or selector channels.

- Emulates up to 128 devices with as many as eight separate sets of contiguous addresses.

- Handles concurrent I/O on all emulating devices.

- Operates with standard 360/370 operating software.

- Is plug-compatible with the standard IBM channel.

- Contains powerful built-in maintenance capability.

- Contains an interface simulator, allowing complete off-line diagnosis.

- Provides a fully buffered I/O (4-byte buffer).

- Handles sequence checking.

- Operates on multiple subchannels.

- Operates on shared or unshared subchannels.

- Operates on selector subchannels.

- Has table-driven status response and burst mode selection.

- Makes available all control unit options.

- Provides hardware fail-soft on program or system latency errors.

#### 1.4 MECHANICAL DESCRIPTION

The DX11-B is housed in a standard 19-in. rack (CAB-11 H960 or H957), containing four H911 Mounting Panels for M-series logic, and IBM 360 connectors for cable connection from the channel and to the next channel unit. Power is provided by an H720e Logic Power Supply, a 716 Power Supply for the indicator panel, and a unit source power panel (EPO) with its power sequence control to the IBM power interface logic. Indicators are provided for logic operation on one panel located on the top front of the unit. Controls are located on the EPO

Figure 1-1 DX11-B, System 360/370 Channel to PDP-11 Unibus Interface

panel available behind a removable front cover, and on the back of the H720e Power Supply, which contains its own power control circuitry. Caravelle fan cooling is provided as part of the basic cabinet. Connections are made between this cabinet and other cabinets containing the PDP-11 Computer and associated equipment. In some installations the PDP-11 can be mounted in the same cabinet with the DX11-B.

Figure 1-2 Typical DX11-B System Block Diagram

# 1.5 SPECIFICATIONS

Physical, environmental, and electrical specifications for the DX11-B are contained in the following paragraphs.

Figure 1-3 DX11-B Functional Block Diagram

#### 1.5.1 Physical

| Dimensions          |         |             |             |

|---------------------|---------|-------------|-------------|

|                     |         | (CAB H960)  | (CAB H957)  |

| Width:              |         | 20-3/16 in. | 20-3/16 in. |

| Height:             |         | 71-7/16 in. | 47-1/2 in.  |

| Depth:              |         | 25 in.      | 25 in.      |

| Service Access Dime | ensions |             |             |

| Front:              |         | 42 in.      | 42 in.      |

| Rear:               |         | 42 in.      | 42 in.      |

# 1.5.2 Environmental

The DX11-B operates under normal conditions of humidity, shock, and vibration.

| Ambient Temperature: |  | <br>50°F to 122°F (10°C to 50°C) |

|----------------------|--|----------------------------------|

| Relative Humidity:   |  | 20% to 95% (noncondensing)       |

#### 1.5.3 Electrical

Estimated Power Consumption (H720e) Logic: Overall AC:

#### 1.5.4 Performance

**Operating Modes:**

Transfer Width:

20A @+5 Vdc 220 VA @ 120 Vac

Program transfer and non-processor transfer depending upon control unit state and channel function being performed.

#### DX11-B to IBM Channel

Eight bits plus parity for information and six individual lines for selection and control.

## IBM Channel to DX11-B

Eight bits plus parity for information and eight bits for selection and control.

Transfer Width (Cont):

#### **DX11-B to/from PDP-11**

All standard Unibus interface signals. Sixteen-bit data path only for data transfers with IBM channel (two bytes/ PDP word).

#### Parity used between DX11-B and IBM Channel

Odd in both directions.

Effective: 2.5 MHz Internal: 5.0 MHz Two discrete time pulses, each standard 50 ns width occurring sequentially 200 ns apart.

#### DX11-B to CH/CH to DX11-B Transfer Rate:

Nominal 250K bytes/sec depending on system (PDP-11 and 360/370) configuration. The theoretical limiting speed caused by the DX11-B clock is 1M bytes/sec.

#### 1.6 ENGINEERING DRAWINGS

DX11-B Clock Frequency:

A complete set of engineering drawings is supplied with each DX11-B System. The engineering drawings are bound in a separate volume entitled *DX11-B System Engineering Drawings*. A list of applicable engineering drawings is included in Chapter 7 of this manual. The general logic symbols used on these drawings are described in the *DEC Logic Handbook*, 1970. Specific symbols and conventions are also included in the *PDP-11 Conventions Manual*, DEC-11-HR6B-D. Specialized symbols and terminology, particularly those used in the flow diagrams for the DX11-B, are explained on the drawings as notes and are further defined in Chapter 5.

#### 1.7 TERMINOLOGY

The *PDP-11 Conventions Manual* contains a list of terminology and abbreviations used with the PDP-11 family of systems. A glossary of PDP-11 terms, as well as general computer and programming terms, is also included. A generic glossary of mnemonic terms used in the DX11-B is given in Appendix A of this manual.

NOTE The documents described in Paragraphs 1.4 and 1.5 are available from the nearest DEC Field Office or from:

Digital Equipment Corporation Communications Services (Direct Mail) 146 Main Street Maynard, Massachusetts 01754

1-5

# CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter contains information on the installation of the DX11-B System. This chapter is not intended to supersede the installation requirements stipulated in the Customer's Site Plan; however, this chapter supplements that information by providing an installation and checkout procedure to confirm operation of the equipment after it has been installed.

#### CAUTION

OEMs should not attempt installation until DEC has been notified and a Field Service representative is present. Failure to do so can void equipment warranty.

## 2.2 CONFIGURATION DIFFERENCES

Installation procedures can vary dependent on the particular system configuration. For example, the DX11-B can be housed in a separate cabinet from the PDP-11, or they can be mounted in the same cabinet. In some-installations, a paper-tape reader will be supplied in the second cabinet with the PDP-11; in still other installations. an RC11 and its companion disk unit can be supplied in a third cabinet. The configurations will vary according to customer's requirements and the 360/370 configuration with which the DX11-B is to operate.

A listing of the basic option designations is given in Table 2-1.

| DX11-B Option Designations |          |         |  |  |

|----------------------------|----------|---------|--|--|

| Nomenclature               | Cab Type | Voltage |  |  |

| DX11-BA                    | H950     | 115 Vac |  |  |

| DX11-BB                    | H950     | 230 Vac |  |  |

| DX11-BC                    | H957     | 115 Vac |  |  |

| DX11-BD                    | H957     | 230 Vac |  |  |

|        | Table 2-1       |      |

|--------|-----------------|------|

| DV11.R | Ontion Designat | tior |

#### 2.3 UNPACKING

The equipment should be unpacked as follows:

1. Place the equipment package within the installation site near its final location. Cut the shipping straps and carefully remove all packing material.

(continued on next page)

- 2. Remove the machine screws that hold the cabinet to the shipping pallet. Slide the cabinet off of the pallet and move to its final location.

- 3. Remove the tape holding the power and interconnecting cables to the cabinet floor.

#### 2.4 INSPECTION

Inspect all of the equipment before installing it, checking each piece against the parts list. Any damage must be reported immediately to the shipper and to the DEC representative. Check the power supplies and power wiring for damage in shipment. Seat modules and perform general visual inspection of the equipment.

#### 2.5 SPACE REQUIREMENTS

No special site preparation is required to install the DX11-B; however, when installing the system, make certain that sufficient access is provided at the front and rear of the cabinets for maintenance personnel. If the cabinets are separated by long distances, consider installing overhead trenching ducts or floor ducts for the cabling. Equipment dimensions and access dimensions are given in Paragraph 1.5 and illustrated in Figure 2-1.

#### 2.6 POWER AND CABLE REQUIREMENTS

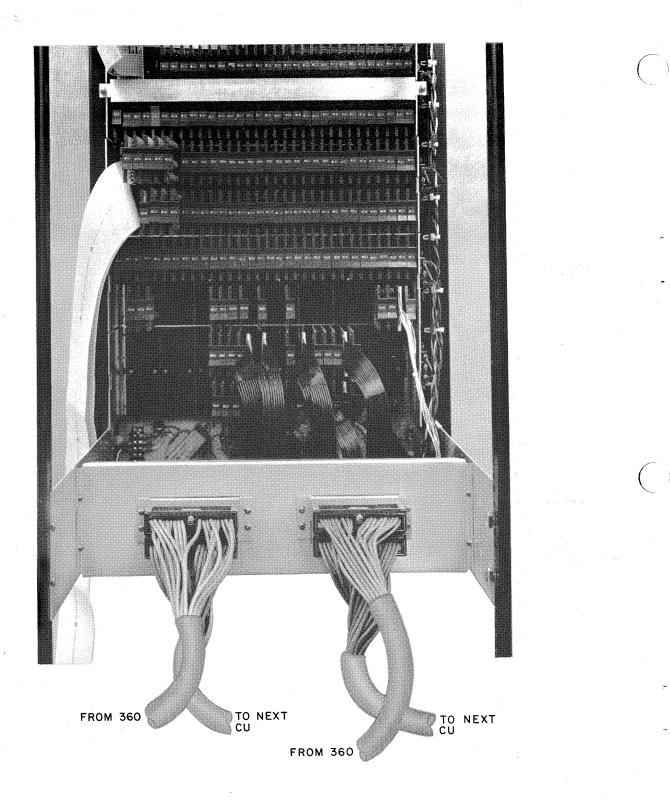

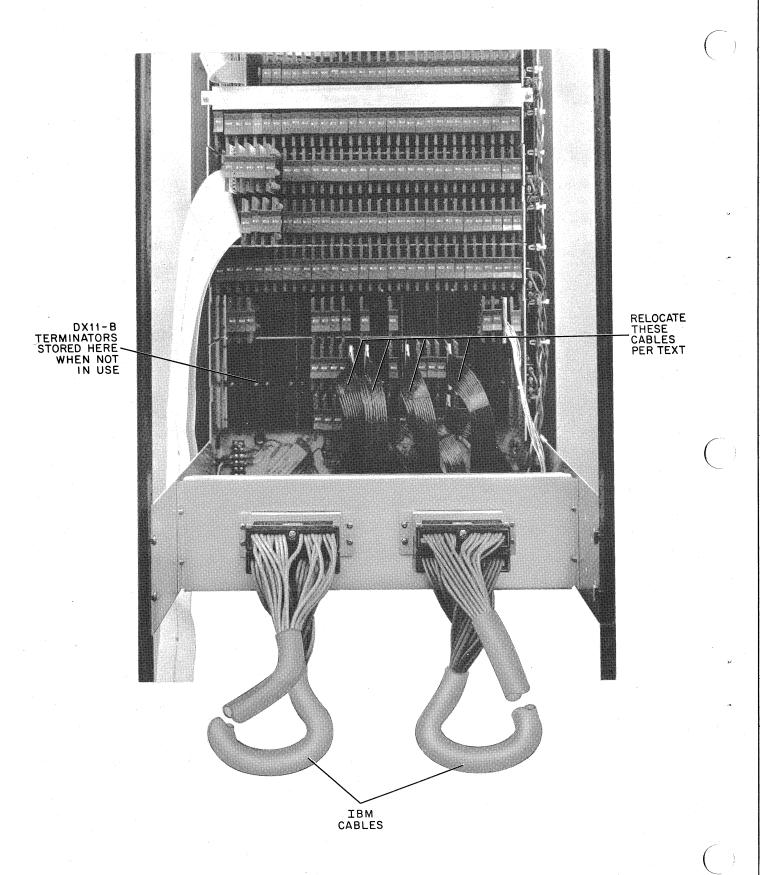

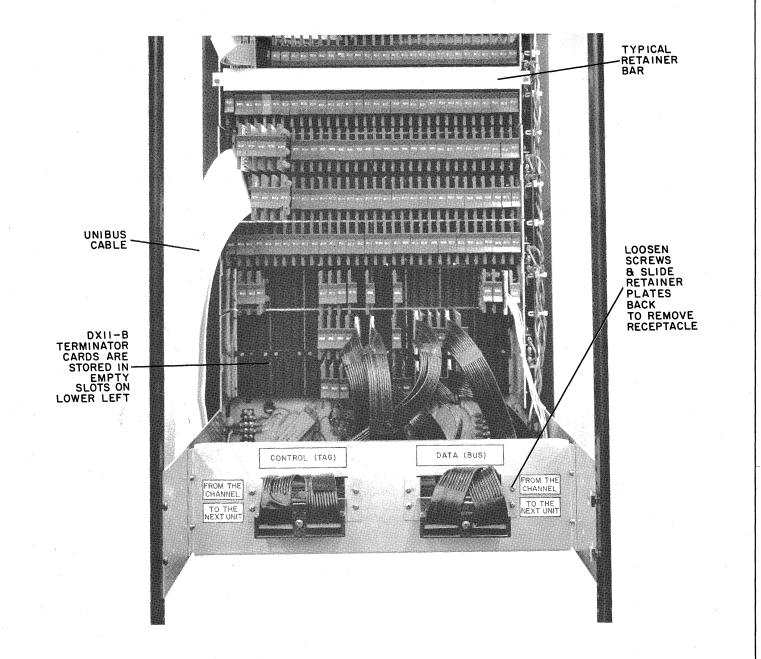

The DX11-B operates from a line voltage of either 115 Vac at 60 Hz or 240 Vac at 50 Hz, depending on the model ordered. The maximum current required is 600 VA @ 120 Vac. Interconnecting cables to the 360/370 System are not supplied as part of the DX11-B but must be supplied by the customer. BC11-A cables connecting the DX11-B and the PDP-11 Unibus are supplied as part of the DX11-B. See Table 2-2 for a list of interconnecting cables and Figure 2-2 for the connections required. If the DX11-B is located on the end of the 360/370 Channel bus, special IBM terminators should be installed in the IBM connectors located inside the back door of the DX11-B cabinet. Install IBM part TAG 2282676 in CONTROL (TAG) TO THE NEXT UNIT receptacle, and IBM part BUS 2282675 in TO THE NEXT UNIT receptacle (Figure 2-3). Figure 2-4 illustrates connections if *not* on end-of-bus.

#### CAUTION

Do not connect 360 cables until the off-line checkout is complete.

| Qty Per EQ | Function              | MFG. Part Number |

|------------|-----------------------|------------------|

| 1          | Power Control Cable   | DEC 70-08288-8   |

| 1          | Unibus Cable          | DEC BC11-A       |

| 1          | EPO Control Cable     | IBM 5351178      |

| 2          | I/O Cables (360 only) | IBM 5353920      |

| 3          | I/O Cables (370 only) | IBM 5466456      |

Table 2-2

DX11-B List of Interconnecting Cables

Figure 2-2 System Power and Cabling Diagram

#### 2.7 INSTALLATION PROCEDURE AND CHECKOUT

To install and checkout the DX11-B, proceed as follows:

#### NOTE

The specifics in this procedure apply to 2848 emulation only. As other emulators are made available, addendums to this procedure will be issued.

- 1. Ensure that the modules, their hold-down bars, and module clips are secure.

- 2. Ensure, on the H720e Power Supply, that the main breaker and the LOCAL-OFF-REMOTE switch are both in the OFF position.

- 3. Connect the Unibus cable (if necessary). DX11-B should be the first device on the Unibus.

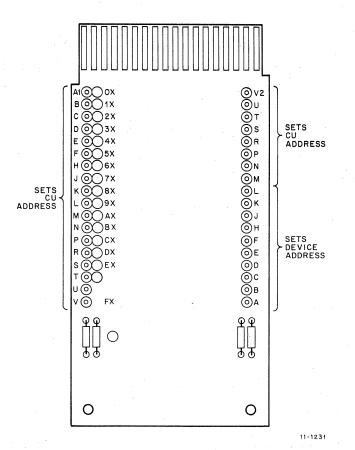

- 4. Wire the M908-YB-A20 360 address jumper card for the correct address selection for the customer's 360/370 installation (see Drawing D-BS-DX11-B-26, and refer to Paragraph 2.9 for more information).

- 5. Check (and rejumper if necessary) the interrupt vector address. The interrupt vector is assigned to the floating vector space.

- 6. Apply power to the PDP-11 and DX11-B.

#### NOTE

When testing the DX11-B with the 360/370, it is mandatory that the IBM computer by solely dedicated to the DX11-B and not occupied in any way with its own operating schedule.

- 7. Load the DX11 diagnostic (MAINDEC-11-DZDXA-[REV]-PB). See the software abstract (MAINDEC-11-DZDXA-[REV]-PB-D) for instructions. Run diagnostic off-line tests.

- 8. Calibrate M306 NPR timeout mono (refer to Paragraph 2.10 for procedure). Perform Cable Check per Paragraph 2.15.

### NOTE BLLM and DXTO will be calibrated later.

Figure 2-3 Normal Cable Connections to Channel Bus if on End of Bus

Figure 2-4 Normal Cable Connections to Channel Bus if Not on End of Bus

(

9. Temporarily label cables as "TAG" and "BUS" and attach DX11-B cables for on-line loop-around tests (Figure 2-5). To do this, remove H/J 07 and plug into H/J 17. Remove H/J 14 and plug into H/J 18. Install M984 terminator cards in H 07, J 07, and H 14. Install terminator card M984-YA in J 14. Include customer-supplied cables in this loop by plugging one side of "TAG" cable into the CONTROL (TAG) FROM THE CHANNEL receptacle and its opposite end into the CONTROL (TAG) TO THE NEXT UNIT receptacle. Loop the "BUS" cable in the same manner using the DATA (BUS) receptacles. The purpose of this test is to assure continuity of the customer-supplied cables. If this test fails, use loop test without cables by removing the receptacles from their panel and mating them to form the loop (Figure 2-6). Once mated, secure connectors with their retaining screws.

#### NOTE

The IBM cables should always be mated dark-to-light and lightto-dark. Interchanging TAG and BUS cables will cause incorrect operation, but will not harm the equipment. Use care in mating these plugs to prevent damage to pins.

- 10. Run diagnostic on-line tests.

- 11. Calibrate DXTO by running diagnostic DXTO calibration test (adjust to 5-10 sec). See Paragraph 2.11 for more information.

- 12. Calibrate BLLM by running diagnostic Fast NPR test. Put oscilloscope on SRVI flip-flop (E32,F2) and adjust BLLM until rising edges of SRVI are  $4 \mu s$  apart: 250K byte/sec data rate.

- 13. Run CTP with off-line DX11-B tests and all other CTP-supported devices to checkout system operation.

- 14. Run GTP with the DX11 overlay (off-line) in 12K systems. Recheck cables per Paragraph 2.15.

- 15. Reset DX11-B cables to normal operational positions. Move cable connector at H/J 17 to H/J 07. Move cable connector at H/J 18 to H/J 14. Remove terminator cards M984 from H07, J07, and H14 and replace in J29, J30, and J31, respectively. Remove terminator card M984-YA from J14 and replace in J32.

- 16. Checkout EPO panel operation as follows (Figure 3-1):

- a. Put ENABLE switch in ON LINE position.

- b. Load and start 2848 RESPONDER.

- c. Check that the DX11-B is on-line (ONLINB=1).

- d. Turn the PDP-11 Processor power off and then on. Check that the DX11-B power first goes off, then that the processor is in the Run state, and that the DX11-B is back on-line (ONLINB=1).

- e. Turn the DX11-B LOCAL POWER switch to OFF position. Check that the DX11-B system power goes off.

- f. Turn the LOCAL POWER switch back to ON position. Check that the processor is in the Run state and that the DX11-B is back on-line (ONLINB=1).

- g. Pull the plug from its outlet and see that the same sequence occurs when it is replaced.

- 17. Connect IBM EPO cable to the DX11-B and put EPO control in SYSTEM position; LOCAL PWR in OFF position. Request that IBM CE power 360/370 up and down. Check for the same indications as described in Step 16. Check PDP-11 power control in REMOTE mode.

(continued on Page 2-9)

2-7

Figure 2-5 Test Bus Cable Connections with IBM Cables in the Loop

Figure 2-6 Test Bus Connections Without IBM Cables

- 18. Have IBM CE attach 360 cables to the channel and run channel diagnostics and device diagnostics with cables butted together or terminated (not connected to DX11-B) until he is satisfied that his equipment is operating satisfactorily.

- 19. Disconnect 360 cables, butted together in Step 15, and connect to the DX11-B. Cable connectors are color coded so that unlike shades mate.

- 20. With the DX11-B off-line (ENABLE switch in OFF LINE position), but powered up, have IBM CE run diagnostics again to ensure that DX11-B is not interfering with other devices on the channel.

- 21. Put ENABLE switch in ON LINE position.

(continued on next page)

- 22. Restart the 2848 RESPONDER in the PDP-11. The DX11-B should be on-line (ONLINB=1) (Paragraph 3.3).

- 23. Have the IBM CE run diagnostics a final time to ensure that the DX11-B in the on-line mode is not interfering with other 360 devices.

- 24. With the RESPONDER still running and with switch 14 down, load and execute the IBM 2848 diagnostic in the 360 for the first two DX11-B addresses (Paragraph 3.3).

- 25. Load FRIEND into the 360 and run the 2848 test procedure (Paragraphs 3.3 and 2.12).

- 26. On the 360 Selectric Keyboard, press REQUEST to stop FRIEND, load CTP, and then select the DX11-B on-line test.

- 27. Run all CTP devices on the PDP-11; with FRIEND in the 360, run the CTP test procedure to check total system operation (Paragraphs 3.3 and 2.13).

## 2.8 CUSTOMER ACCEPTANCE PROCEDURE

To run a customer acceptance procedure, proceed as follows:

- 1. Run off-line diagnostic.

- 2. Cable for "on-line loop-around" and run on-line diagnostic.

- 3. Recable to 360.

- 4. Run GTP (in systems of 12K or more) with DX11 overlay (off-line).

- 5. Run CTP with off-line DX11 test.

- 6. Run CTP with on-line DX11 test driven by FRIEND in the 360.

- 7. Run 2848 RESPONDER with 2848 diagnostic in 360.

- 8. With RESPONDER still running, the customer can optionally run 2848 Online Test Program (OLTEP).

#### 2.9 IBM CONTROL UNIT AND DEVICE ADDRESS JUMPER CARD

The M908B Jumper Card located at A19 is shown in Figure 2-7 as it appears at installation, before the control unit and device addresses have been set by jumpering. This card is equipped with split lugs for easy wiring. In wiring this card, any standard wire can be used. The no. 30 wirewrap is carried by all DEC Field Service representatives and is adequate for this procedure.

The I/O address format is shown in Figure 2-8. The DX11-B never sees the 8-bit channel address portion of the I/O instruction. There are four of these instructions by which the 360/370 CP controls I/O operations. These are: 1) Start I/O, 2) Test I/O, 3) Halt I/O, and 4) Test Channel. A Test Channel instruction does not issue an I/O address, but for the other three, the address is generated and decoded as described in Paragraph 5.5.21. Figures 2-9 through 2-11 give these wiring examples.

In Figure 2-9, jumpering pin B to pin V2 and then running the jumper to pins U through M, the first hex digit (1) is decoded by an M155 module at location A19. When pins K, H, E, and B are jumpered to pin C (gnd), the DX11-B ignores the second hex digit causing it to automatically respond to device addresses 10 through 1F.

Figure 2-10 is an example of wiring for the 32 device addresses 50 through 6F. Note that pin F (5x) is tied to pin V2, while pin H (6x) is tied to pin U before being jumpered through pin M. The second digit is responded to as it is in Figure 2-7.

Figure 2-11 shows the wiring for four device addresses in the range 3x. Pins K and H are grounded by jumpering to pin C. Pin L is jumpered to pin B and pin E is tied to pin D.

From these examples, the wiring for any combination can be derived.

NOTE All addressing, including systems with less than 16 devices, must start on zero boundaries.

Figure 2-7 M908B Module Before Wiring

Figure 2-8 I/O Address Format

2-11

Figure 2-9 Example of Wiring for 16 Devices 10 through 1F (1x)

#### 2.10 NPR TIMEOUT MONO (M306) CALIBRATION PROCEDURE

To calibrate the NPR Timeout Mono, proceed as follows:

- 1. Place channel 1 (sync) probe on the output of the NPRDLY Mono (Pin F04S2). Put sync controls to: Ac Low Frequency Rej., pos. sync. Time base to 100 μs/div.

- 2. Place channel 2 probe on the NPRX flip-flop (pin F04H2).

- 3. Load the diagnostic and run the NPRTO calibration procedure.

- 4. Adjust the mono potentiometer in slot F04 to  $12 \,\mu$ s. (NPRX(1) L neg. edge to NPRDLY). Put X10 mag. on to make measurement (Figure 2-12).

## 2.11 DXTO CALIBRATION PROCEDURE

To calibrate the DX timeout, proceed as follows:

Figure 2-11 Example of Wiring for Four Devices

Figure 2-12 NPR Timeout Mono Calibration Waveform

2-13

- 1. Place processor in HALT state.

- 2. Hit START to cause DX11 initialization.

- 3. Set switch register to 176216 and hit LOAD ADDRESS.

- 4. Set switch register (SR) to 100000 and hit DEPOSIT to cause Operational-In to set.

- 5. Time approximately 5 sec. At this time, DXTO should set.

- 6. Repeat Steps 2–5 to calibrate DXTO mono M306-F03 to approximately 5 sec.

#### 2.12 2848/FRIEND TEST PROCEDURE

To conduct a 2848/FRIEND Test Procedure, proceed as follows:

#### NOTE

On the 360 all console input is terminated by [EOB], obtained by pressing both ALT mode and 5. On the 370, hit END. This refers to every line entered.

- 1. Load FRIEND into 360 (see Paragraph 3.3.2 for 360 load procedure) and reply to CPU model.

- 2. Run 2848 RESPONDER in PDP-11 (see Paragraph 3.3 for operating RESPONDER).

- 3. Type following to FRIEND (underline is program query):

$\underline{\text{DEV}} = XXX [EOB]$ CMD 01 from \$A [EOB]  $\underline{\text{DATA}} = 480C0 [EOB]$ CMD 06 into \$B [EOB]  $\underline{\text{DL}} = 480 [EOB]$ COMPARE \$A, \$B [EOB] GO [EOB] (XXX = DX11 low-order address)

- includes CH number

#### NOTE

(YYY = XXX + 1)

This performs a "write" chained to a "read", then compares the data read back to see that it equals the data written.

- 4. Hit REQUEST on 360 console.

- 5. Type following to FRIEND (if DX11 has more than one contiguous device address):

- DEV= YYY [EOB] CMD 01 from \$C [EOB] DATA= 480C1 [EOB] CMD 06 into \$D [EOB] DL= 480 [EOB] COMPARE \$C, \$D [EOB] GO [EOB]

#### NOTE

This performs the same operation as that above sequentially on the next device.

6. Hit REQUEST, type RESET to terminate test. FRIEND should loop continuously until terminated by this step. Errors will be reported on IBM console typewriter.

#### 2.13 CTP/FRIEND SYSTEM TEST

To perform a CTP/FRIEND System Test, proceed as follows:

NOTE

On the 360 all console input is terminated by [EOB]. On the 370, hit END. This refers to every line entered.

5.1

- 1. Load FRIEND and reply to CPU model.

- 2. Load and start CTP for on-line DX11 test and all other CTP-supported devices.

- 3. Type following to FRIEND:

<u>DEV=</u> XXX [EOB] CMD 01 from \$A [EOB] <u>DATA=</u> 256Xff [EOB] CMD 02 into \$B [EOB] <u>DL=</u> 256 [EOB] COMPARE \$A, \$B [EOB] GO [EOB]

——Includes the CH number

4. Hit REQUEST and type RESET to end test.

#### 2.14 CAUTIONS AND WARNINGS

Various cautions and warnings concerning the installation and operation of the DX11-B have been gathered here for easy reference. As field experience is gained in the use of this equipment, revisions and additions to this list will be made. In this paragraph, a CAUTION is intended to prevent equipment damage or malfunction; a WARNING is intended to prevent bodily harm.

#### WARNING

The ac voltage to the power supply is also provided to the EPO panel terminals 1, 2, 3. This power is NOT switched at any place in the entire system. It can be removed from the cabinet only by pulling the power plug.

#### CAUTION

Be extremely careful when working around the backplane pins in the H and J rows. These pins are connected to the IBM cables and carry signals at all times while the 360/370 system is operating (whether or not the DX11-B has power).

#### CAUTION

Do not remove the G890 Select Bypass Module from the logic rack while the system is cabled to the 360/370 channel. If the module is removed, the SELECT signal path is broken and the 360/370 channel cannot use any control unit attached. If it becomes necessary to remove the G890 while cabled to the channel, follow the directions noted on Drawing DX11-B-29. Do not vibrate the G890.

#### CAUTION

Do not remove any of the 360/370 cable connectors from the logic rack while cabled to the IBM system. All of the IBM signals (control and data) go through the DX11-B. Pulling a cable would cause the 360/370 System to stop. Also, do not disturb the connectors while connected. If it becomes necessary to remove the cables, proceed as follows:

1. Arrange for the 360/370 System operating personnel to stop the system for about 5 minutes.

2. Remove both cables from the control (TAG) side of the connector assembly (power need not be dropped on the 360/370 for this operation).

(continued on next page)

- 3. Mate the light and dark cables together. Repeat the operation for the data (bus) pair of cables.

- 4. Notify the IBM operating personnel of completion.

#### NOTE

Use care to not bend the IBM cable pins during this operation. They bend easily.

#### CAUTION

Do not leave the EPO connector plug unplugged after system installation is completed. If the EPO plug is left out and the 360 System is powered down and then up, the power sequencing will hang trying to turn on the DX11-B.

## 2.15 CABLE CHECK

In addition to a confusion factor in polarizing the IBM connector end of TAG and BUS cables, there is a great chance that the module connector ends of these cables can be incorrectly plugged in to the DX11-B if a cable check is not made prior to making these connections.

There are two possible cable connectors supplied in the field for the IBM double-connector end of these cables. Although they are wired identically, they are marked differently and must be inspected before deciding which connector to plug into which slot.

The dark gray cable which utilizes the IBM-manufactured cable is illustrated in Drawing D-IA-7008777-0-0, titled *IBM 360 Cable Assembly*. The manner in which the double connector is marked is illustrated to the right of the photographic portion of this print. The letters B, D, G, and J appear twice, embossed on the outside lips of the connector. The pins are labeled once between the two rows of pins, also embossed with the numbers 2 through 13. There are two rows of 13 pins each for the B/D side of the connector and for the G/J side of the connector.

The other cable supplied in the field is dark brown and is labeled differently. Although the labels are the same, the B, D, G, and J designations appear embossed within circles either side of the center securing hardware. The pin numbers are embossed below the lower set of pins within the connector lip.

The IBM cable comprises two sets of coaxial leads arranged in a flat ribbon, each set terminating in an individual module connector at the other end. The other cable assembly (brown connector) also consists of two sets of cables, but each set is made up of twisted pairs, formed into a round cable that is wrapped with a polyethylene cover.

Note that although the parts of the two different cables are not interchangeable, they are compatible in that they can be mated if necessary.

Polarization of the module connector ends of these cables is performed identically. Note that one set of cables corresponds to the B and D side of the double connector while the other set of cables correspond to the G and J side.

Referring now to Drawing D-BS-DX11-B-27, Sheet 3, the logic slots into which the module connectors are to be inserted can be derived. On that drawing, the rectangle to the right of each connector represents the pin numbers on the double connector to which these signals go. Depending on whether the large connector is labeled TAG or DATA/1st BUS or NEXT BUS, the proper slot can be determined from this diagram.

For example, if the cable in question is 1st BUS/TAG line, the connector for the cable associated with pins G and J should plug into slot H12. The connector associated with pins B and J plugs into slot H14.

Once this check has been made, it is recommended that these module connectors be labeled for future reference since they are moved around for various tests.

# CHAPTER 3 OPERATION

# 3.1 SCOPE

This chapter provides the information necessary to operate the DX11-B. The description is divided into two major parts: Controls and Indicators, and Special Operating Procedures.

#### 3.2 CONTROLS AND INDICATORS

Figure 3-1 shows the DX11-B control and indicator panels. The indicator panel is located at the top front of the unit. The control panel (EPO) is located in the center front of the unit behind a removable panel. The figure is keyed, by index number, to the functional descriptions given in Table 3-1.

The power controls, located inside the cabinet back door on the Type 720e Power Supply, are not included.

| Index<br>No. | Name        | Function                                                                                                                                                          |

|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | DXDS_00     | <i>Device-Status-Register</i> – Sixteen lamps which indicate the contents of the DX11-B Device Status Register as follows:                                        |

|              | PARER       | <i>Parity-Error</i> – Indicates an even parity condition on Bus-Out, when either a command or data information is sent from CH to CU (DX11-B). (Error indicator.) |

|              | NXM (PDPTO) | Non-existent-Memory – Indicates more than 20 $\mu$ s were required to complete a single NPR. (Error indicator.)                                                   |

| • *          | SELRST      | Selective-Reset – Indicates a malfunctioning DX11-B device. (IBM Reset indicator.)                                                                                |

|              | SYSRST      | System-Reset – Indicates the execution of a System Reset sequence. (IBM Reset indicator.)                                                                         |

|              | INFDSC      | Interface-Disconnect – Indicates that the channel has performed a disconnect operation with the DX11-B. (IBM Reset indicator.)                                    |

|              | UCHKS       | <i>Unit-Check-Sent</i> – Indicates that Unit Check has been presented in the status byte. (Channel Status flag.)                                                  |

Table 3-1DX11-B Controls and Indicators

(continued on Page 3-3)

| Index<br>No. | Name                                                       | Function                                                                                                                                                                                                                                        |

|--------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>(cont)  | CHENDS                                                     | <i>Channel-End-Sent</i> – Indicates to the emulator that Channel End status was sent in a status response. (Channel Status flag.)                                                                                                               |

|              | BSYS                                                       | <i>Busy-Sent</i> – Indicates that Busy status was sent to the channel. (Channel Status flag.)                                                                                                                                                   |

|              | CHIS                                                       | <i>Channel-Initiated-Selection-Sequence</i> – Indicates a channel-<br>initiated sequence is in progress with the DX11-B.                                                                                                                        |

|              | ESEND                                                      | <i>Ending-Sequence-End</i> – Indicates a status byte was presented<br>to the channel as a result of either a program-initiated sequence<br>or a stacked status having been accepted. Can indicate a<br>CUI-ISS contention. (CUI End indicator.) |

|              | CHDEND                                                     | <i>Channel-Data-End</i> – Indicates a channel byte count overflow during a Data Transfer sequence. (CUI End indicator.)                                                                                                                         |

|              | CUDEND                                                     | <i>Control-Unit-Data-End</i> – Indicates an all zero state in the DXBC Register during a Data Transfer sequence. (CUI End indicator.)                                                                                                           |

|              | ISSREJ                                                     | <i>ISS-Rejected</i> – Indicates a channel-initiated selection sequence addressed to the DX11-B was answered by a CU Busy status indication and a short CU Busy sequence. (Special indicator.)                                                   |

|              | CMDCHN                                                     | <i>Command-Chaining</i> – Indicates that another CCW operation will probably follow for the CU/Device currently connected when Device End is presented. (Special indicator.)                                                                    |

|              | STKSTB                                                     | Stack-Status-Byte – Indicates that the status byte being presented<br>on the Bus-In cannot currently be accepted by the channel.<br>(Special indicator.)                                                                                        |

|              | CMDREJ                                                     | <i>Command Reject</i> – Indicates the command sent to the DX11-B was illegal. Unit check is presented in the status byte. The rejected command is indicated in the CUCR. (Special indicator.)                                                   |

| 2            | CUAR_02                                                    | Control Unit Address Register – Eight lamps which indicate the con-<br>tents of the CUAR constituting the right-hand byte of the DXCA<br>(Command and Address Register). Contains the device address from<br>Bus-Out during an ISS.             |

| 3            | CUSR06                                                     | Control Unit Status Register – Eight lamps which indicate the con-<br>tents of the CUSR constituting the right-hand byte of the DXOS<br>(Offset and Status Register). These status bits, transmitted to the<br>channel are as follows:          |

|              | ATTN<br>CUEND<br>BSY<br>CHEND<br>DEVEND<br>UCHECK<br>UXCEP | Attention<br>Control Unit End<br>Busy<br>Channel End<br>Device End<br>Unit Check<br>Unit Exception                                                                                                                                              |

(continued on next page)

(

| Index<br>No. | Name                                                                 | Function                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.           | DXMO14                                                               | Maintenance Out Register – Sixteen lamps which indicate the con-<br>tents of the Maintenance Out Register. This register comprises two<br>subregisters, the left-hand byte constituting the CONO or Control<br>Lines Out Register, and the right-hand byte, the BUSO or Data<br>Lines or IBM Bus-Out Register. These bits are as follows:           |

|              | OPLO                                                                 | Operational-Out – Indicates that the channel is in operation (Selection Control Line)                                                                                                                                                                                                                                                               |

|              | HLDO                                                                 | Hold-Out (Selection Control Line)                                                                                                                                                                                                                                                                                                                   |

|              | SELO                                                                 | Select-Out (Selection Control Line)                                                                                                                                                                                                                                                                                                                 |

|              | SUPO                                                                 | Suppress-Out (Selection Control Line)                                                                                                                                                                                                                                                                                                               |

|              | ADRO                                                                 | Address-Out (Tag Line)                                                                                                                                                                                                                                                                                                                              |

|              | CMDO                                                                 | Command-Out (Tag Line)                                                                                                                                                                                                                                                                                                                              |

|              | SRVO                                                                 | Service-Out (Tag Line)                                                                                                                                                                                                                                                                                                                              |

|              | PARO                                                                 | Parity-Out (Parity Line)                                                                                                                                                                                                                                                                                                                            |

|              | REC'D BUS OUT<br>LINES (BUSO)                                        | Indicate the Bus-Out data bits as seen either directly from the Bus-Out cables or from BUSOB if off-line.                                                                                                                                                                                                                                           |

| 5            | DXMI16                                                               | Maintenance In Register – Sixteen lamps which indicate the con-<br>tents of the Maintenance In Register. This register comprises two<br>subregisters, the left-hand byte constituting the CONI or Control<br>Lines In Register, and the right-hand byte the BUSI or Data Lines<br>or IBM Bus-In Register. These bits are as follows:                |

|              | OPLI<br>SELI<br>REQI<br>ADRI<br>STAI<br>SRVI<br>CLKO<br>PARI<br>BUSI | Operational-In (Selection Control Line)<br>Select-In (Selection Control Line)<br>Request-In (Selection Control Line)<br>Address-In (Tag Line)<br>Status-In (Tag Line)<br>Service-In (Tag Line)<br>Clock-Out (from Bus-Out)<br>Bus Parity In<br>Indicates the data bits enabled to the Bus-In lines for transmission<br>back to the IBM 360 Channel. |

| 6            | DXCB_20                                                              | <i>Control Bits Register</i> – Sixteen lamps which indicate the contents of the Control Bits Register as follows:                                                                                                                                                                                                                                   |

| <br>         | LOCKO                                                                | <i>Lockout</i> – Indicates that the first five programmable registers are made read-only to the PDP-11 program.                                                                                                                                                                                                                                     |

|              | PHASE 2,1,0                                                          | Indicate the existing major phase of the DX11-B.                                                                                                                                                                                                                                                                                                    |

|              | TSFF                                                                 | <i>Time State Flip-Flop</i> $-$ Indicates the state of the clock control (time state) flip-flop.                                                                                                                                                                                                                                                    |

|              |                                                                      | 1 = TS1<br>0 = TS2                                                                                                                                                                                                                                                                                                                                  |

(continued on next page)

)

| Index<br>No. | Name                             | Function                                                                                                                                                                                                                                                 |

|--------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>(cont)  | FASTCU                           | <i>Fast Control Unit Response</i> – This signal is made available for diagnostic test purposes.                                                                                                                                                          |

|              | SYNC                             | Synchronization $Flip$ - $Flop$ — This is a phase synchronizing flip-<br>flop used to disable certain portions of logic within any particular<br>phase.                                                                                                  |

|              | CUDX                             | <i>Control Unit Data Control</i> – Indicates that the Control Unit data (CUCR and CUSR) is available to either the bus-out or bus-in lines.                                                                                                              |

|              | IOD                              | <i>I/O-Done</i> – Indicates an Input-Output Done condition.                                                                                                                                                                                              |

| 1 N N R      | BYPAS                            | Bypass – Indicates one of the following:                                                                                                                                                                                                                 |

|              |                                  | a. This is the first byte of data that is being transmitted or received.                                                                                                                                                                                 |

|              |                                  | b. The device status table will not be accessed by this particular channel-initiated sequence.                                                                                                                                                           |

|              |                                  | c. No address-out has been received.                                                                                                                                                                                                                     |

|              |                                  | d. A copy of the parity okay signal (between Phases 2 and 3).                                                                                                                                                                                            |

|              |                                  | e. A copy of status pending (between TS1 and TS2 of Phase 0 during a CHI sequence).                                                                                                                                                                      |

| قوق ا        | a kana ang sana ang sana sang sa | f. In TS2, indicates that a fast CU Busy was made in TS1.                                                                                                                                                                                                |

|              | NPRX                             | NPR Control Switch – Indicates that the DX11-B is requesting<br>a non-processor or memory-to-device transfer from the PDP-11.<br>When extinguished, indicates that the transfer has been com-<br>pleted.                                                 |

|              | NPRT                             | <i>NPR Transfer Direction</i> – Indicates that data is being sent into PDP-11 core. If extinguished, indicates that data is being taken from PDP-11 core.                                                                                                |

|              | BALF                             | Byte Alternator Load $Flop$ – Indicates that status is pending<br>and that the device for which status is pending has been addressed<br>by the channel. During Phases 5 and 6, it keeps track of which<br>half of the data word is currently being used. |

|              | ONLINB                           | On line $B$ – Indicates whether or not the DX11-B is connected to the I/O interface.                                                                                                                                                                     |

|              | ADRECC                           | <i>Control Unit Address Compare</i> – Indicates that the control unit portion of the address matches Bus-Out.                                                                                                                                            |

|              | ADRECD                           | <i>Device Address Compare</i> – Indicates that the device portion of address matches Bus-Out.                                                                                                                                                            |

| Index<br>No. | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7            | DXND_22 | <i>NPR Data Register</i> – Sixteen lamps that indicate each data word that is transmitted to or from PDP-11 core via NPRs.                                                                                                                                                                                                                                                                               |  |

| 8            | PAROK   | <i>Parity <math>OK</math></i> – Indicates odd parity on the channel and device address from the channel to the DX11-B.                                                                                                                                                                                                                                                                                   |  |

| 9            | DXTO    | <i>DX11-B Timeout</i> – Indicates that while Operational-In was up, the program did not interact for 5 sec. (Program Response Latency error.)                                                                                                                                                                                                                                                            |  |

| 10           | MNCLEN  | Maintenance Clock Enable – (MCLKEN) Indicates that the DX11-B<br>is enabled for maintenance clock mode. When set, the DX11-B will<br>not change time state until Maintenance Clock pulse is set. This<br>flip-flop is pulsed by the SINGLE PULSE switch on the EPO panel.<br>An on and an off condition of the MNCLEN indicator will result in<br>the DX11-B switching from one time state to the other. |  |

| 11           | TIMDIS  | <i>Timeout Disable</i> – Indicates disabling of DXTO during program debugging.                                                                                                                                                                                                                                                                                                                           |  |

| 12           | NPRTO   | <i>NPR Timeout</i> – Indicates that Bus Grant was not received during timeout interval. (NPR Latency error.)                                                                                                                                                                                                                                                                                             |  |

| 13           | ODD     | <i>ODD Flip-Flop</i> – Copy of DXBA (00). Always zero when presented to Unibus (or read by program). This data (odd buffered address) is saved here to initialize BALF.                                                                                                                                                                                                                                  |  |

| 14           |         | Two undesignated lamps that can be jumpered to any signal for observation.                                                                                                                                                                                                                                                                                                                               |  |

| 15           | DXBA_10 | NPR Bus Address Register – Fifteen lamps that indicate the follow-<br>ing:                                                                                                                                                                                                                                                                                                                               |  |

|              |         | NOTE<br>00 is always (0). See Item 13.                                                                                                                                                                                                                                                                                                                                                                   |  |

|              |         | a. During data transfers, points to PDP-11 core location to or from which data will be transferred.                                                                                                                                                                                                                                                                                                      |  |

|              |         | b. During CHIS, points to the SPW and device status byte in PDP-11 core.                                                                                                                                                                                                                                                                                                                                 |  |

|              |         | c. When information is to be stored in the Tumble Table (TT), indicates that address.                                                                                                                                                                                                                                                                                                                    |  |

| 16           | DXCS04  | <i>Control Unit Status Register</i> – Fifteen lamps that indicate the contents of the Control Unit Status Register as follows:                                                                                                                                                                                                                                                                           |  |