# Digital Equipment Corporation Maynard, Massachusetts

LPS11-S laboratory peripheral system maintenance manual

DEC-11-HLPMA-B-D

LPS11-S laboratory peripheral system maintenance manual

digital equipment corporation • maynard, massachusetts

1st Edition, June 1973 2nd Printing, September 1973 3rd Printing (Rev), December 1973 4th Printing, November 1974

#### Copyright © 1973, 1974 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC FLIP CHIP DIGITAL UNIBUS PDP FOCAL COMPUTER LAB

### CONTENTS

Page

| CHAPTER 1        | INTRODUCTION AND DESCRIPTION                        |              |

|------------------|-----------------------------------------------------|--------------|

| 1.1              | INTRODUCTION                                        | 1-1          |

| 1.2              | SCOPE                                               | 1-1          |

| 1.3              | BLOCK DIAGRAM DISCUSSION                            | 1-2          |

| 1.3.1            | Bus Control                                         | 1-2          |

| 1.3.2            | LPSAD-12 A/D Converter System Option                | 1-2          |

| 1.3.3            | LPSKW Programmable Real-Time Clock                  | 1-4          |

| 1.3.4            | LPSVC Display Control                               | 1-4          |

| 1.3.5            | El SDR Digital inpat/output                         | 1-4          |

| 1.4              | SPECIFICATIONS SUMMARY                              | 1-4          |

| 1.4.1            | LPSAD-12 A/D Converter                              | 1-4          |

| 1.4.2            | LPSAM Multiplexer                                   | 1-5          |

| 1.4.3            | LPSAG/LPSAG-VG Preamplifier                         | 1-5          |

| 1.4.4            | LPSKW Real-Time Clock                               | 1-6          |

| 1.4.5            | LPSVC Display Control                               | 1-7          |

| 1.4.6            | LPSDR Digital I/O                                   | 1-7          |

| 1.4.7            | Power Supply                                        |              |

| 1.4.8            | LPSAM-SG/BA408 Switched Gain Multiplexer            | 1-9          |

|                  |                                                     |              |

| <b>CHAPTER 2</b> | INSTALLATION                                        |              |

| · · · · ·        | INTRODUCTION                                        | 2 1          |

| 2.1<br>2.2       |                                                     |              |

| 2.2              | UNPACKING                                           |              |

| 2.3              |                                                     |              |

| 2.4              | INSPECTION                                          |              |

| 2.6              | INITIAL TURN-ON                                     |              |

| 2.7              | SYSTEM INSTALLATION                                 |              |

| 2.7              | CABLE INSTALLATION                                  |              |

| 2.8              | OPTION INSTALLATION                                 |              |

| 2.9              | LPSAD-12 A/D Converter                              |              |

| 2.9.2            | LPSAD-NP Direct Memory Access (DMA)                 |              |

| 2.9.3            | LPSAM 10–17 Channel Multiplexer                     |              |

| 2.9.4            | LPSAG Preamplifier                                  |              |

| 2.9.5            | LPSAG-VG Preamplifier                               |              |

| 2.9.6            | LPSSH Dual Sample-and-Hold                          |              |

| 2.9.7            | LPSKW Real-Time Clock                               |              |

| 2.9.8            | LPSVC Display Control                               |              |

| 2.9.9            | LPSDR Digital Input/Output                          |              |

| 2.9.10           | BA408 Switched Gain Multiplexer (Channels 0–7)      | 2-10<br>2-11 |

| 2.9.10           | LPSAM-SG Switched Gain Multiplexer (Channels 10–17) |              |

| 2.9.11           | BA408 Switched Gain Multiplexer (Channels 10–17)    |              |

| 2.7.12           |                                                     | <u>-12</u>   |

| CHAPTER | 2        | THEORY  | OF.  | ODED  | ATION |

|---------|----------|---------|------|-------|-------|

| LHAPIEK | <b>`</b> | тығаж т | 1.16 | UPP.K |       |

|         |          |         |      |       |       |

| 3.1   | , | BUS CONTROL                  | 1 |

|-------|---|------------------------------|---|

| 3.1.1 |   | Block Diagram Discussion 3-  | 2 |

| 3.1.2 |   | LPS11-S Option Addressing 3- | 2 |

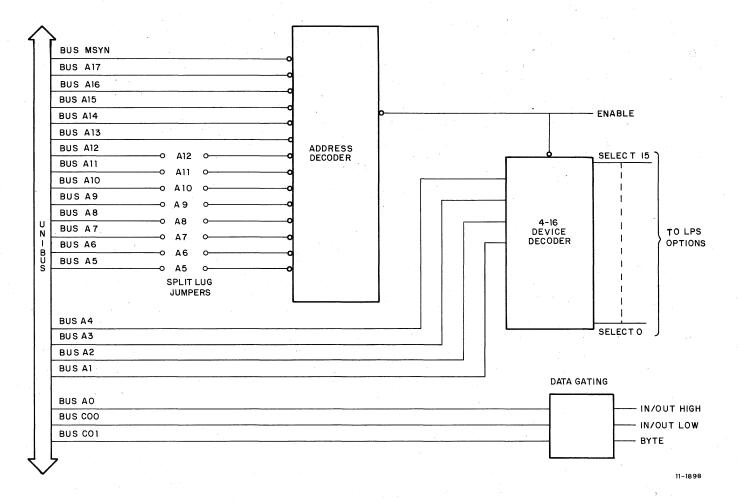

| 3.1.3 |   | Address Control              | 3 |

# **CONTENTS (Cont)**

|          | Page                                     |

|----------|------------------------------------------|

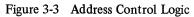

| 3.1.4    | Internal Bus                             |

| 3.1.5    | Interrupt and Priority Logic             |

| 3.2      | ANALOG-TO-DIGITAL CONVERTER SYSTEM       |

| 3.2.1    | Block Diagram Discussion                 |

| 3.2.2    | A/D Programming                          |

| 3.2.2.1  | A/D Status Register                      |

| 3.2.2.2  | LED and A/D Buffer Register              |

| 3.2.3    | Error Flag                               |

| 3.2.4    | Addressing                               |

| 3.2.5    | LED Buffer                               |

| 3.2.6    | A/D Conversion Starts                    |

| 3.2.6.1  | Program Starts                           |

| 3.2.6.2  | Clock Overflow                           |

| 3.2.6.3  | Schmitt Trigger #1                       |

| 3.2.7    | A/D Conversion Timing $3-18$             |

| 3.2.8    | Interrupt                                |

| 3.2.9    | Dual Sample-and-Hold                     |

| 3.2.10   | Analog Components                        |

| 3.2.10.1 | A241 or A242 Preamplifier                |

| 3.2.10.2 | A407 Multiplexer                         |

| 3.2.10.3 | A406 Sample-and-Hold                     |

| 3.2.10.4 | A804 A/D Converter                       |

| 3.2.10.5 | A408 Switched Gain Multiplexer           |

| 3.2.11   | Direct Memory Access (DMA) 3-25a         |

| 3.2.11.1 | DMA Programming 3-25a                    |

| 3.2.11.2 | Single DMA Operation                     |

| 3.2.11.3 | Dual Sample-and-Hold                     |

| 3.2.11.4 | Single Burst Operation                   |

| 3.2.11.5 | Dual Sample-and-Hold Burst Operation     |

|          | LPSKW REAL-TIME CLOCK                    |

| 3.3.1    | Block Diagram Discussion                 |

| 3.3.2    | Programming                              |

| 3.3.3    | Timing Logic                             |

| 3.3.4    | Register Addressing                      |

| 3.3.5    | Rate Selection                           |

| 3.3.6    | Interrupt and Flag Logic                 |

| 3.3.7    | Mode Control                             |

| 3.3.7.1  | Single Interval Mode (Mode 0)            |

| 3.3.7.2  | Repeated Interval Mode (Mode 1)          |

| 3.3.7.3  | External Event Timing Mode (Mode 2)      |

| 3.3.7.4  | External Event Timing from Zero (Mode 2) |

| 3.3.8    | Schmitt Trigger – Pulse Shaping          |

|          | LPSVC DISPLAY CONTROL                    |

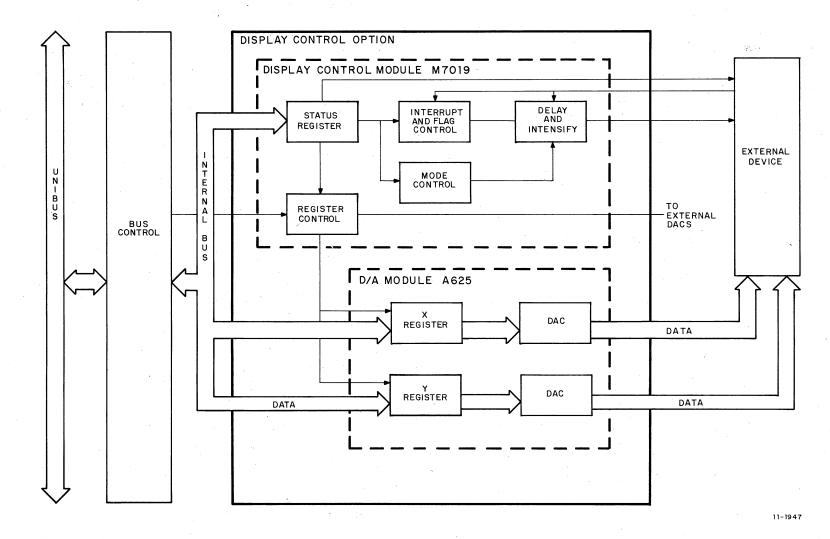

| 3.4.1    | Block Diagram Discussion                 |

| 3.4.2    | Programming                              |

| 3.4.3    | Status Register Gating                   |

| 3.4.4    | Intensification Modes                    |

| 3.4.4.1  | Normal Mode                              |

| 3.4.4.2  | X Mode                                   |

|          |                                          |

# CONTENTS (Cont)

|                                                                                                                                                                                         | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4.4.3                                                                                                                                                                                 | Y Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.4.4.4                                                                                                                                                                                 | XY Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

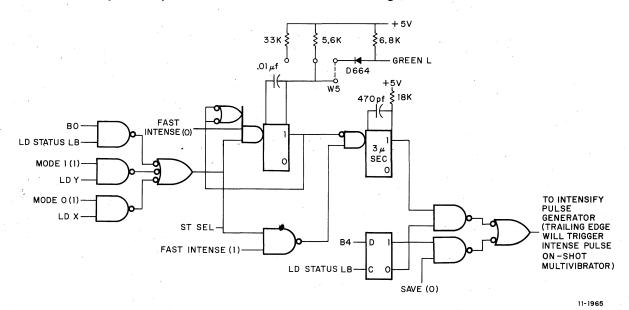

| 3.4.5                                                                                                                                                                                   | Deflection Delay Circuitry 3-56                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.5.1                                                                                                                                                                                 | Normal Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.4.5.2                                                                                                                                                                                 | Fast Intensify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

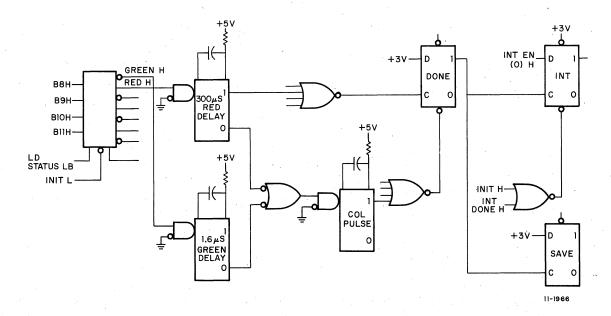

| 3.4.6                                                                                                                                                                                   | VR20 Color Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.4.6.1                                                                                                                                                                                 | Changing Modes (VR20 Setup Delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.4.6.2                                                                                                                                                                                 | Green Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4.6.3                                                                                                                                                                                 | Red Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.4.7                                                                                                                                                                                   | VR14-VR20 Channel Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

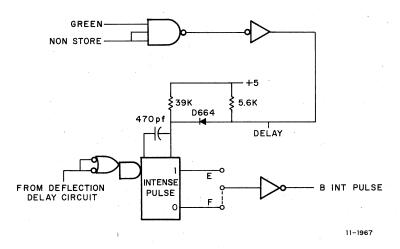

| 3.4.8                                                                                                                                                                                   | Storage Scope Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

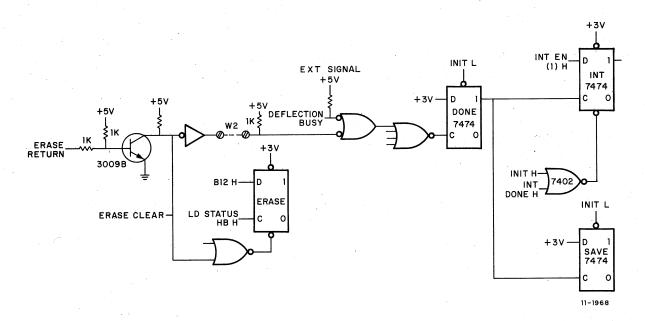

| 3.4.9                                                                                                                                                                                   | Flag and Interrupt Circuits   3-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.4.10                                                                                                                                                                                  | A625 Digital-to-Analog Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.4.11                                                                                                                                                                                  | Intensify Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

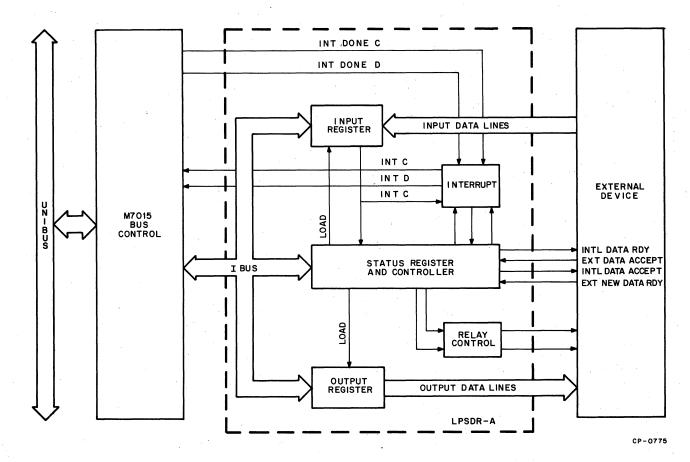

| 3.5                                                                                                                                                                                     | DIGITAL I/O $-$ LPSDR-A                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.1                                                                                                                                                                                   | Block Diagram Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

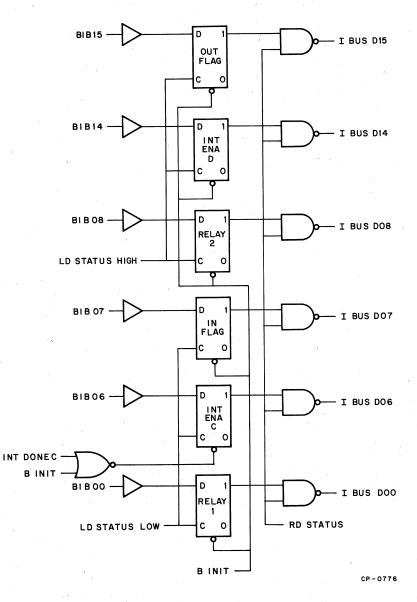

| 3.5.2                                                                                                                                                                                   | Register Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.5.3                                                                                                                                                                                   | Input Register Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.5.4                                                                                                                                                                                   | Input Register Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.5.5                                                                                                                                                                                   | Output Register Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.5.6                                                                                                                                                                                   | Input Control and Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.5.7                                                                                                                                                                                   | Output Control and Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

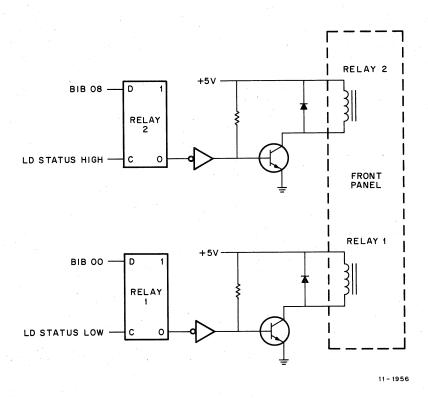

| 3.5.8                                                                                                                                                                                   | Relays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2.0                                                                                                                                                                                   | Itolayo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 359                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.5.9<br>3.6                                                                                                                                                                            | Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6                                                                                                                                                                                     | Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6<br>3.6.1                                                                                                                                                                            | Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6<br>3.6.1<br>3.6.2                                                                                                                                                                   | Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3                                                                                                                                                          | Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

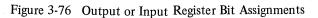

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4                                                                                                                                                 | Programming         3-69           POWER SUPPLY         3-69           Block Diagram Discussion         3-69           Power Control         3-69           +5 Vdc Supply         3-69           ±15V Precision Supply         3-71                                                                                                                                                                                                                                                                |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5                                                                                                                                        | Programming       3-69         POWER SUPPLY       3-69         Block Diagram Discussion       3-69         Power Control       3-69         +5 Vdc Supply       3-69         ±15V Precision Supply       3-71         LTC Circuit       3-71                                                                                                                                                                                                                                                       |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6                                                                                                                               | Programming       3-69         POWER SUPPLY       3-69         Block Diagram Discussion       3-69         Power Control       3-69         +5 Vdc Supply       3-69         ±15V Precision Supply       3-71         LTC Circuit       3-71         AC LOW Circuit       3-71                                                                                                                                                                                                                     |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5                                                                                                                                        | Programming       3-69         POWER SUPPLY       3-69         Block Diagram Discussion       3-69         Power Control       3-69         +5 Vdc Supply       3-69         ±15V Precision Supply       3-71         LTC Circuit       3-71                                                                                                                                                                                                                                                       |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6                                                                                                                               | Programming       3-69         POWER SUPPLY       3-69         Block Diagram Discussion       3-69         Power Control       3-69         +5 Vdc Supply       3-69         ±15V Precision Supply       3-69         ±15V Precision Supply       3-71         LTC Circuit       3-71         AC LOW Circuit       3-71         DC LOW Circuit       3-71         ADJUSTMENT AND CALIBRATION                                                                                                       |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b>                                                                                                  | Programming       3-69         POWER SUPPLY       3-69         Block Diagram Discussion       3-69         Power Control       3-69         +5 Vdc Supply       3-69         ±15V Precision Supply       3-69         ±15V Precision Supply       3-71         LTC Circuit       3-71         AC LOW Circuit       3-71         DC LOW Circuit       3-71         ADJUSTMENT AND CALIBRATION                                                                                                       |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1                                                                                           | Programming       3-69         POWER SUPPLY       3-69         Block Diagram Discussion       3-69         Power Control       3-69         +5 Vdc Supply       3-69         ±15V Precision Supply       3-69         ±15V Precision Supply       3-71         LTC Circuit       3-71         AC LOW Circuit       3-71         DC LOW Circuit       3-71         ADJUSTMENT AND CALIBRATION       4-1                                                                                             |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1                                                                                  | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71ADJUSTMENT AND CALIBRATION4-1M7019 Scope Control Jumper Data4-1                                                                                                                                                                                                                |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2                                                                         | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71ADJUSTMENT AND CALIBRATION4-1M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3                                                                                                                                                                                                                  |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3                                                                | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71ADJUSTMENT AND CALIBRATION4-1M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4                                                                                                                                                                               |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2                                                         | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71ADJUSTMENT AND CALIBRATION4-1M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPSV1-S ANALOG SYSTEM4-5                                                                                                                                                       |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1                                                | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71ADJUSTMENT AND CALIBRATION4-1M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPS11-S ANALOG SYSTEM4-5Initial Conditions4-5                                                                                                                                  |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2                              | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71ADJUSTMENT AND CALIBRATION4-1M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPS11-S ANALOG SYSTEM4-5Initial Conditions4-6Test Equipment and Diagnostic Programs4-6                                                                |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3                              | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71ADJUSTMENT AND CALIBRATIONLPSVC DISPLAY CONTROL4-1M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPS11-S ANALOG SYSTEM4-5Initial Conditions4-5Test Equipment and Diagnostic Programs4-6Single Sample-and-Hold System Calibration4-7                        |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                     | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPS11-S ANALOG SYSTEM4-5Initial Conditions4-5Test Equipment and Diagnostic Programs4-6Single Sample-and-Hold System Calibration4-7Dual Sample-and-Hold System Calibration4-7                                |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5            | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPS11-S ANALOG SYSTEM4-5Initial Conditions4-5Test Equipment and Diagnostic Programs4-6Single Sample-and-Hold System Calibration4-7Switch Gain Multiplexer Calibration4-8                                    |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.5.1 | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71MT019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPS11-S ANALOG SYSTEM4-5Initial Conditions4-5Test Equipment and Diagnostic Programs4-6Single Sample-and-Hold System Calibration4-7Dual Sample-and-Hold System Calibration4-8EDC Voltage Source Available4-8 |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br><b>CHAPTER 4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5            | Programming3-69POWER SUPPLY3-69Block Diagram Discussion3-69Power Control3-69+5 Vdc Supply3-69±15V Precision Supply3-71LTC Circuit3-71AC LOW Circuit3-71DC LOW Circuit3-71DC LOW Circuit3-71M7019 Scope Control Jumper Data4-1A625 DAC Jumper Data4-3A625 Offset and Gain Adjustments4-4LPS11-S ANALOG SYSTEM4-5Initial Conditions4-5Test Equipment and Diagnostic Programs4-6Single Sample-and-Hold System Calibration4-7Switch Gain Multiplexer Calibration4-8                                    |

CHAPTER 5 SYSTEM TROUBLESHOOTING

### ILLUSTRATIONS

| <b>T</b> . |     | T T |  |

|------------|-----|-----|--|

| H 10       | nre | No. |  |

|            |     |     |  |

### Title

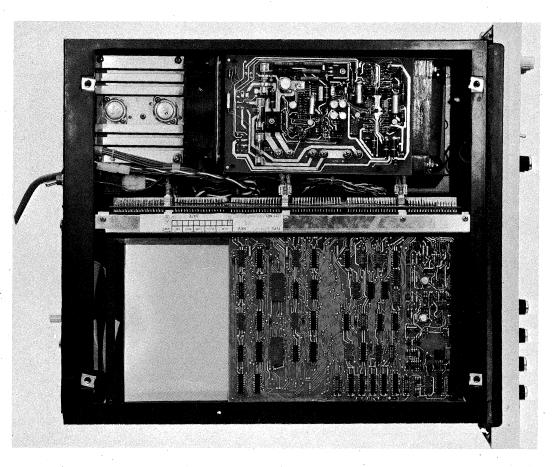

| 1-1          | LPS11-S Laboratory Peripheral System                            | . 1-1  |

|--------------|-----------------------------------------------------------------|--------|

| 1-2          | LPS11-S Laboratory Peripheral System and Options, Block Diagram | . 1-3  |

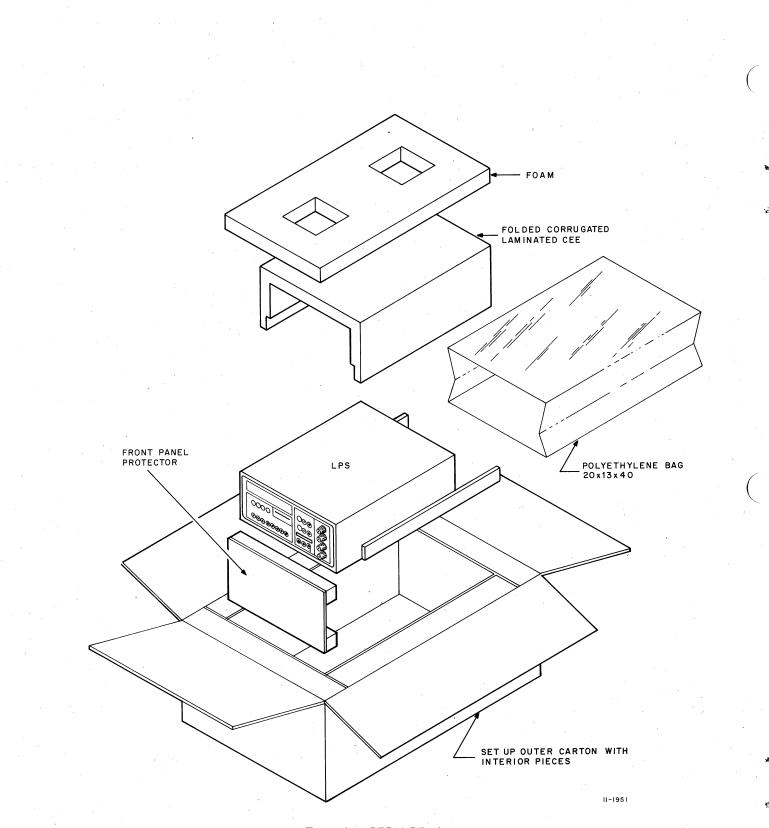

| 2-1          | LPS11-S Packaging                                               |        |

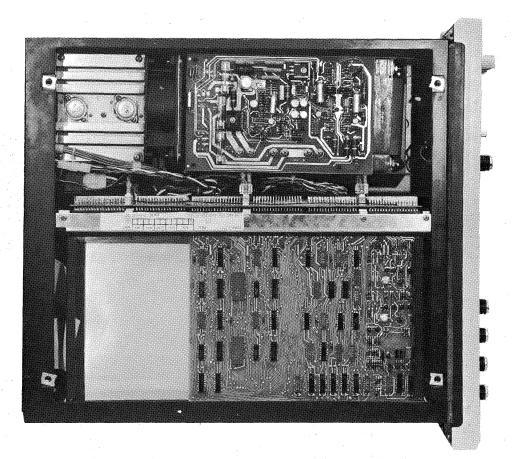

| 2-2          | LPS11-S with Top Cover Removed                                  |        |

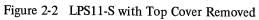

| 2-3          | LPS11-S Mounting Box with Top Cover and Side Panel Removed      |        |

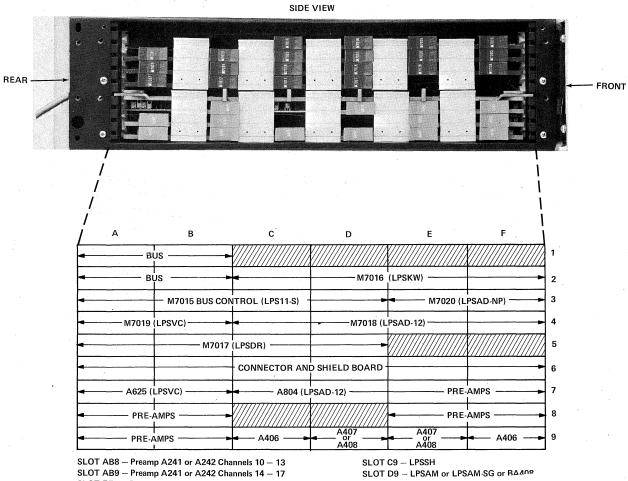

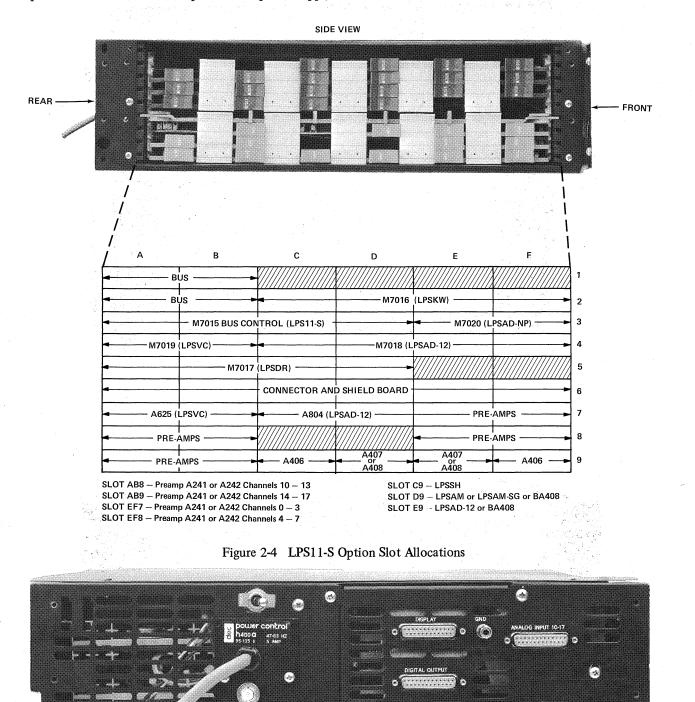

| 2-4          | LPS11-S Option Slot Allocations                                 |        |

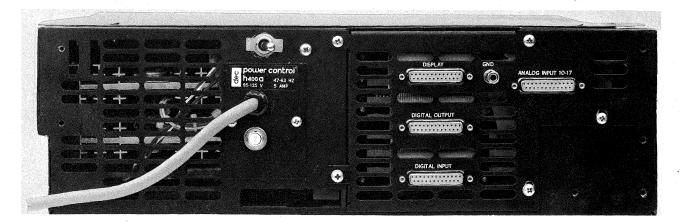

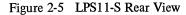

| 2-5          | LPS11-S Rear View                                               |        |

| 3-1          | Bus Control Block Diagram                                       |        |

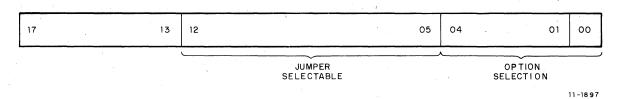

| 3-2          | Address Register Bit Assignments                                |        |

| 3-3          | Address Control Logic                                           |        |

| 3-4          | Internal Bus Logic                                              |        |

| 3-4          |                                                                 |        |

| 3-5<br>3-6   | Bus Request Logic                                               |        |

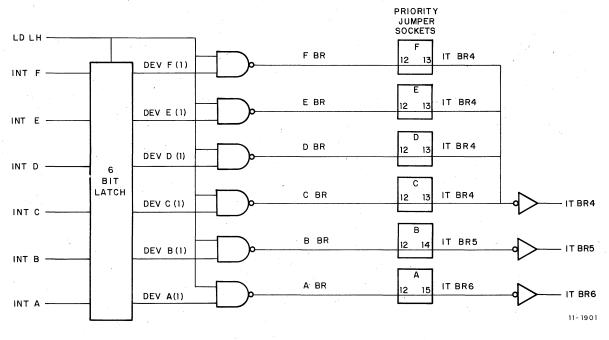

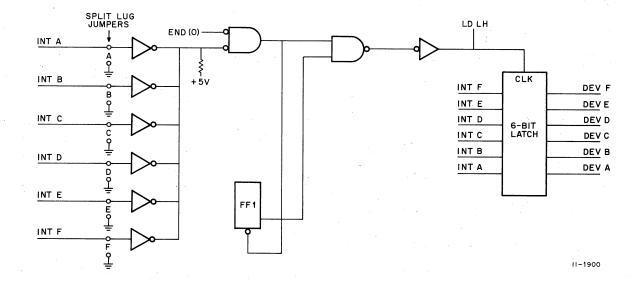

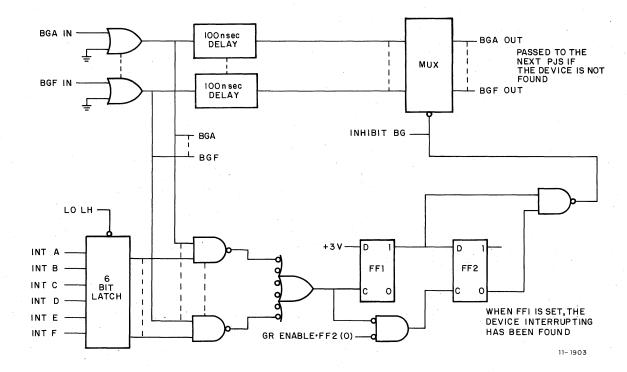

| 3-7          | 6-Bit Latch Logic                                               |        |

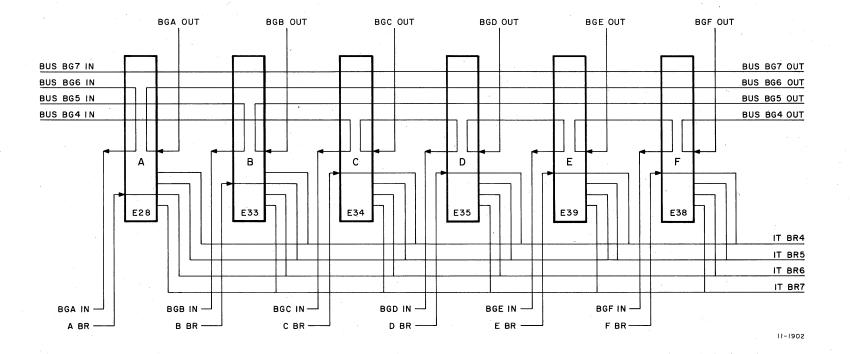

|              | Standard Priority Jumper Configuration                          |        |

| 3-8          | Bus Grant Inhibit Logic                                         |        |

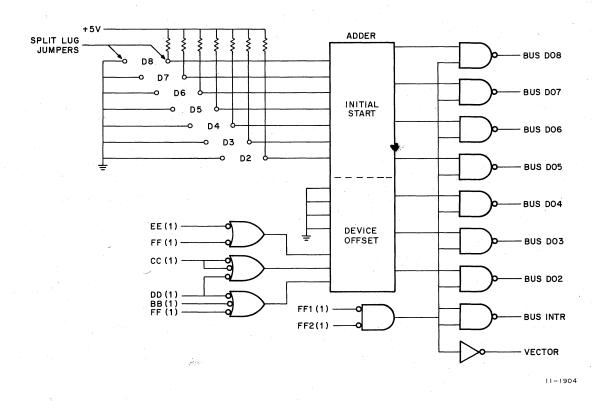

| 3-9          | Vector Address Adder                                            |        |

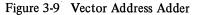

| 3-10         | Interrupt Timing                                                |        |

| 3-11         | A/D Converter Block Diagram                                     |        |

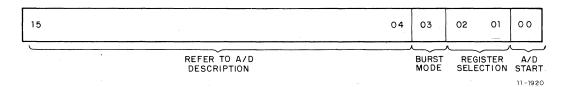

| 3-12         | A/D Status Register Bit Assignments                             |        |

| 3-13         | A/D Buffer Bit Assignments as a Read-Only Address               |        |

| 3-14         | LED Register Bit Assignments as a Write-Only Address            |        |

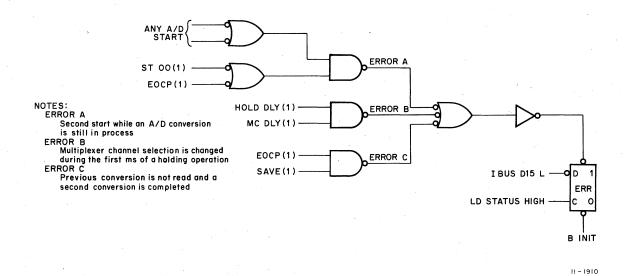

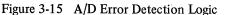

| 3-15         | A/D Error Detection Logic                                       |        |

| 3-16         | A/D Addressing Logic                                            | . 3-17 |

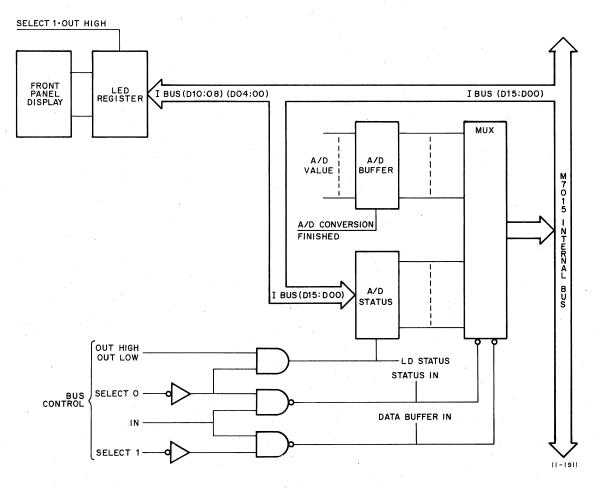

| 3-17         | Program and Clock A/D Start Logic                               | . 3-18 |

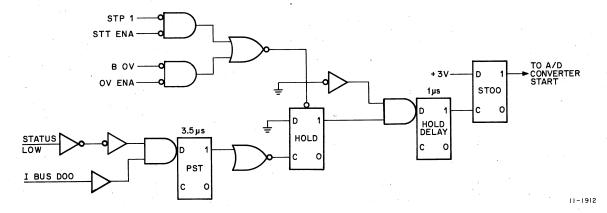

| 3-18         | Basic EOCP Functions and Interrupt Logic                        | . 3-19 |

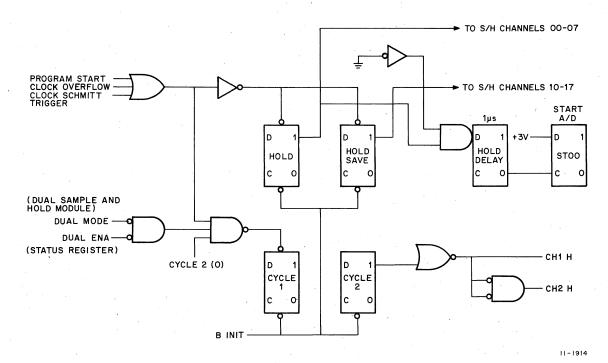

| 3-19         | Dual Sample-and-Hold Control (Sheet 1)                          | . 3-19 |

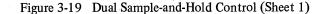

| 3-20         | Dual Sample-and-Hold Control (Sheet 2)                          | . 3-20 |

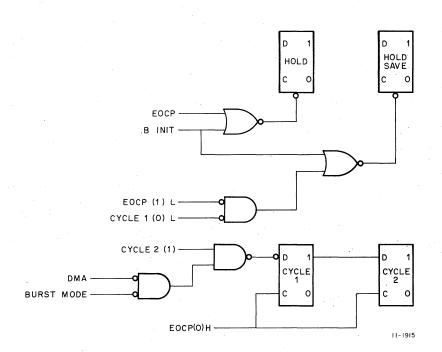

| 3-21         | Dual Sample-and-Hold Timing                                     | . 3-21 |

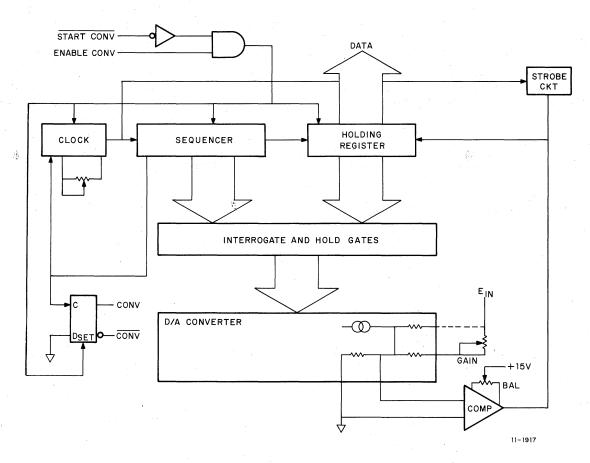

| 3-22         | A804 Simplified Block Diagram                                   |        |

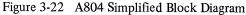

| 3-23         | A804 Timing Requirements                                        |        |

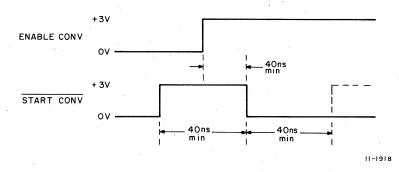

| 3-24         | DMA Register Control Block Diagram                              |        |

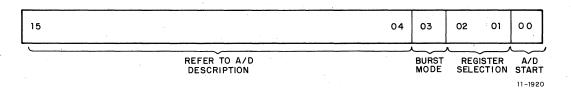

| 3-25         | A/D Status Register DMA Bit Assignments                         |        |

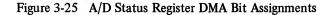

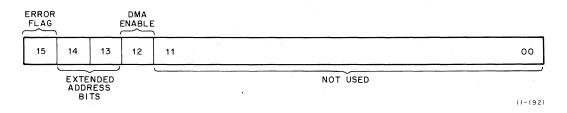

| 3-26         | DMA Status Register Bit Assignments                             |        |

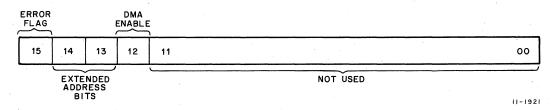

| 3-27         | Word Count Register                                             |        |

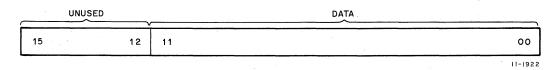

| 3-28         | Current Address                                                 |        |

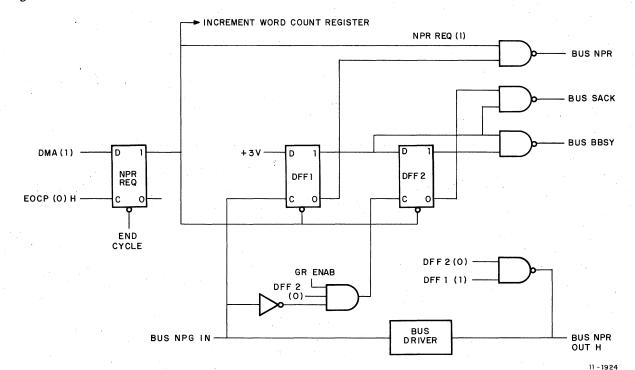

| 3-29         | DMA Bus Control Logic                                           |        |

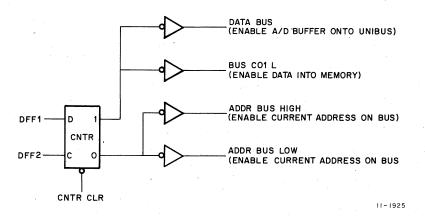

| 3-30         | Functions of the CNTR Flip-Flop                                 |        |

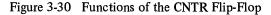

| 3-31         | A/D Buffer to Unibus                                            | 3.29   |

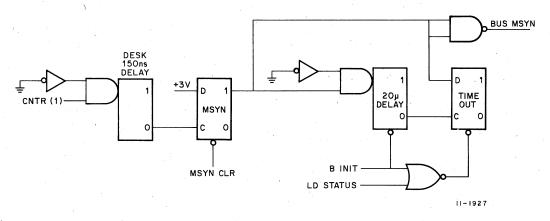

| 3-32         | Generating MSYN                                                 |        |

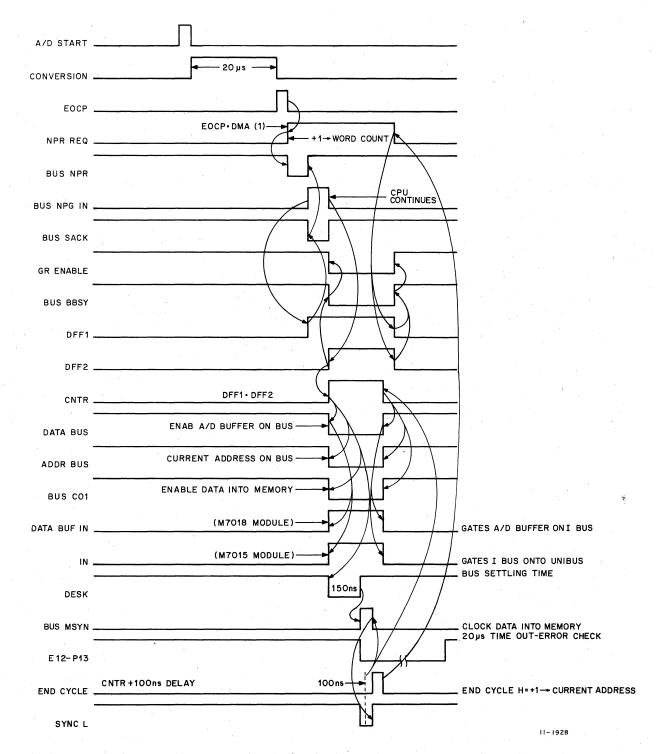

| 3-33         | Single DMA Transfer Timing                                      |        |

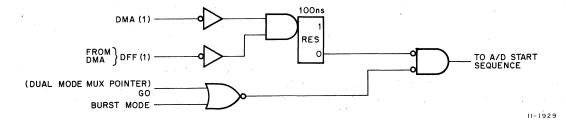

| 3-34         | DMA Dual Sample-and-Hold A/D Conversion Start                   |        |

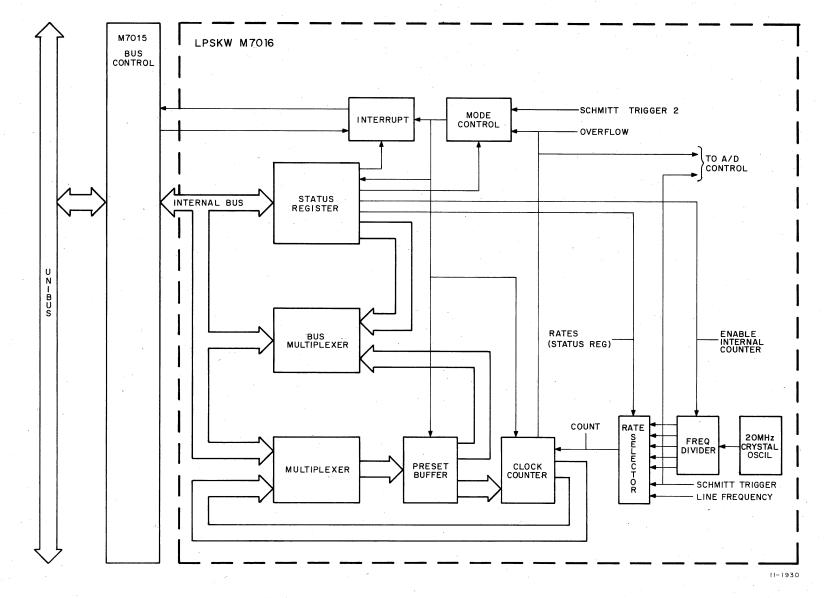

| 3-35         | LPSKW Clock Block Diagram                                       |        |

| 3-36         | Clock Status Register Bit Assignments                           |        |

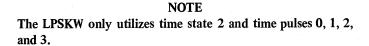

| 3-30         | Timing Generator                                                |        |

| 3-38         | Real-Time Clock Timing Diagram                                  |        |

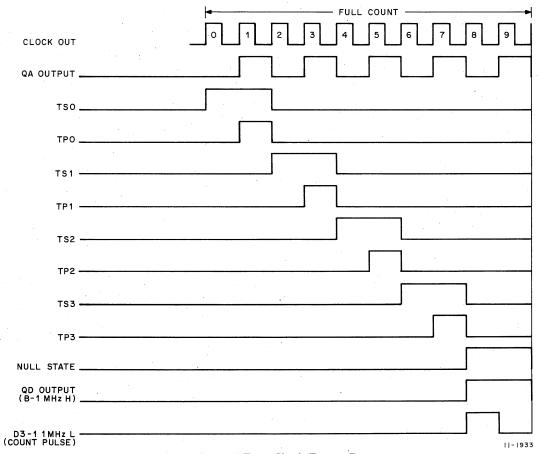

| 3-39         | Clock Status Register Gating                                    |        |

| 3-39<br>3-40 |                                                                 |        |

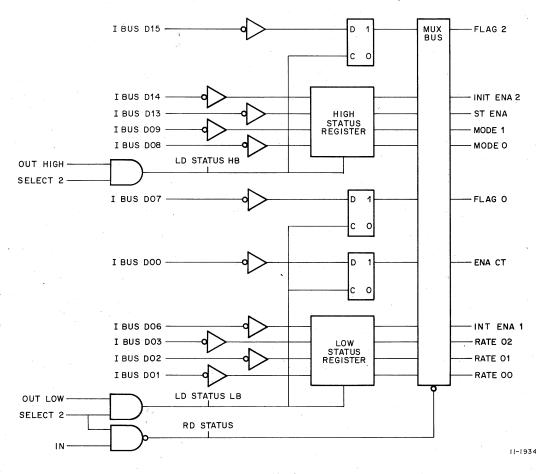

| 3-40         | Clock Preset Buffer Gating                                      | . 3-39 |

# **ILLUSTRATIONS (Cont)**

# Figure No.

# Title

| P | a | g | e |

|---|---|---|---|

| Г | a | g | e |

| 2.41 |                                                  |

|------|--------------------------------------------------|

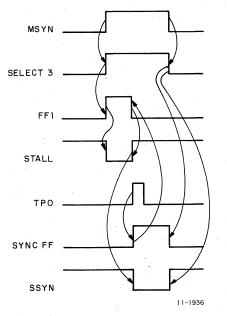

| 3-41 | Load Operation Timing Diagram                    |

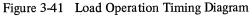

| 3-42 | Rate Selection Logic                             |

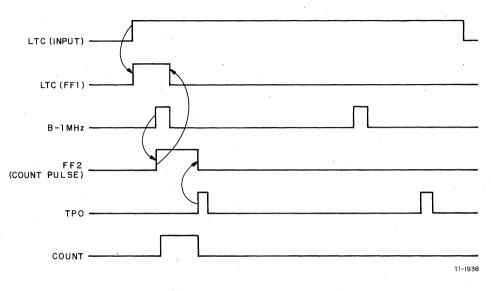

| 3-43 | Count Pulse Timing Diagram                       |

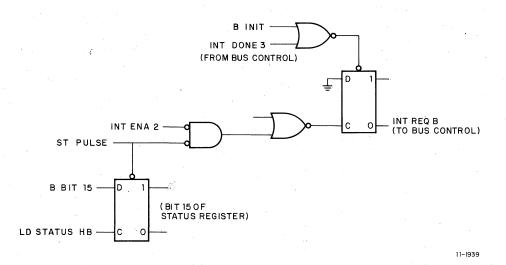

| 3-44 | Schmitt Trigger #1 Interrupt Logic               |

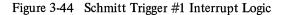

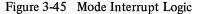

| 3-45 | Mode Interrupt Logic                             |

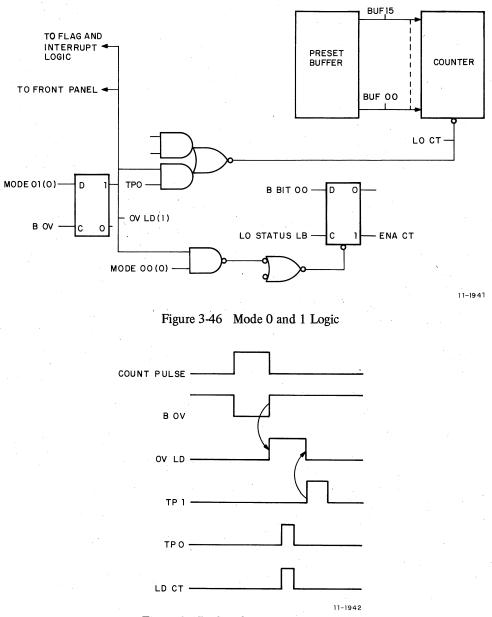

| 3-46 | Mode 0 and 1 Logic                               |

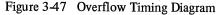

| 3-47 | Overflow Timing Diagram                          |

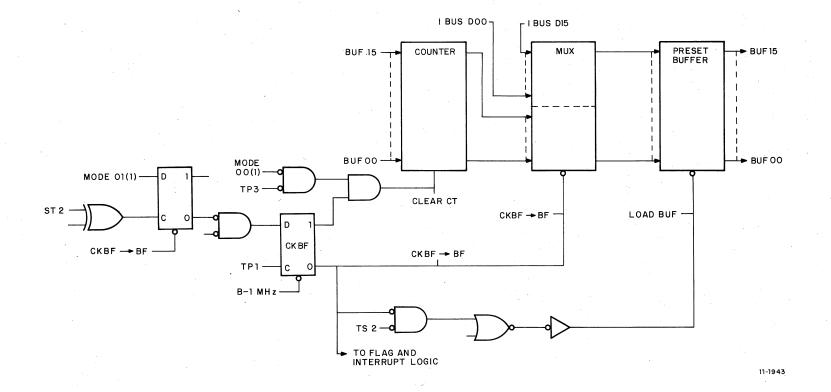

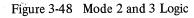

| 3-48 | Mode 2 and 3 Logic                               |

| 3-49 | Mode 2 and 3 Timing                              |

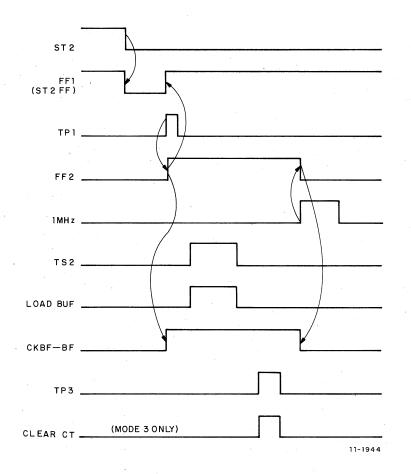

| 3-50 | Hysteresis Example                               |

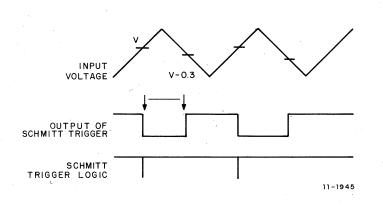

| 3-51 | Schmitt Trigger Simplified Schematic Diagram     |

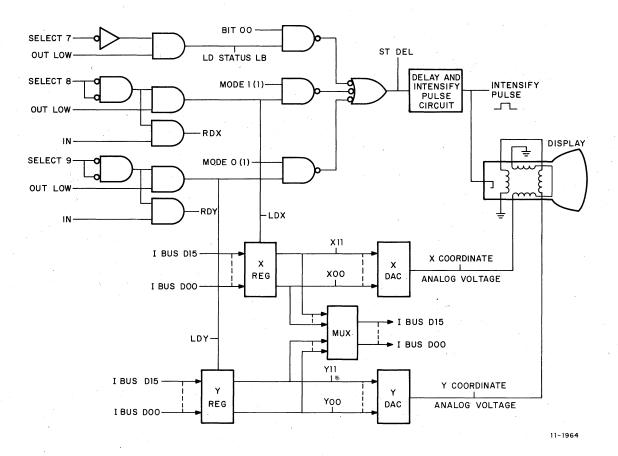

| 3-52 | Display Control Block Diagram                    |

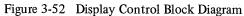

| 3-53 | Display Control Status Register Bit Assignments  |

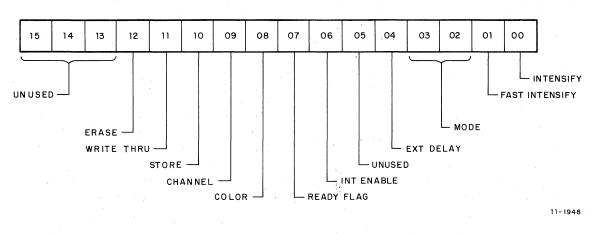

| 3-54 | Display Control Grid Coordinate Scheme           |

| 3-55 | X and Y Register Bit Assignments 3-54            |

| 3-56 | Modes of Intensifying a Point                    |

| 3-57 | Deflection Delay Circuit                         |

| 3-58 | Delay Circuitry for VR20 Setup Time              |

| 3-59 | Intensify Pulse Generator                        |

| 3-60 | Storage Scope Logic                              |

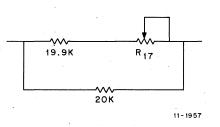

| 3-61 | Example of Rx Value                              |

| 3-62 | Digital I/O Block Diagram                        |

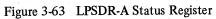

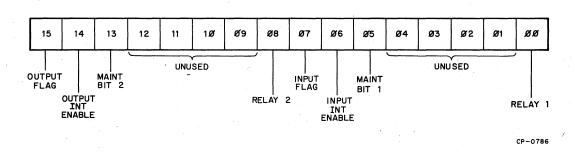

| 3-63 | LPSDR-A Status Register                          |

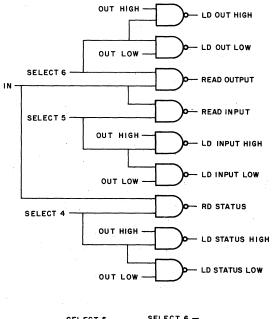

| 3-64 | Address Control Signal Gating                    |

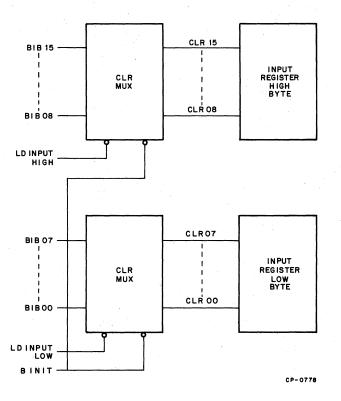

| 3-65 | Clear Multiplexers                               |

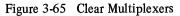

| 3-66 | Input Register                                   |

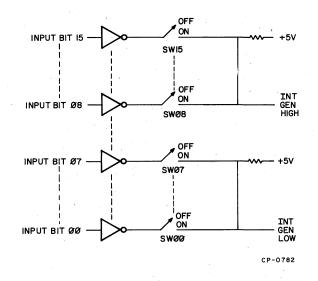

| 3-67 | Input Register Interrupt Switches                |

| 3-68 | Output Register                                  |

| 3-69 | Interrupt Circuit                                |

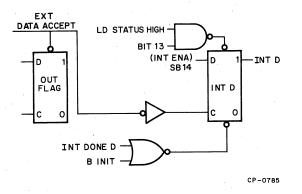

| 3-70 | LPSDR-A Interrupt Structure for Input Register   |

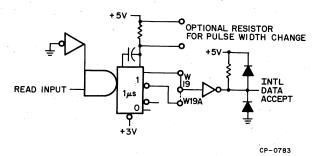

| 3-71 | INTL DATA ACCEPT Circuit                         |

| 3-72 | INTL NEW DATA READY Circuit                      |

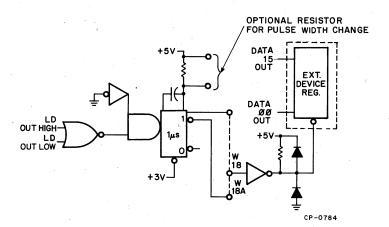

| 3-73 | Output Register Data Accept                      |

| 3-74 | Relays                                           |

| 3-75 | LPSDR-A Status Register Bit Assgnments           |

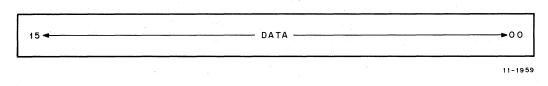

| 3-76 | Output or Input Register Bit Assignments         |

| 3-77 | Power Supply Block Diagram                       |

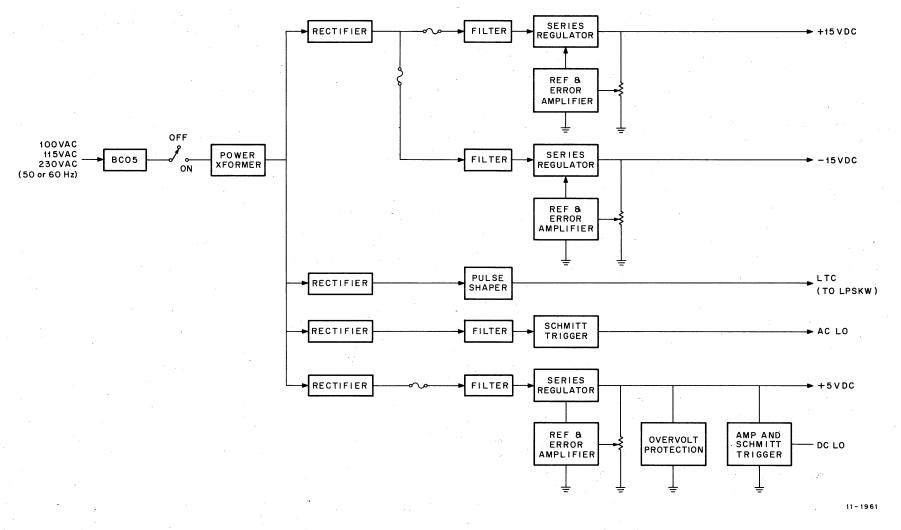

| 4-1  | Location of A625 Offset and Gain Adjustments     |

| 4-1  | EDC Voltage Source, Showing Floating Power Lines |

| -T-2 | EDC voltage Source, Showing Floating rower Lines |

## TABLES

Table No.

| Table No. | Title                                                                | Page         |

|-----------|----------------------------------------------------------------------|--------------|

| 1-1       | Related Documentation                                                | 1-2          |

| 2-1       | 115/230V Jumper and Circuit Breaker Configuration                    |              |

| 2-2       | LPS11-S Power Checks                                                 | · 2-5<br>2-6 |

| 3-1       | LPS11-S Option Address Assignments                                   | 3.2          |

| 3-2       | 4–16 Option Decoder                                                  | 3-3          |

| 3-3       | Data Transfer                                                        | . 3-5        |

| 3-4       | Standard Priority Configuration                                      | 3-6          |

| 3-5       | Standard Vector Address Assignments                                  | . 3-10       |

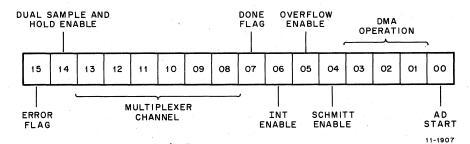

| 3-6       | A/D Status Register Bit Functions                                    | . 3-13       |

| 3-7       | A/D Converter Digital Output With No Offset Applied                  | . 3-14       |

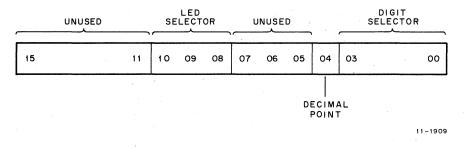

| 3-8       | LED Register Bit Functions                                           |              |

| 3-9       | A804 Coding                                                          | . 3-23       |

| 3-10      | A/D Status Register Illustrating DMA Bit Functions                   | . 3-27       |

| 3-11      | DMA Status Register Bit Functions                                    | . 3-27       |

| 3-12      | Clock Status Register Bit Functions                                  | . 3-34       |

| 3-13      | Divide-by-10 Counter                                                 | . 3-37       |

| 3-14      | Clock Count Rates                                                    | . 3-40       |

| 3-15      | Clock Status Register Bits 09 and 08                                 | . 3-43       |

| 3-16      | =1 Voltage Threshold Positive Slop Chart                             | . 3-48       |

| 3-17      | =1 Voltage Threshold Negative Slop Chart                             |              |

| 3-18      | Display Control Status Register Bit Functions                        |              |

| 3-19      | Modes of Intensification                                             |              |

| 3-20      | Bit 14 and 15 Jumpers                                                |              |

| 3-21      | Mode Selection Jumpers                                               | . 3-65       |

| 3-22      | Pulse Width Resistors for INTL DATA Accept                           | . 3-68       |

| 3-23      | Output Register Bit Functions                                        |              |

| 3-24      | Output Register Bit Functions                                        | . 3-71       |

| 3-25      | Input Register Bit Functions                                         |              |

| 4-1       | LPSVC Display Control Jumper Connection Data                         |              |

| 4-2       | M7019 Gain and Offset                                                |              |

| 4-3       | VR20 Delay Time Variations                                           |              |

| 4-4       | A625 Voltage Gain Selection                                          |              |

| 4-5       | A625 Bipolar/Unipolar Selection                                      |              |

| 4-6       | A625 Jumper Functions                                                | . 4-4        |

| 4-7       | Output Symmetry vs Binary Input                                      |              |

| 4-8       | Initial Calibration Specifications for LPS11-S Analog System Modules |              |

| 4-9       | Sample-and-Hold System Calibration Data                              |              |

| 5-1       | Diagnostic Programs for LPS Options                                  |              |

| 5-2       | LPSKW Data: DZLPD, Test A                                            |              |

| 5-3       | LPSDR Data: DZLPD, Test B                                            |              |

| 5-4       | LPSVC Data: DZLPD, Test C                                            |              |

| 5-5       | LPSAD-12 Data: DZLPC, Test A                                         |              |

| 5-6       | LPSAD-NP Data: DZLPC, Test B                                         |              |

|           |                                                                      |              |

# CHAPTER 1 INTRODUCTION AND DESCRIPTION

#### 1.1 INTRODUCTION

The LPS11-S Laboratory Peripheral System is a high-performance, modular, real-time subsystem that interfaces with the PDP-11 family of computers via a single asynchronous bus, the Unibus. The flexibility of the LPS11-S makes it well suited to a variety of applications in general laboratory operation, including biomedical research, analytical instrumentation, data collection and reduction, monitoring, data logging, industrial testing, engineering, and technical education.

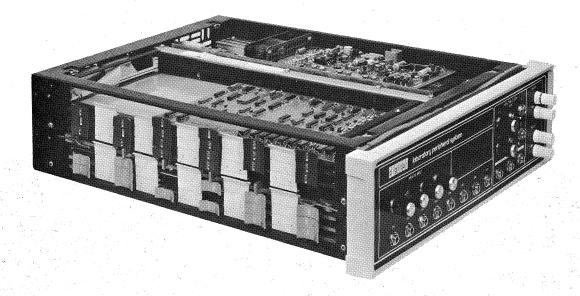

The basic LPS11-S comprises the Unibus interface, front and back access panels, prewired slots for modular plug-in options, and a power supply, all housed within a single cabinet, which can be operated either mounted in a cabinet rack or placed upon a desk or table (Figure 1-1).

Figure 1-1 LPS11-S Laboratory Peripheral System

The plug-in options are defined in relation to the LPS11-S, and not to the PDP-11 Unibus. The basic system can be expanded to contain a 12-bit, 16-channel analog-to-digital system with direct memory access and dual sample-and-hold capabilities and a six-digit numeric light-emitting diode (LED) readout. A real-time programmable clock, a digital input/output interface, and a scope control can be added to make a complete LPS11-S system.

#### 1.2 SCOPE

This manual provides sufficient installation, theory of operation, programming, and maintenance information to enable the user to operate and maintain the LPS11-S Laboratory Peripheral System. Chapter 1 introduces and describes the LPS11-S on a block diagram level and provides specifications for the basic unit and its options.

Chapter 2 deals with the various aspects of installation that pertain to the LPS11-S and each of the available options.

Chapter 3 discusses the theory of operation for the benefit of the LPS11-S user and maintenance personnel. Operation of each subsystem or unit is described from a block diagram and a detailed circuit analysis point of view. Such description presupposes that the reader is familiar with DEC logic and the PDP-11 family of processors.

Chapter 4 describes the various adjustments and calibrations that might be required in the maintenance of the LPS11-S, while Chapter 5 contains reference information necessary for system troubleshooting.

Programming information in this manual is limited to the level required for system maintenance. For detailed information regarding programming, refer to the appropriate manual from the related documentation listed in Table 1-1. Information about other PDP-11 equipment is also available in that list of documentation.

| Related Documentation                                     |                                          |  |  |

|-----------------------------------------------------------|------------------------------------------|--|--|

| Document Title                                            | DEC Document No.                         |  |  |

| LPS11-S Laboratory Peripheral System User's Guide         | DEC-11-HLPGA-A-D                         |  |  |

| PDP-11 Peripherals Handbook                               | DEC, 1973-74                             |  |  |

| LPS11-S Laboratory Peripheral System Engineering Drawings | Refer to DEC Drawing No. D-DI-LPS11-0-0. |  |  |

# Table 1-1Related Documentation

#### **1.3 BLOCK DIAGRAM DISCUSSION**

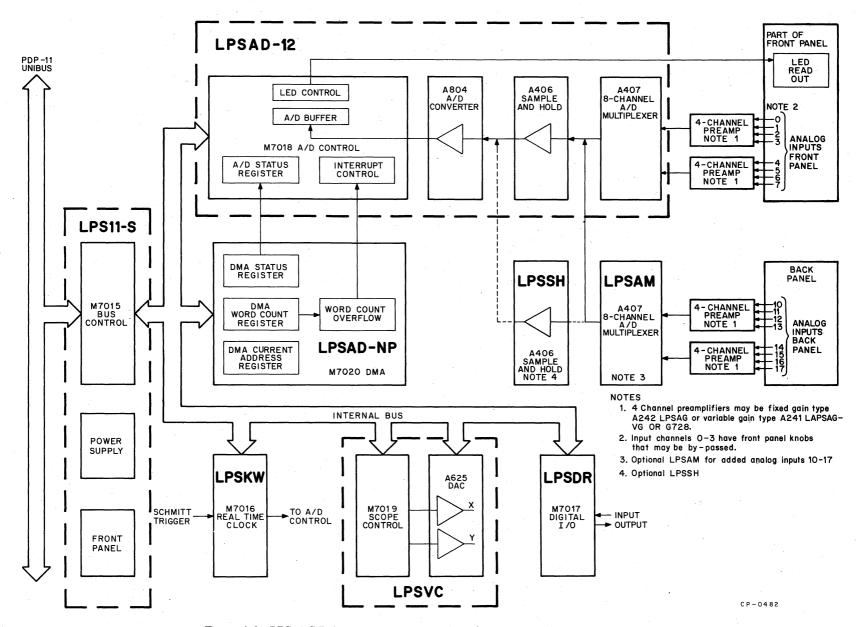

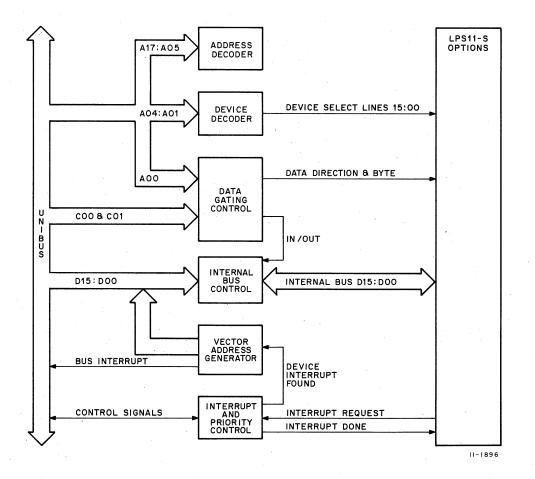

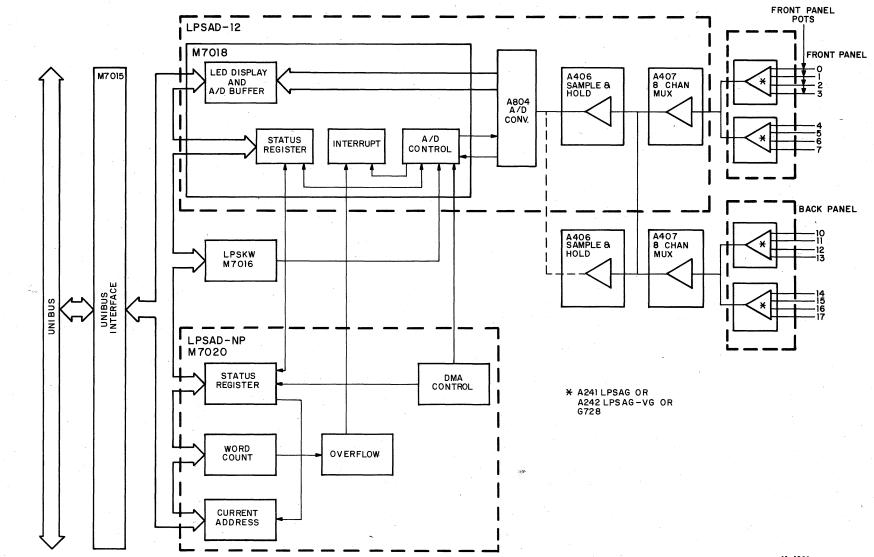

Figure 1-2 is a block diagram of the LPS11-S Laboratory Peripheral System, together with the available options. The system communicates with the PDP-11 Unibus through the M7015 Unibus Interface module, which is referred to herein as the *bus control*.

#### 1.3.1 Bus Control

The bus control decodes all option addresses, controls all interrupts and vector addresses, buffers the PDP-11 Unibus, and creates a secondary internal bus. The bus control is capable of controlling multiple interrupts, each with an assigned priority level. A vector address is associated with each interrupt. The first vector address is jumper-selectable; the remaining five vectors follow in sequence.

The various LPS11-S options are connected to the internal bus, as shown in Figure 1-2, and the bus control serves to buffer the Unibus from them so that the LPS11-S system package appears as a single unit load on the PDP-11 Unibus.

#### 1.3.2 LPSAD-12 A/D Converter System Option

The LPSAD-12 A/D Converter enables the user to sample analog data at specified rates and store the equivalent digital value for subsequent processing. Sample-and-hold circuits ensure accurate A/D conversion of rapidly changing signals by holding the input voltage constant until the A/D conversion process is completed. A multiplexer permits the A/D converter to handle eight analog input channels, which are designated 0 through 7. Channels 0 through 3 are connected to phone jacks on the front panel and/or potentiometers that can be used to establish program parameters. The remaining four channels, 4 through 7, are only accessible via phone jacks on the front panel.

A six-digit LED display on the front panel can be used as a general-purpose programmable device to display A/D conversions, time readout of the real-time clock, processor address readouts, or a digital I/O status indication.

Figure 1-2 LPS11-S Laboratory Peripheral System and Options, Block Diagram

1**-**3

The following options are available with the LPSAD-12 A/D Converter system:

- a. LPSAM 8-Channel Expansion Multiplexer The LPSAM allows the system to be expanded to handle eight additional analog input channels. These channels, designated 10 through 17, are accessible at the rear panel.

- b. LPSAD-NP Direct Memory Access (DMA) The LPSAD-NP Direct Memory Access option allows the A/D conversions to be stored in memory at maximum rates without processor intervention.

- c. LPSAG and LPSAG-VG Preamplifiers The LPSAG 4-Channel Preamplifier option provides preamplifiers for four analog input channels that provide each channel with a ±1V differential input. The LPSAG-VG option provides additional ranges of 0 to 2V, ±5V, and 0 to 10V.

- d. LPSSH Dual Sample-and-Hold The LPSSH Dual Sample-and-Hold option allows the simultaneous acquisition of data from two predetermined channels.

#### 1.3.3 LPSKW Programmable Real-Time Clock

The LPSKW Programmable Real-Time Clock option provides several methods of accurately measuring and counting intervals and events. It can be used to synchronize the central processor to external events, measure time intervals between events, provide interrupts at programmed intervals, or start analog-to-digital conversions with the overflow from the clock counter or the firing of a Schmitt trigger. Many of these operations can be performed concurrently.

#### **1.3.4 LPSVC Display Control**

The LPSVC Display Control option can operate with the DEC VR14 CRT Display or the VR20 Two-Color CRT Display, or with the Tektronix RM503, 602, 604, 611, or 613 Storage Display oscilloscopes. The LPSVC Display Control can produce a display in the form of a  $4096_{10} \times 4096_{10}$  dot array. The display control offers four program-controlled modes of intensification.

#### 1.3.5 LPSDR Digital Input/Output

The LPSDR Digital I/O option consists of a 16-bit buffered input register and a 16-bit buffered output register. Program control of input/output data is achieved in either of two selectable modes. The program transfer mode controls the transfer of data between the digital I/O registers and memory. The external interrupt mode allows an external device to initiate the transfer of data. Two programmable, normally-open relays provide a convenient means of controlling laboratory equipment.

#### 1.4 SPECIFICATIONS SUMMARY

| 1.4.1 LPSAD-12 A/D Converter                  |                                                              |

|-----------------------------------------------|--------------------------------------------------------------|

| Input Voltage Range:                          | ±5V, single-ended                                            |

| Input Channels:                               | 8                                                            |

| Input Impedance:                              | $10^9\Omega$ in parallel with 100 pF, measured at rear panel |

| Input Bias Current:<br>Channel on +10V input: | 200 nA typical; channel on input clamps to $\pm 10V$         |

| Channel off:                                  | 200 nA typical                                               |

| Switching transient:                          | $-5$ mA maximum, 0.5 $\mu$ s maximum                         |

Resolution: 12 bits (1 part in 4096) can be reduced to 8, 9, 10, or 11 bits for faster conversion time with switch on module **Output Format:** Parallel, 12 bits, right-justified, offset binary, double-buffered Accuracy at 25° C: ±0.035% of full scale Linearity: 0.02% of full scale Differential Linearity: 1 LSB Temperature Stability: 30 ppm/° C  $(0.003\% FS/^{\circ} C)$ Repeatability:  $2 \sigma \leq 1/2$  LSB **Conversion Time:** 20  $\mu$ s time lapse from start command until a 12-bit result is acquired Control: Controlled by programmed instructions, clock counter overflow, or Schmitt trigger from LPSKW Maximum Program Throughput Rate: PDP-11/20 with optimal coding Programmed Start: 40 kHz typical Overflow or Schmitt trigger start: 45 kHz typical 1.4.2 LPSAM Multiplexer Input Voltage Range: ±5V, single-ended 8 Input Channels: Input Impedance:  $10^9 \Omega$  in parallel with 100 pF, measured at rear panel Input Bias Current: Channel on +10V input: 200 nA typical; channel on input clamps to ±10V Channel off: 200 nA typical Switching Transient: -5 mA maximum, 0.5  $\mu$ s maximum ±5V Analog Output Voltage Range: 1.4.3 LPSAG/LPSAG-VG Preamplifier Input Voltage Range: ±1V differential LPSAG: LPSAG-VG:  $\pm 1V$ , 0 to  $\pm 2V$ ,  $\pm 5V$ , 0 to  $\pm 10V$

Input Channels:

1-5

4

| Input Impedance:<br>+ to ground: | 128K in parallel with 100 pF                                                                                                        |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| - to ground:                     | 64K in parallel with 100 pF                                                                                                         |

| Differential:                    | 128K in parallel with 50 pF                                                                                                         |

| Input Bias Current:              | 40 nA maximum at + or - input                                                                                                       |

| Common Mode Rejection:           | 60 dB at 0 to 60 Hz                                                                                                                 |

| Accuracy:                        | 0.005% of full scale                                                                                                                |

| Linearity:                       | 0.005% of full scale                                                                                                                |

| Analog Output Voltage Range:     | ±5V                                                                                                                                 |

| Bandwidth:<br>3 dB:              | 60 kHz                                                                                                                              |

| 1 dB:                            | 30 kHz                                                                                                                              |

| Full power:                      | 4 kHz, ±5V output                                                                                                                   |

| Slew Rate:                       | $0.3 V/\mu s$ , typical                                                                                                             |

| 1.4.4 LPSKW Real-Time Clock      |                                                                                                                                     |

| Input Voltage Range:             | ±5V, nominal                                                                                                                        |

| Input Type:                      | Differential                                                                                                                        |

| Input Impedance:                 | 50K                                                                                                                                 |

| Minimum Input Pulse Width:       | $2 \mu s$ square wave                                                                                                               |

| Maximum Input Voltage:           | ±50 Vdc                                                                                                                             |

| Hysteresis:                      | 0.3V, standard                                                                                                                      |

| Common Mode Rejection:           | 35 dB                                                                                                                               |

| Input Threshold:                 | Variable between ±5V                                                                                                                |

| Slope:                           | + and - switch-selectable                                                                                                           |

| Output Voltages:                 | a. 0 to $5V - falling$ edge denotes firing of the Schmitt trigger; resets upon recrossing the threshold voltage for outputs 1 and 2 |

|                                  | b. Clock overflow; 0 to 5V                                                                                                          |

| Maximum Frequency:               | 50 kHz                                                                                                                              |

| Minimum Input Voltage:           | 0.5V, peak-to-peak standard hysteresis                                                                                              |

1-6

## 1.4.5 LPSVC Display Control

These specifications represent the standard configuration for the VR14 and VR20.

DAC Converter Specifications (Internal and External):

| Resolution:1 part in 4096 (0.025% FS)Absolute Accuracy: $0.1\%$ Slewing Speed: $10V/0.5 \ \mu s$ Settling Time to 0.03%: $4 \ \mu s$ Drive Carabilities: $200 \ ft at 50 \ \mu E/ft achle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                     |

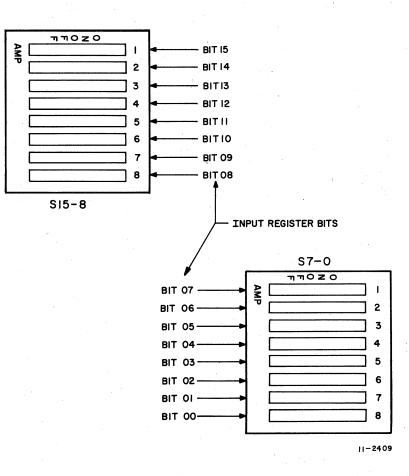

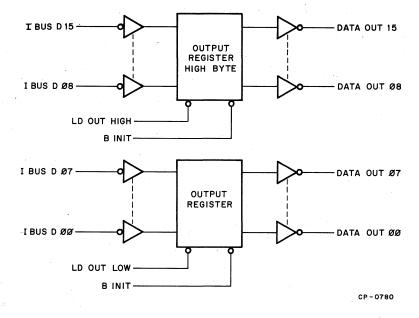

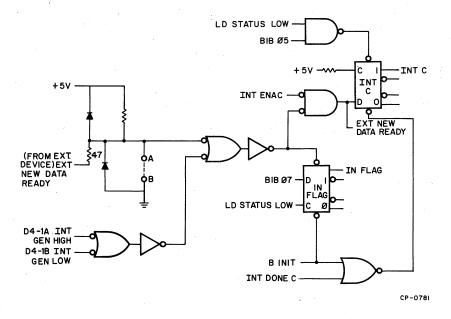

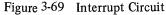

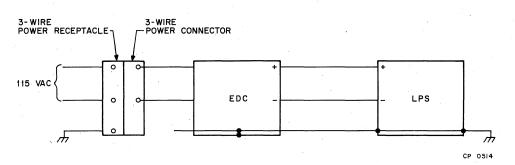

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|