DR11-A General Device Interface

# General Device Interface

DR11-A

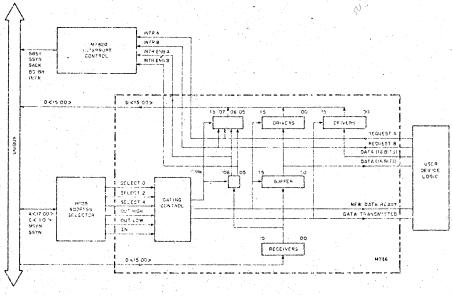

The DR11-A General Device Interface is a set of three logic modules which form a self-contained interface between the PDP-11 UNIBUS and a user's peripheral. The DR11-A performs all of the necessary tasks to communicate with the PDP-11, so that the user may easily interface his device. The simplicity and low cost of the DR11-A demonstrates the utility and power of the PDP-11 UNIBUS concept.

The DR11-A permits bidirectional transfer of 16-bits of information between a user's device and PDP-11 UNIBUS. The three functional sections of the DR11-A are: the M786 16-bit I/O Buffer, the M7820 Bus and Interrupt Control Unit, and the M105 Address Selector Unit.

**OUTPUT:** Information from the UNIBUS is stored in a 16-bit buffer register. Once this register has been set under program control, the outputs are available to the device until the register is loaded with new data from the UNIBUS. The register can also be read onto the UNIBUS.

**INPUT:** The DR11-A also provides 16 lines of input to UNIBUS transmitters. This allows data from user devices to be read onto the UNIBUS. These signals are not held in the flip-flop register of the DR11-A.

**CONTROL:** Upon data transfer to the buffer register, a control signal, NEW DATA READY, indicates to the device that data has been loaded into the register. For input onto the UNIBUS, a control signal, DATA TRANSMITTED, indicates to the device that the input lines have been read.

Two interrupt request lines provide the ability to make vectored interrupt requests to the PDP-11 processor through two sets of unique vector addresses. Interrupt enable/disable circuits are controlled by bits 6 and 5 of the addressable DR11-A control register.

Complete information for designing with the DR11-A is supplied in the PDP-11 UNIBUS Interface Manual, available upon request.

DR11-A General Device Interface Block Diagram

| Registers                                                                                                                                |                              | REQUEST B<br>REQUEST A<br>REQUEST A<br>INT END A                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control                                                                                                                                  |                              |                                                                                                                                                                           |

| Register                                                                                                                                 |                              |                                                                                                                                                                           |

| , 2019년 1월 1997년 1월 1998년<br>1919년 - 1919년 1월 1919년                       | INT ENB A                    | Enables Interrupt requests from request line A.                                                                                                                           |

|                                                                                                                                          | INT ENB B                    | Enables Interrupt requests from request line B.<br>Both may be set or cleared from Unibus.<br>Both are cleared by START or RESET.                                         |

| 에는 사람이 있는 것은 것이 있었다.<br>같은 것이 같은 것은 것이 같은 것이 같이 있는 것이 같이 있는 것이 같이 있다.                                                                    | REQUEST A                    | Indicates status of REQUEST A line; $+3V = 1, 0V = 0.$                                                                                                                    |

| 가려가 가려고 있는 것을 가지 않는다.<br>같은 것이 같은 것이 같이 같은 것이 없다. 것이 | REQUEST B                    | Indicates status of REQUEST B line; $+3V = 1, 0V = 0.$                                                                                                                    |

| Buffer                                                                                                                                   |                              |                                                                                                                                                                           |

| Register                                                                                                                                 |                              |                                                                                                                                                                           |

|                                                                                                                                          |                              | All bits may be cleared or set from Unibus. Register cleared by START or RESET. Outputs available to user.                                                                |

| Input<br>Register                                                                                                                        |                              |                                                                                                                                                                           |

| Register                                                                                                                                 |                              | All bits may be read from UNIBUS. Bit status de-<br>termined by user input lines.                                                                                         |

| Register Addresses                                                                                                                       |                              |                                                                                                                                                                           |

| Control<br>Buffer<br>Input                                                                                                               | 177520<br>177522<br>177524   | Standard factory setting.<br>May be changed by jumpers on M105.                                                                                                           |

| Vector Address A<br>Vector Address B                                                                                                     | 110<br>114                   | Standard factory setting.<br>May be changed by jumpers on M7820.                                                                                                          |

| Priority Level<br>5 normal                                                                                                               |                              | May be changed by priority jumper plug on M786.                                                                                                                           |

| Input Levels<br>+3V = 1, 0V = 0<br>1 TTL unit load                                                                                       |                              |                                                                                                                                                                           |

| Output Levels<br>+3V = 1, 0V = 0<br>capable of driving 8 TTJ                                                                             | , loads                      |                                                                                                                                                                           |

| tions are normally made                                                                                                                  | to the H807's via M92        | vailable on two H807 connectors mounted on the M786. Connec-<br>5 (flexprint connector card) or M927 (cable connector cards with<br>wo M927 Connector Cards are supplied. |

| Euvironmental<br>Temperature<br>Humidity                                                                                                 | 10° - 50°C<br>20% - 90% nonc | ondensating                                                                                                                                                               |

| Physical<br>Mounts in one small per<br>Power derived from H-7                                                                            |                              | DD11-A.                                                                                                                                                                   |

| Features:<br>Low-cost<br>Completely self-containe<br>16-bits input and output<br>Supplies all needed cont                                | ed interface                 |                                                                                                                                                                           |

|                                                                                                                                          | rrupt environment            |                                                                                                                                                                           |

### DR11-A General Device Interface

The DR11-A General Device Interface is a 3-module set that plugs into either a small peripheral slot in the processor or into one of four slots in a DD11 Small Peripheral Mounting Panel. The DR11-A provides the logic and buffer register necessary for transfers of 16-bit input and output data between the PDP-11 System and an external device.

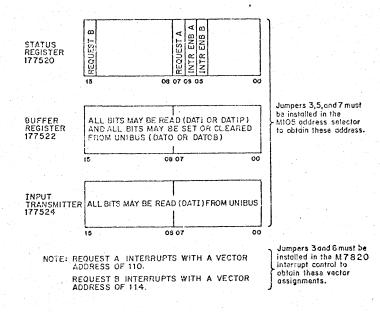

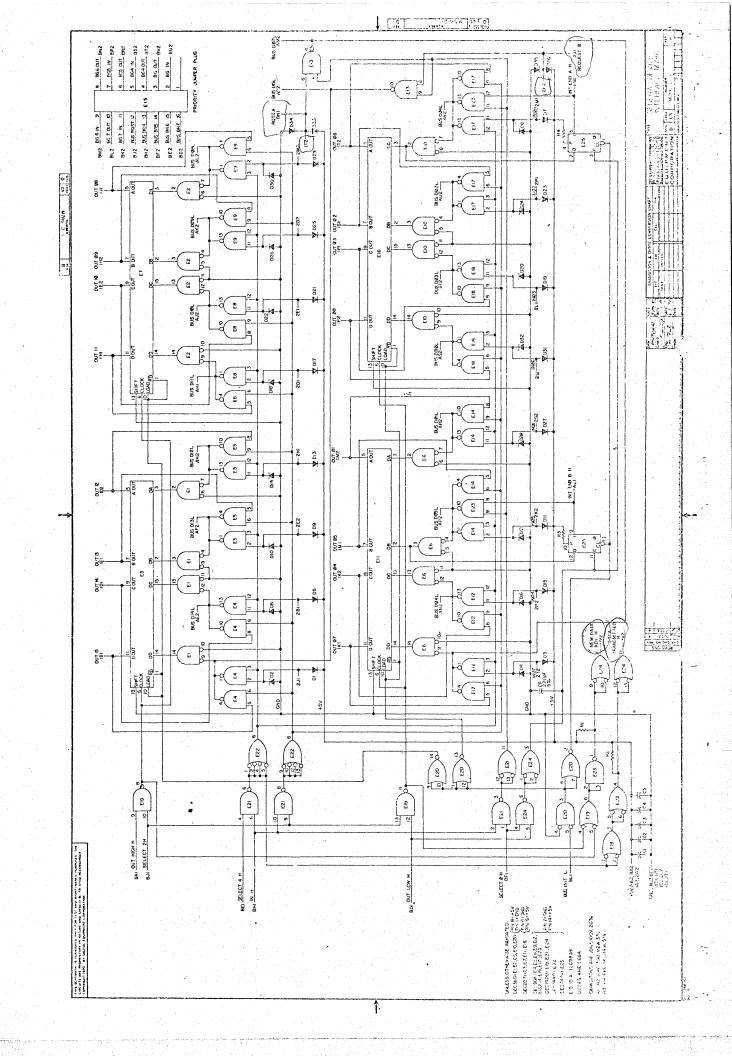

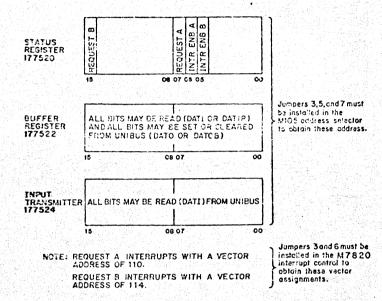

The DR11-A contains three functional sections: a 16-bit buffer register, a 16-bit data input circuit, and a 2-channel flag and interrupt control. Address and bit assignments are shown in Figure 1. The DR11-A contains three physical modules: an M105 Address Selector, an M7820 Interrupt Control and an M786 General Device Interface with two M927 cable connectors.

The 16-bit buffer register is an addressable register that may be read or loaded by instructions transmitted through the Unibus (see Figure 1). The register outputs, together with a control signal pulse (NEW DATA RÉADY) used to indicate that the register has been loaded from the Unibus, are available on a printed circuit edge connector #1 which is mounted on the M786 Module. All bits in the buffer register are cleared to 0s by the occurrence of an INIT signal on the Unibus. These signals are logic levels of either +3V (true) or 0V (false). The NEW DATA READY signal is a pulse which has a leading edge coincident with the loading of the buffer flip-flops. The connector accepts an M927 Cable Connector, which contains solder lugs and can be used with ribbon cable, twisted pair cable, or open wire. The M927 is electrically identical to the M904 Module described in the Logic Handbook.

The interface input circuits consist of 16 bus drivers gated to the bus when the input register is read by a DATI bus sequence (see Figure 1). The 16 input lines are +3V if true or 0V if false. These signals are also applied to the M786 Module through an M927 Cable Connector and a second printed circuit connector #2. When a DATI sequence occurs, a pulse signal (DATA TRANSMITTED) is applied to the external device.

Two additional request lines are furnished and may be asserted (+3V) by the external device to initiate an interrupt or to generate a flag that may be tested by the program. Whether these two request lines cause an interrupt is determined by two interrupt enable flip-flops which form part of the control and status register in the option (see Figure 1). The request lines form two more bits of the status register, independent of the status of the enable flipflops; thus, they may be tested by the program.

The priority level of both interrupts must be the same, with interrupt A on a higher sublevel than interrupt B. The M786 contains a priority jumper plug which is normally set at BR5. The interrupt enable flip-flops are cleared to 0 (inhibit interrupt) by the occurrence of an INIT signal on the Unibus, or may be set or cleared by the program. Priority may be changed by the jumper plug.

The DR11-A pin assignments are listed in Table 1. All inputs are one standard TTL unit load. Inputs have diode protection clamps to ground and +5V. All signals are +3V if true. All outputs are TTL levels capable of eight unit loads. The new data ready and data transmitted signals are positive pulses, approximately 2  $\mu$ s in duration

| 1      | Inputs    |     | Outputs |           |     |

|--------|-----------|-----|---------|-----------|-----|

| Signal | Connector | Pin | Signal  | Connector | Pin |

| IN00   | 2         | S1  | OUT00   | 1         | P2  |

| IN01   | 2         | \$2 | OUT01   | 1         | M2  |

| IN02   | 2         | P1  | OUT02   | 1         | S1  |

| IN03   | 2         | L1  | OUT03   | 1         | P1  |

| IN04   | 2         | P2  | OUT04   | 1         | K2  |

| IN05   | 2         | K2  | OUT05   | 1         | M1  |

| IN06   | 2         | M1  | OUT06   | 1         | S2  |

| IN07   | 2         | T2  | OUT07   | . 1       | L1  |

| IN08   | 2         | M2  | OUT08   | 1         | J1  |

| 11109  | 2         | D2  | OUT09   | 1         | H2  |

| IN10   | 2         | El  | OUT10   | 1         | E2  |

|        | Tab | le 1    |       |

|--------|-----|---------|-------|

| DR11-A | Pin | Assigni | nents |

(continued on next page)

### Table 1 (Cont) DR11-A Pin Assignments

|           | Inputs    | an the second | Out              | puts      |     |

|-----------|-----------|-----------------------------------------------------------------------------------------------------------------|------------------|-----------|-----|

| Signal    | Connector | Pin                                                                                                             | Signal           | Connector | Pin |

| IN11      | 2         | • D1                                                                                                            | OUT11            | 1         | H1  |

| IN12      | 2         | • • • H1 •                                                                                                      | OUT12            | 1         | D2  |

| . IN13    | 2         | E2                                                                                                              | OUT13            | 1         | E1  |

| IN14      | 2         | · B1                                                                                                            | OUT14            | 1         | D1  |

| IN15      | 2         | J1                                                                                                              | OUT15            | 1         | B1  |

| REQUEST A | 1 + 1     | T2                                                                                                              | NEW DATA RDY     | 1         | V2* |

| REQUEST B | 2         | H2                                                                                                              | DATA TRANSMITTED | 2         | V2* |

\*Pulse signals, approximately  $2 \mu s$  wide.

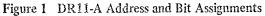

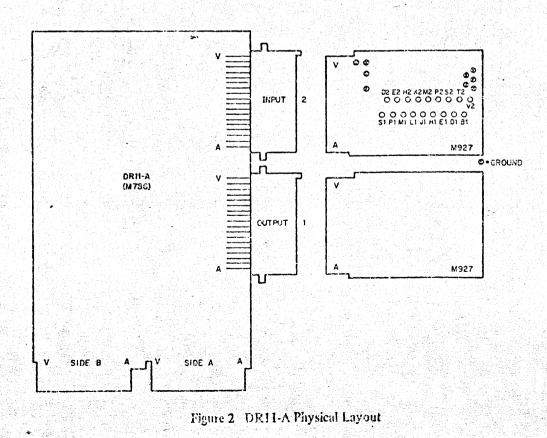

Figure 2 shows the physical layout of the M786 and M927 modules.

Figure 2 DR11-A Physical Layout

al and a second

#### 3.3.4 M105 Address Selector Module

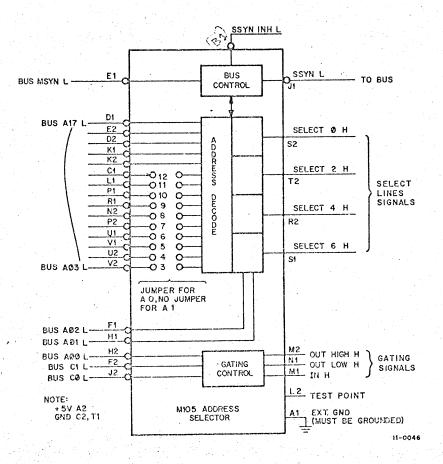

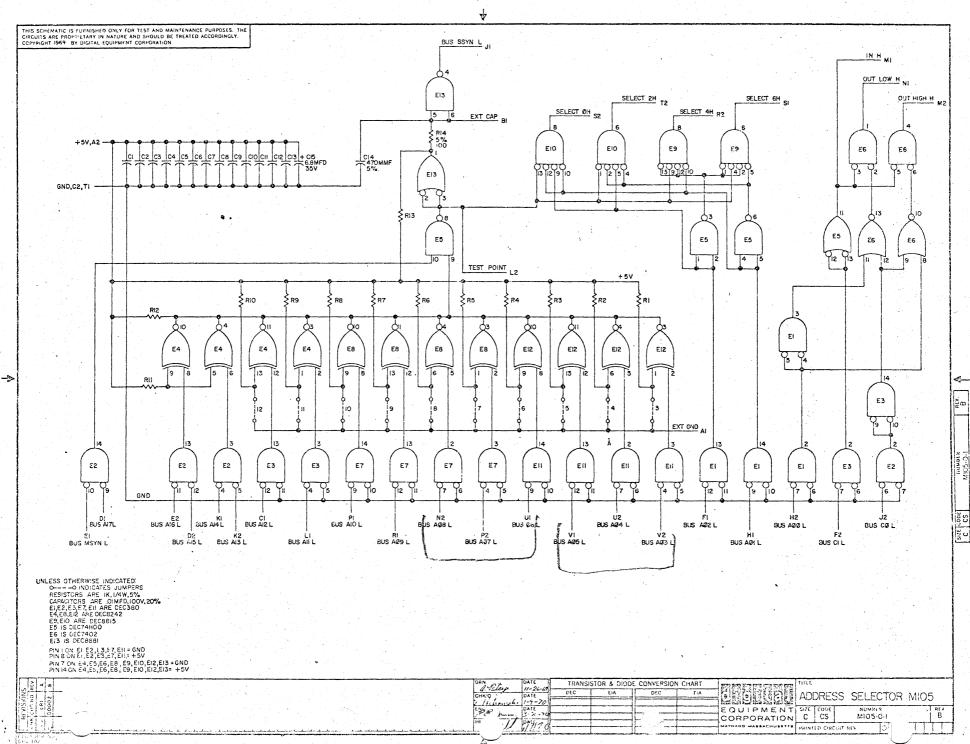

The M105 Address Selector Module provides gating signals for up to 4 full 16-bit device registers. A block diagram of this module is shown in Figure 3-11. Note that IN and OUT are always used with respect to the master (controlling) device. Thus, when the M105 is used in a peripheral device, an OUT transfer is a transfer of data out of the master (such as the processor) and into the device. Likewise, an IN transfer is the operation of the peripheral furnishing data to the processor. The M105 Module is described more fully in following paragraphs.

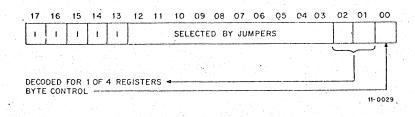

3.3.4.1 Inputs – The M105 Module input signals consist of 18 address lines, A(17:00); 2 bus control lines, (1:0); and a master synchronization (MSYN) line. The address selector decodes the 18-bit address on lines A(17:00) as described below. This address format, used for selecting a device register, is shown in Figure 3-12. Note that all inputs are standard bus receivers.

- a. Line A00 is used for byte control.

- b. Lines A01 and A02 are decoded to select one of the four addressable device registers.

- c. Decoding of lines A(12:03) is determined by jumpers on the module. When a given line contains a jumper, the address selector searches for a zero on that line. If there is no jumper, the address selector searches for a one.

- d. Address lines A(17:13) must be all ones. This specifies an address within the top 8K byte address bounds for device registers.

Figure 3-11 M105 Address Selector

Figure 3-12 Device Register Select Address Format

3.3.4.2 Slave Sync (SSYN) – When SSYN INH is grounded, it inhibits the acknowledgment signa! (SSYN) normally generated by the M105. In this case, the SSYN must be generated by another source. When SSYN INH is not grounded, SSYN is returned to the master 100 ns after register select becomes true. This time may be extended to a maximum of 400 ns by adding an external capacitor between SSYN INH and ground.

**3.3.4.3** Outputs – The M105 Output Signals permit selection of four 16-bit registers and provide three signals used for gating information to and out of the master device. The M105 may be used instead to select up to eight 8-bit registers, or any appropriate combination of byte and word registers:

The input signals select the M105 control output line states as shown in Tables 3-2 and 3-3.

| Input Lines A(02:01)  | Select Lines True (+3V)       |

|-----------------------|-------------------------------|

| 00<br>01              | 0                             |

| 10                    | 2<br>4                        |

| 11                    | 6                             |

|                       |                               |

|                       | NOTE                          |

| 1. Lines A(17:13) m   | ist be all 1s (OV on Unibus). |

| 2. Lines A(12:03) are |                               |

Table 3-2 M105 Select Lines

| T | `ab | le | 3 | -3 |  |

|---|-----|----|---|----|--|

|   |     |    |   |    |  |

| Gating  | Contro | I Signals   |

|---------|--------|-------------|

| Gatting | Conno  | n orginalis |

| Mode<br>Control<br>C(1:0)  | Byte<br>Control<br>A00 | Gating Control<br>Signals True (+3V)        | Bus Sequence                           |

|----------------------------|------------------------|---------------------------------------------|----------------------------------------|

| 00<br>00<br>01<br>01<br>10 | 0<br>1<br>0<br>1<br>0  | IN<br>IN<br>IN<br>IN<br>OUT LOW<br>OUT HIGH | DATI<br>DATI<br>DATIP<br>DATIP<br>DATO |

RUMBER

SIZE CODE

| Mode<br>Control<br>C(1:0) | Byte<br>Control<br>A00              | Gating Control<br>Signals True (+3V)       | Bus Sequence           |

|---------------------------|-------------------------------------|--------------------------------------------|------------------------|

| 10<br>11<br>11            | 1<br>0<br>1                         | OUT LOW<br>OUT HIGH<br>OUT LOW<br>OUT HIGH | DATO<br>DATOB<br>DATOB |

|                           | Gating control si<br>lines are not, | NOTE<br>gnals may become true although     | ı select               |

### Table 3-3 (Cont)Gating Control Signals

3.3.4.4 Specifications - The M105 output fanout is ten standard TTL loads for register select lines and eight

standard TTL loads for gating control lines. The module is a single-height, 8.5-inch-long Flip-Chip. A circuit schematic for this module is shown in Figure 3-13. Note that pin A1 (EXT GND) must be grounded by the user.

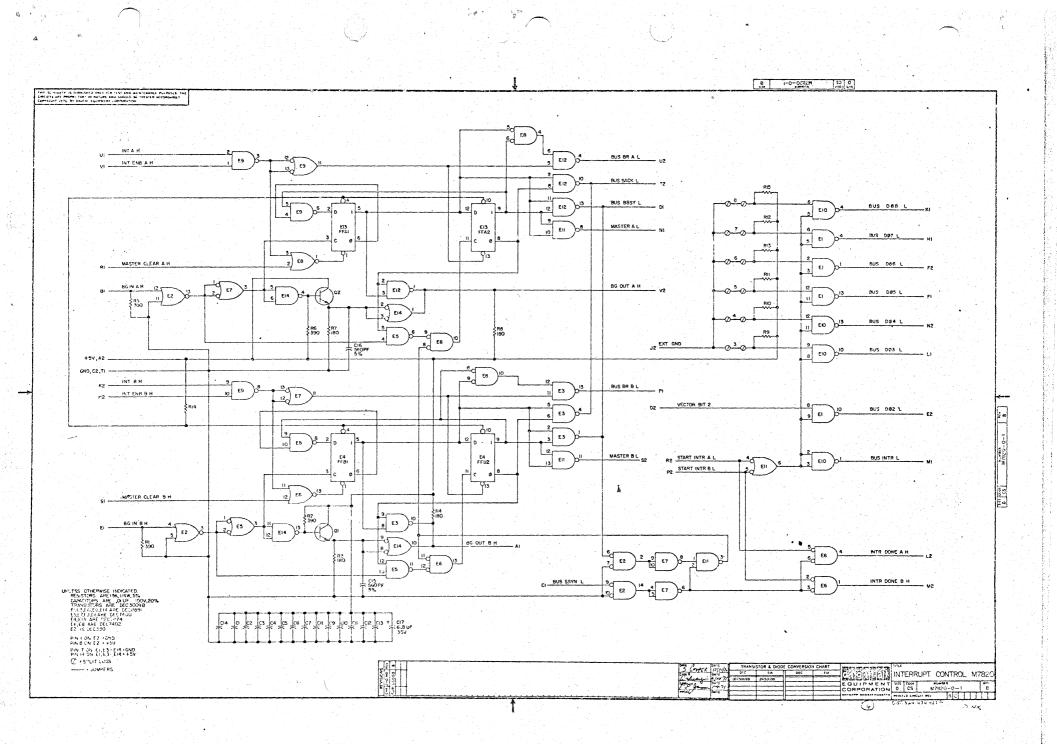

#### 3.3.5 M782 Interrupt Control Module

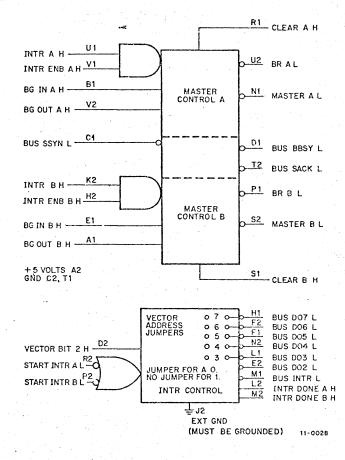

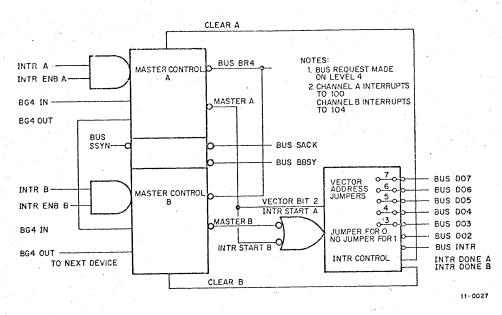

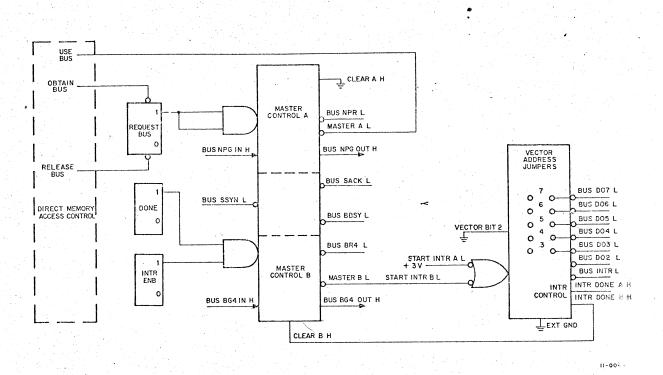

The M782 Interrupt Control Module provides the circuits and logic required to make bus requests and to gain control of the bus (become bus master). The module also includes circuits needed to generate an interrupt, if desired. The module contains two completely independent request and grant acknowledge circuits (channels A and B) for establishing bus control. The interrupt control circuit can be used with either, or both, of the request channels and provides a unique vector address for each channel. Figure 3-14 is a block diagram of the M782 Module, which is a single-height, 8.5-inch-wide Flip-Chip.

Figure 3-14 M782 Interrupt Control (block diagram)

The master control section (either channel A or B) is used to gain control of the bus. When the INTR and INTR ENB requesting inputs are asserted, a bus request is made on the BR level corresponding to the level of the BR line wired to the BR pin of the module. When the priority arbitration logic in the system recognizes the request and issues a bus grant signal, the master control circuit acknowledges with a SACK signal. When the device has fulfilled all requirements to become bus master, the master control circuit asserts BBSY and then asserts a MASTER signal. (Refer to Section 2.4.1.)

Once the device has gained bus control by means of a BR request, an interrupt can be generated. If an interrupt is desired, the module is interconnected as shown in Figure 3-15. This figure illustrates the use of the two channels to first generate requests for bus control and then initiate interrupts. The request from channel A is a slightly higher priority than the channel B request because the bus grant signal first enters A, then enters B.

Figure 3-15 M782 Interconnection for 2-Channel Interrupt

The vector address is selected by jumpers on the M782 Module. Since the vector is a two-word (four-byte) block, it is not necessary to determine the state of bits 0 and 1. The six selectable lines determine the vector address. The least significant line is controlled by the VECTOR BIT 2 input signal. If this input is asserted, then bus line D02 is asserted. Thus, the interrupt on channel A uses a vector at location 100 and channel B uses a vector at location 104.

Figure 3-16 Illustrates an M782 Module used for bus control in a device that directly transfers data to memory and then causes an interrupt when the transfer is completed. Channel A is connected to the NPR and NPG lines and is used to gain bus control for direct to memory, or device-to-device, transfers. Channel B is used to gain bus control for an interrupt.

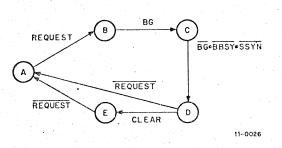

Each M782 Module master control section contains two flip-flops that sequence through four states, thereby controlling the request for bus control. Figure 3-17 is a state diagram of this sequence and Figure 3-18 shows a circuit schematic of the M782. The BG IN signal is allowed to pass through the module to BG OUT when the device is not issuing a request (state A), is master (state D), or has had the request honored (state E). To request bus use, the AND condition of INTR and INTR ENB must be satisfied. These levels must be true at least until the request is granted. Once bus control has been attained, it can be released by either asserting CLEAR or by negating either INTR or INTR ENB. The first method leaves the master control in state E, thereby inhibiting further bus requests 'even if INTR and INTR ENB remain asserted. In order to make another bus request, INTR or INTR ENB must be dropped and then reasserted to cause the module to advance from state E through state A to state B where it asserts the request line. This prevents multiple interrupts when the master control is used to generate interrupts. The second method is used to release the bus after NPR use. Note that pin J2 (EXT GND) must be grounded by the user. A summary of all M782 signals is listed in Table 3-4.

Figure 3-16 M782 Interconnection for Direct Memory Access

Figure 3-17 State Diagram of Master Control

18 M.

| Si | gnal                | Assertion<br>Level | Input Loading | Output Drive |

|----|---------------------|--------------------|---------------|--------------|

| IN | ITR A, B            | Н                  | 1 TTL (éach)  |              |

| IN | TR ENB A, B         | Η                  | 1 TTL         |              |

| CI | LEAR A, B           | Н                  | 1 TTL         |              |

| M  | ASTER A, B          | L                  |               | 10 TTL       |

| SI | TART INTR A, B      | L                  | 2 TTL         |              |

| IN | ITR DONE A, B       | Н                  |               | 10 TTL       |

| BC | G IN A, B           | Η                  | 1 R*          |              |

| BC | GOUT A, B           | Н                  |               | 2 D**        |

| BI | RA, B               | L                  |               | 1 D          |

| V  | ECTOR BIT 2         | Η                  | 1 TTL         |              |

| BU | JS SSYN             | L                  | 1 R           |              |

| BI | JS BBSY             | L                  | 1 R           | 2 D          |

| BU | JS SACK             | L                  |               | 2 D          |

| BI | US INTR             | $\mathbf{L}$       |               | 1 D          |

| BU | US D(07:02)         | L                  |               | 1 D          |

| *  | R = Standard Unibus | receiver load.     |               | 1            |

Table 3-4 Summary of M782 Signals

\*\*D = Standard Unibus transmitter (driver) output.

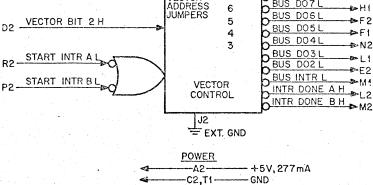

## M7820 Interrupt Control

The M7820 is used in PDP-11 device interfaces. It consists of logic circuits that can be divided into three functional sections: Master Control A, Master Control B, and INTR Control.

The Master Control circuits are used to gain control of the UNIBUS for satisfying the need to either Gain direct memory access (DMA), or to perform the 'NTR bus operation which alters program .ow.

To become master of the bus involves a question of priority. Briefly, this priority question is split into three phases: 1) bus request lines, 2) processor's pririty level, and 3) physical placement of a device on the UNIBUS.

- 1) NPR (highest)

- BR7

BR6 (except for trap instructions) BR5 BR4 (lowest)

- 2) The processor acknowledges BR's of |eve| > N:

where N is an Octal number in processor's status register. (NPR's are not affected.)

3) Highest priority goes to the device closest to the processor on the unique bus grant chain.

#### CLEAR A H R1 INT A H BR A L ►U2 INT ENB A H MASTER CONTROL IN A H Δ MASTER A BG OUT A H BUS SACK L Τ2 BUS SSYN L BUS BBSY L >D1 INT B H K2 BRBL INT ENB B H H2 MASTER BG IN B H CONTROL MASTER B L В >S2 BG OUT B H ∆1≪ CLEAR B H \$1 BUS DOB I VECTOR ADDRESS JUMPERS ⊳KI BUS DO7L 6 E>H1 BUS DOGI 5 DF2

Theory of Operation

i a device wants control of the bus, it asserts both INT A and INT ENB A. Then a request is made on a BR. This then leads to priority determination and a BG results. Now the Master Control A responds with BUS SACK. The processor sees this acknowledgement and removes BG.

E1

### Printed Ckt. Rev.: C

Ckt. Schem. Rev.: B

DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

. .

When BUS BBSY and BUS SSYN are negated, the Master Control A removes its BR and asserts BUS BBSY itself. It also asserts Master A when it is in control of the bus. Now the device can use the bus. To release control of bus, the device can assert CLEAR A or negate: INT A or INT ENB A. Master Control B is identical to A.

The INTR operation transfers a "vector address" to the processor. At this address is stored two consecutive words: 1) the starting address of the interrupt service routine, and 2) a status word. When the processor detects this, a trap sequence is initiated (current value of PC and current status of PS are stored and new ones are fetched). Now the interrupt service routine is executed.

To start the process: START INTR A or START INTR B is asserted. Then BUS INTR is asserted along with a 6-bit address. This is transferred onto the data lines: BUS D (08:02) providing a range of 000 to 774 (OCTAL) in increments of 4. D (08:03) are controlled by jumpers, which when "in", forces the bit to zero. The processor seeing BUS INTR asserts BUS SSYN. When this is detected, an INTR DONE A is asserted which negates the START INTR signal. This in turn negates BUS INTR, which negates BUS SSYN. As a result, a trap sequence is initiated. Vector bit-2 controls D02. When it is asserted D02 is asserted. It does not control any other bits.

LOGIC LEVEL 1 (high) > +3V at 40  $\mu$ A LOGIC LEVEL 0 (low) < .4V at -1.6 mA

Input Loading: One TTL load (each)

Two TTL loads (each)

One UNIBUS receiver load\* (each)

-25 mA (max.)

INT A, B INT ENB A, B MASTER CLEAR A, B VECTOR BIT 2 START INTR A, B

BG IN A,B BUS BBSY BUS SSYN

EXT. GND

\*A UNIBUS receiver load is characterized at:

< 1.4V at 25  $\mu A$  (max.) Low level > 2.5V at 160  $\mu A$  (max.) High level

Output Drive: Ten TTL loads (each)

One UNIBUS driver load\* (each)

Two UNIBUS driver loads\* (each) MASTER A, B INTR DONE A, B BR A, B BUS INTR BUS D (08:02) BUS SACK BUS BBSY BG OUT A, B G. AN

Power: +5 Volts at 277 mA (max.)

The grant chain to tie in the Master Control as follows:

BG IN has  $390\Omega$  to GND and BG has  $180\Omega$  +5 Volts

EXT GND is used for testing purposes and should be tied to ground in normal operations.

Size: Extended length, single height, single width FLIP CHIP module.

\*A UNIBUS driver load is characterized at:

< 0.8V at 50 mA (max.) 25 µA (max.) LOW LEVEL Open collector leakage

|       | Inputs    |           |        | Outputs           |           |       |

|-------|-----------|-----------|--------|-------------------|-----------|-------|

|       | Signal    | Connector | Pin    | Signal            | Connector | Pin   |

|       | IN11      | 2         | . D1   | OUT11             | 1         | Н1 🗸  |

|       | IN12      | 2         | HI     | → OUT12           | 1         | D2 /  |

|       | . IN13    | 2         | E2 —   | <b>&gt;</b> OUT13 | 1         | E1 🗸  |

|       | IN14      | 2         | · B1   | → OUT14           | 1         | D1 🗸  |

|       | IN15      | 2         | 11 & H | UT15              | 1         | B1 🤻  |

|       | REQUEST A | 1         | T2     | NEW DATA RDY      | 1         | V2* 2 |

| out / | REQUEST B | 2         | H2     | DATA TRANSMITTED  | 2         | V2*   |

\*Pulse signals, approximately 2 µs wide.

Figure 2 shows the physical layout of the M786 and M927 modules.

#### DR11-A General Device Interface

The DR11-A General Device Interface is a 3-module set that plugs into either a small peripheral slot in the processor or into one of four slots in a DD11 Small Peripheral Mounting Panel. The DR11-A provides the logic and buffer register necessary for transfers of 16-bit input and output data between the PDP-11 System and an external device.

The DR11-A contains three functional sections: a 16-bit buffer register, a 16-bit data input circuit, and a 2-channel flag and interrupt control. Address and bit assignments are shown in Figure 1. The DR11-A contains three physical modules: an M105 Address Selector, an M7820 Interrupt Control and an M786 General Device Interface with two M927 cable connectors.

The 16-bit buffer register is an addressable register that may be read or loaded by instructions transmitted through the Unibus (see Figure 1). The register outputs, together with a control signal pulse (NEW DATA READY) used to indicate that the register has been loaded from the Unibus, are available on a printed circuit edge connector #1 which is mounted on the M786 Module. All bits in the buffer register are cleared to 0s by the occurrence of an INIT signal on the Unibus. These signals are logic levels of either +3V (true) or OV (false). The NEW DATA READY signal is a pulse which has a leading edge coincident with the loading of the buffer flip-flops. The connector accepts an M927 Cable Connector, which contains solder lugs and can be used with ribbon cable, twisted pair cable, or open wire. The M927 is electrically identical to the M904 Module described in the Logic Handbook.

The interface input circuits consist of 16 bus drivers gated to the bus when the input register is read by a DATI bus sequence (see Figure 1). The 16 input lines are +3V if true or 0V if false. These signals are also applied to the M786 Module through an M927 Cable Connector and a second printed circuit connector #2. When a DATI sequence occurs, a pulse signal (DATA TRANSMITTED) is applied to the external device.

Two additional request lines are furnished and may be asserted (+3V) by the external device to initiate an interrupt or to generate a flag that may be tested by the program. Whether these two request lines cause an interrupt is determined by two interrupt enable flip-flops which form part of the control and status register in the option (see Figure 1). The request lines form two more bits of the status register, independent of the status of the enable flipflops; thus, they may be tested by the program.

The priority level of both interrupts must be the same, with interrupt A on a higher sublevel than interrupt B. The M786 contains a priority jumper plug which is normally set at BR5. The interrupt enable flip-flops are cleared to 0 (inhibit interrupt) by the occurrence of an INIT signal on the Unibus, or may be set or cleared by the program. Priority may be changed by the jumper plug.

The DR11-A pin assignments are listed in Table 1. All inputs are one standard TTL unit load. Inputs have diode protection clamps to ground and +5V. All signals are +3V if true. All outputs are TTL levels capable of eight unit loads. The new data ready and data transmitted signals are positive pulses, approximately 2  $\mu$ s in duration

|        | Inputs    | Outputs |         |              |       |  |  |

|--------|-----------|---------|---------|--------------|-------|--|--|

| Signal | Connector | Pin     | Signal  | Connector    | Pin   |  |  |

| IN00   | 2         | S1 –    | DUT00   | 1            | P2 🗸  |  |  |

| IN01   | 2         | S2 -    | DUT01   | 1            | M2 🗸  |  |  |

| IN02   | 2         | · P1    | DUT02   | 1            | SI 🗸  |  |  |

| IN03   | 2         | L1 ~    | DUT03   | 1            | P1 🗸  |  |  |

| IN04   | 2         | P2 -    | OUT04   | 1            | K2 🗸  |  |  |

| IN05   | 2         | K2      | DUT05   | 1            | MI    |  |  |

| 1N06   | 2         | M1 —    | OUTO6   | $\mathbf{I}$ | S2 🗸  |  |  |

| IN07   | 2         | T2 —    |         | . 1          | L1 +⊤ |  |  |

| IN08   | 2         | M2 -    | > OUT08 | 1            | J1 /  |  |  |

| 1N09   | 2         | D2 -    | > OUTO9 | 1            | H2 // |  |  |

| IN10   | 2         | E1 -    |         | 1 1          | E2 🗸  |  |  |

| ÷ |      | 1. Sec. 1. |       |        |      | 1.1.1 |  |

|---|------|------------|-------|--------|------|-------|--|

|   |      |            | Tabl  | e 1    |      |       |  |

|   |      |            | 1 401 |        |      |       |  |

|   |      |            |       |        |      |       |  |

| ſ | DR 1 | 1.4        | Pin   | A ccin | nine | nte   |  |

(continued on next page)