# peripherals handbook

1916

DIGITAL EQUIPMENT CORPORATION, Corporate Headquarters: Maynard, Massachusetts 01754, Telephone: (617) 897-5111 SALES AND SERVICE OFFICES

UNITED STATES-ALABAMA, Huntsville • ARIZONA, Phoenix and Tucson • CALIFORNIA, El Segundo, Los Angeles, Oakland, Ridgecrest, San Diego, San Francisco (Mountain View), Santa Ana, Santa Clara, Stanford, Sunnyvale and Woodland Hills • COLORADO, Englewood • CONNECTICUT, Fairfield and Meriden • DISTRICT OF COLUMBIA, Washington (Lanham, MD) • FLORIDA, Ft. Lauderdale and Orlando • GEORGIA, Atlanta • HAWAII, Honolulu • ILLINOIS, Chicago (Rolling Meadows) • INDIANA, Indianapolis • IOWA, Bettendorf • KENTUCKY, Louisville • LOUISIANA, New Orleans (Metairie) • MARYLAND, Odenton • MASSACHUSETTS, Marlborough, Waltham and Westfield • MICHIGAN, Detroit (Farmington Hills) • MINNESOTA, Minneapolis • MISSOURI, Kansas City (Independence) and St. Louis • NEW HAMPSHIRE, Manchester • NEW JERSEY, Cherry Hill, Fairfield, Metuchen and Princeton • NEW MEXICO, Albuquerque • NEW YORK, Albany, Buffalo (Cheektowaga), Long Island (Huntington Station), Manhattan, Rochester and Syracuse • NORTH CAROLINA, Durham/Chapel Hill • OHIO, Cleveland (Euclid), Columbus and Dayton • OKLAHOMA, Tulsa • OREGON, Eugene and Portland • PENNSYLVANIA, Allentown, Philadelphia (Bluebell) and Pittsburgh • SOUTH CAROLINA, Columbia • TENNESSEE, Knoxville and Nashville • TEXAS, Austin, Dallas and Houston • UTAH, Salt Lake City • VIRGINIA, Richmond • WASHINGTON, Bellevue • WISCONSIN, Milwaukee (Brookfield) .

INTERNATIONAL – ARGENTINA, Buenos Aires • AUSTRALIA, Adelaide, Brisbane, Canberra, Melbourne, Perth and Sydney • AUSTRIA, Vienna • BELGIUM, Brussels • BOLIVIA, La Paz • BRAZIL, Rio de Janeiro and Sao Paulo • CANADA, Calgary, Edmonton, Halifax, London, Montreal, Ottawa, Toronto, Vancouver and Winnipeg • CHILE, Santiago • DENMARK, Copenhagen • FINLAND, Helsinki • FRANCE, Grenoble and Paris • GERMAN FEDERAL REPUBLIC, Cologne, Frankfurt, Hamburg, Hannover, Munich, Stuttgart and West Berlin • HONG KONG • INDIA, Bombay • INDONESIA, Dajakarta • IRELAND, Dublin • ITALY, Milan and Turin • JAPAN, Osaka and Tokyo • MALAYSIA, Kuala Lumpur • MEXICO, Mexico City • NETHERLANDS, Utrecht • NEW ZEALAND, Auckland • NORWAY, Oslo • PUERTO RICO, Santurce • SINGAPORE • SWEDEN, Gothenburg and Stockholm • SWITZERLAND, Geneva and Zurich • UNITED KINGDOM, Birmingham, Bristol, Edinburgh, Leeds, London, Manchester and Reading • VENEZUELA, Caracas •

# digital

# peripherals handbook

digital equipment corporation

## Copyright © 1976, by Digital Equipment Corporation

٠

DEC, PDP, UNIBUS are registered trademarks of Digital Equipment Corporation.

• .

# TABLE OF CONTENTS

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                                              | R 1 INTRODUCTION<br>SCOPE AND CONTENTS<br>PERIPHERAL EQUIPMENT<br>PDP-11 EQUIPMENT PHILOSOPHY<br>CENTRAL PROCESSOR<br>UNIBUS<br>SOFTWARE<br>PDP-11 WORD                                                                                     | 1-1<br>1-1<br>1-2<br>1-2<br>1-3<br>1-5                                           |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                              | R 2 PROGRAMMING<br>GENERAL<br>ADDRESSES<br>DEVICE REGISTERS<br>PROCESSOR REGISTERS<br>2.4.1 General Registers<br>2.4.2 Processor Status Word<br>INTERRUPT STRUCTURE<br>PROGRAMMING WITH DEVICE REGISTERS<br>DEVICE PRIORITY                 | 2·1<br>2·2<br>2·3<br>2·3<br>2·4<br>2·5<br>2·5<br>2·5                             |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12 | R 3 CATEGORIES OF PERIPHERALS<br>GENERAL<br>MAIN MEMORY<br>TERMINALS<br>PAPER TAPE<br>CARDS<br>PRINTERS<br>MAGNETIC TAPE<br>DISKS<br>DISPLAYS<br>COMMUNICATIONS<br>DATA ACQUISITION<br>UNIBUS EQUIPMENT<br>MOUNTING EQUIPMENT               | 3-1<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-5<br>3-6<br>3-7<br>3-7 |

| 4.2                                                                                 | R 4 DESCRIPTIONS OF PERIPHERALS         INTRODUCTION         EXPLANATION OF TERMS & SPECIFICATIONS         4.2.1 Products         4.2.2 Registers         4.2.3 Specifications         4.2.4 Conversion Factors         LIST OF PERIPHERALS | 4-1<br>4-1<br>4-1<br>4-2<br>4-3<br>4-3                                           |

| CHAPTEI<br>5.1                                                                      | R 5 UNIBUS THEORY AND OPERATION<br>INTRODUCTION<br>5.1.1 Single Bus<br>5.1.2 UNIBUS Lines                                                                                                                                                   | 5-1<br>5-1<br>5-1                                                                |

|         | 5.1.3 Master-Slave Relation                                              | 5-1           |

|---------|--------------------------------------------------------------------------|---------------|

|         | 5.1.4 Interlocked Communication                                          | 5-2           |

| 5.2     | PERIPHERAL DEVICE ORGANIZATION AND CONTROL                               | 5-2           |

| 5.3     | TRANSFER OF BUS MASTER                                                   | 5-2           |

|         | 5.3.1 Transfer Request Handling                                          | 5-2           |

|         | 5.3.2 Priority Structure                                                 | 5-2           |

|         | 5.3.3 Data Transfer                                                      |               |

|         | 5.3.4 Interrupt Requests                                                 | 5-3           |

|         | 5.3.5 Interrupt Procedure                                                | 5.4           |

| 5.4     | UNIBUS SIGNAL LINES                                                      | 5-4           |

| 5.4     | DATA TRANSFER                                                            | 5-5           |

| 5.5     | DATA TRANSFER                                                            | 5- <b>6</b>   |

|         | 5.5.1 Signals used in Data Transfer                                      | 5-6           |

|         | 5.5.2 Conventions and Definitions                                        | 5-10          |

|         | 5.5.3 Equivalent Logic at the Slave                                      | 5-11          |

|         | 5.5.4 Data Transfer Timing                                               | 5-12          |

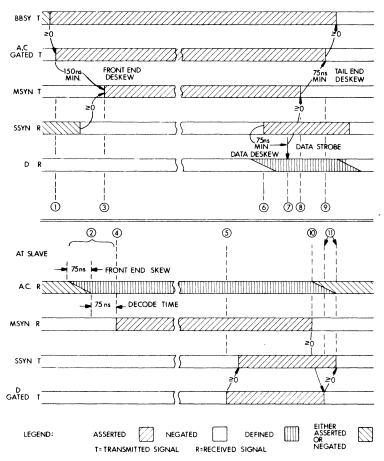

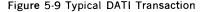

|         | 5.5.5 DATA-IN, DATI or DATIP                                             | 5-12          |

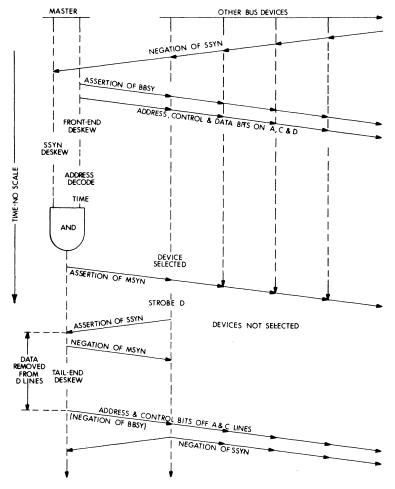

|         | 5.5.6 DATA-OUT, DATO or DATOB                                            | 5-16          |

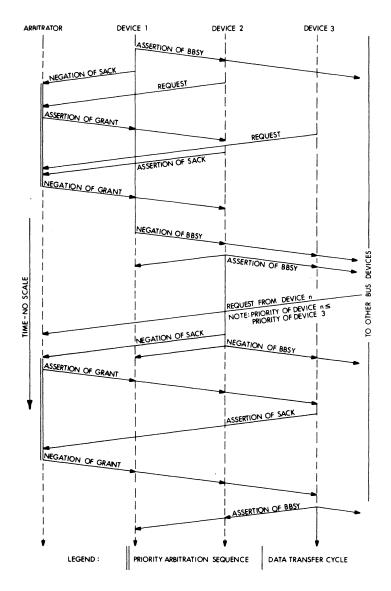

| 5.6     | PRIORITY ARBITRATION TRANSACTIONS                                        | 5-20          |

|         | 5.6.1 Introduction                                                       | 5-21          |

|         | 5.6.2 Detailed Description, Priority                                     | 521           |

|         | Arbitration Transaction                                                  | 5-22          |

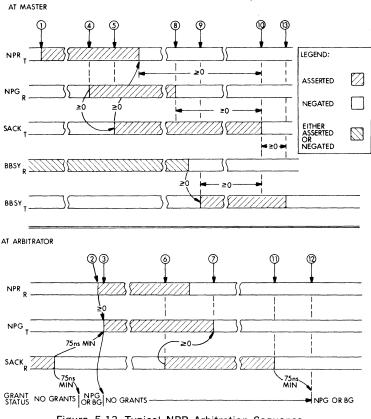

|         | 5.6.3 Detailed Description, NPR                                          | J-22          |

|         |                                                                          | E 00          |

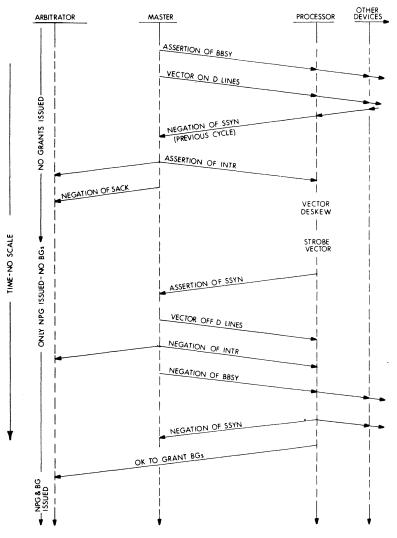

|         | Arbitration Sequence<br>5.6.4 General Description, Interrupt Transaction | 5-23          |

|         |                                                                          | 5-25          |

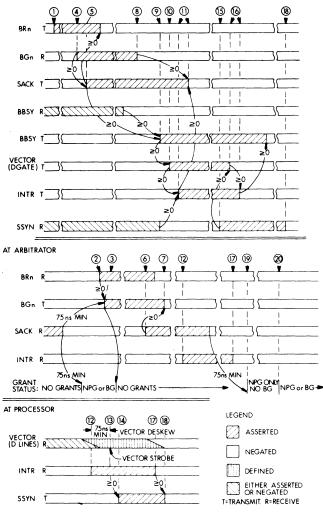

|         | 5.6.5 Detailed Description, BR Interrupt                                 |               |

|         | Arbitration Sequence                                                     | 5-25          |

|         | MISCELLANEOUS CONTROL LINES                                              | 5-30          |

| 5.8     | UNIBUS                                                                   | 5-32          |

|         | 5.8.1 Timing                                                             | 5-32          |

|         | 5.8.2 Time-Out Protection                                                | 5 <b>-3</b> 3 |

|         | 5.8.3 Priority Chaining                                                  | 5-33          |

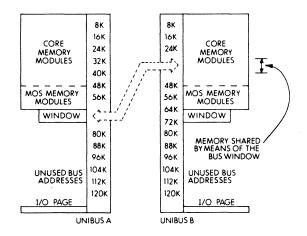

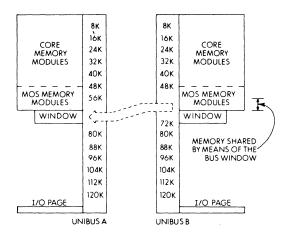

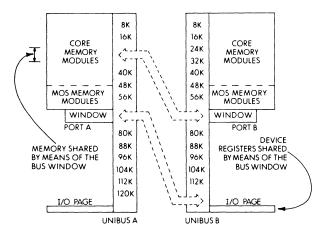

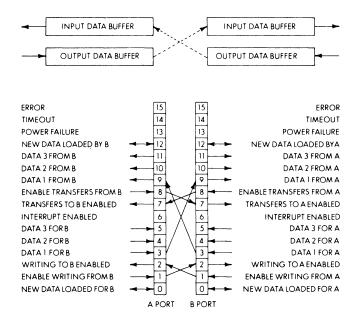

|         | 5.8.4 Address Mapping                                                    | 5-34          |

|         | 5.8.5 Device Registers                                                   | 5-35          |

| 5.9     | COMPARISON BETWEEN NPR & BR OPERATION                                    | 5-38          |

| 0.0     |                                                                          | 0.00          |

| CHAPTER | 6 UNIBUS INTERFACING                                                     |               |

|         | GENERAL                                                                  | 6-1           |

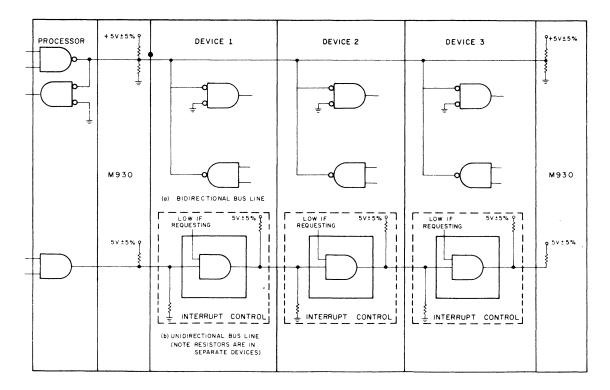

|         | 6.1.1 UNIBUS Transmission                                                | 6.1           |

|         | 6.1.0 UNIDUS Hallshillssion                                              |               |

|         | 6.1.2 UNIBUS Signal Levels                                               | 6-1           |

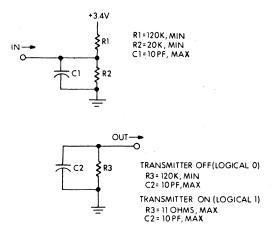

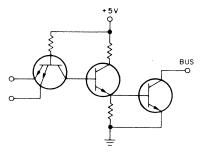

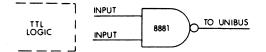

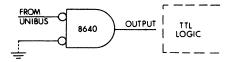

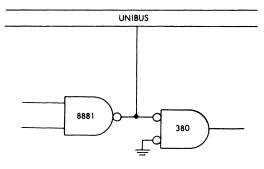

|         | 6.1.3 Bus Receiver and Transmitter Circuits                              | 6-3           |

|         | 6.1.4 UNIBUS Length and Loading                                          | 6-6           |

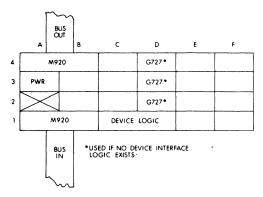

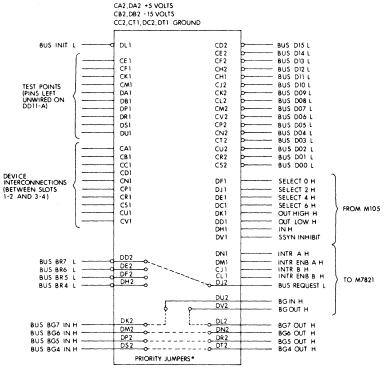

| 6.2     | UNIBUS INTERFACE MODULES                                                 | 6-7           |

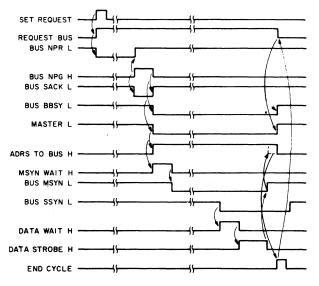

|         | 6.2.1 BC11A, UNIBUS CABLE                                                | 6-8           |

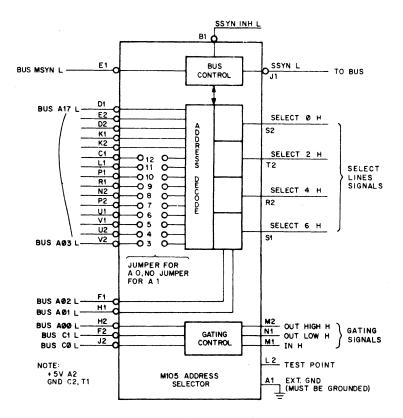

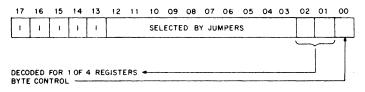

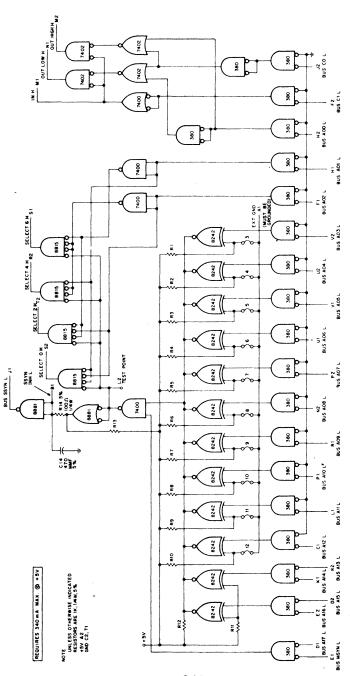

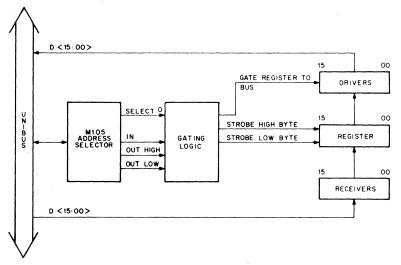

|         | 6.2.2 M105, Address Selector Module                                      | 6-9           |

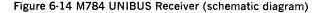

|         | 6.2.3 M783, UNIBUS Transmitter Module                                    | 6-11          |

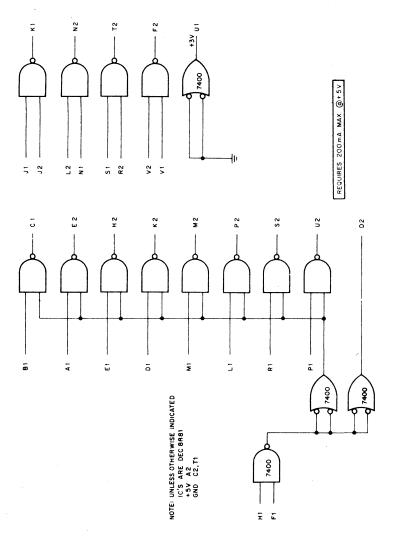

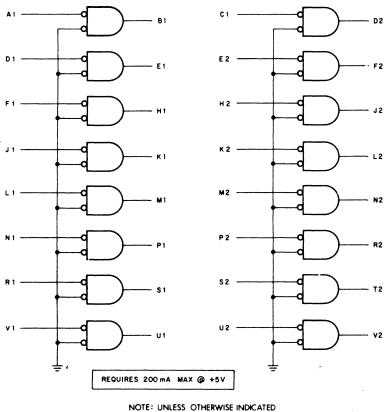

|         | 6.2.4 M784, UNIBUS Receiver Module                                       | 6.11          |

|         | 6.2.5 M785, UNIBUS Transceiver Module                                    | 6-13          |

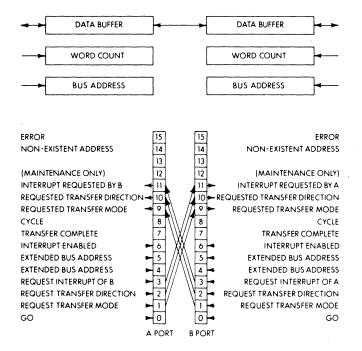

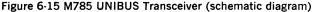

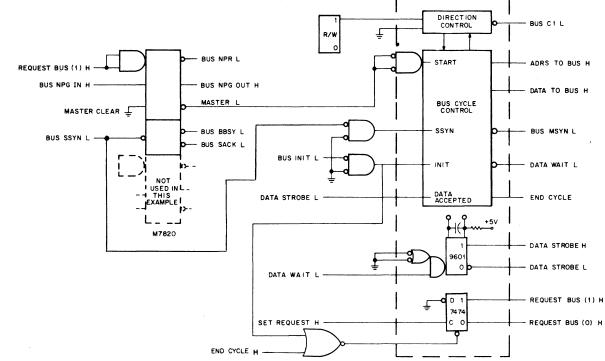

|         | 6.2.6 M795, Word Count and Bus Address Module                            | 6-14          |

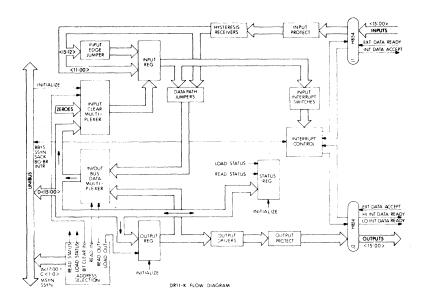

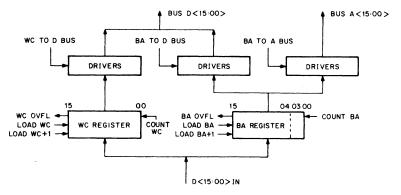

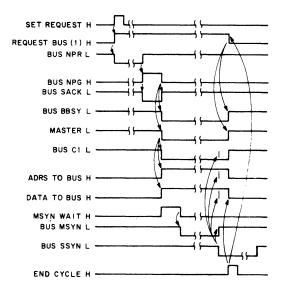

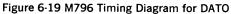

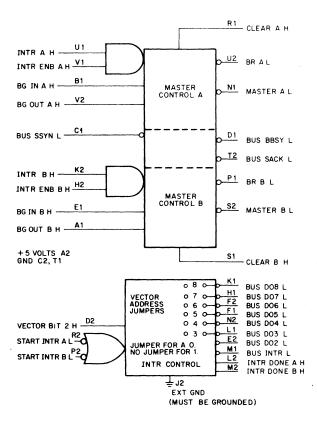

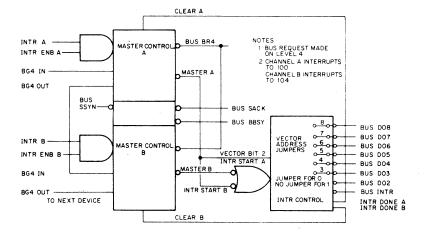

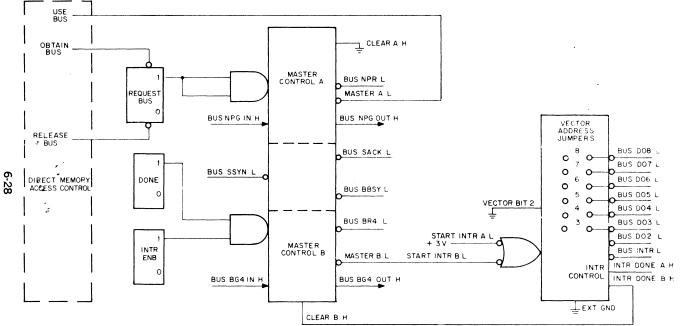

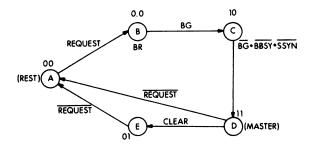

|         | 6.2.7 M796, UNIBUS Master Control Module                                 | 6-17          |

|         | 6.2.8 M920, UNIBUS Jumper Module                                         | 6-24          |

|         | 6.2.9 M930, UNIBUS Terminator Module                                     |               |

|         |                                                                          |               |

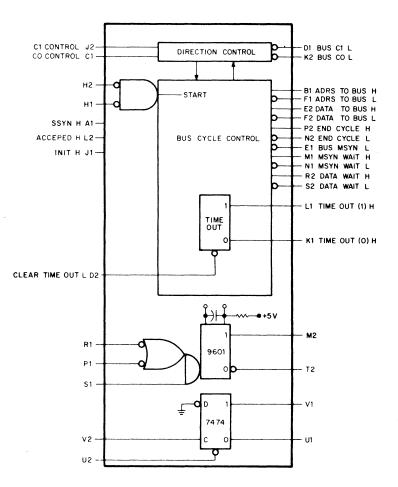

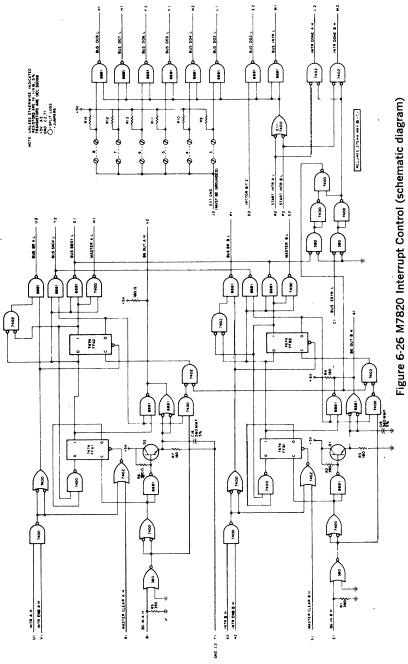

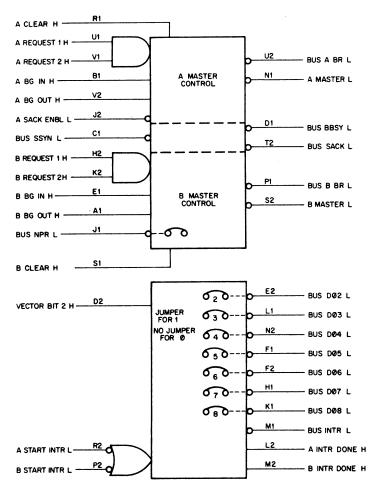

|         | 6.2.10 M7820, Interrupt Control Module                                   |               |

|         | 6.2.11 M7821, Interrupt Control Module                                   | 6-29          |

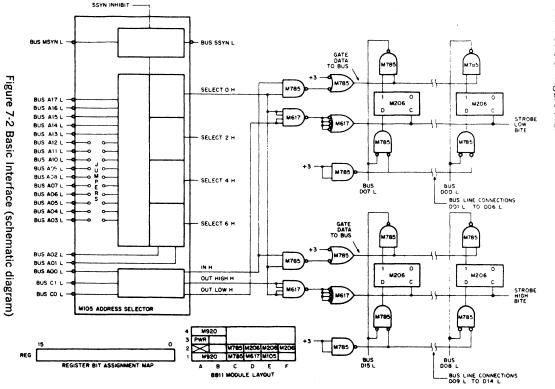

# CHAPTER 7 INTERFACE EXAMPLES

| 7.1 BASIC INTERFACE                         | 7-1         |

|---------------------------------------------|-------------|

| 7.2 PROGRAMMED DEVICE INTERFACE             | 7-4         |

| 7.3 INTERRUPT SERVICED INTERFACE            | 7-8         |

| 7.4 DIRECT MEMORY ACCESS (DMA) INTERFACE    | 7-13        |

| 7.5 OUTPUT INTERFACE WITH INTERRUPT CONTROL | 7-15        |

| 7.6 DAC-DMA INTERFACE                       | 7-19        |

| Appendix A UNIBUS Addresses                 | A-1         |

| Appendix B Miscellaneous Tables and Data    | "B-1        |

| B.1 UNIBUS Pin Assignments (by pin numbers) | B-1         |

| B.2 UNIBUS Pin Assignments (by signal name) | B-2         |

| B.3 BB11 Power Pin Assignments              | <b>B</b> -3 |

| B.4 ASCII Code                              | B-4         |

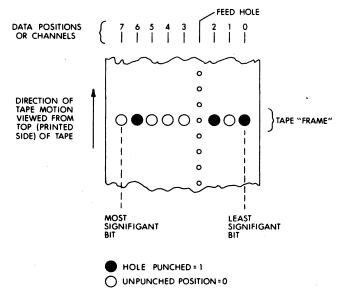

| B.5 Paper Tape Format                       | <b>B</b> -5 |

|                                             |             |

## **CHAPTER 1**

# INTRODUCTION

#### 1.1 SCOPE AND CONTENTS

This Handbook is a reference guide describing PDP-11 equipment other than central processors. It includes descriptions, specifications, programming and interfacing information on PDP-11 peripherals and options. The information in the Handbook supplements material found in the various PDP-11 Processor Handbooks. Familiarity with or access to a Processor Handbook will greatly facilitate an understanding of the material in this Handbook.

The intent of this Handbook is to provide extensive information on opertion of PDP-11 peripheral equipment. It is not intended to be the sole reference for the peripherals. More comprehensive and detailed information is available in Peripherals Manuals, Maintenance Manuals, and Programming Manuals. Improvements and modifications in equipment made after March 1976 are not reflected in this Handbook,

#### **1.2 PERIPHERAL EQUIPMENT**

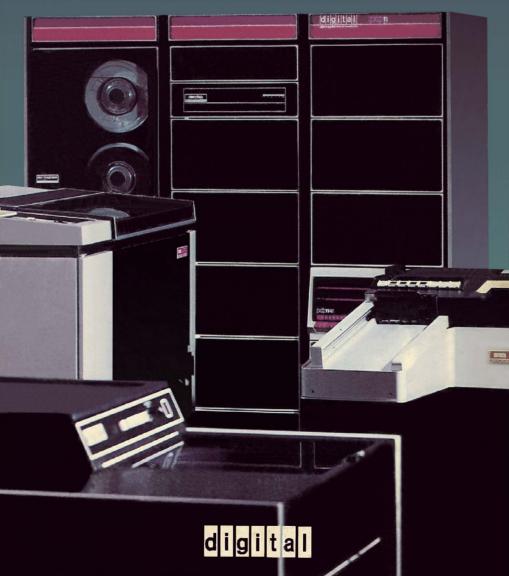

Digital Equipment Corporation designs and manufactures many of the peripheral devices described in this Handbook. The general design criteria was to provide maximum system throughput for peripherals when matched to a PDP-11 central processor—the processors and the peripherals were designed to work together. In addition to providing individual peripheral performance the overall goal is to provide a broad spectrum of compatible peripheral devices. This broad spectrum of peripherals and processors means the user can start with any system and be sure of easy compatible upgrades as needs increase. This ability when coupled with DIGITAL software and support allows going to one source for all data processing needs.

#### 1.3 PDP-11 EQUIPMENT PHILOSOPHY

The PDP-11 family is a comprehensive set of hardware/software facilities that includes various central processors, a large number of peripheral devices and options, and extensive software. Products are compatible with each other. Thus, the user can choose the system which is most suitable to present applications and be sure that as needs change or grow, equipment can easily be changed or added. Some of the characteristics of PDP-11 equipment are:

- 16-bit word (two 8-bit bytes) direct addressing of 32K 16-bit words or 64K 8-bit bytes (K = 1024)

- Word or byte processing central processors are hardwired for word or byte instructions

- Asynchronous operation systems run at their highest possible speed, replacement with faster devices means faster operation with no other hardware or software changes

1 - 1

- Modular component design extreme ease and flexibility in configuring systems

- Direct Memory Access (DMA) inherent in the architecture is direct memory access for multiple devices

- Automatic Priority Interrupt four-line, multi-level system permits grouping of interrupt lines according to response requirements

- Vectored interrupts fast interrupt response without device polling

- Power Fail & Automatic Restart hardware detection and software protection for fluctuations in the AC power

#### **1.4 CENTRAL PROCESSOR**

The central processor, connected to the UNIBUS as a subsystem, controls the time allocation of the UNIBUS for peripherals and performs arithmetic and logic operations and instruction decoding. It contains multiple high-speed general-purpose registers which can be used as accumulators, address pointers, index registers, and other specialized functions. The processor can perform data transfers directly between input/output (I/O) devices and memory without disturbing the processor registers; does both single- and double-operand addressing and handles both 16-bit word and 8-bit byte data.

#### Instruction Set

The instruction complement uses the flexibility of the general-purpose registers to provide over 400 powerful hard-wired instructions. Unlike conventional 16-bit computers, which usually have three classes of instructions (memory reference instructions, operate or control instructions and I/O instructions) all operations in the PDP-11 are accomplished with one set of instructions. Since peripheral device registers can be manipulated as flexibly as core memory by the central processor, instructions that are used to manipulate data in core memory may be used equally well for data in peripheral device registers.

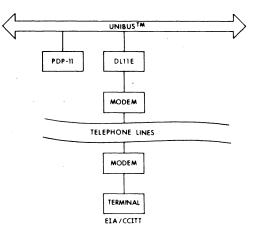

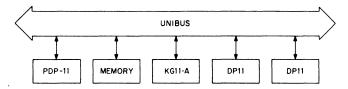

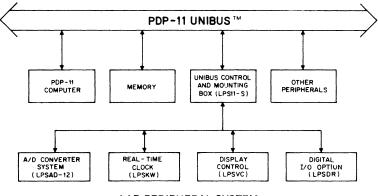

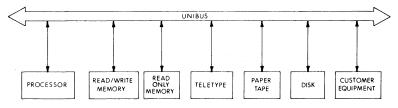

#### 1.5 UNIBUS

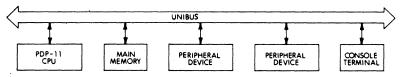

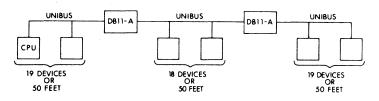

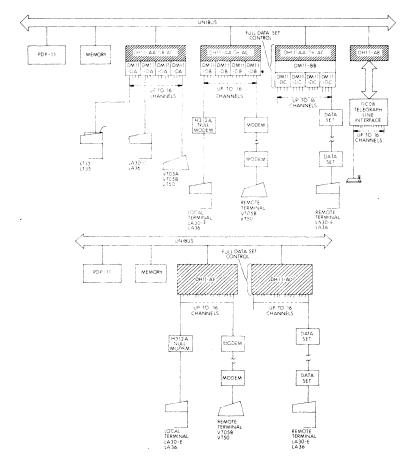

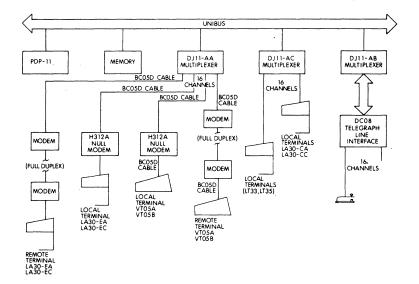

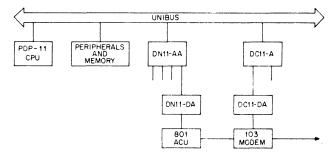

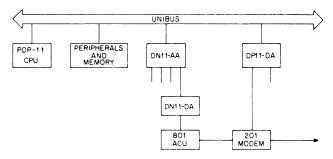

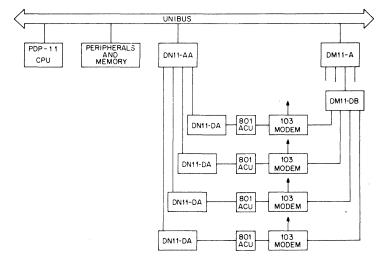

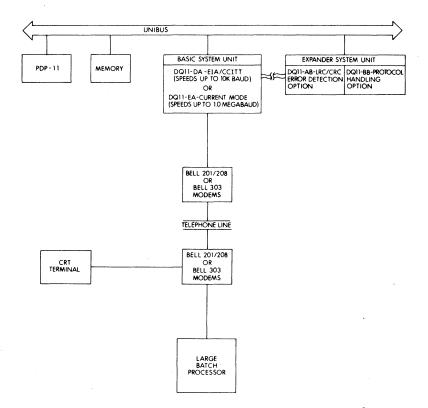

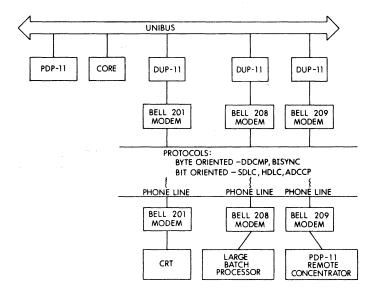

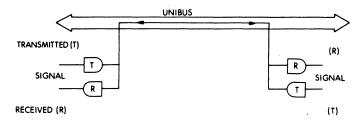

Most computer system components and peripherals connect to and communicate with each other on a high-speed bus known as the UNIBUS, see Figure 1-1.

Figure 1-1 PDP-11 System Block Diagram

The form of communication is the same for every device on the UNIBUS. The central processing unit (CPU) uses the same set of signals to communicate with main memory as with peripheral devices. Peripheral devices also use this set of signals when communicating with the processor, memory or other peripheral devices. Each device, including memory locations, processor registers, and peripheral device registers, is assigned an address on the UNIBUS.

With bidirectional and asynchronous communications on the UNIBUS, devices can send, receive, and exchange data with minimum processor intervention. Because it is asynchronous, the UNIBUS is compatible with devices operating over a wide range of speeds. Interfaces to the UNIBUS are not time dependent; there are no pulse-width or rise-time restrictions.

Full 16-bit words or 8-bit bytes of information can be transferred on the bus. The information can be instructions, addresses, or data. Direct data transfers can occur between a peripheral device control and memory.

Refer to Chapter 5 for more detailed information about the UNIBUS and data transfers.

#### 1.6 SOFTWARE

The PDP-11 family of central processors and peripherals is supported by a comprehensive family of licensed software products. This software family includes support for small stand-alone configurations, disk based real-time and program development systems, large multi-programming and time sharing systems, and many diverse dedicated applications. Some examples of general purpose operating systems and standard high level language processors are:

- PAPER TAPE SYSTEM (PTS-11)—A core only high-speed paper tape system with program development in assembly language. Editor, debugger, and linker are supplied along with a relocating assembler.

- CASSETTE PROGRAMMING SYSTEM (CAPS-11)—A small program development system with a core based monitor, utilizing dual magnetic tape cassettes as file structured media. Complete program development utilities such as a relocating assembler, linker, editor, debugger, and file interchange program are included.

- SINGLE USER ON-LINE PROGRAM DEVELOPMENT SYSTEM (RT-11)— A small, powerful, easy-to-use disk (or DECtape) based system for program development or fast on-line (real-time) applications. A Foreground/Background version can accommodate simultaneous program development in the background with on-line applications in the foreground. A MACRO assembler, linker, editor, debugger, and file utility programs are included.

- REAL-TIME MEMORY-BASED SYSTEM (RXS-11S)—A small, real-time operating system that provides a run-time environment for execution of tasks developed on an RSX-11M host system. RSX-11S is program compatible with both the RSX-11M and RSX-11D systems; any task that executes under RSX-11S will execute under the other two, more

powerful systems. RSX-11S is suitable for dedicated application environments.

- MULTI-TASKING PROCESS CONTROL SYSTEM (RSX-11M)—An efficient multi-tasking system suitable for controlling many processes simultaneously, in a protected environment with concurrent development of new programs. Utilities include a MACRO assembler, task builder (linker), editor, debugger, and file utility programs.

- COMPREHENSIVE MULTI-PROGRAMMING SYSTEM (RSX-11D)—The total job operating system. As a compatible extension of RSX-11M, the system allows concurrent fully hardware protected execution of multiple on-line jobs, with BATCH program development. Complete utilities include a MACRO assembler, task builder (linker), editor, debugger, and file utility programs.

- EXTENDED RESOURCE TIME SHARING SYSTEM (RSTS/E)—A diskbased time sharing system implementing BASIC-PLUS, an enriched version of the popular BASIC language. Up to 32 simultaneous users share system resource via interactive terminals. Additional features such as output spooling, and comprehensive file protection are included.

- INTERACTIVE APPLICATION SYSTEM (IAS)—A multi-function, multilanguage operating system capable of supporting timesharing, realtime, and batch programming concurrently. It supports up to 16 interactive terminals and versions of BASIC, FORTRAN, COBOL, and MACRO assembler.

- BASIC-11—An extended version of Dartmouth Standard BASIC is available for PTS-11, CAPS-11 and RT-11. Many applications, such as signal processing and graphics are accessed by the user through extensions to this simple, yet powerful, language. A multiuser version is available under PTS-11 and RT-11.

- PDP-11 FORTRAN IV—An extended version of ANSI standard FOR-TRAN is supplied with RSX-11M and RSX-11D, and available under RT-11. As an optimizing compiler, FORTRAN IV is designed for fast compilation, yet requires very little main memory, and generates highly efficient code without sacrificing execution speed. Under RT-11, FORTRAN IV features the same signal-processing and graphics extensions as BASIC-11.

- FORTRAN-IV PLUS—A compatible extension to PDP-11 FORTRAN IV, this system uses sophisticated optimizations to achieve the fastest possible execution speed of the generated code. FORTRAN IV-PLUS requires a PDP-11/45 and Floating Point Processor hardware, in addition to the RSX-11D operating system.

- PDP-11 COBOL—To supplement the business data processing needs often associated with large scale PDP-11 system applications, an ANSI-74 COBOL language is available under RSX-11D. Running as a BATCH job, COBOL enhances the RSX-11D total job computing system, where some business data processing is required.

In addition to the above mentioned general purpose licensed software products, DIGITAL offers a great number of addition optional and ap-

plications oriented products. A wide range of educational, consulting, and maintenance services are also offered, to ensure full utility of any PDP-11 system. For a complete and detailed listing of DIGITAL software products and services, consult the latest CATALOG OF SOFTWARE PRODUCTS and SERVICES.

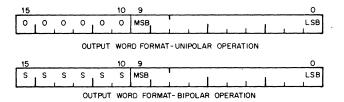

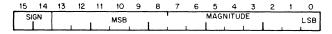

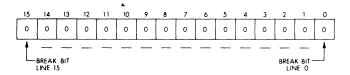

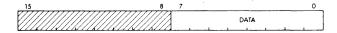

#### 1.7 PDP-11 WORD

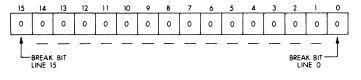

The 16-bit PDP-11 word can be represented conveniently as a 6-digit octal word. Bit 15, the Most Significant Bit (MSB), is used directly as the Most Significant Digit of the octal word. The other 5 octal digits are formed from the corresponding groups of 3 bits in the binary word. See Figure 1-2.

#### **Octal Representation**

Figure 1-2

When an extended address of 18 bits is used (shown later in the Handbook), the Most Significant Digit of the octal word is formed from bits 17, 16, and 15. For unsigned numbers, the correspondence between decimal and octal is:

| Decimal                  | Octal   |                |

|--------------------------|---------|----------------|

| 0                        | 000 000 |                |

| $(2^{16}-1) = 65,535$    | 177 777 | (16-bit limit) |

| $(2^{18} - 1) = 262,143$ | 777 777 | (18-bit limit) |

1.6

## CHAPTER 2

# PROGRAMMING

#### 2.1 GENERAL

Programming of peripherals is extremely simple in the PDP-11; a special class of instruction to deal with input/output operations is unnecessary. The UNIBUS permits a unified addressing structure in which control, status, and data registers for peripheral devices are directly addressed as memory locations. Therefore all operations on these registers, such as transferring information into or out of them or manipulating data within them, are performed by normal memory reference instructions.

The use of all memory reference instructions on peripheral device registers greatly increases the flexibility of input/output programming. For example, information in a device register can be compared directly with a value and a branch made on the result.

All peripheral device registers can be treated as accumulators. There is no need to funnel all data transfers, arithmetic operations, and comparisons through a single or small number of accumulator registers.

#### 2.2 ADDRESSES

#### Words and Bytes

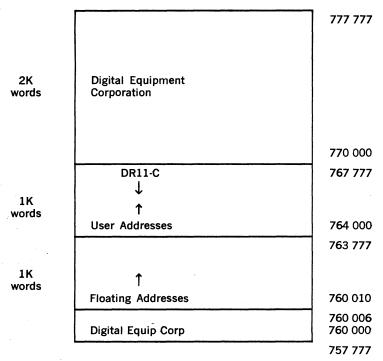

Since the PDP-11 can operate on individual 8-bit bytes, a 16-bit word allows addressing 65,536 bytes ( $2^{16} = 65,536$ ). It is common to refer to this as 64K, where K is equal to 1,024. Thus 64K bytes, or 32K 16-bit words are directly addressable. Actually in the PDP-11, the top 4K addresses are reserved for internal CPU registers and external input/ output (I/O) registers. If all of the memory space were used, there could be 28K words of physical memory plus 4K locations for the CPU and I/O registers.

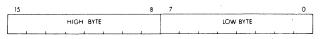

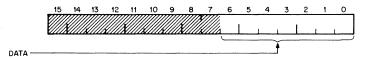

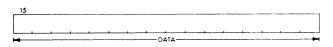

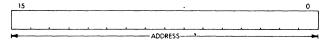

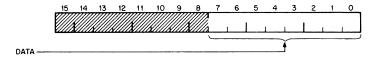

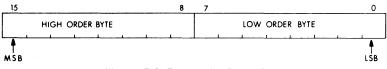

A PDP-11 word is divided into a high byte and a low byte as shown in Figure 2-1.

Figure 2-1 PDP-11 Word

Low bytes are stored at even numbered memory locations and high bytes are stored at odd numbered locations. Words always start at even numbered locations.

#### Expanded Addressing

With the large PDP-11 computers, expansion above 28K of memory can be achieved by using the Memory Management option. Memory Management provides an 18-bit effective memory address which permits addressing up to 124K words of actual memory, or with the PDP-11/70, 22 bits are used to address over 2 million words.

If Memory Management is not used, an octal address between 160 000 and 177 777 is interpreted as 760 000 to 777. That is, if bits, 15, 14, and 13 are 1's, then bits 17 and 16 (the extended address bits) are considered to be 1's, which relocate the last 4K words (8K bytes) to become the highest locations accessed by the UNIBUS.

#### **2.3 DEVICE REGISTERS**

All peripheral devices are specified by a set of registers which are addressed as main memory. There are two types of registers associated with each device:

- a) Control and status

- b) Data buffer

#### **Control and Status Registers**

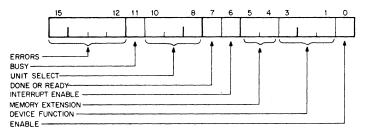

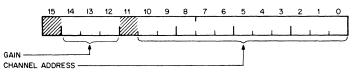

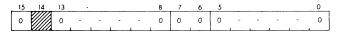

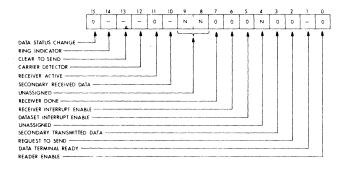

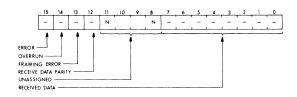

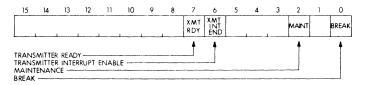

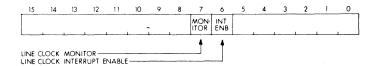

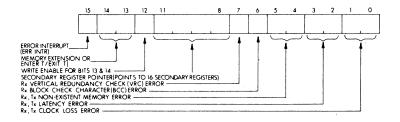

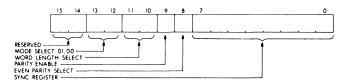

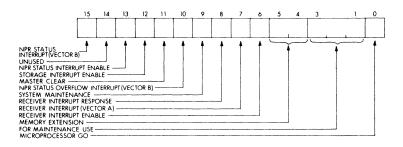

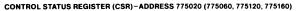

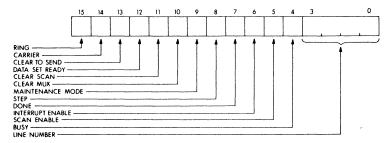

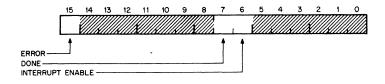

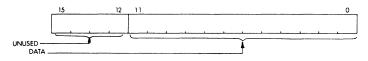

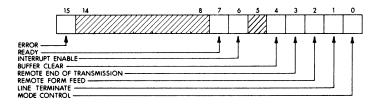

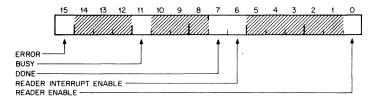

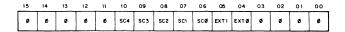

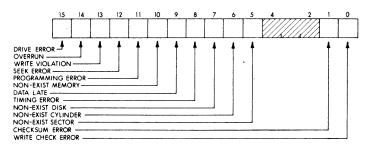

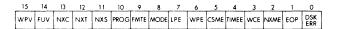

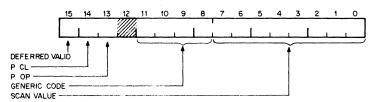

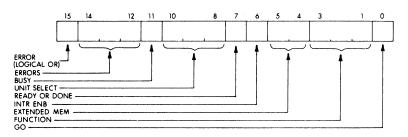

Each peripheral has one or more control and status registers that contain all the information necessary to communicate with that device. The general form, shown in Figure 2-2 does not necessarily apply to every device, but is presented as a guide.

Figure 2-2 Control & Status Register

Many devices require less than 16 status bits. Other devices will require more than 16 bits and therefore will require additional status and control registers.

The bits in the control and status registers are generally assigned as follows:

| BIT   | NAME   | FUNCTION                                                                                                                                                                                                                                                                       |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12 | Errors | Generally there is an individual bit associ-<br>ated with a specific error. When more bits<br>are required for errors, they can be ob-<br>tained by expanding the error section in<br>the word or by using another status word.<br>Generally Bit 15 is the inclusive OR of all |

other error bits (if there is more than one). Most devices will have "hard" error conditions which will cause an interrupt if bit 6 is set. Some may also have "soft" errors (warning types) which do not cause immediate interrupts. All errors are generally indicated by individual status bits.

- 11 Busy Set to indicate that a device operation is being performed.

- 10-8 Unit Select Some peripheral systems have more than one device per control. For example, a disk system can have multiple surfaces per control and an analog-to-digital converter can have multiple channels. The unit bits select the proper surface or channel.

- 7 Done or Ready The register can contain a Done bit, a Ready bit or a Done-Busy pair of bits, depending on the device. These bits are set and cleared by the peripheral device, but may be queried by the program to determine the availability of the device.

- 6 Interrupt Enable Set by the program to allow an interrupt to occur as a result of a function done or error condition.

- 5-4 Memory Extension Allows devices to use a full 18 bits to specify addresses on the bus.

- 3-1 Device Function Bits Specifies the operation that a device is to perform.

- 0 Enable Set to enable the device to perform an operation.

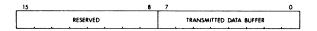

#### Data Buffer Registers

The data buffer register is used for temporarily storing data to be transferred into or out of the computer. The number and type of data registers is a function of the device.

#### 2.4 PROCESSOR REGISTERS

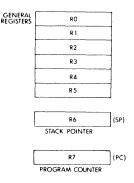

#### 2.4.1 General Registers

The central processor contains 8 general registers which can be used for a variety of purposes. The registers can be used as accumulators, index registers, auto-increment registers, auto-decrement registers, or as stack pointers for temporary storage of data. Arithmetic operations can be from one general register to another, from one memory or device register to another, or between memory or a device register and a general register. Refer to Figure 2-3.

R7 is used as the program counter (PC) and contains the address of the next instruction to be executed. It is a general register normally used only for addressing purposes and not as an accumulator for arithmetic operations.

Figure 2-3 General Registers

The R6 register is normally used as the Stack Pointer indicating the last entry in the appropriate stack (a common temporary storage area with "Last-in First-Out" characteristics).

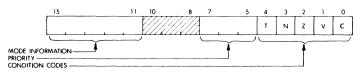

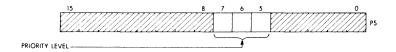

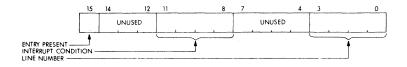

#### 2.4.2 Processor Status Word (PS) 777 776

Figure 2-4 Processor Status Word

The Processor Status word, at location 777776, contains information on the current status of the computer. This information includes the condition codes describing the results of the last instruction; and an indicator for detecting the execution of an instruction to be trapped during program debugging, see Figure 2-4.

Bits 15 to 11 are used in the larger PDP-11 computers for operational mode information, and will not be covered in this Handbook. Refer to the Processor Handbooks for further information.

#### Processor Priority

The central processor operates at any one of eight levels of priority, 0-7. When the CPU is operating at level 7 an external device cannot interrupt it with a request for service. The central processor must be operating at a lower priority than the external device's request in order for the interruption to take effect. The current priority is maintained in the Processor Status word (bits 7-5), with bit 5 being the LSB. The 8 processor levels provide an effective interrupt mask.

#### Condition Codes

The condition codes contain information on the result of the last CPU operation.

The bits are set as follows:

- Z = 1, if the result was zero

- N = 1, if the result was negative

- C = 1, if the operation resulted in a carry from the MSB

- V = 1, if the operation resulted in an arithmetic overflow

#### Trap

The trap bit (T) can be set or cleared under program control. When set, a processor trap will occur through location 14 on completion of instruction execution and a new Processor Status word will be loaded. This bit is especially useful for debugging programs as it provides an efficient method of installing breakpoints.

#### 2.5 INTERRUPT STRUCTURE

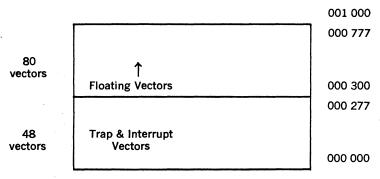

If the appropriate Interrupt Enable bit is set in the control and status register of a device, transition from 0 to 1 of the Ready or Error bit causes an interrupt request to be issued to the processor. Also if Ready or Error is a 1 when the Interrupt Enable is turned on, an interrupt request is made. If the device makes the request at a priority greater than that at which the processor is running and no other conflicts exist, the request is granted and the interrupt sequence takes place:

- a) the current program counter (PC) and processor status (PS) are pushed onto the processor stack;

- b) the new PC and PS are loaded from a pair of locations (the interrupt vector) in addressed memory, unique to the interrupting device.

Since each device has a unique interrupt vector which dispatches control to the appropriate interrupt handling routine immediately, no device polling is required. Furthermore, since the PS contains the processor priority, the priority at which an interrupt request is serviced can be set under program control and is independent of the priority of the interrupt request. The Return from Interrupt Instruction is used to reverse the action of the interrupt sequence. The top two words on the stack are popped into the PC and PS, returning control to the interrupted sequence.

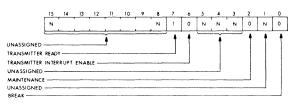

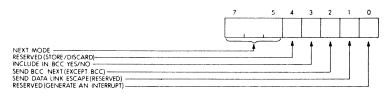

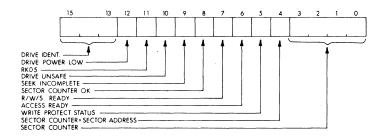

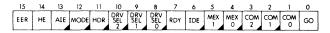

#### 2.6 PROGRAMMING WITH DEVICE REGISTERS

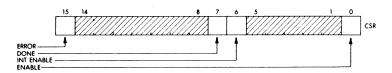

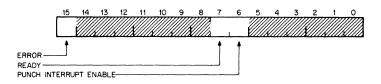

The diagram of Figure 2-5 shows 4 bits that would appear in many common Command and Status registers.

| BIT | NAME                           | FUNCTION ···                                                                                                                 |

|-----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 15  | Error                          | Set when an error occurs.                                                                                                    |

| 7   | Done                           | Set when the device is either ready to ac-<br>cept new information, or has completed<br>an operation and has data available. |

| 6   | Interrupt Enable<br>(INT ENBL) | When set, an interrupt will be requested when Done or Error becomes a 1.                                                     |

| 1   | Device Enable                  | Set to allow the peripheral device to per-                                                                                   |

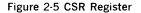

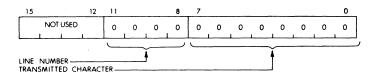

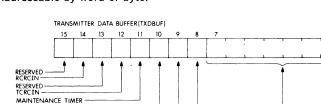

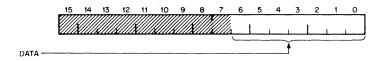

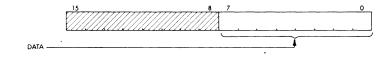

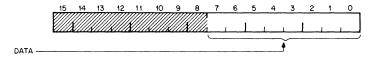

The diagram of Figure 2-6 shows a typical data buffer that can hold an 8-bit character.

form a function.

BIT NAME

(ENBL)

7-0 Data

#### FUNCTION

Holds the ASCII code for a character to be either written to or read from the peripheral device.

In the following examples, these two registers will be referred to by the symbolic designations, CSR and DBR.

**Example:** Transfer information from the peripheral data buffer to general register R3.

#### MOV DBR, R3

Since the information is only 8 bits, and it resides in the low part of the DBR, the byte instruction would accomplish the same purpose;

#### MOVB DBR, R3

The bit manipulating instructions,

- BIT (bit test), set condition codes N & Z according to an AND operation on corresponding bits; neither source nor destination are modified.

- BIC (bit clear), put 0's in all positions of the destination that correspond to a 1 in the source.

- BIS (bit set), put 1's in all positions of the destination that correspond to a 1 in the source (OR operation).

can be used to conveniently modify or test the contents of the CSR register.

**Example:** Enable the peripheral device to perform an I/O function:

BIS #1, CSR ; OR CODE 000 001 WITH THE CSR

This instruction will set bit 0 of the CSR, but leave all other bits unchanged.

**Example:** Test for an error, and branch to an error handling routine if there is an error.

TST CSR ;SET CONDITION CODE BITS ON CONTENTS OF CSR BMI ERRTN ;TEST BIT 15, BRANCH ON MINUS

ERRTN means the address of the error routine. When there is an error, bit 15 = 1, the CSR looks like a negative number (sign bit = 1).

**Example:** Test to see if the peripheral device has performed a read function, and data is available. Transfer to a read subroutine if data is available.

BIT #200, CSR ;TEST BIT 7 OF THE CSR BNE SBR ;BRANCH IF DONE IS SET

The CSR register is ANDed with a word of all 0's except for bit 7. If bit 7 (DONE) of the CSR is a 1, the result is not zero, and a branch on not equal to 0 can be made to a service subroutine (SBR).

Example: Prevent the peripheral device from causing an interrupt.

BIC #100, CSR ;CLEAR THE INT ENBL BIT

Using a source of 000 100 has the effect of clearing bit 6 (INT ENBL), but leaving all other bits of the CSR alone.

**Example:** Have the program continuously check the DONE bit, and read a word when it becomes a 1.

| AGAIN: | TSTB CSR     | ;TEST BIT 7, SIGN BIT |

|--------|--------------|-----------------------|

|        | BPL AGAIN    | ;BRANCH IF NOT SET    |

|        | MOVB DBR, RO | ;TRANSFER DATA TO CPU |

Bit 7 of the CSR is conveniently the sign bit for the low order byte, and can be tested directly by a single instruction.

#### 2.7 DEVICE PRIORITY

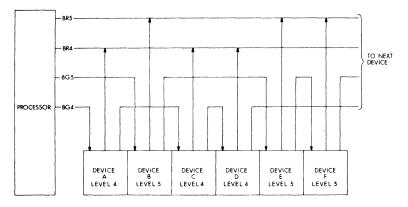

Each peripheral has a priority level assigned to it by hardware, allowing it to interrupt lower priority level devices. To ensure that the CPU which executes the peripheral's service routine is not incorrectly interrupted, the CPU itself must take on the priority level of the interrupting peripheral (Level 4, 5, 6, or 7) while running the service routine, see Figure 2-7.

**Example:** Write a program to service the input keyboard data (register KBB) from the LA30 DECwriter. The interrupt vector is at location 60, and the priority level is 4.

|        | . = 60      |                                     |

|--------|-------------|-------------------------------------|

|        | .WORD KBSBR | ; $PC = KEYBOARD SUBR ADDRESS$      |

|        | . WORD 200  | ; $PS = 4$ (BITS 7, 6, 5, $= 100$ ) |

| KBSBR; | MOV KBB, R1 |                                     |

| ``     | RTI         |                                     |

Example: Set the priority level of the processor to level 3.

| PS = 777776  | ;ADDRESS OF PROC STATUS WORD |

|--------------|------------------------------|

| CLR PS       | ;START WITH ALL 0's          |

| BIS #140, PS | ;SET BITS 6 & 5, PS = 3      |

**Example:** A paper tape reader interrupt service could appear as follows: First the user must initialize the service routine by specifying an address pointer and a word count

| INIT: | MOV #BUFADR, POINTR | ;SET ADDRESS POINTER                                     |

|-------|---------------------|----------------------------------------------------------|

|       | MOV #COUNT,COUNTR   | ;SET COUNTER                                             |

|       | MOV #101,PRS        | ;ENABLE READER PROGRAM TO CON-<br>;TINUE UNTIL INTERRUPT |

When the interrupt occurs and is acknowledged, the processor stores the current PC and PS on the stack. Next it goes to the interrupt vector and picks up the new PC and PS beginning at location 70. When the program was loaded the address of PRSER, the PR service routine, would be put in location 70 and  $200_{\circ}$  in 72 (to set priority at 4). The next instruction executed is the first instruction of PRSER.

| PRSER: | TST PRS          | ;TEST FOR ERROR                        |

|--------|------------------|----------------------------------------|

|        | BMI ERROR        | ;BRANCH IF BIT 15 SET                  |

|        | MOVB PRB,@POINTR | ;MOVE CHARACTER TO BUFFER              |

|        | INC POINTR       | ;INCREMENT POINTER                     |

|        | DEC COUNTR       | ;DECREMENT CHARACTER COUNT             |

|        | BEQ DONE         | BRANCH WHEN INPUT DONE                 |

|        | INC PRS          | ;START READER FOR NEXT CHARAC-<br>;TER |

| DONE:  | RTI              | ;RETURN TO INTERRUPTED PRO-<br>;GRAM   |

# CHAPTER 3

# CATEGORIES OF PERIPHERALS

#### 3.1 GENERAL

This chapter contains general information and comparisons of the PDP-11 peripherals. Sometimes a peripheral will fall into more than one category, and it will be listed wherever applicable.

This chapter shows the broad range of peripheral equipment offered and the wide span of equipment capabilities. Some of them are compared below.

#### **Comparison of Input Equipment**

| MEDIUM        | PRODUCT                                                              | INPUT SPEED (max)                           |

|---------------|----------------------------------------------------------------------|---------------------------------------------|

| Paper tape    | High speed reader/punch, PC11                                        | 300 characters/sec                          |

| Cards         | Card reader, CD11                                                    | 1,600                                       |

| Magnetic tape | Cassette, TA11<br>DECtape, TC11<br>Magtape, TS03<br>, TM11<br>, TU16 | 560<br>10,000<br>10,000<br>36,000<br>72,000 |

| Comparison of | Output Equipment                                                     |                                             |

| MEDIUM        | PRODUCT                                                              | OUTPUT SPEED (max)                          |

| Paper tape    | High speed reader/punch, PC11                                        | 50 characters/sec                           |

| Printer       |                                                                      |                                             |

|               | DECwriter II, LA36<br>DECprinter, LA180<br>Line printer, LP11        | 30<br>180<br>2,600                          |

| CRT terminal  | DECprinter, LA180                                                    | 180                                         |

, TM11 , TU16

Magtape, TS03

#### 3.2 MAIN MEMORY

Memories with different ranges of speeds and various physical and electrical characteristics can be freely mixed and interchanged within a PDP-11 system. Memory is treated as a physically modular, but electrically integral part of the computing system.

10,000

36,000

72,000

#### Types of Memory

Core. semiconductor, and read only memory (ROM) is offered for PDP-11 systems. Semiconductor memory (MOS and bipolar) is available for use with several of the PDP-11 Central Processing Units.

Parity is an available option for both core and semiconductor memory. No increase in mounting space is required.

#### **Operating Speed**

The CPU can begin processing data immediately after accessing it. (Access time is defined as the time interval between request and when the data is available.) Core memory then rewrites itself while the processor is working. (Semiconductor memory contents are not destroyed on read-out.) This makes the access time the important operating parameter for the PDP-11, thus providing increased speed and efficiency. The only effect cycle time has on the PDP 11 is the time needed between successive transfers to memory.

#### Packaging

Memory is offered as a complete system, including control and interfacing logic, interconnecting cables, and mounting assembly. Several of the PDP-11 processors have dedicated, pre-wired areas within the chassis for holding additional memory. In other cases, memory can be added within the CPU mounting assembly, and the necessary power taken from the cabinet power supplies.

#### 3.3 TERMINALS

#### Characteristics and Applications

- a) convenient human interface to the computer

- b) typewriter-like keyboard for data entry

- c) printer or display for output from computer

- d) basic input/output device

- e) can be local (console terminal), or remote

#### Products

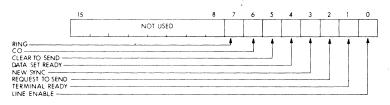

| MODEL                        | DESCRIPTION                                                                                     | OUTPUT SPEED (max)                                                                                                                                                        |

|------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

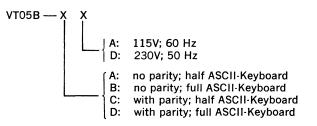

| LA36<br>VT05<br>VT50<br>GT40 | DECwriter II<br>Alphanumeric<br>Alphanumeric<br>Graphic display system<br>(includes a computer) | <ul> <li>30 characters/sec</li> <li>240</li> <li>960</li> <li>960 char/sec as a simple serial<br/>interfaced terminal, opera-<br/>tion can be faster as a syn-</li> </ul> |

| VT52                         | Video display                                                                                   | chronous device<br>960                                                                                                                                                    |

#### 3.4 PAPER TAPE

#### **Characteristics and Applications**

- a) simple medium to use

- b) separate tapes for individual programs

- c) variable program length

- d) data can be read by a person

#### Products

| MODEL | DESCRIPTION             | READ SPEED   | PUNCH SPEED |

|-------|-------------------------|--------------|-------------|

| PC11  | Paper tape reader/punch | 300 char/sec | 50 char/sec |

| PR11  | Paper tape reader       | 300          | —           |

#### 3.5 CARDS

#### Characteristics and Applications

- a) individual records

- b) easy to add, delete, or rearrange a card

- c) possible to print on the card

- d) can be read by a person

#### Products

| MODEL | DESCRIPTION | TYPE ·              | READ SPEED    |

|-------|-------------|---------------------|---------------|

| CM11  | Card reader | mark-sense or punch | 285 cards/min |

| CR11  | Card reader | punch               | 285           |

| CD11  | Card reader | punch               | 1200          |

#### 3.6 PRINTERS

# **Characteristics and Applications**

- a) hard copy for permanent records

- b) impact types can make multiple copies

- c) some plotting capability

#### Products

| MODEL         | DESCRIPTION             | TYPE               | PRINT SPEED                 | COLUMNS           | CHAR.       |

|---------------|-------------------------|--------------------|-----------------------------|-------------------|-------------|

| LA36<br>LA180 | DECwriter<br>DECprinter | impact<br>impact   | 30 char/sec<br>180 char/sec | <b>8</b> 0<br>132 | 64<br>96    |

| LP11          | Line Printer            | impact             | 230 to 1200<br>lines/min    | 132               | 64 or<br>96 |

| LV11          | Printer/plotter         | electro-<br>static | 500 lines/min               | 132               | 96          |

#### 3.7 MAGNETIC TAPE

#### Characteristics and Applications

- a) unlimited off-line storage

- b) removable medium

#### Products

| MODEL                                          | DESCRIPTION                                                            | STORAGE/REEL                                                    | DATA RATE                                            |  |

|------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|--|

| TA11<br>TC11/TU56<br>TS03<br>TM11/TU10<br>TU16 | Cassette<br>DECtape<br>Magnetic tape<br>Magnetic tape<br>Magnetic tape | 90,000 char<br>295,000<br>5,000,000<br>20,000,000<br>32,000,000 | 560 char/sec<br>10,000<br>10,000<br>36,000<br>72,000 |  |

|                                                |                                                                        |                                                                 |                                                      |  |

#### 3.8 DISKS

#### Characteristics and Applications

- a) fast access to on-line storage

- b) swapping programs

- c) virtual memory

- d) efficient bulk storage

- a) Fixed Head-fast access time

- b) Moving head—high storage capacity, more economical storage

- c) Disk pack-removable medium, unlimited off-line storage

The average access time (avg latency) is equal to  $\frac{1}{2}$  the time for a revolution plus the average head positioning time (for moving head disks only).

#### Products

| MODEL     | DESCRIPTION     | CAPACITY/<br>DRIVE | AV ACCESS<br>TIME | DATA<br>RATE |

|-----------|-----------------|--------------------|-------------------|--------------|

| RX11/RX01 | Floppy disk     |                    | 483 msec          | 36 μsec/word |

| RK11/RK05 | Disk cartridge  |                    | 70msec            | 11 μsec/word |

| RP11/RP03 | Disk pack       |                    | 42                | 7.5          |

| RS03      | Fixed head disk |                    | 8.5               | 4 or 8       |

| RS04      | Fixed head disk |                    | 8.5               | 4            |

| RP04      | Disk pack       |                    | 36                | 2.5          |

#### 3.9 DISPLAYS

#### **Characteristics and Applications**

- a) pleasing human interface

- b) soft copy of information

- c) fast presentation of information

- d) alphanumeric and graphic capability

#### Products

#### MODEL DESCRIPTION

- VR01 Oscilloscope

- VR14 Point plot display

- VT01 Storage display

- VT05 Alphanumeric terminal

- VT50 Alphanumeric terminal

- VT52 Alphanumeric terminal

- GT40 Graphic display system

- (includes a computer)

#### 3.10 COMMUNICATIONS OPTIONS Characteristics and Applications

Draduate

- Asynchronous Interfaces—Character transmission time is variable, but bits within the character are timed; a character transmission normally includes a start bit, several data bits, one or more stop bits, and an optional parity bit.

- Synchronous Interfaces—Continuous data stream once the receiver is synchronized; data is generally transmitted in message blocks containing both information and timing signals.

- Ocner Communications Options—Provide error detection, autocalling unit interfacing, and signal conditioning.

| Products      |                                                  |                                                                                                                                                                                                          |

|---------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODEL         | DESCRIPTION                                      | TYPICAL USE                                                                                                                                                                                              |

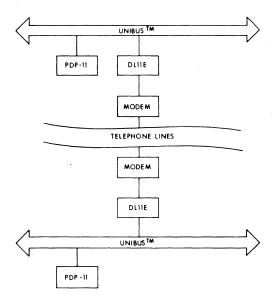

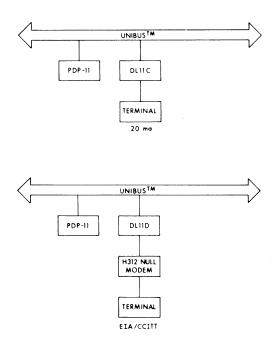

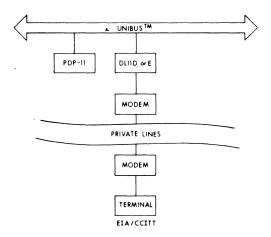

| DL11          | Single Asynchronous Line<br>Interface            | Connects PDP-11 to local<br>terminals (such as Tele-<br>type, LA36 and VT05)<br>or to remote terminals<br>via modems.                                                                                    |

| DJ11          | 16-Line Asynchronous<br>Multiplexer              | Connects PDP-11 to up<br>to 16-local terminals or<br>up to 16-remote ter-<br>minals via modems.<br>Transmission speeds and<br>other parameters are<br>switch or jumper select-<br>able in 4-line groups. |

| DH11          | 16-Line Programmable<br>Asynchronous Multiplexer | Connects PDP-11 to up<br>to 16-local terminals or<br>remote terminals. Trans-<br>mission speeds and<br>parameters are program-<br>mable.                                                                 |

| DN11          | Auto Calling Unit<br>Interface                   | Interfaces PDP-11 to Bell 801 auto calling units.                                                                                                                                                        |

| DU11          | Single Line Synchronous<br>Interface             | Connects PDP-11 to mo-<br>dems for medium speed<br>(up to 9600 Baud)<br>synchronous transmis-<br>sion.                                                                                                   |

| DQ11          | Single Line Synchronous<br>Interface             | Used for high through-<br>put synchronous<br>transmission.                                                                                                                                               |

| KG11          | Communication Arithmetic<br>Element              | Used to detect errors in serially transmitted data.                                                                                                                                                      |

| DC08 and H316 | Telegraph Line Interfaces                        | Connects PDP-11 to tele-<br>graph equipment.                                                                                                                                                             |

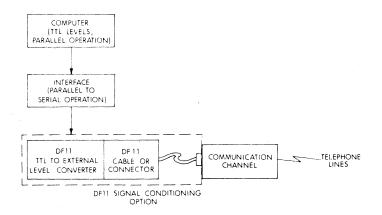

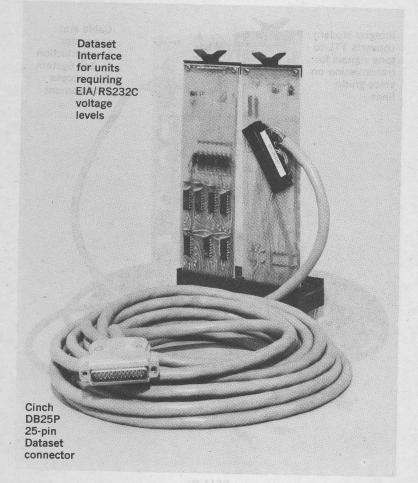

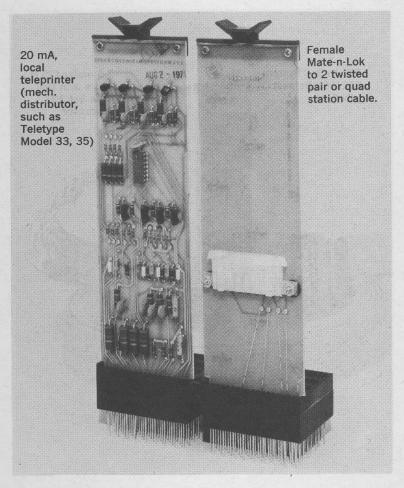

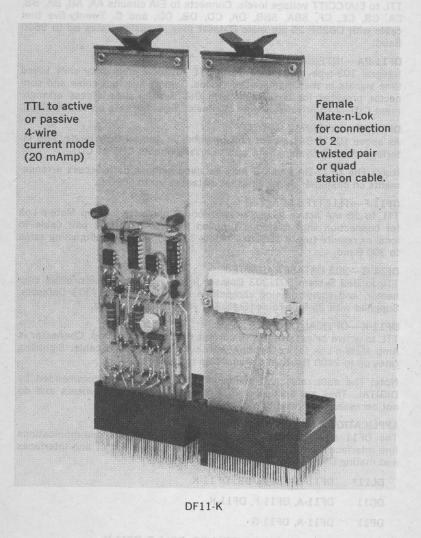

| DF11   | Signal Conditioning Options | Converts computer (TTL)<br>signals to EIA or 20 ma<br>signals. Can be used<br>with DC11, DL11 and<br>DH11 interfaces.              |

|--------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|

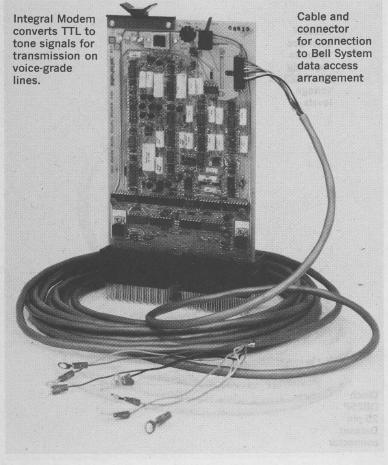

| DF11-B | Integral Modems             | Converts TTL signals to<br>audio frequencies. Used<br>to connect PDP-11<br>directly to Bell Data<br>Access Arrangement<br>options. |

| DF01   | Acoustic Coupler            | Connects terminal<br>(VT05, LA36) to standard<br>telephone for communi-<br>cation with computer via<br>phone lines.                |

| H313-A | Voltage Current Adapter     | Converts Digital supplied<br>TTY output for use with<br>Bell 103 modems or<br>equivalent.                                          |

| H312-A | Null Modem                  | Allows direct connection<br>of a terminal with an EIA<br>cable to a DC11, DL11,<br>or DM11-DB.                                     |

# 3.11 DATA ACQUISITION

# **Characteristics and Applications**

- a) analog conversion equipment

- b) analog circuitry

- c) digital control and monitoring

- d) timing control

- e) laboratory experimentation

- f) industrial control

#### **Products**

- MODELDESCRIPTIONAA11Digital-to-analog conversion subsystem, 12 bitsAD01Analog-to-digital conversion subsystem, 10 or 11 bitsLPS11Lab Peripheral System, 12 bits<br/>(A/D, real time clock, D/A, digital I/O)AFC11Low level analog input subsystem, flying capacitor scanner<br/>UDC11UDC11Digital control subsystem

- KW11-L Line clock

- KW11-P Programmable clock

#### 3.12 UNIBUS EQUIPMENT

#### MODEL DESCRIPTION

- DR11-K General device interface

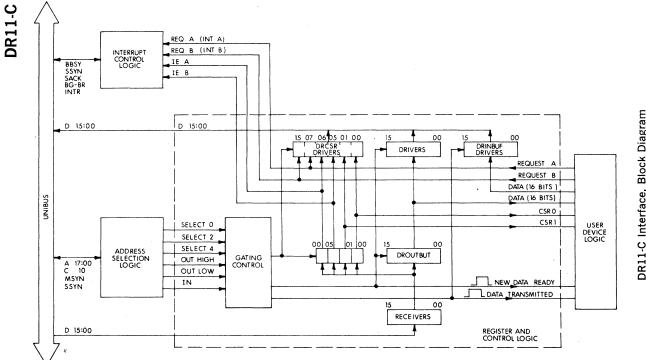

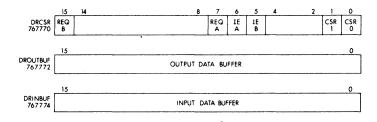

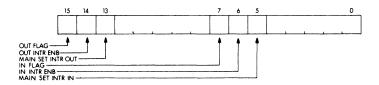

- DR11-C General device interface (program interrupts)

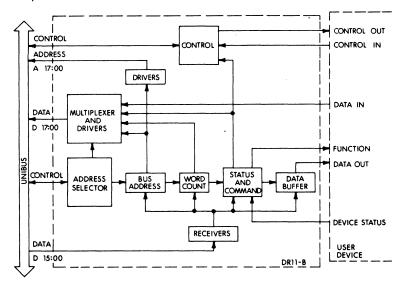

- DR11-B Direct Memory Access interface (NPR data transfers)

- DT03 UNIBUS switch

- DA11-B UNIBUS link

- DA11-F UNIBUS window

#### 3.13 MOUNTING EQUIPMENT

#### SYSTEM UNIT SPACE MODEL DESCRIPTION BB11 Blank mounting panel 1 **DD11** Peripheral mounting panel 1 BA11-K Extension Mounting Box 5 H960-D Cabinet with a drawer 9 Cabinet H960-CA

**·8**

# DESCRIPTIONS OF PERIPHERALS

#### 4.1 INTRODUCTION

This chapter contains detailed descriptions, specifications, programming, and operating information for PDP-11 peripheral equipment. For ease of reference, the peripherals have been arranged alphanumerically by model number, with the model number appearing on the top righthand side of each page.

Since some peripherals have similar descriptions and specifications, related peripherals will be described within the same section. Section 4.3 contains a complete list of all equipment described in this chapter. Appendix E contains an index to all equipment described in this Handbook.

#### 4.2 EXPLANATION OF TERMS AND SPECIFICATIONS

#### 4.2.1 Products

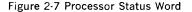

All the peripherals mentioned in this chapter must eventually interface to the UNIBUS. Some of the equipment, such as Line Printers, include a control unit as well as the printer itself. The control unit, sometimes referred to as a controller or interface unit, is the actual logic equipment between the UNIBUS and the peripheral device. With terminals, the control unit and the terminal itself are separate products. In this case, several different control units could be used, depending on the application. In other cases, such as disk drives, a single model number includes a control unit and the first disk drive of the system. Other disk drives, up to the limit of the system, are specified by another model number, see Figure 4-1.

#### 4.2.2 Registers

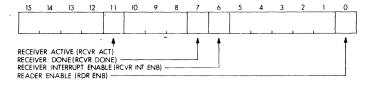

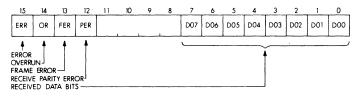

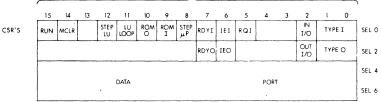

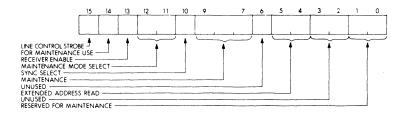

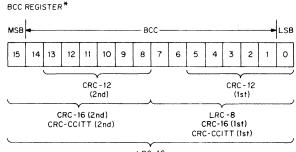

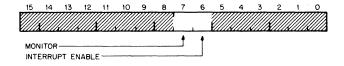

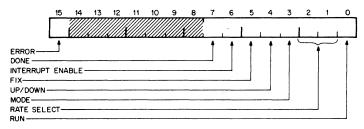

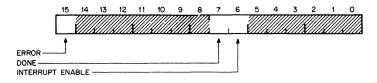

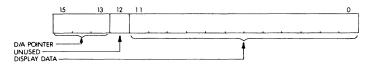

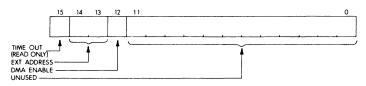

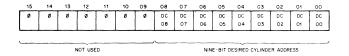

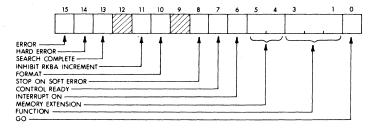

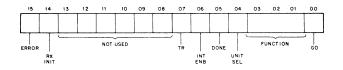

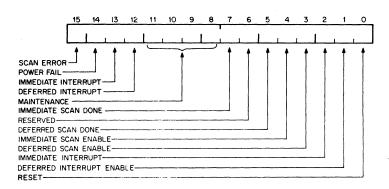

The device registers are shown with their common name, their mnemonic in parentheses, then their UNIBUS address. Note that these addresses begin with 77 or 76 (instead of 17 or 16) to indicate that they are in the highest 4K words of address space. Within the functional description of each bit, if not otherwise indicated, the condition or operation when the bit is set (logic 1) is described.

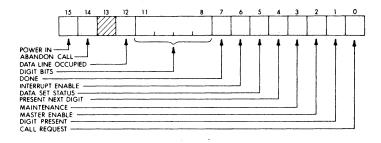

Some bit positions of the registers are not used (not implemented with hardware). When diagrams are shown, unused positions are indicated by cross-hatching. Some of the bits are controlled only by the peripheral device and are indicated as read only (by the program). Some of the bits are write only (by the program), and are always read as zeros. Some bits are cleared (or set) by the UNIBUS master clear signal called Initialize, which has the mnemonic INIT. It is issued by turning Power ON, Console START, or the RESET instruction. Figure 4-2 summarizes the information about the device registers.

Figure 4-1. Disk Storage System

The unused or write only bits are always read as zeros by the program. Trying to load unused or read only bits has no effect on the addressed register.

#### Register (REG) 77x xxx

$\boxtimes$  = unused bit

- Read only: (with respect to the CPU or bus master)—The program can monitor the bit, but cannot modify it.

- Write only: (with respect to the CPU or bus master)—The program can set or clear the bit; but when reading, it will always appear to be a zero.

#### Figure 4-2. Device Register

#### 4.2.3 Specifications

#### UNIBUS Interface

Interrupt and trap vectors are assigned to the lowest part of memory, generally in the range 000 000 to 000 377. Bus Request (BR) levels are indicated; also Non-Processor Request (NPR) operation if applicable. Most devices that interface to the UNIBUS represent only 1 bus load.

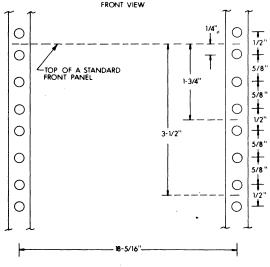

#### **Mechanical**

The mounting arrangement of the equipment is indicated as:

| a) | module:        | plugs into a dedicated logic module slot         |

|----|----------------|--------------------------------------------------|

| b) | SPC:           | fits in a small peripheral controller slot       |

|    |                | (quad module)                                    |

| c) | SU:            | system unit mounting assembly is included        |

| d) | panel:         | uses front panel space in a cabinet              |

| e) | table top:     | suitable for placing on top of a table or a desk |

| f) | free standing: | by itself, not in a cabinet                      |

| g) | cabinet:       | mounts in a standard PDP-11 cabinet              |

Some peripherals include 2 separate physical parts and are indicated by use of a plus (+) sign.

#### Relative Humidity

All humidity specifications mean without condensation.

#### Temperature

Correspondence between Centigrade and Fahrenheit is shown in the following table:

| °F         |

|------------|

| 32         |

| 41         |

| 50         |

| 5 <b>9</b> |

| 68         |

| 77         |

| 86         |

| 95         |

| 104        |

| 113        |

| 122        |

| 131        |

|            |

$$\left[(^{\circ}C) \times \frac{9}{5}\right] + 32 = (^{\circ}F)$$

#### 4.2.4 Conversion Factors

$(inches) \times 2.54 = (cm)$   $(lbs) \times 0.454 = (kg)$  $(Watts) \times 3.41 = (BTU/hr)$

#### 4.3 LIST OF PERIPHERALS

The peripherals described in this chapter are arranged in the following sequence:

| Model Numbers        | Description                | Page |

|----------------------|----------------------------|------|

| AA11 (also BA164)    | D/A subsystem              | 4-5  |

| AD01                 | A/D subsystem              | 4-9  |

| AFC11                | Low level analog subsystem | 4.13 |

| AR11                 | Analog subsystem           | 4-19 |

| BA11-K               | Expansion mounting box     | 4-22 |

| BB11                 | Blank mounting panel       | 4-24 |

| BM792 (also MR11-DB, |                            |      |

| M792)                | Read only memory           | 4-25 |

| BM873             | Restart/Loader                        | 4-27           |

|-------------------|---------------------------------------|----------------|

| CD11              | Punched card reader                   | 4-31           |

| CR11 (also CM11)  | Punched card reader                   | 4-44           |

| DA11-B            | UNIBUS link                           | 4-54           |

| DA11-F            | UNIBUS window                         | 4-5 <b>9</b>   |

| DB11              | Bus repeater                          | 4-67           |

| DD11              | Peripheral mounting panel             | 4-68           |

| DF01              | Acoustic telephone coupler            | 4-72           |

| DF11              | Serial line signal conditioning       | 4-74           |

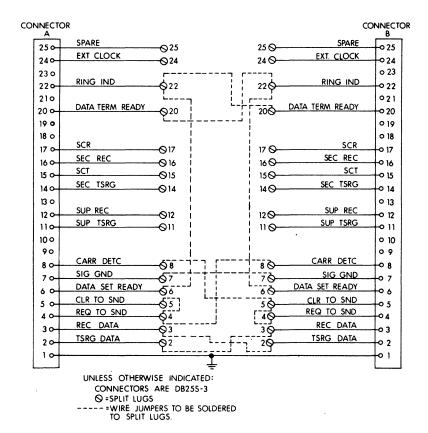

| DH11 (also DM11)  | Asynch serial line multiplexer (prog) | 4-82           |

| DJ11              | Asynch serial line multiplexer        | 4-111          |

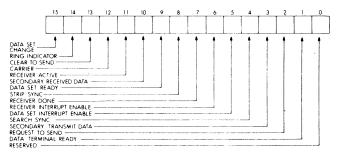

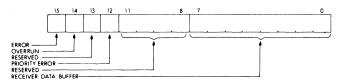

| DL11              | Single asynch serial line interface   | 4-128          |

| DL11-W            | Serial line interface                 | 4.145          |

| DMC11             | Network link                          | 4.150          |

| DN11              | Automatic calling unit interface      | 4-169          |

| DQ11              | NPR synch line interface              | 4.177          |

| DR11-B            | Direct memory access interface        | 4-212          |

| DR11-C            | General device interface              | 4.217          |

| DR11-C<br>DR11-K  | General device interface              | 4-227          |

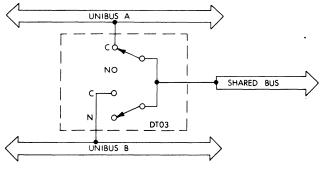

|                   | UNIBUS switch                         | 4.231          |

| DT03              |                                       | 4-231          |

| DU11              | Synchronous line interface            | 4-255          |

| DUP11             | Synchronous line interface            |                |

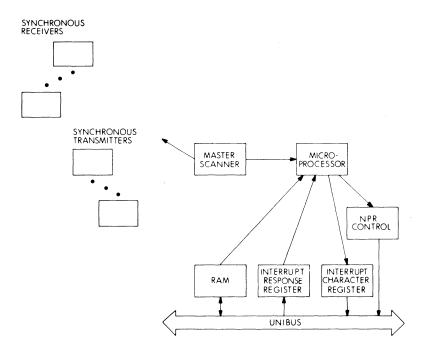

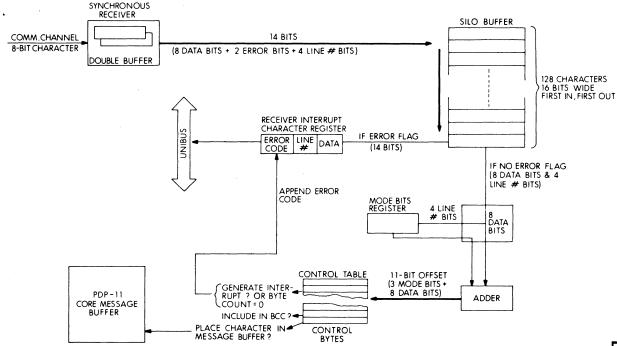

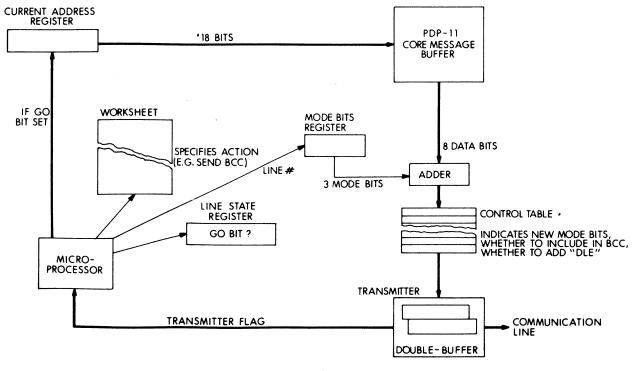

| DV11              | Synchronous preprocessor              | 4.278          |

| GT40              | Graphic display system                | 4-311          |

| H312              | Asynchronous null modem               | 4-317          |

| H960              | Standard PDP-11 cabinet               | 4·318          |

| KE11              | Extended arithmetic element           | 4-320          |

| KG11              | Communications arithmetic option      | 4-323          |

| KW11-L            | Line time clock                       | 4-332          |

| KW11-P            | Programmable real time clock          | 4-333          |

| LA35              | DECwriter II printer                  | 4-33 <b>6</b>  |

| LA36              | DECwriter II terminal                 | 4-341          |

| LA180             | DECprinter                            | 4-34 <b>9</b>  |

| LP11              | High speed line printer               | 4-353          |

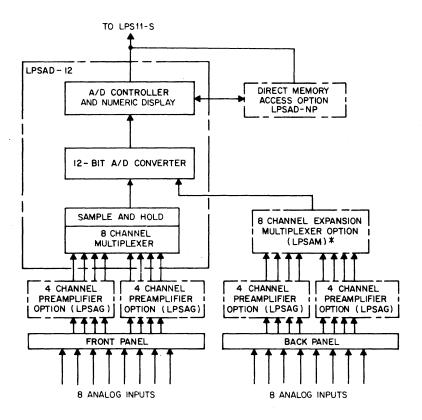

| LPS11             | Lab peripheral system                 | 4-360          |

| LV11              | Electrostatic printer/plotter         | 4-372          |

| PC11 (also PR11)  | High speed paper tape reader/punch    | 4-376          |

| RJP04 (also RP04) | Disk pack                             | 4-3 <b>8</b> 4 |

| RJS04 (also RS04) | Fixed head disk                       | 4-414          |

| RK11 (also RK05)  | DECpack disk cartridge                | 4-433          |

| RP11 (also RP03)  | Disk pack                             | 4-445          |

| RX11 (also RX01)  | Floppy disk                           | 4-455          |

| TA11              | Cassette                              | 4-462          |

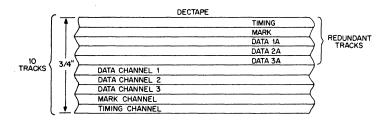

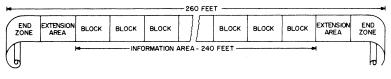

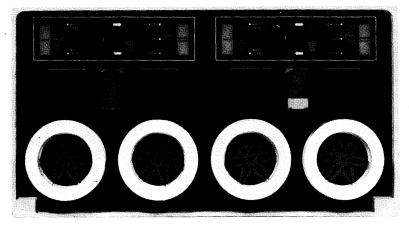

| TC11 (also TU56)  | DECtape                               | 4-467          |

| TJU16 (also TU16) | Magnetic tape                         | 4-480          |

| TM11 (also TU10)  | Magnetic tape                         | 4-501          |

| TS03              | Magnetic tape                         | 4.515          |

| UDC11             | Universal digital control subsystem   | 4-519          |

| VR01 -            | Oscilloscope                          | 4-526          |

| VR14              | Point plot display                    | 4-527          |

| VT01              | Storage display                       | 4-52 <b>9</b>  |

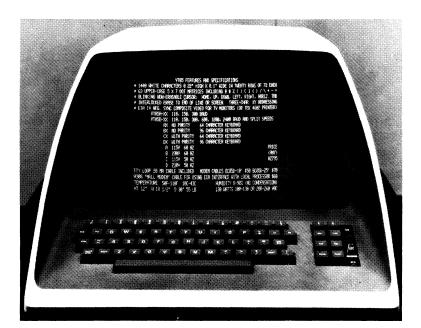

| VT05              | Alphanumeric display terminal         | 4-530          |

| VT50              | Alphanumeric display terminal         | 4-536          |

| VT52              | DECscope terminal                     | 4-542          |

|                   |                                       |                |

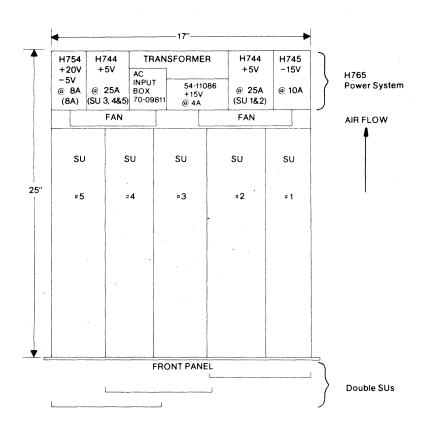

# DIGITAL TO ANALOG SUBSYSTEM, AA11-D

#### DESCRIPTION

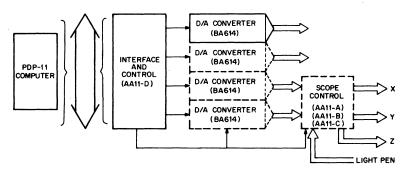

The AA11-D is a low cost, high performance multichannel digital-toanalog conversion subsystem for PDP-11 computers.

Interfacing directly to the PDP-11 UNIBUS, the AA11-D controls up to four single buffered, 12-bit bipolar digital-to-analog converters. Each BA614 converter, which includes output amplifier and reference voltage source, is contained on a plug-in module and provides 10 ma current output at  $\pm$  10 volts. Full scale output voltage is trimpot adjustable from  $\pm$  1v to  $\pm$  10v in two ranges.

Storage scope, display scope, and light pen control options are available for the AA11-D. These options provide Z axis blanking for intensity control and require two D/A converters to control X and Y trace coordinates.

Available as a factory or field installed option, the AA11-D fully implemented with four digital to analog converters and a scope control option, is contained in a single System Unit. A rack mountable power supply is separate.

AA11-D Subsystem

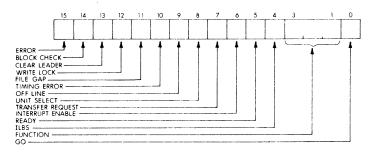

#### REGISTERS

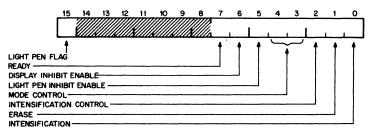

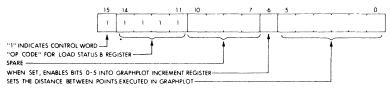

#### Command and Status Register (CSR) 776 756

| BIT   | NAME                     | FUNCTION                                                                                                                                                                                                                       |

|-------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | Light Pen Flag           | If bit 05 is "1," light pen flag causes<br>interrupt. Cleared by INIT and reading<br>the register. Read only.                                                                                                                  |

| 7     | Ready                    | Set when scope is ready for service,<br>because of INTEN or ERASE com-<br>mands or X or Y has been loaded.<br>Interrupt occurs if bit 06 is "1." Bit<br>07 is set by INIT and cleared by dis-<br>playing new point. Read only. |

| 6     | Display Inhibit Enable   | Set to permit interrupts to occur when<br>intensification or erasure is com-<br>pleted. This bit is set by program con-<br>trol and cleared by INIT. Read/Write.                                                               |

| 5     | Light Pen Inhibit Enable | Set to permit interrupts to occur when<br>signal is received from light pen. This<br>bit is set by program control and<br>cleared by INIT. Read/Write.                                                                         |

| 4-3 . | Mode Control             | Determines intensification on loading X or Y.                                                                                                                                                                                  |

| 2     | Intensification Control  | Selects Stored Mode or High Intensity<br>Mode depending on scope used.<br>Read/Write                                                                                                                                           |

| 1     | Erase                    | Set to erase storage scope display.<br>Sets READY bit 7 at end of erase.                                                                                                                                                       |

| 0     | Intensification          | Set to delay display until scope de-<br>flects to new X, Y values, then strobes<br>intensification (Z axis) and sets<br>READY bit 7.                                                                                           |

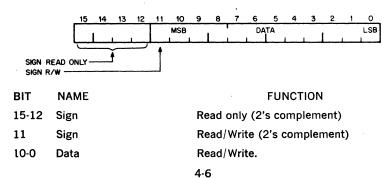

#### Data Registers (DAC) 776 760 to 776 766

DAC1 and 2 may be used either in conjunction with the scope or for D/A channels. DAC3 and 4 may be used for additional D/A channels.

# SPECIFICATIONS FOR AA11-D

| Register | Addresses |

|----------|-----------|

|----------|-----------|

| Command and Status (CSR) |  |

|--------------------------|--|

| Data Register (DAC1)     |  |

| Data Register (DAC2)     |  |

| Data Register (DAC3)     |  |

| Data Register (DAC4)     |  |

# **UNIBUS** Interface

Interrupt vector address: Priority level: Bus loading: 140, 144 BR4, or 5 1 bus load

1 System Unit (SU)

0.5 A at 115 VAC 3 A at + 5 V

Mounting:

Power Input current:

Heat dissipation:

# Environment

Operating temperature: Relative humidity: 10°C to 40°C 10% to 90%

60 W

# Models

AA11-DA: D/A converter subsystem, 115 VAC, 60 Hz AA11-DB: " , 230 VAC, 50 Hz

# SPECIFICATIONS FOR D/A CONVERTER (BA614)

| Digital Input:                             | 11 bits $+$ sign, 2's complement code.                                                                                      |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Digital Storage:                           | Single buffered.                                                                                                            |

| Update Rate/Channel:                       | 50 KHz                                                                                                                      |

| Analog Output Voltage:                     | $2$ continuously adjustable full scale ranges: $1\nu$ to $5\nu$ and $5\nu$ to $10\nu$                                       |

| Current:                                   | 10 ma                                                                                                                       |

| Gain Accuracy:                             | $\pm$ 0.025% of full scale (25 $^{\circ}$ C)                                                                                |

| Linearity:                                 | $\pm~1/2$ least significant bit (LSB)                                                                                       |

| Zero Offset:                               | Adjustable to zero                                                                                                          |

| Settling Time:                             | 20 $\mu$ s max. to within $\frac{1}{2}$ LSB for full scale step change (at output connector with zero capacitance loading). |

| Output Impedance:                          | Less than 1 ohm.                                                                                                            |

| Temp Coefficient:<br>(after 5 min. warmup) | $\pm$ 50 $\mu$ v/ $^{\circ}$ C - zero offset and $\pm$ .003%/ $^{\circ}$ C - gain accuracy                                  |

# SCOPE CONTROL OPTIONS

The following scope controls each require two BA614 digital to analog converters:

# AA11-A Scope Control for Tektronix 611 Storage Display Unit

| Display Rate:<br>Display Time:                        | 30 Hz (min) to 10 KHz (max)<br>deflection time 80 $\mu$ s<br>intensification time 20 $\mu$ s<br>Non-storage mode:<br>deflection time 80 $\mu$ s<br>intensification time 2 $\mu$ s |  |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Erase Time:                                           | 0.5 sec                                                                                                                                                                           |  |  |

| AA11-B Scope Control for Tektronix RM503 Oscilloscope |                                                                                                                                                                                   |  |  |

| Display Rate:                                         | 45 KHz (max)                                                                                                                                                                      |  |  |

| Display Time:                                         | deflection time 20 $\mu$ s intensification time 2 $\mu$ s                                                                                                                         |  |  |

| Intensification: (program selectable)                 | two levels                                                                                                                                                                        |  |  |

| AA11-C Scope Control for VR12 Point Plot Display      |                                                                                                                                                                                   |  |  |

| Display Rate/point:                                   | 40 Hz (min) to 40 KHz (max)                                                                                                                                                       |  |  |

| Display Time:                                         | deflection time 20 $\mu$ s intensification time 2 $\mu$ s                                                                                                                         |  |  |

| Intensification: (program selectable)                 | two levels                                                                                                                                                                        |  |  |

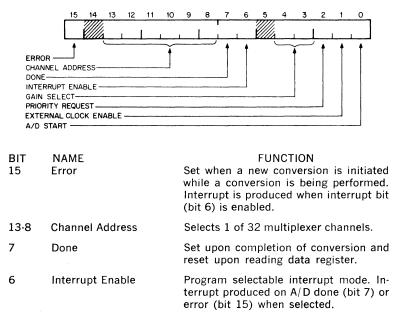

# AD01

# ANALOG TO DIGITAL SUBSYSTEM, AD01-D

# DESCRIPTION

The AD01-D is a flexible, low-cost multichannel analog data acquisition option which interfaces directly to PDP-11 computers. When it is under computer or external clock control, the AD01-D provides 10-bit digitization of unipolar high-level analog signals having a nominal full-scale range of 0 to + 1.25, + 2.5, + 5.0 or + 10.0 volts. An optional sign-bit addition allows 11-bit bipolar operation. Programmable input range selection extends the AD01-D's dynamic range at moderate sampling rates to the equivalent of 13 bits for unipolar signals or 14 bits for bipolar signals.

An optional sample-and-hold amplifier reduces the conversion aperture to 100 nanoseconds.

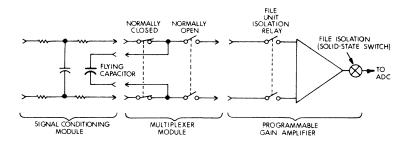

The standard AD01-D consists of an expandable solid-state input multiplexer, programmable input range selector, A/D converter, control, and bus interface in a single  $5\frac{1}{4}$ -inch rack-mountable assembly plus a separate logic power supply. The multiplexer can be expanded by adding 4-channel modules up to 32 channels. An expansion multiplexer may be added to provide a maximum configuration of 64 channels.

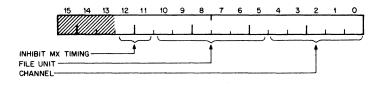

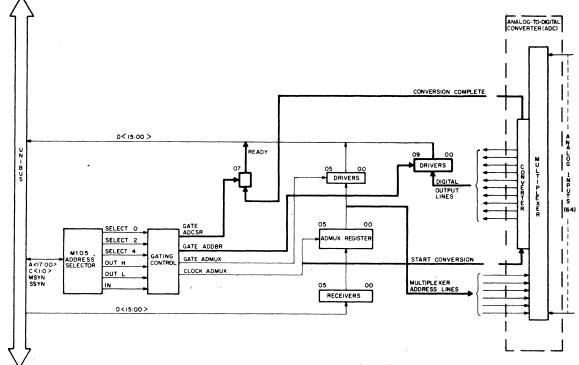

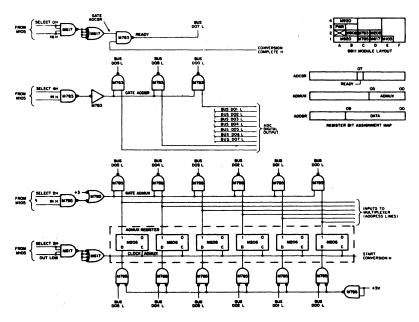

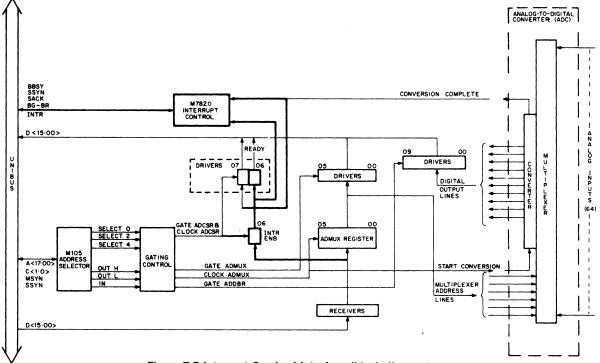

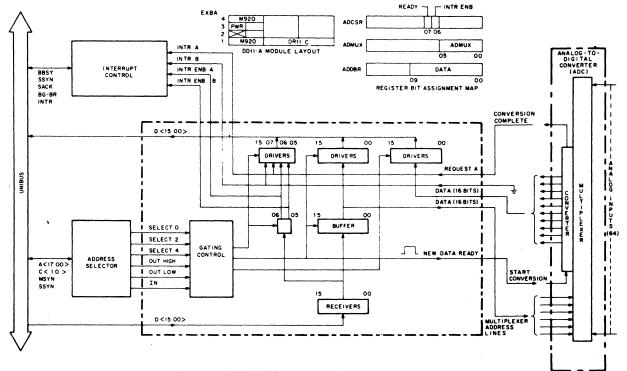

# REGISTERS Control and Status Register (ADCS) 776 770

| 3-4 | Gain Select           | Selects input gain range of 1, 2, 4, or 8.                                                                                                                                      |

|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|