de se destà cé

e al capato e

# CIBCA User Guide

A ATT. SAT . .

SACAMIL, AN

100-004 al

AC) Obi.

r, it: .

EK-CIBCA-UG-001

## CIBCA User Guide

Prepared by Educational Services of Digital Equipment Corporation

MKV87-1038

$(\mathfrak{I})$

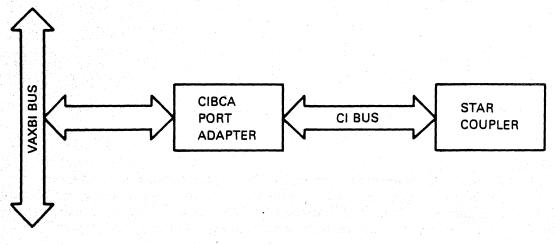

## Figure 1-1 Simplified CIBCA Port Adapter Connection

### 1.2.2 Features

- VAX Backplane Interconnect design

- Diagnostic data loopback (internal/external) capability

- Data integrity via cyclic redundancy checking

- Round-robin arbitration at heavy loading

- Contention arbitration at light loading

- Packet-oriented data transmission

- Immediate acknowledgment of packet reception

- Operational modes

- Disabled

- Enabled

- Uninitialized

- Dual signal paths

## 1.3 SPECIFICATIONS

## **CI GENERAL SPECIFICATIONS**

Priority arbitration

| Light loading<br>Heavy loading | Contention<br>Round-robin                                                                                                               |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Parity                         | Cyclic redundancy check                                                                                                                 |

| Data format                    | Manchester-encoded serial packet                                                                                                        |

| ENVIRONMENTAL SPECIFICATIONS   |                                                                                                                                         |

| Temperature                    |                                                                                                                                         |

| Operating                      | 10°C to 40°C (50°F to 104°F) ambient temperature with a gradient of 10°C (18°F)/hr                                                      |

| Storage/shipping               | -40°C to 70°C (-40°F to 158°F) ambient temperature with a gradient of 2°C (36°F)/hr                                                     |

| Relative Humidity              | 이는 것이 같은 것이 같은 것이 있는 것이 않는 것이 않는 것이 있다.<br>같은 것이 같은 것이 같이 |

| Operating                      | 10% to 90% with a maximum wet bulb temperature of 28°C (82°F) and a minimum dew point of 2°C (36°F) with no condensation                |

| Storage/shipping               | 5% to 95% with no condensation                                                                                                          |

| Altitude                       |                                                                                                                                         |

| Operating                      | Sea level to 2.4 km (8,000 ft)                                                                                                          |

|                                | Maximum operating temperatures decrease by a factor of $1.8^{\circ}C/1000$ (1°F/1000 ft) for operation above sea level.                 |

| Storage/shipping               | Up to 9.1 km (30,000 ft) above sea level (actual or effec-<br>tive by means of cabin pressurization)                                    |

| Shock                          | 5 Gs peak at 7 to 13 ms duration in three axes mutually perpendicular (maximum)                                                         |

| ELECTRICAL SPECIFICATIONS      |                                                                                                                                         |

## Power consumption

+5.0 V at 8 A nominal -5.2 V at 2 A nominal -2.0 V at 1 A nominal

## VAXBI BUS SPECIFICATIONS

**Bus Characteristics**

| Туре                 | Synchronous                                             |

|----------------------|---------------------------------------------------------|

| Width                | 32 data bits                                            |

| Cycle time           | 200 ns                                                  |

| Priority arbitration | Distributed embedded                                    |

| Parity               | Odd                                                     |

| Data transfers       | Block mode (masked)<br>Longword<br>Quadword<br>Octaword |

Transmission Characteristics

Bandwidth

| Master port<br>Slave port | 11.4 Mbytes/s<br>13.3 Mbytes/s |

|---------------------------|--------------------------------|

| Length (maximum)          | 1.5 m (5 ft)                   |

| Bus loading (maximum)     | 16 logical nodes               |

## **CI BUS SPECIFICATIONS**

| Bus Characteristics                               |                   |

|---------------------------------------------------|-------------------|

| Width Serial                                      |                   |

| External length (maximum) 45 m (147.64 ft) radius | from star coupler |

| Data transfer rate 70 Mbits/s (maximum)           |                   |

| Bus loading (maximum) 16 logical nodes            |                   |

| Cable type (BNCIA-XX) Double shielded coaxial     |                   |

| Cable impedance 50 ohms                           |                   |

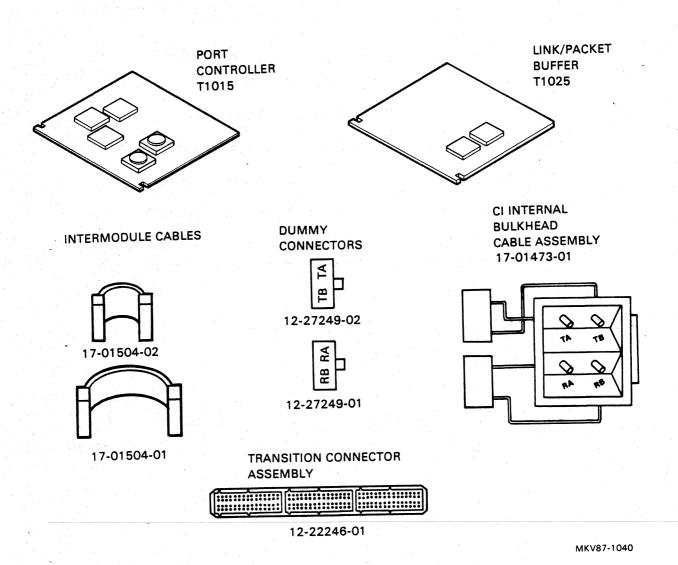

**1.4 PHYSICAL HARDWARE DESCRIPTION** Refer to Table 1-1 and Figure 1-2 for an overview of the hardware components of the CIBCA.

| Part Number | Component Type                        |  |

|-------------|---------------------------------------|--|

| T1015       | Port controller module                |  |

| T1025       | Link/packet buffer module             |  |

| 17-01504-01 | 2.0 inch cable (1 each)               |  |

| 17-01504-02 | 0.7 inch cable (1 each)               |  |

| 17-01473-01 | Internal CI bulkhead cable assembly   |  |

| 12-27249-01 | Dummy connector (Receive)             |  |

| 12-27249-02 | Dummy connector (Transmit)            |  |

| 12-22246-01 | Transition connector assembly (2 each |  |

|             |                                       |  |

Table 1-1 Hardware Components of the CIBCA Adapter

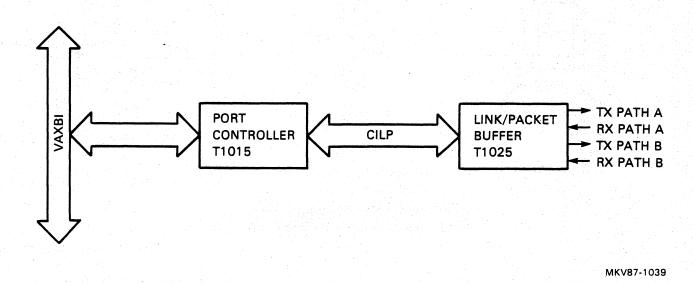

Figure 1-2 Simplified CIBCA Block Diagram

#### **CIBCA HARDWARE**

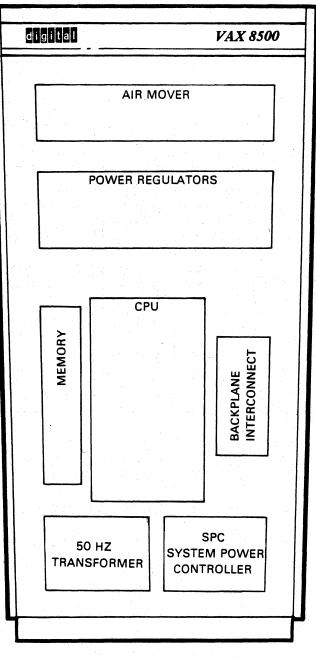

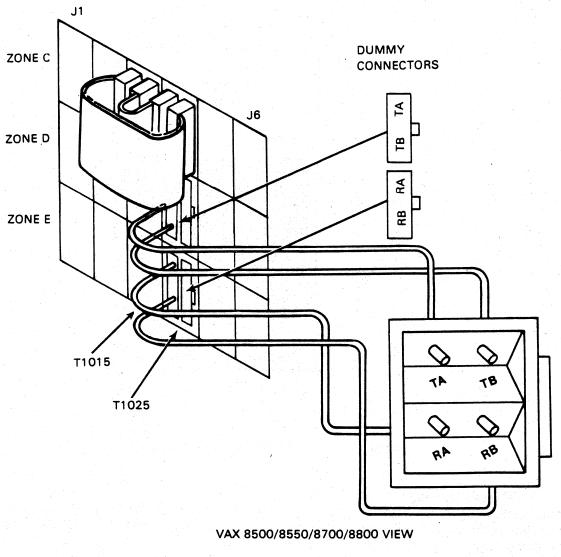

Refer to Figure 1-3. The CIBCA consists of two T-series type modules. The T-series modules are housed in two adjacent slots within an H9400-A VAXBI card cage. These modules are used to interface the host system's VAXBI bus to the CI bus.

Figure 1-3 Hardware Components of the CIBCA

#### The Port Controller Module

The port controller module, part number T1015, contains the VAXBI protocol, the VAXBI control logic, microprocessor, and control store.

#### The Link/Packet Buffer Module

The link/packet buffer module, part number T1025, contains the CI bus protocol logic and CI packet buffer memory.

#### **CIBCA** Cables

The two CIBCA cables are used to electrically interconnect the T1015 and T1025 modules. Each cable consists of two 30-pin female connectors and an interconnecting ribbon cable arranged in a ground-signal-ground-fashion. The cables are mated to cable connectors located on the VAXBI card cage corresponding to Zone C of the modules. The short cable completes the innermost electrical connection while the longer cable completes the outermost electrical connection between the two modules.

#### The CI Bulkhead Connector Panel

The CIBCA is connected internally from the VAXBI backplane to the CI bulkhead connector panel via two pairs of coaxial cables. The CI bulkhead connector panel provides the electrical isolation for the system by creating an EMI/RFI shield without compromising signal integrity. The panel is mounted in the cable connector openings located on the rear inside I/O panels of the cabinet. Two pairs of double-shielded coaxial cables connect the CI paths of the node from the CI bulkhead connector panel to the star coupler. One cable of each pair is for transmitting data, the other for receiving data.

#### **1.5 REFERENCE DOCUMENTS**

| Title                                | <b>Document Number</b> |

|--------------------------------------|------------------------|

| CIBCA Maintenance Print Set          | MP-01836-01            |

| CIBCA Hardware Technical Description | EK-CIBCA-TD            |

| SC008 Star Coupler User's Guide      | EK-SC008-UG            |

|                                      |                        |

DIGITAL personnel may order hardware documents from:

Digital Equipment Corporation 10 Forbes Road Northboro, MA 01532-2597

Attn: Printing and Circulation Services (NRO3/W3) Order Processing Section

Customers may order hardware documents from:

Digital Equipment Corporation Peripherals and Supplies Group Cotton Road Nashua, NH 03063-1260

## CHAPTER 2 SITE PREPARATION AND INSTALLATION

#### 2.1 INTRODUCTION

This chapter contains information on site preparation and installation, including:

**Operating Environment** – Verifying that the CIBCA option meets all of the minimum physical, environmental, and grounding specifications.

System Configurations - Configuring the CIBCA option to various VAX systems with a VAXBI installed.

Unpacking and Inventory – Unpacking and verifying that the shipment is complete and undamaged.

Installation and Configuration – Installing the modules, intermodule cables, and internal CI bulkhead cable assembly; and configuring the node address of the CIBCA adapter option and other jumper selectable parameters.

#### 2.2 OPERATING ENVIRONMENT

#### 2.2.1 Physical Elements

The CIBCA option requires two adjacent VAXBI slots.

There must be two available 5.1 cm  $\times$  10.2 cm (2 in  $\times$  4 in) or one 10.2 cm  $\times$  10.2 cm (4 in  $\times$  4 in) I/O connector panel opening(s) in the cabinet for the CI bulkhead cable connector panel.

#### 2.2.2 System Environment and Grounding Elements

Consult the applicable system installation manual for information regarding system environment and grounding requirements.

#### 2.3 SYSTEM CONFIGURATIONS

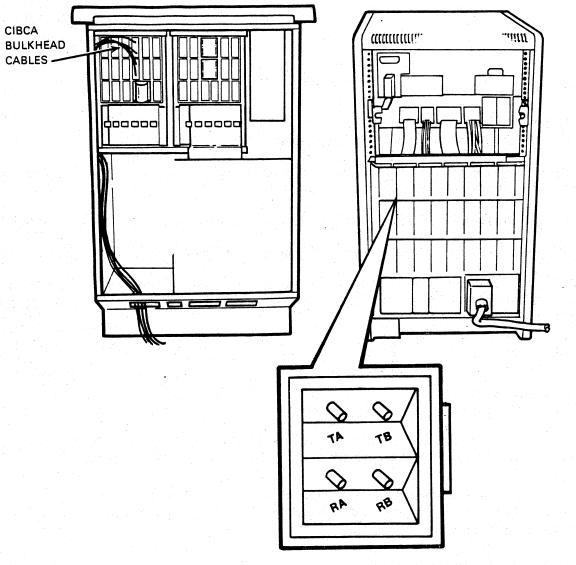

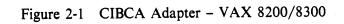

Refer to Figures 2-1, 2-2, and 2-3.

#### NOTE

Ensure that the CIBCA hardware and microcode revision level is consistent with the revision level of the cluster and vice versa. Consult the VAXcluster System Revision Document for more information.

MKV87-1041

MKV87-1042

Figure 2-2 CIBCA Adapter - VAX 8500

| FRONT END CABINET<br>(H9652)                   | CPU CABINET (H9650)                                                                              | EXPAN<br>(H965)<br>(OPTIC | 2)         | EXPANSION CABINET<br>(H9652)<br>(OPTIONAL) |

|------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|------------|--------------------------------------------|

| EXPANDER<br>BOX                                | BLOWER ASSEMBLY<br>ARRAY<br>ARRAY<br>ARRAY<br>CPU<br>LLEFT<br>CPU<br>RIGHT<br>VAXBI 1<br>VAXBI 1 | O IBXEA                   | PANDER BOX | EXPANDER BOX                               |

| 50 HZ<br>TRANSFORMER<br>(OPTIONAL)<br>AC INPUT | NBOX                                                                                             |                           |            |                                            |

Figure 2-3 CIBCA Adapter - VAX 8800

MKV87-1043

#### 2.4 UNPACKING AND INVENTORY

The customer is responsible for the actual movement of the equipment to the installation site.

For all VAXBI systems, ensure that all equipment for the CIBCA option is moved to the designated installation site.

#### **Verifying Shipment Inventory**

#### PROCEDURE

- 1. Inventory all equipment against the shipping list accompanying the equipment.

- 2. Notify the customer of any opened cartons or boxes and document this fact on the installation report.

- 3. Notify the Field Service unit manager of any missing or incorrect items.

- 4. Request that the customer contact the shipping carrier to locate any missing items.

- 5. Request that the Field Service unit manager check with the Digital Equipment Corporation Traffic and Shipping Department if the shipping carrier does not have the missing items.

- 6. Check all boxes for external damage (dents, holes, or crushed corners).

- 7. Notify the customer of all damage and list all damage on the installation report.

#### **Unpacking the Shipping Boxes**

#### PROCEDURE

- 1. Locate and open the box marked "OPEN ME FIRST". It contains the shipping/accessory list.

- 2. Open all remaining boxes and inventory the contents against the shipping/accessory list.

- 3. Inspect the equipment for damage. Report any damage and note it on the installation report.

- 4. If damage is extensive, notify Digital Equipment Corporation for instructions on how to proceed.

2-5

#### 2.5 CIBCA INSTALLATION AND CONFIGURATION

#### 2.5.1 T1015 and T1025 Module Installation

#### CAUTION

Use an antistatic wrist ground strap (Velostat<sup>™</sup> Kit, P/N 29-11762-00) while working on a VAXBI system with its covers removed or when handling any VAXBI module. Do not remove any module from its antistatic packaging until you are ready to install it.

Before installation of the CIBCA, perform the following steps.

1. For CIBCA add-ons, the CIBCA.BIN microcode must be resident on the system console boot device. Before shutting the system down, copy CIBCA.BIN from the appropriate media (supplied with the CIBCA) to the console boot device. Contents of the supplied media are listed below.

#### VAX CIBCA MICROCODE UPDATE FLOPPY

This floppy contains the latest version of the microcode file, CIBCA.BIN. It has the EEPROM Programming and Update utility (EVGDA) which is used to update the CIBCA EEPROM. This floppy is also used to place and/or update the CIBCA microcode on the system console boot device.

**Floppy Directory**

Description

EVGDA.EXE EVGDA.HLP CIBCA.BIN VMB.EXE CIBCA EEPROM PROGRAM UTILITY HELP FILE FOR EVGDA CIBCA MICROCODE FILE VAX PRIMARY BOOT FILE (with CIBCA patch until VMS V4.6 is released)

- 2. Turn OFF power to the system.

- 3. Ground yourself.

- 4. Expose the VAXBI card cage.

#### NOTE

Proceed directly to Section 2.5.2 if the CI bulkhead cable assembly is installed and the VAXBI card cage contains the T1015 module, T1025 module, and the CIBCA intermodule cables.

Velostat is a trademark of the Minnesota Mining and Manufacturing Co.

#### PROCEDURE

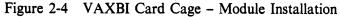

1. Carefully insert the T1015 and T1025 modules into any two unoccupied but adjacent module slots within the same VAXBI card cage (see Figure 2-4). The T1015 is inserted in the lower numbered slot. If the present system cable configuration interferes with the installation of the CIBCA, cables, and jumpers, then the T1015 and T1025 module slot positions (including jumpers and cables) can be interchanged, however, this is *not* recommended.

- 2. If necessary, install the two transition connector assemblies, DEC P/N 12-22246-01, onto the VAXBI backplane on the slots containing the T1015 and T1025 modules. Using the torque screwdriver supplied in the VAXBI tool kit, DEC P/N 29-25608-00, torque the transition connector assemblies to 5 in/lbs ±1 in/lbs.

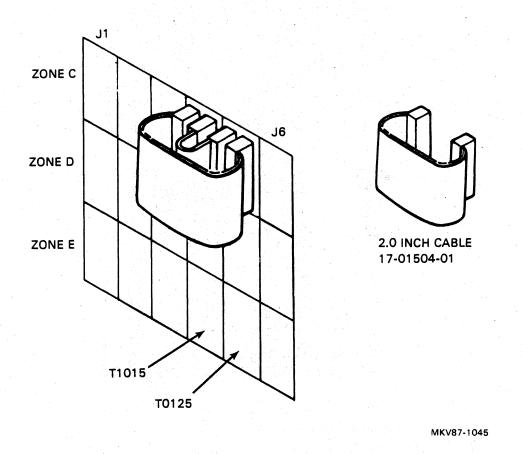

- 3. Refer to Figure 2-5 while carefully connecting the CIBCA intermodule cables to the VAXBI card cage connectors as follows:

Attach a 0.7 inch cable at Zone C between the innermost connectors of the T1015 and T1025 modules.

Form the 2.0 inch cable as shown and attach at Zone C between the outermost connectors of the T1015 and T1025 modules.

Figure 2-5, VAXBI Backplane - CIBCA Intermodule Cable Connections

- 4. Refer to Figure 2-6 while carefully connecting the internal CI bulkhead cables.

- 5. Route the internal CI bulkhead cables and install the I/O bulkhead panel.

- 6. Install the RECEIVE dummy connector in Zone E of the slot containing the T1025 (solder side). Install the TRANSMIT dummy connector in Zone D of the slot containing the T1025 (solder side).

- 7. Install the RECEIVE cable connector into the transition header in Zone E of the slot containing the T1025 (component side). Install the TRANSMIT cable connector into the transition header in Zone D of the slot containing the T1025 (component side). Cables must exit toward Zone E. Use tie-wraps to secure cables.

MKV87-1046

Figure 2-6 CIBCA CI Internal Bulkhead Cable Assembly Installation

#### 2.5.2 VAXBI Backplane Jumper Verification

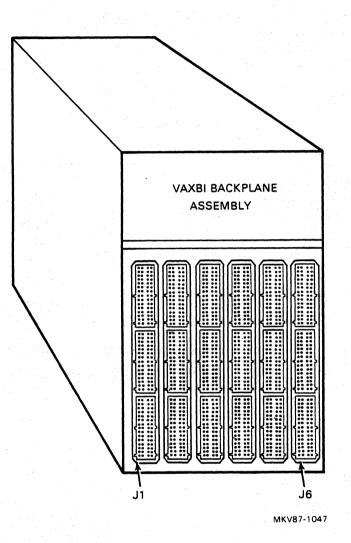

Several jumpers and a VAXBI node ID encapsulated plug are used on the user section of the VAXBI backplane to control certain operating parameters for the CIBCA. These jumpers are configured at the factory for normal operation when the CIBCA is shipped installed in the system. The configuration settings of the CIBCA backplane jumpers must match the parameters selected in the other VAXcluster nodes. Figure 2-7 illustrates a VAXBI backplane assembly.

Figure 2-7 VAXBI Stationary Backplane

#### 2.5.3 VAXBI Node ID Plug

An encapsulated plug on the VAXBI backplane (on the T1015 module slot) provides an encoded 4-bit binary identification number. The decimal equivalent identification number or VAXBI NODE ID is printed on the plug.

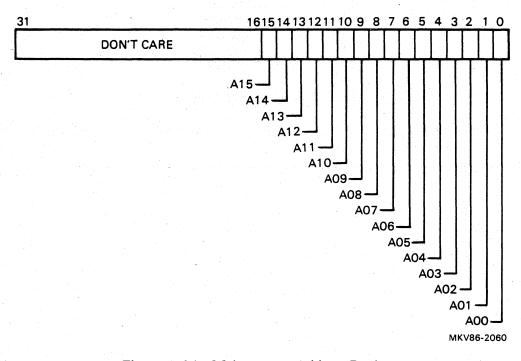

#### 2.5.4 CI Node Address Jumpers

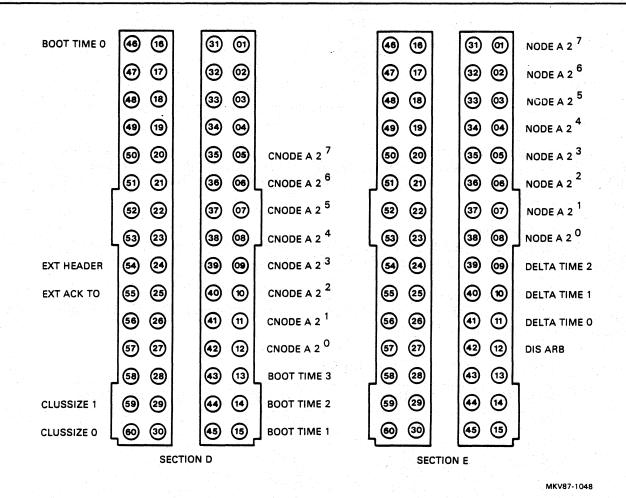

The CI node address is obtained from the T1015 backplane slot. The CI node address and its complement must be configured exactly the same. Table 2-1 lists the way the CI node address jumpers should be configured for a respective address. See Figure 2-8 for a detailed view of CIBCA jumper backplane pinning.

| Table 2-1 | CI | Node | Address | Jumpers |

|-----------|----|------|---------|---------|

|           |    |      |         |         |

| D5-D35<br>E1-E31            | D6-D36<br>E2-E32          | D7-D37<br>E3-E33                      | D8-D38<br>E4-E44                      | D9-D39<br>E5-E35                      | D10-D40<br>E6-E36           | D11-D41<br>E7-E37         | D12-D42<br>E8-E38         | CI NODE<br>ADDRESS<br>DECIMAL |

|-----------------------------|---------------------------|---------------------------------------|---------------------------------------|---------------------------------------|-----------------------------|---------------------------|---------------------------|-------------------------------|

| <b>&lt;2</b> <sup>7</sup> > | < <b>2</b> <sup>6</sup> > | <b>&lt;2</b> <sup>5</sup> <b>&gt;</b> | <b>&lt;2</b> <sup>4</sup> <b>&gt;</b> | <b>&lt;2</b> <sup>3</sup> <b>&gt;</b> | <b>&lt;2</b> <sup>2</sup> > | < <b>2</b> <sup>1</sup> > | < <b>2</b> <sup>0</sup> > | DECRIME                       |

| OUT                         | OUT                       | OUT                                   | OUT                                   | OUT                                   | OUT                         | OUT                       | OUT                       | 0                             |

| OUT                         | OUT                       | OUT                                   | OUT                                   | OUT                                   | OUT                         | OUT                       | IN                        | 1                             |

| OUT                         | OUT                       | OUT                                   | OUT                                   | OUT                                   | OUT                         | IN                        | OUT                       | 2                             |

|                             |                           |                                       |                                       | •                                     |                             |                           |                           |                               |

| IN                          | IN                        | OUT                                   | IN                                    | IN                                    | IN                          | IN                        | OUT                       | 222                           |

| IN                          | IN                        | OUT                                   | IN                                    | IN                                    | IN                          | IN                        | IN                        | 223                           |

| IN                          | IN                        | IN                                    | OUT                                   | OUT                                   | OUT                         | OUT                       | OUT                       | 224                           |

NOTE:

Addresses above 223 decimal are illegal.

Figure 2-8 CIBCA Backplane Jumper Pinning

#### **2.5.5** Boot Time Jumpers

Boot time is the length of time the CIBCA adapter waits after power up before exiting the CI UNINIT state. Table 2-2 identifies jumper positions to select the desired boot time.

| D13-D43 | D14-D44 | D15-D45 | D16-D46 | Time in Seconds |

|---------|---------|---------|---------|-----------------|

| OUT     | OUT     | OUT     | OUT     | 1500 (Default)  |

| OUT     | OUT     | OUT     | IN      | 1400            |

| OUT     | OUT     | IN      | IN      | 1300            |

| OUT     | OUT     | IN      | OUT     | 1200            |

| OUT     | IN      | OUT     | OUT     | 1100            |

| OUT     | IN      | OUT     | IN      | 1000            |

| OUT     | IN      | IN      | OUT     | 0900            |

| OUT     | IN      | IN      | IN      | 0800            |

| IN      | OUT     | OUT     | OUT     | 0700            |

| IN      | OUT     | OUT     | IN      | 0600            |

| IN      | OUT     | IN      | OUT     | 0500            |

| IN      | OUT     | IN      | IN      | 0400            |

| IN      | IN      | OUT     | OUT     | 0300            |

| IN      | IN      | OUT     | IN      | 0200            |

| IN      | IN      | IN      | OUT     | 0100            |

| IN      | IN      | IN      | IN      | 0000            |

Table 2-2Boot Time Jumpers

#### 2.5.6 Disable Arbitration Jumpers

Jumper E12-E42 is the Disable Arbitration jumper. When inserted, this jumper defeats the normal arbitration sequence and allows the T1025 to transmit after waiting only one basic quiet slot (Delta) time. This jumper is normally out.

#### 2.5.7 Extend Header Jumper

Jumper D24-D54 is the Extend Header jumper. When inserted, this jumper allows the T1025 to extend the number of bit synchronous characters in the header. This jumper is normally out.

#### 2.5.8 Alter Delta Time Jumpers

These jumpers force the T1025 to increase the basic CI quiet slot Delta time. Table 2-3 identifies jumper insertion to select the desired Delta time.

| E10-E40 | E11-E41                                    | Quiet Slot Count                         |

|---------|--------------------------------------------|------------------------------------------|

| OUT     | OUT                                        | 7                                        |

| OUT     | IN                                         | 10                                       |

| IN      | OUT                                        | 14                                       |

| IN      | IN                                         | 16                                       |

| OUT     | OUT                                        | 21                                       |

| OUT     | IN                                         | 25                                       |

| IN      | OUT                                        | 32                                       |

| IN      | IN                                         | Illegal                                  |

|         | OUT<br>OUT<br>IN<br>IN<br>OUT<br>OUT<br>IN | OUTOUTOUTININOUTININOUTOUTOUTININININOUT |

| Table | 2-3 | Alter | Delta | Time | Jumpers |

|-------|-----|-------|-------|------|---------|

|       |     |       |       |      |         |

#### 2.5.9 Node Count Jumpers

These jumpers force the CI arbitration logic to arbitrate for more than 16 nodes. Table 2-4 identifies the jumper insertions to select the node count.

| D29-D59 | D30-D60 | Node C<br>(In Dec |  |

|---------|---------|-------------------|--|

| OUT     | OUT     | 16                |  |

| OUT     | IN      | 32                |  |

| IN      | OUT     | 64                |  |

| IN      | IN      | 128               |  |

Table 2-4

Node Count Jumpers

### 2.5.10 Extend ACK Timeout Jumper

Jumper D25-D55 is the Extend ACK Timeout jumper. When installed, this jumper forces the T1025 to increase the timeout period for a CI ACK return. This jumper is normally out.

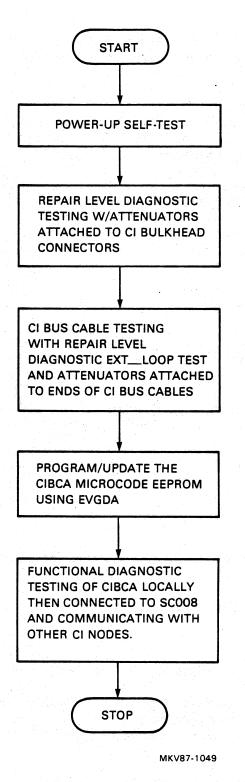

## CHAPTER 3 ACCEPTANCE VERIFICATION

#### 3.1 INTRODUCTION

**Diagnostic** Verification – Verifying the CIBCA hardware operation by running diagnostic tests with the system in a standalone environment.

Maintenance Verification – Facilitating VAXcluster maintenance by describing the tools that are required and/or provided for individual nodes or options within a VAXcluster system.

#### **3.2 POWER-ON PROCEDURE**

Refer to the appropriate system user guide for power-on procedures.

#### **3.3 DIAGNOSTIC VERIFICATION**

To determine if the CIBCA adapter hardware is functioning properly, seven Level 3 diagnostic programs must be executed. These diagnostic programs and their applicable diagnostic supervisor program, are contained on separate RX50 floppy diskettes.

Five of the seven Level 3 diagnostic programs are executed with the system operating in a standalone environment (*not* connected to a VAXcluster and *not* running under the VMS operating system).

Two of the seven Level 3 diagnostic programs are then executed with the system operating in a standalone environment (*not* running under the VMS operating system) but connected to the coupler in order to verify the functional CIBCA hardware operation within the system. This is referred to as functional level testing.

Table 3-1 lists the CIBCA diagnostic programs. Table 3-2 provides a summary of the CIBCA diagnostic testing hierarchy. Figure 3-1 describes the CIBCA acceptance testing flow.

| Program<br>Designation | Program<br>Title                            |

|------------------------|---------------------------------------------|

| EVGCA                  | CIBCA T1015 Repair Level Diagnostic 1       |

| EVGCB                  | CIBCA T1015 Repair Level Diagnostic 2       |

| EVGCC                  | CIBCA T1015 Repair Level Diagnostic 3       |

| EVGCD                  | CIBCA T1015 Repair Level Diagnostic 4       |

| EVGCE                  | CIBCA T1025 Repair Level Diagnostic 1       |

| EVGCK                  | CIBCA Repair Level Microcode 1              |

| EVGCL                  | CIBCA Repair Level Microcode 2              |

| EVGCM                  | CIBCA Repair Level Microcode 3              |

| EVGCN                  | CIBCA Repair Level Microcode 4              |

| EVGDA                  | CIBCA EEPROM Programming and Update Utility |

| EVGAA                  | CI Functional Diagnostic 1                  |

| EVGAB                  | CI Functional Diagnostic 2                  |

| EVXCI                  | CI Exerciser Diagnostic                     |

Table 3-1

List of CIBCA Diagnostic Programs

| Diagnostic<br>Category | Diagnostic<br>Program Level | Testing Function                                              |

|------------------------|-----------------------------|---------------------------------------------------------------|

| Repair                 | 3                           | Tests the detailed hardware operation of the CIBCA adapter.   |

| Functional             | 3                           | Tests the functional hardware operation of the CIBCA adapter. |

| Exerciser              | 2R                          | Tests the communications between CI nodes.                    |

|                        |                             | Detects a failing CI node.                                    |

|                        |                             | Verifies repair of a failing CI node.                         |

Table 3-2 CIBCA Diagnostic Testing Hierarchy

Figure 3-1 CIBCA Acceptance Testing Flow Diagram

#### 3.3.1 Preliminary Setup

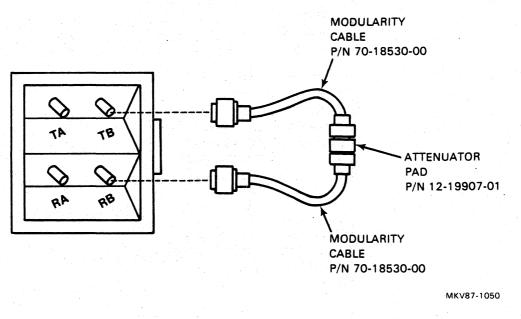

Before running the diagnostics, make the following CI bus loopback connections on the CI bulkhead connector panel located at the back of the cabinet (see Figure 3-2).

#### PROCEDURE

- 1. Using one of the attenuator pads (P/N 12-19907-01) and two of the modularity cables (P/N 70-18530-00) supplied in the CIBCA Controlled Distribution (CD) kit, DEC P/N A2-W1207-10, connect TRANSMIT A to RECEIVE A.

- 2. Perform the same connection for path B using the other attenuator pad and two modularity cables from the CIBCA CD kit. Connect TRANSMIT B to RECEIVE B.

Figure 3-2 Diagnostic Loopback Cable Connections

#### 3.3.2 Loading the Diagnostic Supervisor Program

#### PROCEDURE

- 1. Insert the proper RX50 diskette into the console RX50 disk drive unit 0.

- 2. Load the diagnostic supervisor program into physical memory from the console load device. This procedure may vary depending on the system type in which the CIBCA is installed. Consult the applicable system installation manual for diagnostic supervisor load and run procedures.

The following are examples to load the diagnostic supervisor.

#### VAX 8800 SYSTEMS

>>>@DIABOO (boots the diagnostic supervisor from the VAX console fixed disk)

#### VAX 8200 SYSTEMS

Insert the diagnostic supervisor diskette into the left RX50 drive, then

>>> B CSA1 (boots the diagnostic supervisor from the console load device).

3. Identify the CIBCA adapter and its node configuration parameters to the diagnostic supervisor program. The ATTACH/SELECT sequence will once again vary depending upon the system type in which the CIBCA is installed. It is assumed that the installer is familiar with the diagnostic supervisor ATTACH and SELECT sequences for VAXBI devices on the processor being used. Below are examples for attaching the CIBCA hardware in VAX 8800 and VAX 8200 series system environments.

#### CIBCA ON A VAX 8800

- a. All ATTACHes specifying BI NODE numbers should be documented to show that node numbers are to be in hexadecimal.

- b. BI nodes instead of being attached to HUB should be attached to NBIBn, that is, the following sequence should be added:

ATTACH NBIA HUB NBIAn LOGICAL ADAPTER # ? N

ATTACH NBIB NBIAn Device Name? NBIBn BI # ? n BI Node Number (HEX) ? n

ATTACH Device name? CIBCA Device link? NBIBn Device? PAAn BI Node (DEC) ? n BR Level? 4 CI address (DEC) ? n

For example:

ATTACH NBIA HUB NBIA0 0 ATTACH NBIB NBIA0 NBIB0 1 0 ATTACH CIBCA NBIB0 PAA0 2 4 0

SELECT PAA0

#### CIBCA ON A VAX 8200

ATTACH Device name? CIBCA Device link? HUB Device? PAAn BI Node (DEC) ? n BR Level? n CI address (DEC) ? n ! where n 0 or 1 ! 0 or 1

! where n 0 to 3 ! 0 or 1 ! n 0 to F

! Then attach UUT ! Device to test

! Specify the CI ! BI node # ! BR level 4 ! 0 - 16

! logical unit 0

! BI #1, BI node 0

! BI node 2, BR level 4

! CI node 0

! device to be run

! Then attach UUT ! Device to test

! Specify the CI

! BI node #

! BR level #

! 0 - 16

4. Select the CIBCA adapter as the unit under test, as follows:

DS> SELECT PAA0

5. Show the unit selected, as follows:

DS> SHOW SELECT

#### 3.3.3 Repair Level Testing

A minimum of five successful passes of each diagnostic program must be completed to satisfy acceptance testing requirements. Examples 3-1 through 3-5 provide trace printouts for diagnostics EVGCA through EVGCE, respectively.

#### NOTE

HELP files are available under the diagnostic supervisor for all the diagnostic programs including the supervisor program itself.

#### PROCEDURE

- 1. While proceeding through the diagnostic acceptance testing, ensure that the diagnostics are accessible via the DEFAULT LOAD PATH. This may require changing diagnostic media in the current load path device.

- 2. Load the EVGCA diagnostic program, as follows:

DS> LOAD EVGCA (first repair level diagnostic)

3. Set the desired diagnostic supervisor control flags to enable printing of the number and title of each test before it is executed and to halt on a detected error.

DS> SET FLAGS TRACE, HALT

4. Start the diagnostic program.

DS> START/PASS:5

5. Repeat Steps 1 through 4 to load and execute the remaining repair level diagnostics (EVGCB through EVGCE). Substitute the target filename in Step 2.

DS> ATTACH CIBCA HUB PAAO 12 4 O DS> SEL PAAO DS> SET TRACE, HALT DS> LOAD EVGCA DS> START

.. Program: EVGCA - T1015 CIBCA Repair Level Diagnostic Part 1, Revision 1.0, 13 tests, at 11:45:34.75. Testing: PAAO

Device Type/BIIC Configuration Register Test Test 1: Test 2: BI Control and Status Register Test Test 3: BCA BI Required Register Test Test 4: BCA General Purpose Device Register Test Test 5: BCA User CSR Space Register Test Test 6: Port Status Register Test Test 7: BCA Specific Register Test Local Store/VCDT Address Read/Write Test Test 8: Test 9: Local Store/VCDT Data Read/Write Test Test 10: Local Store/VCDT Dynamic Memory Test Test 11: Control Store Address Test Test 12: Control Store Read/Write Ram Test Test 13: Control Store Ram Dynamic Memory Test .. End of run, O errors detected, pass count is 1, time is 24-0CT-1986 11:47:09.98

Example 3-1 Trace Printout for Repair Level Diagnostic EVGCA

DS> LOAD EVGCB DS> START

.. Program: EVGCB - T1015 CIBCA Repair Level Diagnostic Part 2, Revision 1.0, 17 tests, at 11:49:36.98. Testing: PAAO **EEPROM** Integrity Verification Test Test 1: Internal Bus Branch/Sequencer Jump Test Test 2: Microprogram Controller UPC+1 Test Test 3: Test 4: Microprogram Controller JSB/RSB Test Microprogram Controller Pop Micro Stack Test Test 5: Test 6: Single Operand Instruction Test Test 7: Two Operand Instruction Test Single Bit Shift Instruction Test Test 8: Rotate By n Bit Instruction Test Test 9: Test 10: Set RAM Bit n Instruction Test Test 11: Set Ram MINUM Bit n Instruction Test Test 12: Set ACC Minus Bit n Instruction Test Test 13: Set DLATCH Bit n Instruction Test Test 14: Reset RAM Bit n Instruction Test Test 15: Reset ACC Bit n Instruction Test Test 16: Reset DLATCH Bit n Instruction Test Test 17: Test RAM Bit n Instruction Test .. End of run, O errors detected, pass count is 1, time is 24-0CT-1986 11:50:00.02

Example 3-2 Trace Printout for Repair Level Diagnostic EVGCB

DS> LOAD EVGCC DS> START

.. Program: EVGCC - T1015 CIBCA Repair Level Diagnostic Part 3, Revision 1.0, 18 tests, at 11:50:13.17. Testing: PAAO Test ACC Bit n Instruction Test Test 1: Test 2: Test DLATCH Bit n Instruction Test Test 3: Load RAM Bit n Instruction Test Load RAM NOT Bit n Instruction Test Test 4: Test 5: Load ACC Bit n Instruction Test Test 6: Load ACC NOT Bit n Instruction Test Test 7: Load YBUS Bit n Instruction Test Test 8: Load YBUS NOT Bit n Instruction Test Test 9: Add RAM Bit n Instruction Test Test 10: Add ACC Bit n Instruction Test Test 11: Add DLATCH Bit n Instruction Test Test 12: Rotate and Merge by n Instruction Test Test 13: Rotate and Compare by n Instruction Test Test 14: Prioritize Instruction Test Test 15: CRC Instruction Test Test 16: No Operation Instruction Test Test 17: AMD29116 Internal Register Address Test Test 18: Local Store/VCDT Microcode Access Test . End of run, O errors detected, pass count is 1, time is 24-0CT-1986 11:50:59.24

Example 3-3 Trace Printout for Repair Level Diagnostic EVGCC

DS> LOAD EVGCD DS> START .. Program: EVGCD - T1015 CIBCA Repair Level Diagnostic Part 4, Revision 1.0, 23 tests, at 11:45:34.75. Testing: PAAO Test 1: Register Dual Address Test Test 2: Local Store/Virtual Circuit Descriptor Table Parity Error Test Test 3: Interrupt Test Test 4: MTE During Interrupt Test Test 5: Microword Verification Test Test 6: Control Store Parity Error (CSPE) Test Test 7: Condition Code Branch MUX Test Test 8: Maintenance Timer Disable Branch Test Test 9: Tick Branch Test Test 10: IB Register Read/Write Loopback Test Test 11: BCAI Register Test Test 12: Register Written Test Test 13: BI Master Write/Read Test Test 14: Power Fail Test with Power Fail Disable Set Test Test 15: CBOR/CBIR Port Initiated Loopback Test Test 16: Command Address/Byte Count Register Test 17: Datamover Loopback Test Test 18: Datamover Read/Write to Host Memory Test Test 19: Page Overflow Test Test 20: Write/Stop Command Test Test 21: BI Slave Transaction Test Test 22: Suspend and Release II Bus Test Test 23: Suspend and Release CILP Bus Test . End of run, O errors detected, pass count is 1, time is 24-0CT-1986 11:50:25.08

Example 3-4 Trace Printout for Repair Level Diagnostic EVGCD

DS> LOAD EVGCE DS> START .. Program: EVGCE - CIBCA T1025 Repair Level Diagnostic Revision 1.0, 15 tests, at 11:51:52.34. Testing: PAAO Test 1: Link Configuration & CILP Bus Integrity Test Contents of CONFIGURATION Register O True Node Address : OE Cluster Size : 00 Extended ACK : 00 Extended Header : 00 Disable ARB : 00 : 01 Delta Time Contents of CONFIGURATION Register 1 Complement Node Address : F1 Boot Time : 0 F Test 2: Packet Buffer Data Integrity Test Test 3: Transmit with External/Internal Loopback Set Test Test 4: Transmit with Internal Loopback Set Test Test 5: Transmit with External Loopback Set Test Test 6: Force Transmit Parity Error in Internal Loopback Test Test 7: Invalid Complement Destination Node Number Test Test 8: True/Complement Destination Node Number Swap Test Test 9: Bad CRC Test Test 10: Negative (NAK) Acknowledgement Test Test 11: Transmit Abort Test Test 12: Extended Link Configuration Test Test 13: Valid CI Node Number Test, All Combinations Test 14: Internal Interaction Test Test 15: Arbitration Time Test .. End of run, O errors detected, pass count is 1, time is 24-0CT-1986 11:57:21.16

Example 3-5 Trace Printout for Repair Level Diagnostic EVGCE

#### 3.3.4 CI Bus Cable Testing

After successfully completing five passes of each of the five repair level diagnostics, remove the attenuator pads and modularity cables from the CI bulkhead connectors (J21-J24) and perform the following steps.

### PROCEDURE

- 1. Verify that this CIBCA port has a unique node address within the VAXcluster before connecting any cables.

- 2. Locate the set of four CI bus coaxial cables (BNCIA-XX). Label each end of the CI bus coaxial cables with the CI node and CI path information using the labels provided with the BNCIA-XX cables. Connect one end of each cable to the appropriate CI bulkhead connector.

#### NOTE

#### The coaxial CI bus cables may be connected to or removed from the CI bulkhead connectors without powering down the system. DO NOT unroll or route the CI bus cables at this time.

- 3. Connect the two attenuator pads to the free ends of the coaxial CI bus cables. Be sure to connect TRANSMIT A to RECEIVE A, and TRANSMIT B to RECEIVE B.

- 4. Run five passes of the EXTERNAL\_LOOP section of the diagnostic program EVGCE to test the CI bus cables.

DS> RUN EVGCE/SEC:EXTERNAL\_LOOP/PASS:5

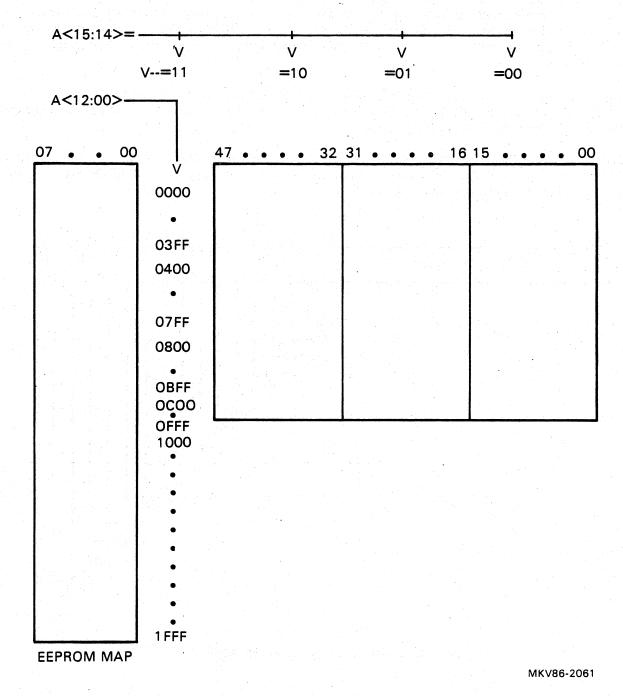

#### 3.3.5 CIBCA EEPROM Programming and Update Utility

#### PROCEDURE

1. Insert the RX50 floppy containing EVGDA and the CIBCA microcode file CIBCA.BIN into the console floppy drive being used as the diagnostic load path.

By default, tests 3 through 5 are run. Tests 1, 2, 6, and 7 are special purpose tests; these are not normally executed in the field.

2. Load the EVGDA diagnostic program as follows:

DS> LOAD EVGDA

3. Start the diagnostic program.

DS> START

Example 3-6 shows a trace printout when running the (default) update section .

.. Program: EVGDA - CIBCA EEPROM Programming and Update Utility, Revision 1.1, 7 tests, at 10:32:34.78. Testing: PAAO

Summary of EEPROM data from File Header The EEPROM Version Number is: 0001 The EEPROM CRC Value is: 5012E01c The EEPROM Starting Logical Block Number is: 1 The EEPROM Microcode Size, in Bytes, is: 8190

Summary of Functional data from File Header The Functional Version number is: 0001 The Functional CRC Value is: 5B9D6A8F The Functional Starting Logical Block Number is: 17 The Functional Microcode Size, in 16-Bit Words, is: 12288

Test 3: Update the EEPROM Microcode Started Update of the EEPROM at 29-0CT-1986 10:32:46.05

CURRENT value of EEPROM Update Counter is : 4

NEW value of EEPROM Update Counter is : 5 Finished with Update of the EEPROM at 29-0CT-1986 10:34:09.39

Test 4: Verify the Contents of EEPROM Started Verification of the EEPROM at 29-0CT-1986 10:34:10.29 Finished with Verification of the EEPROM at 29-0CT-1986 10:34:10.98

Test 5: Execute and Check Selftest Status Started Selftest Execution at 29-0CT-1986 10:34:11.99 Finished Selftest Execution at 29-0CT-1986 10:34:11.99

.. End of run, O errors detected, pass count is 1, time is 29-0CT-1986 10:34:13.24

Example 3-6 Trace Printout for Repair Level Diagnostic EVGDA

#### 3.3.6 Functional Level Testing

With the CI bus cables and attenuator pads providing signal loopback, load and run the CI functional diagnostics EVGAA and EVGAB. A minimum of five passes of each diagnostic must be completed to satisfy acceptance testing requirements. Examples 3-7 and 3-8 show trace printouts for diagnostics EVGAA and EVGAB, respectively.

#### PROCEDURE

- 1. While proceeding through the diagnostic acceptance testing, ensure that the diagnostics are accessible via the DEFAULT LOAD PATH. This may require changing diagnostic media in the current load path device.

- 2. Load the EVGAA diagnostic program.

DS> LOAD EVGAA (first functional diagnostic)

3. Set event flag 1 to load the CIBCA.BIN microcode. This is always required after running the repair level diagnostics.

DS> SET EVENT FLAG 1

4. Set the desired diagnostic supervisor control flags to enable printing of the number and title of each test before it is executed and to halt on a detected error.

DS> SET FLAGS TRACE, HALT

5. Start the EVGAA diagnostic program

DS> START/PASS:5

6. After five successful passes of EVGAA, load and run EVGAB by typing the following.

DS> LOAD EVGAB DS> CLEAR EVENT FLAG 1 DS> START/PASS:5

- 7. Disconnect the attenuators from the ends of the CI bus cables in preparation for routing and connecting the cables to the star coupler.

- 8. Route and connect the CI bus coaxial cables to the coupler.

#### NOTE

For information and connecting of the coaxial CI bus cables to the star coupler, refer to the SC008 Star Coupler User's Guide.

9. Run EVGAA and EVGAB

```

DS> LOAD EVGAA

DS> SET EVENT FLAG 1

DS> SET FLAGS TRACE, HALT

DS> START/PASS:5

.. Program: EVGAA - CI FUNCTIONAL PART I, Revision 4.0,

17 tests, at 11:11:45.99. Testing _PAAD

Event Flag 1 SET = Load CI Microcode

Event Flag 2 SET = Print Queue Entries

Event Flag 3 SET = REQID Loop Function in Test 1

Testing Device PAAO

EEPROM Revision = 0001 Functional Revision = 0001

Test 1: Cluster Configuration

Contents of the

PORT PARAMETER REGISTER

is

PPR:EOFF0010E(X)] ;

CLUSTER SIZE=16,

IBUF LEN=OFFO(X),

MBZ=\overline{O}(X),

DISABLE ARB=O(X),

EXTENDED HEADER=O(X),

SLOT COUNT=10,

PORT NUMBER=OE(X)

Cluster

Configuration

for

Path

Α

You CANNOT Differentiate between a CI780, CI750, or a

CIBCI remotely. (PS = Path Select, TP = Transmit Path, RP

= Receive Path)

Node

Device

Hard

Soft

Port

Path

PTR

Rev. Rev.

SPP

Number

Type

Functionality

Status

_____

_____

_____

02

0007 0007

FFFFOFOO(X)

CIXXX

0K

AAA

03

HSC50

0225

4F710200(X)

0K

AAA

0 E

0001 0001

FFFF0F00(X)

0 K

CIBCA

AAA

Cluster Configuration for Path B

*******

(PS = Path Select, TP = Transmit Path, RP = Receive Path)

Node

Device

Hard

Soft

Port

Path

PTR

Number

Type

Rev.

Rev.

Functionality

S P P

Status

----

----

0007 0007

02

CIXXX

FFFF0F00(X)

0 K

BBB

03

HSC50

0225

4F710200(X)

0 K

BBB

0 E

CIBCA

0001 0001

FFFFOFOO(X)

0K

BBB

```

Example 3-7 Trace Printout for Functional Diagnostic EVGAA (Sheet 1 of 2)

```

Nodes NOT Listed do not exist on Cluster

Test 2: SETCKT with Various Masks and M Values

Test 3: SETCKT for Each Valid Port

Test 4: SETCKT for Invalid Port

Test 5: REQID Basic

Test 6: REQID With 6 Packets on DGFQ

Test 7: Datagram Discard

Test 8: Response Queue Available Interrupt

Test 9: Send Datagram

Test 10: SNDMSG With No Virtual Circuit Open

Test 11: Send Message Crossing Page Boundary

Test 12: Message Length Test

Test 13: Packet Size Violation

Test 14: Send Loopback (SNDLB)

Test 15: SNDLB Full Buffer On Path A

Test 16: SNDLB Full Buffer On Path B

Test 17: SNDLB Automatic Path Selection

... First pass done, 0 errors detected, time is 24-0CT-1986

11:12:55.07

Example 3-7 Trace Printout for Functional Diagnostic EVGAA (Sheet 2 of 2)

DS> LOAD EVGAB

DS> CLEAR EVENT FLAG 1, 2

DS> SET FLAGS TRACE, HALT

DS> START/PASS:5

.. Program: EVGAB - CI FUNCTIONAL PART II, Revision 4.0, 12 tests

at 00:00:00.00. Testing: PAAO

ROM REVISION - 0001 WCS REVISION - 0001

SEND DATA TEST, WITH OFFSET COMBINATIONS

Test 1:

REQUEST DATA TEST, WITH OFFSET COMBINATIONS

Test 2:

INVALIDATE TRANSLATION CACHE TEST

Test 3:

SNDMDAT TEST, ENABLED/MAINTENANCE STATE

Test 4:

Test 5:

SNDMDAT TEST, ENABLED STATE

Test 6:

REQMDAT TEST, ENABLED/MAINT STATE

Test 7:

REQMDAT TEST, ENABLED STATE

Test 8:

SEND RESET TEST IN ENABLED STATE

Test 9:

QUEUE CONTENTION TEST

Test 10: BUFFER READ ACCESS TEST

Test 11: BUFFER WRITE ACCESS TEST

Test 12: WRITE TO GLOBAL BUFFER TEST

... End of run, O errors detected, pass count is 1,

time is 15-JUL-1985 00:00:00.00

```

Example 3-8 Trace Printout For Functional Diagnostic EVGAB

# 3.4 REFERENCES

| Table 3-3         Summary of the Functions of VAXcluster System Maintenance and Management |

|--------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------|

| Tool         | Function                                                                                                                                                                                                                                                                                  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CI Exerciser | A Level 2R multipurpose exerciser that provides local CI interface functional testing as well as a means to determine the ability of VAXcluster nodes to reliably communicate using the CI bus.                                                                                           |

| VAXsim       | A VAX system integrity monitor utility program that monitors and filters errors<br>as they are logged by the VMS operating system. It provides the user with a<br>warning mechanism that quickly identifies an option that is either failed or has<br>degraded operationally. See Note 1. |

| SHOW Cluster | Allows the display of a large variety of utility information relevant to the configur-<br>ation and operation of the VAXcluster of which the host system is a member. See<br>Note 2.                                                                                                      |

| SET HOST/HSC | Allows a terminal on a host VMS system to effectively become an HSC50 terminal. The user may then issue any standard HSC50 commands and look at or control the HSC50 just as if it were a terminal connected directly to one of the HSC50 terminal ports. See Note 3.                     |

- 1. For more information, consult the VAX System Integrity Monitor Manual.

- 2. For more information, consult the VAX/VMS Show Cluster Utility Manual.

- 3. For more information, consult the VAX/VMS DCL Dictionary under SET HOST/HSC.

# CHAPTER 4 CIBCA TROUBLESHOOTING

### 4.1 INTRODUCTION

This chapter provides information that will help in troubleshooting a CIBCA.

### 4.2 CIBCA MICROCODE REVISIONS

The loadable binary file CIBCA.BIN revision can be checked by using the VMS DUMP utility. A dump of the file is illustrated in Example 4-1.

After successful completion of CIBCA self-test, the microcode CIBCA.BIN is loaded into the control store. Control store location bb+108C contains the revision number of the functional microcode and location bb+1090 contains the revision number of the EEPROM code.

Dump of file DISK\$BCA\_LATEST:[BCA\_LATEST.UCODE]CIBCA.BIN;2 on 5-DEC-1986 09:24:22.37 File ID (176,48192,0) End of file block 65 / Allocated 66

| Vir | tual b | Lock numbe | r 1 (000 | 0001), 5 | 12 (0200) | bytes     |          |             | EEPROM VERSION NU | MBER   |

|-----|--------|------------|----------|----------|-----------|-----------|----------|-------------|-------------------|--------|

| 00  | 000000 | 00010000   | 1FFE0000 | 00015012 | E01C3130  | 3030204E  | 49422841 | 43424943    | CIBCA.BIN 0001    | 000000 |

| 00  | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 00000000  | 00000000 | 00000000    |                   | 000020 |

| 00  | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 00000000  | 00000000 | 00000000    |                   | 000040 |

| 00  | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 00000000  | 00000000 | 00000000    |                   | 000060 |

| 00  | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 00000000  | 00000000 | 00000000    |                   | 000080 |

| 00  | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 000000000 | 00000000 | 00000000    |                   | 000040 |

| 00  | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 00000000  | 00000000 | 00000000    |                   | 000000 |

| 0.0 | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 00000000  | 00000000 | 00000000    |                   | 000050 |

| 0.0 | 000000 | 00000000   | 00000000 | 00000001 | 00003000  | 00000011  | 5890648F | 31 30 30 30 | 0001.j.C0         | 000100 |

| 00  | 000000 | 00000000   | 00000000 | 00000000 | 00000000  | 00000000  | 00000000 | 00000000    |                   | 000120 |

|     |        |            |          |          |           |           |          |             |                   |        |

----- FUNCTIONAL VERSION NUMBER

Example 4-1 CIBCA.BIN

## 4.3 CIBCA FRU LIST

See Table 1-1 for a list of the hardware FRUs used in the CIBCA.

#### 4.4 CIBCA SELF-TEST TEST DESCRIPTION

The CIBCA self-test is made up of a collection of tests. These tests, along with a brief description of what each test checks, are listed in Table 4-1.

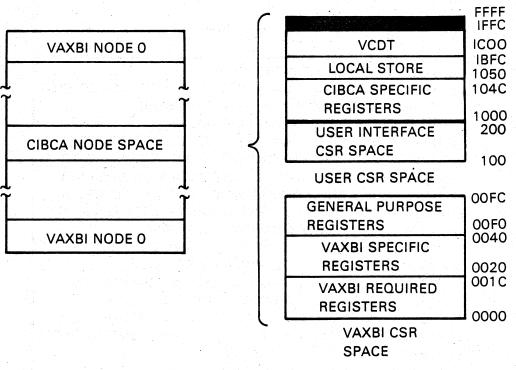

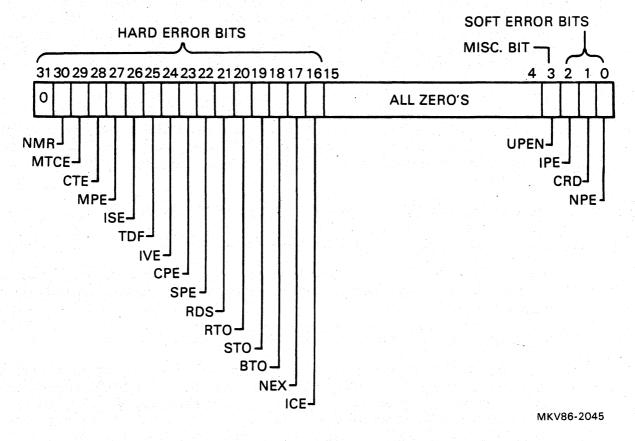

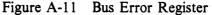

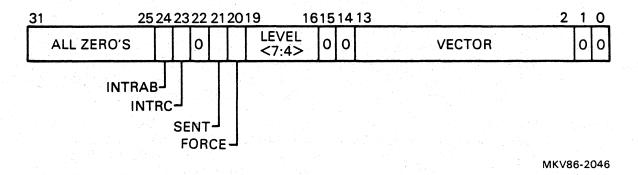

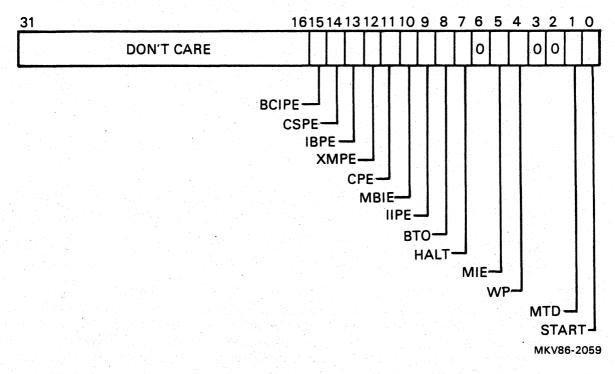

#### 4.5 CIBCA SELF-TEST TEST/FAILURE CODE REGISTER (STFCR) bb+1FFC

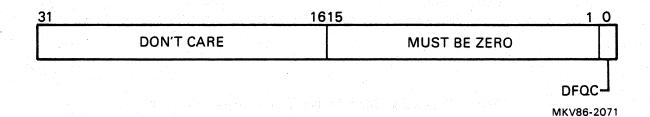

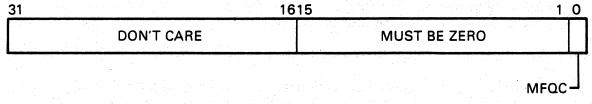

Figure 4-1 illustrates the STFCR register. At the beginning of each test, register STFCR is loaded with the test number and 0 for a failure code. If test 1 is ready to run, the STFCR is loaded with 1000 (hex). During each key failure point of the test, the failure code is incremented in case of a failure. If a failure occurs, the STFCR is written to local store location 3FF (hex) or bb+1FFC (hex) so it can be accessed from the host bus.

| Test<br>Number | Test<br>Name                                                         | Description                                                                                                                                                    |

|----------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | 29116 Status<br>Register Test                                        | Checks the Z, N, O, and C bits.                                                                                                                                |

| 2              | ALU RAM Test                                                         | Checks the 32 RAM locations.                                                                                                                                   |

| 3              | Index Register,<br>Literal Register,<br>Local Store, and<br>MUX Test | Checks the different ways to WRITE and READ the control store.                                                                                                 |

| 4              | Packet Buffer<br>WRITE/READ Test                                     | WRITEs all four packet buffers with a data pattern and then reads/checks the data.                                                                             |

| 5              | Move Data Test                                                       | Performs a loopback of data from the BCAI DMA files through the link/packet buffer module and back into the BCAI DMA files.                                    |

| 6              | (BIIC) STS Bit<br>Set Test                                           | Verifies that the BIIC self-test passed.                                                                                                                       |

| 7              | Data Mover WRITE<br>Loopback to Local<br>Store Test                  | Checks the SEL logic.                                                                                                                                          |

| 8              | WRITE/READ<br>Loopback to<br>Local Store Test                        | Checks the IB, II, BCAI, BIIC, local store, and the 29116 data and address lines.                                                                              |

| 9              | Toggle Register<br>Test                                              | Sets and clears the bits in the toggle register.                                                                                                               |

| Α              | Parity Bits Test                                                     | Checks the different PE bits in the PMCSR register.                                                                                                            |

| B              | XBUS Register<br>Test                                                | WRITEs all the XBUS registers and then checks the data by way of the index register.                                                                           |

| С              | BI WRITE/READ<br>Test                                                | Performs a self-directed WRITE/READ to the BIIC GPR<br>number 0 (defined in CIBCA as the PQBBR) to ensure that<br>the CIBCA can access itself over the BI bus. |

# Table 4-1 CIBCA Self-Test

| 15 | 14 13 12                                                                                                         | 11 10 | 98 | 76      | 5   | 4 3 | 2 1              | 0    |

|----|------------------------------------------------------------------------------------------------------------------|-------|----|---------|-----|-----|------------------|------|

| T  | TEST NUMBER                                                                                                      |       | FA | ILURE C | ODE |     |                  |      |

|    | and the second |       |    |         |     |     | a series a final | 1.11 |

MKV87-1051

# Figure 4-1 Self-Test Failure Code Register (STFCR)

**4.6 CIBCA SELF-TEST FAILURE CODES AND FRUs** The following is a look-up chart for the STFCR register. If the CIBCA self-test fails, the contents of the STFCR register, bb+1FFC, in conjunction with this chart, can be used to identify the failing FRU.

| STFCR Contents | Probable FRU Failure |

|----------------|----------------------|

| 100X           | T1015 PCM            |

| 200X           | T1015 PCM            |

| 3XXX           | T1015 PCM            |

| 400X           | T1015 PCM            |

| 5001           | T1015/T1025 PCM/CCI  |

| 5002           | T1015 PCM            |

| 5003           | T1015 PCM            |

| 5004           | T1015 PCM            |

| 5005           | T1015 PCM            |

| 5006           | T1015 PCM            |

| 5007           | T1025 CCI            |

| 5008           | T1025 CCI            |

| 5009           | T1015 PCM            |

| 500A           | T1025 CCI            |

| 500B           | T1025 CCI            |

| 500C           | T1025 CCI            |

| 500D           | T1015 PCM            |

| 500E           | T1015 PCM            |

| 500F           | T1015 PCM            |

| 501X           | T1015/T1025 PCM/CCI  |

| 5020           | T1015 PCM            |

| 5021           | T1015 PCM            |

| 5022           | T1015 PCM            |

| 5023           | T1015 PCM            |

| 5024           | T1015/T1025 PCM/CCI  |

| 5025           | T1025 CCI            |

| 5026           | T1015 PCM            |

| 5027           | T1015 PCM            |

| 5028           | T1025 CCI            |

| 5029           | T1025 CCI            |

| 502A           | T1025 CCI            |

| 502B           | T1015 PCM            |

| 502C           | T1015 PCM            |

| 502B           | T1015 PCM            |

| 502C           | T1015 PCM            |

| 502D           | T1015 PCM            |

| 502E           | T1015 PCM            |

| 502F           | T1015/T1025 PCM/CCI  |

| 503X           | T1015/T1025 PCM/CCI  |

| 600X           | T1015 PCM            |

| 700X           | T1015 PCM            |

| 800X           | T1015 PCM            |

| 90XX           | T1015 PCM            |

| A0XX           | T1015 PCM            |

| BOXX           | T1015 PCM            |

| COXX           | T1015 PCM            |

|                |                      |

# APPENDIX A CIBCA REGISTER SUMMARY

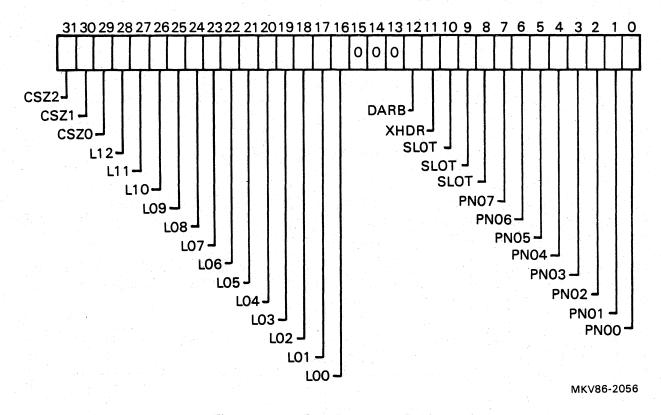

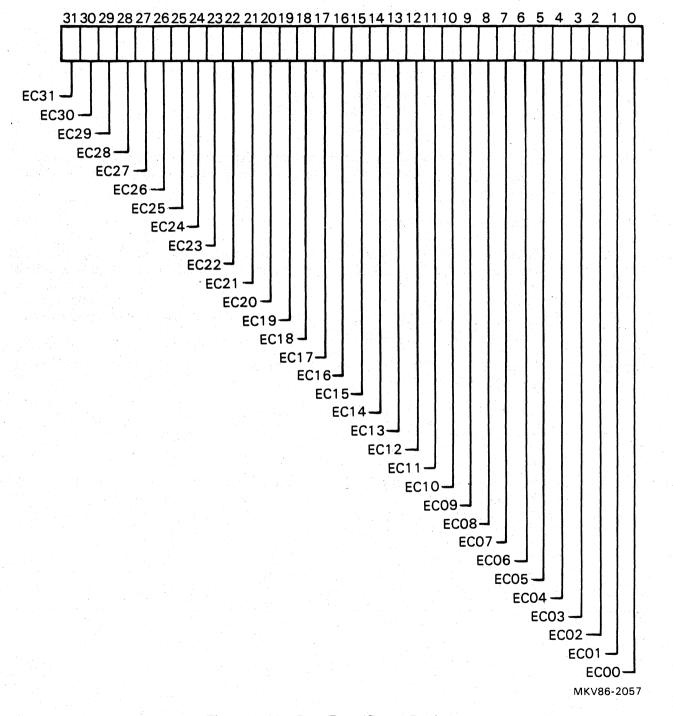

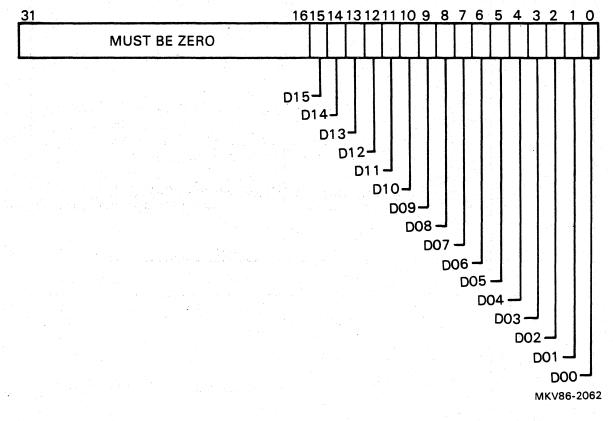

#### A.1 INTRODUCTION

This section presents the interface conventions which allow programmer access to the CIBCA adapter functions and access to the software registers that are used to control and monitor the operation within the CIBCA adapter itself. Entry to these registers is accomplished through the VAXBI address space area.

#### A.2 VAXBI PHYSICAL ADDRESS SPACE

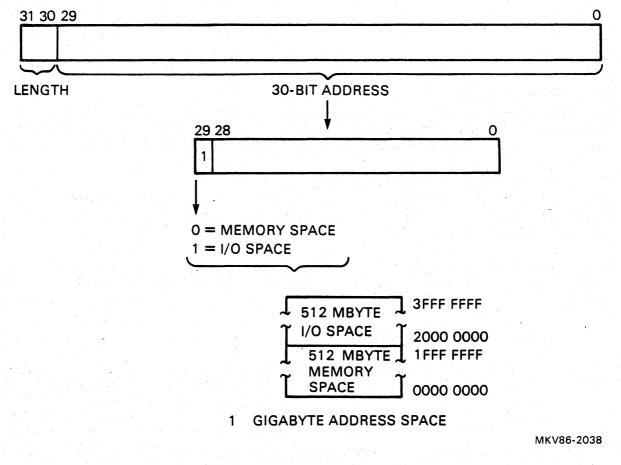

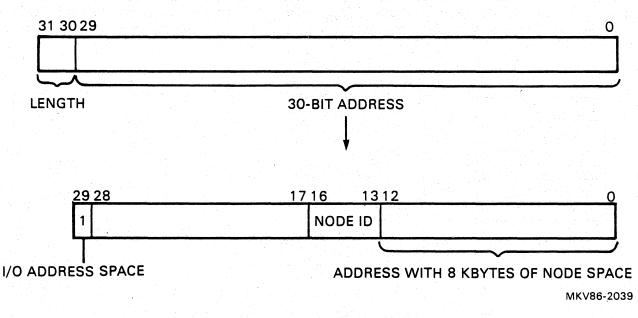

The physical address on the VAXBI is 30 bits long, thereby, providing a VAXBI physical address space of one gigabyte. A program will access this physical address space whenever it makes reference to a CIBCA adapter's hardware or software registers.

The VAXBI physical address space is divided into two parts; memory space and I/O space. Selection of memory space and I/O space is determined by address bit <29> of a READ or WRITE VAXBI bus transaction.

Physical Memory Space Addresses

The first 512 Mbytes (addresses 0000 0000 through 1FFF FFFF hexadecimal) are physical memory space addresses.

I/O Space Addresses

The last 512 Mbytes of the VAXBI physical address space (addresses 2000 0000 through 3FFF FFFF hexadecimal) are I/O space addresses.

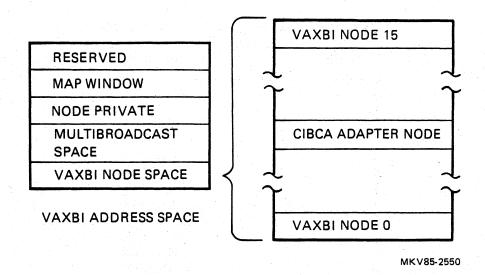

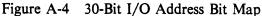

Figure A-1 illustrates the physical partitioning of the VAXBI physical address space. As shown in Figure A-2, the 512 Mbyte VAXBI I/O address space is organized into several categories: map window, broadcast space, and node space. Only the VAXBI node space is used by the CIBCA adapter.

#### Node Space

The VAXBI node space (Figure A-3) is organized into sixteen 8-Kbyte address blocks. The CIBCA adapter hardware is assigned to one of these address blocks. This address block is referred to as the CIBCA adapter node. It is accessed whenever a CIBCA adapter hardware or software register is referenced.

# DURING THE C/A CYCLE ON VAXBI D<31:00>

Figure A-1 VAXBI Physical Address Space

| RESERVED                | 7 |

|-------------------------|---|

| MAP WINDOW              | ] |

| NODE PRIVATE            | 1 |

| MULTIBROADCAST<br>SPACE |   |

| VAXBI NODE SPACE        | 1 |

MKV85-2552

Figure A-2 VAXBI Physical I/O Address Space

## A.3 CIBCA ADAPTER NODE

## A.3.1 Addressing

The address area of the CIBCA adapter node is calculated by taking the base address representing the VAXBI I/O address space (2000 0000 hex) and adding 8K times the node ID, plus the offset address of the device register. For simplicity, this calculated address is represented by "bb+" whenever a reference is made to any of the following register bit maps. Figure A-4 illustrates the format structure of a 30-bit I/O address. Table A-1 lists the starting addresses of the 16 VAXBI node spaces.

DURING THE C/A CYCLE ON VAXBI D<31:00>:

| 2000 0000<br>2000 2000<br>2000 4000<br>2000 6000<br>2000 8000<br>2000 A000 |

|----------------------------------------------------------------------------|

| 2000 4000<br>2000 6000<br>2000 8000                                        |

| 2000 6000<br>2000 8000                                                     |

| 2000 8000                                                                  |

|                                                                            |

| 2000 A000                                                                  |

|                                                                            |

| 2000 C000                                                                  |

| 2000 E000                                                                  |

| 2001 0000                                                                  |

| 2001 2000                                                                  |

| 2001 4000                                                                  |

| 2001 6000                                                                  |

| 2001 8000                                                                  |

| 2001 A000                                                                  |

| 2001 C000                                                                  |

| 2001 E000                                                                  |

|                                                                            |

Table A-1

Node Space Address Assignments

#### A.3.2 Partitioning

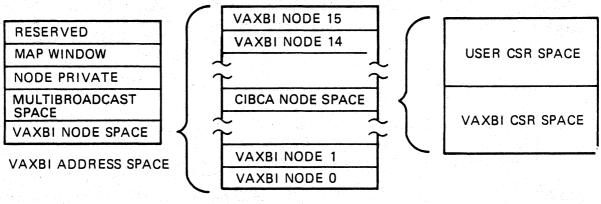

As shown in Figure A-5, the CIBCA node space is divided into two segments: VAXBI CSR space and User CSR space. The VAXBI CSR space occupies the first 256 byte locations and is used by the VAXBI protocol and VAXBI control logic of the CIBCA adapter hardware. The User CSR space occupies the remaining locations of the address block. Only a portion of these addresses are used by the CIBCA adapter. Reading or writing to an unused register address will produce unpredictable results such as, unpredictable data, possible parity errors, and possible VAXBI NO ACK responses.

MKV85-2553

Figure A-5 CIBCA Address Node Space

#### A.3.3 Registers

Figure A-6 shows that the first 256 bytes of the CIBCA node space are reserved for the VAXBI CSR registers. VAXBI required registers and specific device registers fall into the category of VAXBI CSR registers. The VAXBI required registers are used by all VAXBI nodes including the CIBCA. The specific device registers are special-purpose VAXBI registers used to control the VAXBI device window area, and VAXBI data transfer control and interrupt control. The remaining addresses of the CIBCA node space are reserved for User CSR registers. The adapter registers fall into this category and are used for initializing and controlling the CIBCA adapter hardware. All these registers are accessed using longword addresses.

Figure A-7 illustrates the VAXBI interface registers and adapter registers.

NOTE The CIBCA adapter hardware only issues longword or octaword VAXBI bus transactions.

MKV86-2040

Figure A-6 CIBCA Adapter Register Address Space

| ьь+00 [         | VAXBI REQUIRED REGISTERS                                                          |

|-----------------|-----------------------------------------------------------------------------------|

| bb+1C ]         |                                                                                   |

| bb+20           | BIIC SPECIFIC DEVICE REGISTERS                                                    |

| 1               | 승규는 이번 것을 가지 않는 것을 가장하지 않는 것이 없다. 이번 것이 같이 많이 |

| bb+F0           | GENERAL PURPOSE REGISTERS                                                         |

| Î Î             |                                                                                   |

| bb+FC<br>bb+100 | SLAVE-ONLY STATUS REGISTER                                                        |

| ~<br>~          | n an                                          |

| bb+200          | RECEIVE CONSOLE DATA REGISTER                                                     |

| 1               |                                                                                   |

| bb+204          | RESERVED/NOT ASSIGNED                                                             |

| bb+FFC          | RESERVED/NOT ASSIGNED                                                             |

|                 |                                                                                   |

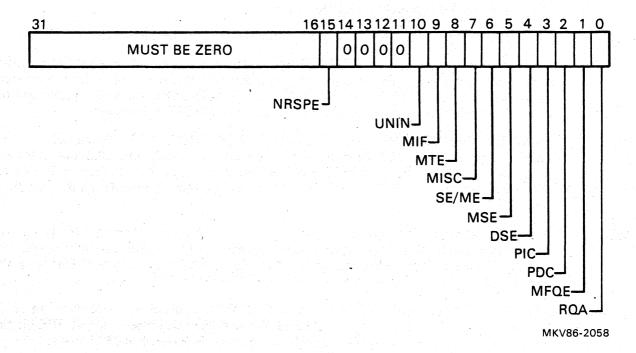

| bb+1000         | PORT STATUS REGISTER                                                              |

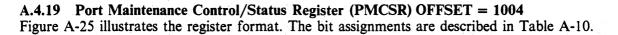

| bb+1004         | PORT MAINTENANCE CONTROL/STATUS REGISTER                                          |

| bb+1008         | MAINTENANCE ADDRESS REGISTER                                                      |

| bb+100C         | MAINTENANCE DATA REGISTER                                                         |

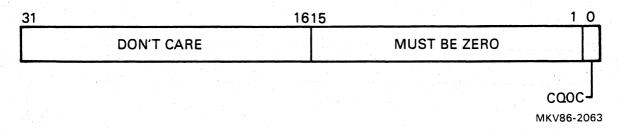

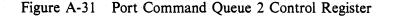

| bb+1010         | PORT COMMAND QUEUE 0 CONTROL REGISTER                                             |

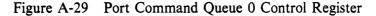

| bb+1014         | PORT COMMAND QUEUE 1 CONTROL REGISTER                                             |

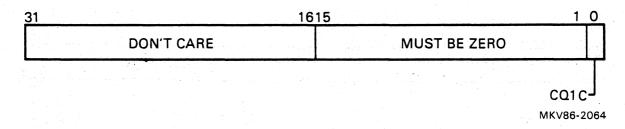

| bb+1018         | PORT COMMAND QUEUE 2 CONTROL REGISTER                                             |

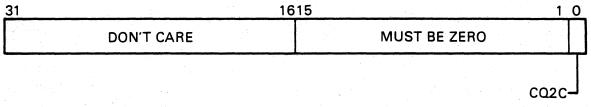

| bb+101C         | PORT COMMAND QUEUE 3 CONTROL REGISTER                                             |

| bb+1020         | PORT STATUS RELEASE CONTROL REGISTER                                              |

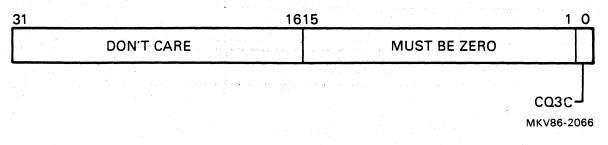

| bb+1024         | PORT ENABLE CONTROL REGISTER                                                      |

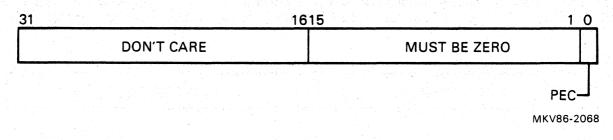

| bb+1028         | PORT DISABLE CONTROL REGISTER                                                     |

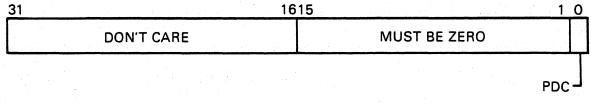

| bb+102C         | PORT INITIALIZE CONTROL REGISTER                                                  |

| bb+1030         | PORT DATAGRAM FREE QUEUE CONTROL REG.                                             |

| bb+1034         | PORT MESSAGE FREE QUEUE CONTROL REG.                                              |

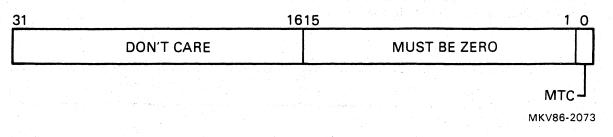

| bb+1038         | PORT MAINTENANCE TIMER CONTROL REG.                                               |

| bb+103C         | PORT MAINT. TIMER EXPIRATION CONTROL REG.                                         |

| bb+1040         | RESERVED REGISTER 3                                                               |

| bb+1044         | RESERVED REGISTER 4                                                               |

| bb+1048         | RESERVED REGISTER 1                                                               |

| bb+104C         | RESERVED REGISTER 2                                                               |

| bb+1050         | LOCAL STORE                                                                       |

| h 1 1 2 5 0 1   |                                                                                   |

| bb+1BFC         |                                                                                   |

| bb+1C00 ]       | VIRTUAL CIRCUIT DESCRIPTOR TABLE                                                  |

| .bb+1FFC        | VIRTUAL CIRCUIT DESCRIPTOR TABLE                                                  |

|                 |                                                                                   |

|                 | MKV86-2041                                                                        |

MKV86-2041

Figure A-7 VAXBI Interface Registers and Adapter Registers

A.4 VAXBI REQUIRED REGISTERS Figure A-8 illustrates a more detailed diagram of the VAXBI required registers.

| bb+0000              | DEVICE REGISTER                        |

|----------------------|----------------------------------------|

| bb+0004              | VAXBI CONTROL AND STATUS REGISTER      |

| bb <del>+</del> 0008 | BUS ERROR REGISTER                     |

| bb+000C              | ERROR INTERRUPT CONTROL REGISTER       |

| bb+0010              | INTERRUPT DESTINATION REGISTER         |

| bb+0014              | IPINTR MASK REGISTER                   |

| bb+0018              | FORCE-BIT IPINTR/STOP DESTINATION REG. |

| bb+001C              | IPINTR SOURCE REGISTER                 |

| bb+0020              | RESERVED                               |

| bb+0024              | RESERVED                               |

| bb+0028              | BCI CONTROL AND STATUS REGISTER        |

| bb+002C              | WRITE STATUS REGISTER                  |

| bb+0030              | RESERVED                               |

| bb+0040              | USER INTERFACE INTERRUPT CONTROL REG.  |

| bb+00F0              | PORT QUEUE BLOCK BASE REGISTER         |

| bb+00F4              | PORT FAILING ADDRESS REGISTER          |

| bb+00F8              | PORT PARAMETER REGISTER                |

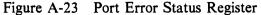

| bb+00FC              | PORT ERROR STATUS REGISTER             |

|                      |                                        |

MKV86-2042

Figure A-8 VAXBI CSR Space

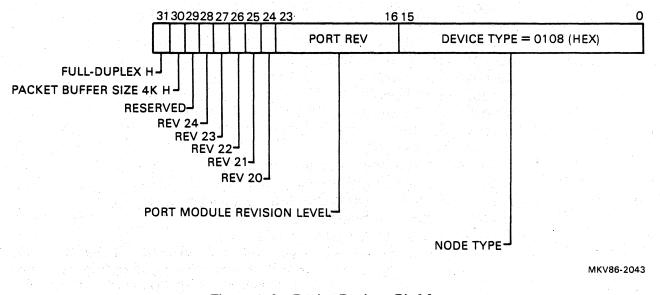

## A.4.1 Device Register (DTYPE) (R/W,DMW,DCLOL) OFFSET = 0000

The Device Register (Figure A-9) address offset = 00 hex, field bits <15:00> identifies the type of node for use by the VMS operating system's device driver software. The device type assigned to the CIBCA adapter is 0108 (hex).

Field bits <23:16> identify the port revision level. Field bits <28:24> identify the link revision level. Bit <29> is reserved. Bit <30> indicates packet buffer size (0=1K, 1=4K). If bit <31> is a 0, it implies half-duplex operation. If bit <31> is a 1, it implies full-duplex operation.

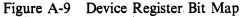

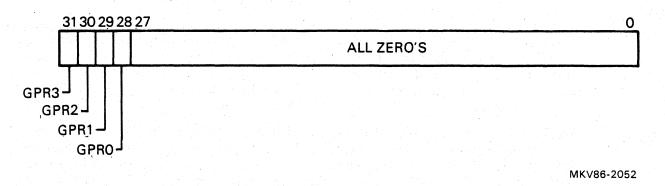

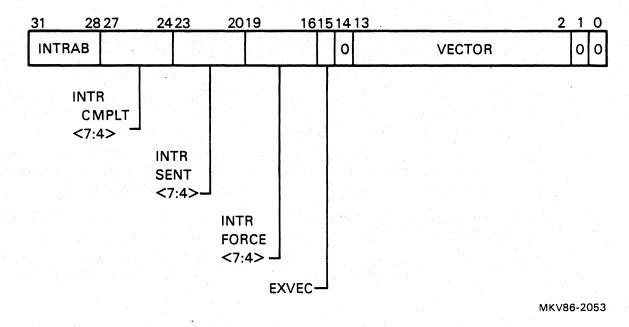

A.4.2 VAXBI Control and Status Register (VAXBICSR) OFFSET = 0004 The VAXBI Control and Status Register, address offset 0004 (hex), contains control and status information bits. It also contains the BIIC type and the node ID, and specifies the mode of arbitration. Figure A-10 illustrates the register format. The bit assignments are described in Table A-2.

Figure A-10 VAXBI Control and Status Register

| Table A-2 | VAXBI ( | Control and | Status Reg | zister Bit | Definitions |

|-----------|---------|-------------|------------|------------|-------------|

|           |         |             |            |            |             |

| Bit     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <31:24> | VAXBI INTERFACE REVISION (RO) - Indicates revision level of the BIIC chip.                                                                                                                                                                                                                                                                                                                                                                          |

| <23:16> | VAXBI INTERFACE TYPE (RO) – Indicates the type of device that provides the primary interface to the VAXBI (always 00000001).                                                                                                                                                                                                                                                                                                                        |

| <15>    | HARD ERROR SUMMARY (RO) – Indicates that one or more of the hard error bits in the Bus Error Register are set.                                                                                                                                                                                                                                                                                                                                      |

| <14>    | SOFT ERROR SUMMARY (RO) – Indicates that one or more of the soft error bits in the Bus Error Register are set.                                                                                                                                                                                                                                                                                                                                      |

| <13>    | INIT – This bit is not used.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <12>    | BROKE (W1C, DCLOS) – Self-test failure. Adapter will clear this bit when both the BIIC's internal self-test and the port's self-test passes. The port will do a self-test on power up only.                                                                                                                                                                                                                                                         |

| <11>    | SELF TEST STATUS (R/W, DCLOC) – This bit will be a "1" if the BIIC's internal self-<br>test passes. This bit enables the BIIC's BI drivers, and, therefore, a chip that fails self-test<br>will be unable to drive the BI. If the node has a reset STS bit, then a WRITE that sets this<br>bit will receive a NOACK response. Because the node's VAXBI driver is disabled, the<br>WRITE must be either a loopback or a VAXBI internode transaction. |

Table A-2

VAXBI Control and Status Register Bit Definitions (Cont)

| Bit     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |