EK-DEUNA-UG-001

# DEUNA USER'S GUIDE

•

EK-DEUNA-UG-001

# DEUNA USER'S GUIDE

Prepared by Educational Services of Digital Equipment Corporation

•

.

#### Copyright © 1983 by Digital Equipment Corporation All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### Printed in U.S.A.

.

The manuscript for this book was created on a DIGITAL Word Processing System and, via a translation program, was automatically typeset on DIGITAL's DECset Integrated Publishing System. Book production was done by Educational Services Development and Publishing in Nashua, NH.

The following are trademarks of Digital Equipment Corporation:

| digital      | DECtape      | Rainbow        |

|--------------|--------------|----------------|

| DATATRIEVE   | DECUS        | RSTS           |

| DEC          | DECwriter    | RSX            |

| DECmate      | DIBOL        | UNIBUS         |

| DECnet       | MASSBUS      | VAX            |

| DECset       | PDP          | VMS            |

| DECsystem-10 | P/OS         | VT             |

| DECSYSTEM-20 | Professional | Work Processor |

## CONTENTS

,

#### CHAPTER 1 INTRODUCTION

| 1.1     | SCOPE                               |

|---------|-------------------------------------|

| 1.2     | ETHERNET OVERVIEW1-1                |

| 1.3     | DEUNA GENERAL DESCRIPTION1-3        |

| 1.4     | DEUNA SYSTEM OPERATION1-5           |

| 1.4.1   | ETHERNET Physical Channel Functions |

| 1.4.2   | ETHERNET Data Link Functions        |

| 1.4.3   | Data Encapsulation1-7               |

| 1.4.4   | Data Decapsulation1-8               |

| 1.4.5   | Link Management1-9                  |

| 1.4.6   | Functional Overview1-9              |

| 1.4.6.1 | Receive Function                    |

| 1.4.6.2 | Transmit Function1-10               |

| 1.4.7   | Diagnostics and Maintenance1-11     |

| 1.5     | DEUNA SPECIFICATIONS1-12            |

| 1.6     | RELATED DOCUMENTS1-13               |

#### CHAPTER 2 INSTALLATION

| 2.1     | SCOPE                                             | 2-1    |

|---------|---------------------------------------------------|--------|

| 2.2     | UNPACKING AND INSPECTION                          | 2-1    |

| 2.3     | PREINSTALLATION CONSIDERATIONS                    | 2-2    |

| 2.3.1   | Backplane Requirements                            | 2-2    |

| 2.3.2   | Bus Latency Constraints                           |        |

| 2.3.3   | Loading Requirements                              |        |

| 2.4     | PREINSTALLATION PREPARATION                       | 2-3    |

| 2.4.1   | Backplane Power Checks and Preparation            | 2-3    |

| 2.4.2   | Device Address Assignment                         | 2-3    |

| 2.4.2.1 | First DEUNA Device Address (774510)               | 2-4    |

| 2.4.2.2 | Second DEUNA Device Address (Floating Address)    |        |

| 2.4.3   | Vector Address Assignment                         |        |

| 2.4.3.1 | First DEUNA Vector Address (120)                  |        |

| 2.4.3.2 | Second DEUNA Vector Address (Floating Vector)     | 2-6    |

| 2.4.4   | Boot Option Selection (PDP-11 Host Systems Only)  | 2-7    |

| 2.4.5   | Self-Test Loop (For Manufacturing Use)            | 2-7    |

| 2.5     | INSTALLATION AND CABLING                          | 2-8    |

| 2.5.1   | M7792 Port Module Installation                    |        |

| 2.5.2   | M7793 Link Module Installation                    | . 2-10 |

| 2.5.3   | Bulkhead Interconnect Panel Assembly Installation |        |

| 2.5.3.1 | Cabinets Without a Cabinet Bulkhead               |        |

| 2.5.3.2 | Cabinets With a Cabinet Bulkhead                  | . 2-13 |

| 2.5.3.3 | Connect the D-Connector                           |        |

| 2.6     | TESTING                                           | . 2-14 |

| 2.6.1   | Postinstallation Power Checks                     | . 2-14 |

| 2.6.2   | Light Emitting Diode (LED) Checks                 |        |

| 2.6.3   | Diagnostic Acceptance Procedure                   | . 2-17 |

#### CHAPTER 3 SERVICE

| 3.1   | SCOPE                                                    |

|-------|----------------------------------------------------------|

| 3.2   | MAINTENANCE PHILOSOPHY                                   |

| 3.3   | DIAGNOSTIC DESCRIPTION                                   |

| 3.3.1 | Self-Test                                                |

| 3.3.2 | DEUNA VAX-11 Functional Diagnostic (EVDWB REV *.*)3-4    |

| 3.3.3 | DEUNA PDP-11 Functional Diagnostic (CZUAB*)              |

| 3.3.4 | DEUNA VAX-11 Repair Level Diagnostic (EVDWA REV *.*) 3-7 |

| 3.3.5 | DEUNA PDP-11 Repair Level Diagnostic (CZUAA*)            |

| 3.3.6 | NI Exerciser (CZUAD*/EVDWC REV *.*)                      |

| 3.3.7 | DEC/X11 DEUNA Module (CXUAC*)                            |

| 3.4   | CORRECTIVE MAINTENANCE                                   |

# CHAPTER 4 PROGRAMMING

.

| 4.1     | INTRODUCTION                                               |

|---------|------------------------------------------------------------|

| 4.2     | PROGRAMMING OVERVIEW                                       |

| 4.3     | PORT CONTROL AND STATUS REGISTERS                          |

| 4.3.1   | Port Control and Status Register 0 (PCSR0)                 |

| 4.4     | PORT CONTROL BLOCK FUNCTIONS                               |

| 4.4.1   | Function Code 0 – No-Operation                             |

| 4.4.2   | Function Code 1 – Load and Start Microaddress              |

| 4.4.3   | Function Code 2 – Read Default Physical Address            |

| 4.4.4   | Function Code 3 – No-Operation                             |

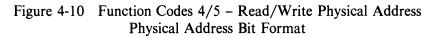

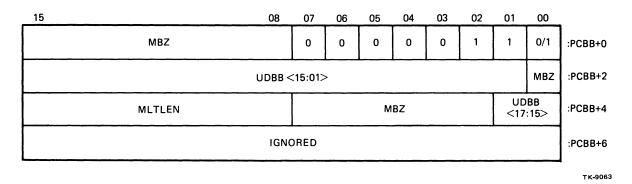

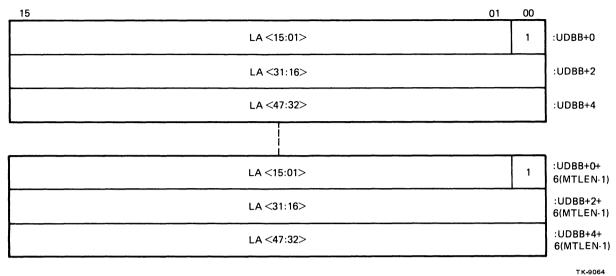

| 4.4.5   | Function Codes 4/5 – Read/Write Physical Address           |

| 4.4.6   | Function Codes 6/7 – Read/Write Multicast Address List     |

| 4.4.7   | Function Codes 10/11 – Read/Write Ring Format              |

| 4.4.8   | Function Codes 12/13 – Read/Read and Clear Counters        |

| 4.4.9   | Function Codes 14/15 – Read/Write Mode                     |

| 4.4.10  | Function Codes 16/17 – Read/Read and Clear Port Status4-39 |

| 4.4.11  | Function Codes 20/21 – Dump/Load Internal Memory           |

| 4.4.12  | Function Codes 22/23 – Read/Write System ID Parameters4-44 |

| 4.4.13  | Function Codes 24/25 – Read/Write Load Server Address      |

| 4.5     | TRANSMIT DESCRIPTOR RING ENTRY                             |

| 4.6     | RECEIVE DESCRIPTOR RING ENTRY                              |

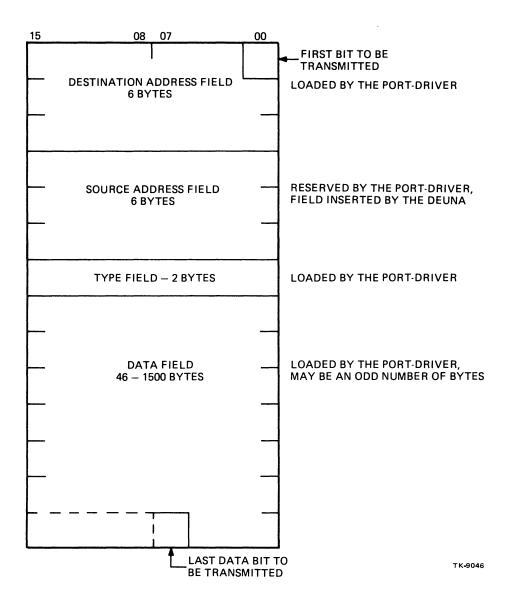

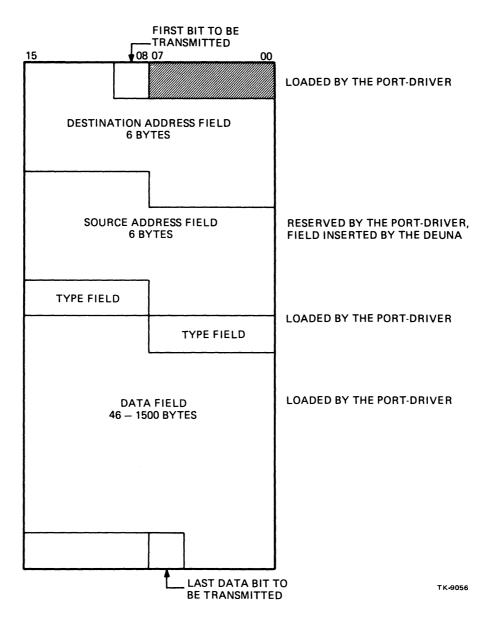

| 4.7     | TRANSMIT DATA BUFFER FORMAT                                |

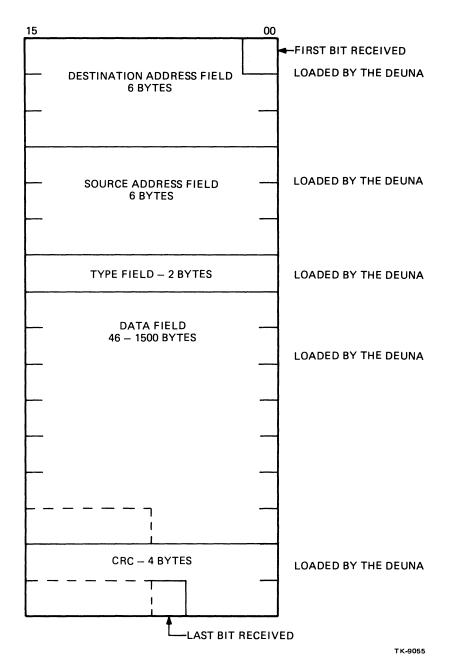

| 4.8     | RECEIVE DATA BUFFER FORMAT                                 |

| 4.9     | DEUNA OPERATION                                            |

| 4.9.1   | Power On                                                   |

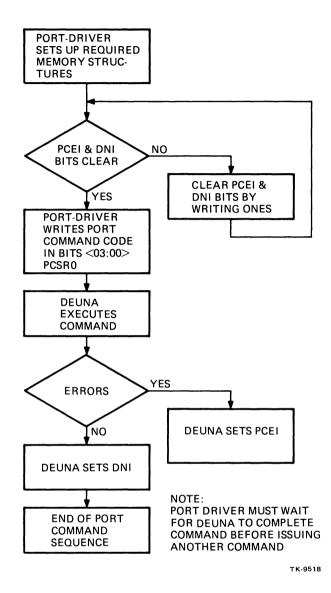

| 4.9.2   | Port Command Capability4-64                                |

| 4.9.3   | Software Initialization                                    |

| 4.9.4   | Polling                                                    |

| 4.9.4.1 | Receive Polling                                            |

| 4.9.4.2 | Transmit Polling                                           |

| 4.9.5   | Datagram Reception                                         |

| 4.9.6   | Datagram Transmission                                      |

| 4.9.7   | Parameter Alteration                                       |

| 4.9.8   | Suspension of Operation-Port Command                       |

| 4.9.9   | Restart of Operation                                       |

| 4.9.10   | DEUNA States                      |  |

|----------|-----------------------------------|--|

| 4.9.10.1 | DEUNA State Related Functions     |  |

| 4.9.10.2 | DEUNA State Transition            |  |

| 4.9.10.3 | DEUNA State Information Retention |  |

| 4.10     | EXCEPTIONAL OPERATIONS            |  |

| 4.10.1   | Channel Loopback                  |  |

| 4.10.2   | Remote Console and Down-Line Load |  |

| 4.10.2.1 | Remote Boot                       |  |

| 4.10.2.2 | Local Boot                        |  |

| 4.10.2.3 | Boot on Power Up                  |  |

| 4.10.2.4 | Primary Load State                |  |

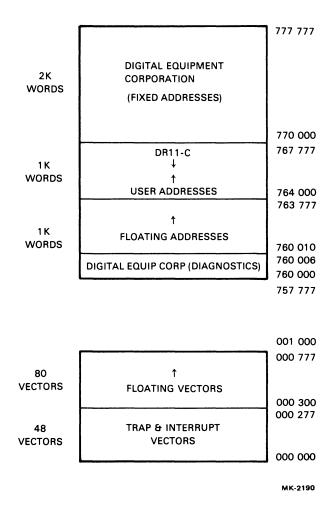

#### APPENDIX A FLOATING DEVICE ADDRESSES AND VECTORS

| A.1 | FLOATING DEVICE ADDRESSES                     | A-1 |

|-----|-----------------------------------------------|-----|

| A.2 | FLOATING VECTOR ADDRESSES                     | A-3 |

| A.3 | DEVICE AND VECTOR ADDRESS ASSIGNMENT EXAMPLES | A-5 |

#### APPENDIX B REMOTE BOOTING AND DOWN-LINE LOADING

| INTRODUCTION B-1                               |

|------------------------------------------------|

| SYSTEM CONFIGURATION GUIDELINES B-1            |

| REMOTE BOOT DISABLED B-2                       |

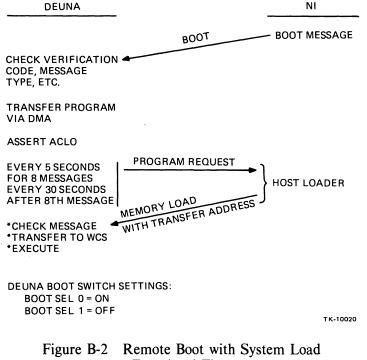

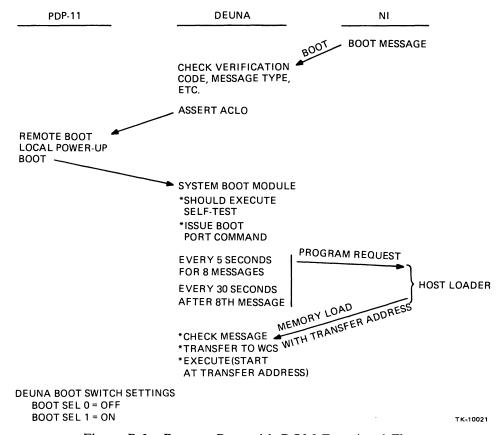

| REMOTE BOOT WITH SYSTEM LOAD B-2               |

| REMOTE BOOT WITH ROM B-4                       |

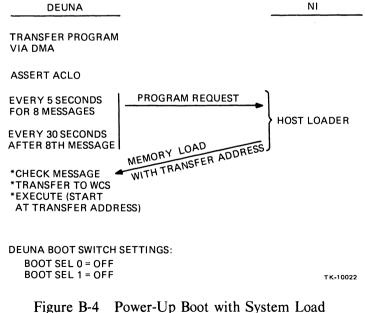

| REMOTE BOOT/POWER-UP BOOT WITH SYSTEM LOAD B-5 |

|                                                |

#### APPENDIX C NETWORK INTERCONNECT EXERCISER

| C.1     | INTRODUCTION C-1                                 |

|---------|--------------------------------------------------|

| C.2     | RUN-TIME ENVIRONMENT REQUIREMENTS C-2            |

| C.3     | FUNCTIONAL DESCRIPTION                           |

| C.3.1   | Unattended Mode C-2                              |

| C.3.1.1 | Build C-2                                        |

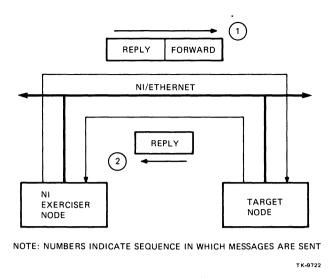

| C.3.1.2 | Direct Loop Message Test C-2                     |

| C.3.1.3 | Pattern Test C-3                                 |

| C.3.1.4 | Multiple Message Activity Test                   |

| C.3.2   | Operator-Directed Section                        |

| C.3.2.1 | Operator Conversation                            |

| C.3.2.2 | Collect IDs (Build) C-7                          |

| C.3.2.3 | Request ID C-7                                   |

| C.3.2.4 | Pair-Node Testing C-7                            |

| C.3.2.5 | NI All Node Communications Test (End-to-End) C-9 |

| C.3.2.6 | Summary Log C-10                                 |

|         |                                                  |

#### APPENDIX D VECTOR ADDRESS (REVB)

.

| D.1   | VECTOR ADDRESS ASSIGNMENT D-1                        |

|-------|------------------------------------------------------|

| D.1.1 | First DEUNA Vector Address (120) D-1                 |

| D.1.2 | Second DEUNA Vector Address (Floating Vector) D-1    |

| D.2   | BOOT OPTION SELECTION (PDP-11 HOST SYSTEMS ONLY) D-3 |

| D.3   | SELF-TEST LOOP (FOR MANUFACTURING USE)               |

#### APPENDIX E DEUNA MICROCODE ECO PROCESS

| E.1 | INTRODUCTION      | E-1 |

|-----|-------------------|-----|

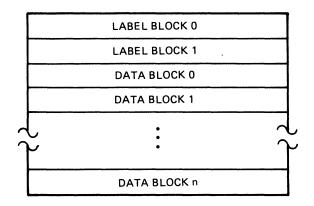

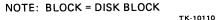

| E.2 | PATCH FILE FORMAT | E-1 |

| E.3 | PATCH PROCEDURE   | E-3 |

•

#### **FIGURES**

| Figure No. | Title Pag                                                                  | ze         |

|------------|----------------------------------------------------------------------------|------------|

| 1-1        | Typical Large-Scale ETHERNET Configuration1-                               | -2         |

| 1-2        | DEUNA to ETHERNET Connection 1-                                            |            |

| 1-3        | PDP-11 Host System Block Diagram 1-                                        | -5         |

| 1-4        | VAX-11 Host System Block Diagram 1-                                        | -6         |

| 1-5        | Format of an ETHERNET Data Packet 1-                                       | -8         |

| 1-6        | DEUNA Receive Data Path 1-1                                                | 0          |

| 1-7        | DEUNA Transmit Data Path 1-1                                               | 1          |

| 2-1        | M7792 Port Module Physical Layout                                          | -4         |

| 2-2        | M7793 Link Module Physical Layout 2-                                       | -8         |

| 2-3        | DEUNA Cable Connection Details                                             | -9         |

| 2-4        | Typical Module Installation                                                | 0          |

| 2-5        | Bulkhead Interconnect Panel Assembly 2-1                                   |            |

| 2-6        | Bulkhead Interconnect Panel Assembly Installation                          |            |

| 2-7        | Typical System Cabinet Bulkhead Installation 2-1                           |            |

| 2-8        | Digital ETHERNET Loopback Connector                                        |            |

| 3-1        | DEUNA Port Module Self-Test LEDs                                           | -2         |

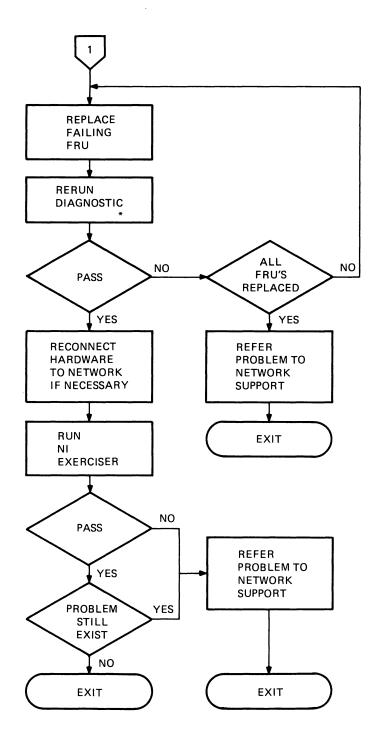

| 3-2        | DEUNA Troubleshooting Procedure                                            | l <b>4</b> |

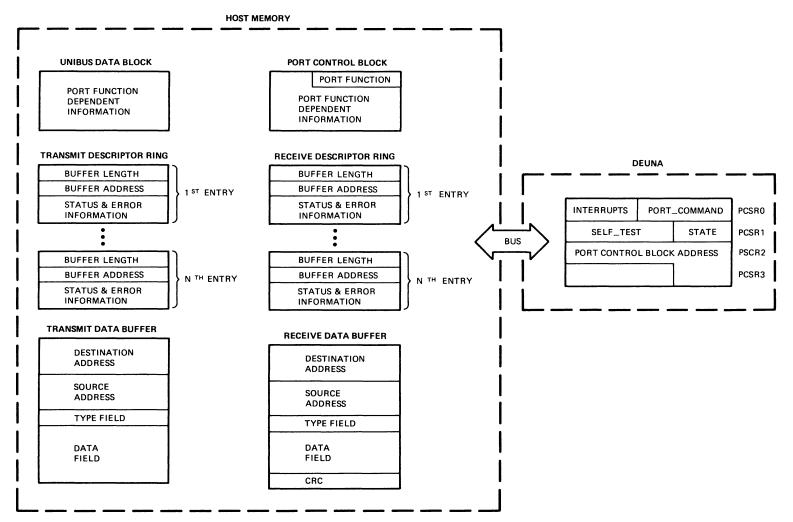

| 4-1        | DEUNA CSRs and Host Memory Data Structures 4-                              |            |

| 4-2        | PCSR0 Bit Format                                                           | 0          |

| 4-3        | PCSR1 Bit Format                                                           |            |

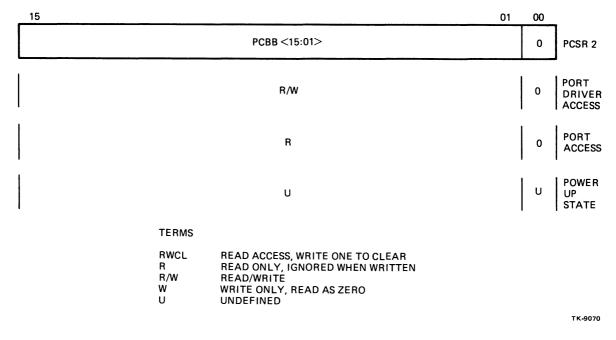

| 4-4        | PCSR2 Bit Format                                                           | 4          |

| 4-5        | PCSR3 Bit Format                                                           | 5          |

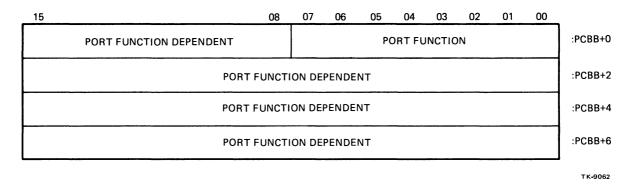

| 4-6        | Port Control Block Diagram 4-1                                             |            |

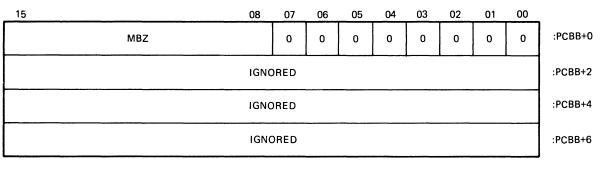

| 4-7        | Function Code 0 – No Operation Bit Format 4-1                              |            |

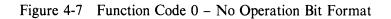

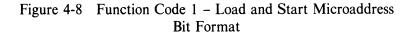

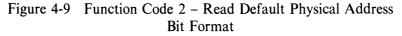

| 4-8        | Function Code 1 – Load and Start Microaddress Bit Format                   |            |

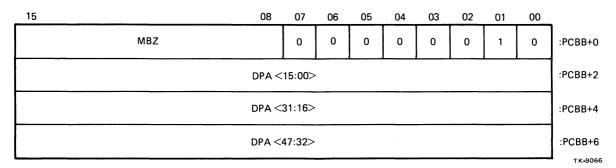

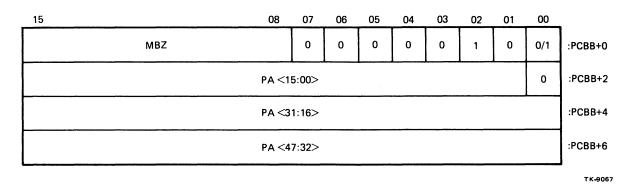

| 4-9        | Function Code 2 – Read Default Physical Address Bit Format                 | 21         |

| 4-10       | Function Codes 4/5 – Read/Write Physical Address Bit Format                | 22         |

| 4-11       | Function Codes 6/7 – Read/Write Multicast Address List PCBB Bit Format 4-2 | 24         |

| 4-12       | Function Codes 6/7 – Read/Write Multicast Address List UDBB Bit Format 4-2 | 26         |

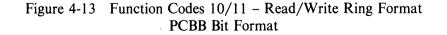

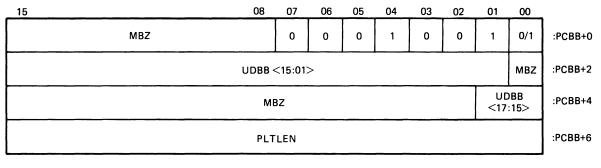

| 4-13       | Function Codes 10/11 – Read/Write Ring Format PCBB Bit Format 4-2          |            |

| 4-14       | Function Codes 10/11 – Read/Write Ring Format UDBB Bit Format              |            |

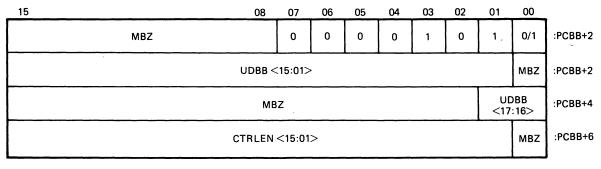

| 4-15       | Function Codes 12/13 – Read/Write and Clear Counters PCBB Bit Format 4-2   | 29         |

| 4-16       | UNIBUS Data Block Format for Counter List 4-3                              | 31         |

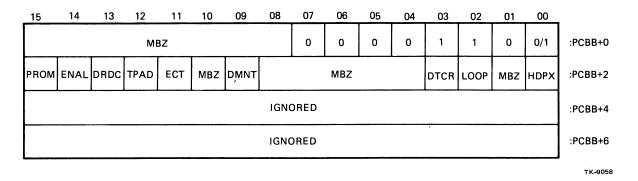

| 4-17       | Function Codes 14/15 – Read/Write Mode PCBB Bit Format 4-3                 | 35         |

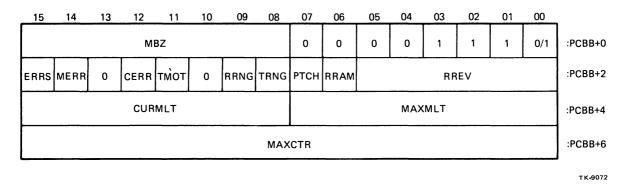

| 4-18       | Function Codes 16/17 – Read/Read and Clear Port Status PCBB Bit Format 4-3 | 39         |

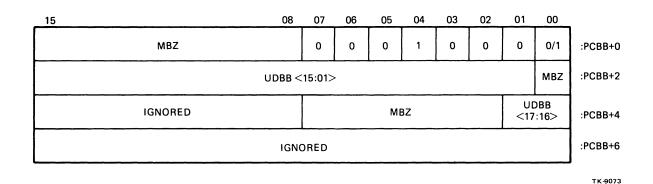

| 4-19       | Function Codes 20/21 – Load/Dump Internal Memory PCBB Bit Format 4-4       | 11         |

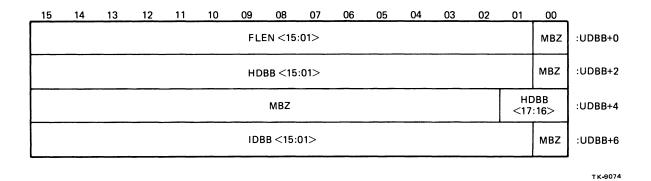

| 4-20       | Function Codes 20/21 – Load/Dump Internal Memory UDBB Bit Format 4-4       | 13         |

| 4-21       | Function Codes 22/23 – Read/Write System ID Parameters PCBB Bit Format 4-4 |            |

| 4-23       | Function Codes 22/23 – Read/Write System ID Parameters UDBB Bit Format 4-4 | 6          |

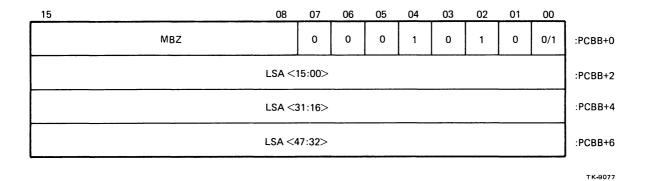

| 4-23       | Function Codes 24/25 – Read/Write Load Server Address PCBB Bit Format 4-5  |            |

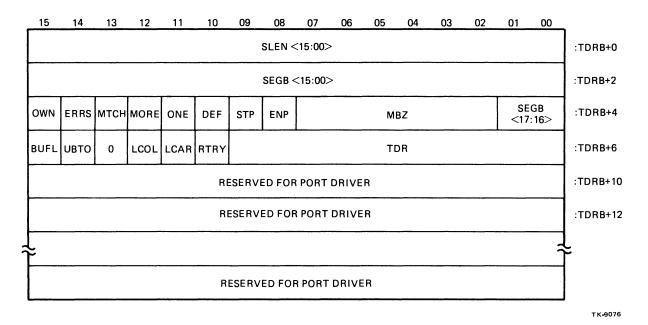

| 4-24       | Transmit Descriptor Ring Entry Format 4-5                                  | 51         |

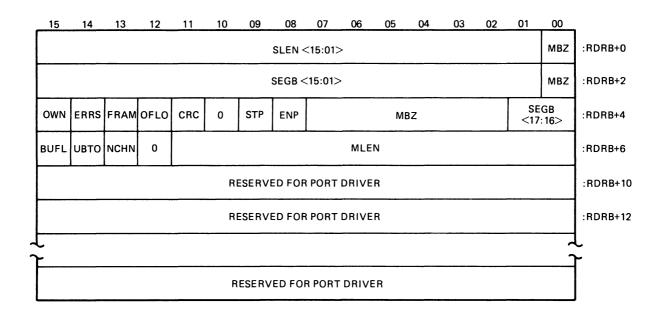

| 4-25       | Receive Descriptor Ring Entry Format 4-5                                   |            |

| 4-26       | Transmit Data Buffer Starting on an Even Byte Boundary                     | 50         |

| 4-27       | Transmit Data Buffer Starting on an Odd Byte Boundary 4-6                  | 51         |

| 4-28       | Receive Data Buffer Format 4-6                                             |            |

| 4-29 | Port Command Sequence                                           | 4-65 |

|------|-----------------------------------------------------------------|------|

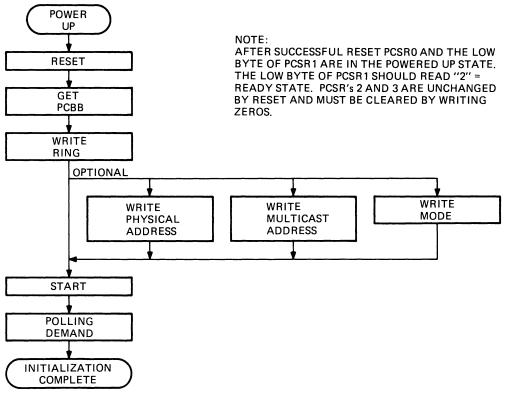

| 4-30 | DEUNA Software Initialization Sequence                          |      |

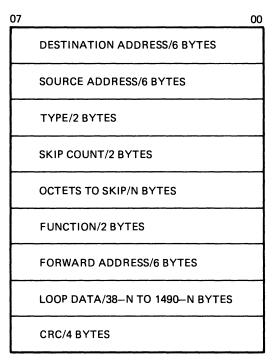

| 4-31 | Loop Message Format                                             |      |

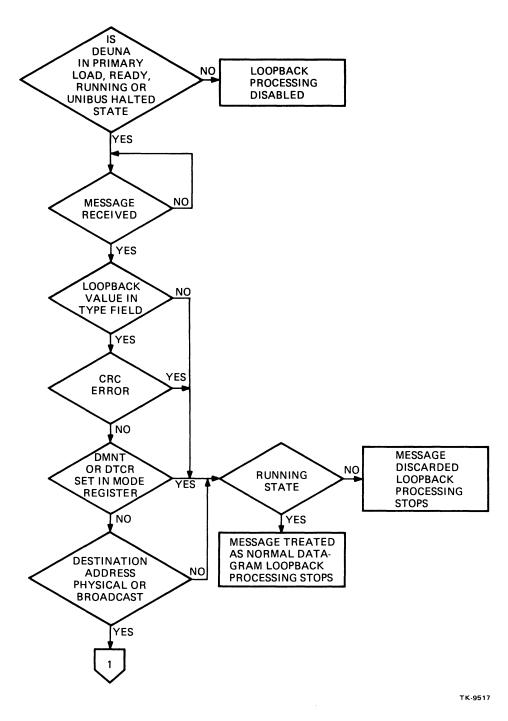

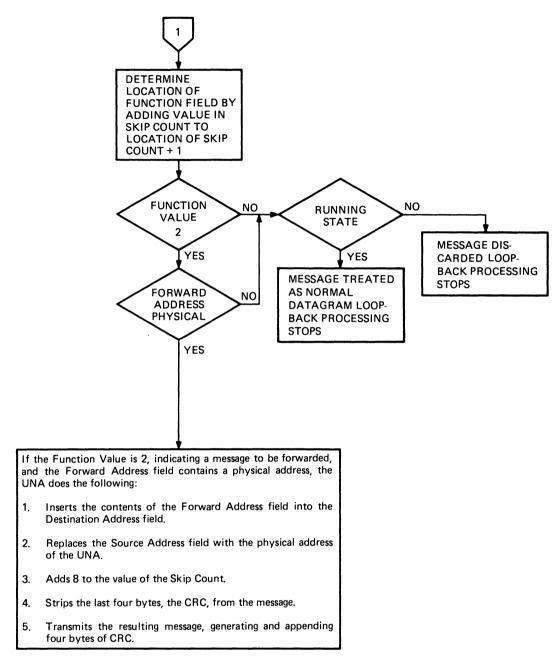

| 4-32 | Loopback Message Processing Flow                                |      |

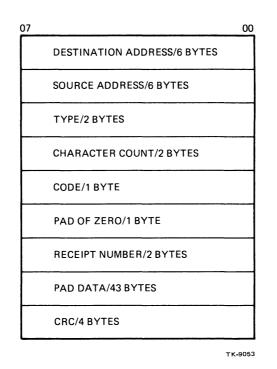

| 4-33 | Request ID Message Format                                       |      |

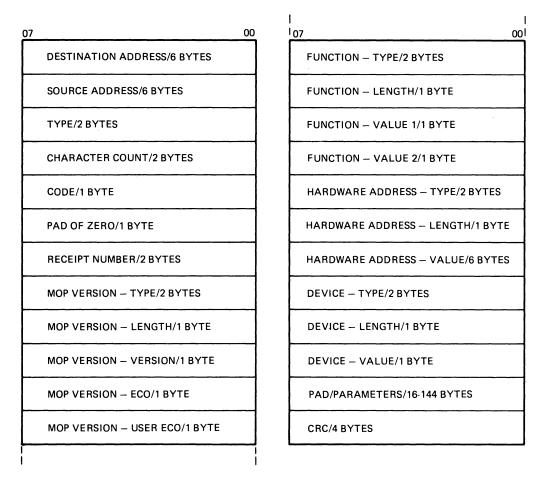

| 4-34 | System ID Message Format                                        |      |

| 4-35 | Boot Message Format                                             |      |

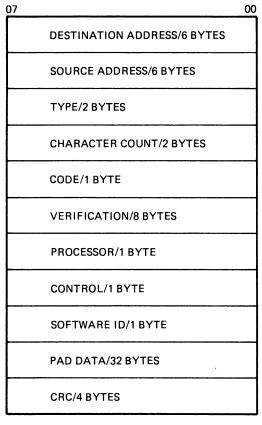

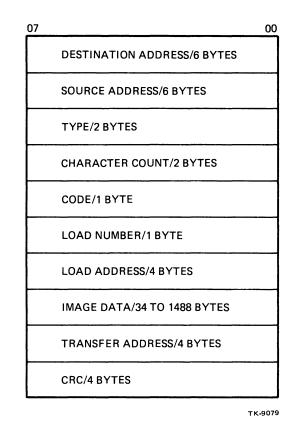

| 4-36 | Program Request Message Format                                  |      |

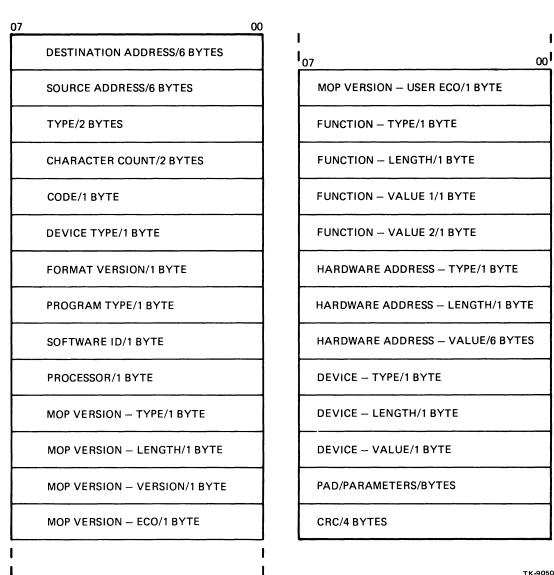

| 4-37 | Memory Load with Transfer Address Message Format                |      |

| A-1  | UNIBUS Address Map                                              | A-1  |

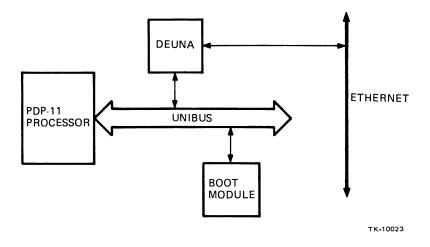

| B-1  | PDP-11 System                                                   | B-1  |

| B-2  | Remote Boot with System Load Functional Flow                    |      |

| B-3  | Remote Boot with System ROM Functional Flow                     | B-4  |

| B-4  | Power-Up Boot with System Load Functional Flow                  | B-5  |

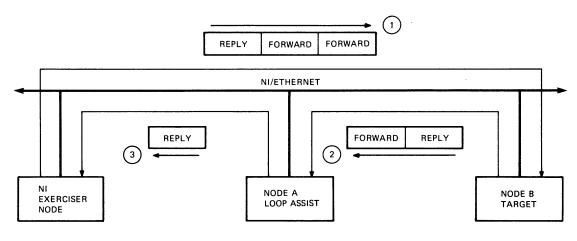

| C-1  | Direct Loop Message Test Example                                | C-3  |

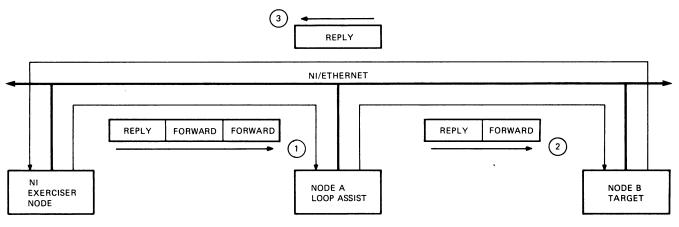

| C-2  | Transmit Assist Loopback Testing Example                        |      |

| C-3  | Receive Assist Loopback Testing Example                         |      |

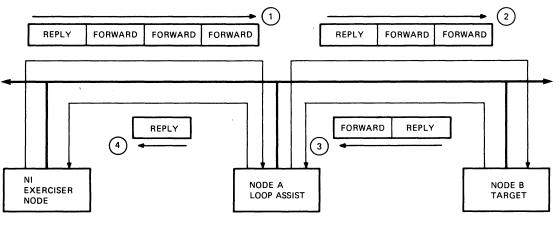

| C-4  | Full Assist Loopback Testing Example                            |      |

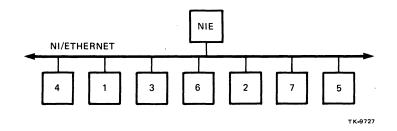

| C-5  | Example Test Configuration for All Node Communications Test C-9 |      |

| D-1  | M7792 Port Module Physical Layout                               | D-2  |

| E-1  | Patch File Format                                               | E-1  |

| E-2  | Data Block Format                                               | E-2  |

|      |                                                                 |      |

#### TABLES

| Table No. | Title                                                        | Page   |

|-----------|--------------------------------------------------------------|--------|

| 1-1       | DEUNA Specifications                                         | . 1-12 |

| 1-2       | Related Hardware and Software Documents                      | . 1-13 |

| 2-1       | DEUNA Parts List                                             | 2-2    |

| 2-2       | DEUNA UNIBUS Loading                                         | 2-3    |

| 2-3       | DEUNA Power Chart                                            | 2-3    |

| 2-4       | Floating Address Assignment                                  | 2-5    |

| 2-5       | Floating Vector Assignment                                   | 2-6    |

| 2-6       | Boot Option Selection (M7792 E62 – S8 & S9)                  | 2-7    |

| 2-7       | Self-Test Loop Switch (M7792 E62 – S10)                      | 2-8    |

| 2-8       | DEUNA LED Indicator Functions                                | 2-16   |

| 2-9       | DEUNA Diagnostics                                            | . 2-17 |

| 3-1       | DEUNA Self-Test LED Codes                                    | 3-3    |

| 3-2       | DEUNA VAX-11 Functional Diagnostic Summary (EVDWB REV*.*)    | 3-4    |

| 3-3       | DEUNA PDP-11 Functional Diagnostic Summary (CZUAB*)          | . 3-5  |

| 3-4       | DEUNA VAX-11 Repair Level Diagnostic Summary (EVDWA REV *.*) | 3-7    |

| 3-5       | DEUNA PDP-11 Repair Level Diagnostic Summary (CZUAA*)        | 3-10   |

| 4-1        | DEUNA Control Functions                                                                             | 4-2          |

|------------|-----------------------------------------------------------------------------------------------------|--------------|

| 4-2        | DEUNA Control runchons                                                                              |              |

| 4-2        | DEUNA Port Commands                                                                                 |              |

|            |                                                                                                     |              |

| 4-4        | DEUNA Ancillary Commands                                                                            |              |

| 4-5        | Maintenance Functions                                                                               |              |

| 4-6        | PCSR 0 Bit Description                                                                              |              |

| 4-7        | PCSR 1 Bit Description                                                                              |              |

| 4-8        | PCSR1 (13.08) Self-Test Codes                                                                       |              |

| 4-9        | PCSR 2 Bit Description                                                                              |              |

| 4-10       | PCSR 3 Bit Description                                                                              | 4-15         |

| 4-11       | Port Control Block Bit Descriptions                                                                 | 4-17         |

| 4-12       | Port Control Functions                                                                              |              |

| 4-13       | Function Code 0 – No-Operation Bit Descriptions                                                     |              |

| 4-14       | Function Code 1 – Load and Start Microaddress Bit Descriptions                                      |              |

| 4-15       | Function Code 2 – Read Default Physical Address                                                     |              |

| 4-16       | Function Codes 4/5 – Read/Write Physical Address Bit Descriptions                                   |              |

| 4-17       | Function Codes 6/7 – Read/Write Multicast Address List PCBB Bit Descriptions                        |              |

| 4-18       | Function Code 10/11 – Read/Write Ring Format PCBB Bit Descriptions                                  |              |

| 4-18       | Function Code 10/11 – Read/Write Ring Format UDBB Bit Descriptions                                  |              |

| 4-19       | Function Code 10/11 – Read/ while King Format ODBB Bit Descriptions                                 |              |

|            | <b>1</b>                                                                                            |              |

| 4-21       | Function Code 12/13 – Read/Read and Clear Counters UDBB Bit Descriptions                            |              |

| 4-22       | Function Code 14/15 – Read/Write Mode PCBB Bit Descriptions                                         |              |

| 4-23       | Function Code 16/17 – Read/Read and Clear Port Status                                               |              |

| 4-24       | Function Code 20/21 – Dump/Load Internal Memory PCBB Bit Descriptions                               |              |

| 4-25       | Function Code 20/21 – Load/Dump Internal Memory UDBB Bit Descriptions                               |              |

| 4-26       | Function Code 22/23 – Read/Write System ID Parameters PCBB Bit Descriptions                         |              |

| 4-27       | Function Code 22/23 – Read/Write System ID Parameters UDBB Bit Description                          | 4-47         |

| 4-28       | Function Code 24/25 – Read/Write Load Server Additional PCBB Bit Descriptions                       | 4-51         |

| 4-29       | Transmission Descriptor Ring Base (TDRB) Bit Descriptions                                           | 4-52         |

| 4-30       | Receive Descriptor Ring Entry Bit Descriptions                                                      | 4-58         |

| 4-31       | DEUNA Self-Test Failure Results                                                                     | 4-63         |

| 4-32       | DEUNA Port Commands                                                                                 | 4-64         |

| 4-33       | Format of an ETHERNET Data Packet                                                                   | 4-69         |

| 4-34       | RUNNING State Parameter Alteration Impact Summary                                                   | 4-70         |

| 4-35       | DEUNA State Function Summary                                                                        |              |

| 4-36       | DEUNA State Transition                                                                              |              |

| 4-37       | State Information Retention Summary                                                                 |              |

| 4-38       | Loopback Message Field Descriptions                                                                 |              |

| 4-39       | Boot Select Capability of the DEUNA                                                                 | 4-82         |

| 4-40       | Request ID Message Field Descriptions                                                               |              |

| 4-41       | System ID Message Field Descriptions                                                                |              |

| 4-42       | Boot Message Field Descriptions                                                                     |              |

| 4-43       | Program Request Message Field Description                                                           |              |

| 4-44       | Memory Load with Transfer Address Message Field Descriptions                                        | 1 00         |

| 4-44       | Memory Load with Transfer Address Message Field Descriptions                                        | 4-77         |

| A-1        | Floating Device Address Ranking Sequence                                                            | <u>م</u> ک   |

| A-1<br>A-2 | Floating Vector Ranking Sequence                                                                    |              |

| A-2        |                                                                                                     | . A-3        |

| B-1        | Remote and Down-Line Load Configuration Guidelines                                                  | . B-2        |

| C 1        | Massage Dattam Test Massage Tumos                                                                   | $\mathbf{C}$ |

| C-1        | Message Pattern Test Message Types                                                                  |              |

| C-2        |                                                                                                     |              |

| $\alpha$   | Operator Command Summary                                                                            |              |

| C-3<br>C-4 | Operator Command Summary         All Node Communications Testing Matrix         Summary Information | <b>C-10</b>  |

| D-1 | Floating Vector Assignment                | <b>D-1</b> |

|-----|-------------------------------------------|------------|

| D-2 | Boot Option Selection (M7792 E62 – S7&S8) | D-3        |

| D-3 | Self-Test Loop Switch (M7792 E62 – S9)    | D-4        |

#### **EXAMPLES**

| Example No. | Title                          | Page |

|-------------|--------------------------------|------|

| 4-1         | Writing Interrupt Bit in PCSR0 | 4-16 |

| 4-2         | Ring Pointer Initialization    | 4-67 |

,

## CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This chapter introduces the DIGITAL Equipment UNIBUS Network Adapter (DEUNA), including its operation and specifications, and overviews the ETHERNET local area network. Additional documents are listed for the reader who wishes more information about the ETHERNET, the DEUNA, or local area networks.

#### **1.2 ETHERNET OVERVIEW**

ETHERNET is a local area network that provides a communications facility for high-speed data exchange among computers and other digital devices located within a moderately sized geographic area. It is intended primarily for use in such areas as office automation, distributed data processing, terminal access, and other situations requiring economical connection to a local communication medium carrying traffic at high-peak data rates.

The primary characteristics of ETHERNET include:

- Topology Branching bus

- Medium Shielded coaxial cable, Manchester encoded digital base-band signaling

- Data Rate (Physical Channel) 10 million bits per second (maximum)

- Maximum Separation of Nodes 2.8 kilometers (1.74 miles)

- Maximum Number of Nodes 1,024

- Network Control Multiaccess fair distribution to all nodes

- Access Control Carrier Sense, Multiple Access with Collision Detect (CSMA/CD)

- Packet Length 64 to 1518 bytes (includes variable data field of from 46 to 1500 bytes less 8-byte preamble).

The ETHERNET falls into a middle ground between long-distance, low-speed networks that carry data for hundreds or thousands of kilometers and specialized high-speed interconnections generally limited to tens of meters. Using a branching bus topoloy, ETHERNET provides a local area communications network allowing a 10M bits/s data rate over a coaxial cable at a distance of up to 2.8 km (1.74 mi).

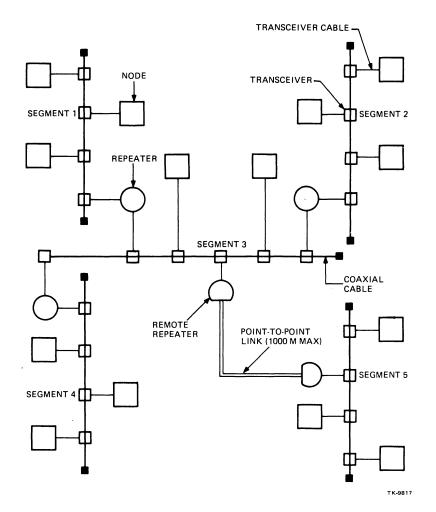

A single ETHERNET can connect up to 1,024 nodes for a local point-to-point/multipoint network. An example of a typical large-scale ETHERNET configuration is shown in Figure 1-1.

Figure 1-1 Typical Large-Scale ETHERNET Configuration

To configure ETHERNET, certain limits are imposed on the physical channel to ensure the optimal performance of the network. The maximum configuration for an ETHERNET is as follows:

- A segment of coaxial cable can be a maximum of 500 meters (1640.5 feet) in length. Each segment must be terminated at both ends in its characteristic impedance.

- Up to 100 nodes can be connected to any segment of the cable. Nodes on a cable segment must be spaced at least 2.5 meters (8.2 feet) apart.

- The maximum length of coaxial cable between any two nodes is 1,500 meters (4921.5 feet).

- The maximum length of the transceiver cable between a transceiver and a controller is 50 meters (164.05 feet).

#### NOTE In addition to internal cabling between the DEUNA and its bulkhead assembly, the DEUNA will support an additional 40 meters of transceiver cable.

- A maximum of 1,000 meters (3281 feet) of point-to-point link is allowed for extending the network.

- Repeaters can be used to continue signals from one cable segment of the ETHERNET to another. A maximum of two repeaters can be placed in the path between any two nodes.

#### **1.3 DEUNA GENERAL DESCRIPTION**

The DEUNA is a data communications controller used to interface VAX-11 and PDP-11 family computers to the ETHERNET local area network. Features of the DEUNA include:

- High speed transmission and reception

- 10M bit data rate

- Transmit and receive data link and buffer management

- Data encapsulation and decapsulation

- Data encoding and decoding

- Collision detection and automatic retransmission

- 32-bit Cyclic Redundancy Check (CRC) error detection

- 32 KB (16 KW) buffer for datagram reception transmission, and maintenance requirements

- Down-line loading and remote load detect capabilities

- Internal ROM based microdiagnostics to facilitate diagnosis and maintenance of both the DEUNA-AA and the DIGITAL H4000 transceiver

- Unique 48-bit Default Physical Address (reprogrammable)

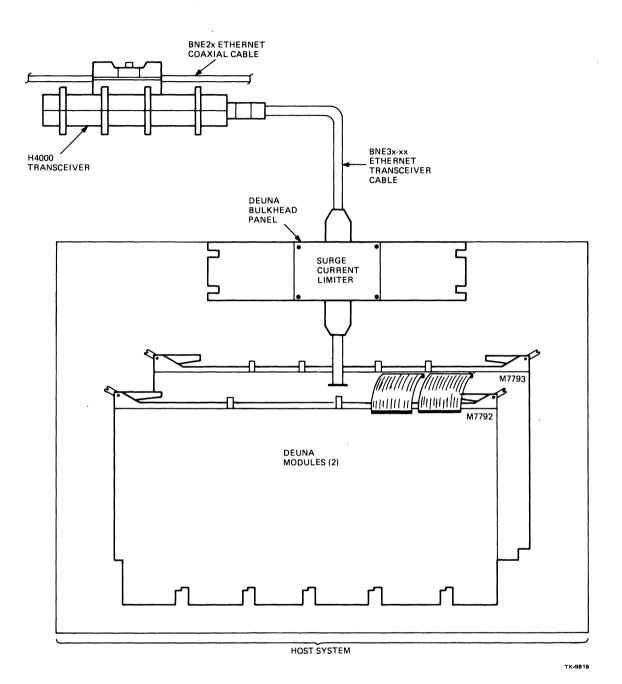

The DEUNA has two hex-height modules, a bulkhead interconnect panel, and associated cables. It physically and electrically connects to the ETHERNET cable via the DIGITAL H4000 transceiver and the appropriate transceiver cable as shown in Figure 1-2.

Figure 1-2 DEUNA to ETHERNET Connection

#### **1.4 DEUNA SYSTEM OPERATION**

The DEUNA controller performs both the ETHERNET data link layer functions and a portion of the physical channel functions. It also provides the following network maintainability features.

- Loopbacks maintenance messages from other stations.

- Periodically transmits system identification.

- Loads and remotely boots UNIBUS systems from other stations on the network.

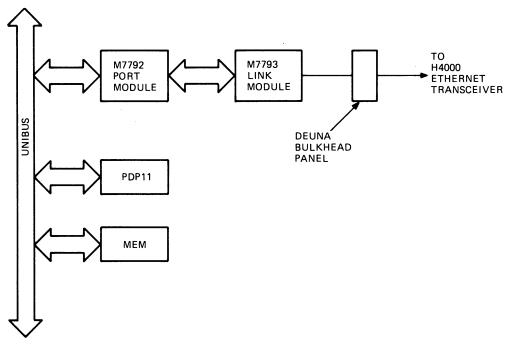

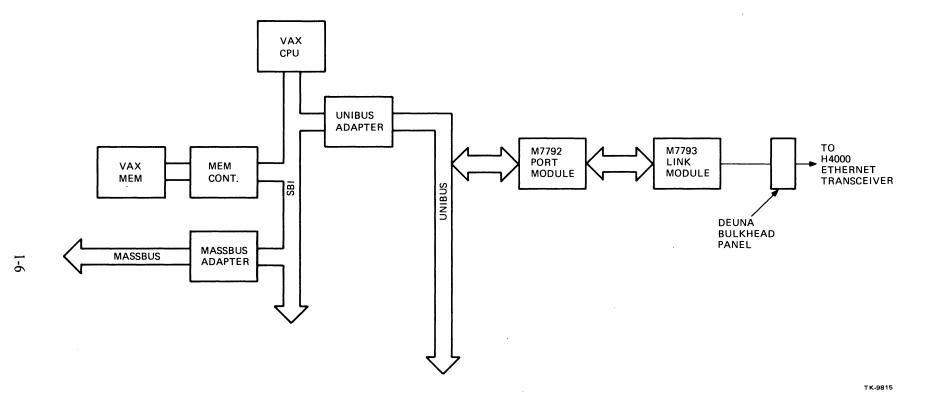

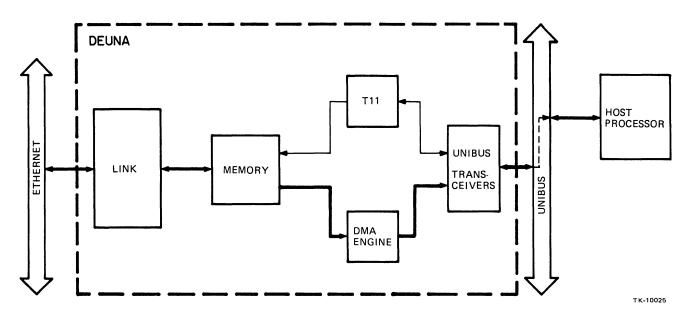

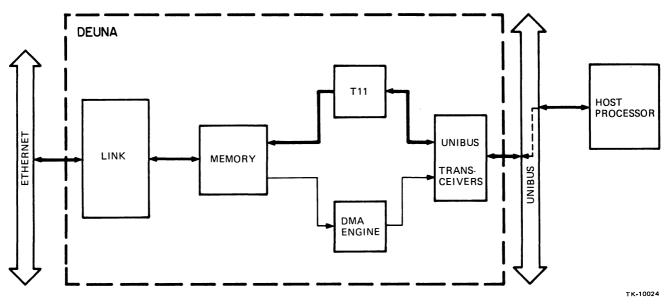

The DEUNA is a microprocessor-based device that, when connected to the DIGITAL H4000 ETHERNET transceiver, provides all the logic necessary to connect VAX-11 and UNIBUS PDP-11 family minicomputers to an ETHERNET local area network (Figures 1-3 and 1-4). The controller performs data encapsulation and decapsulation, data link management, and all channel access functions to ensure maximum throughput with minimum host processor intervention.

тк-9816

Figure 1-3 PDP-11 Host System Block Diagram

.

.

Figure 1-4 VAX-11 Host System Block Diagram

#### **1.4.1 ETHERNET Physical Channel Functions**

The DEUNA provides the following specific ETHERNET physical channel functions necessary to interface to the DIGITAL H4000 ETHERNET transceiver:

#### **During Transmission**

- Generates the 64-bit preamble for synchronization.

- Provides parallel-to-serial conversion of the frame.

- Generates the Manchester encoding of data.

- Ensures proper channel access by monitoring and sensing the carrier from any stations' transmission.

- Monitors the self-test collision detect signal from the DIGITAL H4000 transceiver.

#### **During Reception**

- Senses carrier from any station's transmission.

- Performs Manchester decoding of the incoming bit streams.

- Synchronizes to the preamble and removes it prior to processing.

- Provides serial-to-parallel conversion of the frame.

- Buffers received packets.

#### **1.4.2 ETHERNET Data Link Functions**

The DEUNA provides the following specific ETHERNET data link layer functions:

- Calculates the 32-bit CRC value and places it in the packet sequence field upon transmission.

- Attempts automatic retransmission upon collision detection.

- Checks incoming packets for proper CRC value.

- Performs address filtration.

#### **1.4.3** Data Encapsulation

The ETHERNET packet format is shown in Figure 1-5. Each packet begins with a 64-bit preamble used for synchronization by the receiving station, and ends with a 32-bit packet check sequence. Packets are separated by a specified minimum spacing period of  $9.6 \,\mu s$ .

The destination address field contains the address(es) of the station(s) where the packet is sent. The address may represent: the unique or physical addresses of a particular station; a multicast, or group address, associated with a set of stations; and a broadcast address for all stations on the network.

The source address field specifies the physical address of the transmitting station. Each DEUNA has a unique 48-bit address value determined during manufacture. This value is called the default physical address. The system software can override this value and assign a different physical address.

| PREAMBLE/<br>START BYTE | DEST.<br>ADDRESS | SOURCE<br>ADDRESS | ТҮРЕ    | DATA             | FRAME<br>CHECK<br>SEG. | INTERFRAME<br>SPACING |

|-------------------------|------------------|-------------------|---------|------------------|------------------------|-----------------------|

| 8 BYTES                 | 6 BYTES          | 6 BYTES           | 2 BYTES | 46 TO 1500 BYTES | 4 BYTES                | 9.6 μs<br>דκ-9814     |

Figure 1-5 Format of an ETHERNET Data Packet

The type field is specified for use by high-level network protocols. It indicates how the content of the data field is to be interpreted. The type field is used by higher-level architecture to further decapsulate the data.

The data field may have between 46 and 1500 bytes of data. The DEUNA can be initialized to automatically insert null characters if the amount of data is less than the minimum 46-byte data size.

The packet check sequence contains a 32-bit Cyclic Redundancy Check (CRC) value determined and inserted by the DEUNA during transmission.

#### 1.4.4 Data Decapsulation

The DEUNA continuously monitors the signals transmitted by the DIGITAL H4000 transceiver. After sensing a carrier, the preamble sequence of the received packet is used by the controller for synchronization. It then processes the destination address field through a hardware comparator to determine whether or not the incoming packet is intended for its station. The DEUNA accepts only packets with a destination address that matches one of the following types of address:

- 1. The physical address of the station

- 2. The broadcast address for all stations

- 3. One of the ten multicast group addresses the user may assign to the DEUNA, when desired

- 4. Any multicast address, when desired

- 5. All addresses, when desired

The DEUNA performs a hardware comparison of the 6-byte destination address to determine if there is a match with the station's physical address or with one of the ten user-designated multicast addresses. If necessary, all multicast addresses may be passed to higher-level software for decoding when more than ten multicast address groups are required by the user.

To assist in network management functions and fault diagnosis, the DEUNA can operate in a mode that effectively disregards the internal address filter logic. This allows all packets received from the network to be accepted. The DEUNA verifies the integrity of the received data by performing a 32-bit CRC check on the received packet.

#### 1.4.5 Link Management

The method by the ETHERNET for channel access is called carrier sense, multiple access with collision, detect (CSMA/CD). The DEUNA controls all of the link management functions necessary to successfully place or remove a packet of data on the ETHERNET network. These functions include:

- **Carrier Deference** The DEUNA monitors the physical channel for traffic. When the channel is busy, it defers to the passing packet by delaying any transmission of its own.

- **Collision Detection** Collisions occur when two or more stations attempt to transmit data simultaneously on the channel. The DEUNA monitors the collision sense signal generated by the DIGITAL H4000 transceiver. When a collision is detected, the DEUNA continues to transmit long enough to ensure that all network stations detect the collision.

- **Collision Backoff and Retransmission** When a controller attempts transmission and encounters a collision on the channel, it attempts a retransmission a short time later. The schedule for retransmission is determined by a controlled randomization process. The DEUNA attempts to transmit a total of sixteen times and reports an error if it is not successful.

#### **1.4.6** Functional Overview

The DEUNA is a microprocessor-controlled interface between the UNIBUS (host memory) and the ETHERNET. It has two basic functions: Receive and Transmit.

**1.4.6.1** Receive Function – Figure 1-6 shows the data path through the DEUNA for the receive function. The data travels through the DEUNA as follows:

- 1. Data from the ETHERNET is received by the LINK which:

- Performs Manchester decoding of data

- Decapsulates data

- Filters address

- Converts serial to parallel data

- Checks CRC

- Moves data to local memory and notifies T11 that there is a message to be sent to host memory

- 2. When the message is in local memory, the T11 microprocessor gets the starting address of where the message is to go in host memory and sets up the DMA engine.

- 3. The DMA engine moves the message to host memory.

- 4. After data is moved the T11 informs the host of the message.

Figure 1-6 DEUNA Receive Data Path

**1.4.6.2** Transmit Function – Figure 1-7 shows the data path through the DEUNA for the transmit function. The data travels through the DEUNA as follows:

- 1. The host processor notifies the T11 that there is a message the host wants transmitted on the ETHERNET.

- 2. The T11 moves the message from host memory to local memory via DMA and tells the link there is a message to be transmitted.

- 3. The link transmits the message by doing the following:

- Generates the preamble.

- Performs parallel-to-serial conversion.

- Generates CRC.

- Performs manchester encoding of data.

- Transmits the message.

- If there is a collision on the ETHERNET, attempts to re-transmit the message up to 15 times.

- 4. The T11 notifies the host when the message has been transmitted.

Figure 1-7 DEUNA Transmit Data Path

#### **1.4.7** Diagnostics and Maintenance

The DEUNA utilizes both microdiagnostics and extensive system and network diagnostics to greatly minimize the time to isolate and diagnose a network communication fault. On-board self-test microdiagnostics automatically test the major DEUNA component logic both on powerup and at the user's discretion. Lightemitting diodes on the edge of the port module (M7792) indicate a specific module problem.

The DEUNA does not transmit longer than the maximum ETHERNET packet transmit period. It contains an automatic control to prevent monopolizing the ETHERNET channel. A built-in Time Domain Reflectometry circuit is provided to help find the location and nature of cable faults.

The controller continuously monitors the power applied to the DIGITAL H4000 transceiver to ensure compliance with the tranceiver requirements. In addition, the H4000 provides a positive functional verification (heartbeat) after every attempted transmission which indicates its proper operation, including the collision sense circuitry.

Comprehensive system diagnostics provide loopback capability through the DEUNA, transceiver, or the ETHERNET network itself. The DEUNA allows remote stations to loopback once it has successfully passed the on-board self-test microdiagnostic. This provides both a local and remote station diagnostic capability. Network error conditions are detected and statistics tabulated for use by higher level network management applications.

# **1.5 DEUNA SPECIFICATIONS** Table 1-1 lists the DEUNA specifications.

| Specification                | Description                                                        |  |  |

|------------------------------|--------------------------------------------------------------------|--|--|

| Operating Mode               | Half-duplex                                                        |  |  |

| Data Format                  | ETHERNET specification                                             |  |  |

| Date Rate (Physical Channel) | 10M bits/s                                                         |  |  |

| Network Specifications       | 1024 stations maximum                                              |  |  |

| UNIBUS Bus Loading           |                                                                    |  |  |

| Module Pair                  | 1 dc loads<br>4 ac loads                                           |  |  |

| DC Power Requirements        |                                                                    |  |  |

| Port Module<br>Link Module   | +5 V, 7.0 A<br>+5 V, 9.0 A<br>-15 V, 1.0 A (for H4000 transceiver) |  |  |

| Physical Size                |                                                                    |  |  |

| Port and Link Modules        | Height (hex): 21.4 cm (8.4 in)<br>Length: 39.8 cm (15.7 in)        |  |  |

| Cable Interface Panel        | Height: 10.6 cm (4.0 in)<br>Length: 10.6 cm (4.0 in)               |  |  |

| Operating Environment        |                                                                    |  |  |

| Temperature                  | 10°C to 40°C (50°F to 104°F)                                       |  |  |

| Relative Humidity            | 10 to 90% (noncondensing)                                          |  |  |

| Wet Bulb Temperature         | 28°C (82°F) maximum                                                |  |  |

| Dew Point                    | 2°C (36°F) minimum                                                 |  |  |

| Altitude                     | Sea level to 2.4 km (8,000 ft)                                     |  |  |

| Shipping Environment         |                                                                    |  |  |

| Temperature                  | -40°C to 66°C<br>(-40°F to 151°F)                                  |  |  |

| Relative Humidity            | 0 to 90% (noncondensing)                                           |  |  |

| Altitude                     | Sea level to 9 km (30,000 ft)                                      |  |  |

Table 1-1

DEUNA Specifications

#### **1.6 RELATED DOCUMENTS**

Table 1-2 lists related documents.

| Title                                                                                  | Document Numbers |  |  |

|----------------------------------------------------------------------------------------|------------------|--|--|

| MICRO T-11 Microprocessor User's Guide                                                 | EK-DCT11-UG      |  |  |

| H4000 Technical Description                                                            | EK-H4000-TM      |  |  |

| The ETHERNET, A Local Area Network, Data Link Layer, and Physical Layer Specifications | AA-K759A-TK      |  |  |

| ETHERNET Installation Guide                                                            | EK-ETHER-IN      |  |  |

| Introduction to Local Area Networks                                                    | EB-22714-18      |  |  |

| DEUNA Maintenance Print Set                                                            | MP-10378         |  |  |

#### Table 1-2 Related Hardware and Software Documents

DIGITAL personnel may order hardcopy documents from:

Digital Equipment Corporation 444 Whitney Street Northboro, MA 01532

Attn: Publishing and Circulation Services (NRO3/W3) Order Processing Section

Customers may order hardcopy documents from:

Digital Equipment Corporation Accessories and Supplies Group Cotton Road Nashua, New Hampshire 03060

For information call: 1-800-257-1710

Information concerning microfiche libraries may be obtained from:

Digital Equipment Corporation Micropublishing Group (BUO/E46) 12 Crosby Drive Bedford, MA 01730

### CHAPTER 2 INSTALLATION

#### **2.1 SCOPE**

This chapter provides the necessary information and procedure for installing a DEUNA in a PDP-11 or VAX-11 host system. The chapter is divided into the following sections.

- Unpacking and Inspection Verify that shipment is complete and undamaged.

- Preinstallation Considerations Verify that the host system meets the installation requirements of the DEUNA.

- Preinstallation Preparation Prepare the host system and the DEUNA subsystem for proper operation.

- Installation and Cabling Install and cable the DEUNA in the host system.

- Testing Verify that the DEUNA and the host system are operating correctly.

#### 2.2 UNPACKING AND INSPECTION

Unpacking a DEUNA subsystem consists of removing the equipment from its shipping containers, verifying that there are no missing parts, and inspecting the equipment for damage. Report any damages or shortages to the shipper and notify the DIGITAL representative.

- 1. Before opening the shipping containers, check them for external damage such as dents, holes, or crushed corners.

- 2. Open and unpack each container. Inventory the contents against the shipping list. Table 2-1 lists the parts supplied with each DEUNA subsystem.

#### NOTE Shipping containers and packing materials should be retained if reshipment is contemplated.

3. Inspect each DEUNA part for shipping damage. Check the modules carefully for cracks, breaks, or loose components such as socketed chips.

| Description                          | Part Number |

|--------------------------------------|-------------|

| DEUNA Port Module                    | M7792       |

| DEUNA Link Module                    | M7793       |

| Module Interconnect Cable            | BCO8R-1 (2) |

| Bulkhead Cable Assembly              | 70-18798-08 |

| Bulkhead Interconnect Panel Assembly | 70-18799-00 |

| DEUNA User's Guide                   | EK-DEUNA-UG |

#### Table 2-1DEUNA Parts List

#### 2.3 PREINSTALLATION CONSIDERATIONS

The following factors should be considered before installing a DEUNA to verify that the host system can accept the DEUNA and that it can be installed correctly.

#### **2.3.1 Backplane Requirements**

The DEUNA requires two hex-height, Small Peripheral Controller (SPC) slots that can be configured for Nonprocessor Request (NPR) operation. Two adjacent slots are preferred, but not necessary. Any SPC backplane (DD11-B(REV E) or later) can accept the DEUNA modules. The DEUNA can be placed anywhere on the UNIBUS before all UNIBUS repeaters.

#### **2.3.2** Bus Latency Constraints

Bus latency is an important factor in determining where to place the DEUNA in the backplane. On systems with many high-speed Direct Memory Access (DMA) devices, the bus latency may adversely affect the DEUNA's performance.

To obtain optimum performance, select a backplane location that places DEUNA on the UNIBUS bus before all devices with a lower NPR rate and before all UNIBUS repeaters. The closer the physical placement of the DEUNA to the processor, the higher its DMA device priority. If optimum performance is not a factor, the DEUNA can be installed anywhere on the UNIBUS (before all repeaters) that meets the requirements of the system. Reconfigure the system as necessary to provide the DEUNA with backplane slots at the selected UNIBUS location for the desired performance.

#### **2.3.3 Loading Requirements**

Make sure that system loading capacities are not exceeded as a result of installing the DEUNA subsystem. Tables 2-2 and 2-3 list the UNIBUS loading and power supply current requirements of the DEUNA, respectively.

#### NOTE

Check power supply voltages before and after installation to verify that no overvoltage or overloading conditions exist.

| Modules                  | UNIBUS DC Loads | UNIBUS AC Loads |  |  |

|--------------------------|-----------------|-----------------|--|--|

| M7792 & M7793 (combined) | 1               | 4               |  |  |

#### Table 2-2DEUNA UNIBUS Loading

#### Table 2-3DEUNA Power Chart

| Module | Voltage Rating                               | Maximum<br>Voltage | Minimum<br>Voltage | Backplane<br>Pin |

|--------|----------------------------------------------|--------------------|--------------------|------------------|

| M7792  | + 5 Volts @ 7.0 A                            | + 5.25 Volts       | + 4.75 Volts       | CA2              |

| M7793  | + 5 Volts @ 9.0 A                            | + 5.25 Volts       | + 4.75 Volts       | CA2              |

|        | -15 Volts @ 1.0 A<br>(for H4000 Transceiver) | -15.75 Volts       | -14.25 Volts       | FB2              |

#### 2.4 PREINSTALLATION PREPARATION

Prepare the host system and DEUNA subsystem for proper operation using the following procedure.

#### 2.4.1 Backplane Power Checks and Preparation

Perform the following operations on the backplane slots previously selected for DEUNA module installation.

- 1. With system power OFF, conduct resistance checks on the backplane voltage sources to ground to be sure that no short circuit conditions exist.

- 2. Turn system power ON. Verify that backplane voltages are within specified tolerances. Refer to Table 2-3 for the voltage ranges and backplane pin assignments. Turn system power OFF.

- 3. If present, remove the grant continuity modules.

- 4. If present, remove the Nonprocessor Grant (NPG) jumper wire that runs between backplane pins CA1 and CB1 on the slot selected for installation of the M7792 port module.

#### NOTE

#### If the M7792 port module is removed from the system, be sure to either replace the NPG jumper wire and install a G727 single-height grant module, or install a G7273 dual-height grant module.

#### 2.4.2 Device Address Assignment

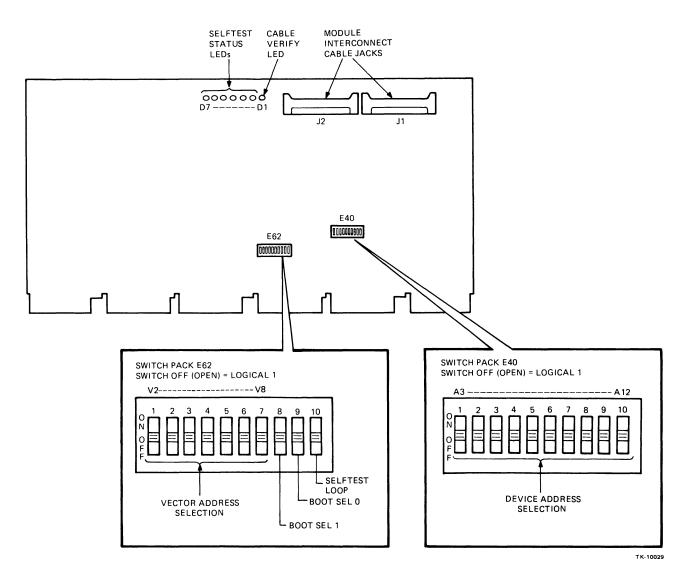

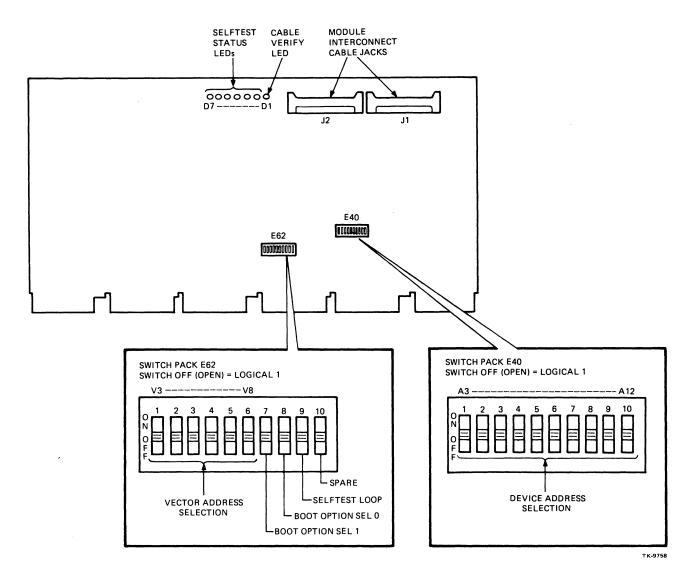

Assign the DEUNA a device address from the Input/Output (I/O) page of memory address space. The first DEUNA being installed in a system must be assigned the address 774510. For the second, and any subsequent DEUNA being installed in the same system, the device address must be selected from the floating address space of the I/O page. The device address is assigned by configuring switch pack E40 on the M7792 port module to the desired address.

**2.4.2.1** First DEUNA Device Address (774510) – Assign device address 774510 to the first DEUNA being installed in a system by configuring switch pack E40 on the M7792 port module as shown below. Note that this address could overlap the twenty-third  $(23^{rd})$  DP11 if present in the system. Refer to Figure 2-1 for the location of E40 on the M7792 module.

|            | M7792 - E40 |            |     |            |            |            |            |     |     |

|------------|-------------|------------|-----|------------|------------|------------|------------|-----|-----|

| <b>S</b> 1 | S2          | <b>S</b> 3 | S4  | <b>S</b> 5 | <b>S</b> 6 | <b>S</b> 7 | <b>S</b> 8 | S9  | S10 |

| OFF        | ON          | ON         | OFF | ON         | OFF        | ON         | ON         | OFF | OFF |

Figure 2-1 M7792 Port Module Physical Layout

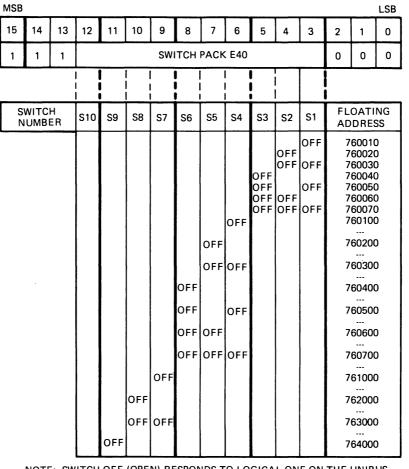

**2.4.2.2** Second DEUNA Device Address (Floating Address) – Assign a device address to the second (or subsequent) DEUNA being installed in a system by configuring switch pack E40 on the M7792 port module to the desired address determined from the floating address allocation. Refer to Table 2-4 for the correlation between switch number and address bit. The ranking device address assignment of the DEUNA is twenty-five (25). Refer to Appendix A for more information on floating address allocation.

NOTE: SWITCH OFF (OPEN) RESPONDS TO LOGICAL ONE ON THE UNIBUS.

тк-9760

#### 2.4.3 Vector Address Assignment

#### NOTE For M7792 Revision B modules, refer to Appendix D of this guide.

Assign the DEUNA a vector address from the reserved vector area of memory address space. The first DEUNA being installed in a system must be assigned the vector 120. The second (and any subsequent) DEUNA being installed in the same system must select the vector address from the floating vector area of reserved vector address space. The vector address is assigned by configuring switch pack E62 on the M7792 port module to the desired vector.

**2.4.3.1** First DEUNA Vector Address (120) – Assign vector address 120 to the first DEUNA in the system by configuring S1-S7 of switch pack E62, on the M7792 port module, as shown below. Note that this vector is also used by the XY11. Refer to Figure 2-1 for the location of E62 on the M7792 module.

|    |    |     | M7 | 792 - E62 |            |            |

|----|----|-----|----|-----------|------------|------------|

| S1 | S2 | S3  | S4 | S5        | <b>S</b> 6 | <b>S</b> 7 |

| ON | ON | OFF | ON | OFF       | ON         | ON         |

|          |        |        | NOTE     |   |         |     |     |    |

|----------|--------|--------|----------|---|---------|-----|-----|----|

| An OFF   | (open) | switch | produces | a | logical | one | (1) | on |

| the bus. |        |        |          |   |         |     |     |    |

**2.4.3.2** Second DEUNA Vector Address (Floating Vector) – To assign a vector address to the second (or subsequent) DEUNA, configure S1-S7 of switchpack E62 on the M7792 port module to the desired vector determined from the floating vector allocation. Refer to Table 2-5 for the correlation between switch number and address bit. The ranking vector address assignment of the DEUNA is forty-seven (47). Refer to Appendix A for more information on floating vector allocation.

| 5 | 14 | 13 | 12 | 11 | 10          | 09          | 08                | 07                                                                 | 06                                                                 | 05                       | 04                              | 03                              | 02                       | 01                                                                                          | 00                                                                                                                                                                                                                                                                                                                          |

|---|----|----|----|----|-------------|-------------|-------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|---------------------------------|---------------------------------|--------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 0  | 0  | 0  | 0  | 0           | 0           |                   | SV                                                                 | итсн                                                               | РАСК                     | E62                             |                                 |                          | 0                                                                                           | 0                                                                                                                                                                                                                                                                                                                           |

|   |    |    |    |    |             |             | Î                 |                                                                    |                                                                    |                          |                                 |                                 | 1                        | 1                                                                                           |                                                                                                                                                                                                                                                                                                                             |

|   |    |    |    |    | SWI1<br>NUM | TCH<br>1BER | S7                | S6                                                                 | S5                                                                 | S4                       | S3                              | S2                              | S1                       |                                                                                             | ATING                                                                                                                                                                                                                                                                                                                       |

|   |    |    |    | ľ  |             |             | OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF<br>OFF<br>OFF | OFF<br>OFF<br>OFF<br>OFF | 3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | 00<br>04<br>10<br>14<br>20<br>24<br>330<br>34<br>40<br>44<br>50<br>54<br>40<br>44<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>54<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50 |

|   |    |    |    |    |             |             |                   |                                                                    | l                                                                  |                          |                                 |                                 |                          |                                                                                             |                                                                                                                                                                                                                                                                                                                             |

| Table 2-5 | Floating  | Vector | Assignment  |

|-----------|-----------|--------|-------------|

|           | 1 IOWCINS |        | 1 KOOLSHINE |

15 0

тк-10019

#### **2.4.4** Boot Option Selection (PDP-11 Host Systems Only)

The DEUNA provides for remote booting and down-line loading of PDP-11 family host systems. These functions are switch selectable via two boot option select switches located on switch pack E62 on the M7792 port module.

#### **NOTE Refer to Appendix B for additional information on DEUNA remote booting and down-line loading.**

When installing a DEUNA in a PDP-11 family host system, configure switches S8 and S9 on switch pack E62 (M7792 module) for the boot function desired. Table 2-6 lists the switch settings and corresponding boot option functions. Refer to Figure 2-1 for the location of E62 on the M7792 module.

When installing a DEUNA in a VAX-11 family host system, set both S8 and S9 on E62 (M7792 module) to the ON (disabled) position of the switch.

#### NOTE An OFF (open) switch produces a logical one (1). This is the ENABLED state of the switch function.

| BOOT SEL 1 | BOOT SEL 0 | Function                                       |

|------------|------------|------------------------------------------------|

| ON*        | ON*        | Remote boot disabled                           |

| OFF        | ON         | Remote boot with system load                   |

| ON         | OFF        | Remote boot with ROM                           |

| OFF        | OFF        | Remote boot with power up boot and system load |

#### Table 2-6Boot Option Selection (M7792 E62 - S8 & S9)

\* Switch settings for a DEUNA installed in a VAX-11 system.

#### 2.4.5 Self-Test Loop (For Manufacturing Use)

#### NOTE For M7792 Revision B modules, refer to Appendix D of this guide.

The self-test loop is provided on the DEUNA for manufacturing testing. This is a switch-selectable feature that allows the on-board self-test diagnostic program, once it is initiated, to continuously loop on itself. This feature is controlled by S10 on switch pack E62 on the M7792 port module and should be disabled during installation.

When installing a DEUNA, disable the self-test loop feature by setting S10 on switch pack E62 (M7792 module) to the ON (closed) position, as indicated in Table 2-7. Refer to Figure 2-1 for the location of E62 on the M7792 module.

| Position         | Function |

|------------------|----------|

| <br>ON* (closed) | DISABLED |

| OFF (open)       | ENABLED  |

Table 2-7 Self-Test Loop Switch (M7792 E62 - S10)

\* Switch setting for normal operation

#### 2.5 INSTALLATION AND CABLING

Install and cable the DEUNA component parts in the host system using the following procedure.

#### 2.5.1 M7792 Port Module Installation

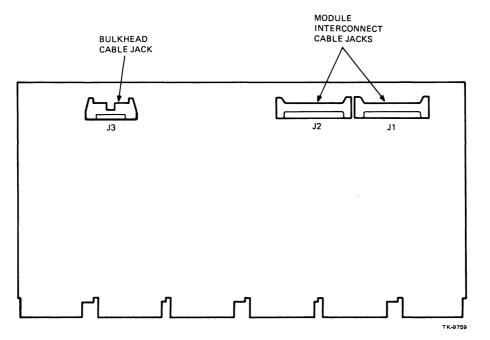

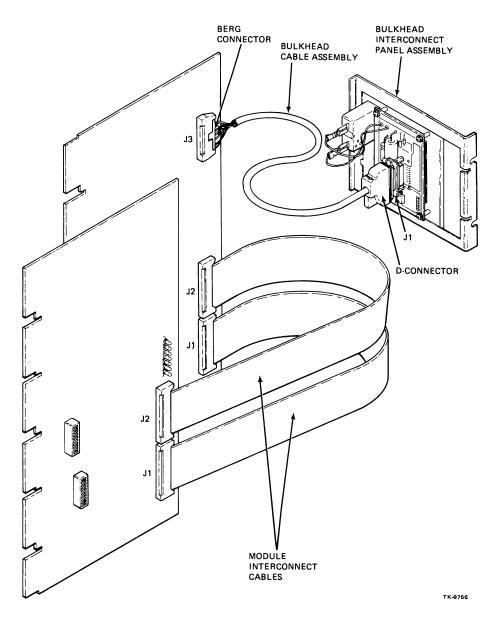

- 1. Locate the two BC08R-1 module interconnect cables supplied.

- 2. Plug one end of one of the cables into J1 on the M7792 module. Plug one end of the second cable into J2. Refer to Figure 2-2 for the physical layout of the M7792 port module and Figure 2-3 for cable connection details.

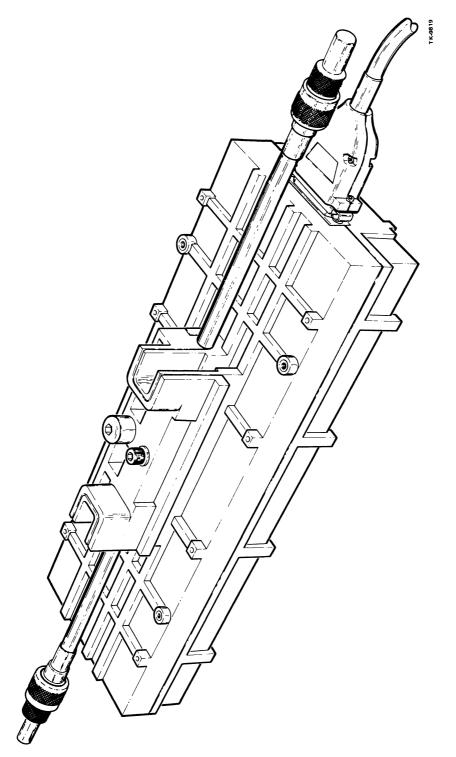

Figure 2-2 M7793 Link Module Physical Layout

Figure 2-3 DEUNA Cable Connection Details

3. Carefully insert and secure the M7792 port module into the SPC backplane slot previously selected (Figure 2-4).

Figure 2-4 Typical Module Installation

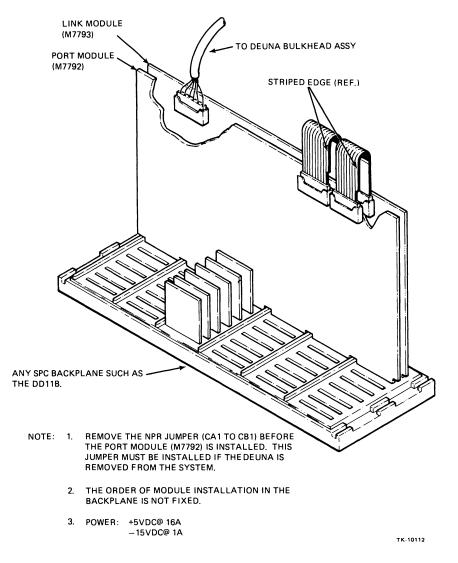

#### 2.5.2 M7793 Link Module Installation

- 1. Slide the M7793 link module into the module guides of a slot adjacent to the M7792 port module. DO NOT insert or secure the module all the way into the slot at this time (Figure 2-4).

- 2. Connect the two BC08R-1 bus cables from J1 and J2 on the port module to J1 and J2 on the link module. There should be NO TWISTS in these cables. Refer to Figure 2-2 for the physical layout of the M7793 module and Figure 2-3 for cable connection details.

- 3. Locate the bulkhead cable assembly supplied (P/N 70-18798-00) and carefully plug the BERG<sup>TM</sup> connector end into J3 on the link module. Do NOT force the connector into the jack. Both the connector and jack are keyed and may be connected together only when aligned correctly.

- 4. Carefully slide the M7793 link module all the way in to the backplane slot and secure it. Fold each of the BC08R-1 cables against the component side of either the port or link module to allow the cables to fit inside of the mounting box.

- 5. Route the bulkhead cable assembly through the cabinet cable ways to the back section of the system cabinet.

### NOTE Make sure that all cables are seated properly.

### 2.5.3 Bulkhead Interconnect Panel Assembly Installation

The Bulkhead Assembly (P/N 70–18799–00) supplied with the DEUNA may be mounted in host system cabinets with or without a cabinet bulkhead.

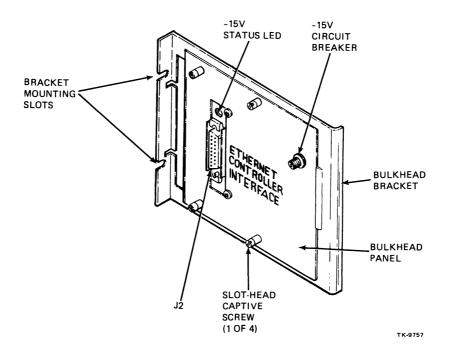

### 2.5.3.1 Cabinets Without a Cabinet Bulkhead -

1. Secure the bulkhead panel to the bulkhead bracket, as shown in Figure 2-5, using the four (4) captive screws.

Figure 2-5 Bulkhead Interconnect Panel Assembly

BERG<sup>™</sup> is a trademark of Berg Electronics.

2. Select a mounting location at the back of the system cabinet with no obstructions. The entire bulkhead assembly should be mounted on the cabinet frame (Figure 2-6).

### CAUTION

The back of the bulkhead panel contains a circuit board which carries -15 V. Be sure this circuitry will not be touching anything that could cause a short circuit on power-up.

Figure 2-6 Bulkhead Interconnect Panel Assembly Installation

- 3. Align the two bulkhead bracket mounting slots (Figure 2-5) with the cabinet frame holes at the selected location and attach two Tinnerman nuts to the cabinet frame at these locations.

- 4. Secure the bracket to the cabinet frame with two  $10 \times 32$  screws.

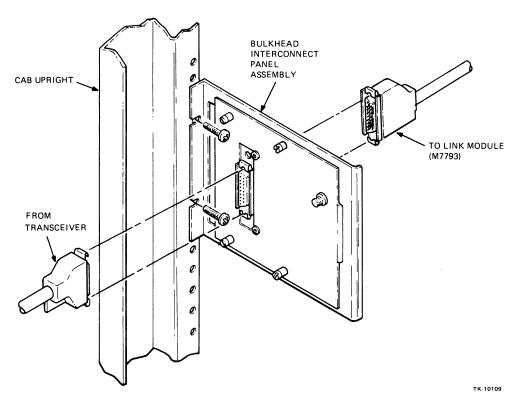

### 2.5.3.2 Cabinets With a Cabinet Bulkhead –

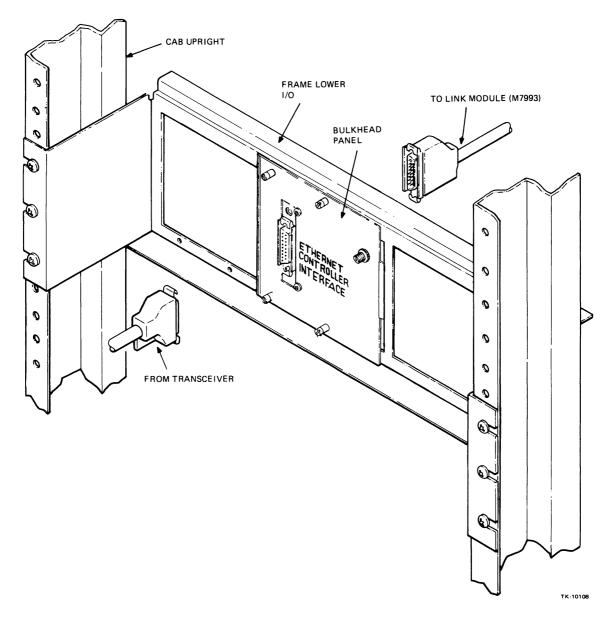

- 1. Mount the bulkhead panel to an available I/O cutout on the cabinet bulkhead (Figure 2-7).

- 2. Secure the bulkhead panel to the cabinet bulkhead with the four captive screws.

Figure 2-7 Typical System Cabinet Bulkhead Installation

**2.5.3.3** Connect the D-Connector – Connect the D-connector on the bulkhead cable assembly to J1 on the back (component side) of the bulkhead panel circuit board as shown in Figure 2-3. Secure the connector and J1 together by sliding the latch assembly located on J1 to the lock position.

### 2.6 TESTING

Perform the following system tests to verify that the DEUNA and the host system are operating correctly.

### NOTE An operational ETHERNET transceiver, or loopback connector, must be connected to the DEUNA for the self-test microdiagnostics to run successfully.

An H4080 loopback test transceiver is not supplied with the DEUNA option. Digital personnel may obtain the H4080 through their local Digital Field Service Branch office. Customers may obtain the H4080 through their local Digital Sales Representative.

### **2.6.1** Postinstallation Power Checks

Perform the following tests on the backplane slots that contain the DEUNA modules.

- 1. Conduct resistance checks on the backplane voltage sources to ground to be sure that no short circuit conditions exist. Refer to Table 2-3 for backplane pin assignments.

- 2. Turn system power on and verify that backplane voltages are within the specified tolerances listed in Table 2-3.

### 2.6.2 Light Emitting Diode (LED) Checks

Eight LEDs are provided on the DEUNA to aid in determining the operational status of the subsystem. Seven of these LEDs are located on the M7792 port module (Figure 2-1); the eighth is located on the bulkhead interconnect panel (Figure 2-5). Refer to Table 2-8 for a summary of the LEDs and their function.

- 1. Connect either an ETHERNET transceiver or a DIGITAL ETHERNET Loopback Connector (Figure 2-8) to J2 on the bulkhead interconnect panel (Figure 2-5).

- 2. Apply system power and wait at least 10 seconds to allow the self-test diagnostics to complete.

- 3. Check the LEDs on the Port module and make sure they cycle ON and OFF. This indicates that the DEUNA sub-tests are running.

Figure 2-8 Digital ETHERNET Loopback Connector

### NOTE If power-up boot is enabled, self-test will not run and all LEDs will be ON.

- 4. Check LEDs D1 D7 on the M7792 port module and verify that they are all lit (ON).

- 5. Check LED D1 on the bulkhead interconnect panel and verify that it is lit (ON).

| Location       | LED     | Function                                                                                                                                                                                                                |  |

|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| M7792 Module   | D1      | When lit (ON), verifies that the two module interconnect cables are properly connected to J1 and J2 on both the port and link modules.                                                                                  |  |

| M7792 Module   | D2 - D7 | Visually indicates the current status of the ROM-based self-test microdiag- nostics. All LEDs are lit (ON) following successful completion of the self-test.                                                            |  |

|                |         | The self-test microdiagnostic program is initiated each time the DEUNA is powered-up, and takes about 10 seconds to run. During this period, these LEDs blink rapidly as the various functions of the DEUNA are tested. |  |

|                |         | NOTE<br>JNA power-up boot is not enabled and the LEDs<br>blink, refer to Chapter 3.                                                                                                                                     |  |

|                |         | When the DEUNA protocol enters the run state under system software,<br>LED D7 blinks ON and OFF at a one second rate (approximate). For<br>more information on the self-test microdiagnostics, see Chapter 3.           |  |

| Bulkhead Panel | Dl      | Indicates that $-15$ V transceiver power is available at bulkhead connector J2. This verifies that                                                                                                                      |  |

|                |         | 1. The bulkhead cable assembly is properly connected at both ends, and                                                                                                                                                  |  |

|                |         | 2. The bulkhead interconnect panel circuit breaker is properly set.                                                                                                                                                     |  |

Table 2-8

DEUNA LED Indicator Functions

### 2.6.3 Diagnostic Acceptance Procedure

The final step in the DEUNA installation procedure is to exercise the M7792 Port module and the M7793 Link module as one complete unit on the UNIBUS bus and on the ETHERNET cable (if possible).

If an ETHERNET transceiver and transceiver cable are available, perform the following steps:

- 1. Connect and lock one end of the transceiver cable to J2 on the bulkhead interconnect panel (Figure 2-5).

- 2. Refer to Table 2-9 and run the appropriate PDP-11 or VAX-11 diagnostic programs (depending on the type of host system). Run the diagnostics in the order listed. When each diagnostic program has run a minimum of five error-free passes, proceed to the next step.

| Diagnostic | PDP-11              | VAX-11                               |

|------------|---------------------|--------------------------------------|

| Repair     | CZUAA* - Standalone | EVDWA REV *.* - Level 3 - Standalone |

| Functional | CZUAB* - Standalone | EVDWB REV *.* - Level 2R - On-Line   |

| DEC/X-11   | CXUAC* - Standalone | N/A                                  |

| Table | 2-9 | DEUNA | Diagnostics |

|-------|-----|-------|-------------|

| 14010 |     |       | Diagnostics |

### NOTES

- 1. VAX-11 Level 2R diagnostics must be run online under VMS.

- 2. PDP-11 standalone diagnostics must be run under the diagnostic supervisor.

- 3. Run the appropriate ETHERNET (NI) exerciser program (CZNID\* for PDP-11 systems or EVPBA REV \*.\* for VAX-11 systems).

If an ETHERNET transceiver and transceiver cable are not available, perform the following steps:

- 1. Connect the H4080 loopback test transceiver (Figure 2-8) to J2 on the bulkhead interconnect panel (Figure 2-5).

- 2. Refer to Table 2-9 and run the appropriate PDP-11 or VAX-11 diagnostic programs (depending on the type of host system). Run the diagnostics in the order listed. When each diagnostic program has run a minimum of five error-free passes, proceed to the next step.

- 3. Disconnect the H4080 loopback test transceiver from J2 on the bulkhead interconnect panel.

**NOTE Refer to Appendix C for additional information on the NI exerciser programs.**

## CHAPTER 3 SERVICE

### **3.1 SCOPE**

This chapter provides information for servicing the DEUNA. It is divided into the following sections:

- Maintenance Philosophy Defines the DEUNA Field Replaceable Unit (FRU).

- Diagnostic Description Describes all VAX-11 and PDP-11 diagnostics for the DEUNA.

- Corrective Maintenance Describes both VAX-11 and PDP-11 corrective maintenance procedures for the DEUNA using troubleshooting flow charts.

A description of the DEUNA Network Interconnect (NI) Exerciser can be found in Appendix C.

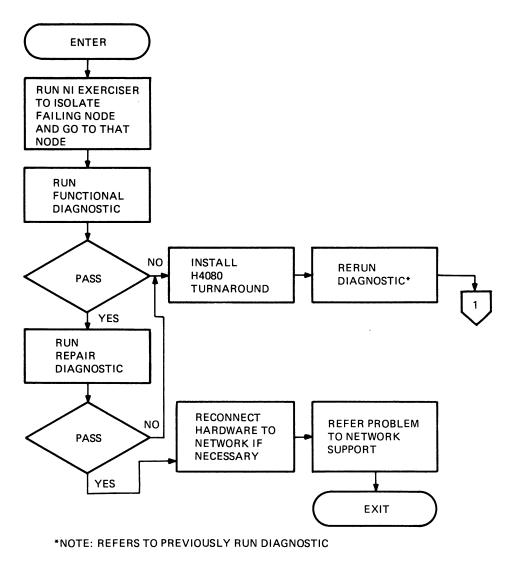

### 3.2 MAINTENANCE PHILOSOPHY

The Maintenance Philosophy for the DEUNA is isolation of the Field Replaceable Unit (FRU). The FRUs for the DEUNA are faulty modules, cables, or the bulkhead assembly.

It is possible for some apparent failures in the DEUNA to be caused by faults in the ETHERNET physical channel; that is, transceiver cable, transceiver, or ETHERNET cable. Faults that can be isolated to the ETHERNET physical channel should be referred to Network support.

#### 3.3 DIAGNOSTIC DESCRIPTION

This section describes the diagnostics available for the DEUNA on both VAX-11 and PDP-11 systems. Section 3.4 describes the proper order for running these diagnostics. The individual diagnostic abstracts provide specific instructions for running each diagnostic.

#### 3.3.1 Self-Test

The DEUNA Self-Test verifies the DEUNA microprocessor, internal memory, the UNIBUS interface, and the link module through various loopback levels. The path from the DEUNA to the transceiver and ETHERNET coaxial cable is also verified during Self-Test.

The ROM-based Self-Test is initiated in two ways: each time the DEUNA is powered up and when a Self-Test Port Command is issued. The Self-Test Port Command is issued by writing a 3 to PCSR0. Refer to Section 4.3 of this document for a description of PCSR0 and the Self-Test Port Command.

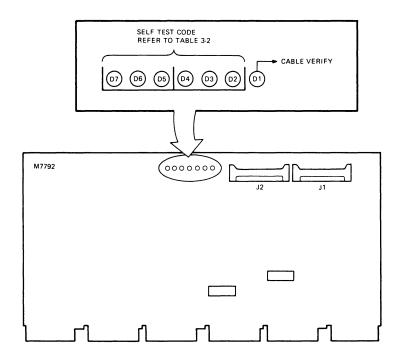

The results of the Self-Test are available on LEDs (D2 through D7) on the Port module (M7792). The execution time of the Self-Test is seven to ten seconds. During execution, the Self-Test LEDs should turn ON and OFF indicating the various tests being performed. If the Self-Test LEDs remain ON and do not cycle ON and OFF, this is considered a DEUNA failure, probably the M7792 module. Refer to Figure 3-1 and Table 3-1 for a description of the Port module LEDs.

In addition to the Self-Test LEDs, one LED on the Port module D1, verifies the cable connection between the Port and Link modules.

NOTE When the DEUNA is in the Running State, LEDs D1 through D6 are constantly on; D7 blinks on and off at a rate of about once per second.