DM C11

IPL microprocessor

user's manual

Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

## **CONTENTS**

|           |                                       | Page   |

|-----------|---------------------------------------|--------|

| CHAPTER 1 | INTRODUCTION                          |        |

| CHAPTER 2 | INSTALLATION                          |        |

| 2.1       | SCOPE                                 | . 2-1  |

| 2.2       | UNPACKING AND INSPECTION              | . 2-1  |

| 2.3       | OPTION DESIGNATIONS                   | . 2-1  |

| 2.4       | MECHANICAL PACKAGING                  | . 2-2  |

| 2.5       | PRE-INSTALLATION PROCEDURES           |        |

| 2.5.1     | General Information                   |        |

| 2.5.2     | Preinstallation Checkout Procedures   | . 2-3  |

| 2.6       | INSTALLATION                          | . 2-4  |

| 2.7       | DEVICE ADDRESSES                      | . 2-5  |

| 2.7.1     | Introduction                          | . 2-5  |

| 2.7.2     | Floating Device Address Assignments   |        |

| 2.7.3     | Device Address Selection              |        |

| 2.8       | VECTOR ADDRESSES                      |        |

| 2.8.1     | Introduction                          |        |

| 2.8.2     | Floating Vector Address Assignment    |        |

| 2.8.3     | Vector Address Selection              |        |

| 2.9       | INSTALLATION CHECKLIST                |        |

|           |                                       |        |

| CHAPTER 3 | PROGRAMMING INFORMATION               |        |

| 3.1       | INTRODUCTION                          | . 3-1  |

| 3.2       | INTERRUPT VECTORS                     |        |

| 3.3       | PRIORITY SELECTION                    | . 3-2  |

| 3.4       | PDP-11 PROGRAMMING INFORMATION        | . 3-2  |

| 3.4.1     | Introduction                          | . 3-2  |

| 3.4.2     | Unibus Control and Status Registers   | . 3-2  |

| 3.4.2.1   | BSELO – Input Register                | . 3-4  |

| 3.4.2.2   | BSEL1 Maintenance Register            | . 3-5  |

| 3.4.2.3   | BSEL2 Output Register                 | . 3-6  |

| 3.4.2.4   | BSEL3 Line Number/Priority Register   | . 3-7  |

| 3.4.2.5   | Data Port Message Formats             | . 3-7  |

| 3.4.3     | Input Transfers                       |        |

| 3.4.4     | Output Transfers                      | . 3-10 |

| 3.4.5     | Initialization                        |        |

| 3.4.6     | DDCMP Start Up                        |        |

| 3.4.7     | Data Transmission                     |        |

| 3.4.8     | Data Reception                        |        |

| 3.4.9     | Control Out Transfers                 |        |

| 3.4.10    | Maintenance Messages                  |        |

| 3.4.11    | Remote Load Detect and Down Line Load |        |

| 3.4.12    | Power Fail Recovery                   |        |

| 3.4.13    | Data Set Control                      |        |

# **CONTENTS** (Cont)

|                                                         | Page                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

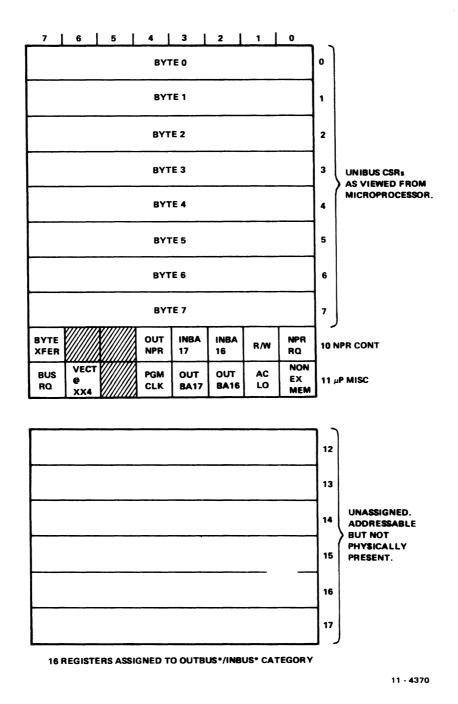

| 3.5                                                     | MICROPROCESSOR CONTROL AND STATUS REGISTERS 3-15                                                                                                                                                                                                                                                                                                                                  |

| 3.5.1                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                      |

| 3.5.2                                                   | OUT BUS*/IN BUS* Registers 0-7                                                                                                                                                                                                                                                                                                                                                    |

| 3.5.3                                                   | NPR Control Register (OUT BUS*/IN BUS* 10)                                                                                                                                                                                                                                                                                                                                        |

| 3.5.4                                                   | Microprocessor Miscellaneous Register                                                                                                                                                                                                                                                                                                                                             |

|                                                         | (OUT BUS*/IN BUS* 11)                                                                                                                                                                                                                                                                                                                                                             |

| 3.5.5                                                   | NPR Bus Address and Data Registers                                                                                                                                                                                                                                                                                                                                                |

|                                                         | (OUT BUS/IN BUS 0-7)                                                                                                                                                                                                                                                                                                                                                              |

| 3.6                                                     | LINE UNIT REGISTERS                                                                                                                                                                                                                                                                                                                                                               |

| 3.6.1                                                   | In/Out Data Silo Registers (10)                                                                                                                                                                                                                                                                                                                                                   |

| 3.6.2                                                   | Out Control Register (11)                                                                                                                                                                                                                                                                                                                                                         |

| 3.6.3                                                   | In Control Register (12)                                                                                                                                                                                                                                                                                                                                                          |

| 3.6.4                                                   | Modem Control Register (13)                                                                                                                                                                                                                                                                                                                                                       |

| 3.6.5                                                   | Sync Register (14)                                                                                                                                                                                                                                                                                                                                                                |

| 3.6.6                                                   | Switch Selectable Registers (15 and 16)                                                                                                                                                                                                                                                                                                                                           |

| 3.6.7                                                   | Maintenance Register (17)                                                                                                                                                                                                                                                                                                                                                         |

| 3.0.7                                                   | Maintenance Register (17)                                                                                                                                                                                                                                                                                                                                                         |

| APPENDIX A                                              | PDP-11 MEMORY ORGANIZATION AND ADDRESSING CONVENTIONS                                                                                                                                                                                                                                                                                                                             |

|                                                         | THE TENEDAL CHOING CONVENTIONS                                                                                                                                                                                                                                                                                                                                                    |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                         | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                     |

| Figure No.                                              | Title Page                                                                                                                                                                                                                                                                                                                                                                        |

|                                                         | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                             |

| 1-1                                                     | DMC11 Remote Line Unit Interface                                                                                                                                                                                                                                                                                                                                                  |

| 1-2                                                     | Directi Remote Ente Cint intertace                                                                                                                                                                                                                                                                                                                                                |

|                                                         | DMC11 Local Line Unit Interface                                                                                                                                                                                                                                                                                                                                                   |

| 1-3                                                     |                                                                                                                                                                                                                                                                                                                                                                                   |

| 1-3<br>2-1                                              | DMC11 Local Line Unit Interface                                                                                                                                                                                                                                                                                                                                                   |

|                                                         | DMC11 Local Line Unit Interface       1-3         Microprocessor Simplified Block Diagram       1-5                                                                                                                                                                                                                                                                               |

| 2-1                                                     | DMC11 Local Line Unit Interface       1-3         Microprocessor Simplified Block Diagram       1-5         Microprocessor Device and Vector Address Switches       2-8                                                                                                                                                                                                           |

| 2-1<br>3-1                                              | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3                                                                                                                                                                                                            |

| 2-1<br>3-1                                              | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3Microprocessor Registers3-16                                                                                                                                                                                |

| 2-1<br>3-1                                              | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3                                                                                                                                                                                                            |

| 2-1<br>3-1                                              | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3Microprocessor Registers3-16                                                                                                                                                                                |

| 2-1<br>3-1<br>3-2<br>Table No.                          | DMC11 Local Line Unit Interface 1-3 Microprocessor Simplified Block Diagram 1-5 Microprocessor Device and Vector Address Switches 2-8 Unibus Control and Status Registers 3-3 Microprocessor Registers 3-16  TABLES Title Page                                                                                                                                                    |

| 2-1<br>3-1<br>3-2<br>Table No.<br>2-1                   | DMC11 Local Line Unit Interface 1-3 Microprocessor Simplified Block Diagram 1-5 Microprocessor Device and Vector Address Switches 2-8 Unibus Control and Status Registers 3-3 Microprocessor Registers 3-16  TABLES  Title Page  Line Unit Option Designations 2-2                                                                                                                |

| 2-1<br>3-1<br>3-2<br>Table No.<br>2-1<br>2-2            | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3Microprocessor Registers3-16TABLESTitlePageLine Unit Option Designations2-2Line Unit Cables2-2                                                                                                              |

| 2-1<br>3-1<br>3-2<br>Table No. 2-1<br>2-2<br>2-3        | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3Microprocessor Registers3-16TABLESTitlePageLine Unit Option Designations2-2Line Unit Cables2-2Guide for Setting Switches to Select Device Address2-7                                                        |

| 2-1<br>3-1<br>3-2<br>Table No. 2-1<br>2-2<br>2-3<br>2-4 | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3Microprocessor Registers3-16TABLESTitlePageLine Unit Option Designations2-2Line Unit Cables2-2Guide for Setting Switches to Select Device Address2-7Guide for Setting Switches to Select Vector Address2-10 |

| 2-1<br>3-1<br>3-2<br>Table No. 2-1<br>2-2<br>2-3        | DMC11 Local Line Unit Interface1-3Microprocessor Simplified Block Diagram1-5Microprocessor Device and Vector Address Switches2-8Unibus Control and Status Registers3-3Microprocessor Registers3-16TABLESTitlePageLine Unit Option Designations2-2Line Unit Cables2-2Guide for Setting Switches to Select Device Address2-7                                                        |

# CHAPTER 1 INTRODUCTION

This manual provides the information necessary to install and operate the DMC11 Microprocessor. Specifically, it covers the DMC11-AL and DMC11-AR Microprocessors, which have their ROMs configured to operate under the discipline of the DDCMP protocol. It is organized into three chapters and one appendix as follows.

Chapter 1 - Introduction Chapter 2 - Installation

Chapter 3 - Device Registers and Programming Information

Appendix A - PDP-11 Memory Organization and Addressing Conventions

In this manual, the term DMC11 denotes the DMC11 Network Link, which consists of a micro-processor module and a line unit module. Explicit references to these modules may or may not be prefixed by the term DMC11.

The DMC11-AR Microprocessor module is designated M8200-YA; the DMC11-AL Microprocessor module is designated M8200-YB.

Where the computers are located remotely and connected via common carrier facilities, DMC11s can be configured to interface to synchronous modems such as Bell models 208 and 209.

The DMC11 ensures reliable data transmission by implementing the DDCMP line protocol in firmware using a high-speed microprocessor. The DDCMP protocol detects errors on the channel interconnecting the systems by using a 16-bit Cyclic Redundancy Check (CRC-16). Errors are corrected, when necessary, by automatic retransmissions. Sequence numbers in message headers ensure that messages are delivered in proper order with no omissions or duplications.

A number of advantages are offered by the DMC11 over conventional interfaces that require a combination of hardware and software to implement a protocol. Programming is greatly simplified. Extensive communications expertise is no longer required when programming the DMC11. PDP-11 memory and processor time are not wasted with instructions implementing the protocol. As a direct result, throughput is enhanced because the DMC11 operates at high speeds and is not delayed when the processor has to perform high priority tasks.

There are two versions of the line unit. The M8202 high-speed line unit is intended for local network applications using coaxial cables. The M8202 contains an integral modem that operates at 1M bps or 56K bps.

The M8201 low-speed unit has no integral modem but contains level conversion logic to interface with EIA/CCITT V24 or CCITT V35 compatible modems at speeds up to 19.2K bps and 56K bps, respectively.

The M8201 and M8202 line units can operate with DDCMP and Bit Stuff protocols.

The line unit is not a stand-alone device. It must be used with a DMC11 Microprocessor.

A separate manual (EK-DMCLU-MM-002) covers the M8201 and M8202 line units.

The microprocessor is a general-purpose control unit that provides a full-duplex parallel data interface between any PDP-11 family central processor and a given DMC11 Line Unit. With the microprocessor/line unit combination, computers can be configured in many different network applications. Where the computers are located at the same facility, DMC11s can be configured for high-speed operation (56,000 or 1,000,000 bps) over inexpensive coaxial cable. The necessary modems are built-in.

Other DMC11 (M8200) features include:

- Down-line loading of satellite computer systems

- Ability to initialize an incorrectly functioning satellite computer system by command over the link (Remote Load Detect)

- Same PDP-11 software supporting local or remote, full- or half-duplex configurations

- Recovery from power failures at either or both ends of a link without loss of data

- 16-bit NPR (DMA) transfers.

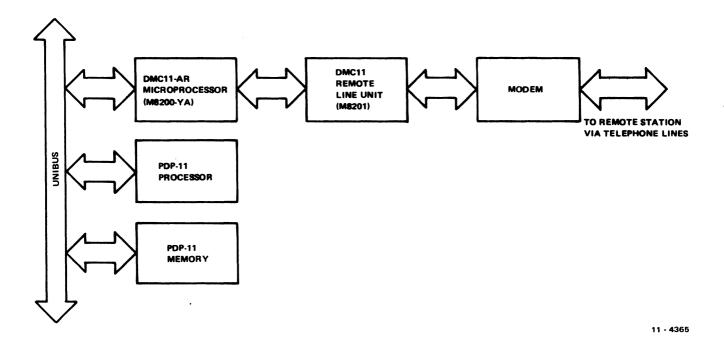

A typical configuration is illustrated in Figure 1-1. Shown is the DMC11-DA (M8201) line unit used for synchronous data communications. The M8201 interface converts data from the DMC11 to a binary serial format compatible with the Electronic Industries Association RS-232C interface specification, used as a standard by nearly all low-speed modern manufacturers.

Figure 1-1 DMC11 Remote Line Unit Interface

The other line unit is the M8202 with an integral modem. The overall system function is identical to that of the M8201. In this case, however, because of the built-in modem, the M8202 interfaces directly to a local coaxial cable.

This configuration uses a single coaxial cable for half-duplex operation or two coaxial cables for full-duplex operation (Figure 1-2).

Figure 1-2 DMC11 Local Line Unit Interface

Figure 1-2 defines, in greater detail, the general interface between the microprocessor and any line unit. First, there are two 8-bit parallel data buses; one is an input bus and the other is an output bus. Two separate buses are used to sustain full-duplex operation. In the line unit, the data source is addressed by the microprocessor using the Input/Output register address bus.

The line unit contains eight registers. During a read operation, which uses the Input bus, the microprocessor uses four addressing bits. The most significant bit is held low to show that a line unit register is being read. The other three bits select the line unit register to be read. During a write operation, which uses the Output register, the microprocessor uses four different addressing bits. The most significant bit is an enabling bit and the other three bits select the line unit register to be written into. Simultaneous addressing on the Input and Output buses is possible.

The remaining bus, the control signal interface, delivers timing and control information to the line unit, such as clock sync and data strobe signals.

Data transfers between the DMC11 and the PDP-11 processor are in the form of the three common bus transactions. They are the NPR bus cycle, the interrupt sequence, and the reading (DATI) and writing (DATO) of DMC11 Control and Status Registers (CSRs).

The Unibus CSRs are composed of eight bytes of device addresses and are accessed by addresses 76XXX0 through 76XXX7. These device addresses are henceforth referred to as Byte Select (BSEL) 0-7 for indicating individual bytes, and SEL, 0, 2, 4, 6 for indicating word transfers (SEL0 consists of BSEL0 and BSEL1, SEL2 consists of BSEL2 and BSEL3, etc...). BSEL0 and BSEL2 are handshaking CSRs, which interlock transfers through a common data port. This data port is accessed through BSEL4-7 (SEL 4, 6).

When the PDP-11 program wishes to transfer data to the DMC11, the program (through BSEL0) sets up a REQUEST IN (RQI) and a function describing the data to be passed. The DMC11 responds by setting READY IN. BSEL4-7 is then loaded by the PDP-11 program, and clears RQI. The DMC11 takes the data and drops RDYI, which completes the exchange.

Similarly, the DMC11 transfers data to the PDP-11 program by setting READY OUT (RDYO) with a function after having loaded BSEL4-7. The PDP-11 program, after reading the required registers, should then clear RDYO, releasing the port for further use.

The DMC11-AR and DMC11-AL are referenced as microprocessors throughout this manual, as well as in other related documentation. This is due to the fact that ROMs are used as controlling elements. The ROMs act as compact logic arrays that replace a large amount of distributive logic. For example, a 2048-bit ROM is organized as 512 words of 4-bits each. Combining four of these ROMs produces 512 words of 16-bits each. Each word in the ROM is pre-programmed and is unalterable. When addressed, a specific word always produces the same output.

The information stored in the ROMs at the word level can be called <u>microsteps</u>. Executing an appropriate series of microsteps is called a <u>microroutine</u>. It can represent a particular instruction or function. The combination of microroutines is called a <u>microprogram</u>.

As the microroutine is being executed, the ROM output signals are sent to the appropriate circuits in the microprocessor to perform the instruction or function that is repesented by the microroutine.

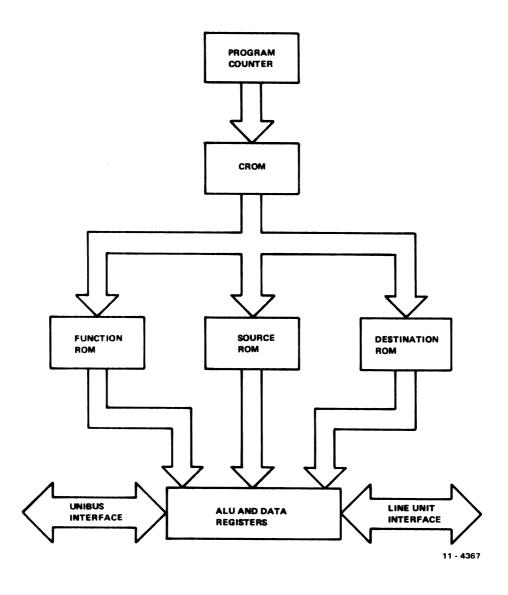

As illustrated in Figure 1-3, the DMC11 essentially connects the Unibus to the line unit interface through internal registers. This allows the data to be processed by the microprocessor as it passes between the two buses. The processing is dependent on the microprogram residing in the microprocessor. Currently, a microprogram is available to accommodate the DDCMP line protocol.

The block diagram in Figure 1-3 very much resembles a processor, hence the term microprocessor. It has a program counter (PC) addressing the microprogram residing in 1K of ROM. Each microinstruction is a 16-bit word. Certain bits of the microinstruction then serve as address bits for three additional ROMs, which control data flow and determine what operation to perform on the operands.

The DMC11 and line unit consist of two separate modules interconnected by a one foot cable. Each is ordered separately. Two microprocessor versions and four synchronous line unit versions are available: local operation at 1M bps, local operation at 56K bps, remote operation with EIA/CCITT V24 compatible modems up to 19.2K bps, and remote operation with CCITT V35 compatible modems up to 56K bps.

Both the DMC11-AR and DMC11-AL microprocessor modules (hex SPC) include a 300 ns bipolar microprocessor, a ROM implementing the DDCMP protocol, local scratchpad memory, and a Unibus interface.

The DMC11-MA line unit module (notched hex) includes a built-in modem for local operation at 1M bps over coaxial cable up to 6,000 feet in length.

NB

Figure 1-3 Microprocessor Simplified Block Diagram

The DMC11-MD line unit module (notched hex) includes a built-in modem for local operation at 56K bps over coaxial cable up to 18,000 feet in length.

Coaxial cables are not included with either line unit. Optional BC03N-A0 coaxial cable is available in 100 foot lengths only. One is required for half-duplex operation and two are required for full-duplex operation.

The two versions of the remote line unit, DMC11-DA and DMC11-FA, use the same module (M8201). Both versions contain level conversion logic that accommodates the EIA/CCITT V24 interface and the CCITT V35 interface. The only difference is the modem cable that is supplied to match the specified interface.

The DMC11-DA is shipped with a 25 foot BC05C cable for the EIA/CCITT V24 interface to accommodate Bell 208 or 209 synchronous modems or their equivalent.

The DMC11-FA is shipped with a 25 foot BC05Z cable for the CCITT V35 interface. This synchronous interface is used in certain European networks and in the domestic Digital Data Service (DDS).

# CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter provides all necessary information for a successful installation and subsequent checkout of the DMC11 microprocessor subsystem.

### 2.2 UNPACKING AND INSPECTION

The microprocessor/line unit system combination arrives at the customer site in one of two ways, either as a part of a complete computer system or as an add-on option. When it arrives as an add-on option, the microprocessor module, line unit module, and associated mounting hardware and cables arrive packaged in a single carton. Inspect the carton visually for any signs of physical damage. Included in the contents of the carton are the following:

- 1. M8200-YA or M8200-YB Microprocessor module

- 2. M8201 or M8202 Line Unit module

- 3. BC08S-1 cable (interconnects microprocessor and line unit)

- 4. BC05C-25 cable (M8201 EIA/CCITT V24 interface only)

- 5. BC05Z-25 cable (M8201 CCITT V35 interface only)

- 6. H325 test connector (M8201 only)

- 7. 12-12528 coaxial cable test connector (M8202 only)

- 8. MAINDEC-11-DZDMC Microprocessor Basic W/R and Up Test

- 9. MAINDEC-11-DZDME Line Unit DDCMP Test

- 10. MAINDEC-11-DZDMF Line Unit Bit Stuff Test

- 11. MAINDEC-11-DZDMG Jump and Free Running Test

- 12. MAINDEC-DEC/XII System Test

- 13. ITEP One Line Test

- 14. EK-DMCUP-MM-001, Microprocessor Manual

- 15. EK-DMCLU-MM-002, Line Unit Manual

## 2.3 OPTION DESIGNATIONS

There are two microprocessors available, both configured to implement the DDCMP protocol only. The DMC11-AR is for remote applications; the DMC11-AL is for local applications.

The various line units and cables are listed in Table 2-1 and 2-2, respectively.

Table 2-1 Line Unit Option Designations

| Option   | Description                                                        |

|----------|--------------------------------------------------------------------|

| DMC11-DA | M8201 Line Unit Module with cable for EIA/CCITT V24 interface      |

| DMC11-FA | M8201 Line Unit Module with cable for CCITT V35 interface          |

| DMC11-MA | M8202-YA Line Unit Module with 1M bps integral modem and no cable  |

| DMC11-MD | M8202-YB Line Unit Module with 56K bps integral modem and no cable |

Table 2-2 Line Unit Cables

| Option   | Description                                                              |

|----------|--------------------------------------------------------------------------|

| BC03N-A0 | 100 foot coaxial cable with connectors, used with M8202 Line Unit module |

| BC05C-25 | 25 foot EIA/CCITT V24 cable for use with DMC11-DA Line Unit              |

| BC05Z-25 | 25 foot CCITT V35 cable for use with DMC11-FA Line Unit                  |

#### 2.4 MECHANICAL PACKAGING

The DMC11 consists of a microprocessor module (hex) and a line unit module (notched hex). These modules plug into any DD11-B Rev E or later, DD11-C, DD11-D, or equivalent SPC system unit. The microprocessor module must always plug into either slot 2 or 3 in the DD11-B or DD11-C. The line unit module may be installed in any of the remaining slots. Should two DMC11s be installed in a single DD11-B, then the line unit module plugs into slot 1 or 4.

The line unit does not interface with the Unibus so module edge connectors A and B are not required. As a result, the corner of the module in the vicinity of the A and B connectors has been removed. This allows the M8201 and M8202 to be installed in the end slots of the DD11-B, C, and D system interfacing units. The module plugs into connectors C, D, E, and F and fits over the Unibus cable connector and short length (approximately 2-1/2 inches) Unibus terminator that are installed in end slot connectors A and B.

The two modules are interconnected by a Berg 40-pin connector and a 1-foot BC08S-1 cable.

## 2.5 PRE-INSTALLATION PROCEDURES

#### 2.5.1 General Information

Installation of the microprocessor/line unit combination should be done in three phases. First, the microprocessor is physically installed then checked and verified with MAINDEC-11-DZDMC. In this manner the microprocessor is checked as a stand-alone module apart from the line unit. Next, the line unit module is installed and operationally verified with MAINDEC-11-DZDME and MAINDEC-11-DZDMR, which also provides an additional confidence factor for the microprocessor. The third and final installation phase involves the execution of MAINDEC-11-DZDMG, which verifies the operational status of both the microprocessor and the line unit as a free running test. Additionally, this test checks the contents of the ROMs (microcode) and the BRANCH instructions.

A minimum of 8K of memory is necessary for execution of the MAINDEC diagnostics.

Check the power supply to ensure against overloading. The microprocessor/line unit total current requirement for the +5 V supply is approximately 8 A. Additionally, the line unit requires  $\pm 15$  V for the silos and the level conversion logic and the integral modem.

Installation requires two adjacent hex SPC slots, one of which can be either the Unibus input or terminator slot if the modules are 2-1/2 inches or less. The DMC11 microprocessor requires a full hex slot, while the line unit fits into any slot in the DD11 backplane. The microprocessor can be installed in the DD11-B Rev E or higher, DD11-C, DD11-D, or equivalent backplanes. Such an equivalent backplane is that used in the PDP-11/04 or PDP-11/34 computers.

## 2.5.2 Preinstallation Checkout Procedures

Before installing the microprocessor module, the following functions must be performed.

- 1. Verify that jumper W1 is installed. This jumper should not be removed in the field. It is removed only at the factory during automated module testing to inhibit the oscillator in the microprocessor clock logic.

- 2. The microprocessor device address must be selected in accordance with Paragraph 2.7.

- 3. The microprocessor vector address must be selected in accordance with Paragraph 2.8.

- 4. Verify that a BR5 priority card is installed in position E75.

- 5. Verify that switch numbers 7 and 9 in the DIP switch package, located in position E76, are both OFF. In this package, switches 1-6 are used for the vector address and switches 8 and 10 are not used.

Switch 7 is the Run Inhibit (RI) switch, which is connected between ground and the CLEAR input of the RUN flip-flop. Normally, it is OFF and the RUN flip-flop cannot be cleared directly. Under normal conditions, initialization of the microprocessor directly sets the RUN flip-flop, which allows the microcode to be executed immediately. Because of an internal malfunction or execution of malicious microcode during power up, it is possible for the microprocessor to hang the Unibus. Now, it is not possible to load the diagnostics to determine the fault. Placing the RI switch in the ON position clears the RUN flip-flop and allows the diagnostics to be loaded.

Switch 9 is the Byte Sel 1 Lockout (BS1) switch. It is related to the "computer in a closet" application, where all programs are down-line loaded. When set, the BS1 switch prevents a runaway program in the PDP-11 processor from preventing a boot or down-line loading operation via the DMC11 link. This switch inhibits all maintenance functions.

#### NOTE

Before installing the microprocessor (M8200), remove the NPR Grant wire that runs between pins CA1 and CB1 on the backplane for the slot that is going to accept the M8200. Do not remove the wire for the slot that is going to accept the line unit (M8201 or M8202).

The M8200 Microprocessor presents one load to the Unibus and the M8201 and M8202 Line Units present no load to the Unibus except for power requirements.

The local DMC11 configuration (DMC11-AL Microprocessor and DMC11-MA or DMC11-MD Line Unit) requires bus placement nearest to the PDP-11 processor; this is due to the high rate of NPR transactions that is required. For example, the DMC11-MA Line Unit (1M bps) requires an average of one NPR every 8  $\mu$ s.

#### 2.6 INSTALLATION

After completing the pre-installation checkout procedures in Paragraph 2.5.2, proceed with the installation as follows:

- 1. Insert the microprocessor module in the proper backplane slot.

- 2. Run MAINDEC-11-DZDMC to verify correct operation of the microprocessor.

#### DIAGNOSTIC NOTE

If the installation is in a system using a PDP-11/04 or other PDP-11 processor that does not have a switch register, a software switch register is used to allow the user the same switch options. If a switch register is available but contains all 1s (177777), the software switch register is used. Refer to the appropriate diagnostic document for further details.

- 3. Check all appropriate switch settings and jumpers on the line unit module in accordance with the recommendations in Chapter 2, Installation, of the line unit manual (EK-DMC11LU-MM-002).

- 4. Insert the line unit module in the proper backplane slot.

- 5. Interconnect the line unit and microprocessor using cable BC08S-1 which is a 1-foot long, 40 conductor flat mylar cable with H856 female connectors on each end. The mating connector on the microprocessor and line unit is an H854 male connector. On the microprocessor, this connector is designated J1. On the M8201 Line Unit, it is designated J2 and on the M8202 Line Unit it is J1.

- 6. On the M8201, install the BC05C-25 cable to connector J1. On the other end of this cable, connect the H325 test connector.

On the M8202, install the 12-12528 coaxial test connector, which ties the two coaxial pigtails together. These two 3-foot cables are soldered to the M8202.

- 7. On the M8202, check that the integral modem clock is within specifications. Refer to the line unit manual.

- 8. On the backplane, check that the supply voltages are within the following tolerances:

|        | Voltage | ,      | Backplane     |  |

|--------|---------|--------|---------------|--|

| Min    | Nominal | Max    | Pin           |  |

| +4.75  | +5.0    | +5.25  | C1A2          |  |

| -14.25 | -15.0   | -15.75 | C1 <b>B</b> 2 |  |

| +14.25 | +15.0   | +15.75 | C1U1          |  |

- 9. Run MAINDEC-11-DZDME and -DZDMF to verify correct line unit operation.

- 10. Run MAINDEC-11-DZDMG to verify correct line unit/microprocessor operation. This diagnostic also tests the microcode and BRANCH instructions.

- 11. Remove the test connector.

For the M8201, connect the BC05C-25 or BC05Z-25 cable to the customer-supplied modem.

# CAUTION The maximum allowable length for the BC05C and BC05Z cable is 50 feet.

For the M8202, connect the pigtails to the customer coaxial cables or the optional 100-foot BC03N-A0 cable.

#### 2.7 DEVICE ADDRESSES

#### 2.7.1 Introduction

Starting with the DJ11, new communications devices are to be assigned floating addresses. The addresses for current production devices are to be retained.

The word floating means that addresses are not assigned absolutely for the maximum number of each communications device that can be used in a system.

## 2.7.2 Floating Device Address Assignments

Floating device addresses are assigned as follows:

- 1. The floating address space starts at location 760010 and extends to location 764000 (octal designations).

- 2. The devices are assigned, in order, by type: DJ11, DH11, DQ11, DU11, DUP11, DMC11, and then the next device introduced into production. Multiple devices of the same type must be assigned contiguous addresses.

- 3. The first address of a new type device must start on a modulo 10<sub>8</sub> boundary, if it contains one to four bus-addressable registers. The starting address of the DH11 must be on a modulo 20<sub>8</sub> boundary because the DH11 has eight registers.

- 4. A gap of 10<sub>8</sub>, starting on a modulo 10<sub>8</sub> boundary, must be left between the last address of one type device and the first address of the next type device. A gap must be left for any device on the list that is not used, if the device following it is used. The equivalent of a gap should be left after the last device assigned to indicate that nothing follows.

- 5. No new type devices can be inserted ahead of a device on the list.

- 6. If additional devices on the list are to be added to a system, they must be assigned contiguously after the original devices of the same type. Reassignment of other type devices already in the system may be required to make room for the additions.

The following examples show typical floating device assignments for communications devices in a system.

## Example 1: No DJ11s, 2 DH11s, 2 DQ11s, 1 DUP11, and 1 DMC11

```

760010

DJ11 gap

760020

DH11 #0 first address

760040

DH11 #1 first address

760060

DH11 gap

760070

DQ11 #0 first address

760100

DO11 #1 first address

760110

DO11 gap

760120

DU11 gap

DUP11 #0 first address

760130

760140

DUP11 gap

760150

DMC11 #0 first address

760160

Indicates no more DMC11s and no other devices following

```

## Example 2: 1 DJ11, 1 DH11, 2 DQ11s, 2 DUP11s, and 2 DMC11s

```

760010

DJ11 #0 first address

760020

DJ11 gap

760040

DH11 #0 first address

760060

DH11 gap

760070

DO11 #0 first address

760100

DQ11 #1 first address

760110

DQ11 gap

760120

DU11 gap

760130

DUP11 #0 first address

760140

DUP11 #1 first address

760150

DUP11 gap

760160

DMC11 #0 first address

760170

DMC11 #1 first address

760200

Indicates no more DMC11s and no other devices following

```

#### 2.7.3 Device Address Selection

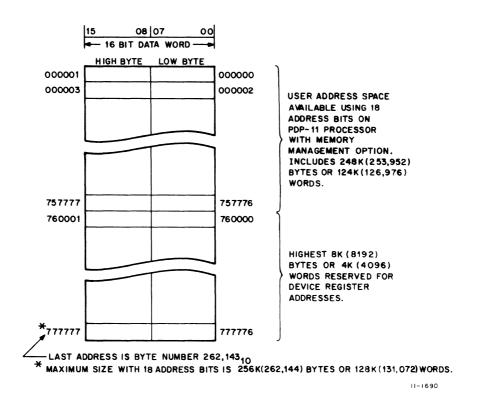

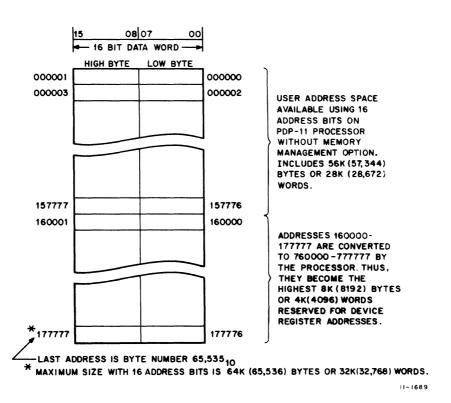

In the floating address space (760010-764000), bits 13-17 are always 1s (function of PDP-11 processor). Appendix A shows the PDP-11 memory organization and addressing conventions. Bits 3-12 are selected by switches in the address decoding logic (Table 2-3). With the switch on (closed), the decoder looks for a 0 on the associated Unibus address line. Bits 0, 1, and 2 are decoded to select 1 of 8 registers.

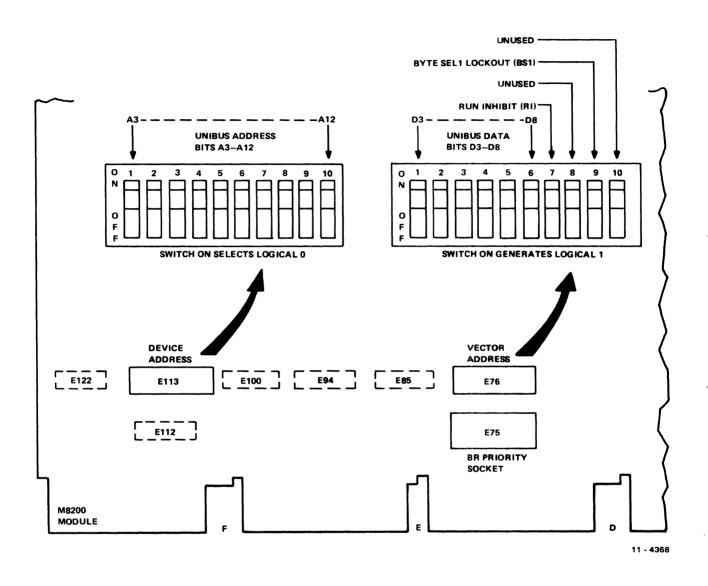

The device address selection switches are contained in one DIP switch package located in position E113. All 10 switches in the package are used. The correlation between switch numbers and address bit numbers is shown in Table 2-3. The ON and OFF positions and the switch numbers are marked on the package. The switches are rocker type and are pushed to the desired position (Figure 2-1).

## 2.8 VECTOR ADDRESSES

#### 2.8.1 Introduction

Communications devices are assigned floating vector addresses. This eliminates the necessity of assigning addresses absolutely for the maximum number of each device that can be used in the system.

Table 2-3 Guide for Setting Switches to Select Device Address

|            |             | <u> </u> |    |   | <u> </u> |             |          | <u> </u> |   |   |         |

|------------|-------------|----------|----|---|----------|-------------|----------|----------|---|---|---------|

| Switch No. | 10          | 9        | 8  | 7 | 6        | 5           | 4        | 3        | 2 | 1 | Device  |

| Bit No.    | 12          | 11       | 10 | 9 | 8        | 7           | 6        | 5        | 4 | 3 | Address |

|            |             |          |    |   |          |             |          |          |   | X | 760010  |

|            |             |          |    | , |          |             |          |          | X |   | 760020  |

|            |             |          |    |   |          |             |          |          | X | X | 760030  |

|            |             |          |    |   |          |             |          | X        |   |   | 760040  |

|            |             |          |    |   |          |             |          | X        |   | X | 760050  |

|            |             |          |    |   |          |             |          | X        | X |   | 760060  |

|            |             |          |    |   |          |             |          | X        | X | X | 760070  |

|            |             |          |    |   |          |             | X        |          |   |   | 760100  |

|            |             |          |    |   |          | X           |          |          |   |   | 760200  |

|            |             |          |    |   |          | X           | X        |          |   |   | 760300  |

|            |             |          |    |   | X        |             |          |          |   |   | 760400  |

|            |             | İ        |    |   | X        |             | X        |          |   |   | 760500  |

|            |             |          |    |   | X        | X           |          |          |   |   | 760600  |

|            |             |          |    |   | X        | X           | X        |          |   |   | 760700  |

|            |             |          |    | X |          |             |          |          |   |   | 761000  |

|            |             |          | X  |   |          |             |          |          |   |   | 762000  |

|            |             |          | X  | X |          |             |          |          |   |   | 763000  |

|            |             | X        |    |   |          |             |          |          |   |   | 764000  |

| NOTES:     | <del></del> | •        |    |   | <b>×</b> | <b>&gt;</b> | <b>×</b> | ×        |   |   | 760740  |

X means switch off (open) to respond to logical 1 on the Unibus.

Switch numbers are physical positions in switch package 1.

Figure 2-1 Microprocessor Device and Vector Address Switches

## 2.8.2 Floating Vector Address Assignment

Floating vector addresses are assigned as follows:

- 1. The floating address space starts at location 300 and proceeds upward to 777. Addresses 500-534 are reserved.

- The devices are assigned in order by type: DC11; KL11/DL11-A, B; DP11; DM11-A; DN11; DM11-BB; DR11-A; DR11-C; PA611 Reader; PA611 Punch; DT11; DX11; DL11-C, D, E; DJ11; DH11; GT40; LPS11; VT20; DQ11; KW11-W; DU11; DUP11; DV11; DMC11.

- 3. If any type device is not used in a system, address assignments move up to fill the vacancies.

- 4. If additional devices are to be added to the system, they must be assigned contiguously after the original devices of the same type. Reassignment of other type devices already in the system may be required.

## 2.8.3 Vector Address Selection

Each drive interrupt vector requires four address locations (two words), which implies only evennumbered addresses. A further constraint is that all vector addresses must end in a 0 or 4. The vector address is specified as a three digit, binary-coded, octal number using Unibus data bits 0-8. Because the vector must end in 0 or 4, bits 1 and 0 are not specified (they are always 0) and bit 2 determines the least significant octal digit of the vector address (0 or 4). The interrupt control logic sends only seven bits (2-8) to the PDP-11 processor to represent the vector address.

The DMC11 is shipped with a BR5 priority selection card installed in the interrupt control logic. This logic generates two vector addresses: RDY I interrupts generate vector addresses of the form XX0, and RDY O interrupts generate vector addresses of the form XX4. For this method of operation, the state of bit 2 is selected by the logic, not by a switch. The two most significant octal digits of the vector address are determined by switches in lines 3-8 (Table 2-4). With the switch OFF (open), a 0 is generated on the associated Unibus data line; with the switch ON (closed), a 1 is generated on the associated Unibus data line.

The vector address selection switches are contained in one DIP package located in position E76 (Figure 2-1). Only 6 of the 10 switches in the package are used for the vector address. The correlation between switch numbers and bit numbers is shown in Table 2-4. The ON and OFF positions and the switch numbers are marked on the package. The switches are rocker type and are pushed to the desired position.

#### 2.9 INSTALLATION CHECKLIST

The following items represent a concise checklist of the important features of the DMC11 installation.

1. Power Requirements

M8200 +5 V @ 4.0 A

M8201 +5 V @ 3.0 A

+15 V @ 0.03 A

-15 V @ 0.31 A

M8202 +5 V @ 3.0 A

+15 V @ 0.18 A

-15 V @ 0.46 A

Table 2-4 Guide for Setting Switches to Select Vector Address

|            | 1   |   |   | <i>f</i> |   |   | 1       |

|------------|-----|---|---|----------|---|---|---------|

| Switch No. | 6   | 5 | 4 | 3        | 2 | 1 | Vector  |

| Bit No.    | 8 7 | 7 | 6 | 5        | 4 | 3 | Address |

|            | X   |   |   | X        | X | X | 300     |

|            | X   |   |   | X        | X |   | 310     |

|            | X   |   |   | X        |   | X | 320     |

|            | X   |   |   | X        | 1 |   | 330     |

|            | X   |   |   |          | X | X | 340     |

|            | X   |   |   |          | X |   | 350     |

|            | X   |   |   |          |   | X | 360     |

|            | X   |   |   | ļ        |   |   | 370     |

|            |     | X | X | X        | X | X | 400     |

|            |     |   |   |          |   |   |         |

|            |     | X |   | X        | X | X | 500     |

|            |     |   |   |          |   |   |         |

|            |     |   | X | X        | X | X | 600     |

|            |     |   |   |          |   |   |         |

|            |     |   |   | X        | X | X | 700     |

| NOTES      |     |   | × |          | • |   | 670     |

#### NOTES:

X means switch off (open) to produce a logical 0 on the Unibus. 1.

- Switch numbers are physical positions in switch package 2.

- Unibus Loading. The M8200 presents one Unibus load. The M8301 and M8202 present no Unibus loads.

- 3. Special Installation Requirements

- M8200 Microprocessor. Before installing, remove the NPR Grant continuity wire that runs between pins CA1 and CB1 on the backplane for the slot that is going to accept the M8200. If a system change requires removal of the M8200, the wire must be replaced.

- M8200 Microprocessor with Local Line Units (DMC11-MA or DMC11-MD). This configuration must be placed on the Unibus closest to the PDP-11 processor because of the high rate of NPR transactions that are required. It must also be placed before a DB11-A Bus Repeater if one is used.

- 4. M8200 Microprocessor Switch Settings

- 160270

a. Address Selection (E113)

| Switch No. | Address Bit |

|------------|-------------|

| 1          | 3           |

| 2          | 4           |

| 3          | 4<br>5<br>6 |

| 4          | 6           |

| 5          | 7           |

| 6          | 8           |

| 7          | 9           |

| 8          | 10          |

| 9          | 11          |

| 10         | 12          |

Switch OFF (open) to respond to logical 1 on Unibus.

Switch ON (closed) to respond to logical 0 on Unibus.

b. Vector Selection (E76)

| Switch No. | Vector Bit |

|------------|------------|

| 1          | 3          |

| 2          | 4          |

| 3          | 5          |

| 4          | 6          |

| 5          | 7          |

| 6          | 8          |

Switch OFF (open) to produce a logical 0 on the Unibus.

Switch ON (closed) to produce a logical 1 on the Unibus.

c. Remaining switches in E76

Switch 7 is RUN INHIBIT (RI) and should be OFF.

Switch 9 is BYTE SEL 1 LOCKOUT (BS1) and should be OFF.

Switches 8 and 10 are not used and should be OFF.

- 5. Line unit switch settings and jumper configuration as shipped.

- a. Switch Settings

- (1) Switch Pack No. 2 (E87 on M8201 and E90 on M8202) All switches should be OFF.

- (2) Switch Pack No. 3 (E88 on M8201 and E91 on M8202) All switches should be OFF.

- (3) Switch Pack No. 1 (E26 on M8201 and E29 on M8202) The switches should be positioned as shown in Table 2-5.

- b. The jumpers should be configured as shown in Table 2-5.

Table 2-5 Configuration of Jumpers and Switch Pack No. 1 on Line Unit

| *<br>Switch No. | DMC11-DA<br>M8201 | DMC11-FA<br>M8201 | DMC11-MA/MD<br>M8202 |

|-----------------|-------------------|-------------------|----------------------|

| 1               | OFF               | OFF               | OFF                  |

| 2               | OFF               | OFF               | OFF                  |

| 3               | OFF               | OFF               | OFF                  |

| 4               | OFF               | ON                | OFF                  |

| 5               | OFF               | OFF               | OFF                  |

| 6               | OFF               | OFF               | OFF                  |

| 7               | ON                | ON                | OFF                  |

| 8               | ON                | ON                | OFF                  |

| Jumper No.      |                   |                   |                      |

| 1               | IN                | IN                | IN                   |

| 2               | IN                | IN                | OUT                  |

| 3               | OUT               | OUT               | OUT                  |

| 4               | IN                | IN                | OUT                  |

| 5               | OUT               | OUT               | OUT                  |

| 6               | Not Present       | Not Present       | OUT (FD)             |

|                 | i i               |                   | IN (HD)              |

## **NOTES**

FD = Full Duplex.

HD = Half Duplex.

<sup>\*</sup>Switch pack no. 1 located at E26 on M8201 and E29 on M8202.

# CHAPTER 3 **PROGRAMMING INFORMATION**

## 3.1 INTRODUCTION

This chapter contains general information necessary for PDP-11 programming of the DMC11 Microprocessor. In general, the information is presented by operational categories such as input transfers, output transfers, etc. Also included are descriptions of the Unibus control and status registers, microprocessor control and status registers, and line unit control and status registers.

The information in this chapter is arranged as follows.

| Description                                 | Paragraph<br>Number |

|---------------------------------------------|---------------------|

| Introduction                                | 3.1                 |

| Interrupt Vectors                           | 3.2                 |

| Priority Selection                          | 3.3                 |

| PDP-11 Programming Information              | 3.4                 |

| Introduction                                | 3.4.1               |

| Unibus Control and Status Registers         | 3.4.2               |

| Input Transfers                             | 3.4.3               |

| Output Transfers                            | 3.4.4               |

| Initialization                              | 3.4.5               |

| DDCMP Start Up                              | 3.4.6               |

| Data Transmission                           | 3.4.7               |

| Data Reception                              | 3.4.8               |

| Control Out Transfers                       | 3.4.9               |

| Maintenance Messages                        | 3.4.10              |

| Remote Load Detect and Down Line Load       | 3.4.11              |

| Power Fail Recovery                         | 3.4.12              |

| Microprocessor Control and Status Registers | 3.5                 |

| Line Unit Registers                         | 3.6                 |

## 3.2 INTERRUPT VECTORS

The DMC11 generates two vector addresses: input (PDP-11 to microprocessor) interrupts generate vector addresses of the form XX0; and output (microprocessor to PDP-11) interrupts generate vector addresses of the form XX4. The conditions that initiate the interrupts are:

XX0 – An interrupt at address XX0 occurs when the PDP-11 requests the port (SEL4 or SEL6) and the microprocessor responds by asserting Ready In (RDYI) and Interrupt Enable In (IEI).

XX4 - An interrupt at address XX4 occurs when, after charging the port with data, the microprocessor asserts Ready Out (RDYO) and Interrupt Enable Out (IEO).

#### 3.3 PRIORITY SELECTION

The priority for the interrupts is selectable on the microprocessor via a plug-in priority selection card. It is shipped with a card that establishes BR5 as the priority level.

#### 3.4 PDP-11 PROGRAMMING INFORMATION

## 3.4.1 Introduction

Programming the DMC11 is described at two levels. The first level describes how a PDP-11 program uses the DMC11 control and status registers together with the interrupt system for transfer of control and status information between the PDP-11 program and the DMC11 microprogram. The second level describes details of these transactions, including formats, details of device and protocol initialization, data transfer, and unusual cases.

In order to successfully program the DMC11, it is not necessary to be familiar with the details of DDCMP protocol operation. These are handled by the DMC11 microprogram. However, some familiarity with the protocol operation is useful in interpreting the significance of the various error counters provided to assess the quality of the circuit connecting the two computers. If a DMC11 is to communicate with a different interface, which uses a software implementation of DDCMP, the person programing the software implementation should consult the DDCMP protocol standard document.

### 3.4.2 Unibus Control and Status Registers

Communication of control and status information between the PDP-11 and the DMC11 uses eight bytes of control and status registers (CSRs). These are addressed as 76XXX0, 76XXX1, 76XXX2, 76XXX3, 76XXX4, 76XXX5, 76XXX6, and 76XXX7. These device addresses are subsequently referred to as Byte Select 0 to 7 (BSEL0 – BSEL7) for indicating individual bytes and as SEL0, SEL2, SEL4, and SEL6 for indicating words.

### NOTE

The CSRs are implemented with Random Access Memory (RAM). Thus, at power on, the CSRs come up in random states. As part of the microprocessor initialization, the CSRs (SEL0-6) are cleared with the exception of bit 15 of SEL0 (RUN) which is set. The lower order 8 bits of SEL0 (BSEL0) are cleared first. Due to the high speed of the microprocessor, the registers are cleared before access by the PDP-11 is possible.

BSEL4-7 comprise a 32-bit data port that is used to pass information between the microprocessor and the PDP-11. The transfer of information from the PDP-11 to the microprocessor is called an Input Transfer, often abbreviated IN or I. The transfer of information from the microprocessor to the PDP-11 is called an Output Transfer, often abbreviated OUT or O. These terms are not to be confused with sending and receiving data on the serial line which are called sending or transmission, and receiving or reception.

BSEL0 controls input transfers and BSEL2 controls output transfers. BSEL1 contains bits used for maintenance purposes which are of no concern to the programmer. It also contains the MASTER CLEAR bit which can be used to initialize the DMC11 microprocessor. BSEL2 is not used. A switch on the microprocessor module prevents the PDP-11 program from clearing RUN or performing other maintenance functions in BSEL1 which would disable the microprocessor's ability to initialize an unattended PDP-11 computer system.

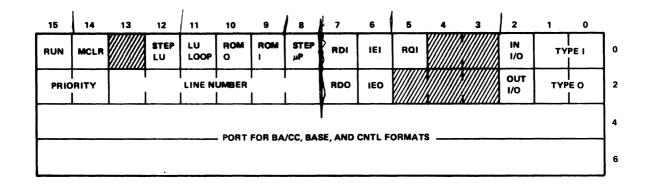

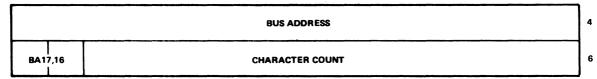

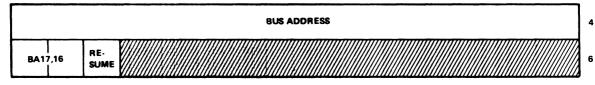

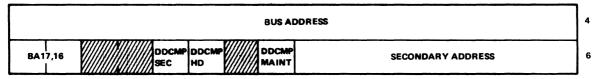

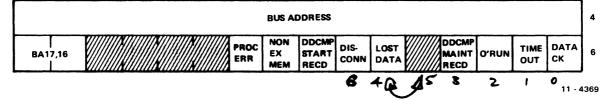

As reference for the programmer, the bit assignments for the Unibus CSRs are shown in Figure 3-1. A detailed description of each register is shown in tabular form.

#### BA/CC I AND BA/CC O FORMATS

#### BASE I FORMAT

## CNTL I FORMAT

### CNTL O FORMAT

Figure 3-1 Unibus Control and Status Registers

LOST DATA = 4.

3.4.2.1 BSEL0 - Input Register - This register comprises the low byte of address 76XXX0 (Figure 3-1).

| Bit  | Name                | Description                          |                                               |                                                                                                                                                                                                                                                 |

|------|---------------------|--------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0, 1 | TYPE INPUT          | These b                              | oits define                                   | the type of input transfer as follows.                                                                                                                                                                                                          |

|      | (TYPE I)            | <b>Bit 1</b><br>0                    | <b>Bit 0</b><br>0                             | Buffer Address/Character Count In (BA/CC I)                                                                                                                                                                                                     |

|      |                     | 0                                    | 1                                             | Control In (CNTL I)                                                                                                                                                                                                                             |

|      |                     | 1                                    | 0                                             | Reserved                                                                                                                                                                                                                                        |

|      |                     | 1                                    | 1                                             | Base In (BASE I)                                                                                                                                                                                                                                |

|      |                     | Each o                               | f these tra                                   | ansfers is explained in detail.                                                                                                                                                                                                                 |

|      |                     | REQU<br>process<br>for pur<br>14-bit | EST IN (sor by the poses of t                 | dress/Character Count In utilized with (RQI). This is a request to the micro-PDP-11 to use the data port (BSEL4-7) transferring an 18-bit bus address and a count must be expressed as a positive                                               |

|      |                     | of the o                             | data port (                                   | - When used with RQI, requests the use (BSEL4-7) from the microprocessor for transferring protocol and/or process tion.                                                                                                                         |

|      |                     | 10 Res                               | erved                                         |                                                                                                                                                                                                                                                 |

|      |                     | used w                               | rith RQI,<br>data port<br>to an 18-           | In provides a base address which, when requests from the microprocessor the (BSEL4-7) for the purpose of transferbit Base Address and RESUME (power                                                                                             |

| 02   | IN I/O              | output<br>new B<br>whether           | (transmit<br>A/CC, therefore this was         | s (BA/CC, etc.) for Input (receive) or c). For example, if BSEL4-7 contained a e microprocessor would need to know a block to be transferred out, or a bufe to be received.                                                                     |

| 3, 4 | RESERVED            | ,                                    |                                               |                                                                                                                                                                                                                                                 |

| 5    | REQUEST IN<br>(RQI) | by the serves use of 40 bits         | PDP-11 vas an into<br>the data p<br>of data f | 11 to request an input transfer. Cleared when the data has been loaded. This bit erlock bit, which is used to request the fort (BSEL4-7) in order to transfer up to from the PDP-11 program. The RQI bit by type of transfer as defined by bits |

| Bit | Name                            | Description                                                                                                                                                                                                             |

|-----|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | INTERRUPT ENABLE<br>INPUT (IEI) | When set, allows the microprocessor to vector interrupts to XX0 having set RDY I.                                                                                                                                       |

| 7   | READY IN<br>(RDY I)             | This is a microprocessor response to RQI. When asserted, it indicates to the PDP-11 program to proceed with loading the data port (BSEL4-7). This bit is cleared by the microprocessor at the end of an input transfer. |

3.4.2.2 BSEL1 Maintenance Register - This CSR contains all maintenance functions other than MASTER CLEAR and is not intended for normal user communications between the PDP-11 program and the microprocessor. These functions override all other control functions. All bits are read/write; however, only MASTER CLEAR is functional if BSEL1 LOCK OUT is set. This register comprises the high byte of address 76XXX0 (Figure 3-1).

| Bit | Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | STEP MICRO-<br>PROCESSOR<br>(STEP MP) | This bit, when set, steps the microprocessor through one instruction cycle, composed of five 60-ns clock pulses. The RUN flip-flop should be cleared before executing this control function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9   | ROM INPUT<br>(ROM I)                  | When set, directs the contents of BSEL6-7 as the next microinstruction to be executed by the microprocessor when STEP MP is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10  | ROM OUTPUT<br>(ROM 0)                 | When set, modifies the source paths for BSEL4-7 to be the contents of the addressed CROM or the next microinstruction executed when STEP MP is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11  | LINE UNIT LOOP<br>(LU LOOP)           | This control function, when asserted, connects the line unit's serial line out back to its serial line in. This is done at the TTL level, before level conversion. When the LINE UNIT LOOP bit is set and RUN is cleared, the STEP LU clock is the only clock available for shifting data out or in. When LU LOOP is set and RUN is set data is clocked at a 10K bps rate. If the H325 loop back connector is installed at the end of the EIA cable with RUN set and not in LU LOOP mode, data is shifted by a free running clock of approximatly 10K bps.  The 1M bps and 56K bps line units require a 12-12528 coaxial adapter installed at the line unit pigtail cables to provide the loop back. The line unit operates at the clock rate of the integral modem in this case. |

| 12  | STEP LINE UNIT<br>(STEP LU)           | This control function is used in conjunction with LU LOOP. When asserted, the transmitter shifts, and when negated, the receiver shifts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13  | RESERVED                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |