KE11-E and KE11-F instruction set options manual

# KE11-E and KE11-F instruction set options manual

digital equipment corporation · maynard, massachusetts

First Edition, January 1973 2nd Printing (Rev), June 1973 3rd Printing, December 1974 4th Printing, January 1975

## Copyright © 1973, 1974, 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

> DEC FLIP CHIP DIGITAL UNIBUS

PDP FOCAL COMPUTER LAB

# INTRODUCTION

This manual describes the KE11-E Extended Instruction Set (EIS) and KE11-F Floating Instruction Set (FIS) Options to the KD11-A Programmed Data Processor for the PDP-11/40 System. These two options are described in one manual because of their interdependency, in that KE11-F cannot be installed without the KE11-E being first installed. The purpose of this manual is to:

- 1. Provide an overall understanding of the functions of these options in a PDP-11/40 System.

- 2. Explain how the KE11-E and KE11-F can be used in software operating systems.

- 3. Describe the options in sufficient detail to enable maintenance personnel to perform on-site troubleshooting and repair.

In this manual each chapter is split in two with the first half of the chapter presenting information concerning the KE11-E Option and the second half being devoted to comparable information for the KE11-F Option. This organization is intended to facilitate greater ease in use by those customers who utilize only the EIS hardware. Note that due to the dependency of FIS hardware on the inclusion of EIS hardware, this split is not used in Chapter 4.

Chapter 1 provides an introduction to the options and lists brief specifications. Chapter 2 contains programming information, listing instructions and illustrating their formats. Chapter 3 gives a discussion of the theoretical principles implemented by these options. Chapter 4 comprises a block diagram discussion, a flow diagram discussion, and detailed descriptions of the logic functions. Content and organization of this chapter are based on the block schematics contained in a separate Engineering Drawings volume. Chapter 5 references the installation and maintenance procedures provided in the *PDP-11/40 System Maintenance Manual*. Specific procedures are given for modifications necessary to the processor, and for use of the Maintenance Module Overlay for these options.

Detailed descriptions of processor, console, Unibus, and memory logic that interface with these options are provided in the following related documents:

PDP-11/40 System Maintenance Manual KD11-A Central Processor Unit Maintenance Manual DEC-11-H40SA-A-D EK-KD11A-MM-001

# CONTENTS

Page

| CHAPTER 1                                                                                                                                                         | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                                                               | KE11-E Extended Instruction Set 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.1.1                                                                                                                                                             | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1.2                                                                                                                                                             | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.1.3                                                                                                                                                             | Specifications 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.2                                                                                                                                                               | KE11-F Floating Instruction Set 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.2.1                                                                                                                                                             | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2.2                                                                                                                                                             | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.2.3                                                                                                                                                             | Specifications 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CHAPTER 2                                                                                                                                                         | PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1                                                                                                                                                               | KE11-E Extended Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.1.1                                                                                                                                                             | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1.2                                                                                                                                                             | Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1.3                                                                                                                                                             | Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2                                                                                                                                                               | KE11-F Floating Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2.1                                                                                                                                                             | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.2.2                                                                                                                                                             | Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2.3                                                                                                                                                             | Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2.4                                                                                                                                                             | Programming Example 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CHAPTER 3                                                                                                                                                         | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CHAPTER 3<br>3.1                                                                                                                                                  | KE11-E Extended Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                   | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1                                                                                                                                                               | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1<br>3.1.1                                                                                                                                                      | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1<br>3.1.1<br>3.1.2                                                                                                                                             | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3                                                                                                                                    | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                                                                           | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-5         Multiplication       3-5         Multiplication       3-5         Algorithms For KE11-E Operations       3-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                                                                  | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-5         Multiplication       3-6         Division       3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1                                                                                                       | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-6         Division       3-8         Arithmetic Shift       3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2                                                                                            | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-6         Division       3-8         Arithmetic Shift       3-10         Arithmetic Shift Combined       3-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3                                                                                 | KE11-E Extended Instruction Set3-1Binary 2's Complement Notation3-1Multiplication3-2Division3-3Basic Shift Operation3-5Algorithms For KE11-E Operations3-5Multiplication3-6Division3-8Arithmetic Shift3-10Arithmetic Shift Combined3-11KE11-F Floating Instruction Set3-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4                                                                      | KE11-E Extended Instruction Set3-1Binary 2's Complement Notation3-1Multiplication3-2Division3-3Basic Shift Operation3-3Algorithms For KE11-E Operations3-5Multiplication3-6Division3-8Arithmetic Shift3-10Arithmetic Shift Combined3-11KE11-F Floating Instruction Set3-12Polish Mode3-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4<br>3.2                                                               | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-5         Multiplication       3-6         Division       3-8         Arithmetic Shift       3-10         Arithmetic Shift Combined       3-11         KE11-F Floating Instruction Set       3-12         Polish Mode       3-12         Floating-Point Arithmetic       3-13                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4<br>3.2<br>3.2.1                                                      | KE11-E Extended Instruction Set3-1Binary 2's Complement Notation3-1Multiplication3-2Division3-3Basic Shift Operation3-5Algorithms For KE11-E Operations3-5Multiplication3-6Division3-8Arithmetic Shift3-10Arithmetic Shift3-10Arithmetic Shift Combined3-12Polish Mode3-12Floating-Point Arithmetic3-13Floating-Point Addition and Subtraction3-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4<br>3.2<br>3.2.1<br>3.2.2                                             | KE11-E Extended Instruction Set3-1Binary 2's Complement Notation3-1Multiplication3-2Division3-3Basic Shift Operation3-3Basic Shift Operation3-5Algorithms For KE11-E Operations3-5Multiplication3-6Division3-8Arithmetic Shift3-10Arithmetic Shift3-10Arithmetic Shift Combined3-12Polish Mode3-12Floating-Point Arithmetic3-13Floating-Point Addition and Subtraction3-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4<br>3.2<br>3.2.1<br>3.2.2<br>3.2.1                                    | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-5         Multiplication       3-6         Division       3-8         Arithmetic Shift       3-10         Arithmetic Shift       3-10         Arithmetic Shift Combined       3-11         KE11-F Floating Instruction Set       3-12         Polish Mode       3-12         Floating-Point Arithmetic       3-13         Floating-Point Addition and Subtraction       3-13         Floating-Point Multiplication and Division       3-14         Algorithms for KE11-F Operations       3-15                                                                                                                                                                                       |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4<br>3.2<br>3.2.1<br>3.2.2<br>3.2.2.1<br>3.2.2.2<br>3.2.3.1            | KE11-E Extended Instruction Set3-1Binary 2's Complement Notation3-1Multiplication3-2Division3-3Basic Shift Operation3-3Basic Shift Operation3-5Algorithms For KE11-E Operations3-5Multiplication3-6Division3-8Arithmetic Shift3-10Arithmetic Shift3-11KE11-F Floating Instruction Set3-12Polish Mode3-12Floating-Point Arithmetic3-13Floating-Point Addition and Subtraction3-13Floating-Point Multiplication and Division3-14Algorithms for KE11-F Operations3-15Floating-Add and Floating-Subtract3-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4<br>3.2<br>3.2.1<br>3.2.2<br>3.2.2.1<br>3.2.2.2<br>3.2.3.1<br>3.2.3.2 | KE11-E Extended Instruction Set       3-1         Binary 2's Complement Notation       3-1         Multiplication       3-2         Division       3-3         Basic Shift Operation       3-5         Algorithms For KE11-E Operations       3-5         Multiplication       3-6         Division       3-8         Arithmetic Shift       3-10         Arithmetic Shift       3-10         Arithmetic Shift       3-10         Polish Mode       3-12         Polish Mode       3-12         Floating-Point Arithmetic       3-13         Floating-Point Addition and Subtraction       3-13         Floating-Point Multiplication and Division       3-14         Algorithms for KE11-F Operations       3-15         Floating-Add and Floating-Subtract       3-16         Floating-Multiply       3-18 |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.5.1<br>3.1.5.2<br>3.1.5.3<br>3.1.5.4<br>3.2<br>3.2.1<br>3.2.2<br>3.2.2.1<br>3.2.2.2<br>3.2.3.1            | KE11-E Extended Instruction Set3-1Binary 2's Complement Notation3-1Multiplication3-2Division3-3Basic Shift Operation3-3Basic Shift Operation3-5Algorithms For KE11-E Operations3-5Multiplication3-6Division3-8Arithmetic Shift3-10Arithmetic Shift3-11KE11-F Floating Instruction Set3-12Polish Mode3-12Floating-Point Arithmetic3-13Floating-Point Addition and Subtraction3-13Floating-Point Multiplication and Division3-14Algorithms for KE11-F Operations3-15Floating-Add and Floating-Subtract3-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

)

J

# **CONTENTS (Cont)**

Page

| 4.1Scope4.2Functional Block Diagram Discussion               |        |

|--------------------------------------------------------------|--------|

|                                                              |        |

| $\tau_{, \omega}$                                            |        |

| 4.3 Detailed Block Diagram Discussion                        | . 4-4  |

| 4.4 Interface                                                |        |

| 4.5 ROM Programming Philosophy                               |        |

| 4.6 Control ROM                                              |        |

| 4.6.1 KD11-A ROM Word                                        |        |

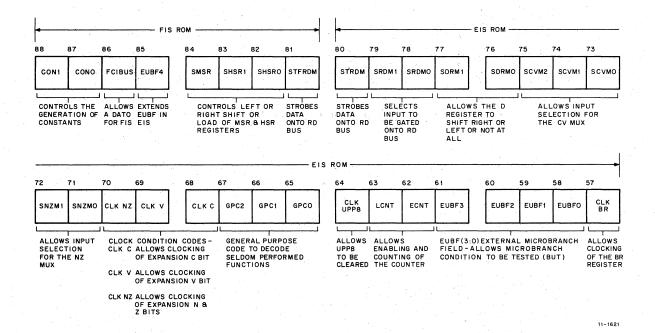

| 4.6.2 KE11-E/F ROM Word                                      |        |

| 4.7 Flow Diagram Discussion                                  |        |

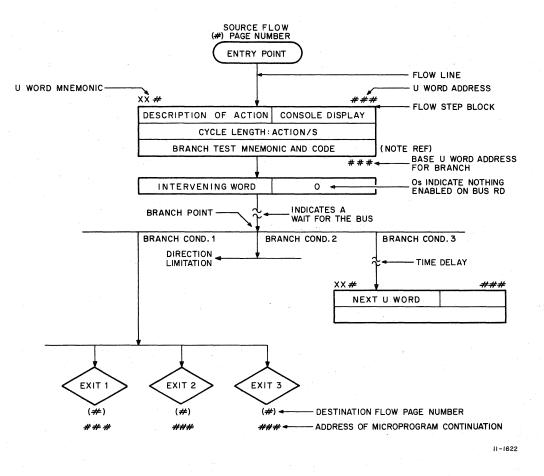

| 4.7.1 Symbology of the Flows                                 |        |

| 4.7.2 KD11-A Flow Discussion                                 |        |

| 4.7.3 KE11-E Flow Diagram Discussion                         | . 4-26 |

| 4.7.3.1 Destination Calculation                              |        |

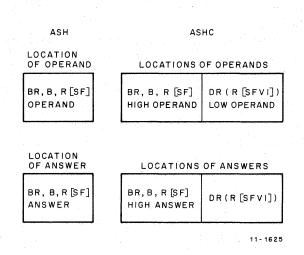

| 4.7.3.2 Arithmetic Shift and Artihmetic Shift Combined       |        |

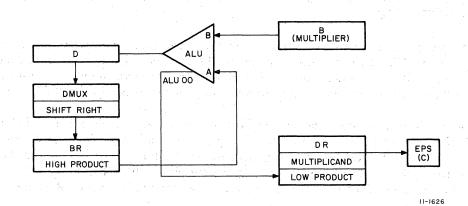

| 4.7.3.3 Multiply                                             |        |

| 4.7.3.4 Divide                                               |        |

| 4.7.4 KE11-F Flow Diagram Discussion                         |        |

| 4.7.4.1 FIS Entry                                            |        |

| 4.7.4.2 FADD and FSUB                                        |        |

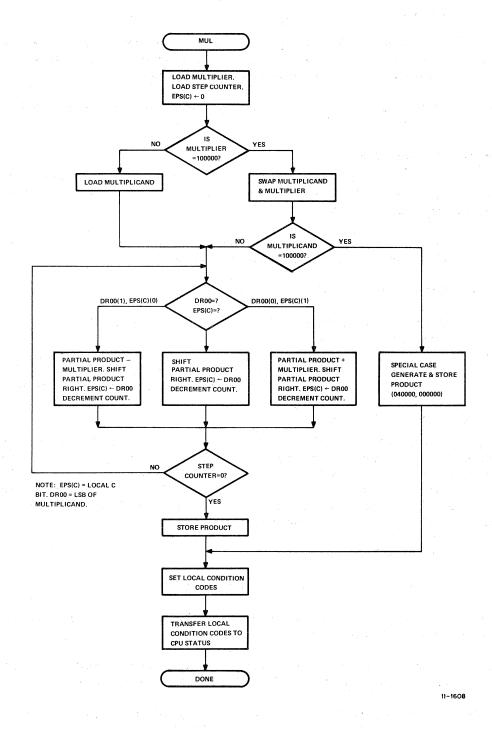

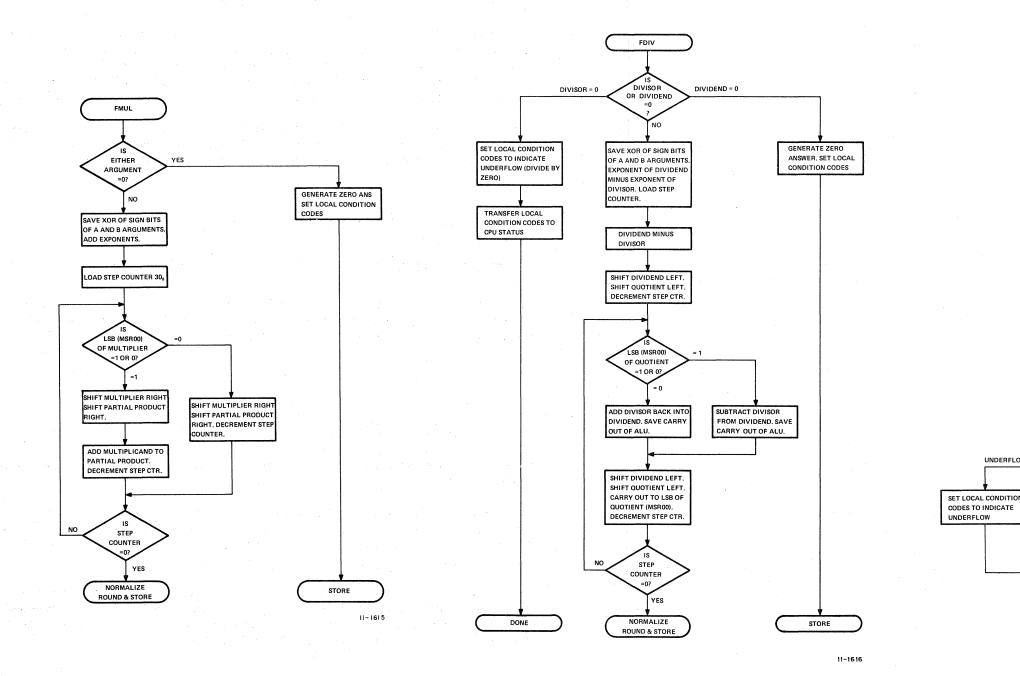

| 4.7.4.3 FMUL                                                 |        |

| 4.7.4.4 FDIV                                                 |        |

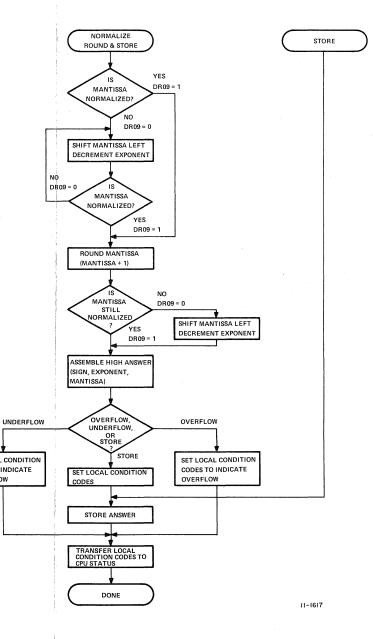

| 4.7.4.5 Normalize, Round and Store                           |        |

| 4.8 Logic Descriptions                                       |        |

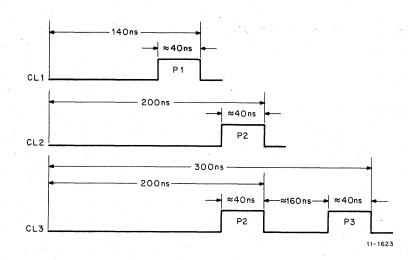

| 4.8.1 Basic CPU Timing                                       |        |

| 4.8.2 BR and DR Registers (Dwg KE-2)                         |        |

| 4.8.3 RDMUX (Dwg KE-3)                                       |        |

| 4.8.4 EUBC Control (Dwg KE-4)                                |        |

| 4.8.5 Control (Dwg KE-5)                                     |        |

| 4.8.6 EPS and Count (Dwg KE-6)                               |        |

| 4.8.7 KE ROM Word (Dwg KE-7)                                 |        |

| 4.8.8 KD ROM Word (Dwgs KE-8 and KE-9)                       |        |

| 4.8.9 HSR and MSR (Dwg KF-2)                                 |        |

| 4.8.10 FRDMUX(15:00) (Dwg KF-3)                              |        |

| 4.8.11 ROM and Control (Dwg KF-4)                            |        |

|                                                              |        |

| CHAPTER 5 INSTALLATION AND MAINTENANCE REFERENCE INFORMATION |        |

| 5.1 Installation                                             | . 5-1  |

| 5.2 Maintenance                                              | . 5-1  |

| 5.2.1 Diagnostic Programs                                    | . 5-2  |

| 5.2.2 Troubleshooting Test Procedures                        | . 5-2  |

| APPENDIX A GLOSSARY OF TERMS                                 |        |

| A.1 General                                                  | . A-1  |

# **ILLUSTRATIONS**

| Figure No. | Title                                              |   |     | Page |

|------------|----------------------------------------------------|---|-----|------|

| 2-1        | EIS Number Formats                                 |   |     | 2-2  |

| 2-2        | EIS Instruction Format                             |   |     | 2-3  |

| 2-3        | ASH Operation                                      |   |     |      |

| 2-4        | ASHC Operation                                     |   |     | 2-5  |

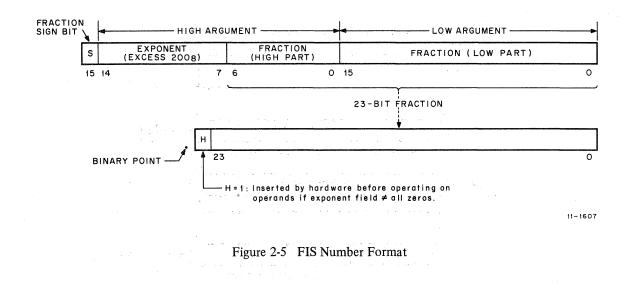

| 2-5        | FIS Number Format                                  |   |     |      |

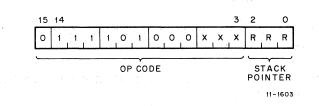

| 2-6        | FIS Instruction Format                             |   |     |      |

| 3-1        | KE11-E MUL Algorithm                               |   |     | 3-6  |

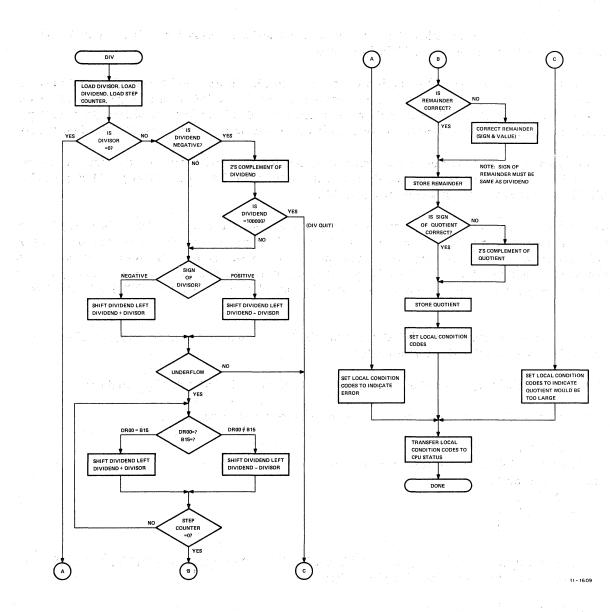

| 3-2        | KE11-E DIV Algorithm                               |   |     | 3-8  |

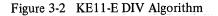

| 3-3        | KE11-E ASH Algorithm                               |   |     | 3-11 |

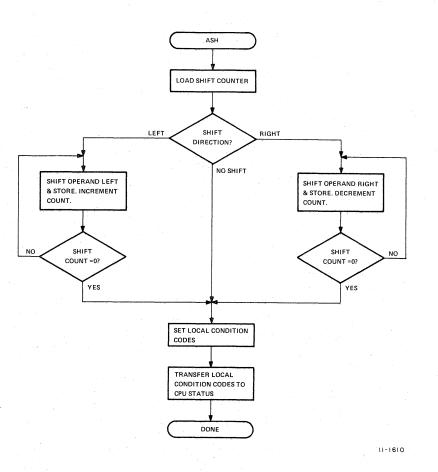

| 3-4        | KE11-E ASHC Algorithm                              |   |     | 3-12 |

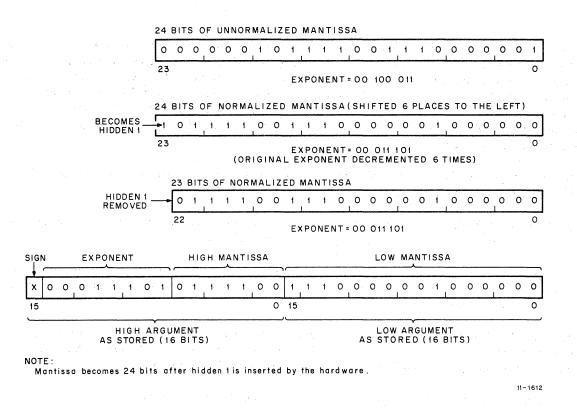

| 3-5        | Floating-Point Representation                      |   |     | 3-14 |

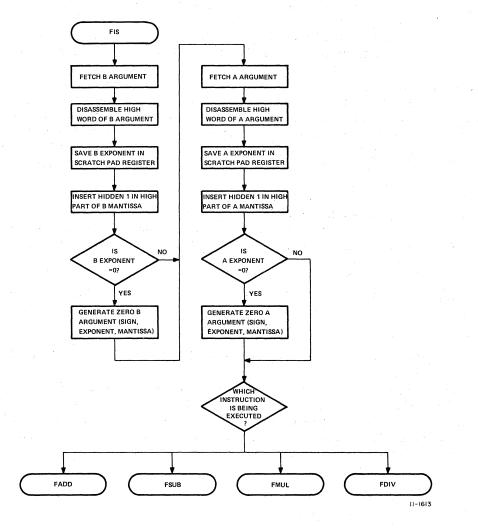

| 3-6        | Floating Entry Algorithm                           |   |     | 3-15 |

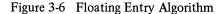

| 3-7        | KE11-F FADD and FSUB Algorithm                     |   |     | 3-17 |

| 3-8        | KE11-F FMUL Algorithm                              | • |     | 3-19 |

| 3-9        | KE11-F FDIV Algorithm                              |   | ••• | 3-19 |

| 3-10       | KE11-F Normalize, Round & Store Algorithm          |   |     | 3-19 |

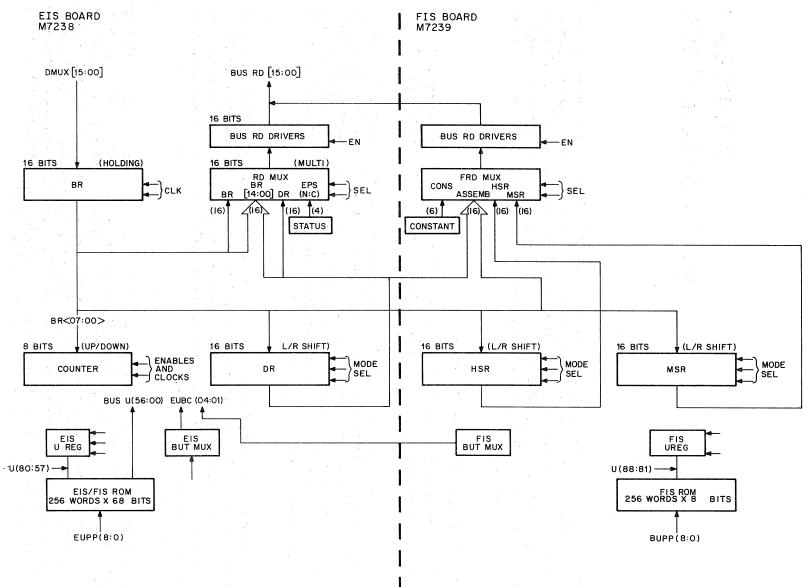

| 4-1        | EIS/FIS Functional Block Diagram                   |   |     |      |

| 4-2        | KE11-E/F/KD11-A Interfacing Signals                |   |     |      |

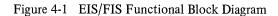

| 4-3        | KD11-A ROM Format                                  |   |     |      |

| 4-4        | KE11-E/F ROM Format                                |   |     |      |

| 4-5        | KD11-A ROM Words Generated by the Options (Sample) |   |     | 4-16 |

| 4-6        | Comparable EIS/FIS ROM Words (Sample)              |   |     |      |

| 4-7        | Flow Diagram Conventions                           |   |     |      |

| 4-8        | ASH and ASHC Locations of Operands and Answers     |   |     |      |

| 4-9        | MUL Flow, Block Diagram                            |   |     |      |

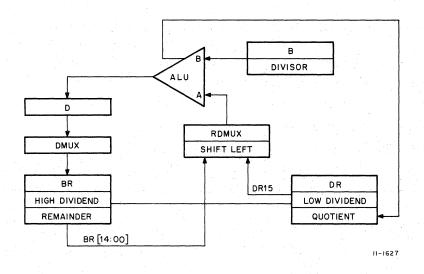

| 4-10       | DIV Flow Block Diagram                             |   |     |      |

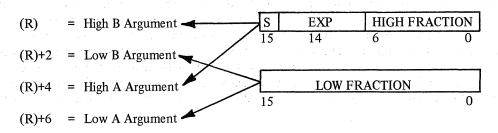

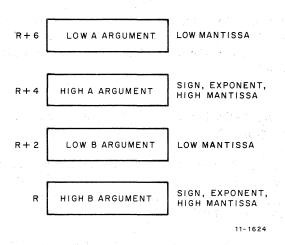

| 4-11       | Floating-Point Arguments Order on the Stack        |   |     |      |

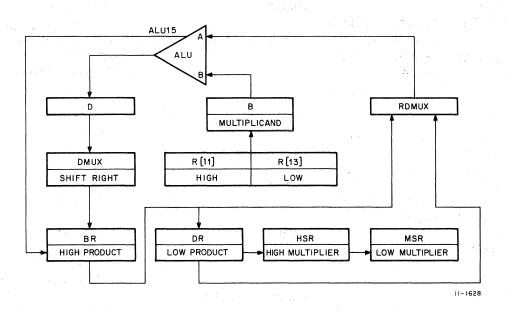

| 4-12       | FMUL Flow, Block Diagram                           |   |     |      |

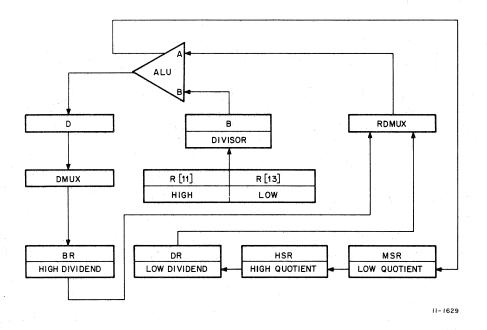

| 4-13       | FDIV Flow Block Diagram                            |   |     |      |

| 4-14       | Basic KD11-A Timing                                |   |     |      |

| 5-1        | KE11-E/F Maintenance Module Overlay                |   |     |      |

# TABLES

## Table No.

)

Ì

)

-

)

J

# Title

Page

| 1-1 | KE11-E (EIS) Specifications 1-1 |

|-----|---------------------------------|

| 1-2 | KE11-F (FIS) Specifications 1-3 |

| 4-1 | KE11-E/F/KD11-A Interface 4-8   |

| 4-2 | KD11-A ROM Word                 |

| 4-3 | KE11-E/F ROM Word               |

| 4-4 | KE-2 Output Signals             |

| 4-5 | KE-3 Output Signals             |

| 4-6 | KE-4 Output Signals             |

| 4-7 | KE-5 Output Signals             |

| 4-8 | KE-6 Output Signals             |

# TABLES (Cont)

| Table No. | Title                                  | Page   |

|-----------|----------------------------------------|--------|

| 4-9       | KE-7 Output Signals                    | . 4-5' |

| 4-10      | KE-8 and KE-9 Output Signals           | . 4-58 |

| 4-11      | KF-2 Output Signals                    | . 4-59 |

| 4-12      | KF-3 Output Signals                    | . 4-60 |

| 4-13      | KF-4 Output Signals                    | . 4-60 |

| 5-1       | KE11-E and KE11-F Diagnostic Programs  | . 5-2  |

| 5-2       | KE11-E/F Maintenance Module Indicators | . 5-3  |

| A-1       | Glossary of Terms                      | . A-   |

# CHAPTER 1 GENERAL DESCRIPTION

This chapter contains a general description of both the KE11-E and KE11-F Options. Mechanical descriptions are given together with engineering specifications for each option. The chapter is divided in half with the EIS information presented first, followed by comparable information for the FIS hardware.

#### 1.1 KE11-E EXTENDED INSTRUCTION SET

The KE11-E Extended Instruction Set is a hardware option to the basic PDP-11/40 Computer System. It is supplied as a pluggable option to the KD11-A Central Processor.

### 1.1.1 Purpose

The KE11-E Option expands the instruction set of the KD11-A Central Processor to provide extended manipulation of fixed-point numbers. When installed, it adds the capability of Arithmetic Shift, Arithmetic Shift Combined, Multiply, and Divide. With these additional instructions, the system can multiply and divide signed 16-bit numbers, and can shift signed 16-bit or 32-bit numbers. Condition codes are set in the processor on the result of each instruction.

#### 1.1.2 Configuration

The KE11-E Option consists of one module. The single-hex  $\times$  8-1/2 in. M7238 module plugs directly into slot 2 (A–F) of the processor system unit. This is a dedicated prewired slot such that no other modules need be moved to accommodate its installation. When installed, the module functions as an extension of the basic KD11-A data paths, branch control, and control ROM. Basic timing of the processor is not degraded by use of this module, nor is the NPR latency affected when its instructions are being executed. Interrupts are serviced at the end of each instruction in the standard manner.

#### 1.1.3 Specifications

Specifications for the KE11-E Option are given in Table 1-1.

| Instructions | Arithmetic Shift (ASH)<br>Arithmetic Shift Combined (ASHC)<br>Multiply (MUL)<br>Divide (DIV) |  |

|--------------|----------------------------------------------------------------------------------------------|--|

| Operations   | Multiplication and division of signed 1<br>Arithmetic shifting of signed 16-bit or           |  |

# Table 1-1KE11-E (EIS) Specifications

| Addressable Registers | None in option. Operands fetched | from core or proce | ssor general registers.                                   |

|-----------------------|----------------------------------|--------------------|-----------------------------------------------------------|

| Timing                | Time = SRC Time + EF Time        |                    |                                                           |

|                       | SRC Mode                         | SRC Time           | e                                                         |

|                       | <b>0</b>                         | 0.28 μs            |                                                           |

|                       | <b>1</b> , $1$ , $1$ , $2$       | 0.78 μs            |                                                           |

|                       | 2                                | 0.98 μs            |                                                           |

|                       | 3                                | 1.74 μs            |                                                           |

|                       | 4                                | 0.98 μs            |                                                           |

|                       | 5                                | 1.74 μs            |                                                           |

|                       | 6                                | 1.74 μs            |                                                           |

|                       | <b>.</b>                         | 2.64 μs            |                                                           |

|                       | Instr                            | EF Time            | Notes                                                     |

|                       | MUL                              | 8.88 µs            |                                                           |

|                       | DIV                              | 11.30 μs           |                                                           |

|                       | ASH (right)                      | 2.58 µs            | +0.30 µs/shift                                            |

|                       | ASH (left)                       | 2.78 µs            | +0.30 µs/shift                                            |

|                       | ASHC (no shift)                  | 2.78 μs            |                                                           |

|                       | ASHC (shift)                     | 3.26 µs            | +0.30 µs/shift                                            |

| Size                  | Single Hex module (M7238)        |                    | n an the space of the sec<br>Sector sector space from the |

| Power Required        | +5V, 2.3A                        |                    | an an Araba<br>An Anna Anna Anna<br>An Anna Anna Anna An  |

## Table 1-1 (Cont) KE11-E (EIS) Specifications

## 1.2 KE11-F FLOATING INSTRUCTION SET

The KE11-F Floating Instruction Set is a hardware option to the basic PDP-11/40 Computer System. It is supplied as a pluggable option to the KD11-A Central Processor and requires that the KE11-E described above be installed as a prerequisite.

#### 1.2.1 Purpose

The KE11-F Floating Instruction Set (FIS) enables direct operations on single-precision 32-bit words in floating-point arithmetic. Since the KE11-E is a prerequisite to the KE11-F, extended manipulation of fixed-point numbers is available as well. The KE11-F Option further extends the PDP-11/40 instruction set to include Floating Add, Floating Subtract, Floating Multiply, and Floating Divide. As with the KE11-E, condition codes in the Processor Status Register are set on the result of each instruction. The prime advantage of this option is increased speed without the necessity of writing complex floating-point software routines.

#### 1.2.2 Configuration

The KE11-F Option consists of one single-quad  $\times 8 \cdot 1/2$  in. M7239 module with the KE11-E Option described above being a prerequisite. This FIS module plugs directly into slot 1 (A–D) also a dedicated prewired slot in the basic KD11-A. No degradation of processor timing or NPR latency is effected by the use of this option. Floating instructions are aborted if a BR request is issued before the instruction is within approximately 8  $\mu$ s of completion, at which time the Program Counter (PC) is adjusted to point to the aborted floating instruction so that the instruction will be restarted upon return from the interrupt.

# 1.2.3 Specifications

)

)

Specifications for the KE11-F Option are given in Table 1-2.

|                       | KE11                                                                                                                                  | Table 1-2<br>-F (FIS) Spec       |                                                |                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------|------------------------------------|

| Prerequisite          | KE11-E Ex                                                                                                                             | tended Instru                    | action Set Option                              |                                    |

| Instructions          | Floating-point Addition (FADD)<br>Floating-point Subtraction (FSUB)<br>Floating-point Multiply (FMUL)<br>Floating-point Divide (FDIV) |                                  |                                                |                                    |

| Operations            | Single-precision floating-point addition, subtraction, multiplication, and division of 24-bit numbers                                 |                                  |                                                |                                    |

| Addressable Registers | None in option. Operands fetched from core.                                                                                           |                                  |                                                |                                    |

| Size                  | Single-quad module (M7239)                                                                                                            |                                  |                                                |                                    |

| Power Required        | +5V, 1.1A (typical)                                                                                                                   |                                  |                                                |                                    |

| Timing                | Time = Basic Time + Binary Point Alignment Time + Normalization Time                                                                  |                                  |                                                |                                    |

|                       | Instr                                                                                                                                 | Basic<br>Time* μs                | Binary Point<br>Alignment Time<br>Per Shift µs | Normalization Time<br>Per Shift μs |

|                       | FADD<br>FSUB<br>FMUL<br>FDIV                                                                                                          | 18.78<br>19.08<br>29.00<br>46.27 | 0.30<br>0.30<br>                               | 0.34<br>0.34<br>0.34<br>0.34       |

\*Basic instruction times for FADD and FSUB assume exponents are equal or differ by one.

1-3

# CHAPTER 2 PROGRAMMING

This chapter is devoted to general programming information for the KE11-E and KE11-F Options. It provides general descriptions of their operation, the formats and instructions for each. In addition, programming examples are supplied for each option. This chapter is intended merely as an introduction to the programming of this hardware. For more detailed information refer to the pertinent software documentation generated for these options. As with Chapter 1, information has been separated for each option.

#### 2.1 KE11-E EXTENDED INSTRUCTION SET

There are no addressable registers in the KE11-E Option. EIS operands are fetched from either core memory or from the general processor registers. The result of each operation is stored in the general registers.

#### 2.1.1 Operation

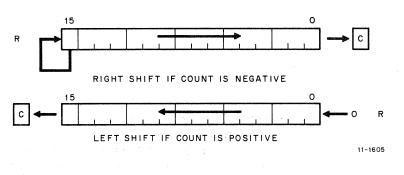

When the <u>Arithmetic Shift (ASH)</u> instruction is used, the contents of the selected register is shifted right or left the number of places specified by a count. This shift count is a 6-bit, 2's complement number which is the least significant 6 bits of the source operand. If the count is positive, the number is shifted left; if it is negative, the number is shifted right. This allows for shifts from 31 positions left to 32 positions right (+31 to -32) although a shift of greater than 16 places loses all significance. A count of 0 causes no change in the number.

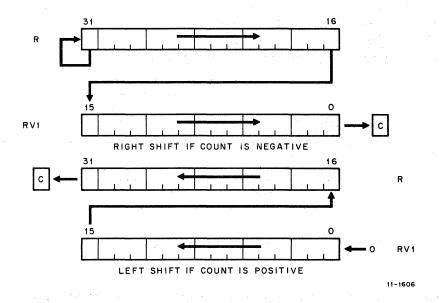

When the Arithmetic Shift Combined (ASHC) instruction is used, the contents of the register (R) and the register ORed with 1 (RV1) are treated as a single 32-bit word. Register RV1 represents bits (15:00), register R represents bits (31:16). This 32-bit word is shifted right or left the number of places specified by a count. This shift count is the same as that described for the ASH instruction and permits shifts from +31 to -32. If the selected register (R) is an odd number, then R and RV1 are the same. In this case, the right shift becomes a rotate and the 16-bit word is rotated right the number of bits specified by the count for up to 16 shifts.

When the <u>MUL</u>tiply (MUL) instruction is used, the contents of the Destination Register and the source are multiplied as 2's complement integers. The result is stored in the Destination Register R and the register ORed with 1 (RV1). If the register is odd, only the low-order product is stored. This instruction multiplies full 16-bit numbers.

When the <u>DIV</u>ide (DIV) instruction is used, a 32-bit dividend in R and RV1 is divided by a 16-bit divisor to provide a 16-bit quotient and a 16-bit remainder. The sign of the remainder is always the same as the sign of the dividend unless the remainder is 0. Overflow is indicated if more than 16 bits are required to express the quotient. In this case, the instruction is aborted. If the content of the Source Register is 0, indicating divide by 0, an overflow is indicated.

#### 2.1.2 Formats

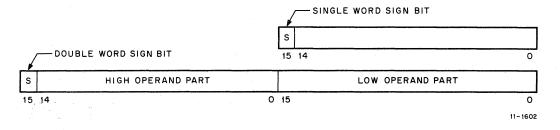

The number formats for the KE11-E Option are shown in Figure 2-1. A single word is 16-bits long and a double word is 32-bits long. In the single word, bit 15 is the sign of the number; and in the double word, the sign bit is bit 15 of the high number part. The S bit is 0 for positive quantities and is 1 for negative quantities.

Figure 2-1 EIS Number Formats

## 2.1.3 Instructions

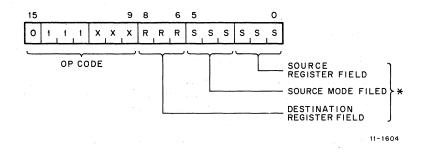

The EIS instruction format is shown in Figure 2-2. It is a double operand instruction in which bits (15:09) comprise the Op code, bits (08:06) designate the Destination Register field (RRR), bits (05:03) indicate the Source Address Mode (SSS), and bits (02:00) specify the Source Address Register (SSS). The octal coding is in the form 07XRSS. There are four EIS instructions, as follows:

| MUL 070RSS                 |                                                                                  |                                                                                                                                                           |

|----------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAT IT 4:1                 |                                                                                  |                                                                                                                                                           |

| MULtiply                   |                                                                                  |                                                                                                                                                           |

| Operation:                 | R, RV1 ← R X(SRC)                                                                |                                                                                                                                                           |

| •                          |                                                                                  |                                                                                                                                                           |

| Condition Codes:           | N: set if product is $< 0$ ; cleared oth                                         | nerwise                                                                                                                                                   |

| condition codes.           | <ul> <li>Z: set if product is &lt; 0; cleared off</li> <li>V: cleared</li> </ul> |                                                                                                                                                           |

|                            |                                                                                  | $2^{15}$ or is greater than or equal to $2^{15}-1$ ; cleared                                                                                              |

| Description:               | are multiplied and stored in the Dest                                            | ister R and source taken as 2's complement integers tination Register R and the succeeding register $RV1$ w-order product is stored. Assembler syntax is: |

|                            | MUL S, R. (Note that the actual dest odd.)                                       | ination is R, RV1 which reduces to just R when R is                                                                                                       |

| Example:                   | 16-bit product (R is odd)                                                        |                                                                                                                                                           |

| 000241<br>012701<br>070127 |                                                                                  | ;Clear carry condition code                                                                                                                               |

| 1034xx                     |                                                                                  | ;Carry will be set if                                                                                                                                     |

|                            |                                                                                  | ;product is less than                                                                                                                                     |

|                            |                                                                                  | $-2^{15}$ or greater than or                                                                                                                              |

|                            |                                                                                  | ;equal to 2 <sup>15</sup>                                                                                                                                 |

|                            |                                                                                  | ;no significance lost                                                                                                                                     |

|                            | <b>Before</b><br>(R1)=000400                                                     | After<br>(R1)=004000                                                                                                                                      |

\*Note that for the EIS instructions the Source Register is considered the Destination since the answer is stored in that register. The Destination Mode and Register Field are considered to be the source. This is not consistent with other PDP-11 family instruction formats but is used throughout the discussions of the EIS instructions in this manual.

Figure 2-2 EIS Instruction Format

| DIV | 071RSS |

|-----|--------|

|     |        |

DIVide

**Operation**:

Condition Codes:

$R \leftarrow R, RV1 \div (SRC) RV1 \leftarrow Remainder$

N: set if quotient < 0; cleared otherwise.

Z: set if quotient = 0; cleared otherwise.

- V: set if source = 0 or if the absolute value of the register is larger than the absolute value of the source. (In this case, the instruction is aborted because the quotient would exceed 16 bits.)

- C: set if divide by 0 attempted; cleared otherwise.

Description:

The 32-bit 2's complement integer in R and RV1 is divided by the source operand (SSS). The quotient is placed in R; the remainder is placed in RV1 with the same sign of the dividend. R must be even.

Example:

005000 012701,20001 071027,2 CLR R0 MOV #20001,R1 DIV #2, R0

Before (R0)=000000 (R1)=020001 After (R0)=010000 (R1)=000001

Quotient Remainder

ASH 072RSS

Arithmetic SHift

| Operation:       | $R \leftarrow R$ shifted arithmetically NN places to right or left, where NN = low-order 6 bits of source.                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Condition Codes: | <ul> <li>N: set if result &lt; 0; cleared otherwise.</li> <li>Z: set if result = 0; cleared otherwise.</li> <li>V: set if sign of register changed during left shift; cleared otherwise.</li> <li>C: loaded from last bit shifted out of register.</li> </ul>                                        |

| Description:     | The contents of the register are shifted right or left the number of times specified by the shift count. The shift count is taken as the low-order 6 bits of the source operand (SSS). This number ranges from $-32$ to $+31$ . Negative is a right shift and positive is a left shift (Figure 2-3). |

| Example:         | ASH R0, R3<br>Before After                                                                                                                                                                                                                                                                           |

Figure 2-3 ASH Operation

#### ASHC 073RSS

Arithmetic SHift Combined

**Operation**:

R, RV1  $\leftarrow$  R, RV1. The double word is shifted NN places to the right or left, where NN = low-order six bits of source.

(R3)=000003

(R0)=012340

Condition Codes:

N: set if result < 0; cleared otherwise.

(R3)=000003

(R0)=001234

Z: set if result = 0; cleared otherwise.

V: set if sign bit changes during the left shift; cleared otherwise.

C: loaded with the last bit shifted out of the register.

Description:

The contents of the register and the register ORed with 1 are treated as one 32-bit word. RV1 (bits 15:00) and R (bits 31:16) are shifted right or left the number of times specified by the shift count. The shift count is taken as the low-order 6 bits of the source operand. This number ranges from -32 to +31. Negative is a right shift and positive is a left shift (Figure 2-4). When the register chosen is an odd number, the register and the register ORed with 1 are the same. In this case, the right shift becomes a rotate. The 16-bit word is rotated right the number of bits specified by the shift count for up to 16 shifts.

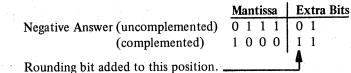

Figure 2-4 ASHC Operation