# RL01 / RL02 DISK DRIVE

# Technical Manual

PRELIMINARY

EK-RLØ12-TM-PRE (PRELIMINARY)

RLØ1/RLØ2 DISK DRIVE TECHNICAL MANUAL

DIGITAL EQUIPMENT CORPORATION COLORADO SPRINGS, CO 80919 Preliminary Edition, September 1978 (Revision) August 1978 (2nd Revision) March 1979 (3rd Revision) December 1979

Copyright © 1978, 1979 by Digital Equipment Corporation

The information in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL'S WPS-8 Word Processing System.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECUS        | DECnet    |

|--------------|--------------|-----------|

| DECsystem-10 | DECSYSTEM-20 | DECwriter |

| DIBOL        | Digital Logo | EduSystem |

| IAS          | LSI-11       | MASSBUS   |

| OMNIBUS      | PDP          | PDT       |

| Q-BUS        | RSTS         | RSX       |

| UNIBUS       | VAX          | VMS       |

|              | VT           |           |

# TABLE OF CONTENTS

# SECTION I TECHNICAL DESCRIPTION

| CHAPTER                                                                                                                                                                                                                      | 1 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.3.1<br>1.1.3.2<br>1.1.3.2<br>1.1.3.3<br>1.1.3.4<br>1.1.3.5<br>1.1.3.6<br>1.1.3.7<br>1.1.3.8<br>1.1.3.9<br>1.1.4<br>1.1.4.1<br>1.1.4.2<br>1.1.4.1<br>1.1.4.2<br>1.1.4.4<br>1.1.5<br>1.2 |   | GENERAL DESCRIPTION1-1Servo-In-Data Concept1-1Storage Medium1-3Mechanical Partitioning1-3Air Flow System1-3Air Filter1-3Positioner Assembly1-6Brush Drive Assembly1-6Read/Write Heads1-6Read/Write Board1-6Power Panel1-6Control Panel1-11Drive Electronics Fartitioning1-14DC Servo Module1-16Read/Write Module1-16Read/Write Module1-16Servo Specification1-16Read/Write Module1-16Read/Write Module1-16Read/Write Module1-16Read/Write Module1-16Read/Write Module1-16Read/Write Module1-16Subsystem Specifications1-17 |

| CHAPTER                                                                                                                                                                                                                      | 2 | SYSTEM - LEVEL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1                                                                                                                                                                                                                          |   | RLØ1/RLØ2 MASS STORAGE SUBSYSTEM 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1     | RL01/RL02 MASS STORAGE SUBSYSTEM |

|---------|----------------------------------|

| 2.2     | DISK CARTRIDGE FORMAT 2-1        |

| 2.2.1   | Data Format                      |

| 2.2.2   | Servo Data                       |

| 2.2.2.1 | Introduction 2-4                 |

| 2.2.2.2 | Modes of Operation 2-4           |

| 2.2.2.3 | Generation of Servo Signals      |

| 2.2.2.4 | Velocity Mode Operation          |

| 2.2.2.5 | Position Mode 2-9                |

| 2.2.2.6 | Guard Band 2-9                   |

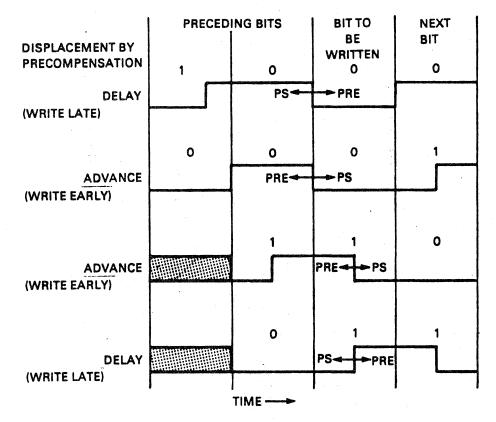

| 2.2.3   | MFM Encoding and Precompensation |

| 2.2.4   | Bad Sector File 2-12             |

|         |                                  |

# CHAPTER 3 INTERFACE - LEVEL DESCRIPTION

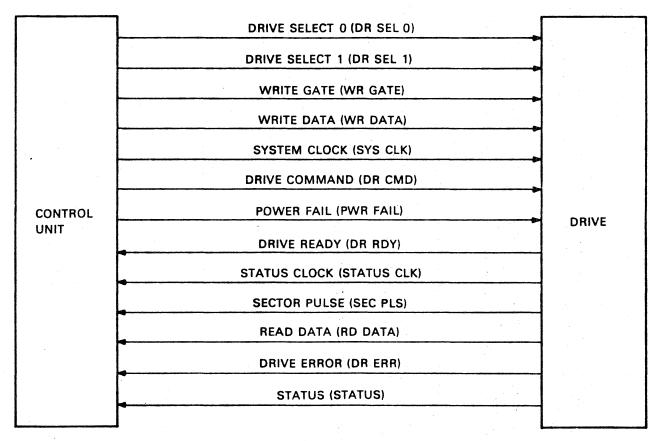

| 3.1 | CONTROLLER/DRIVE INTERFACE LINE DESCRIPTIONS | 3-1 |

|-----|----------------------------------------------|-----|

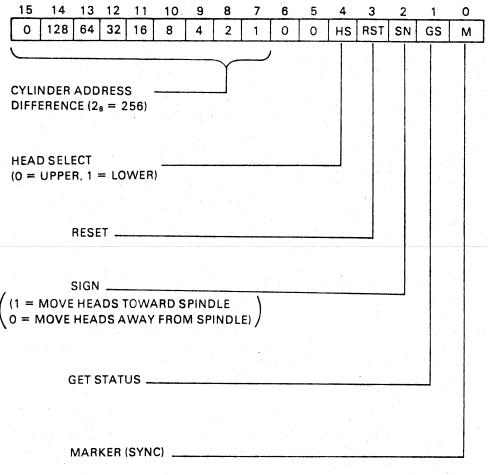

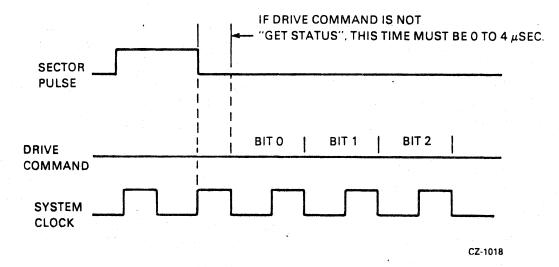

| 3.2 | DRIVE COMMAND WORD                           | 3-6 |

| 3.3 | GET STATUS COMMAND RESPONSE                  | 3-7 |

# CHAPTER 4 FUNCTIONAL DESCRIPTION

| 4.1 | DEVICE OPERATIONS       | 4-1 |

|-----|-------------------------|-----|

| 4.2 | INTERNAL MACHINE CYCLES | 4-1 |

| 4.2.1 | Power Up 4-4                  |

|-------|-------------------------------|

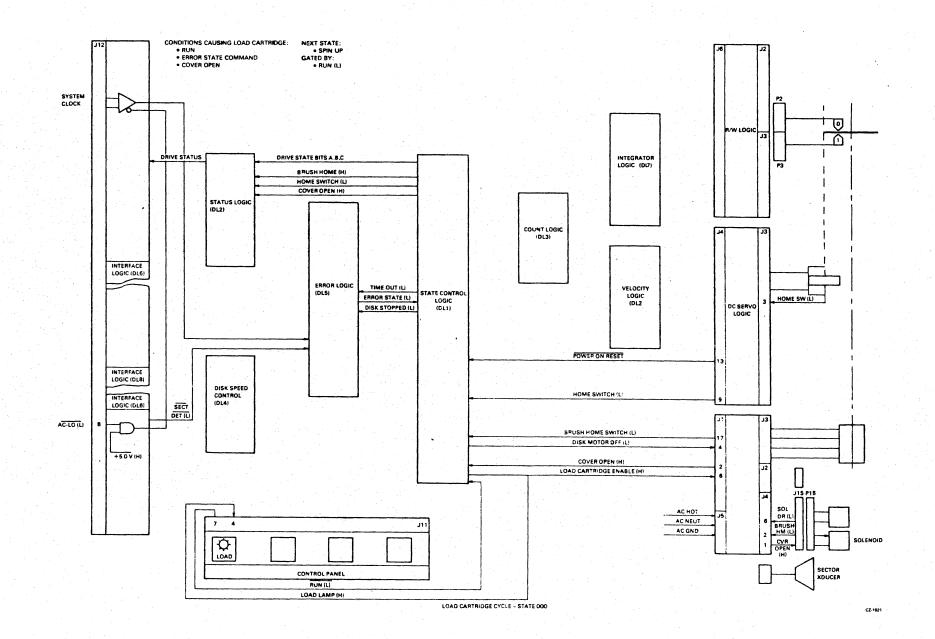

| 4.2.2 | Load Cartridge Cycle 4-4      |

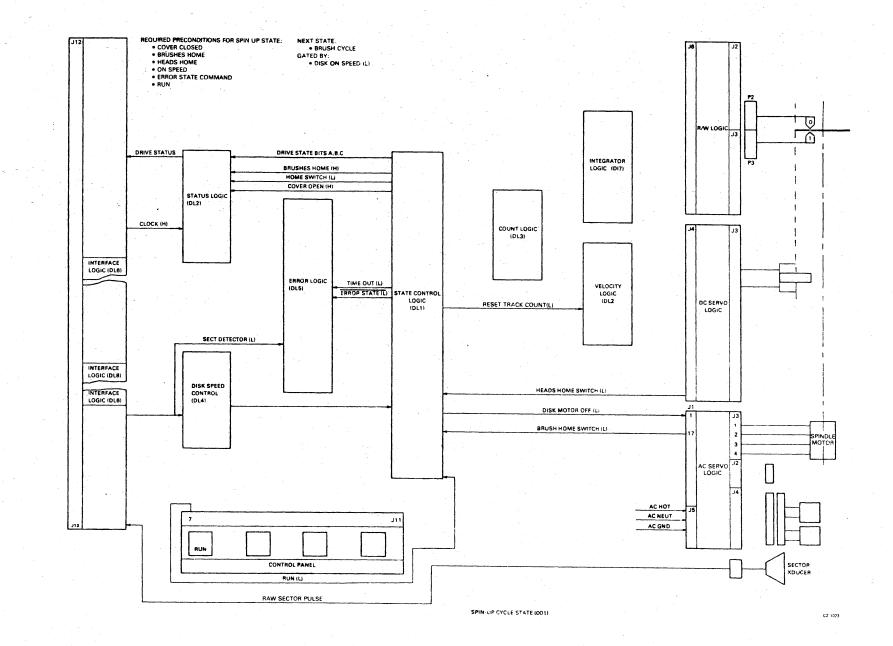

| 4.2.3 | Spin-Up Cycle 4-7             |

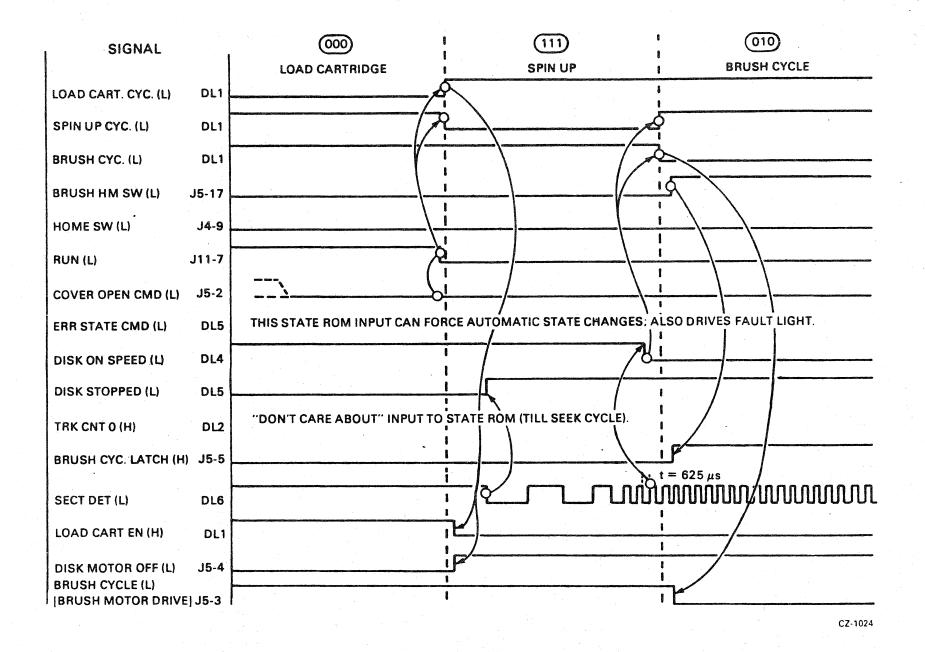

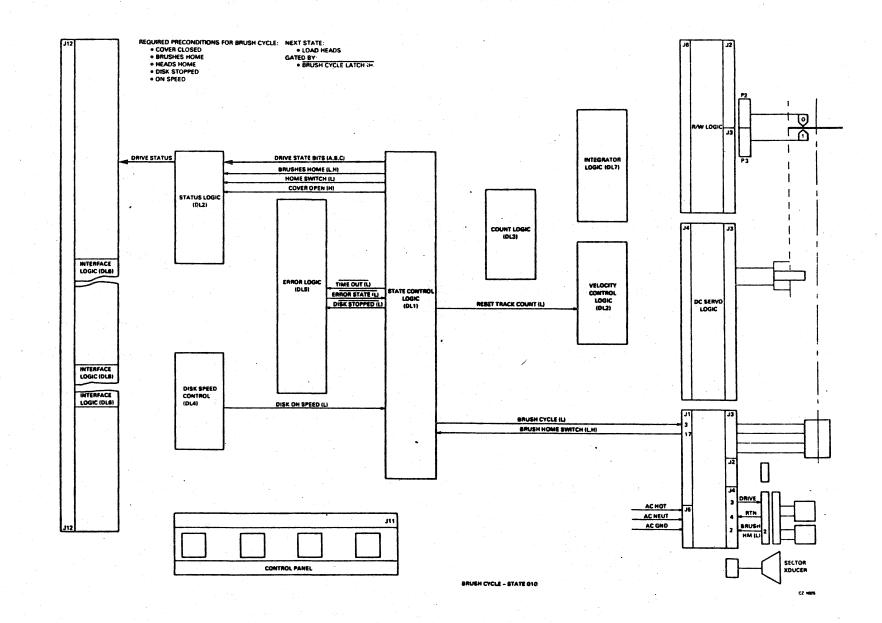

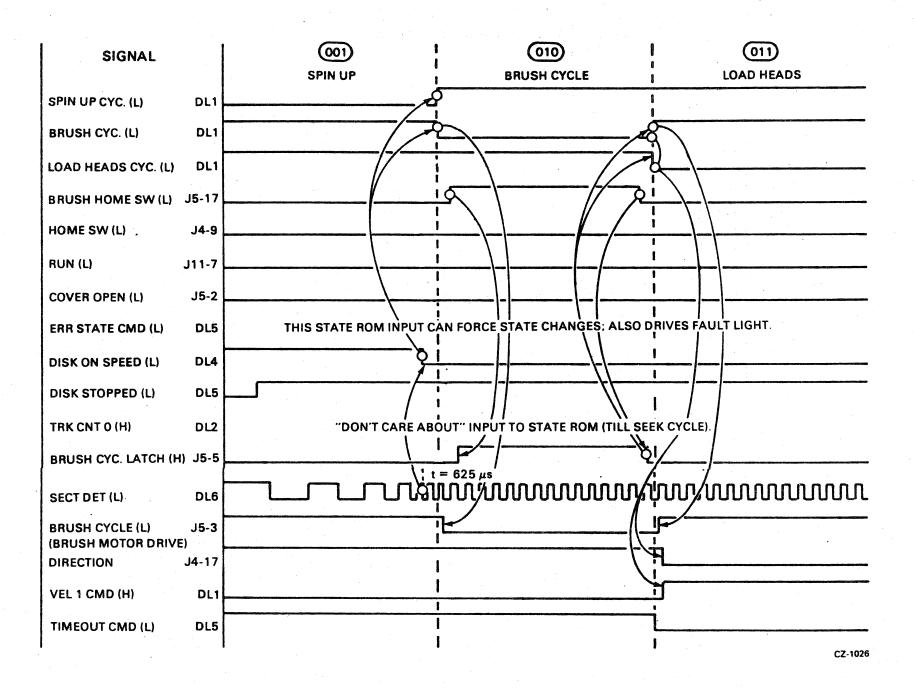

| 4.2.4 | Brush Cycle 4-10              |

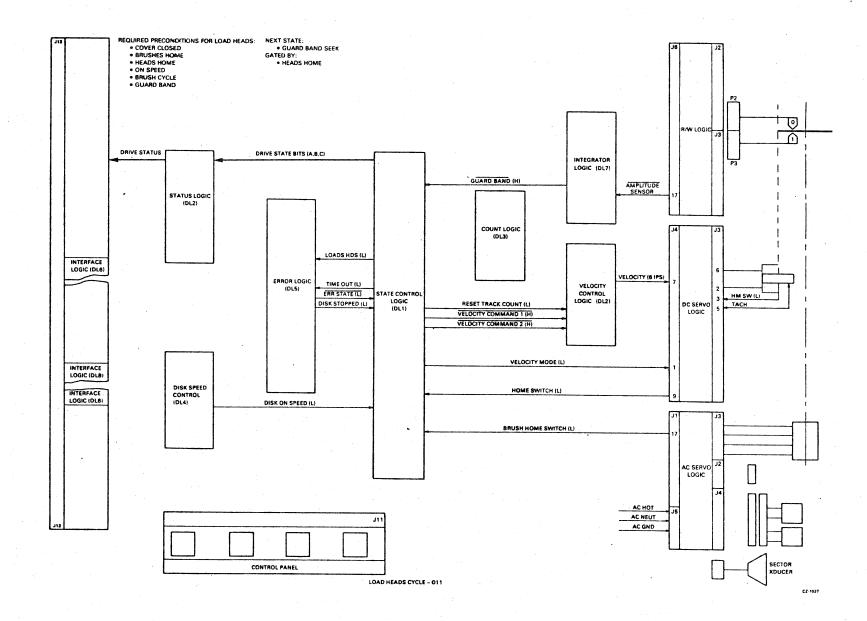

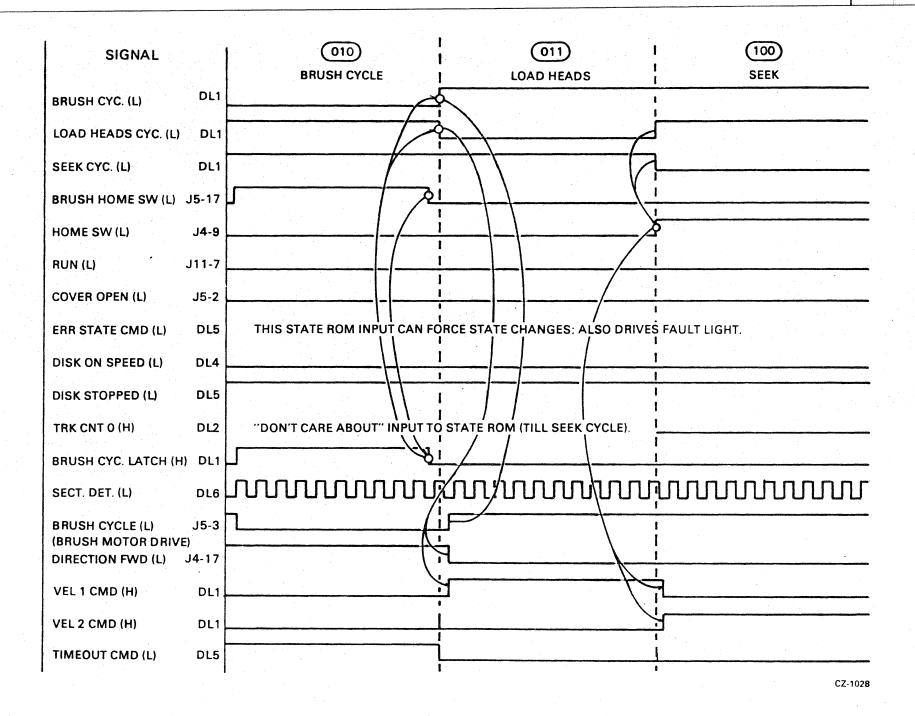

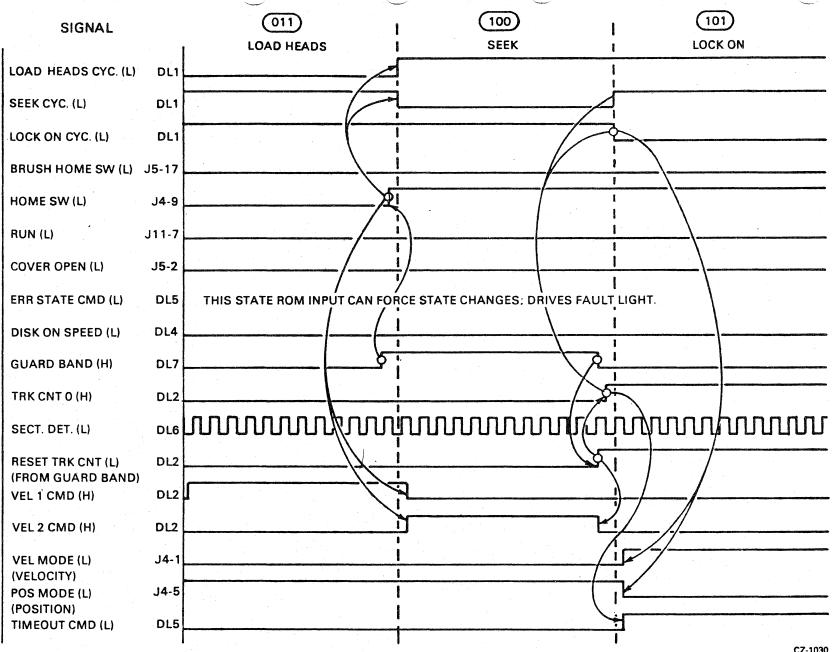

| 4.2.5 | Load Heads Cycle 4-10         |

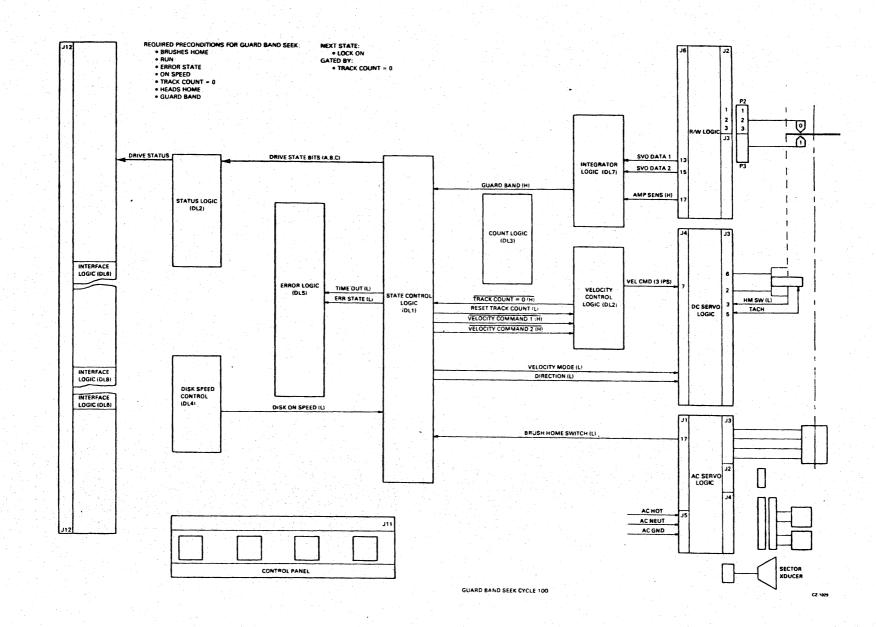

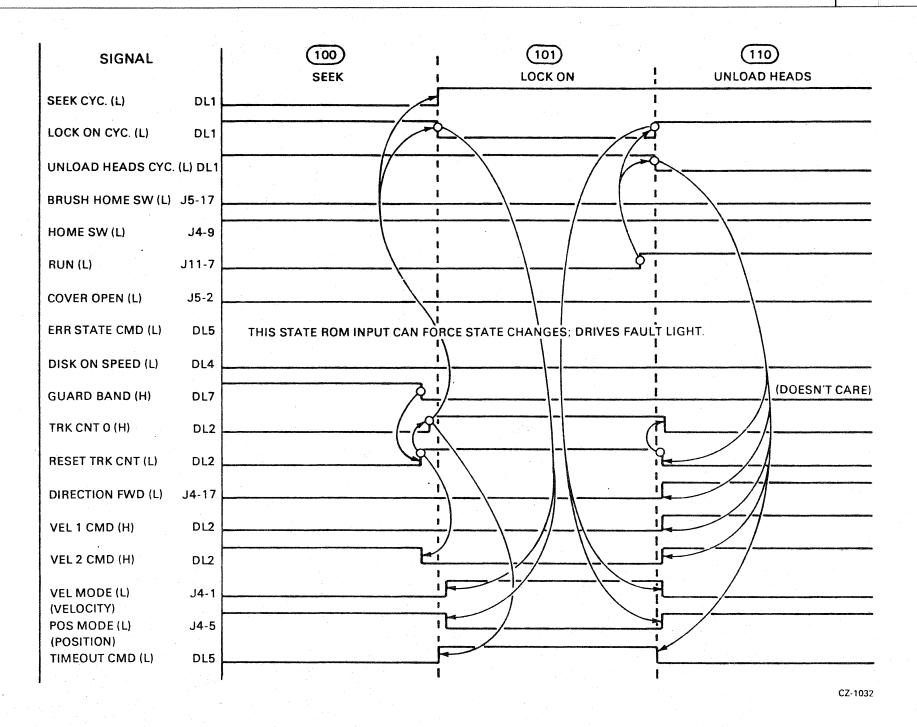

| 4.2.6 | Seek Cycle 4-15               |

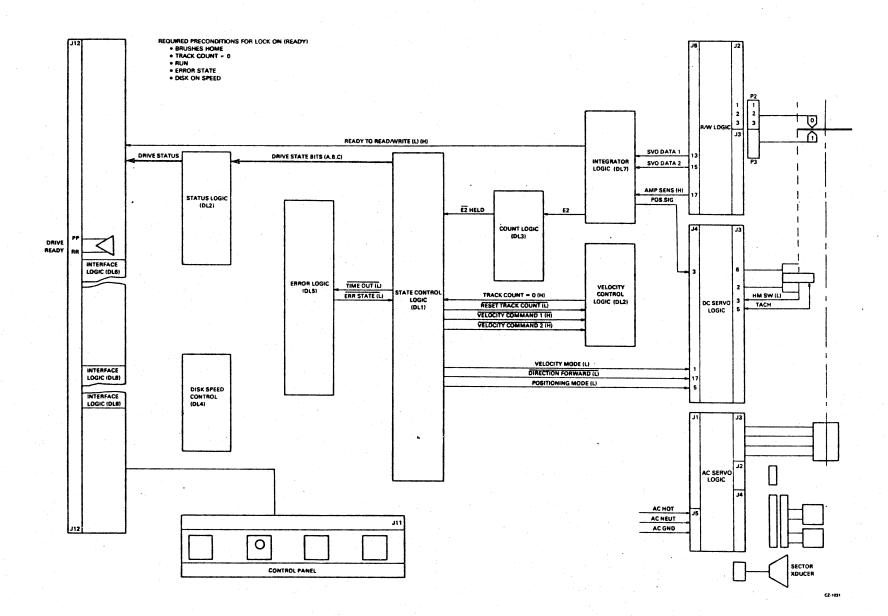

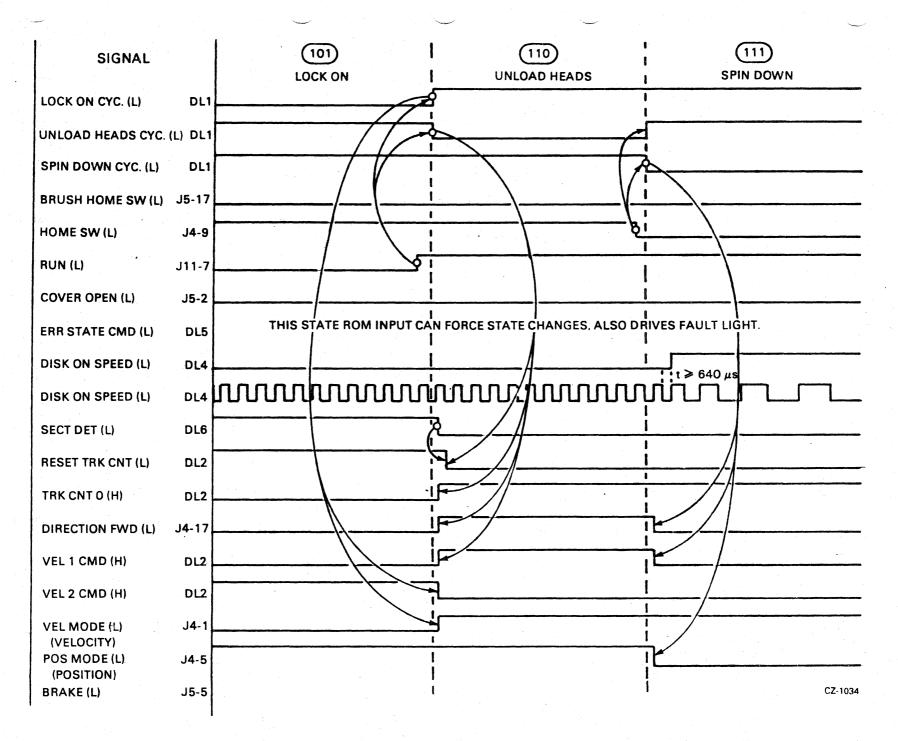

| 4.2.7 | Lock On (Device Ready) 4-18   |

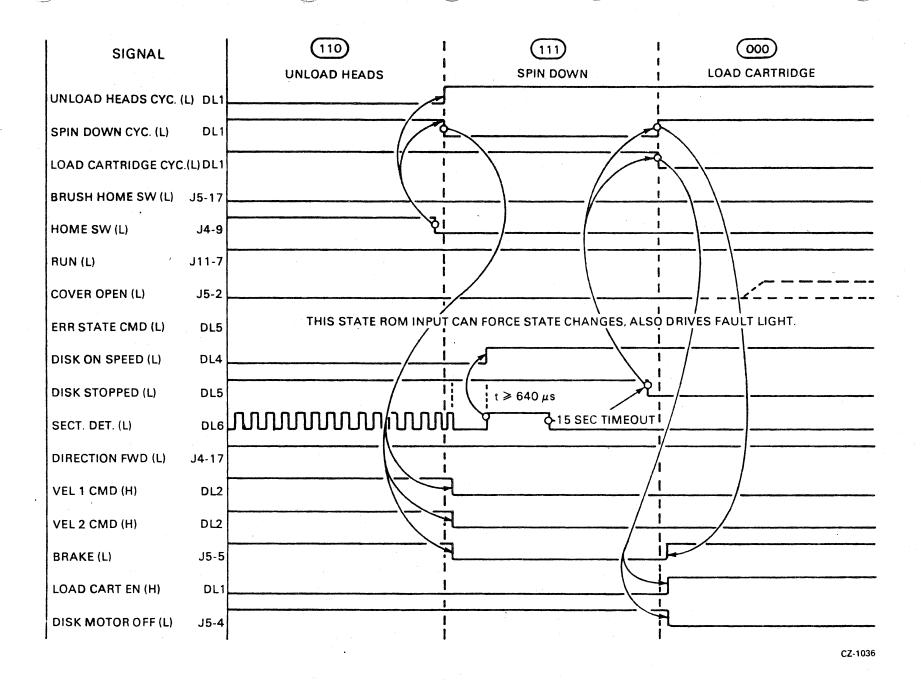

| 4.2.8 | Unload Heads 4-21             |

| 4.2.9 | Spin-Down Cycle 4-21          |

| 4.3   | EXTERNAL DRIVE FUNCTIONS 4-26 |

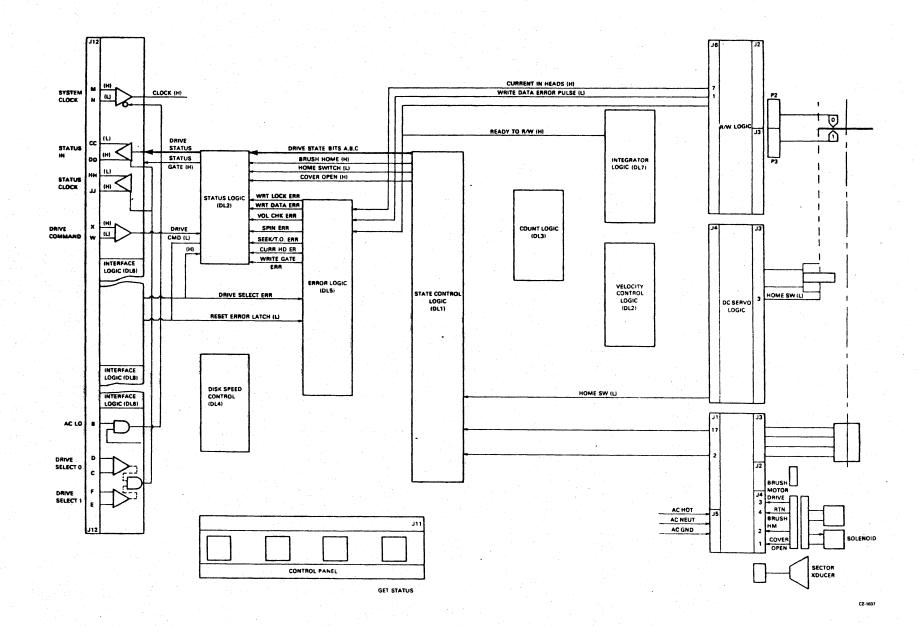

| 4.3.1 | Get Status 4-26               |

| 4.3.2 | Seek 4-29                     |

| 4.3.3 | Read Data 4-32                |

| 4.3.4 | Write Data 4-35               |

# CHAPTER 5 UNIT - LEVEL DESCRIPTION

| 5.1      |   | DRIVE LOGIC MODULE THEORY OF OPERATION 5-1     |

|----------|---|------------------------------------------------|

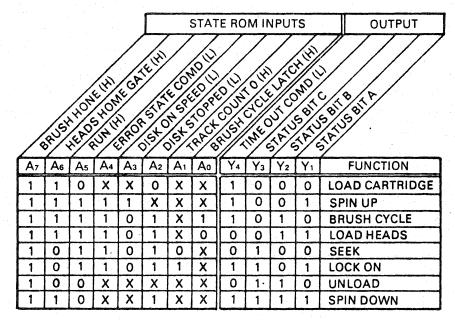

| 5.1.1    | * | State Control Logic (DL1)                      |

| 5.1.1.1  |   | State ROM 5-1                                  |

| 5.1.1.2  |   | State ROM Decoder                              |

| 5.1.1.3  |   | Seek Control ROM                               |

| 5.1.1.4  |   | Brush Cycle Latch                              |

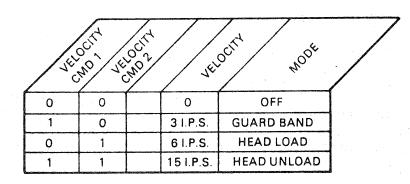

| 5.1.2    |   | Velocity Command and Status Data Control Logic |

|          |   | (DL2)                                          |

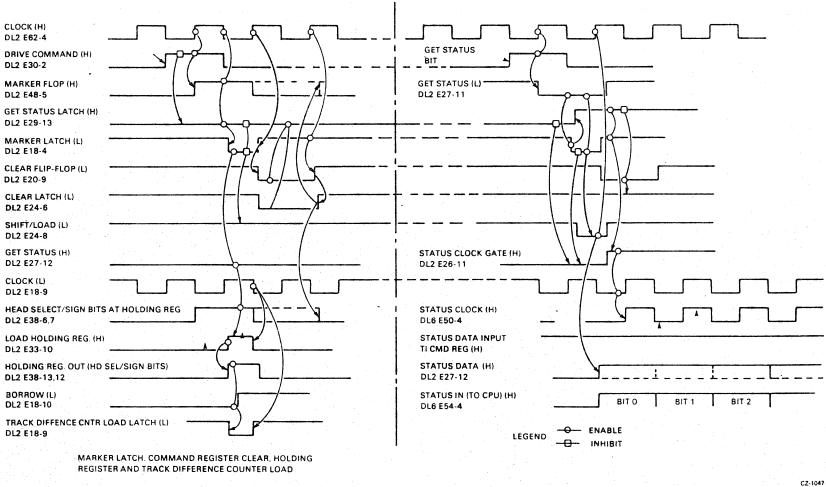

| 5.1.2.1  |   | Device Command/Status Register 5-8             |

| 5.1.2.2  |   | Marker Flip-Flop 5-10                          |

| 5.1.2.3  |   | Marker Latch                                   |

| 5.1.2.4  |   | Clear Latch 5-10                               |

| 5.1.2.5  |   | Load Registers Gate                            |

| 5.1.2.6  |   | Shift/Load Gate 5-11                           |

| 5.1.2.7  |   | Get Status Latch                               |

| 5.1.2.8  |   | Status Clock Gate 5-11                         |

| 5.1.2.9  |   | Track Difference Counter 5-11                  |

| 5.1.2.10 |   | Track Difference Counter Load Latch 5-12       |

| 5.1.2.11 |   | Head Select/Sign Bit Holding Register 5-12     |

| 5.1.2.12 |   | Track Count = $\emptyset$ Gate                 |

| 5.1.2.13 |   | Reset Error Latches Gate 5-13                  |

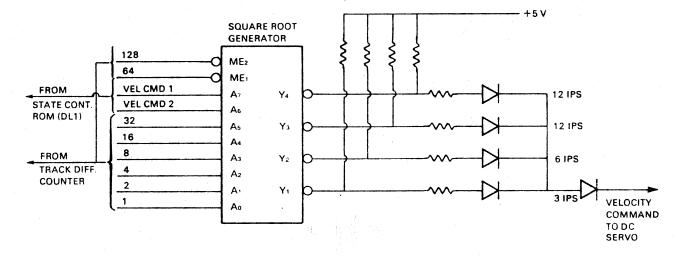

| 5.1.2.14 |   | Velocity ROM                                   |

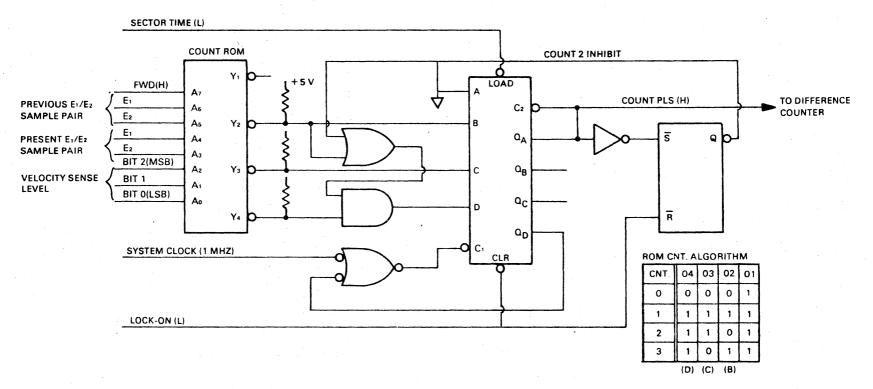

| 5.1.3    |   | Count Logic (DL3) 5-13                         |

| 5.1.3.1  |   | Count ROM                                      |

| 5.1.3.2  |   | El Held Flip-Flop 5-17                         |

| 5.1.3.3  |   | E2 Held Flip-Flop 5-20                         |

| 5.1.3.4  |   | Velocity Level Detectors                       |

| 5.1.3.5  |   | Disable Count 2 Latch 5-20                     |

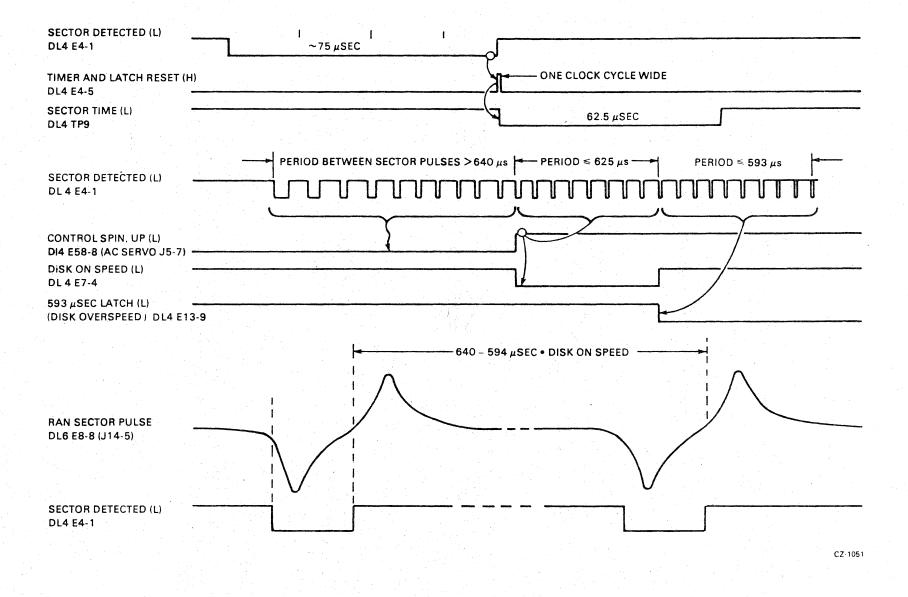

| 5.1.4    | 4 | Disk Speed Control Logic (DL4) 5-20            |

| 5.1.4.1  |   | Sector Detection Timer                         |

| 5.1.4.2  |   | Disk On Speed Latch 5-21                       |

| 5.1.4.3  |   | Sector Time Latch 5-21                         |

| 5.1.4.4  |   | 593 Microsecond Latch 5-21                     |

| 5.1.4.5  |   | Control Speed-up Gate 5-21                     |

| 5.1.4.6  |   | Timer and Latch Reset Flip-Flop 5-21           |

| 5.1.5    |   | Error Logic (DL5) 5-23                         |

| 5.1.5.1    | Disk Stopped Timer                          | 5-23 |

|------------|---------------------------------------------|------|

| 5.1.5.2    | Disk Spinup Timer and Error Latch           | 5-23 |

| 5.1.5.3    | Write Protect Detection and Error Latch     | 5-23 |

| 5.1.5.4    | Clock Error Detector                        | 5-23 |

| 5.1.5.5    | Write Gate Error Flip-Flop                  | 5-23 |

| 5.1.6      | Interface Logic (DL6 and DL8)               | 5-24 |

| 5.1.6.1    | Sector Pulse Detector                       | 5-24 |

|            | Enable/Disable Interface Controls           | 5-24 |

| 5.1.6.2    |                                             | 5-25 |

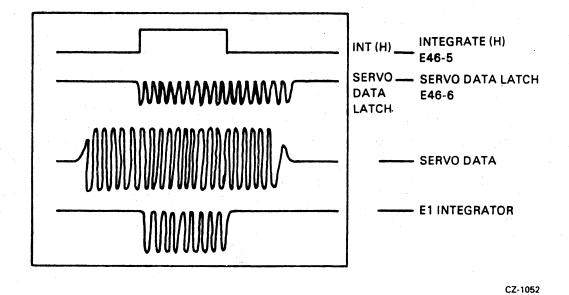

| 5.1.7      | Integrator Logic (DL4)                      | 5-25 |

| 5.1.7.1    | El and E2 Servo Sample Generation and       | r 0r |

|            | Integration                                 | 5-25 |

| 5.1.7.2    | Positioner Signal and Ready to Read/Write   |      |

|            | Logic                                       | 526  |

| 5.2        | DC SERVO AND POWER MODULE                   | 5-3Ø |

| 5.2.1      | Voltage Regulators                          | 5-3Ø |

| 5.2.2      | Overvoltage Crowbar                         | 5-32 |

| 5.2.3      | +5 Volt Disable and Emergency Retract       | 5-32 |

| 5.2.4      | Undervoltage Detector                       | 5-32 |

| 5.2.5      | Invert/Noninvert Selection Control          | 5-32 |

| 5.2.6      | Velocity/Positioner Mode Selection Switches | 5-32 |

| 5.2.7      | Tachometer Amplifier                        | 5-32 |

| 5.3        | READ/WRITE MODULE                           | 5-33 |

| 5.3.1      | Head Selection and Steering Circuits        | 5-33 |

| 5.3.2      | Write Current Source and Drivers            | 5-34 |

| 5.3.3      |                                             | 5-34 |

| 5.3.4      | Write Error Detector                        | 5-34 |

| 5.3.5      | Current in Heads Detector                   | 5-34 |

| 5.3.6      | Read Amplifier Circuits                     | 5-34 |

| 5.3.7      | Zero Crossing Detectors                     | 5-34 |

| 5.3.8      | Amplitude Sensor                            | 5-34 |

| 5.4        | AC SERVO MODULE                             | 5-35 |

| 5.4.1      | Cartridge Access Door Solenoid              | 5-35 |

| 5.4.2      | Brush Drive Motor Control                   | 5-35 |

|            |                                             | 5-35 |

| 5.4.3      |                                             | 5-35 |

| 5.4.3.1    | Spin-up State                               | 5-36 |

| 5.4.3.2    | Controlled Speed State                      |      |

| 5.4.3.3    | Spin-down State                             | 5-36 |

|            |                                             |      |

|            |                                             |      |

| CECUTON IT | SERVICING PROCEDURES                        |      |

| DECITON II | DREATCING LUCCHDOURD                        |      |

| CHAPTER 1 | MAINTENANCE                  |

|-----------|------------------------------|

| 1.1       | MAINTAINABILITY FEATURES     |

| 1.1.1     | Hardware Maintenance Plan    |

| 1.1.2     | Additional Documentation     |

| 1.1.3     | Field Replacable Units       |

| 1.1.4     | Recommended Spare Parts List |

| 1.2       | SOFTWARE RESOURCES           |

| 1.2.1     | Diagnostics                  |

| 1.2.2     | Diagnostic Supervisor        |

| 1.2.2.1   | Hardcore Questions           |

|           |                              |

V

1-1 1-1 1-1

1-31-41-51-51-51-51-5

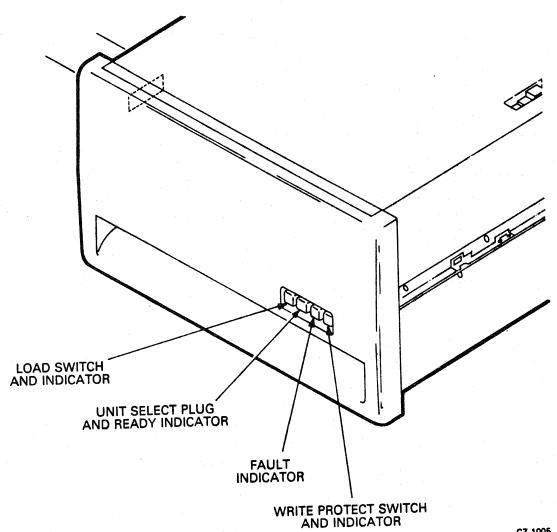

| 1.2.2.2<br>1.2.3.3<br>1.2.2.4<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5<br>1.3.6                                        | Console Controls 1-9<br>Hardware Questions 1-9<br>Software Question 1-9<br>MAINTENANCE CONTROLS AND INDICATORS 1-9<br>Power ON/OFF Circuit Breaker 1-9<br>Power Terminal Block Assembly 1-9<br>RUN/STOP Switch with LOAD Indicator 1-12<br>Unit Select (Ø, 1, 2, 3) Switch with READY<br>Indicator 1-12<br>FAULT Indicator 1-12<br>WRITE PROTect Switch and Indicator 1-12 |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 2                                                                                                                         | REMOVAL AND REPLACEMENT PROCEDURES                                                                                                                                                                                                                                                                                                                                         |

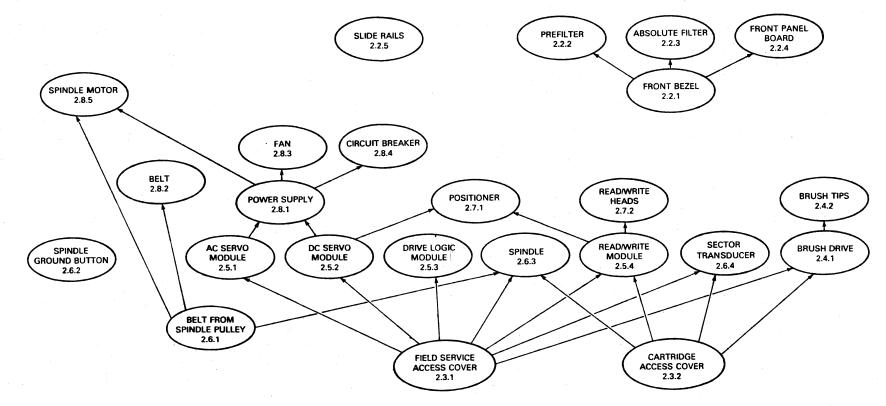

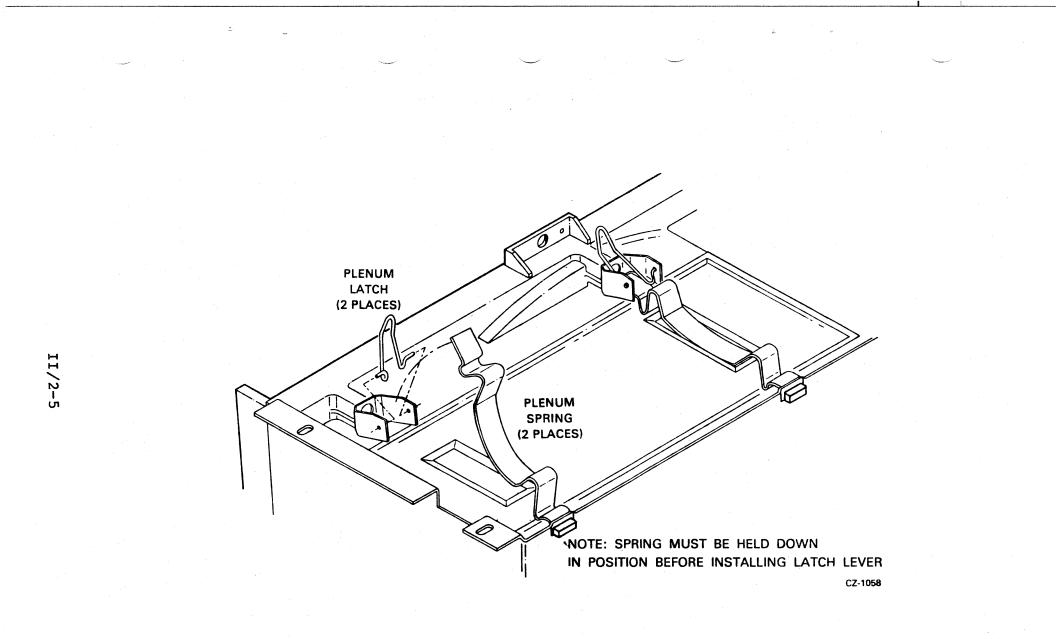

| 2.3.1<br>2.3.2<br>2.4<br>2.4.1<br>2.4.2<br>2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4                                                | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                               |

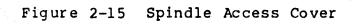

| 2.6<br>2.6.1<br>2.6.2<br>2.6.3<br>2.6.4<br>2.7<br>2.7.1<br>2.7.2<br>2.8<br>2.8.1<br>2.8.2<br>2.8.3<br>2.8.4<br>2.8.5<br>CHAPTER 3 | SPINDLE AREA2-24Belt from Spindle Pulley2-24Spindle Ground Button2-24Spindle2-24Sector Transducer2-28POSITIONER AREA2-29Positioner2-31Read/Write Heads2-31REAR PANEL AREA2-33Power Supply2-33Spindle Drive Belt2-34Circuit Breaker2-34Circuit Breaker2-40Spindle Drive Motor2-40CHECKS, ADJUSTMENTS AND ALIGNMENTS                                                         |

| 3.1<br>3.2<br>3.3<br>3.4                                                                                                          | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                               |

| 3.5                | POSITIONER RADIAL ALIGNMENT 3-6           |

|--------------------|-------------------------------------------|

| 3.6                | HEAD ALIGNMENT 3-11                       |

| 3.7                | READ SIGNAL AMPLITUDE CHECK 3-18          |

| 3.8                | SPINDLE RUNOUT CHECK 3-20                 |

| 3.9                | POSITION SIGNAL GAIN CHECK 3-22           |

| 3.10               | TACHOMETER AC NOISE PICK-UP CHECK 3-25    |

| 3.11               | VELOCITY PROFILE CHECK 3-27               |

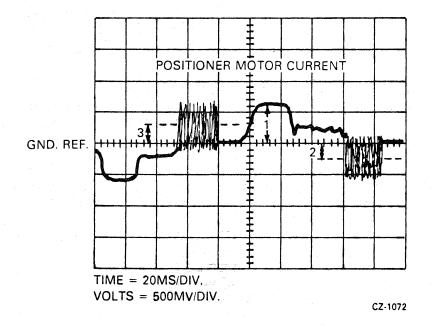

| 3.12               | SERVO DRIVE MOTOR CURRENT CHECK 3-29      |

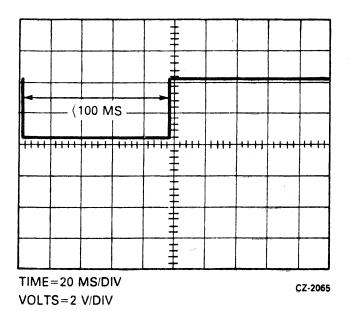

| 3.13               | ACCESS TIME CHECK 3-31                    |

| APPENDIX A         | REGISTER DESCRIPTIONS                     |

|                    |                                           |

| A.1                | RL11/RLV11 ADDRESSABLE REGISTERS A-1      |

| A.1.1              | Control Status Register A-2               |

| A.1.2              | Bus Address Register A-5                  |

| A.1.3              | Disk Address Register A-5                 |

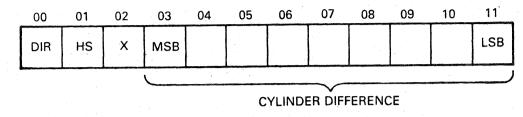

| A.1.3.1            | Disk Address Register During a Seek       |

|                    | Command A-5                               |

| A.1.3.2            | Disk Address Register During a Read or    |

|                    | Write Data Command A-6                    |

| A.1.3.3            | Disk Address Register During a Get Status |

|                    | Command A-7                               |

| A.1.4              | Multipurpose Register A-7                 |

| A.1.4.1            | Multipurpose Register During a Get Status |

|                    | Command A-7                               |

| A.1.4.2            | Multipurpose Register During a Read       |

|                    | Header Command A-9                        |

| A.1.4.3            | Multipurpose Register During a Read or    |

|                    | Write Command A-10                        |

| A.2                | RL8-A ADDRESSABLE REGISTERS A-11          |

| A.2.1              | Command Register A A-12                   |

| A.2.1.1            | Command Register A During a Seek          |

|                    | Command A-12                              |

| A.2.1.2            | Command Register A During a Read or       |

|                    | Write Data Command A-12                   |

| A.2.2              | Command Register B A-13                   |

| A.2.3              | Break Memory Address Register A-14        |

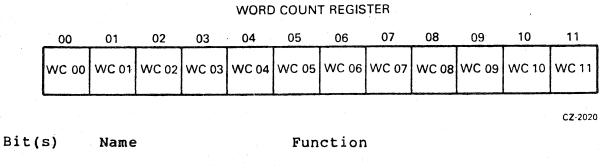

| A.2.4              | Word Count Register A-15                  |

| A.2.5              | Sector Address Register A-15              |

| A.2.6              | Error Register A-15                       |

| A.2.7              | Silo Buffer A-17                          |

| A.2.7.1            | Silo Register After a Get Status          |

| M • Z • I • I      | Command                                   |

| A.2.7.2            | Silo Data Buffer During a Read Header     |

|                    | Command A-19                              |

|                    |                                           |

| APPENDIX B         | SUBSYSTEM INSTALLATION PROCEDURES         |

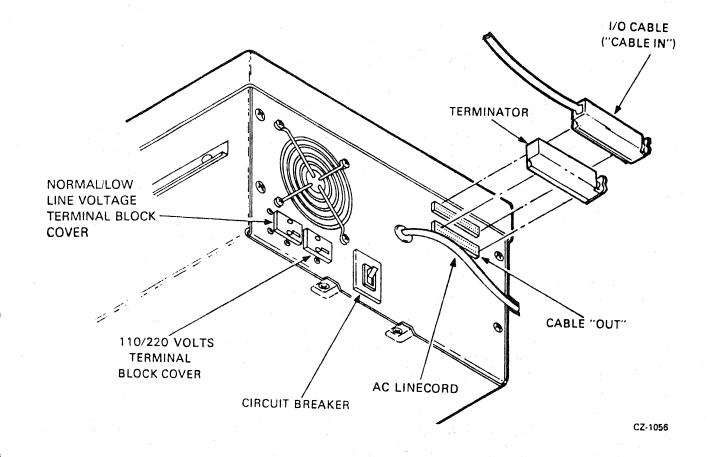

| B.1                | SITE PREPARATION AND PLANNING B-1         |

| B.1.1              | Environmental Considerations              |

| B.1.1.1            | Cleanliness B-1                           |

| B.1.1.2            | Space Requirements B-1                    |

| B.1.1.3            | Floor Loading B-1                         |

| B.1.1.3<br>B.1.1.4 | Heat Dissipation                          |

| тетет              | HEAR DISTIARIAN                           |

| B.1.1.5     | Acoustics B-2                                                    |

|-------------|------------------------------------------------------------------|

| B.1.1.6     | TemperatureB-2                                                   |

| B.1.1.7     | Relative HumidityB-2                                             |

| B.1.1.8     | Altitude B-2                                                     |

| B.1.1.9     | Power and Safety Precautions B-2                                 |

| B.1.1.10    | Radiated Emissions B-3                                           |

| B.1.1.11    | Attitude/Mechanical Shock B-3                                    |

| B.1.2       | Options B-3                                                      |

| B.1.3       | AC Power Requirements                                            |

| B.1.3.1     | Standard Applications                                            |

| B.1.3.2     | Optional Applications                                            |

|             |                                                                  |

| B.1.4       | Grounding Requirements B-6                                       |

| B.1.5       | Installation Constraints B-10                                    |

| B.2         | AC CABLING                                                       |

| B.3         | INSTALLATION - GENERAL                                           |

| B.4         | RL11 CONTROLLER INSTALLATION B-13                                |

| B.5         | RLV11 CONTROLLER INSTALLATION B-23                               |

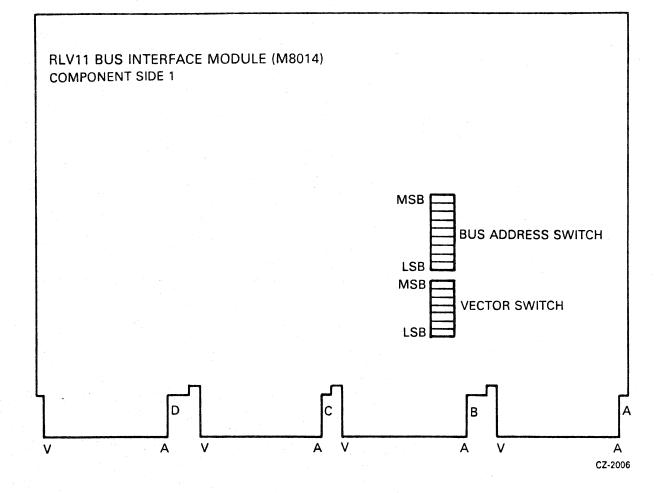

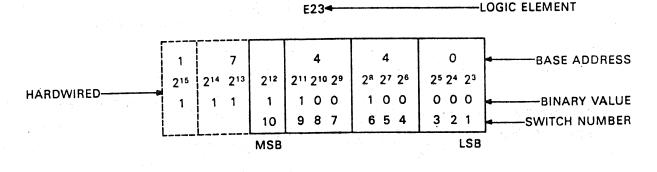

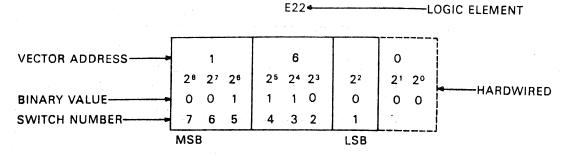

| B.5.1       | Bus Interface Module B-23                                        |

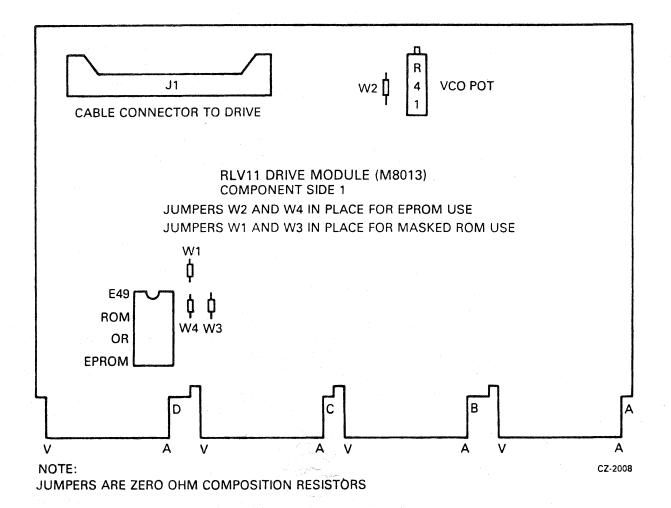

| B.5.2       | Drive Module B-27                                                |

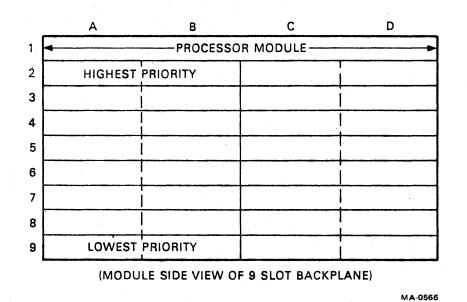

| B.5.3       | Module Slot Location B-27                                        |

| B.5.4       | Module Installation B-27                                         |

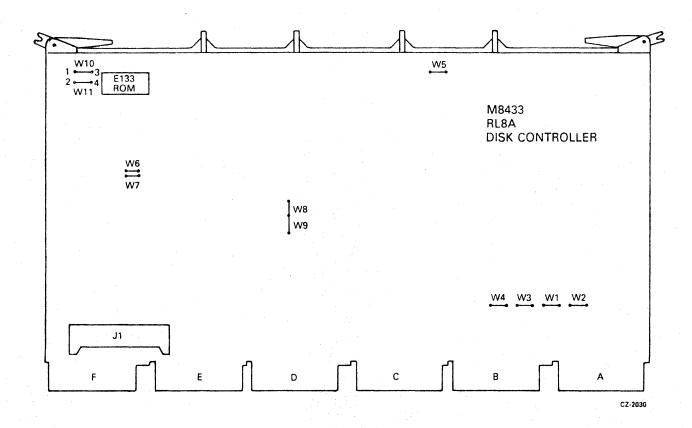

|             | RL8-A CONTROLLER INSTALLATION B-29                               |

| B.6.1       | Introduction B-29                                                |

| B.6.2       | Module Slot Location B-29                                        |

| B.6.3       | Module Installation B-29                                         |

| B.7         | RLØ1/RLØ2 DISK DRIVE INSTALLATION B-31                           |

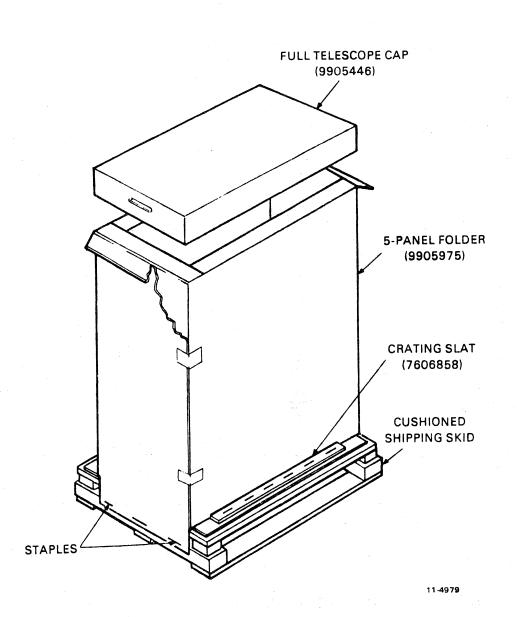

| B.7.1       | Unpacking and Inspection B-31                                    |

| B.7.2       | RLØ1/RLØ2 Disk Drive Unit Mounting B-33                          |

| B.7.3       | Drive Prestart Inspection B-38                                   |

| B.7.4       | Drive Start-up Operation Check B-40                              |

| B.8         | CONFIDENCE TESTING                                               |

| B.8.1       | RL11-Based Diagnostics B-43                                      |

| B.8.2       | RLV11-Based Diagnostics B-45                                     |

| B.8.3       | RL8A-Based Diagnostics B-45                                      |

| B.9         | USE OF THE M9312 BOOTSTRAP WITH AN RL11                          |

|             | SYSTEM B-48                                                      |

|             |                                                                  |

| APPENDIX C  | TOGGLE-IN PROGRAMS                                               |

|             | URAD CREEGERON DOODAN DOD DELL (DEVIL)                           |

| C.1         | HEAD SELECTION PROGRAM FOR RL11/RLV11 C-1                        |

| C.2<br>C.3  | HEAD SELECTION PROGRAM FOR RL8-A C-2                             |

| C.3         | GET STATUS (WITH OR WITHOUT RESET) ON AN                         |

| C.4         | RL11/RLV11 SUBSYSTEM C-3<br>GET STATUS ON AN RL8-A SUBSYSTEM C-4 |

| C.5         |                                                                  |

| C.6         | OSCILLATING SEEK FOR RL11/RLV11 C-5                              |

| C.0         | OSCILLATING SEEK FOR RL8-A C-6                                   |

| APPENNTY D  | RL11 CONFIGURATION AND INSTALLATION CONSIDERATIONS               |

| MELDINDIA D | ABIL CONFIGURATION AND INDIALENTION CONDIDERATIONS               |

|             |                                                                  |

| D.1         | SPC CONSIDERATIONS                                               |

| D.1<br>D.2  | SPC CONSIDERATIONS D-1<br>CONFIGURATION CONSIDERATIONS D-2       |

FIGURES

| Figure No.                                                                                                                                         | Title Page No.                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/1-1<br>I/1-2<br>I/1-3<br>I/1-4<br>I/1-5<br>I/1-6<br>I/1-7<br>I/1-8<br>I/1-9<br>I/1-10                                                            | Typical Disk Drive I/1-2<br>Major Subassemblies and Air Flow I/1-4<br>Positioner Assembly I/1-5<br>Spindle Assembly I/1-7<br>Brush Assembly I/1-7<br>Read/Write Heads I/1-9<br>Rear Panel Assembly I/1-10<br>Control Panel I/1-12<br>Logic Modules I/1-15<br>Data Format I/1-22                                                                                                                                   |

| I/2-1<br>I/2-2<br>I/2-3<br>I/2-4<br>I/2-5<br>I/2-6<br>I/2-7<br>I/2-8<br>I/2-9                                                                      | Typical RLØ1/RLØ2 Mass Storage SubsystemI/2-2RLØ1K/RLØ2K Disk Cartridge CharacteristicsI/2-3Servo Sample GenerationI/2-6Servo Data WaveformsI/2-7Generation of El and E2I/2-8Servo Data PatternI/2-10MFM EncodingI/2-11MFM PrecompensationI/2-13Bad Sector FileI/2-14                                                                                                                                             |

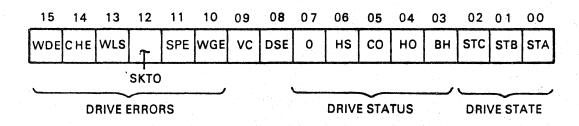

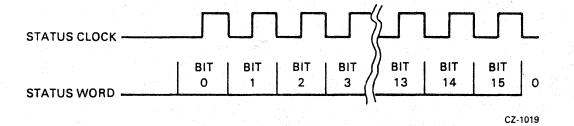

| I/3-1<br>I/3-2<br>I/3-3<br>I/3-4                                                                                                                   | Control Unit/Drive Interface Lines I/3-2<br>Drive Command Word Configuration I/3-8<br>Relationship Between System Clock<br>and Drive Command Word Bits I/3-9<br>Drive Status Word I/3-10                                                                                                                                                                                                                          |

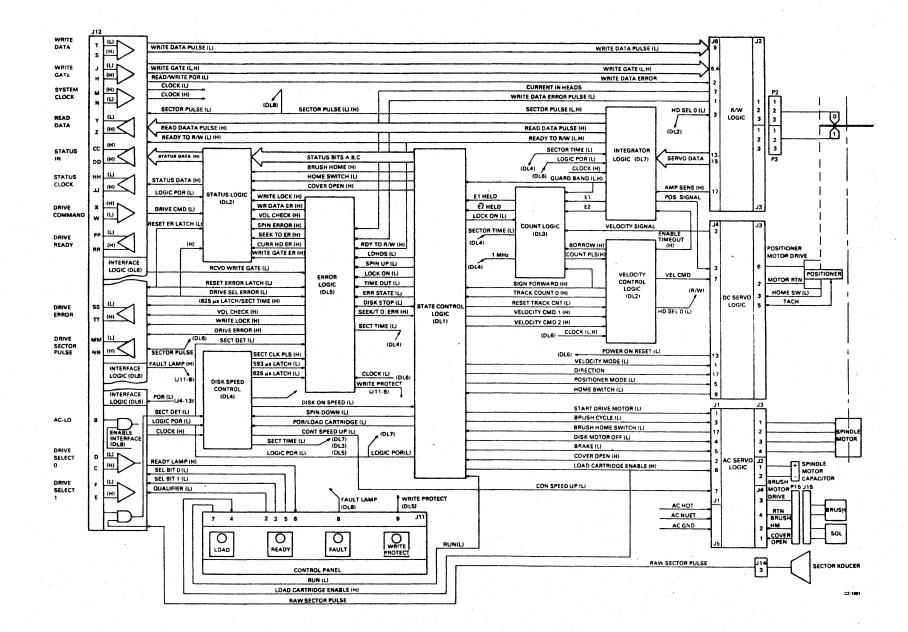

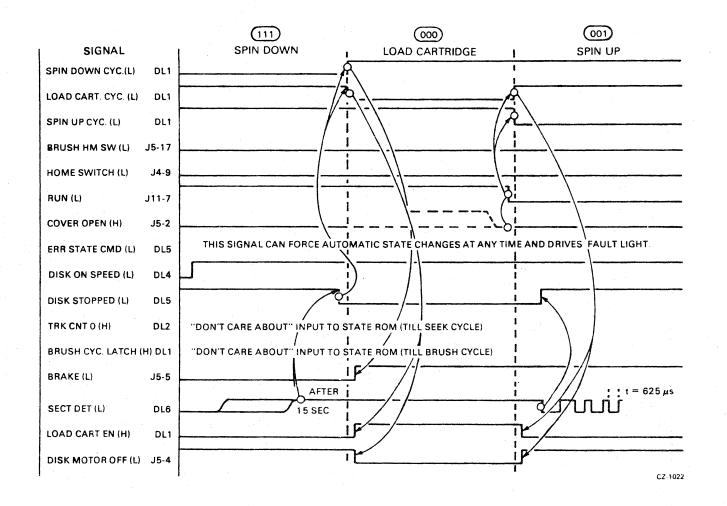

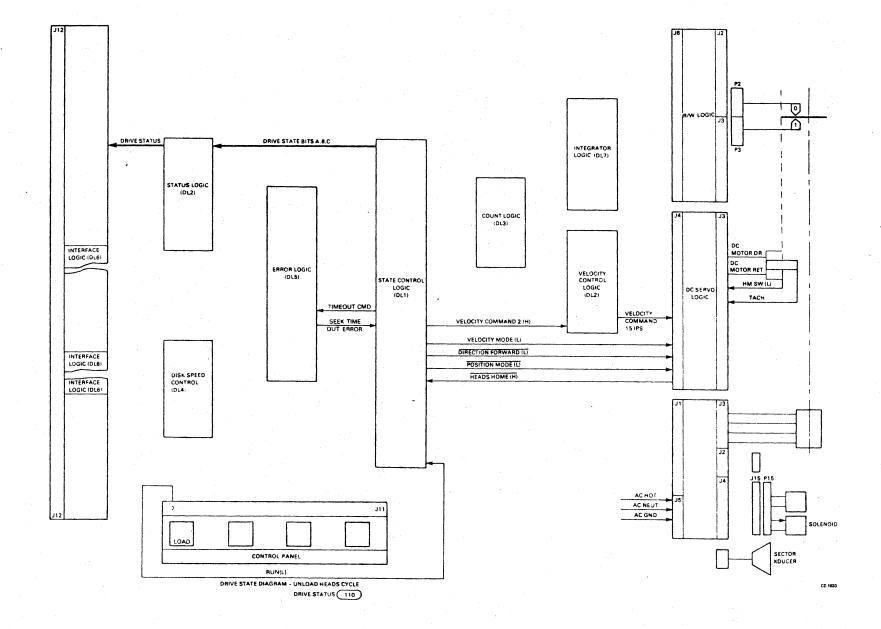

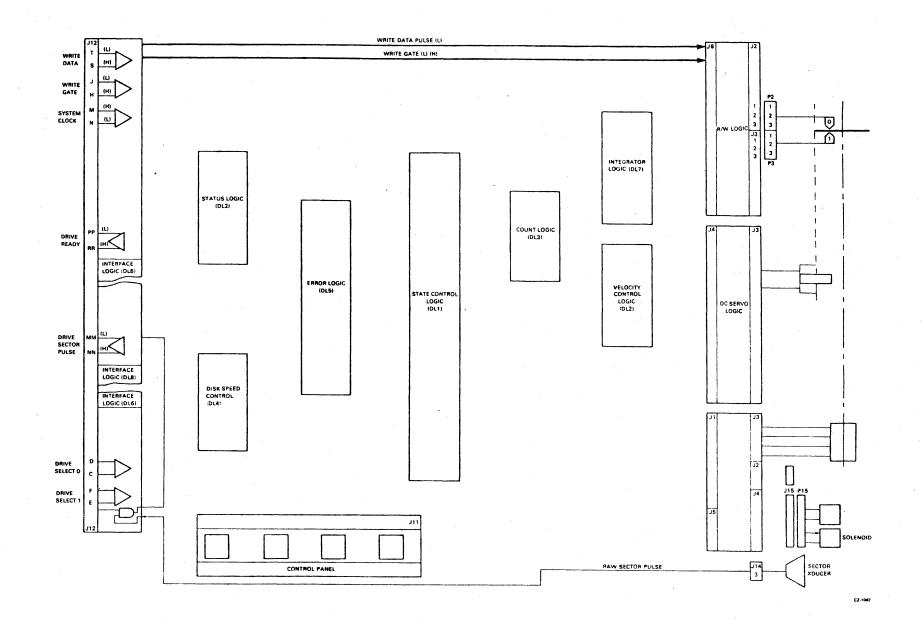

| I/4-1<br>I/4-2<br>I/4-3<br>I/4-4<br>I/4-5<br>I/4-6<br>I/4-7<br>I/4-8<br>I/4-9                                                                      | Disk Drive Detailed Block Diagram I/4-3<br>Device Startup - Load Cartridge Cycle I/4-5<br>Device Startup - Load Cartridge Timing I/4-6<br>Device Startup - Spin-up Cycle I/4-8<br>Device Startup - Spin-up Cycle Timing I/4-9<br>Device Startup - Brush Cycle I/4-11<br>Device Startup - Brush Cycle Timing I/4-12<br>Device Startup - Load Heads Cycle I/4-13<br>Device Startup - Load Heads Cycle Timing I/4-14 |

| I/4-10<br>I/4-11<br>I/4-12<br>I/4-13<br>I/4-14<br>I/4-15<br>I/4-16<br>I/4-17<br>I/4-18<br>I/4-19<br>I/4-20<br>I/4-20<br>I/4-21<br>I/4-22<br>I/4-23 | Device Startup - Seek Cycle                                                                                                                                                                                                                                                                                                                                                                                       |

| I/5-1<br>I/5-2<br>I/5-3<br>I/5-4<br>I/5-5<br>I/5-6<br>I/5-7<br>I/5-8<br>I/5-9<br>I/5-10 | State Control ROM Addressing                                |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------|

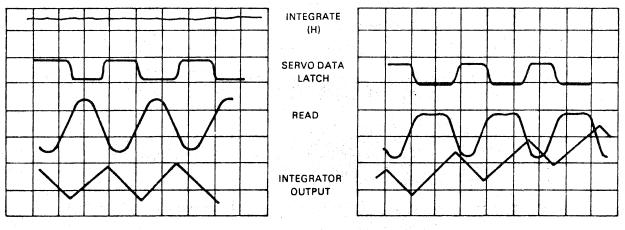

| I/5-11                                                                                  | Integrator Logic Waveforms 1/4-29                           |

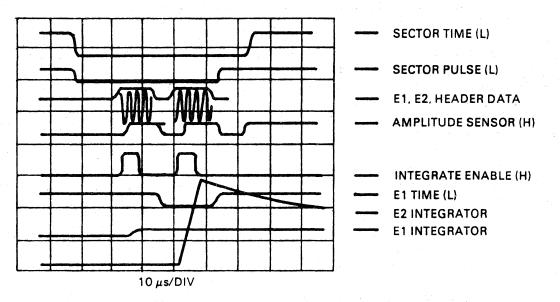

| 1/5-12                                                                                  | Ready to Read/Write Generation I/4-31                       |

| II/1-1                                                                                  | Disk Drive Controls and Indicators<br>(Front Panel) II/1-10 |

| II/1-2                                                                                  | Disk Drive Controls and Indicators<br>(Rear Panel) II/1-11  |

| II/2-1                                                                                  | Removal and Replacement Sequence Flow Chart II/2-2          |

| II/2-2                                                                                  | Front Bezel II/2-3                                          |

|                                                                                         |                                                             |

| II/2-3                                                                                  |                                                             |

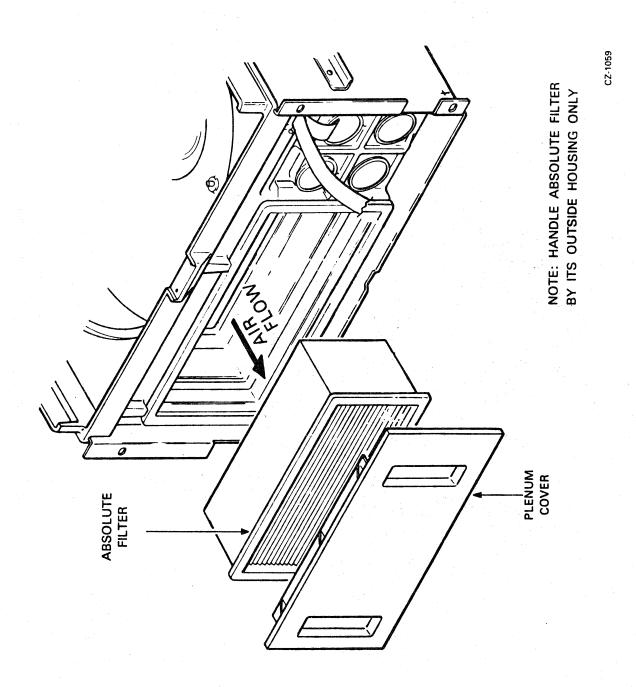

| II/2-4                                                                                  | Absolute Filter II/2-6                                      |

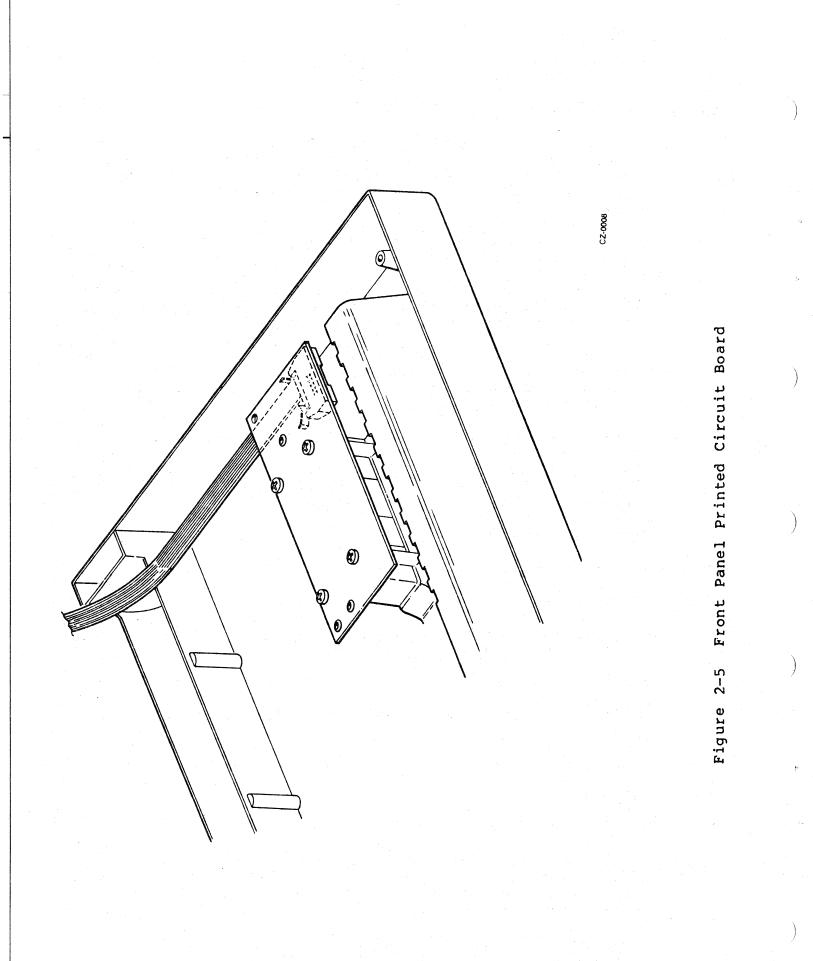

| II/2-5                                                                                  | Front Panel Printed Circuit Board II/2-8                    |

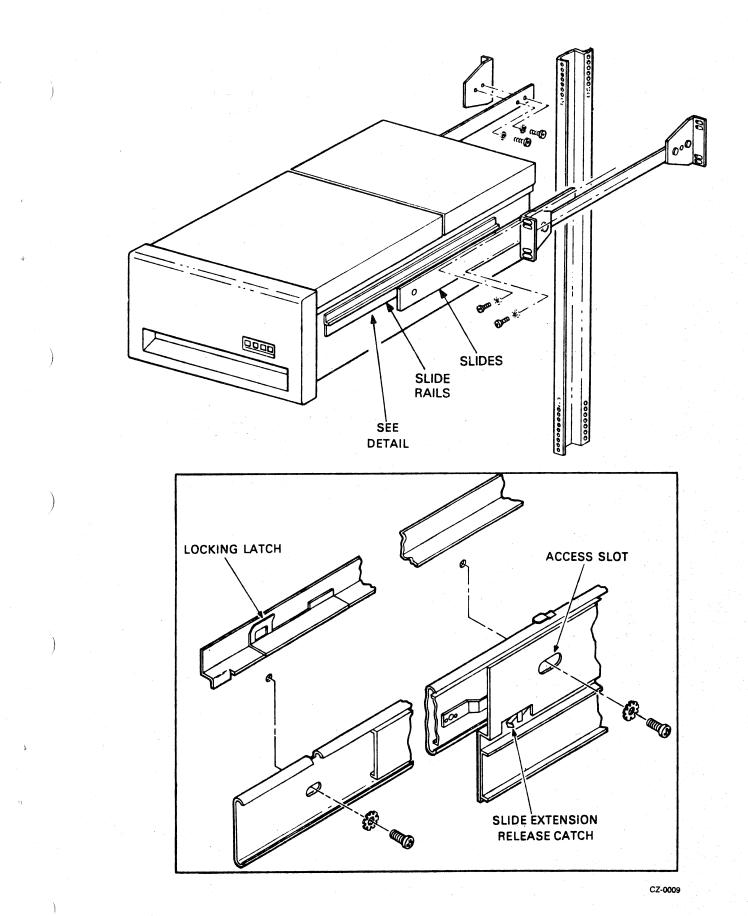

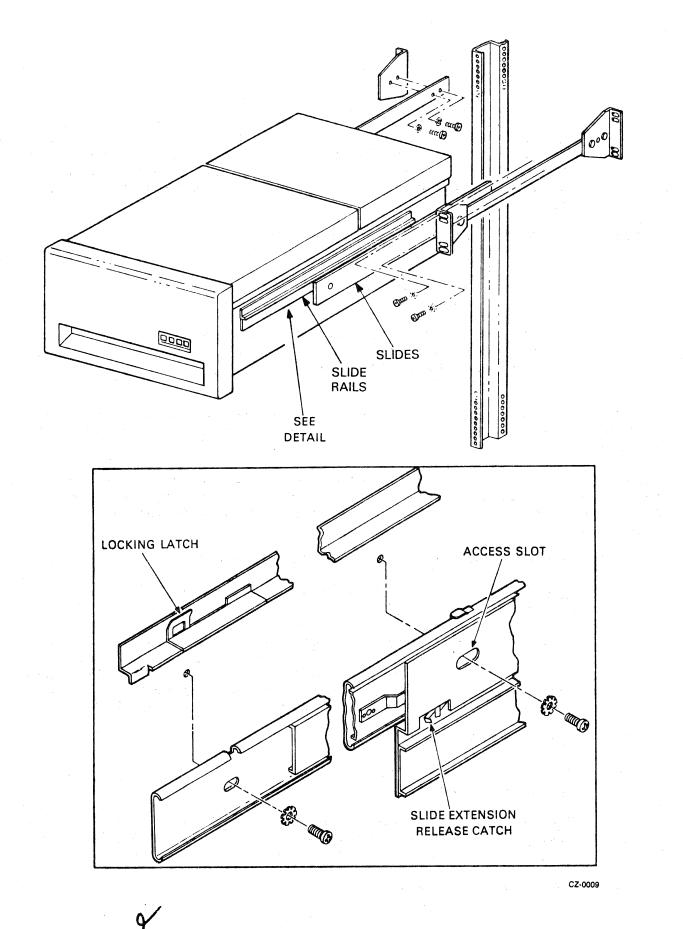

| II/2-6                                                                                  | Slide Rails II/2-9                                          |

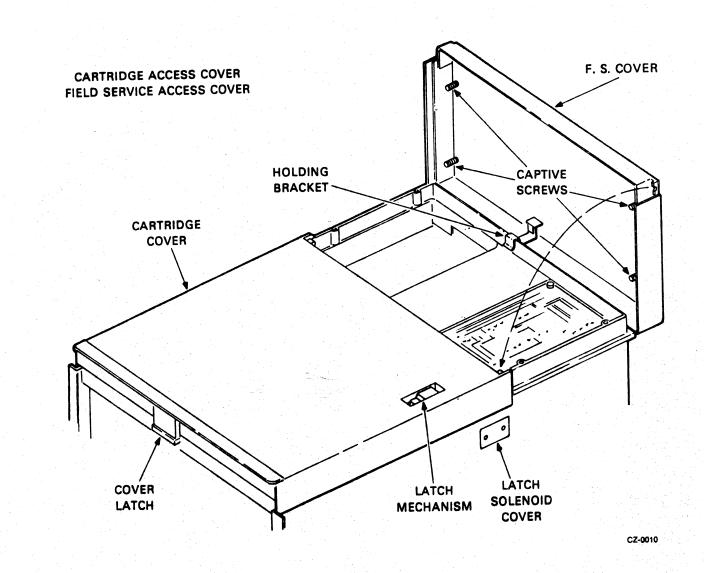

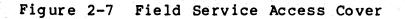

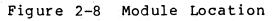

| II/2-7                                                                                  | Field Service Access Cover II/2-11                          |

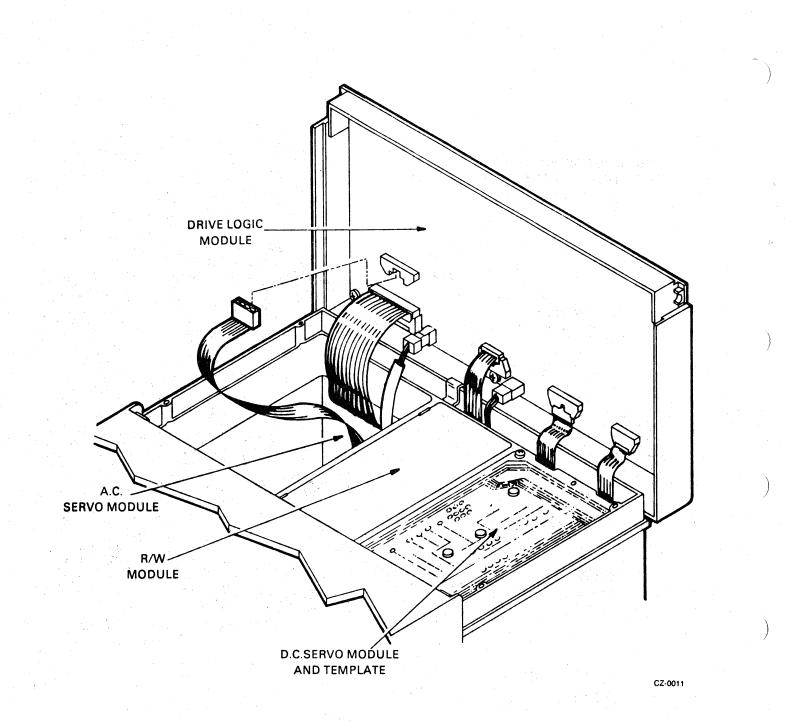

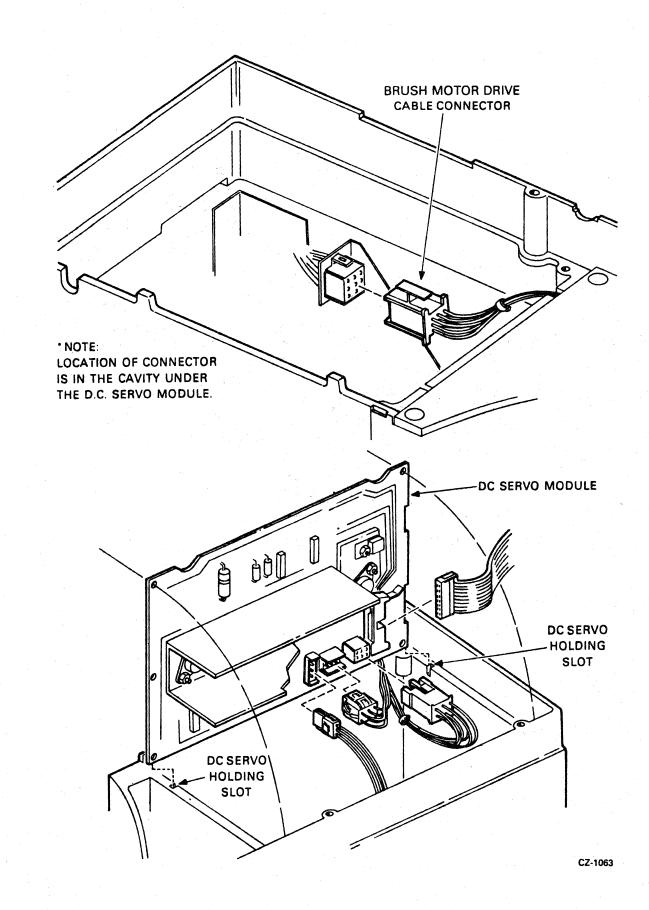

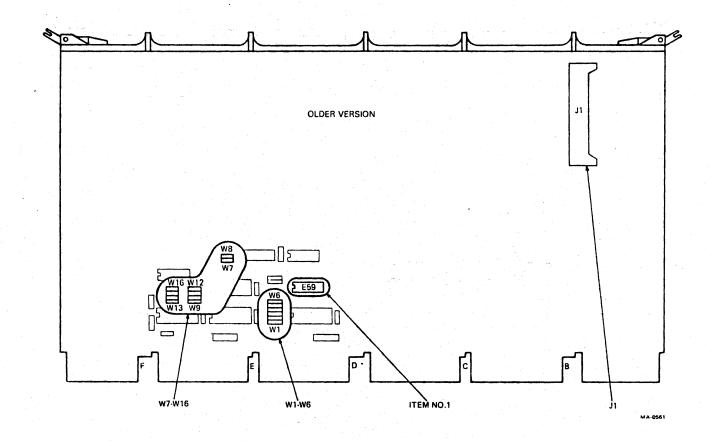

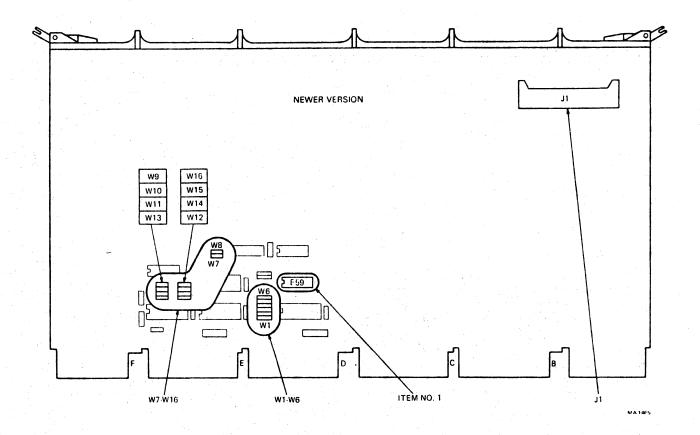

| II/2-8                                                                                  | Module Location II/2-12                                     |

| II/2-9                                                                                  | DC Servo Module II/2-15                                     |

| II/2-10                                                                                 | Exposed Drive Baseplate II/2-16                             |

| II/2-11                                                                                 | Exposed Brush Drive Assembly II/2-17                        |

| 11/2 - 12                                                                               | AC Servo Module II/2-19                                     |

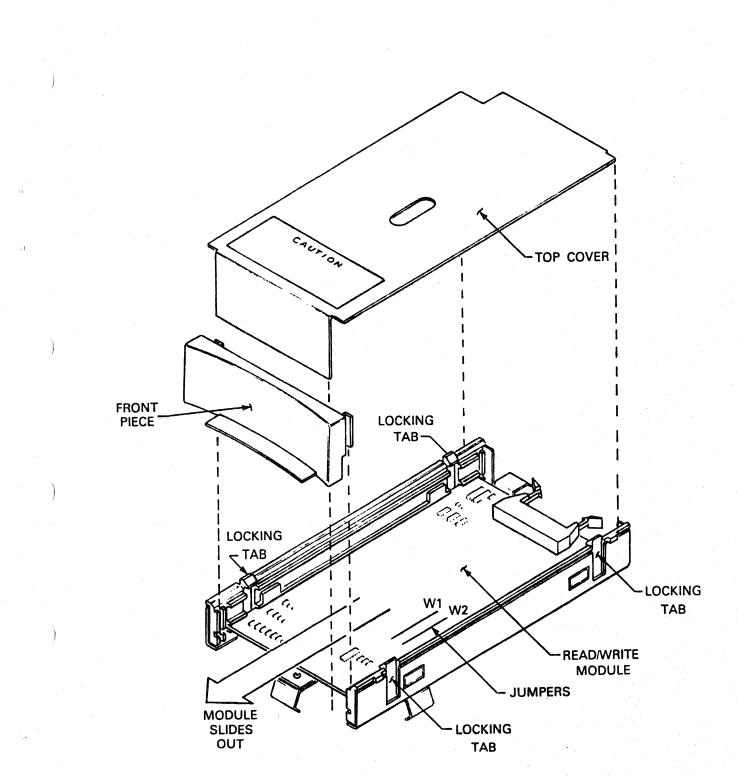

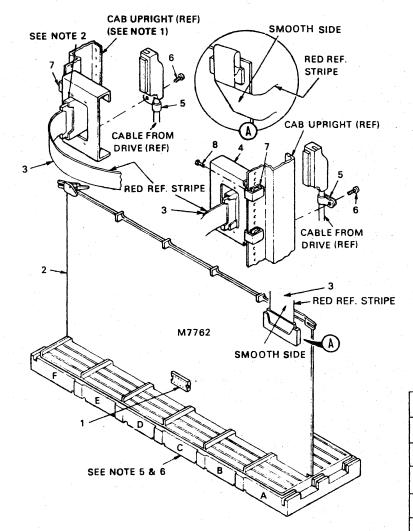

| II/2-13                                                                                 | Read/Write Module (Upright) II/2-22                         |

| II/2 - 14                                                                               | Read/Write Module Box Disassembly II/2-23                   |

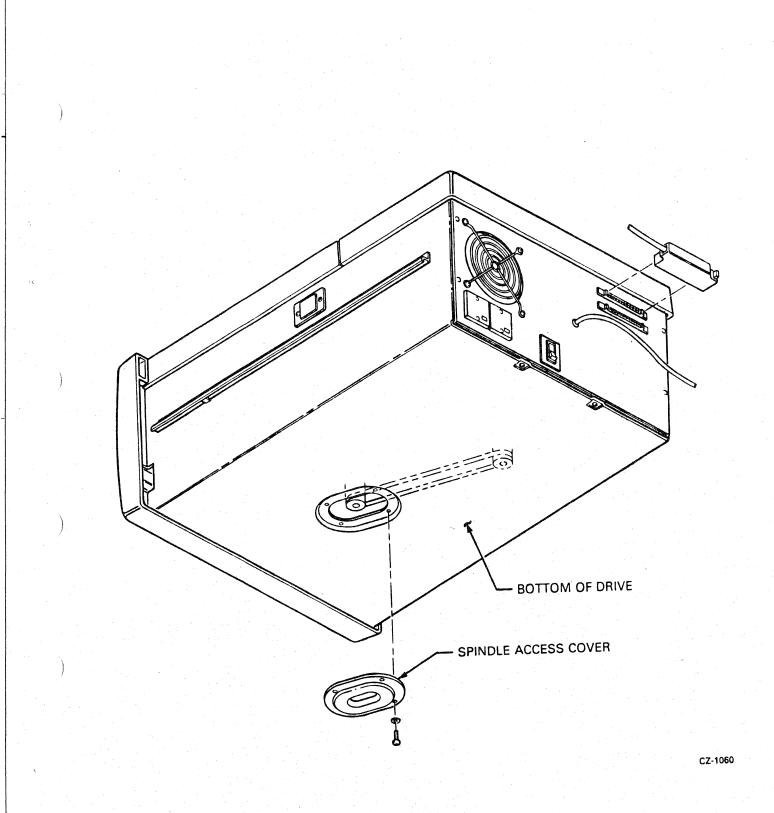

| II/2-15                                                                                 | Spindle Access Cover II/2-25                                |

| II/2 - 16                                                                               | Spindle Ground Button II/2-26                               |

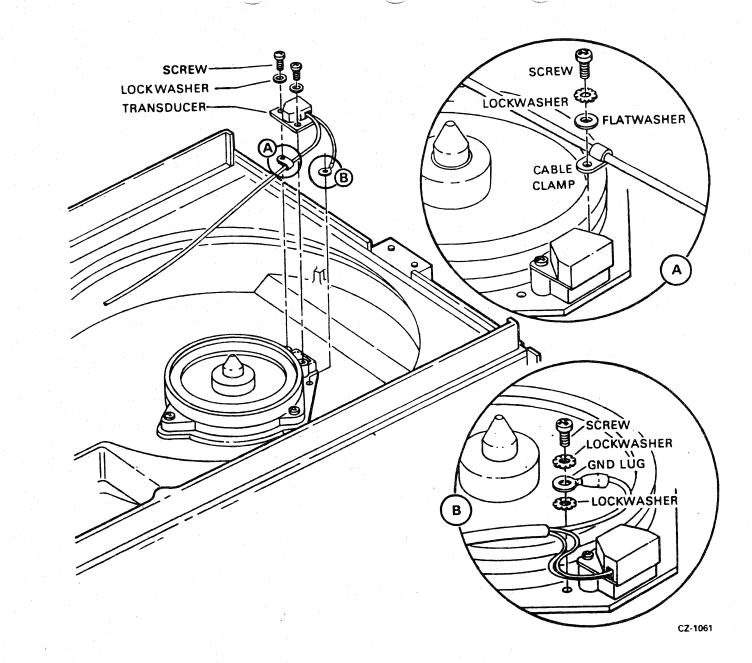

| II/2-17                                                                                 | Sector Transducer Mounting II/2-27                          |

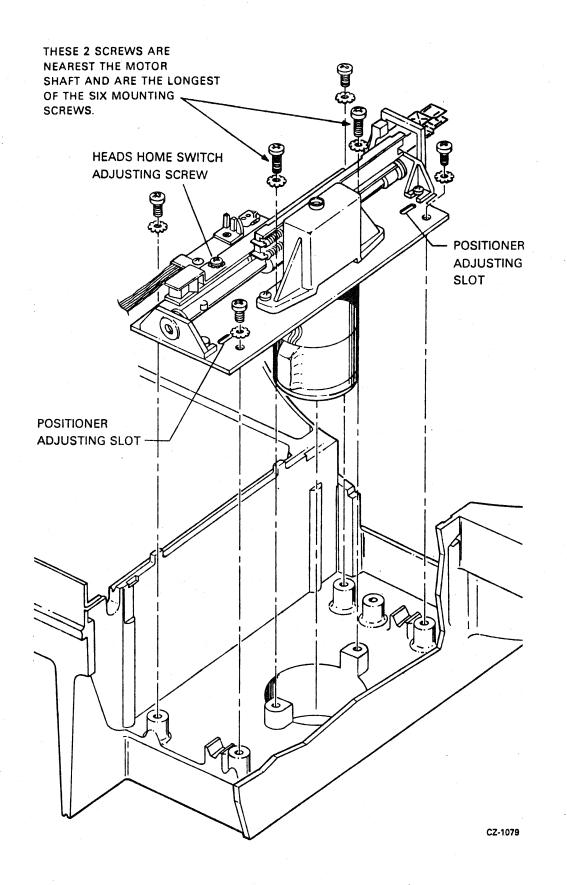

| II/2-18                                                                                 | Positioner Assembly II/2-30                                 |

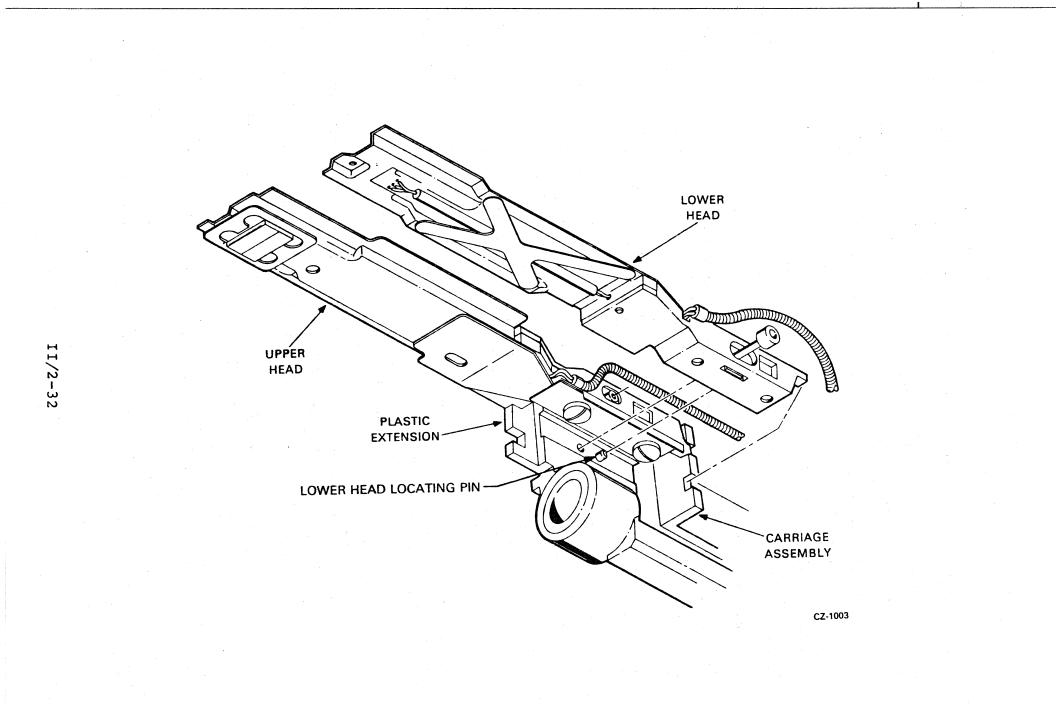

| II/2-19                                                                                 | Read/Write Heads II/2-32                                    |

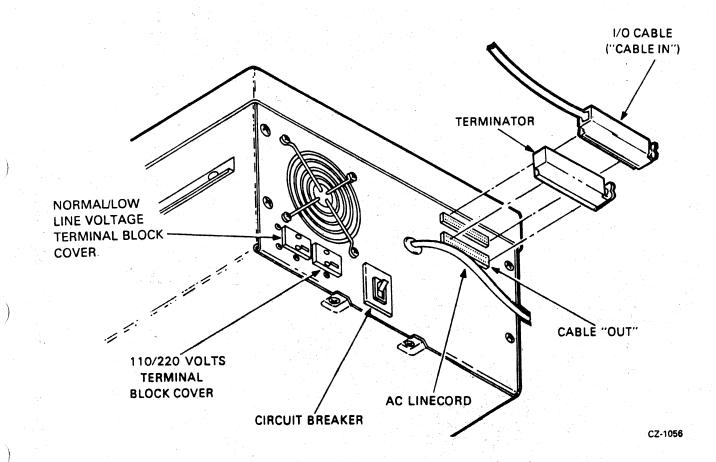

| 11/2-20                                                                                 | Rear View of Drive II/2-35                                  |

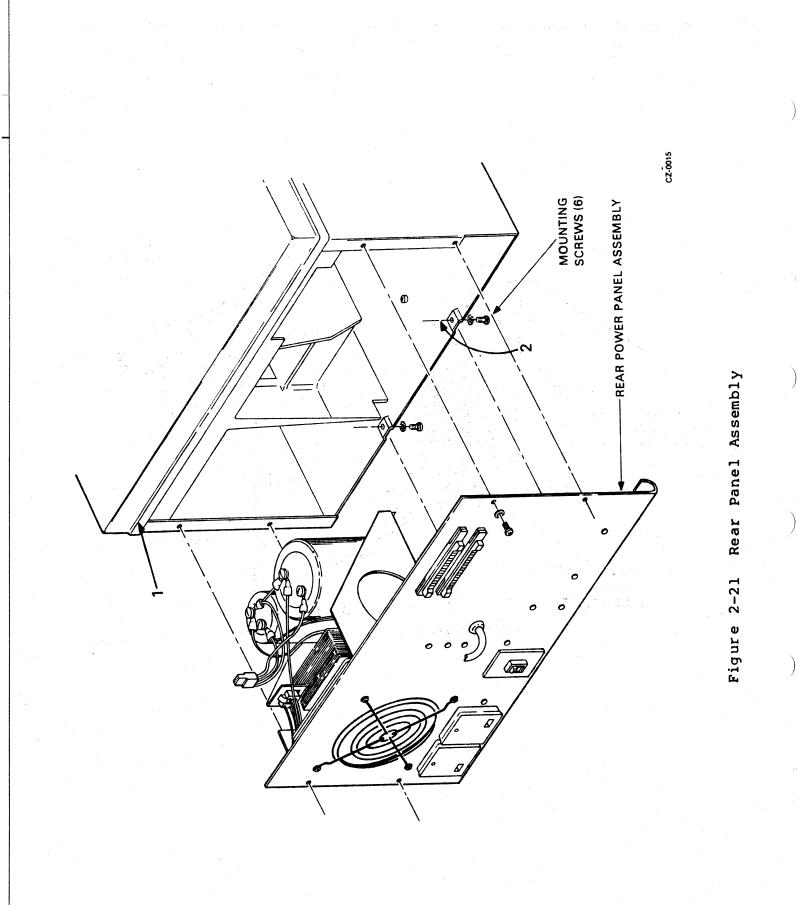

| II/2-21                                                                                 | Rear Panel Assembly II/2-36                                 |

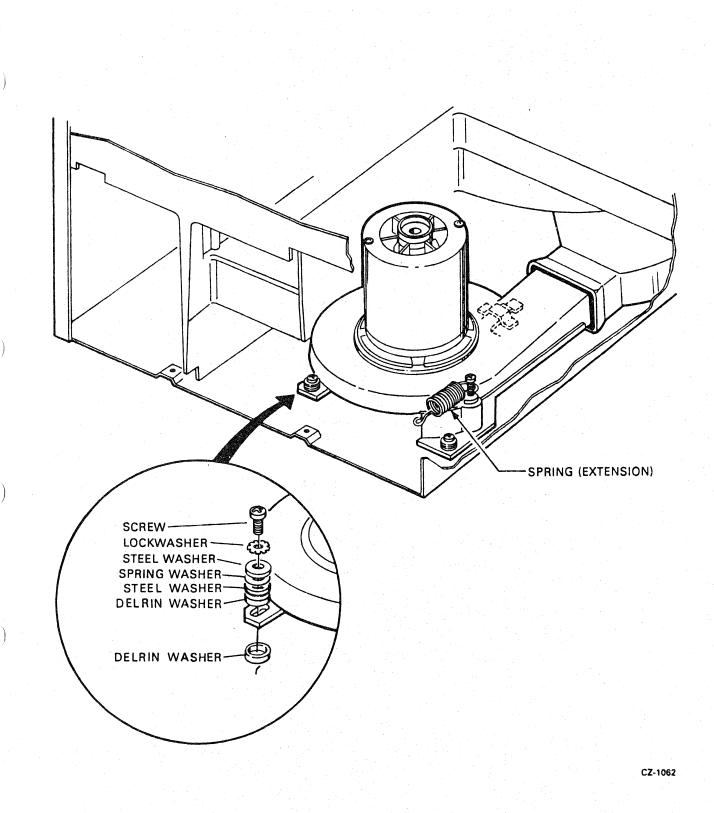

| II/2-22                                                                                 | Drive Motor Mounting II/2-37                                |

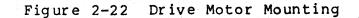

| 11/2 - 23                                                                               | Drive Belt Tension II/2-39                                  |

| II/2-24                                                                                 | Circuit Breaker II/2-41                                     |

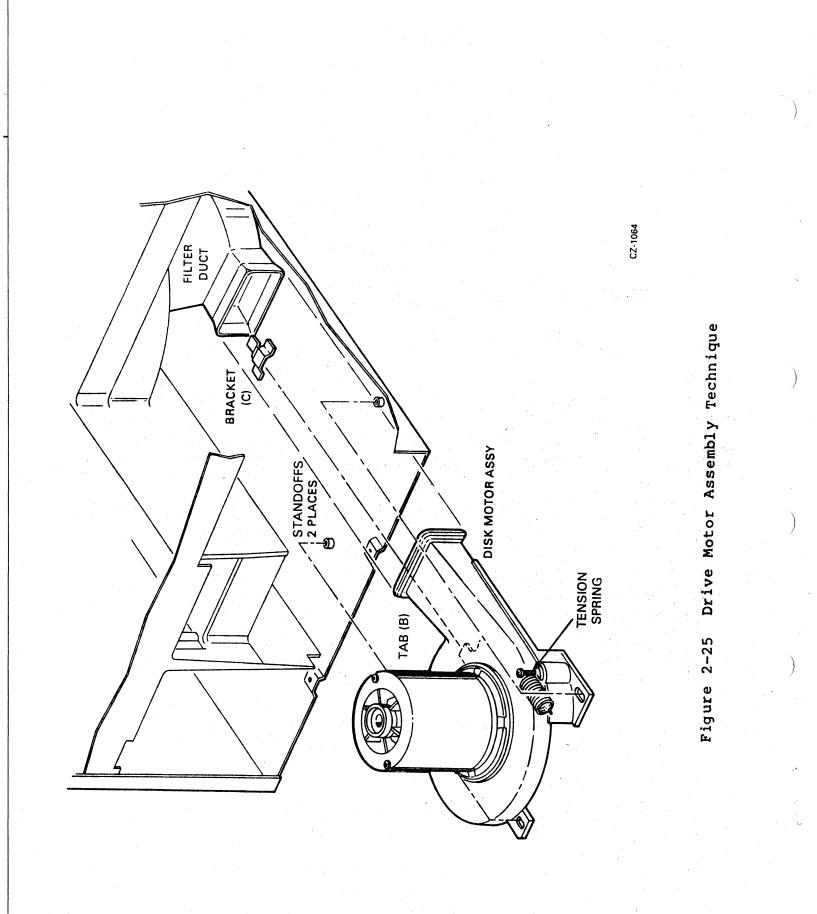

| II/2-25                                                                                 | Drive Motor Assembly Technique II/2-41                      |

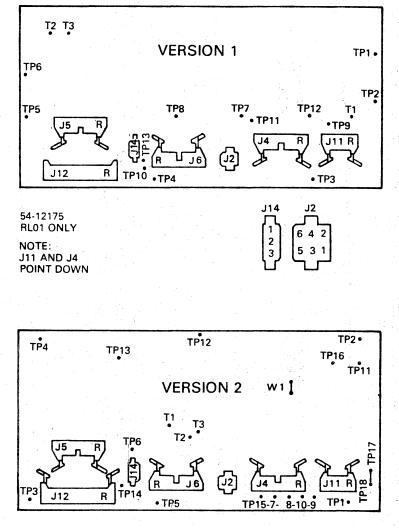

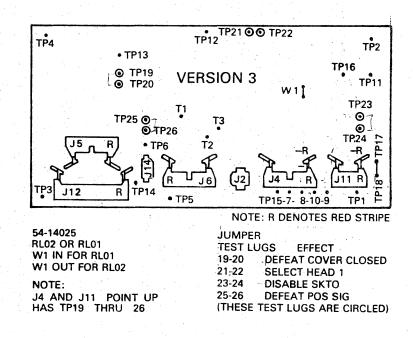

| II/3-1                                                                                  | Drive Logic Module Layout II/3-2                            |

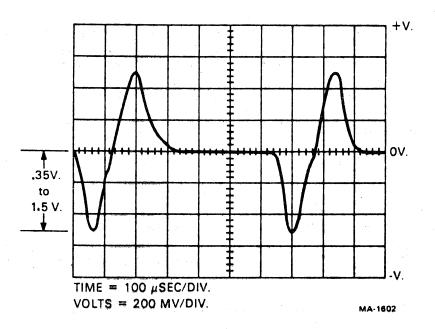

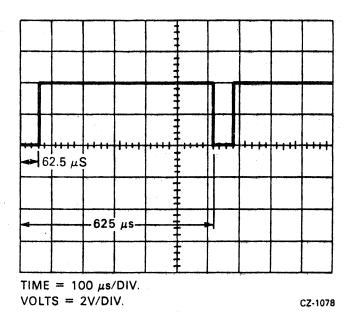

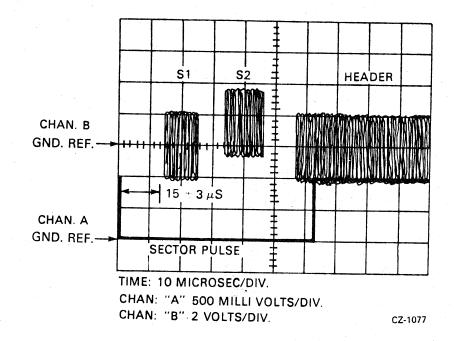

| II/3-2                                                                                  | Sector Transducer Output II/3-5                             |

| II/3-3                                                                                  | Sector Pulse Timing II/3-7                                  |

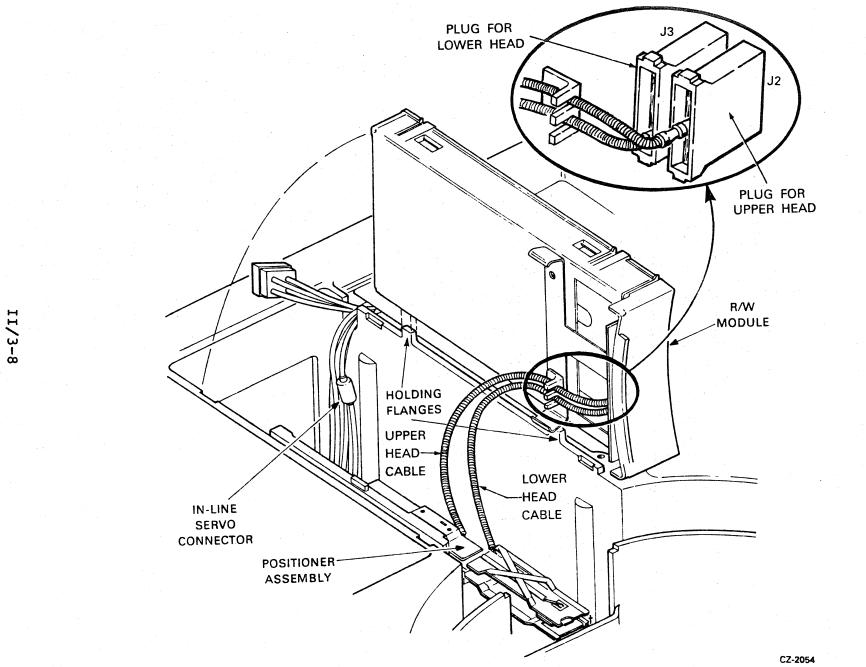

| II/3-4                                                                                  | Positioner and Read/Write Module Box                        |

|                                                                                         | Assembly II/3-8                                             |

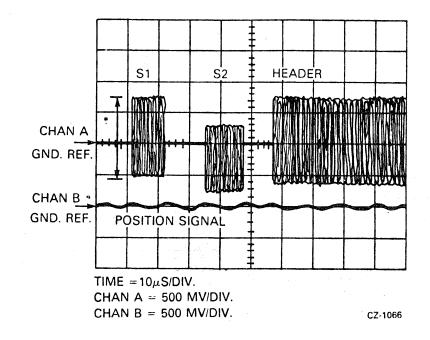

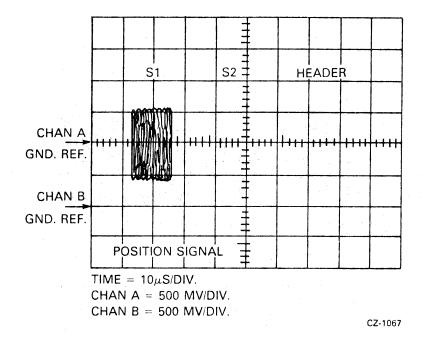

| II/3-5                                                                                  | Servo Bursts and Sector Pulse II/3-10                       |

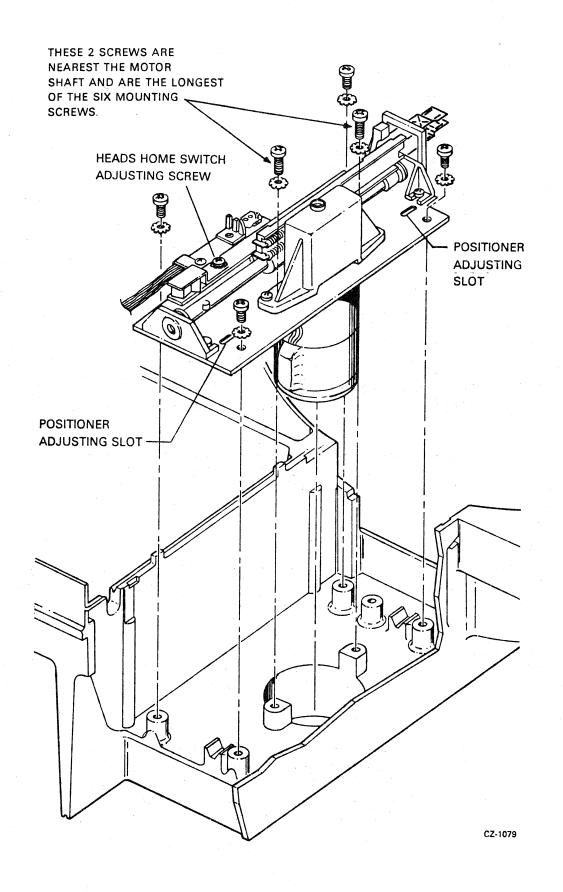

| II/3-6                                                                                  | Positioner Assembly II/3-12                                 |

| II/3-7                                                                                  | Servo Bursts and Position Signal II/3-15                    |

| II/3-8                                                                                  | Outer Guard Band Servo Data II/3-16                         |

|                                                                                         |                                                             |

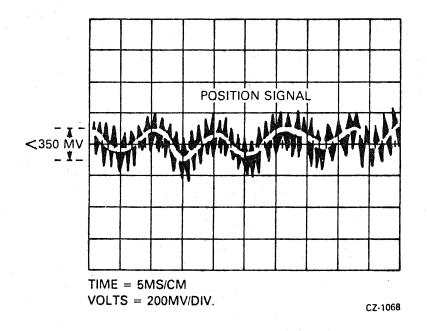

| II/3-9                                                                                  | Position Signal II/3-21                                     |

)

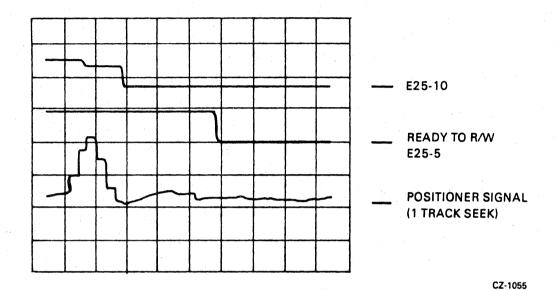

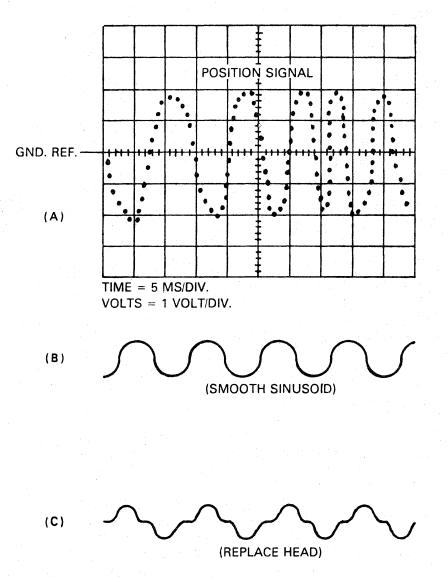

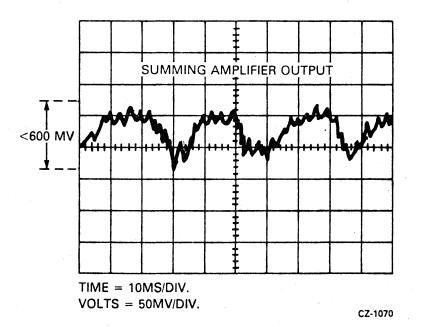

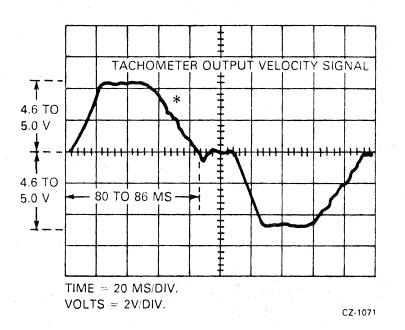

| II/3-10<br>II/3-11<br>II/3-12<br>II/3-13<br>II/3-14<br>II/3-15<br>II/3-16                                                                              | Position Signal Gain Check Waveforms II/3-24<br>Summing Amplifier Output II/3-26<br>Tachometer Output Velocity Signal II/3-28<br>Positioner Motor Current Check II/3-30<br>Access Time Check (One Track Seek) II/3-32<br>Access Time Check (85 Track Seek) II/3-34<br>Access Time Check (255 Track Seek) II/3-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

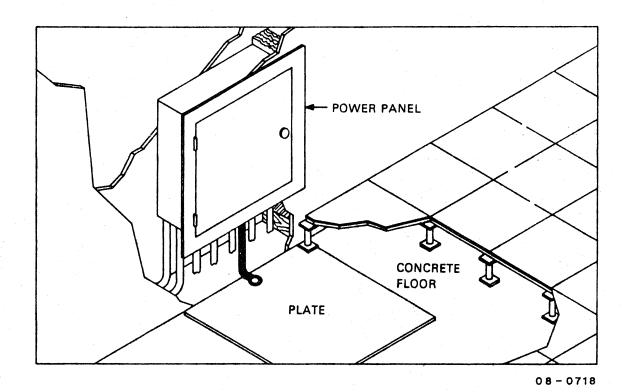

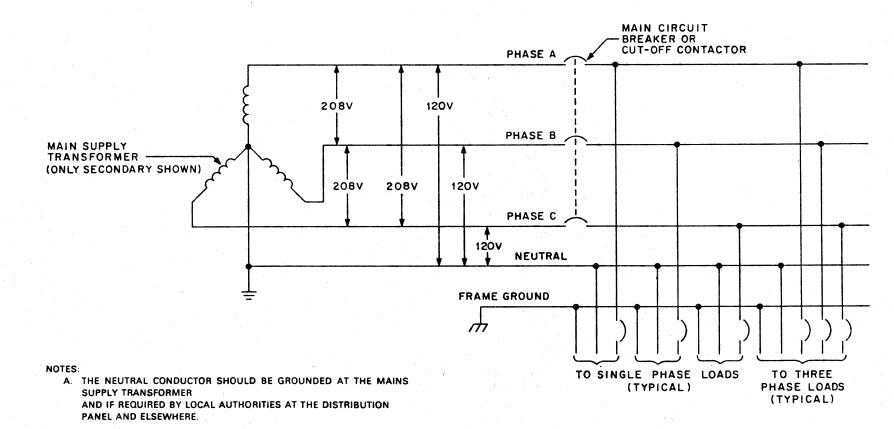

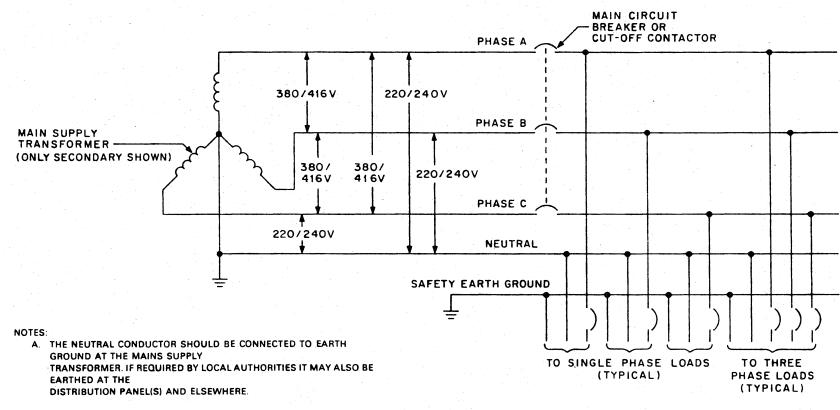

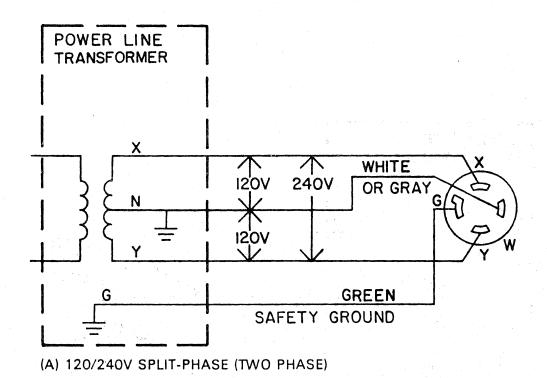

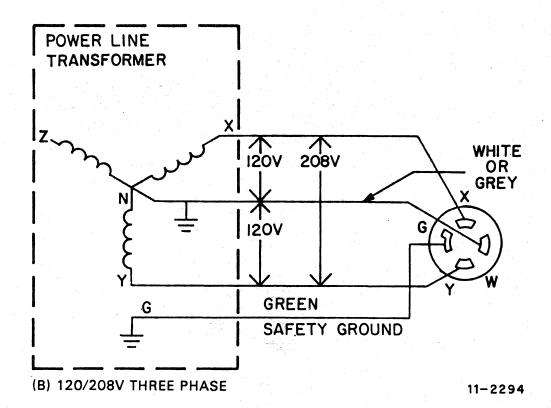

| II/3-16<br>B-1<br>B-2<br>B-3<br>B-4<br>B-5<br>B-6<br>B-7<br>B-8<br>B-9<br>B-10<br>B-11<br>B-12<br>B-13<br>B-14<br>B-15<br>B-16<br>B-17<br>B-18<br>B-19 | Access Time Check (255 Track Seek) II/3-35<br>RLØ1/RLØ2 Disk Drive - Rear View B-7<br>Approved Electrical Plugs and Receptacles B-8<br>Power Panel Grounded to Building Frame B-9<br>Power Panel Grounded to Metal Plate B-11<br>Typical 60 Hz Power System B-12<br>Typical 50 Hz Power System B-14<br>Split Phase (2-Phase) Power System B-15<br>Three Phase Y Power System B-16<br>RL11 Component Layout B-17<br>RL11 Base and Vector Address Jumper<br>Configuration B-20<br>RL11 Priority Jumper Assembly Connections B-21<br>RL11 Controller Installation B-22<br>RLV11 Bus Interface Module (M8014)<br>(Component Side) B-24<br>RLV11 Base Address Switch Settingss B-26<br>RLV11 Vector Address Switch Settings B-28<br>H9273 Backplane Grant Priority Structure B-30<br>H950 Shipping Package B-30 |

| B-2Ø                                                                                                                                                   | RLØ1/RLØ2 Cabinet Installation B-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

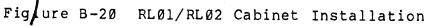

| B-21                                                                                                                                                   | RLØ1/RLØ2 - Covers Removed B-36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

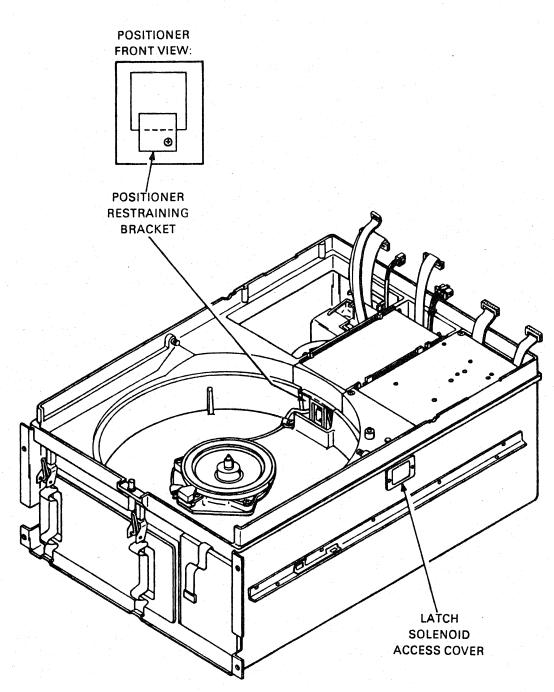

| B-22                                                                                                                                                   | RLØ1/RLØ2 Disk Drive - Rear View B-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B-23                                                                                                                                                   | RLØ1/RLØ2 Disk Drive - Front View B-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B-24                                                                                                                                                   | RLØ1/RLØ2 Disk Drive - Exposed Drive Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                        | Module B-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# TABLES

| Table No.                                                   | Title                                                                                                                                                                                                                                                                         | Page No.                                                            |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| I/1-1<br>I/1-2                                              | RLØ1/RLØ2 Subsystem Documentation<br>RLØ1/RLØ2 Disk Drive Physical and                                                                                                                                                                                                        |                                                                     |

| I/1-3                                                       | Environmental Specifications<br>RLØ1/RLØ2 Disk Drive Operational                                                                                                                                                                                                              | . I/1-18                                                            |

| I/1-4                                                       | Specifications<br>RLØ1K/RLØ2K Disk Cartridge Specifications                                                                                                                                                                                                                   |                                                                     |

| I/3-1<br>I/3-2                                              | Drive Bus Interface Lines<br>Drive Status Word                                                                                                                                                                                                                                |                                                                     |

| I/5-1<br>I/5-2<br>I/5-3<br>I/5-4                            | Velocity ROM Addressing<br>Track Count vs. Servo Samples and Direction .<br>Distance and Velocity Thresholds<br>Count ROM Map                                                                                                                                                 | • I/5-18<br>• I/5-19                                                |

| II/1-1<br>II/1-2<br>II/1-3<br>II/1-4<br>II/1-5              | RLØ1/RLØ2 Documentation<br>FRU Part Numbers and Interchangeability<br>Recommended Spare Parts List<br>Diagnostic Supervisor Commands<br>Command Parameters                                                                                                                    | . II/1-3<br>. II/1-4<br>. II/1-6                                    |

| II/3-1<br>II/3-2                                            | Service Jumpers for Drive Logic Module<br>Method for Selecting Heads                                                                                                                                                                                                          |                                                                     |

| A-1<br>A-2                                                  | Controller Addressable Registers<br>RL8-A Instruction Set                                                                                                                                                                                                                     | A-1<br>A-11                                                         |

| B-1<br>B-2<br>B-3<br>B-4<br>B-5<br>B-6<br>B-7<br>B-8<br>B-9 | Saleable RLØ1/RLØ2 Subsystem Options<br>Saleable Cabinet Options<br>Diagnostic Catalogs and Indexes<br>RL11-Based Diagnostics<br>RL11 Diagnostic Kit Numbers<br>RL11 Diagnostic Components<br>User Documents<br>RLV11 Diagnostic Components<br>RL8/RLØ1 Diagnostic Components | B-5<br>B-42<br>B-43<br>B-43<br>B-43<br>B-44<br>B-45<br>B-46<br>B-46 |

| B-10<br>B-11<br>B-12                                        | RL8/RL01 Diagnostic Kits<br>RL8/RL02 Diagnostic Kits<br>RL8/RL02 Diagnostic Components                                                                                                                                                                                        | B-47                                                                |

SECTION 1 TECHNICAL DESCRIPTION

# CHAPTER 1 INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

The RLØ1/RLØ2 Disk Drive is a random access mass storage device. Both drives utilize a removable, single platter top-loading disk cartridge. The RLØ1K cartridge provides five million bytes of storage, and the RLØ2K cartridge will hold ten million bytes. Up to four RLØ1 or RLØ2 Disk Drives may be used per controller to provide up to 40 million bytes of storage for PDP-8, PDP-11, and LSI-11 computer system applications.

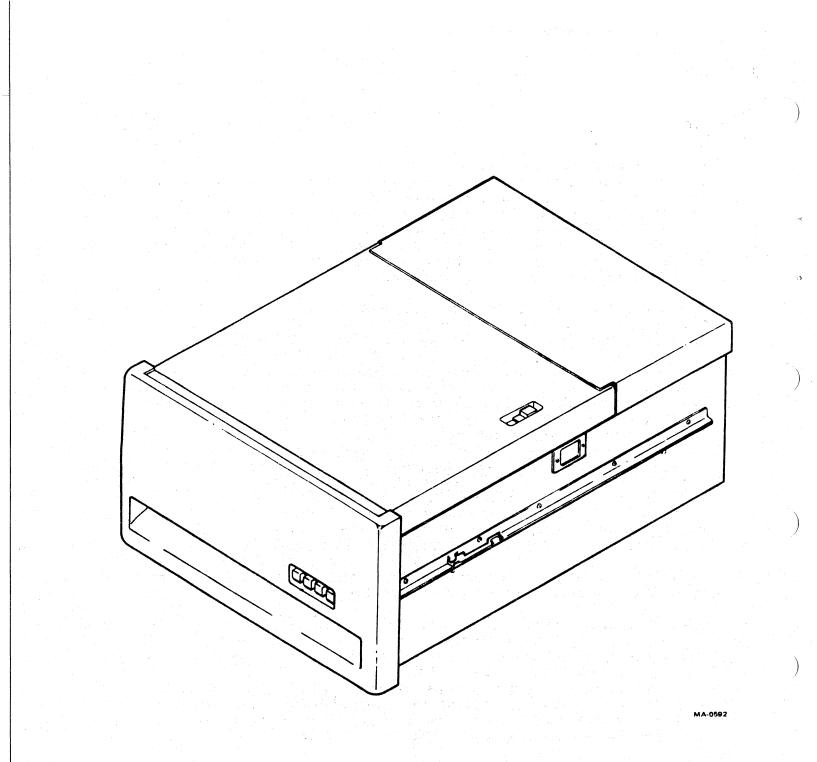

The RLØ1/RLØ2 Disk Drive (Figure 1-1) is mounted on slides and is 26.6 cm (10.5 in) high, 63.5 cm (25 in) deep (compatible in width to a 19 inch RETMA rack) and weighs 34 kg (75 lbs).

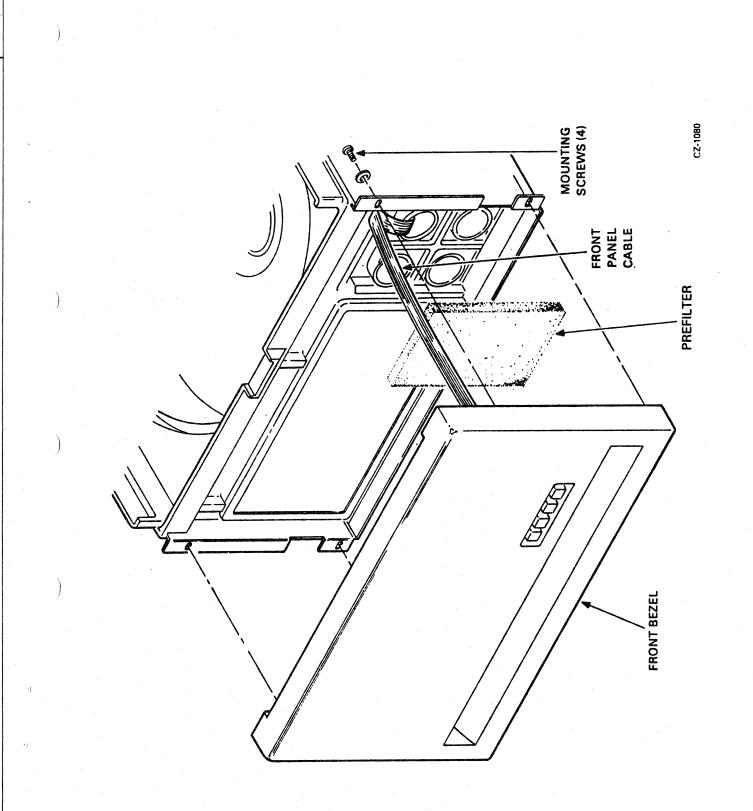

Operating controls and indicators plus a removable air filter are located at the front of the drive. Access to the cartridge is provided by a lift-up cover incorporating a safety interlock. All servicing can be achieved from the top of the drive or front or rear of the corporate cabinet.

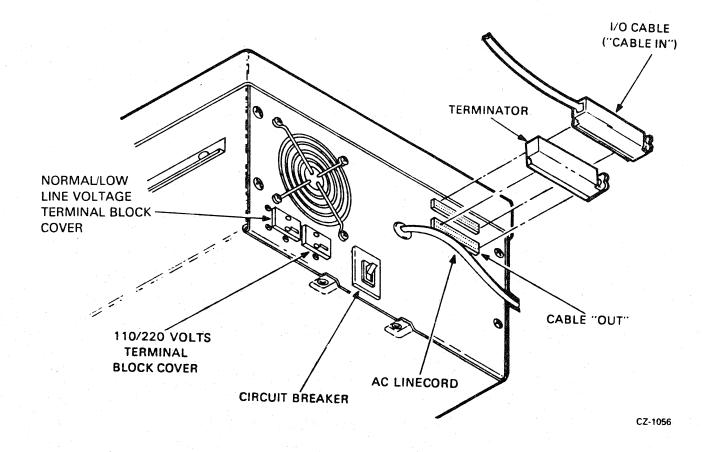

RL01/RL02 Disk Drives are shipped from the factory as 115 Vac/60 Hertz units. Field change to 230 Vac/50 or 60 Hertz is accomplished by reversing either of two terminal block covers located externally at the rear of the drive. The line cord plug may be cut and replaced with an applicable 230 Vac line plug. The RL01/RL02 Disk Drive is UL listed and CSA certified.

Interlocks are provided where the potential exists for damage to the drive, media, operators, or service personnel.

The RLØ1/RLØ2 Disk Drive provides high field performance and maintainability. The drive is designed for easy removal and replacement of logic and electromechanical subassemblies to result in an average replacement time of not more than 15 minutes. Special tools and alignment packs or fixtures are not required for on-site maintenance. Only two adjustments are required under normal service conditions. All logic modules are placed so that they may be accessed without the use of extenders.

#### 1.1.1 Servo-In-Data Concept

Key to the performance of the RLØ1/RLØ2 is the servo-in-data concept. The concept allows the derivation of head positioning and track counting information from pulses imbedded within the data track. Each read/write head seeking to a desired track becomes its own servo transducer. Data tracks could conceivably be located within a band anywhere on the recordable disk surface as long asthe positioner does not run out of travel limits. Since the heads seek and center on data tracks, environmental problems related to mechanical drift and tolerances become practically nonexistent. Precise head alignment requiring the use of special fixtures is unnecessary.

Figure 1-1 Typical Disk Drive

#### 1.1.2 Storage Medium

The RLØ1K or RLØ2K Disk Cartridge is a modified 5440 type removable, top-loading, single platter cartridge with 256 discrete data tracks on each of the two recording surfaces. The cartridge armature plate contains 40 sector slots, defining 40 sectors per track. Servo information (servo-in-data) from which sector and track determinations are made is prerecorded on the cartridge at the factory and cannot be reformatted in the field. Bad sector information is contained on the last data track.

RLØ1K and RLØ2K cartridges are intended as a means of data interchange between computer systems. Data written on one RLØ1 Disk Drive will be readable on any other RLØ1 drive, and the same is true for any two RLØ2 drives, provided that both drives have been properly maintained and that the computer systems and controllers are compatible with respect to word length. Note, however, that an RLØ1K cartridge cannot be used on an RLØ2 drive, nor can an RLØ2K cartridge be used on an RLØ1 drive. While either cartridge will physically fit into either drive, the results of using the wrong cartridge are unpredictable. The cartridge are color keyed and labeled to help prevent incorrect use.

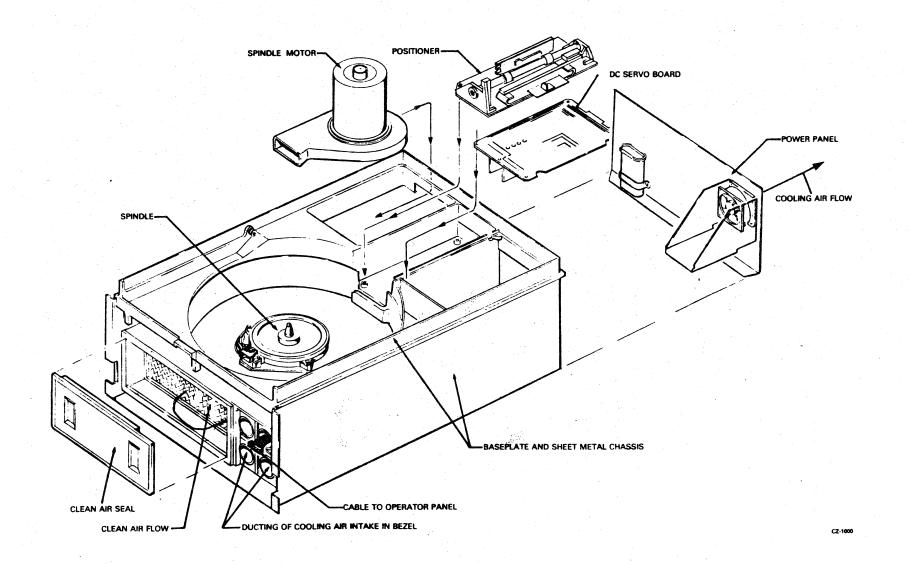

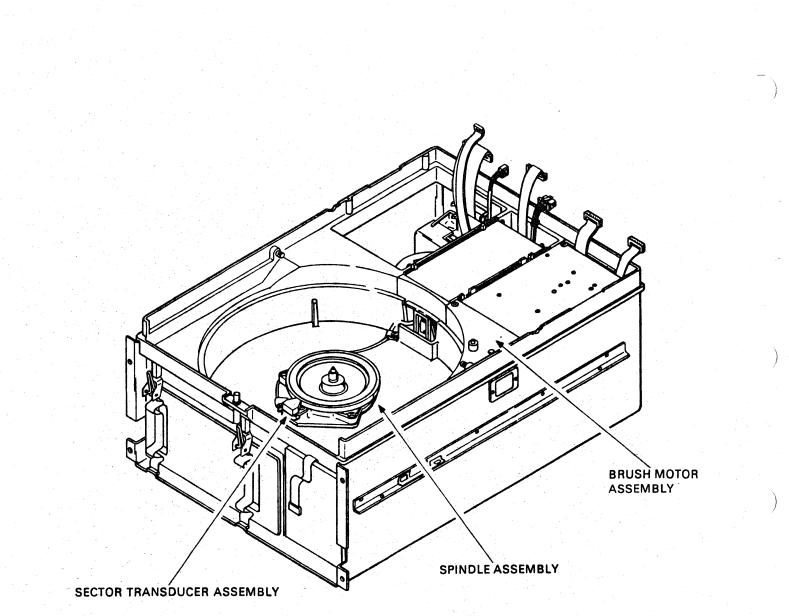

1.1.3 Mechanical Partitioning Figure 1-2 shows location of the major drive subassemblies and air flow through the drive chassis.

Air Flow System - The RLØ1/RLØ2 Disk Drive is designed 1.1.3.1 to achieve maximum protection of the head/disk interface even in a contaminated environment. The air flow system (Figure 1-2) is separated into a recirculating clean air supply and a cooling air The cooling air is drawn in through the bezel and is supply. exhausted out the rear of the drive by a muffin fan. The recirculating clean air is moved through the duct system by an impeller attached to the spindle drive motor. Before the clean air is recirculated to the disk cartridge, the duct system routes it through a high efficiency filter and a heat exchanger. The heat exchanger is cooled by the cooling air supply.

1.1.3.2 Air Filter - The absolute air filter is a self-contained throwaway unit. Because of the two air systems, replacement of the absolute filter is only required on a yearly basis.

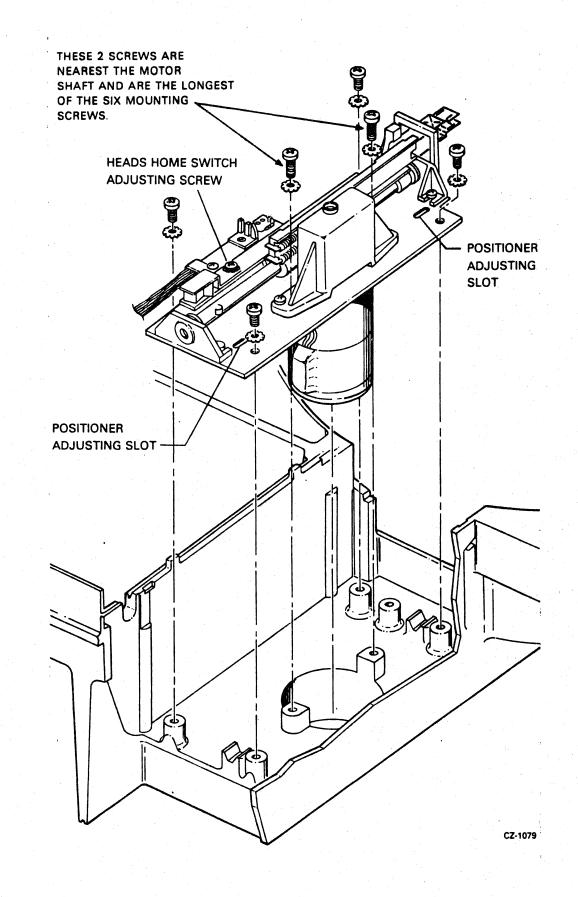

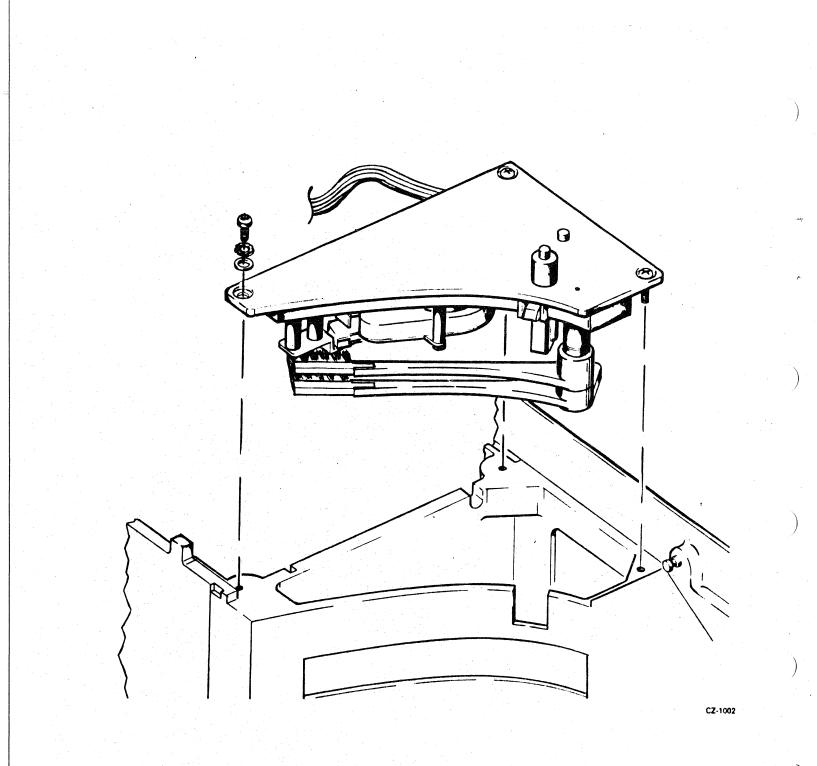

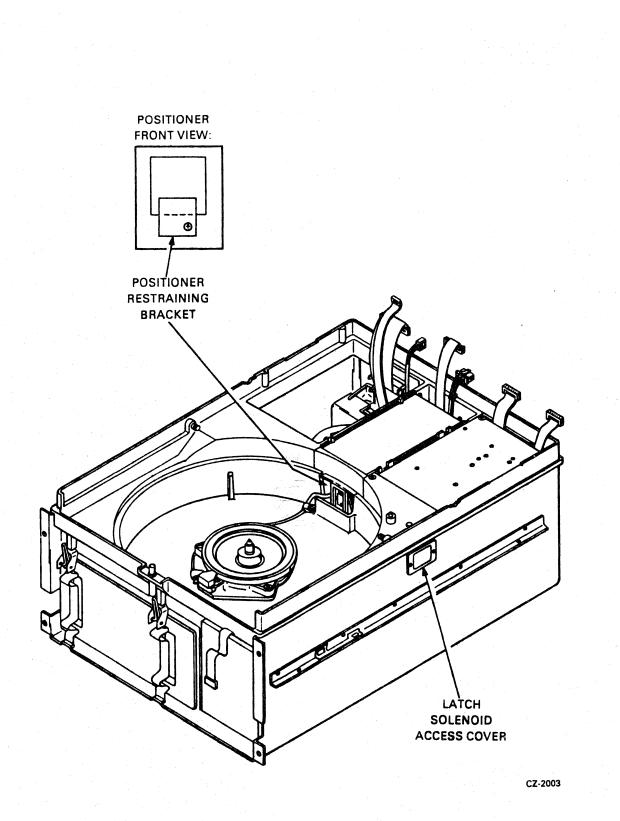

1.1.3.3 Positioner Assembly - The positioner assembly consists of a carriage, servo motor with capstan and tension cable, linear tachometer, head load cam, and home switch. The magnetic read/write heads are mounted on the carriage. Figure 1-3 illustrates the principle components of the positioner assembly. The positioner subplate can be moved laterally to align head access radially to the disk.

1/1-4

Figure 1-2 Major Subassemblies and Air Flow

# Figure 1-3 Positioner Assembly

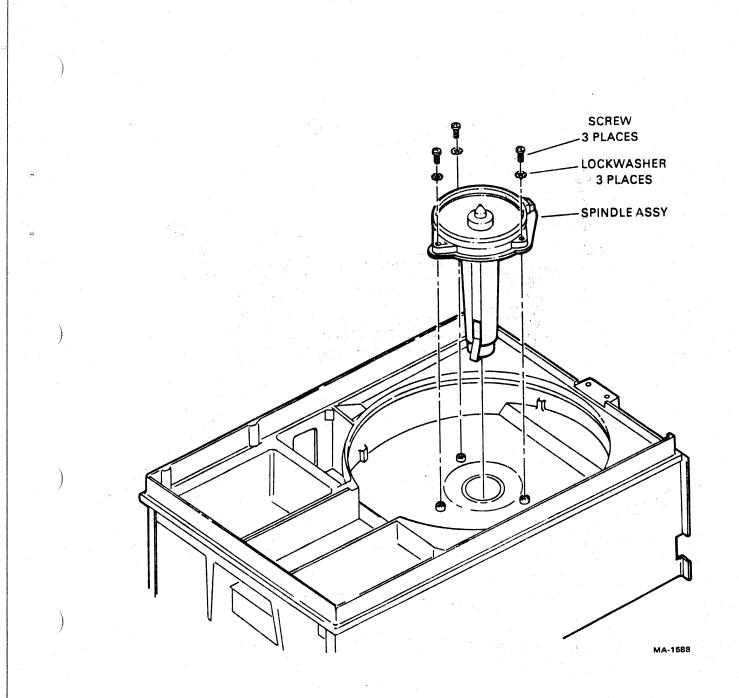

1.1.3.4 Spindle Assembly - The Spindle Assembly comprises a housing, the rotating cartridge interface hub, the spindle ground button, and the drive belt. Figure 1-4 shows the Spindle Assembly.

The sector transducer mounts and aligns itself on the spindle housing.

The disk cartridge interfaces the spindle via a cone located in the center of the spindle, a 14.0 cm (5.5 in) diameter stabilizing hub, and a hold-down magnet.

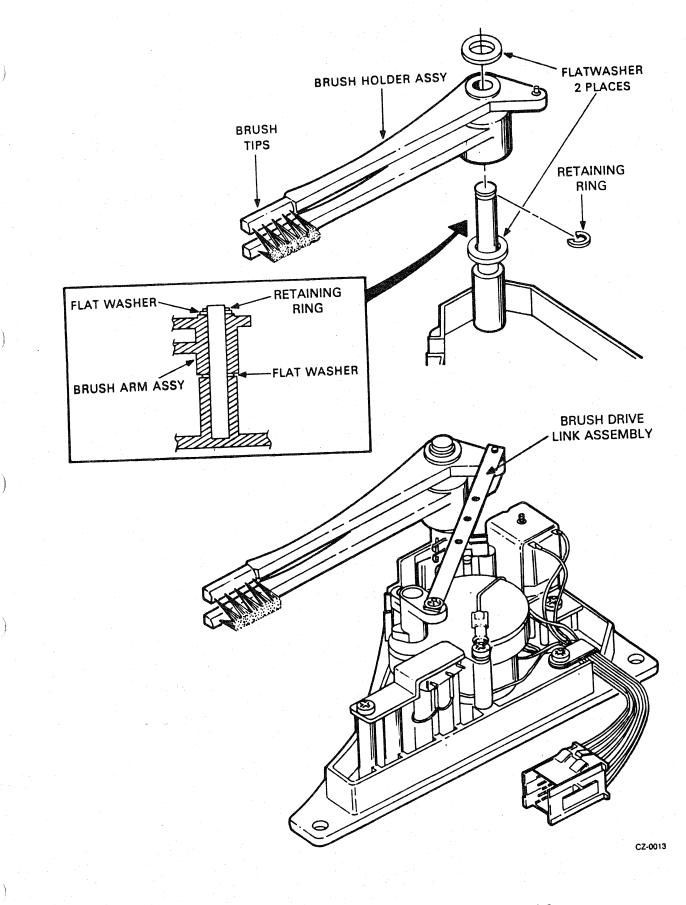

1.1.3.5 Brush Drive Assembly - The RLØ1/RLØ2 Disk Drive has motor-driven cleaning brushes (refer to Figure 1-5) which automatically sweep across the disk surfaces each time the spindle drive motor is started. The brush cycle must be completed and the brushes retracted before the heads will load. In order to prevent damage to the read/write heads and cartridge, the cartridge access cover remains interlocked so that the cartridge cannot be removed in the event that the brushes fail to return to their home position. The brush holder assembly is a field replaceable unit.

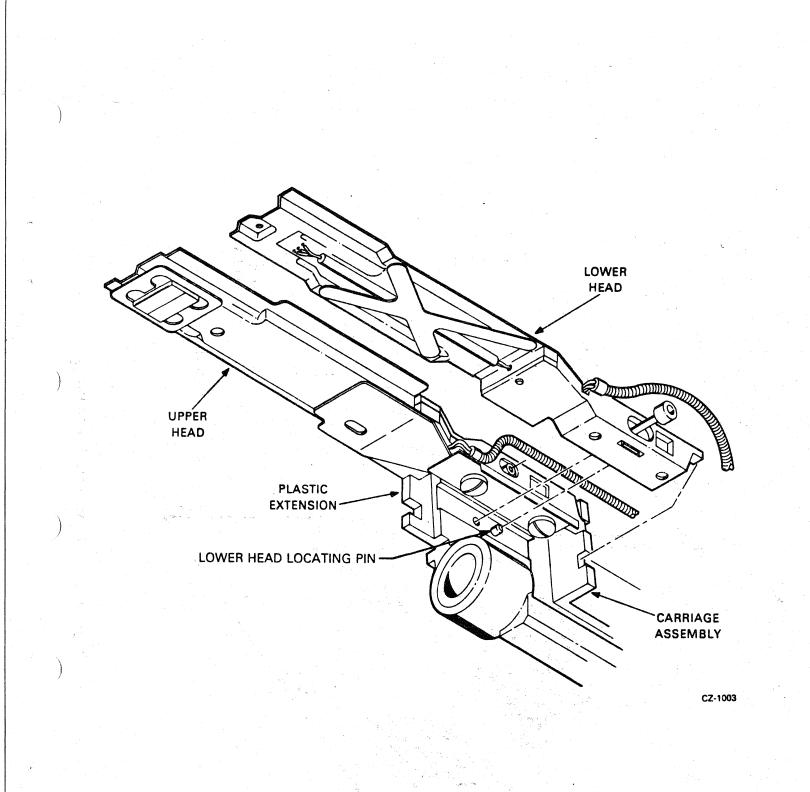

1.1.3.6 Read/Write Heads - Each head (Figure 1-6) is made up of a magnetic core structure mounted in a ceramic slider pad and is supported on an arm. Each head is also provided with a flexible cable that terminates with a connector. When both heads are loaded and positioned with the disk rotating at 2400 | 2% rpm, each head is supported by a boundary layer of air approximately 50 microinches thick. The "up" head is used for reading and writing data on the bottom surface (surface 1) of the disk and the "down" head is used for reading and writing data on the top surface (surface 0) of the disk. Each head is loaded and unloaded from the rotating disk by the force of a cam against the 30 degree ramp in the head arm.

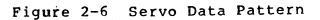

The heads operate at 4.1 megaflux-reversals per second maximum using the Modified Frequency Modulation (MFM) method for encoding or decoding data. This corresponds to a maximum density of 3725 bits per inch on the inner track (track 255, decimal).

1.1.3.7 Read/Write Board - The read/write board is contained in a subchassis to provide shielding for the logic.

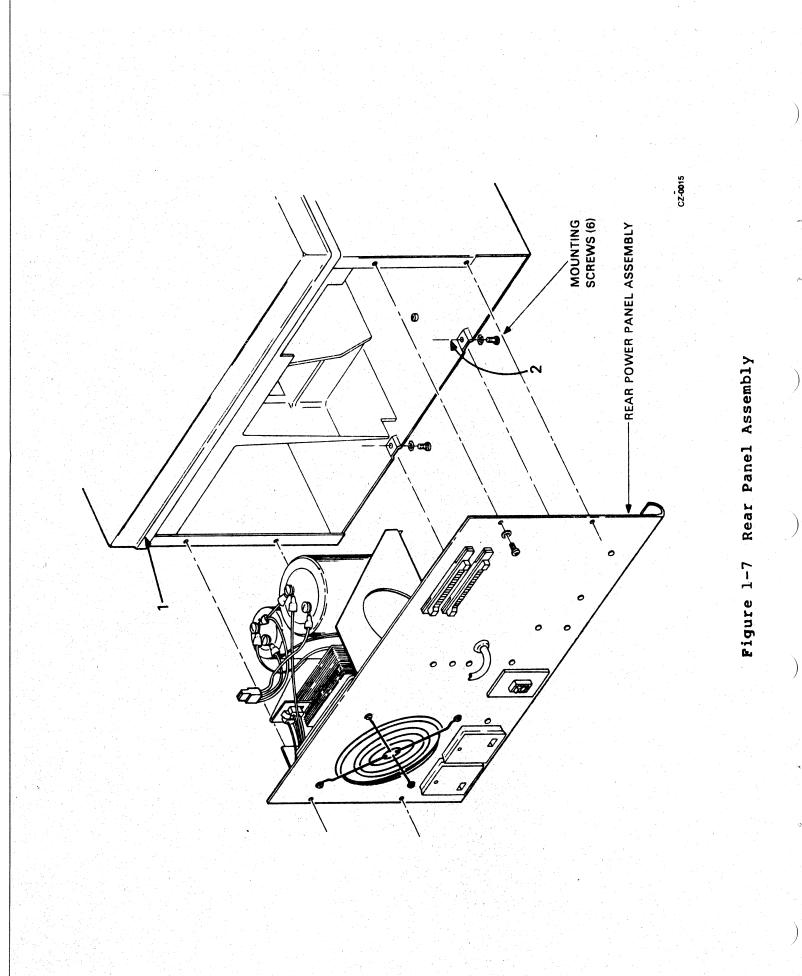

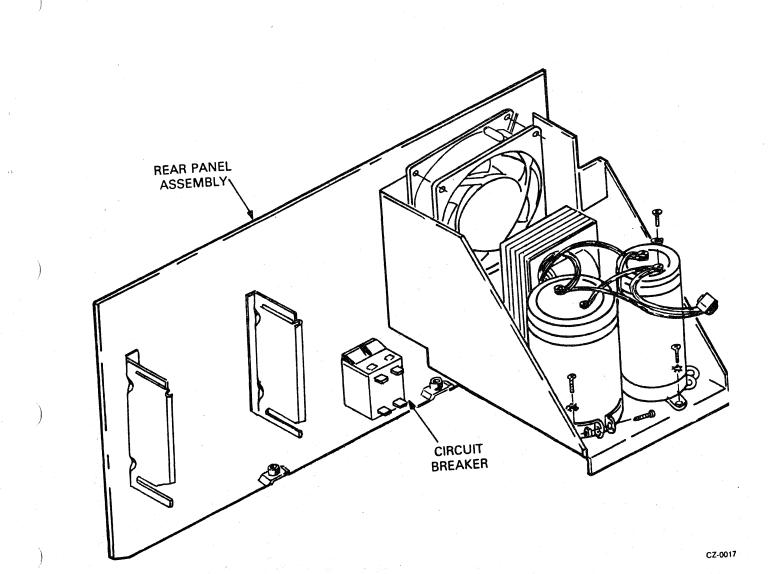

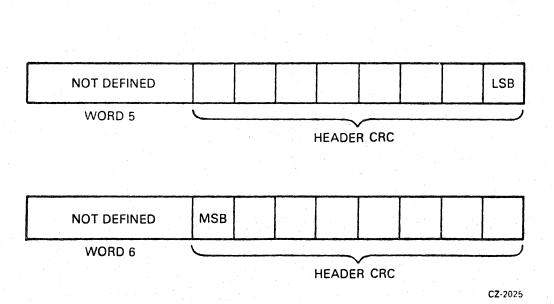

1.1.3.8 Power Panel - The removable rear panel of the drive contains a muffin type fan, I/O connectors, an ac circuit breaker, an RFI filter, the spindle motor capacitor, the ac terminal assembly block and the ac servo module chassis. Refer to Figure 1-7. The ac circuit breaker provides power ON/OFF control for the drive and is normally left in the ON position.

# Figure 1-4 Spindle Assembly

Figure 1-5 Brush Assembly

# Figure 1-6 Read/Write Heads

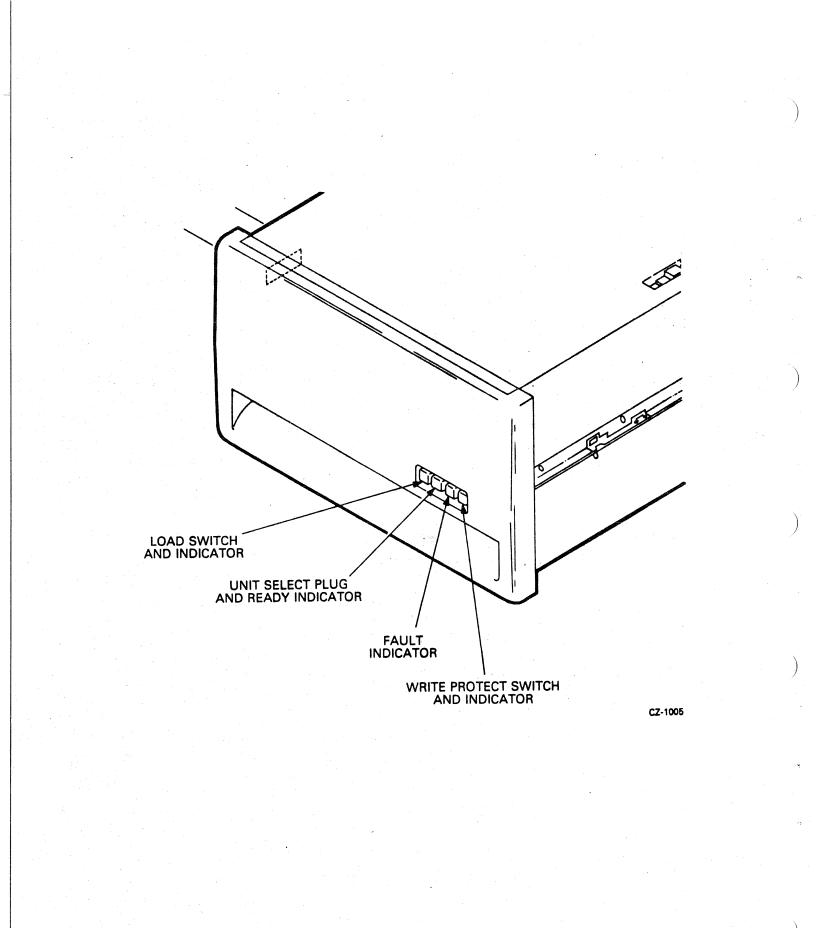

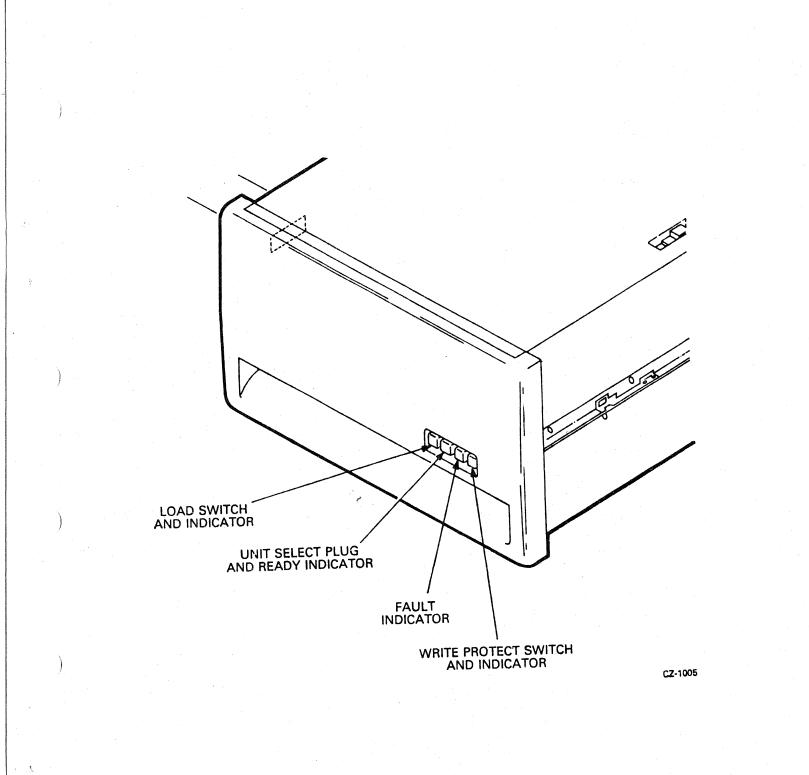

1.1.3.9 Control Panel - The operator's control panel is located at the front of the drive. The following push on/push off alternating action switches and indicators are located on the drive control panel (Figure 1-8):

- Run/Load switch with LOAD indicator

- Unit Select switch with READY indicator

- FAULT indicator

- Write Protect switch with WRITE PROTect indicator

Run/Load Switch with LOAD Indicator

This push on/push off alternating action switch, when depressed, energizes the spindle motor providing the following conditions have been met:

- The disk cartridge has been installed

- The cartridge protection cover is in place and the cartridge access cover is closed and latched

- All ac and dc voltages are within specifications

- The read/write heads are home

- The brushes are home

When this switch is released (depressed a second time), the spindle drive motor is deenergized if the read/write heads are not loaded. If the heads are loaded, they are retracted before the spindle drive motor is deenergized. In the event of a main power interrupt and subsequent power restoration, the drive will cycle up again if the switch is depressed since it contains mechanical memory.

The LOAD enable indicator is illuminated whenever:

- The spindle is stopped

- The read/write heads are home

- The brushes are home

- The spindle drive motor is at rest

# Figure 1-8 Control Panel

# Unit Select (0, 1, 2, 3) Switch with READY Indicator

The unit select switch is a cam operated switch which is actuated by inserting a numbered, selectively cammed button. The switch contacts are binary encoded so the drive interface logic recognizes the matching controller generated drive address code and the corresponding unit select number  $(\emptyset, 1, 2 \text{ or } 3)$ .

The numbered indicator, when lit, indicates a drive READY condition. This condition exists when:

- The spindle is up to speed

- The brushes are home

- The read/write heads are loaded

- The heads are detented on a specific track

# FAULT Indicator

The FAULT indicator is lit whenever the following fault or error conditions develop in the disk drive:

- Drive Select Error

- Seek Time Out Error

- Write Current in Heads During Sector Time Error

- Loss of System Clock

- Write Protect Error

- Write Data Error

- Spin Error

WRITE PROTect Switch and Indicator

This alternating action push on/push off switch, when depressed, sets the drive in write protect mode whether or not the Write Gate line is asserted (refer to interface line descriptions). If the Write Gate line is asserted when WRITE PROTect is on, the drive will generate a Write Gate error (which will light FAULT). The write protect mode will be immediately removed upon release of the switch.

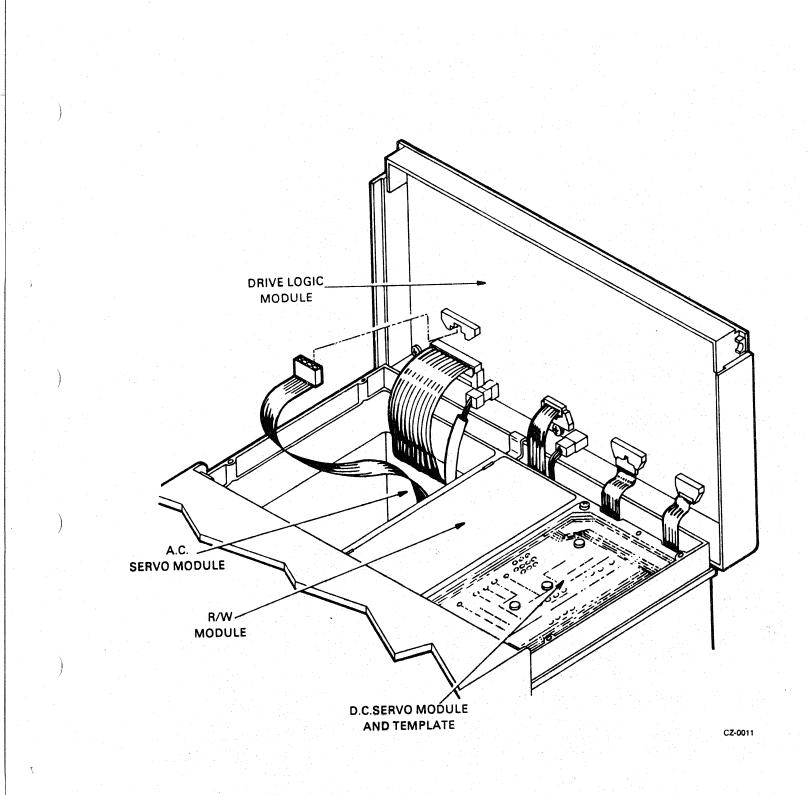

#### 1.1.4 Drive Electronics Partitioning

A large percentage of the drive electronics is contained on the drive logic module. Additional electronics are on these modules:

- The dc servo module

- The ac servo module

- The read/write module

This design concept enhances the module-swap maintenance philosophy.

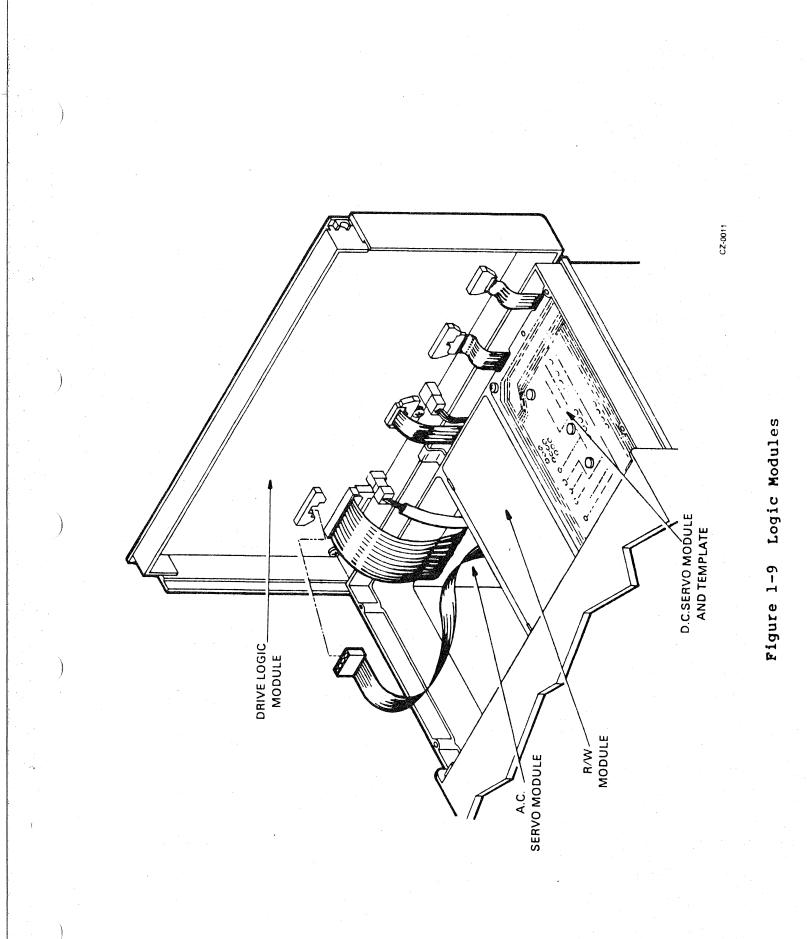

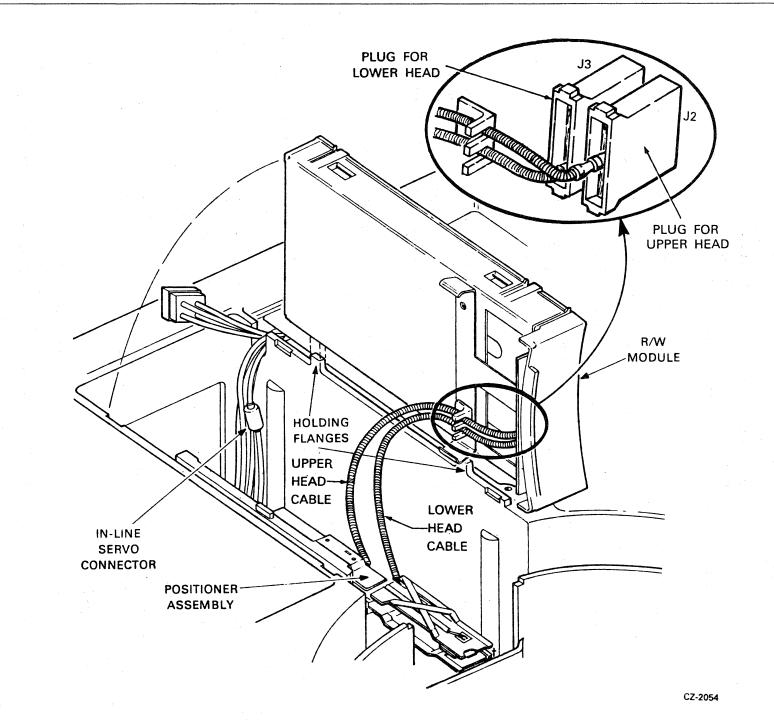

The drive logic module, mounted inside the rear cover at the top of the drive, is a single hex-sized board. The rear cover can be detached and positioned vertically on the rear edge of the base plate. Refer to Figure 1-9.

Opening the rear cover exposes the read/write module and the dc servo module. Both the read/write module and dc servo module can be placed on their sides to allow easy access to the positioner assembly, module chips and test points. Refer to Figure 1-9. The ac servo module is located on the removable power panel. Refer to Figure 1-9.

**1.1.4.1** Drive Logic Module - The drive logic module provides the drive with the following functions:

- Interface to the controller via a 40 pin PC-mounted connector and flat ribbon cable

- Interface enabling and control circuits

- State control logic (load/run sequencing)

- Seek control and track counting logic

- Device command/status register

- Positioner velocity command generation

- Disk drive motor speed control

- Error detection and status data generation

- Servo data detection logic

1.1.4.2 DC Servo Module - The dc servo module contains the positioner servo amplifier and dc voltage regulators. The voltage regulators are mounted on a U-shaped heat sink which faces down into the cooling air chamber. This module also serves a mechanical function in that it seals a portion of the cooling air system from the clean air system.

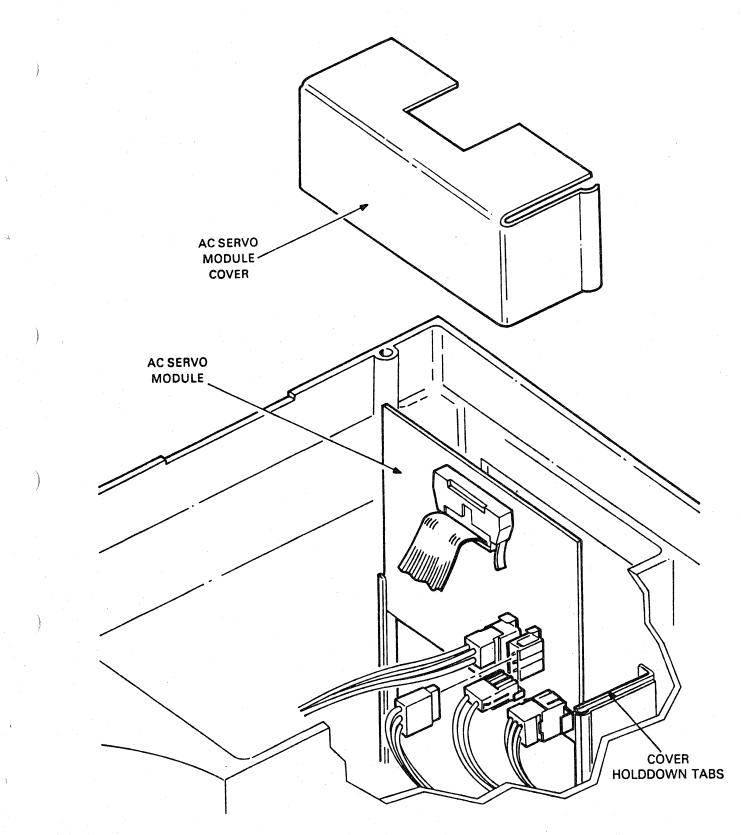

**1.1.4.3.** AC Servo Module - The ac servo module provides the following functions:

- Control circuits for the brush motor

- Control circuits for the spindle drive motor

- Cover solenoid drive circuit

**1.1.4.4** Read/Write Module - The functions provided by the read/write module are:

- Servo and read data preamplifier, filters, differentiator and limiter

- Head selection

- Write drivers and write current sensing

- Write error sensing

#### 1.1.5 Documentation

Table 1-1 lists the documents that will be available to describe the RLØ1/RLØ2 Subsystem.

Hard copy user documentation consisting of the RLØ1/RLØ2 Disk Subsystem User's Guide (which contains operation and installation information) will ship with each subsystem.

#### Table 1-1 RLØ1/RLØ2 Subsystem Documentation

| Title                                            | Microfiche<br>Number | Hard Copy<br>Number |

|--------------------------------------------------|----------------------|---------------------|

| RLV11 Controller Technical<br>Description Manual | EP-RLV11-TD          | EK-RLV11-TD         |

| RL11 Controller Technical<br>Description Manual  | EP-ØRL11-TD          | EK-ØRL11-TD         |

| RL8A Omnibus Controller<br>Technical Manual      | EP-ØRL8A-TM          | EK-ØRL8A-RM         |

| RLØ1/RLØ2 Preventive Maintenance<br>Procedures   | EP-00008-PM          | EK-RLØ12-PM         |

| RLØl Illustrated Parts Breakdown                 | EP-00016-IP          | EK-ØRLØ1-IP         |

| RLØ2 Illustrated Parts Breakdown                 | EP-00016-IP          | EK-ØRLØ2-IP         |

| RLØ1/RLØ2 Disk Subsystem User's<br>Guide         | N/A                  | EK-RLØ12-UG         |

| RLØ1/RLØ2 Pocket Service Guide<br>I/l-           |                      | EK-RLØ12-PG         |

# 1.2 SUBSYSTEM SPECIFICATIONS

This section provides the following specificataion for the RLØ1 and RLØ2 Disk Subsystem:

- Table 1-2: RLØ1/RLØ2 Disk Drive Physical and Environmental Specifications

- Table 1-3: RLØ1/RLØ2 Disk Drive Operational Specifications

- Table 1-4: RLØ1K/RLØ2K Disk Cartridge Operational Specifications

| Table 1-2 RLØ1 Dis        | k Drive Physical and Environmental<br>Specifications                                                                                    |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Width                     | Compatible with 19 inch RETMA rack                                                                                                      |

| Depth                     | 63.5 cm (25 in) behind bezel                                                                                                            |

| Height                    | 26.5 cm (10.5 in)                                                                                                                       |

| Weight                    | 34 kg (75 lbs)                                                                                                                          |

| Mounting                  | The drive mounts on chassis slides.                                                                                                     |

| Power Sources             | 90-127 Vac (47.5-63 Hz)                                                                                                                 |

|                           | 180-254 Vac (47.5-63 Hz)<br>(Manually selectable)                                                                                       |

| Input Power               | 200 watts maximum at 115 Vac, 60 Hz                                                                                                     |

| Power Factor              | Greater than Ø.85                                                                                                                       |

| Starting Current          | 3.5 amps RMS maximum<br>@ 90 Vac/47.5-63 Hz                                                                                             |

|                           | 5.0 amps RMS maximum<br>@ 127 Vac/47.5-63 Hz                                                                                            |

|                           | 1.75 amps RMS maximum<br>@ 180 Vac/47.5-63 Hz                                                                                           |

|                           | 2.5 amps RMS maximum<br>@ 254 Vac/47.5-63 Hz                                                                                            |

| Power Cord and Connector: | A molded line cord compatible with the<br>drive operating voltage and the 861<br>Power Control for 120 Vac is attached<br>to the drive. |

|                           | The power cord is 2.74 m (9 ft) long and the plug is NEMA 5-15P.                                                                        |

|                           | The 230 Vac plug to be attached to high voltage drives is NEMA 6-15P.                                                                   |

| Safety                    | The RLØ1/RLØ2 Disk Drive is UL listed and CSA certified.                                                                                |

| Interlocks                | Interlocks are used where potential<br>exists for damage to drive, media,<br>operators or service personnel.                            |

# Temperature/Humidity

Operating:

Temperature:  $10^{\circ}$  C ( $50^{\circ}$  F) to  $40^{\circ}$  C ( $104^{\circ}$  F).

Derate Temperature 5.9° C/1000 m (1.8° C/1000 ft)

Relative Humidity: 10% to 90% with maximum wet bulb  $28^{\circ}$  C ( $82^{\circ}$  F) and minimum dew point  $2^{\circ}$  C ( $36^{\circ}$  F).

Non-Operating:

Temperature:  $-40^{\circ}$  C  $(-40^{\circ}$  F) to  $66^{\circ}$  C  $(151^{\circ}$  F)

Relative Humidity: 10% to 95%

Operating: 2440 m (8,000 f) maximum.

Non-Operating: 9.1 km (30,000 f) maximum.

**Operating:** Half sine shock pulse of 10 Gpk and  $10 \pm 3$  msec duration applied once in either direction of three orthagonal axes (3 pulses total).

Non-Operating: Half sine shock pulses of 40 Gpk and 30 +10 ms duration perpendicular to each of six package surfaces.

# Operating:

Sinusoidal vibration (sweep rate 1 octave/min)

5-50 Hz

0.002" DA

50-500 Hz

0.25 Gpk

500-50 Hz

0.25 Gpk

50-5 Hz

0.002" DA

# Non-Operating:

Vertical Axis Excitation - 1.40 Grms overall from 10 to 300 Hz. Power spectral density 0.029 g/Hz from 10 to 50 Hz with 8 dB/octave rolloff from 50-300 Hz.

# Altitude

Shock

) **V**ibration

Longitudinal and Lateral Axis Excitation -  $\emptyset.68$  Grms Overall from 1 $\emptyset$ to 2 $\emptyset\emptyset$  Hz. Power spectral density  $\emptyset.007$  g/Hz from 1 $\emptyset$  - 5 $\emptyset$  Hz with 8 dB/octave rolloff from 5 $\emptyset$  to 2 $\emptyset\emptyset$  Hz.

The drive will operate in an ambient atmosphere of less than 5 million particles Ø.5 microns or larger per cubic foot of air. The drive is intended to run in a light industry (or cleaner) environment.

Maximum pitch: +5 degrees

Maximum roll: +5 degrees

546 BTU/hour maximum

Heat Dissipation

Dust

Attitude

#### RLØ1/RLØ2 Disk Drive Operational Specifications Table 1-3

General

Linear bit density: 147 bits/mm (3725 bits/in) at innermost track

16 bit words per sector: 128

Number of sectors: 40/track

Track density: 4.9/mm (125/in) for RLØ1K, 9.8/mm (250/in) for RLØ2K

Number of recording tracks: 256/surface for RLØ1K, 512/surface for RLØ2K

Number of surfaces: 2

Formatted capacity (megabytes): 5.2 for RLØ1K, 10.4 for RLØ2K

Encoding method: MFM

4.1 megabits/sec +1%

Bit Cell Width: 244 nsec +1%

Words (16 bit): 256 kilowords/sec +1% Rotational Frequency: 2400 rpm +0.25%

Average latency: 12.5 msec +0.25%

Maximum latency 25.0 msec +0.25%

Average seek time 55 msec max (85 RLØ1, tracks for 120 tracks for RL02)

One cylinder track 5 msec max seek time

Maximum seek time

tracks (256 for RLØ1, 512 tracks for RLØ2)

100 msec max

30 seconds

Head switch time 8 msec

Start time: 45 seconds

Stop time:

Refer to Figure 1-10 I/1-21

Start/Stop Time

Data Format

Transfer Rate Bit Rate:

(unbuffered values)

Latency

Seek Time

Figure 1-10 Data Format

1/1-22

### Table 1-4

### -4 RLØ1K/RLØ2K Disk Cartridge Specifications

Operating Environment

Storage

Dimensions (Cartridge)

Maximum Speed

Track Geometry

The cartridge will operate in air whose temperature lies between  $40^{\circ}$  C to  $48^{\circ}$  C  $(40^{\circ}$  F to  $120^{\circ}$  F) at a relative humidity of 8 to 80 %. The wet bulb reading shall not exceed 25° C  $(78^{\circ}$  F). Before a cartridge is placed into operation, it shall be conditioned within its cover for a minimum of two hours in the same environment as that in which the disk drive is operating. The above specified range does not necessarily apply to the disk drive.

The cartridge must be stored at a temperature Environment between -  $40^{\circ}$  C to  $65^{\circ}$  C  $(-40^{\circ}$  F to  $150^{\circ}$  F). The wet bulb reading not exceeding 29° C ( $85^{\circ}$  F). For wet bulb temperatures between  $0.56^{\circ}$  C and 29° C ( $33^{\circ}$ F and  $85^{\circ}$  F) the disk cartridge shall be able to withstand a relative humidity (noncondensing) of 8 to 80%. The stray magnetic field intensity shall not exceed 50 oersteds.

External Diameter

The external diameter of the top cover is 38.35 cm (15.1 in).

The external diameter of the protection cover is 37.03 cm (14.58 in).

The external height of the cartridge when resting on its bottom surface is 6.19 cm (2.44 in).

The rotating parts of the disk cartridge are capable of withstanding the effect of stress at the speed of 2,500 rev/min.

Number of Tracks - There are 256 discrete concentric tracks per data surface for the RLØ1K, 512 tracks per data surface for the RLØ2K.

## Identification of Data Tracks

Data Track Identification - Data track identification is a three digit decimal number  $(\emptyset 0 \emptyset - 255, RL \emptyset 1K, \emptyset 0 \emptyset - 511, RL \emptyset 2K)$  that numbers data tracks consecutively starting at the outermost data track of each data surface.

Data Surface Identification - The data surfaces are numbered  $\emptyset$  and 1 starting with the uppermost surface and corresponding with the head numbers.

Cylinder Address - A cylinder is defined as the data tracks on the data surface with a common data track identification.

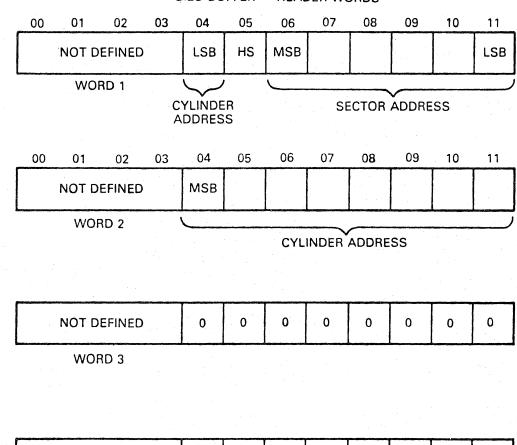

Data Track Address - A 16-bit word, where bits  $\emptyset$  - 5 define a binary sector number, bit 6 defines surface, and bits 7 - 15 define a binary cylinder address. This information is in word 1 of each sector's header.

### CHAPTER 2 SYSTEM-LEVEL DESCRIPTION

### 2.1 RLØIRLØ2 MASS STORAGE SUBSYSTEM

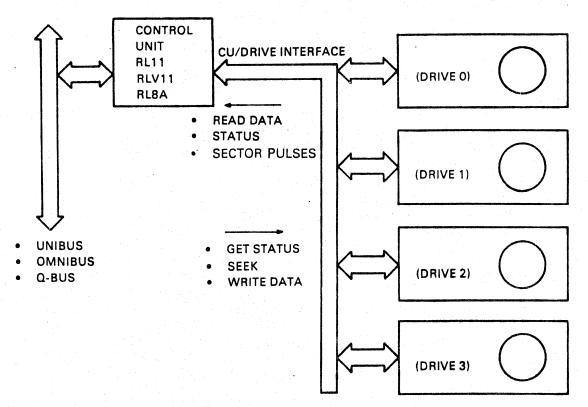

The RLØ1/RLØ2 Mass Storage Subsystem consists of up to four drives in a daisy-chain configuration, and a controller (RL11, RLV11 or RL8A). Additional drives, if required, necessitate a second controller. Figure 2-1 illustrates a typical subsystem.

#### 2.2 DISK CARTRIDGE FORMAT

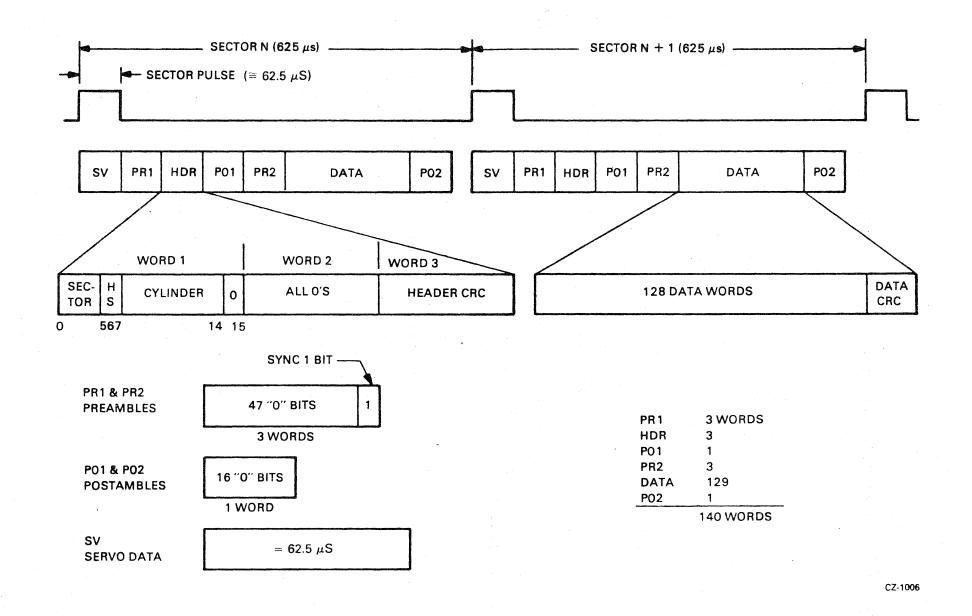

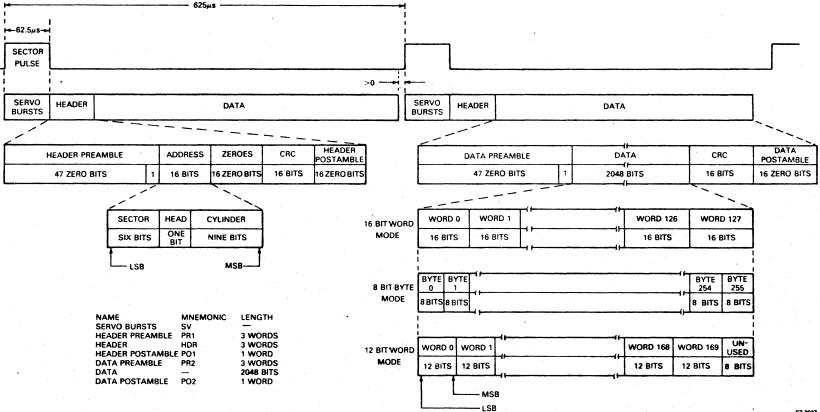

Figure 2-2 shows servo, header, sector and data formatting for the RLØ1K/RLØ2K Disk cartridge.

Servo and header information for each sector is prerecorded at the factory and cannot be modified or rewritten in the field. Accidental overwriting or destruction of the servo information is prevented by logic within the drive.

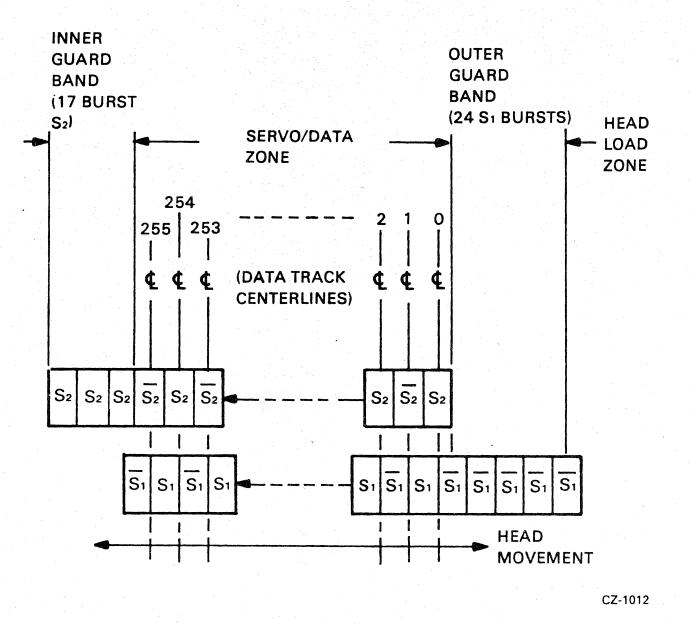

Each RLØ1K disk recording surface has a total of 256 data tracks (numbered  $\emptyset$  to 255) and each RLØ2K surface has 512 tracks (numbered  $\emptyset$  to 511). Thus, there are 256 cylinders on an RLØ1K cartridge and 512 clinders on an RLØ2K.

### 2.2.1 Data Format

Each track on the recording surface is divided into 40 equal-length sectors which are further subdivided into fields. The six fields in each sector contain a total of 140 words of 16 bits each. One hundred twenty eight of the 140 words contain data.

Header Preamble (PR1) - These three words precede the header information and contain 47 "Ø" bits followed by a marker "1" (Sync Bit) to indicate the start of valid information.

Header - This field contains three words of 16 bits each. The first word identifies the disk surface (upper or lower), the cylinder address (1 of 256, RLØ1; 1 of 512, RLØ2), and the sector address (1 of 40).

The second header word is all Øs. The third word is the header CRC word. This check word is prerecorded on the track, as are the other two header words. During a read operation, the header is checked for errors. If one is detected, an error flag is raised.

Header Postamble (PO1) - This field contains 16 "0" bits. It separates the header and data fields to allow for mechanical tolerances between drives.

Data Preamble (PR2) - This field contains 47 "Ø" bits followed by a marker "l" (Sync Bit) to indicate the start of the data field and is written in conjunction with the data.

I/2-1

CZ-1007

Figure 2-1 Typical RLØ1/RLØ2 Mass Storage Subsystem

Figure 2-2 RLØ1K/RLØ2K Disk Cartridge Characteristics

I/2-3

CZ-2027

Data - This field accommodates a block of 128 16-bit data words (2048 bits) followed by a 16-bit data CRC word. When writing data, a data CRC word is generated by the controller and appended to the 128-word data block. The contents of the CRC word vary with the contents of the data block. When reading the data from the drive, the data block and CRC word are checked in the controller. Detection of a data reading error results in a data CRC flag.

Data Postamble (PO2) - This field consists of 16 "Ø" bits. Write current is turned off at the end of this field so that data CRC information will not be destroyed.

2.2.2 Servo Data

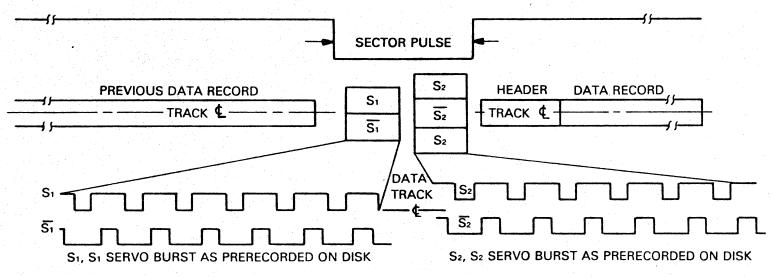

2.2.2.1 Introduction - One of the features of the servo-in-data design approach for track counting and carriage positioning is the fact that it shares read/write heads and circuitry. This is different from IBM 3330 technology which, in general, requires a dedicated servo head and servo track. While 3330-type servo information is monitored continuously as the disk is spinning, the RL01 or RL02 only takes servo samples (much like snapshots) during each sector pulse.

The servo data bursts are prerecorded on the disk surface during a certain time period within the sector pulse. The sector pulse is generated by a separate magnetic transducer mounted on the spindle which senses each of the 40 sector slots in the cartridge armature plate.

Since the cartridge disk spins at 2400 rpm and there are 40 sector slots, the drive takes servo samples for positioning and track counting every 625 microseconds.

**2.2.2.2** Modes of Operation - While the heads are flying, the drive operates in either of two modes:

- Velocity (seek and track counting) mode, or

- Position (track following) mode

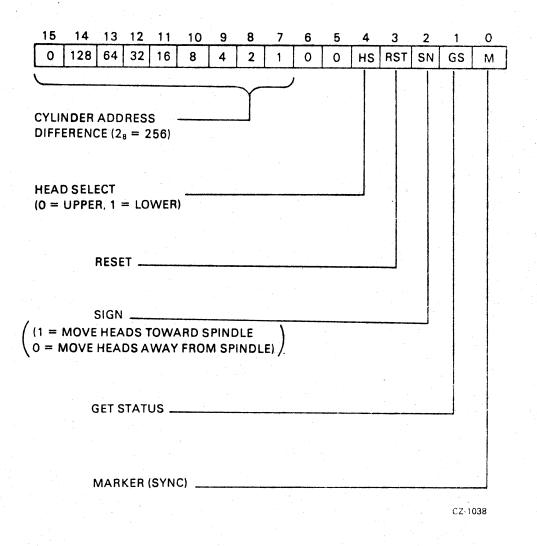

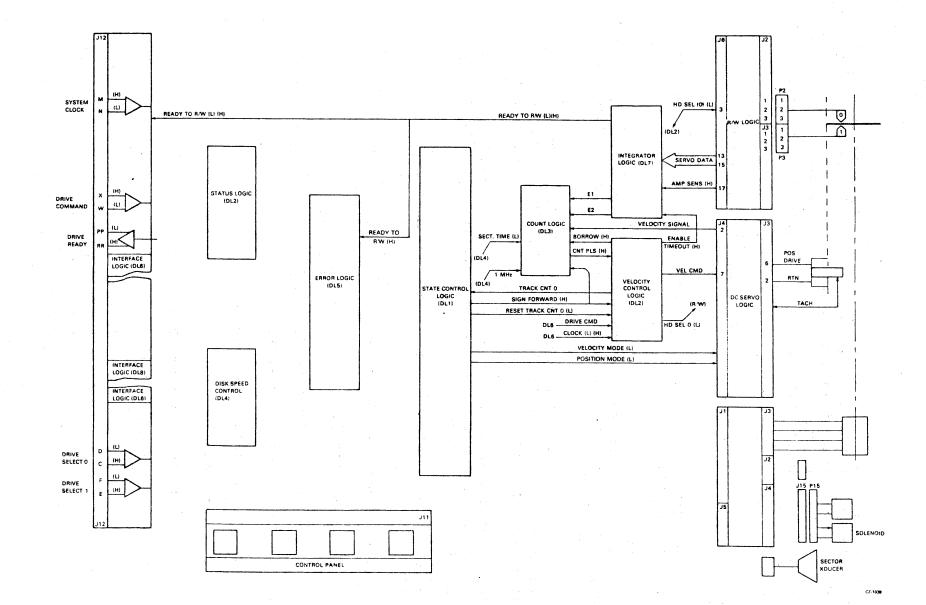

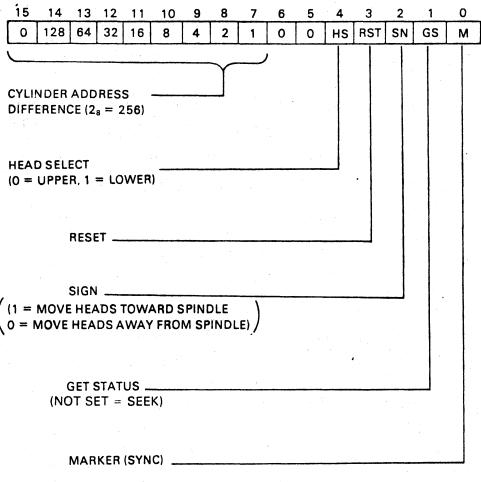

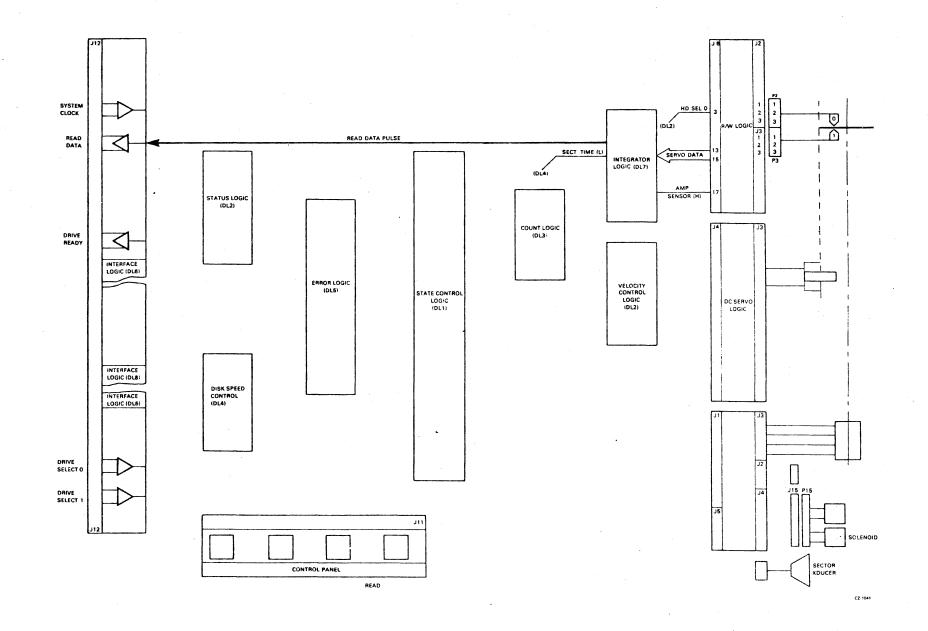

In <u>velocity mode</u>, the drive logic counts track crossings by using servo information recorded on the disk surface and converting this information into binary format. This information is used in conjunction with carriage velocity (sensed by the tachometer) to decrement a track difference counter and ultimately to control the velocity of the positioner. This process is described in Paragraph 2.2.2.4.