ISA & EISA

By Edward Solari

# Theory and Operation

# Including PC, XT, AT, ISA, and EISA I/O Bus Operation

Annabooks San Diego

## ISA & EISA THEORY AND OPERATION by Edward Solari

**PUBLISHED BY**

Annabooks 15010 Avenue of Science, Suite 101 San Diego, CA. 92128 USA

619-673-0870

Copyright © Annabooks 1992

All Rights Reserved. No part of the contents of this book may be reproduced or transmitted in any form or by any means without the prior written permission of the publisher, except for the inclusion of brief quotations in a review.

Printed in the United States of America

ISBN 0-929392-15-9

First Printing November 1992

Library of Congress Cataloging-in-Publication Data

```

Solari, Edward.

ISA & EISA : PC, XT, AT, and EISA PC I/O BUS timing / by Edward

Solari.

p. cm.

Includes bibliographical references and index.

ISBN 0-929392-15-9

1. Microcomputers--Buses. 2. EISA (Computer bus) I. Title.

II. Title: ISA and EISA.

TK7895.B87S66 1992

621.39'81--dc20

92-39819

CIP

```

Information provided in this publication is derived from various sources, standards, and analyses. Any errors or omissions shall not imply any liability for direct or indirect consequences arising from the use of this information. The publisher and author make no warranty for the correctness or for the use of this information, and assume no liability for direct or indirect damages of any kind arising from technical interpretation or technical explanations in this book, for typographical or printing errors, or for any subsequent changes.

The publisher and author reserve the right to make changes in this publication without notice and without incurring any liability.

The publisher and author would like to acknowledge the co-operation of the IEEE P996 Working Group. Scott Hopkinson of Dernier Corporation and Mike Fung of S3 Corporation were particularly helpful in obtaining permission of the IEEE to quote portions of the P996 proposed standard.

The A.C. timing tables and signal waveform drawings in this book represent a composite of information from several sources in addition to the information that is original to this book. The following sources have provided portions of the A.C. timing and signal waveforms:

"ISA BUS SPECIFICATIONS and APPLICATION NOTES, January 30, 1990", Copyright 1989, Intel Corporation

"TECHNICAL REFERENCE GUIDE, EXTENDED INDUSTRY STANDARD ARCHITECTURE EXPANSION BUS", Copyright Compaq Computer Corp., 1989

"EXTENDED INDUSTRY STANDARD ARCHITECTURE SPECIFICATION Rev. 3.12", Copyright 1989-1992 BCPR Services, Inc.

"PERSONAL COMPUTER BUS STANDARD P996" DRAFT D2.02, January 18, 1990, Copyright IEEE Inc., 1990.

IBM, IBM PC, PC/XT, and PC/AT are trademarks of IBM Corporation.

Intel, 8088, 80286, 80386, 80486, 8284A, 8288, 8237A-5, 82284, 82288, 8042, 8259, 8254, and Multibus II are trademarks of Intel Corporation.

COMPAQ is a trademark of COMPAQ Corporation.

# Dedication

To my mother and father for my education, and to my wife for her patience.

# **ISA & EISA THEORY AND OPERATION**

## **Contents**

## Foreword

# Preface

| Chapter One, Architectural Overview1      |

|-------------------------------------------|

| Introduction1                             |

| ISA Compatible Platform                   |

| Host Bus3                                 |

| ISA Bus                                   |

| Platform CPU 5                            |

| Math Co-Processor                         |

| Cache                                     |

| Memory                                    |

| DMA Controller                            |

| Refresh Controller                        |

| Interrupt Controller                      |

| Keyboard and Mouse7                       |

| Video7                                    |

| Timer and Real-Time Clock7                |

| Interface Circuitry                       |

| Add-On Cards                              |

| E-ISA Compatible Platform                 |

| Configuration Space                       |

| Control Interface with Arbiter and        |

| AENx Control                              |

| EISA Compatible Platform                  |

| Control Interface with Arbitration and    |

| AENx Control                              |

| Summary of Bus Standard Differences       |

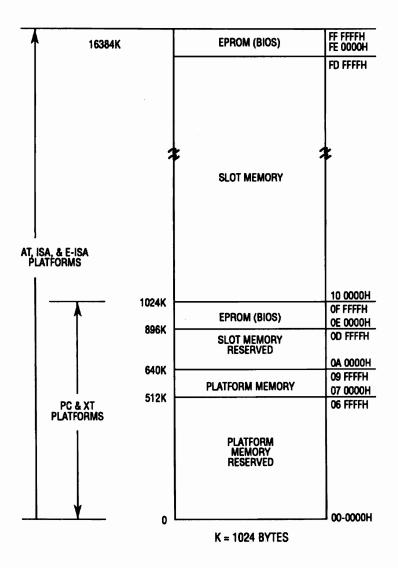

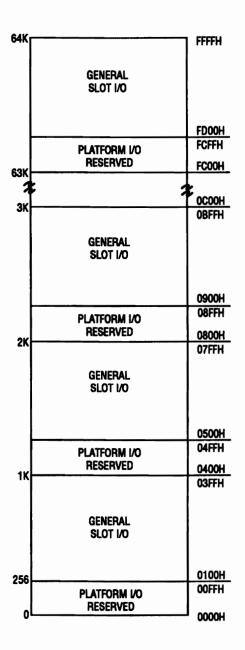

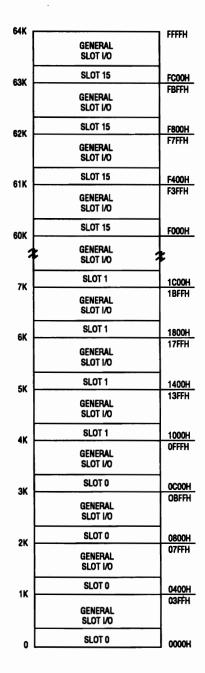

| Chapter Two, Memory and I/O Address Space |

| Introduction                              |

| Memory Address Space                      |

| I/O Address Space                         |

| Chapter Three, Generic Bus Cycles<br>Introduction                                           | 35  |

|---------------------------------------------------------------------------------------------|-----|

| Introduction                                                                                |     |

| 3.0 ISA Specific Access Cycles on<br>ISA and E-ISA Platforms                                | 37  |

| 3.1 EISA Bus Master Access Cycles to<br>EISA Resources on EISA Platforms                    | 44  |

| 3.2 EISA Bus Master Access Cycles to<br>ISA and E-ISA Resources on EISA Platforms           | 58  |

| 3.3 ISA and E-ISA Bus Master Access Cycles to<br>EISA Resources on EISA Platforms           | 67  |

| 3.4 DMA Transfer Cycles on<br>ISA and E-ISA Platforms                                       | 70  |

| 3.5 DMA Transfer Cycles on EISA Platforms                                                   | 81  |

| 3.6 Refresh Cycle                                                                           | 92  |

| 3.7 Arbitration Cycle                                                                       | 96  |

| Chapter Four, Interaction Among ISA, E-ISA, and EISA<br>Add-On Cards and Platform Resources | 99  |

| 4.0 General Information                                                                     | 99  |

| 4.1 ISA Compatible Add-On Slave Cards<br>Memory Access Cycles to                            | 101 |

| ISA Compatible Add-On Slave Cards                                                           | 101 |

| 8 Data Bit Memory Resource                                                                  | 101 |

| 16 Data Bit Memory Resource                                                                 | 102 |

| ISA Compatible Add-On Memory Slave Card<br>Issues                                           |     |

| Issues<br>I/O Access Cycles to ISA Compatible                                               | 103 |

| Add-On Slave Cards                                                                          | 105 |

| 8 Data Bit I/O Resource                                                                     |     |

| 16 Bit Memory Resource                                                                      | 105 |

| ISA Compatible Add-On I/O Slave Card Issues.<br>Access Cycle Data Size Mismatch with        | 106 |

| ISA Compatible Add-On Slave Cards                                                           | 108 |

| Transfer Cycles and ISA Compatible             |                |

|------------------------------------------------|----------------|

| Add-On Slave Cards                             | 0              |

| Transfer Cycle Data Size Mismatch with an      |                |

| ISA Compatible Add-On Slave Card               | 3              |

|                                                | Č              |

| 4.2 ISA Compatible Add-On Bus Owner Cards 11   | 5              |

| 4.3 E-ISA Compatible Add-On Memory and         |                |

| I/O Slave Cards11                              | 7              |

| Transfer Cycles and E-ISA Compatible           |                |

| Add-On Slave Cards                             | 9              |

| Transfer Cycle Data Size Mismatch              |                |

| with an E-ISA Compatible Add-On Slave Card 12  | 0              |

|                                                |                |

| 4.4 E-ISA Compatible Add-On Bus Owner Cards 12 | :0             |

| 4.5 EISA Compatible Add-On Slave Cards         | 1              |

| Memory Access Cycles to EISA Compatible        |                |

| Add-On Slave Cards12                           | 2              |

| 8 Data Bit Memory Resources                    | $\overline{2}$ |

| 16 & 32 Data Bit Memory Resources              | 3              |

| I/O Access Cycles to EISA Compatible           | Č              |

| Add-On Slave Cards                             | Δ              |

| 8 Data Bit I/O Resource                        |                |

| 14  fr  22  Data Dit I/O Resource              | 5              |

| 16 & 32 Data Bit I/O Resource                  | ົ່             |

| Access Cycle Data Size Mismatch with           | _              |

| EISA Compatible Add-On Slave Cards 12          | ./             |

| Transfer Cycles and EISA Compatible            | _              |

| Add-On Šlave Cards                             | 7              |

| Transfer Cycle Data Size Mismatch with an      |                |

| EISA Compatible Add-On Slave Card              | 0              |

| -                                              |                |

| 4.6 EISA Compatible Add-On Bus Owner Cards 13  | 1              |

|                                                | -              |

| 4.7 Refresh                                    | 2              |

| 4.7 Konoshaaaaa 10                             | 2              |

| 4.8 Arbitration13                              | 3              |

| Chapter Five, Signal Line Definition           | 5              |

| Introduction                                   |                |

| Overview of ISA and E-ISA Compatible           | 5              |

| Signal Lines                                   | E              |

| Signal Lines                                   | S              |

| Overview of EISA Compatible Signal Lines       | )/             |

| Conventions                          | 140  |

|--------------------------------------|------|

| Address Signal Lines                 | 141  |

| BALE                                 | .142 |

| SA<0-19>                             | 143  |

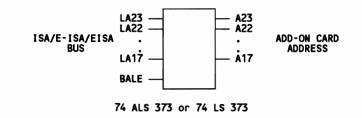

| LA<17-23>                            | 144  |

| LA<2-16> / LA*<24-31>                | 145  |

| SBHE*                                | 145  |

| AENx                                 | 146  |

| BE*<0-3>                             | 148  |

| Data Signals                         | 151  |

| SD<br>Cycle Control Signals<br>MEMR* | 151  |

| Cycle Control Signals                | 152  |

| MEMR*                                | 152  |

| SMEMR*                               | 152  |

| MEMW <sup>*</sup>                    | 153  |

| SMEMW*                               | 153  |

| IOR *                                | 154  |

| IOW*<br>MEMCS16*                     | 155  |

| MEMCS16*                             | 155  |

| IOCS16*                              | 157  |

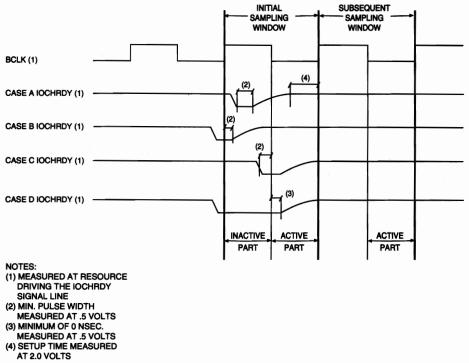

| IOCHRDY                              | 159  |

| IOCHRDY Signal Line Enhancement      | 161  |

| SRDY* (NOWS*)                        | 165  |

| START <sup>*</sup>                   | 168  |

| CMD*                                 | 169  |

| W-R                                  | 170  |

| M-IO<br>EX16* and EX32*              | 170  |

| EX16* and EX32*                      | 171  |

| EXRDY<br>SLBURST* and MSBURST*       | 172  |

| SLBURST* and MSBURST*                | 173  |

| LOCK <sup>*</sup>                    | 174  |

| Bus Control Signals                  | 174  |

| REFRESH <sup>*</sup>                 | 175  |

| MASTER16*                            | 175  |

| IOCHK*                               | 176  |

| RESET                                |      |

| BCLK                                 | 177  |

| OSC                                  | 178  |

| Interrupt Signals                    | 178  |

| IRQx                                 | 178  |

| DMA Signals                          | 180  |

| DROx                                 | 180  |

| DAČKx*                               | 181  |

|                                      |      |

| TC                                                                                                             | 182 |

|----------------------------------------------------------------------------------------------------------------|-----|

| MREQx <sup>*</sup>                                                                                             | 182 |

| MAKx*                                                                                                          | 182 |

| Power Signals                                                                                                  | 182 |

|                                                                                                                |     |

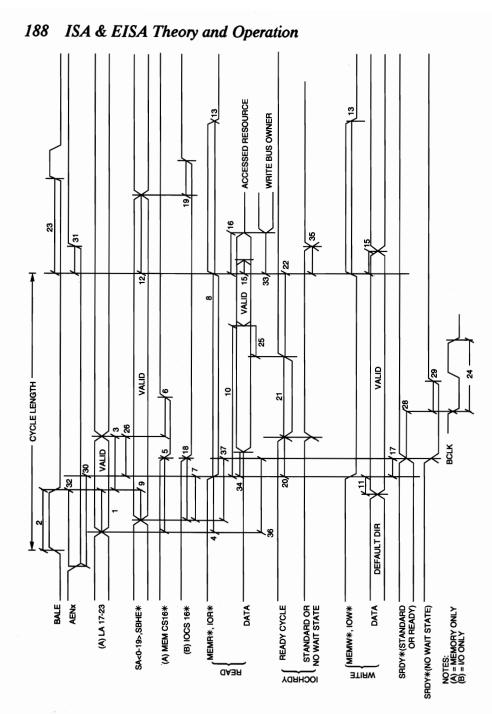

| Chapter Six, Bus Access Cycles                                                                                 | 185 |

| 6.0 ISA Specific Access Cycles on                                                                              |     |

| ISA and E-ISA Platforms                                                                                        | 185 |

| Introduction                                                                                                   | 185 |

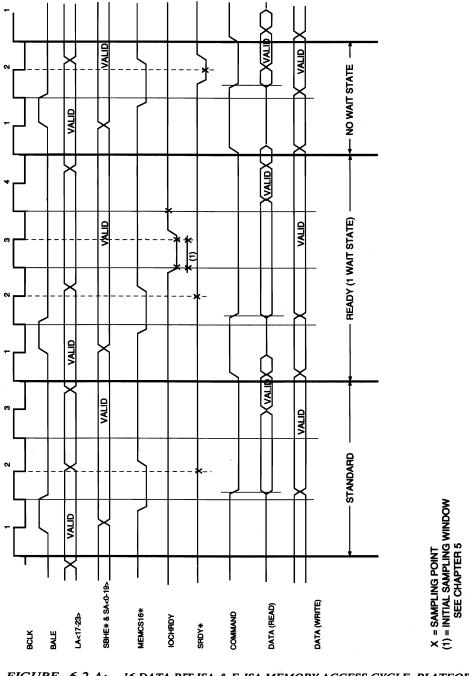

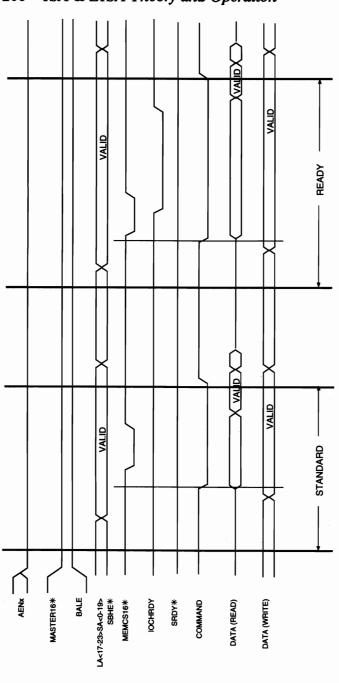

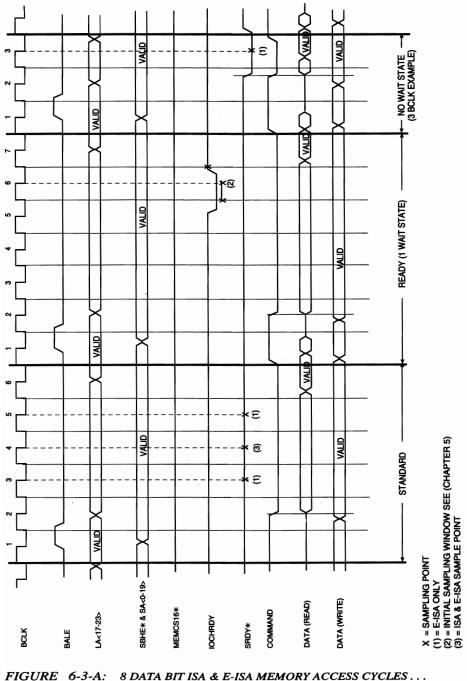

| Standard Memory Access Cycle (ISA Platform)                                                                    | 203 |

| Standard Memory Access Cycle (E-ISA Platform)                                                                  | 206 |

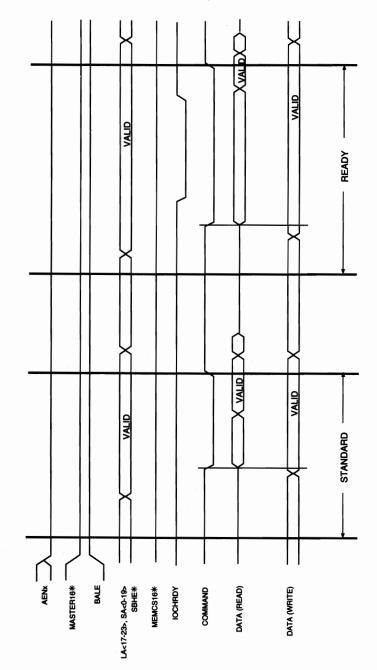

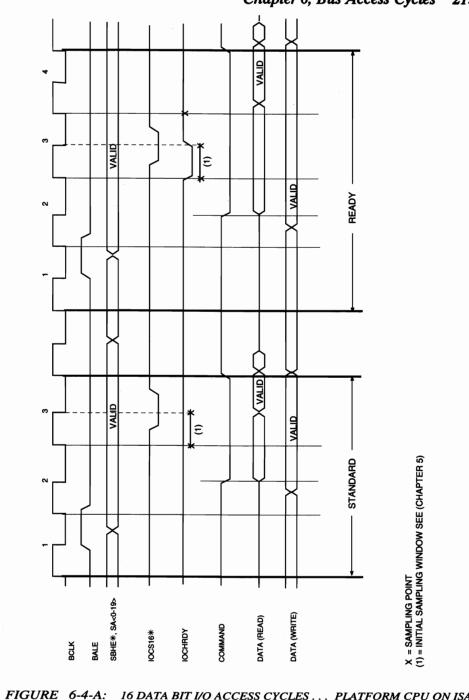

| Standard I/O Access Cycle (ISA Platform)                                                                       | 211 |

| Standard I/O Access Cycle (E-ISA Platform)                                                                     |     |

| Ready Memory Access Cycle (ISA Platform)                                                                       | 217 |

| Ready Memory Access Cycle (E-ISA Platform)                                                                     | 219 |

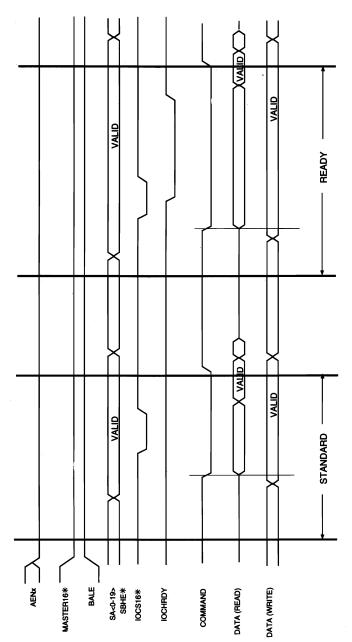

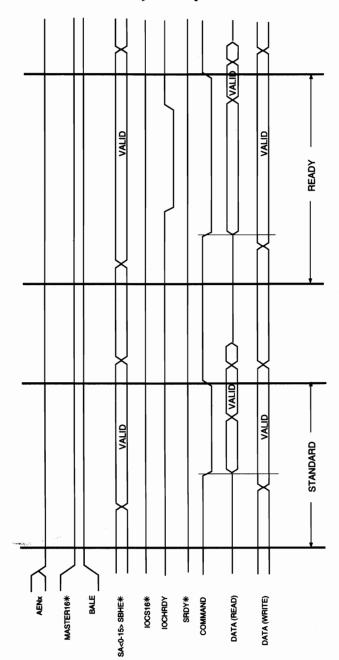

| Ready I/O Access Cycle (ISA Platform)                                                                          | 220 |

| Ready I/O Access Cycle (E-ISA Platform)                                                                        | 221 |

| No-wait-state Memory Access Cycle                                                                              |     |

| (ISA Platform)                                                                                                 | 222 |

| No-wait-state Memory Access Cycle                                                                              |     |

| (E-ISA Platform)                                                                                               | 223 |

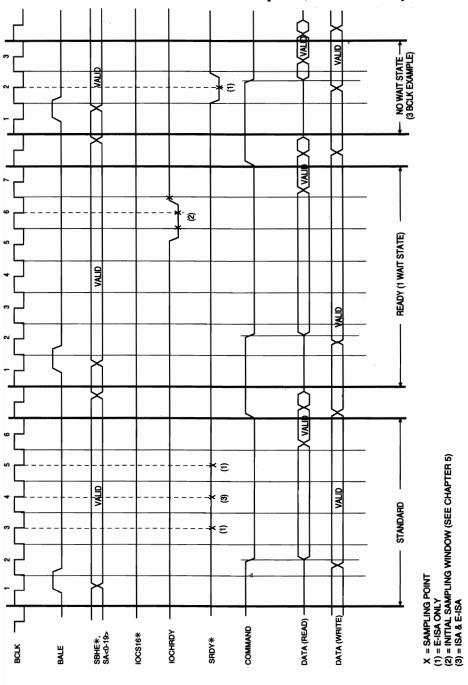

| No-wait-state I/O Access Cycle (ISA Platform)                                                                  | 225 |

| No-wait-state I/O Access Cycle (E-ISA Platform)                                                                | 227 |

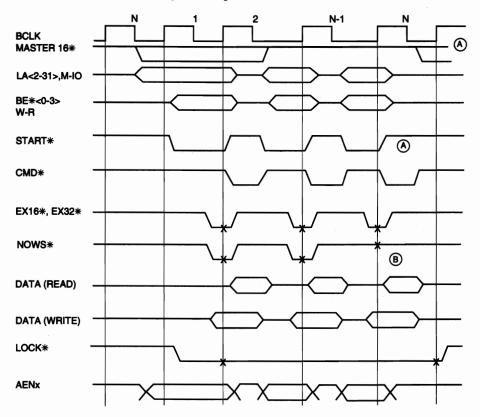

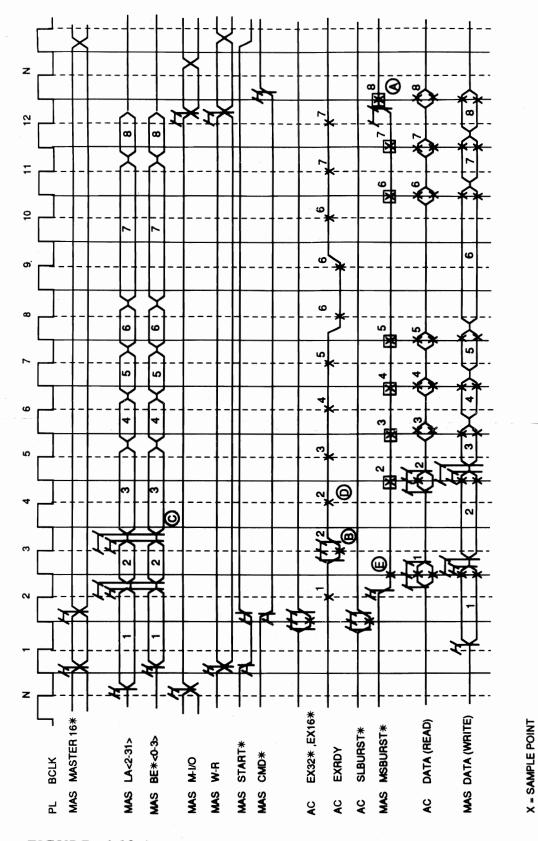

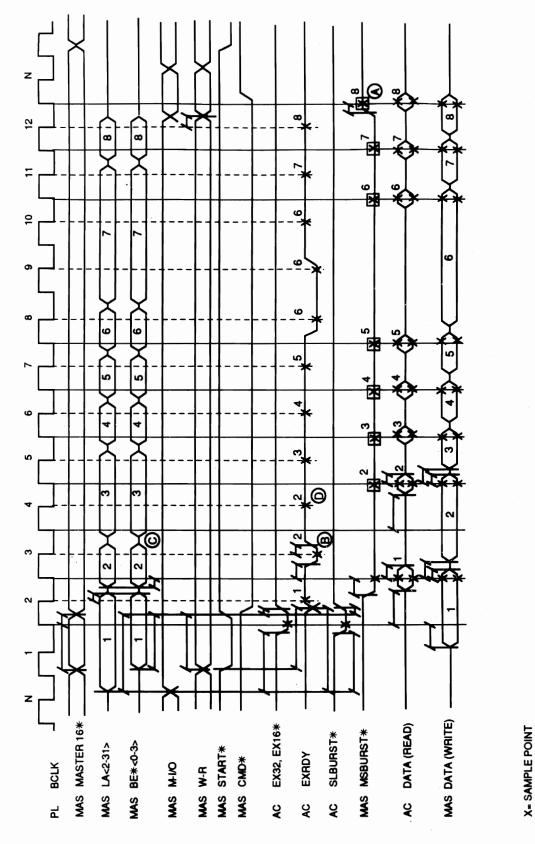

| 6.1 EISA Specific Access Cycles on EISA Platforms                                                              | 220 |

| Unit EISA Specific Access Cycles on EISA Flationitis                                                           | 223 |

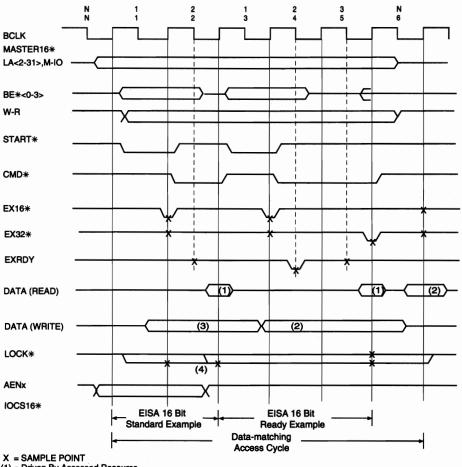

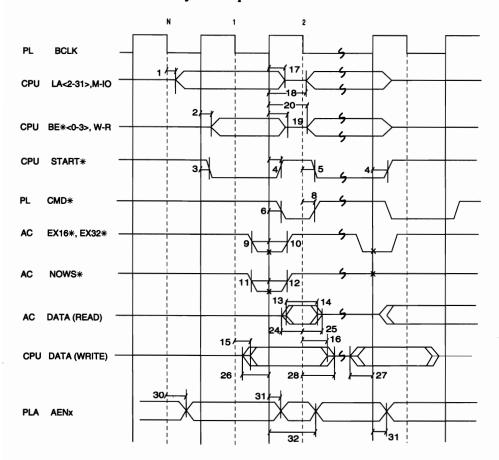

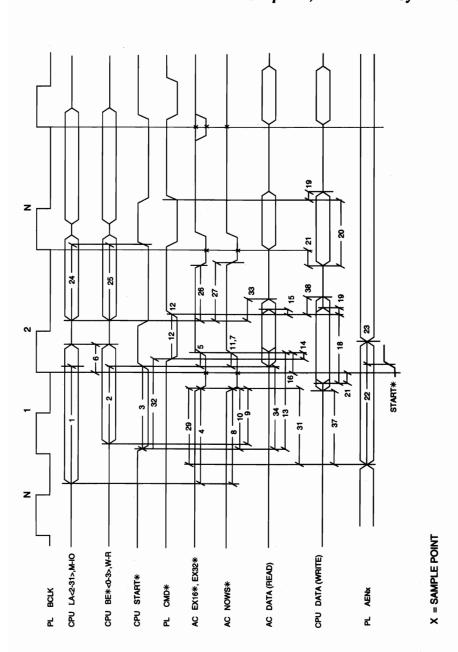

| Introduction<br>EISA Standard Memory or I/O Access Cycle                                                       | 227 |

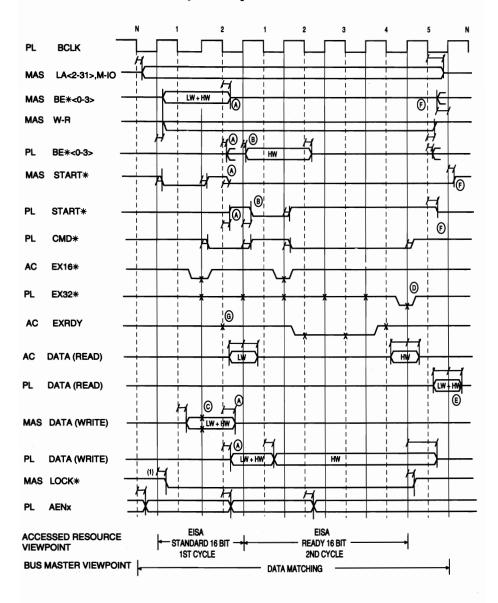

| (EISA Platform)                                                                                                | 241 |

| EISA Ready Memory or I/O Access Cycle                                                                          | 241 |

| (EISA Platform)                                                                                                | 216 |

| EISA Data-Matching Mamory or I/O Access                                                                        | 240 |

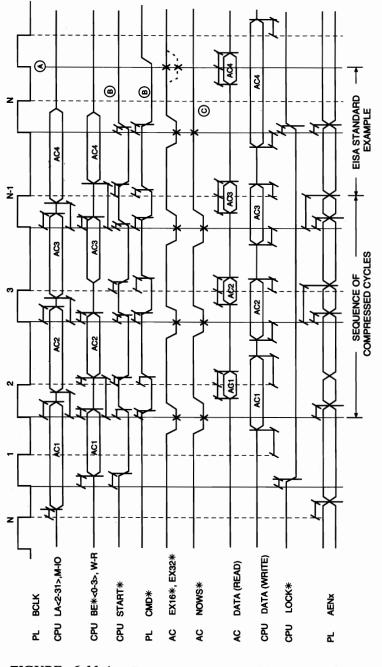

| EISA Data-Matching Memory or I/O Access<br>Cycle (EISA Platform)<br>EISA Compressed Memory or I/O Access Cycle | 251 |

| FISA Compressed Memory or I/O Access Cycle                                                                     | 201 |

| (EISA Platform)                                                                                                | 263 |

| (EISA Platform)                                                                                                | 203 |

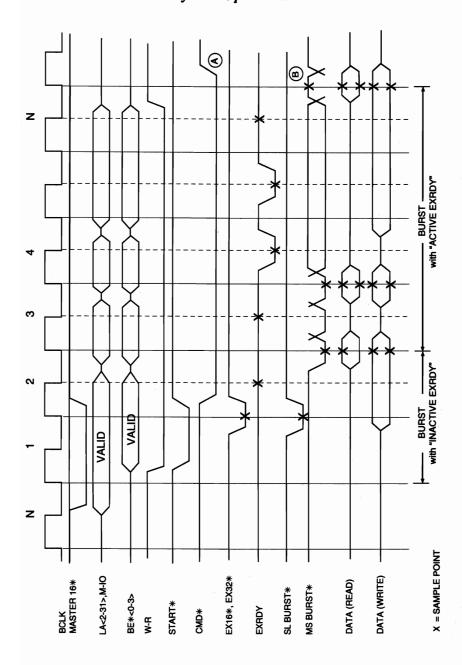

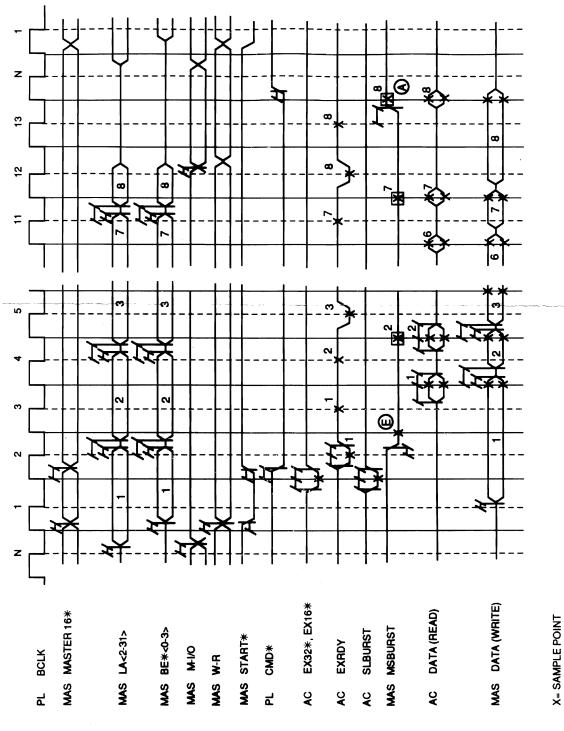

| Buist Memory Access Cycle (EISA Flattorin)                                                                     | 270 |

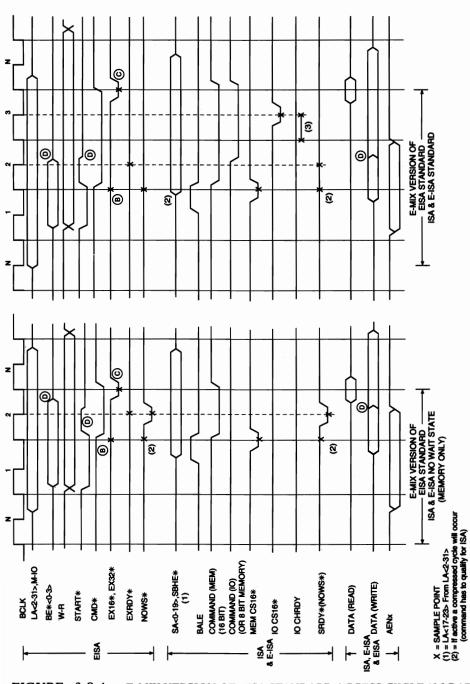

| 6.2 EISA Bus Master Access Cycles to ISA and                                                                   |     |

| 6.2 EISA Bus Master Access Cycles to ISA and<br>E-ISA Resources (EISA Platforms)                               | 298 |

| Introduction                                                                                                   | 298 |

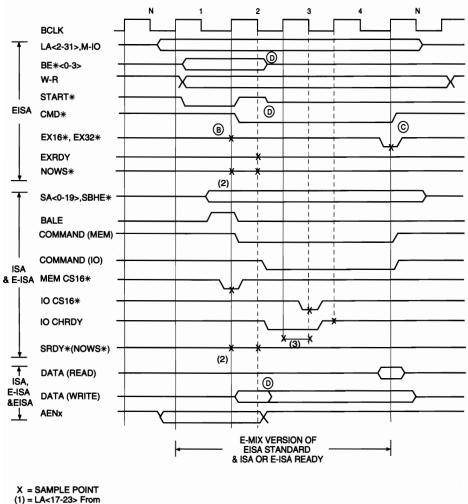

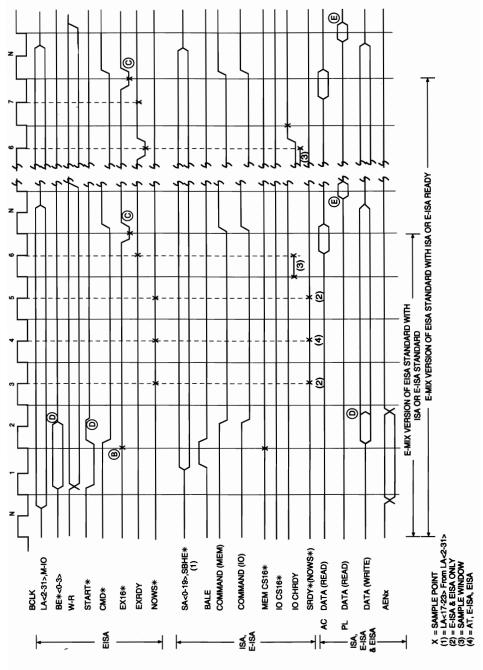

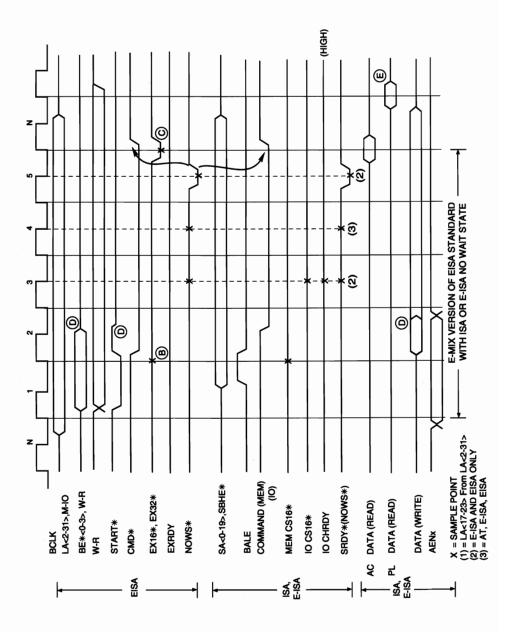

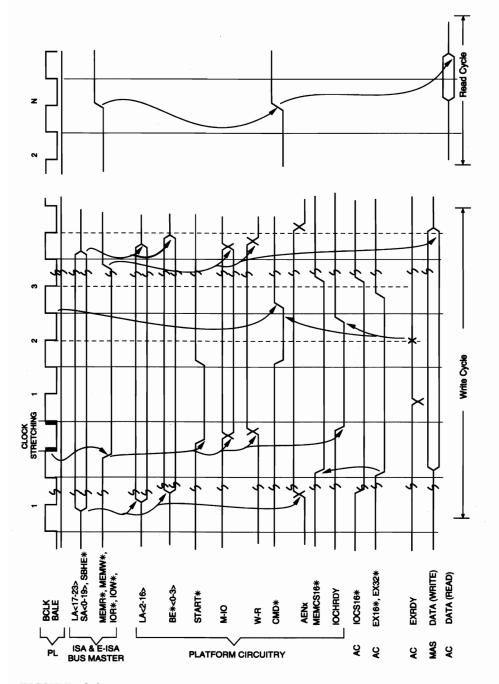

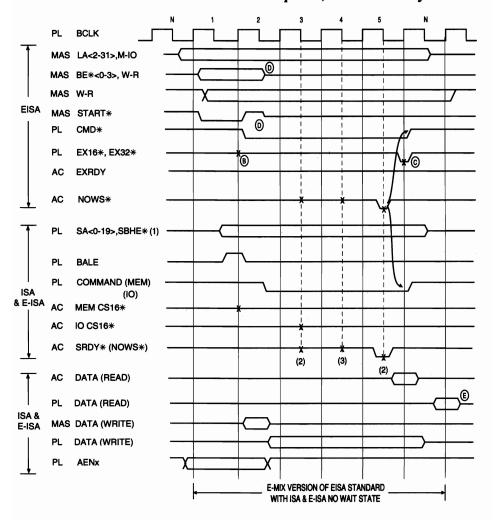

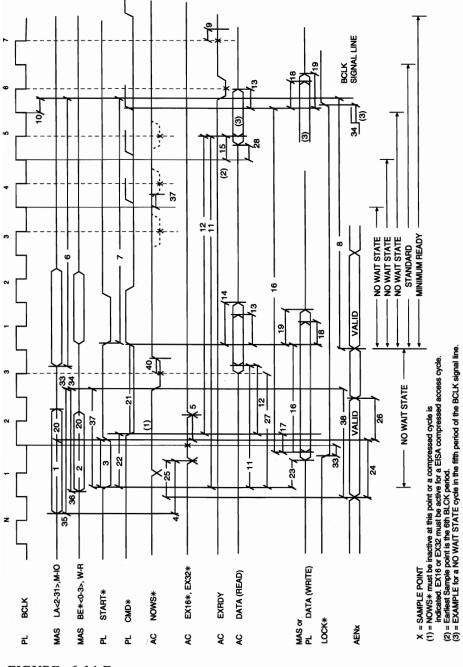

| E-MIX Version of the EISA Standard Access                                                                      |     |

| Cycle (EISA Platform)                                                                                          | 307 |

|                                                                                                                |     |

| Special Consideration: E-MIX Version of the<br>EISA Standard Access Cycle to an 8 Data Bit<br>EISA I/O Resource<br>E-MIX Version of the EISA Data-Matching<br>Access Cycle<br>Special Consideration: E-MIX Version of the<br>EISA Data-Matching Access Cycle to an<br>8 Data Bit EISA I/O Resource | 313<br>318<br>323 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

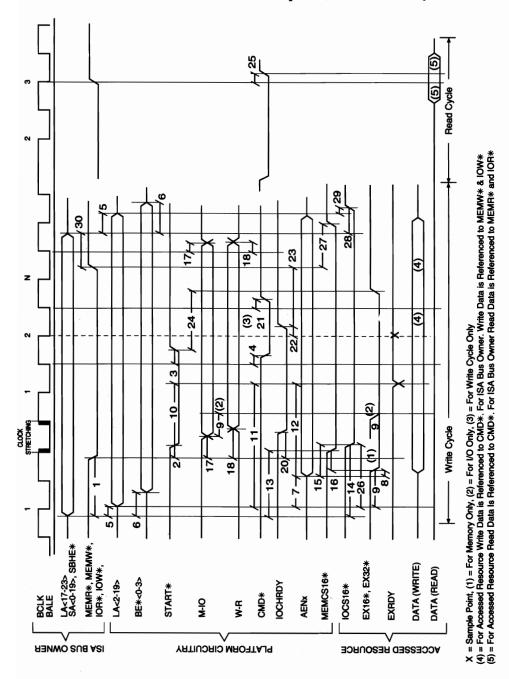

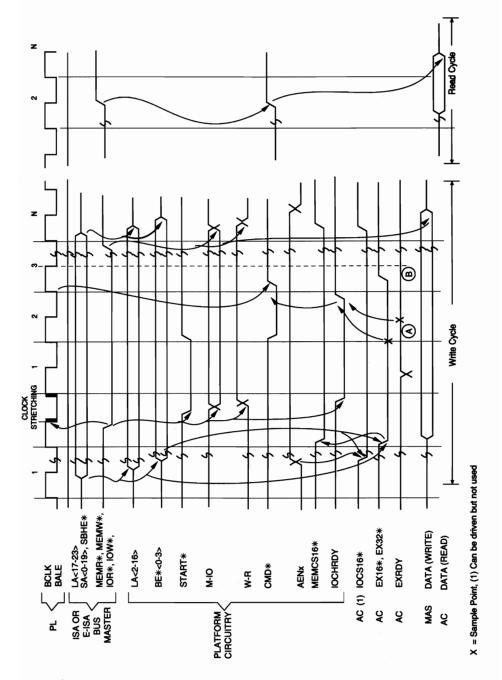

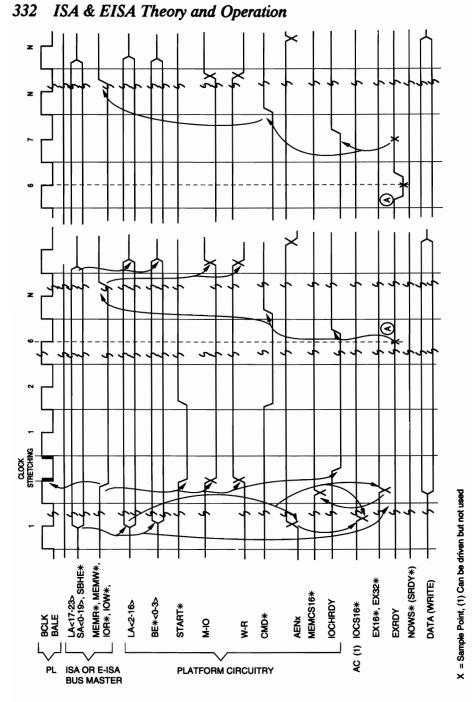

| 6.3 ISA and E-ISA Bus Master Access Cycles<br>to EISA Resources (EISA Platforms)<br>Introduction<br>First Part of the I-MIX Access Cycle<br>Determination of Resource Type<br>Continuation of the I-MIX Access Cycle                                                                               | 323<br>331<br>334 |

| 6.4 Lock Cycles                                                                                                                                                                                                                                                                                    | 338               |

| 6.5 Back to Back Protocol                                                                                                                                                                                                                                                                          | 339               |

| Chapter Seven, DMA Transfer Bus Cycles                                                                                                                                                                                                                                                             | 343               |

| 7.0 General Information                                                                                                                                                                                                                                                                            | 343               |

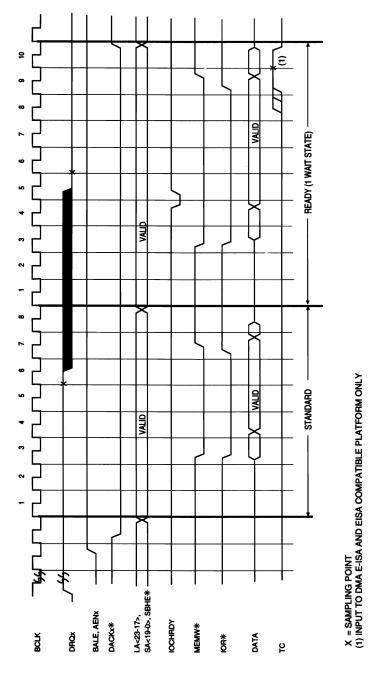

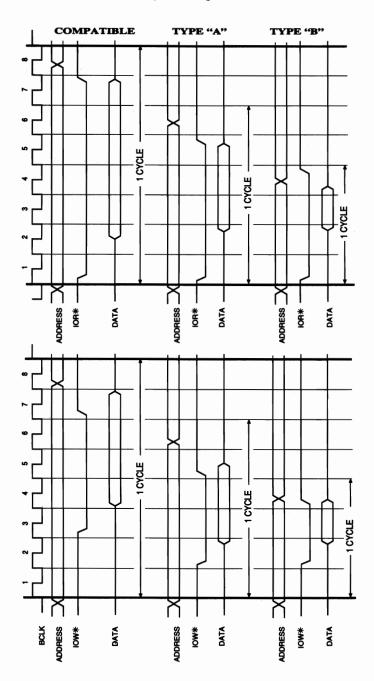

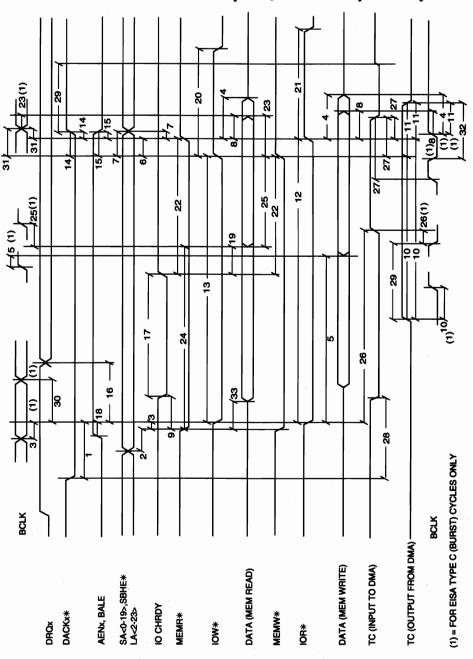

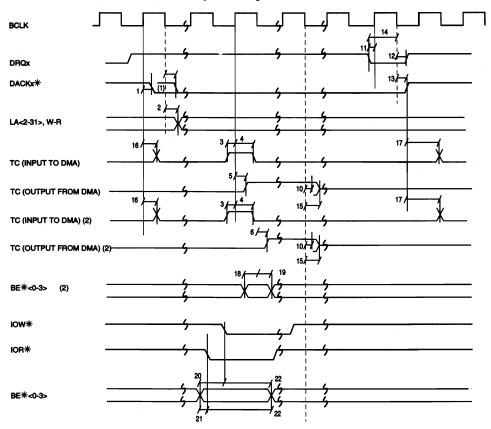

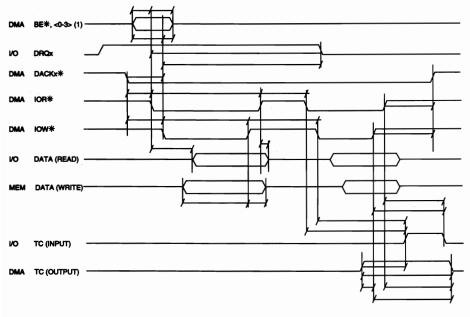

| Standard Version of the Compatible Transfer<br>Cycle on an ISA Platform<br>Standard Versions of the Compatible, TYPE A,                                                                                                                                                                            | 346<br>356        |

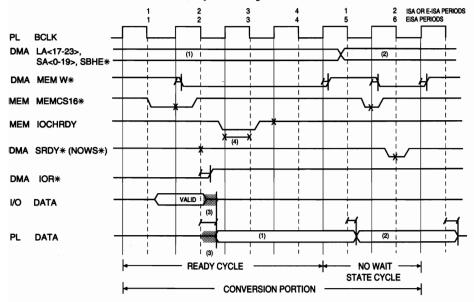

| and TYPE B Transfer Cycles on an E-ISA<br>Platform<br>Ready Version of the Compatible Transfer Cycle<br>on an ISA Platform                                                                                                                                                                         | 362               |

| on an ISA Platform<br>Ready Versions of the Compatible, TYPE A,<br>and TYPE B Transfer Cycles on an E-ISA<br>Platform                                                                                                                                                                              | 373               |

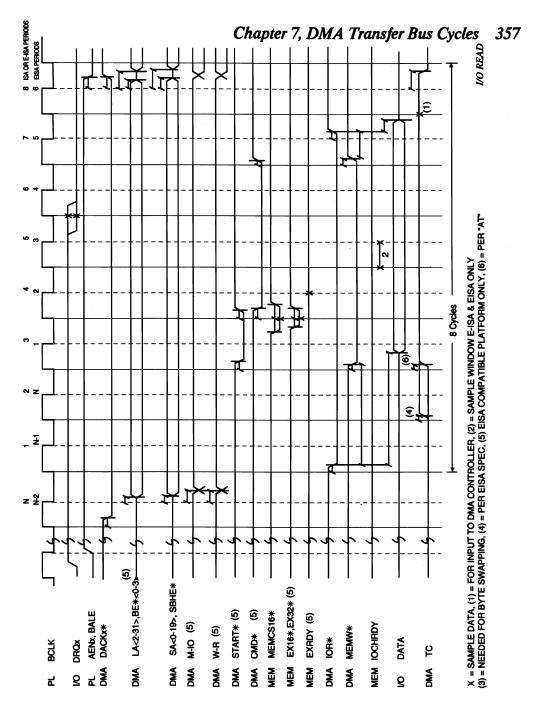

| 7.2 DMA Transfer Cycles on EISA Platforms<br>Introduction<br>Incremental Support                                                                                                                                                                                                                   | 377               |

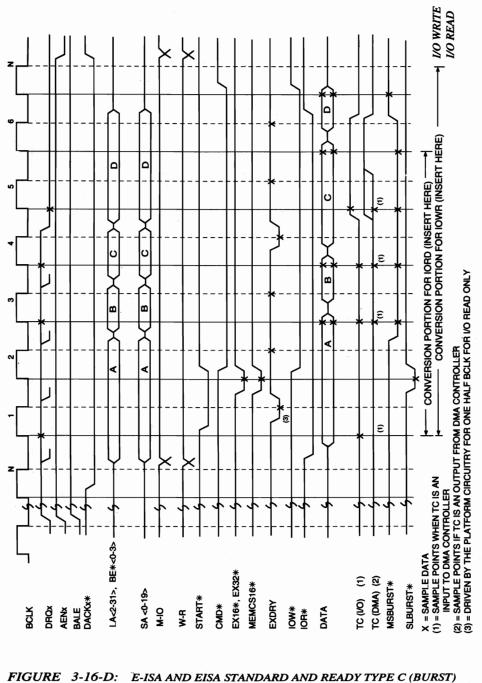

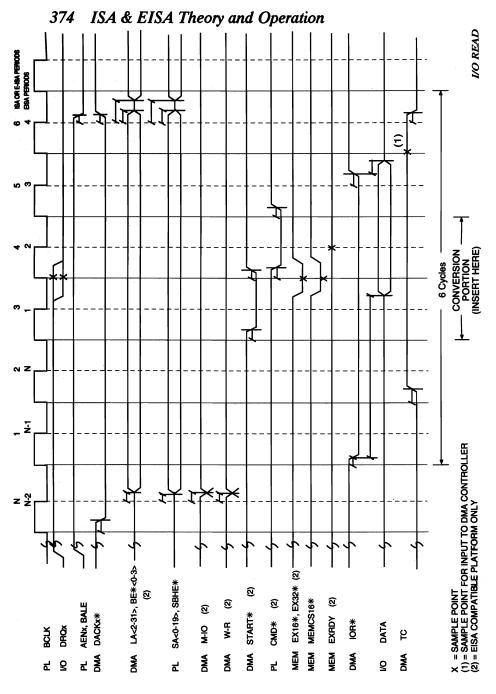

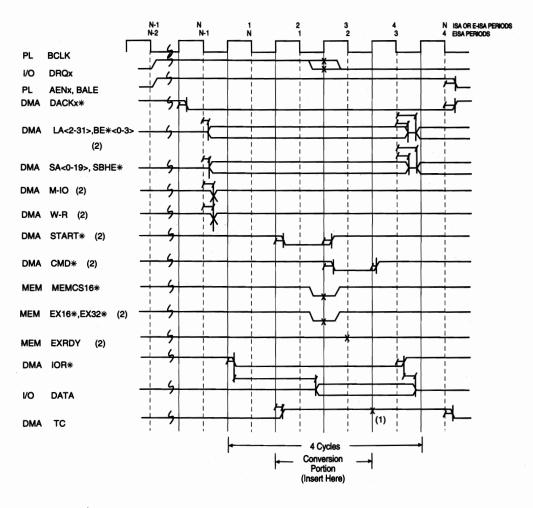

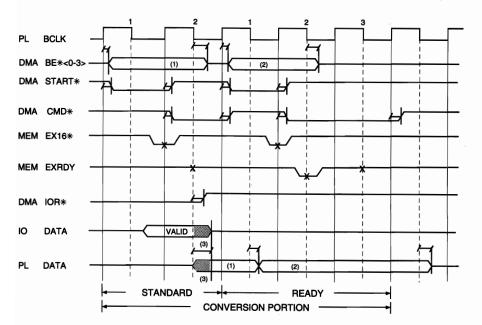

| TYPE A and TYPE B Transfer Cycles with<br>Conversion on EISA Platforms                                                                                                                                                                                                                             |                   |

| TYPE C (Burst) Transfer Cycles on EISA                      |       |

|-------------------------------------------------------------|-------|

| Platforms                                                   | . 393 |

| Platforms                                                   |       |

| Conversion                                                  | . 396 |

| Conversion                                                  | . 400 |

| 7.3 DMA Modes                                               | . 407 |

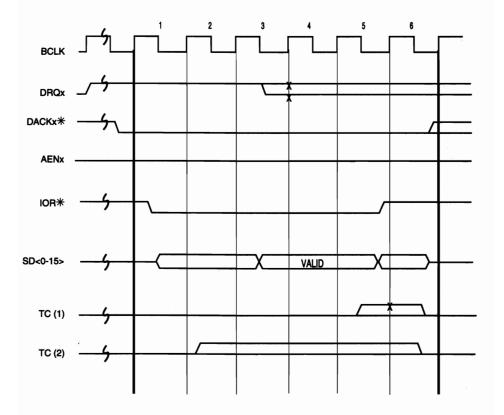

| 7.4 DRQx and TC Considerations                              | . 410 |

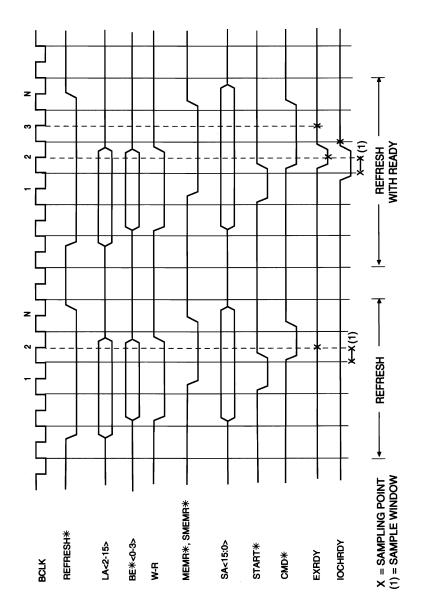

| Chapter Eight, Refresh Cycles                               | . 413 |

| Introduction                                                | . 413 |

| Refresh Cycle                                               | . 419 |

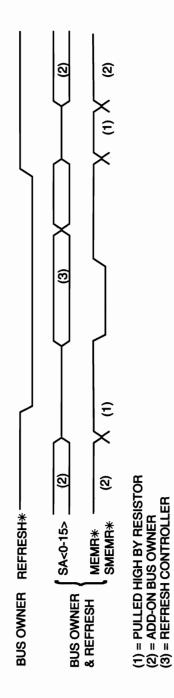

| Refresh Cycle<br>Special Considerations for ISA and         |       |

| E-ISA Platforms                                             | . 420 |

| Changes Nine Artistantion Coulor                            | 172   |

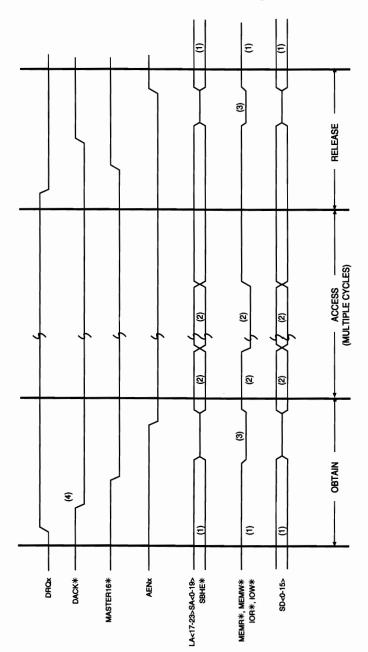

| Chapter Nine, Arbitration Cycles                            | . 423 |

| Introduction<br>Arbitration Protocol for ISA or E-ISA       | 423   |

|                                                             |       |

| Add-On Bus Owner Cards on ISA or                            | 407   |

| E-ISA Compatible Platforms                                  | 42/   |

| Arbitration Protocol for ISA or E-ISA                       |       |

| Add-On Bus Owner Cards on                                   | 400   |

| EISA Compatible Platforms                                   | 428   |

| Arbitration Protocol for EISA Add-On Bus                    | 400   |

| Owner Cards on EISA Compatible Platforms                    | 428   |

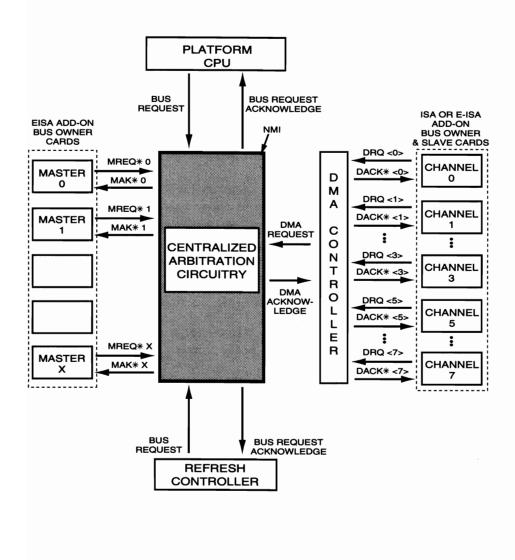

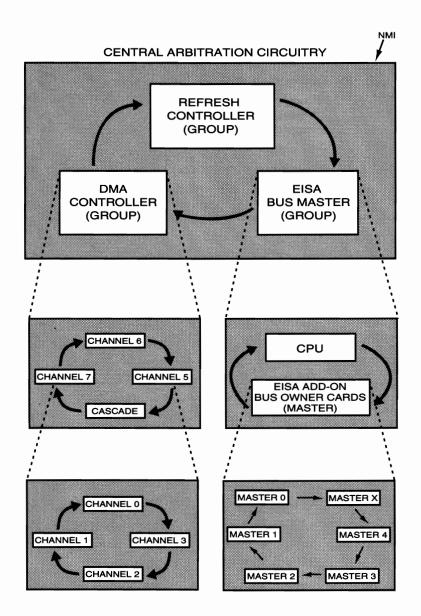

| System Arbitration Priorities.                              |       |

| ISA or E-ISA Compatible Platform                            | 435   |

| EISA Compatible Platform                                    | 430   |

| Chapter Ten, Bus Integrity                                  | . 441 |

| Introduction                                                | 441   |

| Introduction<br>D.C. Loading and A.C. Timing Considerations | 442   |

| Signal Line Drivers                                         | 443   |

| Settling Time                                               | 446   |

| Timing Table Interpretation                                 | 447   |

| Chapter Eleven, Performance                                 | . 451 |

| Chapter Twelve, Configuration Space                         | 455   |

| Introduction                                                | 455   |

| Introduction<br>Reserved Registers                          | 455   |

|                                                             | 400   |

| Chapter Thirteen, Power and Initialization |     |

|--------------------------------------------|-----|

| Power Tolerance                            | 457 |

| Initialization                             | 459 |

| Chapter Fourteen, Mechanical Notes         |     |

| Appendix A, Fast EISA                      |     |

| Appendix B, PC/96 Bus                      |     |

| Appendix C, PC/104                         | 477 |

| Appendix D, PCXI Passive Backplane         |     |

| Index                                      |     |

|                                            |     |

١

# List of Figures

| 1-1: ISA, E-ISA,                | , and EISA Platform                                                                                                    | rage                 |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2-1: Memory Ad                  | ldress Space                                                                                                           | 28                   |

| 2-2: ISA I/O Ad                 | ldress Space                                                                                                           | 31                   |

| 2-3: E-ISA and                  | EISA I/O Address Space                                                                                                 | 32                   |

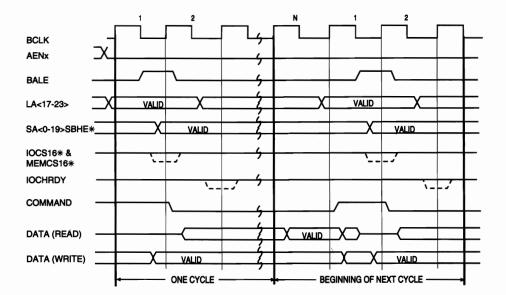

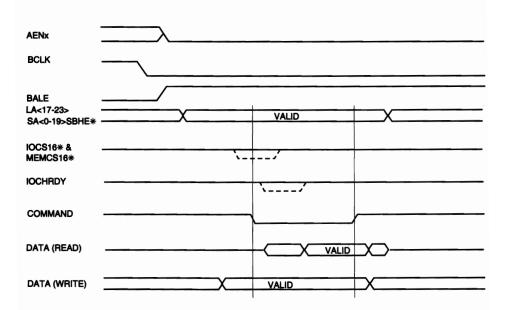

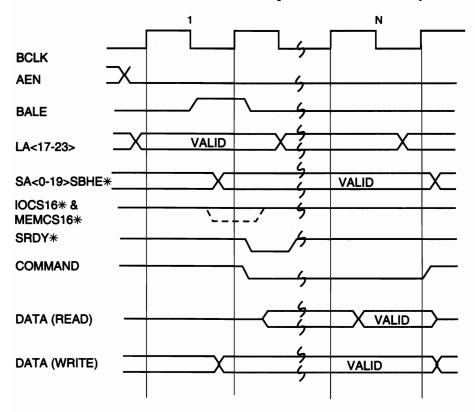

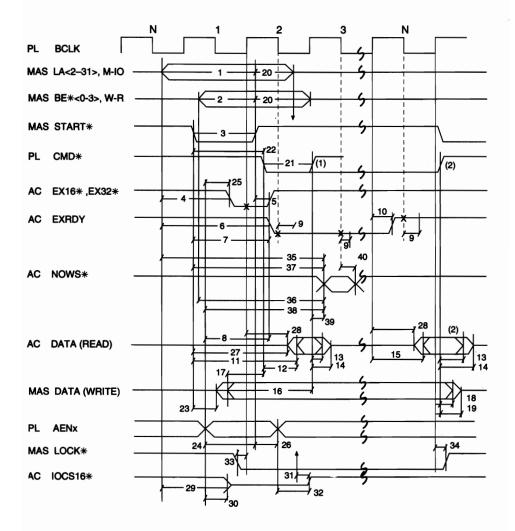

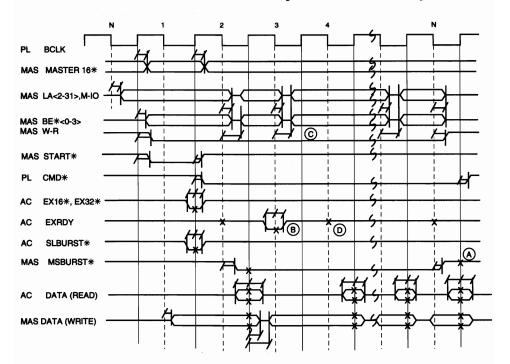

| 3-1: Generic ISA<br>(Platform C | A and E-ISA Standard and Ready Acce<br>PU)                                                                             | ess Cycle<br>        |

| 3-2: Generic ISA<br>(Add-On Bu  | A and E-ISA Standard and Ready Acco<br>Is Owner Card)                                                                  | ess Cycle<br>40      |

|                                 | A and E-ISA No-wait-state Cycle<br>PU and E-ISA Add-On Bus Owner Ca                                                    | rd) (BALE is High)41 |

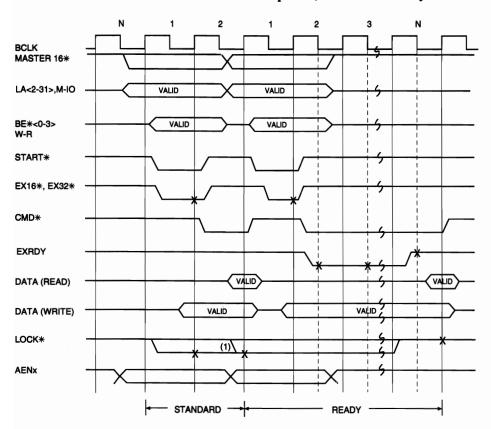

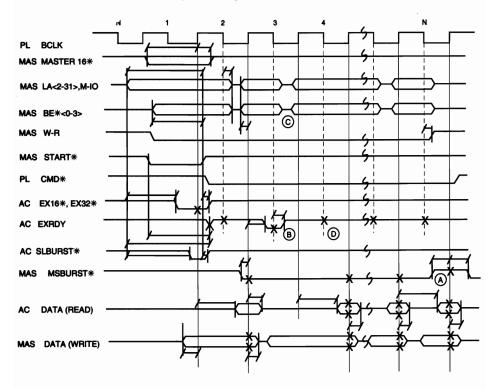

| 3-4: Generic EIS                | SA Standard and Ready Access Cycle                                                                                     | 49                   |

|                                 | SA Data-Matching Access Cycle<br>t Bus Master to 16 Data Bit Accessed F                                                | Resource Example)51  |

| 3-6: Generic EIS                | SA Compressed Access Cycle                                                                                             | 54                   |

| 3-7: Generic EIS                | SA Burst Access Cycle                                                                                                  | 57                   |

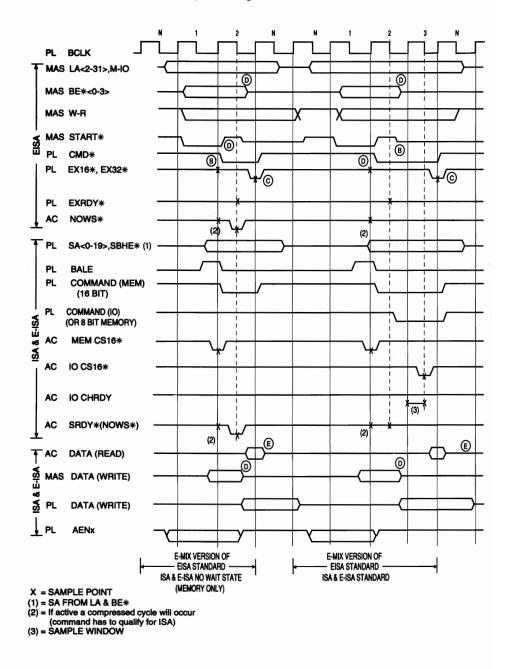

| (16 Data Bit                    | <sup>r</sup> ersion of EISA Standard Access Cycle<br>t Access Cycle to ISA or E-ISA<br>Add-On Slave Card) (MASTER16* = |                      |

| (16 Data Bit                    | 'ersion of EISA Standard Access Cycle<br>t Access Cycle to ISA or E-ISA<br>Add-On Slave Card) (MASTER16* =             |                      |

| (8 Data Bit )                   | <pre>'ersion of EISA Standard Access Cycle Access to ISA or E-ISA 8 Data Bit rd) (MASTER16* = 0 or 1)</pre>            |                      |

| (8 Data Bit )                   | <pre>/ersion of EISA Standard Access Cycle Access Cycle to ISA or E-ISA 8 Data E rd) (MASTER16* = 0 or 1)</pre>        | Bit                  |

| 3-9: Generic I-M<br>to EISA 16  | IIX Access Cycle (ISA Bus Owner Car<br>Data Bit Accessed Resource                                                      | d<br>69              |

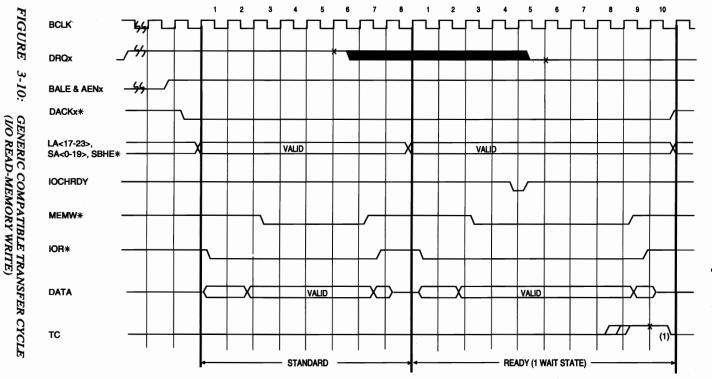

| 3-10: Generic Co                | ompatible Transfer Cycle (I/O Read -                                                                                   | Memory Write)71      |

$\sim$

| 6-8: EISA                | Data-Matching Access Cycle EISA Bus Master Viewpoint                                                                   | 254 |

|--------------------------|------------------------------------------------------------------------------------------------------------------------|-----|

| 6-9: EISA                | Data-Matching Access Cycle EISA Bus Master Viewpoint                                                                   | 258 |

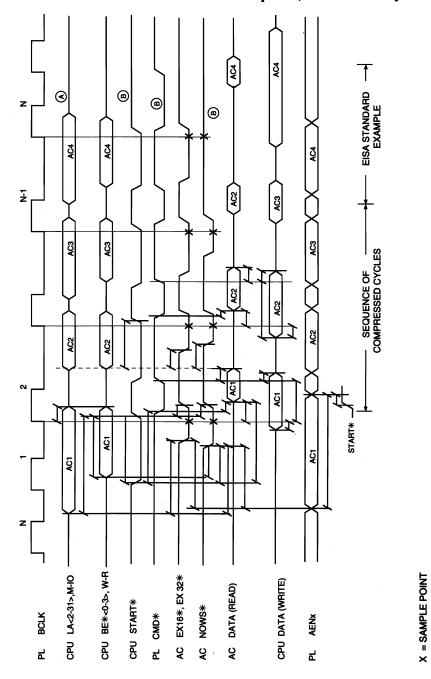

| 6-10-A: El               | ISA Compressed Access Cycle Platform CPU Viewpoint                                                                     | 266 |

| 6-10-B: El<br>(Acces     | ISA Compressed Access Cycle Add-On Slave Card ssed Resource) Viewpoint                                                 | 267 |

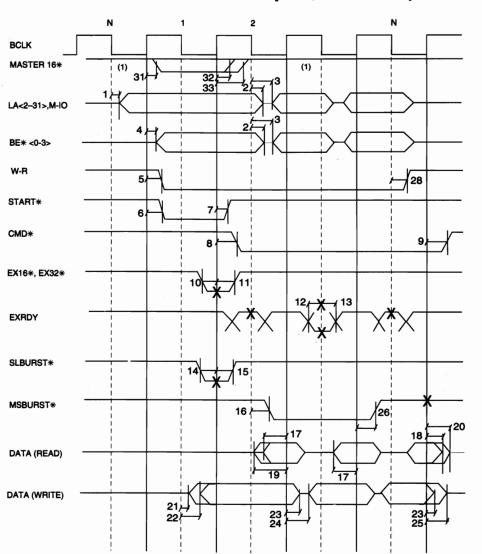

| 6-11-A: El               | ISA Compressed Access Cycle Platform CPU Viewpoint                                                                     | 274 |

| 6-11-B: El               | ISA Compressed Access Cycle Add-On Slave Card Viewpoint.                                                               | 275 |

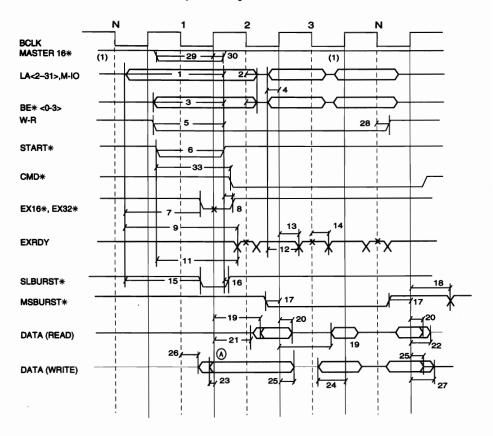

| 6-12-A: El               | ISA Burst Access Cycle EISA Bus Master Viewpoint                                                                       | 281 |

| 6-12-B: El               | ISA Burst Access Cycle EISA Accessed Resource Viewpoint                                                                | 282 |

| 6-13: "Dov<br>(Write Exa | wnshift" EISA Bus Master and Platform Data Drive<br>umple)                                                             | 292 |

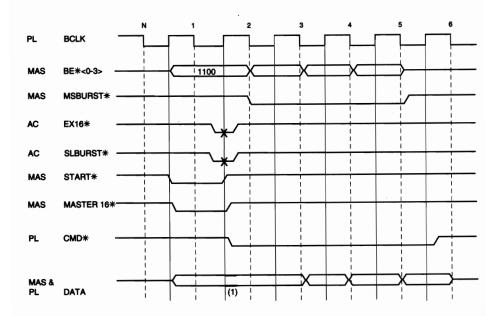

| 6-13-A: El               | ISA Burst Cycle EISA Bus Master Viewpoint                                                                              | 293 |

| 6-13-B: El               | ISA Burst Cycle Accessed Resource Viewpoint                                                                            | 294 |

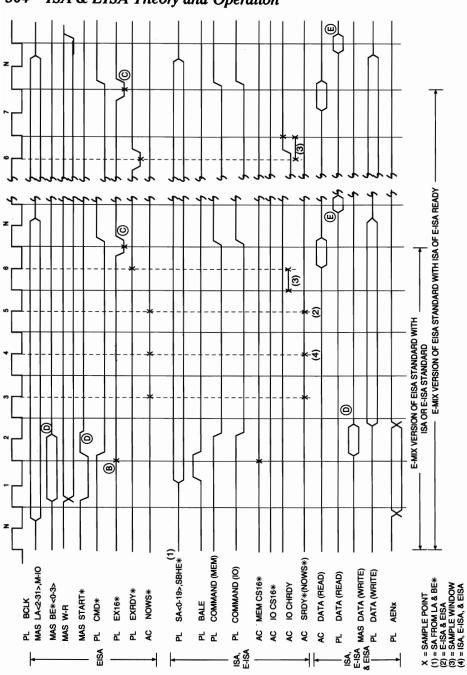

| Access                   | -MIX Version of EISA Standard 16 Data Bit<br>ss Cycle to ISA or E-ISA 16 Data Bit<br>On Slave Card (MASTER16* = 0)     | 302 |

| Acces                    | '-MIX Version of EISA Standard 16 Data Bit<br>ss Cycle to ISA or E-ISA 16 Data Bit<br>On Slave Card (MASTER16* = 0)    | 303 |

| Access                   | -MIX Version of EISA Standard 8 Data Bit<br>ss Cycle to ISA or E-ISA 8 Data Bit<br>On Slave Card (MASTER16* = 0 or 1)  | 304 |

| Access                   | S-MIX Version of EISA Standard 8 Data Bit<br>ss Cycle to ISA or E-ISA 8 Data Bit<br>On Slave Card (MASTER16* = 0 or 1) | 305 |

| 6-14-E: E-<br>(Reson     | T-MIX Access Cycle to 8 Data Bit EISA I/O<br>purce Viewpoint)                                                          | 313 |

|                          | IX Access Cycle ISA or E-ISA Bus Owner Add-On Card<br>SA Accessed Resource                                             | 325 |

| 6-16-A: I-MIX Access Cycle ISA or E-ISA Bus Owner Add-On Card<br>to 16 Data Bit EISA Accessed Resource                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6-16-B: I-Mix Access Cycle ISA or E-ISA Bus Owner Add-On Card<br>to 8 Data Bit EISA Accessed Resource                                                                                                                      |

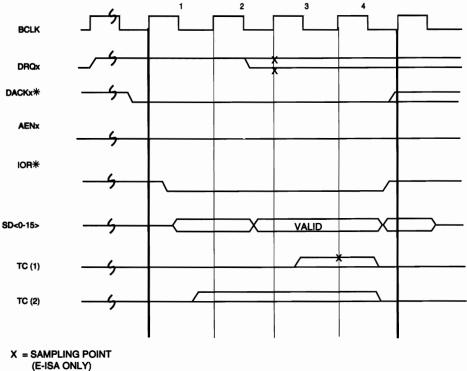

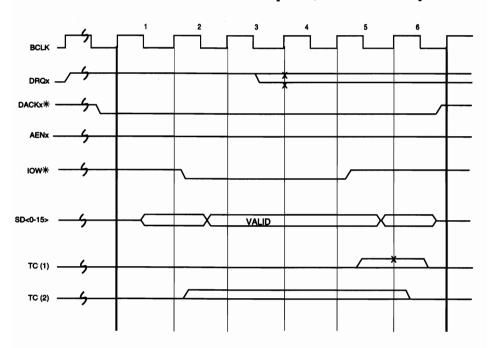

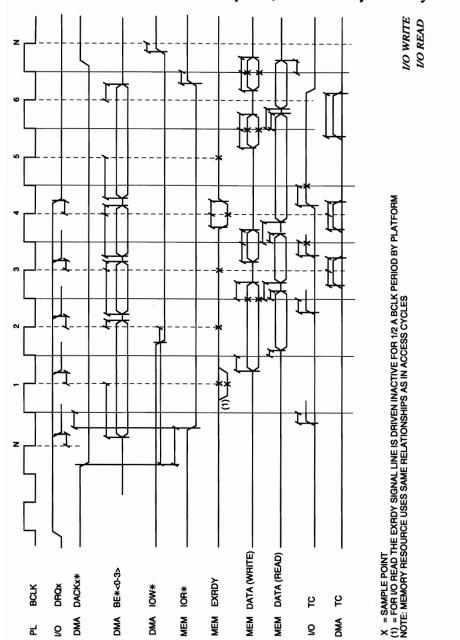

| 7-1-A: Transfer Cycle                                                                                                                                                                                                      |

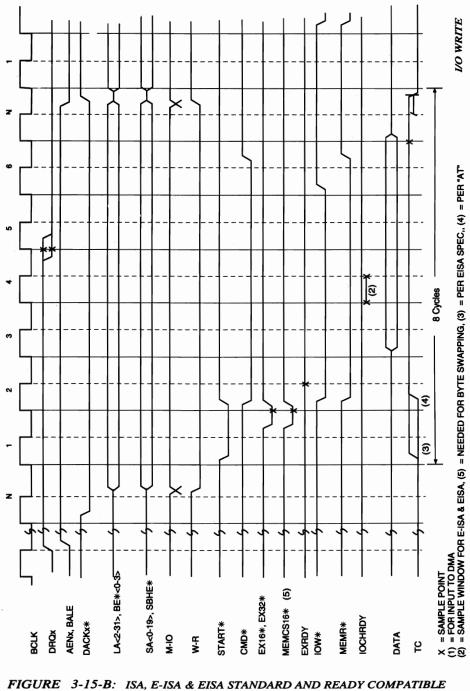

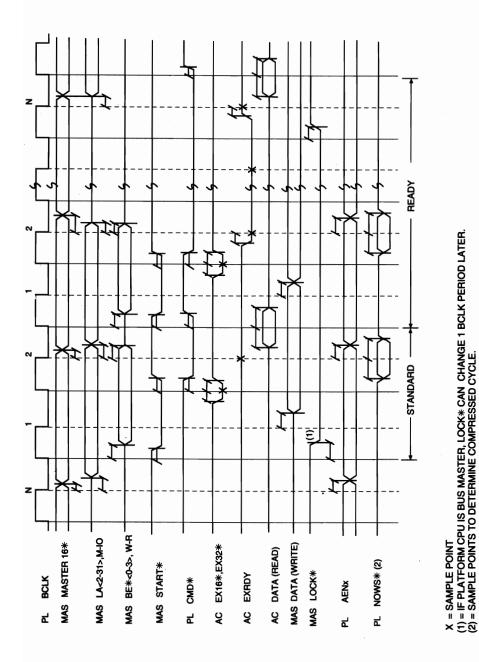

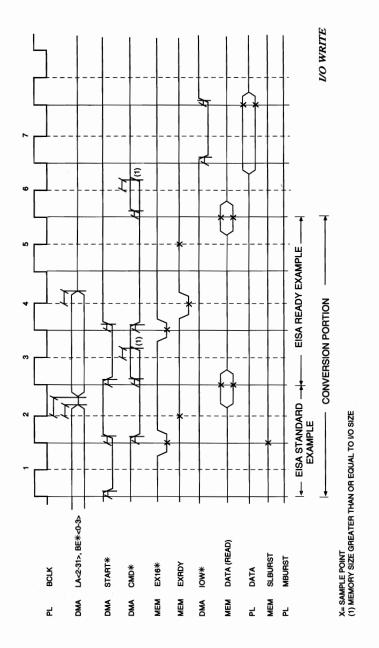

| 7-1-B: ISA, E-ISA, and EISA Standard and Ready Compatible<br>Transfer Cycle DMA Controller and Platform Circuitry Viewpoint357                                                                                             |

| 7-1-C: ISA, E-ISA, and EISA Standard and Ready Compatible<br>Transfer Cycle DMA Controller and Platform Circuitry Viewpoint358                                                                                             |

| 7-2: Transfer Cycles Additional Timing Relationships on<br>E-ISA and EISA Compatible Platforms                                                                                                                             |

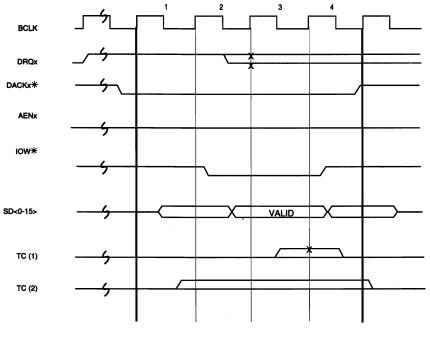

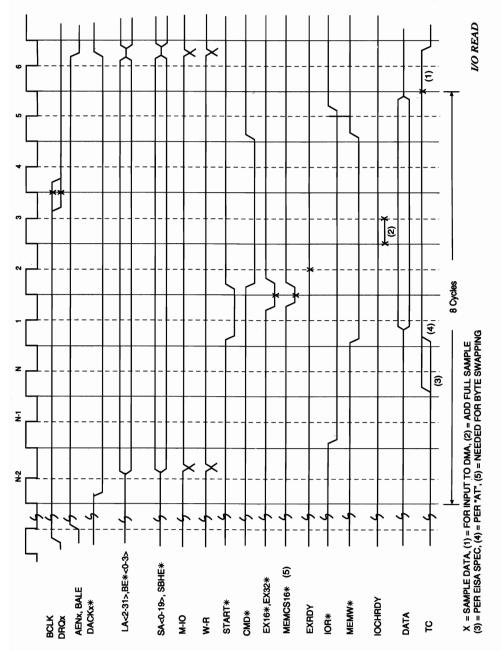

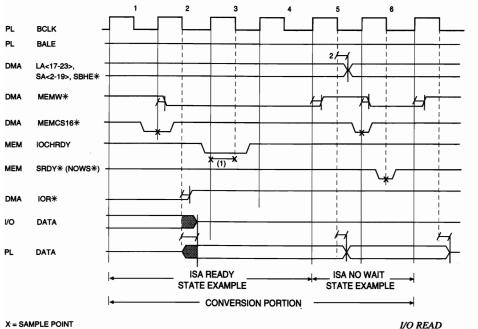

| 7-3: ISA, E-ISA, and EISA Standard and Ready Compatible<br>Types A and B Transfer Cycle DMA I/O Add-On Slave<br>Card Resource Viewpoint                                                                                    |

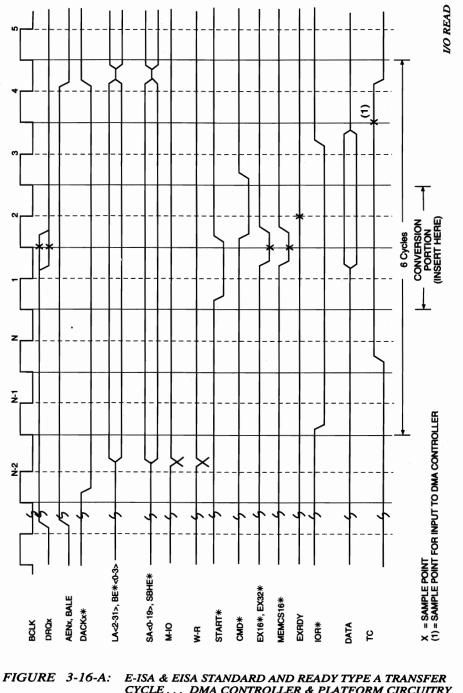

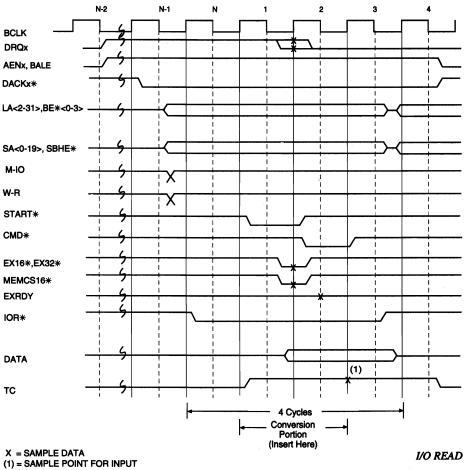

| 7-4-A: E-ISA and EISA Standard and Ready Type A Transfer Cycle<br>(No Conversion) DMA Controller and Platform Circuitry Viewpoint374                                                                                       |

| 7-4-B: E-ISA and EISA Standard and Ready Type A Transfer Cycle<br>(No Conversion) DMA Controller and Platform Circuitry Viewpoint375                                                                                       |

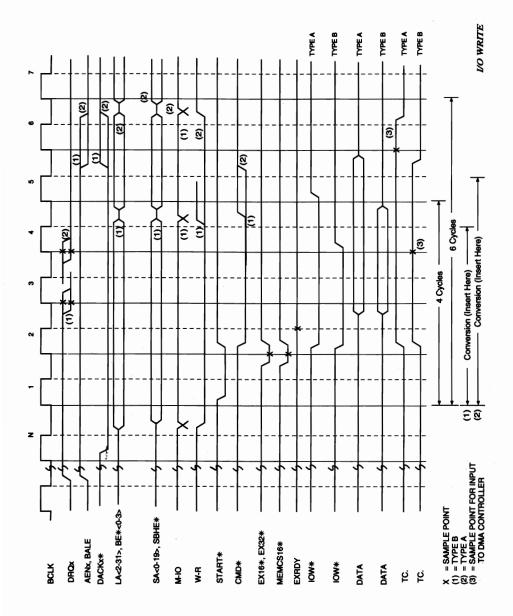

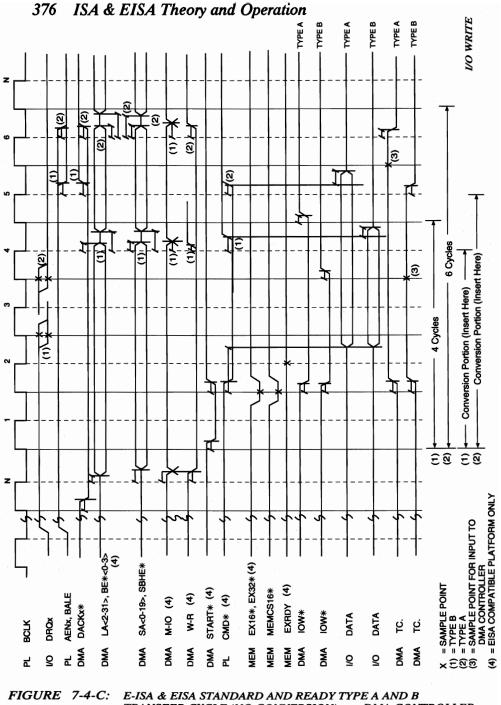

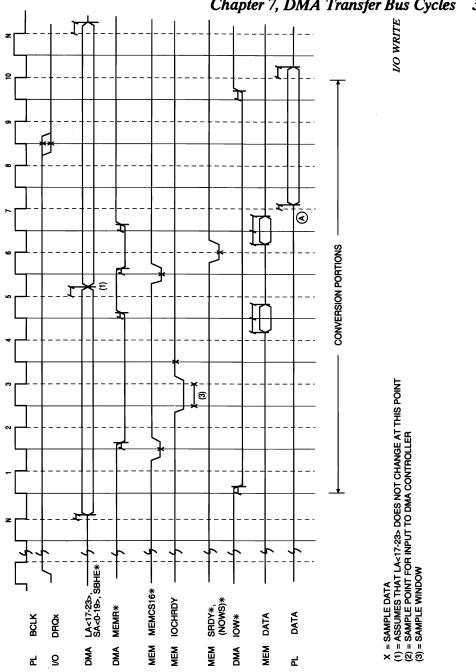

| 7-4-C: E-ISA and EISA Standard and Ready Type A and B Transfer Cycle<br>(No Conversion) DMA Controller and Platform Circuitry Viewpoint376                                                                                 |

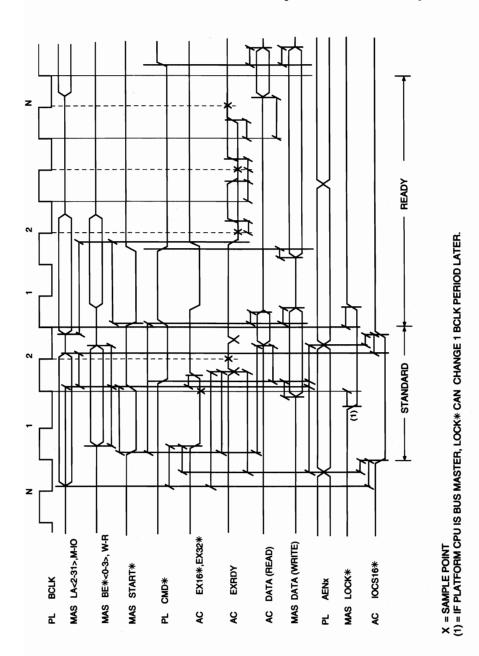

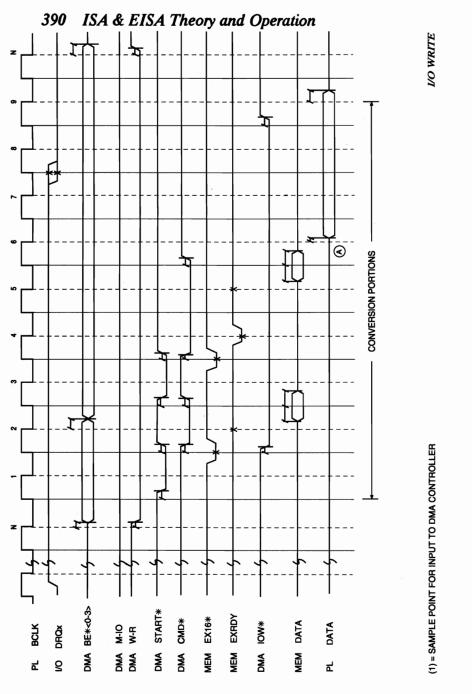

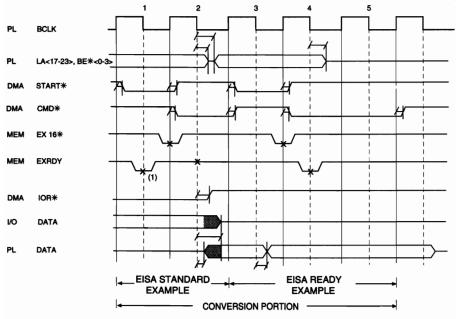

| 7-5-A: Conversion Portion of Type A or B Transfer Cycle with<br>ISA and E-ISA Memory (16 Data Bit Memory to 32 Data Bit<br>I/O Example) DMA Controller and Platform Circuitry<br>Viewpoint (EISA Compatible Platform Only) |

| 7-5-B: Conversion Portion of Type A Transfer Cycle with<br>ISA and E-ISA Memory (16 Data Bit Memory to 32 Data Bit<br>I/O Example) DMA Controller and Platform Circuitry<br>Viewpoint (EISA Compatible Platform Only)      |

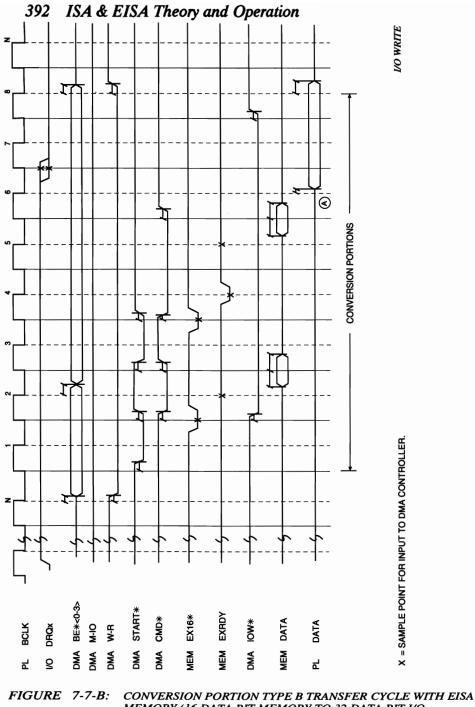

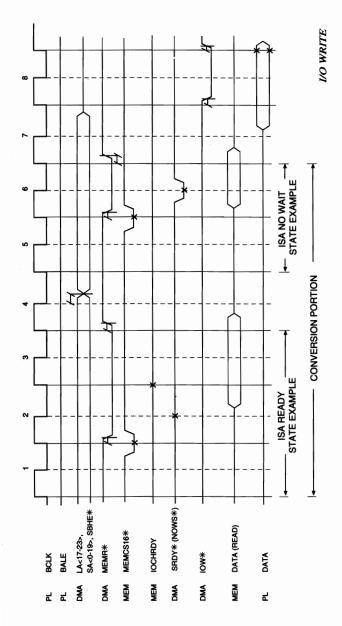

| 7-6-A: Conversion Type A Transfer Cycle with ISA and E-ISA<br>Memory (16 Data Bit Memory to 32 Data Bit I/O Example)<br>DMA Controller and Platform Circuitry Viewpoint<br>(EISA Compatible Platform Only)                 |

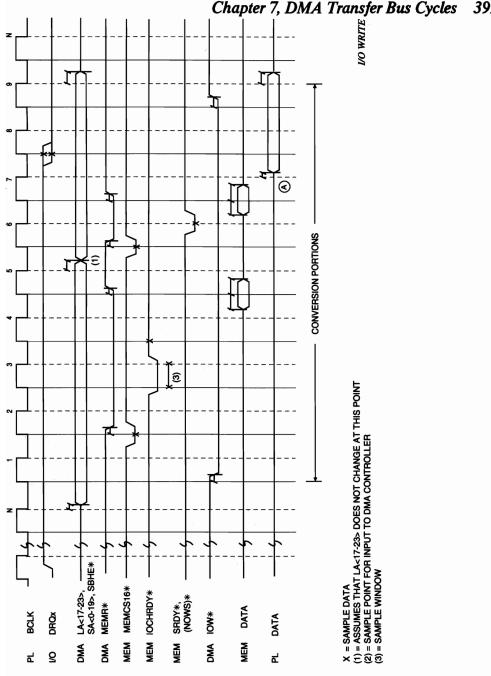

| 7-6-B: Conversion Type A Transfer Cycle with EISA<br>Memory (16 Data Bit Memory to 32 Data Bit I/O Example)<br>DMA Controller and Platform Circuitry Viewpoint          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (EISA Compatible Platform Only)                                                                                                                                         |

| 7-7-A: Conversion Type B Transfer Cycle with ISA and E-ISA<br>Memory (16 Data Bit Memory to 32 Data Bit I/O Example)<br>DMA Controller and Platform Circuitry Viewpoint |

| (EISA Compatible Platform Only)                                                                                                                                         |

| 7-7-B: Conversion Type B Transfer Cycle with EISA                                                                                                                       |

| Memory (16 Data Bit Memory to 32 Data Bit I/O Example)                                                                                                                  |

| DMA Controller and Platform Circuitry Viewpoint                                                                                                                         |

| (EISA Compatible Platform Only)                                                                                                                                         |

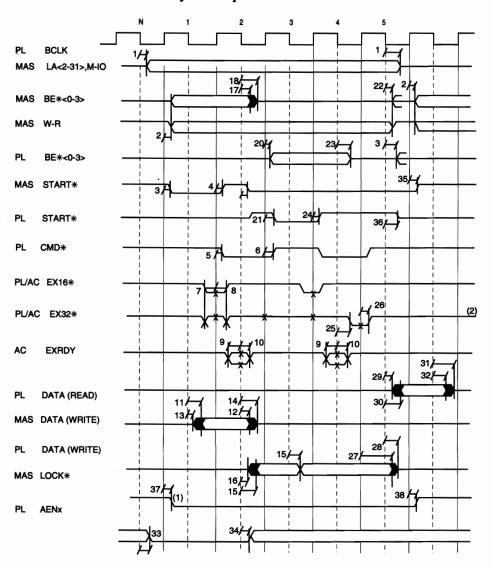

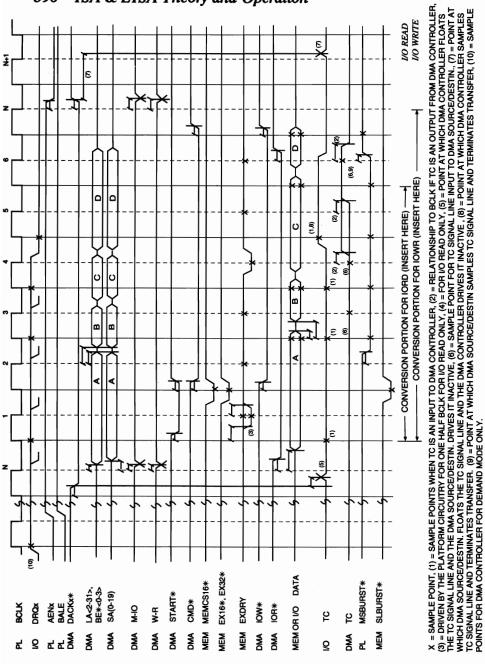

| 7-8-A: EISA Standard and Ready Type C (Burst) Transfer Cycle                                                                                                            |

| DMA Controller and Platform Circuitry Viewpoint                                                                                                                         |

| (EISA Compatible Platform Only)                                                                                                                                         |

| 7-8-B: EISA Standard and Ready Type C (Burst) Transfer Cycle                                                                                                            |

| DMA I/O (Add-On Slave Card) Resource Viewpoint                                                                                                                          |

| (EISA Compatible Platform Only)                                                                                                                                         |

| 7-9-A: EISA Standard and Ready Type C (Burst) Transfer Cycle<br>With Conversion With ISA and E-ISA Memory (16 Data Bit Memory                                           |

| to 32 Data Bit I/O Example) DMA Controller and Platform                                                                                                                 |

| Circuitry Viewpoint (EISA Platform Only)403                                                                                                                             |

| 7-9-B: EISA Standard and Ready Type C (Burst) Transfer Cycle                                                                                                            |

| With Conversion With EISA Memory (16 Data Bit Memory                                                                                                                    |

| to 32 Data Bit I/O Example) DMA Controller and Platform                                                                                                                 |

| Circuitry Viewpoint (EISA Platform Only)404                                                                                                                             |

| 7-10-A: EISA Standard and Ready Type C (Burst) Transfer Cycle                                                                                                           |

| With Conversion With ISA and E-ISA Memory (16 Data Bit Memory                                                                                                           |

| to 32 Data Bit I/O Example) DMA Controller and Platform                                                                                                                 |

| Circuitry Viewpoint (EISA Platform Only)405                                                                                                                             |

| 7-10-B: EISA Standard and Ready Type C (Burst) Transfer Cycle                                                                                                           |

| With Conversion With EISA Memory (16 Data Bit Memory                                                                                                                    |

| to 32 Data Bit I/O Example) DMA Controller and Platform                                                                                                                 |

| Circuitry Viewpoint (EISA Platform Only)406                                                                                                                             |

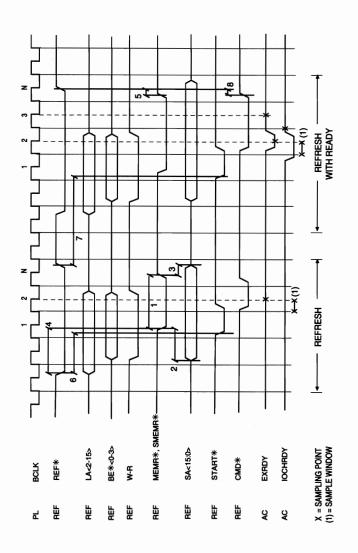

| 8-1: Refresh Cycle Timing                                                                                                                                               |

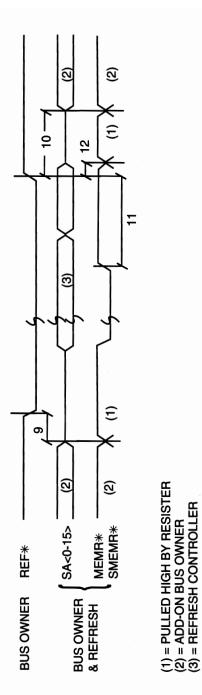

| 8-2: ISA and E-ISA Add-On Bus Owner Card Refresh Request                                                                                                                |

| 9-1: ISA and E-ISA Add-On Bus Owner Card Arbitration Protocol |

|---------------------------------------------------------------|

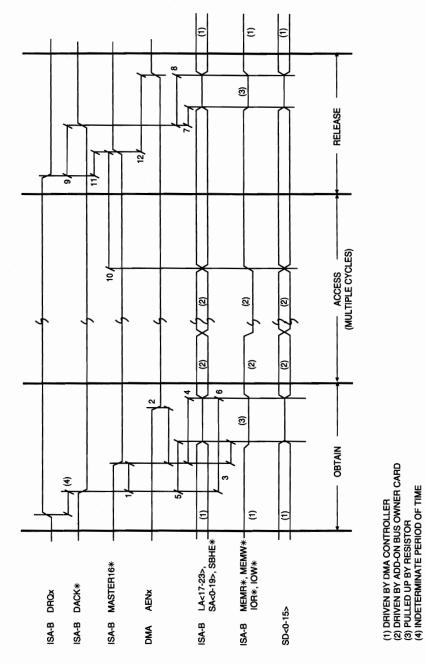

| 9-2: EISA Add-On Bus Owner Card Arbitration Protocol          |

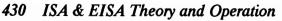

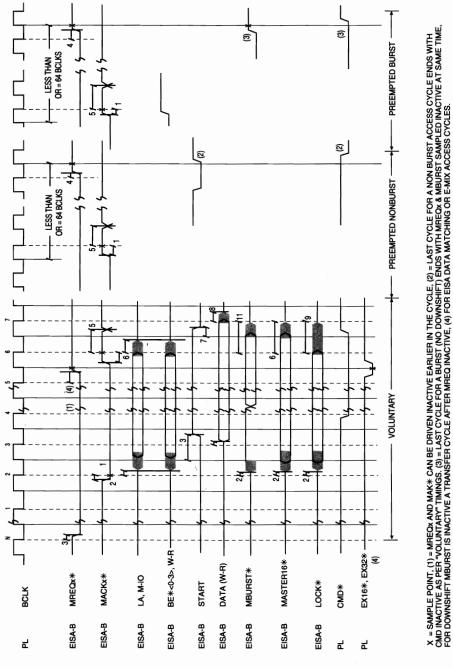

| 9-3: EISA Compatible Platform Arbitration                     |

| 9-4: CAC Operation with Fixed DMA Channel Priority            |

| 9-5: CAC Operation with Rotating DMA Channel Priority         |

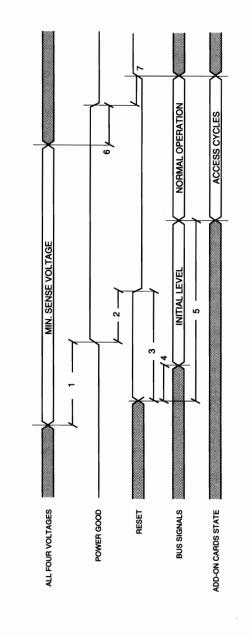

| 13-1: Power On Sequence                                       |

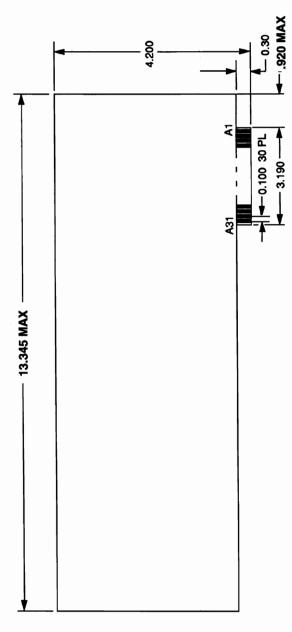

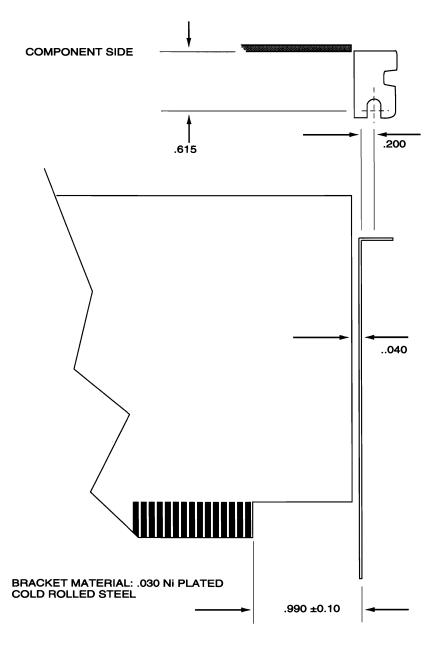

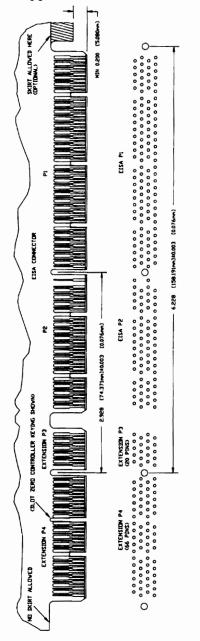

| 14-1: ISA Bus Pin Identification                              |

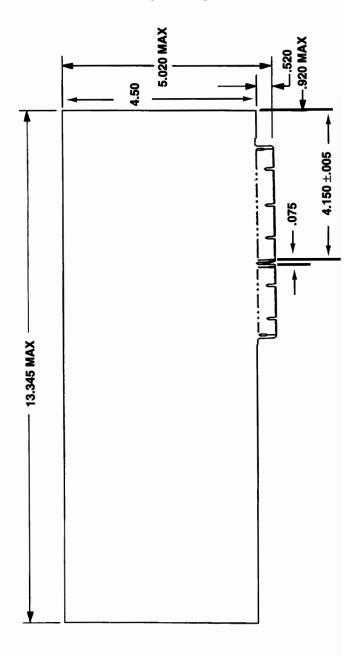

| 14-2: ISA 8 Bit Add-On Card Configuration                     |

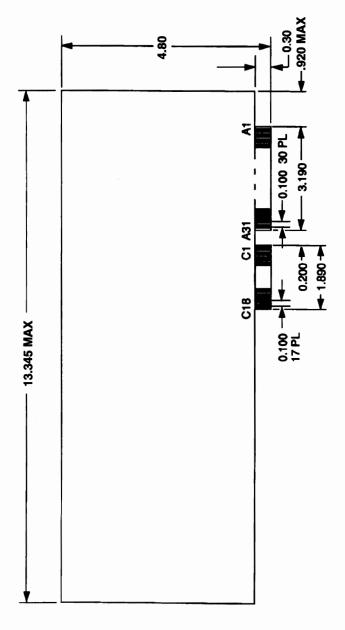

| 14-3: ISA 8/16 Bit Add-On Card Configuration                  |

| 14-4: ISA and EISA Card Bracket Mounting Position             |

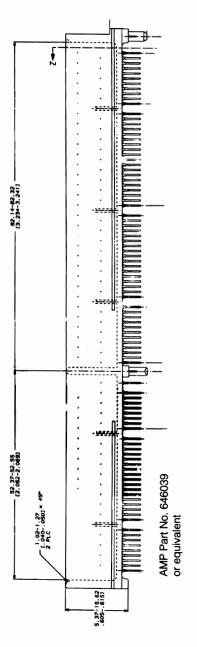

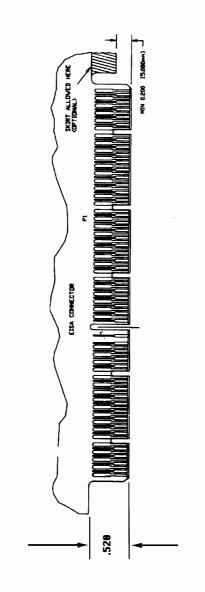

| 14-5: EISA Bus Pin Identification                             |

| 14-6: EISA Add-On Card Configuration                          |

| 14-7: EISA Connector Detail                                   |

| 14-8: EISA Card Edge Detail                                   |

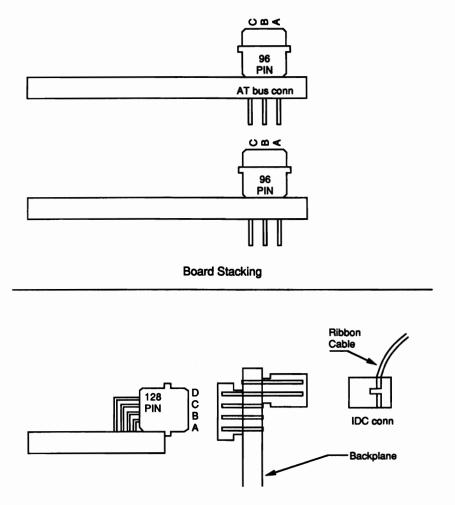

| B-1: PC/96 Pin Identification                                 |

| B-2: PC/96 Backplane Stacking Methods                         |

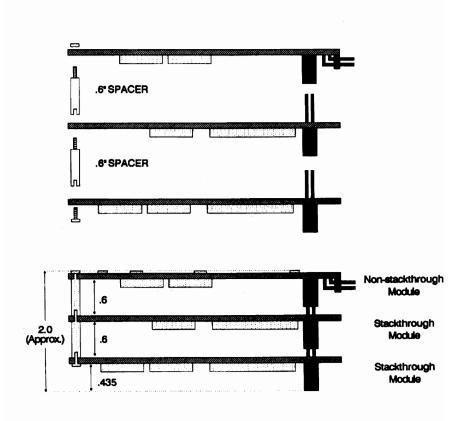

| C-1: PC/104 Typical Module Stack                              |

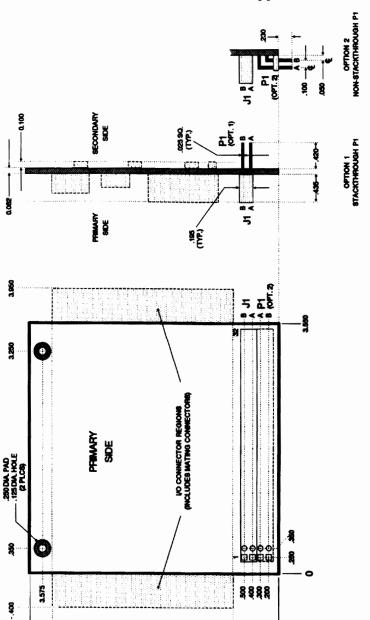

| C-2: PC/104 8 Bit Module Dimensions                           |

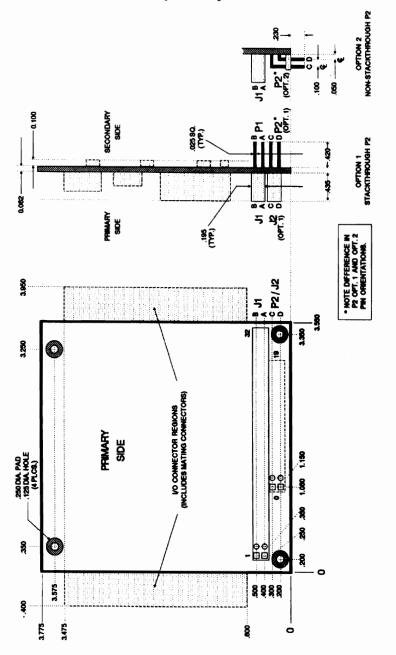

| C-3: PC/104 16 Bit Module Dimensions                          |

| C-4: PC/104 Bus Signal Assignments                            |

| D-1: Slot 0 and P3/P4 Card-Edge Connector                     |

| D-2: Slot 0 Pinout                                            |

| D-3: Non-Slot 0 Pinout                                        |

# List of Tables

| 1-1: General Platform Features                                                                                                                                           | 14 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1-2-A: Add-On Card Support on PC, XT, AT, or E-ISA Platforms.<br>Platform CPU Data Size Less Than or Equal To Accessed<br>Resource Data Size                             | 17 |

| 1-2-B: Add-On Card Support on PC, XT, AT, and E-ISA Platforms.<br>Platform CPU Data Size Greater Than Accessed Resource<br>Data Size                                     | 18 |

| 1-3-A: Add-On Card Support. Add-On Bus Owner Card Data Size<br>Less Than or Equal To Accessed Resource Data Size                                                         | 19 |

| 1-3-B: Add-On Card Support. Add-On Bus Owner Card Data Size<br>Greater Than Accessed Resource Data Size                                                                  | 19 |

| 1-3-C: Add-On Bus Owner Card Cycle Support. Add-On Bus Owner<br>Card Data Size Less Than or Equal To Accessed Resource Data Size                                         | 20 |

| 1-3-D: Add-On Bus Owner Card Cycle Support. Add-On Bus Owner<br>Card Data Size Greater Than Accessed Resource Data Size                                                  | 20 |

| 1-4-A: EISA Bus Master Cycle Support. Data Size Requested (BE*)<br>Less Than or Equal To Accessed Resource Data Size<br>(MEMCS16*, IOCS16*, EX16*, and EX32*)            | 21 |

| 1-4-B: EISA Bus Master Cycle Support. Bus Master Data Size<br>Requested (BE*) Less Than or Equal To Accessed Resource Data<br>Size (MEMCS16*, IOCS16*, EX16*, and EX32*) | 22 |

| 1-4-C: EISA Bus Master Cycle Support. Bus Master Data Size<br>Requested (BE*) Greater Than Accessed Resource Data Size<br>(MEMCS16*, IOCS16*, EX16*, and EX32*)          | 22 |

| 1-4-D: EISA Bus Master Cycle Support. Bus Master Data Size<br>Requested (BE*) Greater Than Accessed Resource Data Size<br>(MEMCS16*, IOCS16*, EX16*, and EX32*)          | 23 |

| 1-5-A: PC, XT, AT, and E-ISA Platform DMA Transfer Cycles                                                                                                                | 24 |

| 1-5-B: EISA Platform DMA Transfer Cycles                                                                                                                                 | 25 |

| 3-1-A: PC, XT, ISA, and E-ISA Platform Access Cycles<br>All Data Sizes                                                                                                   | 42 |

| 3-1-B: All EISA Platform Access Cycles Bus Master Requested<br>Data Size is Equal To or Less Than Accessed Resource Data Size45 |

|---------------------------------------------------------------------------------------------------------------------------------|

| 3-1-C: All EISA Platform Access Cycles Bus Master Requested<br>Data Size is Greater Than Accessed Resource Data Size47          |

| 3-2: ISA Compatible Platform DMA Transfer Cycles                                                                                |

| 3-3: E-ISA Compatible Platform DMA Transfer Cycles                                                                              |

| 3-4: EISA Compatible Platform DMA Transfer Cycles82                                                                             |

| 4-1: ISA and E-ISA Add-On Slave Card as Memory Resource                                                                         |

| 4-2: ISA and E-ISA Add-On Slave Card as I/O Resource108                                                                         |

| 4-3: Byte Swapping for Access Cycles to ISA and E-ISA Add-On<br>Slave Cards                                                     |

| 4-4: ISA and E-ISA Add-On Slave Card as I/O Resource<br>(Data Destination) for Transfer Cycles112                               |

| 4-5: ISA and E-ISA Add-On Slave Card as I/O Resource<br>(Data Source) for Transfer Cycles112                                    |

| 4-6: ISA and E-ISA Add-On Slave Card as Memory Resource<br>(Data Destination) for Transfer Cycles112                            |

| 4-7: ISA and E-ISA Add-On Slave Card as Memory Resource<br>(Data Source) for Transfer Cycles113                                 |

| 4-8: Byte Swapping for ISA and E-ISA Compatible<br>Memory and I/O Resources for Transfer Cycles115                              |

| 4-9: EISA Add-On Slave Card as Memory Resource124                                                                               |

| 4-10: EISA Add-On Slave Card as I/O Resource                                                                                    |

| 4-11: DMA Transfer Cycles on EISA Compatible Platforms                                                                          |

| 5-1-A: ISA and E-ISA Signal Line Overview136                                                                                    |

| 5-1-B: ISA and E-ISA Signal Line Overview136                                                                                    |

| 5-1-C: ISA and E-ISA Signal Line Overview                                                                                       |

| 5-1-D: ISA and E-ISA Signal Line Overview137                                                               |

|------------------------------------------------------------------------------------------------------------|

| 5-1-E: ISA and E-ISA Signal Line Overview137                                                               |

| 5-2-A: ISA, E-ISA, and EISA Signal Line Overview138                                                        |

| 5-2-B: ISA, E-ISA, and EISA Signal Line Overview138                                                        |

| 5-2-C: ISA, E-ISA, and EISA Signal Line Overview                                                           |

| 5-2-D: ISA, E-ISA, and EISA Signal Line Overview139                                                        |

| 5-2-E: ISA, E-ISA, and EISA Signal Line Overview140                                                        |

| 5-3: Conversion of BE* Signal Lines to SA0, SA1, and SBHE*<br>Signal Lines on EISA Compatible Platforms149 |

| 5-4: Conversion of SA0, SA1, and SBHE* Signal Lines to BE*<br>Signal Lines on EISA Compatible Platforms150 |

| 5-5: Connector Current                                                                                     |

| 6-1-A: Access Cycle Timings Platform CPU or ISA Bus Owner<br>Add-On Card                                   |

| 6-1-B: Access Cycle Timings Accessed Resource (Platform and<br>Add-On Slave Card)195                       |

| 6-2: ISA and E-ISA Platform Memory Cycle Data Size                                                         |

| 6-3: ISA and E-ISA Platform Standard Memory Access Cycle Length205                                         |

| 6-4: ISA and E-ISA Platform I/O Access Cycle Data Size211                                                  |

| 6-5: ISA and E-ISA Platform Standard I/O Access Cycle Length212                                            |

| 6-6: ISA and E-ISA Platform Minimum Ready Memory Access<br>Cycle Length219                                 |

| 6-7: ISA and E-ISA Platform Minimum Ready I/O Access Cycle Length221                                       |

| 6-8: ISA Platform No-wait-state Memory Access Cycle Length                                                 |

| 6-9: E-ISA Platform No-wait-state Memory Access Cycle Length225                                            |

| 6-10-A: ISA Platform No-wait-state I/O Access Cycle Length                                                 |

| (                                                                                                                                                        | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6-10-B: E-ISA Platform No-wait-state I/O Access Cycle<br>Minimum Length                                                                                  | 229  |

| 6-11-A: EISA Specific Access Cycle Bus Master Viewpoint<br>(Platform CPU, EISA Compatible Add-On Bus Owner Card<br>or Platform Circuitry)                | 234  |

| 6-11-B: EISA Specific Access Cycle Accessed Resource Viewpoint<br>(Platform Resources or Add-On Slave Card)                                              | 237  |

| 6-12: EISA Platform Write EISA Standard or Ready Access Cycle<br>Byte Lanes. Data Size Requested Less Than or Equal To<br>Data Size of Accessed Resource | 244  |

| 6-13: EISA Platform Read EISA Standard or Ready Access Cycle<br>Byte Lanes. Data Size Requested Less Than or Equal To<br>Data Size of Accessed Resource  | 245  |

| 6-14: EISA Specific EISA Standard Access Cycle Length                                                                                                    | 246  |

| 6-15: EISA Specific Minimum EISA Ready Access Cycle Length                                                                                               | 251  |

| 6-16: EISA Specific Data-Matching Access Cycle EISA Bus Master<br>Viewpoint (Platform CPU or EISA Compatible Add-On<br>Bus Owner Card)                   | 256  |

| 6-17: EISA Platform Write Data-Matching Access Cycle Byte Lanes                                                                                          | 262  |

| 6-18: EISA Platform Read Data-Matching Access Cycle Byte Lanes                                                                                           | 262  |

| 6-20-A: EISA Specific Compressed Access Cycle Bus Master<br>Viewpoint (Platform CPU Only)                                                                | 268  |

| 6-20-B: EISA Specific Compressed Access Cycle Accessed Resource<br>Viewpoint (Add-On Slave Card)                                                         | 270  |

| 6-21: EISA Platform EISA Compressed Access Cycle Length                                                                                                  | 278  |

| 6-21-A: EISA Specific Burst Access Cycle Bus Master Viewpoint<br>(Platform CPU or EISA Compatible Add-On Bus Owner Card)                                 | 283  |

| 6-21-B: EISA Specific Burst Access Cycle Accessed Resource<br>Viewpoint (EISA Compatible Platform or Add-On Slave Card)                                  | 285  |

| 6-22: EISA Platform Write EISA Burst Access Cycle Byte Lanes                                                                                             | 295  |

| 6-23: EISA Platform Read EISA Burst Access Cycle Byte Lanes                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 6-24: EISA Platform E-MIX Version of the EISA Standard Write<br>Access Cycle Byte Lanes                                                            |

| 6-25: EISA Platform E-MIX Version of the EISA Standard Read<br>Access Cycle Byte Lanes                                                             |

| 6-11-B Addendum: E-MIX Access Cycle to an 8 Data Bit EISA I/O<br>Resource Accessed Resource Viewpoint (Platform Resources<br>or Add-On Slave Card) |

| 6-26: EISA Platform E-MIX Data-Matching Write Access Cycle<br>Byte Lanes                                                                           |

| 6-27: EISA Platform E-MIX Data-Matching Read Access Cycle<br>Byte Lanes                                                                            |

| 6-28: I-MIX Access Cycle Timings                                                                                                                   |

| 6-29: EISA Bus Master Back to Back Timing                                                                                                          |

| 6-30: ISA or E-ISA Bus Master Back to Back Timing                                                                                                  |

| 7-1-A: Compatible Transfer Cycle Timings                                                                                                           |

| 7-1-B: Type A and B Transfer Cycle Timings                                                                                                         |

| 7-3: Cycle Length of Standard Transfer Cycles                                                                                                      |

| 7-4: ISA Compatible Platform DMA Transfer Cycles                                                                                                   |

| 7-5: Additional Transfer Cycle Timing Relationships on<br>E-ISA and EISA Compatible Platforms                                                      |

| 7-6: E-ISA Platform DMA Transfer Cycles                                                                                                            |

| 7-7: Cycle Length of Ready Transfer Cycles                                                                                                         |

| 7-8: EISA Compatible Platform Transfer Cycles                                                                                                      |

| 7-9: TYPE C (Burst) Transfer Cycle Timings                                                                                                         |

| 8-1: Refresh Cycles418                                                                                                                             |

| 8-2: Refresh Address Mapping                                                                                                                       |

| 9-1: ISA and E-ISA Add-On Bus Owner Card Arbitration Protocol                                    | 426             |

|--------------------------------------------------------------------------------------------------|-----------------|

| 9-2: EISA Add-On Bus Owner Card Arbitration Protocol                                             | 431             |

| 10-1: ISA, E-ISA, and EISA Platform and Slot Interface                                           | 442             |

| 10-2: Output Current Requirements                                                                |                 |

| 10-3-A: Output Driver Types for ISA, E-ISA, and EISA                                             | 445             |

| 10-3-B: Output Driver Types, EISA Specific                                                       | 445             |

| 11-1: ISA and E-ISA Platform CPU Access to ISA or E-ISA<br>Slave Memory Access Performance       | 451             |

| 11-2: ISA and E-ISA Platform CPU Access to ISA or E-ISA<br>Slave I/O Access Performance          | 452             |

| 11-3: ISA and E-ISA Add-On Bus Owner Card Access to ISA or E-ISA<br>Slave Memory Performance     | 4<br><i>452</i> |

| 11-4: ISA and E-ISA Add-On Bus Owner Card Access to ISA or E-ISA<br>Slave I/O Access Performance |                 |

| 11-5: EISA Bus Master Access to EISA Memory Performance                                          | 452             |

| 11-6: EISA Bus Master Access to EISA I/O Performance                                             | <b>4</b> 53     |

| 11-7: Compatible Transfer Performance                                                            | 453             |

| 11-8: Type A Transfer Performance                                                                | <b>4</b> 53     |

| 11-9: Type B Transfer Performance                                                                | 452             |

| 11-10: Type C Transfer Performance                                                               | 454             |

| 13-1: Power Per Slot                                                                             |                 |

#### Foreword

When we published Ed Solari's first book "AT Bus Design" in early 1990, the PC revolution had been under way for over eight years. And for all of those years, clones and add-on cards had been designed by hundreds of designers working without a formal and uniform specification. Millions of PCs and tens of millions of addin cards were produced, sold to the masses, installed usually by amateurs, and, in spite of the nearly limitless number of possible combinations, the resulting systems almost always worked. Truly a tribute to the conservative original designers at IBM, and to the idea of an open architecture. Unfortunately, however, not quite so open as to provide engineers with everything they needed to know. So let's also have a round of applause for all the nervous designers betting their company on their reverse engineering talents!

As the performance demands on the PC grew, designs became less and less conservative. The need for publicly available specifications grew as the bus speed increased and the timing tolerances became tighter. One result was the formation of the IEEE 996 committee, which reverse engineered the newly-named Industry Standard Architecture (ISA) bus so that a uniform standard could be published. And since Solari and Annabooks came out with "AT Bus Design" we have shipped thousands of copies to over 60 countries.

The Extended Industry Standard Architecture (EISA) bus is being formally specified from the start, as is necessary for a higherperformance bus. And an important consideration is backwards compatibility to the ISA bus. So while the pure 32 bit portion of the EISA bus (or 64 bits for Fast EISA) holds promise for a fresh, pristine architecture, the important requirement for ISA compatibility adds a great deal of complication. Which brings us to this book.

There are now, and probably always will be, more ISA designs in progress than EISA designs. Just the growth in popularity of ISA compatibility for embedded systems practically guarantees this. So we don't want to force the ISA designer to extract from the EISA specification the information he needs to produce his design. On the other hand, we didn't want to keep "AT Bus Design" in print. The reason is that Ed wants to present ISA in an improved way, more consistent with the way in which EISA is presented. So aside from correcting a few errors in the original book, the most important consideration is a slightly different, more consistent, and better organized presentation.

The first part of each chapter covers ISA, so the ISA designer shouldn't have too much concern with the rest of the material until it is needed. The remainder of each chapter concerns E-ISA (8 and 16 bit systems that use some of the EISA features) and EISA. Much of the remaining detail involves the mixture of 8, 16, 24, and 32 bit platforms and resources. We've tried to bring order to the bewildering array of possibilities.

As Ed points out in the Preface, there are actually two sets of numbers presented in this book. It should always be clear which direction the conservative designer should go. When adequate time has not been allowed for bus settling times, Ed says so, and suggests an appropriate number. And if the designer uses a different pull-up value or has a different capacitive load, the effect should be evident. The important thing is to build stuff that works.

It's been a pleasure to work with Ed on such a challenging subject. His productivity and attention to detail are amazing. And we've also been impressed, along with the students, by his classes at Annabooks University. The direct feedback we get from you, the designer, is valuable in organizing material for presentation in person or in a book. So we all benefit from your comments. Please let us hear from you.

John P. Choisser Annabooks San Diego, California

#### Preface

The ISA bus, based on the IBM AT, continues to dominate the personal computer platform architecture. As more power is needed for network servers and workstations, some platforms are implementing the Enhanced ISA (EISA) bus as an extension of the ISA bus. The widening use of these two busses requires solid bus specifications. The lack thereof is the key motivation for writing this book.

The ISA bus at first evolved without any generally-available written specifications, in spite of the highly desirable open nature of the architecture. The IEEE 996 committee and my previous book "AT Bus Design" attempted to document the architecture, timing, and mechanical specifications to promote the compatible design of ISA platforms and add-on cards. The early versions of the EISA bus specification from COMPAQ also attempted to document the ISA bus, as well as the enhancements added to form the EISA bus. This book represents the next step in documenting both the ISA and EISA busses. It corrects errors in the IEEE 996 specification that "AT Bus Design" was based upon and clarifies the bus operation as outlined in both my previous book and the COMPAO EISA specification. In addition, this book provides missing information in the EISA specification to insure proper operation of EISA or ISA add-on cards installed in EISA compatible platforms.

You will notice that this book contains two sets of A.C. bus timings. One set is from the EISA Rev. 3.12 bus specification. This specification does not always indicate if the timings were based on an 8.00 or 8.33 MHz bus clock, does not always include sufficient bus settling time, and, in some cases, is overly restrictive in its A.C. timing requirements. Consequently, the other set of numbers represents a recalculation that includes bus settling, and includes entries for both 8.00 and 8.33 MHz bus clocks. Also, where the EISA bus specification was unclear, too restrictive, or incomplete, the recalculations have used the Intel 350DT chip set timings as the defacto standard. (After all, in some ways the EISA standard has been guided by the implementation of the bus by the Intel chip set.)

Both Annabooks and I are interested in the continuing evolution, clarification, and corrections to this book. Please direct any related inputs to Annabooks.

Finally, special thanks to John Choisser of Annabooks for the editing and data transcription. Also special thanks to Phil Vargas of Designline Creative Services for the graphics and jacket design.

Ed Solari Monmouth, Oregon

## CHAPTER ONE

# ARCHITECTURAL OVERVIEW

#### **INTRODUCTION**

There are now three basic iterations of the IBM Personal Computer: the original PC, the XT, and the AT. The platform CPU for the PC and XT is the 8 bit Intel 8088, and for the AT it is the 16 bit Intel 80286. The platforms vary in other ways besides the processor, such as memory capacity, existence of an audio cassette interface, and the number of slots for the add-on cards. There are two versions of the add-on card slots: the 8 bit slots on the PC and XT, and the 8 and 8/16 bit slots on the AT.

The PC and XT both use the Intel 8284A chip for clock generation, the Intel 8288 chip for bus control, a 4.77 MHz platform CPU and bus clock, and the Intel 8237A-5 DMA controller. The operation of the 8 bit slots on the two platforms is identical, and establishes the standard 8 bit compatibility for processor access cycles and DMA transfer cycles. Both platforms use one of the DMA channels to execute refresh cycles on the bus.

The AT differs from the PC and XT in other ways besides processor type and the data width of the bus slots. First, the AT uses the Intel 82284 chip for clock generation and the Intel 82288 chip for bus control. Second, the AT comes in two versions with two different system and platform CPU clocks: 6 and 8 MHz. Third, additional DMA channels and interrupt signal lines are present on the bus. Fourth, add-on cards can replace the platform CPU as the bus owner. Fifth, an additional signal line is available to support faster no-wait-state cycles. Finally, the refresh cycle execution by the DMA controller on the PC and XT is replaced by discrete circuitry.

The differences in the AT relative to the PC and XT are further complicated because companies other than IBM have replaced the platform CPU with the Intel 80386 or 80486 CPUs. The use of these CPUs eliminates the use of the Intel bus controller and clock generation chips, and permits the use of other platform CPU clock frequencies.

Compaq has introduced a further extension of the IBM Personal Computer. This extension supports all PC, XT, and AT hardware (add-on cards) and software. Additionally, it supports an enhancement for a bus width of 32 data bits in a 32 bit address space.

In order to permit the development of add-on cards in some reasonable fashion, the IEEE, Intel, and a consortium of companies (lead by Compaq) have developed three sets of bus specifications. The IEEE and Intel have focused on the 8 and 8/16 bit slots of the AT as the standard. The COMPAQ-led consortium also focused on the 8 and 8/16 bit slots of the AT as part of its expanded 32 bit standard.

This book is focused on the PC, XT, and AT bus requirements established by IBM and the expanded 32 bit bus established by the COMPAQ-led consortium. The generic name for the 8 bit and 8/16 bit PC, XT, and AT compatible bus is INDUSTRY STANDARD ARCHITECTURE (ISA). This book will also focus on the 32 bit extension to the ISA standard developed by the COMPAQ-led consortium known as the EXTENDED INDUSTRY STANDARD ARCHITECTURE (EISA).

In developing the EISA bus specification, the COMPAQ-led consortium added features beyond the increase of the data and address width. Some of these features can be used by ISA platforms that only support 8 and 8/16 bit slots. Thus, for the purposes of this book, the following definitions will be used:

ISA refers to the PC, XT (8 slot), and AT compatible (8 or 8/16 slot) bus specification. It does not use any of the enhancements of the EISA bus specification, and does not have the extra connector pins to support the enhanced 32 data bit EISA bus.

An E-ISA platform is the same as an ISA platform, except it includes those EISA enhancements that do not require EISA cycles or the additional pins of the 8/16/32 bit EISA slots. An E-ISA platform can be viewed as the 8 and 8/16 bit slots of an EISA platform that uses only ISA compatible signal lines.

An EISA platform conforms to the full EISA bus specification, which includes all of the ISA and E-ISA features. It also contains extra circuitry and connector pins to support EISA cycles and 8, 8/16, and 8/16/32 bit EISA slots. In that the additional signal lines needed to support EISA are not included in the 8 and 8/16 bit slots, by definition these slots are E-ISA compatible.

Finally, by definition, the references to ISA compatible signal lines also apply to E-ISA.

## **ISA COMPATIBLE PLATFORM**

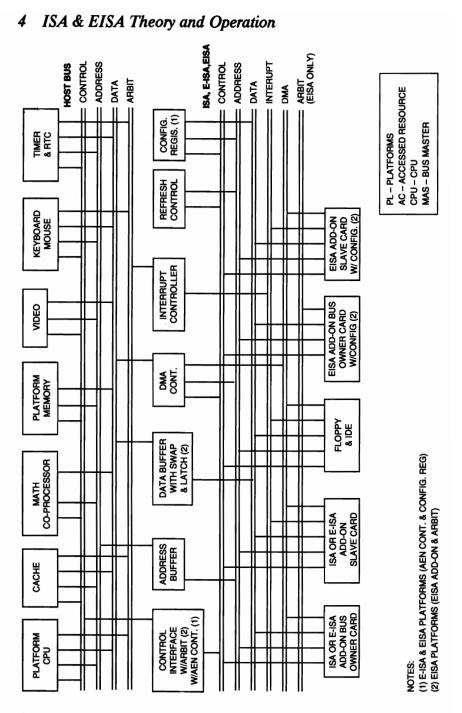

The ISA platform is the basic model for all PC, XT, and AT platforms. (See Figure 1-1.) The basic platform consists of the following:

#### **HOST BUS**

This is the generic bus for all platform resources (i.e. the resources not attached via the connectors on the ISA bus). On most systems, the Host bus consists of several busses; usually the platform CPU and cache are one bus, the platform memory another, and the balance of the resources are on a third bus.

FIGURE 1-1: ISA, E-ISA, & EISA PLATFORM

## ISA BUS

This is a set of connectors interconnected by the ISA bus signal lines. Each connector site is called a slot. Two types of connectors can reside at each slot: 8 bit and 8/16 bit. The 8 bit slot is a single 62 pin connector, and only supports 8 bit add-on slave cards. The 8/16 bit slot contains both the 8 bit slot 62 pin connector and an additional 36 pin connector. This expanded connector supports a larger address space, additional DMA channels, additional interrupt request lines, and additional data lines. The expanded connector also allows add-on bus owner cards to be used. PC and XT compatible platforms only support the 8 bit slot (62 pin connector).

## PLATFORM CPU

This is the primary CPU of the platform. It is the first bus owner after power up and after every reset. All other bus owners must obtain bus ownership by halting code execution by the platform CPU. It is directly tied to the clock circuitry which drives the bus clock; consequently, it is the only resource that can use the no-wait-state access cycles. For software compatibility, it must be compatible to the Intel 8088, 80286, 80386, 80486, X86 family of processors.

## MATH CO-PROCESSOR

This resource is a companion to the platform CPU. It is an option that computes math-related functions faster than the platform CPU. It is invisible to the slot in terms of bus cycles. In some of the more advanced Intel processors, it is integrated into the platform CPU.

## CACHE

This is a high speed memory resource accessible only by the platform CPU.

## **MEMORY**

Memory resources can exist either on the platform or on the bus as an add-on slave card. Platform memory can be of any byte width compatible to the platform CPU. The data width of the addon memory slave card does not have to match the platform CPU. Circuitry exists to compensate for data size mismatches. Conversely, the data size for bus owner add-on cards accessing the platform memory does not have to match the data size of the platform memory. Platform memory is commonly implemented with DRAM.

### DMA CONTROLLER

This is one of the platform resources that can become system owner. Its purpose is to transfer data between I/O and memory resources with minimum circuitry needed by either resource. It is the only resource on the bus that monitors the DMA signal lines on the bus. An active DMA request signal line will cause the DMA controller to obtain bus ownership and execute transfer cycles.

On an ISA or E-ISA platform, the DMA controller also operates as the arbiter for the system ownership by the platform CPU, DMA controller, refresh controller, and add-on bus owner cards.

#### **REFRESH CONTROLLER**

This is one of the other platform resources that can become system owner. Its purpose is to execute refresh cycles for platform and bus memory components. On the PC and XT it is actually a DMA channel 0 cycle. On the AT, E-ISA and EISA compatible platforms it is composed of separate dedicated circuitry.

## INTERRUPT CONTROLLER

This platform resource supports all of the bus interrupt request signal lines. The software can enable or disable individual interrupt channels. An active interrupt signal line on an enabled channel generates an interrupt to the platform CPU, and provides information to identify which interrupt signal lines are active.

#### **KEYBOARD** and **MOUSE**

On the PC and XT platforms, the keyboard interface is handled by discrete circuitry. On the AT, E-ISA, and EISA compatible platforms, this function is provided by the Intel 8042 microcontroller with a built-in BIOS. Recent platforms have implemented the mouse interface using the Intel 8042.

#### VIDEO

There is a wide variety of video controllers that are software compatible. The reading and writing of registers and video memory creates a display on the user's CRT.

## TIMER and REAL TIME CLOCK (RTC)

These platform resources are needed for software compatibility and have no direct relationship with the ISA bus. The timer generates a pulse every 15.6 microseconds to the refresh circuitry to request a refresh cycle. The real time clock provides time and date information.

## **INTERFACE CIRCUITRY**

This circuitry consists of three parts: Control Interface, Address Buffer, and Data Buffer with Swap. The purpose of these platform resources are to interface the resources on the host bus with the resources on the ISA bus.

- Control Interface: Translates the Host Bus control lines protocol to the ISA bus control lines protocol and vice versa.

- Address Buffer: Buffers the address signal lines between the two buses.

- Data Buffer With Swap: Buffers the data signal lines between the two buses. It also contains the circuitry to swap data between the low and high byte lanes for data size mismatches.

## ADD-ON CARDS

The bus allows for the insertion of add-on cards. Add-on cards that only respond to access, transfer, or refresh cycles are defined as add-on slave cards. Add-on cards that can become bus owners are defined as add-on bus owner cards. An add-on card may be of both types; but, for a given bus cycle, it can only be either a bus owner or a slave.

ISA add-on slave cards will work on AT compatible platforms. The ISA 8 bit version of these cards will also work on PC and XT platforms.

Add-on bus owner cards can only be installed in AT compatible platforms of the ISA family.

## **E-ISA COMPATIBLE PLATFORM**

The lack of a generally available industrial standard for the AT bus, prior to the efforts of Intel, the IEEE P996 committee, and the EISA consortium, has resulted in the defacto ISA standard. Unfortunately, this defacto standard has had to reflect design errors in early platforms, misinterpretation of bus cycles, and other types of errors and inconsistencies. The operation of the 8 and 8/16 bit slots in a platform compatible with the EISA bus specification must maintain compatibility with the ISA standard, at the same time allowing the use of the enhancements outlined in the EISA bus specification. In order to differentiate between 8 and 8/16 bit slots on platforms that adhere to the ISA standard versus platforms and add-on cards that adhere to the full EISA bus specification, the concept of E-ISA compatible platforms and addon cards has been adopted.

THE E-ISA COMPATIBLE PLATFORM SHOULD BE VIEWED SIMPLY AS A CONCEPT. IT IS USED TO DISTINGUISH BETWEEN "HISTORICAL" ISA BUS PLATFORMS (PC, XT, and AT) AND THE "ENHANCED" ISA BUS (8 AND 8/16 BIT SLOTS CONFORMING TO THE EISA BUS SPECIFICATION).

An E-ISA compatible platform is conceptually the same as the ISA compatible platform. It only supports 8 and 8/16 bit slots, and is compatible with ISA add-on cards. However, it provides enhancements provided by the EISA bus specification that can be exploited by E-ISA compatible add-on cards.

An E-ISA add-on card is conceptually the same as an ISA addon card. It can function in ISA and E-ISA 8 and 8/16 bit slots, and can also be used in a platform that adheres to the full EISA bus specification.

The significance of an E-ISA compatible platform is that it is an enhanced ISA platform that only adopts the 8 and 8/16 "asynchronous" slots of the EISA bus specification. It does not

adopt the additional overhead of the full 8/16/32 "synchronous" slots of the EISA bus specification.

The enhancements of an E-ISA compatible platform or add-on card versus an ISA compatible platform or add-on card are as follows:

- Configuration space is supported.

- I/O space addressing is slot specific.

- Maximum frequency of the BCLK signal line is 8.33 MHZ.

- The INTERRUPT signal lines can be programmed for edge or level trigger. The level trigger provides the "ORING" of several interrupts on a single INTERRUPT signal line.

- The IOCHRDY and DRQx signal lines are referenced to the BCLK signal line.

- The SRDY\* signal line (permitting no-wait-state access cycles) can be supported by add-on bus owner cards.

- 8 data bit memory and I/O resources support an expanded definition of no-wait-state access cycles.

- Any DMA channel may be programmed for 8 or 16 bit transfers.

- Add-on I/O slave cards can support faster DMA transfer rates (TYPE A and TYPE B).

- The TC signal line is bi-directional.

## **CONFIGURATION SPACE**

Except for the Configuration Space, the above enhancements do not change the architecture of the platform or add-on cards. The Configuration Space consists of input and output registers within the I/O address space which are reserved for platform and add-on card configuration. These input and output registers allow software configuration and monitoring of hardware. (See Figure 1-1.)