# TONY DOWDEN Inside the FISSA DESCRIPTION

### **Inside the EISA Computers**

-----

# Inside the EISA Computers

### TONY DOWDEN

### \*\*

Addison-Wesley Publishing Company, Inc. Reading, Massachusetts Menlo Park, California New York

Don Mills, Ontario Wokingham, England Amsterdam Bonn Sydney Singapore Tokyo Madrid San Juan Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial capital letters.

#### Library of Congress Cataloging-in-Publication Data

Dowden, Tony Inside the EISA computers / Tony Dowden. p. cm. ISBN 0-201-52397-3 1. EISA (computer bus) 2. Computer architecture. I. Title. TK7895.B87D69 1990 621.39'16--dc20 90-14 CIP

Copyright © 1990 by Tony Dowden

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

Cover design by Doliber Skeffington Text design by Total Concept Associates Set in 11-point Century Schoolbook by Impressions Publishing Services

ISBN 0-201-52397-3 ABCDEFGHLJ-MW-9543210

First Printing, February 1990

This book is dedicated to the hundreds of hard-working engineers in the EISA consortium. They had a challenge: to forge on in the face of adversity and create a new bus, computers, and accessories that can answer the needs of computer users for years to come. They did it.

# Acknowledgments

Making acknowledgments in this book is a difficult task, because I am grateful to so many. I can only hope to acknowledge almost everyone and sincerely apologize to anyone I have omitted. None of you will ever be forgotten, and you will always be remembered with gratitude. The list is in no particular order for it is difficult to say that any one did any more than any other. Thanks to:

My wife, Patty, who tolerated the long hours required to do this book. Her suggestions were invaluable; without them this book would be far less than it is.

Gayle Dolby of Hewlett-Packard, who went far out of her way to assist me in securing clearance from the corporate powers to do this book.

Rich Archuletta, who first saw the value of a book like this. It was he who championed it through the EISA consortium, and acted as a buffer from the politics that accompanies an effort of this nature.

Alan VanWinkle and especially Eric Behnke of Hewlett-Packard, programmers of the highest caliber, who provided a great deal of assistance in the software sections of this book. Jon M. Greenwood and others of Micrografx, Inc. Their contribution of Micrografx Designer version 2.0 allowed me to do the artwork in this book far faster and better than I could have otherwise.

Behind every successful book is a publisher's staff, editors, and assistants, who make the book so much better with their efforts. To Julie Stillman, Carole McClendon, Beth Burleigh, Colleen Jensen, and so many others . . . thanks.

And last but not least, I must acknowledge the assistance of Gato (Attila the Fun), my Maine Coon cat. A gentle giant, he kept me company long after the rest of the family went to bed. It was he who always had praise, showing it with a purr at every opportunity. If only I could get him to sleep someplace other than the top of the laser printer.

## Contents

1

Preface xvii

### 1 Introduction

Notation and Conventions 4 The History of EISA 5 EISA Providers 8 Summary 10

### 2 Inside the EISA Computer 11

Central Processing Unit 14 The Binary Numbering System 15 The Hex Numbering System 16 Back to the CPU 18 RAM and ROM 19 I/0 20**EISA** Computer Hardware 21 The EISA Connector 22Card Size 27 The EISA Component Interface 28 82358 EISA Bus Controller 29 82357 Integrated System Peripheral 29 82352 EISA Bus Buffer 29 82355 Bus Master Interface Controller 30 30 Summarv

### **3** The Operating System

Software Architecture 33 BIOS 34 **Operating System** 37 **Application Software** 37 **DOS 4 Overview** 38 **DOS 4 File Structures** 39 **DOS 4 Enhancements** 39 DOS 4 Commands and Programs 41 Other File Types 48 config.sys 49 Autoexec.bat 51**Batch Files** 51Summary 53

### 4 The EISA Bus

**Bus Differences** 57Address and Data Bus Signals 59 **Data Transfer Control Signals** 60 **Bus Arbitration Signals** 62 Utility Signals 62 Signal Use 63 **EISA** Signals 63 **ISA** Signals 64

31

55

Connector Specifications 65 Summary 65

### 5 The EISA Interrupts, DMA, and I/O Structures

Interrupts 69 Interrupt Controller I/O Addresses 70 **Interrupt Sequence** 70 Non-Maskable Interrupts 71 Interval Timers 71 Direct Memory Access (DMA) 72 **ISA-Compatible Cycles** 72Type A Cycles 72 Type B Cycles 73 Burst DMA Cycles 73 Input/Output (I/O) 73

### 6 EISA Software

**EISA** Configuration 85 **Configuration Utility** 85 System Configuration Menu 86 Nonvolatile Memory 89 Configuration (CFG) Files 90 **CFG Filename Format** 90 **CFG File Format** 90 **Brief CFG Description** 91 **CFG File Examples** 93 **ISA Serial Board** 93 EISA Serial/Parallel Board 95 EISA VGA Video Board 98 **Overlay (OVL) Files** 99 **OVL** File Structure 100 **OVL** Example 101 **OVL** Functions 106 **OVL Function INIT** 106

67

119

OVL Function CHANGE106OVL Function UPDATE112OVL Memory Allocation112OVL Summary114Summary118

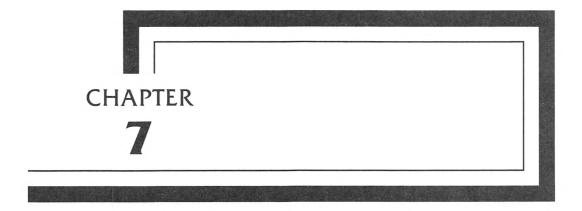

### 7 The VGA Video Interface

VGA General Description 121 **Compatibility Standards** 121 VGA Video Connector 122 Modes of Operation 123VGA Components 123Programming the VGA 124 **Register Definitions** 124**External Registers** 125Miscellaneous Output Register 125Feature Control Register 126 Input Status Register 0 126 Input Status Register 1 126 127 Sequencer Registers Sequencer Address Register 127**Reset Register** 127128 **Clocking Mode Register** Map Mask Register 129 Character Map Select Register 129 Memory Mode Register 130 **CRT** Controller Registers 130 Address Register 130Horizontal Total Register 131Horizontal Display Enable End Register 131 Start Horizontal Blanking Register 131 End Horizontal Blanking Register 131 Start Horizontal Retrace Pulse Register 132 End Horizontal Retrace Pulse Register 132 Vertical Total Register 132 **CRT** Controller Overflow Register 132Preset Row Scan Register 133

Maximum Scan Line Register 133Cursor Start Register 134 **Cursor End Register** 134 Start Address High Register 134 134 Start Address Low Register 135Cursor Location High Register Cursor Location Low Register 135Vertical Retrace Start Register 135135Vertical Retrace End Register Vertical Display Enable End Register 136 **Offset Register** 136 **Underline Location Register** 136 Start Vertical Blanking Register 137 End Vertical Blanking Register 137 Mode Control Register 137 138 Line Compare Register **Graphics Controller Registers** 138 138 Graphics Address Register Set/Reset Register 138 139 Enable Set/Reset Register Color Compare Register 139 139Data Rotate Register 140 Read Map Select Register Mode Register 140Miscellaneous Register 141 141 Color Don't Care Register Bit Mask Register 142 142**Attribute Controller Registers** Attribute Address Register 142**Palette Registers** 142 143 Mode Control Register 144 **Overscan** Color Register 144 Color Plane Enable Register Horizontal Pel Panning Register 144 Color Select Register 144 Using VGA BIOS Functions 145 Set Mode 145 Get Video State 145 Set Active Page 146

157

Set Cursor Type 146 Set Cursor Position 146 **Read Cursor Position** 147 Write Text Functions 147 Write Character and Attribute 147 Write Character Only Function 147 **Read Character and Attribute Function** 148 Write TTY Function 149 Write String Function 149 Scroll Up 150 Scroll Down 150 **Read Dot Function** 150 Write Dot Function 151 Set Color Palette Function 151 **Programming Examples** 152**Display a Character Using MS-DOS** 152**Display a Character String Using MS-DOS** 152**Display a Character Using BIOS** 154**Display a Character String Using BIOS** 155 Summary 156

### 8 Serial Data Communications

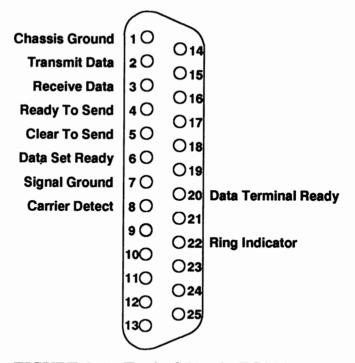

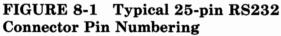

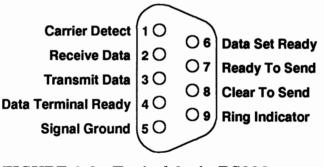

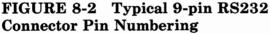

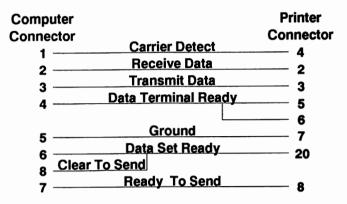

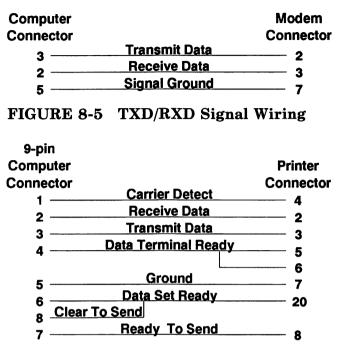

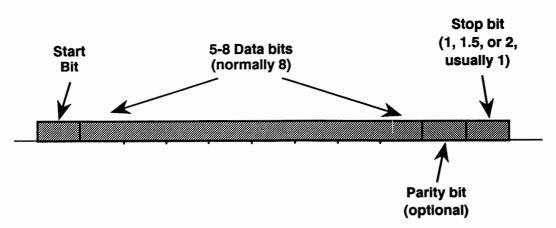

The Serial Connector 160 **RS-232C Signals** 162 **PG**–**Protective** Ground 164 **TXD**-Transmit Data 164 **RXD**-Receive Data 164 RTS-Ready To Send 164 CTS-Clear To Send 164 DSR-Data Set Ready 165SG-Signal Ground 165 DCD-Data Carrier Detect 165 **DTR-Data Terminal Readv** 165 **RI-Ring Indicator** 165 **Typical Communications** 166 **Connector Configurations** 167 Serial Data Format 171

Serial I/O Ports and Interrupts 173Serial Port Registers 173173Transmit Buffer Register 174 **Receive Buffer Register** 174 **Divisor Latch Registers** Interrupt Enable Register 175**Interrupt Identification Register** 176 Line Control Register 176 Modem Control Register 177 Line Status Register 178 180 Modem Status Register Serial Port BIOS Routines 180 INIT 181 XMIT 183 RECV 183 STATUS 184 EXTENDED\_INIT 184 **Programming Examples** 185 **Initialize Serial Port** 185 Read Serial Port Status 186 Send/Receive Character From Serial Port 187 189 Summary

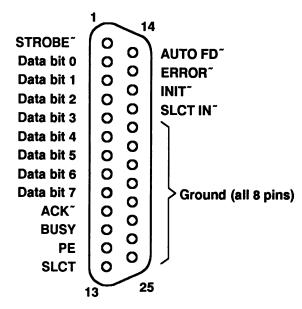

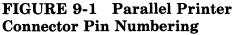

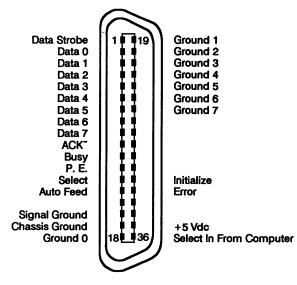

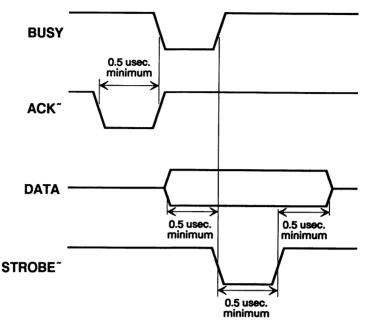

### 9 The Parallel Printer Connector 191

The Parallel Port Connector 193 **Parallel Printer Signals** 195 Signal Timing 195 Parallel Port Addresses/Registers 195 Data Register 198 Printer Control Register 198 **Printer Status Register** 199 Parallel Port BIOS Routines 200PUT\_CHAR 200 INIT 201 STATUS 201 **Programming Examples** 201Send Character to Printer 201

| Send Strip | ng to Printer | 204 |

|------------|---------------|-----|

| Summary    | 206           |     |

| 10 | The 80486 (i486) CPL                                                             | I   | 207 |

|----|----------------------------------------------------------------------------------|-----|-----|

|    | Compatibility 211<br>Segmentation Architecture<br>Coprocessor 212<br>Summary 213 | 212 |     |

|    | Glossary                                                                         |     | 215 |

|    | Appendix                                                                         |     | 221 |

|    | Index                                                                            |     | 227 |

### Preface

Today's personal computer is almost a decade old, a quite significant age in a time when changes and new technology pop up overnight, continuously replacing last week's innovations with newer and better innovations. The personal computer is just such a creature, with manufacturers announcing newer and faster versions, seemingly on a weekly basis. Indeed, it is doubtful that anyone can claim to have seen or used one of every model of personal computer that has been marketed in the last ten years.

Through this decade of change, one thing seemed to remain constant—the bus connectors inside the computer where accessory cards could be installed. These accessory cards enhanced the power of the computer, allowing it to use more and more peripherals, contain more memory (RAM and disk drives), and display more lines of more colors.

Over time, the bus went from a single connector with 8 data bits to a double connector with 16 data bits. This allowed more data to flow faster, and with that came the newer 16-bit processors with their faster clock speeds. Finally, IBM decided that the original bus was no longer serviceable and came out with a new computer using their MCA (Micro Channel Architecture) bus. This bus used entirely different connectors and, in fact, had an entirely different concept in accessory card implementation.

However, there were other companies who had large investments in the old bus and were not ready to abandon it. They felt it needed only an enhancement to bring it up to, and perhaps exceed, the performance of the MCA bus. Thus the EISA bus was born, a bus which fulfills the hope of performance exceeding the MCA bus while retaining the ability to use all of the existing cards.

Detractors from the EISA bus were against the enhanced standard, saying it was a "new" standard and the interests of the users would not be well served by yet another standard. The EISA bus is *not* a new standard that renders anything obsolete; it is a significant enhancement of the old standard.

Although this is one of its benefits, it is by no means the most significant benefit. When new computers are announced, there is often a lag of a year or more before significant numbers of expansion cards or compatible software are available for the new computer. With the EISA computer, the announcement of the first computers presents no such problem. Over 1,000 expansion cards are already available that are compatible with the EISA bus!

At the same time, the new EISA computers have room for expansion well beyond their present configurations. They are designed to accommodate processors currently available, such as the Intel 80486, and processors as yet unannounced or even conceived.

In writing this book, I became aware that the first of the EISA computers is not representative of the full power of the bus, but merely an introduction—a glimpse—into the incredible power that EISA-based computers will provide in the next decade.

## Introduction

Welcome to EISA, the computer architecture "for the rest of us." This book will guide you through the EISA computer from the perspective of a user, an engineer, and a programmer. A lot of information is contained in this book, some of it introductory-for the newcomer, and some of it technical-for the engineer. This book dissects the EISA computer, probing some of its secrets and learning about the source of its power.

And powerful it is. The EISA bus is an enhancement that will serve the computer community for many years, providing the platform upon which to build machines with as yet undreamed of power. It supports Intel processors from the 8086 to the 80486 and beyond. It also supports processors from other sources, such as the Motorola 68000 family. It can even run different processors simultaneously as multiple bus masters, and allow multiple users to simultaneously run different software packages and different operating systems, such as OS/2 and UNIX.

This book is your first step toward understanding the power of the EISA bus and the operation of EISA-based computers. From here, you can move on to learning more about computer architecture, hardware and software, or using applications programs. This book also serves as a basis for understanding the differences in the EISA architecture as offered by different manufacturers.

This book assumes that you have at least a small knowledge of computers. The more you know about computers in general, the easier it will be for you to grasp the concepts presented here. However, if you are a computer novice, you will still get a great deal of understanding and appreciation of the world of EISA.

Throughout this book, you will find terms like "usually" or "typically." I am not trying to be vague—that wouldn't be nice and authors are supposed to be nice. What I am doing, however, is to warn you that although the information presented in that specific area is both typical and accurate, different manufacturers may deviate in an effort to distinguish their equipment from the offerings of other manufacturers.

This book begins with a history of the EISA organization and then turns to an overview of the workings of an EISA computer, both hardware and software. The discussion is of a general nature, and a newcomer to the world of computers should have little trouble with the section. From there it jumps into the heart of the computer with a more technical discussion, revealing the workings of the EISA bus, the operation of associated hardware and software routines, and then on to EISA software. Following that, the loose ends are tied with a discussion of video and peripheral interfaces and the 80486 processor. A glossary, some handy reference tables, and an index round it out. Programming examples are included to help you understand some of the concepts presented, and you are free to use any of them in any way that may help you. Modifications may be required for them to execute on a particular system.

If you are looking for in-depth engineering information, this book is just a starting point. In-depth information can be obtained only from the EISA specification itself (at this time, over 430 pages of detailed and complex information). Note that EISA is not all that complex: the specification is just that complete.

### **Notation and Conventions**

In this book, some forms of notation may be new to you or may not be consistent with what you are accustomed to seeing. They are defined below.

• Signal names are shown in their active state. When a signal is active high, it is represented by its mnemonic name. When it is active low, its mnemonic name is followed by a tilde (~). (This technique allows the computer to sort the names properly on signal name lists.)

In addition, some signal names may differ from manufacturer to manufacturer. The signal names used here are provided in the EISA specification.

- Some signal lines are **slot specific**. The slot number is shown by a lower case x that, in some references, may be replaced by the number of the slot.

- A **bus name** is identified by its mnemonic name, followed by the range of bits the bus covers enclosed in angle brackets and separated by a colon. For example, D<15:8> covers the data lines from D15 to D8.

- **Program listings** are shown in a fixed-width typeface, and follow the conventions of the Microsoft Assembler.

- **Hexadecimal numbers** are shown with a lowercase letter **h** suffix. Any numbers without the **h** suffix are decimal values.

- Logic levels are represented as high (1) or low (0). Specific voltage level equivalents are a function of the source component and should be obtained from the manufacturer's specification sheet.

### The History of EISA

On September 13, 1988, a group of computer industry leaders announced that they had joined their engineering forces to create a major enhancement to the ISA (Industry Standard Architecture) bus. This group, a consortium of over 50 leading manufacturers, was led by a core of nine member companies: Hewlett-Packard, Compaq, Zenith, Wyse, Epson, AST, Olivetti, NEC, and Tandy. They called their concept the EISA (Extended Industry Standard Architecture) bus, and provided a full 32-bit enhancement for the 16-bit ISA standard as used in the AT-class computers. In part an answer to the announcement by IBM of their MCA (Micro Channel Architecture), the EISA bus standard was to provide an entirely different approach to the solutions required by the problems of the ISA bus. The ISA bus had served well, but the requirements of the industry, primarily data transfer rates between bus peripherals, could no longer be met by the ISA standard.

IBM's answer to the limitations of the ISA bus was the MCA bus, a complete redesigning of the bus to make it 32 bits, and a redesigning of the computer as a whole. The new IBM computers used the latest technology available at the time, from lowpower components to surface-mount components, to offer a series of desktop and deskside computers. A big disadvantage of the new MCA bus was the lack of accessories for the MCA-based machines, something that numbered in the thousands for the old ISA standard. The companies who announced the new EISA architecture took a very different approach. Their solution to the problem of bus throughput was also to expand the data bus to 32 bits, but they did it using a modified version of the ISA connector. Their modifications essentially added a second row of contacts above the ISA connection pins, and by putting in some blocks to keep the ISA cards from being inserted too far, they could accommodate all of the earlier ISA designs in addition to any of the new 32-bit cards to be provided by members of the consortium or outside vendors.

Among the many advantages cited by the consortium was that all of the expansion cards available at the time were still fully functional in the new computer design. This was often misunderstood, for many of those who questioned the standard thought that the motivation was that people could simply pull the cards out of their old computers and plug them into the new computer. Although this is indeed possible, it is an unlikely possibility. People usually pass on their computers whole to the next owner when they acquire a new computer. The real advantage of the EISA configuration is that, at the time the first EISA computers became available, over 1,000 already existing cards could plug right in and work. This provides complete functionality for any configuration that a user might want, using the components of today. It also provides the basis of an enhanced system using cards that take full advantage of the power of the 32-bit EISA bus. This includes features such as automatic configuration of the cards (no more DIP switches to set), and the power that comes with a 32-bit data bus, such as data transfer rates up to 33MB per second.

After the initial announcement in September, 1988, the industry began buzzing with rumors about the EISA bus, especially the connector. Many magazine articles were written about it, some of them claiming it would be an additional connector in front of the other two original connectors. Others claimed it would be an additional connector next to the original connector. The only ones who were not speculating were the actual engineers working on the connector, and they had something much better in mind. They were working with several connector manufacturers on a design that would provide all the signal lines required, but would require no additional insertion forces, no additional real estate on the mother board, and would provide an increase in reliability. In the end, the Burndy Corporation, a well-known and respected industry leader working with the mechanical engineers, came up with just the right combination of contact designs, connector molding, pin locations, and other factors that made the EISA bus what it is today. Other connector companies will be supplying the connector as well.

The EISA consortium was picking up momentum, and new companies were joining almost daily. In fact, as of this writing, the number of companies on the roster is over 200, and still growing. As each of the new companies joined, they received a copy of the EISA specification and access to any information they required to design computers, accessories, or software for the EISA system. As the specification was refined, updates were sent out to each of the member companies.

At the same time as the connector was being finalized, Intel was busy working on a chip set to complement the EISA bus. The result of their efforts is the 82350 EISA chip set, four integrated circuits that replace most of the components found in the IBM AT-style computers. The EISA chip set was designed to be compatible with both the 80486, the 80386, and the 30386SX CPUs. The 82350 EISA chip set uses CHMOS technology for low power operation and fully supports the ISA bus as well as the EISA bus.

Simultaneously with the development of the connector and the chip set, several of the companies, notably Hewlett-Packard and Compaq, were busy developing the DMA and interrupt concepts and the configuration software. The DMA and interrupt concepts that resulted provided speed and power that were undreamed of in the earlier ISA bus. The configuration software, a package that would eventually find its way into the hands of all developers, was designed to allow each manufacturer to customize it for a particular system. Both of the main software packages that were developed, one for configuring the computer's nonvolatile memory, and one for creating configuration files for accessories, required a great deal of cooperative interaction on the part of Hewlett-Packard and Compag. The result, however, is a software package that provides all the necessary functionality, and has been translated by the creating companies into a number of foreign languages for the markets in the rest of the world.

On October 10, 1989, Hewlett-Packard announced the first of the EISA computers. Significant in the announcement was not only the 25 MHz 80486 computer, but the fact that the H-P Apollo workstation division would also be using the EISA bus in some of its products. Other announcements followed, and the number of EISA computers keeps growing on a weekly basis.

The result of this historic cooperation is a computer system that is fully compatible among the different manufacturers. And because the specification is the result of cooperation among these companies, the EISA computers represent the best thinking of all these engineering departments, and a stability that comes from an agreement between the top engineering departments of companies who are truly concerned about the needs of their customers.

### **EISA Providers**

Through October 10, 1989, the following companies have publicly stated that they intend to provide EISA products. Of these, there are nine core members, often referred to as the "gang of nine," shown here in bold print. In addition to these companies, there are a number of additional companies (about 50) who prefer to have their names withheld until a future date.

| 3COM Corporation<br>ACC Microelectronics Corp.<br>Acer Technology<br>Adaptec, Inc. |

|------------------------------------------------------------------------------------|

| Adra Systems, Inc.                                                                 |

| Advanced Hardware                                                                  |

| Architecture                                                                       |

| American Megatrends, Inc.                                                          |

| Amp, Inc.                                                                          |

| Amstrad Plc                                                                        |

| Apollo Computer, Inc.                                                              |

| Arche Technologies Inc.                                                            |

| Arnet Controls, Inc.                                                               |

| ASEM S.P.A.                                                                        |

| Ashton Tate                                                                        |

AST Research, Inc. Atlas Computer Systems AT&T Computer Systems Austek Microsystems Autocomputer Co., Ltd. Autodesk, Inc. Banyan Systems Inc. Borland International Burndy Corporation Bustek Chase Research Limited Chicony Electronic Co., Ltd. Chips & Technologies, Inc. Cirrus Logic, Inc. Clone Computers

Codenoll Technology Corp. Communication Mach. Corp. Compag Computer Corp. **Computer Associates Micro** Products Computone Systems, Inc. **Compu-Shack Electronic** GmbH **Comtrol Corporation** Conner Peripherals, Inc. Control Systems, Inc. Cordata Technologies, Inc. Corollary, Inc. CSS Laboratories, Inc. **Datamedia** Corporation Datatronic **Digital Communication** Associates, Inc. Digital Equipment Corp. Digital Research, Inc. **Donatec** Company DPT DTK Computer, Inc. **Epson America**, Inc. Everex Systems, Inc. Excelan, Inc. **Future Domain Corporation** Hauppauge Computer Works Headland Technology Inc. **Hewlett-Packard Company** HMC Technology Ltd. **IMC** Networks Information Builders, Inc. Infotronic S.P.A. **Intel Corporation** Interactive Systems Corp. **Interphase** Corporation **IOMEGA** Itausa Informatica S/A

ITT Cannon I-Bus Kaypro Corporation Kayser Threde GmbH Kontron Electroniks Laguna Systems Laser Computer, Inc. Leukhardt Systems Lotus Development Lucid. Inc. Madge Networks Ltd. Matrox Electronic System Medidata Informatica S/A Methode Electronics, Inc. Micro Computer Systems, Inc. Micronics, Inc. Micronyx, Inc. Microsoft Corp. Miniscribe Mitac Molex. Inc. National Instruments National Semiconductor Corp. **NEC Information Systems,** Inc. Nixdorf Computer AG Nixdorf Computer Corp. Nokia Novell. Inc. Oak Technologies, Inc. Olivetti **Oracle** Corporation Parallax Computer Corp. PC Calc Ltd. Peter Norton Computing **Phoenix Technologies** Procomp USA, Inc. Proteon, Inc. Quantam Corporation

### **Summary**

As is obvious by the number and caliber of members, the EISA specification consortium is a powerful and committed force. Although their history is unusual in the level of cooperation that has been shown among otherwise competing companies, they have all made a commitment to the success of EISA, and with the computers announced so far from companies such as Hewlett-Packard and Compaq, that success appears assured.

## Inside the EISA Computer

$\mathbf{T}$ his chapter discusses the architecture of the EISA computer: the relationship of the CPU, RAM memory, ROM memory, I/O, and related concepts. It also discusses the function of the BIOS and how it relates to the computer hardware and the software such as the operating system and applications programs.

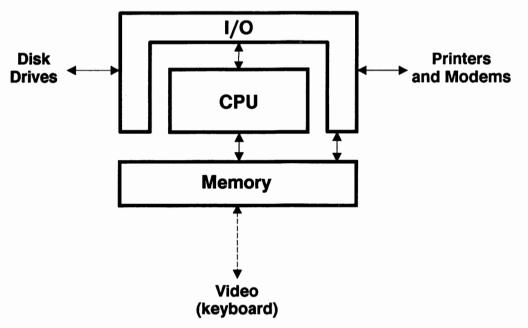

Figure 2-1 shows the structure of a typical computer in very general form. Note that it consists of only three parts: the CPU, the memory, and the I/O. The CPU, or Central Processing Unit, provides the "brains" of the computer. This may be an Intel 80486, a Motorola 68020, or one of many dozens of other processors. The memory stores programs and data while the computer is operating. When the power is turned off, most of the contents of this memory is lost. The I/O, or Input/Output functions, includes everything from the video display and keyboard interface to the operation of hard and floppy disk drives and the external ports for connecting printers, modems, and so forth.

The following paragraphs look at each of these areas in more depth. Although this discussion is geared towards the EISA com-

FIGURE 2-1 General Computer Architecture

puter, it applies equally to any of the PCs based on the Intel 8086, 80286, 80386, 80486, among others.

### **Central Processing Unit**

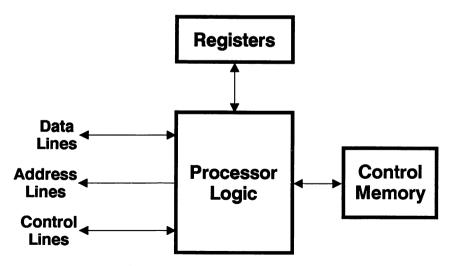

The CPU consists of a number of registers (places that store and manipulate data) and a lot of logic circuitry to control what happens and when. Figure 2-2 shows a simplified functional block diagram of a CPU. In this case the CPU has 16 data lines and 32 address lines coming out of it. This means that it can read or write two bytes  $(2 \times 8 \text{ bits})$  of data at a time and address  $2^{32}$  memory addresses. A number of control lines also come out that control what the address and data lines do and when they do it.

Before going any further, a little detour into the world of computer numbering schemes is in order. Computers are binary devices, which means that all numbers are represented by binary numbers. In order to understand many aspects of computer operation, you need to understand the binary and hexadecimal numbering systems.

FIGURE 2-2 General CPU Architecture

#### The Binary Numbering System

Binary numbers are represented by 1s and 0s. For example, a 0 in binary is a 0 in decimal numbers. A 1 in binary is a 1 in decimal numbers. But there the similarity ends. A decimal 2 is too big to be represented by either a 0 or a 1, so we need a second digit. Figure 2-3 shows the decimal-binary relationship for some small numbers. For example, a decimal 2 is written in binary as 10. This means there is one unit of 2 and no unit of 1. An examination of Figure

| Decimal<br>Number | Binary<br>Number |                                                                                   |                                      |

|-------------------|------------------|-----------------------------------------------------------------------------------|--------------------------------------|

| 0                 | 0                |                                                                                   |                                      |

| 1                 | 1                |                                                                                   |                                      |

| 2                 | 10               |                                                                                   |                                      |

| 2<br>3            | 11               |                                                                                   |                                      |

| 4                 | 100              |                                                                                   |                                      |

| 5                 | 101              |                                                                                   |                                      |

| 6                 | 110              |                                                                                   |                                      |

| 7                 | 111              |                                                                                   |                                      |

| 8                 | 1000             |                                                                                   |                                      |

| 9                 | 1001             |                                                                                   |                                      |

| 10                | 1010             |                                                                                   |                                      |

| 11                | 1011             |                                                                                   |                                      |

| 20                | 10100            |                                                                                   |                                      |

| 40                | 101000           |                                                                                   |                                      |

| 350               |                  | How<br>many<br>1's<br>2's<br>4's<br>8's<br>16's<br>32's<br>64's<br>128's<br>256's | FIGURE 2-3<br>Basic Binary Numbering |

2-3 shows how the binary numbering system expands to cover larger numbers.

Longer binary strings represent larger numbers. For example, Figure 2-4 shows an assortment of numbers that can be represented by 8 bits. As shown, 8 binary bits can represent decimal numbers from 0 to 255. Adding more bits increases the size of number that can be represented. Figure 2-4 also adds the leading 0s that are used in typical computer binary notation, thus showing a full byte.

#### The Hex Numbering System

Computers normally use a numbering system that is neither binary nor decimal. It is the hexadecimal numbering system, or hex, rep-

| Decimal<br>Number                                             | Binary<br>Number                                         |                                                                                          |

|---------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------|

| 0<br>14<br>40<br>80<br>100<br>127<br>128<br>200<br>250<br>255 | 00000000<br>00001110<br>00101000<br>01010000<br>01100100 | How<br>many<br>– 1's<br>– 2's<br>– 4's<br>– 3's<br>– 16's<br>– 32's<br>– 64's<br>– 128's |

FIGURE 2-4 Expanded Binary Numbering resented by the digits 0-9 and the letters A-F. Figure 2-5 shows the decimal and hex numbering systems with equivalents from 0 to 15 (0 to F hex) and some larger numbers that require two hex digits. Note that if you compare the hex numbers with their binary

| Decimal<br>Numbers | Hex<br>Numbers | Binary<br>Numbers |

|--------------------|----------------|-------------------|

| 0                  | 0              | 00000000          |

| 1                  | 1              | 00000001          |

| 2                  | 2              | 00000010          |

| 3                  | 3              | 00000011          |

| 4                  | 4              | 00000100          |

| 5                  | 5              | 00000101          |

| 6                  | 6              | 00000110          |

| 7                  | 7              | 00000111          |

| 8                  | 8              | 00001000          |

| 9                  | 9              | 00001001          |

| 10                 | Α              | 00001010          |

| 11                 | В              | 00001011          |

| 12                 | С              | 00001100          |

| 13                 | D              | 00001101          |

| 14                 | E              | 00001110          |

| 15                 | F              | 00001111          |

| 16                 | 10             | 00010000          |

| 17                 | 11             | 00010001          |

| 20                 | 14             | 00010100          |

| 40                 | 28             | 00101000          |

| 80                 | 50             | 01010000          |

| 100                | 64             | 01100100          |

| 127                | 7F             | 01111111          |

| 128                | 80             | 1000000           |

| 200                | C6             | 11001000          |

| 250                | <b>8</b> A     | 11111010          |

| 255                | FF             | 11111111          |

| 350                | 100            | 101011110         |

FIGURE 2-5 Basic Hex Numbering

equivalents, the larger digits are simply four binary digits per hex digit.

As with the binary and decimal numbering systems, larger numbers are represented with more digits. In EISA computers, data, addresses, and I/O locations are usually represented with the hex numbering system. It is common to encounter addresses like 0C32FBh, which equals 799483 decimal, or 11000011001011111011 binary.

### **Back to the CPU**

This detour into numbering is relevant since the CPU's addresses and data are all represented in the hex numbering system. You first need to master this system if you are planning to learn or understand the concepts of programming.

Next, you will need to understand the operating concepts behind the CPU. They are best understood by tracing the operation of a typical CPU when the power is first applied.

Once the power is applied to all the electronics, a reset signal is sent to the CPU. This reset signal is generated by an external source, either a digital pulse generator or some type of RC network. (An RC network is a resistor/capacitor network that causes a time delay.)

The CPU responds to the reset signal by clearing out all its registers and setting the address lines to a specific address. In the case of the 80486, this address is FFFFFF0h. (Here's where the hex numbering system is used. If you convert this to a binary number, you'll find that since each F equals 4 bits, the address bus contains 28 bits set to 1 and the last 4 set to 0.)

With the address lines set to a specific address, the CPU then reads the data lines to read in the data at that address. The typical EISA computer will have the first part of a boot routine at that address. As it reads the instruction at address FFFFFF0h and up, it is instructed to jump to another address in the ROM. The program that the computer needs to run in order to start will be at this new address. These routines usually set up the serial and parallel ports, test the memory, and determine the hardware configuration of the system. At this point, the CPU is instructed to read in the operating system software from a disk drive. Typically this will be from a hard drive, though the computer first checks to see if the floppy drive (usually drive A) contains a disk; if so, it boots from the floppy drive instead of the hard drive. This allows the user to boot a different version of the operating system than that which is on the hard disk, or to boot special operating systems or programs that contain their own operating systems. The EISA computers themselves are a good example, since many of them will boot up from a floppy disk during the initial setup procedure or at certain times when reconfiguring the system.

Once the system has booted up, the operating system, along with the programs and overlays called in by the CONFIG.SYS and AUTOEXEC.BAT files, determines the final configuration of the system. Let's now look at some of the other hardware aspects of an EISA computer system.

### **RAM and ROM**

RAM (Random Access Memory) is the main memory of the computer. As programs are run, they first load into RAM from the disk drive, and the operating system then "jumps" to the beginning of the program to begin executing the program. Program data, such as the data in a spreadsheet or the text of a word processor, also loads into the computer's RAM. As changes are made in the data, the contents of the RAM are altered, and when the user finishes with the application, the revised data is copied back to the disk drive.

ROM (Read Only Memory) is the part of memory where, normally, the BIOS of the computer resides. The BIOS is the interface between the computer's hardware and the operating system and applications software. ROM is a "read only" device; you can read program information from it but you cannot write to it under most circumstances.

The size of the RAM and ROM, and the locations of various components, is shown with a memory map. This is a table (or graphic) representation of the memory locations. Table 2-1 shows a memory map of a typical EISA computer system.

| Address           | Description                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00000000-0009FFFF | This area is the main system memory, and<br>consists of 640K of RAM. Some systems may<br>have only 512K, in which case their upper ad-<br>dress will be 0008FFFF instead of 0009FFFF. |

| 000A0000-000BFFFF | This 128K memory area is reserved for use by the video card.                                                                                                                          |

| 000C0000-000DFFFF | This 128K memory area is reserved for addi-<br>tional ROMs normally used to expand the sys-<br>tem's BIOS ROMs. This is usually a ROM on<br>an EGA card.                              |

| 000E0000-000FFFFF | This 128K memory area is reserved for option and BIOS ROMs.                                                                                                                           |

| 00100000-03FFFFFF | This area is the rest of addressable memory<br>up to 64MB. Some systems have the ability to<br>address only 32MB of RAM and will end at<br>address 01FFFFFF.                          |

TABLE 2-1

EISA Computer System Memory Map

The remainder of the system's memory map is dependent on the particular requirements of the individual manufacturers.

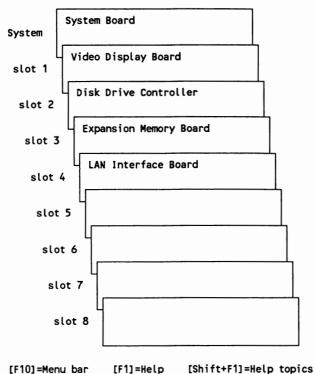

### I/0

I/O (Input/Output) is a mapped area similar to the memory map. Different addresses, or groups of addresses, are assigned to specific functions. However, the I/O map is much more extensive and complex, with different functions assigned to each of the addresses through 04FFh (1,280 addresses). If you need detailed information on the I/O map, you should obtain a copy of the EISA specification that details this information. A word of warning—this is technical engineering material and not casual reading for most people. Table 2-2 shows a summary of the I/O addresses.

| Address   | Description                                                                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|

| 0000-00FF | ISA main system board components.                                                                                             |

| 0100-03FF | ISA expansion cards.                                                                                                          |

| 0400-04FF | Reserved for main system board controllers.                                                                                   |

| 0800-08FF | Reserved for the system board.                                                                                                |

| 0C00-0CFF | Reserved for the system board.                                                                                                |

| 1000-1FFF | Dedicated to expansion slot 1.                                                                                                |

| 2000-2FFF | Dedicated to expansion slot 2.                                                                                                |

| 3000-3FFF | Dedicated to expansion slot 3.                                                                                                |

| 4000-4FFF | Dedicated to expansion slot 4.                                                                                                |

| 5000-5FFF | Dedicated to expansion slot 5.                                                                                                |

| 6000-6FFF | Dedicated to expansion slot 6.                                                                                                |

| 7000-7FFF | Dedicated to expansion slot 7.                                                                                                |

| 8000-8FFF | Dedicated to expansion slot 8.                                                                                                |

| 9000-FFFF | Continuation of the address range from 1000-8FFF for<br>additional expansion slots. Most EISA computers will<br>have 8 slots. |

TABLE 2-2

EISA Computer System I/O Map Summary

### **EISA Computer Hardware**

The EISA computers now coming on the market and those yet to be developed will come in a large variety of configurations. Models currently in development by a number of companies will sit on the desktop or at the deskside (on the floor). Both of these configurations offer nothing radically new in their packaging other than enhancements that the individual manufacturers may offer, such as the convenient front-panel power switches of the Hewlett-Packard versions. And in the not-too-distant future, it is possible that there will be portable models with an EISA slot or slots that will accommodate all of the new EISA boards soon to be announced.

The big difference between the current ISA computers and the new EISA computers will be the inside of the computers. They will contain a full complement of EISA connectors, and quite probably an Intel 80486 processor. Although the EISA bus is not restricted to a specific CPU, manufacturers are sure to continue to develop computers to the latest Intel CPU. One of the strengths of the EISA bus is its flexibility; it will be able to handle the processors of the future, in addition to the processors of today.

In fact, the only significant change will be the bus connector. Remember, one of the important advantages of the EISA bus it its ability to accommodate any of the over 1,000 cards currently available as well as cards yet to be developed.

#### The EISA Connector

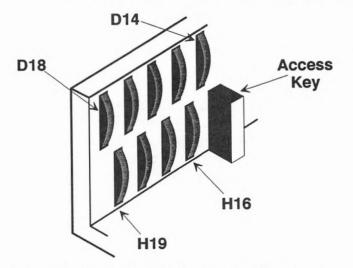

The connector is truly innovative: it is fully compatible with all of the old cards and is designed to absolutely prevent damage if an old card is plugged into the EISA bus connector. Figure 2-6 shows a cutaway section of the new style of connector and how the connector fingers are staggered.

When an EISA card is plugged into the connector, the card goes past the top row of contacts and into the lower row. As the lower row of contacts on the EISA card goes past the upper contacts

FIGURE 2-6 EISA Connector Finger Locations

in the connector, contact is not made since the connector contacts are centered between the connector fingers on the EISA card. As the card is pushed further into the connector, the lower row of contacts makes contact with the lower row of fingers on the card. At the same time, the upper row of contacts makes contact with the upper row of fingers on the card.

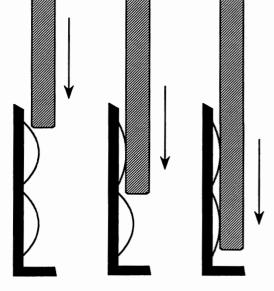

Insertion force, the difficulty of pushing the card into the connector, is not increased as a result of the additional number of contacts because most of the insertion force comes from pushing the connector contacts aside as the card is inserted, as shown in Figure 2-7. Once the contacts have been moved away to allow the board to slide in, the friction of the fingers is nominal. In fact, testing has shown that the insertion force is virtually the same for standard ISA connectors as it is for the standard EISA connector.

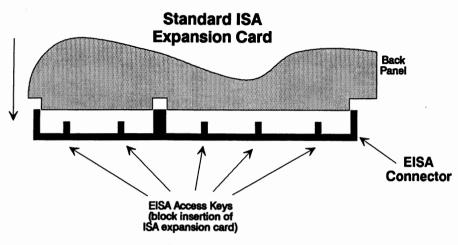

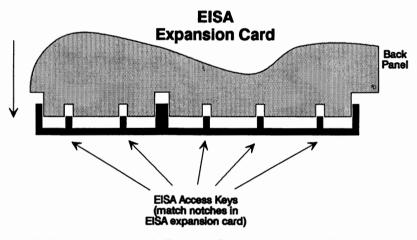

An ISA card cannot be pushed all the way into an EISA connector. As an ISA card is pushed into an EISA connector, small access keys prevent the card from being pushed further into the connector than is necessary, as shown in Figure 2-8. EISA cards can be pushed all the way in since the card is notched to allow it to get past the access keys, as shown in Figure 2-9.

FIGURE 2-7 EISA Connector Finger Contacts

FIGURE 2-8 EISA Connector ISA Card Blocks

FIGURE 2-9 EISA Board Connector Notching

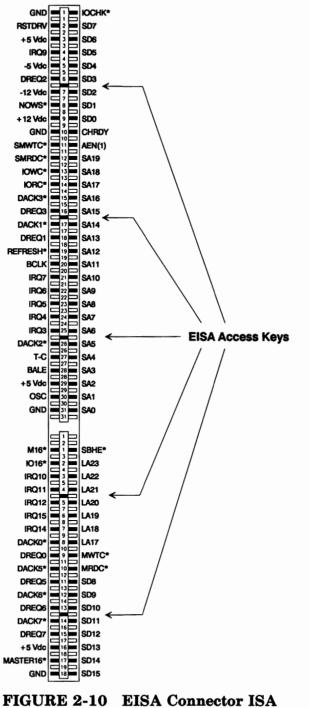

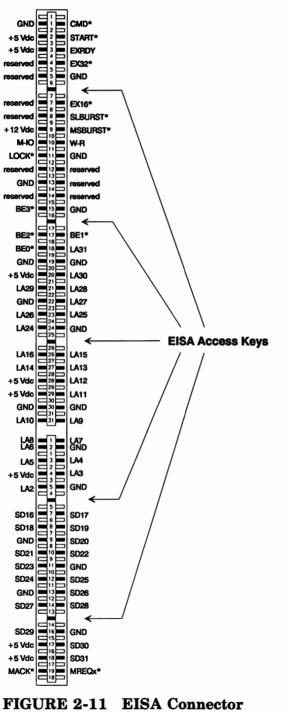

Figure 2-10 shows the signals appearing on the connector for an ISA card as dark pins that make up the upper row of connections on the connector. Note that the upper row of connector fingers is numbered exactly the same as the old ISA standard. Figure 2-11 shows the signals appearing on the connector for an EISA card as dark pins that make up the lower row of connections on the connector. Chapter 4, *The EISA Bus*, contains a complete discussion of the signals on the connector.

Beyond the new connectors there are few surprises in the new EISA computers. For example, some of the EISA computers will have the video circuitry, such as an EGA or VGA interface, built into the computer and others will have the video circuitry on a plug-in card. Some of the EISA computers will have one or two serial ports and one or two parallel ports built into the computer.

#### Card Size

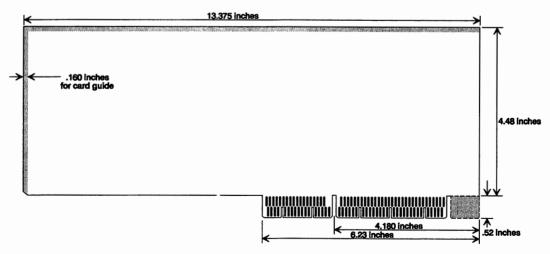

Due to the freedom of defining a new standard, the EISA standard allows some fairly large cards to be plugged into the system. As shown in Figure 2-12, the area available for mounting components on the card measures 4.50 by 13.21 inches, which makes over 59 square inches of board area that can contain components. In addition, because of the advances made in a technology called SMT, or surface-mount technology (as opposed to the conventional method called through-hole mounting), components can now be mounted on both sides of the card. The EISA specification allows 0.525 inches on one side of the board (the side where components are normally mounted) and 0.150 inches on what is now called the solder side of the board. This 0.150 allows room for most of the surface-mount components, such as integrated circuits, capacitors,

FIGURE 2-12 EISA Expansion Card Dimensions

and resistors, to be mounted. This yields a total usable board area of almost 120 square inches in a single card.

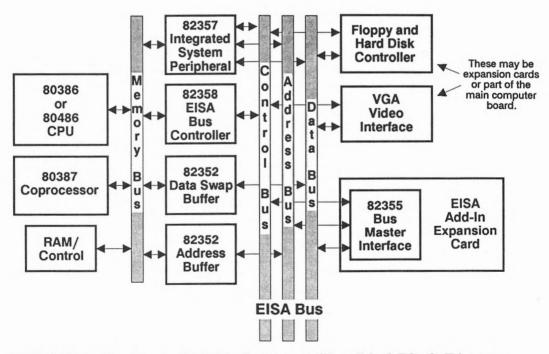

#### The EISA Component Interface

So far we've looked only at the architecture of a typical computer and at the EISA card and connector. The EISA hardware interface, a set of chips designed by Intel for the EISA computer bus, ties these together. This interface is called the 82350 EISA Chip Set and consists of an 82358 EISA Bus Controller, an 82357 Integrated System Peripheral, an 82352 EISA Bus Buffer, and an 82355 Bus Master Interface Controller. Figure 2-13 shows a functional block diagram of a typical EISA computer using the Intel 82350 chip set.

As shown in Figure 2-13, the CPU of most of the EISA computers will be either an 80386 or 80486. If the 80386 processor is used, a socket will normally be provided for the addition of a coprocessor such as the 80387. If an 80486 processor is used, the

FIGURE 2-13 Typical EISA Computer Simplified Block Diagram

coprocessor socket is not required since the coprocessor is built into the processor. The functionality of each of the Intel chips is covered in more detail in the following sections.

#### 82358 EISA Bus Controller

The EISA bus controller is the main component of all EISA systems. It provides an interface between the CPU and the EISA bus and an interface among the different buses of the EISA system. It provides translations among the cycles of the CPU, the ISA cards, the EISA cards, and generates ISA signals where necessary for the EISA bus masters. It provides an interface among multiple bus masters, and provides the timing functions that allow communications among the different buses. It provides EISA/ISA bus cycle compatibility in the EISA/ISA standard memory or I/O cycle, the EISA burst cycles. It also provides control signals for the address buffers.

#### 82357 Integrated System Peripheral

The integrated system peripheral chip works with the EISA bus controller to provide the system functions required in EISA applications. Most of these functions are similar to existing functions provided by a large number of components on existing systems, plus the addition of EISA-specific functions. These functions include a 7-channel DMA controller with full timing control for 8-, 16-, and 32-bit DMA transfers with up to 33MB per second data transfer rate, a bus arbitrator for bus sharing among multiple masters, a 15-level interrupt controller with the functionality of two 8259 controllers, refresh address generation and control functions, and five 16-bit counter/timers (8254 compatible) for interrupts and bus time-outs, DMA refresh requests, and other timing requirements.

#### 82352 EISA Bus Buffer

The EISA bus buffer operates in three modes for use as data swap buffer logic, address buffers, and data parity buffers. It combines the functions typically provided by up to 17 separate components in previous designs, reducing the chip count, board complexity, and design complexity. By reducing the chip count, radio frequency interference generated by computer signals is reduced.

#### 82355 Bus Master Interface Controller

The bus master interface controller is often located on each of the EISA add-in cards. It provides an interface among the functions of the add-in card and the address, data, and control lines of the EISA bus. It includes full support of burst mode for data transfer rates up to 33MB per second, and a 32-bit address bus which allows addressing 4GB as provided in the EISA specification. It also supports the EISA automatic configuration functions. There are two data transfer channels, which allows the processor to set up one data transfer while another is currently being performed.

### Summary

The basic architecture of the EISA computers differs little from the ISA computers that have gained acceptance and familiarity over the past decade. The improvements are in the EISA bus connector, the new EISA chip set, and the software that is discussed in later chapters.

# The Operating System

This chapter covers the operating system of a typical EISA computer. Although there are a number of operating systems that will no doubt be used, among them DOS 3.3, OS/2, and UNIX, DOS 4 will be by far the most common. DOS 4 has the advantage of requiring less memory than operating systems such as OS/2 or UNIX, and it costs significantly less than either. Users requiring multitasking capability are likely to turn to additional programs such as Quarterdeck's Desqview or Microsoft's Windows running under DOS 4. Both provide excellent solutions to multitasking requirements, and each is best suited to specific applications.

In order to understand the operation and concepts of the operating system, we first need to look at the organization and structure of all the different types of software in the system.

# **Software Architecture**

There are two structures in a personal computer, the software structure and the hardware structure. Chapter 2, *Inside the Computer*, discusses the hardware aspects of the computer and this chapter discusses the software structure.

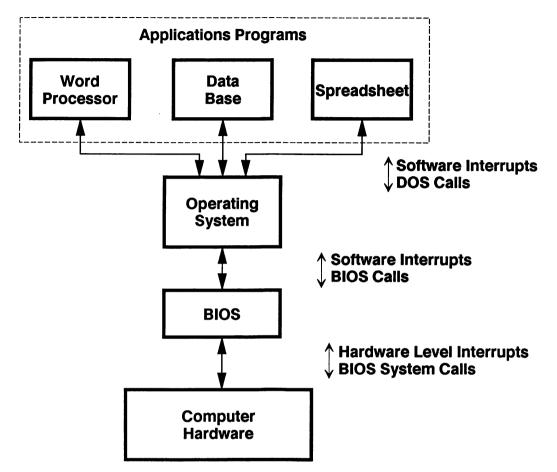

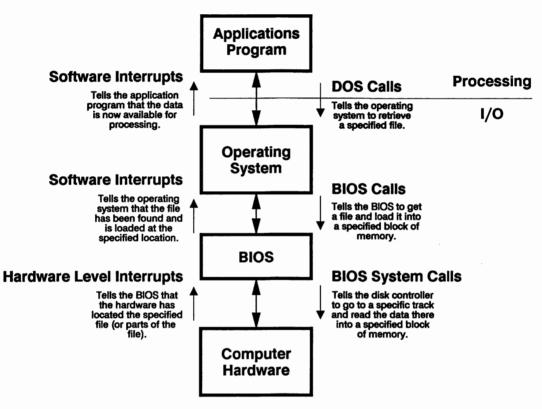

Figure 3-1 shows the general relationship of the three functional areas of software in the computer. You are probably most familiar with the application programs. These are the programs you use to perform work on the computer, and might be anything from a word processing program, a database program, a spreadsheet program, a drawing or graphics program, to a game. These programs are the only kind that most computer users ever know or care about. An application program interface consists of its information on the screen and the keystrokes and mouse movements required to use the program. However, two other levels of software are also being run, and they are very important.

The next level down from the application program is the operating system (in this case, DOS). DOS accepts the commands from the keyboard or from the application software and causes things to happen, such as saving a file on disk or displaying the information on the screen. The third level is the BIOS (Basic Input/Output System). This software contains the hardware-specific instructions that tell DOS how to perform the requested task.

#### FIGURE 3-1 Software Structure

Communication among the various software entities takes place through program structures called "calls" and "interrupts." Figure 3-1 shows the communications paths among the various software system entities.

Each of the pieces shown in Figure 3-1 is seen in more detail in Figure 3-2.

#### **BIOS**

The BIOS software (often called firmware since it is not normally accessible or alterable) resides in a ROM (Read Only Memory).

FIGURE 3-2 Software Structure Interface

The function of the BIOS is to provide an interface between the hardware and the software. In a sense, it translates the software commands and requirements into hardware commands. The BIOS is provided by the computer manufacturer and contains information that is particular to the specific hardware. In addition to this ROM BIOS, additional cards that plug into the computer may include BIOS extensions (additional software pertaining to those specific cards). Usually these would be cards such as a hard disk controller or an EGA card.

Using the example of a parallel printer output port, we will look at this in more detail. The component that interfaces the computer processor to the outside world has eight data lines that are connected to the data bus of the computer. In addition, there are other lines connected to the address lines and some of the control lines. When the control lines and address lines (under control of the microprocessor) tell the parallel interface to send a character out to the printer, the parallel interface looks at the data bus, gets the data, and sends it out to the printer. The instructions that tell the parallel interface to do this are contained in the ROM BIOS. Typically, these instructions are received from the operating system through BIOS calls. After completing the task, the BIOS responds through a software interrupt. An example of this technique is given in Chapter 9, *The Parallel Interface*.

The computer hardware accesses the BIOS through a scheme called hardware interrupts. When a signal comes in through one of the hardware interfaces (for example from the keyboard, a serial port, or a parallel port), it causes one of the hardware signal lines to change state. This change in state is called a hardware interrupt, and the system microprocessor responds to this interrupt as follows:

- 1. The interrupt causes the system microprocessor to pause and determine where the interrupt is coming from.

- 2. The system microprocessor then, through what is referred to as a system call, determines what the hardware wants. Usually, the hardware has a byte of information and wants the system microprocessor to accept it and do something with it, such as place it in memory.

- 3. The system microprocessor reads the byte of data, and sends it wherever it should go. The system microprocessor then returns to the previous task in progress before the interrupt occurred.

The ROM BIOS also provides a number of functions other than hardware interface and definition. When the computer is initially turned on (or reset), the CPU goes to the BIOS for operating instructions. The BIOS first verifies the proper operation of the system. This process, called a power-on test, provides a quick test of the computer's memory. Depending on the extent of the test and the amount of memory in the system, this process can take up to several minutes, though the typical test takes about 10 seconds. After the RAM is tested, the BIOS verifies a part of memory called CMOS RAM. This is a special block of memory where the system configuration is stored. CMOS RAM is normally kept "alive" with a battery in the computer and is not lost when power is removed from the computer. Next, the BIOS determines what equipment is in the system. This information is contained in the CMOS RAM, and includes small programs which may need to be run to initialize some of the accessory cards plugged into the system.

After the testing and initializing is complete, the BIOS attempts to load the operating system from one of the disk drives. Normally, this is from a hard disk assigned as drive C, though it can be from any other hard disk or even from a floppy disk. Once the operating system is loaded in, the BIOS "jumps" to the operating system and the DOS prompt appears on the screen. The system is now ready to run programs.

#### **Operating** System

The middle level of software is the operating system, in this example MS-DOS 4.0, also called DOS. One of the functions of DOS is to provide a basic level of commands that allow the user to:

- examine information, such as displaying the directory of a disk (DIR)

- request file management functions, such as erasing some of the files (ERASE or DEL), or copying a file from one location (drive or subdirectory) to another (COPY).

The operating system also provides a standard software interface that can be accessed by application software.

The interface between DOS and the BIOS is handled through a standard set of software interrupts and BIOS calls. When the operating system wants a function performed, such as writing a file to disk, it first loads certain registers with information about the file, such as where it is and how big it is. It then jumps to a routine in the BIOS to read the registers and write the file to disk.

#### **Application Software**

Application software is the final level in the software structure. It includes applications like word processing and spreadsheet programs, as well as utilities such as the configuration program that all EISA computers use to initially set up the computer and later make changes to the system configuration. In addition to these programs, a large number of utility programs are provided with DOS and from other sources. These utility programs do things like display the directory in different formats, back up the hard disk, or alter display characteristics.

Virtually all of the processing takes place through application software. For every instruction sent to the operating system or BIOS, hundreds are used within the application program to calculate what should be done. For example, if you are running a spreadsheet program and the program recalculates some of the cells, it is the spreadsheet program that is doing all the work. The only time the processor goes out to the operating system (or sometimes directly to the BIOS) is when it is actually updating the video screen.

### **DOS 4 Overview**

This section describes the DOS 4 operating system in greater detail. DOS 4 is similar to DOS 3.3 in many areas, enough so that a person familiar with DOS 3.3 will not need to learn anything new to be both comfortable and productive. However, DOS 4 does add some nice features. For example:

- Hard disks greater than 32MB are supported without partitioning. For example, this means that you can have a hard disk of 150MB partitioned as drive C with 30MB and drive D with 120MB. Also, because of the expansion of the 16-bit logical sector numbers to 32-bit size, DOS 4 can handle disk sizes of up to 2GB (2000MB).

- DOS 4 provides an optional shell program that operates in a menu style. For many users, the DOS command line is difficult to use, and they prefer an icon or menu type user interface. Now users have a choice between a menu, a command line, or both.

- The Expanded Memory Specification (EMS) written to the Lotus/Intel/Microsoft (LIM 4.0) standard is fully sup-

ported by DOS 4. This means the computer will easily handle much more memory, (depending on the implementation, from 4MB to 64MB of additional memory). The INT 67H interface, defined by the LIM 4.0 specification, provides access to the memory. This maximizes compatibility with existing products designed for compatibility with LIM 4.0 specification. The LIM 4.0 emulator is provided with the file memm.sys.

- Installation of the DOS 4.0 operating system is performed through a menu-style interface, the **select** program, making installation easier for the novice user.

- The video support has been improved to allow the printing of graphics screens and displaying more lines of text.

- Many of the programs (commands) that come with DOS have been enhanced.

#### **DOS 4 File Structures**

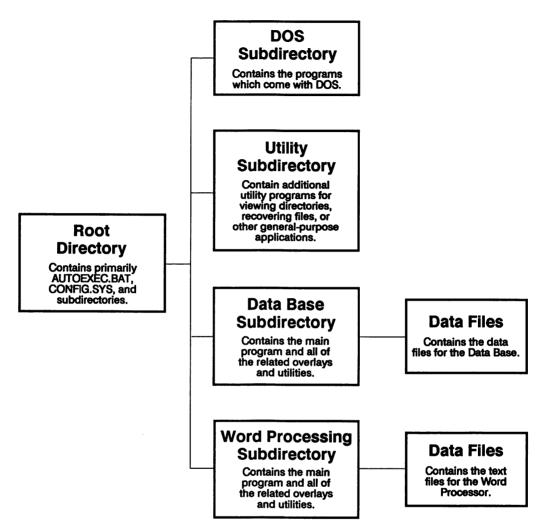

Files, and the way they are stored on disk, are often compared to a row of filing cabinets containing a number of drawers, each drawer containing a number of folders, and each folder containing a number of documents. Although this comparison can be confusing, it effectively shows how DOS starts with a single undivided storage area (the root directory), and expands by adding subdirectories. Figure 3-3 shows the organization of a possible system.

The files begin at the left with the root directory. This is usually the point where all the directories are located and, typically, very few files are stored here.

Usually, each of the directories is dedicated to a particular function, such as all the EISA files, or word processing, or a spreadsheet, or games. Going into the directory for games, for example, you might find chess, checkers, and poker. In fact, the games directory could contain subdirectories that contain different versions of chess games or poker games.

#### **DOS 4 Enhancements**

DOS is an evolutionary operating system. It has come from its original version (nominally 1.0) to its present version of 4.01. There

FIGURE 3-3 File Organization

will, no doubt, be another version of DOS to succeed version 4, probably version 5. There are also variations on the theme, such as Presentation Manager, OS/2, and Windows. However, this book will concern itself with DOS version 4 and comparison with its popular predecessor, DOS 3.3. The following sections discuss the benefits of the new version of DOS, and discuss in general terms the command set of DOS 4. A complete discussion of DOS 4 is

beyond the scope of this book, and I recommend you obtain a copy of *Expert Advisor: DOS* by Jonathan Kamin (Addison-Wesley, 1989). However, a summary of the commands is presented here along with the enhancements in DOS 4.

The **select** command provides an enhanced installation program that makes installation and system configuration simple. It also creates the required *config.sys* and *autoexec.bat* files. Using **select**, the user can install DOS 4 either on an existing system using an earlier version of DOS, or on a new system with an empty formatted disk.

The **mem** command is new and provides complete information on the memory being used, how it is configured, and what programs are loaded.

The **tree** command is more graphical, making the structure of the disk easier to understand.

The **del** command can be told to display a prompt before it deletes a file.

Graphics support is provided for EGA and VGA displays, and the graphics support also includes a number of printers for screen dumps. Video support in DOS 4 covers everything from the original monochrome and CGA modes to the VGA modes. **cls**, **dir**, **more**, **edlin**, **con** and *ansi.sys* are now sensitive to the video mode and will display properly according to the current screen length. In addition, **graphics** has been extended to support the graphics modes for the EGA and VGA display.

A number of other commands have been enhanced to provide additional functions. Most of these enhancements provide compatibility with the new video displays and the larger hard disk formats.

Certain manufacturers, such as Hewlett-Packard and Compaq, have provided additional features that apply primarily to their own machines. These include features like disk caching (allows the computer to get to frequently accessed files faster) and more advanced and sophisticated memory management (allowing the use of RAM as a disk drive, or the use of larger amounts of memory, ranging from 1 to 64MB).

#### **DOS 4 Commands and Programs**

DOS 4 provides a number of commands that are used for manipulating files, data, and system configuration. These commands are in two formats, programs that reside on the disk and are loaded and executed every time they are used, and commands which are a part of DOS and reside in the operating system when it is loaded in memory. In the following descriptions the term "command" will refer to memory resident (DOS) commands and the term "program" will refer to programs which, though a part of DOS, reside on a disk and are loaded each time they are used.

This is not a complete description of the commands, but rather a summary of the commands highlighting the elements that are new for DOS 4. Refer to the documentation that came with DOS 4 for a complete description of the commands.

| <b>append</b> program | Allows the user to define the search path<br>for data files. This is often used with word<br>processing, database, and spreadsheet pro-<br>grams to tell programs where to search for<br>data files, much like the <b>path</b> command<br>defines where to look for executable files.<br>Also see the <b>path</b> command for a similar<br>function. |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>assign</b> program | Reassigns the disk requests. For example,<br>when a program has been told to look for<br>files on drive C:, the <b>assign</b> command can<br>make the computer look for the files on<br>drive A: instead.                                                                                                                                            |

| <b>attrib</b> program | Changes the status of the archive and<br>read-only status bits for a file or group of<br>files. This is often used with batch-type<br>backup programs or when write-protect-<br>ing or hiding files.                                                                                                                                                 |

| backup program        | Allows the user to make a backup copy of<br>files. Typically this command is used to<br>back up files from a hard disk to floppy<br>disks for archiving in the event of a hard<br>disk failure. Also see the program <b>restore</b><br>for a complementary function. In the DOS<br>4 version of <b>backup</b> , the program will de-<br>fault to the /f switch mode (formats the<br>destination floppy disk). Also, the DOS 4<br>version allows the user to place the<br><i>backup.log</i> file on the target drive. |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| break command         | Makes Ctrl-Break and Ctrl-C operate at<br>all times, rather than just during keyboard,<br>video, and printer input/output opera-<br>tions.                                                                                                                                                                                                                                                                                                                                                                           |

| cd or chdir           | Allows the user to move around between                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| command               | the different directories on a drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>chkdsk</b> program | Tests the condition of a disk or files on a<br>disk. If any files, or the disk itself, are<br>found to have a problem, it is reported.<br>Note that this is not a complete disk<br>check, though it provides a reliable check<br>of the integrity of the files and directory<br>on the disk.                                                                                                                                                                                                                         |

| comp program          | Compares two files and displays the dif-<br>ferences between the files. <b>comp</b> is nor-<br>mally only used to compare executable<br>files and not data. Also see the <b>fc</b> program<br>for a similar function.                                                                                                                                                                                                                                                                                                |

| copy command          | Copies from one disk (source) to another (destination). Also see the program $\mathbf{xcopy}$ for a similar but more enhanced function.                                                                                                                                                                                                                                                                                                                                                                              |

| ctty command          | Allows the user to change the console from<br>the normal keyboard and display to an-<br>other I/O device. This is often used to al-<br>low the computer to be run from another<br>location over a modem connected to one<br>of the serial ports.                                                                                                                                                                                                                                                                     |

| date command            | Allows the user to display or change the date information in the computer. Also see the <b>time</b> command for a similar function.                                                                                                                                                                                                                                                                            |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>debug</b> program    | Included with DOS 4 from most manu-<br>facturers. It is a debugging/programming<br>tool normally used by programmers for<br>testing new applications programs, though<br>it can be used for many other jobs, such<br>as patching programs or examining files<br>for format. The DOS 4 version of <b>debug</b><br>has been enhanced to support expanded<br>memory with four new commands, XA,<br>XD, XM and XS. |